# A reduced complexity parallel least mean square algorithm for adaptive beamforming

Ghattas Akkad

### ▶ To cite this version:

Ghattas Akkad. A reduced complexity parallel least mean square algorithm for adaptive beamforming. Electronics. ENSTA Bretagne - École nationale supérieure de techniques avancées Bretagne, 2020. English. NNT: 2020ENTA0005 . tel-03368386

### HAL Id: tel-03368386 https://theses.hal.science/tel-03368386v1

Submitted on 6 Oct 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

**ENSTA Bretagne**

Comue Université Bretagne Loire

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : (voir liste des spécialités)

Par

## **Ghattas AKKAD**

### A Reduced Complexity Parallel Least Mean Square Algorithm for **Adaptive Beamforming**

Thèse présentée et soutenue à Brest, le 7 Decembre 2020 Unité de recherche: Lab-STICC, UMR 6285

Thèse No:

#### Rapporteurs avant soutenance :

Karim ABED-MERAIM Professor à l'Université d'Orléans Nadège THIRION-MOREAU Professor à l'Université de Toulon

### **Composition du Jury:**

Président : Christian JUTTEN Professor à l'Université Grenoble Alpés

Examinateur: Emanuel RADOI Professor à l'Université Bretagne Occidentale

Dir. de thèse : Ali MANSOUR Professor à l'ENSTA Bretagne

Co-dir. de thèse : Bachar ELHASSAN Professor à l'Univérsité Libanaise

Invité(s):

Professor à l'École Nationale d'Ingénieurs de Brest Stephane AZZOU Elie INATY Associate Professor à l'Université du Balamand

Benoit ZERR Professor à l'ENSTA Bretagne

# **ACKNOWLEDGEMENT**

First and foremost I would like to express my deepest gratitude for my thesis supervisor Professor Ali MANSOUR, for without his unending guidance, mentoring, support, and warm hospitality this work would have never come to light. I would like to also thank my thesis co-supervisor Professor Bachar ELHASSAN for the similar and for his continuous encouragment.

Second, I would like to thank the jury committee president Professor Christian JUT-TEN and the committee members: Professor Karim ABED-MERIAM, Professor Stephane AZZOU, Associate Professor Elie INATY, Professor Emanuel RADOI, Professor Nadège THIRION-MOREAU and Professor Benoit ZERR. It is an honor to have my work examined and assessed by professional experts such as yourselves.

Third, I am grateful to AID - DGA (l'Agence de l'Innovation de Defense - Direction Générale de l'Armement – Ministére des Armées) & ANR (Agence Nationale de la Recherche en France) for supporting our ANR-ASTRID – Project (ANR-19-ASTR-0005-03).

Moreover, I would like to heartily thank my mentors, colleagues and best friends at the University of Balamand (UOB) and in Lebanon: Associate Professor Rafic AYOUBI, Engineer Nayla Greige BALESH, Engineer Nassif DAOUD, Associate Professor Nabil KARAMI and Assistant Professor Mohamad NAJEM. A special thank you for UOB's Vice President and Dean of the Faculty of Engineering (FOE) Professor Rami ABBOUD for his encouragement and support. Indeed your hard work and dedication toward the advancement of the UOB and the FOE, despite all the unaccounted for challenges, is inspiring and motivational. Eventhought I did not get the chance to work with you, I am, without a single doubt, definite that the FOE will thrive under your guidance and supervision.

Additionally, I would like to thank the previous Vice President and previous Dean of the UOB Faculty of Engineering Professor Michel NAJJAR for his limitless support. It has been an honour and a privilege to have studied and worked in a university and a faculty that you have devoted your life to build. It is with your effort and dedication that it has reached its international exposure and distinguished reputation. It has become a second home for the many and has taught us that home is not made of bricks and stones but where the heart and mind belongs.

I would like to, also, express my unending and immeasurable appreciation and gratitude for Mrs Mimo NAKAD, my eternal best friend and my source of boundless motivation. She is an enthusiastic, dedicated and wholehearted person, a true star. From her I learned that, quoting Gibran Khalil Gibran, "You give but little when you give of your possessions. It is when you give of yourself that you truly give".

Finally, I would like to thank my mother Mirana Abed AKKAD, my father Michel AKKAD, my aunt Kety Akkad SAWAYA, my sister Mariam AKKAD and my brothers Charbel and Roufaeil AKKAD, for without them I am nothing.

# TABLE OF CONTENTS

| A             | cknov                  | wledge  | ment                                 | 4  |

|---------------|------------------------|---------|--------------------------------------|----|

| Ta            | able (                 | of Con  | tents                                | 5  |

| $\mathbf{Li}$ | $\operatorname{st}$ of | Figure  | es                                   | 9  |

| Li            | $\operatorname{st}$ of | Table   | 5                                    | 13 |

| N             | omer                   | ıclatur | re                                   | 15 |

| 1             | Ada                    | ptive   | Beamforming: A History               | 27 |

|               | 1.1                    | Signal  | Processing in Wireless Communication | 29 |

|               |                        | 1.1.1   | Adaptive Beamforming                 | 30 |

|               | 1.2                    | Our R   | desearch Project                     | 31 |

|               |                        | 1.2.1   | Motivation                           | 32 |

|               |                        | 1.2.2   | Outlines                             | 33 |

| 2             | Fun                    | damer   | ntals of Antenna Array Beamforming   | 37 |

|               | 2.1                    | Introd  | luction                              | 37 |

|               | 2.2                    | Anten   | na Array Architecture                | 38 |

|               |                        | 2.2.1   | Linear Array                         | 39 |

|               |                        | 2.2.2   | Circular Array                       | 44 |

|               |                        | 2.2.3   | Planar Array                         | 45 |

|               | 2.3                    | Spatia  | l Filtering and Beamforming          | 46 |

|               |                        | 2.3.1   | Beam Steering                        | 46 |

|               | 2.4                    | Concl   | usion                                | 49 |

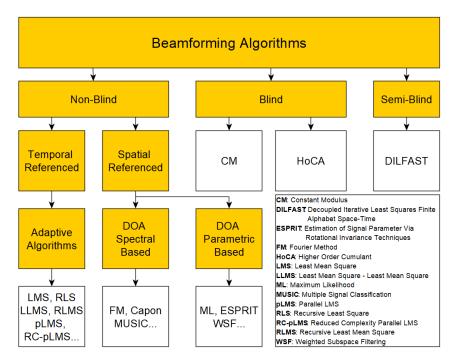

| 3 | Ove | erview | of Adaptive Beamforming Algorithms                            | 51 |

|---|-----|--------|---------------------------------------------------------------|----|

|   | 3.1 | Introd | luction                                                       | 51 |

|   | 3.2 | Adapt  | cive Beamforming                                              | 51 |

|   |     | 3.2.1  | Non-Blind based Beamforming                                   | 52 |

|   |     | 3.2.2  | Blind Based Beamforming                                       | 54 |

|   |     | 3.2.3  | Semi-Blind based Beamforming                                  | 55 |

|   | 3.3 | Adapt  | ive Algorithms                                                | 55 |

|   |     | 3.3.1  | MVDR Algorithm for Beamforming                                | 56 |

|   |     | 3.3.2  | Least-Mean Square (LMS) Algorithm                             | 57 |

|   |     | 3.3.3  | Recursive Least-Square (RLS) Algorithm                        | 60 |

|   |     | 3.3.4  | RLMS Adaptive Beamformer                                      | 61 |

|   |     | 3.3.5  | Parallel RLMS Adaptive Beamformer                             | 63 |

|   |     | 3.3.6  | LLMS Adaptive Beamformer                                      | 64 |

|   |     | 3.3.7  | Comparison and Discussion                                     | 66 |

|   | 3.4 | Concl  | usion                                                         | 69 |

| 4 | Ove | erview | of Digital Signal Processing Implementation Techniques on     | L  |

|   | Em  | bedded | d Systems                                                     | 71 |

|   | 4.1 | Introd | luction                                                       | 71 |

|   | 4.2 | Embe   | dded Systems for Digital Signal Processing (DSP) Applications | 73 |

|   |     | 4.2.1  | Programmable DSP Processors (PDSP)                            | 74 |

|   |     | 4.2.2  | Field Programmable Gate Arrays (FPGA) Processors              | 75 |

|   |     | 4.2.3  | System on Chip (SoC) Processors                               | 78 |

|   | 4.3 | Hetero | ogeneous Systems Design Techniques                            | 79 |

|   |     | 4.3.1  | High Level Synthesis (HLS) Design                             | 80 |

|   | 4.4 | FFT a  | and The Dynamic Twiddle Factor Generator                      | 81 |

|   |     | 4.4.1  | Twiddle Factor Generator Using Chebyshev Polynomials          | 83 |

|   |     | 4.4.2  | Computer Simulations                                          | 85 |

|   | 4.5 | Hardy  | ware Implementation and Comparison                            | 87 |

|   |     | 4.5.1  | Fast Fourier Transform (FFT) Design Using HDL                 | 87 |

|   |     | 4.5.2  | Fast Fourier Transform (FFT) Design Using HLS                 | 89 |

|   |              | 4.5.3  | Twiddle Factor Generation Using Chebyshev Polynomials in HDL $$ . | 90 |

|---|--------------|--------|-------------------------------------------------------------------|----|

|   |              | 4.5.4  | Delay Relaxed Look-Ahead LMS                                      | 93 |

|   | 4.6          | Conclu | usion                                                             | 98 |

| 5 | $Th\epsilon$ | Paral  | lel LMS and it's Pipeline Hardware Implementation                 | 99 |

|   | 5.1          | Introd | uction                                                            | 99 |

|   | 5.2          | Multi  | Stage Parallel LMS (pLMS) Algorithm                               | 00 |

|   |              | 5.2.1  | Theoretical Stability Analysis                                    | 03 |

|   |              | 5.2.2  | First LMS Stage                                                   | 03 |

|   |              | 5.2.3  | Transfer Function Approximation                                   | 06 |

|   | 5.3          | pLMS   | Pipeline Hardware Implementation                                  | 07 |

|   |              | 5.3.1  | Delay and Sum Relaxed Look Ahead pLMS                             | 07 |

|   |              | 5.3.2  | DpLMS Hardware Architecture                                       | 09 |

|   |              | 5.3.3  | Implementation and Synthesis Results                              | 10 |

|   | 5.4          | Hardw  | vare and Software Simulations                                     | 11 |

|   |              | 5.4.1  | Mean Square Error Convergence Analysis                            | 12 |

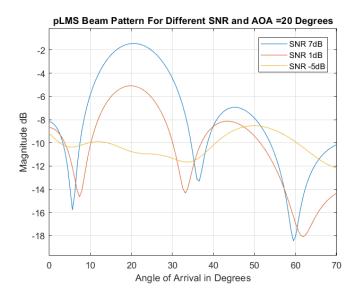

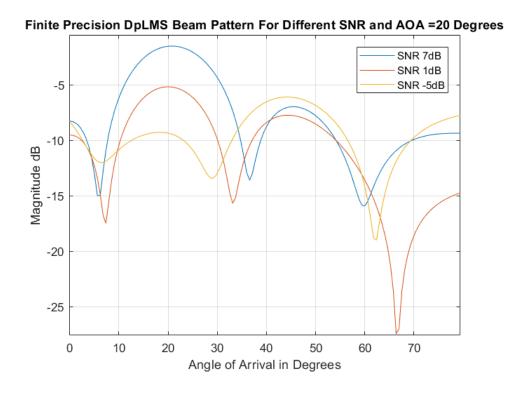

|   |              | 5.4.2  | Beam Radiation Pattern                                            | 15 |

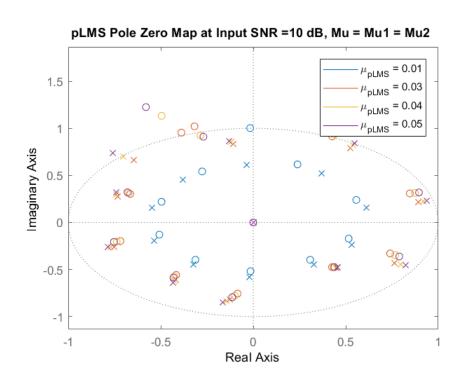

|   |              | 5.4.3  | Pole Zero Map Stability Plot                                      | 17 |

|   |              | 5.4.4  | Computational Complexity Comparison                               | 18 |

|   | 5.5          | Conclu | usion                                                             | 19 |

| 6 | The          | Redu   | ced Complexity Parallel LMS and its Pipeline Hardware Im-         |    |

|   | pler         | nentat | ion 1                                                             | 21 |

|   | 6.1          | Introd | uction                                                            | 21 |

|   | 6.2          | Reduc  | ed Complexity Multi Stage Parallel LMS (RC-pLMS) Algorithm $$ 1   | 22 |

|   |              | 6.2.1  | Stability Analysis                                                | 26 |

|   |              | 6.2.2  | Transfer Function Approximation                                   | 28 |

|   |              | 6.2.3  | Quantization Effect Analysis                                      | 28 |

|   | 6.3          | DRC-   | pLMS Pipelined Hardware Implementation                            | 31 |

|   |              | 6.3.1  | DRC-pLMS Hardware Architecture                                    | 31 |

|   |              | 6.3.2  | Implementation and Synthesis Results                              | 34 |

|   | 6.4          | Hardw  | vare and Software Simulations 1                                   | 35 |

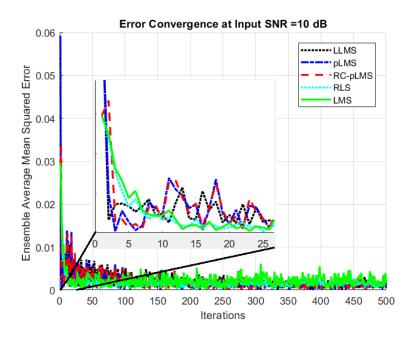

|               | 6.4.1                    | Mean Square Error Analysis          | . 136 |

|---------------|--------------------------|-------------------------------------|-------|

|               | 6.4.2                    | Beam Radiation Pattern              | . 138 |

|               | 6.4.3                    | Pole Zero Map Stability Plot        | . 140 |

|               | 6.4.4                    | Computational Complexity Comparison | . 141 |

| 6.5           | Conclu                   | usion                               | . 142 |

| Conclu        | ısion a                  | nd Future Work                      | 145   |

| Appen         | dix A                    |                                     | 153   |

| Appen         | dix B                    |                                     | 155   |

| Appendix C 15 |                          |                                     | 157   |

| Appen         | dix D                    |                                     | 161   |

| Appendix E    |                          |                                     | 165   |

| List of       | List of Publications 167 |                                     |       |

| Bibliog       | graphy                   |                                     | 169   |

# **LIST OF FIGURES**

| 1.1 | Classical Adaptive Filter                                                                | 27 |

|-----|------------------------------------------------------------------------------------------|----|

| 1.2 | Simple Antenna Array                                                                     | 29 |

| 1.3 | Adaptive Beamforming System                                                              | 30 |

| 2.1 | Antenna Array Radiation Pattern (Cartesian Plot)                                         | 39 |

| 2.2 | Uniform Linear Antenna Array Structure                                                   | 40 |

| 2.3 | Beam Radiation Pattern Vs Number of Antenna Elements with an Angle                       |    |

|     | of Arrival of $0^{\circ}$ and an Inter Element Spacing of $D_a = \frac{\lambda}{2}$      | 42 |

| 2.4 | ULA array Beam Radiation Pattern for Angle of Arrival $0^{\circ}$ and an Inter           |    |

|     | Element spacing of $D_a = \frac{\lambda}{2} \dots \dots \dots \dots \dots \dots$         | 43 |

| 2.5 | Grating Lobes for Different Inter Element Spacing $D_a$                                  | 43 |

| 2.6 | Uniform Circular Array [33]                                                              | 44 |

| 2.7 | Uniform Rectangular Array [33]                                                           | 45 |

| 2.8 | Main Beam and Null Steering to $\theta_0=50^\circ$ and $\theta_1=-15^\circ$ Respectively | 48 |

| 3.1 | Beamforming Algorithms                                                                   | 52 |

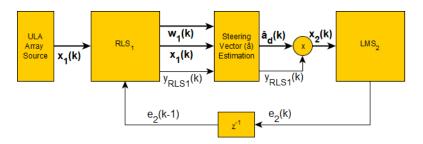

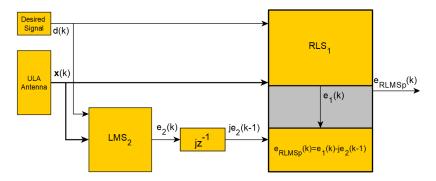

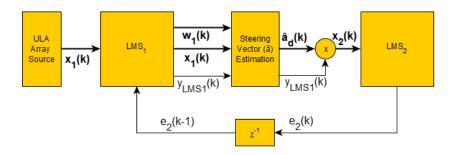

| 3.2 | Cascaded RLMS                                                                            | 61 |

| 3.3 | Parallel Input RLMS (RLMSp)                                                              | 63 |

| 3.4 | Cascaded LLMS                                                                            | 65 |

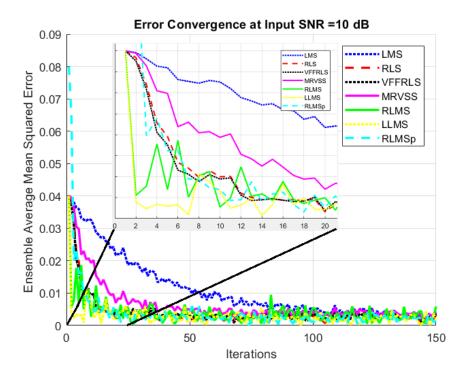

| 3.5 | MSE Convergence Behavior For The LMS and RLS Adaptive Beamformers                        |    |

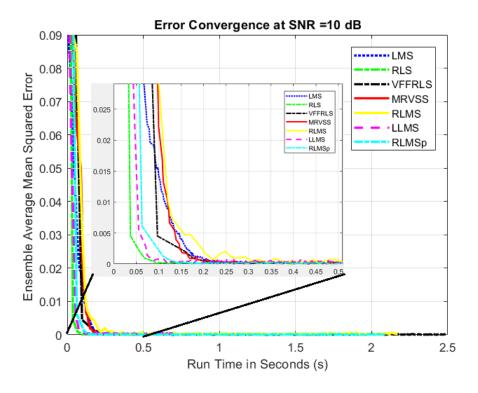

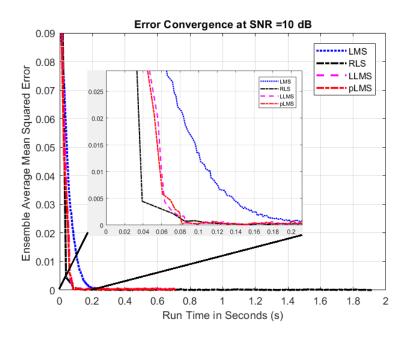

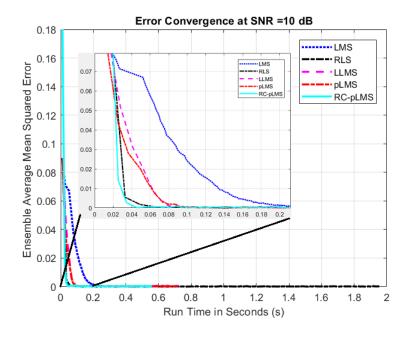

|     | and Their Variants For SNR = 10 dB                                                       | 67 |

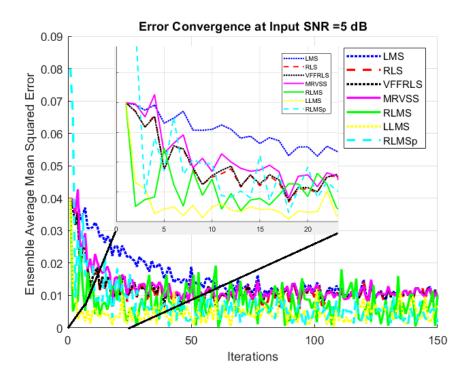

| 3.6 | MSE Convergence Behavior For The LMS and RLS Adaptive Beamformers                        |    |

|     | and Their Variants For SNR = 5 dB $\dots$                                                | 68 |

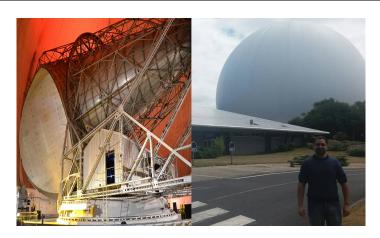

| 4.1 | Pleumeur-Bodou Ground Station For Satellite Broadcasting [71]                            | 72 |

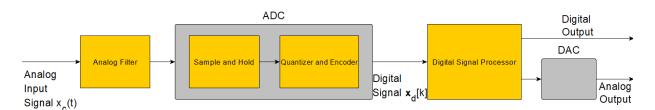

| 4.2 | General DSP System Structure                                                             | 73 |

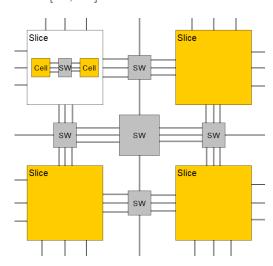

| 4.3 | Xilinx Spartan 3 Simplified FPGA CLB Fabric                                              | 75 |

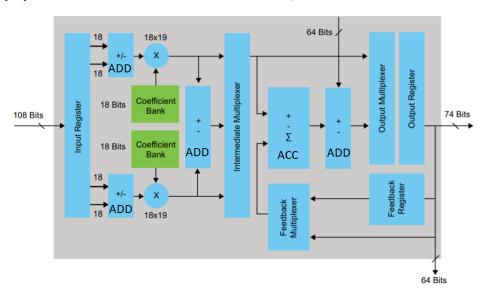

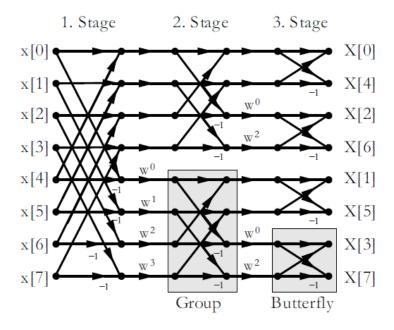

| 4.4  | Altera Stratix V Variable Precision DSP Block in Standard Precision Mode                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------|

|      | $[76] \dots \dots$ |

| 4.5  | Altera Stratix V Variable Precision DSP Block in High Precision Mode [76] 77                                             |

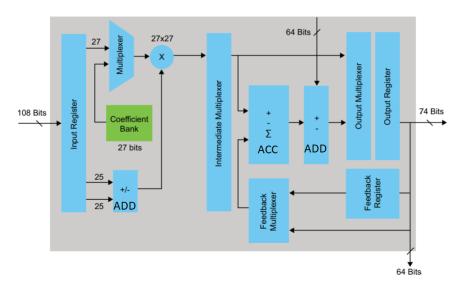

| 4.6  | ARM Cortex A9 Architecture [25]                                                                                          |

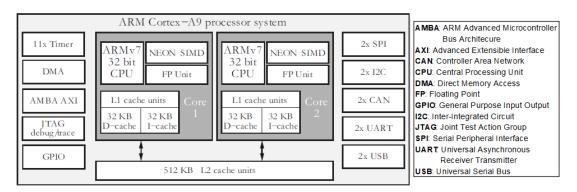

| 4.7  | FFT Radix-2 DIF For an Input Sequence of Length $N=8$ [25] 82                                                            |

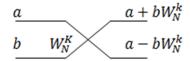

| 4.8  | FFT Radix-2 Butterfly Processor                                                                                          |

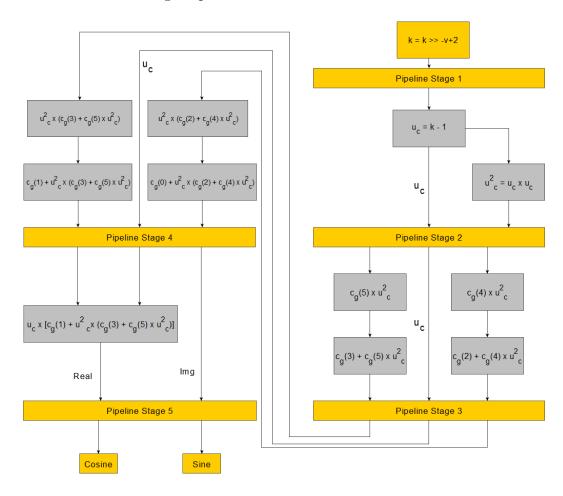

| 4.9  | $5^{th}$ Order Polynomial Hardware Architecture                                                                          |

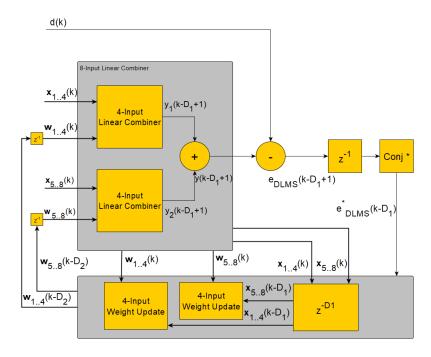

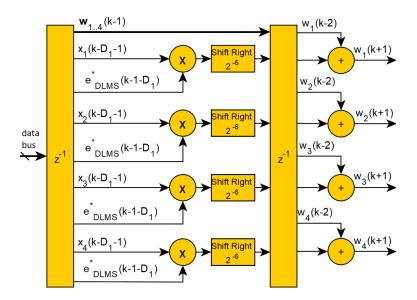

| 4.10 | Delay Relaxed Look Ahead LMS Hardware Architecture                                                                       |

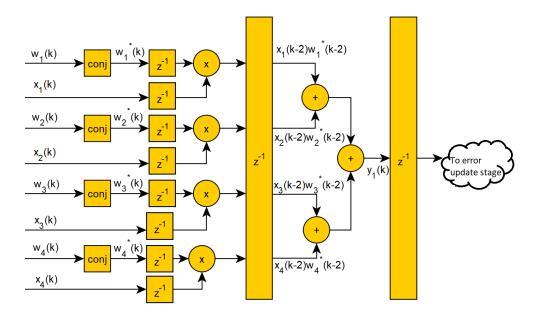

| 4.11 | Delay Relaxed Look Ahead LMS 4-Input Linear Combiner Architecture 95                                                     |

| 4.12 | Delay Relaxed Look Ahead LMS 4-Input Weight Update Architecture 96                                                       |

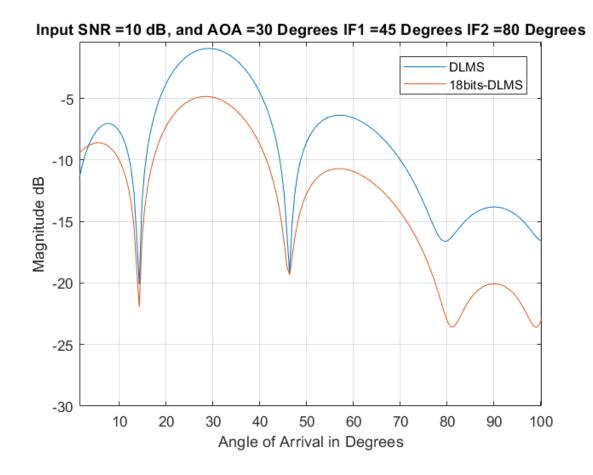

| 4.13 | Infinite and Finite Precision DLMS Beam Radiation Pattern                                                                |

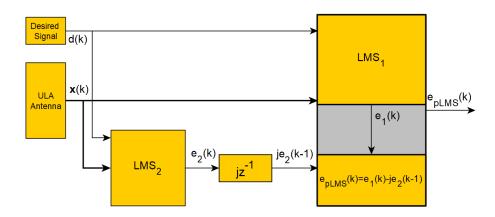

| 5.1  | pLMS Architecture                                                                                                        |

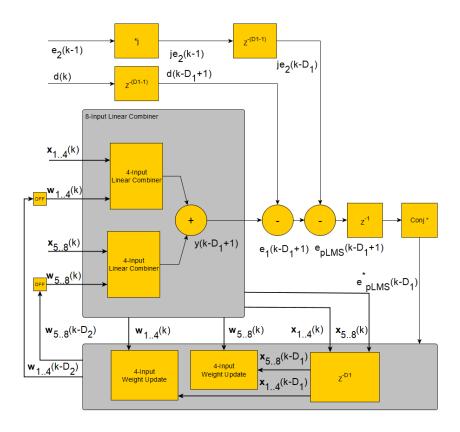

| 5.2  | 8-Elements DpLMS Hardware Architecture [24]                                                                              |

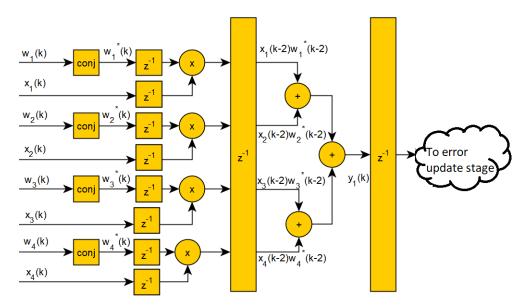

| 5.3  | 4-Input Linear Combiner Block                                                                                            |

| 5.4  | 4-Input Weight Update Block                                                                                              |

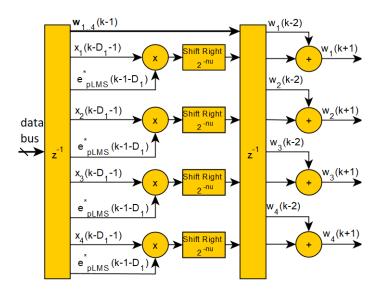

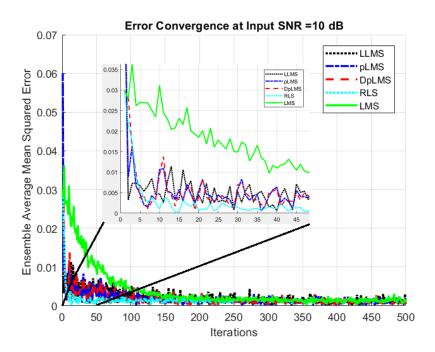

| 5.5  | pLMS MSE Convergence Behavior                                                                                            |

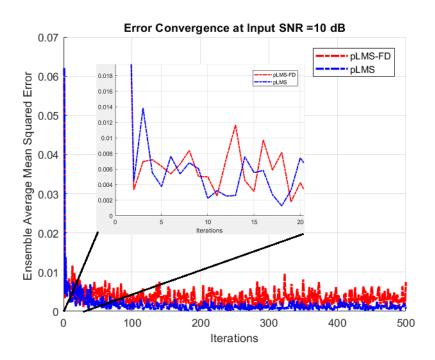

| 5.6  | pLMS and pLMS-FD MSE Convergence Behavior For Fractional Delay Filter 113 $$                                             |

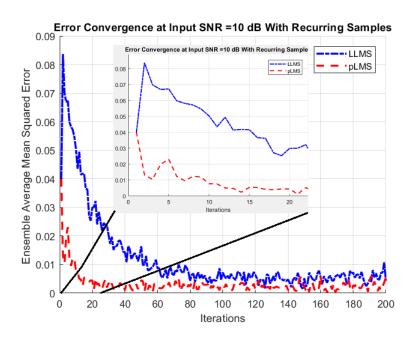

| 5.7  | LLMS and pLMS MSE Convergence Behavior for Recurring Samples $$ 114                                                      |

| 5.8  | pLMS MSE Convergence Behavior for Different SNR Environments 114                                                         |

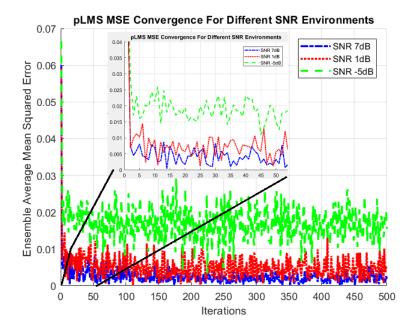

| 5.9  | DpLMS MSE Convergence Behavior for Different SNR Environments $$ 115                                                     |

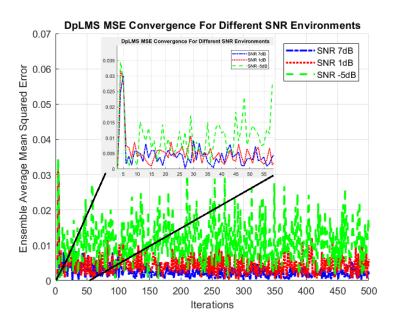

| 5.10 | DpLMS Finite and Infinite Precision Beam Radiation Pattern                                                               |

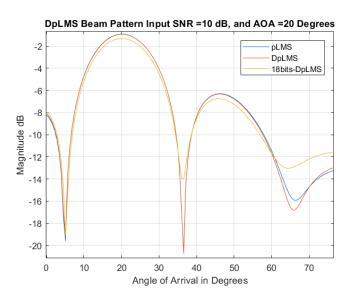

| 5.11 | pLMS Beam Pattern for Different SNR                                                                                      |

| 5.12 | Finite Precision DpLMS Beam Pattern for Different SNR                                                                    |

| 5.13 | pLMS Pole Zero Map for Different $\mu$ [14]                                                                              |

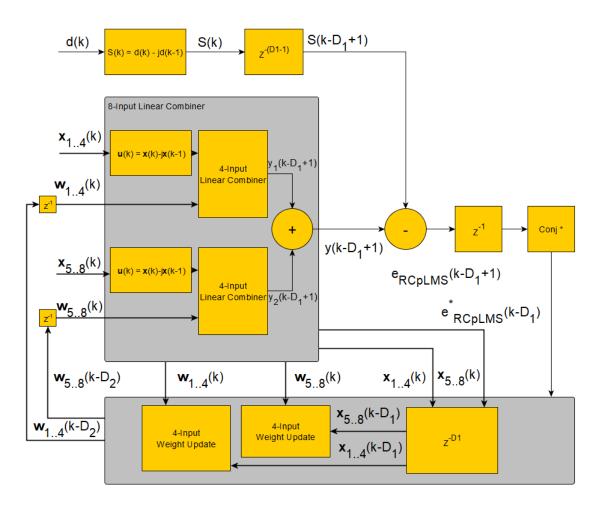

| 6.1  | Reduced Complexity pLMS (RC-pLMS)                                                                                        |

| 6.2  | 8-Input DRC-pLMS Beamformer Architecture [4]                                                                             |

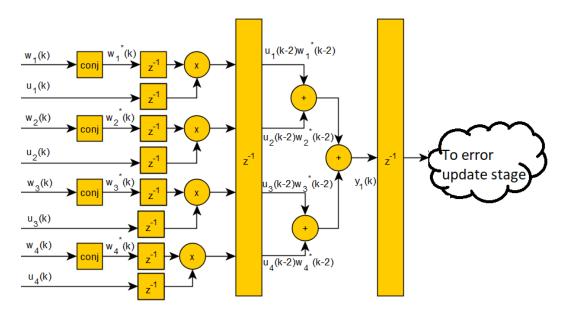

| 6.3  | DRC-pLMS 4-Input Linear Combiner Architecture [4]                                                                        |

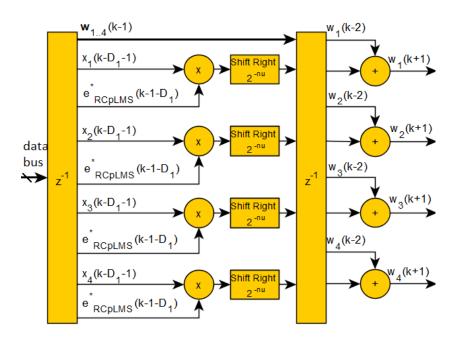

| 6.4  | DRC-pLMS 4-Input Weight Update Architecture                                                                              |

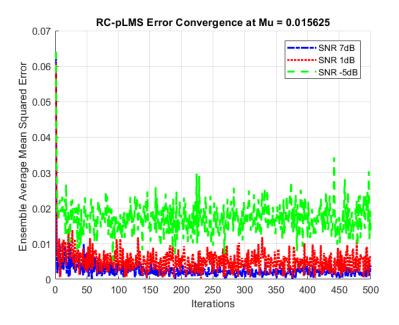

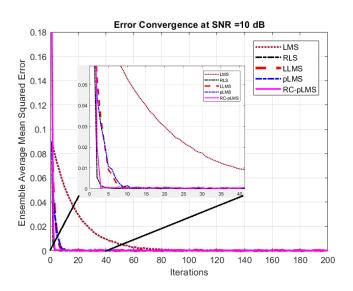

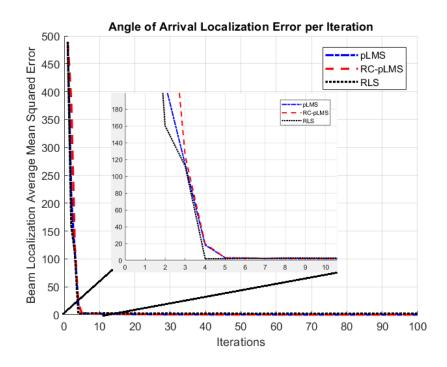

| 6.5  | RC-pLMS MSE Convergence Comparison [4]                                                                                   |

| 6.6  | RC-pLMS Convergence Behavior [4]                                                                                         |

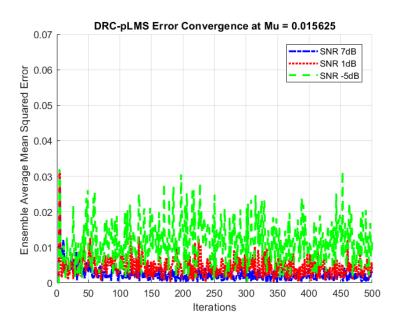

| 6.7  | DRC-pLMS Convergence Behavior [4]                                                  |

|------|------------------------------------------------------------------------------------|

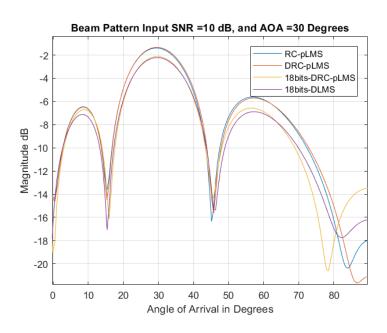

| 6.8  | Infinite and Finite Precision Beam Radiation Pattern for an Angle of Ar-           |

|      | rival 30° [4]                                                                      |

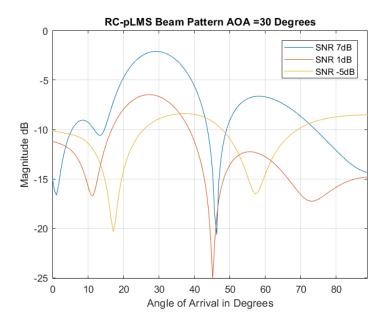

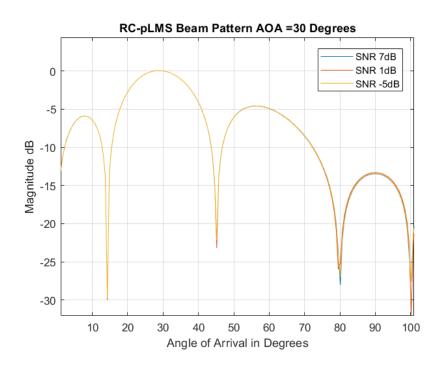

| 6.9  | RC-pLMS Beam Radiation Pattern for an Angle of Arrival $30^\circ~[4]~\dots~139$    |

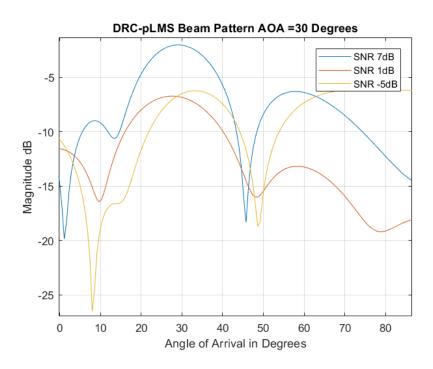

| 6.10 | DRC-pLMS Beam Radiation Pattern for an Angle of Arrival 30° [4] $$ 140             |

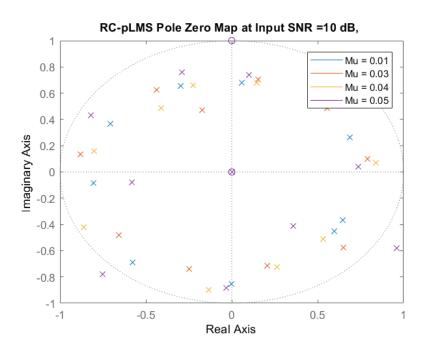

| 6.11 | RC-pLMS Pole Zero Map for Different $\mu$                                          |

| 6.12 | RC-pLMS MSE Convergence Behavior for a Simple 2-PSK Message Signal 157             |

| 6.13 | RC-pLMS Beam Radiation Pattern for a Simple 2-PSK Message Signal and               |

|      | Different SNR                                                                      |

| 6.14 | RC-pLMS Beam MSE Localization With Respect to the Angle of Arrival $$ . 159        |

| 6.15 | LMS, RLS and Other Variants MSE Convergence vs Time Plot $\ \ldots \ \ldots \ 165$ |

| 6.16 | pLMS MSE Convergence Behavior MSE vs Time Plot                                     |

| 6.17 | RC-pLMS MSE Convergence Behavior vs Time Plot                                      |

# **LIST OF TABLES**

| 3.1  | Simulation Initial Parameters                                                       | 66  |

|------|-------------------------------------------------------------------------------------|-----|

| 3.2  | Theoretical Complexity and Resource Usage                                           | 69  |

| 4.1  | Implementation Comparison for DSP Applications [62]                                 | 79  |

| 4.2  | $5^{th}$ order Chebyshev Polynomial Coefficients For sine and cosine Approxi-       |     |

|      | mations                                                                             | 85  |

| 4.3  | Twiddle Factor Direct Computation                                                   | 85  |

| 4.4  | Twiddle Factor Computation Using $5^{th}$ Order Taylor Approximation                | 86  |

| 4.5  | Twiddle Factor Computation Using $5^{th}$ Order Chebyshev Approximation .           | 86  |

| 4.6  | Taylor and Chebyshev Infinite Precision Approximation MSE                           | 86  |

| 4.7  | ZynQ and Cyclone IV Resource Comparison                                             | 87  |

| 4.8  | FFT Radix-2 DIF ZynQ Implementation and Synthesis Results                           | 88  |

| 4.9  | FFT Radix-2 DIF Cyclone IV Implementation and Synthesis Results                     | 89  |

| 4.10 | $\operatorname{ZynQ}$ FFT Radix-2 DIF Implementation Using HLS (Without For Loop) . | 89  |

| 4.11 | $\operatorname{ZynQ}$ FFT Radix-2 DIF Implementation Using HLS (With For Loop)      | 90  |

| 4.12 | $5^{th}$ Order Polynomial SoC Implementation                                        | 92  |

| 4.13 | $5^{th}$ Order Taylor Approximation In $Q3.14$ Finite Precision Format              | 92  |

| 4.14 | $5^{th}$ Order Chebyshev Approximation In $Q2.15$ Finite Precision Format $$        | 93  |

| 4.15 | Taylor and Chebyshev Finite Precision Approximation MSE                             | 93  |

| 4.16 | 8-Input Delay Relaxed Look Ahead LMS Synthesis Results                              | 96  |

| 5.1  | DpLMS Beamformer Synthesis Results                                                  | 110 |

| 5.2  | Simulation Initial Parameters                                                       | 111 |

| 5.3  | Theoretical Complexity and Resource Usage [14]                                      | 119 |

| 6.1  | 8-Input RC-pLMS Beamformer Synthesis Results                                        | 135 |

| 6.2  | Simulation Initial Parameters                                                       | 135 |

| 6.3 Theoretical Complexity and Resource Usage [4] |  |  | 142 |

|---------------------------------------------------|--|--|-----|

|---------------------------------------------------|--|--|-----|

# NOMENCLATURE

### List of Abbreviations

AD Analog to Digital

AOA Angle of Arrival

AP Array Processing

ARM Advanced RISC Machines

BRAM Block Random Access Memory

CAN Controller Area Network

CAWGN Complex Additive White Gaussian Noise

CLB Configurable Logic Block

CM Constant Modulus

CORDIC Coordinate Rotation Digital Computer

DAC Digital to Analog Converter

DFT Discrete Fourier Transform

DIF Decimation in Frequency

DILFAST Decoupled Iterative Least Squares Finite Alphabet Space-Time

DIT Decimation in Time

DMA Direct Memory Access

DOA Direction of Arrival

DoF Degrees of Freedom

DRC-pLMS Delayed Reduced Complexity Parallel Least Mean Square

EF-LSL Error-Feedback LSL

ESPRIT Estimation of Signal Parameter Via Rotational Invariance Techniques

EVD Eigenvalue Decomposition

FA Finite Alphabet

FIR Finite Input Response

FM Fourrier Method

FNBW First Null Beam width

FPGA Field Programmable Gate Array

FPU Floating Point Unit

GPP General Purpose Processor

GS-FAP Gauss-Seidel Fast Affine Projection

HLL High Level Language

HLS High Level Synthesis

HoCA Higher Order Cumulant

HPBW Half Power Beam width

I2C Inter-Integrated Circuit

IF Intermediate Frequency

IIR Infinite Input Response

IOB Input/Output Block

IP-core Intellectual Property

LC Linear Combiner

LLMS Least Mean Square - Least Mean Square

LMS Least Mean Square

LS Least Squares

LUT Look Up Table

MAC Multiply Accumulate

ML Maximum Likelihood

MMSE Minimum Mean Square Error

MRVSS Modified Robust Variable Step Size

MSE Mean Square Error

MSINR Maximum Signal to Interference Plus Noise Ratio

MUSIC Multiple Signal Classification

MVDR Minimum Variance Distortionless Response

NLMS Normalised Least Mean Square

PDSP Programmable Digital Signal Processing Processor

PLL Phased Locked Loop

pLMS Parallel Least Mean Square

QoS Quality of Service

RAM Random Access Memory

RC-pLMS Reduced Complexity Parallel Least Mean Square

RF Radio Frequency

RISC Reduced Instruction Set Computer

RLMS Recursive Least Mean Square

RLS Recursive Least Squares

RTL Register Transfer Level

SGD Stochastic Gradient Descent

SLL Side Lobe Level

SNR Signal to Noise Ratio

SoC System on Chip

SOCP Second Order Cone Programming

SPI Serial Peripheral Interface

UART Universal Asynchronous Reciever-Transmitter

USB Universal Serial Bus

VSSLMS Variable Step Size Least Mean Square

WSS Wide Sense Stationary

#### List of Variables

$(AF(\theta))_n$  Array Factor Normalized at Unity

$\alpha$  RLS Forgetting Factor

$\eta_{Sy}$  Multi-Stage Overall Desired and Output Signals Quantization Error

$\eta_S$  Multi-Stage Overall Desired Signals Quantization Error

$\eta_u$  Multi-Stage Overall Input Signals Quantization Error

$\eta_w$  Adaptive Filter Weight Signals Quantization Error

$\eta_y$  Multi-Stage Output Signals Quantization Error

$\hat{a}_{d,m}$   $m^{th}$  Element of the Desired Signals Steering Vector Estimate

$\lambda$  Carrier Signals Wavelength

$\lambda_{A,max}$  Maximum Eigenvalue in Matrix **A**

$\lambda_i$   $i^{th}$  Eigenvalues

$\lambda_{R,max}$  Maximum Eigenvalue in Matrix **R**

$\bar{\mathbf{v}}(k)$  Mean Coefficient Error Vector

$\bar{\mathbf{w}}(k)$  Adaptive Filters Mean Weight Vector

$\hat{\mathbf{a}}_d$  Desired Signals Steering Vector Estimate

$\widehat{\mathbf{R}}_{i+n}(\tau)$  Interference Plus Noise Correlation Matrix Estimate

A Multi Stage Adaptive Algorithm Overall Input Auto-Correlation Matrix

$\mathbf{a}_d$  Desired Signals Steering Vector

$\mathbf{a}_{i,l}$  lth Interference Signals Steering Vector

$\mathbf{A}_i$  Matrix of Steering Vectors

$\mathbf{c}_i$  Beamformer Constraint Vector

d Desired Signal Vector

| $\mathbf{H}_b$          | Communication Channel Transfer Function                                 |

|-------------------------|-------------------------------------------------------------------------|

| I                       | Identity Matrix                                                         |

| $\mathbf{i}_l$          | $l^{th}$ Interference Signal                                            |

| $\mathbf{L}(k)$         | RLS Gain Matrix                                                         |

| $\mathbf{m}(k)$         | Mean Coefficient Error Vector in a Rotated Coordinate System            |

| $\mathbf{n}(k)$         | Complex Additive White Gaussian Noise Vector Signal                     |

| O                       | Unitary Matrix of Eigenvectors Rows                                     |

| $\mathbf{p}(	au)$       | Adaptive Filters Input and Desired Signals Cross Correlation Vector     |

| $\mathbf{p}_t$          | FFT Rotation, Twiddle, Factor Exponent Input Vector                     |

| $\mathbf{Q}(	au)$       | RLS Input Signals Auto-Correlation Matrix                               |

| $\mathbf{Q}_r(	au)$     | RC-pLMS Input Signals Cross-Correlation Matrix                          |

| $\mathbf{R}(	au)$       | Adaptive Filters Input Signals Auto-Correlation Matrix                  |

| $\mathbf{R}_{i+n}(	au)$ | Interference Plus Noise Correlation Matrix                              |

| $\mathbf{S}_b$          | Unknown Data Signal                                                     |

| $\mathbf{u}(k)$         | RC-pLMS Total Input Vector                                              |

| $\mathbf{u}_q(k)$       | RC-pLMS Total Input Vector Subject to Quantization Error                |

| $\mathbf{w}(k)$         | Adaptive Filters Weight Vector                                          |

| $\mathbf{w}_{14}(k)$    | Adaptive Filters Weight Vector With Respect to First Four Input Samples |

| $\mathbf{w}_1(k)$       | First Stage Adaptive Filters Weight Vector                              |

| $\mathbf{w}_2(k)$       | Second Stage Adaptive Filters Weight Vector                             |

| $\mathbf{w}_{58}(k)$    | Adaptive Filters Weight Vector With Respect to Last Four Input Samples  |

| $\mathbf{w}_i(k)$       | $i^{th}$ Stage Adaptive Filters Weight Vector                           |

| $\mathbf{w}_{MVDR}$     | MVDR Adaptive Beamformers Optimal Weight Vector                         |

| $\mathbf{w}_{opr}$   | RC-pLMS Adaptive Beamformers Optimal Weight Vector                             |

|----------------------|--------------------------------------------------------------------------------|

| $\mathbf{w}_{op}$    | pLMS Adaptive Beamformers Optimal Weight Vector                                |

| $\mathbf{w}_q$       | RC-pLMS Weight Vector Subject to Quantization Error                            |

| $\mathbf{x}(k)$      | Adaptive Filters Input Signal Vector                                           |

| $\mathbf{x}_{14}(k)$ | First Four Samples of the Adaptive Filters Input Signal Vector                 |

| $\mathbf{x}_1(k)$    | First Stage Adaptive Filters Input Signal Vector                               |

| $\mathbf{x}_2(k)$    | Second Stage Adaptive Filters Input Signal Vector                              |

| $\mathbf{x}_{58}(k)$ | Last Four Samples of the Adaptive Filters Input Signal Vector                  |

| $\mathbf{X}_b$       | Input Signals Matrix                                                           |

| $\mathbf{x}_d$       | Discrete Time FFT Input Signal Vector                                          |

| $\mathbf{x}_f$       | Adaptive Filters Input Signal Vector Subject to Fractional Delay               |

| $\mathbf{z}(	au)$    | RLS Input and Desired Signals Cross Correlation Vector                         |

| $\mathbf{z}_r(	au)$  | RC-pLMS Input and Desired Signals Cross Correlation Vector at Different $\tau$ |

| 11                   | RC-pLMS Optimization Step Size                                                 |

| $\mu$                |                                                                                |

| $\mu_1$              | First LMS Stage Optimization Step Size                                         |

| $\mu_2$              | Second LMS Stage Optimization Step Size                                        |

LMS Adaptive Beamformers Optimal Weight Vector

$\mathbf{w}_{oplms}$

$\mu_{LMS}$

$\mu_{pLMS}$

$\nabla_{LMS}$

$\nabla_{pLMS}$

$\nabla_{RC-pLMS}$

LMS Optimization Step Size

pLMS Optimization Step Size

LMS Cost Functions Gradient

pLMS Cost Functions Gradient

RC-pLMS Cost Functions Gradient

| Υ                   |                                                                 |

|---------------------|-----------------------------------------------------------------|

| $\psi$              | Phase Shift                                                     |

| $\Psi(arepsilon)$   | Set of Erroneous Steering Vectors With Respect to $\varepsilon$ |

| $\psi_x$            | Phase Shift for Elements Placed in the $x$ Plane                |

| $\psi_y$            | Phase Shift for Elements Placed in the $y$ Plane                |

| $\sigma_a^2$        | Variance of the Constant $a$                                    |

| $\sigma_d^2$        | Desired Signals Variance                                        |

| $\sigma_p^2$        | In Phase Message Signals Variance                               |

| $\sigma_q^2$        | Out Of Phase Message Signals Variance                           |

| au                  | Signal Lag in a Wide Sense Stationary Process                   |

| $	au_d$             | Time Delay Between Two Consecutive Antenna Elements             |

| $\theta$            | Antenna Arrays Elevation Angle of Arrival                       |

| $\varepsilon$       | Maximum Mismatch Error                                          |

| Λ                   | Diagonal Matrix of Eigenvalues $\lambda_i$                      |

| $\vartheta$         | Very Small User Introduced Constant                             |

| $\xi_{LMS}$         | LMS Cost Function                                               |

| $\xi_{pLMS}$        | LMS Cost Function                                               |

| $\xi_{RC-pLMS}$     | RC-pLMS Cost Function                                           |

| $\xi_{RLS}$         | RLS Cost Function                                               |

| $AF(\theta)$        | Array Factor With Respect to Angle of Arrival $\theta$          |

| $BW_{3\mathrm{dB}}$ | 3 dB Beamwidth                                                  |

| c                   | Celerity of Electromagnetic Waves                               |

| C(k)                | Chebyshev Polynomial Coefficients                               |

|                     |                                                                 |

Antenna Arrays Azimuth Angle of Arrival

$\phi$

| $c_g(k)$         | Chebyshev Polynomial General Expanded Form Coefficients                       |

|------------------|-------------------------------------------------------------------------------|

| $c_m$            | Erroneous Steering Vector                                                     |

| d(k)             | Desired Signal Instantaneous Sample                                           |

| D(z)             | z Transform Sequence of the Desired Signal $d(k)$                             |

| $D_1$            | Delay in the Adaptive Filters Instantaneous Error Signal                      |

| $D_2$            | Delay in the Adaptive Filters Weight Update                                   |

| $D_3$            | Sum Relaxation Delay in the Adaptive Filters Weight Update                    |

| $D_{ax}$         | Distance Between Two Consecutive Array Elements in the $\boldsymbol{x}$ Plane |

| $D_{ay}$         | Distance Between Two Consecutive Array Elements in the $y$ Plane              |

| $D_a$            | Distance Between Two Consecutive Array Elements                               |

| e(k)             | Adaptive Filters Instantaneous Error Signal                                   |

| $e_1(k)$         | First Stage Adaptive Filters Instantaneous Error Signal                       |

| $e_2(k)$         | Second Stage Adaptive Filters Instantaneous Error Signal                      |

| $e_{DLMS}(k)$    | Delay LMS Instantaneous Error Signal                                          |

| $e_i(k)$         | $i^{th}$ Stage Adaptive Filters Instantaneous Error Signal                    |

| $e_{LLMS}(k)$    | LLMS Instantaneous Error Signal                                               |

| $e_{LMS}(k)$     | LMS Instantaneous Error Signal                                                |

| $e_m$            | Mismatch Error in the Desired Signals Steering Vector                         |

| $e_{pLMS}(k)$    | pLMS Instantaneous Error Signal                                               |

| $e_q(k)$         | Adaptive Filters Instantaneous Error Signal Subject to QuantizationError      |

| $e_{RC-pLMS}(k)$ | ) RC-pLMS Instantaneous Error Signal                                          |

| $e_{RLMSp}(k)$   | RLMSp Instantaneous Error Signal                                              |

| $e_{RLMS}(k)$    | RLMS Instantaneous Error Signal                                               |

|                  |                                                                               |

$e_{RLS}(k)$  RLS Instantaneous Error Signal

$e_t(k)$  Multi-Stage Adaptive Filters Total Instantaneous Error Signal

$f_c$  Carriers Signals Frequency

g Antenna Directivity Gain

H(z) LMS z Transfer Function

$H_{pLMS}(z)$  pLMS z Transfer Function

$H_{RC-pLMS}(z)$  RC-pLMS z Transfer Function

j Imaginary Complex Number

J(z) z Transform Sequence of the Instantaneous Error Signal e(k)

Number of Antenna Elements

$N_c$  FFT Sequence Length

$N_x$  Number of Antenna Elements in the x Plane

$N_y$  Number of Antenna Elements in the y Plane

nu Step Size Exponent

P Power Radiated by the Antenna

$P_c$  Projection to the x-y Plane

$p_t$  FFT Rotation, Twiddle, Factor Exponent

q Taylor Series Polynomial Expansion Point

r Base Radix - r Number Representation

R(z) z Transform Sequence of the Input Signals Auto-Correlation Matrix  $\mathbf{R}(\tau)$

$R_c$  Circular Antenna Arrays Radius

$r_{k-i}$  Fractional Delay Filters Input Signal Auto-Correlation Estimate Time Av-

erage

| $r_{ki}$                | Fractional Delay Filters Input Signal Auto-Correlation Estimate                   |

|-------------------------|-----------------------------------------------------------------------------------|

| RD                      | Antenna Radiation Directivity                                                     |

| S(k)                    | RC-pLMS Total Desired Signal                                                      |

| s(k)                    | Message Signal                                                                    |

| $S_q(k)$                | RC-pLMS Total Desired Signal Subject to Quantization Error                        |

| $S_{RLMSp}(k)$          | RLMSp Total Desired Signal                                                        |

| $S_{RLMS}(k)$           | RLMS Total Desired Signal                                                         |

| $T_k(u_c)$              | Chebyshev Polynomial Representation With Respect to $u_c$                         |

| U                       | Antenna Radiation Sensitivity (Practical)                                         |

| $U_0$                   | Antenna Radiation Sensitivity (Theoretical)                                       |

| $u_c$                   | Chebyshev Polynomials Change of Variable                                          |

| $U_{max}$               | Maximum Antenna Radiation Sensitivity                                             |

| $v_1$                   | Random Gaussian Real Sequence                                                     |

| $v_2$                   | Random Gaussian Real Sequence                                                     |

| $v_m$                   | Random Complex Gaussian Sequence                                                  |

| $w_{1,m}$               | $m^{th}$ Element, First Stage, Instantaneous Weight                               |

| $W^{kn}_{rac{N_c}{2}}$ | $kn^{th}$ Rotation, Twiddle, Factor for an FFT Sequence of Length $\frac{N_c}{2}$ |

| $W_{N_c}^k$             | $k^{th}$ Rotation, Twiddle, Factor for an FFT Sequence of Length $N_c$            |

| X[k]                    | FFT Sequence                                                                      |

| $x_{1,m}$               | $m^{th}$ Element, First Stage, Instantaneous Input Signal                         |

| $x_{2,m}$               | $m^{th}$ Element, Second Stage, Instantaneous Input Signal                        |

| $x_c(t)$                | Analog Input Signal                                                               |

| $x_d[k]$                | Discrete Time Input Signals Sample                                                |

|                         |                                                                                   |

y(k)Adaptive Filters Output Signal First  $\frac{N}{2}$  Elements Adaptive Filters Output Signal  $y_1(k)$ Second $\frac{N}{2}$  Elements Adaptive Filters Output Signal  $y_2(k)$  $y_d(k)$ Adaptive Filters Message Signal Subject to Fractional Delay  $y_{i,j}(k)$ Adaptive Filters  $j^{th}$  Interference Signal Subject to Fractional Delay  $y_{LMS1}(k)$ First LMS Stage Output Signal  $y_{LMS2}(k)$ Second LMS Stage Output Signal  $y_q(k)$ RC-pLMS Output Signal Subject to Quantization Error  $y_{RLS1}(k)$ First RLS Stage Output Signal

# **ADAPTIVE BEAMFORMING: A HISTORY**

Since the dawn of digital signal processing, researchers have thrived to develop realtime adaptive systems that can independently self-adjust to estimate/filter the desired data from an incoming noisy signal. The ability of an adaptive system/filter to autonomously operate in an unknown noisy environment, makes it an inevitable feature in numerous applications, such as: wireless communication, digital communication, biomedical engineering, control systems, geology and so on. While these adaptive filters still share a common mode of operation, the manner in which they extract the signal of interest changes for each class of applications [1, 2, 3]. Thus, the operation of a linear adaptive filter at a discrete time instance k can be summarized as follows: for an input vector signal  $\mathbf{x}(k)$ , a desired reference signal d(k) and an output signal y(k), the adaptive algorithm computes the error signal e(k) = d(k) - y(k) to estimate the variable filter weight vector  $\mathbf{w}(k+1)$  [2].

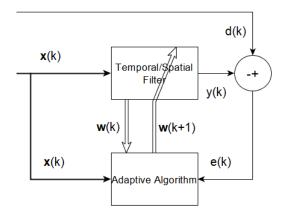

Figure 1.1 – Classical Adaptive Filter

As shown in Figure 1.1, the initial building blocks of an adaptive system are the linear filter and the adaptive algorithm. Moreover, the linear filter block can be modeled with a finite impulse response (FIR) or an infinite impulse response (IIR) for a one dimensional input vector (one sensor) or a spatial filter, i.e. linear combiner (LC) for a N dimensional input (sensor array). For spatial filters, the filtered output signal, y(k), is obtained as a linear combination of the input signal  $\mathbf{x}(k) = [x_1(k), x_2(k), ..., x_N(k)]^T$  and the filter weights  $\mathbf{w}(k) = [w_1(k), w_2(k), ..., w_N(k)]^T$  and is given as  $y(k) = \mathbf{w}^H(k)\mathbf{x}(k)$ , where the superscripts T and T denote respectively the vector transpose and the Hermitian operator, i.e. the conjugate transpose. Furthermore, the adaptive algorithm block is used to estimate the variable filter weights based on certain optimization algorithms. Two classical methods exist, in wide sense stationary (WSS) environments, for deriving recursive algorithms [2]:

- 1. Stochastic gradient descent (SGD): In SGD, the cost function is defined as the mean squared value of the error, and it is represented by a 2<sup>nd</sup> order function of the filter weights. For recursive applications, the instantaneous squared error is supplied to update the variable weights. As such, the SGD technique refers to the least mean square (LMS) algorithm [2].

- 2. Least squares (LS): In this method, the cost function is defined as the sum of weighted error squares. In contrast to the SGD technique, LS utilizes matrix operations to compute the gain matrix and updates the variable weights. Such technique is referred to as the recursive least squares (RLS) [2].

With the recent, exponential, spread of wireless connected devices and their requirements in data rate and accuracy, the complexity of array processing algorithms have drastically increased [3, 4]. Such unprecedented growth resulted in a highly congested frequency spectrum [5]. Therefore, many researchers have coupled adaptive signal processing algorithms with antenna arrays to implement adaptive beamforming methods and further increase the spectral efficiency while simultaneously providing a high quality of service (QoS), higher data rates and a wider coverage at a reduced cost. However, the introduction of complex adaptive algorithms, in wireless communication, enforced new limitations on their hardware architecture, such as the need of reduced arithmetic complexity and that of pipeline and parallelism while preserving accelerated convergence and a low residual error in finite precision considerations [4]. Thus, in this chapter, we introduce the recent challenges in

signal processing for wireless applications and one of the most adopted array processing technique, i.e. adaptive beamforming. Additionally, we present our research objectives and motivation towards the imposed challenges.

### 1.1 Signal Processing in Wireless Communication

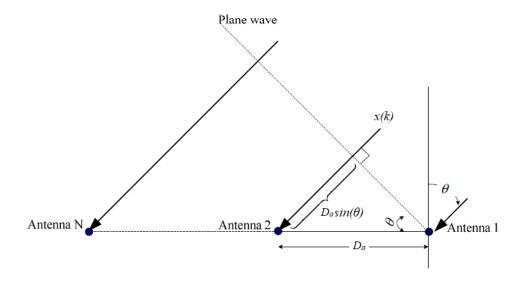

In practice, the majority of wireless communication applications, i.e. mobile communication, radar or sonar, involves spatial filtering techniques [1]. Such techniques are achieved by employing a sensor array architecture, generally, with equally spaced homogeneous elements, as shown in Figure 1.2 [4]. With the first antenna element acting as

Figure 1.2 – Simple Antenna Array

a reference,  $\theta$  is the angle of arrival (AOA),  $D_a$  is the distance between two consecutive antenna elements and  $\mathbf{x}(k)$  is the input signal. In effect, the acquired signal is sampled in space to exploit the spatial properties of signals and noise through array processing (AP) methods, i.e. beamforming [1].

### 1.1.1 Adaptive Beamforming

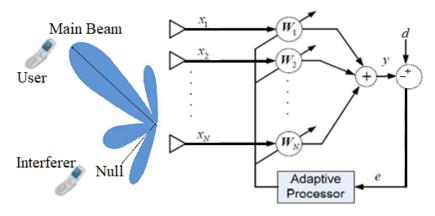

Adaptive beamforming is a spatial multiplexing technique, for antenna arrays, used in performing directional signal reception and transmission. Its is achieved by generating a main, pencil, beam in the direction of the desired signal component, while steering nulls in the direction of interferences [6]. As shown in Figure 1.3 [4] a linear antenna with N sensors points its highest gain beam, main beam, towards the desired user while directing nulls to unwanted inputs.

Figure 1.3 – Adaptive Beamforming System

The first beamforming system, i.e. the intermediate frequency (IF) side-lobe canceler was introduced by Howells in 1957 [2, 7]. Howells demonstrated the use of one degree of freedom, two sensor antenna array in amplifying a desired signal while attenuating interference. In his antenna architecture, Howells implemented a high gain antenna element with respect to a low gain, reference, omnidirectional, antenna forming a configurable array with a steerable main beam and null [2, 7]. Subsequently, in 1966, Applebaum derived the control law implementing a control loop for each antenna element [8, 9]. Applebaum's technique resulted in a generalization of Howells side lobe canceler and was based on maximizing the signal to noise ratio (SNR) of the antenna arrays output for random noise environments [2, 8, 9]. Another classical, fully adaptive beamformer, was developed by Widrow et al in 1967 [10]. In [10], the authors demonstrated the effective use of the LMS algorithm in providing a low complexity adaptive beamformer based on the steepest descent optimization technique and the use of the stochastic gradient [2].

The LMS algorithm, presented by Widrow et al, iteratively computes the filter weights by minimizing a pre-defined cost function based on the auto-correlation of the input signal and the cross-correlation of the input and the reference signal [10]. Moreover, a minimum variance distortionless response (MVDR) [11, 12] adaptive beamformer was later introduced by Capon in 1969 [2]. In this algorithm, Capon proposed minimizing the output average power (variance) subject to a pre-set constraint maximizing that of the desired signal [2]. Unlike the LMS, Capcon's MVDR requires previous knowledge on the incoming signals direction, i.e. the AOA [13]. Numerous modifications and algorithms were later on derived based on the classical approaches to accurately achieve optimal behavior, through the use of multi stage beamformers, in recovering the signal of interest and attenuating interference and noise [4, 5, 6, 13, 14, 15]. Some multi stage beamformers are the least mean square - least mean square (LLMS) algorithm [5], the recursive least mean square (RLMS) algorithm [15], the reduced complexity parallel RLMS (RLMSp) [6] and the parallel LMS (pLMS) [14].

### 1.2 Our Research Project

While the currently employed adaptive algorithms demonstrate satisfactory behavior and convergence in infinite precision mode, in practical applications, i.e within a finite precision mode, their performance is known to degrade. Such degradation is governed by the resource limitations and analog to digital converters of the hosting processor leading to the accumulation of round off and quantization errors [4, 16, 17, 18]. Additionally, the increase in complex computations, i.e. matrix operations, divisions and matrix inversions, due to the nature of the operations, severely degrades the speed of operations which in turn affects the beamformers reliability. Several variants of the classical beamformers have been proposed to present a parallel and easy to pipeline architecture while preserving convergence and acceptable performance. Such techniques are and not limited to: the Gauss-Seidel Fast Affine Projection (GS-FAP) algorithm [19], the a Priori Error-Feedback LSL (EF-LSL) algorithm using a logarithmic arithmetic [20], the relaxed look ahead pipelined LMS [21], the time sharedlook up table (LUT)-less LMS architecture [22] and the division free and variable regularized LMS [23], and the relaxed look ahead par-

allel LMS [24]. The GS-FAP demonstrates better performance over the LMS and some of its variants; However, at the cost of an increase in complexity and processing stages [19]. The EF-LSL structure presents a considerable reduction in the processing time and look up table usage; However, it is based on the least square algorithm, of  $O(N^2)$  complexity, and requires the use of a logarithmic number system with a dedicated arithmetic unit [20]. The LLMS [5] and RLMS [15] are multi-stage LMS/LMS and RLS/LMS separated by an estimate of the steering vector and connected by a delayed error feedback. These techniques show upper level performance over other LMS and RLS variants at the cost of doubling the computational requirements. Nevertheless, presenting a pipeline hardware architecture for the multi stage algorithms is difficult given the design error feedback path and its computational complexity. The previous cascade RLMS algorithm is thus simplified to present a parallel input structure as shown in [6] by eliminating the need for a cascading stage. However, the suggested improvement does not reduce the  $O(N^2)$ complexity and does not provide an easy to pipeline architecture. On the other hand, the relaxed look-ahead pipeline LMS, and the time shared LUT-less LMS discussed in [21, 22], present a pipeline architecture for the classical LMS with no noticeable enhancement in the convergence speed nor in the error floor. Furthermore, the pipeline division free variable regularized LMS architecture presented in [23] still presents considerable complexity and requires an on-the-fly computation of its step size compared to the classical LMS. Therefore, it is of utmost importance to achieve a parallel, reduced complexity and easy to pipeline beamformer with improved convergence and low residual error.

#### 1.2.1 Motivation

In this context, the main motivation of our research is to eliminate the trade off between the computational complexity and the performance of the multi-stage algorithms while presenting a suitable hardware architecture for limited resource devices. Through the use of the delay feedback technique [5, 6, 14, 15], we propose a two stages, parallel input LMS algorithm with an accelerated convergence and a minimal residual error for adaptive beamforming (pLMS). pLMS is formed of two LMS stages operating in parallel, where the final error signal is derived as a combination of individual stage errors. The error signal

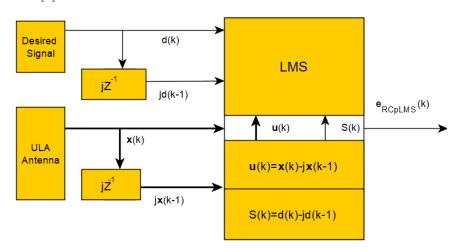

of the second LMS stage  $(LMS_2)$  is multiplied by the imaginary number  $j = \sqrt{-1}$  to combine with that of the first LMS stage  $(LMS_1)$ . Additionally, we further simplify the pLMS to achieve a reduced complexity parallel LMS design (RC-pLMS). The RC-pLMS is obtained by adding a phased sample delayed version of the inputs to the  $LMS_1$  to eliminate the need for a second independent set of weights. In order to present a pipeline, parallel, hardware architecture for the RC-pLMS, we propose the application of the delay and sum relaxed look-ahead technique (DRC-pLMS). Convergence and stability analysis are performed to determine the upper bound of the step size. The quantization effect analysis is conducted to assess the system performance within finite precision arithmetic. Finally, a hardware implementation of the DRC-pLMS design is done in order to study its resource consumption and behavior in finite precision arithmetic. The architecture is implemented using  $Q2.15^{1}$  format [4, 25].

### 1.2.2 Outlines

In chapter 1, we first present an overview on the concept of adaptive filtering and the advantages it provides for different digital signal processing (DSP) applications. Second, we discuss the benefits of applying adaptive filtering techniques in wireless communication in order to ease spectral congestion and improve overall performance through beamforming. Finally, we perform a comparative study on different, previous and recent, adaptive beamforming algorithms and hardware implementation while commenting on their advantages and disadvantages.

In chapter 2, we detail the basics of antenna arrays, the popular architectures currently adopted and their essential role in exploiting the spatial domain through beamforming. Concurrently, we explain the basic concepts in spatial filtering and beamforming such as: beam steering, null placement and array ambiguity.

In chapter 3, we highlight the different types and sub-types of adaptive beamforming techniques, i.e. blind, semi-blind, non-blind, temporal based and spatial based. Additionally, we provide an extensive mathematical overview for different, popular, temporal and spatial referenced adaptive beamforming algorithms and their variants. We then present

<sup>1.</sup> One signed bit, two integer bits and fifteen precision bits

a comparative study on the performance of each, with respect to the convergence profile, through the use of the mean square error (MSE) criteria. Additionally, we list some of the multi stage, cascade, adaptive beamforming algorithms, i.e. LLMS and RLMS, and we propose a reduced complexity parallel input RLMS structure.

Our contributions are detailed in chapters 4, 5 and 6 and are summarized as follows:

- A comparative experimental study is conducted in order to assess the performance of different processors and tools in implementing DSP related routines. The fast Fourier transform (FFT) is the core of numerous DSP applications and is implemented, in parallel and sequential forms, on different field programmable gate array (FPGA) and system on chip (SoC) families. Moreover, the FFT architecture is modeled through the use of various development techniques and tools such as: traditional hardware description language (HDL), high level language (HLL) and high level synthesis (HLS) tools. Synthesis results have shown that an HDL like, high speed design, can be obtained through the effective use of HLL design techniques and proper HLS compiler directives. Moreover, HLL and HLS tools provides a simple and easy method to target multi processor architectures and heterogeneous systems with a shorter design and testing time. However, the concluded disadvantage of using HLS tools is that optimization related tasks is offloaded to the compiler and is dependent on the proper use of compiler directives.

- A high accuracy, low complexity dynamic twiddle function generator using Chebyshev polynomial approximation. While the FFT contributes in accelerating numerous DSP applications, when implemented in finite precision, on limited resource devices, its performance tend to degrade due to the resulting loss of accuracy. As such, we propose a low complexity, high accuracy, dynamic twiddle factor computation method based on Chebyshev polynomial approximation. Moreover, we present its low complexity, low latency, high throughput architecture in finite precision mode. Simulation and synthesis results highlight the superior performance of the adopted approximation method compared to the classical Taylor approximation. In contrast, to the Taylor approximation method, the Chebyshev approximation achieved an accuracy of three decimal digits and smaller resource usage for a fifth order polynomial.

- A two stages parallel LMS (pLMS), its transfer function approximation and pipeline

hardware implementation for adaptive beamforming. In order to eliminate the LMS convergence speed and error floor trade off, while preserving a parallel and low latency architecture, we propose a multi stage parallel LMS architecture connected by error feedback. Where the pLMS overall error is formed as a combination of individual stage errors. In order to numerically compute the maximum step size, the pLMS transfer function approximation derived by modeling the input antenna as a finite input response (FIR) fractional delay filter using Lagrange interpolation. While the proposed pLMS structure is formed of two LMS stages in parallel, presenting a pipeline design is not straight forward given the dependency on the error feedback paths. As such, we propose the application of the delay and sum relaxed look ahead technique, independently, for each of the LMS stages. Thus, the resulting delay pLMS (DpLMS) is obtained and implemented in high throughput, low latency, parallel and pipeline architecture with finite precision. Software simulation results, reflected by the MSE and output beam pattern validated the superior performance of the pLMS with respect to other variants in different signal to noise ratio (SNR) environments. Moreover, with respect to the output beam pattern, the DpLMS implemented in finite precision, showed similar accuracy to that of the infinite precision one. Finally, synthesis results shows that the DpLMS achieved a maximum operating frequency of 208.33 MHz in a low complexity, high throughput architecture.

— A reduced complexity parallel LMS (RC-pLMS), its transfer function approximation and pipeline hardware implementation for adaptive beamforming. While the pLMS eliminated the LMS trade off while maintaining a parallel easy to pipeline design, it is formed of two LMS stages and requires twice the LMS resources. As such, in order to maintain an LMS like complexity while preserving pLMS convergence profile, we propose a single stage RC-pLMS design. RC-pLMS is obtained by modeling the pLMS as a single stage LMS with additional modified inputs, i.e. original input and desired signal subject to a one sample delay. Thus eliminating the need for a second LMS filter and reducing the complexity by half. Similarly, the RC-pLMS transfer function approximation is derived to numerically determine the maximum step size by modeling the input linear combiner as a FIR fractional

delay filter. The RC-pLMS pipeline hardware architecture is obtained through the application of the delay and sum relaxed look ahead techniques (DRC-pLMS) and implemented in finite precision mode. Simulation results, reflected by the MSE and output beam pattern highlight the superior performance of the RC-pLMS, compared to the pLMS and other variants in different SNR environments. Regardless of the adopted approximation, the RC-pLMS presented accelerated convergence, i.e. first 3 iterations, and low steady error while maintaining a low complexity LMS like design. Additionally, hardware simulation show that the finite precision DRC-pLMS achieved similar beam pointing accuracy to the, theoretical, infinite precision. In contrast to the pLMS, synthesis results shows that the DRC-pLMS is obtained at the cost of a marginal, negligible, increase in resource utilization compared to the classical LMS.

# FUNDAMENTALS OF ANTENNA ARRAY BEAMFORMING

#### 2.1 Introduction

In order to better illustrate the advantages of antenna arrays, their geometry and radiation pattern, it is important to first present an overview of the basic concepts of a simple antenna element, i.e. an Hertzian Dipole [26]. The Hertzian Dipole or short dipole, first introduced by Heinrich Hertz in 1886, and is formed of two conductor wires of equal length oriented end-to-end with a center-feeding source for transmitting or receiving RF energy [27, 28]. In order to achieve a greater communication range, in 1895 Macroni introduced a special case of the dipole structure, the vertical antenna, by grounding one end of the conductor wires, hence mono-pole, i.e. half dipole [27]. In theory, simple antenna elements are assumed isotropic radiators, i.e. an element which dissipates equal amount of power P in all directions with a radiation intensity  $U_0 = \frac{P}{4\pi}$  [26]. As such, for an antenna radiating the same amount of power P, the directive gain can be defined as:

$$g = \frac{U}{U_0} = 4\pi \frac{U}{P} \tag{2.1}$$

where U is the practical antenna radiation intensity. From (2.1) we can define the radiation directivity (RD) as a function of the maximum radiation intensity  $U_{max}$  [26], such as:

$$RD = \frac{U_{max}}{U_0} = 4\pi \frac{U_{max}}{P} \tag{2.2}$$

However, for the Hertzian Dipole [26], we have:

$$RD = 1.5 \tag{2.3}$$

It is clear from (2.3) that the radiation directivity for a Hertzian Dipole is a constant and thus uncontrollable. However, to exploit the spatial domain and infer frequency reuse, it is mandatory to have an antenna architecture with a configurable and a controllable beam radiation pattern. Given their proven benefit in providing an electronically steerable beam radiation pattern through the application of adaptive beamforming techniques, antenna arrays can be reliably employed to perform spatial multiplexing and frequency reuse. Thus, in this chapter, we present the popular antenna array geometries as well as the basic concepts of the spatial filtering and beamforming.

# 2.2 Antenna Array Architecture

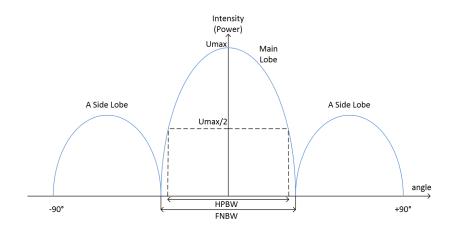

Antenna arrays were introduced to perform beamforming techniques for directional signal transmission and reception. Therefore, a beamforming is achieved by forming a main beam towards the direction of a signal of interest and nulls in the direction of interfering signals [5]. Moreover, the desired radiation pattern is achieved automatically by computing the convenient feeding currents phase and amplitude for each antenna element through the use of an adaptive algorithm. From Figure 2.1, the antenna arrays radiation pattern can be defined as follows [26]:

- Main beam: The main lobe which holds the highest power, i.e. the strongest radiation intensity  $U_{max}$ .

- Side lobes: The side beams acting as a local maxima with a radiation intensity  $U < U_{max}$ .

- Nulls: The angle at which no power or radio waves is radiated.

- Half Power Beam Width (HPBW): The HPBW characterizes the ability of an antenna to direct a beam and represented the 3 dB beamwidth, i.e.  $BW_{3dB}$ . The HPBW angle occupies the intensity region satisfying the condition  $\frac{U_{max}}{2} \leq U \leq U_{max}$ .

- First Null Beam width (FNBW): The FNBW describes the ability of the antenna to attenuate and reject interfering signals. The FNBW angle is formed by the main lobe.

- Side Lobe Level (SLL): The radiation intensity of the highest side lobe with respect to the peak of the main beam.

Figure 2.1 – Antenna Array Radiation Pattern (Cartesian Plot)

For focused transmission, with minimal power loss, it is desirable to decrease the HPBW, i.e. 5° for space communication [26]. With dipole antennas, the decrease in HPBW can only be achieved by increasing the length of the antenna; However, that may generate additional multi-lobes [26]. Consequently, the generated multi-lobes severally degrade the performance for long distance transmission by diminishing the power radiating in the direction of interest [26]. In contrast to dipole antennas, antenna arrays can be electronically configured to construct radiation patterns with specific beamwidth and orientation [26]. As such, different antenna array geometries and structures, i.e. linear, planar and circular, can be built in order to achieve the desired radiation properties [26].

# 2.2.1 Linear Array

The simplest and most popular type of antenna arrays is the linear array. The linear array consists of a number of antenna elements mounted on a straight line and separated

by a spatial distance. For an equally spaced element configuration, the linear array is said to be uniformly spaced and thus the notation uniform linear antenna (ULA). Figure 2.2 presents a ULA of N equally spaced antenna elements [29].

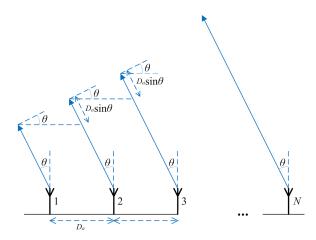

Figure 2.2 – Uniform Linear Antenna Array Structure

For narrow-band complex signals incoming from the far field [30] and with the first antenna element acting as a reference,  $\theta$  is the angle of arrival,  $D_a$  and  $\tau_d$  are the distance and time delay between consecutive antenna elements, respectively. The time delay  $\tau_d$  is given by:

$$\tau_d = \frac{D_a \sin(\theta)}{c} \tag{2.4}$$

where c is the celerity of electromagnetic waves.

Let the input vector,  $\mathbf{x}(k) = [x_1(k), x_2(k), \dots, x_N(k)]^T$ , where N is the number of antenna elements, at the discrete time instant, k, to the narrow-band beamformer be defined by:

$$\mathbf{x}(k) = \mathbf{a}_d s_d(k) + \sum_{l=0}^{N-1} \mathbf{a}_{i,l} \mathbf{i}_l(k) + \mathbf{n}(k)$$

(2.5)

with  $[.]^T$  denotes the matrix transpose,  $s_d(k)$  and  $\mathbf{i}_l(k)$  are, respectively, the desired and interfering signals with l < N,  $\mathbf{a}_d$  and  $\mathbf{a}_{i,l}$  are the  $N \times 1$  complex array steering vector for

the desired signal and for  $l^{th}$  interference, respectively, and  $\mathbf{n}(k)$  stands for the complex additive white Gaussian noise (CAWGN) vector. A general form of  $\mathbf{a}_d$  and  $\mathbf{a}_{i,l}$  is given by:

$$\mathbf{a} = [1, e^{-j\psi}, e^{-j2\psi}, \dots e^{-j(N-1)\psi}]^T$$

(2.6)

where the imaginary number  $j = \sqrt{-1}$  and  $\psi$  is the phase shift of the received signal corresponding to the time delay  $\tau_d$  such as:

$$\psi = 2\pi f_c \tau_d = \frac{2\pi c \tau_d}{\lambda} = 2\pi \frac{D_a \sin(\theta)}{\lambda}$$

(2.7)

where  $\lambda$  is the carrier signal wavelength, of frequency  $f_c$  defined as:

$$\lambda = \frac{c}{f_c} \tag{2.8}$$

Assuming the antenna array is of unity amplitude and zero phase weighting, from (2.6), the array sensitivity response, i.e. array factor (AF), for an angle of arrival (AOA),  $\theta$ , to the acquired signal and its normalized form at unity,  $(AF(\theta))_n$ , can be represented as:

$$AF(\theta) = \sum_{i=1}^{N} e^{-j(i-1)\psi} = \frac{e^{-jN\psi} - 1}{e^{-j\psi} - 1} = \frac{\sin(\frac{N\psi}{2})}{\sin(\frac{\psi}{2})} e^{-\frac{j(N-1)\psi}{2}}$$

(2.9)

$$(AF(\theta))_n = \frac{\sin(\frac{N\psi}{2})}{N\sin(\frac{\psi}{2})}e^{-\frac{j(N-1)\psi}{2}}$$

(2.10)

From (2.10) and [26, 31] the 3 dB beamwidth, can be expressed as:

$$BW_{3dB} = 0.866 \frac{\lambda}{ND_a} \tag{2.11}$$

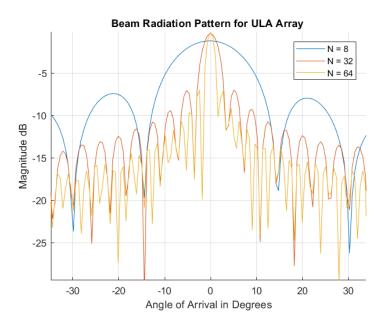

it is clear from (2.11) that the main beams 3 dB beamwidth, i.e. HPBW, is inversely proportional to the number of antenna elements [26]. As shown in Figure 2.3 for N=8, N=32 and N=64 antenna elements, a more accurate and precise pointing beam can be achieved by increasing the number of antenna elements [26]. While (2.11) demonstrated the effect of array elements on the HPBW, its denominator exhibits additional variations dependent on the inter element spacing  $D_a$ .

Figure 2.3 – Beam Radiation Pattern Vs Number of Antenna Elements with an Angle of Arrival of 0° and an Inter Element Spacing of  $D_a = \frac{\lambda}{2}$

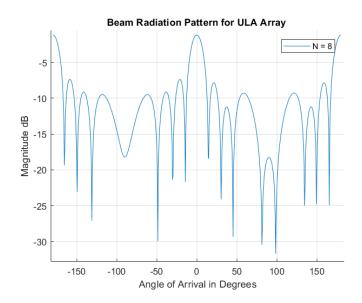

For arrays following custom configuration or design constraints, a maladjustment in inter element spacing can make rise to grating lobes, i.e. array ambiguity and aliasing issues [26]. An example of a grating lobe is shown in Figure 2.4 for a ULA array of N=8 elements with inter element spacing of  $D_a=\frac{\lambda}{2}$ . From figure 2.4, it is clear that the main beam is directed towards the pre-set AOA of 0°; Moreover, the radiation pattern plot shows additional peaks at  $\pm 180^{\circ}$ , respectively. The additional peaks presented are referred to grating lobes and results in array ambiguity and uncertainty towards the true direction of interest [26]. To mathematically illustrate the grating lobes effect, the modulus, |.|, of the normalized array factor is obtained from (2.10) as:

$$|(AF(\theta))_n| = \frac{1}{N} \frac{|\sin(\frac{\pi D_a N \sin(\theta)}{\lambda})|}{|\sin(\frac{\pi D_a N \sin(\theta)}{\lambda})|}$$

(2.12)

thus, for the 90°, Cartesian coordinate, plane, the position of the grating lobes is obtained at  $\max(|(AF(\theta))_n|)$ , i.e. when  $\theta = \arcsin(\frac{n_i\lambda}{D_a})$  where  $n_i \in \{1, 2, ...., N\}$  [26].

Figure 2.4 – ULA array Beam Radiation Pattern for Angle of Arrival 0° and an Inter Element spacing of  $D_a=\frac{\lambda}{2}$

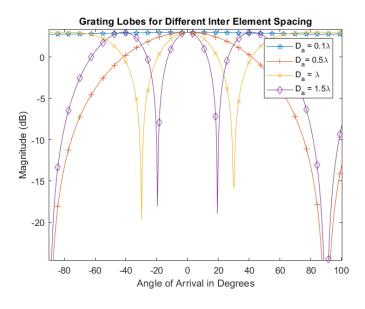

An example of grating lobes for different inter element spacing is shown in Figure 2.5.

Figure 2.5 – Grating Lobes for Different Inter Element Spacing  $D_a$

From the radiation obtained in Figure 2.5, it is clear that the main beam HPBW becomes narrower as the element spacing becomes wider, however for an element spacing  $D_a > 0.5\lambda$  additional lobes appear with and incremental energy as  $D_a$  becomes larger [26].

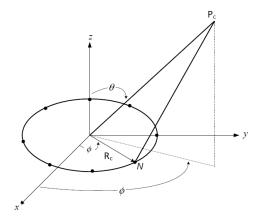

## 2.2.2 Circular Array

In a circular antenna array, the elements are arranged in a circular shape with a radius  $R_c$ . The circular array does not suffer from array ambiguity, produces wider beams and provides full coverage on the azimuth plane [26, 29, 32]. An N elements circular antenna array with radius  $R_c$  is shown in Figure 2.6.

Figure 2.6 – Uniform Circular Array [33]

where  $\phi$  is the azimuth angle and  $\theta$  is the elevation angle and  $P_c$  is a projection point. As such, the new array factor for a circular geometry becomes:

$$AF(\theta,\phi) = \sum_{i=1}^{N_x} e^{-j2\pi \frac{r}{\lambda} sin(\theta)cos(\phi - \frac{2i\pi}{N})}$$

(2.13)

Given its previously stated advantages the circular array is a popular antenna geometry employed in application where the signal of interests is known to arrive from an azimuth angle. However, this configuration is at the cost of higher side lobe levels [29, 32].

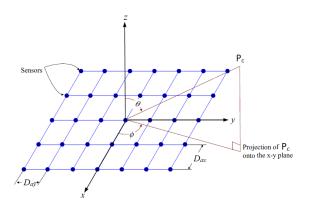

#### 2.2.3 Planar Array

A planar array is a 2D extension of the linear array, i.e. array elements arranged in the x, y plane. A popular planar array configuration is the rectangular array as shown in Figure 2.7.

Figure 2.7 – Uniform Rectangular Array [33]

As shown in Figure 2.7, the planar array is a uniform rectangular array with inter elements spacing of  $D_{ax}$  and  $D_{ay}$ , respectively. The rectangular array is formed of a total of  $N_x \times N_y$  elements, where  $N_x$  is the number of antennas along the x-plane and  $N_y$  is the number of antennas along the y-plane, respectively. In this example, the total number of elements is 24 with  $N_x = 4$  and  $N_y = 6$ . Thus, the overall array factor becomes [26]:

$$AF(\theta,\phi) = \sum_{i=1}^{N_x} \sum_{k=1}^{N_y} e^{-j(i-1)\psi_x} e^{-j(k-1)\psi_y}$$

(2.14)

$$\psi_x = 2\pi \frac{D_{ax}\sin(\theta)\cos(\phi)}{\lambda} \tag{2.15}$$

$$\psi_y = 2\pi \frac{D_{ay}\sin(\theta)\cos(\phi)}{\lambda} \tag{2.16}$$

In contrast to the ULA and the circular array, the planar array allows the production of pencil beams by steering the main beam in the elevation plane as well [26].

# 2.3 Spatial Filtering and Beamforming

Spatial filtering is an inevitable feature of modern wireless communication systems and is used for inferring frequency reuse, limiting interference and providing higher data rates and signal to noise ratio (SNR). An antenna array geometry allows the creation of electronically steerable beams and nulls by specific current feeding and element configuration, i.e. beamforming [26]. The use of a beamforming technique steers the antennas main beam, with constructive amplitude, towards a signal coming from a desired location while directing nulls towards interference, i.e. spatial filtering [2, 26, 30].

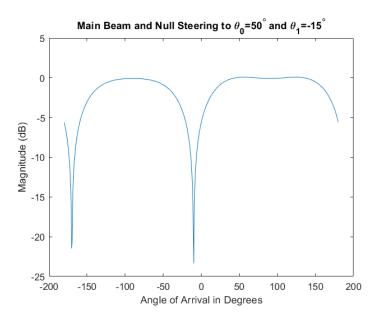

#### 2.3.1 Beam Steering

An efficient form of adaptive beamforming is achieved by connecting the antenna array to a beamformer processor through the use of a signal conditioning circuit and high speed analog to digital (AD) converters [2, 26, 34, 35]. The received signals are spatially sampled and collected by each antenna element, converted to their digital form and fed to the beamformer. Through the use of an adaptive algorithm, with respect to a desired reference signal, the beamformer appropriately weights the input samples to automatically steer the main beam towards the direction of the desired AOA while placing nulls in the direction of interference [2, 4, 26]. The adaptive weighting correctly filters the interfering signals irrespective of their characteristics and AOA [26].

Adaptive arrays controls the main beams and null steering towards specific direction with respect to a reference signal. Beam steering is achieved through appropriate complex weighting, i.e. appropriate setting of the complex amplitude and phase of the feeding currents [26]. The complex weights, for steering control, are of the form  $w_n = \rho_n e^{j\omega_n}$  where  $w_n$  is the complex weight of the  $n^{th}$  antenna element,  $\rho_n$  and  $\omega_n$  are the corresponding amplitude and phase, controlling the main beam and nulls angles, their beamwidth and their side lobe levels, respectively [13, 26].

The main beam steering equation, assuming no noise nor interference, can be written as [26]:

$$\mathbf{w} = \frac{1}{N} \mathbf{a}_d(\theta) \tag{2.17}$$

where **w** is the linear combiner filter weights, the added factor  $\frac{1}{N}$  is a normalization factor to obtain a unity response in the direction of interest. Thus, for a 4 element ULA array, i.e. N=4 with inter element spacing of  $D_a=\frac{\lambda}{2}$  the required weights to steer the main beam towards a desired AOA of  $\theta=30^{\circ}$  can be computed from (2.9) and (2.17), as follows:

$$\mathbf{w} = \frac{1}{4} [1, e^{-j1.5708}, e^{-j3.1416}, e^{-j4.9348}]$$

(2.18)

While the application of (2.17) successfully steers the main beam towards the desired AOA, it does not null any interfering signals.