# Méthodologie d'évaluation d'effets des radiations dans les systèmes numériques: du niveau composant au niveau système

Israel da Costa Lopes

# ▶ To cite this version:

Israel da Costa Lopes. Méthodologie d'évaluation d'effets des radiations dans les systèmes numériques : du niveau composant au niveau système. Electronique. Université Montpellier, 2020. Français. NNT :  $2020 \mathrm{MONTS078}$ . tel-03380468

# HAL Id: tel-03380468 https://theses.hal.science/tel-03380468

Submitted on 15 Oct 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

# **En Electronique**

École doctorale I2S - Information Structures et Systèmes

IES - Institut d'Electronique et des Systèmes

Méthodologie d'évaluation d'effets des radiations dans les systèmes numériques : du niveau composant au niveau système

# Présentée par Israel DA COSTA LOPES

Le 11 Décembre 2020

Sous la direction de Vincent POUGET

# Devant le jury composé de

| M. DUTERTRE Jean-Max | Maitre de Conférences, Ecole des Mines de Saint-Etienne | Rapporteur         |

|----------------------|---------------------------------------------------------|--------------------|

| M. ENTRENA Luis      | Professeur, Université de Madrid                        | Examinateur        |

| M. LEVEUGLE Régis    | Professeur, Grenoble INP, Université Grenoble Alpes     | Rapporteur         |

| M. MILLER Florent    | Ingénieur, Nuclétudes                                   | Examinateur        |

| M. POUGET Vincent    | Chargé de Recherche, CNRS, IES                          | Directeur de thèse |

| M. SAIGNÉ Frédéric   | Professeur, Université de Montpellier, IES              | Examinateur        |

To my family,

# ACKNOWLEDGEMENT

This work has received funding from the European Union's Horizon 2020 research and innovation programme under the Marie-Skolodowska-Curie grant agreement number 721624.

First, I would like to thank Mr. Vincent Pouget for having been an excellent supervisor guiding me so that I could become an excellent researcher as he is. I thank him for his technical, professional and personal advises that I will carry on for the rest of my life. I also would like to thank him for being a real leader not only giving orders but also motivating me during the ambitious and complex 3-year journey of my PhD.

I also thank Mr. Frédéric Saigné for giving me the honor of accepting the function of the president of the jury of my defense.

I would like to thank the reviewers: Mr. Jean Dutertre and Mr. Régis Leveugle for dedicating their time for reviewing my thesis and providing important comments about it.

I also would like to thank the examiners: Mr. Luis Entrena, Mr. Florent Miller and Mr. Frédéric Saigné for having accepted being part of the jury of my defense giving important feedback to my PhD work.

I thank the RADSAGA leader: Mr. Ruben Garcia Alia for his excellent work managing this ambitious project and providing several radiation collective campaigns during my PhD that allowed me to perform different kinds of radiations experiments.

I would like to thank the ChipIR facility staff: Mr. Chris Frost and Mr. Carlo Cazzaniga for their efficient technical support for solving different issues during my first radiation campaign in my PhD. I also would like to thank Andrea Coronetti and Kimmo Niskanen for their support during the experiments.

I also thank the KVI-CART facility staff: Mr. M.J. van Goethem and Mr. Harry Kiewiet for their effort in providing a stable beam and for their technical support during the protons experiments. I also would like to thank Andrea Coronetti and Daniel Söderström for their support.

I thank the Mr. Tadec Marine for his support in different situations, such as providing the equipment, doing conference registration, managing the radiation safety, and for his technical support during the X-ray experiments in the PRESERVE facility of our institute.

I would like to thank the RADIAC group in general for the good environment to work, important feedback during meeting and technical support.

I strongly thank my family for supporting me financially and emotionally, and for educating me and showing the importance of education, respect, empathy and honesty.

I also thank my PhD colleagues for sharing good moments and giving me support to different issues: Matthias Carneiro, Ygor Aguiar, Arthur Vallet, Cathrine Ngom, Hoang Nguyen, Salvatore Galliardo, Kimmo Niskanen, Samir Boursin, Thomas Borel, Pierre Pallet, Alex Mendes, Thomasz Rajkowski and all the other involved and not mentioned here.

## LIST OF ACRONYMS

ACE - Architectural Correct Execution **DSP - Digital Processing Processor DUE - Detected Unrecoverable Errors** ADC - Analog-to-Digital Converter **AEC - Automotive Electronics Council ECC - Error Correction Code** AES - Advanced Encryption Standard **EEPROM - Electrical Erasable Programmable** Read-Only Memory AHB - Advanced High-performance Bus EIA - Electronic Industries Alliance AMP - Asymmetric Multiprocessing ELF - Executable and Linkable Format APB - Advanced Peripheral Bus EM - Electromigration APU - Application Processing Unit eMMC - embedded Multimedia Card AVF - Architecture Vulnerability Factor EPROM - Erasable Programmable Read-Only AXI - Advanced eXtensible Interconnect Memory AXIS - Advanced eXtensible Interface Stream ESCC - European Space Components Coordination **BRAM - Block Random Access Memory** ESD - Electrostatic Discharge BSP - Board Support Package **ESP - Emission of Solar Protons** BT - Bias Temperature instability FBGA - Fine Pitch Ball Grid Array **CB** - Carrier Board FF - Flip-Flop CCI - Cache-Coherent Interconnect FIFO - First-in-First-out CERN - European Organization for Nuclear FIR - Finite-Impute-Response Filter Research FMECA - Failure Mode, Effects and Criticality CLB - Configurable Logic Block Analysis CME - Coronal Mass Ejections FPD - Full-Power Domain CMOS - Complementary Metal-Oxide-FPGA - Field Programmable Gate Array Semiconductor FSBL - First Stage Boot Loader CoM - Computer-on-Module FSM - Finite-State Machine COOT - Constant On/Off Time GCR - Galactic Cosmic Ray COTS - Commercial-Off-The-Shelf GEO - Geostationary orbit **CPU - Central Processing Unit** GLE - Ground Level Enhancement **CRAM - Configurable Rand Access Memory GP - Geometry Processor** DCDC - Direct Current to Direct Current GPIO - General Purpose Input-Output DDR - Double Data Rate **GPU - Graphics Processing Unit DFSR - Data Fault Status Register HCI - Hot Carrier Injection DMA - Direct Access Memory HEH - High Energy Hadrons** DRAM - Dynamic Random Access Memory

| HKMG - High-k Metal Gate                          | MLC - Multi Level Cell                             |

|---------------------------------------------------|----------------------------------------------------|

| HMI - Human Machine Interface                     | MMCM - Mixed-Mode Clock management                 |

| HPC - High Performance Computing                  | MPSoC - Multi-Processor System-on-chip             |

| HPS - Hard Processing System                      | NIST - National Institute of Standards and         |

| HTOL - High Temperature Operation Life            | Technology                                         |

| IO - Input/output                                 | NoC - Network-on-Chip                              |

| I2C - Inter-Integrated Circuit                    | NVM - Non-Volatile Memory                          |

| IC - Integrated Circuit                           | OCM - On-chip-Memory                               |

| IDDQ - Supply Voltage Quiescent Current           | OPAL - ONERA Proton Altitude Low                   |

| IDDT - Supply Voltage Transient Current           | OS - Operating System                              |

| IEC - International Electrotechnical Commission   | PCB - Printed Circuit Board                        |

| IES - Institute d'Électronique et des Systèmes    | PCI - Peripheral Component Interconnect            |

| IL - Instrumentation Level                        | PE - Processing Element                            |

| IP - Intellectual Property                        | PFM - Pulse-Frequency Modulation                   |

| IRPP - Integral Rectangular Parallel Piped        | PID - Proportional-Integral-Derivative             |

| ISO - International Organization for              | PL - Programmable Logic                            |

| Standardization                                   | PLL - Phase-Locked Loop                            |

| JEDEC - Joint Electron Device Engineering Council | PoP - Package-on-package                           |

| JTAG - Joint Test Action Group                    | PP - Pixel Processors                              |

| KVI-CART - KVI Center for Advanced Radiation      | PQFN - Power Quad Flat No-Lead                     |

| Technology                                        | PS - Processing System                             |

| LEO - Low Earth orbit                             | PSoC - Programmable System-on-chip                 |

| LET - Linear Energy Transfer                      | PSYCHIC - Prediction of Solar Particles Yields for |

| LHC - Large Hadron Collider                       | Characterizing Integrated Circuits                 |

| LPD - Low-power domain                            | PWM - Pulse-Width-Modulation                       |

| LUT - Look-up Table                               | QSPI - Quad Serial Peripheral Interface            |

| LUTRAM - Look-up Table Random Access Memory       | Rad-hard - Radiation-hardened                      |

| MBU - Multi Bit Upset                             | RAM - Random Access Memory                         |

| MCU - Microcontroller Unit                        | RDM - Radiation Design Margins                     |

| MCU - Multiple Cell Upset                         | RHA - Radiation Hardness Assurance                 |

| MDB - Mission Database                            | RILC - Radiation Induced Leakage Current           |

| MEO - Medium Earth orbit                          | RISC - Reduced Instruction Set Computer            |

|                                                   | RO - Ring Oscillator                               |

| MIO - Multiplex Input Output                      | ROI - Region of interest                           |

SO-DIMM - Small Outline Dual In-line Memory **ROM - Read-Only Memory** Module **RPU - Real-time Processing Unit** SOI - Silicon-on-Insulator RTL - Register Transfer Level SoM - System-on-Modules SAA - South Atlantic Anomaly SPA - Single Photon Absorption SBC - Board Computer SRAM - Static Rand Access Memory SBU - Single Bit-Upset STI - Shallow Trench Insolation SDC - Silent Data Corruption SUT - System Under Test SDK - Software Development Kit TCM - Tightly Coupled Memory SDR - Single Data Rate TDDB - Time Dependent Dielectric Breakdown SDRAM - Synchronous Dynamic Random Access **TEM - Transmission Electron Microscopy** Memory SEAM - Systems Engineering and Assurance TID - Total Ionizing Dose Modeling TTL - Transistor-Transistor Logic SEB - Single Event Burn-Out UART - Universal Asynchronous Receiver SEE - Single Event Effects Transmitter SEFI - Single Event Functional Interrupt UART - Universal Asynchronous Receiver-Transmitter SEL - Single Event Latch-up USB - Universal Serial Bus SEP - Solar Energetic Particle VCU - Video Control Unit SET - Single Event Transient VHDL - Very High Speed Integrated Circuit SEU - Single Event Upset Hardware Description SILC - Stress Induced Leakage Current WCA - Worst Case Analysis SiP - System-in-Package WFE - Work Function Engineering SLC - Single Level Cell XSDB - Xilinx Software Debugger SMU - Source and Measurement Unit Z7 - Zynq7000 SoC - System-on-Chip ZU+ - ZynqUltrascale+

# TABLE OF CONTENTS

| ACK  | NOWLEDO   | GEMENT                                                          | 5  |

|------|-----------|-----------------------------------------------------------------|----|

| LIST | OF ACRO   | NYMS                                                            | 7  |

| RÉSI | JMÉ EN FI | RANÇAIS                                                         | 13 |

| 1.   | INTRODU   | JCTION                                                          | 19 |

| 2.   | RADIATIO  | ON AND AGING EFFECTS ON DIGITAL SYSTEMS                         | 21 |

| 2.   | 1. DIGI   | TAL SYSTEMS                                                     | 21 |

|      | 2.1.1.    | Modern CMOS technology process                                  | 21 |

|      | 2.1.2.    | Components of typical digital embedded systems                  | 23 |

|      | 2.1.3.    | System platform solutions for aerospace and ground applications | 28 |

| 2.   | 2. RAD    | IATION EFFECTS                                                  | 31 |

|      | 2.2.1.    | Radiation environments                                          | 31 |

|      | 2.2.2.    | Particle-component interaction                                  | 36 |

|      | 2.2.3.    | Single Event Effects                                            | 40 |

|      | 2.2.4.    | Total Ionizing Dose                                             | 47 |

|      | 2.2.5.    | Commercial-of-the-shelf vs hardened components                  | 50 |

| 2.   | 3. AGII   | NG MECHANISMS IN CMOS TECHNOLOGIES                              | 51 |

|      | 2.3.1.    | Bias Temperature Instability                                    | 51 |

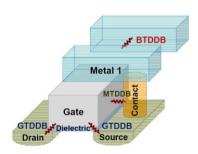

|      | 2.3.2.    | Time-Dependent-Dielectric-Breakdown                             | 52 |

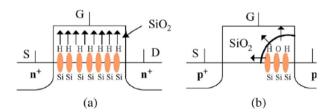

|      | 2.3.3.    | Hot Carrier Injection                                           | 53 |

|      | 2.3.4.    | Electromigration                                                | 54 |

|      | 2.3.5.    | Coupled effects                                                 | 54 |

| 2.   | 4. Con    | clusions                                                        | 55 |

| 3.   | CASE STU  | JDY DEVELOPMENT AND INSTRUMENTATION                             | 57 |

| 3.   | 1. Targ   | et System-On-Modules                                            | 57 |

|      | 3.1.1.    | System-on-chips                                                 | 58 |

|      | 3.1.2.    | DDR SDRAM memories                                              | 62 |

|      | 3.1.3.    | Flash memories                                                  | 63 |

|      | 3.1.4.    | DC-DC converters                                                | 64 |

| 3.   | 2. Dev    | elopment tools                                                  | 65 |

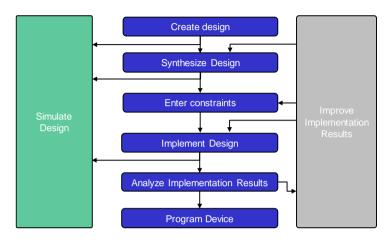

|      | 3.2.1.    | SoC FPGA design tool                                            | 65 |

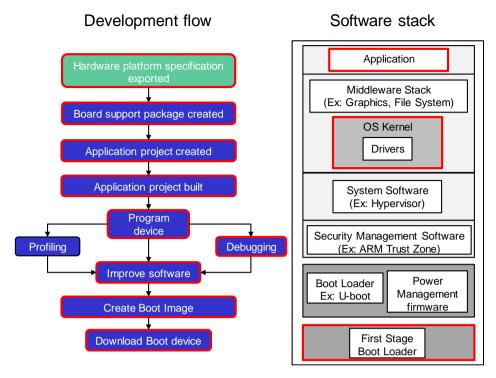

|      | 3.2.2.    | Software Development tools                                      | 65 |

| 3.   | 3. Emb    | edded Application                                               | 67 |

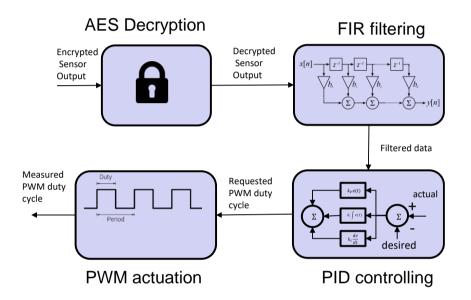

|      | 3.3.1.    | SEE Space and Aviation application                              | 67 |

|      | 3.3.2.    | SEE Benchmark application                                       | 73 |

|      | 3.3.3.    | TID and Aging Benchmark application                             | 75 |

| 3.   | 4. Test   | ability and data analysis on system-level radiation testing     | 79 |

| 3.4.2. Impact of limited observability on root cause analysis 3.5. Software Instrumentation 3.5.1. Computation verification and control flow checking 3.5.2. Instrumentation levels 3.6. Test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | 3.4  | 4.1.    | Testing metrics on radiation and aging testing          | 79  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|---------|---------------------------------------------------------|-----|

| 3.5.1. Computation verification and control flow checking 3.5.2. Instrumentation levels 3.6. Test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.4.2. |      | 4.2.    | Impact of limited observability on root cause analysis  | 80  |

| 3.5.2. Instrumentation levels. 3.6. Test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | 3.5. | Soft    | ware Instrumentation                                    | 81  |

| 3.6. Test setup 3.6.1. Generic test setup 3.6.2. Test script 3.7. Carrier boards 3.7.1. Custom carrier board PCB design 3.7.2. Commercial carrier board 3.8. Conclusions 4. RADIATION EXPERIMENTS 4.1. Experiment objectives and chronology 4.2. Package test considerations on the target hardware systems 4.3. Atmospheric neutrons experiments 4.3.1. Facility parameters 4.3.2. Experimental setup 4.3.3. Test methodology 4.3.4. Results 4.4. High energy protons experiments 4.4.1. Facility parameters 4.4.2. Experimental setup 4.4.3. Test methodology 4.4.4. 27 result presentation 4.4.5. 27 proton result discussion 4.4.6. ZU+ result presentation 4.4.7. ZU+ proton result discussion 4.5. X-ray experiments 4.5.1. Facility parameters 4.5.2. Experimental setup 4.5.3. Test methodology 4.5.4. Results presentation 4.5.5. TID results analysis 4.6. Laser experiments 4.6.1. Facility parameters |        | 3.5  | 5.1.    | Computation verification and control flow checking      | 81  |

| 3.6.1. Generic test setup 3.6.2. Test script 3.7. Carrier boards 3.7.1. Custom carrier board PCB design 3.7.2. Commercial carrier board 3.8. Conclusions. 4. RADIATION EXPERIMENTS 4.1. Experiment objectives and chronology. 4.2. Package test considerations on the target hardware systems. 4.3.1. Facility parameters 4.3.2. Experimental setup 4.3.3. Test methodology. 4.3.4. Results 4.4.1. Facility parameters 4.4.2. Experimental setup 4.4.3. Test methodology. 4.4.4. Zr result presentation 4.4.5. Z7 proton result discussion 4.4.6. ZU+ result presentation 4.5. X-ray experiments 4.5.1. Facility parameters 4.5.2. Experimental setup 4.5.3. Test methodology 4.5.4. Results presentation 4.5.5. TiD results presentation 4.5.6. Laser experiments 4.6.1. Facility parameters                                                                                                                     |        | 3.5  | 5.2.    | Instrumentation levels                                  | 84  |

| 3.6.2. Test script 3.7. Carrier boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 3.6. | Test    | setup                                                   | 86  |

| 3.7. Carrier boards 3.7.1. Custom carrier board PCB design 3.7.2. Commercial carrier board 3.8. Conclusions 4. RADIATION EXPERIMENTS 4.1. Experiment objectives and chronology 4.2. Package test considerations on the target hardware systems 4.3. Atmospheric neutrons experiments 4.3.1. Facility parameters 4.3.2. Experimental setup 4.3.3. Test methodology 4.3.4. Results 4.4. High energy protons experiments 4.4.1. Facility parameters 4.4.2. Experimental setup 4.4.3. Test methodology 4.4.4. 27 result presentation 4.4.5. 27 proton result discussion 4.4.6. ZU+ result presentation 4.7. ZU+ proton result discussion 4.5. X-ray experiments 4.5.1. Facility parameters 4.5.2. Experimental setup 4.5.3. Test methodology 4.5.4. Results presentation 4.5.5. TiD results analysis 4.6. Laser experiments 4.6.1. Facility parameters 4.6.1. Facility parameters                                     |        | 3.6  | 6.1.    | Generic test setup                                      | 86  |

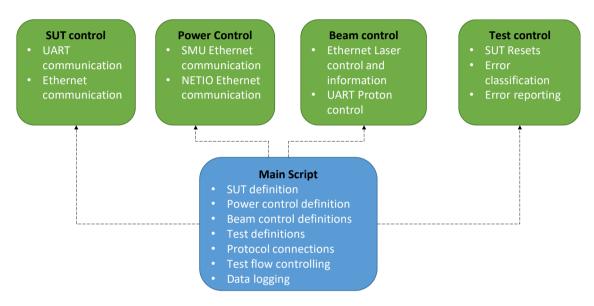

| 3.7.1. Custom carrier board PCB design. 3.7.2. Commercial carrier board. 3.8. Conclusions. 4. RADIATION EXPERIMENTS. 4.1. Experiment objectives and chronology. 4.2. Package test considerations on the target hardware systems. 4.3. Atmospheric neutrons experiments. 4.3.1. Facility parameters. 4.3.2. Experimental setup. 4.3.3. Test methodology. 4.3.4. Results 4.4. High energy protons experiments. 4.4.1. Facility parameters. 4.4.2. Experimental setup. 4.4.3. Test methodology. 4.4.4. 27 result presentation 4.4.5. 27 proton result discussion. 4.4.6. ZU+ result presentation 4.7. ZU+ proton result discussion. 4.8.5. X-ray experiments. 4.5.1. Facility parameters 4.5.2. Experimental setup. 4.5.3. Test methodology. 4.5.4. Results presentation. 4.5.5. TiD results analysis 4.6. Laser experiments 4.6.1. Facility parameters.                                                             |        | 3.6  | 6.2.    | Test script                                             | 87  |

| 3.7.2. Commercial carrier board. 3.8. Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | 3.7. | Carr    | ier boards                                              | 87  |

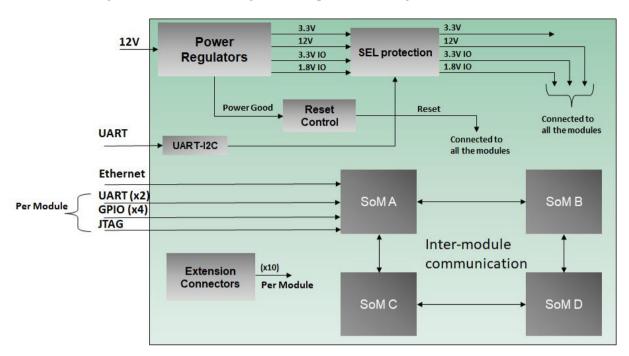

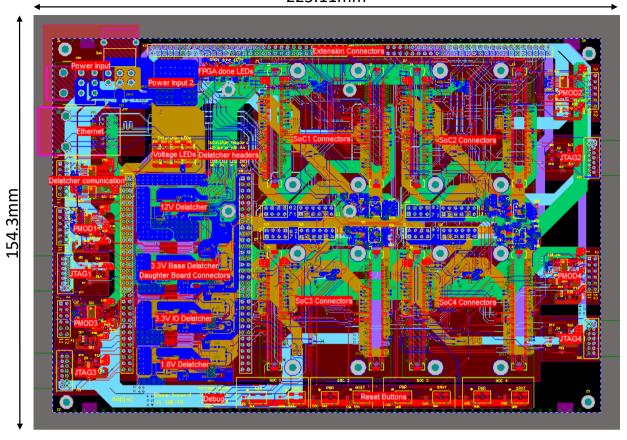

| 3.8. Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        | 3.7  | 7.1.    | Custom carrier board PCB design                         | 88  |

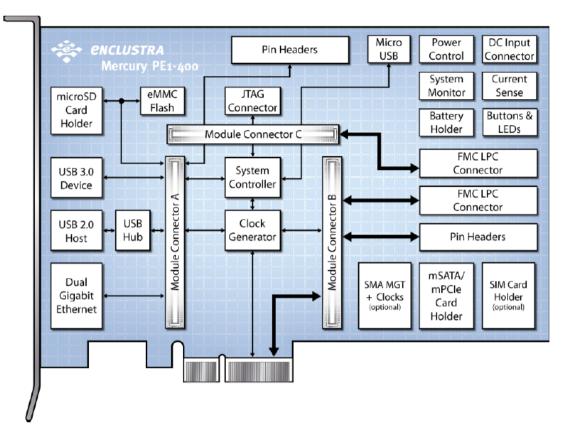

| 4.1. Experiment objectives and chronology 4.2. Package test considerations on the target hardware systems 4.3. Atmospheric neutrons experiments 4.3.1. Facility parameters 4.3.2. Experimental setup 4.3.3. Test methodology 4.3.4. Results 4.4. High energy protons experiments 4.4.1. Facility parameters 4.4.2. Experimental setup 4.4.3. Test methodology 4.4.4. Z7 result presentation 4.4.5. Z7 proton result discussion 4.4.6. ZU+ result presentation 4.5. X-ray experiments 4.5.1. Facility parameters 4.5.2. Experimental setup 4.5.3. Test methodology 4.5.4. Results presentation 4.5.5. TID results analysis 4.6. Laser experiments 4.6.1. Facility parameters 4.6.1. Facility parameters                                                                                                                                                                                                            |        | 3.7  | 7.2.    | Commercial carrier board                                | 90  |

| 4.1. Experiment objectives and chronology 4.2. Package test considerations on the target hardware systems 4.3. Atmospheric neutrons experiments 4.3.1. Facility parameters 4.3.2. Experimental setup 4.3.3. Test methodology 4.3.4. Results 4.4. High energy protons experiments 4.4.1. Facility parameters 4.4.2. Experimental setup 4.4.3. Test methodology 4.4.4. Z7 result presentation 4.4.5. Z7 proton result discussion 4.4.6. ZU+ result presentation 4.5. X-ray experiments 4.5.1. Facility parameters 4.5.2. Experimental setup 4.5.3. Test methodology 4.5.4. Results presentation 4.5.5. TID results analysis 4.6.1. Facility parameters 4.6.1. Facility parameters 4.6.1. Facility parameters                                                                                                                                                                                                        |        | 3.8. | Con     | clusions                                                | 91  |

| 4.2. Package test considerations on the target hardware systems.  4.3. Atmospheric neutrons experiments.  4.3.1. Facility parameters.  4.3.2. Experimental setup.  4.3.3. Test methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.     | RA   | ADIATIO | ON EXPERIMENTS                                          | 93  |

| 4.3.1. Facility parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 4.1. | Expe    | eriment objectives and chronology                       | 93  |

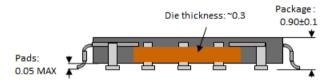

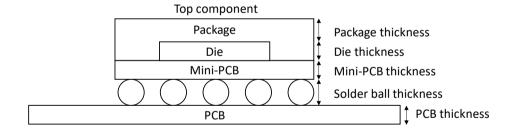

| 4.3.1. Facility parameters  4.3.2. Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 4.2. | Pacl    | kage test considerations on the target hardware systems | 94  |

| 4.3.2 Experimental setup 4.3.3 Test methodology 4.3.4 Results 4.4. High energy protons experiments 4.4.1 Facility parameters 4.4.2 Experimental setup 4.4.3 Test methodology 4.4.4 Z7 result presentation 4.4.5 Z7 proton result discussion 4.4.6 ZU+ result presentation 4.7 ZU+ proton result discussion 4.5 X-ray experiments 4.5.1 Facility parameters 4.5.2 Experimental setup 4.5.3 Test methodology 4.5.4 Results presentation 4.5.5 TID results analysis 4.6 Laser experiments 4.6.1 Facility parameters 4.6.1 Facility parameters                                                                                                                                                                                                                                                                                                                                                                        |        | 4.3. | Atm     | ospheric neutrons experiments                           | 95  |

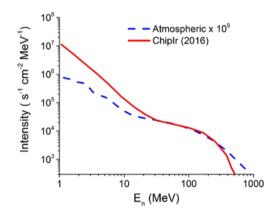

| 4.3.3. Test methodology 4.3.4. Results  4.4. High energy protons experiments 4.4.1. Facility parameters 4.4.2. Experimental setup 4.4.3. Test methodology 4.4.4. Z7 result presentation 4.4.5. Z7 proton result discussion 4.4.6. ZU+ result presentation 4.4.7. ZU+ proton result discussion 4.5. X-ray experiments 4.5.1. Facility parameters 4.5.2. Experimental setup 4.5.3. Test methodology 4.5.4. Results presentation 4.5.5. TID results analysis 4.6.1. Facility parameters 4.6.1. Facility parameters                                                                                                                                                                                                                                                                                                                                                                                                   |        | 4.3  | 3.1.    | Facility parameters                                     | 95  |

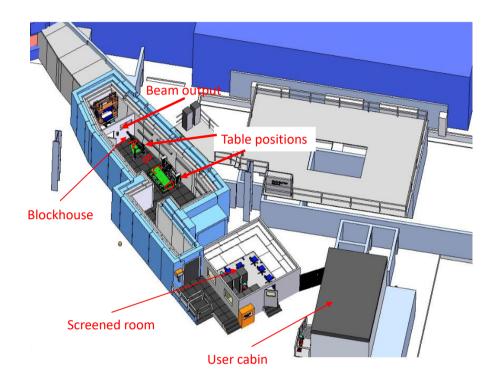

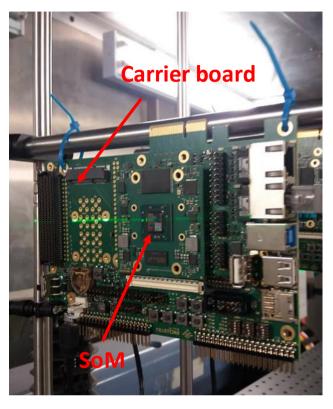

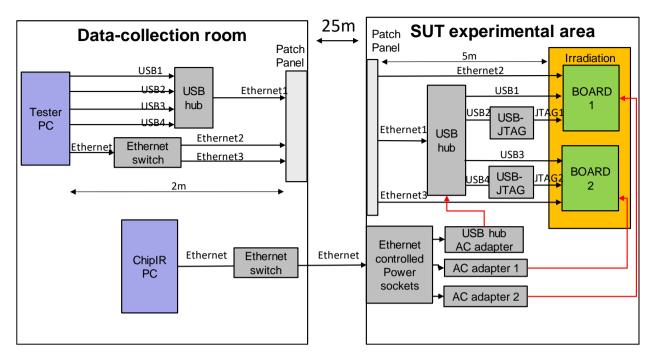

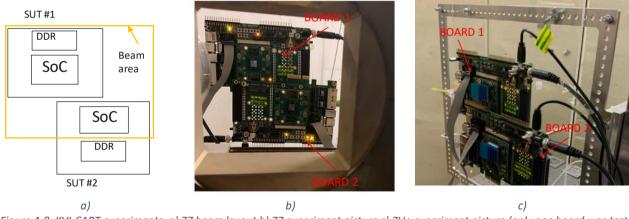

| 4.3.4. Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4      |      | 3.2.    | Experimental setup                                      | 97  |

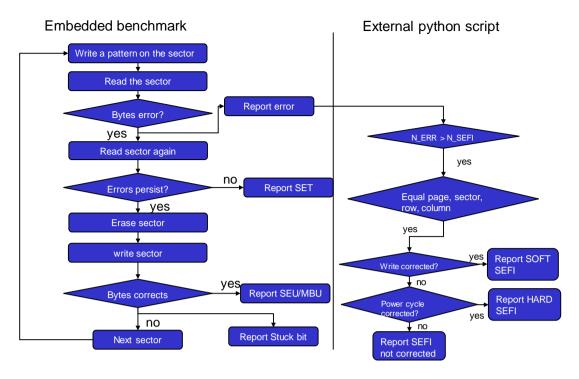

| 4.4.1. Facility parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 4.3  | 3.3.    | Test methodology                                        | 98  |

| 4.4.1. Facility parameters  4.4.2. Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 4.3  | 3.4.    | Results                                                 | 100 |

| 4.4.2. Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 4.4. | High    | n energy protons experiments                            | 102 |

| 4.4.3. Test methodology 4.4.4. Z7 result presentation 4.4.5. Z7 proton result discussion 4.4.6. ZU+ result presentation 4.4.7. ZU+ proton result discussion 4.5. X-ray experiments 4.5.1. Facility parameters 4.5.2. Experimental setup 4.5.3. Test methodology 4.5.4. Results presentation 4.5.5. TID results analysis 4.6.1. Facility parameters 4.6.1. Facility parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 4.4  | 4.1.    | Facility parameters                                     | 102 |

| 4.4.4. Z7 result presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 4.4  | 4.2.    | Experimental setup                                      | 102 |

| 4.4.5. Z7 proton result discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | 4.4  | 4.3.    | Test methodology                                        | 103 |

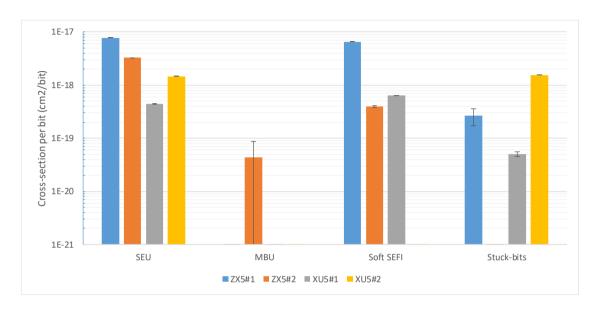

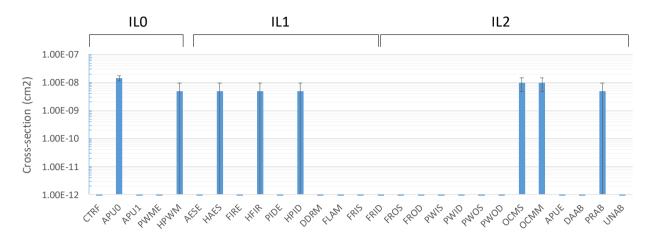

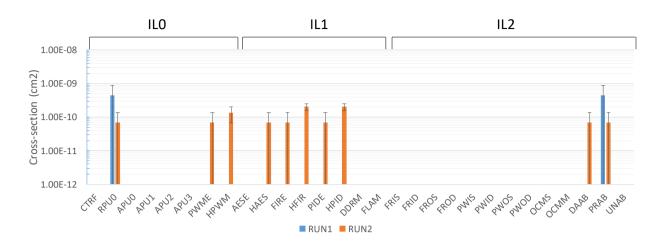

| 4.4.6. ZU+ result presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | 4.4  | 4.4.    | Z7 result presentation                                  | 105 |

| 4.4.7. ZU+ proton result discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | 4.4  | 4.5.    | Z7 proton result discussion                             | 107 |

| 4.5. X-ray experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 4.4  | 4.6.    | ZU+ result presentation                                 | 109 |

| 4.5.1. Facility parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 4.4  | 4.7.    | ZU+ proton result discussion                            | 109 |

| 4.5.2. Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 4.5. | X-ra    | y experiments                                           | 110 |

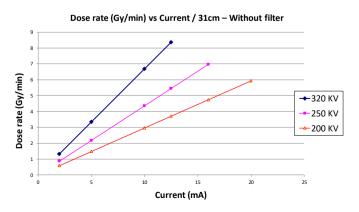

| 4.5.3. Test methodology  4.5.4. Results presentation  4.5.5. TID results analysis  4.6. Laser experiments  4.6.1. Facility parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 4.5  | 5.1.    | Facility parameters                                     | 110 |

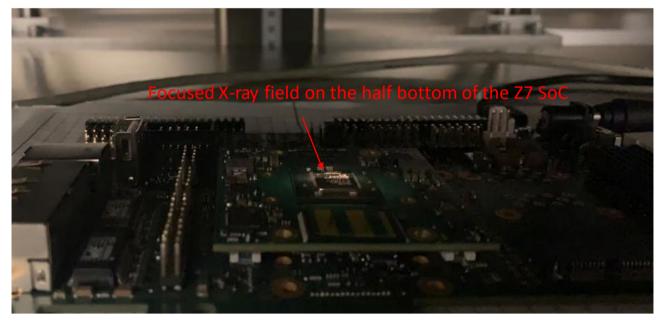

| 4.5.4. Results presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | 4.5  | 5.2.    | Experimental setup                                      | 111 |

| 4.5.5. TID results analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | 4.5  | 5.3.    | Test methodology                                        | 112 |

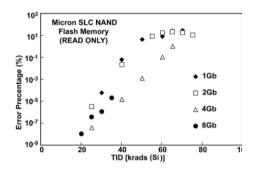

| 4.6. Laser experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 4.5  | 5.4.    | Results presentation                                    | 113 |

| 4.6.1. Facility parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 4.5  | 5.5.    | TID results analysis                                    | 117 |

| 4.6.1. Facility parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 4.6. | Lase    | er experiments                                          | 118 |

| 4.6.2. Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 4.6  |         |                                                         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | 4.6  | 6.2.    | Experimental setup                                      | 119 |

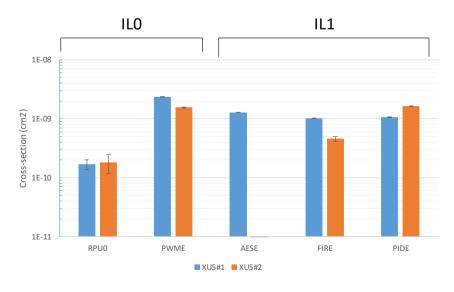

| 4.6.3. Test methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 4.0  | 6.3.    | Test methodology                                        | 120 |

|      | 4.6                                       | 5.4.  | Results and discussion                                            | . 122 |

|------|-------------------------------------------|-------|-------------------------------------------------------------------|-------|

|      | 4.7.                                      | Con   | clusions                                                          | 123   |

| 5.   | BRI                                       | IDGIN | G METHODOLOGY DISCUSSION AND PROPOSAL                             | . 125 |

|      | 5.1.                                      | Guio  | delines and recommendations for system-level test                 | 125   |

|      | 5.1                                       | .1.   | Experiment preparation                                            | 125   |

|      | 5.1                                       | 2.    | Experiment execution                                              | 128   |

|      | 5.2.                                      | Prop  | oosed bridging methodology from component to system-level         | 130   |

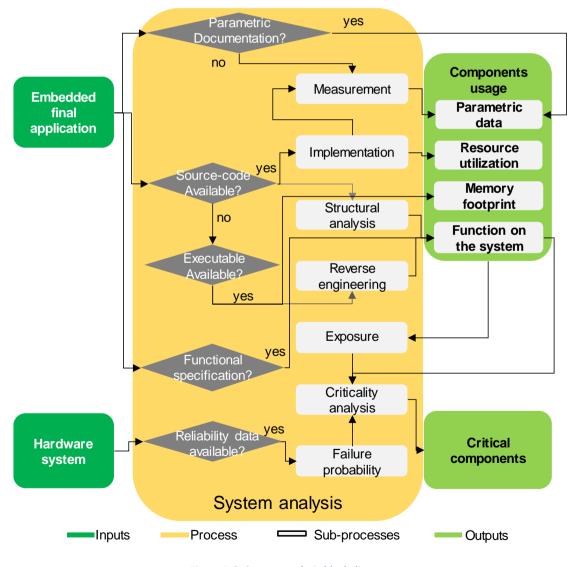

|      | 5.2                                       | .1.   | System analysis                                                   | 130   |

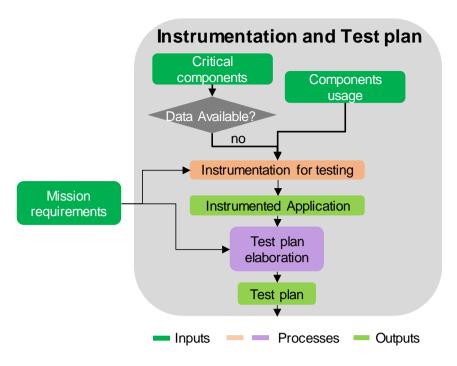

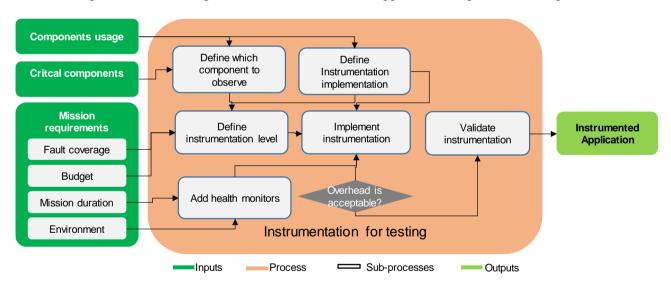

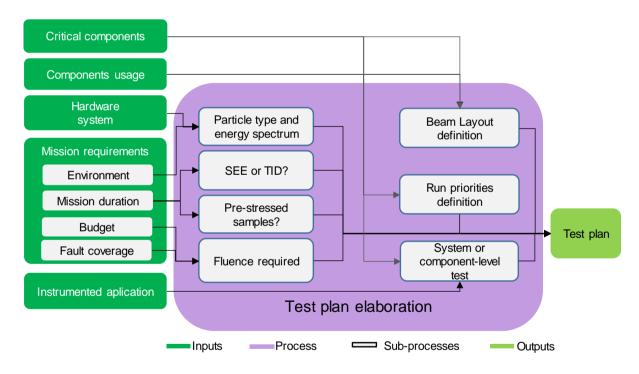

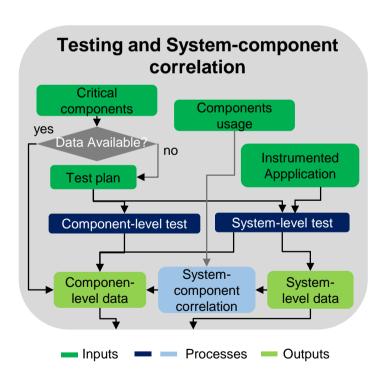

|      | 5.2                                       | .2.   | Instrumentation for testing and test plan elaboration             | 132   |

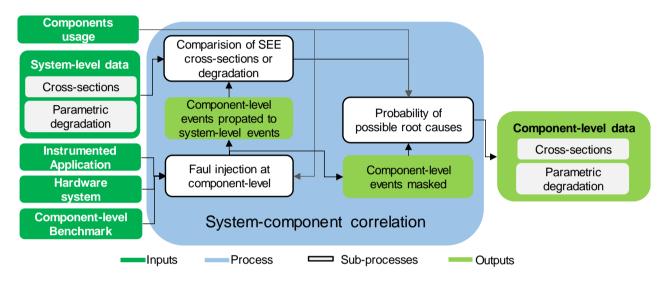

|      | 5.2                                       | .3.   | Radiation experiments and data analysis                           | 136   |

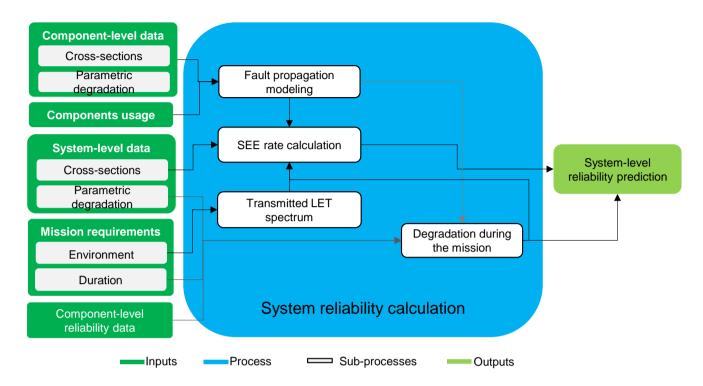

|      | 5.2                                       | .4.   | System-level reliability calculation                              | 139   |

|      | 5.2                                       | .5.   | Methodology summary                                               | 140   |

|      | 5.2                                       | .6.   | Limitations and possible improvements of the proposed methodology | 140   |

|      | 5.3.                                      | Met   | hodology case study discussion                                    | 142   |

|      | 5.4.                                      | Con   | clusions                                                          | 144   |

| 6.   | СО                                        | NCLUS | SIONS AND PROSPECTIVE                                             | 147   |

| 7.   | REI                                       | FEREN | CES                                                               | 149   |

| Α.   | API                                       | PENDI | X                                                                 | 166   |

|      | A.1.                                      | TID   | benchmark details                                                 | 166   |

|      | A.2.                                      | Neu   | trons experiment details                                          | 166   |

| A.3. |                                           | Prot  | ons experiment details                                            | 167   |

|      | A.4.                                      | Lase  | r experiment details                                              | 168   |

| Lie  | st of Publications and Communications 171 |       |                                                                   |       |

# RÉSUMÉ EN FRANÇAIS

Les investissements d'initiative privée dans les applications aérospatiales augmentent chaque année dans ce qu'on appelle le New Space [SVWD18]. Récemment, SpaceX est devenue la première entreprise privée à lancer des humains sur l'orbite terrestre. Dans le même temps, sur le terrain, l'intelligence artificielle nécessaire au fonctionnement des voitures autonomes [SAMS18] pousse les exigences de performance et les contraintes de puissance sur les dispositifs informatiques, conduisant la mise à l'échelle des technologies nanoélectroniques au plus près de la limite d'échelle atomique [TSMC20].

Afin de rester compétitifs et de satisfaire les exigences de leurs clients, les fabricants de systèmes doivent intégrer les dernières générations de *Commercial-Off-The-Shelf* (COTS) [BKAQ15]. Compte tenu de la complexité et du coût de la conception et de la qualification des cartes de circuits imprimés (ou PCB de l'anglais *Printed Circuit Board*) pour des composants complexes, il existe également un intérêt croissant pour l'utilisation de cartes ou de modules commerciaux à faible coût qui incluent déjà tous les circuits périphériques requis par ces composants.

Dans les domaines qui nécessitent des niveaux de fiabilité très élevés, comme les industries spatiales ou automobiles, la contrainte spécifique des environnements radiatifs doit être prise en compte. En effet, les circuits intégrés exposés aux radiations peuvent faire face à différents types de perturbations ou de pannes induites par l'interaction des particules avec leurs matériaux. Par conséquent, la fiabilité des circuits intégrés doit être caractérisée en utilisant des méthodologies d'assurance de la résistance aux radiations (RHA de l'anglais *Radiation Hardness Assurance*).

Depuis de nombreuses années, les méthodologies standard des RHA ont consisté à tester les différents composants d'un système en présence de sources de radiation ou de faisceaux de particules et d'analyser leur réponse afin de quantifier la fiabilité de chaque composant individuellement [ESA14][DOD95]. La fiabilité sous radiations au niveau système est ensuite estimée dans une approche ascendante [SCSD13]. Du point de vue des tests, cette approche classique est appelée approche au niveau composant. Elle permet de mieux comprendre le comportement des différents composants du système lorsqu'ils sont exposés à des radiations. Les résultats au niveau composant peuvent également être réutilisés pour différents systèmes et applications ou extraits de la littérature, ce qui réduit le coût de l'expérience.

Néanmoins, l'approche au niveau des composants présente plusieurs inconvénients. Le temps de faisceau de particules nécessaire pour tester chaque composant est coûteux, tout comme le développement de bancs de test spécifiques pour chaque génération de composant. L'ensemble du processus prend du temps, augmente le temps d'accès au marché (time-to-market) des applications industrielles et est devenu incompatible avec le rythme de renouvellement des technologies. Combinés à l'impossibilité de tester des composants complexes de manière exhaustive [JEDE06] et à la tendance à utiliser les *Systems-Off-The-Shelf* (systèmes sur étagère) comme briques élémentaires de systèmes plus grands, ces inconvénients rendent l'approche au niveau des composants de moins en moins attractive de nos jours. Idéalement, les fabricants de systèmes souhaiteraient être en mesure de qualifier un système pour un environnement radiatif en effectuant un seul test de l'ensemble du système sous radiations. Cela donne lieu à une méthodologie RHA émergente :

l'approche au niveau système [GUGU17] [SGPB18][RASB17]. Dans cette approche, comme son nom l'indique, l'ensemble du système matériel intégrant son application logicielle finale doit être caractérisé simultanément. Ainsi, le temps de faisceau et les coûts de développement du banc de test associés à de nombreuses campagnes de radiation pour différents composants seraient réduits et la réponse aux radiations au niveau système pourrait être directement obtenue. De toute évidence, les tests sous radiations et la prévision de la fiabilité ne sont pas si simples, et il existe actuellement de nombreuses limitations ou questions techniques qui nécessitent des réponses pour qu'une telle approche au niveau système soit utilisable et adoptée par l'industrie. C'est l'un des objectifs du projet européen RADSAGA, piloté par le CERN, de contribuer à la normalisation de l'approche au niveau système pour les tests sous radiations.

L'objectif de ce travail, dans le contexte du projet RADSAGA, est d'étudier la possibilité de définir une approche intermédiaire qui combinerait le concept de test au niveau système avec les connaissances et pratiques existantes des méthodologies RHA au niveau composant. Cette approche constituerait au moins une première étape, et éventuellement une passerelle vers une future méthodologie de test au niveau système. Ainsi, dans ce travail, nous étudions la définition d'une méthodologie de transition du niveau composant au niveau système pour l'évaluation des effets des radiations dans le cas particulier des systèmes numériques, et plus particulièrement dans le cas des systèmes-sur-module commerciaux (SoM de l'anglais *System-on-Module*).

Nous présentons dans un premier temps l'état de l'art des effets des radiations et d'autres problèmes de fiabilité des composants numériques, ainsi que les méthodologies actuelles de test sous radiations au niveau composant. Dans la première section, une approche ascendante est utilisée pour présenter les systèmes numériques à partir du processus de fabrication jusqu'aux solutions de systèmes numériques. Dans la deuxième section, une approche ascendante est également utilisée pour expliquer les effets des radiations sur les systèmes numériques en décrivant les différents environnements, l'interaction particule-composant et les effets des radiations au niveau transistor, composant et système. Les méthodologies classiques et émergentes pour caractériser ces effets et garantir la résistance aux radiations des systèmes numériques sont décrites. Les limites de la méthodologie de test classique au niveau composant sont signalées, telles que les exigences de préparation des échantillons. En ce qui concerne la nouvelle méthodologie de test au niveau système, les exigences sur les moyens d'irradiation pour tester différentes classes de systèmes numériques sont énumérées, telles que l'homogénéité du faisceau, la pénétration élevée et la grande taille du faisceau. Enfin, les principaux éléments constitutifs des méthodologies RHA prenant en compte les effets d'événement unique (SEE de l'anglais *Single-Event-Effects*) et la dose ionisante totale (TID de l'anglais *Total-Ionizing-Dose*) sont expliqués.

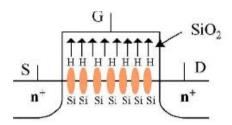

La troisième et dernière section décrit brièvement le principal mécanisme de vieillissement qui peut affecter la fiabilité des systèmes numériques et leur sensibilité aux radiations, dont l'instabilité thermique (BTI de l'anglais *Bias-Temperature-Instability*), la rupture diélectrique en fonction du temps (TDDB de l'anglais *Time-Dependent-Dielectric-Breakdown*), l'injection de porteurs chauds (HCI de l'anglais *Hot-Carrier-Injection*) et l'électromigration (EM). Ensuite, les effets possibles du vieillissement sur la sensibilité à radiation (et réciproquement), les effets dits couplés, sont brièvement présentés. Enfin, nous expliquons comment ce contexte motive le développement de nouvelles méthodologies RHA orientées vers les tests au niveau système, en particulier pour les applications à faible coût ou haut risque acceptable.

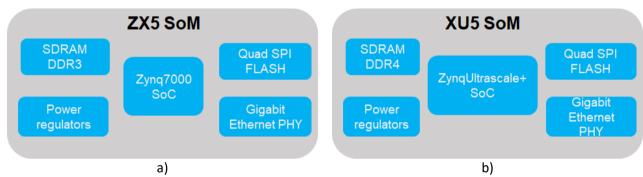

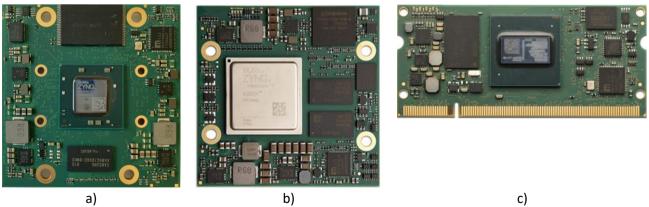

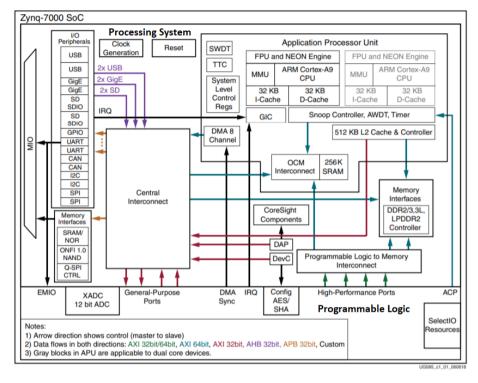

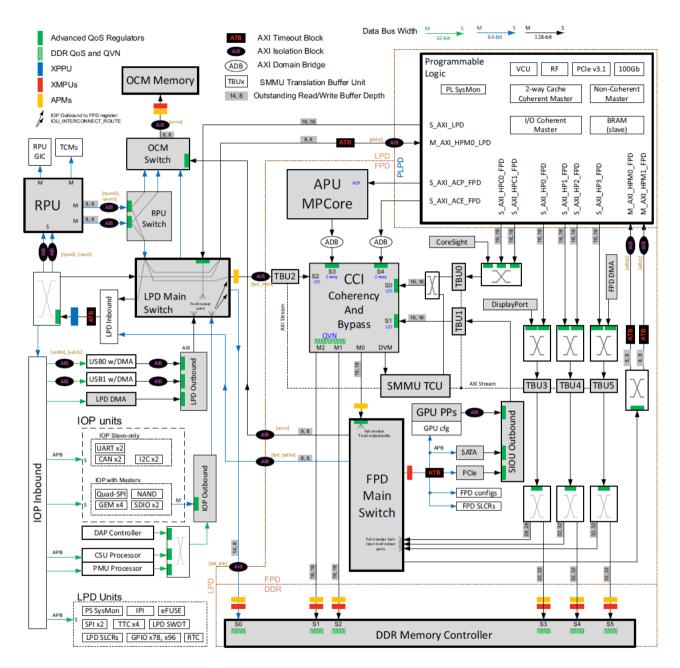

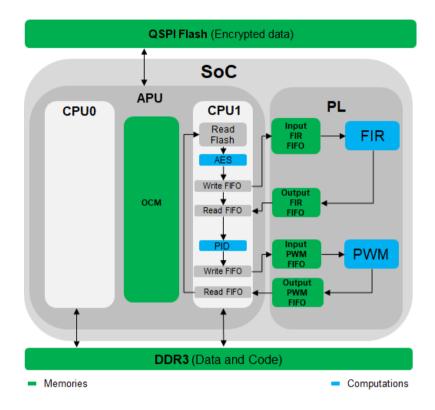

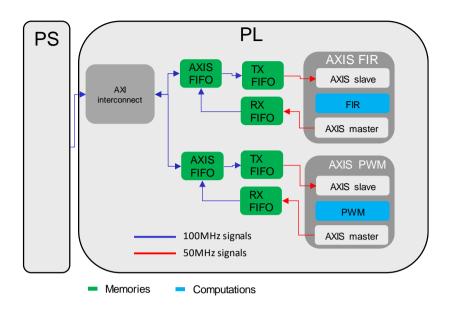

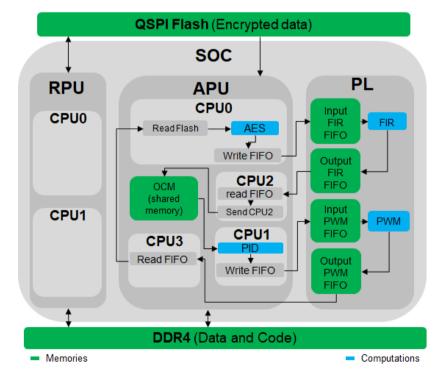

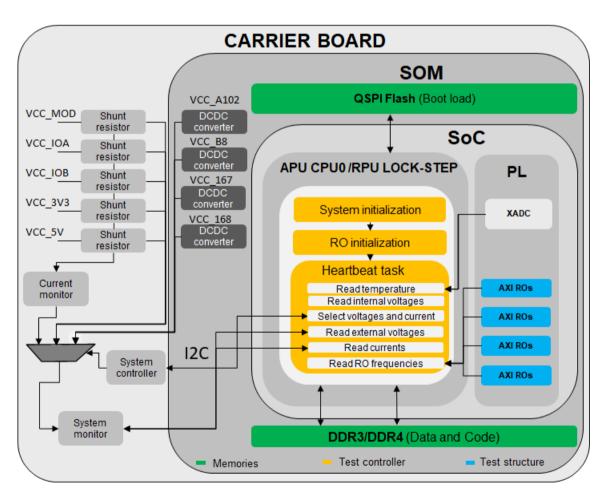

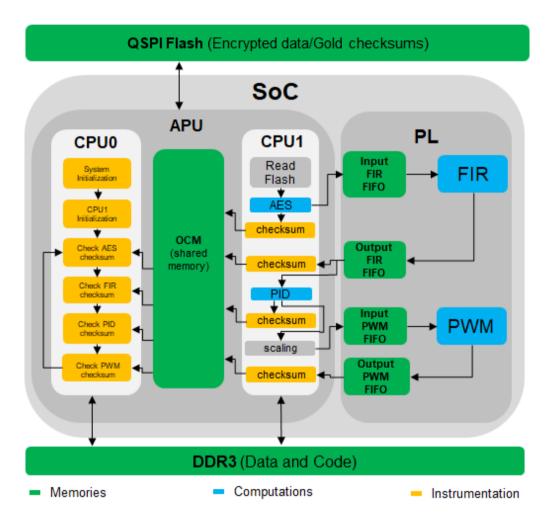

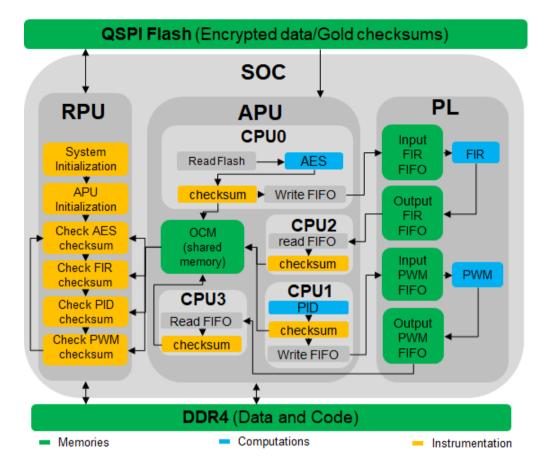

Le chapitre suivant présente le système numérique et une application spécifique que nous avons conçue comme une étude de cas pour ce travail. Une application finale destinée à être représentative de systèmes numériques aérospatiaux simples a été développée et mise en œuvre sur des SoM industriels commerciaux basés sur des SoC récents en 28nm Planar et 16 FinFET CMOS. L'ancienne technologie SoM comprend les SoC Zynq7000 (Z7) et DDR3 et les SoM les plus récents incluent les mémoires DDR4 et SoC ZynqUltrascale+ (ZU+).

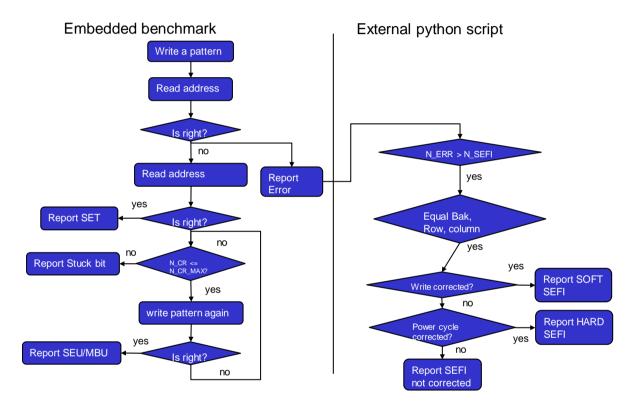

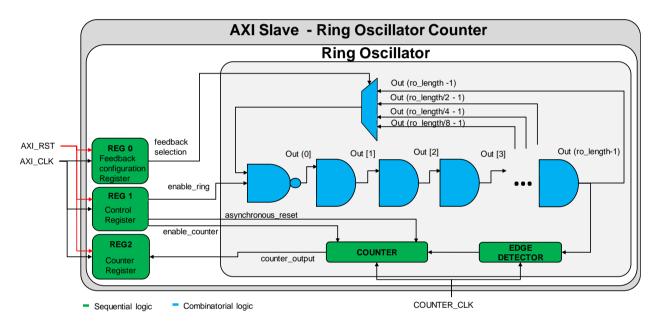

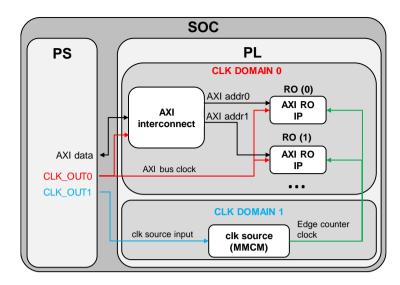

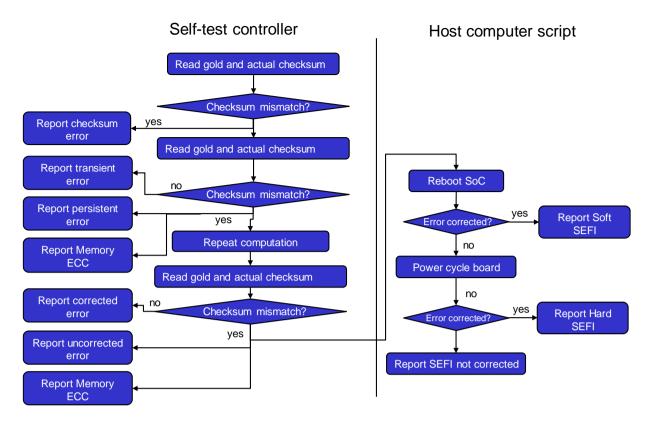

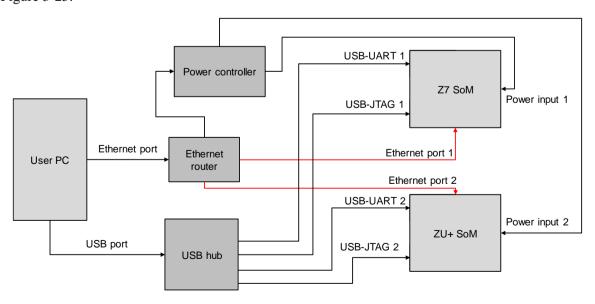

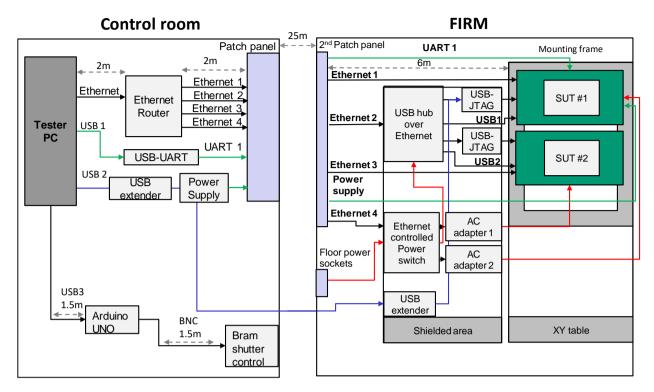

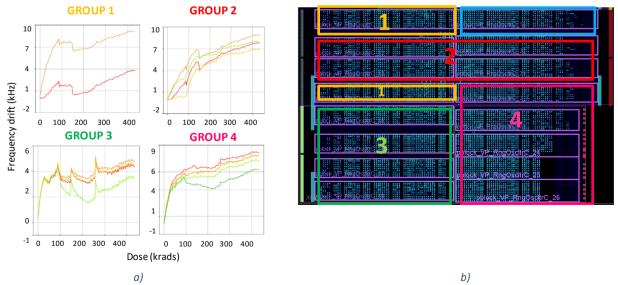

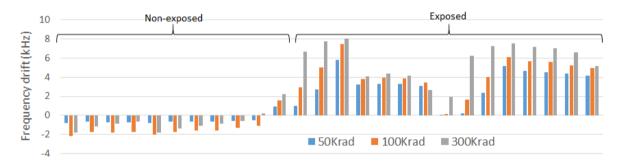

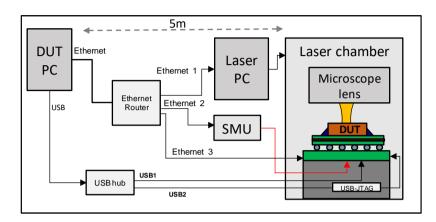

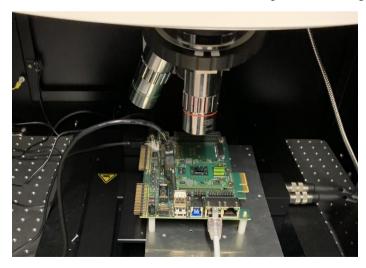

Le concept d'instrumentation, dans le cadre de ce travail, est introduit, consistant à insérer des blocs de code, des blocs IP (de l'anglais *Intelectual-Property*) ou des modifications matérielles mineures pour augmenter l'observabilité du système lors des tests au niveau système. Ainsi, le code et les blocs IP d'instrumentation qui ont été ajoutés à l'application finale afin d'améliorer l'observabilité des expériences SEE et TID, sont détaillés et discutés. Des détails de mise en œuvre du banc expérimental sont également fournis, tels que les scripts Python pour le contrôle du faisceau, du banc expérimental et du système sous test (SUT de l'anglais System-Under-Test), ainsi que la carte mère dédiée qui a été conçue et la carte mère commerciale utilisée pour opérer les SoMs.

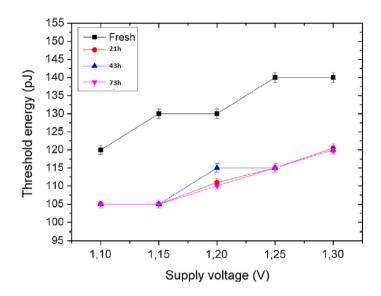

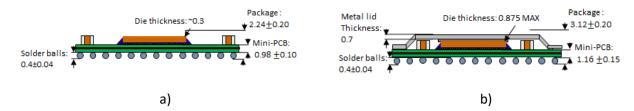

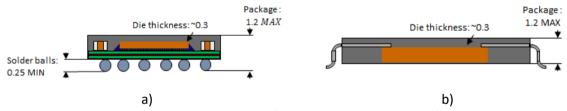

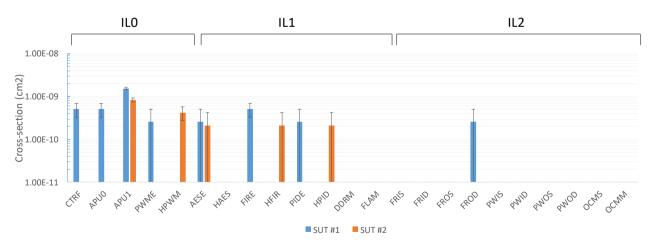

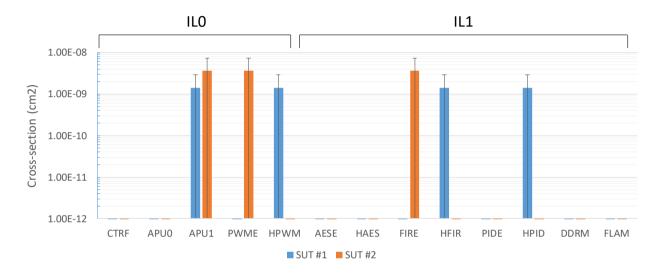

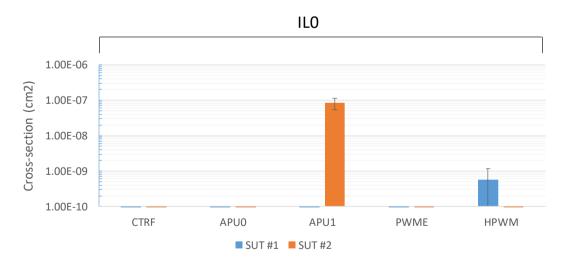

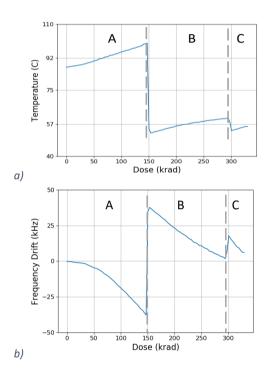

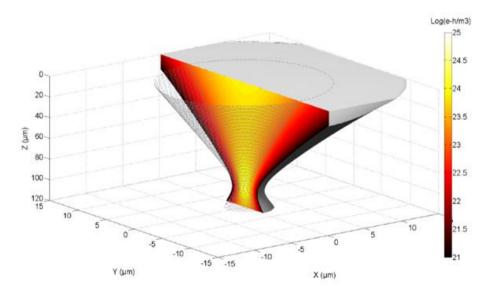

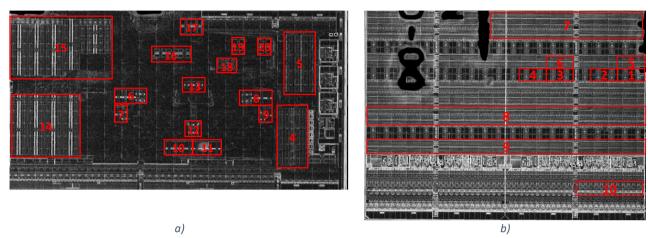

Le troisième chapitre présente les différentes campagnes de tests sous radiations qui ont été réalisées, au sein du consortium RADSAGA, afin d'accumuler des données pour évaluer la fiabilité de nos systèmes. Dans la première expérience, des neutrons atmosphériques ont été utilisés dans lequel un prototype de l'application finale et le logiciel de test de mémoire développé par le fabricant ont été utilisés pour effectuer une analyse de premier ordre des événements observables au niveau système et de sa corrélation avec les événements au niveau des composants. Ensuite, des expériences sous protons de 184MeV ont été menées sur des versions améliorées de l'application finale et de l'instrumentation, permettant d'observer davantage d'évènements.. Afin d'obtenir des données TID sur le composant le plus complexe du système (SoC), une irradiation localisée sous rayons X a été réalisée pour comparer la dégradation des performances de la logique programmable (PL de l'anglais *Programmable-Logic*) des deux technologies étudiées. Enfin, les résultats des protons ont été mieux analysés en irradiant les ressources processeurs (PS de l'anglais *Processing-System*) et configurables (PL, programmable logic) des SoC à l'aide d'un laser impulsionnel à 1064 nm. Les résultats sont présentés et discutés. Ils confirment que les tests avec des protons de haute énergie devraient être la méthode à privilégier pour le test SEE des systèmes à faible coût.

Le dernier chapitre résume les leçons tirées de nos campagnes de tests au niveau système. La préparation de l'expérience comprend une bonne élaboration du plan de test, un banc expérimental fiable et une instrumentation validée. Ensuite, de bonnes pratiques lors des tests au niveau système sont proposées, telles que l'augmentation des niveaux d'irradiation, de l'exposition du système et de l'observabilité.

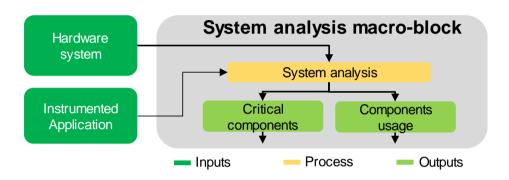

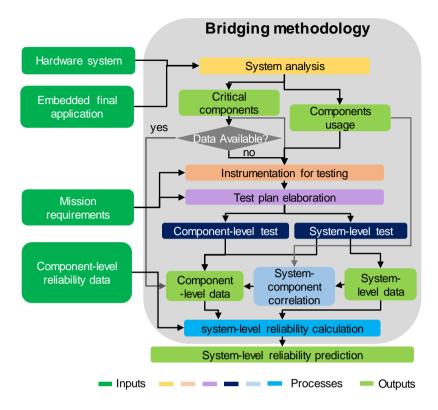

Par la suite, une méthodologie passerelle qui pourrait être appliquée pour l'évaluation de la sensibilité aux radiations de systèmes similaires est proposée. La méthodologie de transition commence par l'analyse du système qui consiste à identifier les composants critiques et l'utilisation des composants. Ensuite, le système est instrumenté et le plan de test est élaboré en fonction de l'utilisation des composants, des composants critiques et des exigences de la mission telles que le budget et le profil de la mission. Ensuite, des

caractérisations sous radiations sont effectuées en suivant les recommandations décrites précédemment. Une étape importante est la corrélation composant-système qui vise à obtenir des données au niveau composant à partir de données au niveau système. Enfin, les données au niveau composant et système sont utilisées pour calculer et prédire la fiabilité au niveau système. Une étude de cas d'estimation de la fiabilité a été présentée, considérant l'utilisation de nos systèmes dans une mission LEO-ISS.

En ce qui concerne l'analyse de la cause originelle des pannes au niveau système, il existe actuellement une bonne quantité de données expérimentales sous radiations disponibles dans la littérature qui peuvent aider concernant les mémoires externes telles que les composants DDR et Flash. Cela peut s'expliquer par le fait que ces composants sont relativement simples à tester de manière exhaustive sous radiations, ce qui n'est pas le cas des processeurs, FPGA, microcontrôleurs... Ainsi, l'enjeu sur les systèmes numériques est de comprendre comment et où les défauts sont générés sur ces composants complexes. Dans cette mesure, le laser impulsionnel et les irradiations locales sous rayons X permettent une meilleure compréhension des mécanismes de défaillance et de dégradation de ces composants. Ces techniques contribuent à valider et à améliorer les modèles de génération et de propagation des évènements et, par conséquent, la qualité des prévisions de fiabilité du système.

La méthodologie de transition proposée tente de faire une utilisation optimale des données, des outils et des méthodes existants issus de l'approche classique au niveau composant. Une contribution importante de ce travail est liée à la conception et à l'insertion d'instrumentation à l'application embarquée finale afin d'améliorer considérablement l'observabilité des différents types d'événements lors des tests au niveau système. L'instrumentation doit être considérée comme un moyen d'avoir un aperçu à l'intérieur de la «boîte noire» du système. La version finale du code d'instrumentation permet cela tout en ajoutant une faible taille de code et sans impact notable sur les performances de l'application. L'exploration des capacités de contrôle et de correction intégrées aux composants a montré qu'elles représentaient également un moyen efficace d'instrumentation à faible coût. De plus, la mise en œuvre d'un logiciel flexible de test TID et vieillissement ont permis d'observer et de comparer la dégradation paramétrique des deux technologies testées sous la dose totale. De telles informations sont rares dans la littérature et revêtent une grande importance pour les concepteurs de FPGA travaillant sur des conceptions avec des critères de performance élevés pour des applications spatiales.

Plusieurs pistes ont été identifiées pour améliorer la méthodologie proposée. Développer la portabilité de l'instrumentation sur différentes architectures FPGA et processeurs permettrait de généraliser l'approche. Des outils pourraient être développés afin d'automatiser l'insertion de l'instrumentation logicielle et matérielle. Nous avons également observé la nécessité d'une norme spécifique aux radiations pour la classification et la notification des événements au niveau système observés au cours d'un test au niveau système afin de faciliter la réutilisation partielle de ces données.

La prédiction des taux de SEE au niveau système à partir des tests au niveau système est une tâche complexe et la méthodologie de transition proposée utilisant à la fois les tests au niveau système et l'analyse au niveau composant est un premier pas vers cet objectif. Afin d'étendre la méthodologie à une gamme plus

large de systèmes et d'applications, davantage d'études de cas et d'options d'instrumentation devraient être étudiées. En outre, une extension possible de la méthodologie proposée pourrait inclure la surveillance des effets couplés des radiations et du vieillissement. En effet, à ce jour, ces effets couplés sont généralement pris en compte en augmentant les marges de conception des systèmes, ce qui a des implications importantes tant au niveau économique que sur celui des performances.

## 1. INTRODUCTION

The private initiative investments in aerospace applications are increasing every year in what is called New Space [SVWD18]. Recently, SpaceX became the first private company to launch humans into the Earth orbit. At the same time, on the ground, the artificial intelligence required for operating autonomous cars [SAMS18] is pushing the performance requirements and the power constraints on computing devices, driving the scaling of nanoelectronics technologies close to the atomic scale limit [TSMC20].

In order to stay competitive and satisfy their customer requirements, systems manufacturers need to integrate recent generations of Commercial-Off-The-Shelf (COTS) [BKAQ15]. Considering the complexity and cost of designing and qualifying printed circuit boards (PCBs) for complex components, there is also a growing interest in using low-cost commercial boards or modules that already include all the peripheral circuitry required by those components.

In domains that require very high levels of reliability, like the space or automobile industries, the specific constraint of radiation environments has to be considered. Indeed, integrated circuits exposed to radiation can face different kinds of perturbations or failures induced by the interaction of particles with their materials. Therefore, the reliability of integrated circuits should be characterized by using Radiation Hardness Assurance (RHA) methodologies.

For many years, standard RHA methodologies have consisted in testing the different components of a system in the presence of radiation sources or particle beams and analyzing their response in order to quantify the reliability of each component individually [ESA14][DOD95]. The system-level reliability under radiation is then estimated in a bottom-up approach [SCSD13]. From a testing point of view, this classical approach is called the component-level approach. It allows a better understanding of how the different components of the system behave when exposed to radiation. The component-level results can also be reused for different systems and applications or extracted from the literature reducing the experiment cost.

Nonetheless, the component-level approach has several disadvantages. The particle beam time required for testing each component is expensive, as is the development of specific testbenchs for each generation of component. The whole process is time-consuming, increasing the time-to-market for industrial applications, and has become incompatible with the pace of renewal of the technologies. Combined with the impossibility to test exhaustively complex components [JEDE06] and with the trend to use Systems-Off-The-Shelf as the elementary bricks of larger systems, those disadvantages make the component-level approach less and less attractive nowadays. Ideally, systems manufacturers would like to be able to qualify a system for a radiation environment by performing a single radiation test on the whole system. This gives rise to an emerging RHA methodology: the system-level approach[GUGU17][SGPB18][RASB17]. In this approach, as the name implies, the whole hardware system embedding its final software application should be characterized simultaneously. Thus, the beam time and testbench development costs associated to many radiation campaigns for different components would be reduced and the system-level response to radiation could be directly obtained. Obviously, radiation testing and reliability prediction are not so simple, and there are currently many technical limitations or questions that require answers for such system-level approach to be usable and adopted

by the industry. It is one the objectives of the European RADSAGA project, driven by the CERN, to contribute to the standardization of the system-level approach for radiation testing.

The objective of this work, in the context of the RADSAGA project, is to investigate the possibility to define an intermediate approach that would combine the concept of system-level testing with the existing knowledge and practices of component-level RHA methodologies. This approach would constitute at least a first step, and possibly a gateway towards a future system-level testing methodology. Thus, in this work, we investigate the definition of a bridging methodology from component to system-level for the assessment of radiation effects in the particular case of digital systems, and more specifically in the case of commercial System-on-Modules.

In the first chapter, the state-of-the-art of the radiation effects and aging mechanisms on digital systems will be introduced. We will present the technologies and components used in digital systems as well as the radiation environments and their effects on integrated circuits. The current test and RHA methodologies will be discussed.

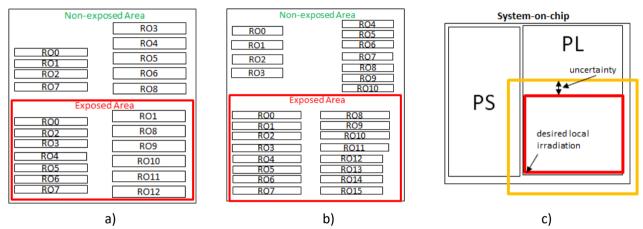

The second chapter will present the technical details of the system that we designed using recent technologies as a case study for this work. The hardware targets, i.e. the System-on-Modules (SoM) under test, as well as the embedded software application will be described. The instrumentation that was added to the system and that constitutes an essential element of our bridging methodology will be detailed, and its benefits and impacts discussed.

The next chapter will present the different radiation testing campaigns that were performed on our system using neutrons, protons, X-ray and laser beams. The experimental results will be synthetized and discussed.

Based on the lessons learned during those campaigns, the last chapter will summarize our guidelines and recommendations for performing system-level experiments. Then, the elements of a bridging methodology will be presented for evaluating the reliability of a system under radiation from system-level testing. The methodology will be applied to our case-study before discussing its limitations and the possible paths for improvement.

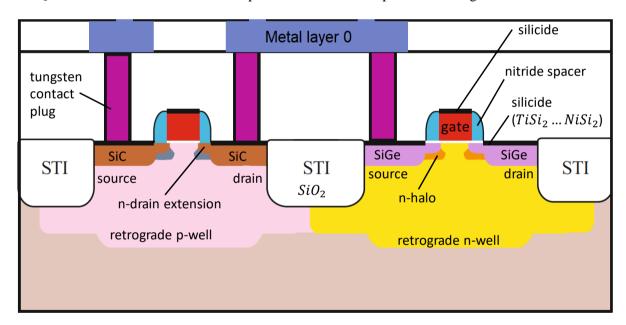

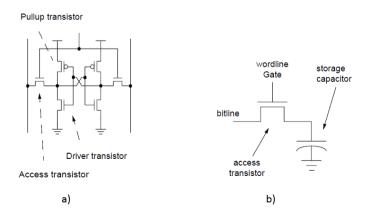

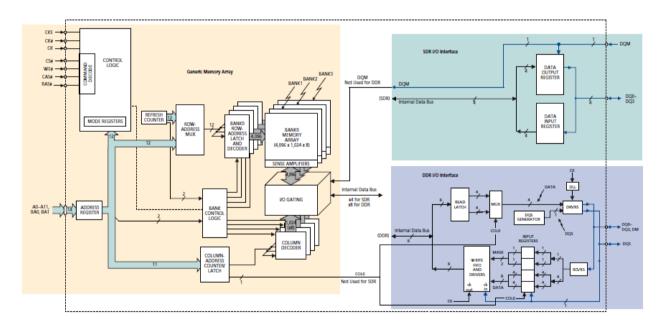

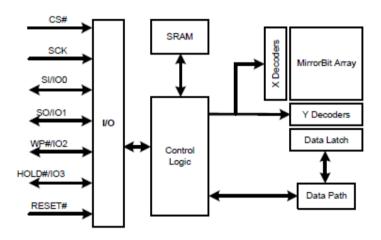

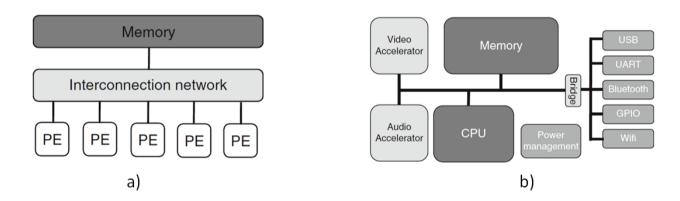

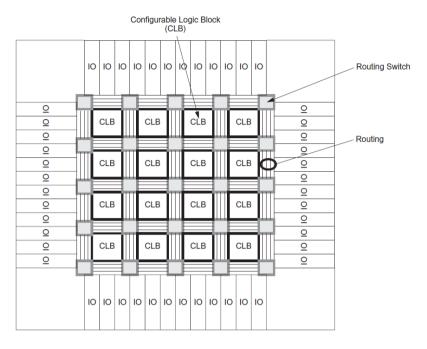

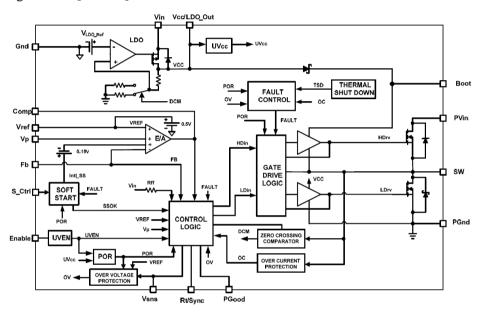

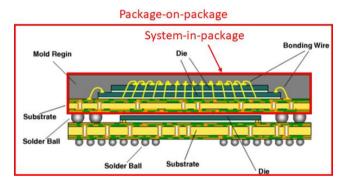

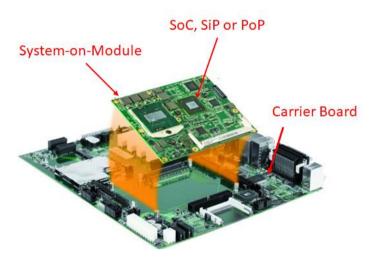

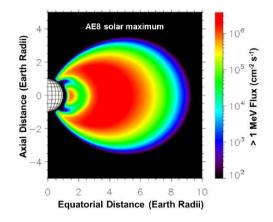

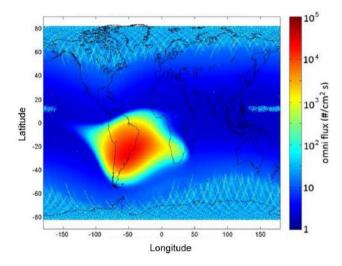

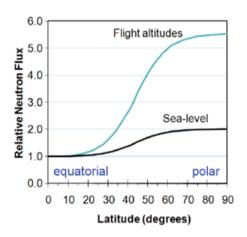

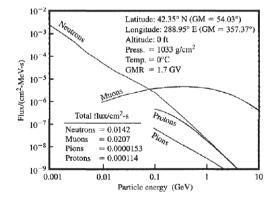

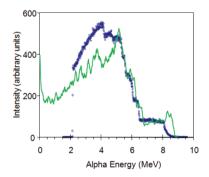

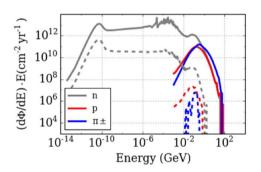

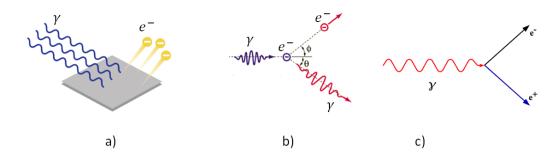

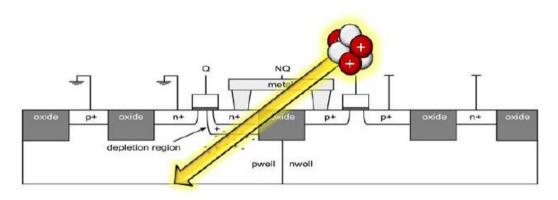

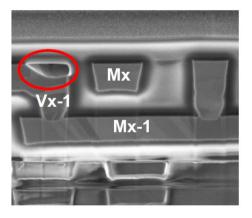

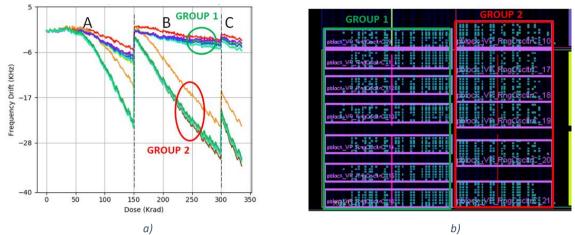

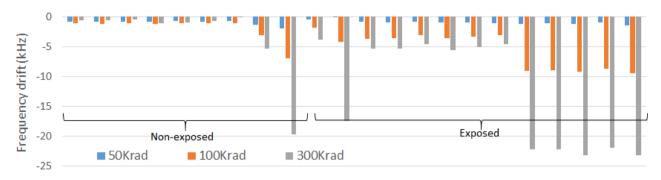

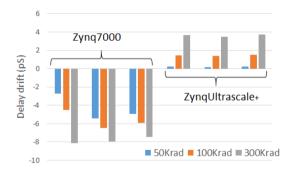

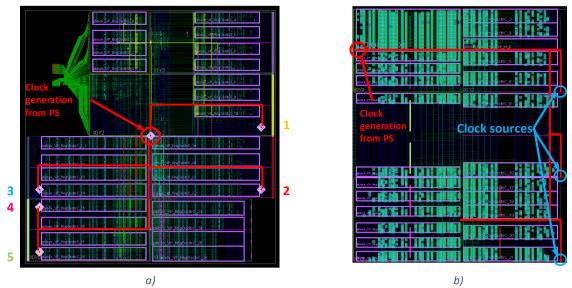

# 2. RADIATION AND AGING EFFECTS ON DIGITAL SYSTEMS