# Predictive tools and Radiation-Hardening-by-Design (RHBD) techniques for SET and SEU in digital circuits

Ygor Quadros de Aguiar

#### ▶ To cite this version:

Ygor Quadros de Aguiar. Predictive tools and Radiation-Hardening-by-Design (RHBD) techniques for SET and SEU in digital circuits. Electronics. Université Montpellier, 2020. English. NNT: 2020MONTS085. tel-03380597

## HAL Id: tel-03380597 https://theses.hal.science/tel-03380597

Submitted on 15 Oct 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITE DE MONTPELLIER

#### En Électronique

École doctorale : Information, Structures, Systèmes

Unité de recherche : Institut d'Electronique et des Systèmes - IES

Predictive tools and Radiation-Hardening-by-Design (RHBD) techniques for SET and SEU in digital circuits

## Présentée par Ygor QUADROS DE AGUIAR Le 8 décembre 2020

Sous la direction de Prof. Frédéric WROBEL et Prof. Jean-Luc AUTRAN

#### Devant le jury composé de

| BARELAUD Bruno, Pr., XLIM                        | Rapporteur   |

|--------------------------------------------------|--------------|

| GIRARD Sylvain, Pr., Université de Saint-Etienne | Rapporteur   |

| LEROUX Paul, Pr., KU Leuven                      | Examinateur  |

| SAIGNE Frédéric, Pr., Université de Montpellier  | Examinateur  |

| AUTRAN Jean-Luc, Pr., Aix-Marseille Université   | Co-directeur |

| WROBEL Frédéric, Pr., Université de Montpellier  | Directeur    |

# Contents

| A                      | ckno  | wledgement                                      | 1  |

|------------------------|-------|-------------------------------------------------|----|

| $\mathbf{A}^{\dagger}$ | bstra | act                                             | 3  |

| R                      | ésum  | <b>né</b>                                       | 5  |

| 1                      | Intr  | roduction                                       | 7  |

|                        | 1.1   | Context and Overview                            | 7  |

|                        | 1.2   | Objectives and Contributions                    | 9  |

|                        | 1.3   | Thesis Organization                             | 10 |

| 2                      | Rac   | liation Effects and Prediction                  | 11 |

|                        | 2.1   | Radiation Environments                          | 11 |

|                        | 2.2   | Radiation Effects                               | 16 |

|                        |       | 2.2.1 Energy Deposition                         | 16 |

|                        |       | 2.2.2 Charge Collection                         | 19 |

|                        |       | 2.2.3 Charge Sharing and Pulse Quenching Effect | 20 |

|                        |       | 2.2.4 Masking Effects                           | 22 |

|                        | 2.3   | Modeling and Prediction                         | 25 |

|                        | 2.4   | Proposed Prediction Methodology                 | 27 |

|                        | 2.5   | Conclusion                                      | 31 |

| 3                      | Rac   | liation Hardening                               | 33 |

|                        | 3.1   | Radiation Hardening by Process (RHBP)           | 35 |

|                        | 3.2   | Radiation Hardening by Design (RHBD)            | 39 |

|                        |       | 3.2.1 Layout-based techniques                   | 39 |

4 CONTENTS

|   |     | 3.2.2    | Circuit-based techniques                                  | . 44  |

|---|-----|----------|-----------------------------------------------------------|-------|

|   | 3.3 | Concl    | usions                                                    | . 47  |

| 4 | Ana | alysis o | of RHBD at Layout-level                                   | 49    |

|   | 4.1 | Gate     | Sizing and Transistor Stacking                            | . 49  |

|   |     | 4.1.1    | Gate Sizing (GS) $\dots$                                  | . 50  |

|   |     | 4.1.2    | Transistor Stacking (TS)                                  | . 55  |

|   |     | 4.1.3    | Comparison of power and area overhead                     | . 58  |

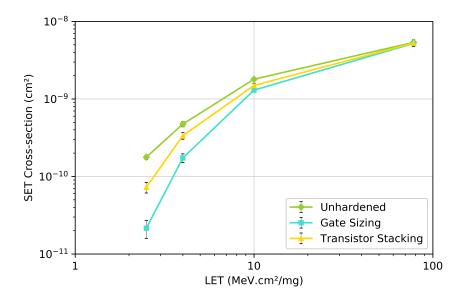

|   |     | 4.1.4    | Impact on the SET cross-section                           | . 60  |

|   | 4.2 | Trans    | istor Folding (TF)                                        | . 67  |

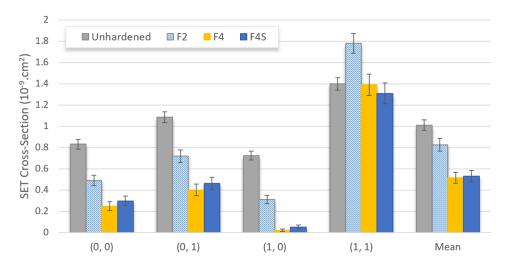

|   |     | 4.2.1    | Impact on the SET cross-section                           | . 70  |

|   |     | 4.2.2    | Asymmetric designs                                        | . 78  |

|   |     | 4.2.3    | Impact on the in-orbit SET rate: LEO and ISS orbits       | . 83  |

|   |     | 4.2.4    | Transistor Scaling and Angular Dependence                 | . 85  |

|   | 4.3 | Concl    | usions                                                    | . 86  |

| 5 | Ana | alysis o | of RHBD at Circuit-level                                  | 89    |

|   | 5.1 | Reliab   | pility-driven Synthesis                                   | . 89  |

|   |     | 5.1.1    | Multiple $V_{th}$ cells and Voltage Scaling               | . 93  |

|   |     | 5.1.2    | Technology Mapping                                        | . 95  |

|   | 5.2 | Pin A    | ssignment                                                 | . 112 |

|   |     | 5.2.1    | Optimization of Pin Assignment for Single-Event Tran-     |       |

|   |     |          | sients                                                    | . 114 |

|   |     | 5.2.2    | Impact on the SET cross-section of standard cells $$ . $$ | . 119 |

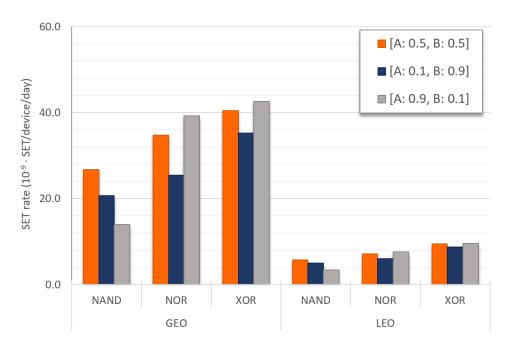

|   |     | 5.2.3    | Impact on the in-orbit SET rates                          | . 123 |

|   | 5.3 | Concl    | usions                                                    | . 125 |

| 6 | Har | dness    | improvement of RHBD techniques                            | 127   |

|   | 6.1 | Gate     | Sizing and Transistor Stacking                            | . 127 |

|   | 6.2 | Hardy    | vare Redundancy                                           | . 131 |

|   | 6.3 | Concl    | usions                                                    | . 146 |

| 7 | Con | nclusio  | ns and Outlook                                            | 149   |

|   | 7.1 | Thesis   | s Summary                                                 | . 149 |

| CONTENTS | 5 |

|----------|---|

|          |   |

| 7.2  | Future   | e Work                                                   |

|------|----------|----------------------------------------------------------|

| 7.3  | List o   | f Publications                                           |

| A Ré | sumé é   | tendu 155                                                |

| A.1  | l Introd | luction et Motivation                                    |

| A.2  | 2 Métho  | odologie de Prédiction                                   |

| A.3  | 3 Résult | tats                                                     |

|      | A.3.1    | Durcissement par design (RHBD) au niveau du layout       |

|      |          | physique                                                 |

|      | A.3.2    | Durcissement par design (RHBD) au niveau du circuit 162  |

|      | A.3.3    | Amélioration de l'efficacité des techniques de durcisse- |

|      |          | ment                                                     |

|      | A.3.4    | Conclusions                                              |

6 CONTENTS

# List of Figures

| 2.1  | Space Radiation Environment                                               | 12 |

|------|---------------------------------------------------------------------------|----|

| 2.2  | Solar Cycle Flux Progression: current solar cycle 24 and pre-             |    |

|      | diction of cycle 25 based on the sunspot number. $\dots$                  | 13 |

| 2.3  | Van Allen's Radiation Belts                                               | 14 |

| 2.4  | Flux intensity map for the $>10~\mathrm{MeV}$ channel at 500 km altitude. | 15 |

| 2.5  | Secondary radiation induced by a proton interaction with an               |    |

|      | atmospheric atom and leading to a cosmic ray air shower                   | 15 |

| 2.6  | Variation of Linear Energy Transfer (LET) as function of en-              |    |

|      | ergy for different ions in silicon                                        | 18 |

| 2.7  | Representation of Direct Ionization and Indirect Ionization for           |    |

|      | heavy ions, neutrons and protons interaction with matter (Si              |    |

|      | stands for Silicon)                                                       | 19 |

| 2.8  | Charge collection mechanisms due to an ion strike in a p-n                |    |

|      | junction                                                                  | 20 |

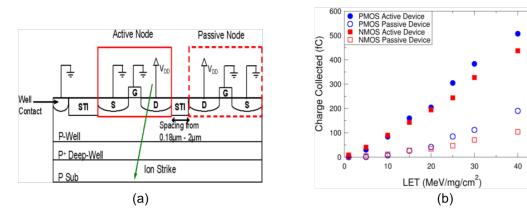

| 2.9  | (a) outline of two NMOS adjacent devices and (b) charge col-              |    |

|      | lected for PMOS and NMOS as active and passive devices                    | 21 |

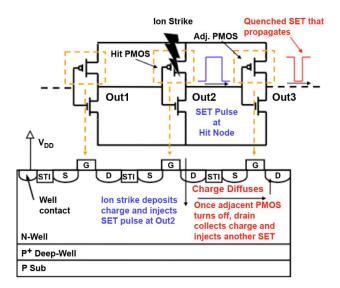

| 2.10 | SET Pulse Quenching Effect in a inverter chain                            | 22 |

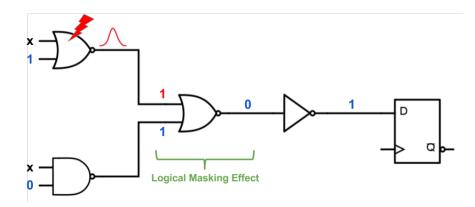

| 2.11 | Illustration of the logical masking effect of a SET event in a            |    |

|      | 2-input NOR gate within a block of combinational circuit. $$              | 23 |

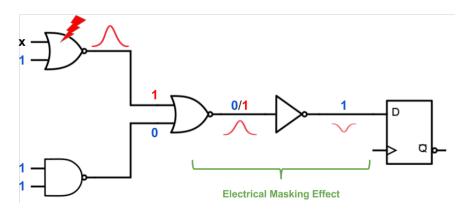

| 2.12 | Illustration of the electrical masking effect of a SET event due          |    |

|      | to electrical losses in a logic path                                      | 24 |

| 2.13 | Illustration of the latching-window masking effect of a SET               |    |

|      | pulse by a flip-flip (FF) circuit                                         | 25 |

| 2.14 | Representation of the extraction of the collecting areas from                                                                            |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the circuit design (GDSII file) and the energy deposition and                                                                            |    |

|      | charge collection calculation in the MC-Oracle tool                                                                                      | 29 |

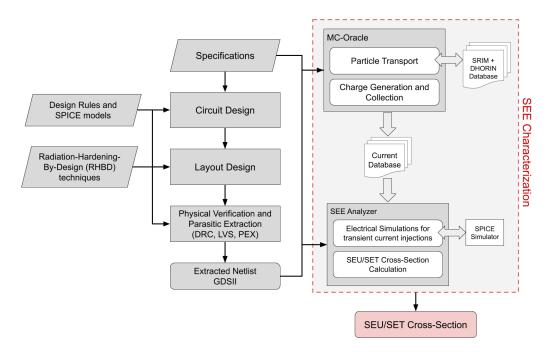

| 2.15 | Simulation chain proposed as the SEE Prediction Methodology                                                                              | 30 |

| 3.1  | Classification of hardening techniques based on the abstraction level: from manufacturing process to system level                        | 34 |

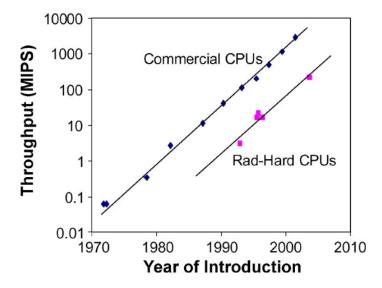

| 3.2  | Comparing of commercial and rad-hard processors in terms of throughput (in Million Instructions Per Second, MIPS)                        | 37 |

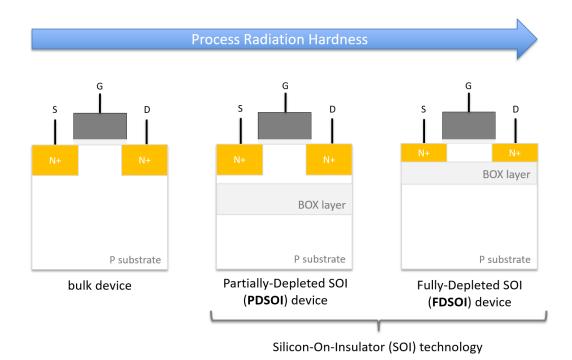

| 3.3  | Simplified representation of a NMOS device manufactured in a bulk technology and two variants of a Silicon-On-Insulator (SOI) technology | 38 |

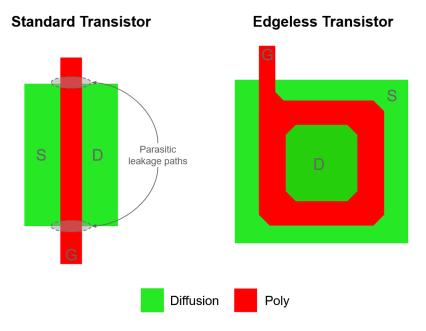

| 3.4  | Comparison between a standard transistor layout and the edgeless transistor layout (ELT)                                                 | 40 |

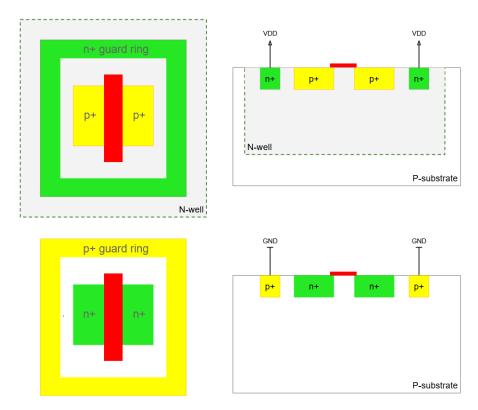

| 3.5  | Layout and cross-sectional representation of guard rings around PMOS and NMOS transistors                                                | 41 |

| 3.6  | Recovery current reinforcement induced by the increased parasitic bipolar effect due to the close proximity NMOS device .                | 42 |

| 3.7  | Illustration of the LEAP principle for an inverter gate                                                                                  | 43 |

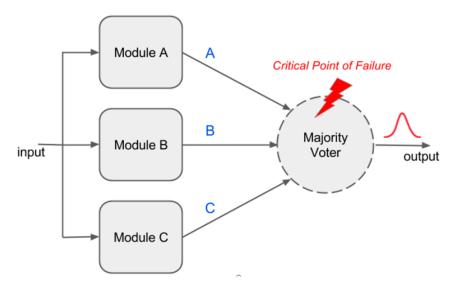

| 3.8  | Diagram of the Triple Modular Redundancy (TMR) fault tolerance technique                                                                 | 45 |

| 3.9  | Two circuit architectures based on reinforcement feedback $$                                                                             | 46 |

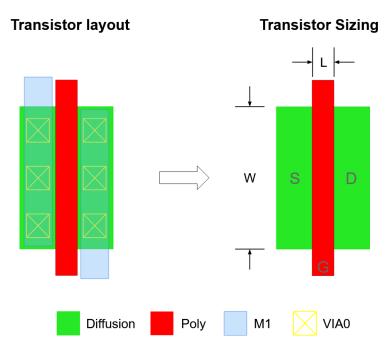

| 4.1  | MOS transistor layout and its main feature sizing: width $W$ and length $L$ of the transistor channel                                    | 51 |

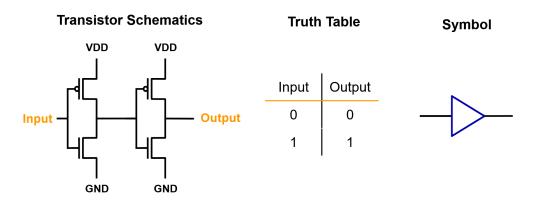

| 4.2  | Transistor schematics of a CMOS inverter, the truth table and its symbol                                                                 | 52 |

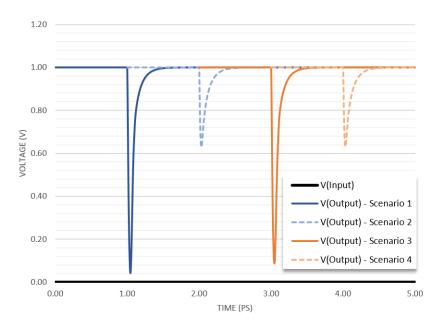

| 4.3  | SET injection at the output of a CMOS Inverter with different sizing scenarios when the NMOS device is sensitive                         | 53 |

| 4.4  | SET injection at the output of a CMOS Inverter with different sizing scenarios when the PMOS device is sensitive                         | 55 |

LIST OF FIGURES 9

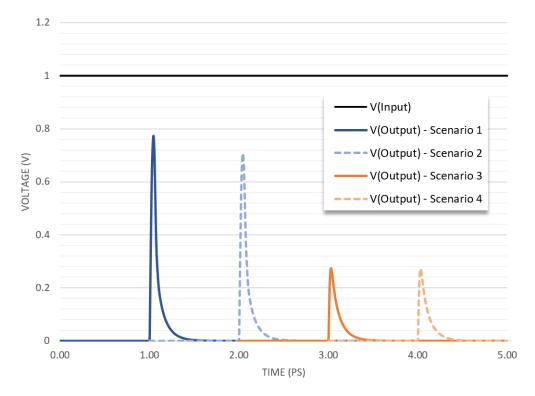

| 4.5  | Application of transistor stacking in an inverter design based      |    |

|------|---------------------------------------------------------------------|----|

|      | on a SOI technology and the representation of a heavy-ion ion-      |    |

|      | ization. The electron-hole pairs generated within the insulator     |    |

|      | are omitted due to its negligible contribution to the SEE effects.  | 56 |

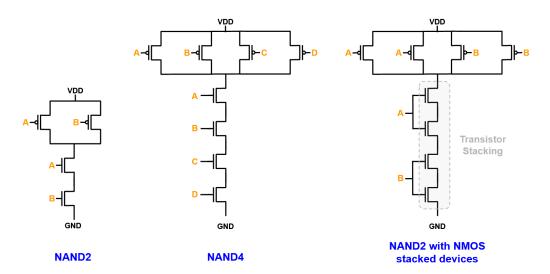

| 4.6  | Using 4-input NAND gate to achieve stacking transistors for         |    |

|      | a 2-input NAND function with standard-cell libraries                | 57 |

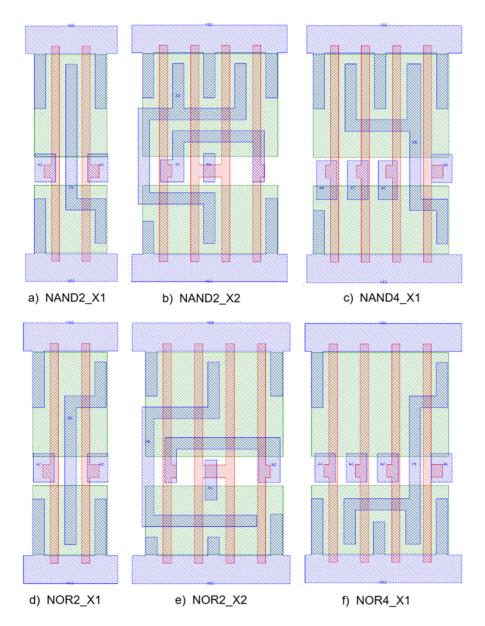

| 4.7  | Simplified cell layout design of logic gates from the 45-nm bulk    |    |

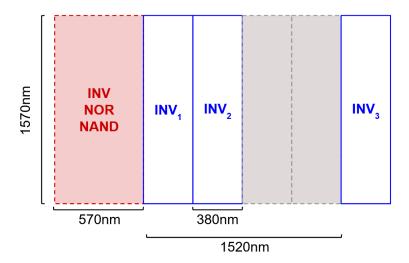

|      | CMOS containing metal<br>1, active diffusion and poly layers. $$    | 59 |

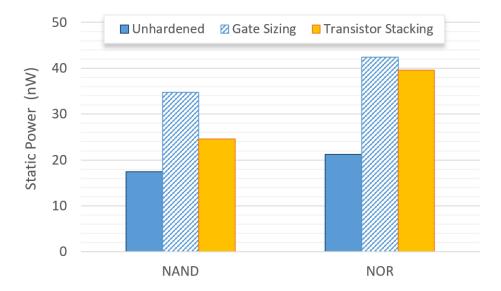

| 4.8  | Static power consumption estimation for original, gate sizing       |    |

|      | and transistor stacking implementations of the NAND and             |    |

|      | NOR gates                                                           | 61 |

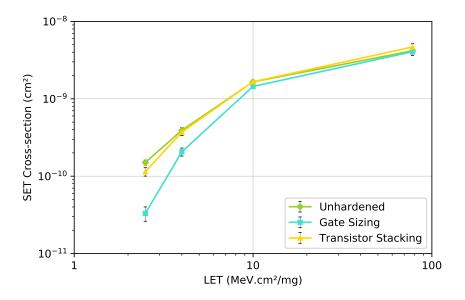

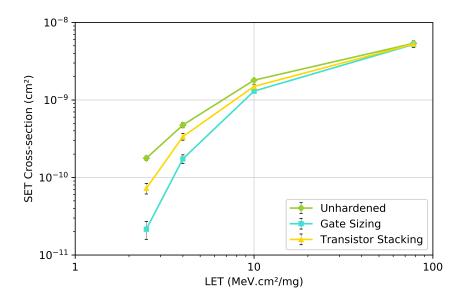

| 4.9  | Average of the SET cross-section for each input signal the          |    |

|      | NAND logic gate: minimum sized (Original), using Gate Siz-          |    |

|      | ing; and Transistor Stacking                                        | 62 |

| 4.10 | Average of the SET cross-section for each input signal the          |    |

|      | NOR logic gate: minimum sized (Original), using Gate Sizing;        |    |

|      | and Transistor Stacking                                             | 63 |

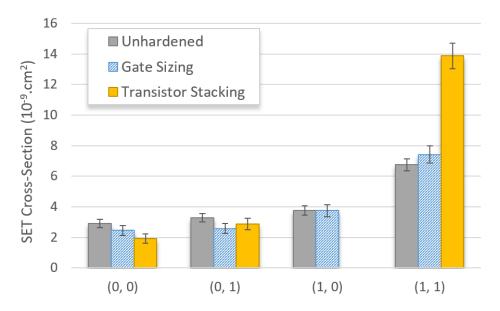

| 4.11 | SET cross-Section for each input signal combination of the          |    |

|      | NAND gate under 78 $MeV.cm^2/mg$                                    | 64 |

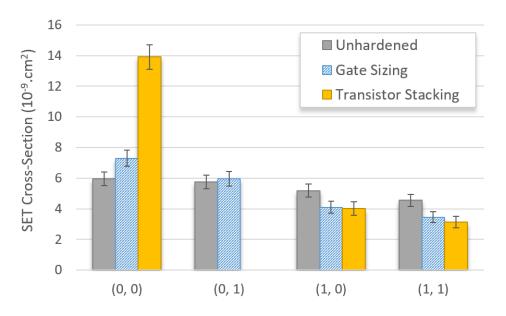

| 4.12 | SET cross-section for each input signal combination of the          |    |

|      | NOR gate under 78 $MeV.cm^2/mg$                                     | 64 |

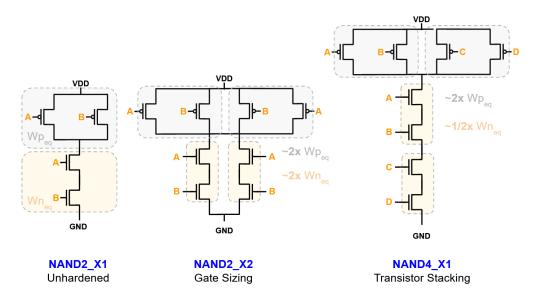

| 4.13 | Transistor schematics and the equivalent driving strength of        |    |

|      | NAND2_X1 (unhardened), NAND2_X2 (Gate Sizing) and                   |    |

|      | NAND4_X1 (Transistor Stacking)                                      | 65 |

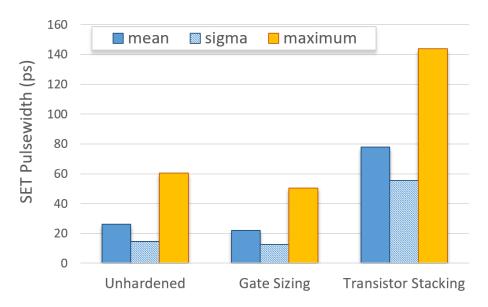

| 4.14 | SET pulse width measurements for the NAND gate under 78             |    |

|      | $MeV.cm^2/mg$                                                       | 66 |

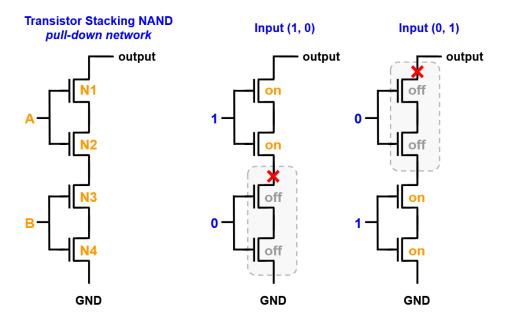

| 4.15 | Pull-down transistor network of the TS-based NAND gate and          |    |

|      | the implications of input $(1, 0)$ and $(0, 1)$ . Particle hits are |    |

|      | represented by a red cross                                          | 67 |

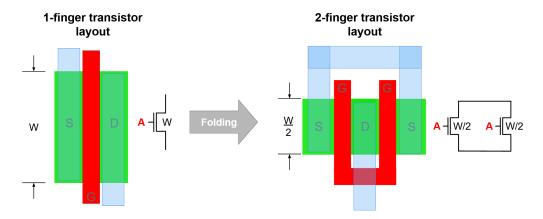

| 4.16 | Transistor Folding Layout technique                                 | 68 |

| 4.17 | Standard quadruple-finger folded transistor layout vs. folded       |    |

|      | transistor layout with Diffusion Splitting (DS) technique           | 71 |

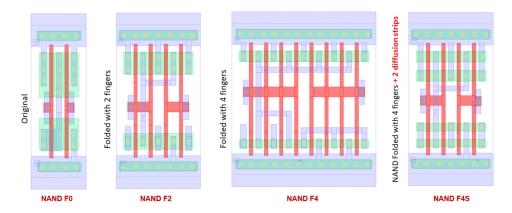

| 4.18 | Simplified layout design of NAND F0 (no folding, unhard-                            |            |

|------|-------------------------------------------------------------------------------------|------------|

|      | ened), NAND F2 (2-finger design), NAND F4 (4-finger design)                         |            |

|      | and NAND F4S (4-finger design with diffusion splitting)                             | 72         |

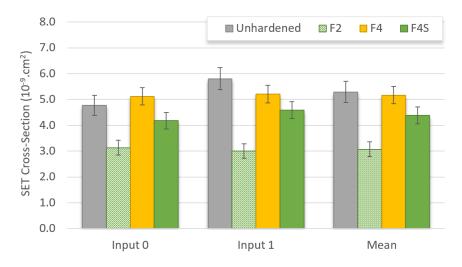

| 4.19 | SET cross section for the inverter designs under LET $= 78.23$                      |            |

|      | $MeV.cm^2/mg$ considering input 0, input 1 and the mean value.                      | 73         |

| 4.20 | SET cross section for the inverter designs under LET $= 5.43$                       |            |

|      | $MeV.cm^2/mg$ considering input 0, input 1 and the mean value.                      | 74         |

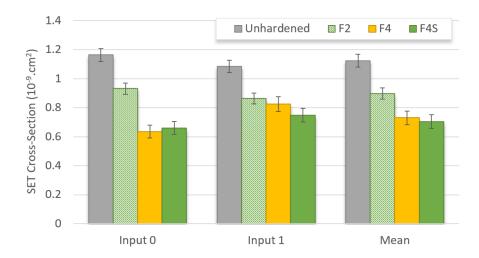

| 4.21 | Log-Log representation of the mean SET cross section curves                         |            |

|      | for the inverter designs. No event was observed in the 4-finger                     |            |

|      | designs (triangle and rhombus curves) for LET lower than $5.43$                     |            |

|      | $MeV.cm^2/mg$                                                                       | 74         |

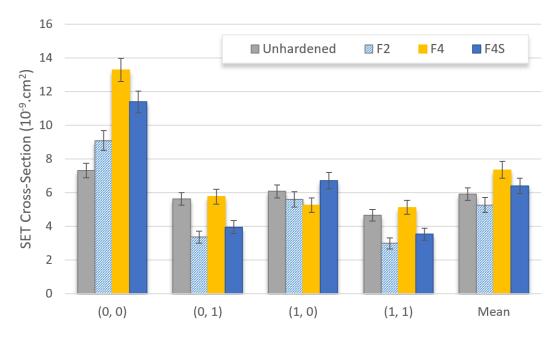

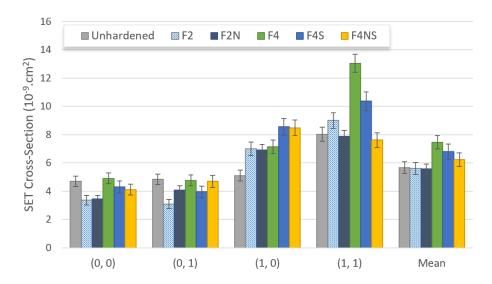

| 4.22 | SET cross section for the NAND designs at LET $= 78.23$                             |            |

|      | $MeV.cm^2/mg$ for each input signal and the mean value                              | 75         |

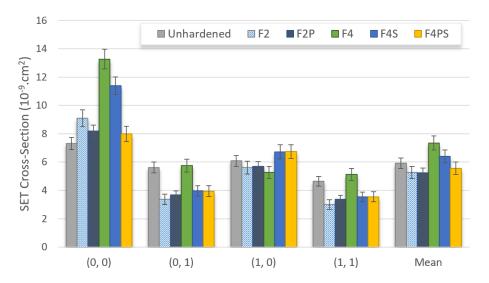

| 4.23 | SET cross section for the NOR designs at LET = $78.23~MeV.cm^2/m^2$                 | $m_{\ell}$ |

|      | for each input signal and the mean value                                            | 76         |

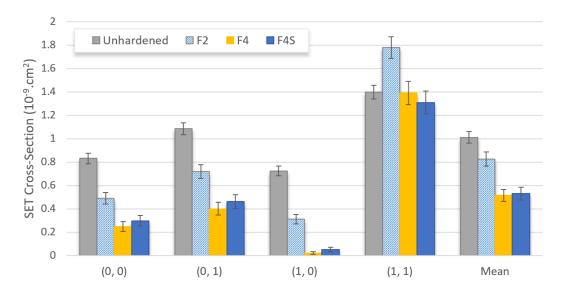

| 4.24 | SET cross section for the NAND designs at LET = $5.43~MeV.cm^2/$                    | m          |

|      | for each input signal and the mean value                                            | 77         |

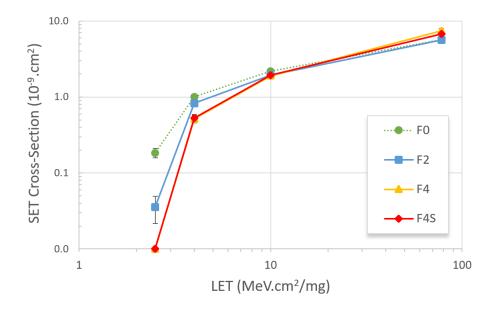

| 4.25 | Log-log representation of the mean SET cross section curves                         |            |

|      | for the NAND designs (F0: unfolded, F2: 2-finger, F4: 4-                            |            |

|      | finger, F4S: 4-finger design with diffusion splitting)                              | 78         |

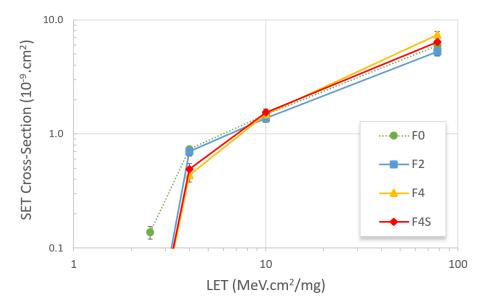

| 4.26 | Log-log representation of the mean SET cross section curves                         |            |

|      | for the NOR designs (F0: unfolded, F2: 2-finger, F4: 4-finger,                      |            |

|      | F4S: 4-finger design with diffusion splitting)                                      | 79         |

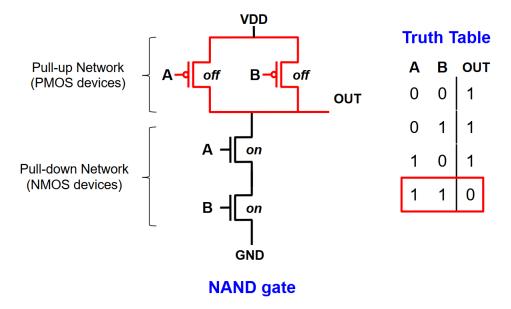

| 4.27 | Transistor network of an NAND gate and its truth table. $On$ -                      |            |

|      | state and $\mathit{off}\text{-state}$ are indicated for the transistors considering |            |

|      | the worst-case input scenario, i.e. input $(1, 1)$                                  | 80         |

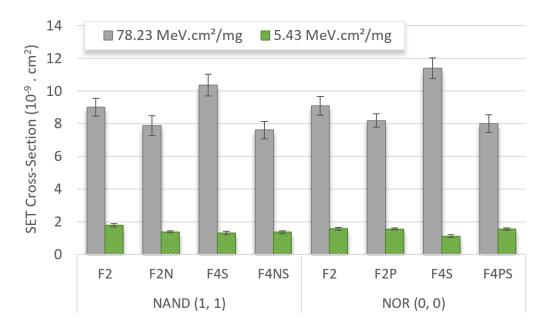

| 4.28 | SET cross-section for symmetric and asymmetric designs of 2-                        |            |

|      | finger and 4-finger with diffusion splitting of NAND and NOR $$                     |            |

|      | gates in the worst-case input scenario, i.e. input $(1, 1)$ and                     |            |

|      | input $(0, 0)$ , respectively                                                       | 81         |

| 4.29 | SET cross section for the NOR designs at LET = $78.23~MeV.cm^2/m^2$                 | $m_{\ell}$ |

|      | for each input signal and the mean value                                            | 81         |

| 4.30 | SET cross section for the NAND designs at LET $= 78.23$             |    |

|------|---------------------------------------------------------------------|----|

|      | $MeV.cm^2/mg$ for each input signal and the mean value              | 82 |

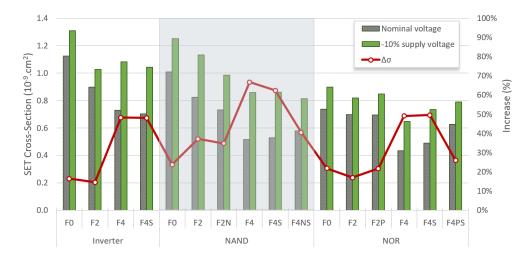

| 4.31 | SET cross section considering a voltage drop of $10\%$ over the     |    |

|      | nominal supply voltage and a particle LET of 5 $MeV.cm^2/mg$ .      | 83 |

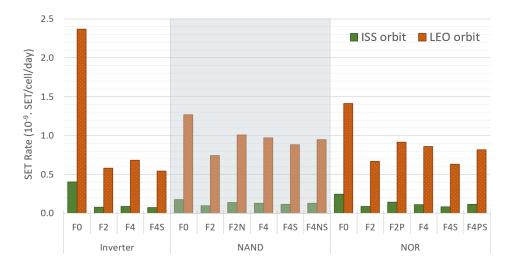

| 4.32 | Heavy-ions SET rate estimated with OMERE for each circuit           |    |

|      | and its hardened version considering the LEO (800km, $98^\circ)$    |    |

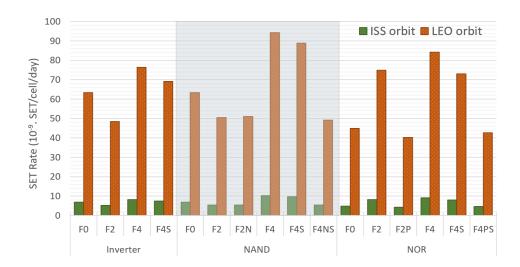

|      | and ISS (400km, 51.64°) orbit $\dots \dots \dots \dots \dots \dots$ | 85 |

| 4.33 | Total SET rate estimated with OMERE for each circuit and its        |    |

|      | hardened version for the LEO (800km, $98^\circ)$ and ISS (400km,    |    |

|      | $51.64^{\circ}$ ) orbit considering heavy ions and protons          | 86 |

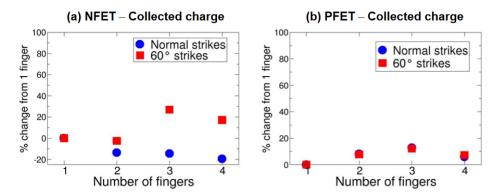

| 4.34 | Collect Charge (CC) for normal and $60^\circ$ strikes at the center |    |

|      | of the drain area in the NFET and PFET devices for a particle       |    |

|      | LET of $40 \ MeV.cm^2/mg$                                           | 87 |

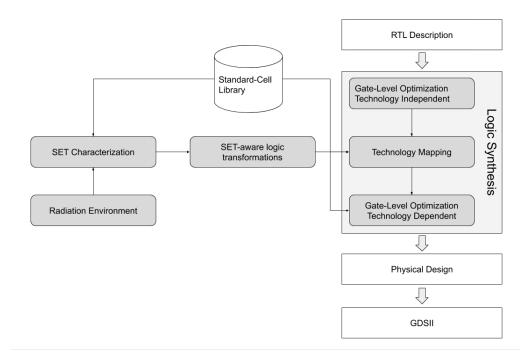

| 5.1  | Integration of the proposed SET characterization of standard-       |    |

|      | cell libraries into the logic synthesis                             | 91 |

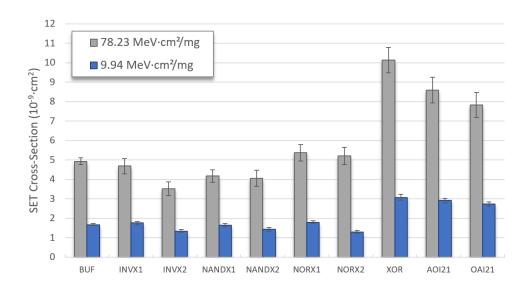

| 5.2  | SET cross-section for eight standard-cell gates from 45nm Nan-      |    |

| • -  | Gate, for LET equals to 78.23 and 9.94 $MeV.cm^2/mg.$               | 92 |

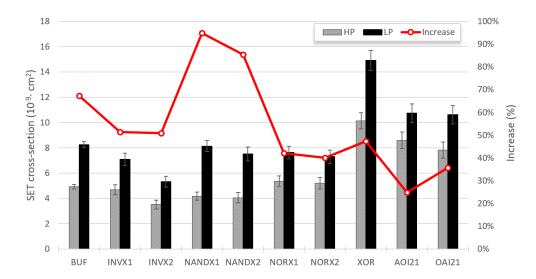

| 5.3  | Impact of different threshold voltage devices: High-Performance     |    |

|      | (HP) vs. Low-Power (LP) devices                                     | 94 |

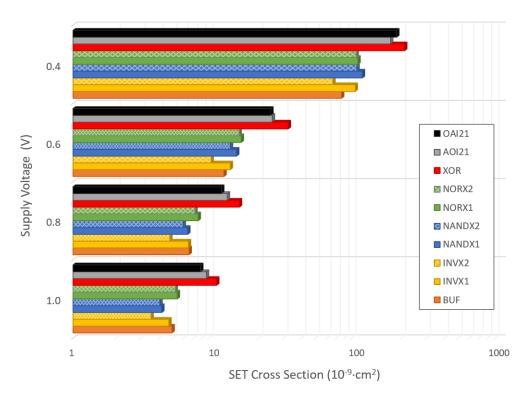

| 5.4  | Estimation of the dynamic voltage scaling impact on the SET         |    |

|      | cross section of the standard cells                                 | 94 |

| 5.5  | Transistor schematics, truth table and symbol of a digital          |    |

|      | CMOS buffer gate                                                    | 96 |

| 5.6  | Cell placement setup used for the MC-Oracle simulations             | 97 |

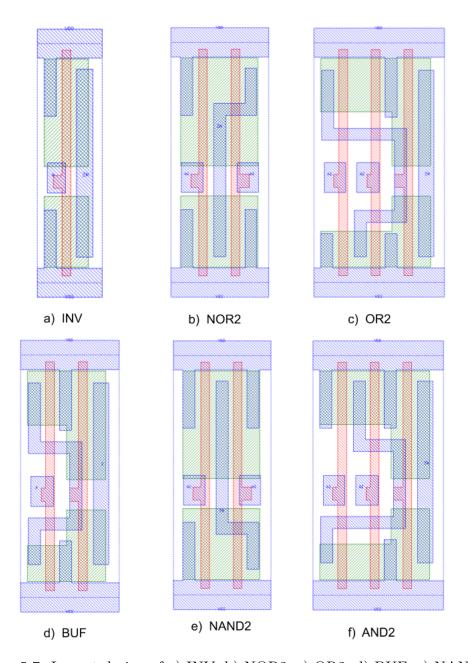

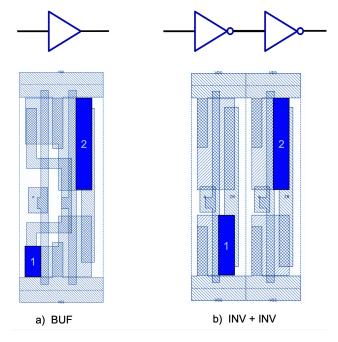

| 5.7  | Layout design of a) INV, b) NOR2, c) OR2, d) BUF, e)                |    |

|      | NAND2 and f) AND2 in the 45nm Open Cell Library                     | 98 |

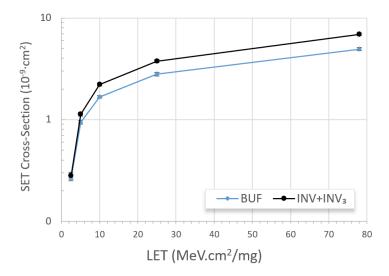

| 5.8  | SET cross-section curve for the BUF gate and the INV+INV            |    |

|      | circuit                                                             | 99 |

| 5.9  | Comparison of the collecting drain area of the sensitive elec-      |    |

|      | trodes in the first and second stage inverters from the BUF         |    |

|      | gate and INV+INV design                                             | 99 |

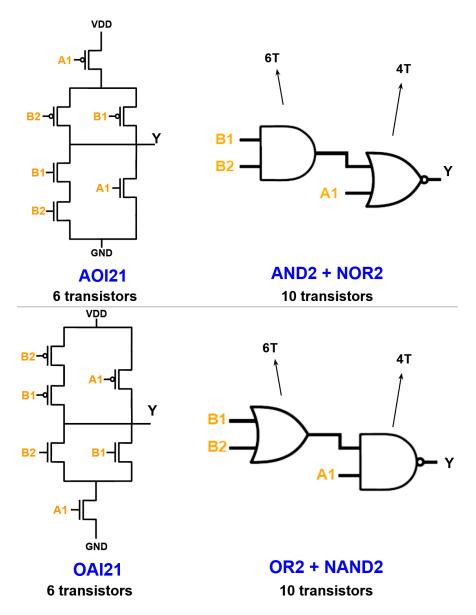

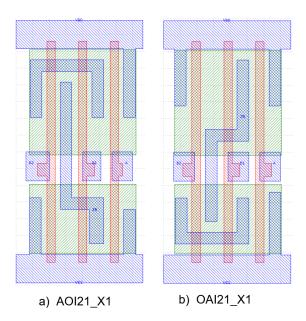

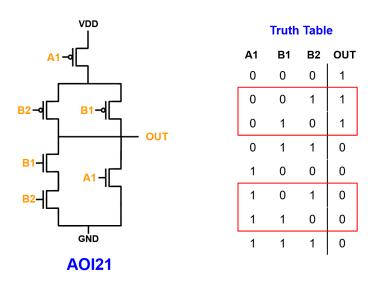

| 5.10 | MOS transistor network of the complex logic gates AOI21 and                          |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | OAI21 and its correspondent implementation with the gates:                           |     |

|      | AND2, NOR2, OR2, and NAND2                                                           | 102 |

| 5.11 | Cell layout of the complex gates: (a) AOI21 and (b) OAI21.                           |     |

|      | For clarity, only the layers metal1 (blue), active diffusion (green)                 |     |

|      | and poly layers (red) are shown                                                      | 103 |

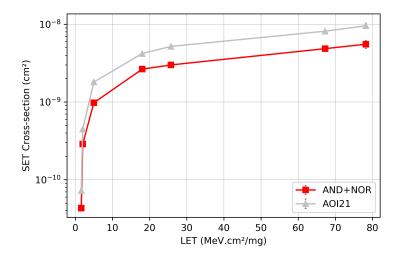

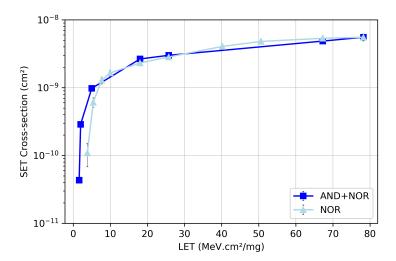

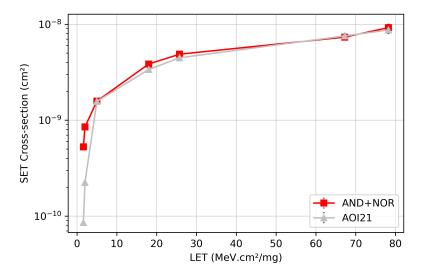

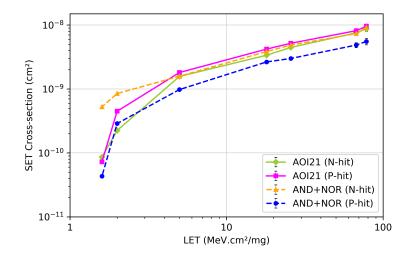

| 5.12 | SET cross-section curve of P-hit interactions for the complex                        |     |

|      | logic AOI21 gate and AND + NOR implementation                                        | 105 |

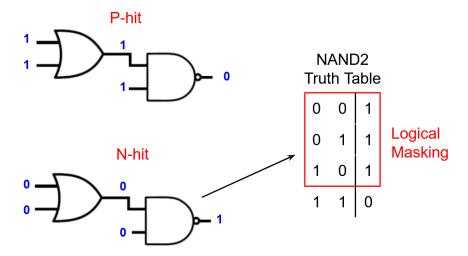

| 5.13 | Logical masking effect for the P-hit configuration in the combi-                     |     |

|      | national logic circuit AND+NOR. There is no logical masking                          |     |

|      | when both inputs are set to logic zero                                               | 105 |

| 5.14 | Comparison of SET cross-section curve of the AND+NOR im-                             |     |

|      | plementation and the standalone NOR gate                                             | 106 |

| 5.15 | SET cross-section curve of N-hit interactions for the complex                        |     |

|      | logic AOI21 agate and AND + NOR implementation                                       | 107 |

| 5.16 | SET cross-sectional curve of P-hit interactions for the complex                      |     |

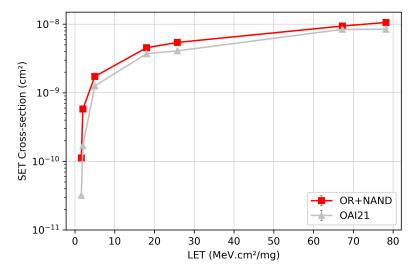

|      | logic OAI21 gate and OR + NAND implementation                                        | 108 |

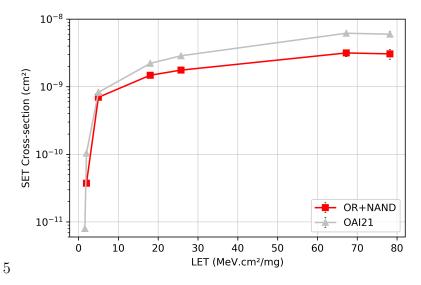

| 5.17 | SET cross-sectional curve of N-hit interactions for the complex                      |     |

|      | logic OAI21 agate and OR + NAND implementation                                       | 109 |

| 5.18 | Logical masking effect for the N-hit configuration in the combi-                     |     |

|      | national logic circuit $OR + NAND$ . There is no logical masking                     |     |

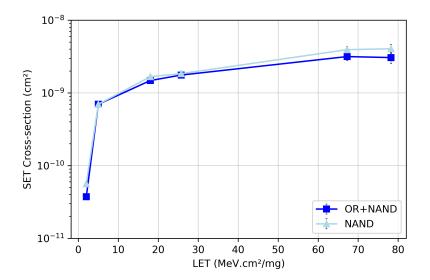

|      | when both inputs are set to logic one                                                | 110 |

| 5.19 | Comparison of SET cross-sectional curve of the $OR + NAND$                           |     |

|      | implementation and the standalone NAND gate                                          | 110 |

| 5.20 | ${\it Log-log \ representation \ of \ SET \ cross-sectional \ curves \ for \ AOI21}$ |     |

|      | and AND $+$ NOR considering N-hit interactions and P-hit in-                         |     |

|      | teractions                                                                           | 111 |

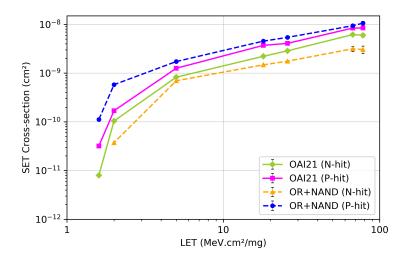

| 5.21 | ${\it Log-log representation of SET cross-sectional curves for OAI21}$               |     |

|      | and $OR + NAND$ considering N-hit interactions and P-hit in-                         |     |

|      | teractions                                                                           | 112 |

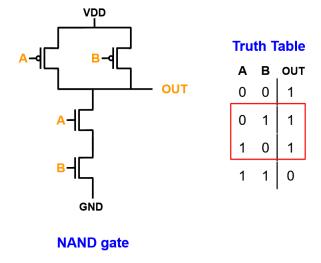

| 5.22 | Transistor network and truth table of a 2-input NAND gate.                           |     |

|      | The interchangeable input combinations are highlighted by the                        |     |

|      | red rectangular                                                                      | 114 |

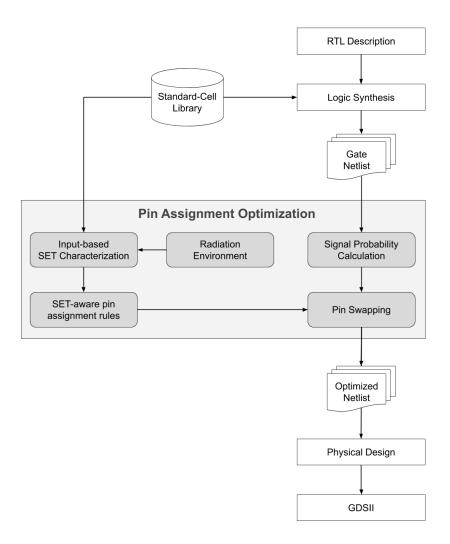

| 5.23 | SET-aware Pin Assignment Optimization in a cell-based VLSI           |

|------|----------------------------------------------------------------------|

|      | circuit design flow                                                  |

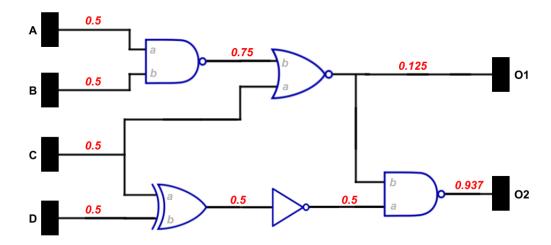

| 5.24 | Signal probability estimation for a combinational logic circuit. 117 |

| 5.25 | Input SET cross-section for the NAND, NOR and XOR gates              |

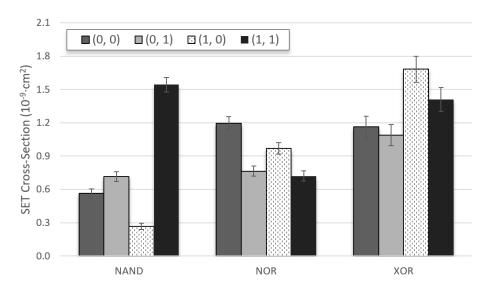

|      | under a particle with LET = $5 MeV.cm^2/mg.$ 119                     |

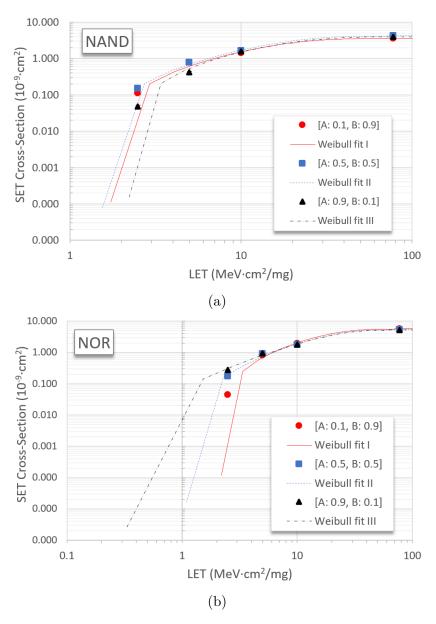

| 5.26 | SET cross-section curves for the NAND and NOR gate in 3              |

|      | input scenarios                                                      |

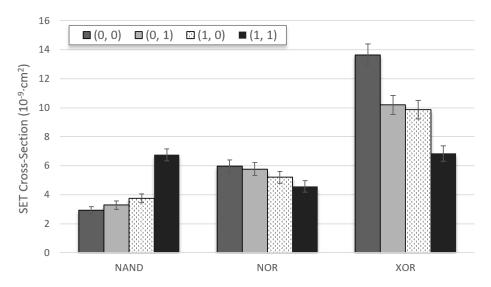

| 5.27 | Input SET cross-section for the NAND, NOR and XOR gates              |

|      | under a particle with LET = $78~MeV.cm^2/mg.$ 121                    |

| 5.28 | Transistor network and truth table of the AOI21 gate. The            |

|      | two group of symmetric input relationship are highlighted by         |

|      | the red rectangular                                                  |

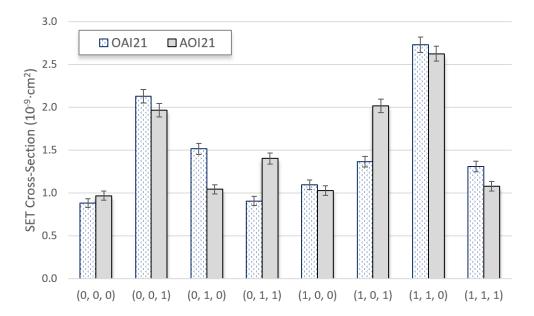

| 5.29 | Input SET cross-section for the AOI21 and OAI21 gates under          |

|      | a particle with LET = 5 $MeV.cm^2/mg.$                               |

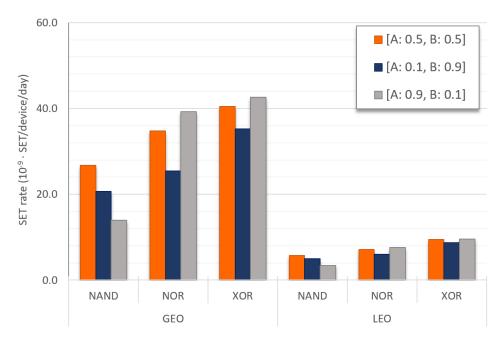

| 5.30 | In-orbit SET rate for the NAND, NOR and XOR in the Geo-              |

|      | stationary orbit (GEO), 35,784 km, and International Space           |

|      | Station (ISS) orbit, 400 km, 51.64°                                  |

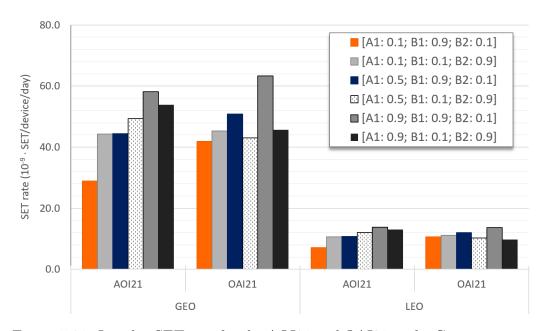

| 5.31 | In-orbit SET rate for the AOI21 and OAI21 in the Geostation-         |

|      | ary orbit (GEO), 35,784 km, and International Space Station          |

|      | (ISS) orbit, 400 km, 51.64°                                          |

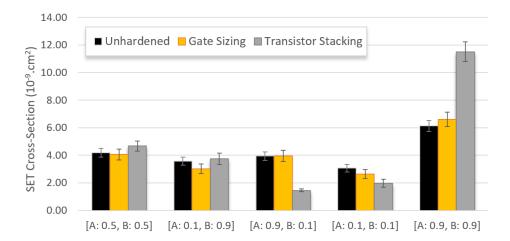

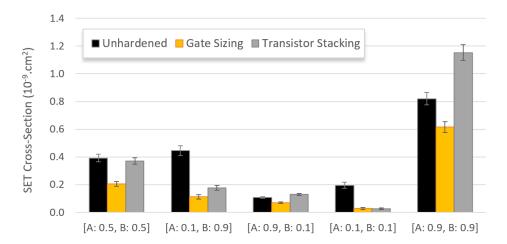

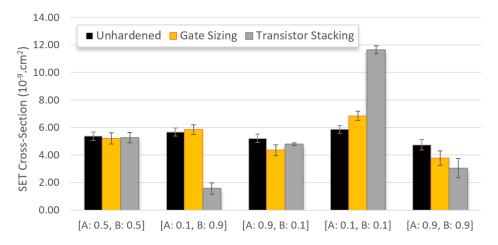

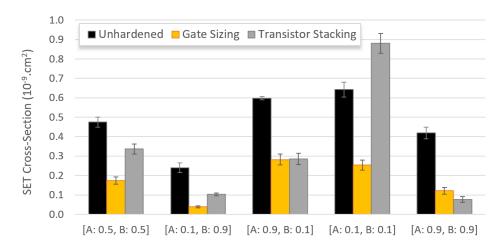

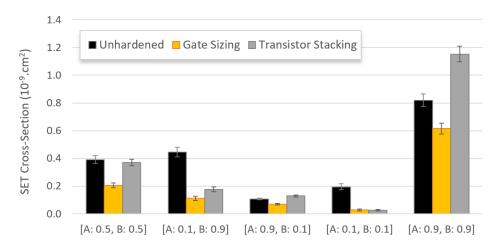

| 6.1  | SET cross-section for the NAND gate (unhardened, gate sizing         |

| 0.1  | and transistor stacking versions) under particle LET of 78.23        |

|      | $MeV.cm^2/mg$ considering five signal probability scenarios 129      |

| 6.2  | SET cross-section for the NAND gate (unhardened, gate sizing         |

| 0.2  | and transistor stacking versions) under particle LET of 3.89         |

|      | $MeV.cm^2/mg$ considering five signal probability scenarios 129      |

| 6.3  | SET cross-section for the NOR gate (unhardened, gate sizing          |

| 0.0  | and transistor stacking versions) under particle LET of 78.23        |

|      | $MeV.cm^2/mg$ considering five signal probability scenarios 130      |

| 6.4  | SET cross-section for the NOR gate (unhardened, gate sizing          |

|      | and transistor stacking versions) under particle LET of 3.89         |

|      | $MeV.cm^2/mg$ considering five signal probability scenarios 131      |

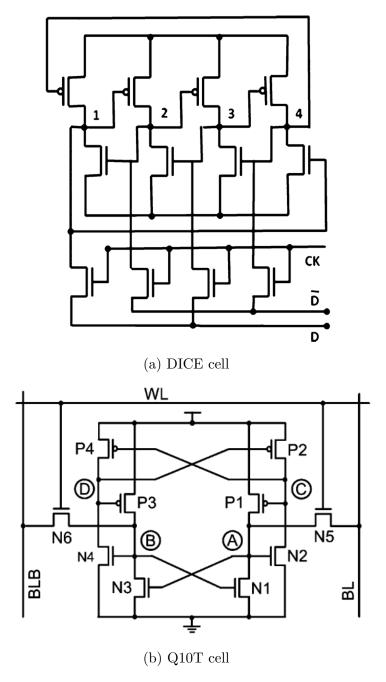

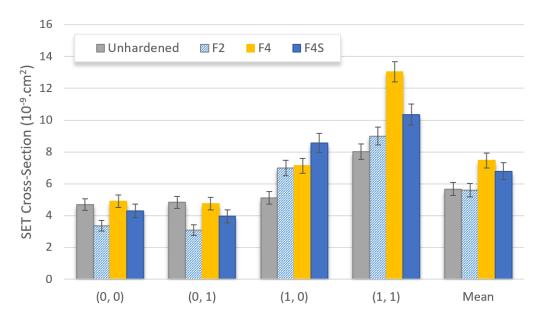

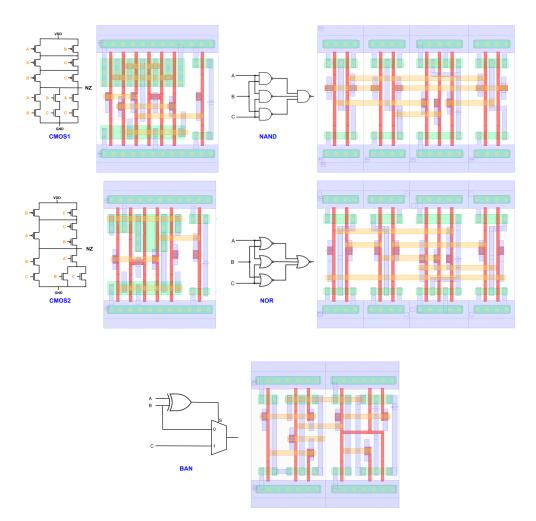

| 6.5  | Circuit- and Layout-level implementations of the complex-gate and standard-cell-based majority voter architectures. For simplicity, only metal1 (blue), metal2 (orange), active diffusion (green) and poly (red) layers are shown |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

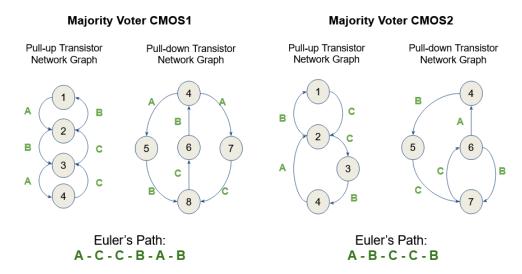

| 6.6  | Euler's path graph theorem applied to the majority voter CMOS1 and CMOS2 layout designs                                                                                                                                           |

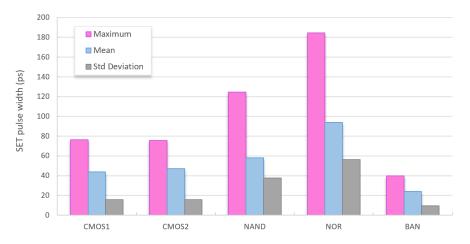

| 6.7  | Maximum, mean and standard deviation of the SET pulse width distribution for the CMOS1, CMOS2, NAND, NOR and BAN voters under particle LET = $78.23~MeV.cm^2/mg.$ $136$                                                           |

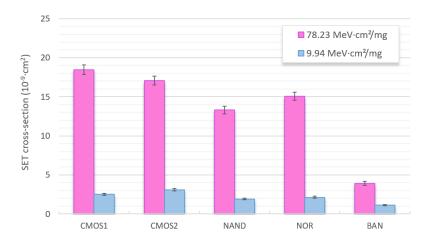

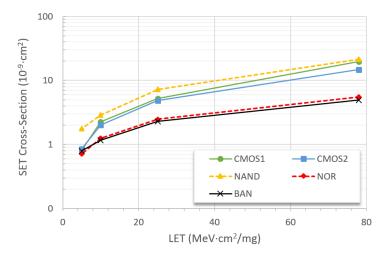

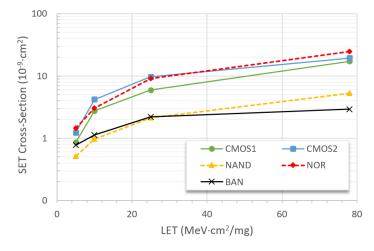

| 6.8  | SET cross-section estimation for CMOS1, CMOS2, NAND, NOR and BAN majority voter architectures considering particle LET equals to $78.23$ and $9.94~MeV.cm^2/mg.$ 13°                                                              |

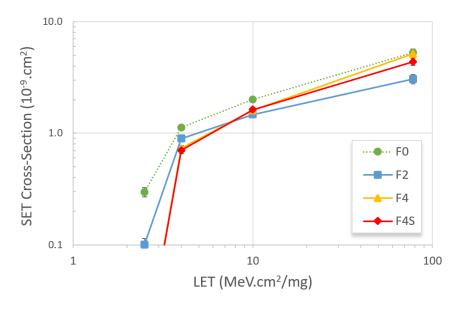

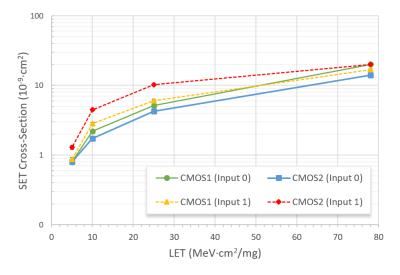

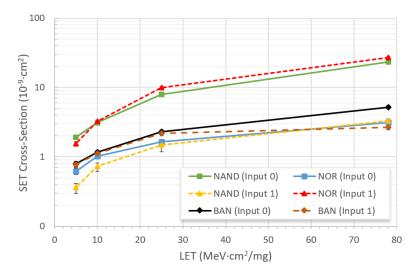

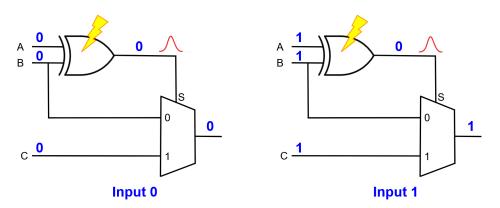

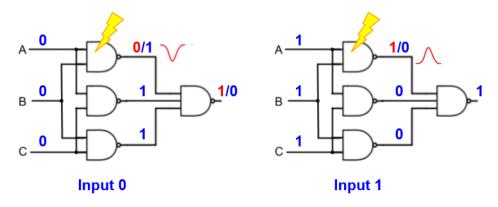

| 6.9  | SET cross-section for the complex-gate architectures considering the two possible input configuration in a fault-free TMR scheme: all inputs in high logic level (Input 1); and, all inputs in low logic level (Input 0)          |

| 6.10 | SET cross-section for the basic-logic gate architectures considering the two possible input configuration in a fault-free TMR scheme: all inputs in high logic level (Input 1); and, all inputs in low logic level (Input 0)      |

| 6.11 | Logical masking capability within the BAN voter architecture. 140                                                                                                                                                                 |

| 6.12 | Logical masking capability within the NAND voter architecture.14                                                                                                                                                                  |

| 6.13 | SET cross-section curves calculated for the majority voters considering a signal probability $p$ of 0.1, i.e. higher probability of a fault-free TMR condition in the input combination $(0, 0, 0)$                               |

| 6.14 | SET cross-section curves calculated for the majority voters considering a signal probability $p$ of 0.9, i.e. higher probability of a fault-free TMR condition in the input combination $(1, 1, 1)$                               |

|      | 1)                                                                                                                                                                                                                                |

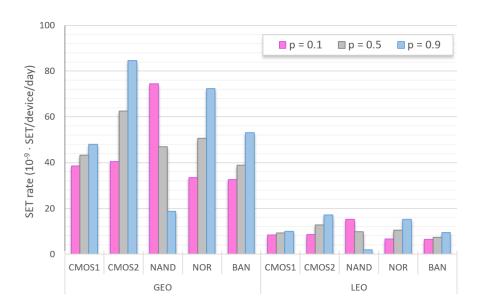

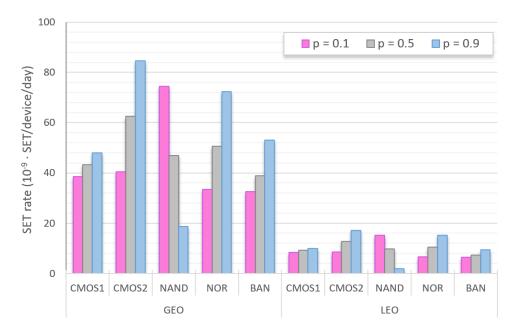

| 6.15 | In-orbit SET rate calculated with OMERE for the Geostation-         |       |

|------|---------------------------------------------------------------------|-------|

|      | ary orbit (GEO), 35,784 km, and for the International Space         |       |

|      | Station (ISS) orbit, 400 km, 51.64°. Three signal probability       |       |

|      | is considered: $p = 0.1$ , $p = 0.5$ and $p = 0.9$                  | . 143 |

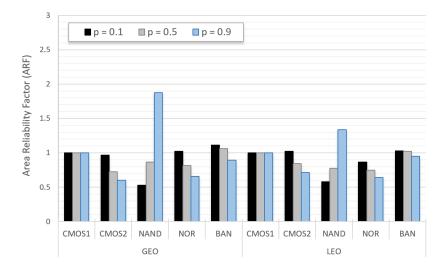

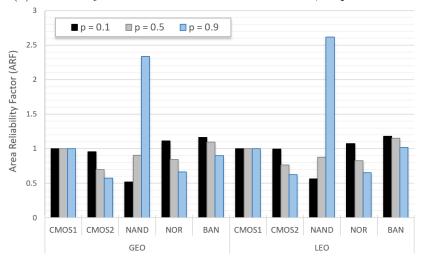

| 6.16 | Normalized Area Reliability Factor (ARF) for: (a) same co-          |       |

|      | efficient for area and reliability, and (b) reliability coefficient |       |

|      | (80%) is higher than area coefficient $(20%)$                       | . 145 |

| A.1  | Chaîne de simulation proposée comme méthodologie de pré-            |       |

|      | diction de SEE                                                      | . 158 |

| A.2  | Courbes de section efficace au SET pour le circuit NOR orig-        |       |

|      | inale et en utilisant des techniques de durcissement aux ray-       |       |

|      | onnements                                                           | . 160 |

| A.3  | Section efficace au SET du circuit NAND originale et avec           |       |

|      | transistors repliées (LET = $5.43~MeV.cm^2/mg$ )                    | . 161 |

| A.4  | Taux SET pour le circuit NAND, NOR et XOR sur l'orbite              |       |

|      | géostationnaire (GEO), à 35784 km, et l'orbite de la station        |       |

|      | spatiale internationale (ISS), 400 km, 51.64°                       | . 163 |

| A.5  | Section efficace au SET pour le circuit NAND (versions non          |       |

|      | durci, dimensionnement de grille et empilement de transistors)      |       |

|      | sous particules avec LET de 3,89 $MeV.cm^2/mg$ en considérant       |       |

|      | cinq scénarios de probabilité de signal                             | . 164 |

| A.6  | Taux SET calculé pour l'orbite géostationnaire (GEO), 35784         |       |

|      | km, et l'orbite de la station spatiale internationale (ISS), à 400  |       |

|      | km, 51,64 °. La probabilité de trois signaux est considérée :       |       |

|      | $p = 0.1, p = 0.5 \text{ et } p = 0.9. \dots$                       | . 166 |

# List of Tables

| 2.1 | List of simulation tools dedicated to study radiation effects on electronics                                                                                                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | Gate sizing scenarios for the SET injection at an inverter $52$                                                                                                                                                                                                                              |

| 4.2 | Layout and drain area of the unhardened design, and applying gate sizing and transistor stacking techniques (Area increase is expressed in percentage)                                                                                                                                       |

| 4.3 | Total area for each original unhardened cell layout design $(\mu m^2)$ and the increase factor for its correspondent folded designs                                                                                                                                                          |

| 4.4 | SET cross-section for each original cell layout design $(10^{-9}.cm^2)$ for particle LET = $5.43~MeV.cm^2/mg$ and the decrease percentage for its correspondent folded designs                                                                                                               |

| 5.1 | Total area for the cell layout design for the OR and AND logic implementations and the SET cross-section for a LET = $78.23$ $MeV.cm^2/mg$ and input $(1, 1) \ldots $ |

| 5.2 | Total area for each cell layout design, total sensitive region and P-hit and N-hit sensitive area $(\mu m^2)$                                                                                                                                                                                |

| 5.3 | Total area for each cell layout design, total sensitive region and P-hit and N-hit sensitive area $(\mu m^2)$                                                                                                                                                                                |

| 5.4 | Signal Probability Estimation for the INV, NAND, NOR and XOR gates                                                                                                                                                                                                                           |

18 LIST OF TABLES

| 5.5 | Weibull fitting parameter from the cross-section curves of Fig- |     |

|-----|-----------------------------------------------------------------|-----|

|     | ure 5.26. Saturation cross-section and threshold LET corre-     |     |

|     | spond to Sat XS and $LET_{TH}$ values, respectively             | 121 |

| 6.1 | Number of transistors, layout and drain area $(\mu m^2)$ of the |     |

|     | CMOS1, CMOS2, NAND-based, NOR-based and BAN ma-                 |     |

|     | iority architectures                                            | 13! |

# Acknowledgement

Firstly, I would like to thank my supervisors Prof. Frédéric WROBEL and Prof. Jean-Luc AUTRAN, for their support throughout this journey during my Ph.D. project. I have really enjoyed and grown as a scientist during my period in the University of Montpellier and Aix-Marseille University. Thank you, Prof. Wrobel, for believing in me for the development of this project since the first online interview in 2017. Also, for teaching me a lot about particle interaction mechanisms, prediction methodologies and for the numerous valuable discussions. And, thank you, Prof. Autran for giving me the opportunity to completely design for the first time my own test chip to study radiation effects (a special thanks to my colleague Jean-Pierre Walder who has guided me though this process).

Secondly, I would like to show my gratitude to all my colleagues from the RADIAC team. From staff to students, you were all essential for the creation of a perfect environment for the development of this thesis. A special thanks goes out to my colleague Salvatore Guagliardo, who I had the pleasure to share an office during these past 3 years. I will miss this incredible team. Also, I would like to thank my colleagues from the RADSAGA project for the discussions and for the shared moments in the countless RADSAGA related events. A special thanks to Vanessa Wyrwoll and Sascha Lüdeke for their friendship.

And lastly, I would like to thank my family and friends that even from far, have shown all the support that I needed during this period. I wouldn't be here if it wasn't for you all.

# Abstract

The reliability of electronic circuits is subject to physical damage or functional failures due to the influence of the application environment, such as the presence of atmospheric or space radiation. The particle interaction within silicon can lead to permanent or transient effects such as the Single-Event Effects (SEEs). Due to the intrinsic masking effects of combinational circuits in digital designs, Single-Event Transient (SET) effects were considered irrelevant compared to the data rupture caused by Single-Event Upset (SEU) effects. However, the importance of considering SET in Very-Large-System-Integration (VLSI) circuits increases given the reduction of the transistor dimensions and the logic data path depth in advanced technology nodes. Accordingly, the threat of SET must be carefully addressed along with the SEU characterization in electronics systems from space to ground applications. Also, to increase the reliability of the systems, radiation hardening techniques can be adopted in the process or design levels. The characterization process is usually experimental-test oriented, however, the need of adopting modeling simulations to study fundamental radiation effects and improve testing methodologies has led to an increase interest in developing SEE characterization methodologies based on simulation tools. Accordingly, this thesis provides a complete simulation chain based on a multi-physics and multi-scale approach to characterize electronics component against SEU/SET effects. Additionally, radiation-hardening-by-design (RHBD) techniques were evaluated and proposed at physical layout and circuit levels. The physical layout design influences the SEE generation mechanisms induced by a particle strike hence hardening techniques are widely used in the layout level to reduce the charge collection process. Besides analyzing 4 LIST OF TABLES

the gate sizing and transistor stacking, in this work, the transistor folding layout is proposed along with the diffusion splitting technique. The results have shown that folded designs can provide lower SET cross-section in addition to the higher threshold LET than the observed for the unfolded designs. At circuit-level, the implications of logic synthesis of cell-based designs are studied. Additionally, given the input dependence of the RHBD techniques, signal probability is proposed as an application-specific hardening approach in order to improve the hardening efficiency while reducing the design drawbacks and, very importantly, avoid misleading qualifications. For instance, a pin assignment optimization targeting SET effects can provide reduction on the overall SET rate without any area overhead. Additionally, selective TMR block insertion methodologies can be optimized based on the signal probability of the critical nodes and the majority voter architectures.

## Résumé

La fiabilité des circuits électroniques est sujette à des dommages physiques ou à des défaillances fonctionnelles en raison de la présence du rayonnement atmosphérique ou spatial. L'interaction des particules dans le silicium peut entraîner des effets permanents ou transitoires tels que les effets d'événement singulier (SEE). En raison des effets de masquage intrinsèques des circuits combinatoires dans les conceptions numériques, les événements singuliers transitoires (SET) ont été considérés comme non pertinents par rapport à la rupture de données causée par les aléas logiques (SEU). Cependant, l'importance de considérer les SETs dans les circuits VLSI (Very-Large-System-Integration) augmente étant donnée la réduction des dimensions des transistors et de la profondeur du chemin de données logique dans les technologies avancées. En conséquence, la menace associée aux SET doit être soigneusement traitée en même temps que la caractérisation du SEU dans les systèmes électroniques des applications spatiales, avioniques et même pour les applications au sol. De plus, pour augmenter la fiabilité des systèmes, des techniques de durcissement peuvent être adoptées dans les niveaux de processus ou de conception. Le processus de caractérisation est généralement orienté vers les tests expérimentaux, mais la nécessité d'adopter des simulations de modélisation pour étudier les effets fondamentaux des rayonnements et améliorer les méthodologies de test a conduit à un intérêt accru pour le développement de méthodologies de caractérisation des SEEs basées sur des outils de simulation. En conséquence, cette thèse fournit une chaîne de simulation numérique complète basée sur une approche multi-physique et multi-échelle pour caractériser les composants électroniques contre les effets SEU / SET. De plus, des techniques de durcissement par design (RHBD)

6 LIST OF TABLES

ont été évaluées et proposées au niveau du layout physique et du circuit. La conception du layout physique influence les mécanismes de génération de SEE induits par une collision des particules. Par conséquent, les techniques de durcissement sont largement utilisées au niveau du layout pour réduire le processus de collecte des charges. Au-delà de l'analyse du dimensionnement et de l'empilage des transistors, ce travail propose l'utilisation du layout de transistors repliés ainsi que la technique de « diffusion splitting ». Les résultats ont indiqué que les designs repliés peuvent offrir une section efficace de SET inférieure ainsi qu'un LET seuil plus élevé que celui observé pour les designs non repliés. Au niveau des circuits, les implications de la synthèse logique des conceptions à base de cellules sont étudiées. En outre, étant donné la dépendance des techniques RHBD par rapport au signal d'entrée, la probabilité du signal est proposée comme une approche de durcissement spécifique à l'application afin d'améliorer l'efficacité du durcissement tout en réduisant les inconvénients de conception et d'éviter les qualifications trompeuses. Par exemple, une optimisation de l'affectation des broches qui vise les effets SET peut permettre de réduire le taux global de SET. De plus, les méthodologies d'insertion sélective de blocs TMR (Triple Modular Redundancy) peuvent être optimisées en fonction de la probabilité de signal des nœuds critiques et des architectures de votes majoritaires.

## 1

# Introduction

#### 1.1 Context and Overview

The reliability of electronic circuits is subject to physical damage or functional failures due to the influence of the environment, such as the presence of atmospheric or space radiation [1]. The energy deposition of a single energetic particle in the sensitive areas of a circuit can lead to destructive or non-destructive failures, known as Single-Event Effects (SEE). Initially, the first studies on circuit reliability under radiation effects were conducted for military or space applications. Back in 1962, the work developed in [2] was the first study to predict that cosmic radiation could become a threat for circuit design as the technology is scaled down into the nanometer world. And, only later in 1975, Binder et al. [3] were able to identify anomalies in the bit storage of flip-flop circuits within a satellite and attributed to the cosmic radiation effects.

Besides the radiation effects observed in space applications, anomalies in the circuit operation at sea level were also identified as early as 1978 [4]. However, the root of the anomalies observed in memory circuits were associated to the alpha particles emitted from the uranium and thorium naturally present in the package material surrounding the device. This paper used for the first time the term *soft errors* to associate the non-destructive radiation effects in electronics, and it is still largely adopted in the research

community. In the year after, Guenzer et al. [5] have shown that neutrons and protons can also induce upsets in memory elements when they trigger nuclear reactions within the circuit material. In this paper, the term *Single-Event Upset* (SEU) were first adopted to address the bit-flips observed in memory circuits due to the incidence of particle radiation.

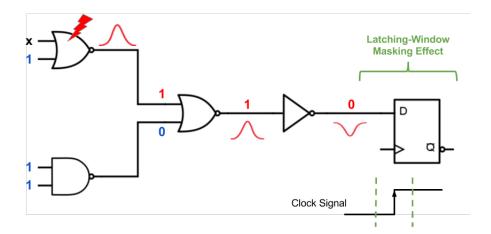

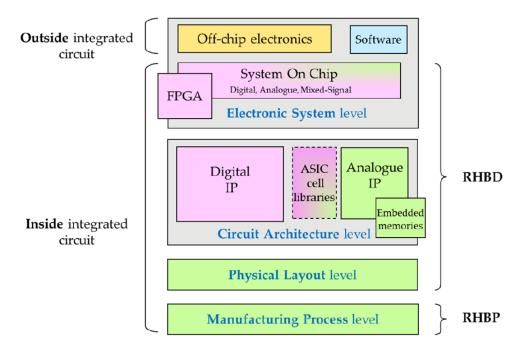

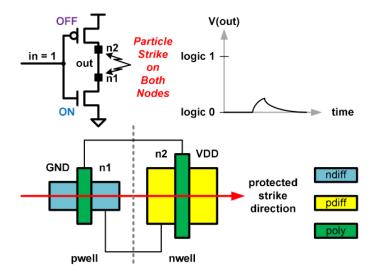

Initially, most of the studies were focused in the radiation effects on memories due to the higher impact on the functionality of the systems. Only after nearly 10 years, since the first observation of upsets in satellites by Binder et al. [3], that the transient effects were observed in combinational logic circuits by May et al. [6]. Then, several works during the 90's started to look over the anomalies in the combinational part of logic circuits and it was getting more attention from the radiation effects research community [7]. It was in the work developed in [8] which reported that radiation-induced transients could propagate and upset latch gates. Though the transient effects were observed since 1984, the term Single-Event Transient (SET) was only first adopted in 1990, by Newberry et al. [9]. Historically, SEUs have been vastly studied in the literature while SETs were not given as much importance due to the intrinsic masking effects of combinational logic circuits [7]. There are three main masking effects inherent in digital circuits: i) electrical masking, in which the transient pulse is not able to propagate through a logic path due to electrical losses and attenuation of its amplitude; ii) logical masking, in which a SET will be masked due to the logic dependence of each digital signal; and, iii) latch-window masking or temporal masking, in which the SET pulse is masked by the latching window of a memory element, i.e. the SET does not reach the memory element on its writing mode operation. However, the transistor scaling, the reduced logic data path depth and increased operating frequencies have attenuated the electrical, logical and latch-window masking effects of logic circuits at advanced technology nodes [10–13]. Accordingly, several works started the development of radiation hardening techniques and mitigation schemes to reduce the impact of soft errors (both SEU and SET).

In this context, an Innovative Training Network (ITN) funded by the European Commission through the Marie Skłodowska-Curie Actions has been

approved in 2016 to foster the development of research on the radiation effects in electronics and to support the interaction among industry, university and laboratories. The ITN RADSAGA (RADiation and reliability challenges for electronics used in Space, Aviation, Ground and Accelerators) is composed by 31 partners from 11 European countries where 15 PhD projects [14]. The present thesis was developed in the framework of the RADSAGA Work Package 2 (Reliability and Testing).

### 1.2 Objectives and Contributions

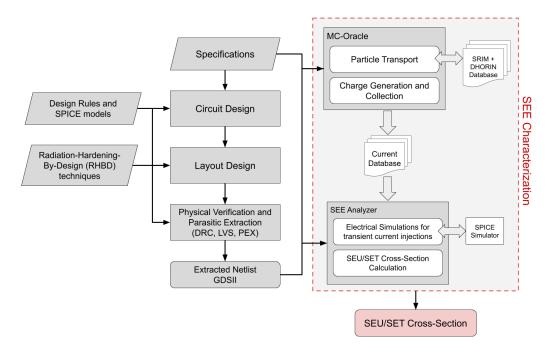

The goal of this thesis is twofold: to propose a general methodology based on a simulation chain to predict the SEE susceptibility of circuits, and by using this methodology, to provide analysis of radiation-hardening-by-design (RHBD) techniques. The main investigated effect will be the Single-Event Transient (SET) in typical CMOS circuits such as standard-cell gates, adders, multipliers, etc.

The contributions of this thesis can be summarized as follows:

- 1. A simulation chain based on a multi-physics and multi-scale approach is proposed and used to analyze RHBD techniques.

- 2. We provided a deep analysis of RHBD approaches at layout-level such as Gate Sizing, Transistor Stacking and Transistor Folding;

- 3. By better understanding the input dependence of SET cross-section, strategies were proposed to improve the hardening efficiency of well-known RHBD techniques. For instance, we have shown that by identifying the input dependence of majority voter architectures, Triple-Modular Redundancy (TMR) insertion optimization can be improved to obtain higher fault coverage and less overhead, which is very crucial when adopting radiation hardening by design techniques;

- 4. We discussed how the proposed methodology can be integrated into a VLSI design methodology in order to obtain a reliability-driven synthesis, whether during the physical or the logic synthesis. Also, a pin

- assignment optimization based on the signal probability is proposed to improve the circuit reliability with no overhead in area.

- 5. A test chip design was completely developed using a commercial 65nm bulk CMOS technology. The chip contains 18 blocks of circuits: 10 majority voter architectures, 4 circuits to study the complex-logic gate layout effects and 4 circuits to study the transistor folding layout effects. Due to limited time, experimental results were not available to be included in the thesis.

#### 1.3 Thesis Organization

In Chapter 2, the natural radiation sources and the basic mechanisms of particle interaction with matter are described to introduce to the radiation effects analyzed in this work. Also, the well-known prediction models and the proposed prediction methodology is discussed in this chapter. Chapter 3 provides a report on well-known and state-of-the-art radiation hardening techniques. After reviewing some hardening techniques, Chapter 4 and Chapter 5 provide our analysis of some RHBD techniques. The layout-based techniques such as Gate Sizing, Transistor Stacking and Transistor Folding are explored specifically in Chapter 4. On the other hand, the circuit-level techniques are explored in Chapter 5. The proposed improvements of the radiation hardness of RHBD techniques is presented in Chapter 6. To conclude, besides providing a summary of the results obtained in this thesis and the list of publications, Chapter 7 provides a discussion on prospective future research in this subject.

# Radiation Effects and Prediction

The evaluation of the reliability of circuits operating in harsh environments is a crucial process in order to prevent functional failures and even catastrophic events. This chapter provides the foundations to understand the dynamics of natural radiation environments and the prominent effects observed in electronic components.

#### 2.1 Radiation Environments

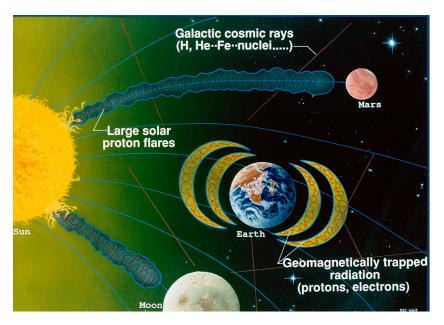

In this section, space and atmospheric radiation are discussed in terms of radiation sources, particles and fluxes. For projects aiming at the near-Earth space environment, there are three main source of radiation that need to be considered as shown in Figure 2.1: the Solar Energetic Particles (SEPs), Galactic Cosmic Rays (GCRs) and geomagnetically trapped particle radiation (Van Allen's radiation belts). The SEPs are particles continuously released by the sun due to its activity. While the GCRs are radiation coming from outside of our Solar System and it is believed to be product from supernova explosions, the Van Allen's radiation belts are composed of both solar and galactic cosmic radiation trapped by the Earth's geomagnetic field. The Sun activity is the main radiation modulator of the space environment in

the vicinity of Earth, influencing not only on the solar particles, but also on the fluxes of GCRs and the radiation trapped by the Earth's magnetosphere. Thus, to understand the dynamics of the natural space radiation environment, it is imperative to study the solar activity, which is closely related with the number of observable sunspots in the photosphere, i.e. the sun's surface.

Figure 2.1: Space Radiation Environment [15].

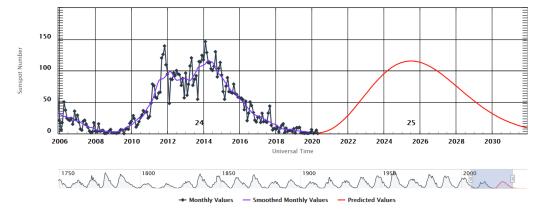

The sun has a cyclic activity of approximately 11 years, divided into solar maximum (about 7 years) and solar minimum (about 4 years). Based on the sunspot number (also known as Wolf number), Figure 2.2 shows the current solar activity, cycle 24, and the predictions for the following cycle. The sun is continuously emitting low-energy particle radiation composed mostly of protons and electrons, the so-called solar wind. However, solar particle events, such as the Coronal Mass Ejection (CME) and solar flares, are rare events in which a massive number of high energetic particles are emitted and can reach the Earth's atmosphere in a relatively short time (few hours or days). The intensity of solar winds and the frequency of solar particle events are directly dependent on the solar activity, i.e. the number of sunspots. For instance, CMEs and solar flares are known to occur more often

during the solar maximum, especially in the declining phase [36 uznanski]. On the other hand, the GCR modulation shows an anti-correlation with the solar activity: a higher activity leads to a lower GCR flux and vice-versa [16–18]. Generally, GCRs present the lowest particle flux, however, as it is composed of high energetic particles, they are highly penetrating particles which shielding technology is not an effective solution to reduce radiation exposure. Thus, despite its low flux, GCRs are a threat for space-borne electronics and human health.

Figure 2.2: Solar Cycle Flux Progression: current solar cycle 24 and prediction of cycle 25 based on the sunspot number [19].

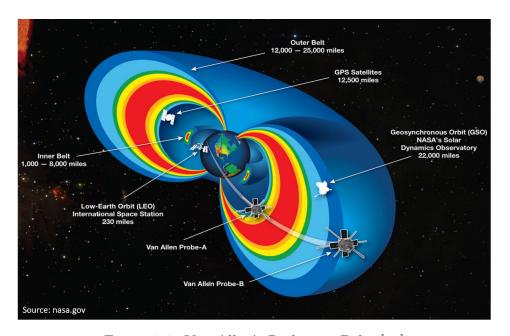

The trapped particle radiation in the Van Allen's belts are clearly separated into two different belts: the outer belt consisting mainly of electrons from solar winds, and, the inner belt composed mostly of protons product of cosmic-ray interactions in the Earth's atmosphere [20]. As can be seen in Figure 2.3, the outer belt is wider than the inner belt, and it is also the most unstable due to the weaker influence of the Earth's magnetosphere. Similarly as the GCRs, the trapped radiation is also modulated by the solar activity: the higher the activity, the higher is the electron intensity and the lower is the proton intensity [21]. The Van Allen's radiation belts have been always a concern for space mission designs due to its impact on the electronics reliability. Protons are able to induce a variety of effects ranging from parametric degradation due to observed dose to even singular effects. These radiation effects are further detailed in the next section. Another important

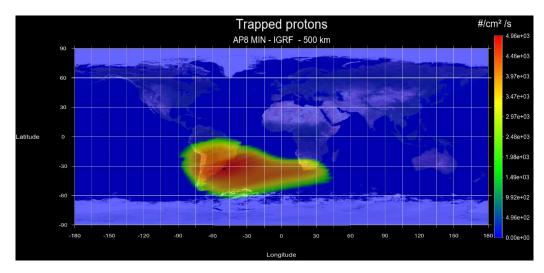

aspect to be considered in the design of components for space applications is the anomaly present in the Earth's magnetosphere. Due to a displacement and misalignment between the Earth's geomagnetic and rotational axes, energetic particles can reach low altitudes in the south of Brazil in response to a weakness in the magnetic field over South America (and, in the same way, a stronger field is observed in Northern Asia). This phenomenon is known as South Atlantic Anomaly (SAA). The SAA is a dominant contributor to the radiation damage observed in spacecraft in the low-earth orbit (LEO). This anomaly is illustrated in Figure 2.4 in which, by using the AP8 MIN model, the high proton flux is identified at altitudes as low as 500 km and below.

Figure 2.3: Van Allen's Radiation Belts [15]

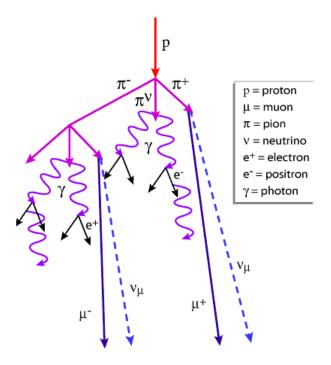

When the cosmic radiation enters the Earth's atmosphere, they collide with the atmospheric atoms (such as nitrogen and oxygen) and produce secondary radiation. Similarly, these secondary particles can also interact with the atmospheric atoms and produce new secondary particles as shown in Figure 2.5. This phenomenon is known as *cosmic ray air shower*. Historically, the secondary neutrons have been the most expressive contributor to the radiation effects observed in the atmospheric environment. However, with the

Figure 2.4: Flux intensity map for the > 10 MeV channel at 500 km altitude. Higher proton flux in the South Atlantic Anomaly (SAA) region. The graph is obtained using the AP8 model available in the OMERE software tool [22].

Figure 2.5: Secondary radiation induced by a proton interaction with an atmospheric atom and leading to a cosmic ray air shower [23].

technology scaling, muons have shown an increased capability of inducing radiation damage on microelectronics and, thus, they can also be considered a threat to the system reliability [24]. The neutron density increases as the altitude decreases until about 20km which the peak density is reached [25]. At ground level the density decreases to 1/500 the peak flux.

#### 2.2 Radiation Effects

In the previous section the dynamics and the composition of the radiation environments in space and atmosphere were presented. This section provides an introduction to particle interaction physics related to the radiation effects observed in electronic components. These effects can be classified into two groups: Cumulative effects, comprising the Total Ionizing Dose (TID) and Displacement Damage (DD); and, Single-Event Effects (SEEs), a group of effects in which a single particle hit is able to disturb the correct operation of electronic devices. In this thesis, the research is focused on the study and mitigation of SEEs, more specifically the non-destructive effects, i.e. the *soft errors*. Accordingly, the following sections will be particularly directed to understand these effects.

#### 2.2.1 Energy Deposition

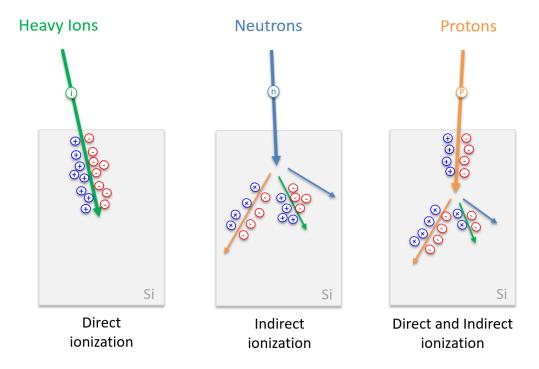

Particle interactions with matter can be classified into two groups when considering SEEs: (1) interactions induced by charged particles; and, (2) induced by uncharged particles, i.e. neutrons. When a charged particle, such as protons and heavy ions, travels through the matter, it loses energy as it collides with the electrons and nuclei of the target material [26]. These collisions can lead to the generation of electron-hole pairs when sufficient energy is transferred in order to eject the electron from the valance band. This phenomenon is known as *ionization*. The main mechanism responsible for this energy transfer is the inelastic collision due to the higher probability of interaction with the atomic electrons rather than the atomic nuclei itself [26]. However, protons can also lose energy through nuclear reactions. In the

end of the interaction path, when the particle has lost most of its energy, the main energy transfer occurs due to nuclear elastic collisions, i.e. the particle collides with the nuclei and it can lead to the displacement of the lattice.

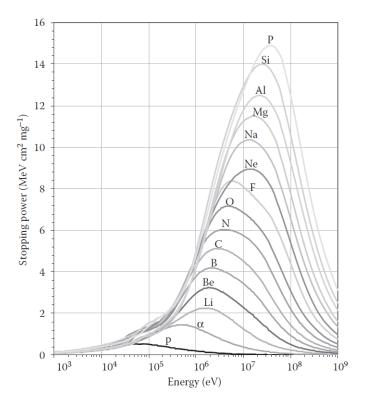

These interactions are responsible for the energy loss and the particle slowdown. The amount of energy that a particle can lose per unit length travelled corresponds to what we call the *stopping power*. There are two classifications based on the nature of the energy loss: (1) the *electronic stopping power*, for the energy loss induced by collisions with the electrons of the target material, and (2) the *nuclear stopping power*, for the energy loss due to nuclear elastic collisions. For the radiation effects concerned in this thesis, the nuclear stopping power does not provide a great contribution. Thus, only the electronic stopping power, also known as *Linear Energy Transfer* (LET) in the radiation effects community, is taken into consideration [26]. The LET measures the energy deposition induced by the ionization process and it can described as the following equation:

$$LET = -\frac{1}{\rho} \frac{dE}{dx} \tag{2.1}$$

where  $\rho$  is the density of the target material,  $\Delta E$  is the energy loss, and  $\Delta x$  is the ionizing path length. The LET unit is given in megaelectronvolts square centimeter per milligram  $(MeV.cm^2/mg)$ . For electronics, the silicon density is used,  $\rho_{Si} = 2.32g.cm^{-3}$ . The LET depends not only on the particle type, but also on its energy and the target material where the ionization takes place. In Figure 2.6, the variation of LET is shown as function of the ion energy in silicon. The LET of a particle increases as the energy increases until it reaches the Bragg peak, the highest LET value. Then, it decreases along with the increase in particle energy. It can be noticed that different ion species with different energies can provide the exact same LET value.

So far, only the *direct ionization* has been discussed, i.e. when the incident particle is the primary contributor to the creation of electron-hole pairs. However, high-energy protons and neutrons can experience nuclear reactions resulting in secondary particles that may be able to ionize the matter. This process is known as *indirect ionization* and it is also highly

Figure 2.6: Variation of Linear Energy Transfer (LET) as function of energy for different ions in silicon [26].

important in the analysis and qualification of radiation effects on electronic components. Figure 2.7 illustrates the direct and indirect ionization of a heavy ion and a neutron, respectively. Protons interact through both direct and indirect ionization depending on its energy.

The energy deposition in the semiconductor leads to a nearly linear path of electron-hole pairs (ehp). The minimum energy required to generate a electron-hole pair can be estimate based on the band-gap energy  $E_g$  of the material using the Equation 2.2 [27]:

$$E_{\rm ehp} = 2.73 E_g + 0.55 eV \tag{2.2}$$

For silicon-based devices, the silicon band-gap energy  $E_g$  is equal to 1.11 eV, therefore, the ionization energy  $E_{ehp}$  is approximately 3.6 eV/ehp. The higher the band-gap energy of the material, the higher is the energy required

Figure 2.7: Representation of Direct Ionization and Indirect Ionization for heavy ions, neutrons and protons interaction with matter (Si stands for Silicon).

to ionize the matter. This explains why wide-bandgap electronics such as the SiC- and GaN-based devices show a better radiation performance.

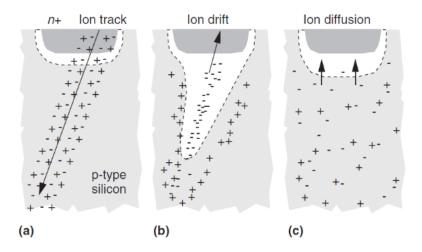

#### 2.2.2 Charge Collection

After the energy deposition, the released carriers are transported and collected by the junctions of the device. There are two main transport mechanisms to be considered in SEEs, the *drift* and the *diffusion*. Drift is a mechanism governed by the electric field present in the p-n junction of the sensitive devices. For instance, when a particle hits directly the sensitive collecting area of the circuit, the carriers will be rapidly collected due to the high electric field present in the reverse-biased p-n junctions. On the other hand, diffusion is a carrier transport mechanism governed by the carrier concentration gradients. It means that the carriers will transport from regions with high to low carrier concentration. In Figure 2.8, the ionization

process followed by carrier drift and diffusion is illustrated for a ion strike in a reverse-biased p-n junction .

Figure 2.8: Charge collection mechanisms due to an ion strike in a p-n junction [28].

If the particle strikes in or near the p-n junction, the charge collection can be enhanced due the funneling effect in the electrical field which increases the depletion region and improve the collection efficiency (Figure 2.8 (b)). The drift and funneling effect are two very fast process due to the high electric field present in the junction. Following these processes, the remaining carriers are collected by the diffusion process or recombined. The minimum collected charge necessary to observe a SEE in a component is known as the critical charge  $Q_{crit}$ .

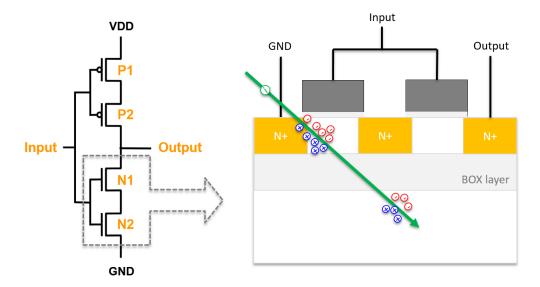

## 2.2.3 Charge Sharing and Pulse Quenching Effect

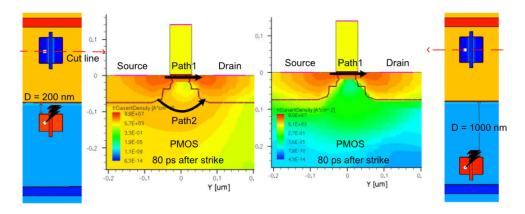

With the technology integration, transistors are placed more closely together and the critical charge is reduced. As a consequence, a single incident particle is able to induce sufficient charge collection from multiple electrodes. This phenomenon is known as charge sharing effect. The work developed by Amusan et al. [29] provides an analysis of the charge sharing effect in adjacent devices for NMOS and PMOS transistors. In Figure 2.9 (a), the outline of two adjacent NMOS devices is illustrated and two notations are given: the

active device/node, for the device that got hit by a particle and it is actively collecting the carriers; and, the passive device/node, for the device that was not hit by the particle but it is passively collecting the diffused carriers. In the Figure 2.9 (b) the collected charge is shown for the active and passive devices when PMOS and NMOS transistors are used. Clearly, it can be seen that the passive PMOS is able to collect more than a passive NMOS device. For instance, the passive PMOS collected about 40% of the charge collected by the active PMOS device, while less than 25% is collected by the passive NMOS transistor. The authors attributed this difference to the difference of the carrier diffusion coefficient of electrons and holes, and, to the bipolar amplification effect that enhances the charge collection in the PMOS devices [29][30].

Figure 2.9: (a) outline of two NMOS adjacent devices and (b) charge collected for PMOS and NMOS as active and passive devices [29].

Though the charge sharing mechanism is responsible for the increase of SEE sensitivity due to multiple SETs or multiple SEUs, it was shown that it can also reduce the SET pulse width in combinational cells [31][32]. Due to the similar time constant for the circuit delay and the diffusion process, the radiation-induced transient is able to activate the charge collection by electrodes from following stage of circuits in such a way that the resultant transient is shortened (i.e., quenched). This phenomenon is known as Pulse Quenching Effect (PQE) and it can be better understood by analyzing the Figure 2.10. To observe the PQE, the involved circuits must have an inverting

relationship as shown in the inverter chain in Figure 2.10. The charge sharing and pulse quenching effect are two very important mechanisms necessary to understand the SEE sensitivity of state-of-the-art electronic components. Accordingly, both of them will be extensively used to discuss the results observed in this thesis.

Figure 2.10: SET Pulse Quenching Effect in a inverter chain [31].

## 2.2.4 Masking Effects

Besides the charge sharing effects, the inherent masking effect ability of digital circuits are also fundamental when studying soft errors. They can be classified into three effects: *electrical masking*, *logical masking* and *latching-window masking* (also known as temporal masking).

#### Logical masking effect

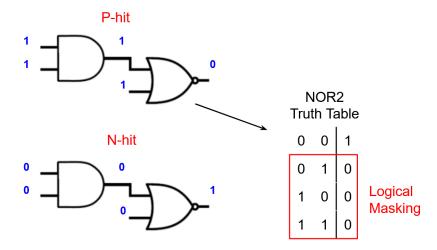

Combinational circuits provide the logical masking effect when the SET event occurs in a logic gate where its output does not determine the output signal of the subsequent logic stage. For instance, a 2-input NOR gate has its output determined whenever one of its input signal is evaluated to 1, i.e. whenever one input signal is at logic 1, the output evaluates to logic

0. This phenomenon can be better understood by analyzing the block of combinational logic in Figure 2.11. A SET event occurs in the first NOR gate, in which the output signal initially was evaluated to logic 0. The SET pulse propagates to the next logic stage, which is also a NOR gate. However, this logic stage has already been evaluated to logic 0 due to the input signal provided by the NAND gate. Since the output of the second NOR gate has already been determined by the one of its inputs, the SET pulse is not able to change it, hence it is logically masked and cannot propagate to the next logic stage and reach a memory element, for instance. Although the effectiveness of this mechanism, recent technologies have shown a reduction in the logic depth of combinational circuits, thus logical masking effect has been reduced [33].

Figure 2.11: Illustration of the logical masking effect of a SET event in a 2-input NOR gate within a block of combinational circuit [34].

#### Electrical masking effect

The electrical masking effect is another phenomenon that can occurs in a combinational circuit and prevent the propagation of a SET pulse. Due to electrical losses, a SET pulse suffers from magnitude and amplitude attenuation and it might not be able to propagate to a memory element as observed in Figure 2.12. The initial SET pulse has its waveform affected by each stage of logic, being vanished near the memory element. In this case, the propagated SET pulse did not have sufficient amplitude to upset

the memory element due to the electrical masking effect. However, it was shown that not only the transient pulse can suffer from attenuation, but it can also experience broadening effect, the so-called Propagation-Induced Pulse Broadening (PIPB) [35, 36]. The pulse width of the SET depends on the restoring current of the struck circuit and its capacitive load (fan-out). Larger capacitance can lead to increase of the critical charge, however it can lead to pulse broadening due to the longer time to restore the output voltage [37].

Figure 2.12: Illustration of the electrical masking effect of a SET event due to electrical losses in a logic path [34].

#### Latching-window masking effect

In the end, if the SET pulse has not been masked logically or electrically, it might still be masked by the latching window of a memory element. This window is composed by the setup time  $(T_{setup})$  and the hold time  $(T_{hold})$  around the edge of the clock signal of a flip-flop circuit. If the SET pulse does not arrive during this latching window, it will not be able to induce a bit upset, i.e. a change in the stored bit value. Figure 2.13 illustrates this phenomenon. Due to the high operating clock frequencies in advanced technologies, the latching-window effect is expected to be reduced given the short  $T_{setup}$  and  $T_{hold}$  of FF designs.

Figure 2.13: Illustration of the latching-window masking effect of a SET pulse by a flip-flip (FF) circuit [34].

# 2.3 Modeling and Prediction

The usage of modeling and simulation has always been present in the study of physical phenomena, especially in the field of electronics to study the behavior of MOS transistors [38, 39]. Further, with the increase of complexity of very-large-scale-integration (VLSI) system, it is increasingly necessary to use the support of simulation studies to verify and assist the development of such circuits. In this sense, Monte Carlo simulation tools have solid foundations to be used in the study of radiation effects on electronics [40]. There are many works in the literature which propose the research of radiation effects on electronics exploiting simulations and avoiding the time consuming and expensive radiation campaigns [41–48]. Mixed-mode Technology Computer-Aided Design (TCAD) simulations have been vastly used to understand the main mechanisms in SEEs on electronics. However, Monte Carlo simulation codes can have a computation time several orders of magnitude lower than TCAD simulations [40, 47]. The randomness and stochastic nature of particle interaction with the matter is a perfect fit for Monte Carlo (MC) simulations. Accordingly, a diverse number of modeling based on the MC method have been proposed to estimate and predict the radiation robustness of electronics [41–44, 47]. In contrast to deterministic models, in the MC

method, random sampling and statistical modeling are used to approximate solutions for stochastic problems, such as in particle physics.

Historically, the well-known rectangular parallelepiped (RPP) analytical model [49], also known as chord-length model, has been vastly used to analyze and predict the radiation response of electronic components [50]. In this approach, the device is assumed to have a well-defined sensitive volume (SV) in the form of a rectangular parallelepiped. The ionization track path is determined by the depth of the SV and the incidence angle,  $\theta$ . It is assumed that charge collection induced by diffusion from ion striking outside the RPP is negligible and thus not considered. Also, the LET is assumed to be constant over the ionization path so that generated charge within the SV can be calculated by the product of the LET value and the ionization path length, l. In the case of a normal incidence, the ionization path length is equal to the sensitive volume depth, d. Thus, the deposited charge can be calculated using the Equation 2.3. Accordingly, if sufficient charge is deposited inside the SV, i.e. if the deposited charge  $Q_{dep}$  is superior to the critical charge  $Q_{crit}$ , a SEE is assumed to be observed in the circuit.

$$Q_{dep} [pC] = 0.01035 \cdot LET [MeV.cm^2/mg] \cdot d [\mu m]$$

(2.3)

Despite the popularity and its widespread use, the RPP model has turned out to be inadequate when used in advanced technology due to the complex geometry of transistors, the small sensitive volumes and the close proximity of devices. Emerging effects such as charge sharing due to multiple node collection and parasitic bipolar amplification have limited the application of the RPP approach in some cases. One possible extension to this model is the Integral Rectangular Parallelepiped (IRPP) model [51], in which not only a single SV is defined, but a collection of multiple SVs. The IRPP method is widely used to predict SEE rates in the radiation effects community and it is the standard method specified by the European Cooperation for Space Standardization (ECSS) [52]. Alternatively, the diffusion-collection model [53] has been proposed to address the limitations observed in the analytical approaches. By considering a physics-based Monte Carlo simulation,

| Ref. | Tool       | Institution                                     | Radiation Effects |

|------|------------|-------------------------------------------------|-------------------|

| [54] | DASIE      | AIRBUS                                          | SEU               |

| [55] | SEMM-2     | $_{ m IBM}$                                     | SEU               |

| [56] | MRED       | Vanderbilt Univeristy and<br>NASA/GSFC          | SEU               |

| [43] | MC-ORACLE  | Université de Montpellier                       | SEU/SET           |

| [57] | TIARA-G4   | Aix-Marseille University and STMicroelectronics | SEU/SET           |

| [58] | FLUKA      | CERN and INFN                                   | SEU               |

| [42] | MUSCA-SEP3 | ONERA                                           | SEU/SET/SEL       |

Table 2.1: List of simulation tools dedicated to study radiation effects on electronics

it is possible to account for the multiple node charge collection and emerging effects observed in advanced technology nodes. This method will be further explained in the next section, as it is adopted in our prediction methodology. In Table 2.1, a non-exhaustive list of simulation tools dedicated to model and study radiation effects on electronics is presented. Further details adopted in each tool can be found in its respective reference. In this thesis, the MC-Oracle tool [43] is used to account for the energy deposition and charge collection in our SEE predictive methodology.

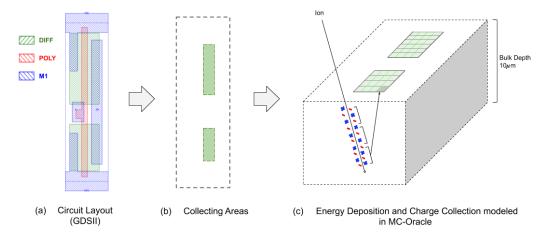

# 2.4 Proposed Prediction Methodology

To accurately assess the SEE immunity of digital circuits, it is highly recommended to adopt a multi-scale and multi-physics methodology due to the plurality of complex effects involved at silicon and circuit level [56, 42]. Different approaches taking into consideration the aspects from the particle interaction physics to the circuit layout design is explored in different codes as shown in [47]. As aforementioned, due to the technology scaling, emerging effects as parasitic bipolar amplification (PBA) and charge sharing effects need to be carefully addressed [44, 59, 60]. Therefore, layout information from the circuit design is an important determinant on the SEE prediction of electronic circuits. Accordingly, in this work a layout-based methodology