# RNS-Flexible hardware accelerators for high-security asymmetric cryptography

Libey Djath

#### ▶ To cite this version:

Libey Djath. RNS-Flexible hardware accelerators for high-security asymmetric cryptography. Cryptography and Security [cs.CR]. Université de Bretagne occidentale - Brest, 2021. English. NNT: 2021BRES0030 . tel-03393289

### HAL Id: tel-03393289 https://theses.hal.science/tel-03393289

Submitted on 21 Oct 2021

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE

### L'UNIVERSITÉ DE BRETAGNE OCCIDENTALE

ÉCOLE DOCTORALE Nº 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Informatique

Par

## **Libey DJATH**

# Accélérateurs matériels RNS flexibles pour la cryptographie asymétrique à haute sécurité

RNS-Flexible Hardware Accelerators for High-Security Asymmetric Cryptography

Thèse présentée et soutenue à Brest, le 25 mai 2021 Unité de recherche : Lab-STICC, CNRS UMR 6285

#### Rapporteurs avant soutenance:

Laurent-Stéphane DIDIER Professeur, Université de Toulon, IMATH

Christophe NÈGRE Maître de conférences HDR, Université de Perpignan, LIRMM

#### Composition du Jury:

Président : Jean-Claude BAJARD Professeur, Sorbonne Université, IMJ-PRG

Examinateurs : Roselyne CHOTIN Maître de conférences HDR, Sorbonne Université, LIP6

Laurent-Stéphane DIDIER Professeur, Université de Toulon, IMATH

Christophe NÈGRE Maître de conférences HDR, Université de Perpignan, LIRMM

Encadrant : Karim BIGOU Maître de conférences, Université de Bretagne Occidentale, Lab-STICC

Dir. de thèse: Arnaud TISSERAND Directeur de recherche CNRS, Lab-STICC

#### Invité:

Benoît GÉRARD Expert cryptographie, DGA

In memory of my parents, who taught me to think for myself

### **ACKNOWLEDGEMENT**

I articulate my appreciation to my advisors, Karim Bigou and Arnaud Tisserand, for their guidance throughout the PhD. Besides, they provide valuable feedback which help improve the clarity of this thesis. I also thank Vianney Lapôtre and Laurent-Stéphane Didier for pointing out what is expected from me at the end of the PhD, in our two annual meetings.

For accepting the task of reviewing my PhD thesis, Laurent-Stéphane Didier and Christophe Nègre have my gratitude. I am also appreciative of Jean-Claude Bajard and Roselyne Chotin agreements to examine my PhD.

I thank my family for their support during the PhD and far beyond. I am particularly grateful to Bughsin' and Pidassa for reading this thesis in its entirety, eagerly seeking ill-formed sentences.

## **C**ONTENTS

| Li            | st of | Figure   | es                                                           | 11        |

|---------------|-------|----------|--------------------------------------------------------------|-----------|

| Li            | st of | Tables   | S                                                            | 15        |

| Li            | st of | Algor    | ithms                                                        | 17        |

| $\mathbf{Li}$ | st of | Abbre    | eviations                                                    | 19        |

| In            | trodi | uction   |                                                              | 21        |

| 1             | Stat  | te of tl | ne Art                                                       | <b>27</b> |

|               | 1.1   | Asymi    | metric Cryptography                                          | 27        |

|               |       | 1.1.1    | Overview of Asymmetric Cryptography                          | 27        |

|               |       | 1.1.2    | Elliptic Curve Cryptography                                  | 30        |

|               | 1.2   | Modul    | lar Reduction                                                | 38        |

|               |       | 1.2.1    | Montgomery Reduction                                         | 38        |

|               |       | 1.2.2    | Barrett Reduction                                            | 39        |

|               |       | 1.2.3    | On Pseudo-Mersenne Numbers                                   | 40        |

|               | 1.3   | Residu   | ie Number System                                             | 41        |

|               |       | 1.3.1    | Overview of the Residue Number System                        | 41        |

|               |       | 1.3.2    | RNS Inherent Properties and Complexity Measurement           | 44        |

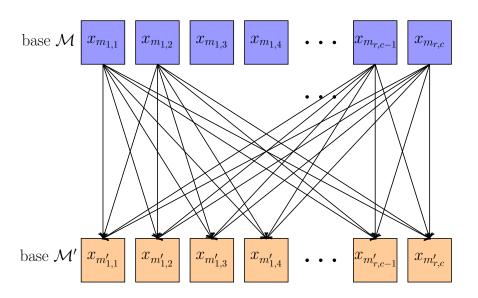

|               |       | 1.3.3    | Base Extension                                               | 46        |

|               |       | 1.3.4    | RNS Modular Reduction                                        | 51        |

|               | 1.4   | Field 1  | Programmable Gate Arrays                                     | 53        |

|               |       | 1.4.1    | Overview of FPGAs                                            | 53        |

|               |       | 1.4.2    | Some RNS Implementations of Asymmetric Cryptosystems on FPGA |           |

|               |       |          | from the Literature                                          | 56        |

|               |       | 1.4.3    | High-Level Synthesis                                         | 58        |

|               | 1.5   | Concli   |                                                              | 59        |

#### CONTENTS

| <b>2</b>     | Hie   | rarchio  | cal Base Extension                                     |                        | 61  |

|--------------|-------|----------|--------------------------------------------------------|------------------------|-----|

|              | 2.1   | Notati   | ions                                                   |                        | 62  |

|              | 2.2   | Kawai    | mura Base Extension                                    |                        | 62  |

|              |       | 2.2.1    | Overview of KBE                                        |                        | 62  |

|              |       | 2.2.2    | KBE Algorithm                                          |                        | 64  |

|              |       | 2.2.3    | The Cox-Rower Architecture                             |                        | 66  |

|              | 2.3   | Hierar   | rchical Base Extension                                 |                        | 67  |

|              |       | 2.3.1    | Overview of HBE                                        |                        | 67  |

|              |       | 2.3.2    | HBE Algorithm                                          |                        | 68  |

|              |       | 2.3.3    | A Cox-Rower Architecture Adapted for HBE               |                        | 79  |

|              | 2.4   | Applie   | cation to RNS Modular Multiplications                  |                        | 81  |

|              | 2.5   | FPGA     | A Implementation Results                               |                        | 84  |

|              | 2.6   | Concl    | usion                                                  |                        | 85  |

| 3            | RN    | S-Flex   | tible Hardware Accelerators for ECC                    |                        | 89  |

|              | 3.1   | Notati   | ions and Definitions                                   |                        | 91  |

|              | 3.2   | Flexib   | ole Kawamura Base Extension                            |                        | 92  |

|              |       | 3.2.1    | Algorithmical Description of the Flexible KBE          |                        | 92  |

|              |       | 3.2.2    | Architecture of the Flexible KBE                       |                        | 92  |

|              |       | 3.2.3    | FPGA Implementation Results                            |                        | 94  |

|              | 3.3   | Flexib   | ole Hierarchical Base Extension                        |                        | 99  |

|              |       | 3.3.1    | Algorithmical Description of the Flexible HBE          |                        | 99  |

|              |       | 3.3.2    | Architecture of the Flexible HBE                       |                        | 99  |

|              |       | 3.3.3    | FPGA Implementation Results                            |                        | 103 |

|              | 3.4   | Flexib   | ole Elliptic Curve Scalar Multiplication               |                        | 106 |

|              |       | 3.4.1    | Overview of the Flexible ECSM                          |                        | 107 |

|              |       | 3.4.2    | FPGA Implementation Results                            |                        | 112 |

|              | 3.5   | Concl    | usion                                                  |                        | 124 |

| Co           | onclu | ısion    |                                                        | -                      | 127 |

| $\mathbf{A}$ | Cor   | nparai   | son d'algorithmes de réduction modulaire en HLS sur FP | $\mathbf{G}\mathbf{A}$ | 131 |

| В            | Ger   | neralize | ed Weierstraß Equation of Elliptic Curves              |                        | 143 |

|              |       |          | the Chinese Remainder Theorem                          | -                      | 145 |

|                                | CONTENTS |

|--------------------------------|----------|

|                                |          |

| Résumé substantiel en français | 147      |

| Bibliography                   | 151      |

## LIST OF FIGURES

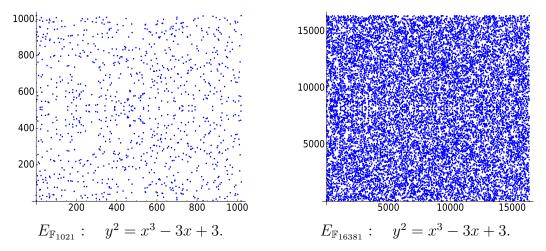

| 1.1 | Example of an elliptic curve defined over two finite fields                                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

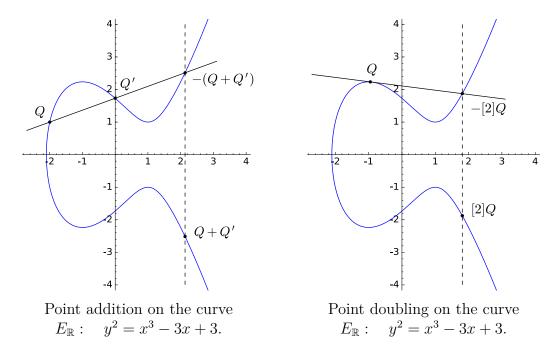

| 1.2 | Geometric description of point addition and point doubling                                                                                                                                                                                                                                                                                                                                                                                                      | 32 |

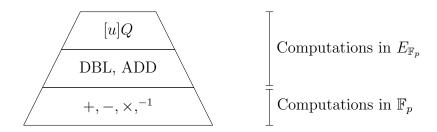

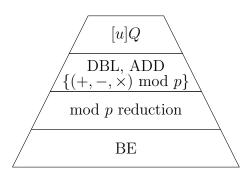

| 1.3 | Hierarchical description of computations involved in an ECSM                                                                                                                                                                                                                                                                                                                                                                                                    | 36 |

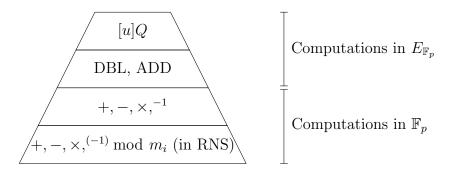

| 1.4 | Hierarchical description of computations involved in an ECSM with RNS                                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | as chosen number system                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38 |

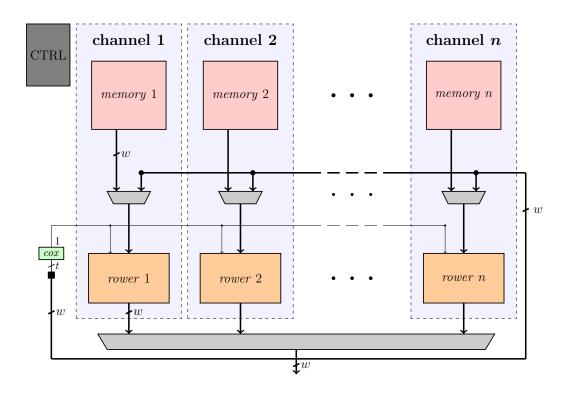

| 1.5 | The cox-rower architecture in [Gui10], adapted from [KKSS00]                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

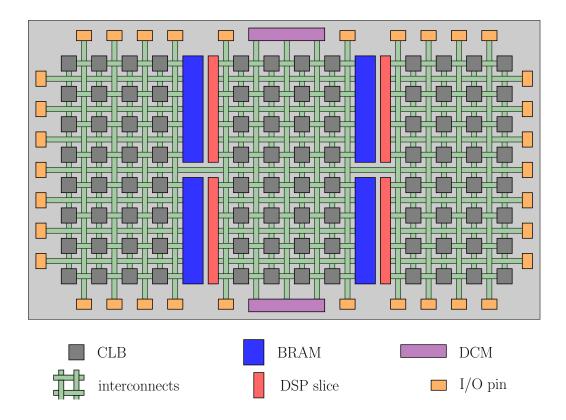

| 1.6 | Simplified view of an FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54 |

| 1.7 | Basic functionalities of the DSP slice in 7-series FPGAs from Xilinx (from                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | [Xil18a])                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55 |

| 1.8 | Excerpt of C code for HLS to explain the multiplication of arrays elements on two channels. Each of the components mul0 and mul1 is dedicated to a channel and performs a multiplication of a value received as input by a precomputed value stored internally. The description made in the component prod allows the components mul0 and mul1 to run in parallel. #pragma HLS PIPELINE allows to pipeline the operations within the loop of the component prod | 59 |

| 2.1 | Simplified description of KBE                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63 |

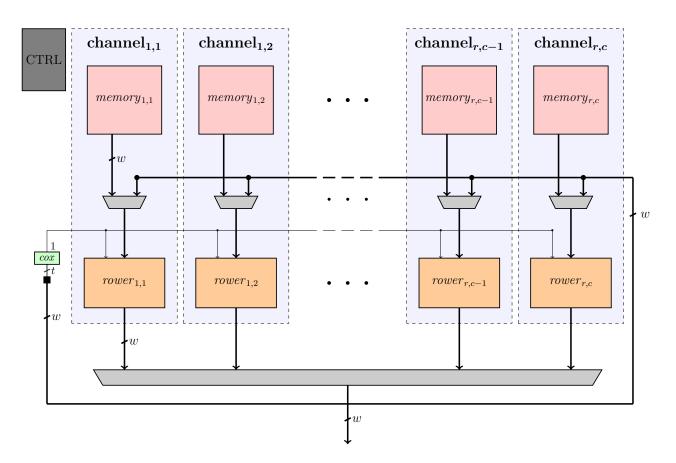

| 2.2 | The cox-rower architecture in [Gui10], adapted from [KKSS00]                                                                                                                                                                                                                                                                                                                                                                                                    | 66 |

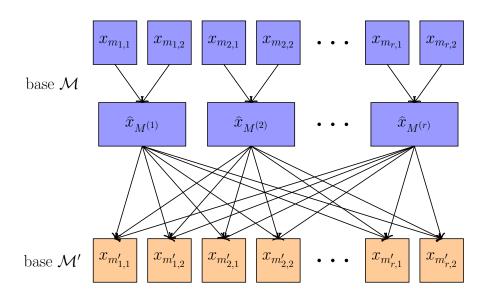

| 2.3 | Simplified description of HBE $c=2$                                                                                                                                                                                                                                                                                                                                                                                                                             | 68 |

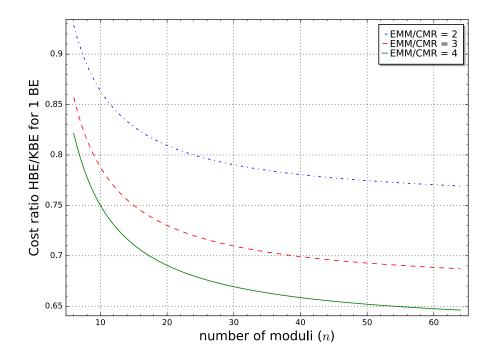

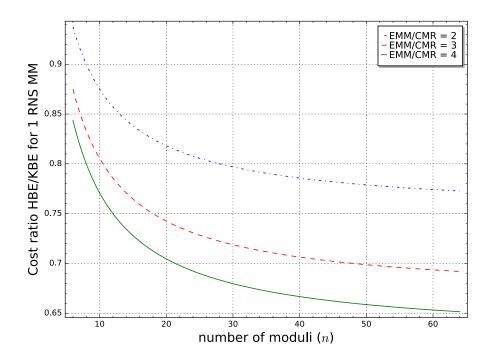

| 2.4 | Theoretical cost ratio HBE/KBE of one BE for various estimations EM-                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | M/CMR(2w+1, w) and numbers n of moduli                                                                                                                                                                                                                                                                                                                                                                                                                          | 79 |

| 2.5 | Architecture of HBE $c=2.$                                                                                                                                                                                                                                                                                                                                                                                                                                      | 80 |

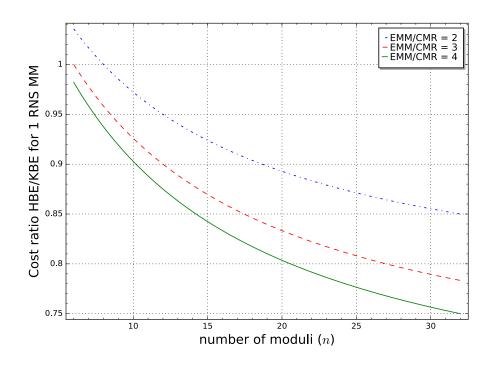

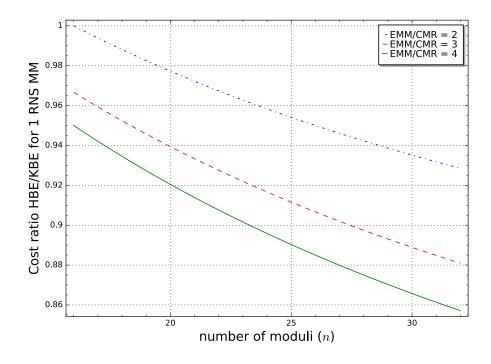

| 2.6 | Theoretical cost ratio HBE/KBE of one RNS MM, with optimizations from $$                                                                                                                                                                                                                                                                                                                                                                                        |    |

|     | [GLP+12], for various estimations EMM/CMR( $2w+1,w$ ) and numbers $n$                                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | of moduli                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82 |

| 2.7 | Theoretical cost ratio HBE/KBE of one RNS MM with $HPR\ d=2$ [BT15]                                                                                                                                                                                                                                                                                                                                                                                             |    |

|     | for various estimations $\mathrm{EMM}/\mathrm{CMR}(2w+1,w)$ and numbers $n$ of moduli                                                                                                                                                                                                                                                                                                                                                                           | 83 |

| 2.8 | Theoretical cost ratio HBE/KBE of one RNS MM with $HPR d = 4$ [BT16]                              | 0.9 |

|-----|---------------------------------------------------------------------------------------------------|-----|

|     | for various estimations EMM/CMR( $2w + 1, w$ ) and numbers $n$ of moduli.                         | 83  |

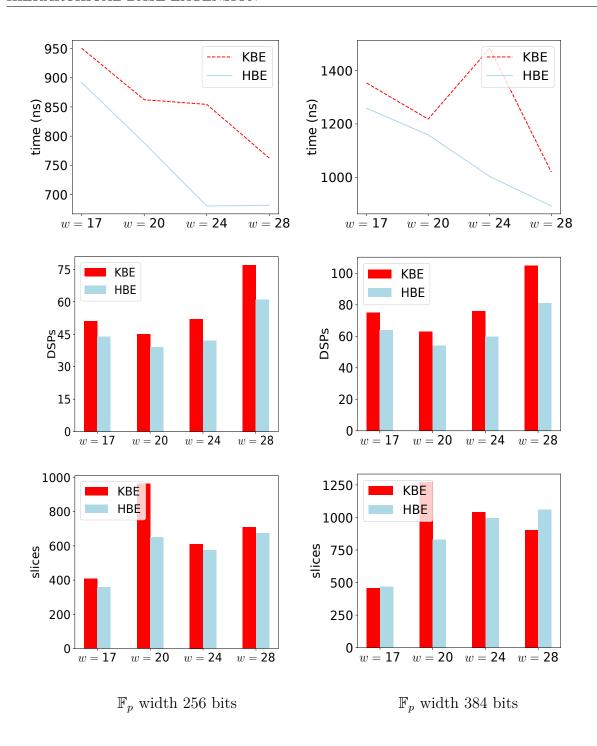

| 2.9 | Comparison of the time, the numbers of DSPs and slices between HBE                                |     |

|     | c=2 (from [DBT19]) solutions and KBE (from [KKSS00]) ones                                         | 86  |

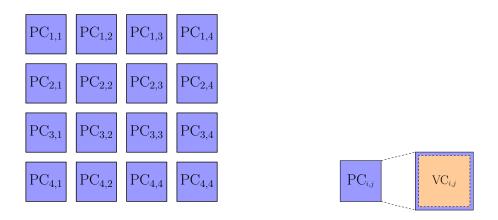

| 3.1 | Decomposition of the numbers $n$ of VCs and $q$ of PCs in usual RNS im-                           |     |

|     | plementations of the ECSM, that is, $q = n$ . In this example, $q = n = 16$ .                     |     |

|     | Computations related to one VC is performed on each PC                                            | 90  |

| 3.2 | Example of decomposition of the numbers $n$ of VCs and $q$ of PCs in RNS                          |     |

|     | implementations of the ECSM when $q = 4$ and $n = 16$ . Computations                              |     |

|     | related to $n/q = 4$ VCs are performed on each PC. At a time, each PC                             |     |

|     | deals with one VC, and the 4 VCs are processed one after another                                  | 90  |

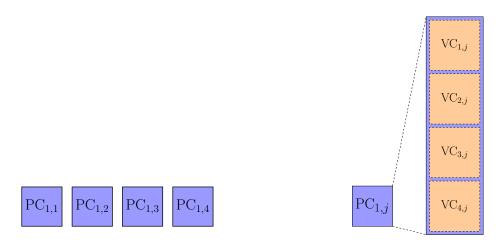

| 3.3 | The architecture for the flexible KBE (adapted from the cox-rower archi-                          |     |

|     | tecture [KKSS00]): example with $q=4$ PCs and $c=2$                                               | 94  |

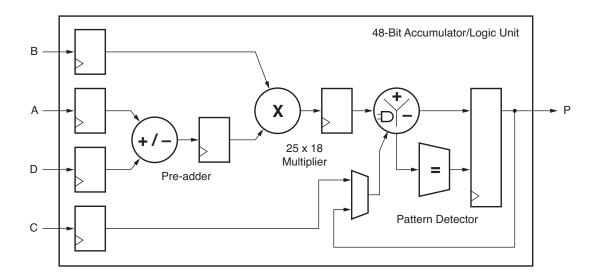

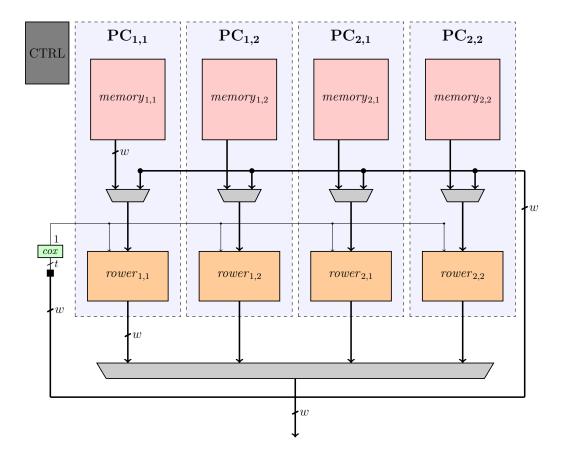

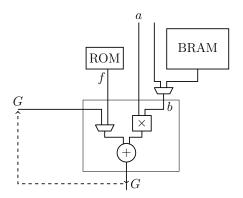

| 3.4 | Structure of the arithmetic processing performed by a rower. The rower                            |     |

|     | performs the operation $g \leftarrow (g + a \times b + f) \mod m$ , where $m = 2^w - \varepsilon$ |     |

|     | (with $\varepsilon < 2^{w/2}$ ), and $a, b, f$ and $g$ are of size $w$ bits                       | 95  |

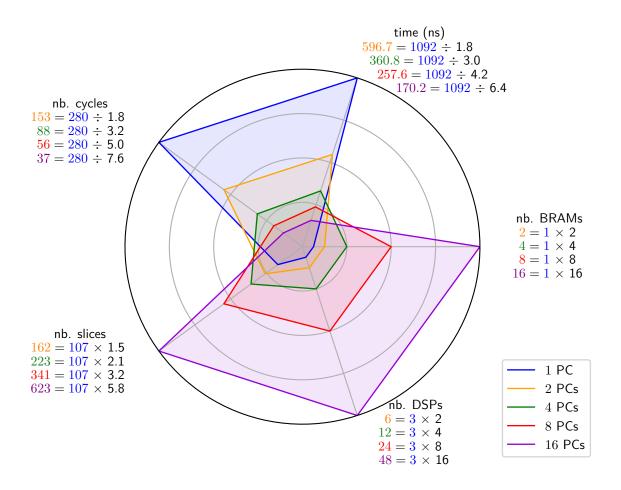

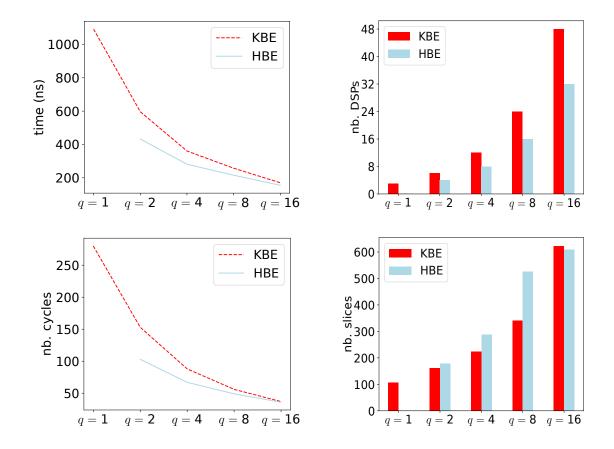

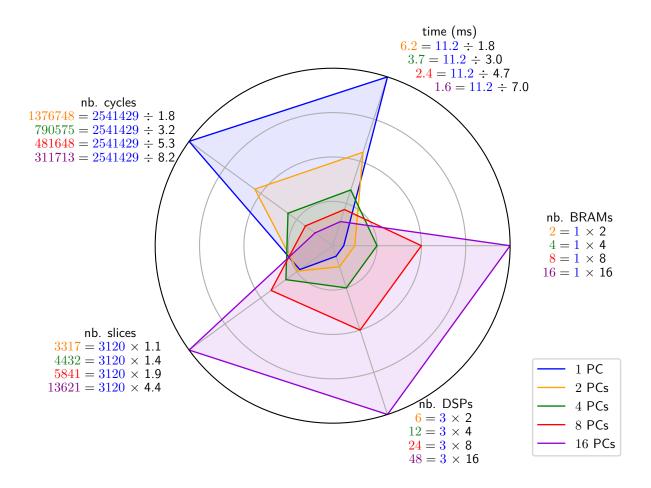

| 3.5 | Comparison of FPGA implementation results of the flexible KBE (adapted                            |     |

|     | from [KKSS00]) for $q \in \{1, 2, 4, 8, 16\}$ PCs. Finite fields are of 256-bit                   |     |

|     | elements and the width of the PCs is 17 bits                                                      | 97  |

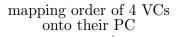

| 3.6 | Example of numbers cycles used by one PC to perform all computations                              |     |

|     | related to the $16/q$ VCs it handles. The PC sequentially 'uploads' the $16/q$                    |     |

|     | VCs. Computations on the same PC are pipelined. In this typical example                           |     |

|     | of loops at lines 1–4 of Algorithm 13, the computations related to the $rc=$                      |     |

|     | 16 VCs are equally shared by the $q$ PCs in use. At the left figure, $q=2$ PCs                    |     |

|     | are used and each PC handles 8 VCs. At the first cycle (top to bottom),                           |     |

|     | computations related to the first VC start. At the next cycle, computations                       |     |

|     | related to the next VC start, and so on until computations related to all 8                       |     |

|     | VCs (mapped onto the PC) start. Meanwhile, it is possible that the PC has                         |     |

|     | terminated the computations related to the VCs that started earlier. Still, a                     |     |

|     | few cycles are needed by the PC to terminate the remaining computations                           |     |

|     | related to its ongoing VCs, that is, to empty out the pipeline. At the right                      |     |

|     | figure, $q = 4$ PCs are used and each PC handles 4 VCs. The filling and                           | 00  |

|     | emptying of the pipeline are similar to the ones at the left figure                               | 98  |

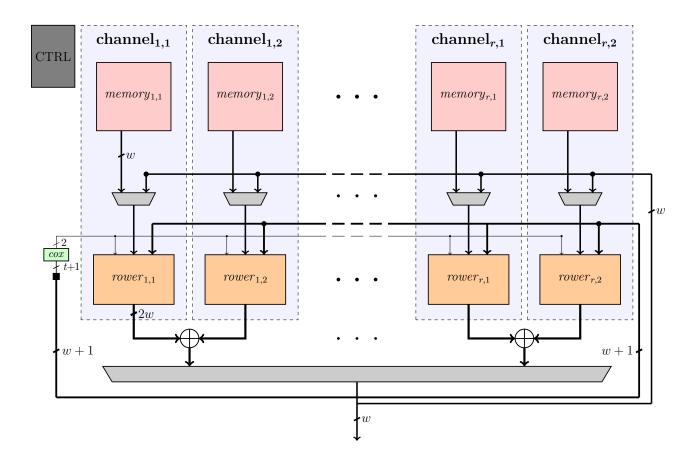

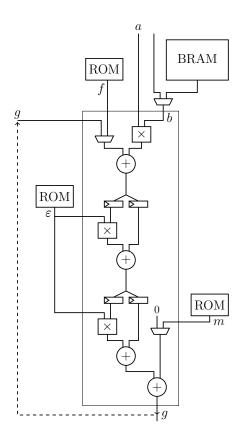

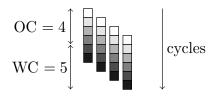

| 3.7  | The flexible architecture for HBE (adapted from the HBE architecture in [DBT19], itself inspired by the $cox$ -rower architecture [KKSS00]): example with $q=4$ PCs and $c=2$                                                                                                                                                                                                                                                                                                          | 101 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

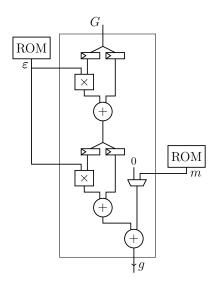

| 3.8  | Structure of the upper part of the arithmetic processing performed by a rower in the flexible HBE $(c=2)$ . The upper part of the rower performs the operation $G \leftarrow G + a \times b + f$ , where $a, b$ and $f$ are of size $w$ bits, and $G$ of size at most $2w+1$ bits                                                                                                                                                                                                      | 102 |

| 3.9  | Structure of the lower part of the arithmetic processing performed by a rower in the flexible HBE $(c=2)$ . The lower part of the rower performs the operation $g \leftarrow G \mod m$ , where $m=2^w-\varepsilon$ (with $\varepsilon < 2^{w/2}$ ), $g$ is of size $w$ bits, and $G$ of size at most $2w+1$ bits                                                                                                                                                                       | 102 |

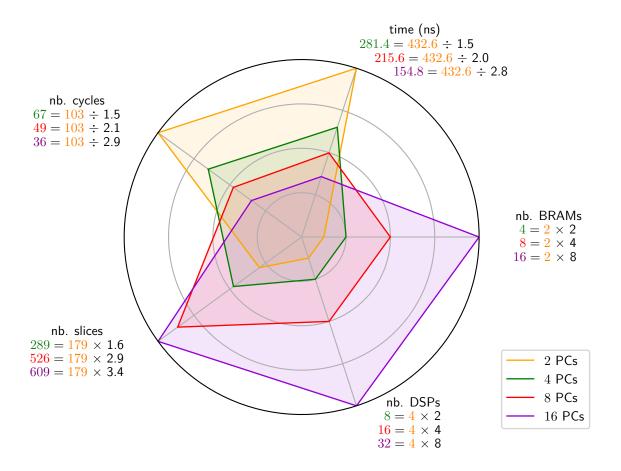

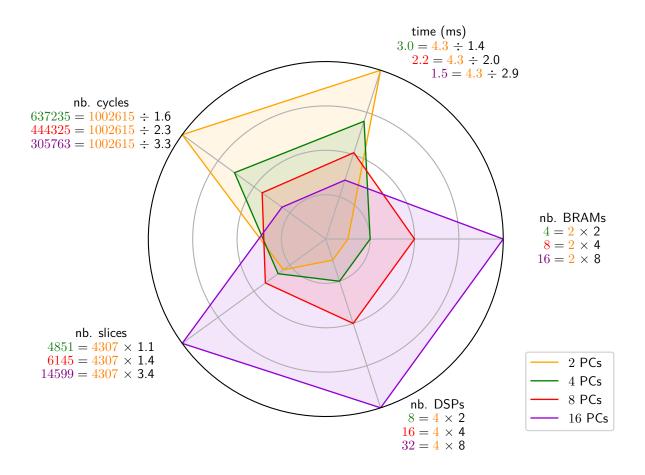

| 3.10 | Comparison of FPGA implementation results of the flexible HBE (adapted from [DBT19]) for $q \in \{2,4,8,16\}$ PCs. Finite fields are of 256-bit elements and the width of the PCs is 17 bits                                                                                                                                                                                                                                                                                           | 104 |

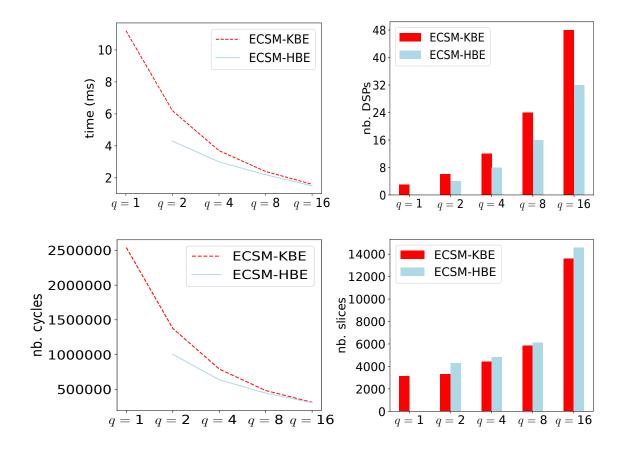

| 3.11 | Comparison of the time, the numbers of cycles, DSPs and slices between the flexible HBE solutions and the flexible KBE ones for various numbers of PCs. HBE is not implemented for one PC                                                                                                                                                                                                                                                                                              | 106 |

| 3.12 | Hierarchical description of RNS computations of the ECSM. The ECSM is computed from a few hundreds point doublings and additions. If Algorithm 15 of the Mongomery ladder [Mon87] is used, each iteration of its loop requires two dozens basic operations and a dozen RNS mod $p$ reductions. Each mod $p$ reduction is made of two BEs and a few basic operations. The cost of the ECSM is mainly driven by that of the mod $p$ reduction, which is itself driven by that of the BEs | 107 |

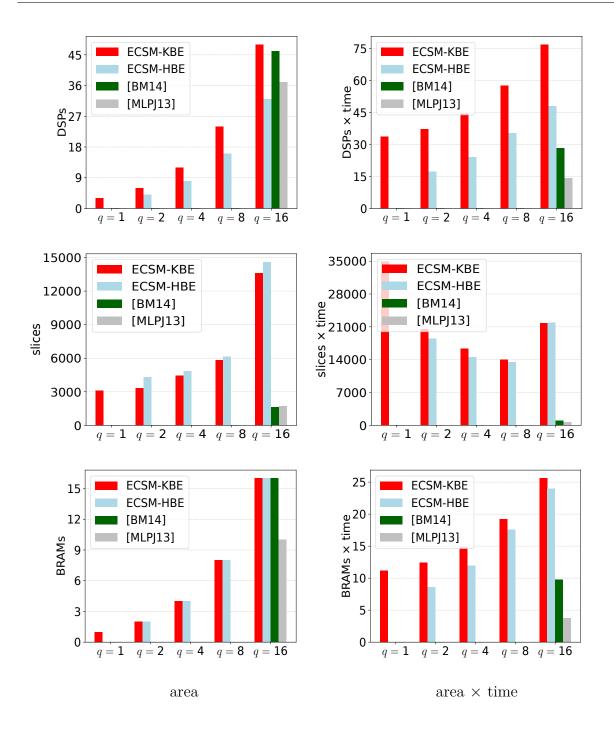

| 3.13 | Comparison of FPGA implementation results of the flexible ECSM-KBE for $q \in \{1, 2, 4, 8, 16\}$ PCs. Finite fields are of 256-bit elements and the PCs 17-bit wide                                                                                                                                                                                                                                                                                                                   | 114 |

| 3.14 | Comparison of FPGA implementation results of the flexible ECSM-HBE for $q \in \{2, 4, 8, 16\}$ PCs. Finite fields are of 256-bit elements and the PCs 17-bit wide                                                                                                                                                                                                                                                                                                                      |     |

| 3.15 | Comparison of the time, the numbers of cycles, DSPs and slices between<br>the flexible ECSM-HBE solutions and the flexible ECSM-KBE ones for<br>various numbers of PCs. ECSM-HBE is not implemented for one PC.                                                                                                                                                                                                                                                                        | 110 |

|      | - various munibers of EUS-EU-S-EU-SIVI-DIDE/IS HOL HIDDEMENLEG FOR ONE PU-                                                                                                                                                                                                                                                                                                                                                                                                             | 110 |

#### LIST OF FIGURES

| 3.16 | Comparison of the area and area $\times$ time trade-offs of our ECSM imple-         |

|------|-------------------------------------------------------------------------------------|

|      | mentations with the one in $[BM14]$ and the best one in $[MLPJ13]$ . ECSM           |

|      | implementations from [BM14, MLPJ13], and generally from the literature,             |

|      | are not flexible                                                                    |

|      |                                                                                     |

| A.1  | Extraits de codes C de notre bibliothèque (haut) et de son utilisation (bas). 136   |

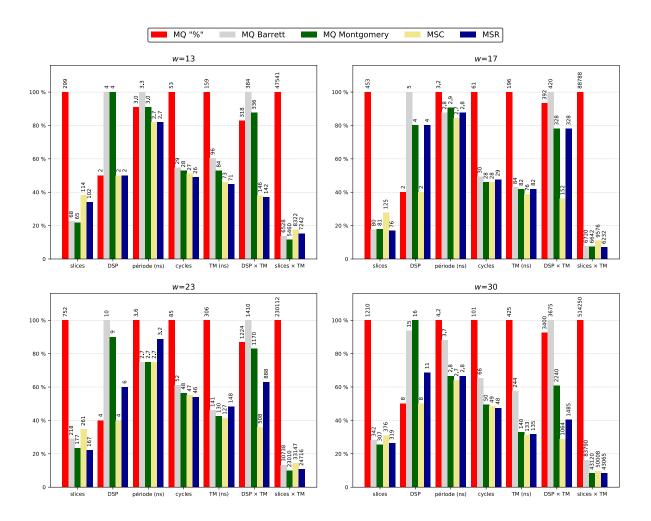

| A.2  | Comparaison des différents algorithmes de réduction pour $w \in \{13, 17, 23, 30\}$ |

|      | bits pour le motif M2 RSF avec $N=20.\ldots 138$                                    |

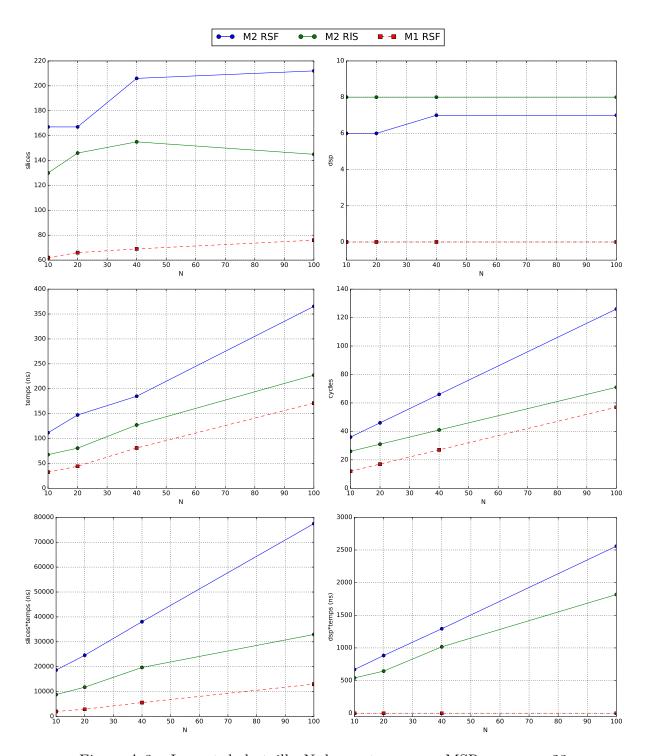

| A.3  |                                                                                     |

## LIST OF TABLES

| 1.1 | Some RNS implementations of asymmetric cryptosystems on FPGA from the literature. The $\operatorname{size}^{(\star)}$ is the operand size (for example the modulus size for RSA or the size of the underlying field of the curve for ECC) 57                                                         |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | FPGA implementation results for $CMR(2w+1,w)$ and EMM operations on a Xilinx XC7Z020 FPGA                                                                                                                                                                                                            |

| 2.2 | HLS implementation results on a XC7Z020 FPGA for HBE $c=2$ (from [DBT19]) and KBE (from [KKSS00]) algorithms for two widths of prime field elements and four RNS channel widths $w.$                                                                                                                 |

| 3.1 | HLS implementation results on a XCZU7EV-FFVC1156 FPGA for the flexible KBE (adapted from [KKSS00]) using $q \in \{1, 2, 4, 8, 16\}$ PCs. Finite fields are of 256-bit elements and the width of the PCs is 17 bits 96                                                                                |

| 3.2 | HLS implementation results on a XCZU7EV-FFVC1156 FPGA for the flexible HBE (adapted from [DBT19]) using $q \in \{2,4,8,16\}$ PCs. Finite fields are of 256-bit elements and the width of the PCs is 17 bits 103                                                                                      |

| 3.3 | Comparison of FPGA implementation results of the flexible HBE (adapted from [DBT19]) with those of the flexible KBE (adapted from [KKSS00]) for various number of PCs. The flexible HBE is not implemented for one PC. Finite fields are of 256-bit elements and the width of the PCs is 17 bits.105 |

| 3.4 | Generalized Montgomery curve formulas to curves in short Weierstraß equation [BJ02, IT02]. The formulas are in projective coordinates. The value $x_Q$ denotes the affine $x$ -coordinate of $Q$ , the input point of Algorithm 15 about the Montgomery ladder                                       |

| 3.5 | Steps to compute point addition and doubling formulas from [BJ02, IT02] reported in Table 3.4                                                                                                                                                                                                        |

| 3.6  | HLS implementation results on a XCZU7EV-FFVC1156 FPGA for the                                                                                                        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | ECSM-KBE using $q \in \{1, 2, 4, 8, 16\}$ PCs. Finite fields are of 256-bit elements and the PCs 17-bit wide                                                         |

| 3.7  | HLS implementation results of the ECSM-KBE according to introduced metrics of area $vs.$ time trade-offs for $q \in \{1, 2, 4, 8, 16\}$ PCs 115                      |

| 3.8  | HLS implementation results on a XCZU7EV-FFVC1156 FPGA for the ECSM-HBE using $q \in \{2,4,8,16\}$ PCs. Finite fields are of 256-bit elements and the PCs 17-bit wide |

| 3.9  | HLS implementation results of the ECSM-HBE according to introduced metrics of area $vs.$ time trade-offs for $q \in \{2,4,8,16\}$ PCs                                |

| 3.10 | Comparison of flexible ECSM-HBE solutions with flexible ECSM-KBE ones for the various numbers of PCs. ECSM-HBE is not implemented for one PC. 118                    |

| 3.11 | Comparison of our FPGA implementation results of the ECSM with the ones from the literature                                                                          |

| A.1  | Impact des directives d'optimisation pour M2 RSF, MSR, $w=23$ et $N=20.139$                                                                                          |

| A.2  | Impact des stratégies de réduction pour $w=23$ et $N=20$                                                                                                             |

## LIST OF ALGORITHMS

| 1   | Diffie-Hellman key-exchange protocol [DH76]                                                                                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | Private- and public-key generation in RSA [RSA78]                                                                                          |

| 3   | Encryption and decryption procedures in RSA [RSA78]                                                                                        |

| 4   | Elliptic curve version of the Diffie-Hellman key-exchange protocol [Mil85] 35                                                              |

| 5   | Double-and-add algorithm (see, for example [HMV04])                                                                                        |

| 6   | Montgomery ladder algorithm [Mon87]                                                                                                        |

| 7   | Montgomery reduction algorithm [Mon85]                                                                                                     |

| 8   | RNS-to-MRS conversion algorithm [Val56, Gar59]                                                                                             |

| 9   | Base extension $BE_{\mathcal{M}\to\mathcal{M}'}(x)$ [KKSS00]                                                                               |

| 10  | RNS Montgomery reduction algorithm [PP95]                                                                                                  |

| 11  | Kawamura base extension $BE_{\mathcal{M}\to\mathcal{M}'}(x)$ adapted from [KKSS00] 65                                                      |

| 12  | Hierarchical base extension $BE_{\mathcal{M}\to\mathcal{M}'}(x)$ [DBT19] 69                                                                |

| 13  | Flexible KBE $BE_{\mathcal{M}\to\mathcal{M}'}(x)$ adapted from [KKSS00]. The function $f(v,i)$ is given by $f(v,i) = \frac{q}{c}(v-1) + i$ |

| 14  | Flexible HBE $BE_{\mathcal{M}\to\mathcal{M}'}(x)$ adapted from [DBT19]. The function $f(v,i)$ is                                           |

| 1 - | given by $f(v,i) = \frac{q}{c}(v-1) + i$                                                                                                   |

| 15  | Montgomery ladder algorithm [Mon87]                                                                                                        |

| 16  | RNS Montgomery reduction algorithm [PP95]                                                                                                  |

| 17  | Flexible basic operation in the RNS base $\mathcal{M}$ . The function $f(v,i)$ is given                                                    |

|     | by $f(v,i) = \frac{q}{c}(v-1) + i$ 110                                                                                                     |

## LIST OF ABBREVIATIONS

ADD elliptic curve point addition

ANSSI Agence nationale de la sécurité des systèmes d'information (France)

**ASIC** application specific integrated circuit

BE base extension

BRAM block RAM

CAD computer-aided design

**CADD** cost of an addition/subtraction

CLB configurable logic blockCMUL cost of a multiplicationCMR cost of a modular reduction

CRT Chinese remainder theorem

DBL elliptic curve point doubling

DCM digital clock manager

**DLP** discrete logarithm problem (in finite fields)

DPA differential power analysis

DSA digital signature algorithm

DSP slice digital signal processing slice

ECC elliptic curve cryptography

ECDH elliptic curve Diffie-Hellman protocol

ECDLP elliptic curve discrete logarithm problem

ECDSA elliptic curve digital signature algorithm

${f ECSM}$  elliptic curve scalar multiplication

EMA elementary modular addition

**EMM** elementary modular multiplication

FF flip-flop

FPGA field programmable gate array

HBE hierarchical base extension

HDL hardware description language

HECC hyperelliptic curve cryptography

#### LIST OF ABBREVIATIONS

**HLS** high-level synthesis

**HPR** modular multiplication algorithm proposed in [BT15, BT16]

HTTPS hypertext transfer protocol secure

I/O input/output

**KBE** Kawamura base extension

LSB least significant bit

LUT look-up table

${f MM}$  modular multiplication

MR modular reductionMRS mixed-radix systemMSB most significant bit

**NIST** National Institute of Standards and Technology (United States)

**OC** number of operation cycles

PC physical channel

RAM random access memoryRNS residue number system

**RSA** Rivest Shamir Adleman (the cryptosystem proposed in [RSA78])

RTL register transfer levelSPA simple power analysisTLS transport layer security

VC virtual channel

VHDL VHSIC hardware description languageVHSIC very high speed integrated circuits

WC number of wait cycles

### INTRODUCTION

#### Context

Hardware accelerators of asymmetric cryptosystems with flexible utilization of resources are proposed in this thesis. Asymmetric cryptography is used in various applications in order to, among others, securily exchange a secret key, digitally sign documents or authenticate for example, to a server. For instance, the transport layer security (TLS) protocol, used notably in the hypertext transfer protocol secure (HTTPS), relies on asymmetric cryptography for the server/client authentication during the TLS handshake. Asymmetric cryptosystems are implemented in many devices used on a daily basis such as smartphones, personal computers, TV sets and smart cards. These devices have various security requirements to protect the sensitive data they handle. The implementations of the cryptosystems have to be secure and efficient to protect the involved data and to avoid poor performance of the devices.

Computations in current asymmetric cryptosystems involve large operands. For example, operands in RSA [RSA78] are integers of more than 2000-bit size, and operands in *elliptic curve cryptography* (ECC) [Mil85, Kob87] are finite field elements of more than 2000-bit size. Therefore, an efficient arithmetic suitable for large operands is needed.

The residue number system (RNS) [Val56, Gar59] is a nonpositional number system wherein large operands are represented by their residues over a set (called base) of small coprime moduli  $m_i$  (a few dozens-bit size). Basic operations such as multiplication, addition and subtraction are independently performed on the small residues. Computations on large operands are then replaced by parallel computations on small operands, leading to faster basic operations. This independence also induces carry-free operations between the moduli [ST67]. These advantages recently motivate uses of RNS in implementations of asymmetric cryptosystems; see, for example [NMSK01, SFM<sup>+</sup>09, Gui10, BM14].

On the drawback side, position-related operations such as modular reductions (MRs), divisions and comparisons are difficult since the representation is nonpositional. Indeed, the order of magnitude of operands is more difficult to evaluate than in a positional representation.

Numerous MRs have to be performed in current asymmetric cryptosystems owing to

the modular operations therein. For instance, the main operation in RSA is the modular exponentiation. For ECC applications, the main operation is the elliptic curve scalar multiplication (ECSM), which itself is computed through numerous operations on finite field elements. To reduce the cost of the RNS MR in [PP95], the base extension (BE) proposed in [KKSS00] is used. The BE becomes an important operation in RNS implementations of asymmetric cryptosystems because the cost of the RNS MR is substantially the cost of the two BEs it comprises.

A channel is the hardware support of basic operations on small residues modulo an element  $m_i$  of the RNS base. In current RNS implementations of asymmetric cryptosystems (see, for example [NMSK01, SFM<sup>+</sup>09, Gui10, BM14]), the number of used channels is the number of moduli needed to represent the large operands. The quantity of hardware resources used in implementations is then related to the size of the large operands involved in the computations of asymmetric cryptosystems. The quantity of needed hardware resources becomes a problem whenever it is greater than the one available on the integrated circuit.

Most integrated circuits are primarily used for noncryptographic applications such as signal processing. After taking into account the hardware resources for the primary applications, the remaining hardware resources can be insufficient to implement the desired asymmetric cryptosystem. In such cases, the circuit designer is forced to choose between lowering the performance of the primary applications and reducing the level of security needed to protect the involved data. However, in many domains such as defense or aerospace industries, this choice is not acceptable.

The lack of hardware resources (on an integrated circuit) to implement a desired asymmetric cryptosystem can also occur over time. The recommended levels of security for asymmetric cryptosystems increase over some time. This increase is usually followed by an increase in the sizes of the large operands involved in computations of asymmetric cryptosystems. For instance, the recommended minimal level of security for ECC applications grows recently from 80 bits to 128 bits, resulting in a growth of the minimal size of finite field elements from 160 bits to 256 bits; see, for example [oST09, ndlsdsd11, oST13]. The increase in the sizes of the operands is translated into an increase in the quantity of hardware resources needed for implementing the desired cryptosystem on the same device.

An integrated circuit (reconfigurable) on which is implemented an asymmetric cryptosystem can lack hardware resources for a new implementation of the same cryptosystem but with larger operands that guarantee a greater level of security. To maintain the per-

formance of other applications and upgrade to a greater level of security, the designer has to acquire a new integrated circuit larger than his/her previous one in use. For most designers, this solution is not desirable owing to its financial cost.

Designing hardware accelerators for asymmetric cryptosystems with resource utilization adaptable to the resources available on an integrated circuit is a solution to the mentioned problem. We refer to such accelerators as *flexible* hardware accelerators. In RNS implementations of asymmetric cryptosystems, such accelerators can be achieved by using *fewer* channels than normally needed to perform computations on the large operands. In this case, we refer to these fewer channels as physical channels (PCs) to differenciate them from the in-number normally needed channels that we name virtual channels (VCs).

The work presented in this thesis primarly targets ECC applications. However, some of the contributions are also adaptable to other asymmetric cryptosystems such as RSA.

To evaluate our propositions and compare our solutions with the state-of-the-art ones whenever the latter are existent, we implemented the propositions on *field programmable gate arrays* (FPGAs) using *high-level synthesis* (HLS) tools. FPGAs are integrated circuits configurable after manufacture. Their reconfigurability and lower costs (in design complexity and time, financial cost per unit <sup>1</sup>) compared with ASICs <sup>2</sup> are reasons that motivate their use for hardware implementations—generally, and particularly in the work presented in this thesis—despite their lower performance (see, for example [ST12]). HLS allows to use a high-level description (for example in C or C++) to automatically describe a register transfer level (RTL) design in a hardware description language (HDL). Compared with HDLs, HLS facilitates fast configurations of FPGAs; more configuration details are handled by the HLS tools.

#### Contributions

We have investigated two aspects of the BE. The choice of BE as our primary subject of investigation is motivated by the fact that the BE is the most important operation in the ECSM when targeting RNS implementations. One investigated aspect of the BE is its speed. A new BE algorithm with a theoretical cost smaller than that of the state-of-the-art

<sup>1.</sup> According to [ST12], the manufacturing cost of FPGAs is paid off by the numerous clients owing to the large quantity in which they are usually produced. For ASICs<sup>2</sup> to become profitable, they must be produced in extremely large quantity because of the important cost in human resources, equipement, design complexity and time they require.

<sup>2.</sup> ASICs stand for application specific integrated circuits.

algorithm will ultimately result in performance improvements of RNS implementations of the ECSM. The other invertigated aspect is the flexibility of the BE and the translation of the latter to the ECSM. In RNS implementations of the ECSM, the BE is not only the most important operation, but also the most complex one. Implementing a flexible BE is therefore essential in implementing an RNS-flexible ECSM.

The first contribution of this thesis is a new BE algorithm [DBT19], named hierarchical base extension (HBE). HBE relies on a hierarchical approach for computing the Chinese remainder theorem (CRT). The approach comprises two phases. In the first phase, the input residues are combined by pairs through computations of partial CRTs in the input RNS base. In the second phase, the remaining of the CRT computation is proceeded on the results of these partial CRTs in the output RNS base. The theoretical cost of the HBE algorithm is smaller than that of the BE algorithm proposed in [KKSS00], named KBE (in this thesis) and largely regarded as the state-of-the-art BE. This cost reduction translates to a cost reduction of the RNS MR operation using HBE compared with the one using KBE. To exploit the inherent parallelism of RNS well preserved in the coxrower architecture proposed in [KKSS00], the latter is adapted to support HBE. HLS implementations on FPGA of the two algorithms for various finite field sizes and channel widths show that HBE solutions are always faster and in nearly all cases smaller than KBE ones. The area vs. time trade-off is always in favor of HBE. As a consequence, similar performance improvements are expected in ECSM implementations using HBE compared with the ones using KBE; this expectation is verified in the next contribution.

[DBT19] L. Djath, K. Bigou and A. Tisserand. Hierarchical approach in RNS base extension for asymmetric cryptography. In 26th IEEE Symposium on Computer Arithmetic (ARITH), pages 46–53. IEEE, 2019.

DOI: 10.1109/ARITH.2019.00016

Also available from https://hal.archives-ouvertes.fr/hal-02096353

The second contribution of this thesis is two RNS-flexible hardware accelerators for the ECSM on FPGA. The BE operation, either HBE [DBT19] or KBE [KKSS00], is demonstrated to be *flexible*. In other words, for a given size of finite field, each of the two BEs can be implemented using a flexible quantity of hardware resources. An architecture is derived for each of the flexible HBE and KBE. The number of PCs in each architecture is flexible. The two BEs are implemented on FPGA with HLS for various numbers of PCs ranging between the divisors of the number of VCs. Implementation solutions show

that when the number of used PCs increases from q to kq with k > 1, the solution time decreases with a factor less than k, regardless of the BE. This observation results from the constancy of the number of wait cycles between pipelined loops independently of the number of used PCs. The solutions with the best area vs. time trade-offs are obtained with implementations using a few PCs. HBE solutions remain faster with better area vs. time trade-offs than KBE ones.

The new flexible architectures are then used to implement two flexible ECSMs, one using HBE [DBT19] and the other KBE [KKSS00]. These flexible ECSM implementations use adaptable quantities of hardware resources. The used quantities of hardware resources depend on the number of PCs chosen (at design time) for the RNS implementation of the ECSMs. Similarly to the flexible BEs, our flexible ECSM solution time decreases with a factor less than k when the number of used PCs increases from q to kq, regardless of the BE in use. Again, implementations using a few PCs present the best solutions in area vs. time trade-offs. Also, the ECSM solutions using HBE are faster and present better area vs. time trade-offs than the ones using KBE. Last, though comparable in area vs. time trade-offs with the best implementation results from the literature, most of our flexible ECSM solutions are much smaller. Therefore, our flexible ECSM solutions can be implemented on integrated circuits with limited hardware resources. The proposed RNS-flexible architectures can also be used to implement multi-level security hardware accelerators. We plan to submit this contribution in the near future.

The last contribution of this thesis is an auxiliary project started in the early months of the PhD. We studied how to efficiently perform modular multiplications and accumulations (typical operations in RNS implementations of asymmetric cryptosystems) on FPGA using HLS tools. HLS favors fast explorations of different parameters for various implementation constraints (for example, loop unrolling). Parameters considered in our study include the size and the shape (arbitrary, specific) of the moduli as well as the type of series (with and without intermediate MR) for the modular operations. The report of this study, presented in [DZBT19] in French, is put in Appendix A.

[DZBT19] L. Djath, T. Zijlstra, K. Bigou and A. Tisserand. Comparaison d'algorithmes de réduction modulaire en HLS sur FPGA. In *Conférence d'informatique en Parallélisme*, *Architecture et Système* - Compas'19, 2019.

Also available from https://hal.archives-ouvertes.fr/hal-02129095

#### Outline

This thesis comprises three chapters. In the first chapter, we detail the context of this thesis, namely ECC. The ECSM and computations involved in its computation are also introduced. Besides ECC in the first chapter, we present the RNS and its inherent properties as well as a survey of BEs and RNS MRs. The first and the second contributions of this thesis are respectively presented in the second and the third chapters.

## STATE OF THE ART

### 1.1 Asymmetric Cryptography

#### 1.1.1 Overview of Asymmetric Cryptography

Asymmetric cryptography is based on the idea of publicizing a key. In asymmetric cryptography, each individual possesses two keys: a private key, and a public key usually computed from the private one. The private key is known only by its owner while the public key is revealed.

The safety of revealing the public key without giving information about the private key is associated with the hardness of inverting one-way functions. A function  $f: x \mapsto f(x)$  is one way if computing f(x) from x is easy while computing x from f(x) is hard. Easy means computing f(x) from f(x) in polynomial time for all attempting probabilistic algorithms is extremely unlikely. However, proving the hardness of inverting functions is difficult in itself. In practice, functions largely regarded as computationally difficult to invert are used. A practical way to view the hardness: If computing f(x) takes considerable amount of time (say, hundreds of years) with the best known algorithms and a huge computation power, then the function f is largely regarded as hard to invert.

In asymmetric cryptography, the hardness should only exists for an eavesdropper. An authorized individual should be able to efficiently compute x from f(x). This ability is usually provided by a trap door that the authorized individual possesses. For instance, the private key of the authorized individual is used as the trap door in an asymmetric cryptosystem.

Applications of asymmetric cryptography include key exchange [DH76] and digital signature [RSA78, Elg85]. Applications of asymmetric cryptography are used in many practical contexts such as in establishing secure communications with an e-commerce website or in authenticating to a server.

Diffie-Hellman key-exchange protocol and the RSA cryptosystem, two notable advancements in asymmetric cryptography, are presented in the following subsections. Elliptic curve cryptography (ECC) is then described.

#### Diffie-Hellman Key-Exchange Protocol [DH76]

The safety of the Diffie-Hellman key-exchange protocol [DH76] is based on the assumption that the discrete logarithm problem (DLP) in finite field is computationally difficult for well chosen parameters. The parameters to consider include, among others the size of the field, and tailored properties against known attacks such as the Pohlig-Hellman attack [PH78]. Current recommended sizes are a few thousands bits (say, 2048 or 3072 bits); see for example [oST13].

Let p be a prime, g be a primitive element of the finite field  $\mathbb{F}_p$ . The DLP can be stated: Knowing  $n = q^x \mod p$ , find x. The function

$$f: x \mapsto n = q^x \bmod p$$

can be viewed as a one-way function associated with the DLP.

Two individuals, Alice and Bob, want to share a common key over a network. The Diffie-Hellman key-exchange protocol [DH76] is described in Algorithm 1. At the end of the exchange Alice and Bob have a common secret key  $K_{AB} = K_{BA}$  since  $n_B^{x_A} \mod p = n_A^{x_B} \mod p = g^{x_A x_B} \mod p$ . An eavesdropper has to solve the DLP if he/she intends to recover the secret operands  $x_A$  or  $x_B$  from  $n_A$  or  $n_B$ . Besides, computing the shared key  $K_{AB}$  from  $n_A$  or  $n_B$  without knowledge of respectively  $x_B$  or  $x_A$  involves solving the DLP.

#### **Algorithm 1:** Diffie-Hellman key-exchange protocol [DH76].

**Input:** p a prime, and g a primitive element of  $\mathbb{F}_p$

**Output:** Alice and Bob have a common key  $K_{AB} = K_{BA} = g^{x_A x_B} \mod p$

- 1 Alice chooses a random number  $x_A \in \mathbb{F}_p$  and keeps it secret

- **2** Alice computes  $n_A = g^{x_A} \mod p$  and sends it to Bob

- **3** Bob chooses a random number  $x_B \in \mathbb{F}_p$  and keeps it secret

- 4 Bob computes  $n_B = g^{x_B} \mod p$  and sends it to Alice

- **5** Alice receives  $n_B$  and computes  $K_{AB} = n_B^{x_A} \mod p$

- 6 Bob receives  $n_A$  and computes  $K_{BA} = n_A^{x_B} \mod p$

#### RSA Cryptosystem [RSA78]

The RSA cryptosystem [RSA78] was the first published work allowing two individuals to exchange a message over a network using a pair of keys (private and public). In RSA, the safety of keeping secret the private key in spite of revealing the public key relies on the considered difficulty of factoring large integers.

The problem of the factorization can be put: Knowing an integer n, factorize n. The function

$$f:(p,q)\mapsto n=p\times q$$

can be viewed as a one-way function associated with the problem of the factorization. Computing n is straightforward (through a multiplication algorithm) but computing p and q from n requires considerably more effort. In practice, an attacker has to factorize a number n of a few thousands bits. For example, the recommended sizes for the RSA modulus n in [oST13] are 1024, 2048 and 3072 bits.

Alice wants to generate her private key (d, n) and her public key (e, n). The simplified procedure is presented in Algorithm 2. For an eavesdropper, computing the decryption key d from the encryption key e requires to factor e.

Bob wants to send a message (also called plaintext) m,  $0 \le m \le n-1$  to Alice. Bob gets the public key (e, n) of Alice. The encryption and decryption procedures are described in Algorithm 3.

At the end, Alice gets m since  $c^d \mod n = (m^e)^d \mod n = m$ . An eavesdropper who gets the ciphertext c has to solve the following problem: Find the eth root of  $c \mod n$ . This problem is also considered to be computationally difficult. By assumption, the eavesdropper does not possess the decryption key d of Alice. Strictly speaking, an eavesdropper able to solve one of the factorization problem and the eth root mod n problem can recover the plaintext m.

#### **Algorithm 2:** Private- and public-key generation in RSA [RSA78].

**Output:** private key (d, n) and public key (e, n)

- 1 Alice chooses two random large primes p and q and computes n = pq

- 2 Alice chooses a random large integer d coprime with (p-1)(q-1)

- **3** Alice computes e, the inverse of  $d \mod (p-1)(q-1)$

- 4 Alice keeps (d, n) secret and publicizes (e, n)

#### **Algorithm 3:** Encryption and decryption procedures in RSA [RSA78].

**Input:** Bob gets the public key (e, n) of Alice with the intention of sending her a plaintext m

Output: Alice recovers m

1 Encryption

**2** Bob computes  $c = m^e \mod n$  and sends c to Alice

3 Decryption

4 Alice receives c and computes  $c^d \mod n = m$

#### 1.1.2 Elliptic Curve Cryptography

#### Elliptic Curves

Part "Elliptic Curves" of the current subsection is a synthesis of basic concepts on elliptic curves from [Hus04, CF06, Sil09] useful in the work presented in this thesis.

An elliptic curve is a nonsingular cubic curve along with a stated base point. In this thesis the following simplified definition is considered, though restrictive on the characteristic of the underlying field of the curve.

**Definition 1** (Elliptic Curve). Let K be a field of characteristic  $\neq 2, 3$ . An *elliptic* curve  $E_K$  defined over K is the set of elements  $(x, y) \in K^2$  satisfying the equation

$$E_K: \quad y^2 = x^3 + ax + b \tag{1.1}$$

where  $a, b \in K$  are such that  $-16(4a^3 + 27b^2) \neq 0$ .

The quantity  $\Delta = -16(4a^3 + 27b^2)$  is the discriminant of Equation 1.1 and  $\Delta \neq 0$  conveys the nonsingularity of the curve  $E_K$ .

The elements of the elliptic curve  $E_K$  are called points. Figure 1.1 depicts the points of an elliptic curve defined over the finite fields  $\mathbb{F}_{1021}$  and  $\mathbb{F}_{16381}$ .

Equation 1.1 is the short Weierstraß equation of an elliptic curve. The generalized Weierstraß equation of an elliptic curve defined over a field of arbitrary characteristic can be found in [Hus04, CF06, Sil09], and is presented in Appendix B.

Two points Q and Q' of an elliptic curve  $E_K$  can be added by drawing a line (QQ') through them and taking the symmetric (in relation to the x-axis) of the third point of intersection between the line (QQ') and the curve  $E_K$ . The point addition of Q and Q' is denoted Q+Q'. The addition of Q and Q is referred to as point doubling and denoted [2]Q. The construction of the point [2]Q is similar to that of the point Q+Q', the tangent at Q

Figure 1.1 – Example of an elliptic curve defined over two finite fields.

to the curve replacing the line (QQ'). Constructions of point addition and doubling are illustrated on the curve  $E_{\mathbb{R}}: y^2 = x^3 - 3x + 3$  in Figure 1.2.

Point addition Q+Q' and point doubling [2] Q are also obtained through formulas

$$\begin{cases} x_{Q+Q'} = \lambda^2 - x_Q - x_{Q'} \\ y_{Q+Q'} = \lambda(x_Q - x_{Q+Q'}) - y_Q \end{cases}$$

and

$$\begin{cases} x_{[2]Q} = \mu^2 - 2x_Q \\ y_{[2]Q} = \mu(x_Q - x_{[2]Q}) - y_Q \end{cases}$$

(1.2)

where

$$\lambda = \frac{y_Q - y_{Q'}}{x_Q - x_{Q'}}$$

and  $\mu = \frac{3x_Q^2 + a}{2y_Q}$ .

Formulas in Equation 1.2 include divisions (for the introduced values  $^1$   $\lambda$  and  $\mu$ ). In general, divisions are difficult to perform. A solution to avoid computing the inherent divisions of Equation 1.2 is to homogenize the equation of the curve  $E_K$ , that is, to express it in projectives coordinates. By substituting x = X/Z and y = Y/Z into Equation 1.1 we obtain

$$E_K: Y^2 Z = X^3 + aXZ^2 + bZ^3.$$

(1.3)

Using projective coordinates to express the formulas in Equation 1.2 yields

$$\begin{cases} X_{Q+Q'} = BC \\ Y_{Q+Q'} = A(X_Q Z_{Q'} B^2 - C) - Y_Q Z_{Q'} B^3 \\ Z_{Q+Q'} = Z_Q Z_{Q'} B^3 \end{cases} \text{ and } \begin{cases} X_{[2]Q} = 2FH \\ Y_{[2]Q} = E(4G - H) - 8Y_Q^2 F^2 \\ Z_{[2]Q} = 8F^3 \end{cases}$$

(1.4)

<sup>1.</sup> The values  $\lambda$  and  $\mu$  are the slopes of the line (QQ') and the tangent at Q to the curve  $E_K$  respectively.

Figure 1.2 – Geometric description of point addition and point doubling.

where

$$A = Y_{Q'}Z_Q - Y_QZ_{Q'}$$

,  $B = X_{Q'}Z_Q - X_QZ_{Q'}$ ,  $C = Z_QZ_{Q'}A^2 - (X_{Q'}Z_Q + X_QZ_{Q'})B^2$ ;  $E = 3X_Q^2 + aZ_Q^2$ ,  $F = Y_QZ_Q$ ,  $G = X_QY_Q^2Z_Q$ ,  $H = E^2 - 8G$ .

Besides projective coordinates, there exist other systems of coordinates wherein the computation of the inherent divisions of Equation 1.2 can be avoided. The reader is referred to [CF06] for a presentation of some of these systems of coordinates and the formulas of point addition and doubling within them.

The point  $\mathcal{O} = (0:1:0)$  is the base point (also called point at infinity) expressed in projective coordinates.

**Lemma 1** (Group Law on Elliptic Curve). Let  $E_K$  be an elliptic curve defined over a field K. The points of  $E_K$  provided with the operation + is a group of neutral element the point  $\mathcal{O}$ .

A proof of Lemma 1 can be found in [Sil09].

**Definition 2** (Elliptic Curve Scalar Multiplication). Let  $E_K$  be an elliptic curve

defined over a field K. The elliptic curve scalar multiplication (ECSM) is the function

$$f: (\mathbb{Z}_+ \setminus \{0\}) \times E_K \to E_K$$

$(u, Q) \mapsto [u]Q = \underbrace{Q + Q + \dots + Q}_{u \text{ terms}}.$

Definition 2 of the ECSM is generalized to all  $u \in \mathbb{Z}$  by writing

$$[u]Q = \begin{cases} \mathcal{O} & \text{if } u = 0\\ Q + Q + \dots + Q & \text{if } u > 0\\ (-Q) + (-Q) + \dots + (-Q) & \text{otherwise,} \end{cases}$$

where the point -Q is the symmetric of the point Q in relation to the x-axis.

In the following, ECC is presented through the lens of the elliptic curve discrete logarithm problem (ECDLP).

#### Elliptic Curve Discrete Logarithm Problem

Let  $E_{\mathbb{F}_q}$  be an elliptic curve defined over a finite field  $\mathbb{F}_q$ , and Q a point of  $E_{\mathbb{F}_q}$  of order v. The ECDLP is stated: Knowing the point [u]Q of the curve  $E_{\mathbb{F}_q}$  (and the point Q), find the unique scalar u,  $0 \le u \le v - 1$  by which the point Q is multiplied. The function

$$f_Q: u \mapsto [u]Q$$

can be viewed as a one-way function associated with the ECDLP. Computing [u]Q from u is easily performed using one of the various state-of-the-art algorithms (for example double and add in [HMV04]) while computing u from [u]Q is difficult for well-chosen parameters. The involved parameters are the underlying finite field of the curve and the curve itself.

When choosing the underlying finite field  $\mathbb{F}_q$  of the curve  $E_{\mathbb{F}_q}$  the aim is to have a field on which the arithmetic is efficient while the curve still ensures a good level of security (meaning the ECDLP should be hard to solve). Several types of fields (prime fields, fields of prime characteristic, binary fields, etc.) have been studied and some fields have been standardized; see, for example the ones in [ndlsdsd11] (from ANSSI<sup>2</sup>) and in [oST13]

<sup>2.</sup> ANSSI stands for Agence nationale de la sécurité des systèmes d'information (France).

(from NIST<sup>3</sup>). The reader should bear in mind that regardless of the type of fields from which is selected the underlying finite field  $\mathbb{F}_q$ , the cardinality q of  $\mathbb{F}_q$  should never be small. The theorem of Hasse says that the cardinality  $\sharp E_{\mathbb{F}_q}$  of the curve is bounded as follows:

$$q + 1 - 2\sqrt{q} \le \sharp E_{\mathbb{F}_q} \le q + 1 + 2\sqrt{q}.$$

(1.5)

If q is small, then  $\sharp E_{\mathbb{F}_q}$  is small. The consequence is that the ECDLP on such a curve  $E_{\mathbb{F}_q}$  can be solved through exhaustive search attack.

Choosing the curve is tricky and two types of attacks on the ECDLP have to be considered when doing so. The first type consists of attacks on arbitrary curves such as the Pohlig-Hellman attack [PH78] and the Pollard Rho method [Pol78]. The Pohlig-Hellman attack is performed by computing u modulo each prime factor (raised to its maximum power within the prime decomposition) of  $\sharp E_{\mathbb{F}_q}$  and recovering u through the Chinese remainder theorem (CRT). The u-modulo-prime-factor step becomes easy if the mentioned prime factors are small. Choosing the curve such that v, the order of the point Q and hence a factor of  $\sharp E_{\mathbb{F}_q}$ , be a large prime prevents this attack. The Pollard rho method can be viewed as a randomized equivalent of the baby-step giant-step method. Despite its effectiveness, the Pollard Rho method still runs in exponential time.

The second type of attacks is about attacks on specific curves. Examples of these attacks are the Menezes-Okamoto-Vanstone attack [MOV93] and the Frey-Rück attack [FR94] which exploit the fact that, under some circumstances, the ECDLP can be reduced to the DLP in some extension field  $\mathbb{F}_{q^l}$  (of the underlying field  $\mathbb{F}_q$  of the curve). The DLP in the extension field can be solved if l is small. Examples of curves subject to these attacks are supersingular curves and curves  $E_{\mathbb{F}_q}$  of cardinality q-1. These attacks are prevented by choosing the curves such that v is not a factor of  $q^l-1$  for all small l. Menezes [Men01] suggested that, when  $v>2^{160}$ , checking this condition for  $1 \le l \le 20$  is enough. Another example of attacks on specific curve is the attack on curves  $E_{\mathbb{F}_p}$  of cardinality p for which authors of [Sem98] and [SA98] prove that the ECDLP can be solved in polynomial time. This attack is prevented by ensuring the cardinality of the curve is not p when choosing the curve.

The idea of ECC, proposed in [Mil85, Kob87], is to use asymmetric cryptographic applications based on the ECDLP. The preference of the ECDLP to the DLP (in finite field) is motivated by the fact that there is no known algorithm solving the ECDLP for general cases in sub-exponential time, contrary to the DLP in finite field (for example,

<sup>3.</sup> NIST stands for National Institute of Standards and Technology (United States).

the index calculus). An inherent consequence is that the cryptographic operands in ECC are smaller than the ones in asymmetric cryptographic applications based on the DLP for the same level of security. For example, the elliptic curve digital signature algorithm (ECDSA<sup>4</sup>) with public-key size of 256 bits is considered providing roughly the same level of security (approximately 128 bits of security) as the digital signature algorithm (DSA<sup>5</sup>) with public-key size of at least 2048 bits; see [oST13] for recommendations on parameter sizes for signature algorithms based on the DLP and the ECDLP.

Protocols of asymmetric cryptographic applications (key exchange, digital signature, public-key encryption) based on the DLP are adaptable to elliptic curves. As an example, Algorithm 4 describes the elliptic curve version (ECDH) [Mil85] of the Diffie-Hellman key-exchange protocol presented in Subsection 1.1.1. An eavesdropper who gets  $[u_A]Q$  or  $[u_B]Q$  has to solve the ECDLP to recover the (secret) scalars  $u_A$  or  $u_B$ . Moreover, solving the ECDLP is a crucial part of forging the agreed key  $[u_Au_B]Q$  from  $[u_A]Q$  or  $[u_B]Q$  without knowledge of  $u_A$  or  $u_B$ .

**Algorithm 4:** Elliptic curve version of the Diffie-Hellman key-exchange protocol [Mil85].

**Input:**  $E_{\mathbb{F}_q}$  is an elliptic curve defined over  $\mathbb{F}_q$ , and Q a point of  $E_{\mathbb{F}_q}$  of order v

Output: Alice and Bob have a common key

$$[u_A u_B]Q = [u_A]([u_B]Q) = [u_B]([u_A]Q) = [u_B u_A]Q$$

- 1 Alice chooses a random number  $u_A$ ,  $0 \le u_A \le v 1$  and keeps it secret

- 2 Alice computes  $[u_A]Q$  and sends it to Bob

- **3** Bob chooses a random number  $u_B$ ,  $0 \le u_B \le v 1$  and keeps it secret

- 4 Bob computes  $[u_B]Q$  and sends it to Alice

- **5** Alice receives  $[u_B]Q$  and computes  $[u_A]([u_B]Q) = [u_Au_B]Q$

- 6 Bob receives  $[u_A]Q$  and computes  $[u_B]([u_A]Q) = [u_Bu_A]Q$

In the remaining of this thesis we assume the curve is defined over a prime field  $\mathbb{F}_p$ . Our assumption is motivated by the fact that in practice, curves over prime fields have proven to be more resistant (to attacks) than curves defined over other fields. Among others, curves defined over binary fields have been subject to attacks; see, for example [GHS02b, GHS02a, Hes03, MTW04].

<sup>4.</sup> The ECDSA is based on the ECDLP.

<sup>5.</sup> The DSA is based on the DLP.

#### Computations Involved in an ECSM

The ECSM results from several point doublings and additions (operations in  $E_{\mathbb{F}_q}$ ), which in turn are obtained through operations in the finite field  $\mathbb{F}_p$ . This hierarchical description is presented in Figure 1.3.

Figure 1.3 – Hierarchical description of computations involved in an ECSM.

There exist several algorithms in the literature to compute the ECSM. The elementary double-and-add algorithm (see, for example [HMV04, p. 97]) is presented in Algorithm 5. The double-and-add algorithm is an elliptic curve adaptation of the square-and-multiply algorithm for exponentiation (for example  $x^5 = ((1^2 \times x)^2)^2 \times x$ ). Other algorithms for exponentiation such as the sliding window method have also been adapted to elliptic curves. The reader is referred to [HMV04] for some of these algorithms.

Algorithm 6 presents the *Montgomery ladder* [Mon87] which was initially proposed for curves of equations of the form  $by^2 = x^3 + ax^2 + x$ . Thanks to [BJ02, IT02], the use of this algorithm has been extended to curves of equation in short Weierstraß form. The use of Algorithm 6 presents two major advantages. First, the Y-coordinate (in projective

```

Algorithm 5: Double-and-add algorithm (see, for example [HMV04]).

Input: Q a point of the elliptic curve E_{\mathbb{F}_p}

u an integer written in binary representation as u_{s-1}u_{s-2}...u_0

Output: R = [u]Q

1 R \leftarrow \mathcal{O}

2 for i \leftarrow s - 1 to 0 do

3 R \leftarrow [2]R

4 if u_i = 1 then

5 R \leftarrow R + Q

```

**Algorithm 6:** Montgomery ladder algorithm [Mon87].

```

Input: Q a point of the elliptic curve E_{\mathbb{F}_p}

u an integer written in binary representation as u_{s-1}u_{s-2}...u_0

Output: Q_1 = [u]Q

1 Q_1 \leftarrow \mathcal{O}; Q_2 \leftarrow Q

2 for i \leftarrow s-1 to 0 do

3 | if u_i = 0 then

4 | Q_1 \leftarrow [2]Q_1; Q_2 \leftarrow Q_1 + Q_2

5 | else

6 | Q_2 \leftarrow [2]Q_2; Q_1 \leftarrow Q_1 + Q_2

```

system of coordinates) does not need to be computed during the ECSM. Therefore, the cost of the algorithm is reduced. Note that the Y-coordinate can be recovered at the end of the algorithm if necessary. Second, regardless of the bit of the scalar u, a point doubling and a point addition are performed. In other words, the number, the type and the order of operations are the same regardless of the value of the bit of u. This constancy of the number, the type and the order of operations per bit of u constitutes an advantage in terms of protection against some side-channel attacks such as simple power analysis (SPA).

Point doublings and additions are computed through formulas elaborated depending on the parameters of the curve (underlying field, curve equation) and the system of coordinates in use. The reader is referred to [CF06] for some of these formulas. Regardless of the chosen formulas, they involve operations in  $\mathbb{F}_p$ . Therefore, using an efficient arithmetic in  $\mathbb{F}_p$  is crucial in computing the ECSM.

In the work presented in this thesis, we choose to use the residue number system (RNS) to perform operations in  $\mathbb{F}_p$  because RNS provides several efficiency advantages described in Subsection 1.3.2. The hierarchical description of ECSM computations in Figure 1.3 is extended by adding an extra layer at its basis; see Figure 1.4. The contributions of this thesis reside in this extra layer about computations in  $\mathbb{F}_p$  using RNS.

The existence of operations in  $\mathbb{F}_p$  implies a need for efficient modular reductions (MRs). Some MR algorithms from the literature are presented before delving into RNS.

Figure 1.4 – Hierarchical description of computations involved in an ECSM with RNS as chosen number system.

## 1.2 Modular Reduction

Computations of point doublings and additions, useful in ECSM computations involve numerous MRs since operands are in finite fields. For example, over a finite field  $\mathbb{F}_p$  of 256-bit elements, one ECSM requires a few thousands mod p reductions. Therefore, it is crucial to ensure MRs are efficient. In this section some MR algorithms from the literature are presented.

## 1.2.1 Montgomery Reduction

Montgomery [Mon85] introduces a MR algorithm that avoids computing the costly naive division. The idea is to use an auxiliary number r by which the MR and the division are straightforward. For example, in binary representation, mod  $2^l$  reduction and (integer) division by  $2^l$  are respectively performed by selecting the l least significant bits (LSBs) and by taking all the bits except these l LSBs of the considered numbers. The MR idea is described in Algorithm 7. Note that the output of the algorithm on input x is  $xr^{-1} \mod p$  and not  $x \mod p$ .

Besides its efficiency, Algorithm 7 is consistent with multiplications and additions/subtractions. Indeed,

$$xr^{-1} \times x'r^{-1} = (xx'r^{-1})r^{-1} \mod p$$

and  $xr^{-1} + x'r^{-1} = (x + x')r^{-1} \mod p$ .

In other words, there is a correspondence between the product and the sum/difference of operands in the input space on one hand, and the product and the sum/difference of operands in the output space on the other hand. Owing to this correspondence in

**Algorithm 7:** Montgomery reduction algorithm [Mon85].

```

Input: x such that x < pr

Precomp.: p, r coprime with p such that r > p and r^{-1} < p

p' \text{ such that } p' < r \text{ and } rr^{-1} - pp' = 1

Output: y = xr^{-1} \mod p < 2p

1 \quad z \leftarrow (x \mod r)p' \mod r

2 \quad t \leftarrow x + zp

3 \quad y \leftarrow t/r

```