# Continuous-Time Bandpass (BP) sigma delta modulator (SDM)

Zoltan Nemes

#### ▶ To cite this version:

Zoltan Nemes. Continuous-Time Bandpass (BP) sigma delta modulator (SDM). Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2021. English. NNT: 2021GRALT041. tel-03411459

## HAL Id: tel-03411459 https://theses.hal.science/tel-03411459

Submitted on 2 Nov 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE GRENOBLE ALPES

Spécialité : Nano Electronique et Nano Technologies

Arrêté ministériel: 25 mai 2016

Présentée par

#### **Zoltan NEMES**

Thèse dirigée par

Dominique MORCHE, Professeur, CEA,

et codirigée par

Maurits ORTMANNS, Professeur, Université de Ulm, et

Stéphane LE TUAL, Ingénieur, STMicroelectronics

préparée au sein du CEA LETI au Laboratoire d'Architectures Intégrées Radiofréquence (LAIR) et STMicroelectronics et à l'Institut de Microélectronique de l'Université de Ulm dans l'École Doctorale électronique, électrotechnique, automatique, traitement du signal (EEATS)

# Conception d'un récepteur à formation de faisceaux numérique pour petites cellules millimétriques 5G

Thèse soutenue publiquement le **30 juin 2021**, devant le jury composé de :

#### Pr. Salvador MIR

Directeur de recherche laboratoire TIMA, Président

#### Pr. Hassan ABOUSHADY

Professeur associé à Sorbonne Université, Rapporteur

#### Pr. Boris MURMANN

Professeur à l'Université de Stanford, Rapporteur

#### Pr. Sven MATTISSON

Professeur assistant à l'Université de Lund, Membre

#### M. Cédric DEHOS

Ingénieur de recherche au CEA LETI, Invité

## Acknowledgment

During any PhD, one goes through many hardships, and when comes the time to acknowledge the ones who allowed him to over pass these hardships, comes the fear to forget someone. I am no exception to this statement. Thankfully, I know that the people who kindly helped me will not feel offended if by mistake I do not mention them.

First, I would like to thank Stéphane Le Tual, my supervisor and college at ST. When I decided to undertake the challenge of a PhD, I asked him right away if he wanted to be part of the project. Thankfully he accepted, allowing me to wright these lines today. I must Also thank Olivier Rossetto for accepting me in the master program and then following me through to the end. It is during this master's degree that I met Dominique Morche who would become my director. He made me redo many, if not all, of my presentations multiple times, until it was deemed good enough. Thank you for believing in me when didn't myself, it was worse it. I was lucky to have as co-director Maurits Ortmanns, his mind speed and sharpness pushed me further than I could imagined. Thank you for your benevolent pressure.

I want to thank Sven Mattisson both for the exchanges we add early in my PhD and for being a member of my jury. Similarly, I want to thank Cedric Dehos for all the system discussions, for being a member of my CSI and finally for being part of the jury as well. I also thank Hassan Aboushady for his interest in my work during the CSI meetings and for being reporter jury member. I want to thank Boris Murmann for getting up that early on the defense day, and of course for being a reporter member of the jury. I also thank Mir Salvador for presiding the jury.

I want to thank Pierre-Olivier Jouffre for supporting this project all along as well as Yves Desserez for his precious help on the layout. I thank Michael Pelissier for our discussion on compress sensing and Alexandre Giry for teaching me the basics on power amplifiers.

I need to thank all my fellow PhD student at CEA/LETI and ST, for the technical discussions and all the rest.

I thank my family, in particular my mother my sister and my brother for supporting me until the end.

Last, I am proud to thank Aline for being the spark of this adventure and for joining me until its end.

#### **Abstract:**

The fifth-generation mobile network, or 5G, will become a standard for nearly all forms of wireless communication. In that purpose, it will use a larger part of the spectrum. The sub-6GHz 5G is currently being deployed. The millimeter wave spectrum exploitation will start in the coming years. This part of the spectrum is envisioned to provide enhanced Mobile Broad Band (eMBB) over small areas. These access points with limited coverage are called small-cells and are the focus of this manuscript. More specifically, the challenges of base station receivers for these small cells in the 28GHz band will be studied. This work is divided into three parts. First, the system is analyzed to establish the receiver requirements. Second, these requirements are used to propose an innovative receiver's architecture. Finally, an implementation of the proposed architecture is described and evaluated.

The system analysis starts from 5G's Key Performance Indicators (KPI). A system architecture in line with these KPI is established and becomes the basis to evaluate the receiver's requirements in a multiple operator scenario. One specific trait of the receiver is its beamforming ability using a large antenna array. While this approach has the potential to deliver the desired performances, it also increases the receiver's complexity. The system has many parameters (number of antennas, array topology, ...), leading to many possible configurations. Finding the optimal configuration is very challenging. To alleviate this problem, as many parameters as possible were fixed, based on practical considerations. This significantly reduces the size of the problem and simplifies the analysis.

Beamforming consists in combining the signals from multiple antennas, to receive only the radio waves from a given direction, forming a beam in that direction. Prior to recombination, the signals must be delayed and weighted. The domain where these operations are performed defines the receiver architecture. When in the analog domain, it is analog beamforming. When in the digital domain, it is Digital Beamforming (DBF) and when in both domains, it is hybrid beamforming. DBF offers the best performances but has the most challenging RF front end implementation, requiring a full receiver per antenna. The proposed analysis shows that the performances required for these individual receivers are significantly relaxed, the challenge laying more on the digital side, due to the large amount of data to process in a short time.

Hence, receivers benefiting from relaxed requirements, while reducing the digital processing were investigated. Using band pass Sigma-Delta Modulators (SDM) for analog to digital conversion can reduce the digital processing, thanks to its oversampling and low-resolution output. The former provides a nearly free delay by just selecting the samples. The later provides a cheap multiplexer-based multiplication. To simplify the receiver as much as possible, RF sampling was investigated, where the receiver is reduced to the SDM. This was made possible by using a sub-sampling approach. Even though, the sampling frequency remains high, and closing the loop and compensating for Excess Loop Delay (ELD) are very challenging. One major result was to show that some sub-sampling SDM could be made ELD compensation free and provide more than one clock cycle to close the loop. This allows for a two-times interleaved quantizer and is a key enabler.

In addition to the interleaved quantizer, the proposed implementation features transformer-based resonators. The additional degree of freedom offered by the ratio between the primary and secondary inductances is very useful to improve power efficiency. While simulation results are below expectation, they are good enough for a proof of concept. A test chip integrating 8 parallel receivers was send for fabrication in a CMOS 28nm FDSOI process from STMicroelectronics and is yet to be tested.

**Key words:** 5G, Millimeter Wave, Digital Beamforming, Analog to Digital Converters, Band Pass Continuous Time Sigma Delta Modulators, Excess Loop Delay, Sub-sampling, RF Sampling, CMOS.

#### Résumé:

Le réseau mobile de cinquième génération, ou 5G, tend à devenir le standard pour l'ensemble des communications sans fil. Il utilisera une plus grande portion du spectre. Les déploiements actuels se concentre sur la bande sous 6GHz. L'exploitation du spectre millimétrique commencera elle dans les années à venir. Il servira à fournir un service mobile large band amélioré sur de petites surfaces. Ces points d'accès à couverture limitée s'appellent petite cellule et sont le sujet de ce travail de thèse. Le cœur de l'étude porte sur le récepteur de ces petites cellules, dans la bande à 28GHz. Elle se divise en trois parties. Une analyse système permettant d'établir les spécifications du récepteur, la proposition d'une architecture de récepteur innovante et une description et une évaluation de l'implémentation proposée.

L'analyse système se base sur les indicateurs de performance clés de la 5G. En partant d'une architecture en ligne avec ces indicateurs, on dérive les spécifications requises du récepteur dans un scénario multi-opérateur. Une caractéristique spécifique de ces récepteurs est leur capacité à former des faisceaux à l'aide de larges tableaux d'antennes. Bien que cette approche ait le potentiel pour satisfaire les objectifs de la 5G, elle est plus complexe. Les nombreux paramètres (nombre d'antennes, topologie du tableau, ...) engendrent beaucoup de configurations possibles et trouver l'optimum devient difficile. Une solution est de fixe un maximum de paramètres sur la base de considérations pratiques, permettant une analyse simplifiée.

La formation de faisceaux se fait par la combinaison des signaux de plusieurs antennes pour recevoir les ondes provenant d'une direction privilégiée. Avant cette combinaison, les signaux sont retardés et pondérés. Le domaine dans lequel ces opérations sont faites défini l'architecture du récepteur. Si elles s'opèrent dans les domaines analogique, numérique ou une combinaison des deux, on parle de formation de faisceaux analogique, numérique ou hybride. L'approche numérique est la plus performante, mais la plus difficile à implémenter. Il faut une chaine complète de réception par antenne. L'analyse proposée montre que les performances requises pour ces récepteurs individuels sont relâchées, et que le défi se trouve dans la gestion en temps réel des données numériques.

Ainsi, les récepteurs permettant une réduction du traitement numérique furent investigués. L'utilisation de Modulateurs Sigma-Delta (MSD), pour la conversion analogique numérique, peut réduire le traitement numérique, grâce à leur sur-échantillonnage et leurs signaux de sortie de faible résolution. L'un permet la réalisation d'un retard presque gratuit en sélectionnant les échantillons. L'autre fourni une multiplication bas coût, à base de multiplexer. Pour simplifier le récepteur, l'échantillonnage direct du signal RF fut investiguée. Le récepteur est alors réduit au MSD. C'est rendu possible grâce au sous-échantillonnage. La fréquence d'échantillonnage reste élevée, et la fermeture de la boucle ainsi que la compensation du Retard de Boucle (RB) reste un défi. Un résultat majeur fut de montrer que certain MSD sous-échantillonnés pouvaient être réalisé sans compensation du RB et avec un temps de fermeture de boucle supérieure à une période d'horloge. Cela permet l'utilisation d'un quantificateur deux fois entrelacé en temps, et rend cette approche réalisable.

En plus du quantificateur entrelacé, l'implémentation proposée présent des résonateurs à base de transformateurs. Le degré de liberté offert par le rapport entre les inductances du primaire et du secondaire est très utile pour améliorer la consommation énergétique. Bien que les résultats de simulations soient moins bons qu'escompté, ils sont suffisamment bons pour établir une preuve de concept. Une puce de test intégrant 8 récepteurs en parallèle fut envoyée en fabrication dans un procédé CMOS 28nm FDSOI de STMicroelectronics et reste à être mesuré.

**Mots clés :** 5G, Ondes Millimétriques, Formation de Faisceaux Numérique, Convertisseurs Analogique Numérique, Modulateurs Sigma Delta Passe Bande à Temps Continu, Retard de Boucle, Souséchantillonnage, Échantillonnage RF, CMOS.

## **List of Publications:**

• Z. Nemes, D. Morche, S. L. Tual and M. Ortmanns, "A Feasibility Study of Digital Beamforming for 5G mmWave Massive MIMO Base Station Receivers," 2018 16th IEEE International New Circuits and Systems Conference (NEWCAS), Montreal, QC, Canada, 2018, pp. 1-5.

## **Table of Contents**

| Acknowledg     | gment                                                                | i   |

|----------------|----------------------------------------------------------------------|-----|

| Abstract       |                                                                      | ii  |

| Résumé         |                                                                      | iii |

| List of Publi  | ications                                                             | iv  |

| List of Acro   | nyms                                                                 | ix  |

|                | 'es                                                                  |     |

|                | es                                                                   |     |

|                | r I: Introduction                                                    |     |

| •              | Generation mobile network overview                                   |     |

| 1.1.1          | The three aspects of 5G: mMTC, URLLC, and eMBB                       |     |

| 1.1.2          | eMBB: Foreseen technologies                                          |     |

| 1.2 Fo         | ocus of this work: Small cell receivers with large antenna arrays    |     |

|                | eferences                                                            |     |

| 2 Chapte       | r II: System analysis                                                | 9   |

|                | formation theory                                                     |     |

| 2.1.1          | Noisy-channel coding theorem                                         | 9   |

| 2.1.2          | Shannon-Hartley theorem                                              | 10  |

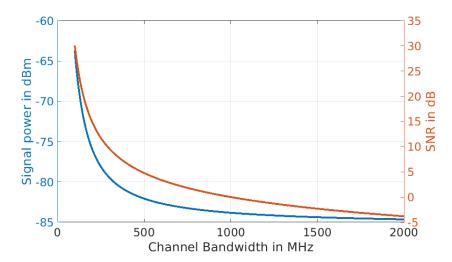

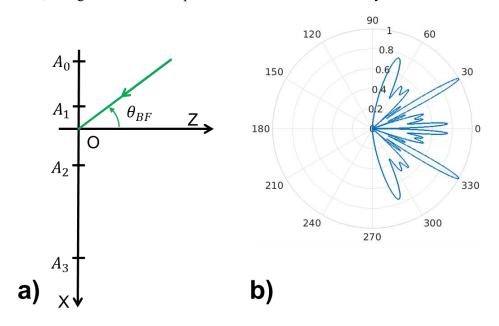

| 2.1.3          | Signal power versus Bandwidth                                        | 11  |

| 2.1.4          | Conclusion                                                           | 12  |

| 2.2 Be         | eamforming                                                           | 12  |

| 2.2.1          | Basic principle                                                      | 13  |

| 2.2.2          | Beamforming algorithm                                                | 15  |

| 2.2.3          | Antenna Array Topology                                               | 23  |

| 2.2.4          | Beamforming receiver architectures                                   |     |

| 2.2.5          | Implementation considerations                                        |     |

| 2.2.6          | Conclusion                                                           |     |

|                | etwork architecture                                                  |     |

| 2.3.1          | Heterogeneous Network                                                |     |

| 2.3.2          | Wireless Backhauling                                                 |     |

| 2.3.3          | Small cell architecture                                              |     |

|                | nk budget                                                            |     |

| 2.4.1<br>2.4.2 | Friis law                                                            |     |

|                | Link budget sensitivity to design variablesvstem sizing and capacity |     |

| ∠. <i>5</i> Sy | stem sizing and capacity                                             | 44  |

| 2.5.1    | System sizing                                             | 44  |

|----------|-----------------------------------------------------------|-----|

| 2.5.2    | Compliance to 5G KPIs                                     | 46  |

| 2.5.3    | Conclusion                                                | 48  |

| 2.6 N    | Aultiple operator scenario                                | 48  |

| 2.6.1    | Worst case scenario in a two-operator environment         | 49  |

| 2.6.2    | OoBI Power Spectral Characteristics                       | 49  |

| 2.6.3    | Conclusion                                                | 53  |

| 2.7      | Conclusion                                                | 53  |

| 2.8 R    | Leferences                                                | 53  |

| 2.9 A    | nnex 2.1                                                  | 56  |

| 2.10 A   | nnex 2.2                                                  | 57  |

| 2.11 A   | nnex 2.3                                                  | 58  |

| 2.12 A   | nnex 2.4                                                  | 60  |

| 2.12.1   | Derivation of equation (2.36)                             | 61  |

| 2.12.2   | Uplink average rate                                       | 61  |

| 2.12.3   | Uplink peak rate                                          | 63  |

| 2.12.4   | Downlink average rate                                     | 64  |

| 2.12.5   | Downlink peak rate                                        | 64  |

| 3 Chapte | er III: Receiver specifications                           | 67  |

| 3.1 H    | ligh level receiver's specifications                      | 67  |

| 3.1.1    | Center Frequency, Bandwidth, Noise Figure and Sensitivity | 67  |

| 3.1.2    | Linearity and Local Oscillator's Phase Noise              | 67  |

| 3.1.3    | Conclusion                                                | 80  |

| 3.2 F    | easibility of DBF                                         | 81  |

| 3.2.1    | Single Receiver architecture description.                 | 81  |

| 3.2.2    | Center frequency and bandwidth                            | 85  |

| 3.2.3    | Gain specification                                        | 86  |

| 3.2.4    | NF specification                                          | 86  |

| 3.2.5    | Linearity specification.                                  | 87  |

| 3.2.6    | Image rejection and anti-aliasing filter                  | 89  |

| 3.2.7    | Analog to Digital Converter specifications                | 90  |

| 3.2.8    | State of the art on building blocks                       | 91  |

| 3.2.9    | Conclusion on feasibility                                 | 94  |

| 3.3      | Conclusion                                                | 95  |

| 3.4 R    | Leference                                                 | 95  |

| 3.5 A    | annex 3.1                                                 | 97  |

| 3.6 A    | NNEX 3.2                                                  | 102 |

| Ļ | Chapter I | V: Receiver's architecture                                 | 105 |

|---|-----------|------------------------------------------------------------|-----|

|   | 4.1 Digi  | tal processing efficient implementation                    | 105 |

|   | 4.1.1     | Digital down-mixing                                        | 105 |

|   | 4.1.2     | True time delay                                            | 106 |

|   | 4.1.3     | Efficient symbol rotation                                  | 107 |

|   | 4.1.4     | Decimation filter                                          | 108 |

|   | 4.1.5     | Conclusion                                                 | 109 |

|   | 4.2 Sign  | na-Delta Modulators                                        | 109 |

|   | 4.2.1     | Basic concepts                                             | 109 |

|   | 4.2.2     | Continuous time modulators                                 | 117 |

|   | 4.2.3     | "fs/4" Modulators                                          | 128 |

|   | 4.2.4     | Sub-sampling modulators                                    | 129 |

|   | 4.2.5     | ELD compensation in Sub-sampling modulators                | 131 |

|   | 4.2.6     | Conclusion                                                 | 133 |

|   | 4.3 Prop  | oosed architecture                                         | 133 |

|   | 4.3.1     | Architecture                                               | 133 |

|   | 4.3.2     | Modulator simulation and characterization                  | 136 |

|   | 4.3.3     | Non-zero ELD modulators                                    | 140 |

|   | 4.3.4     | Robustness optimization to feedback coefficient variations | 147 |

|   | 4.3.5     | Sensitivity to ELD variations                              | 151 |

|   | 4.3.6     | Individual feedback path ELD optimization                  | 153 |

|   | 4.4 Con   | clusion                                                    | 154 |

|   | 4.5 Refe  | erences                                                    | 155 |

|   | 4.6 AN    | NEX 4.1                                                    | 156 |

| , | Chapter V | V: Implementation                                          | 158 |

|   | 5.1 Buil  | ding blocks topologies                                     | 158 |

|   | 5.1.1     | Feedforward weighting coefficients                         | 158 |

|   | 5.1.2     | Feedback DACs                                              | 162 |

|   | 5.1.3     | Resonator topology                                         | 168 |

|   | 5.1.4     | Quantizer implementation                                   | 178 |

|   | 5.1.5     | Clock and Data distribution trees                          | 186 |

|   | 5.1.6     | Testing features and calibration procedure                 | 188 |

|   | 5.2 Opti  | mization methodology                                       | 189 |

|   | 5.2.1     | Initial LC based modulator sizing                          | 190 |

|   | 5.2.2     | Transformer based modulator sizing                         | 193 |

|   | 5.2.3     | Transient simulations                                      | 198 |

|   | 5.2.4     | Conclusion                                                 | 200 |

| 5.3 Test Chip Top level |       | 201                           |     |

|-------------------------|-------|-------------------------------|-----|

|                         | 5.3.  | 1 Top Level Block Diagram     | 201 |

|                         | 5.3.2 | 2 Top level layout            | 202 |

|                         | 5.3.  | 3 State of the Art comparison | 204 |

|                         | 5.4   | Conclusion                    | 205 |

|                         | 5.5   | References                    | 206 |

| 6                       | Con   | clusion                       | 208 |

# List of Acronyms

| ·       |                                                 |

|---------|-------------------------------------------------|

| AAP     | Adaptive Array Processing                       |

| ABF     | Analog Beamforming                              |

| AC      | Alternating Current                             |

| ACLR    | Adjacent Channel Leakage Ratio                  |

| ADC     | Analog to Digital Converter                     |

| AF      | Array Factor                                    |

| ALTR    | ALTernate channel leakage Ratio                 |

| AoA     | Angle of Arrival                                |

| AWGN    | Additive White Gaussian Noise                   |

| BB      | Base Band                                       |

| BBP     | Base Band Processor                             |

| BG      | Back Gate                                       |

| BiCMOS  | Bipolar-CMOS                                    |

| BLER    | BLock Error Rate                                |

| BPCTSDM | Band Pass Continuous Time Sigma-Delta Modulator |

| BPDTSDM | Band Pass Discrete Time Sigma-Delta Modulator   |

| BS      | Base Station                                    |

| CDMA    | Code Division Multiple Access                   |

| CDS     | Correlated Double Sampling                      |

| CMOS    | Complementary Metal Oxid Semiconductor          |

| CMRR    | Common Mode Rejection Ratio                     |

| СР      | Charge Pump                                     |

| CSI     | Channel State Information                       |

| CT      | Continuous Time                                 |

| CTFBIR  | Continuous Time Feedback Impulse Response       |

| CTSDM   | Continuous Time Sigma-Delta Modulators          |

| CVDAC   | Capacitively coupled Voltage DAC                |

| DAC     | Digital to Analog Converters                    |

| DBF     | Digital Beamforming                             |

| dBm     | decibels per milli-Watt                         |

| DC      | Direct Current                                  |

| DFT     | Discrete Fourier Transform                      |

| DQAM    | Differential QAM                                |

| DR      | Dynamic Range                                   |

| DS      | Delay and Sum                                   |

| DT      | Discrete Time                                   |

| DTFBIR  | Discrete Time Feedback Impulse Response         |

| DTSDM   | Discrete Time Sigma-Delta Modulator             |

| DWS     | Delay Weight and Sum                            |

| ELD     | Excess Loop Delay                               |

| eMBB    | enhanced Mobile Broad Band                      |

| ESD     | Electro-Static Discharge                        |

|         |                                                 |

| EVM             | Error Vector Modulation                      |

|-----------------|----------------------------------------------|

| FD              | Frequency Divider                            |

| FDMA            | Frequency Division Multiple Access           |

| FDSOI           | Fully Depleted Silicon on Insulator          |

| FIR             | Finite Impulse Response                      |

| GSG             | Ground Signal Ground                         |

| GSM             | Global System for Mobile communication       |

| HBF             | Hybrid Beamforming                           |

| HPBW            | Half Power Beam Width                        |

| HRZ             | Half delayed Return to Zero                  |

| IBI             | In Band Interferers                          |

| ICI             | Inter Carrier Interference                   |

| IDAC            | Current DAC                                  |

| IF              | Intermediate Frequency                       |

| IIP3            | third order Input Intercept Point            |

| IL              | Insertion Loss                               |

| IM3             | third order Inter-Modulation                 |

| IM5             | fifth order Inter-Modulation                 |

| IRR             | Interferer Rejection Ration                  |

| ISF             | Impulse Sensitivity Function                 |

| KPI             | Key Performance Indicators                   |

| LDPC            | Low Density Parity Check                     |

| LED             | Light Emitting Diode                         |

| LF              | Loop Filter                                  |

| LNA             | Low Noise Amplifier                          |

| LO              | Local Oscillator                             |

| LoS             | Line of Sight                                |

| LP              | Low Pass                                     |

| LPDTSDM         | Low Pass Discrete Time Sigma-Delta Modulator |

| LPF             | Low Pass Filter                              |

| LTI             | Linear Time Invariant                        |

| LTV             | Linear Time Varying                          |

| MACLR           | Modified ACLR                                |

| M-BS            | Macro-cell BS                                |

| MC-UCA          | Multiple Concentric UCA                      |

| MIMO            | Multiple Input Multiple Output               |

| ML              | Maximum Likelihood                           |

| MMSE            | Minimum Mean-Square Error                    |

| mMTC            | massive Machine Type Communication           |

| MPW             | Multi-Project Wafer                          |

| MRC             | Maximum Ratio Combining                      |

| MU Massive      | Multiple Users Massive MIMO                  |

| MIMO<br>MU-MIMO | Multiple User MIMO                           |

| TATO-TATTIATO   | Interrible Oper Interrior                    |

| Near-ZIF | Near Zero Intermediate Frequency              |

|----------|-----------------------------------------------|

| NF       | Noise Figure                                  |

| NLoS     | None Line of Sight                            |

| NOMA     | Non-Orthogonal Multiple Access                |

| NPR      | Noise Power Ratio                             |

| NRZ      | Non-Return to Zero                            |

| NTF      | Noise Transfer Function                       |

| NTN      | Non-Terrestrial Networks                      |

| NZ       | Nyquist Zone                                  |

| OFDM     | Orthogonal Frequency Division Multiplexing    |

| OFDMA    | Orthogonal Frequency Division Multiple Access |

| OIP3     | third order Output Intercept Point            |

| OMA      | Orthogonal Multiple Access                    |

| OoBI     | Out of Band Interferers                       |

| OS       | OverShoot                                     |

| OSR      | Over Sampling Ratio                           |

| PA       | Power Amplifier                               |

| PAPR     | Peak to Average Power Ratio                   |

| PCB      | Printed Circuit Board                         |

| PFD      | Phase Frequency Detector                      |

| PLL      | Phase Lock Loop                               |

| PM       | Phase Margin                                  |

| PN       | Phase Noise                                   |

| PSD      | Power Spectral Density                        |

| PSL      | Peak Side Lobe                                |

| PSS      | Phase Shift and Sum                           |

| PVT      | Process and Temperature Variations            |

| QAM      | Quadrature Amplitude Modulation               |

| RB       | Resource Block                                |

| RE       | Resource Element                              |

| RF       | Radio Frequency                               |

| RMS      | Root Mean Square                              |

| RRC      | Root Raise Cosine                             |

| Rx       | Receiver                                      |

| RZ       | Return to Zero                                |

| SAR      | Successive Approximation Register             |

| S-BS     | Small-cell BS                                 |

| SCS      | Sub Carrier Spacing                           |

| SDM      | Sigma-Delta Modulators                        |

| SF       | Source Follower                               |

| SFDR     | Spurious Free Dynamic Range                   |

| SH       | Sample and Hold                               |

| SINR     | Signal to Interferer plus Noise Ratio         |

| SMS      | Short Messaging System                        |

| SNR   | Signal to Noise Ratio                    |

|-------|------------------------------------------|

| SOI   | Silicon On Insulator                     |

| SPI   | Serial Parallel Interface                |

| SQNR  | Signal to Quantization Noise Ratio       |

| SRx   | Single Receiver                          |

| SSB   | Single Side Band                         |

| STF   | Signal Transfer Function                 |

| TDD   | Time Division Duplexing                  |

| TDMA  | Time Division Multiple Access            |

| THD   | Total Harmonic Distortion                |

| TSPC  | True Single-Phase Clock                  |

| Tx    | Transmitter                              |

| UCA   | Uniform Circular Arrays                  |

| UE    | User Equipment                           |

| ULA   | Uniform Linear Arrays                    |

| UPA   | Uniform Planar Arrays                    |

| URLLC | Ultra-Reliable Low Latency Communication |

| VCO   | Voltage Controlled Oscillator            |

| ZF    | Zero Forcing                             |

# **List of Figures**

| Figure 1-1: 4G versus 5G Key Performance Indicators                                                | 2      |

|----------------------------------------------------------------------------------------------------|--------|

| Figure 1-2: Radio frame division and sub-division in the time domain                               | 3      |

| Figure 1-3: Representation of the resource grid                                                    | 4      |

| Figure 2-1: Binary symmetric noisy channel                                                         | 10     |

| Figure 2-2: Signal power and SNR versus channel bandwidth for a constant channel capacity of 10    | Gbit/s |

|                                                                                                    | 12     |

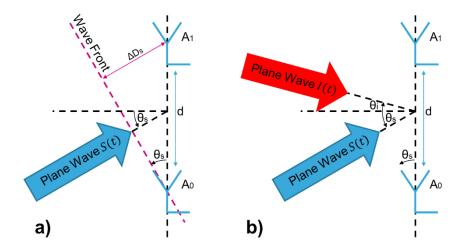

| Figure 2-3: Two elements antenna array with a) One incoming plane wave b) Two incoming             | plane  |

| waves                                                                                              | 13     |

| Figure 2-4: Plots of incoming plane waves, antenna received signals and beamformed signals         | 14     |

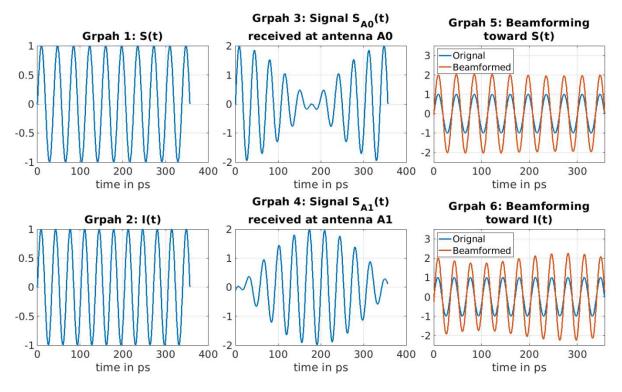

| Figure 2-5: a) Linear antenna array b) Corresponding radiation pattern                             | 15     |

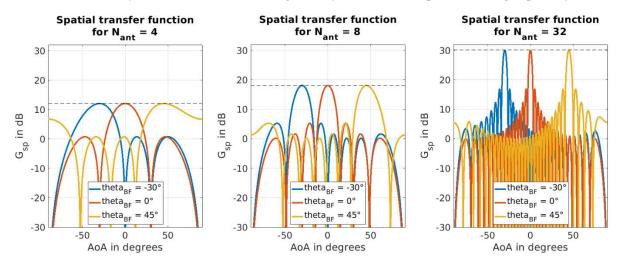

| Figure 2-6: Spatial transfer function for ULAs with 4, 8 and 32 antennas for various beamfor       | rming  |

| angles                                                                                             | 18     |

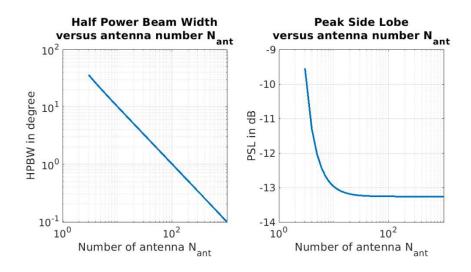

| Figure 2-7: HPBW (left) and PSL (right) for ULAs versus the number of antennas Nant                | 18     |

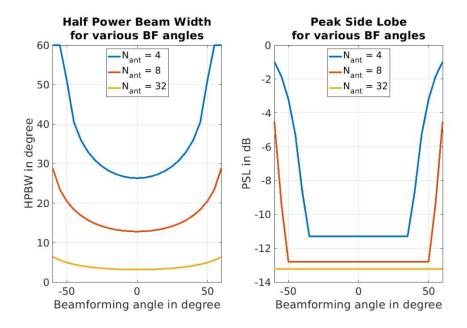

| Figure 2-8: HPBW and PSL for ULA's with 4, 8 and 32 antennas for various beamforming angle         | s19    |

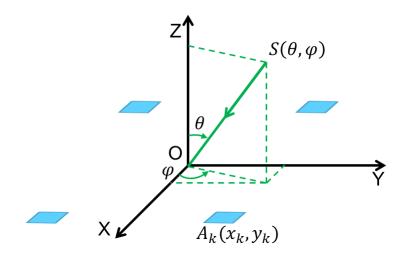

| Figure 2-9: Used convention to describes UPAs                                                      | 24     |

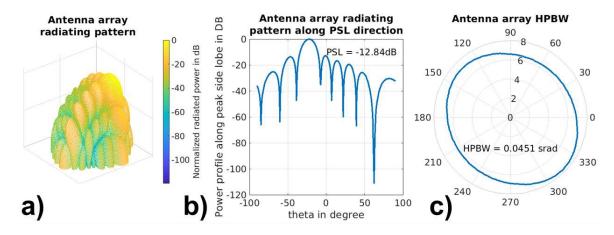

| Figure 2-10: 64 element UPA a) Radiation Pattern b) Profile along PSL c) HPBW contour              | 25     |

| Figure 2-11: HPBW (left) and PSL (right) for square UPAs versus the number of antennas Nant        | 25     |

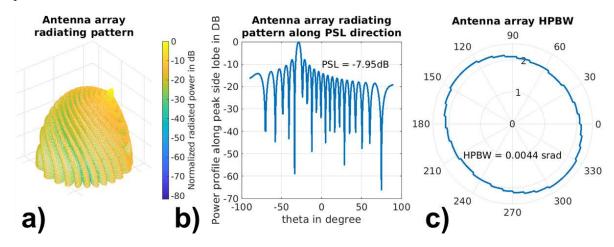

| Figure 2-12: 64 element UCA a) Radiation Pattern b) Profile along PSL c) HPBW contour              | 26     |

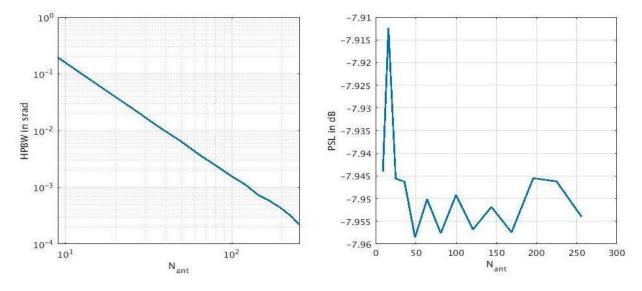

| Figure 2-13: HPBW and PSL for UCAs versus the number of antennas Nant                              | 26     |

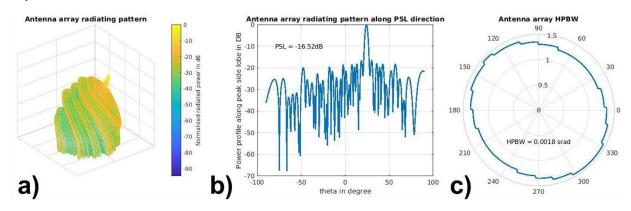

| Figure 2-14: 364 elements MC-UCA a) Radiation Pattern b) Profile along PSL c) HPBW contour         | r27    |

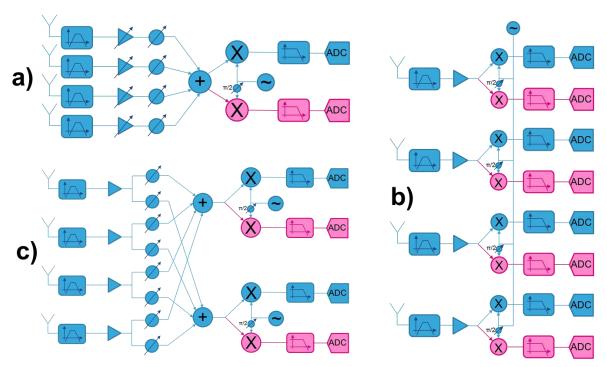

| Figure 2-15: Beamforming Receiver block diagram: a) ABF b) DBF c) HBF                              | 28     |

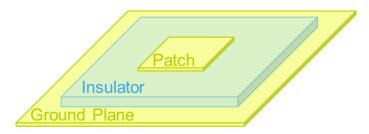

| Figure 2-16: Basic architecture of a patch antenna                                                 | 30     |

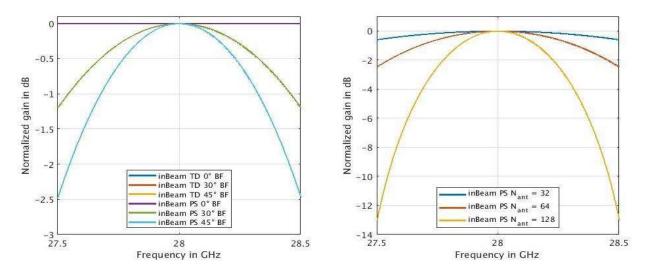

| Figure 2-17: In Beam frequency response of time delay versus phase shift beamforming. Left:        |        |

| with 64 elements for steering angles of 0°, 30° and 45°. Right: Steering angle of 45° using phase  | shift  |

| beamforming for ULAs with 32, 64 and 128 elements                                                  |        |

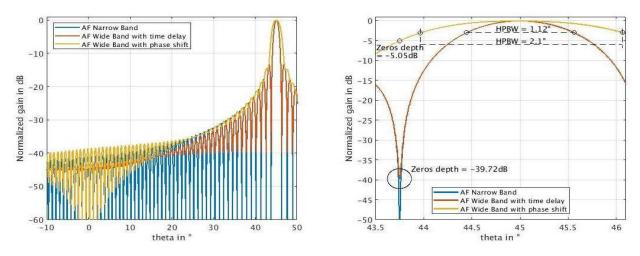

| Figure 2-18: Array factor for a 128-element ULA for narrow and wide band signal with time dela     | y and  |

| phase shift beamforming                                                                            | 31     |

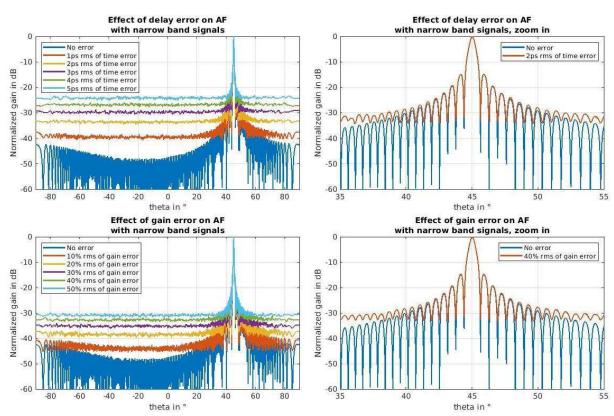

| Figure 2-19: Top graphs: Average impact of time delay error on Array Factor. Bottom graphs: Av     |        |

| impact of gain error on Array Factor                                                               |        |

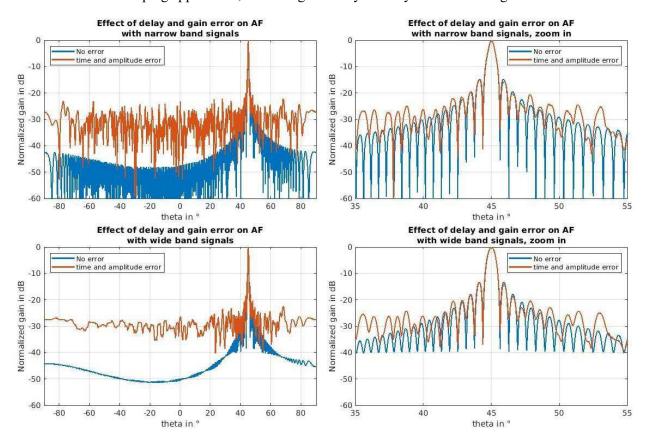

| Figure 2-20: Top graphs: Impact of delay and gain error on Array Factor for narrow band signals Be |        |

| graphs: Impact of delay and gain error on Array Factor for wide band signals                       |        |

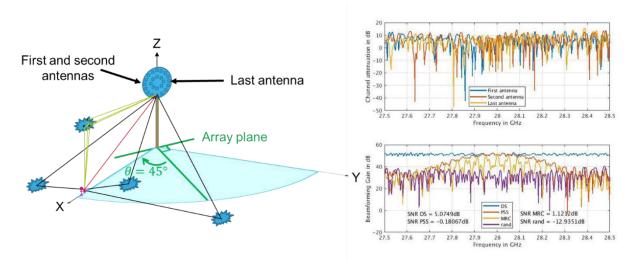

| Figure 2-21: Left: multipath channel model. Top Right: Channel response for the two adjacent mo    |        |

| antennas and the most right one. Bottom Right: Beamforming gain for various beamforming me         |        |

|                                                                                                    |        |

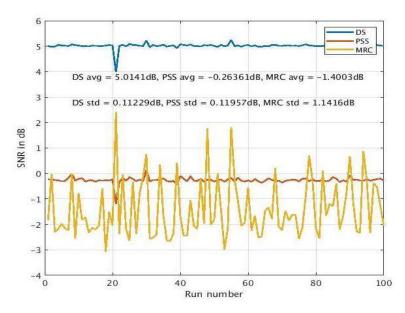

| Figure 2-22: SNR for 100 channel realizations for DS, PSS and MRC beamforming                      |        |

| Figure 2-23: 5G Network deployment strategy                                                        |        |

| Figure 2-24: Potential deployment scenario for heterogeneous network and backhaul                  |        |

| Figure 2-25: LoS probability for a user at distance d and average LoS probability in a cell of ra- |        |

|                                                                                                    |        |

| Figure 2-26: Distribution of backhaul links per sector for a cell division in four                 |        |

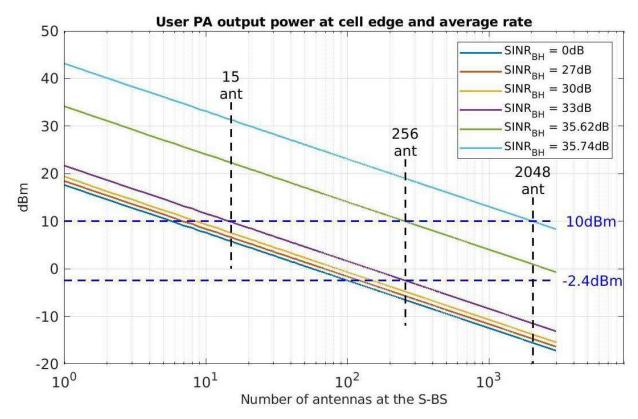

| Figure 2-27: Users' PA output power at cell edge and average rate as a function of the numb        |        |

| receiving antennas for various SINRBH                                                              |        |

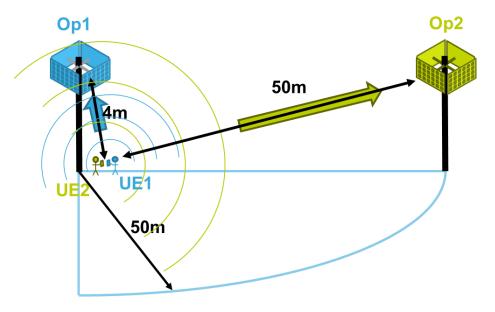

| Figure 2-28: Worst case UE configuration                                                           |        |

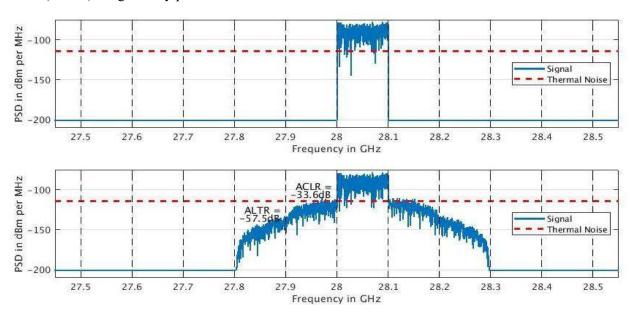

| Figure 2-29: Impact of non-linearity on wide band signals. Top: original signal. Bottom: signal    |        |

| undergoing non-linearity of third and fifth order                                                  |        |

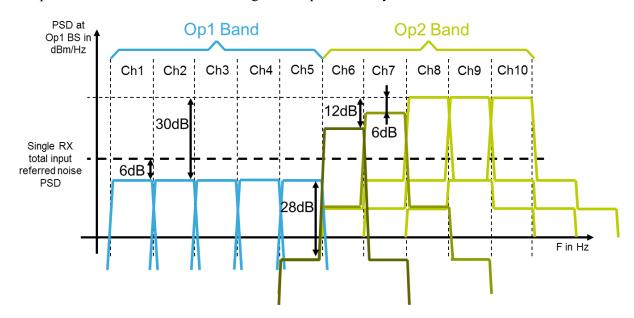

| Figure 2-30: Op1 S-BS single receiver PSD profile                                                  |        |

| Figure 3-1: Left graph: Leaked power in channel 5 from non-linearity versus IIP3. Top right g      |        |

| input signal. Bottom right graph: Output distorted signal                                          | 69     |

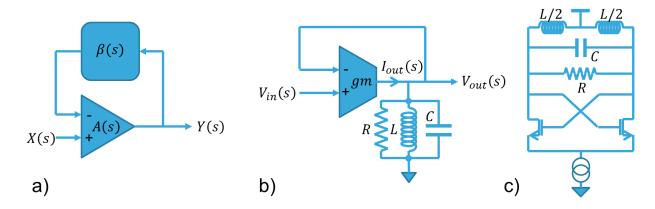

| Figure 3-2: a) Linear Time Invariant (LTI) model of an oscillator b) Block diagram for an RLC resonator                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| c) Differential implementation using a cross-coupled pair for negative trans-conductance70                                                                    |

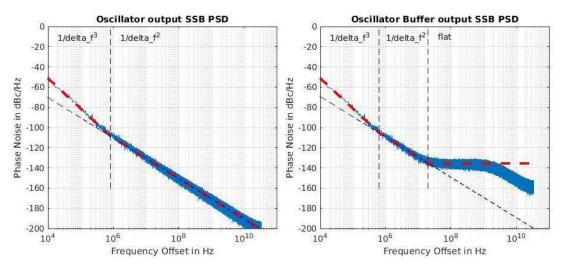

| Figure 3-3: Typical Single Side Band PSD of a free running oscillator on the left and of its limiting                                                         |

| amplifier output on the right                                                                                                                                 |

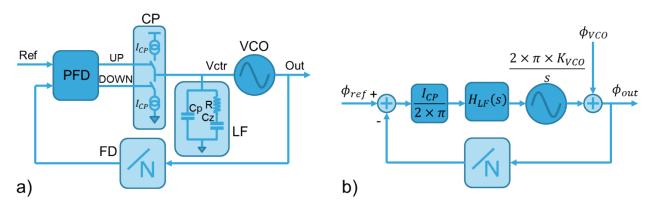

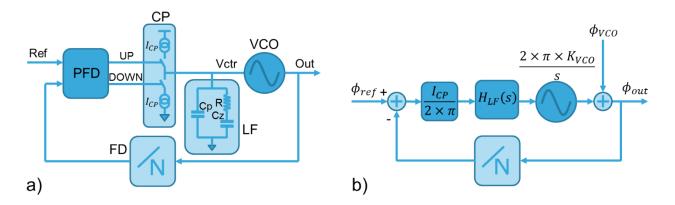

| Figure 3-4: a) PLL Classical implementation b) Equivalent Linear Time Invariant (LTI) model 73                                                                |

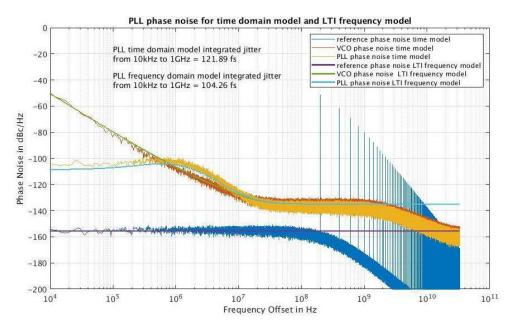

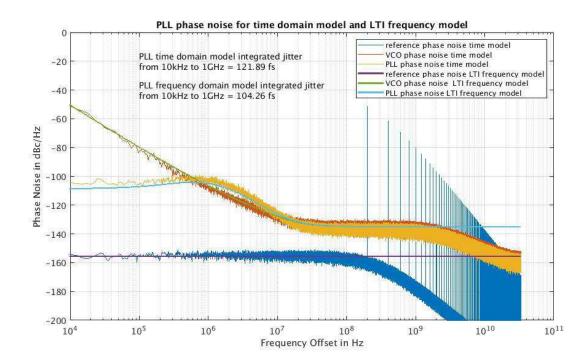

| Figure 3-5: Phase Noise of a matlab time domain implementation of the PLL versus the LTI frequency                                                            |

| model with a center frequency of 22.4GHz74                                                                                                                    |

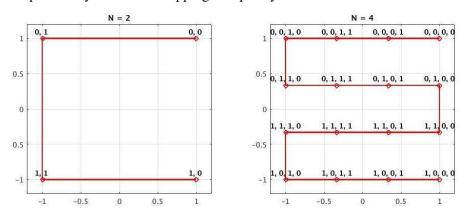

| Figure 3-6: Symbol mapping for 2-bit symbols on the left and 4-bit symbols on the right                                                                       |

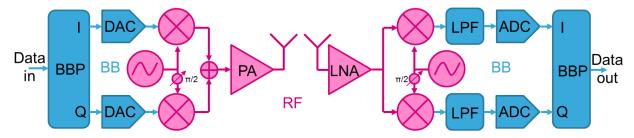

| Figure 3-7: Block diagram of a wireless transmission chain with homodyne transmitter and receiver 75                                                          |

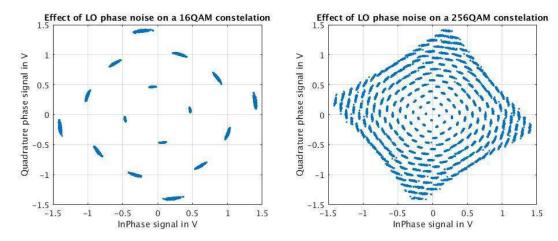

| Figure 3-8: Impact of phase noise on received QAM symbols for 100us long symbol stream a                                                                      |

| 100Msymbols/s                                                                                                                                                 |

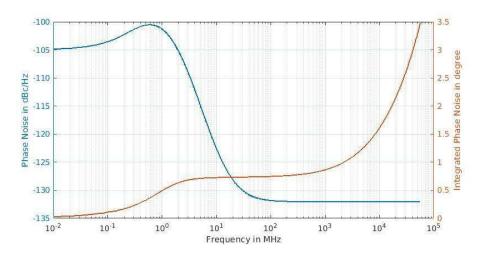

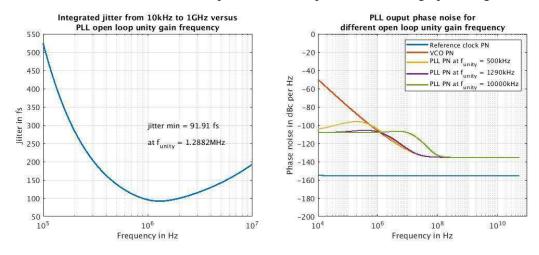

| Figure 3-9: PLL phase noise and integrated phase noise as a function of frequency                                                                             |

| Figure 3-10: Received signal spectrum and received symbols for three different cases: left) No phase                                                          |

| noise. center) Phase noise added after filtering. right) Phase noise added before filtering78                                                                 |

| Figure 3-11: Evaluation of reciprocal mixing between a modulated interferer and a noisy LO80                                                                  |

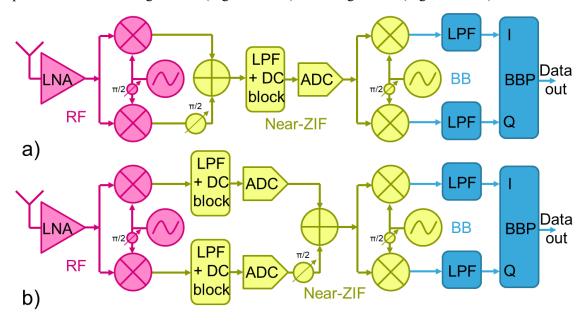

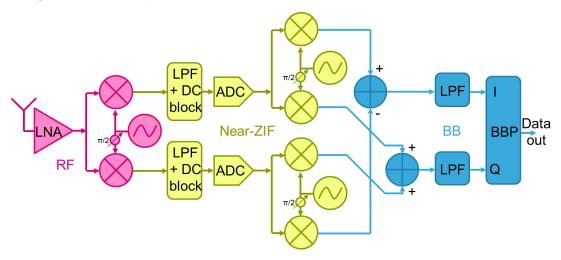

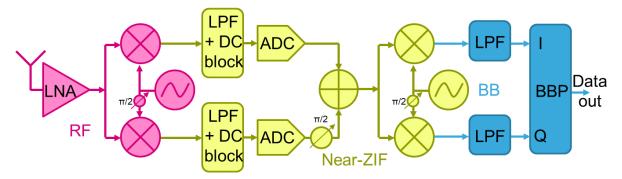

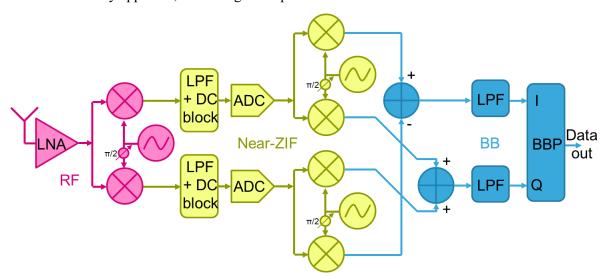

| Figure 3-12: a) Rx homodyne architecture b) Rx Near-ZIF naive architecture                                                                                    |

| Figure 3-13: Impact of Image frequency on a Near-ZIF naive implementation                                                                                     |

| Figure 3-14: Near-ZIF receiver using the Hartley image cancelling approach a) with an analog                                                                  |

| implementation, b) with a digital implementation                                                                                                              |

| Figure 3-15: Near-ZIF receiver using the Weaver image cancelling approach with a digital                                                                      |

| implementation                                                                                                                                                |

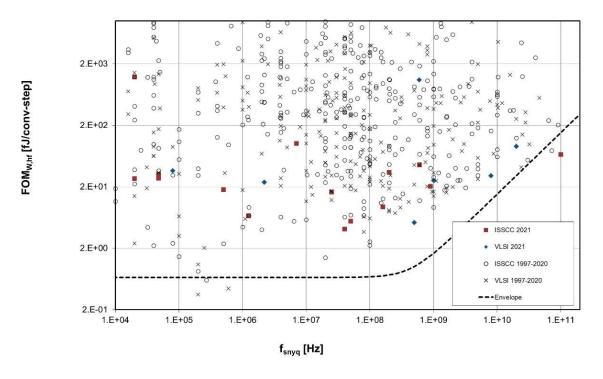

| Figure 3-16: Walden Figure of Merit versus sampling frequency                                                                                                 |

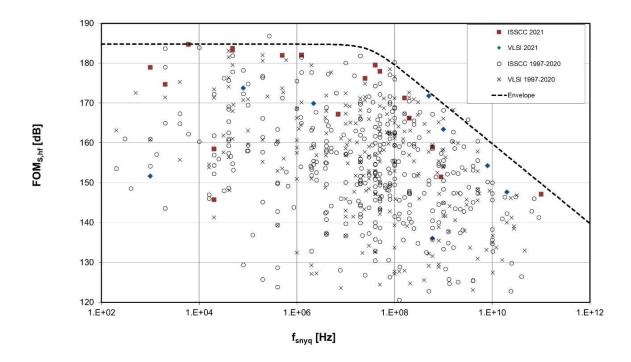

| Figure 3-17: Schreier Figure of Merit versus sampling frequency                                                                                               |

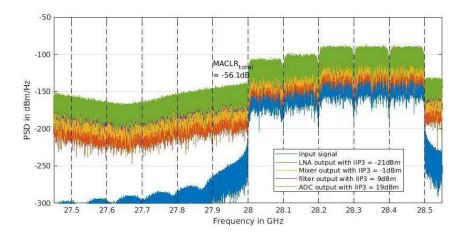

| Figure 3-18: Output spectrum of the different building blocks for IIP3 compatible with MACLR                                                                  |

| specifications                                                                                                                                                |

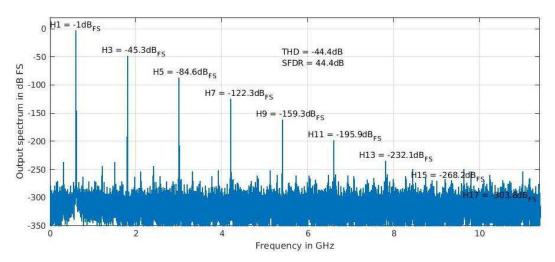

| Figure 3-19: ADC output spectrum for a single tone input at $-1dBFS$                                                                                          |

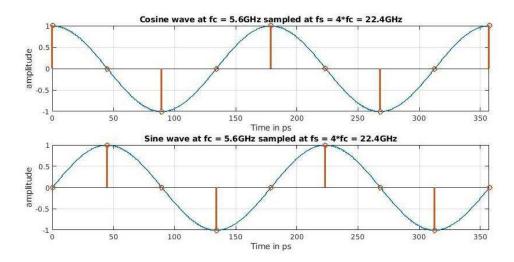

| Figure 4-1: Cosine (top) and sine (bottom) waves sampled at $fs = 4 \times fc$                                                                                |

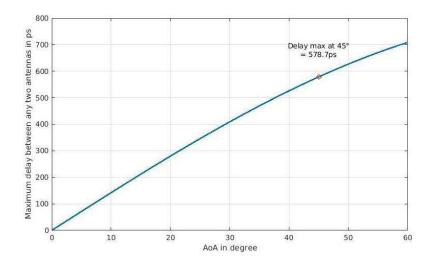

| Figure 4-2: Maximum delay between any two antennas versus the angle of arrival for an MC-UCA of                                                               |

| 364 elements with an outer diameter of 24cm                                                                                                                   |

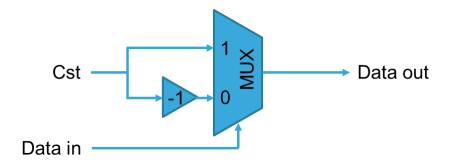

| Figure 4-3: Multiplexer based multiplier                                                                                                                      |

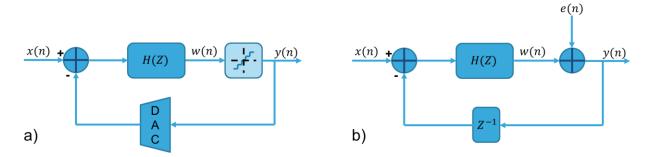

| Figure 4-4: a) Basic schematic of a DT sigma-delta modulator, b) LTI equivalent model                                                                         |

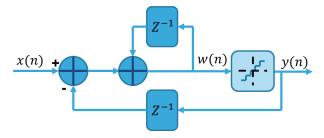

| Figure 4-5: Simulation model of a first order LPDTSDM                                                                                                         |

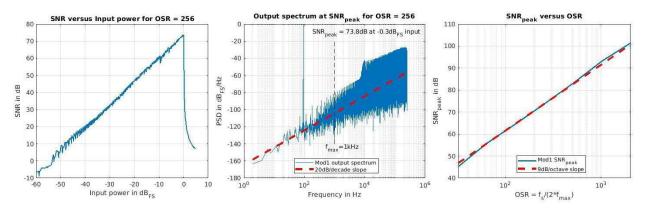

| Figure 4-6: Simulation of a first order LPDTSDM. Left: SNR versus input power. Middle: Output                                                                 |

| spectrum at SNRpeak . Left: SNRpeak versus OSR                                                                                                                |

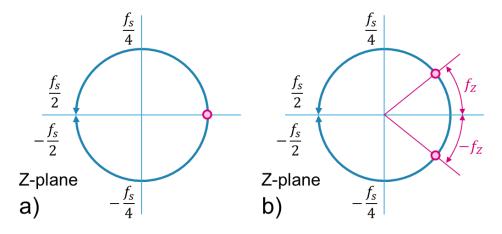

| Figure 4-7: a) Zeros' location of a first order LPDTSDM. b) Zero locations of second order BPDTSDM.                                                           |

|                                                                                                                                                               |

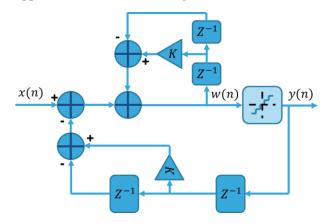

| Figure 4-8: Simulation model of a second order BPDTSDM 114                                                                                                    |

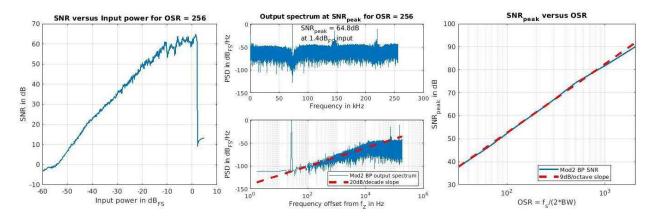

| Figure 4-9: Simulation of a second order BPDTSDM. Left: SNR versus input power. Middle: Output                                                                |

| spectrum at SNRpeak. Right: SNRpeak versus OSR                                                                                                                |

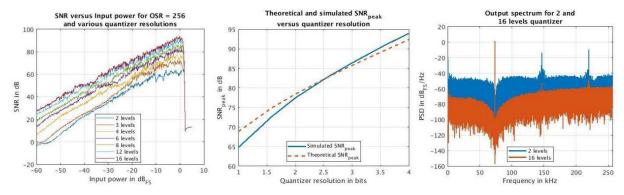

| Figure 4-10: Simulation of a second order BPDTSDM for various quantizer resolution. Left: SNR                                                                 |

| versus input power. Middle: Theoretical and simulated peak SNR. Right: Output spectrum for a 2 and                                                            |

| a 16 level quantizer                                                                                                                                          |

| Figure 4-11: 3 level quantizer BPDTSDM. Left) SNR versus input power + PAPR for multiple tone                                                                 |

| inputs. Middle) Theoretical and simulated SNR +PAPR versus number of input tones. Right) SNR peak                                                             |

| spectrum for single and 10 tones inputs                                                                                                                       |

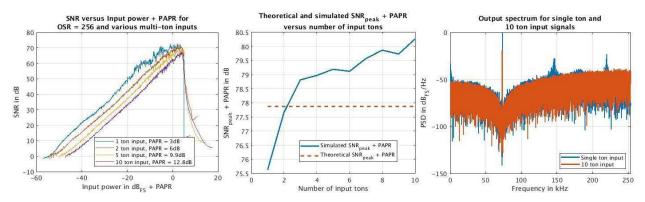

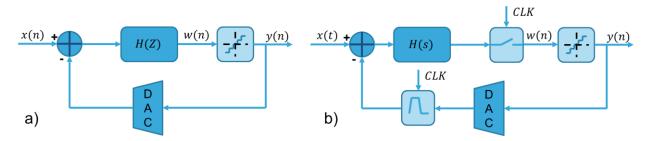

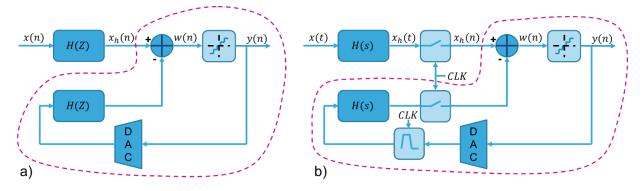

| Figure 4-12: a) Discrete time sigma-delta modulator b) Continuous time sigma-delta modulator 117                                                              |

| Figure 4-12: a) Discrete time signia-detta modulator b) Continuous time signia-detta modulators b) Continuous time signia-detta modulators b) Continuous time |

| sigma-delta modulators                                                                                                                                        |

| Figure 4-14: General representation of CTSDM                                                                                                                  |

|                                                                                                                                                               |

| Figure 4-15: Signal Transfer Function characteristics of a first order LPCTSDM with an OSR of               |       |

|-------------------------------------------------------------------------------------------------------------|-------|

| and a bandwidth of 1kHz                                                                                     | 121   |

| Figure 4-16: BPCTSDM parametric architecture                                                                |       |

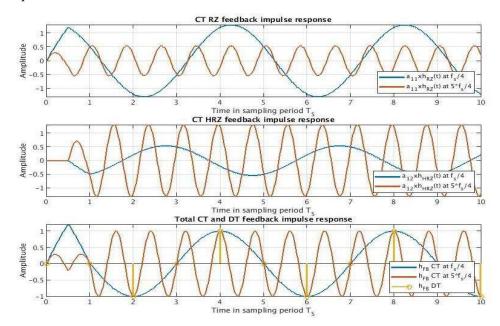

| Figure 4-17: CT and DT feedback impulse response for $fZ = fs/8$                                            | 125   |

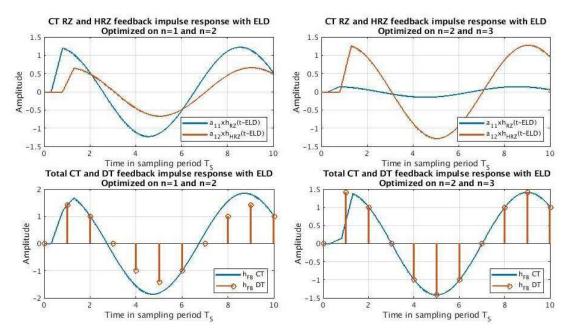

| Figure 4-18: Impact of $ELD = 0.3 \times TS$ on the CT impulse responses for $fZ = fs/8$ .                  | Left) |

| Optimization done using $n = 1$ and $n = 2$ . Right) Optimization done using $n = 2$ and $n = 3$            | 126   |

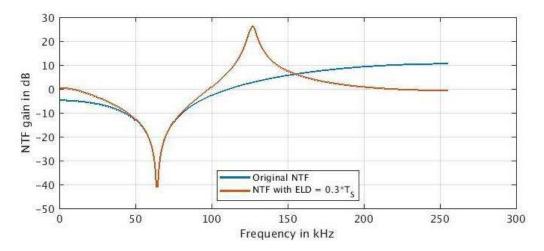

| Figure 4-19: ELD impact of the NTF                                                                          | 127   |

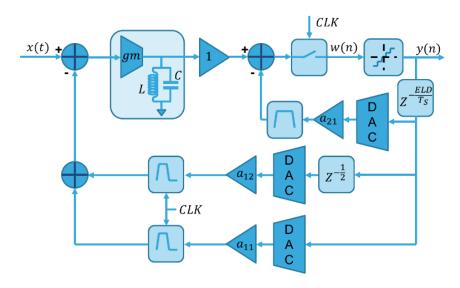

| Figure 4-20: Modified BPCTSDM architecture for ELD compensation                                             | 127   |

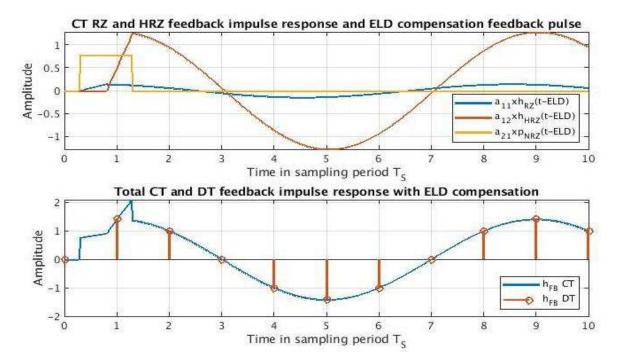

| Figure 4-21: Feedback impulse response with ELD compensation                                                | 128   |

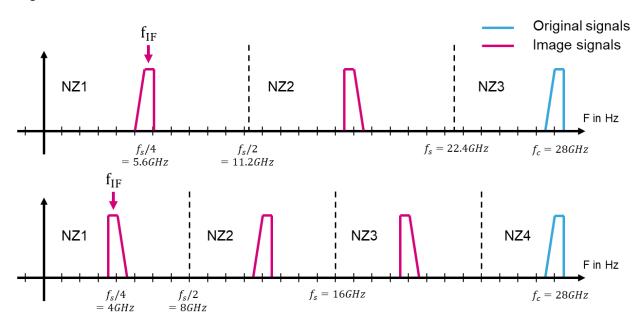

| Figure 4-22: Frequency planning for a sampling frequency of 22.4GHz on top and 16GHz or                     | n the |

| bottom                                                                                                      | 130   |

| Figure 4-23: Impulse response comparison between $fs/4$ and $5 \times fs/4$ resonators                      | 131   |

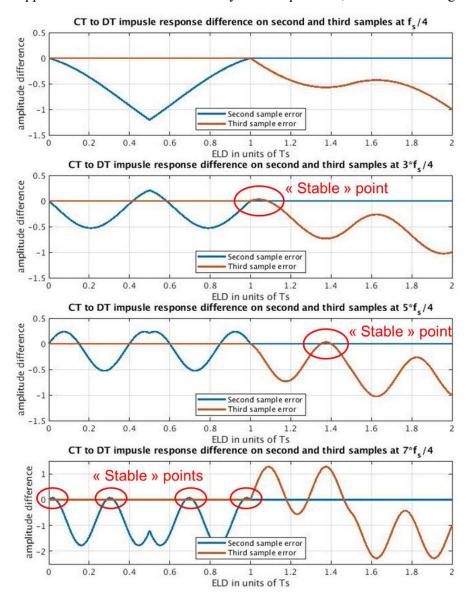

| Figure 4-24: Second and third sample errors versus ELD for, from top to bottom, $fs/4$ ; $3 \times fs/4$ ;  |       |

| $fs/4$ ; and $7 \times fs/4$ modulators                                                                     | 132   |

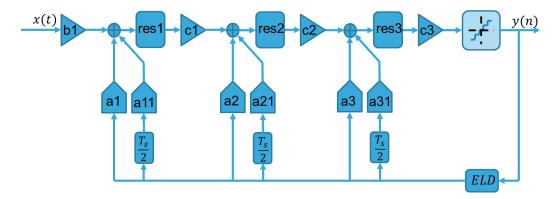

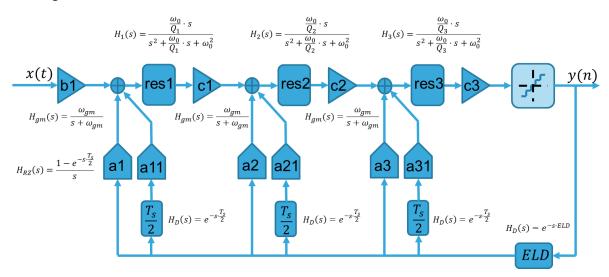

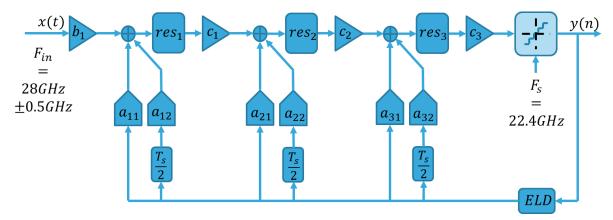

| Figure 4-25: Modulator's architecture                                                                       | 135   |

| Figure 4-26: Modulator's architecture with its associated Laplace transforms                                | 136   |

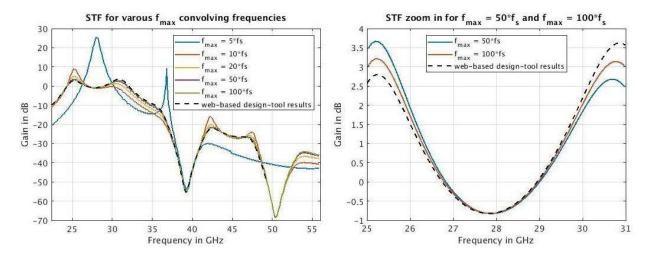

| Figure 4-27: STF versus maximum convolving frequency                                                        | 137   |

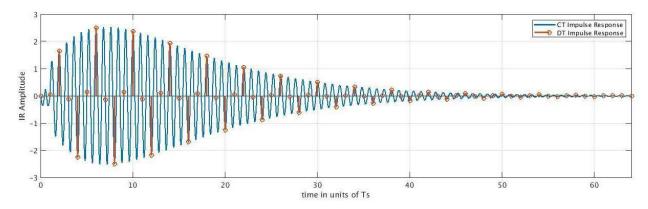

| Figure 4-28: Continuous and Discrete Time Feedback Impulse Response over 64 sampling peri                   | iodes |

|                                                                                                             |       |

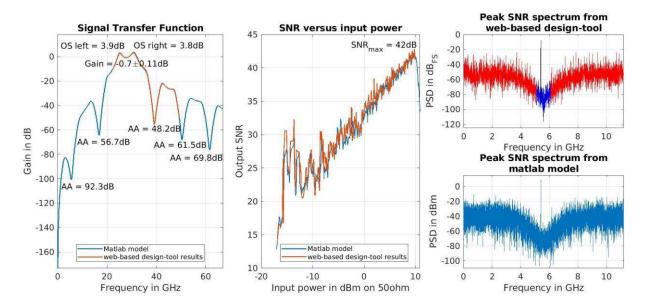

| Figure 4-29: Comparison between web-based design-tool results and proposed matlab model re-                 |       |

|                                                                                                             | 138   |

| Figure 4-30: Input full scale optimization results                                                          | 139   |

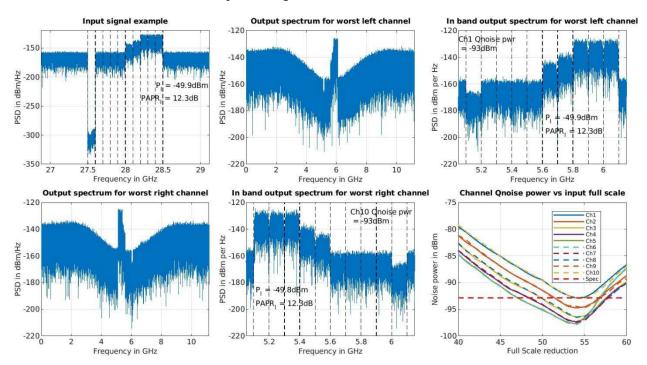

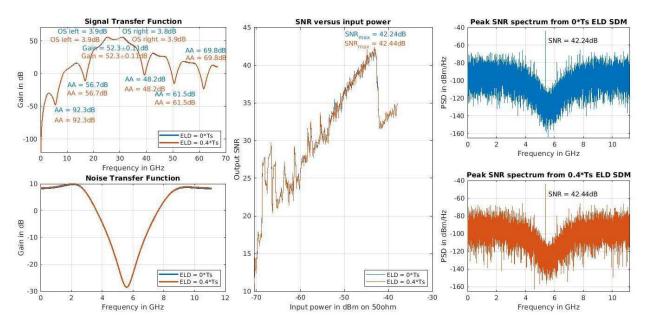

| Figure 4-31: Comparison of modulators with respectively 0 and 0.4 × TS ELD                                  | 141   |

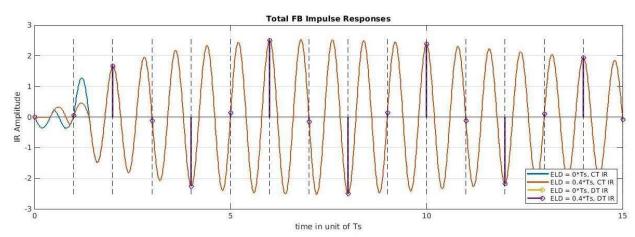

| Figure 4-32: Comparison of modulators' feedback impulse responses for 0 and $0.4 \times TS$                 | ELD   |

| modulators                                                                                                  | 141   |

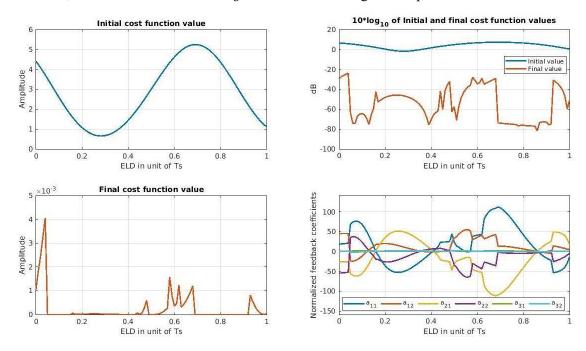

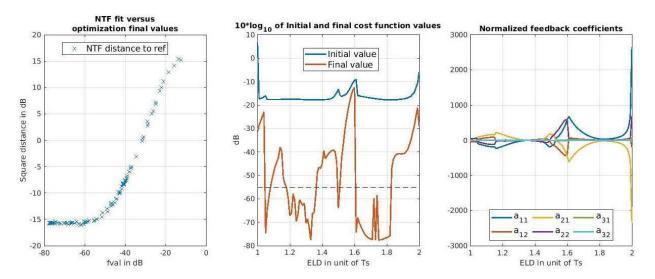

| Figure 4-33: Optimization results for ELD values from 0 to TS                                               | 142   |

| Figure 4-34: Optimization final value impact                                                                | 143   |

| Figure 4-35: STF and NTF comparison when feedback impulse response second sample set to                     | zero  |

|                                                                                                             |       |

| Figure 4-36: STF and NTF comparison when feedback impulse response odd samples are set to                   | zero  |

|                                                                                                             |       |

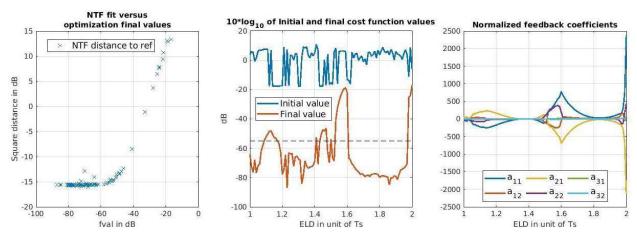

| Figure 4-37: Optimization results for ELD values from 1 to 2 TS                                             | 145   |

| Figure 4-38: Optimization results for ELD values from 1 to 2 TS using previous point for initializ          | ation |

|                                                                                                             |       |

| Figure 4-39: Optimization results for ELD values from 1 to 2 TS using the refined procedure                 |       |

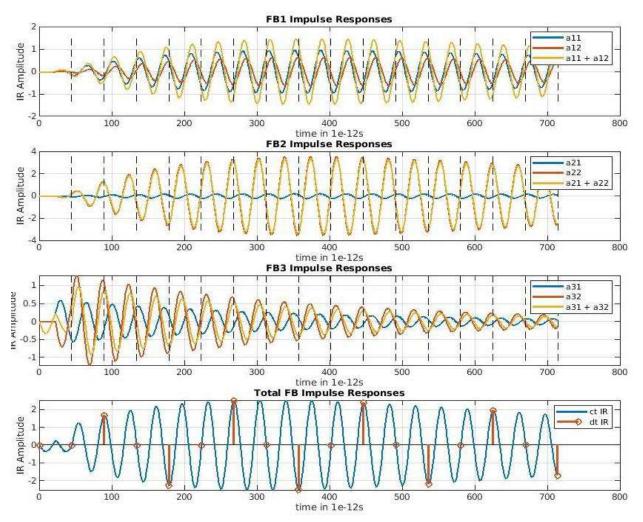

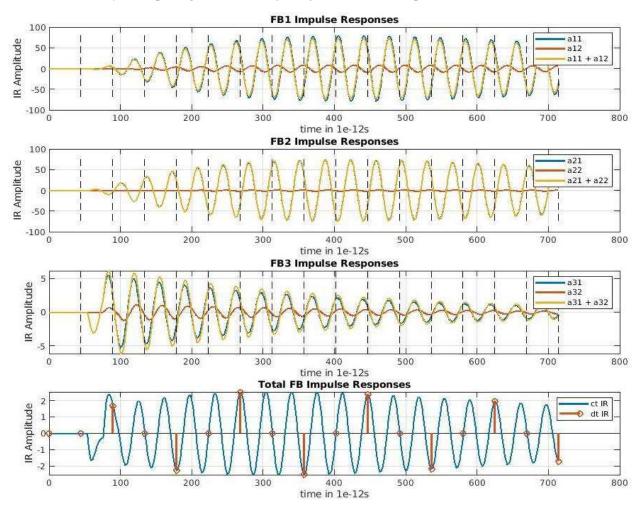

| Figure 4-40: Individual continuous time impulse response of individual feedback paths of the refer          | rence |

| modulator                                                                                                   |       |

| Figure 4-41: Individual continuous time impulse response of individual feedback paths of the 1.2 of         |       |

| cycle ELD modulator                                                                                         |       |

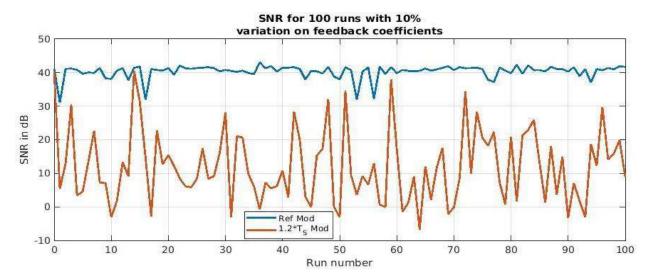

| Figure 4-42: Reference and 1.2 clock cycle ELD modulators SQNR for Gaussian feedback coefficients           |       |

| varations over 100 runs                                                                                     |       |

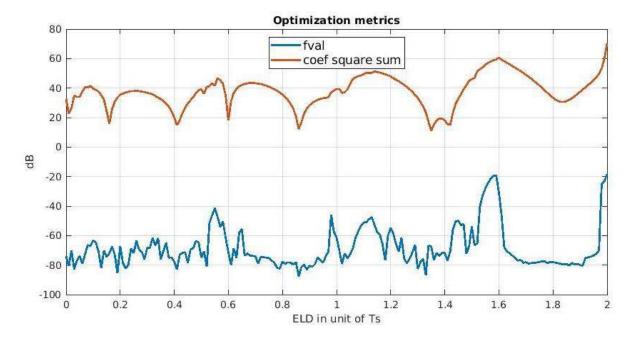

| Figure 4-43: Optimizer final value and feedback coefficients' square sum                                    |       |

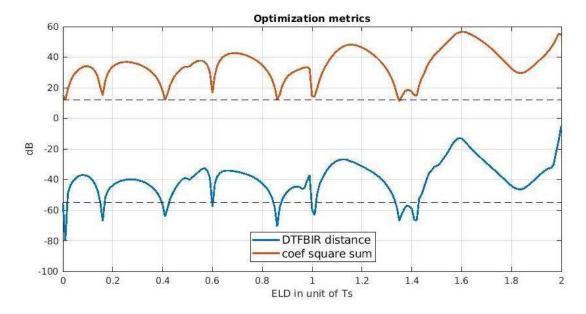

| Figure 4-44: DTFBIR distance to reference modulator and feedback coefficients' square sum vo                |       |

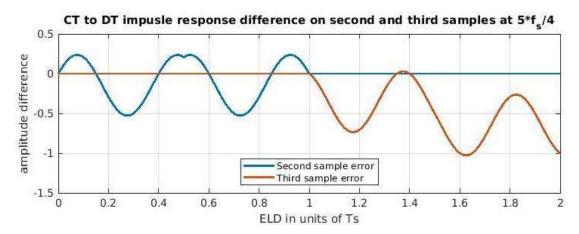

| Figure 4-45: Second and third feedback impulse response sample errors versus ELD for a $5 \times t$         |       |

| second order BPCTSDM                                                                                        | 151   |

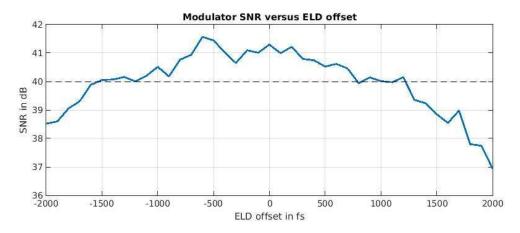

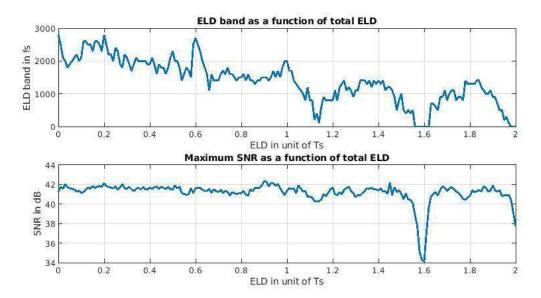

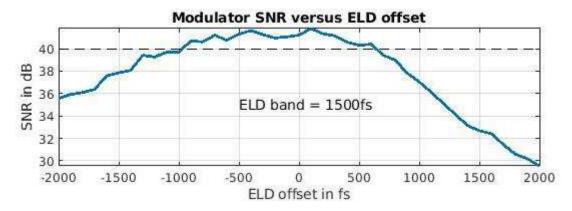

| Figure 4-46: Reference modulator SNR versus ELD offset from $-2ps$ to $2ps$ with a step of 10               | -     |

| Figure 4-47: Top) ELD band for modulators with per design ELD between $0 \times TS$ and $2 \times TS$ . Bot |       |

| Maximum SNR within the ELD band.                                                                            | 152   |

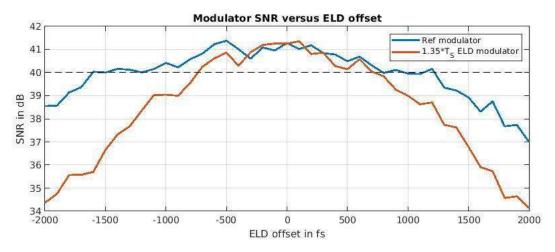

| Figure 4-48: SNR versus ELD offset from $-2ps$ to $2ps$ with a step of $100fs$ for the reference     | and   |

|------------------------------------------------------------------------------------------------------|-------|

| $1.35 \times TS$ ELD modulators                                                                      | 153   |

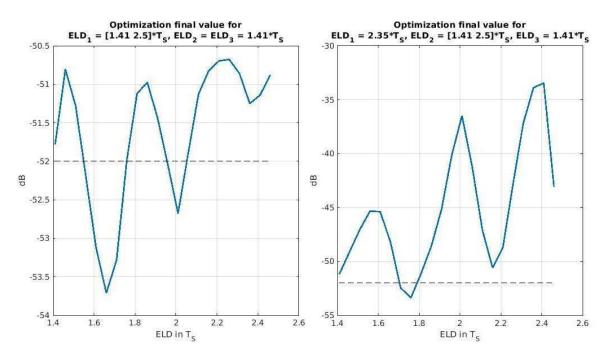

| Figure 4-49: ELD1 and ELD2 scan for optimization's first step                                        | . 154 |

| Figure 4-50: ELD robustness test on a modulator with individually optimized                          | . 154 |

| Figure 5-1: Modulators architecture                                                                  |       |

| Figure 5-2: a) Implementation principle schematic of c2. b) Transistor level schematic               | . 159 |

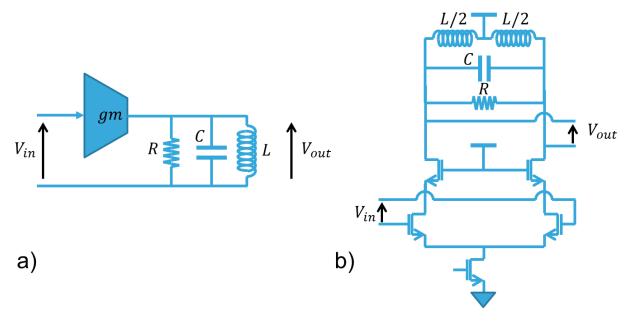

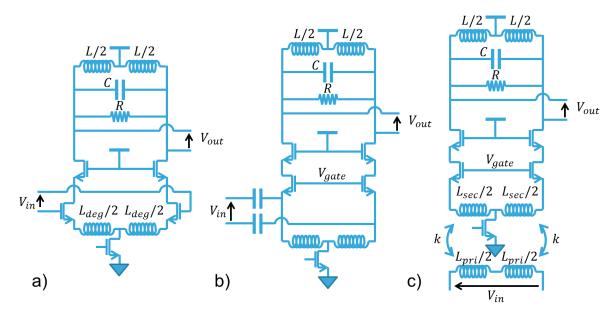

| Figure 5-3: a) Inductively degenerated common source topology. b) Common gate topology               | with  |

| capacitive coupling input signal feed. c) Common gate topology with inductive coupling input s       | ignal |

| feed                                                                                                 |       |

| Figure 5-4: gm-boosted common gate LNA with tranformer feed                                          |       |

| Figure 5-5: Simple implementation of a current steering DAC                                          |       |

| Figure 5-6: a) Classic current steering feedback DAC. b) Capacitively coupled Voltage feedback       |       |

|                                                                                                      |       |

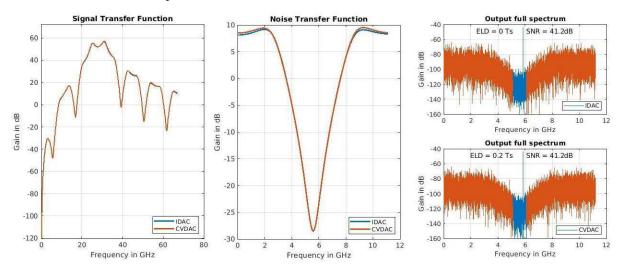

| Figure 5-7: Comparison between an IDAC and CVDAC modulator                                           |       |

| Figure 5-8: Comparison between an IDAC and CVDAC modulator after optimization                        |       |

| Figure 5-9: Feedback RZ Voltage DAC topology                                                         |       |

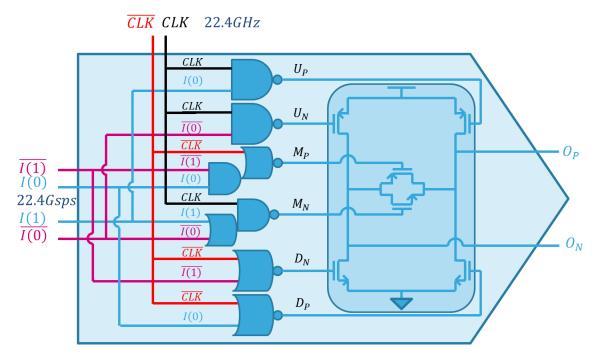

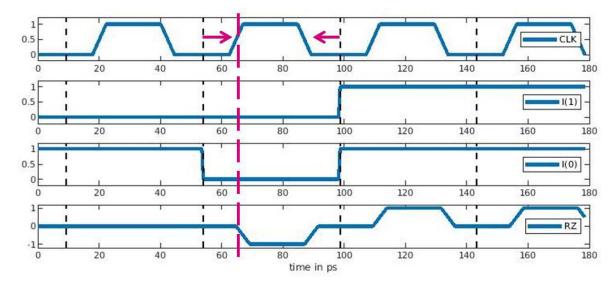

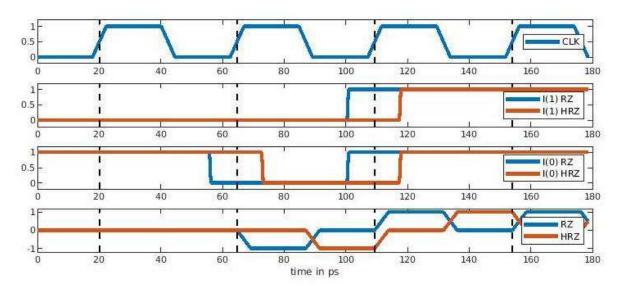

| Figure 5-10: RZ Voltage DAC chronograms                                                              |       |

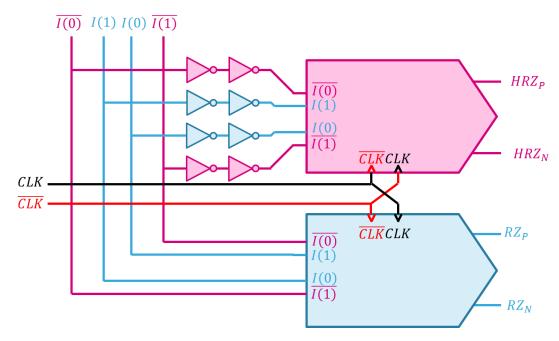

| Figure 5-11: RZ and HRZ Voltage DAC assembly                                                         |       |

| Figure 5-12: HRZ and RZ Voltage DAC assembly chronograms                                             |       |

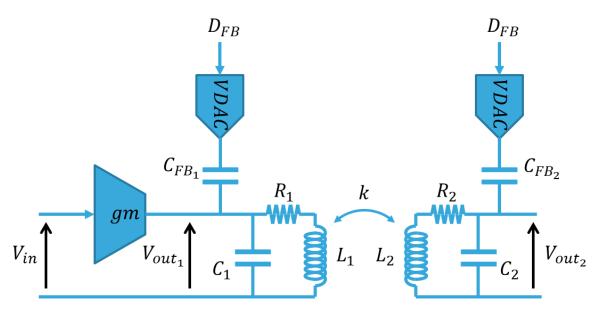

| Figure 5-13: Proposed Transformer based gm-LC resonator                                              |       |

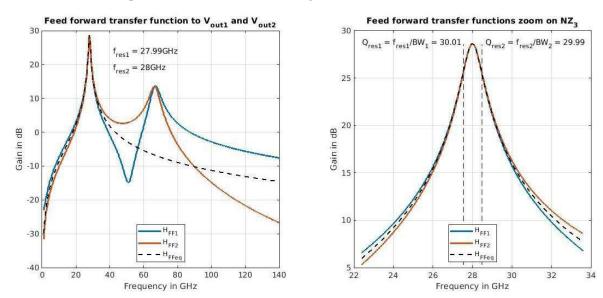

| Figure 5-14: Feedforward transfer functions of a transformer-based resonator                         |       |

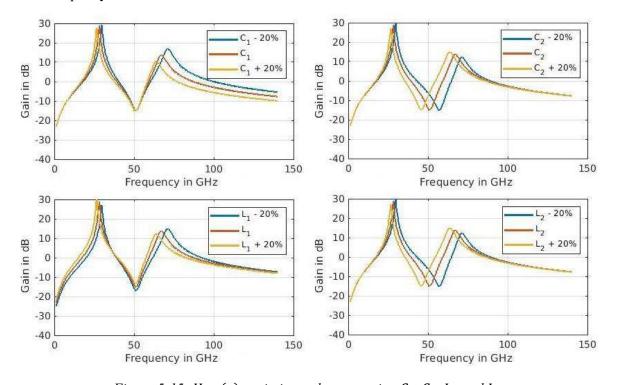

| Figure 5-15: <i>HFF1s</i> variations when sweeping <i>C</i> 1, <i>C</i> 2, <i>L</i> 1 and <i>L</i> 2 |       |

| Figure 5-16: <i>HFF2s</i> variations when sweeping <i>C</i> 1, <i>C</i> 2, <i>L</i> 1 and <i>L</i> 2 |       |

| Figure 5-17: Feedforward transfer functions variations when sweeping <i>k</i>                        |       |

| Figure 5-18: Feedforward transfer functions variations when sweeping the ratio $L2/L1$               |       |

| Figure 5-19: Feedforward transfer functions variations when sweeping C1, with $L1 = L2 = 400pH$      |       |

| adjusting C2 for a constant 28GHz resonating frequency                                               |       |

| Figure 5-20: C2, Q and fSR as a function of C1                                                       |       |

| Figure 5-21: Transformer based resonator feedforward and feedback transfer functions to the se       |       |

| output Vout2 and ideal parallel RLC resonator feedforward and feedback unit transfer functions.      |       |

| Figure 5-22: a) Digitally controllable unit capacitance. b) Equivalent circuit for on switch state   |       |

| Equivalent circuit for off switch state                                                              |       |

| Figure 5-23: a) Negative-gm circuit topology. b) Principle single ended equivalent                   |       |

| Figure 5-24: Time-interleaved quantizer principle schematic                                          |       |

| Figure 5-25: a) I and Q half rate clock generator b) True Single Phase Clock D-flip-flop topology    |       |

| Figure 5-26: a) Classic pulse extender schematic. b) Pulse extender chronograms. c) Proposed 1       | _     |

| extender schematic                                                                                   |       |

| Figure 5-27: Clock generator simulation results                                                      |       |

| Figure 5-28: Quantizer and latching comparator principle schematics                                  |       |

| Figure 5-29: Clocked comparator's topology                                                           |       |

| Figure 5-30: Clocked Comparator output chronogram                                                    |       |

| Figure 5-31: a) True Single Phase Clock D-flip-flop schematic. b) True Single Phase Clock D-flip     | _     |

| chronograms.                                                                                         |       |

| Figure 5-32: Simulation of the proposed latching comparator                                          |       |

| Figure 5-33: a) Output MUX topology. b) Simulation results                                           |       |

| Figure 5-34: Modulator's simplified implementation schematic                                         |       |

| Figure 5-35: a) Tunable delay cell topology. b) Static control DAC characteristic                    |       |

| Figure 5-36: Delay elements tuning range                                                             |       |

| Figure 5-37: Feedback DACs' differential outputs                                                     |       |

| Figure 5-38: Initial LC based modulator perforamnces                                                 | . 191 |

| $\sim { m _{XVi}} \sim$                                                                              |       |

| Figure 5-39: Feed forward analog path layout                                                       | 194   |

|----------------------------------------------------------------------------------------------------|-------|

| Figure 5-40: S11 parameter characterizing the input matching of the SDM                            | 195   |

| Figure 5-41: Signal Path transfer function from GSG input to comparator input                      | 196   |

| Figure 5-42: Left graphs, from top to bottom: First, second and third feedback transfer functions. | Right |

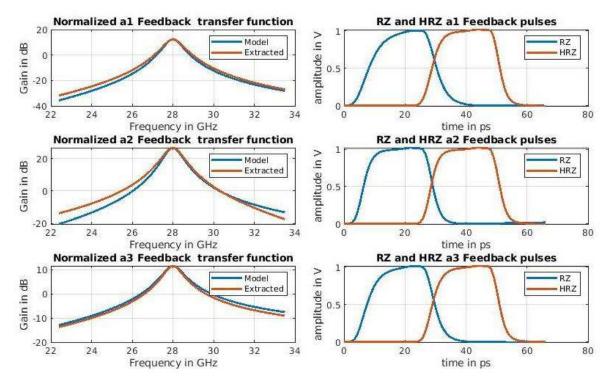

| graphs, from top to bottom: First, second and third feedback pulses for the RZ and HRZ DACs        | 196   |

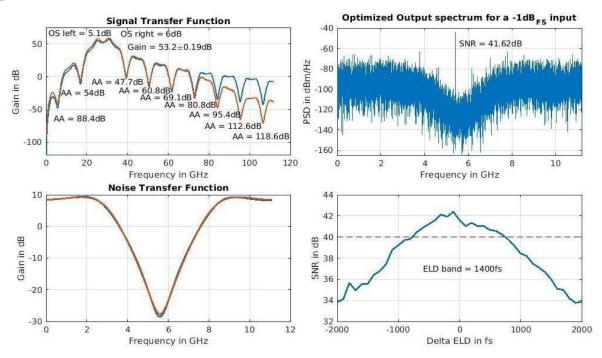

| Figure 5-43: Performance summary of the SDM final optimization                                     | 197   |

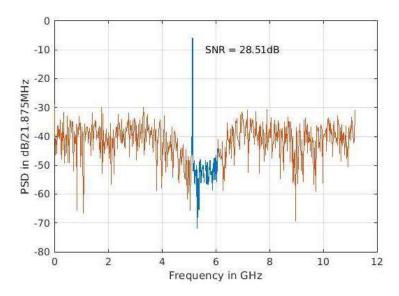

| Figure 5-44: Modulator output spectrum from transient post layout simulation                       | 198   |

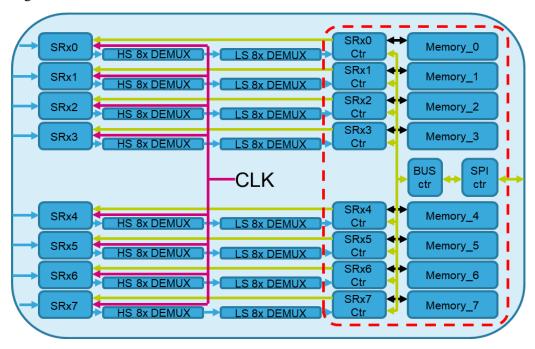

| Figure 5-45: Test chip top level block diagram                                                     | 201   |

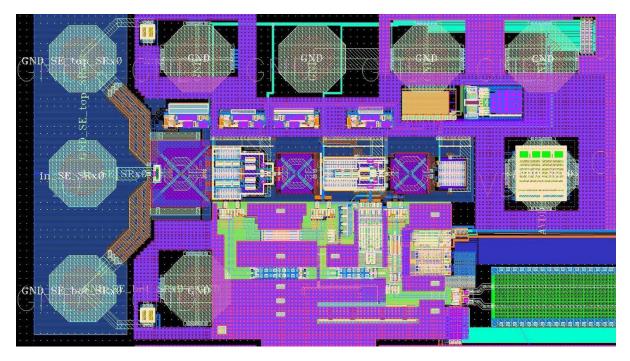

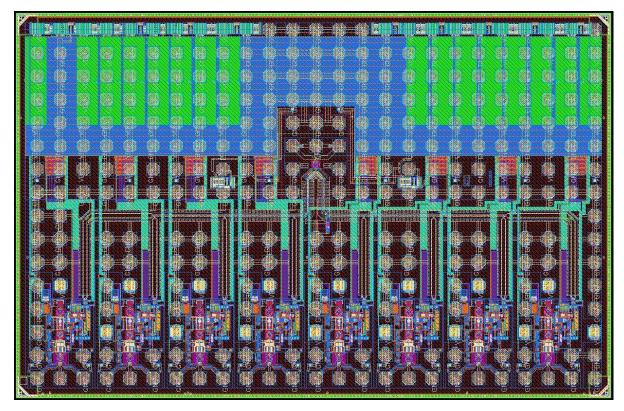

| Figure 5-46: Single Receiver's layout                                                              | 203   |

| Figure 5-47: Test chip layout                                                                      | 203   |

# **List of Tables**

| Table 2-1: 5G KPIs and System performances summary                                     | 47  |

|----------------------------------------------------------------------------------------|-----|

| Table 3-1: NF specifications of the SRx building blocks                                | 87  |

| Table 3-2: Linearity specifications of the SRx building blocks                         | 88  |

| Table 3-3: Building Blocks specifications summary                                      | 91  |

| Table 3-4: PLL state of the art performance summary                                    | 91  |

| Table 3-5: LNA state of the art performance summary                                    | 92  |

| Table 3-6: Mixer state of the art performance summary                                  | 92  |

| Table 3-7: Filter state of the art performance summary                                 | 93  |

| Table 3-8: ADC state of the art performance summary                                    | 93  |

| Table 4-1: Frequency and OSR for inputs in NZ 1 to 5                                   |     |

| Table 4-2: Updated NF budget                                                           | 139 |

| Table 5-1: Model parameters' values                                                    |     |

| Table 5-2: Model's parameters' values for Figure 5-21                                  | 175 |

| Table 5-3: Initial LC based modulator coefficients, ELD and resonators Q-factor values | 191 |

| Table 5-4: Initial Guess on resonators' total capacitance and feedback capcitances     | 192 |

| Table 5-5: State of the art comparison                                                 | 204 |

#### 1 CHAPTER I: INTRODUCTION

The history of wireless communication goes back to the end of the 19<sup>th</sup> century, with the pioneer work on wireless telegraphy from Guglielmo Marconi. This was made possible thanks to the understanding of the electromagnetism laws, theorized by James Clerk Maxwell in 1865, and experimentally confirmed by Heinrich Hertz in the 1880's. From that point on the field of wireless communication developed tirelessly until today and the current deployment of the 5<sup>th</sup> generation mobile network, going by the name of 5G.

The DNA of modern wireless communication is often tied to the year 1948. This year saw two major advances that are still the base for 5G. First is the publication by Claud Shannon of his funding article on information theory, which is the base to devise efficient and error free communication systems in a noisy environment. Second is the invention of the bipolar junction transistor by William Shockley, which allows to build more compact and power efficient transceivers.

While these two fields are still at the root of today's mobile systems, they have greatly evolved. Modern error correcting codes are nearly reaching Shannon's limit, and transistors' performances, as well as their integration, have improved by several orders of magnitude. It is now common to find chips with several billion transistors in a volume smaller than Shockley's original single transistor.

Like many fields, wireless communications were greatly developed under military impulse, before reaching our everyday life. They are now omnipresent in the modern society. This manuscript will focus on the use case consisting in providing a two-way communication link to a mobile user that can roam virtually anywhere. This has been achieved by deploying networks of fixed antennas, each of them covering an area called a cell. All the antennas form what is called a mobile network. Today, the fifth generation is being deployed. Each of them has one or more technical specificities which are often inherited by the following generations.

The first generation was based on an analog modulation of the signal and was designed to only carry the voice. Already, the covered areas were divided into cells, each of them covered by a single antenna, or Base Station (BS), connected to the landlines, thereby making a cellular network.

The second generation introduced a digital modulation of the signal, improving significantly on the communications' quality. It also allows for the transmission of small amount of other than voice data. This was used to create the Short Messaging System or SMS. This second generation, named Global System for Mobile communication (GSM), was the first mobile network to meet a commercial success.

The third-generation innovation was about handling users' multiple access. While previous generation were using a combination of Frequency Division Multiple Access (FDMA) and Time Division Multiple Access (TDMA), 3G used Code Division Multiple Access (CDMA) which allows for multiple users to communicate over the same frequency at the same time. It also improved the network capability to transmit larger amount of data. Its commercial success was not on par with its predecessor. In its early deployment, its improved ability for data transfer was virtually unused since no device could actually use it efficiently at the time. Once the smartphone revolution came in, its data rate proved to be insufficient, rapidly calling for the deployment of the next generation.

The fourth-generation network answered the call for higher data rate, introducing multiple innovations. First is a combination of a new modulation, the Orthogonal Frequency Division Multiplexing (OFDM) with an increase of the channel bandwidth up to 20MHz. OFDM Allows for a better bandwidth efficiency as well as being more robust to fast fading channels, making it a good solution for wider bandwidth and allowing the channel width increase. Second is the possibility to use carrier aggregation up to three channels for a maximum cumulated bandwidth of 60MHz. Finally, it also introduced Multiple Input Multiple Output (MIMO) communications with up to eight antennas on each side. In the

latest release of the standard all these improvements combined allows for a theoretical downlink data rate up to 300Mb/s, and 150Mb/s in uplink. In practice users rarely get rates above 100Mb/s, and typical rates are generally in the range from 1Mb/s to 10Mb/s. This discrepancy between theoretical and experienced data rates has two major reasons. Channels with a quality allowing for peak rate are extremely rare, if not inexistent, and the network is often near saturation of its capacity. This means that, even if the communication channel between a user and a BS is good enough for a 100Mb/s downlink communication, because the BS must serve multiple users at the same time it may not be able to provide this data rate without reducing the service to other users. Hence the limitation comes more from the network total throughput than the user link itself. This limitation comes from, either the BS capacity itself or from the backhaul link establishing the connection between the BS and the core network.

One of 5G goals is to provide a solution for this limitation. It will be shown that it is in fact much more ambitious than that and aims at becoming a standard for nearly all forms of wireless communications.

#### 1.1 5<sup>th</sup> Generation mobile network overview

5G has been marketed as a disruptive technology with a capacity increase of two orders of magnitude compared to 4G, with data rates up to 10Gb/s or even 20Gb/s delivered to a single user. While this is already an ambitious goal, it aims at providing much more than that. As already discuss one challenge coming along increased peak rate is increased network capacity. This is generally referred to as enhanced Mobile Broad Band (eMBB). Beyond that, 5G also aims at providing the framework for massive Machine Type Communication (mMTC), also called the Internet of Things (IoT), where a very large number of devices are connected to the network. The last goal for 5G is to provide an Ultra Reliable Low Latency Communication (URLLC) system for mission critical applications. There are also discussions about including Non-Terrestrial Networks (NTN) using satellites or any other kind of air born vehicles to create a network. It is not clear yet if it will or how it could be part of 5G, so it will not be discussed further but it shows the ambition of 5G to propose a common framework for as many wireless communication systems as possible.

#### 1.1.1 The three aspects of 5G: mMTC, URLLC, and eMBB

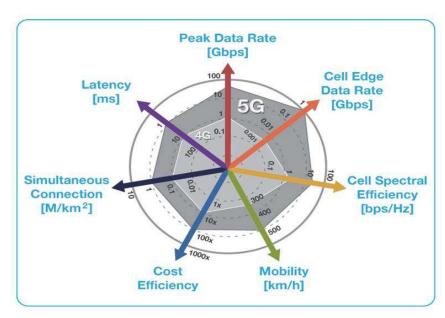

The evolution from 4G to 5G is often represented by the Key Performance Indicators (KPI) diagram in Figure 1-1.

Figure 1-1: 4G versus 5G Key Performance Indicators

While the data it contains are accurate this diagram must be properly read. While 5G's target is to outperform 4G by one or two orders of magnitude in all aspects, it is not aiming at doing so all at the same time. This is simply and purely forbidden by the laws of physics as they are currently known.

For example, peak data rate, cell edge data rate and cell spectral efficiency will be the playground of eMBB but in these conditions the number of simultaneous connections will never even be close to a million connections per square kilometer. This level of connection density is only aimed for mMTC, while eMBB targets a user density of ten thousand users per square kilometer, each of them experiencing an average data rate of 100Mb/s, far from the ten or twenty gigabit per second peak rate. Similarly, the one millisecond latency only applies to URLLC. The target latency for eMBB is around 10 milliseconds, on par with current 4G performances.

One of the challenges is to provide a framework that is compatible with all three cases. An overview of mMTC and URLLC will be presented here. eMBB will be the focus of this manuscript and will be further detailed in the subsequent sections. First, a short description of the radio frame structure together with some vocabulary is required.

#### 1.1.1.1 Radio frame structure

For a given cell, there is only a limited amount of time-frequency resource dedicated to 5G. The radio frame structure basically describes how this resource is organized, how it is divided into sub-pieces of resources. In general, it is desirable for all sub-resources to be orthogonal to each other. This means that a given piece of spectrum at a given time will belong to a single sub-resource. By doing so it is then possible to allocate these different sub-resources to different users. This gives rise to the broad category of Orthogonal Multiple Access (OMA). 5G uses an OFDM modulation, hence the specific multiple access technique used is Orthogonal Frequency Division Multiple Access (OFDMA).

A frame corresponds to a piece of spectrum, also called a channel, for a given duration. In 5G the frame duration is fix and equal to ten milliseconds, while the channel bandwidth is flexible.

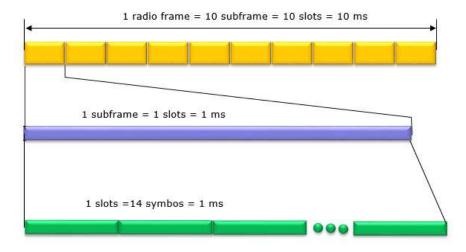

In the time domain the frame is divided into ten sub-frames of one millisecond. Each sub-frame is divided into a flexible number of slots, each of them being made of 14 symbols. There is a case where a slot can be made of only 12 symbols but, for the sake of brevity, it will not be discussed here. The number of slots per sub-frame then depends on the symbol duration. This will be defined when looking at the structure in the frequency domain. Figure 1-2 gives a visual representation of this frame slicing for the case of one slot per sub-frame.

Figure 1-2: Radio frame division and sub-division in the time domain

In the frequency domain the channel bandwidth is divided into sub-channels. This is characterized by the Sub Carrier Spacing (SCS) which is flexible. It is the SCS  $\Delta f$  that also defines the symbol duration  $T_{sym} = 1/\Delta f$ . The smallest SCS  $\Delta f$  is 15kHz and can be increased by powers of two up to 240kHz. Doubling the SCS halves the symbol duration and doubles the number of slots per sub-frame.

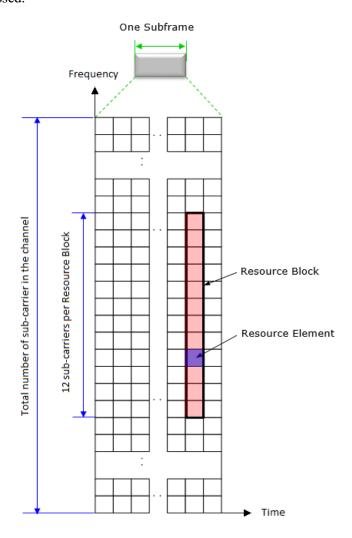

It is common to represent one sub-frame by the resource grid from Figure 1-3. One slot of one sub-carrier is called a Resource Element (RE). The REs are assembled by groups of twelve consecutive sub-carriers over the same slot to form a Resource Block (RB). RBs are the smallest resource that can be allocate to a user. From this basic description of the radio frame structure, the challenges of mMTC and URLLC can be discussed.

Figure 1-3: Representation of the resource grid

#### 1.1.1.2 mMTC overview

The purpose of mMTC is to provide a long range ultra-low power low data rate wireless link with a simultaneous connection density of one million devices per square kilometers or more. These objectives pose two challenges, to connect all these devices at the same time, and to do it with a high level of power efficiency. To address these challenges several new technologies are envisioned. The focus here will be only on the two major ones.

The challenge on connection density is linked to the RB size. Based on the following note a simple back of the envelope calculation can be made:

A resource block always contains the same number of symbols, the 14 symbols of a slot over 12 subcarriers for a total of 168 symbols. For larger subcarrier spacing, one RB will occupy a larger bandwidth over a smaller duration such that its surface in the time-frequency plane is constant. Hence the total number of available RBs is independent of the SCS, so only the case of the smallest SCS of 15kHz needs to be considered in the following argument.

Considering an RB bandwidth of 180kHz (12 sub-carriers of 15kHz) over a 1ms slot, then a 1GHz of bandwidth, for the duration of a radio frame, contains around 56000 RBs. This can cover an area of  $0.056km^2$  with the target one million devices per square kilometer connection density. It is equivalent to a cell radius of about 135m. It is clear here that, if the minimum payload size remains an RB, the desired user density or the long range targeted by mMTC cannot be reached. It would also be very spectrally inefficient since, for applications such as remote sensor reading, it is expected to transmit only few bits of information at a time. The numbers provided here only give the order of magnitude, but show that 5G's radio frame structure, regardless of its high flexibility, cannot accommodate mMTC efficiently.

One intuitive solution would be to reduce the RB size in order to have more of them available. But even reducing the RB to a single symbol would only allow a cell of 1.7km and would leave no room for eMBB and URLLC.

The envisioned solution is to use Non-Orthogonal Multiple Access (NOMA) [1-1] which allows for the BS to connect multiple devices using the same RB. The details on how this is achieved will not be explained here but in practice it is equivalent to build artificial flexibility on the RB size, hence creating enough of them to address all the devices.

The challenge on power efficiency partly comes from the digital processing. To be able to communicate properly, the data must be encoded before transmission. It is said that redundancy is added. This allows to recover some eventual transmission errors, ensuring proper communication. This will be studied more deeply into the next chapter. Current coding technologies such as turbo codes or Low-Density Parity Check (LDPC) allow to reach near optimal channel capacity but at the cost of relatively high digital processing. This digital processing capacity is not expected to be present on devices that aims at ten years' lifetime over a small battery. This will be solved by using a new code family called polar coding [1-2]. Under certain circumstances compatible with mMTC link requirements, these codes allow to reach optimal channel capacity at a much lower digital processing cost.

These two main technologies, together with the flexible radio frame structure, are the principal enablers for mMTC as envisioned for 5G

#### 1.1.1.3 URLLC

The purpose of URLLC is exactly as its name suggests, to provide an ultra-reliable low latency communication link with a moderate data rate. In more practical terms the target is to achieve a latency of one millisecond for the over the air interface with a BLock Error Rate (BLER) blow  $10^{-6}$ . In comparison the target BLER in 4G is 0.1.

To achieve these performances, the system physical layer has been optimized and the radio frame structure high flexibility allows the possibility to prioritize URLLC traffic over mMTC and eMBB. As for mMTC the details on how it is done will not be discussed here.

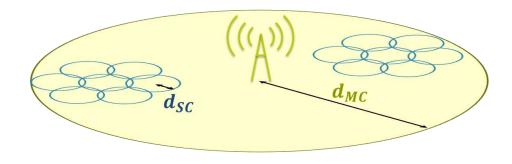

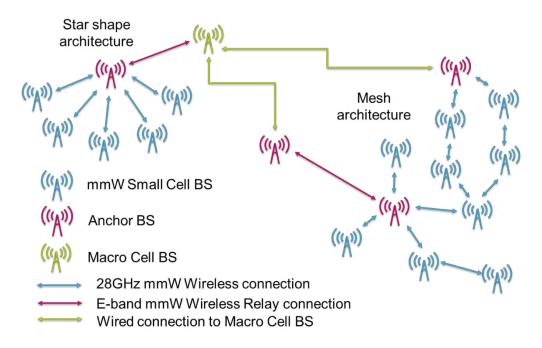

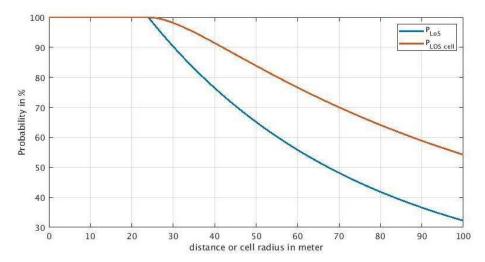

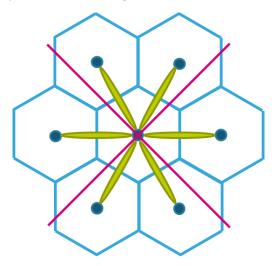

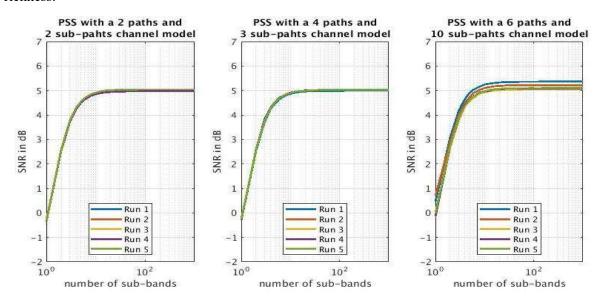

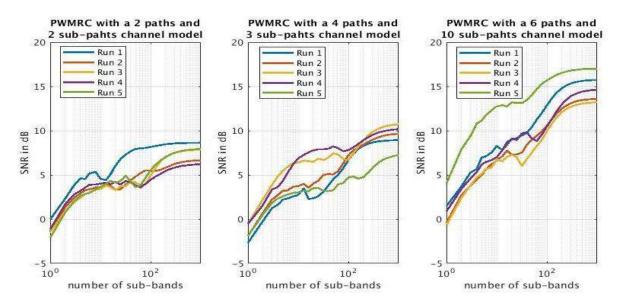

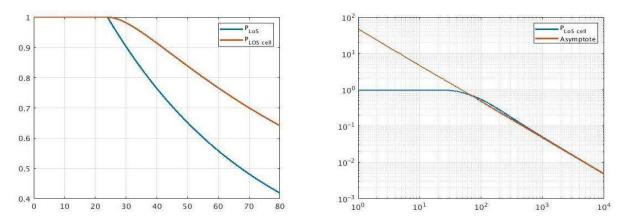

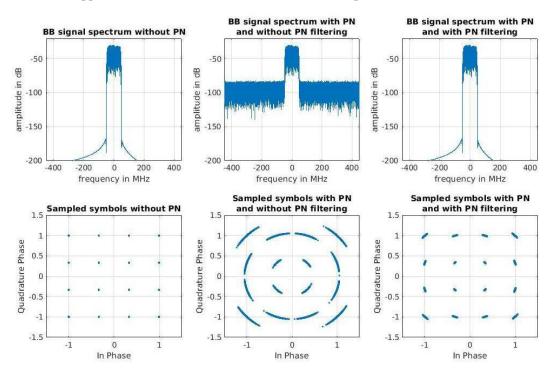

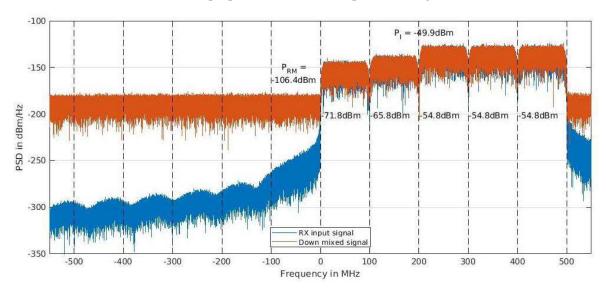

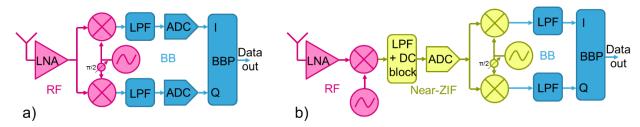

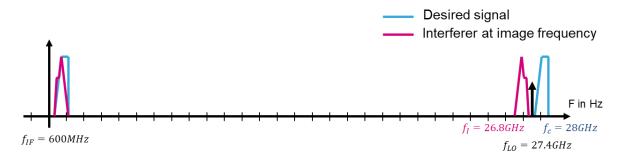

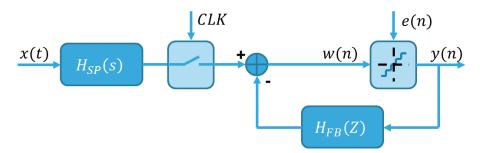

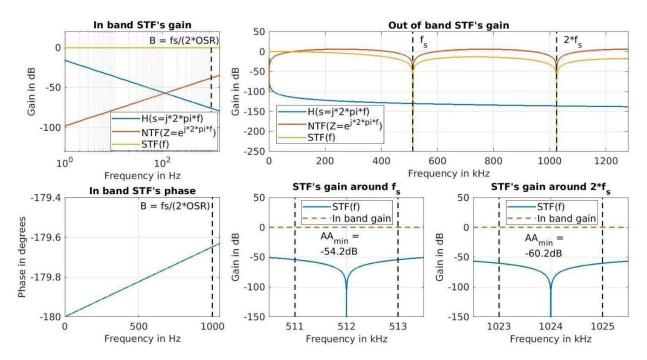

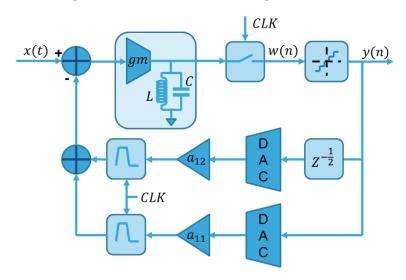

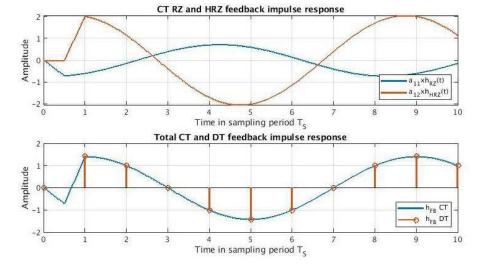

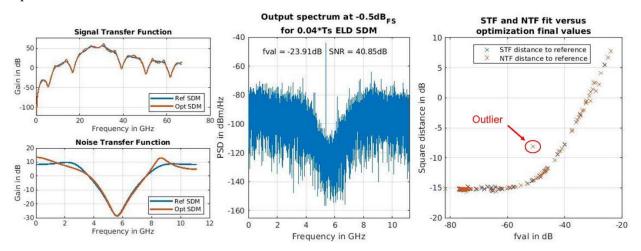

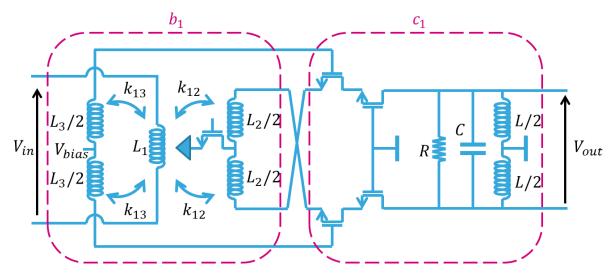

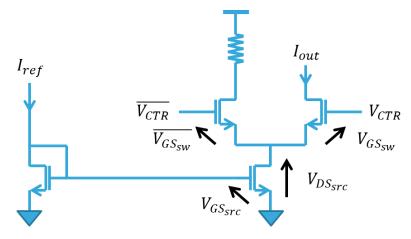

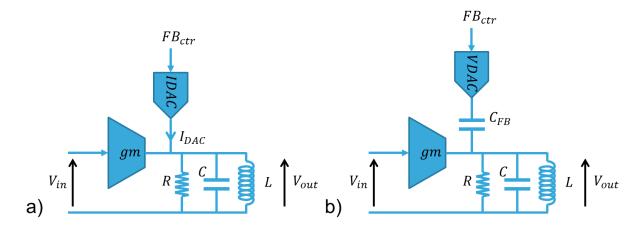

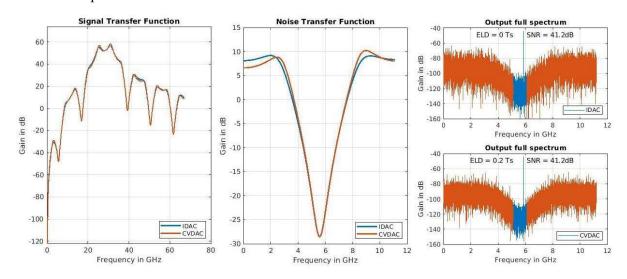

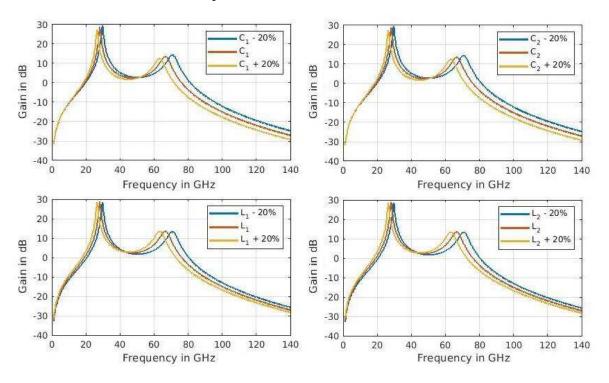

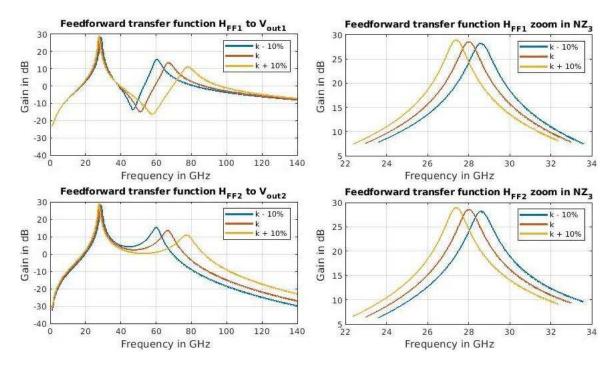

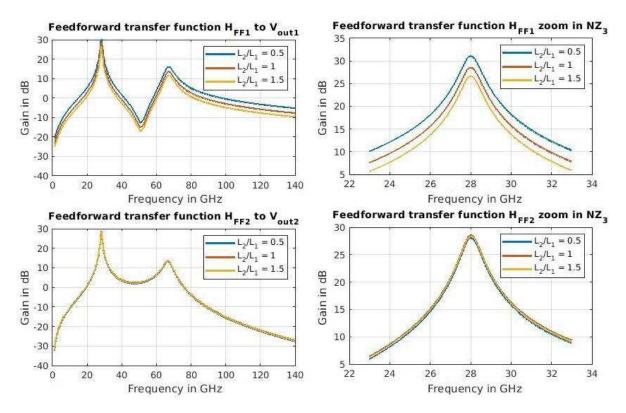

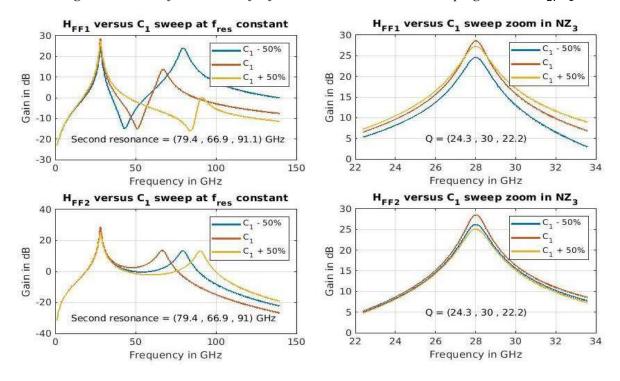

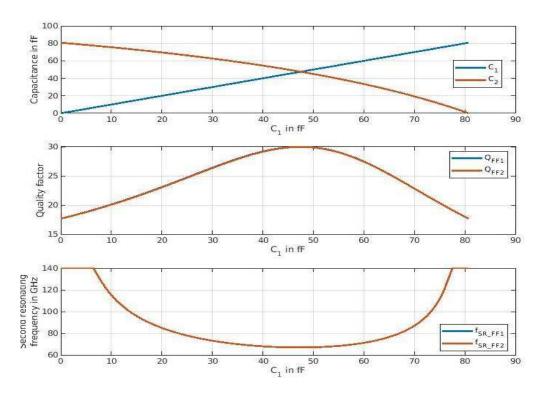

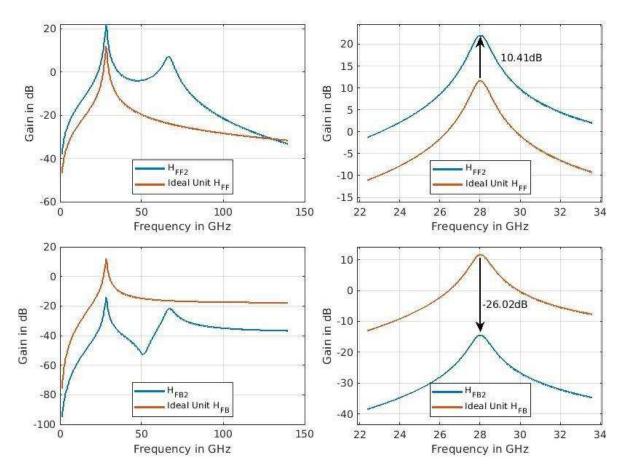

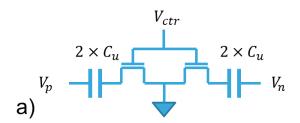

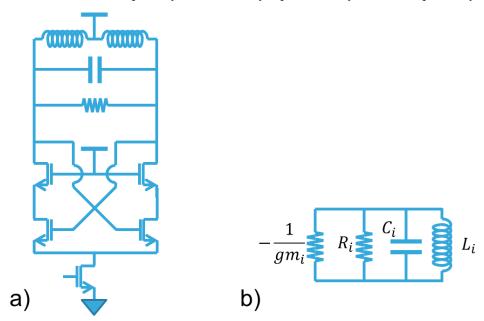

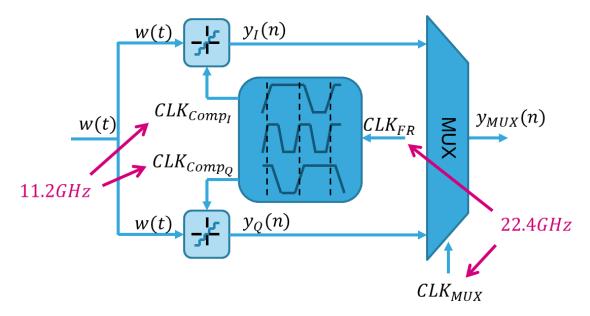

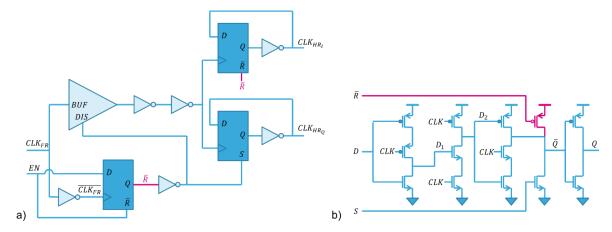

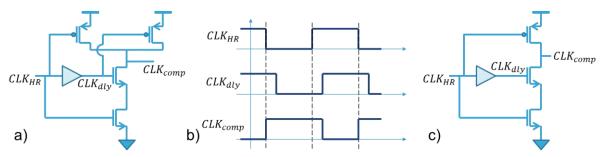

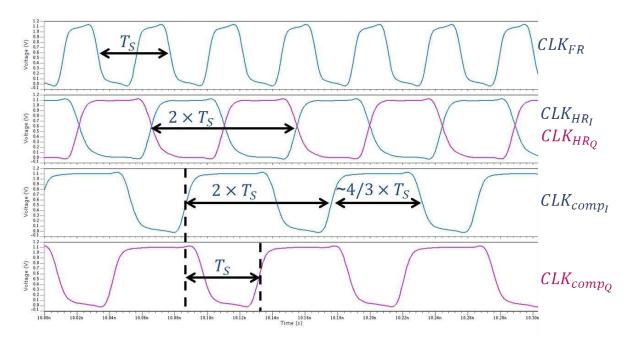

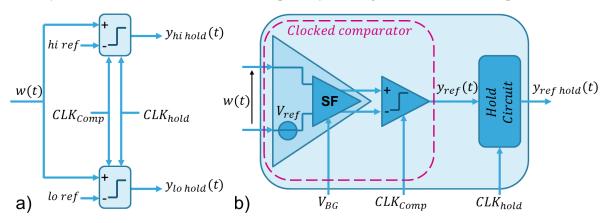

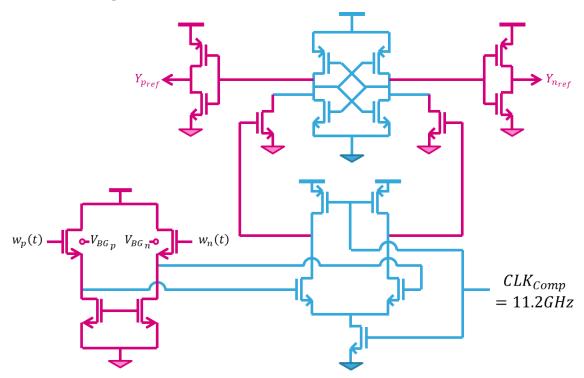

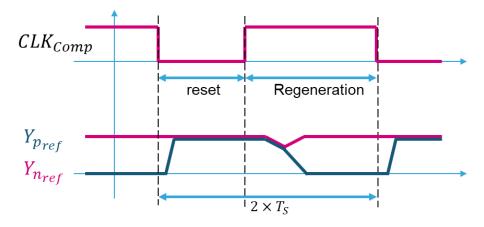

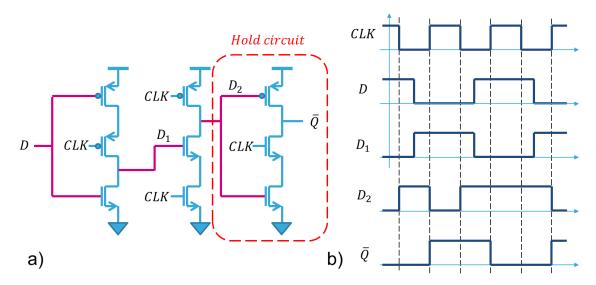

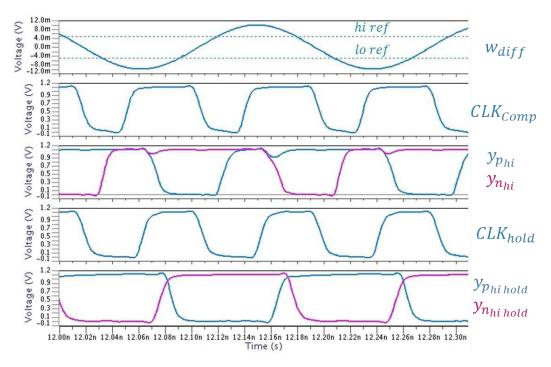

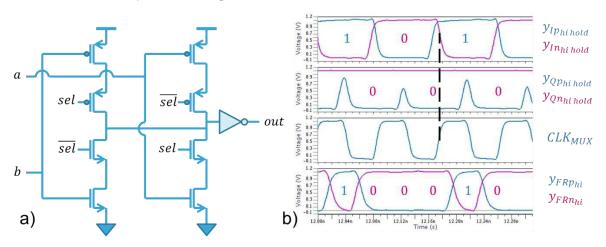

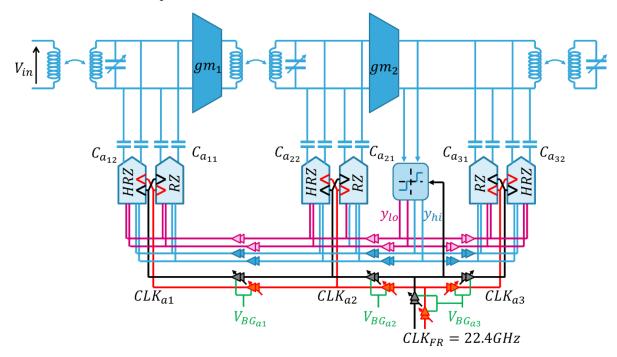

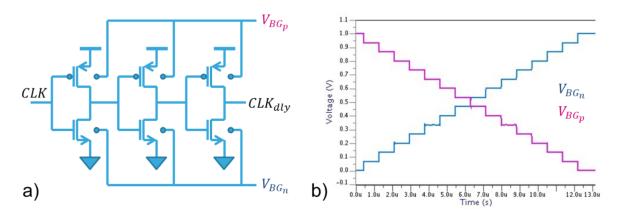

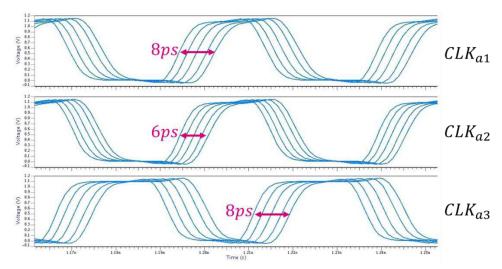

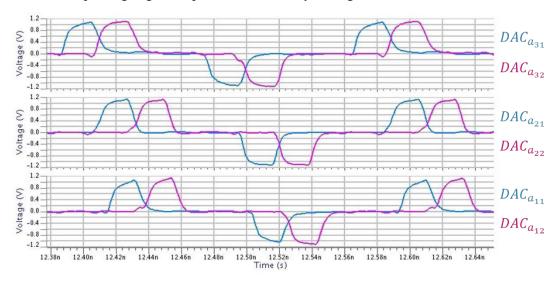

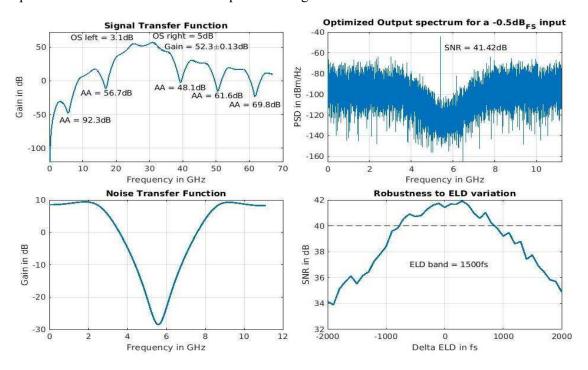

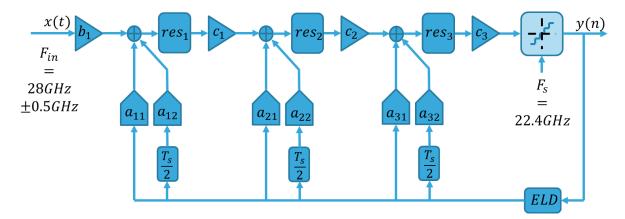

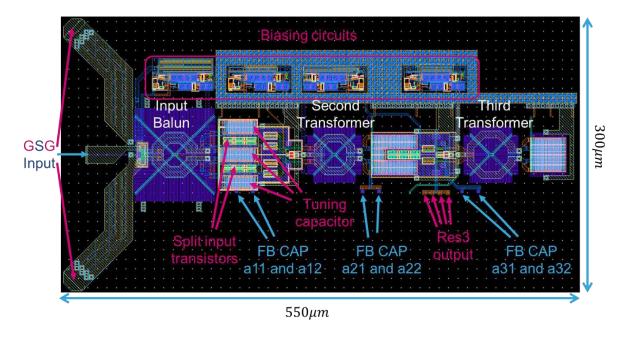

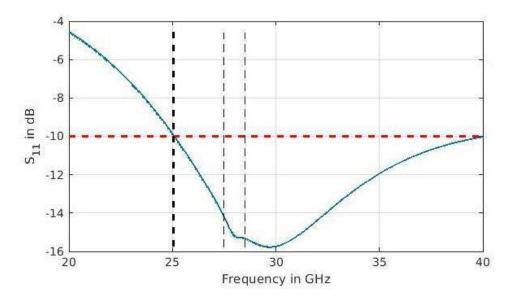

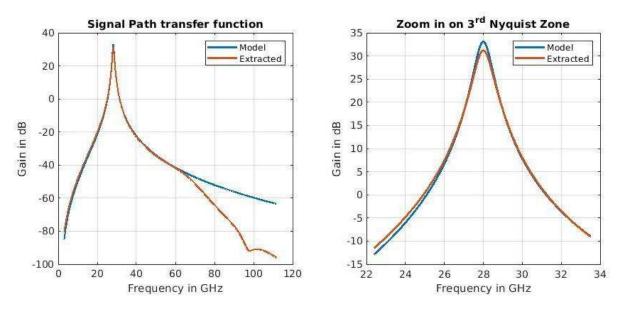

#### 1.1.2 eMBB: Foreseen technologies