# Neuromorphic algorithms and hardware for event-based processing

Gregor Lenz

#### ▶ To cite this version:

Gregor Lenz. Neuromorphic algorithms and hardware for event-based processing. Robotics [cs.RO]. Sorbonne Université, 2021. English. NNT: 2021SORUS108. tel-03474197

### HAL Id: tel-03474197 https://theses.hal.science/tel-03474197

Submitted on 10 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

Spécialité : Ingénierie Neuromorphique

École doctorale nº391: Sciences mécaniques, acoustique, électronique et robotique

Sujet de la thèse:

## Neuromorphic Algorithms and Hardware for Event-based Processing

réalisée

à l'Institut de la Vision - Équipe vision et calcul naturel

sous la direction de Sio-Hoi Ieng

présentée par

### Gregor Lenz

pour obtenir le grade de :

#### DOCTEUR DE SORBONNE UNIVERSITÉ

soutenue le 6 juillet 2021

devant le jury composé de :

Pr. Alejandro Linares-Barranco Rapporteur Pr. Sylvain Saïghi Rapporteur Pr. Bruno Gas Examinateur

Dr. Sio-Hoi Ieng Directeur de thèse

## Neuromorphic Algorithms and Hardware for Event-based Processing

**Abstract**: The demand for computing power steadily increases to enable new and more intelligent functionalities in our current technology. The combined computing power of mobile systems such as phones, drones, autonomous vehicles and embedded systems increases rapidly, but each system has a limited power budget. Efficient computation is thus of utmost importance. For the past decades we have relied on the growing amount of transistors per unit area to keep up with computing demand while keeping power consumption in check, but this trend is declining as transistor sizes are reaching physical limits. While architecture improvements stagnate, we find ourselves in the early stages of creating intelligent systems, which raises the question how current system can scale and which makes the exploration of alternative computing principles worth wile. This thesis examines the role of new bio-inspired computation paradigms for low-power computation, to drive a future generation of intelligent systems. Neuromorphic computing is an emerging interdisciplinary field that looks at biological systems such as the retina or the brain for inspiration on how to compute efficiently. From that it is possible to create sensors, algorithms and hardware that process information much closer to how the biological model works than current conventional computer architecture. We examine how neuromorphic cameras, algorithms and hardware can gradually replace conventional components to make the system overall use less power. We approach the issue through the lens of efficiency, and propose an event-based face detection algorithm, a framework that brings event-based computer vision to mobile devices with optimised hardware and methods based on precise timing for spiking neural networks on neuromorphic hardware. In this attempt we bring technology into being that starts to resemble the organic counterpart, to show the capabilities of brain-inspired computing.

**Keywords**: neuromorphic computing, event-based processing, non-von neumann computing, low-power computer vision, neuromorphic hardware, spiking neural networks

### Algorithmes et Architectures Matérielles Neuromorphiques pour le Calcul Évènementiel

Résumé: La demande en puissance de calcul augmente régulièrement pour permettre de nouvelles fonctionnalités plus intelligentes au vu de la technologie actuelle. La puissance de calcul disponible des systèmes mobiles tels que les téléphones, les drones, les véhicules autonomes et les systèmes embarqués augmente rapidement, mais chaque système a un budget limité. Le calcul efficace est donc de la plus haute importance. Au cours des dernières décennies, nous nous sommes appuyés sur la densité croissante de transistors integrés dans un processeur, pour répondre à la demande en puissance de calcul tout en maîtrisant la consommation d'énergie, mais cette tendance diminue à mesure que les tailles des transistors atteignent leurs limites physiques. Alors que les améliorations de l'architecture stagnent, nous nous trouvons dans les premières étapes de la création de systèmes intelligents, ce qui rend l'exploration de principes de calcul alternatifs indispensable. Cette thèse examine le rôle des nouveaux paradigmes de calcul bio-inspirés permettant le calcul à faible coût indispensable à la conception de la future génération de systèmes intelligents. Le calcul neuromorphique est un domaine interdisciplinaire émergent qui s'inspire des systèmes biologiques tels que la rétine ou le cerveau pour calculer efficacement. À partir de là, il est possible de créer des capteurs, des algorithmes et du matériel qui traitent les informations de façon bio-inspirée. Nous examinons comment les caméras neuromorphiques, les algorithmes et ainsi que le matériel peuvent remplacer progressivement les composants conventionnels pour arriver à un système moins gourmand en énergie. Nous abordons le problème à travers le prisme de l'efficacité et proposons un algorithme bio-inspiré de détection de visage, puis un cadriciel permettant de développer des algorithmes neuromorphiques sur des smartphones. Enfin nous proposons de porter des méthodes basées sur la précision temporelle dans les réseaux de neurones impulsionnels sur du matériel neuromorphique. Avec cette tentative, nous apportons une technologie qui commence à ressembler à la contrepartie organique, pour montrer les capacités de l'informatique inspirée du cerveau.

Mots clés : calcul neuromorphique, calcul évènementiel, vision par ordinateur à faible puissance, matériel neuromorphique, efficacité énergétique, réseaux de neurones impulsionnels

## Acknowledgments

I would like to thank the many people who have helped this thesis to see the light of the day. I would like to express my gratitude:

To Ryad for showing me how to walk off the beaten path and the fact that he give me a chance to prove myself.

To Sio for making sure that I do things the right way.

To Serge for helping me out in a difficult situation.

To Alexandre for his way to explain things in detail, stimulating discussions and writing great software that made a lot of my work possible.

To Lena, who is amazing at what she does and incredibly humble at the same time. I can learn a lot from you.

To Gerhard and Vera who have always supported me, no matter what path I chose.

To Ozan, Jose, Carlos, Jorge and Jonathan, from whom I learned so much over the years. I'm lucky to be able to call you my friends and I cannot wait for the next time we meet!

To *les loulous*, with whom I enjoyed exploring the beautiful city of Paris and its hidden corners!

To Marco and Dounia, with whom I had really good times in- and outside the lab. I miss you!

To Clemi for an amazing friendship and bond. Many more years to come!

To my catamaran sailing gym buddy, Iftar host and good friend Omar, who helped me keep my sanity and without whom I probably couldn't have completed this manuscript.

To Ira Bunny, who has supported me with all her heart, whom I admire deeply and whose love I cherish.

## List of contributions

### **Journals**

- Lenz G, Ieng SH and Benosman R. High Speed Event-based Face Detection and Tracking Using the Dynamics of Eye Blinks, Frontiers of Neuroscience 2020 [1].

- Lenz G, Oubari O, Orchard G and Ieng SH. Neural Computation Using Precise Timing on Loihi, in preparation 2021.

- Lenz G and Ieng SH. A Framework for Event-based Computer Vision on a Mobile Device, in preparation 2021.

- Oubari O, Exarchakis G, Lenz G, Benosman R and Ieng SH. Efficient Spatiotemporal Feature Clustering for Large Event-based Datasets, submitted 2021.

### **Conferences**

- Maro JM, Lenz G, Reeves C and Benosman R. Event-based Visual Gesture Recognition with Background Suppression running on a smart-phone, 14th ICAG 2019 [2].

- Haessig G, Lesta DG, Lenz G, Benosman R and Dudek P. A Mixed-Signal Spatio-Temporal Signal Classifier for On-Sensor Spike Sorting, ISCAS 2020 [3].

#### **Awards**

14th IEEE International Conference on Automatic Face & Gesture Recognition Best Demo Award, 2019.

### Open source software

- Frog: An Android framework for event-based vision.

- Loris: Python library to handle files from neuromorphic cameras.

- Tonic: Event-based datasets and transformations based on PyTorch.

- Quartz: ANN to SNN conversion using temporal coding.

## **C**ontents

| 1 | Intr | roducti | ion                                             | 1  |

|---|------|---------|-------------------------------------------------|----|

|   | 1.1  | Motiva  | ation and Objectives                            | 4  |

|   | 1.2  | Rethir  | nking the Way our Cameras See                   | 5  |

|   |      | 1.2.1   | Taking Inspiration from the Human Visual System | 6  |

|   |      | 1.2.2   | A Paradigm Shift in Signal Acquisition          | 7  |

|   |      | 1.2.3   | A Novel Sensor for Machine Vision               | 9  |

|   | 1.3  | Event-  | -based Computer Vision and Applications         | 10 |

|   |      | 1.3.1   | A Temporal Component to Understand Visual Input | 10 |

|   |      | 1.3.2   | The Era of Deep Learning                        | 11 |

|   |      | 1.3.3   | Event-based Processing                          | 12 |

|   | 1.4  | Spikin  | g Neural Networks                               | 13 |

|   |      | 1.4.1   | Sparse Data Representations                     | 13 |

|   |      | 1.4.2   | Training Spiking Neural Networks                | 15 |

|   | 1.5  | Low-p   | ower Hardware for Mobile Systems                | 17 |

|   |      | 1.5.1   | Neuromorphic Hardware                           | 18 |

|   |      | 1.5.2   | Hardware Benchmarking and Scalability           | 19 |

|   | 1.6  | Thesis  | Outline                                         | 20 |

| 2 | Eve  | ent-bas | ed Processing: Face Detection and Tracking      | 23 |

|   | 2.1  | Introd  | uction                                          | 24 |

|   |      | 2.1.1   | ATIS                                            | 24 |

|   |      | 2.1.2   | Face Detection                                  | 25 |

|   |      | 2.1.3   | Human Eye Blinks                                | 26 |

|   | 2.2  | Metho   | ods                                             | 27 |

|   |      | 2.2.1   | Temporal Signature of an Eye Blink              | 27 |

|   |      | 2.2.2   | Gaussian Tracker                                | 30 |

|   |      | 2.2.3   | Global Algorithm                                | 31 |

|   | 2.3  | Exper   | iments and Results                              | 31 |

|   |      | 2.3.1   | Indoor and Outdoor Face Detection               | 32 |

|   |      | 2.3.2   | Face Scale Changes                              | 33 |

|   |      | 2.3.3   | Multiple Faces Detection                        | 34 |

|   |      | 2.3.4   | Pose Variation Sequences                        | 34 |

|   |      | 2.3.5   | Summary                                         | 36 |

|   | 2.4  | Discus  | ssion                                           | 37 |

viii *CONTENTS*

| 3            | $\mathbf{A}$ N | Mobile  | Framework for Event-based Computer Vision                       | <b>39</b> |

|--------------|----------------|---------|-----------------------------------------------------------------|-----------|

|              | 3.1            | Introd  | luction                                                         | 39        |

|              | 3.2            | Mobile  | e Device and Event Camera                                       | 42        |

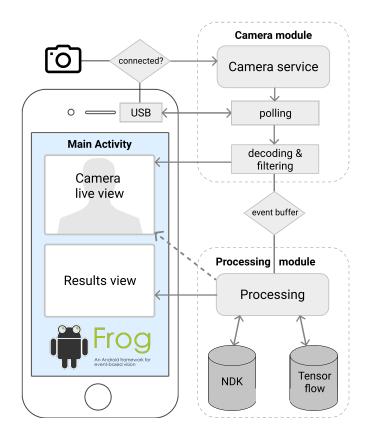

|              | 3.3            | Andro   | oid Application Framework                                       | 44        |

|              |                | 3.3.1   | Main Activity                                                   | 45        |

|              |                | 3.3.2   | Camera Module and Event Buffer                                  | 45        |

|              |                | 3.3.3   | Processing Module                                               | 46        |

|              | 3.4            | Perfor  | rmance Measurement Methods                                      | 47        |

|              |                | 3.4.1   | Camera Latency                                                  | 47        |

|              |                | 3.4.2   | Buffering Latency                                               | 47        |

|              |                | 3.4.3   | Execution Latency                                               | 47        |

|              | 3.5            | Exper   | iments and Results                                              | 48        |

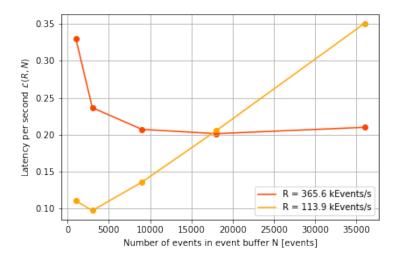

|              |                | 3.5.1   | Measuring Throughput of Camera Module and Event Buffer Latency  | y 48      |

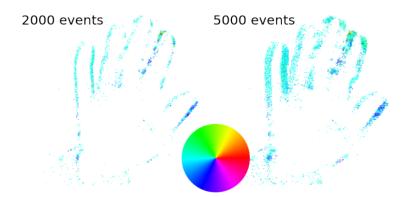

|              |                | 3.5.2   | Aperture Robust Event-based Optical Flow                        | 49        |

|              |                | 3.5.3   | Event-by-event Gesture Recognition                              | 50        |

|              |                | 3.5.4   | Leveraging Pre-trained Neural Networks for Image Reconstruction | 53        |

|              | 3.6            | Discus  | ssion                                                           | 55        |

| 4            | Neı            | ıral Co | omputation on Loihi                                             | 57        |

|              | 4.1            |         | luction                                                         | 58        |

|              | 4.2            | STICE   | K                                                               | 59        |

|              | 4.3            | Loihi   |                                                                 | 60        |

|              |                | 4.3.1   | Hardware                                                        | 60        |

|              |                | 4.3.2   | Neuron Models Implement STICK Synapses                          | 62        |

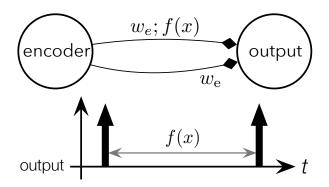

|              |                | 4.3.3   | Value Encoding Using Delays                                     | 63        |

|              | 4.4            | Comp    | osing Networks For Computation Using STICK                      | 64        |

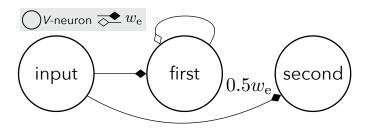

|              |                | 4.4.1   | Storing Values                                                  | 64        |

|              |                | 4.4.2   | Branching Operations Minimum and Maximum                        | 65        |

|              |                | 4.4.3   | Linear Operations                                               | 67        |

|              |                | 4.4.4   | Nonlinear Operations                                            | 68        |

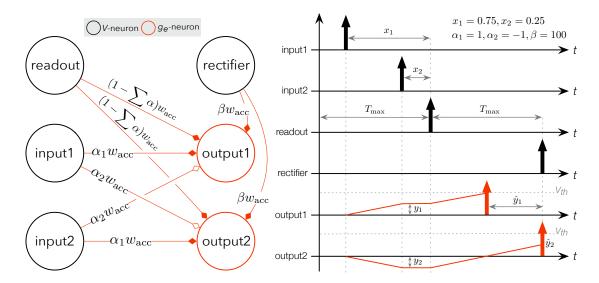

|              |                | 4.4.5   | ANN-SNN Network Conversion                                      | 70        |

|              | 4.5            | Exper   | iments and Results                                              | 72        |

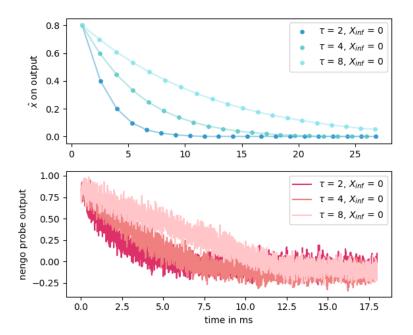

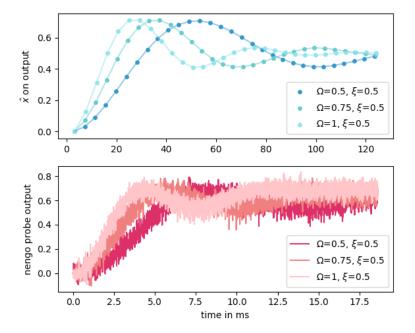

|              |                | 4.5.1   | Computing Dynamic Systems                                       | 73        |

|              |                | 4.5.2   | Converting Pre-trained ANNs                                     | 77        |

|              | 4.6            | _       | ssion                                                           | 80        |

| 5            | Cor            | nclusio | n                                                               | 83        |

|              |                |         |                                                                 |           |

| $\mathbf{A}$ | Aut            | hored   | Software Packages                                               | 91        |

| A.1 | Loris . | <br> |  |  |  | <br> |  |  |  |  |  |  | <br> |  |  |  |

|-----|---------|------|--|--|--|------|--|--|--|--|--|--|------|--|--|--|

|     | Tonic . |      |  |  |  |      |  |  |  |  |  |  |      |  |  |  |

| A.3 | Frog .  | <br> |  |  |  | <br> |  |  |  |  |  |  | <br> |  |  |  |

| A.4 | Quartz  | <br> |  |  |  | <br> |  |  |  |  |  |  | <br> |  |  |  |

## **Acronyms**

**AI** Artificial Intelligence. 2, 4, 5, 17, 18, 20

**ANN** Artificial Neural Network. 12, 14–16, 58, 70–72, 77, 78, 81, 88, 96, 97

**ATIS** Asynchronous Time-based Image Sensor. 10, 13, 24, 25, 41–43, 91, 95

CF Correlation Filter. 32, 36, 37

CNN Convolutional Neural Network. 10, 32, 96

CPU Central Processing Unit. 3, 5, 12, 17, 32, 38, 45, 48, 55, 79, 80, 86

**DAVIS** Dynamic and Active pixel Vision Sensor. 10, 12

**DVS** Dynamic Vision Sensor. 10, 13, 24, 42, 91

EDP Energy Delay Product. 78–80, 82, 88

FPGA Field-Programmable Gate Array. 12, 42, 45, 78

fps frames per second. 32, 38

FRCNN Faster Region Based Convolutional Neural Network. 32, 36–38

**GPU** Graphics Processing Unit. 2, 4, 10, 12, 15, 17, 18, 25, 38, 55–57, 77, 80, 83, 85, 86, 88, 90, 96

**HATS** Histogram of Averaged Time Surfaces. 38

**HOTS** Hierarchy of Time Surfaces. 12, 38, 51, 52

IoT Internet of Things. 10, 18, 89

MIPI Mobile Industry Processor Interface. 56, 95

**NDK** Native Development Kit. 41, 46, 52, 54, 55

NEF Neural Engineering Framework. 73, 80, 86

xii Acronyms

RISC Reduced Instruction Set Computer. 17, 39, 89, 90

RNN Recurrent Neural Network. 15, 20, 88

$\mathbf{SNN} \ \, \text{Spiking Neural Network.} \ \, 13-16, \, 18, \, 21, \, 57, \, 58, \, 70-72, \, 77-79, \, 81, \, 82, \, 86-88, \, 96$

SoC System on Chip. 17

SSD Single Shot Detector. 32, 36–38

**STDP** Spike-Time Dependent Plasticity. 15, 16

STICK Spike Time Computation Kernel. 57, 59–62, 70, 72, 74, 77, 79, 80, 82, 87

**TPU** Tensor Processing Unit. 18, 25

**TTFS** Time To First Spike. 71, 72, 78, 81, 88

$\mathbf{USB}\,$  Universal Serial Bus. 10, 41–48, 56, 85, 95

**VJ** Viola-Jones. 32, 36–38

## **List of Figures**

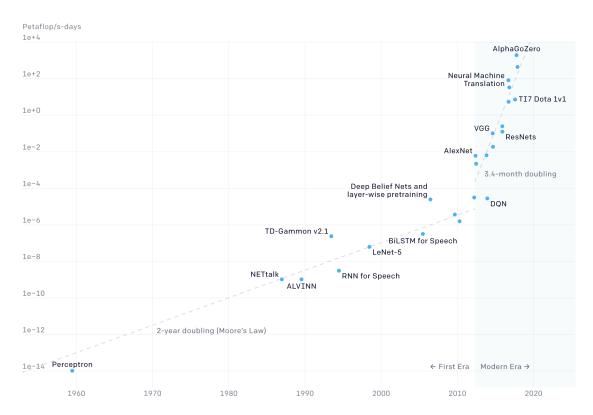

| 1.1  | Number of operations needed to train machine learning models                             | 2  |

|------|------------------------------------------------------------------------------------------|----|

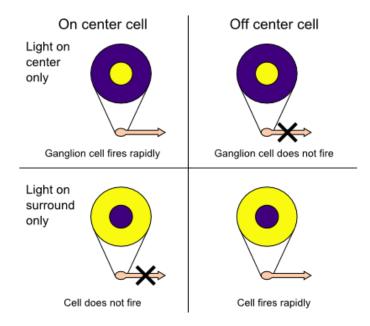

| 1.2  | Image blur in frames when using conventional cameras                                     | 6  |

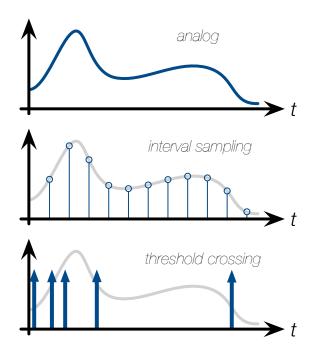

| 1.3  | Center-surround receptive fields in the mammalian retina                                 | 7  |

| 1.4  | Different sampling theorems: digital and level crossing sampling                         | 8  |

| 1.5  | Event stream visualisation                                                               | 9  |

| 1.6  | Point cloud that encodes an object needs temporal components                             | 11 |

| 1.7  | Time surface features and their generation                                               | 13 |

| 1.8  | Neuron models in an ANN and in an SNN                                                    | 14 |

| 1.9  | Commonly used derivatives as a replacement for spike activation                          | 16 |

| 1.10 | Comparison of two System on Chips from 2018 and 2020                                     | 17 |

| 1.11 | Energy and latency comparison of neuromorphic hardware to other archi-                   |    |

|      | tectures                                                                                 | 20 |

| 2.1  | Event-based face detection exemplary results                                             | 23 |

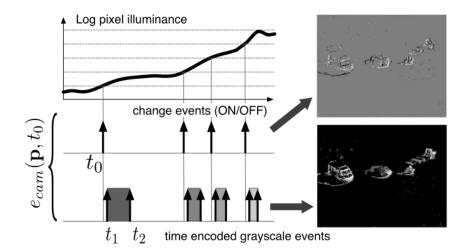

| 2.2  | ATIS event camera working principle for grey-level encoding                              | 25 |

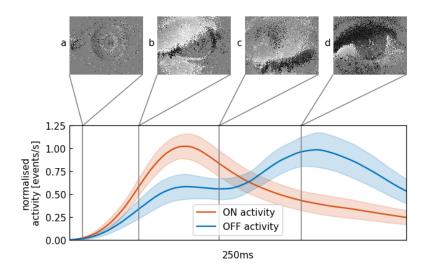

| 2.3  | Activity profile for a human blink generated from events                                 | 26 |

| 2.4  | Activity of ON and OFF events when subject is blinking                                   | 27 |

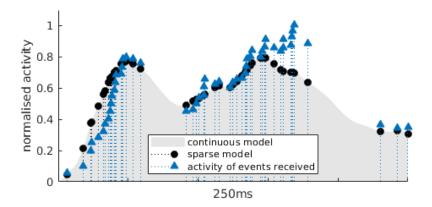

| 2.5  | Sparse cross correlation method                                                          | 29 |

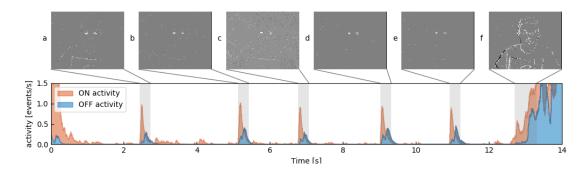

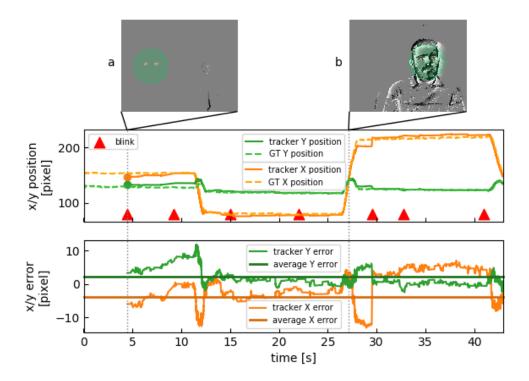

| 2.6  | Face tracking recording for one subject                                                  | 33 |

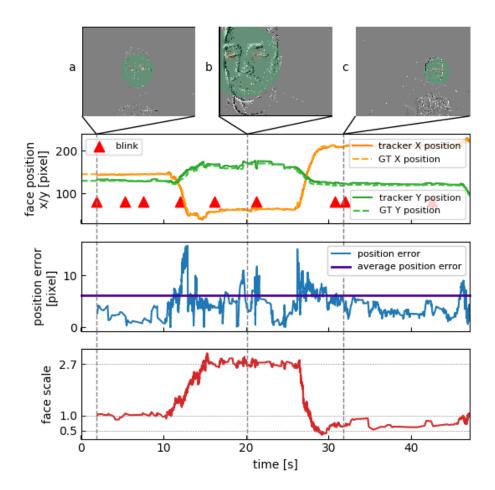

| 2.7  | Face tracking recording while verifying robustness to scale                              | 34 |

| 2.8  | Face tracking recording for multiple faces at the same time                              | 35 |

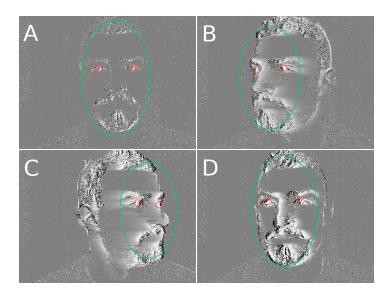

| 2.9  | Face tracking results for varying pose                                                   | 36 |

| 3.1  | Screenshots of proposed Android app for live view and gesture recognition.               | 41 |

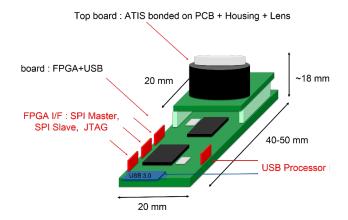

| 3.2  | Prototype device that shows connected event camera                                       | 43 |

| 3.3  | Small form-factor event camera assembly                                                  | 43 |

| 3.4  | Android application software architecture                                                | 44 |

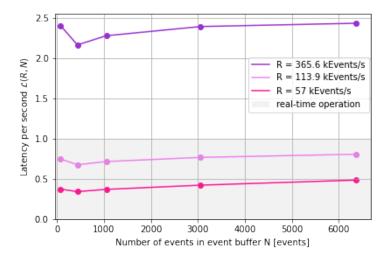

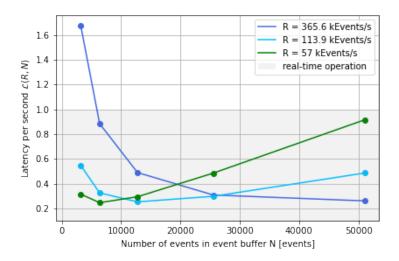

| 3.5  | Accumulated latency per second for aperture robust event-based optical                   |    |

|      | flow on a mobile phone                                                                   | 49 |

| 3.6  | Visual results when computing aperture-robust event-based optical flow. $\boldsymbol{.}$ | 50 |

| 3.7  | Gesture recognition method overview                                                      | 51 |

| 3.8  | Accumulated latency per second when computing HOTS features and                          |    |

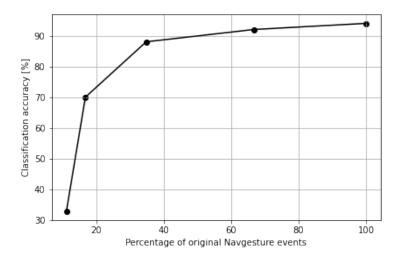

|      | classifying on the phone                                                                 | 52 |

| 3.9  | Event-by-event gesture classification results on NavGesture-sit                          | 52 |

xiv LIST OF FIGURES

| 3.10 | Gray-level frame reconstruction from events using a pre-trained FireNet                                                 |    |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

|      | $model. \ \dots $ | 53 |

| 3.11 | Accumulated latency per second when reconstructing grey-level frames from                                               |    |

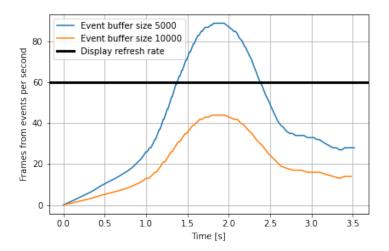

|      | events on the phone                                                                                                     | 54 |

| 3.12 | Event frames per second for an example gesture recording of $3.5\mathrm{s.}$                                            | 55 |

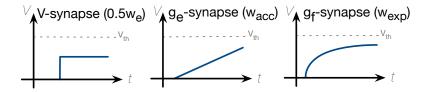

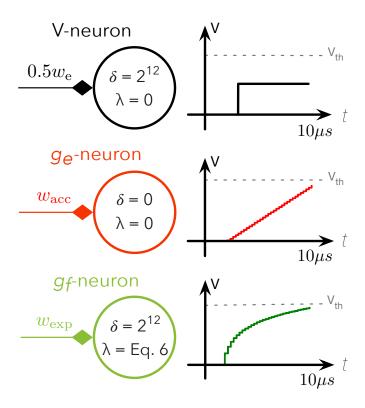

| 4.1  | The effect of three different synapses $V, g_e$ and $g_f$                                                               | 59 |

| 4.2  | Three different Loihi neurons $V$ , $g_e$ and $g_f$                                                                     | 61 |

| 4.3  | Dendritic tree for Loihi multicompartment neuron                                                                        | 62 |

| 4.4  | Delay encoder network on Loihi                                                                                          | 63 |

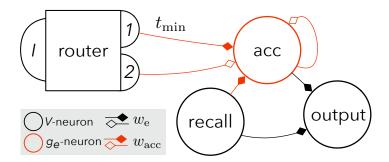

| 4.5  | Router network on Loihi                                                                                                 | 64 |

| 4.6  | Inverting memory network on Loihi                                                                                       | 64 |

| 4.7  | Memory network on Loihi                                                                                                 | 65 |

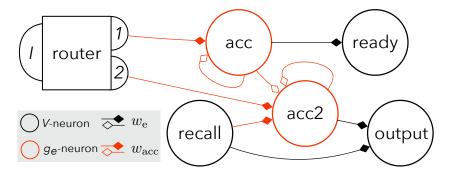

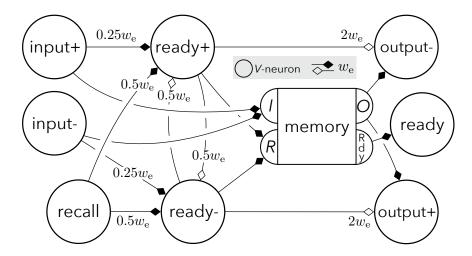

| 4.8  | Signed memory network on Loihi                                                                                          | 66 |

| 4.9  | Synchroniser network on Loihi                                                                                           | 66 |

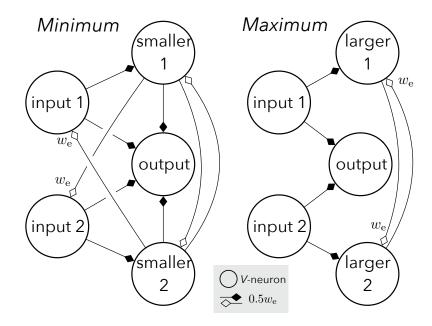

| 4.10 | Minimum and maximum networks on Loihi                                                                                   | 67 |

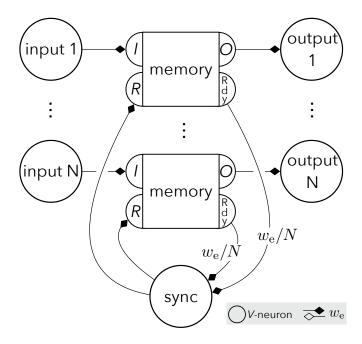

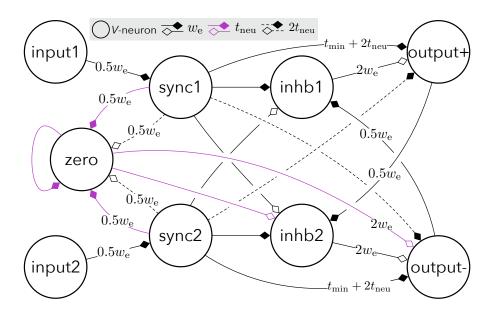

| 4.11 | Subtractor network on Loihi                                                                                             | 68 |

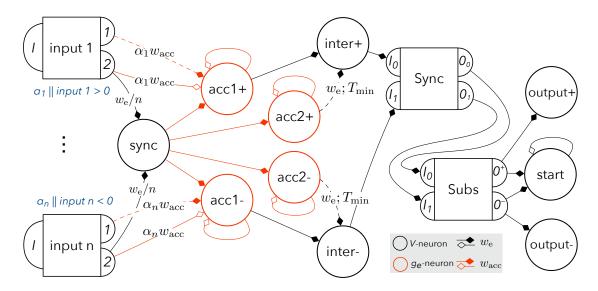

| 4.12 | Linear Combination network on Loihi                                                                                     | 69 |

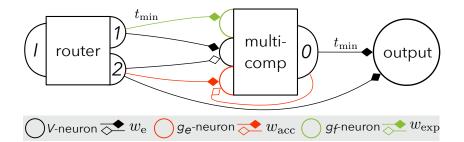

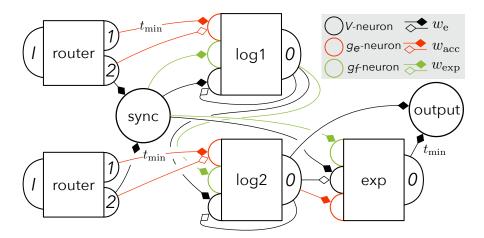

| 4.13 | Natural logarithm network on Loihi                                                                                      | 69 |

| 4.14 | Exponential network on Loihi                                                                                            | 70 |

| 4.15 | Multiplier network on Loihi                                                                                             | 70 |

| 4.16 | Conversion of 2 ANN units to an SNN using STICK on Loihi                                                                | 71 |

| 4.17 | Outputs of a first order system network on Loihi                                                                        | 73 |

| 4.18 | Outputs of a second order system network on Loihi                                                                       | 74 |

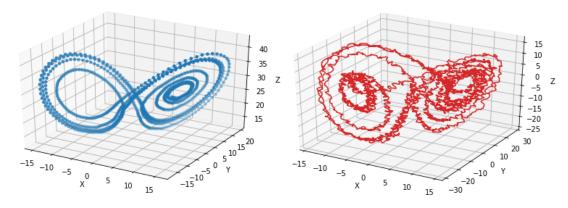

| 4.19 | Outputs in X, Y and Z for Lorenz system network on Loihi                                                                | 75 |

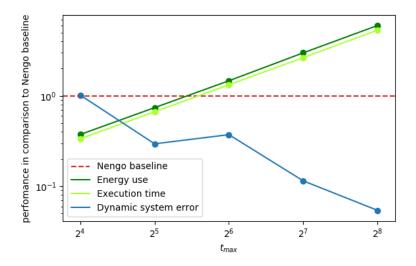

| 4.20 | Performance comparison between proposed networks and Nengo implemen-                                                    |    |

|      | tation for 3 dynamic systems                                                                                            | 76 |

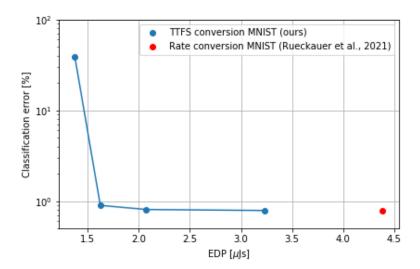

| 4.21 | Classification error plotted over Energy-delay product for MNIST                                                        | 78 |

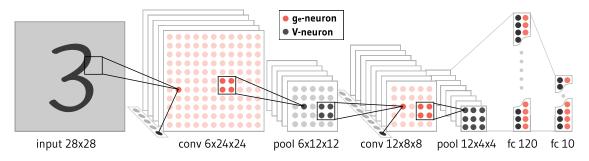

| 4.22 | Converted spiking neural network architecture diagram                                                                   | 79 |

| A.1  | Logos for Frog and Tonic software packages                                                                              | 94 |

| A.2  | Screenshots for Frog Android app                                                                                        | 95 |

## **List of Tables**

| 2.1 | Mean blinking rates for human subjects                                                              | 27 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 2.2 | Summary of face tracking detection results                                                          | 37 |

| 3.1 | Classification latency for 6 different gestures from the Navgesture database.                       | 53 |

| 4.1 | Comparison of accuracy and performance to other SNNs for a classification task on MNIST             | 78 |

| 4.2 | Breakdown of static and dynamic power consumption per MNIST classifi-<br>cation inference on Loihi. | 79 |

## Chapter 1

## Introduction

How much of a machine is human? And how much of a human is a machine? This question will become somewhat more important and at the same time more difficult to answer in the future as the dividing lines will gradually get blurrier [4]. Modern technology is a powerful tool that provides humanity with the means to transform cognitive abilities into skills and machines. Our biological bodies will inevitably merge with this technology to extend and offload capabilities. It will feel very natural, as new generations raised in the information age experience the extraordinary benefits and looming drawbacks of being online on-demand and in an instant. We are not far now from the point where we will have a direct, physical connection to a mobile system such as a brain machine interface [5, 6]. To be implanted such an interface will become as much of a routine treatment as getting dental braces or replacing a hip joint. To make the connection between human body and human-made technology as natural as possible, one can imagine that a system that processes information much like a biological organism does, is much easier to interface with [7, 8].

From a certain standpoint, humans can already be considered cyborgs [9, 10], defined as beings with both organic and artificial body parts. Examples of such parts are pacemakers, prostheses or neurostimulators. We might not have a physical connection to our beloved handheld devices such as phones and tablets, but it would not be an overstatement to say that we are at least psychologically attached to them. One could even go as far as to claim that we are overly dependent on them [11]. It's specifically the *smart* ones, those that can tell us jokes and enable us to connect to anyone and anything on the internet around the world in a matter of seconds. Mobile handheld devices have truly taken the world by storm since the year the smartphone took off in 2008. With the iPhone and Android fresh into the market back then, 17% of people in the Western world owned a smartphone at that time. Since then this number has risen to 93% across adults in the Western world [12]. In developing countries, mobile communication has largely leapfrogged wired telephone lines and conventional banking all together [13, 14]. Our smartphones or tablets are now embedded in our daily lives and act as a central hub to an even larger array of connected devices, such as smart speakers, watches or cameras.

As those devices become somewhat more intelligent and human-like, Artificial Intelligence (AI)-driven features become critical differentiating factors for a saturated market of smart technology. Voice or automated driving assistants add an undeniable surplus value to existing systems, and no company that produces consumer goods can afford to ignore this trend. The training of modern AI models consumes enormous amounts of energy, and these energy requirements are growing at a breathtaking rate. In the deep learning era, the computational resources needed to produce a best-in-class AI model has on average doubled every 3.4 months [15] as illustrated in Figure 1.1. As a result these models are costly to train and develop, both financially, due to the cost of hardware and electricity or cloud compute time, and environmentally, due to the carbon footprint required to fuel modern tensor processing hardware [16]. Generative Pre-trained Transformer-3, the latest language model by OpenAI to produce human-like text, consists of 175 billion parameters, more than a 100 times more than the previous year's biggest model [17]. It took an estimated 355 Graphics Processing Unit (GPU)-years, \$4.6m and 1 GWh of energy to train it. We see diminishing returns from scaling up machine learning models with a breathtaking rate.

Fig. 1.1 Number of total operations needed to train some of the most well-known models in computer vision, natural language processing and reinforcement learning. Image taken from OpenAI's blog post [15].

This stands in contrast to battery density that has been improving at an averaged rate of 7.5 percent a year between 2011 to 2017 [18]. While the daily usage of smart mobile devices especially among younger adults has steadily increased [19], the time a device can be used before it needs recharging has stagnated. Over time, more and more features have merged into our mobile devices, which is very costly in terms of computation. Therefore a lot of smart functionality is offloaded to be computed in the cloud, on a remote server. But the continuous exchange of private data over the network raises privacy concerns for end users. It also means that many devices stop being *smart* when problems with server availability or Wi-Fi connections arise. For the smart functionality that does not require a network connection, we have relied on the growth of numbers of transistors per unit area to satisfy the growing demand in computing power. Nowadays we are encountering the physical limits of this scaling process [20], with fabrication processes constructing transistors as little as 5 nm apart [21, 22]. Not only does processing logic reach physical speed limits, but already today Central Processing Unit (CPU)s spend a lot of their time waiting for new data to be fetched from memory, which is an issue that is only going to become more problematic with growing amounts of data to be processed. In response to that, industry has largely changed to horizontal scaling such as increasing the number of cores among other mitigation tactics in order to guarantee performance improvements. But the issue remains one around bandwidth and the sequential nature of reading instructions from memory, processing them and storing the result.

The race is on to explore new computing architectures and paradigms, which seem more promising than ever before. The field of neuromorphic engineering is one alternative route, exploring biological concepts of information processing in order to imitate them on a hardware level. It takes inspiration from neuroscience, machine learning and electrical engineering to build hardware that computes using silicon neurons [23, 24]. The guiding philosophy is not to copy the wetware such as our brain in complete detail, but to search for organising principles that can be applied in practical devices [25]. The essential components are artificial neurons, which emit short electrical pulses of action-potentials called spikes to other neurons via synaptic connections. Even so, building and connecting large numbers of artificial neurons on its own is not enough. With a new kind of hardware comes the need for new algorithms, which handle spikes from neurons in an asynchronous fashion. By doing that, the hope is to find a more efficient way to represent information and to compute. This parallel track to classic computing will not replace clocked, synchronous, high-throughput computation anytime soon. Rather it should be seen as catering to a growing demand for efficient, fault-tolerant, low-power computation. This demand is especially pressing on mobile systems, where specialised chips can naturally co-exist with current systems on a single device, devices that have an increasing gamut of functionalities that we happily rely on.

### 1.1 Motivation and Objectives

The current success story of deep learning and AI is powered by the interplay of data, algorithms and dedicated hardware. This hardware is based on the same computing architecture since the inception of the modern computer that separates processing unit from memory. Given that we stand just at the beginning of an age of AI, we have to ask the question how current trends in machine learning model sizes can continue to scale. Moore's law has been surpassed by Huang's law, named after NVIDIA's chief executive officer Jensen Huang, which predicts that the performance of GPUs will more than double every two years [26]. For battery-powered devices that rely on a lot of dedicated hardware to be efficient, advancements in powerhouse technology alone will not cut it. As technology powered by machine learning enters cars, watches, tablets and other mobile systems, power consumption in such environments will be critical to the success of those systems.

The goal of this thesis is to find ways that are inspired by biology to compute more efficiently than current computer systems. Neuromorphic engineering, taking inspiration from biological systems, rethinks computation from the ground up, as our brains do not separate memory from processing but combine the two principles in each and every neuron. We could build an end-to-end neuromorphic pipeline that exists in parallel to existing systems, but due to expensive sensors and processing hardware that is still in a research stage, this is not a straightforward feat. Alternatively we can replace parts of the conventional machine learning pipeline and examine how neuromorphic equivalents can contribute to saving power. These replacements are neuromorphic cameras, algorithms and hardware.

Neuromorphic cameras use a novel sampling theorem to imitate the asynchronous firing pattern of the mammal retina to avoid capturing redundant information and therefore save energy. This class of vision sensors has promising applications in machine vision that need to record a visual scene as efficiently as possible, while still exhibiting superior dynamic range and temporal resolution. We raise the question to what extent we can make use of event camera properties in neuromorphic algorithms to compute more efficiently than conventional architectures that use image-capturing cameras.

Mobile devices with their optimised processing hardware should be able to profit directly from such efficient sensors and algorithms. They already integrate a growing amount of sensors for specific tasks and specialised hardware that takes up an increasing share of silicon area. Neuromorphic sensors and algorithms can be added to this mix to help reduce power consumption further. The integration should be seamless to ensure adoption for devices that are ubiquitous in our lives.

The use of low-power conventional hardware as used in mobile devices can be seen as

intermediate step, but neuromorphic computing will eventually make use of dedicated hardware to unlock its full potential. Much like conventional neural networks do not seem as powerful when executed on a CPU, bio-inspired algorithms will benefit from hardware that boasts artificial neurons. The recent past has shown that the co-design of algorithms and hardware is more important than ever.

We explore algorithms that use asynchronous, event-based computation on both conventional hardware that is widely available today and on neuromorphic hardware that is emerging. Neuromorphic computing has the potential to follow a similar success story as deep learning and outperform current AI and machine learning architectures when it comes to power efficiency. Artificial general intelligence using 20 Watts is the ultimate goal to be as efficient as our brain, but until then it is still a long way to go. The advancements in neuromorphic technology will at the very least help devices to use less power and hopefully make technology function more human-like. Starting from the basic elements of neurons, the goal is to facilitate the successful merging of human and machine.

In the remainder of our introduction, we provide an overview about components of a neuromorphic system that can gradually replace and complement current technology. The combination of new sensors, algorithms and hardware will help to enable applications that are inherently low-power and might help us find new ways of biologically plausible learning.

### 1.2 Rethinking the Way our Cameras See

We want machines to be able to see like us, and in that effort have created cameras. The field of modern computer vision is based on the common output format of those sensors: frames. However, the way we humans perceive the world with our eyes is very different. Most importantly, we do it with a fraction of the energy needed by a conventional camera [27]. The field of neuromorphic vision tries to understand how our visual system processes information, in order to give modern cameras that same efficiency and it looks like a substantial shift in technology for machine vision.

We are so focused on working with data that modern cameras provide, that little thought is given about how to capture a scene more efficiently in the first place. Current cameras acquire frames by reading the brightness value of all pixels at the same time at a fixed time interval, the frame rate, regardless of whether the recorded information has actually changed. A single frame acts as a photo; as soon as we stack multiple of them per second it becomes a motion picture. This synchronous mechanism makes acquisition and processing predictable. But it comes with a price, namely the recording of redundant data. And not too little of it. As shown in Figure 1.2, redundant information about the background is

captured even though it does not change from frame to frame, when at the same time, high velocity scene activity results in motion blur.

Fig. 1.2 Image blur can occur in a frame depending on the exposure time.

#### 1.2.1 Taking Inspiration from the Human Visual System

The human retina has evolved to encode information extremely efficiently. Narrowing down the stimuli of about 125 million light sensitive photoreceptors to just 1 million ganglion cells which relay information to the rest of the brain, the retina compresses a visual scene into its most essential parts. Photoreceptor outputs are bundled into receptive fields of different sizes for each retinal ganglion cell as shown in Figure 1.3. The way a receptive field in the retina is organised into center and surround allows ganglion cells to transmit information about spatial contrast, encoded as the differences of firing rates of cells in the center and surround. Retinal ganglion cells are furthermore capable of firing independently of each other, thus decoupling the activity of receptive fields from each other. Even if not triggered by external stimulus, a retinal ganglion cell will have a spontaneous firing rate, resulting in millions of spikes per second that travel along the optic nerve. It is thought that in order to prevent the retinal image from fading and thus be able to see the non-moving objects, our eyes perform unintentional rapid jumps called micro-saccades. This movement only happens once or twice per second, so in between micro-saccades, our vision system probably relies on motion. To put it in a nutshell, our retina acts as a pre-processor for our visual system, extracting contrast as an important stream of information that then travels along the optical nerve to the visual cortex. In the cortex it is processed for higher-level conscious processing of the visual scene.

Inspired by the efficiency and complexity of the human visual system, Misha Mahowald developed a new artificial stereo vision system in the late 80s [28]. She was one of Carver Mead's students, a scientist at Caltech who spawned the field of Neuromorphic Engineering at that time. In his lab, Misha built what would become the first silicon retina in the

Fig. 1.3 Center-surround receptive fields in the mammalian retina.

early 90s [29]. It was based on the same principle of center-surround receptive fields in the human retina, which emit spikes independently of each other depending on the contrast pattern observed.

Although Misha drafted the beginning of a new imaging sensor, the design did not provide a practical implementation at first. In response, the neuromorphic community simplified the problem by dropping the principle of center-surround pixels [30]. Instead of encoding spatial contrast across multiple pixels which needed sophisticated circuits, the problem could be alleviated by realising a circuit that could encode *temporal* contrast for single pixels. That way, pixels could still operate individually as processing units just as receptive fields in the retina do and report any deviations in illuminance over time. While the first silicon retinas where fully analog [31, 32], it would take until 2008 when the first refined temporal contrast sensors was published based on digital architecture [33], the event cameras as they are known today.

### 1.2.2 A Paradigm Shift in Signal Acquisition

The new architecture led to a paradigm shift in signal acquisition, illustrated in Figure 1.4. Standard cameras capture absolute illuminance at the same time for all pixels driven by a clock and encoded as frames. One fundamental approach to dealing with temporal redundancy in classical videos is frame difference encoding. This simplest form of video compression includes transmitting only pixel values that exceed a defined intensity change threshold from frame to frame after an initial key-frame. Frame differencing is naturally

performed in post-processing, when the data has already been recorded. Trying to take inspiration from the way our eyes encode information, event cameras capture changes in illuminance over time for individual pixels corresponding to one retinal ganglion cell and its receptive field.

Fig. 1.4 Different sampling theorems. The 'real world' is a collection of analog signals, which in order to store and digitise it we transform into numbers. Digital signal acquisition relies on regular sampling along the time axis. An alternative approach is level or threshold crossing, where the signal is sampled whenever it surpasses a threshold on the y-axis.

If light increases or decreases by a certain percentage, one pixel will trigger what's called an event, which is the technical equivalent of a cell's action potential. One event will contain information about a timestamp, x/y coordinates and a polarity depending on the sign of the change. Pixels can trigger completely independently of each other, resulting in an overall event rate that is directly driven by the activity of the scene. It also means that if nothing moves in front of a static event camera, no new information is available hence no pixels fire apart from some noise. The absence of accurate measurements of absolute lighting information is a direct result of recording change information. This information can be refreshed by moving the event camera itself, much like a saccade.

Because of the considerable size of the circuit that enables temporal contrast for each pixel, it didn't leave much room for the photo diode to capture incoming photons. The ratio of a pixel's light sensitive area versus the total area is called fill factor and amounted

to 9.4% for the first event camera [33]. Modern CMOS (Complementary Metal Oxide Semiconductor) technology will enable a fill factor of above 90% at a fabrication process of 180 nm. With a reduced fill factor the photon yield will be low, which will in turn drive image noise. This was thus a major obstacle for event camera mass production early on. Nevertheless already this first camera was able to record contrast changes under moonlight conditions. New generations of event cameras use backside illumination in order to decouple the processing circuit for each pixel from the photo diode, by flipping the silicon wafer during manufacturing [34]. Most of today's smartphone cameras already use backside illumination in order to maximise illumination yield at the expense of fabrication cost.

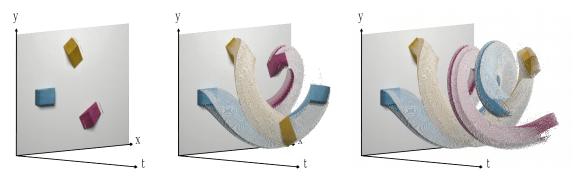

Fig. 1.5 An event-camera will only record change in brightness and encode it as events in x, y and time. Colour is artificial in this visualisation. Note the fine-grained resolution on the t-axis in comparison with the frame animation in Figure 1.2. Thanks to Alexandre Marcireau for the data. Visualisation has been created using Rainmaker\*.

### 1.2.3 A Novel Sensor for Machine Vision

Overall an event camera has three major advantages compared to conventional cameras: since pixel exposure times are decoupled of each other, very bright and very dark parts can be captured at the same time, resulting in a dynamic range of up to 125dB. The decoupled, asynchronous nature furthermore frees bandwidth so that changes for one pixel can be recorded at a temporal resolution and latency of microseconds. This makes it possible to track objects with very high speed and without blur as exemplified in Figure 1.5. The third advantage is low power consumption due to the sparse output of events, which makes the camera suitable for mobile and embedded applications. As long as nothing in front of the camera moves, no redundant data is recorded by the sensor which reduces computational load overall. It also relieves the need for huge raw data files. Current drawbacks for most commercially event cameras available today are actually further downstream, namely

<sup>\*</sup>https://github.com/neuromorphic-paris/command\_line\_tools

the lack of hardware and algorithms that properly exploit the sparse nature of an event camera's data. Rethinking even the most basic computer vision algorithms without frames takes a considerable effort.

Over the years, event cameras have seen drastic improvements in spatial resolution and signal to noise ratio. The main generations of cameras are Dynamic Vision Sensor (DVS) [33], Asynchronous Time-based Image Sensor (ATIS) [35] and the Dynamic and Active pixel Vision Sensor (DAVIS) [36]. Examples of companies that produce commercially available event cameras are Samsung [37], Prophesee [38], Celepixel and Insightness [36]. Most commercially available event cameras are still large in size, but small form factor version have been developed too. Event cameras for mobile applications include a small embedded DVS system [39] and a small ATIS which can be connected via mini-Universal Serial Bus (USB) [40], which is explained in more detail in Chapter 3. The first commercially available single-chip neuromorphic vision system for mobile and Internet of Things (IoT) applications is called Speck<sup>†</sup>, which combines a DVS and the Dynap-se neuromorphic Convolutional Neural Network (CNN) processor. The rise of the event camera has been relatively slow, as larger gains in power efficiency are being made by focusing on the processing of image data further downstream, notably on a GPU. This trend however is also likely to saturate at some point and will make it worth to further explore and employ this novel image sensor [41].

### 1.3 Event-based Computer Vision and Applications

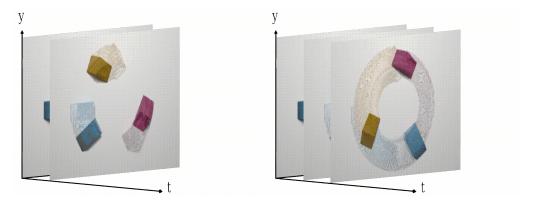

#### 1.3.1 A Temporal Component to Understand Visual Input

In 1975, Swedish perceptual psychologist Gunnar Johannson writes:

The eye is often compared to the camera, but there is one enormous difference between the two. In all ordinary cameras a shutter 'freezes' the image [...]. In all animals, however, the eye operates without a shutter. Why, then, is the world we see through our eyes not a complete blur? [42]

Animals integrate visual information over time into a continuous, conscious stream. Johannson proposed that an object can be recognised purely by its motion, based on the idea of continuous input [43]. Figure 1.6 shows one of his examples and more can be found online<sup>‡</sup>. Humans can indeed easily recognise objects that are represented by several simple dots moving, suggesting that timing is important for our visual system. At the same time, research has also shown that it is harder for humans to correctly identify a point-light walker when it is positioned upside down, suggesting that a spatial component is in fact

<sup>†</sup>https://www.speck.ai/

<sup>&</sup>lt;sup>‡</sup>A video of a Johannson experiment can be found under https://youtu.be/rEVB6kW9p6k

also necessary to detect an object [44].

Fig. 1.6 The points themselves make it hard to identify the object behind it. Can you guess what it is once the points start to move? Check https://tinyurl.com/y3yehcur

#### 1.3.2 The Era of Deep Learning

The success of deep learning using neural networks has proven triumphantly that a computer can recognise objects at a superhuman level by analysing purely spatial compositions (such as an image). To understand more subtle concepts such as actions, intents or emotions in an effort to be more *intelligent*, there has to happen some form of aggregation of information over time. And to make that possible on an embedded system, computation using frames that carry a lot of redundant information seems counter-intuitive. Recent research focuses on making neural networks more efficient by using techniques such as pruning [45, 46], quantization [47, 48, 49, 50], knowledge distilling [51] or finding functionally similar but smaller sub-networks [52]. Taking quantization to the extreme leads to binary weights, which significantly reduces model size and inference time [53, 54]. Neural networks have successfully been optimised to use fewer multiplier-accumulator operations and parameters by designing novel network architectures that exploit computation or memory efficient operations such as depthwise separable convolutions to fit on mobile devices [55, 56, 57, 58]. The most prominent examples of this endeavour are the MobileNet architectures, which is a family of computer vision neural network models designed to maximise accuracy while being mindful of the restricted resources for an on-device or embedded application [59, 60, 61].

These measures take effect late in the pipeline, still recording and processing redundant data. If we work with highly sparse data such as from event cameras in order to save power, we need a form of temporal component in our models.

### 1.3.3 Event-based Processing

The field of event-based computer vision has grown rapidly over the last years, as event cameras have the potential to displace standard cameras in wearable technology, robotics and mobile applications. Applications that are currently available specifically on mobile systems include drowsiness driving detection systems [62], proximity sensing for handheld devices [63], motion detection [64] or gesture recognition as described in Chapter 3. Mobile autonomous robots can learn to cooperate [65] and drones learn autonomous flight [66, 67, 68].

Rooted in classical computer vision, a lot of work focuses on accumulating events into bins of fixed or variable length depending on scene activity [69], thus artificially creating frames from a sparse output signal. This group of algorithms leverages existing advances, most notably analog artificial neural networks to use them for optical flow [70, 71], depth prediction [72], high dynamic range image reconstruction from events [73, 74, 75], or Simultaneous Localisation and Mapping (SLAM) [76, 66]. Other applications include image deblurring [77], star tracking [78] or object segmentation [79, 80].

This approach also allows the use of GPUs when spatially sparse frames or volumes are processed using Artificial Neural Network (ANN)s, which results in processing a lot of redundant information because of the high temporal data precision. Aiming to increase the speed and power efficiency with which inference can be done, certain computations can be skipped using dedicated hardware [81, 82, 83, 84].

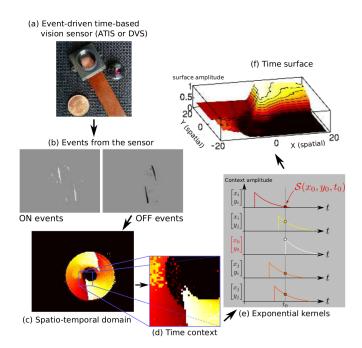

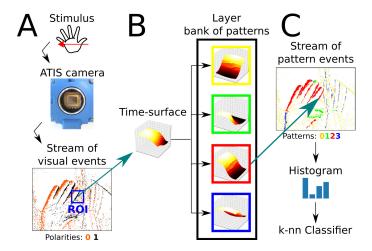

Another approach tries to get the best of both worlds, frames and events, by mixing them together, which works well with hybrid sensors such as the DAVIS but is computationally very demanding [86, 69, 87]. Methods that can possibly achieve the lowest latency and power consumption work on an event-by-event basis. This approach advocates short, incremental calculations triggered by each event, and requires rethinking computer vision algorithms from the ground up. The downside of this method is that they cannot make use of dedicated hardware such as GPUs at the moment, being restricted to highly parallel CPUs in most cases. There are exemptions of Field-Programmable Gate Array (FPGA) implementations to speed up the low-latency processing [88, 89, 90, 91]. Exemplary applications of event-by-event methods include event stream classification [85, 92], optical flow [93, 94, 95, 96], corner detection [97, 98, 99], pose estimation [100] and tracking [101]. It lead to the emergence of new features called time surfaces [85, 78, 102], which are spatio-temporal features generated for each event as shown in Figure 1.7. They resemble local patches of temporal gradients and have been employed in bag-of-features methods such as Hierarchy of Time Surfaces (HOTS) [85], which creates a hierarchy of time surfaces with different time constants. Other bag-of-features methods build on time surfaces as

Fig. 1.7 Time surface generation from the spatio-temporal context of events. A time surface resembles a local image patch that is generated for each event. (a,b) An event camera such as the ATIS or DVS records motion in a visual scene, represented by ON and OFF events over time. (c) If we represent the accumulated events in one image, brighter pixels signify more recent events. (d) focusing on a spatial region of interest we generate a local time surface by applying an exponential kernel (e) to the timing of events in the neighbourhood. Image taken from Lagorce et al. [85].

well [103, 92].

### 1.4 Spiking Neural Networks

### 1.4.1 Sparse Data Representations

A more biologically-inspired possibility is to turn to a Spiking Neural Network (SNN) for learning tasks. Labelled as the 3rd generation neural network archetype [104], data is represented in binary form, where a neuron can either spike or not. Every neuron has an internal state such as membrane potential, threshold and decay times. Neurons in an SNN do not fire automatically when new input is presented, but only when enough spikes per time unit accumulate so as to push the membrane potential across its threshold. The spike emitted will then be propagated forward, subject to synapse weights and delays. The sparse nature of communication offers the potential to encode and transmit information

in a significantly more energy efficient manner.

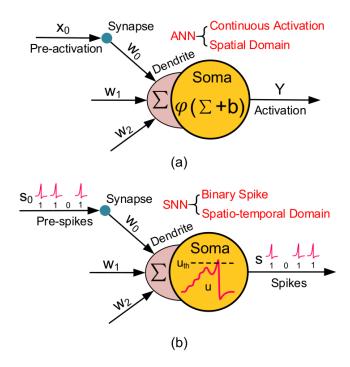

Figure 1.8 shows the principal difference between a neuron unit in an ANN and in an SNN. Whereas the input for an ANN is typically a tensor with high data precision, but low temporal resolution, the input for an SNN are binary flags of spikes with comparatively high temporal precision in the order of µs. The unit in the SNN integrates all of the incoming spikes, which affect the internal parameters such as membrane potential. The unit in the ANN merely computes the linear combination for inputs on all synapses and outputs that. Although there are ANN units with memory characteristics and internal states such as recurrent or long short-term memory units [105, 106], they typically operate on much wider time frames such as a few words in a sentence or a video frame that is captured every 25 ms.

Fig. 1.8 Basic neuron model in (a) ANNs and (b) SNNs. Picture taken from Deng et al. [107].

The development in SNNs has focused to a great extent on vision tasks such as image classification or object detection, largely driven by the need to compare new work to existing classical architectures. However, SNNs are likely not going to outperform ANNs in every aspect, but rather fill a niche. What this niche is, is an interesting research question at the moment. Some groups have developed spiking sorting algorithms [108], or spike time encoded addressable memory [109]. Certainly the ability for near-sensor feature extraction, ultra-low power neural network inference, local continual learning [110]

or constraint satisfaction problems [111, 112] are tasks where SNNs can already excel. The stateful, recurrent architecture of Recurrent Neural Network (RNN) also seems suitable to be mapped to SNNs [113, 114].

There are other areas of artificial intelligence that are little explored when it comes to employing SNNs, such as in reinforcement learning [115] or attention-based models. Deep reinforcement learning uses deep learning to model complex value functions for continuous high-dimensional state spaces that allows an agent to perform actions even though while training it only encountered a small subset of states during trial and error learning [116, 117]. Deep reinforcement learning suffers from high sensitivity to noisy, incomplete, and misleading input data and SNNs with their inherent stochastic nature could provide some robustness to that [115]. In the same vein, ANNs are notoriously sensitive to malevolent adversarial attacks. Sharmin et al. demonstrate that SNNs tend to show more resiliency compared to ANN under black box attack scenario, which could help deploy them in real-world scenarios [118].

So far SNNs have not proven that they perform better in general. The rise of attention-based deep neural network architectures called transformers [119, 120] make it clear that time and recurrent architectures are not a necessity when computing on sequences. They allow for parallel training on multiple tokens at the same time but need lots of parameters. Transformers are causing a stir in deep learning and are being used not only in natural language processing but also vision and audio tasks. However, they work with highly dense training data such as images and regularly sampled audio files. A crucial point that neuromorphic computing relies on is sparsity. This is, after all, the strength of event-based sensing and the principle of threshold crossing. No change in the input signal means no data recorded. Nevertheless there are different training methods how an SNN can extract features from input data.

#### 1.4.2 Training Spiking Neural Networks

Training SNNs follows one of 3 major pathways: converting the weights of pre-trained ANN [121, 122], supervised learning using backpropagation with spikes [123, 124, 125, 126] or local learning rules based on Spike-Time Dependent Plasticity (STDP) [127, 128] or local errors [129]. The most straightforward path to create an SNN is to convert an ANN which had previously been trained on a GPU. The idea is to trade a small impact in performance for reduced latency and power efficiency. Continuous values are hereby transformed into rate-coded schemes [122]. Alternatively, the network can also be converted using a temporal coding scheme [130], which we explore in more detail in Chapter 4. Converted SNNs benefit from a large ecosystem available for GPU-based training of ANNs and certain training mechanisms such as batch normalisation [131] or dropout [132].

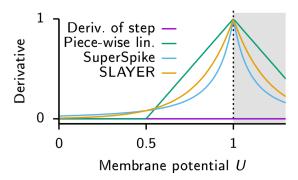

Fig. 1.9 Commonly used derivatives as a replacement for spike activation to provide a differentiable signal when training spiking neural networks. The step function has zero derivative (violet) everywhere except at 0 where it is ill defined. Examples of replacement derivatives which have been used to train SNNs are in Green: Piece-wise linear [133, 134, 135]. Blue: Derivative of a fast sigmoid [136]. Orange: Exponential [124]. Figure taken from Neftci et al. [137].

In order to facilitate learning in an SNN directly, we can apply methods from classical neural network training, such as backpropagation through time [138], to our SNN. Since the activation of a single spike, which resembles a Dirac impulse, is not differentiable, methods resort to smoothing spike activation itself [135, 136, 133, 137] as shown in Figure 1.9. A recent method has also adapted backpropagation to spikes without approximations [126]. Training methods using a global error signal achieve very good results, but are not very plausible to happen in the brain. SNNs that have been trained directly with backpropagation have yet to achieve the accuracy of converted SNNs when it comes to deeper networks, but the end-to-end training also speeds up the overall time needed for one network propagation and therefore reduces latency [139].

Local learning rules strive for biological plausibility without sacrificing performance too much. *DECOLLE* [110] and *e-prop* [114] are two recent examples of those algorithms that can both be implemented in neuromorphic hardware. Lastly, unsupervised feature extraction using local learning rules such as STDP [140, 141] relies purely on the timing between pre- and postsynaptic spike. It is biological plausible since it is without need for a global error signal, but has yet to reach ANN performance. The introduction of a third factor such as a global reward signal to complement the learning rule [142, 143] seems like a promising path forward. Overall, event-based vision promises efficient processing for naturally sparse inputs. An asynchronous network such as an SNN however needs asynchronous hardware to fully exploit its advantages.

### 1.5 Low-power Hardware for Mobile Systems

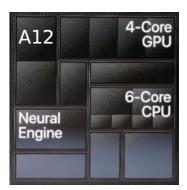

When power efficiency for a computing system is of utmost importance, dedicated hardware plays a crucial role. A System on Chip (SoC), soldered onto the mainboard of a mobile device, bundles multiple components into single chip to save space, cost and power consumption. It combines CPU, GPU and neural processing unit among other vital parts to act as integral computation unit of the device. ARM cores with their Reduced Instruction Set Computer (RISC) architecture achieve a much better performance per Watt ratio as opposed to x86 cores which use complex instruction sets and have become the de facto industry standard for CPUs in mobile phones and tablets. Apple announcing in 2020 that it is going to switch to ARM-based architecture for their latest laptop series products underlines the importance of low-power computer architecture in the mid-term future [144]. The SoC also includes dedicated graphics processors, as demand for highfidelity, multi-user games has continuously increased over the years. Although GPUs have been diverted as AI accelerators on desktops, where power consumption does not play such an important role, mobile systems cannot afford the overhead of computing with double precision and off-chip memory. Neural processing unit, AI accelerator or Machine Learning processor are all terms that describe hardware which is specifically optimised for neural network operations. These processors are the newest class of dedicated silicon within a SoC and take up a growing percentage of the overall chip as shown in Figure 1.10. They make their way into mobile devices to enable biometric security features such as face or fingerprint unlocks, predictive text, voice assistants, content providers, system optimisation, navigation, health monitoring, intelligent cameras and more.

Fig. 1.10 Two of Apple's SoCs, from 2018 on the left and 2020 on the right. The amount of silicon space dedicated to neural network accelerators is growing from year to year, up to a quarter in the latest version.

Specifically photo and video capturing is an important feature for consumers, with phone manufacturers embedding no less than 4 cameras into their phones in 2020 [145]. Because

of the high power consumption involved in capturing and processing photos and videos in comparison to other embedded sensors [146], Vision Processing Units are yet another AI accelerator designed to improve performance of specific machine vision tasks that use embedded cameras. They are different from GPUs since they may include direct interfaces to the cameras, process using on-chip buffers and low precision fixed point arithmetic for image processing. Intel's Movidius Vision Processing Units [147] targets mobile devices, the IoT and the digital camera market. Qualcomm introduced the Darwin Neural Processing Unit already in 2015, which is a highly configurable neuromorphic hardware co-processor based on SNNs implemented with digital logic [148]. In the same year Google introduced the first generation of its Tensor Processing Unit (TPU), another neural network accelerator to speed up training and inference and has since made it available for third party use [149, 150]. In 2018 they announced the Edge TPU as part of their Coral line<sup>§</sup>, which is a smaller and low-power version specifically for inference on power-constrained devices. An integrated version of the Edge TPU is already used in Google's own mobile phone series, the Google Pixel 4 [151].

#### 1.5.1 Neuromorphic Hardware

Companies increasingly focus on a tight integration between hardware and software by designing the chips themselves to get a competitive advantage, as the race for more compute accelerates. Neuromorphic chips are posed to claim a share of the dedicated computing space for machine learning related tasks. A decisive factor will be whether hardware and algorithms together can exploit the sparsity inherent to some sensors, such as event cameras, to accomplish the same task using less energy. The hardware mimics the natural biological structures of a mammal nervous system, trying to imitate the power-efficient brain as a whole by rebuilding its basic components, the neurons, in silicon. This network of silicon neurons is the matching hardware to SNNs in the software domain. At the moment, neuromorphic chip design targets three main areas of research: 1. the exploration of new, asynchronous, bio-inspired algorithms for computation 2. helping neuroscientists understand the brain by being able to use billions of artificial neurons in scaled-up systems [152] 3. low-power applications more generally.

Neuromorphic hardware is either based on a fully digital design or alternatively brings analog components into the mix. Analog circuitry emulates the behaviour of neurons directly [153, 24], which means that a neuron's membrane potential and spike behaviour on chip can be followed on an oscilloscope if so desired. The routing of spikes however still uses digital circuitry and an asynchronous communication protocol [154]. Examples of this approach are CAVIAR [155], BrainScaleS [156], DYNAPs [157, 158] and Neurogrid [159].

<sup>\$</sup>https://www.coral.ai/

Their major advantage is power efficiency by using transistors in a sub-threshold regime, and the operation in real-time independently of the model size or complexity. The drawback is a large silicon area per neuron, reducing the number of neurons per chip overall, as well as sensitivity to temperature, noise and *mismatch*, which is a term to summarise production variations of transistors across the silicon wafer. This class of neuromorphic hardware is used when low power is of utmost importance, but boundaries are pushed even further by exploring new materials to replace the relatively large analog circuits. A new electrical 2-terminal component called memristor [160, 161] can be used as an artificial synapse with adjustable weights [162, 163]. Memristors can be packed extremely densely in so-called crossbar arrays, to which the weights of a neural network can be mapped directly to perform in-place computation.

Digital chips abstract away some of the downsides of analog logic at the expense of power consumption. Examples of fully digital chips are SpiNNaker v1 and v2 [164, 165], TrueNorth [166] and Loihi [167]. They contain many processing cores distributed across the chip, where each core simulates a bundle of neurons and stores their membrane potential and variables related to learning in memory. Their advantage is deterministic neuron behaviour and fully-fledged learning capabilities. Fully digital architectures are used to help drive the exploration of novel spike-based algorithms, as they provide more reliable systems.

#### 1.5.2 Hardware Benchmarking and Scalability

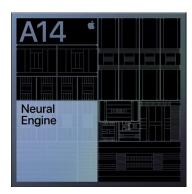

Research currently encounters a growing interest in benchmarking the power consumption of machine learning models [168] and making efficiency an evaluation criterion alongside accuracy as a related measure [169, 107]. Some preliminary work has explored the advantages of event-based sensing over classical frame-based methods in terms of power consumption during motion tracking [1], object tracking [170] or resilience to difficult lighting conditions [30]. Figure 1.11 shows the time to solution plotted over energy spent in comparison to Loihi for different tasks. This is an important task to carve out the areas where neuromorphic computing can excel and to guide future research. To put a price on energy used for machine learning models will also play a vital role in the effort to produce computing systems that are not completely detached from the limits of what biology can do.

An important question of hardware is the question of scalability. Neuromorphic hardware developed in research labs has seen a steady increase in amount of artificial neurons and learning capabilities over the past decade. Some large-scale neuromorphic systems that contain hundreds of chips in parallel now make available for computation an amount of artificial neurons that is comparable to the brain of a mouse [172, 173, 174]. Industry

Fig. 1.11 This plot compares the latest neuromorphic hardware against other architectures in terms of energy and latency for certain tasks. Whereas Loihi is really good at solving constraint satisfaction problems, large scale nearest neighbour search or RNN, the situation for feed forward networks is not so clear yet. Plot taken from Davies et al. [171].

currently releases ultra-low power programmable chips for edge computing such as GrAI One [175] or the Akida Neural Processor [176]. As the spiking ecosystem evolves, it will define the area of where it will excel over and succumb to classical AI accelerators.

#### 1.6 Thesis Outline

In this thesis we look at neuromorphic algorithms that are combined with both von Neumann and neuromorphic hardware to compute more efficiently than conventional systems.

In Chapter 2 we make use of event camera properties such as high temporal precision and robustness to different lighting conditions to explore the generation of spatio-temporal features that take into account fine-grained temporal signatures. We use the spatio-temporal signature of eye blinks that can be captured well with event cameras for event-based face detection and tracking. We do not rely on frame representations as as an alternative to conventional, frame-based methods. We show that when exploiting the sparse nature of the camera, we can use less power than gold-standard alternatives.

In Chapter 3 we turn to hardware that is optimised for battery-powered systems. Much

1.6 Thesis Outline 21

of the efficiency in mobile systems comes from several dedicated chips that are designed to execute specific tasks. Due to the use of conventional cameras however, such systems are not suited for always-on sensing. Always-on sensing is too costly when done using conventional cameras, especially for tasks that happen infrequently such as gesture recognition. This is unfortunate as it it deprives a growing population of elderly and visually impaired users of an intuitive interface. We present an Android framework that enables always-on sensing using an event camera, by avoiding computation in the absence of new visual information. Our framework connects the world of event-based computer vision to mobile devices that are powered by conventional hardware.

Neuromorphic computing is designed to work with artificial neurons and spikes. To leverage its full potential, we explore SNNs on neuromorphic hardware in Chapter 4. This hardware enables us to execute execute asynchronous algorithms efficiently. The chapter shines light on how it is possible to compute using the precise timing of spikes on neuromorphic hardware and how pre-trained networks can be ported for power-efficient inference on Loihi. This platform has superb support for power benchmarking, which plays a vital role in evaluating the strengths and weaknesses of spiking hardware over other specialised hardware.

Chapter 5 concludes our work and puts it into a bigger perspective. We draw parallels to the ascent of deep learning and how it is similarly backed by the development of dedicated hardware and give an outlook of developments in neuromorphic computing yet to come.

## Chapter 2

# **Event-based Processing: Face Detection and Tracking**

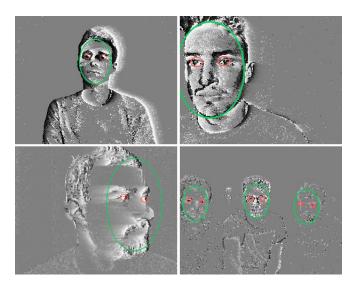

We start by looking at algorithms for event-based processing and introduce the first purely event-based method for face detection. It uses the high temporal resolution properties of an event-based camera to detect the presence of a face in a scene using eye blinks. Eye blinks are a unique and stable natural dynamic temporal signature of human faces across population that can be fully captured by event-based sensors. We show that eye blinks have a unique temporal signature over time that can be easily detected by correlating the acquired local activity with a generic temporal model of eye blinks that has been generated from a wide population of users. In a second stage once a face has been located it becomes possible to apply a probabilistic framework to track its spatial location for each incoming event while using eye blinks to correct for drift and tracking errors. Results are shown for several indoor and outdoor experiments as exemplified in Figure 2.1. We also released an annotated data set that can be used for future work on the topic.

Fig. 2.1 Event-based face tracking in different scenes. From left to right, top to bottom:  $\mathbf{a}$ ) indoors  $\mathbf{b}$ ) varying scale  $\mathbf{c}$ ) with one eye occluded  $\mathbf{d}$ ) multiple faces at the same time.

#### 2.1 Introduction

The method exploits the dynamic properties of human faces to detect, track and update multiple faces in an unknown scene. Although face detection and tracking are considered practically solved in classic computer vision, it is important to emphasise that current performances of conventional frame based techniques come at a high operating computational cost after days of training on large databases of static images. Event-based cameras record changes in illumination at high temporal resolutions (in the range of 1 µs to 1 ms) and are therefore able to acquire the dynamics of moving targets present in a scene [33]. In this work we will rely on eye blink detection to determine the presence of a face in a scene to in a second stage initialise the position of a Bayesian tracker. The permanent computation of eye blinks will allow to correct tracking drifts and reduce localisation errors over time. Blinks produce a unique space-time signature that is temporally stable across populations and can be reliably used to detect the position of eyes in an unknown scene. This work extends the sate-of-art by:

- Implementing a low-power human eye-blink detection that exploits the high temporal precision provided by event-based cameras.

- Tracking of multiple faces simultaneously at µs precision, once they have been detected.