## System and Networking Aspects of the Transition of High-Performance Applications from Dedicated to Commodity Hardware: the Example of Media Production for Professional Broadcast

Mohammed Hawari

#### ▶ To cite this version:

Mohammed Hawari. System and Networking Aspects of the Transition of High-Performance Applications from Dedicated to Commodity Hardware: the Example of Media Production for Professional Broadcast. Networking and Internet Architecture [cs.NI]. Institut Polytechnique de Paris, 2021. English. NNT: 2021IPPAX053. tel-03505917

## HAL Id: tel-03505917 https://theses.hal.science/tel-03505917

Submitted on 1 Jan 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# System and Networking Aspects of the Transition of High-Performance Applications from Dedicated to Commodity Hardware: the Example of Media Production for Professional Broadcast

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à l'École polytechnique

École doctorale n°626 École doctorale de l'Institut Polytechnique de Paris (EDIPP) Spécialité de doctorat : Réseaux, Informations, et Communications

Thèse présentée et soutenue à Palaiseau, le 6 juillet 2021, par

#### M. MOHAMMED HAWARI

#### Composition du Jury:

Nadia Boukhatem

Professeur, Telecom ParisTech (LTCI)

Président

Laurent Toutain

Professeur, IMT Atlantique (SRCD)

Rapporteur

Lars Eggert

Directeur Technique, NetApp Rapporteur

Colin Perkins

Associate Professor, University of Glasgow Examinateur

Thomas Clausen

Professeur, l'École polytechnique Directeur de thèse

System and Networking Aspects of the Transition of High-Performance Applications from Dedicated to Commodity Hardware: the Example of Media Production for Professional Broadcast

Mohammed Hawari

2020

### Abstract

Due to the increasing performance offered by commodity servers and to the general availability of multi-gigabit Ethernet-based networking hardware, a growing number of performance-intensive and network-intensive applications are being migrated from dedicated to commodity hardware. Examples thereof include scientific computing and network-packet processing, historically implemented by dedicated super-computing clusters and by dedicated packet-processing hardware, respectively. However, media production for professional broadcast (i.e., the process by which multiple audiovisual sources are mixed and processed, in real-time, to elaborate the audiovisual stream as it will be consumed by the final viewer) is still being implemented with dedicated hardware equipment, based on the Serial Digital Interface (SDI), an interconnection technology carrying the legacy of analog video. Despite an ongoing industrial effort to replace SDI with IP-based interconnection – as specified by the SMPTE 2022-6 and 2110 standards — the delay-sensitive nature of media production still challenges its total transition to software running on commodity servers. This thesis solves different aspects of that problem.

First, the high rates and low jitter-tolerance of media production packet streams have motivated a quantitative and qualitative study of the sources of jitter undergone by those streams when they are processed by commodity servers. In addition to results specific to Linux x86 64 servers, that work has yielded a general jitter exploration methodology, applicable to any operating system and hardware commodity servers. Second, a generic platform enabling the implementation of custom high-accuracy instrumentation for hardware-based packet timestamping has been developed. By exposing a high-level programming interface — relying on the P4 language — that platform, despite being FPGA-based, allow network and broadcast operators with little hardware design skills to specify custom logic for line-rate packet processing and timestamping. In particular, such instrumentation can be used to qualify the jitter properties of media production streams. Third, a system to perform packet-pacing — i.e., the transmission of a constant-rate packet stream with negligible jitter — has been proposed. By exclusively but cleverly relying on commodity hardware, that work invalidates the common belief according to which software-based media-production is impossible on commodity servers (due to the jitter they introduce). The proposed system has been formally and experimentally proven to yield a jitter, conforming to the requirements of media production streams. Finally, a software framework easing the implementation of media-production applications has been developed. That framework relies on a separation between media processing and media transport: the media processing logic receives and transmits full media frames (e.g., video frames) from the media transport logic, which handles high-performance packet processing with techniques such as zero-copy and kernel bypass networking. Those last techniques have been shown to notably increase the scalability of media production on commodity servers.

**Keywords** — media processing, commodity servers, packet pacing, jitter, instrumentation, Field Programmable Gateway Array, kernel bypass, zero copy, software architecture

#### Résumé

La production de média pour la diffusion audiovisuelle (i.e., le processus par lequel plusieurs sources audiovisuelles sont mélangées et traitées en temps réel pour élaborer le flux consommé par le téléspectateur) est généralement implémentée par du matériel dédié, basé sur la Serial Digital Interface (SDI), une technologie d'interconnection dérivé de la télévision analogique. Malgré l'effort industriel présent pour remplacer le SDI par de l'IP (ainsi que spécifié par les standards SMPTE 2022-6 et 2110) la sensibilité au délai de la production de média rend difficile une transition totale vers un traitement logiciel sur des serveurs générique. Cette thèse résout different aspects de ce problème.

Premièrement, il a été conduit une étude quantitative et qualitative de la gigue subie par ces flux lors d'un traitement logiciel. Au delà de résultats obtenus pour des serveurs Linux x86\_64, il a été dérivé une méthodologie générale, applicable à tout système d'exploitation et architecture matérielle, permettant d'étudier la gigue introduite.

Deuxièmement, une plateforme générique a été proposé afin de permettre la réalisation de système d'instrumentation personnalisé, pour l'horodatage précis de packet réseaux. Bien qu'étant basée sur la technologie des FPGA, cette plateforme permet à tout opérateur réseau ou de diffusion audiovisuelle de spécifier une logique d'horodatage personnalisée en utilisant le langage P4. Cela permet en particulier la conception d'une instrumentation pour la qualification de flux média.

Troisièmement, un système de lissage de traffic (packet-pacing) a été proposé, afin de permettre l'envoi de flux de paquets avec une gigue négligeable. Malgré un emploi exclusif de matériel générique, il a été prouvé formellement et expérimentalement que la gigue ainsi obtenue était suffisamment faible pour des flux média.

Finalement, un cadre logiciel facilitant l'écriture d'applications de traitement média a été proposé. Ce cadre repose sur la séparation entre le traitement et le transport des flux média, la couche de transport s'occupant du traitement haute performance des paquets réseaux par l'emploi de techniques comme le zero-copy, ou le kernel-bypass.

Mots-clefs — traitement média, lissage de trafic, gigue, instrumentation, serveurs standards, architecture logicielle, instrumentation, FPGA

#### Remerciements

Au nom de Dieu, le Tout Miséricordieux, le Très Miséricordieux

Avant tout, j'aimerais remercier mon cher directeur de thèse, Thomas Clausen, pour son dévouement et la qualité exceptionnelle de son encadrement. Thomas, je pense pouvoir dire sans me tromper, qu'il y a bien peu d'encadrants dont l'implication et le dévouement pourraient ne serait-ce qu'être comparés aux tiens. Bien au delà de ton rôle, tu m'as accompagné dans la découverte de la science des réseaux informatiques (en 2014 déjà), la construction de mon projet professionnel et académique, et tu m'as soutenu dans les moments les plus difficiles de ma thèse en ayant toujours un mot encourageant, sans pour autant compromettre les standards de qualité auxquels tu tiens des étudiants.

Bien évidemment, je ne peux parler d'encadrant de qualité sans remercier André Surcouf, qui est celui sans qui le fil conducteur même de ma thèse n'existerait pas. André, merci d'avoir proposé des problèmes techniques et scientifiques de qualité, d'avoir vu le potentiel de valorisation dans chacune de mes idées et de m'avoir exposé à la dure réalité de l'innovation dans le monde industriel, loin des rêves de laborantins. Je peux dire avec certitude que tu as contribué de façon décisive à construire l'ingénieur que je suis devenu.

Je remercie mes rapporteurs, Lars Eggert et Laurent Toutain pour leur lecture attentive de mon manuscript, ainsi que pour la qualité, la minutie, et la pertinence de leurs rapports. Merci également aux autres membres du jury, Nadia Boukhatem, et Colin Perkins pour leur présence, et la qualité de leurs interventions pendant la soutenance.

Merci également à mes collègues thésards et jeunes diplômés à Cisco : Aloÿs Augustin pour m'avoir prouvé qu'il n'y a pas besoin de faire un doctorat pour atteindre les 1000 citations, Yoann Desmouceaux pour son mentoring délicat et pour m'avoir montré que toute idée mérite exploration, Marcel Enguehard pour son mentoring incisif, et m'avoir montré que tout résultat mérite publication, Jacques Samain pour son expertise en chatbot déjantés, et Guillaume Ruty pour m'avoir appris à rester serein en toute circonstance.

Merci à Jordan Augé qui, par nos passionnantes discussions scientifiques et non scientifiques, a su rendre mes trajets quotidiens en RER C bien moins moroses. Merci également à Jérôme Tollet, qui a su créer au sein de notre zone d'open space, une atmosphère équilibrée et agréable, teintée de professionnalisme, d'enthousiasme, de passion, mais aussi d'humour.

Merci à tout mes collègues de Cisco qui ont contribué techniquement et humainement à mon épanouissement durant ces trois années : Axel Taldir, Pierre Pfister, Mark Townsley, Julien Barbot, Fabien Andrieux, Franck Bachet, Enzo Fenoglio, David Gaumont, Jeremie Garnier, Ghislain Bourgin, Alain Fiocco, Benoît Ganne, Guillaume Ladhuie, Malycia Ly, Guillaume Sauvage de Saint Marc, Hassen Siad, Éric Vyncke, Zhiyuan Yao, Thomas Feltin, Giovanna Carofiglio, Lura Muscariello, Alberto Compagno, Michele Papalini, Mohsin Kazmi, Neale Ranns, Nathan Skrzypczak, Arthur Toussaint et tant d'autres.

Merci à Jiazi Yi et Juan-Antonio Cordero-Fuertes, véritables piliers de l'équipe de recherche à l'école Polytechnique pour leur soutien et leur aide dans la rédaction d'articles. Je souhaite également remercier les membres de l'administration de l'école doctorale de l'École polytechnique pour leur incroyable flexibilité et leur accompagnement dans toutes les tracasseries administratives.

Des remerciements tout particuliers à Carole Reynaud, sans laquelle il m'aurait tout simplement été impossible de déjouer les subtilités administratives et/ou financières découlant de tout partenariat entre une entreprise d'envergure internationale et une entité académique publique.

Enfin je souhaite terminer par les remerciements les plus importants : ceux dédiés à mes parents ainsi qu'à mes frère et soeurs pour leur soutien au cours de cette aventure.

## Contents

| $\mathbf{A}$ | bstra | ct          |                                                        | iii          |

|--------------|-------|-------------|--------------------------------------------------------|--------------|

| $\mathbf{R}$ | ésum  | ıé          |                                                        | $\mathbf{v}$ |

| $\mathbf{R}$ | emer  | ciemei      | nts                                                    | vii          |

| $\mathbf{C}$ | onter | $_{ m nts}$ |                                                        | ix           |

| 1            | Intr  | oducti      | ion                                                    | 1            |

|              | 1.1   | Profes      | ssional Broadcasting                                   | 2            |

|              |       | 1.1.1       | Media Distribution: From Internet Protocol Television  |              |

|              |       |             | (IPTV) to Over-The-Top (OTT)                           | 4            |

|              |       | 1.1.2       | Media Production: The Serial Digital Interface (SDI) . | 6            |

|              | 1.2   | Media       | Production on Commodity Hardware                       | 11           |

|              |       | 1.2.1       | Packetising SDI                                        | 11           |

|              |       | 1.2.2       | Software-based Media Processing on Commodity Serv-     |              |

|              |       |             | ers: Challenges and Limitations of SMPTE 2022-6        | 15           |

|              | 1.3   | Thesis      | s Contributions                                        | 19           |

|              | 1.4   | Public      | cations and Software Production                        | 20           |

| <b>2</b>     | Cha   | sing L      | inux Jitter Sources for Uncompressed Video             | 23           |

|              | 2.1   | _           | wire to application                                    | 25           |

|              |       | 2.1.1       | From Wire to Interrupt                                 | 25           |

|              |       | 2.1.2       | From Interrupt to Application                          | 26           |

|              |       | 2.1.3       | Network-Independent Jitter                             | 27           |

|              | 2.2   | Exper       | imental Setup                                          | 27           |

|              |       | 2.2.1       | A Packet Sink VPF                                      | 27           |

|              |       | 2.2.2       | Quantitative Scope                                     | 28           |

|              |       | 2.2.3       | Hardware setup                                         | 29           |

|              | 2.3   | Exper       | iments and Results                                     | 29           |

|              |       | 2.3.1       | Baseline: Minimal Jitter                               | 30           |

|   |     |        |                                             |       |      |     | NTS<br>NTS |

|---|-----|--------|---------------------------------------------|-------|------|-----|------------|

|   |     | 2.3.2  | Baseline: Experiments and Results           |       |      |     | 32         |

|   |     | 2.3.3  | ISR Start Of Execution                      |       |      |     |            |

|   |     | 2.3.4  | Linux Scheduler induced jitter              |       |      |     |            |

|   |     | 2.3.5  | Interrupt Throttling jitter                 |       |      |     |            |

|   | 2.4 | Concl  | usion                                       |       |      |     |            |

| 3 |     |        | ringing Advanced Network Packet Time        | esta  | mp   | ing | _          |

|   |     | the F  |                                             |       |      |     | 39         |

|   | 3.1 |        | ed Work and Limitations                     |       |      |     |            |

|   |     |        | Performance                                 |       |      |     |            |

|   |     | 3.1.2  | Programmability                             |       |      |     |            |

|   | 3.2 |        | ware Architecture                           |       |      |     |            |

|   |     | 3.2.1  | Packet Flow                                 |       |      |     |            |

|   |     | 3.2.2  | Timestamp Acquisition                       |       |      |     |            |

|   |     | 3.2.3  | Reconfigurable Packet Processor             |       |      |     |            |

|   | 3.3 | -      | mentation                                   |       |      |     |            |

|   |     | 3.3.1  | Overview                                    |       |      |     | 45         |

|   |     | 3.3.2  | DMA Core integration                        |       |      |     | 46         |

|   |     | 3.3.3  | P4 Packet Processor and Partial Reconfigura | tion  |      |     | 46         |

|   |     | 3.3.4  | Discussion                                  |       |      |     | 48         |

|   | 3.4 | Case   | Study: OP4T for Software Switch Testing     |       |      |     | 49         |

|   |     | 3.4.1  | Scenario                                    |       |      |     | 50         |

|   |     | 3.4.2  | OP4T-SST Packet Processor                   |       |      |     | 50         |

|   |     | 3.4.3  | Precision and Cross-connect                 |       |      |     | 51         |

|   | 3.5 | Evalu  | ation                                       |       |      |     | 51         |

|   |     | 3.5.1  | FPGA Resource utilisation                   |       |      |     | 51         |

|   |     | 3.5.2  | Experimental Setup                          |       |      |     | 51         |

|   |     | 3.5.3  | Results                                     |       |      |     | 53         |

|   | 3.6 | Concl  | usion                                       |       |      |     | 54         |

| 4 | Hig | h-Acc  | uracy Packet Pacing on Commodity Serve      | rs fo | or ( | Cor | ıstant     |

|   | Rat | e Flov | vs                                          |       |      |     | <b>57</b>  |

|   | 4.1 | Syster | m Model                                     |       |      |     | 61         |

|   |     | 4.1.1  | Time sequences                              |       |      |     |            |

|   |     | 4.1.2  | (b, f)-paced streams                        |       |      |     |            |

|   | 4.2 | Limit  | ations of a pure software approach          |       |      |     |            |

|   |     | 4.2.1  | Software Execution Model                    |       |      |     |            |

|   |     |        | Timers                                      |       |      |     | 66         |

4.2.3

4.2.4

4.2.5

Quantitative analysis of the impact of SMIs  $\dots 70$

68

68

## $\begin{array}{c} CONTENTS \\ CONTENTS \end{array}$

|   | 4.3 | Pacing          | g with a Pacing-Assistant                                     |

|---|-----|-----------------|---------------------------------------------------------------|

|   |     | 4.3.1           | Assisted Pacing                                               |

|   |     | 4.3.2           | PA-based free-running pacing                                  |

|   |     | 4.3.3           | PA-based frequency-controlled pacing                          |

|   | 4.4 | Analys          |                                                               |

|   |     | $4.4.1^{\circ}$ | Safety                                                        |

|   |     | 4.4.2           | Free-running pacer period                                     |

|   |     | 4.4.3           | Frequency-controlled pacer period                             |

|   |     | 4.4.4           | ALT-Jitter                                                    |

|   | 4.5 | Consti          | ructing a PA and a frequency-controller 80                    |

|   |     | 4.5.1           | Constructing a Pacing-Assistant 80                            |

|   |     | 4.5.2           | Constructing a frequency controller: basic version $F_b$ . 81 |

|   |     | 4.5.3           | Constructing $F: N_W$ -regularized version, $F_r$ 83          |

|   |     | 4.5.4           | Implementation considerations of algorithms 1 and 2 . 83      |

|   | 4.6 | -               | imental Evaluation                                            |

|   | 1.0 | 4.6.1           | Setup and methodology                                         |

|   |     | 4.6.2           | Results                                                       |

|   |     | 4.6.3           | Experimental qualification of $F$                             |

|   |     | 4.6.4           | Operational perspective                                       |

|   | 4.7 |                 | ssion                                                         |

|   | 1.1 | 4.7.1           | Practical impact of jitter reduction 91                       |

|   |     | 4.7.2           | Quantitative impact of drift compensation                     |

|   | 4.8 |                 | usion                                                         |

|   | 1.0 | Conten          | 301011                                                        |

| 5 |     |                 | ware Architecture for Transparent High-Performance            |

|   | Me  | dia Tra         | ansport 93                                                    |

|   | 5.1 | Motiva          | ation                                                         |

|   |     | 5.1.1           | SDI-based media production: analysis 96                       |

|   |     | 5.1.2           | Processing high-throughput packet streams for media-          |

|   |     |                 | production                                                    |

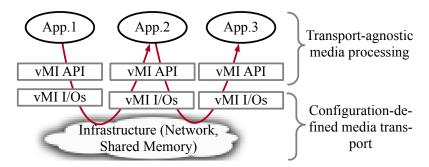

|   | 5.2 | Overv           | iew of the vMI framework                                      |

|   |     | 5.2.1           | Main Concepts                                                 |

|   |     | 5.2.2           | The Flow of a vMI frame                                       |

|   |     | 5.2.3           | Disaggregated media-processing                                |

|   | 5.3 | High-p          | performance vMI frame transport                               |

|   |     | 5.3.1           | Interprocess vMI frame sharing                                |

|   |     | 5.3.2           | Kernel-bypass networking                                      |

|   | 5.4 | Impler          | mentation                                                     |

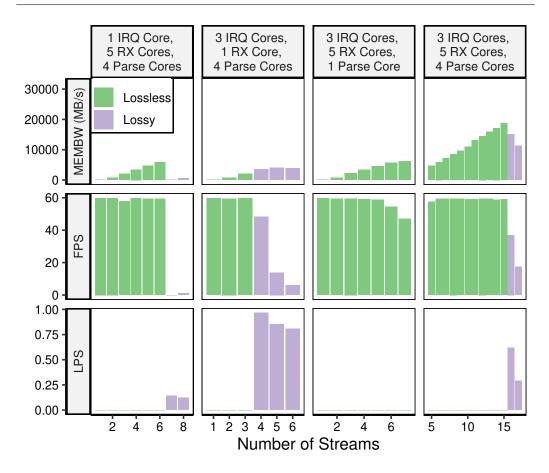

|   | 5.5 |                 | ation                                                         |

|   |     | 5.5.1           | Experimental methodology                                      |

|   |     | 5.5.2           | Microbenchmarks 112                                           |

|              |                 |                                      | CONTENTS<br>CONTENTS |  |

|--------------|-----------------|--------------------------------------|----------------------|--|

|              | 5.6             | 5.5.3 Full media-processing pipeline |                      |  |

| 6            | Coı             | nclusion                             | 121                  |  |

| $\mathbf{A}$ | Ma              | thematical Proofs for Chapter 4      | 125                  |  |

| В            | Rés             | sumé en français                     | 131                  |  |

| Li           | st of           | Figures                              | 133                  |  |

| Li           | st of           | Tables                               | 137                  |  |

| Li           | st of           | Algorithms                           | 139                  |  |

| Bi           | Bibliography 14 |                                      |                      |  |

## Chapter 1

## Introduction

Prior to the development of general-purpose multi-core Central Processing Units (CPU) and commoditised, multi-gigabit Ethernet hardware, a class of performance-demanding applications was implemented either as Application-Specific Integrated Circuits (ASIC), or as software running on dedicated High-Performance Computing (HPC) clusters of — possibly application-specific — servers. These are interconnected with also proprietary interfaces such as InfiniBand [1] or Omni-Path [2]. The prohibitive Non-Recurring Engineering (NRE) costs of ASIC development are in opposition to the increasing demand for flexibility in application development. Moreover, despite ongoing standardisation efforts — e.g., by the InfiniBand Trade Association [3] — HPC interconnection technologies are proprietary and subject to vendor lock-in, hence uncontrollable costs.

The availability of multi-core CPUs within the Intel x86\_64 and ARM architecture, of Graphical Processing Units (GPU) bringing massive vectorised compute capacity, and of Ethernet networking equipment supporting rates above 10 Gbit/s, materialises a performance increase in general-purpose computing architectures. That initiated a paradigm change, even for the most specialised and performance-demanding applications: they are increasingly implemented modularly, as sets of **micro-services**, distributed across commodity servers in a data-centre. Such an implementation increases flexibility and vendor-independence, reduces the infrastructure cost, and enables **resource pooling**, which, ultimately, allows deploying applications **in the cloud** and full externalisation of all infrastructure-related costs.

This transition from dedicated to commodity hardware has benefitted fields such as scientific computing, machine learning and artificial intelligence [4–9]. Those workloads have the particularity of not being subject to tight timing constraints, *i.e.*, tasks do not have tight deadlines by which they must be completed. Therefore, that transition could be achieved

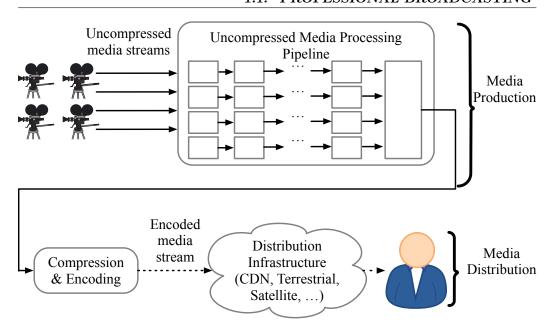

Figure 1.1: Functional overview of professional broadcasting

without considering the ability of the used commodity hardware, and of the software-stack (e.g., operating systems, hypervisors, and application-level frameworks), to deliver guaranteed delays and task completion times.

In this thesis, transition from dedicated to commodity hardware is studied for a class of performance-demanding applications, subject to real-time constraints, rendering them more challenging to implement on commodity hardware: media-production for professional broadcasting.

## 1.1 Professional Broadcasting

Professional broadcasting is the activity of acquiring one or multiple media streams, applying a pipeline of media processing operations, and delivering the processed media stream to the end users. A functional, technology-independent, overview of a generic professional broadcasting setup is depicted in figure 1.1, where a set of media streams is generated by media sources, e.g., video cameras, and microphones.

Media streams are subject to media processing, *i.e.*, to a sequence of audiovisual content alterations such as image insertion (e.g., a television channel's logo), text insertion (e.g., contextual banners related to the broadcasted program), video frame-rate adaptation, video deinterlacing, audio signal pro-

## CHAPTER 1. INTRODUCTION 1.1. PROFESSIONAL BROADCASTING

cessing, etc. Eventually, all those streams are *mixed*, *i.e.*, are merged into a single stream, which will transport the content as seen by the end-user. Mixing can consist of either *selecting* only one media input, or *merging* multiple streams according to various strategies (*e.g.*, picture-in-picture, mosaic, etc...). Those operations constitute the *media production* phase, as its finality is the production (*i.e.*, the elaboration) of the content as finally viewed by the end-user. Any audio or video compression occurring before the end of media production would result into quality degradation and latency increase — media streams are, therefore, kept uncompressed during media production.

The resulting stream is uncompressed and has a high data rate (e.g., in the order of a gigabit-per-second for a High-Definition (HD) video stream at 30 Frames Per Second (FPS)), which makes it impractical for delivery to a client. This uncompressed stream is, therefore, to be prepared for delivery during a subsequent media distribution phase, starting with compression and encoding. Those result in an encoded stream whose data-rate is in the megabit-per-second order, depending on the used compression and encoding algorithms. Finally, the encoded stream is transmitted to the end-user over one or multiple distribution channels such as Terrestrial television or radio, Satellite links, Content Distribution Networks (CDN) for Internet distribution, etc.

As shown in table 1.1, media production and distribution have different requirements. For example, a delay in the order of seconds is acceptable between the beginning and the end of media distribution (i.e., between the end of media production and media consumption by a client). However, a delay exceeding hundreds of milliseconds should not be introduced by media production, given that it includes some processing steps — e.g., mixing — which are controlled by humans operators, who, therefore, need to visualise the output of media production. That visual feedback must be obtained with a latency imperceptible to a human operator, i.e., in the order of hundreds of milliseconds at most.

As a consequence of those different requirements, the methods applicable to migrate media distribution from dedicated to commodity hardware are different from the ones applicable to migrate media production. Reviews of state-of-the-art solutions to implement media distribution and media production are given in sections 1.1.1 and 1.1.2, respectively. As detailed in the following, the media distribution field is more advanced in its migration towards commodity hardware than is the media production field, as the former is subject to less challenging data-rates and delay constraints than the latter.

|                 | Media Distribution       | Media Production                      |  |

|-----------------|--------------------------|---------------------------------------|--|

| Data rates      | $\approx$ 1 Mbit/s (com- | $\approx 1  \text{Gbit/s}$ (raw audio |  |

|                 | pressed audio and        | and videos)                           |  |

|                 | video)                   |                                       |  |

| Acceptable      | Seconds                  | Hundreds of milli-                    |  |

| latency         |                          | seconds                               |  |

| Stream replica- | Thousands of clients     | Almost none (only a                   |  |

| tion            | for a given stream       | reduced number of                     |  |

|                 |                          | endpoints involved in                 |  |

|                 |                          | production)                           |  |

| Control over    | Low because distribu-    | High because media                    |  |

| the infrastruc- | tion depends on the      | production is per-                    |  |

| ture            | medium used by the       | formed in controlled                  |  |

|                 | end-user (terrestrial,   | studios.                              |  |

|                 | satellite, Internet,).   |                                       |  |

Table 1.1: Requirements for media distribution vs production

# 1.1.1 Media Distribution: From Internet Protocol Television (IPTV) to Over-The-Top (OTT)

The development of Internet Protocol Television (IPTV) [10–12] demonstrated the feasibility of using commodity hardware and general-purpose networking equipment to implement media distribution by Internet Service Providers (ISP). IPTV relies on the ISP's Internet Protocol (IP) networks to deliver media content, transported by IP packets.

Because IPTV is implemented by ISPs, it can use two features which are only available across operator networks, *i.e.*, networks that are managed by a single operator, as opposed to features available across the wider Internet. First, IPTV leverages IP multicast (which is unavailable across the Internet), avoiding redundant packet transmissions and reducing the load on the operator network. Second, Quality-of-Service (QoS) policies can be consistently defined and enforced in operator networks, so as to prioritise IPTV streams [13], since those are less resilient to packet losses than, *e.g.*, TCP-based web traffic.

Over-The-Top (OTT)<sup>1</sup> media distribution [14] also transports media content over IP packets. Specifically, to define how media content is encapsu-

$<sup>^{1}</sup>$ Here, OTT media distribution is only considered in the context of live content, *i.e.*, in the context of professional broadcast. In the literature, OTT may also refer to techniques used to distribute Video on Demand (VoD), which, unlike live content, is not subject to delay constraints.

## CHAPTER 1. INTRODUCTION 1.1. PROFESSIONAL BROADCASTING

lated into network streams, OTT media distribution standardised transport methods such as Dynamic Adaptive Streaming over HTTP (DASH) [15] and HTTP Live Streaming (HLS) [16]. However, that OTT traffic is transmitted — as the name suggests — over the Internet, and is, therefore, likely to traverse multiple independent operator networks. As a consequence, neither IP multicast nor QoS policing are applicable to OTT media distribution, differentiating it from IPTV. OTT traffic is necessarily unicast and is subject to best-effort service. Therefore, IP multicast and QoS policing (used in IPTV) need both be replaced by alternative techniques, which are not dependent on the network infrastructure, and which are detailed in the following.

First, because those transport methods use the Hypertext Transfer Protocol (HTTP), they can be implemented by reusing components alreadyused for content distribution, such as web servers and Content Delivery Networks (CDN) [17–21]. The caching and geographical replication features offered by CDNs enable network load reduction when streaming to several end-users, and hence, are an alternative to IP multicast (used in IPTV), although they are independent from the network infrastructure, and are usable across the Internet.

Second, to maintain a guaranteed Quality of Experience (QoE) in the absence of QoS policing, OTT media distribution exploits adaptive bitrate streaming [22–24], i.e., the receiver-initiated adaptation of the bitrate of the streamed media content to the network conditions (as evaluated by the media receiver). For example, DASH and HLS belong to a class of transport methods, implementing adaptive bitrate streaming, and called HTTP Adaptive Streaming (HAS). HAS-based transport methods all rely on chunking, *i.e.*, the discretisation of the media stream into atomic elements, called encoded chunks. Encoded chunks are sequentially generated by the "Compression and Encoding" stage of figure 1.1. Specifically, that stage discretises the input uncompressed media stream into a sequence of uncompressed chunks — each typically amounting to two to four seconds of media content for DASH and HLS. Then, each uncompressed chunk is compressed and encoded using multiple encoding rate, and hence, with multiple quality levels, yielding chunks of various sizes. The resulting encoded chunks are finally made available for OTT distribution, through web servers and CDNs. Upon media playback, the receiver continuously downloads encoded chunks corresponding to consecutive intervals of time, and decodes them to reproduce the original media content. For each interval of time, depending on the current connectivity conditions, the receiver chooses the bitrate (and, therefore, size) of the encoded chunk to download — resulting into an implementation of adaptive bitrate streaming.

As documented in [25], media chunking and HAS both increase the delay

between media production and media playback at the receiver. That increase is mainly due to two reasons. First, the generation of an encoded chunk of two seconds requires the availability of two seconds of uncompressed media prior to their compression, encoding, and delivery via web servers and/or CDNs. Therefore, the Compression and Encoding stage must accumulate at least two seconds of uncompressed media content before emitting the first encoded chunk, *i.e.*, that stage adds a delay necessarily superior to two seconds. Second, playback by the receiver requires media buffering, to accommodate for any network delay variation (and avoid any playback interruption). This buffering occurs with the granularity of a full encoded chunk, *i.e.*, it introduces a delay, which is an integer multiple of the duration of an encoded chunk, *e.g.*, two seconds. That coarse granularity is therefore likely to increase the playback delay (as observed by the receiver).

To summarise, while the techniques developed for OTT media **distribution** have been showed to enable the transition of media distribution to a general-purpose infrastructure (e.g., IP packet networks, web servers, CDNs), those techniques necessarily introduce a delay superior to a second, rendering them impractical to use for media **production**.

# 1.1.2 Media Production: The Serial Digital Interface (SDI)

Media production has historically been implemented by chaining dedicated hardware appliances, interconnected by the Serial Digital Interface (SDI) [26–29], as standardised by the Society of Motion Picture and Television Engineers (SMPTE). SDI specifies an encapsulation of media content over coaxial cables, at a fixed data-rate of 270 Mbit/s for Standard Television Television (SDTV), and either 1.485 Gbit/s, or  $\frac{1.485\,\text{Gbit/s}}{1.001}\approx 1.483\,\text{Gbit/s}^2$  for High-Definition Television (HDTV). SDI was designed as a replacement for analog video transmission standards [31] used in media production before the development of digital television [32–34]. As a consequence, SDI shares several features with analog video transmission standards over coaxial cables, and offers a type of connectivity that is fundamentally different from that provided by IP networking.

<sup>&</sup>lt;sup>2</sup>The latter 1.483 Gbit/s rate is mainly used in North America, and the 1.001 ratio can be traced back to the frame rate of  $\frac{30}{1.001} \approx 29.97$  FPS defined by the National Television System Committee (NTSC) analog color system [30].

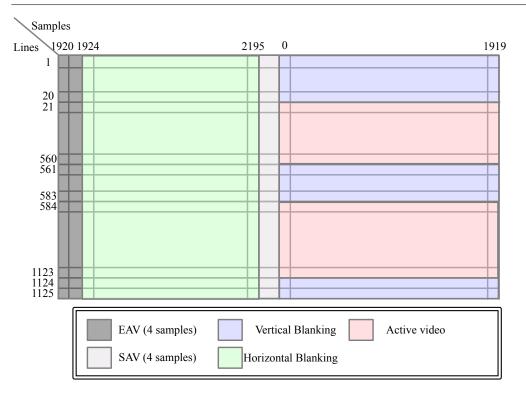

Figure 1.2: Structure of an SDI video frame encoding a High-Definition, interlaced, 1920x1080, 30 frames-per-second video stream. Each line contains synchronisation sequences denoted as End of Active Video (EAV) and Start of Active Video (SAV). Synchronisation sequences are 4-samples long and contain information describing the current line. The frame is separated in two fields from line 21 to 560 and 584 to 1123, corresponding to oddly and evenly numbered lines on the video.

#### The Serial Digital Interface: Legacy from Analog Video

Following the SDI specification, a media stream is transmitted as a sequence of **video frames**. Each video frame is transmitted as a sequence of **video lines**, and each video line is transmitted as a sequence of **video samples**. A video sample is encoded as two consecutive **10-bits words**. This specifies a sequence of 10-bits words which are channel-coded — by scrambled Non Return to Zero Inverted (NRZI) coding [35] — and serially transmitted over the wire.

The information contained in a video frame and a video line are better understood when considering analog video and Cathode Ray Tube (CRT) displays. Schematically, a CRT screen is periodically scanned, line-by-line, by an electron beam, whose intensity is modulated by the image to be displayed,

i.e., by the input analog video signal. At the end of the scan of each line, the electron beam must be repositioned at the beginning of the next line. This repositioning time is the **Horizontal Blanking Interval (HBI)**, and is included in the input analog video signal. Similarly, at the end of the last scan line, the electron beam must be repositioned at the top of the screen, during the **Vertical Blanking Interval (VBI)**. Finally, to improve the perceived frame-rate, instead of displaying, e.g., 30 images per second, **interlaced video** works by first scanning all the odd-numbered lines, and then, after a first VBI, scanning all the even-numbered ones. That doubles the refresh-rate, at the cost of only refreshing half the image at each scan, i.e., between each VBI.

SDI was directly derived from the concepts from analog video thus, a video frame transmitted by SDI also provisions one or two (if the transmitted video is interlaced) VBIs. The video lines corresponding to those are defined as **inactive lines** while the video lines containing information used to display an image are **active lines**. Similarly, in an SDI active video line, some video samples correspond to the HBI and are **inactive samples**, while others each contain two 10-bits words encoding the color of an image pixel, and are **active samples**.

Figure 1.2 depicts the structure of an SDI frame containing interlaced, High-Definition (HD) video at 30 frames per second. This structure shows that a significant fraction of the 1.485 Gbit/s serial data stream corresponds to HBIs and VBIs and does not carry any active video, *i.e.*, any information required to display the current picture. To avoid wasting that fraction of the channel's capacity, for each SDI video frame, VBIs and HBIs are used to carry **ancillary data** [36], *i.e.*, non-video information related to the SDI video frame.

Ancillary data embedded in the HBI is called Horizontal Ancillary Data (HANC) and consists of content that needs to be synchronised with the granularity of a video line. With the example depicted in figure 1.2, that granularity is  $\frac{1}{1125*30\,\mathrm{Hz}} \approx 29.6\,\mathrm{\mu s}$ . Because of this fine granularity, HANC data is typically used to embed audio samples [37,38], accurately synchronised with the current video. Ancillary data embedded in the VBI is called Vertical Ancillary Data (VANC) and consists of content that needs to be synchronised with the granularity of the full SDI video frame, e.g., per-frame closed-captions<sup>3</sup> [40,41].

Finally, an SDI receiver consumes SDI video frames at a fixed framerate, defined consistently across a **media production** setup. To guarantee

<sup>&</sup>lt;sup>3</sup>This is, in essence, no different from the way teletext is embedded in the VBI of analog video broadcast transmissions [39].

## CHAPTER 1. INTRODUCTION 1.1. PROFESSIONAL BROADCASTING

such a consistent **frequency**, a common time reference — i.e., **a clock** — must be delivered to every SDI-based appliance. Furthermore, media streams originating from different media sources (e.g., different video cameras) must be sampled with the same **phase**, i.e., the acquisition of the first video sample of the first video line must be synchronised across all media sources. Indeed, an SDI-based appliance mixing input streams with unsynchronised phases can only generate a consistent SDI output stream by artificially delaying all input streams, except the one with the most advanced phase. This is suboptimal, as media production is very sensitive to end-to-end delay, as summarised in table 1.1.

To ensure phase synchronisation in a media production setup, all the SDI-based appliances receive a shared **external signal**, defining the times at which the sampling of SDI video frames should start. A possible implementation of that external signal is the **tri-level synchronisation signal**, which has standardised electrical specifications [31]. Furthermore, because that external signal defines the occurrence times of periodic events (*i.e.*, SDI video frame sampling), it is usable as a clock shared by all SDI-based appliances and, therefore, also enables frequency synchronisation.

To summarise, the SDI specification is highly influenced by analog video transmission, and is very similar to the straight-forward digitisation thereof. As a consequence, SDI-based transmissions have a **fixed data-rate**, independently from the information actually transmitted, *i.e.*, whether it is only solely video, or video and ancillary data such as audio and closed-captions. Because of that fixed-rate, an external signal is distributed across a media production setup to synchronise all SDI-based appliances.

#### SDI Video Routers

As depicted in figure 1.1, a media production workflow consists of a chain of media sources and processing elements. However, directly interconnecting them with physical SDI cables limits the flexibility of the physical installation: any workflow evolution requires time-consuming, and error-prone, physical rewiring of the media production setup. That lacks of flexibility motivated the use of **SDI video routers** to interconnect media sources and processing elements.

SDI video routers – also called **video switchers** – appeared early during the transition from analog to digital television [42]. An SDI video router is a piece of equipment with multiple SDI inputs and outputs, and is configurable to replicate each input on one or multiple outputs. In a media production setup, all the SDI outputs from the media sources and processing elements are connected to the inputs of an SDI video router, and all the

SDI inputs from the media processing elements are connected to its outputs. As a consequence, any media-processing pipeline can be implemented by reconfiguring the SDI video router, with no physical rewiring. This allows to dynamically repurpose the physical infrastructure to accommodate for multiple media production pipelines. It is, therefore, a first step into media processing resource pooling.

#### SDI connectivity vs the IP networking model

The serial, fixed-rate, synchronous, data transmission model, as defined by SDI, is different from the packet-based IP networking model:

- 1. SDI only allows **point-to-point unidirectional** data transmission, *i.e.*, a physical SDI connexion has only one input and one output. Consequently, any media stream replication must be performed by a specific piece of equipment (an SDI video router). This is in contrast to the IP networking model allows either **point-to-multipoint unidirectional** data transmission (through IP multicast), or **point-to-point unidirectional** or **bidirectional** data transmission (through IP unicast). The network infrastructure, therefore, provides stream replication through IP multicast<sup>4</sup>.

- 2. The SDI specification allows **no multiplexing** over a given physical channel, *i.e.*, one coaxial cable can transport only one media stream. For example, an SDI connection capable of transporting an HDTV stream (*e.g.*, at 1.485 Gbit/s) cannot be reconfigured to carry multiple SDTV streams (each of 270 Mbit/s), despite the SDI physical layer being theoretically capable of doing so.

- That is different from the IP network model, as the latter is packetbased, and enables the **multiplexing of packets belonging to different logical flows** over a given network path. In other words, the IP network model allows network capacity pooling across different logical flows.

- 3. In a media production setup, all SDI-based data transmission are **synchronous with a centralised clock**. This raises operational challenges because the tri-level synchronisation signal must be explicitly

<sup>&</sup>lt;sup>4</sup>Here, IP multicast is assumed to be a viable option for the transport of media production streams, because the packet switches constituting a potential IP-based media production setup are assumed to be all operated by a single entity. It would not be the case if a media production setup spanned over multiple network domains which are connected through the Internet.

distributed to all appliances. For example, the lengths of the cables used to distribute that signal have an impact on the signal transmission delay, and thus, might cause inconsistent synchronisation of those appliances. The IP networking model does not make any synchronisation assumptions on the underlying link-level layer, which can, therefore, implement asynchronous packet transmissions. For example, at the physical-layer, a 802.3 Ethernet [43] packet is transmitted synchronously with a clock, which is local to the transmitter. At the receiver, the Physical Medium Attachment (PMA) layer includes a Clock and Data Recovery (CDR) function which, for each incoming packet transmission, synchronises with the transmitter's clock, and recovers the transmitted packet. As a consequence, no explicit clock distribution is needed across an IP/Ethernet network, making the latter easier to manage than an SDI-based installation.

The IP networking model differs from SDI connectivity in a way similar to how packet-switched and circuit-switched communications differ. For example, SDI video routers and Plain Old Telephone Service (POTS) switches are essentially similar, as switching occurs on a per-call basis (in the case of telephone services) or on a per-programme basis (in the case of media production for professional broadcast). This is opposed to packet switching, which occurs on a per-packet basis, with no notion of established connection. In that sense, a parallel can be made between the migration of media production from dedicated to commodity hardware, and the evolution from circuit-switched to packet-switched networking.

## 1.2 Media Production on Commodity Hardware

This section gives an overview of the existing standards and technologies, which enable the migration of media production from SDI-based to IP-based media transport, and from SDI-based circuit-switching to IP-based packet-switching. Furthermore, the main limitations of those standards and technologies are presented.

## 1.2.1 Packetising SDI

To bring the benefits from the IP networking model (*i.e.*, point-to-multipoint communication, the ability to multiplex multiple media streams over a single physical connection, and the absence of required physical-level clock synchronisation) to media production, a natural idea consists of packetising the serial data stream defined by the SDI standards, and encapsulating the result

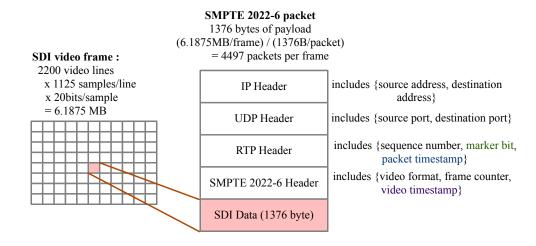

marker bit = set if the packet is the last of the SDI video frame

packet timestamp = sampling time of the embedded data

video timestamp = increasing counter, synchronous with the number of transmitted samples.

Figure 1.3: Structure of a SMPTE 2022-6 packet transporting an SDI stream

into IP packets. This approach was specified in 2012 by the SMPTE 2022-6 standard [44], and is historically the first step to enable the transport of media production streams over IP networks.

#### **SMPTE 2022-6**

As depicted in figure 1.3, a SMPTE 2022-6 packet includes IP, User Datagram Protocol (UDP) [45], Real-Time Protocol (RTP) [46] and SMPTE 2022-6 headers. The endpoint identifiers at the IP layer (source and destination addresses) and at the UDP layer (source and destination ports) provide a four-tuple, uniquely identifying a SMPTE 2022-6 media stream. As a consequence, packets belonging to different SMPTE 2022-6 media streams can be multiplexed over a shared commodity network infrastructure. Moreover, IP multicast enables in-network replication of IP packets, and hence, of media streams.

SMPTE 2022-6 packets are derived from SDI data by individually dividing each SDI video frame into a sequence of 1376-byte chunks. As the size of an SDI video frame is not necessarily a multiple of 1376 bytes, the last chunk of that sequence is completed with padding until its size reaches 1376 bytes. As depicted in figure 1.3, each chunk is prepended with a SMPTE 2022-6 and an RTP header.

## CHAPTER 1. INTRODUCTION 1.2. MEDIA PRODUCTION ON COMMODITY HARDWARE

The RTP header provides a packet sequence number and a packet timestamp. Because the IP network layer provides best-effort service, packet drops may occur. Those are detectable by the receiver, as a sequence number discontinuity. Moreover, best-effort service does not formally provide any guaranteed packet transmission delay, *i.e.*, the packet reception time is not sufficient to infer the associated media sampling time. It must therefore be embedded explicitly, as the RTP packet timestamp. This piece of data enables SMPTE 2022-6-based media processing to be performed synchronously with regards to a centralised clock, and hence enables mixing applications, similarly to the mixing of multiple, phase-synchronised, SDI streams. Finally, if the chunk transported by the RTP packet is the last of an SDI video frame, a marker bit contained in the RTP header is set.

The SMPTE 2022-6 header describes the format of the transported SDI stream (video frame-rate and resolution), and includes a frame counter and a video timestamp. The frame counter is incremented for each newly transmitted SDI frame, and thus provides a unique identifier for each of these. The video timestamp is a counter, giving the number of transmitted video samples (*i.e.*, pairs of 10-bit words) before the first video sample fully included in the current chunk. Contrary to the RTP packet timestamp, the value of the video timestamp is not necessarily synchronised with a centralised clock. As the frequency of the video timestamp is equal to the video sampling frequency (*e.g.*, for interlaced HD video at  $\frac{30}{1.001}$ FPS, that frequency is 1125 lines × 2200 samples ×  $\frac{30}{1.001}$ FPS =  $\frac{74.25}{1.001}$  MHz), it can be used by a SMPTE 2022-6 receiver to recover the underlying SDI video sample clock [44].

## From the Tri-Level Synchronisation Signal to Precision Time Protocol (PTP) clocks

In an SDI-based installation, all equipment is synchronised by the trilevel synchronisation signal. Ethernet-based networks do not provide a similar physical-layer-based synchronisation feature. Thus SMPTE 2059 [47,48] specifies the use of the Precision Time Protocol (PTP) [49] to distribute a common time reference in a media production setup. The Technical Recommendation 4 (TR-04) by the Video Service Forum (VSF) [50] completes the SMPTE-provided standards by specifying how the RTP packet timestamps from SMPTE 2022-6 are to be deterministically derived from a PTP-distributed time reference.

#### Use Case: Replacing SDI Video Routers with Packet Switches

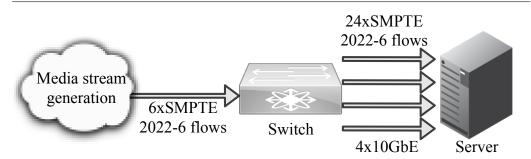

Migrating a media production setup from dedicated to commodity hardware requires the replacement of SDI-based media-processing equipment with general-purpose, IP-based equipment. Because of the cost of this equipment, this migration is, most commonly, gradual. Specifically, the first step of this migration consists of only replacing SDI video routers with their IP-based counterparts, *i.e.*, IP/Ethernet packet switches transporting SMPTE 2022-6 streams [51]. This first step alone bring two operational benefits:

- 1. As the throughput of a single HD SMPTE 2022-6 stream is 1.5 Gbit/s, a single full-duplex 10 Gbit/s Ethernet port on a packet switch can simultaneously receive and transmit up to six different media streams. Therefore, it is functionally equivalent to six SDI inputs and six SDI outputs on an SDI video router.

- From an operational perspective, in a media production setup, transporting a given number of media streams requires less ports (and less cables) when media-transport is IP-based than when it is SDI-based.

- 2. Any physical piece of equipment implementing SDI-based video routing depends on the transported media format. For example, an SDI video router designed for SDTV streams cannot receive and transmit HDTV streams, despite the physical SDI connectors being identical. Consequently, any video format evolution requires upgrades of the SDI video routers interconnecting the media production setup. IP/Ethernet based packet switches are agnostic to the media format of the transported streams, provided that their throughputs do not exceed the network link capacities. That makes a media production setup based on IP/Ethernet packet switches more evolutive than one based on SDI video routers.

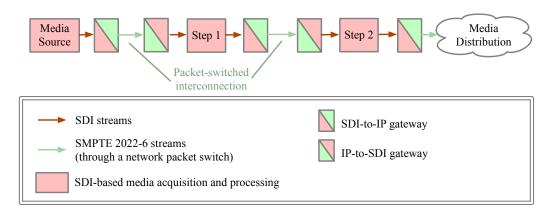

To enable a gradual migration from SDI-based to IP-based equipment, the replacement of SDI video routers with IP packet switches should be possible without replacing all SDI-based media processing appliances with IP-based ones. Therefore, to convert SDI streams into SMPTE 2022-6 ones (and vice versa), SDI-to-IP (or IP-to-SDI) gateway devices have appeared.

Specifically, media sources generate SDI streams, which are transformed into SMPTE 2022-6 streams and fed into network packet switches. For each step of a media processing pipeline, the SMPTE 2022-6 streams are switched to an IP-to-SDI gateway, media processing is performed by SDI-based equipment, and the resulting stream is transmitted to an SDI-to-IP gateway, and then back to the network packet switch. Such a **hybrid media production**

## CHAPTER 1. INTRODUCTION 1.2. MEDIA PRODUCTION ON COMMODITY HARDWARE

Figure 1.4: Functional illustration of an hybrid SDI and SMPTE 2022-6 media production setup. SDI-based media acquisition and processing components are interconnected by a packet switched architecture, SDI-to-IP and IP-to-SDI gateways.

setup, mixing SMPTE 2022-6 based interconnection (with commodity network packet switches) and SDI-based media acquisition and processing (with dedicated hardware) is depicted in figure 1.4.

While the sole replacement of SDI video routers with network packet switches brings clear operational benefits, it is only the first step in the migration from dedicated hardware to commodity hardware. The next natural step consists of directly processing SMPTE 2022-6, with commodity hardware capable of transmitting and receiving network packets.

## 1.2.2 Software-based Media Processing on Commodity Servers: Challenges and Limitations of SMPTE 2022-6

Processing a packet-based, SMPTE 2022-6 stream with commodity servers appears to be a straight-forward process, as those are equipped with inexpensive general-purpose Network Interface Cards (NIC), capable of receiving and transmitting network packets at multi-gigabit data-rates. However, while SMPTE 2022-6 enables replacing SDI-based connectivity in a hybrid media production setup, that standard is ill-adapted to software-based media processing for two main reasons: media essence multiplexing, and undefined packet transmission timing.

#### From Multiplexed To Separate Media Essences

As a packetised version of SDI, a SMPTE 2022-6 stream embeds audio, video, and ancillary data. When the receiver is implemented as SDI-based dedicated hardware, multiplexing those three logical data streams over a single serial digital transmission brings operational benefits, as it avoids the necessity for three distinct physical connexions. Moreover, the digital logic required to demultiplex video, audio and ancillary data has limited complexity, as the layout of an SDI video frame and the locations of VANC and HANC are well-defined by the SDI standards. In other words, multiplexing the audio, video, and ancillary **media essences** $^5$  in the SDI payload is adapted to media production setups where, eventually, media streams are received and processed as SDI streams — e.g., the hybrid media production setup of figure 1.4.

However, if the receiver consists of software processing packets through a network stack, the previous benefits of multiplexed media essences vanish. First, a network path can already, natively, multiplex as many logical data streams as needed, each of which being identified by a unique **five-tuple** (IP protocol number, the source and destination IP addresses, and source and destination transport-layer ports). Five-tuple-based demultiplexing only requires parsing IP and UDP headers. Demultiplexing audio, video, and ancillary data streams from a SMPTE 2022-6 stream is more CPU-intensive, as it requires parsing each 10-bit word of each SMPTE 2022-6 packet. Further, in a software-based media production setup with multiple servers hosting media-processing application, audio, video and ancillary data streams are not necessarily processed at the same location, which makes the use of the multiplexed SMPTE 2022-6 format impractical.

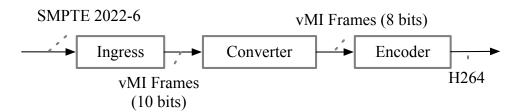

Because multiplexed media essences — as required by SMPTE 2022-6 — are unadapted to software-based media processing, the SMPTE 2110 family of standards [52] was developed. It specifies distinct packet-based transport for each media essence: SMPTE 2110-20 [53] for video transport, SMPTE 2110-30 [54] for audio transport and SMPTE 2110-40 [55] for ancillary data transport.

While audio and ancillary data transported in an SDI or a SMPTE 2022-6 stream are naturally synchronised with the corresponding video (as they are associated with a given SDI video frame for VANC or with a given video line for HANC), that synchronisation disappears when decoupling the trans-

<sup>&</sup>lt;sup>5</sup>Despite its lacking of a formal definition, the term of art **media essence** designates a sub-stream belonging to a media stream, and transporting media data of a single nature. Typically, a media stream has three media essences: video data, audio data, and ancillary data.

## CHAPTER 1. INTRODUCTION 1.2. MEDIA PRODUCTION ON COMMODITY HARDWARE

port of the different media essences, as specified by SMPTE 2110. SMPTE 2110-10 [56] addresses that issue by specifying a unified timing framework, connecting the different timestamps appearing in the packet transporting audio, video, and ancillary data.

To summarise, SMPTE 2110 enables separate processing of the audio, video and ancillary data component included in a media stream, without sacrificing the synchronisation between those components. That eases software-based processing, as it removes the requirement for any CPU-intensive demultiplexing of the different media essences included in an SDI or SMPTE 2022-6 stream. Moreover, it eases the pooling of compute and network resources in a data-centre, as the different essences are transported independently and can be processed by different pieces of equipment.

#### **Undefined Packet Transmission Timing**

The SMPTE 2022-6 standard only specifies a packet format to transport SDI data and does not mandate any property relating to packet transmission timing. As a consequence, it is implied that packet transmissions are lossless and occur in such a way that a SMPTE 2022-6 receiver is always able to consume a packet from its internal buffer, if it needs to do so. In other words, SMPTE 2022-6 does not include any flow or congestion control mechanism, but relies on the assumption that the network provides reliable transport and ensures transmission delays consistent with the packet consumption schedule of the receiver.

In practice, despite an unspecified timing behaviour, SMPTE 2022-6 transmitters are implemented so that packets are transmitted at a constant packet-rate, as implied, e.g., by the data sheet of a Xilinx FPGA intellectual property core implementing an SDI to SMPTE 2022-6 converter [57]. However, even if packet transmissions occurs at a constant-rate, i.e., with a constant Packet Inter-arrival Time (PIT), an IP/Ethernet packet-switched network introduces a non-constant delay, causing packet arrival jitter at a SMPTE 2022-6 receiver, which, therefore, needs buffer packets, so as to be able to consume them at a constant rate. Because SMPTE 2022-6 does not constraint that jitter, buffer dimensioning at the receiver is challenging and must be done empirically.

If SMPTE 2022-6 is only used to replace SDI video routers with packet switches in a hybrid media production setup as depicted in figure 1.4, packets are periodically transmitted by SDI-to-IP gateways, and periodically consumed by IP-to-SDI gateways. Latency measurements [58] show that packet switches typically used for hybrid media production introduce a jitter lower than two microseconds. As a consequence, and given that the nominal PIT

of a SMPTE 2022-6 stream — e.g., 7.419 µs when transporting interlaced, 1920x1080, 30 frames-per-second video — is considerably higher than that jitter, very limited buffering at the IP-to-SDI gateway is sufficient to ensure that packet can be consumed at a constant-rate.

Conversely, commodity servers running packet-processing software introduce substantial jitter when receiving and transmitting SMPTE 2022-6 streams. Because SMPTE 2022-6 does not specify the jitter that a receiver must tolerate, it is impossible to formally specify real-time constraints on a packet-processing software, so that it accommodates any SMPTE 2022-6 receiver.

Consequently, the SMPTE 2110 family of standards constrains timing more explicitly than does SMPTE 2022-6. In particular, SMPTE 2110-21 [59] defines a set of packet transmission **profiles** to which any SMPTE 2110 sender must conform. A profile is formally defined by the behaviour of a packet receiver, *i.e.*, a receive buffer size, and a packet consumption schedule. A SMPTE 2110 sender conforms to a profile if no receive buffer overflow or starvation occurs for a hypothetical packet receiver behaving as defined in the profile, and connected to the sender by way of an hypothetical network introducing no delay.

For example, hardware-based receivers may have reduced buffering capabilities — e.g., because they may be implemented on Field Programmable Gate Arrays with limited memory. Consequently, SMPTE 2110-21 defines a Narrow (N) profile, associated with a reduced buffer size. An SMPTE 2110 sender, conforming to the N profile, must transmit packets in such a way that a receiver with reduced buffering capabilities will experience no starvation nor overflow. In particular, such a sender is compatible with hardware-based receivers. Similarly, software-based receivers have higher buffering capabilities — e.g., because modern NICs support large receive queue sizes and thus, SMPTE 2110-21 defines a Wide (W) profile, associated with a high buffer size. Consequently, senders compliant with the W profile are compatible with software-based receivers, but may incur buffer overflow or starvation on hardware-based receivers.

In summary, as neither any flow control method nor any packet transmission timing property are defined by SMPTE 2022-6, that standard cannot be used beyond the scope of hardware-based SMPTE 2022-6 generation (through SDI-to-IP gateways), delivery (through packet switches) and consumption (through IP-to-SDI gateways), *i.e.*, it cannot be used for software-based media production stream processing. Indeed, the latter yields non-negligible jitter thus, an accurate specification of packet transmission timing is needed, which is achieved by the SMPTE 2110-21 standard. That standard specifies the packet transmission regularity required from a SMPTE 2110

sender by providing normative information, which is differentiated depending on the type of the targeted receiver (software- or hardware-based).

Migrating media production from dedicated hardware to commodity servers and networking equipment is a gradual process, and raises challenges due to fundamental differences between SDI-based and packet-switched data transport. While the SMPTE 2022-6 and 2110 standards have been shown to offer the tools to accurately **specify** the desired behaviour of both hardware-based or software-based packet-based media production components, those standards leave open the problem of **implementing** such components.

#### 1.3 Thesis Contributions

Going one step beyond the **specification problem** (largely covered by SMPTE 2110 and SMPTE 2022-6), this thesis addresses the **implementation problem**, which is:

To what extent can software-based media production be realised on commodity servers and general-purpose networking hardware?

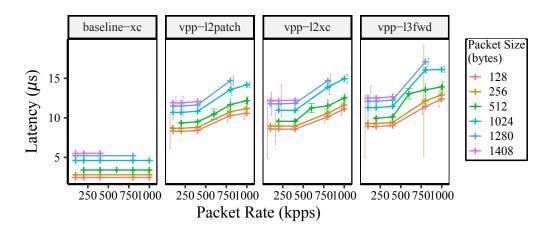

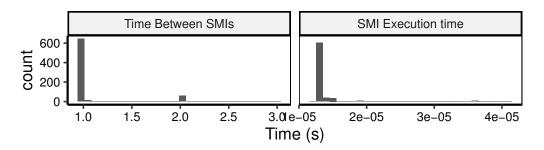

Chapter 2 proposes a reproducible, software-based, experimental methodology to evaluate the jitter incurred by a periodic packet stream — such as a SMPTE 2022-6 stream — upon reception by software executed on a commodity server. Specifically, that methodology includes the exhaustive enumeration of all jitter sources — depending on the hardware, the used operating system, the properties of the network-stack, etc — and the relative contributions thereof to the overall jitter. That methodology is applied to a Linux-based, x86\_64 commodity server receiving a SMPTE 2022-6 stream. The obtained experimental results support the fact that, as stated in section 1.2, software-based packet processing for media production introduces an amount of jitter which is incompatible with hardware-based receivers with a limited buffering capability.

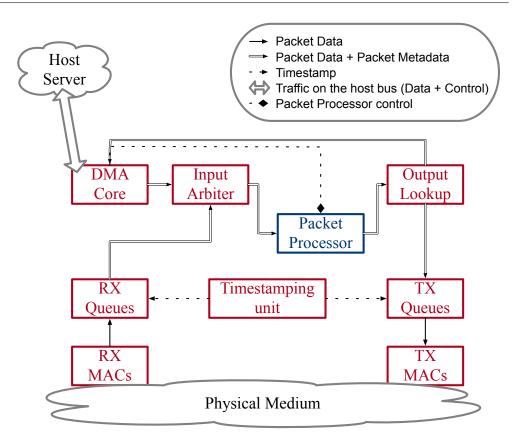

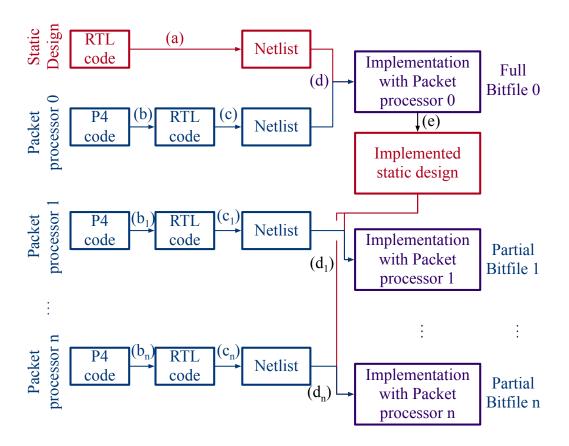

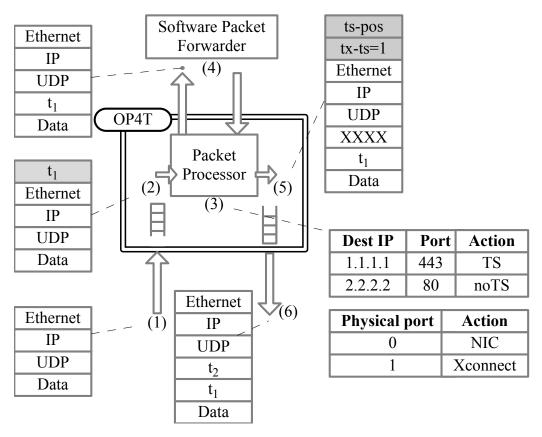

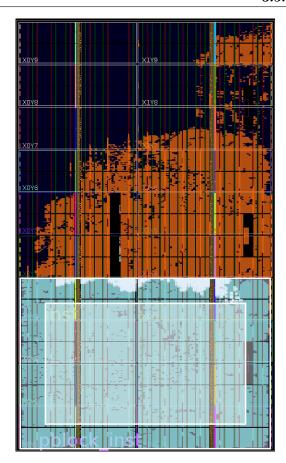

The contribution presented in chapter 3 extends jitter evaluation to hard-ware-based methods. Specifically, the development of hardware-based packet timestamping tools is made easier, through the proposal of a novel FPGA-based framework: the Open Platform For Programmable Precise Packet Timestamping (OP4T). By leveraging the packet-processing-oriented P4 programming language [60], OP4T renders the design of custom, hardware-based measurement tools, accessible to broadcasting and network operators with little hardware design expertise. Furthermore, an implementation of OP4T is experimentally evaluated, and shown to allow packet timestamping with a

microsecond-scale accuracy — which is necessary to assess the conformity of media production streams to packet timing profiles, such as those specified in SMPTE 2110-21.

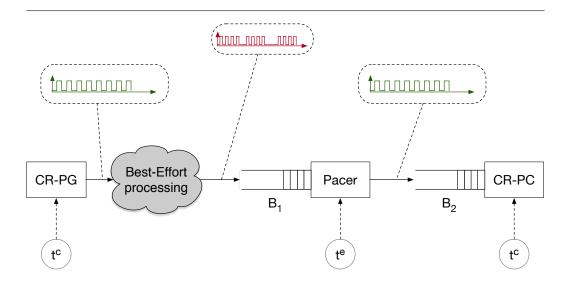

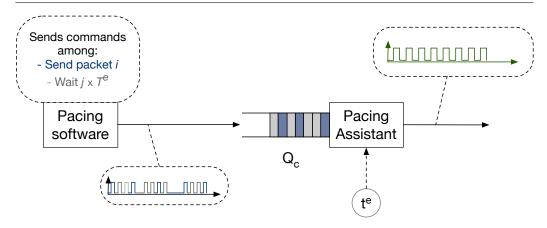

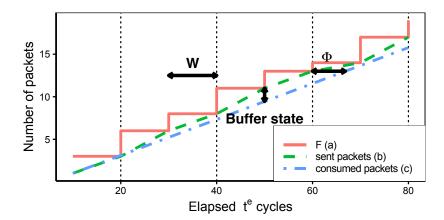

Chapter 4 offers an extensive analysis of packet pacing on commodity server, *i.e.*, the transmission of a packet stream, as periodically as possible, and with a minimal jitter. To that end, a mathematical definition of jitter is first proposed, and then, is used to expose the root causes limiting the accuracy of software-based packet pacing on commodity servers. To overcome that limitation, this chapter introduces the notion of **pacing assistant**, *i.e.*, an auxiliary component, external to the server, and which is able to provide sufficient assistance to the server, to enable high-accuracy packet pacing. A pacing architecture, and algorithms relying on a pacing assistant, are given and the achievable jitter is mathematically quantified. Furthermore, pacing assistants are shown to be effectively implementable with existing commodity hardware and packet switches and thus, are proven not to be purely abstract constructs. In summary, the work of chapter 4 is a key enabler for the transmission of low-jitter SMPTE 2022-6 and 2110 packet streams for media production on commodity servers.

Finally, chapter 5 proposes a software framework and architecture, which ease the implementation of media-processing applications. That is achieved by abstracting media transport away from media processing, *i.e.*, by hiding the entire packet processing details from media-processing applications. Therefore, instead of the traditional socket API, a media-processing application is exposed a **virtual Media Interface (vMI)**, which, instead of packets, relies on a coarser data unit: **media frames**. A media frame is a generalisation of an SDI video frame, *i.e.*, correspond to a an atomic element belonging to a media stream. In chapter 5, that vMI architecture is specified, implemented, and shown to improve the performance and scalability of realistic media processing pipelines.

#### 1.4 Publications and Software Production

This section enumerates the scientific and software production resulting from this thesis.

- Arthur Toussaint, Mohammed Hawari, Thomas Clausen, "Chasing Linux Jitter Sources for Uncompressed Video" in 2018 14th International Conference on Network and Service Management (CNSM), derived from the work presented in chapter 2.

- Mohammed Hawari, Juan-Antonio Cordero-Fuertes, Thomas Clausen,

## CHAPTER 1. INTRODUCTION 1.4. PUBLICATIONS AND SOFTWARE PRODUCTION

"High-Accuracy Packet Pacing on Commodity Servers for Constant-Rate Flows" accepted for publication in *IEEE/ACM Transactions On Networking*, derived from the work presented in chapter 4.

- Mohammed Hawari, Axel Taldir, André Surcouf, Yoann Desmouceaux, Thomas Clausen, "vMI: Software Architecture for Transparent High-Performance Media Transport" submission in preparation, derived from the work presented in chapter 5.

- Mohammed Hawari, Thomas Clausen, "OP4T: Bringing Advanced Network Packet Timestamping into the Field" submission in preparation, derived from the work presented in chapter 3.

- The software and hardware design developed for OP4T, open-source release in preparation, derived from the work presented in chapter 3.

- Cisco Herisson, available at https://github.com/cisco/herisson as open source code, derived from the work of chapters 4 and 5.

# CHAPTER 1. INTRODUCTION 1.4. PUBLICATIONS AND SOFTWARE PRODUCTION

# Chapter 2

# Chasing Linux Jitter Sources for Uncompressed Video

As discussed in chapter 1, the development of network-based transport for media streams — such as SMPTE 2022-6 and SMPTE 2110 — is an enabler for software-based media processing on commodity servers, because those have Network Interface Cards (NICs), and, therefore, can receive, process, and transmit network packets. However, those streams have high datarates — around 1.5 Gbit/s for SMPTE 2022-6 — and high packet-rates around 135000 packets per second for SMPTE 2022-6 — causing Packet Inter-arrival Times (PIT) in the order of a 7.41 µs. Moreover, chapter 1 detailed the reasons justifying those streams undergoing Constant Rate (CR) packet transmission, and justifying their sensitivity to packet jitter. As a consequence, it is critical to understand and to be able to quantify the jitter introduced by software-based packet processing of CR packet streams, when it is performed on commodity servers running general-purpose Operating Systems (OS). An understanding of this jitter informs of the suitability of using commodity servers for software-based media-processing, and informs on the buffering capacity required at a SMPTE 2022-6 or 2110 receiver consuming a software-processed media stream.

In this chapter, the term Video Processing Function (VPF) generically designates a piece of software receiving a packet-based media stream.

#### Related Work

Understanding jitter on general-purpose OS'es has, especially, been studied for real-time or High-Performance Computing (HPC) applications. OS jitter quantifies how unpredictable the performance of a running application will be. An experimental analysis of the effects hereof on CPU-bound

tasks in a distributed HPC environment is given in [61] – which shows that jitter affects the overall performance of multi-stage workloads, where each stage is running on parallel nodes. Specifically, jitter significantly impacts the synchronisation steps between each stage, incurring a significant waste of computing capacity. In-kernel methods to quantify accurately the contribution of each jitter source to the overall system jitter are developed and evaluated in [62,63].

For hard real-time applications, a deterministic lower bound on the performance is required. A recurring problem is determining the variability of the response time i.e., the total elapsed time from when an interrupt request is raised, and until the corresponding application-level thread is scheduled. From this perspective, [64] compares Real-Time Operating Systems (RTOS) and general purpose OS'es, in the context of embedded systems used in experimental nuclear physics.

Aside from the analysis in [65] of periodic networked systems with events in the order of 100 µs on a FreeBSD-based Commercial Off-The-Shelf (COTS) server, little attention has been given to characterising jitter on periodic events.

Yet, with SMPTE 2022-6 receivers expecting a CR stream giving rise to a packet arrival time with a periodicity in the order of 7.41 µs, if a VPF is to be successfully executed on a COTS server, a granular understanding of its jitter properties is required.

#### Statement of Purpose

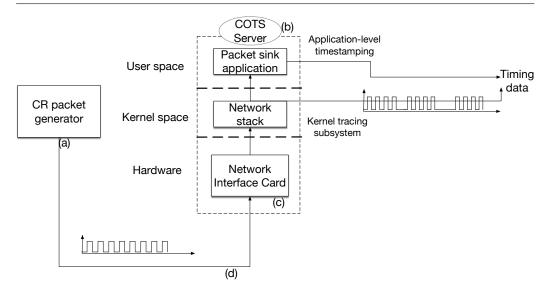

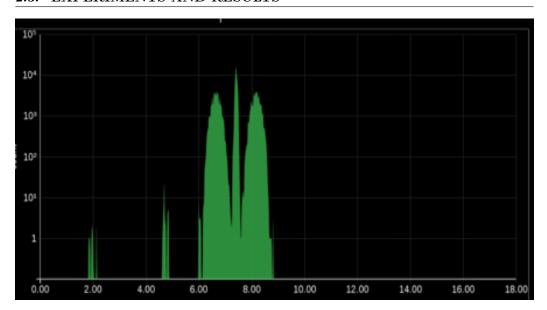

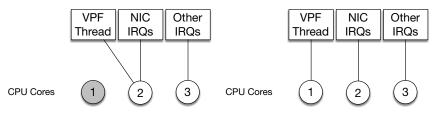

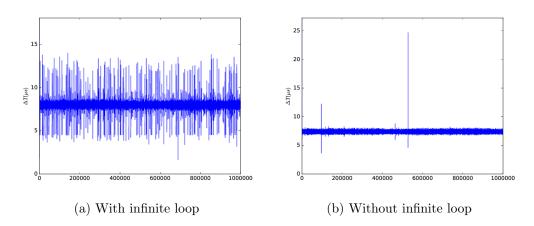

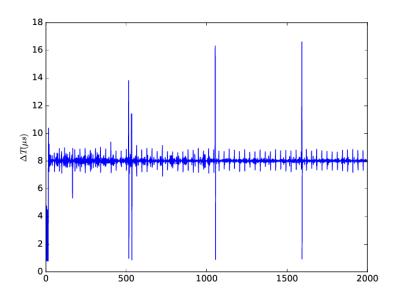

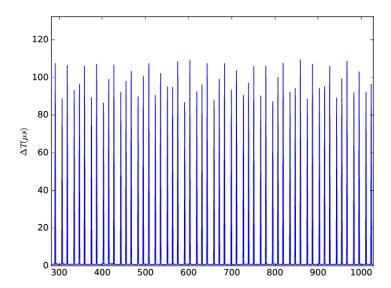

This chapter characterises the jitter, introduced by a COTS x86 server running a Linux-based operating system, upon **reception** of network packets corresponding to a SMPTE 2022-6 video stream. This includes an analysis of the packet reception path in the Linux kernel, an enumeration of identified jitter sources, and an experimental quantification of the relative contribution of each of these.

#### Chapter Outline

The remainder of this chapter is organised as follows: section 2.1 describes the data-path taken by a packet, from wire to application, enumerating the potential sources of jitter that can be encountered. Section 2.2 motivates and introduces the experimental setup used to quantify these sources of jitter, which is then used for producing the results presented in section 2.3. This chapter is concluded in section 2.4.

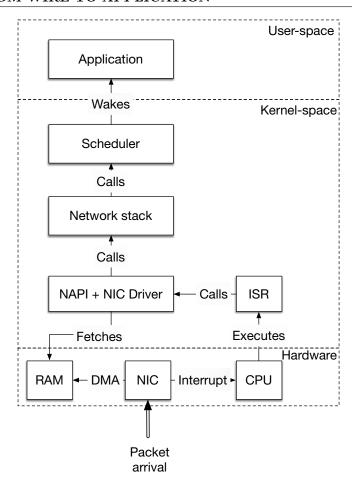

Figure 2.1: Schematic view of the path taken by a data packet – from Network Interface Card (NIC) to Application.

#### 2.1 From wire to application

The jitter sources along the path of a packet through a COTS server, depicted in figure 2.1, from its arrival at the Network Interface Card (NIC) until it is delivered to an application, are analysed in this section.

#### 2.1.1 From Wire to Interrupt

When a packet arrives at the NIC, it is decoded and copied into RAM using *Direct Memory Access* (DMA). DMA allows external devices, such as NICs, controlled access to a portion of the CPU's RAM.

DMA uses the system PCI bus, which is a shared resource with potential contention for access – and hence, is a potential source of jitter. Another

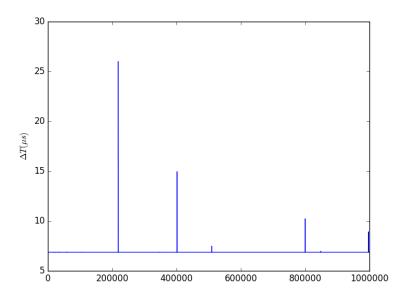

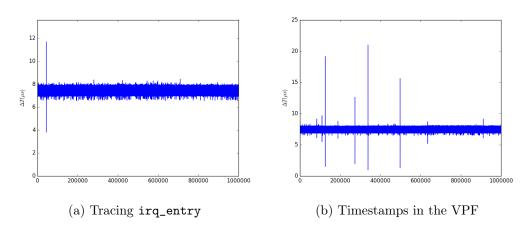

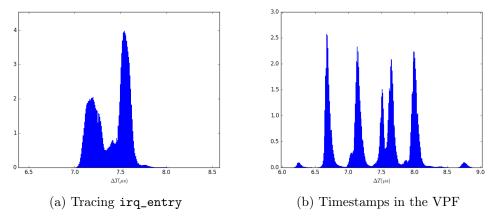

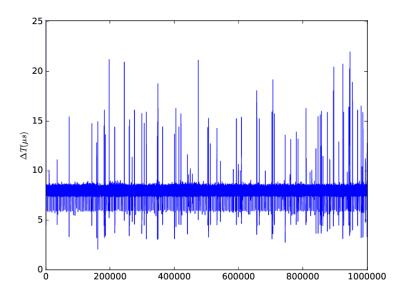

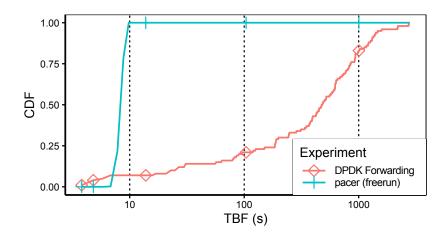

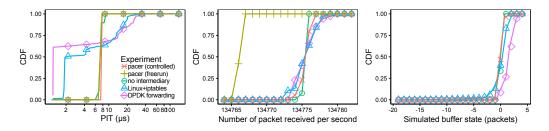

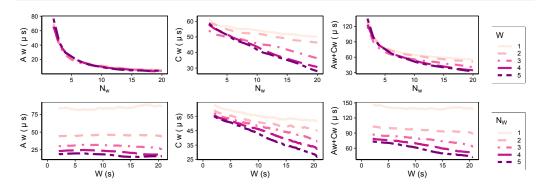

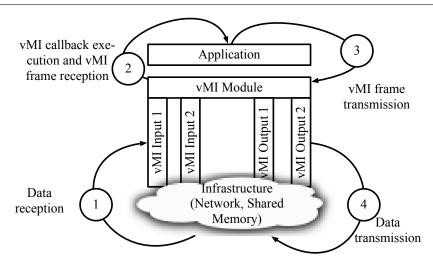

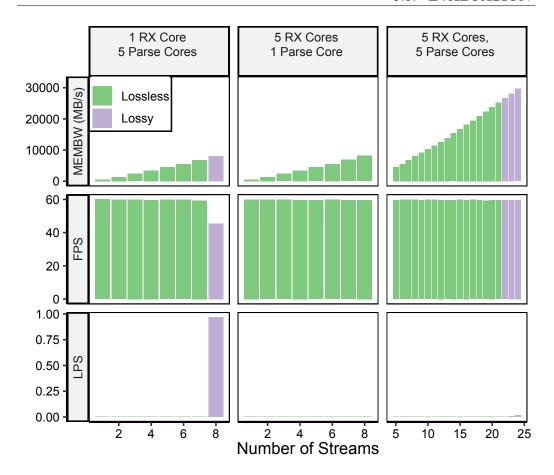

source of jitter is access to the RAM itself, since the NIC (hardware), and the NIC driver (part of the operating system) will be competing for access hereto. Finally, multiple layers of cache, which are shared with all the processes of a CPU, can introduce further jitter during the phases of copying data to and from RAM.