## Investigation and Modeling of High Frequency Effects in SiGe HBTs

Bishwadeep Saha

### ▶ To cite this version:

Bishwadeep Saha. Investigation and Modeling of High Frequency Effects in SiGe HBTs. Electronics. Université de Bordeaux; Indian Institute of technology (Chennai, Inde), 2021. English. NNT: 2021BORD0250. tel-03506299

## HAL Id: tel-03506299 https://theses.hal.science/tel-03506299v1

Submitted on 2 Jan 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE EN COTUTELLE PRÉSENTÉE POUR OBTENIR LE GRADE DE

### **DOCTEUR DE**

## L'UNIVERSITÉ DE BORDEAUX ET INDIAN INSTITUTE OF TECHNOLOGY MADRAS

## ÉCOLE DOCTORALE SCIENCES PHYSIQUES ET DE L'INGÉNIEUR ÉCOLE DOCTORALE MICROELECTRONICS

Specialité Électronique

Par Bishwadeep SAHA

# **Investigation and Modeling of High Frequency Effects in SiGe HBTs**

Sous la direction de : Thomas ZIMMER Co-directeur : Anjan CHAKRAVORTY Co-encadrant : Sébastien FREGONESE

Soutenue: 26-10-2021

#### Membres du jury:

| M. Thomas ZIMMER          | Professeur          | Université de Bordeaux       | Directeur de these    |

|---------------------------|---------------------|------------------------------|-----------------------|

| M. Philippe FERRARI       | Professeur          | Université de Grenoble-Alpes | Rapporteur            |

| M. Fabien PASCAL          | Professeur          | Université de Montpellier    | Président             |

| M. Anjan CHAKRAVORTY      | Professeur          | IIT Madras                   | Co-directeur de these |

| M. Sébastien FREGONESE    | Chargé de Recherche | CNRS                         | Co-encadrant          |

| M. Nihar Ranjan MAHAPATRA | Professeur          | IIT Gandhinagar              | Examinateur           |

#### **ABSTRACT**

#### Investigation et Modélisation de la Haute Fréquence Effets dans les HBT SiGe

Résumé: Ce travail de thèse présente une étude concernant la caractérisation des effets haute fréquence dans les transistors bipolaires à hétérojonction (HBT) en SiGe. Lors de ces travaux, le transistor du procédé BiCMOS B55 (55nm) de STMicroelectronics a été principalement analysé. Cette technologie à l'état de l'art est caractérisée par une fréquence de transition de 320 GHz et une fréquence maximale d'oscillation  $(f_{MAX})$  de 370 GHz. Les travaux se divisent en trois sous-thèmes dont les objectifs sont une meilleure caractérisation et une meilleure modélisation de ces composants. Une première partie concerne l'extraction de la  $f_{MAX}$  des transistors miniaturisés. En effet, cette fréquence  $f_{MAX}$  est une figure de mérite de première importance qui est utilisée pour valoriser une technologie. Malheureusement, on observe que la méthodologie utilisée pour extraire  $f_{MAX}$  en utilisant directement la formule de gain de Mason sur les données mesurées donne des résultats très incertains sur les composants très avancés. Ceci complexifie l'analyse des lots de fabrication de transistors. Il a été démontré qu'un modèle petit signal simple extrait à partir des paramètres Y supprime les incertitudes d'extraction et permet l'évaluation fine d'une technologie. La seconde partie concerne le substrat du transistor. En effet, cette zone du transistor est la plus importante en terme de géométrie entrainant des effets distribués dont la contribution est plus importante à haute fréquence. Celui-ci joue donc un rôle essentiel dans la modélisation des caractéristiques des paramètres S à haute fréquence des HBT SiGe modernes. Dans ce travaux, nous avons donc étendu et validé le modèle du substrat du transistor et nous avons confronté les simulations de type SPICE et les mesures jusqu'à des fréquences supérieures à 300 GHz. Finalement, dans une troisième partie, nous avons cette fois orienté nos travaux de modélisation vers les accès de base, collecteur et émetteur ainsi que sur le transistor intrinsèque. En effet, à très haute fréquence, c'est-à-dire au-delà de 100 GHz pour cette technologie, les accès du transistor doivent être modélisés par des éléments distribués. Le transistor intrinsèque est quant à lui sujet à des effets dits non-quasi-statiques. Des études de sensibilité des paramètres haute fréquences du modèle HICUM ont été menées permettant d'établir une stratégie d'extraction de paramètres. Les paramètres haute fréquence sont extraits à l'aide de la simulation TCAD et comparés aux mesures des paramètres S jusqu'à 500 GHz. **Mots-clés :** SiGe HBT,  $f_{MAX}$ , Impédance de sortie, Effets haute fréquence, TCAD, HICUM

#### **Investigation and Modeling of High Frequency Effects in SiGe HBTs**

**Abstract:** This thesis presents a study concerning the characterization of high frequency effects in bipolar heterojunction transistors (HBT) in SiGe. During this work, the transistor of the BiC-MOS B55 process (55nm) from STMicroelectronics was mainly analyzed. This state-of-the-art technology is characterized by a transition frequency of 320 GHz and a maximum oscillation frequency  $(f_{MAX})$  of 370 GHz. The work is divided into three sub-themes, the objectives of which are better characterization and better modeling of these components. The first part concerns the extraction of  $f_{MAX}$  from miniaturized transistors. Indeed, this  $f_{MAX}$  frequency is a figure of merit of the first importance which is used to promote a technology. Unfortunately, it is observed that the methodology used to extract  $f_{MAX}$  by directly using Mason's gain formula on the measured data gives very uncertain results on very advanced components. This complicates the analysis of transistor manufacturing batches. It has been shown that a simple small signal model extracted from the Y parameters removes the extraction uncertainties and allows the fine evaluation of a technology. The second part concerns the substrate of the transistor. In fact, this zone of the transistor is the most important in terms of geometry, leading to distributed effects, the contribution of which is greater at high frequency. This therefore plays an essential role in the modeling of the characteristics of the high frequency S parameters of modern HBT SiGe. In this work, we therefore extended and validated the transistor substrate model and we compared the SPICE-type simulations and measurements up to frequencies above 300 GHz. Finally, in a third part, we have oriented our modeling work towards the base, collector and emitter accesses as well as on the intrinsic transistor. Indeed, at very high frequency, that is to say above 100 GHz for this technology, the transistor accesses must be modeled by distributed elements. The intrinsic transistor is itself subject to so-called non-quasi-static effects. Sensitivity studies of the high frequency parameters of the HICUM model were carried out to establish a parameter extraction strategy. The high-frequency parameters are extracted with the support of the TCAD simulation and compared with S parameters measurements up to 500 GHz.

# **QUOTATIONS**

"Live as if,

you were to die tomorrow.

Learn as if,

you were to live forever."

MAHATMA GANDHI

## **DEDICATION**

To My Parents and sister...

## **List of Publications**

The publications arising out of the work mentioned in this thesis are given as follows:

#### I. REFEREED JOURNALS BASED ON THE THESIS

- 1. Bishwadeep Saha, Sébastien Frégonese, Bernd Heinemann, Patrick Scheer, Pascal Chevalier, Klaus Aufinger, Anjan Chakravorty, Thomas Zimmer. Reliable Technology Evaluation of SiGe HBTs and MOSFETs:  $f_{MAX}$  Estimation From Measured Data. *IEEE Electron Device Letters*, 42, 14-17, (2021).

- Bishwadeep Saha, Sébastien Frégonese, Anjan Chakravorty, Soumya Ranjan Panda, Thomas Zimmer. Sub-THz and THz SiGe HBT Electrical Compact Modeling *Electronics*, 10, 1397, (2021).

#### II. PRESENTATIONS IN CONFERENCES

Bishwadeep Saha, Sébastien Frégonese, Soumya Ranjan Panda, Anjan Chakravorty, Thomas Zimmer. Collector substrate modeling of SiGe HBTs up to THz range. 2019 IEEE BiCMOS and Compound semiconductor Integrated Circuits and Technology Symposium (BCICTS), 1-4, (2019).

### ACKNOWLEDGEMENTS

As a student under the newly initiated joint Ph.D. programme between Indian Institute of Technology, Madras and the University of Bordeaux, France, first I would like to acknowledge Prof. Anjan Chakravorty, Prof. Thomas Zimmer and Dr. Sébastien Frégonese for their guidance, support and orientation. Their constant enthusiasm and strong encouragement have always served as a source of motivation. In research, their valuable advices and critical questions always help me to think about the given problem from the grass-roots level. I am fortunate to learn the compact modelling aspect from Prof. Anjan Chakravorty through weakly group meetings and discussions. Despite research work, Prof. Thomas Zimmer and Dr. Sébastien Frégonese are always kept their door open to discuss various issues such as administration, renting the home, etc. which I encountered in France. Specially during the COVID-19 pandemic, their ongoing support for doing the research from home was phenomenal. I sincerely thanking jointly Prof. Abhijit Mallik and Prof. Anjan Chakravorty for providing me the opportunity to pursue such prestigious joint Ph.D. programme and keep faith in doing fruitful research. For everything above and beyond, I want to express my heartfelt gratitude for them.

I wish to thank the members of the thesis/doctoral committee: Prof. Nathalie Labat, Prof. Sylvie Renaud, Prof. Valérie Vigneras Lefebvre (from France) and Prof. Enakshi Bhattacharya, Prof. Anbarasu Manivannan, Prof. Deleep R Nair (from India) for their valuable feedback, suggestions and support to the different stages of my work. I thank Prof. Amitava DasGupta for his critical questions about my work that I presented in my seminar.

Besides my Ph.D. advisors and collaborators, I wish to express my gratitude to Suresh Balanethiram, Chandan Yadav and Chhandak Mukherjee, who were my mentors at the early stage of my thesis. Beside them, I must thank my lab mates Kalparupa, Mathieu, Marco, Soumya, Aakashdeep, Shubham, Nidhin, Sruthi and Ajay for giving a

great company in the lab.

I am profoundly grateful to my mother and my family members for their tremendous support and understanding in allowing me to pursue my Ph.D. specially outside of my home country. I cannot thank my mother and sister enough for all the sacrifices that they made during these years. Finally, I thank God for all the opportunities that I have had during this time.

## TABLE OF CONTENTS

| Al         | BSTR | ACT.             |                                                           | 1    |

|------------|------|------------------|-----------------------------------------------------------|------|

|            |      |                  |                                                           | Page |

| <b>A</b> ( | CKNO | OWLED            | OGEMENTS                                                  | i    |

| LI         | ST O | F TABI           | LES                                                       | vi   |

| LI         | ST O | F FIGU           | JRES                                                      | xii  |

| AI         | BBRE | EVIATIO          | ONS                                                       | xiv  |

| NO         | OTAT | ION .            |                                                           | xvi  |

|            |      | TER 1:<br>N OF B | PRINCIPLES OF BIPOLAR TRANSISTOR AND EVALICMOS TECHNOLOGY | 1    |

|            | 1.1  | Basic o          | of bipolar transistor device physics                      | 2    |

|            |      | 1.1.1            | Bipolar junction transistor                               | 2    |

|            |      | 1.1.2            | The SiGe HBT transistor                                   | 4    |

|            | 1.2  | Micro            | meter to THz waves and application                        | 7    |

|            | 1.3  | SiGe E           | BiCMOS technology, HBT device modeling and limitation     | 10   |

|            |      | 1.3.1            | Technology Evaluation                                     | 10   |

|            |      | 1.3.2            | HBT device modeling and limitation                        | 13   |

|            | 1.4  | Project          | t                                                         | 17   |

|            | 1.5  | This th          | nesis                                                     | 19   |

|            | 1.6  | Thesis           | organization                                              | 21   |

| CI         | НАРТ | TER 2:           | AVAILABLE STATE-OF-THE-ART IN LITERATURE                  | 22   |

|            | 2.1  | Introdu          | action                                                    | 22   |

|            | 2.2  | Review           | v                                                         | 22   |

|            |      | 2.2.1            | Conventional $f_{MAX}$ extraction approach                | 22   |

|            |      | 2.2.2            | Substrate model of bipolar transistor                     | 24   |

|      | Table of      | Contents (continued)                                                                 | Page |

|------|---------------|--------------------------------------------------------------------------------------|------|

|      | 2.2.3         | Compact model evaluation                                                             | 25   |

| 2.3  | Object        | ive of this work                                                                     | 26   |

| СНАР | <b>TER 3:</b> | <b>FAST EVALUATION OF</b> $f_{MAX}$ <b>FOR SiGe HBTs</b>                             | 28   |

| 3.1  | Introdu       | action                                                                               | 28   |

| 3.2  | State-c       | of-the-art $f_{MAX}$ extraction                                                      | 29   |

| 3.3  | Model         | Development strategy                                                                 | 31   |

|      | 3.3.1         | Basic model: small-signal hybrid $\pi$ -model and approximations                     | 32   |

|      | 3.3.2         | Y-parameters in high-frequency analysis and its significance .                       | 34   |

|      | 3.3.3         | Model formulation                                                                    | 34   |

| 3.4  | Results       | s and discussion                                                                     | 36   |

| 3.5  | Limita        | tion                                                                                 | 40   |

|      | 3.5.1         | Choice of Calibration method                                                         | 40   |

|      | 3.5.2         | De-embedding accuracy                                                                | 41   |

|      | 3.5.3         | Comparison of de-embedding structures to transistor measurements                     | 43   |

|      | 3.5.4         | Interpolated and measured y-parameters in Mason's gain formula: measurement accuracy | 44   |

| 3.6  |               | arison and limits of the traditional method for $f_{MAX}$ determina-                 | 47   |

| 3.7  | Case s        | tudy: Impact of Back-end-of-line (BEOL) on measured $f_{MAX}$ .                      | 51   |

| 3.8  | Conclu        | asion                                                                                | 53   |

| СНАР | <b>TER 4:</b> | SUBSTRATE MODELING FOR SiGe HBTs                                                     | 55   |

| 4.1  | Introdu       | action                                                                               | 55   |

| 4.2  | TCAD          | based simulations considering different structures                                   | 56   |

| 4.3  |               | tor-substrate model in HICUM and doping dependent substrate                          | 58   |

| 4.4  | State-o       | of-the-art model and limitation                                                      | 60   |

| 4.5  | An adv        | vanced collector-substrate model                                                     | 63   |

|      | 4.5.1         | Substrate network and model formulation                                              | 66   |

|      | 452           | Parameter extraction                                                                 | 67   |

| 4.6           | Results | s                                                                                                 | 68           |

|---------------|---------|---------------------------------------------------------------------------------------------------|--------------|

|               | 4.6.1   | Variation of collector-substrate parameters on $f_{MAX}$ : observation from TCAD based structures | 71           |

|               | 4.6.2   | Variation of collector-substrate parameters on $f_{MAX}$ : observation from HICUM                 | 72           |

|               | 4.6.3   | Observation in the forward bias                                                                   | 75           |

| 4.7           | Conclu  | asion                                                                                             | 77           |

| CHAPT<br>TCAD |         | HIGH-FREQUENCY BEHAVIOUR OF SIGe HBTs: HICUM<br>EASURED DATA                                      | <b>I,</b> 78 |

| 5.1           | Introdu | action                                                                                            | 78           |

| 5.2           | State-c | of-the-art HICUM NQS models and discussion                                                        | 79           |

| 5.3           | _       | requency measurement environment and TCAD device calibra-                                         | 80           |

| 5.4           | Quasi-  | static (QS) model parameter estimation                                                            | 82           |

| 5.5           | High-f  | requency compact model parameter estimation                                                       | 85           |

|               | 5.5.1   | NQS parameter                                                                                     | 86           |

|               | 5.5.2   | Parasitic parameters                                                                              | 88           |

|               | 5.5.3   | Sensitivity analysis                                                                              | 92           |

| 5.6           | State-c | of-the-art compact model evaluation                                                               | 95           |

|               | 5.6.1   | Observation from internal, junction and parasitic charges                                         | 98           |

|               | 5.6.2   | Limitations at HF measurement and possible source of error .                                      | 99           |

| 5.7           | Conclu  | asion                                                                                             | 101          |

| CHAP          | ΓER 6:  | CONCLUSION                                                                                        | 102          |

| 6.1           | Summ    | ary of the work                                                                                   | 102          |

| 6.2           | Scope   | for the future research                                                                           | 104          |

| APPEN         | DIX A:  | FAST EVALUATION OF $f_{MAX}$ FOR SiGe HBTs $\ldots$ .                                             | 105          |

| A.1           | Analyt  | ical development of the small-signal y-parameters                                                 | 105          |

| A.2           | Parame  | eter verification and $f_{MAX}$ variation                                                         | 108          |

| REFER         | RENCES  | S                                                                                                 | 120          |

## LIST OF TABLES

| <b>Fable</b> | Title                                                                                                                            | Page |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1          | Possible regions of operation and application of bipolar transistor                                                              | 3    |

| 1.2          | Possible circuit configuration for bipolar transistor                                                                            | 3    |

| 1.3          | Evaluation of SiGe BiCMOS technology in STMicroelectronics                                                                       | 12   |

| 3.1          | Definition of the four $y$ -parameters of a two-port network                                                                     | 34   |

| 3.2          | Transistors from different fabrication process: BiCMOS and FDSOI and comparison of the measured and interpolated $f_{MAX}$ value | 37   |

| 3.3          | Impact on measured $y$ -parameters on $f_{MAX}$ : data shown for 55 nm BiCMOS technology                                         | 46   |

| 3.4          | Impact on measured $y$ -parameters on $f_{MAX}$ : data shown for 130 nm BiCMOS technology                                        | 47   |

| 4.1          | Substrate parameters as a function of substrate doping                                                                           | 60   |

| 4.2          | 55 nm BiCMOS technological data                                                                                                  | 66   |

| 4.3          | SPICE model parameters                                                                                                           | 67   |

| 4.4          | Varying RC time constants of $R_{sub}$ - $C_{sub}$ network                                                                       | 73   |

| 4.5          | Constant RC time constants of $R_{sub}$ - $C_{sub}$ network                                                                      | 74   |

| 4.6          | $R_{per}$ - $C_{per}$ as a function of deep trench width                                                                         | 75   |

| A.1          | Extracted small-signal parameters of both BiCMOS technologies                                                                    | 108  |

| A.2          | Co-efficients in formulated model: Interpolated and calculated from small-signal parameters                                      | 109  |

## LIST OF FIGURES

| Figure | Title                                                                                                                                                                                                                                                              | Page     |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1    | High-speed SiGe HBT $f_T$ and $f_{MAX}$ roadmap (a), and ring oscillator gate delay (b) versus year of production (source: ird (2020))                                                                                                                             | 2        |

| 1.2    | Current components inside the n-p-n bipolar transistor operating in the forward active mode (source: Ashburn (2003))                                                                                                                                               | 4        |

| 1.3    | Basic cross-sectional view of a SiGe HBT structure (a), and comparison of energy band diagram in between silicon BJT (dashed line) and a SiGe HBT (solid line) (b) (source: Ashburn (2003))                                                                        | 5        |

| 1.4    | Triangular Ge profile for a graded base SiGe HBT (a), and energy band diagram showing silicon BJT (solid line) and a SiGe HBT (dashed line) (b) both biased at forward active mode with low injection operation (source: Cressler (2008))                          | 6        |

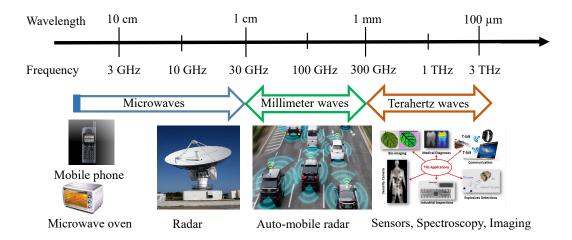

| 1.5    | Micro, millimeter, and sub-millimeter wave range                                                                                                                                                                                                                   | 8        |

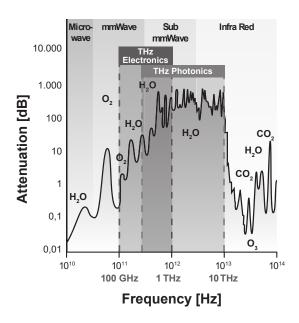

| 1.6    | Impact of atmosphere on the electromagnetic spectrum (source: Pfeiffer and Öjefors (2010))                                                                                                                                                                         | 9        |

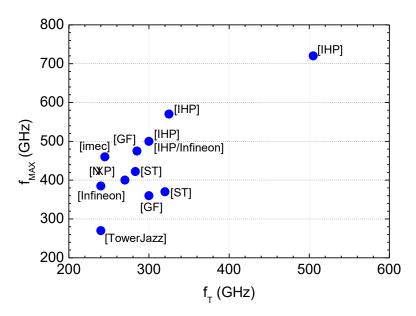

| 1.7    | Peak $f_{MAX}$ and $f_T$ of the SiGe HBT from various companies (source: Chevalier <i>et al.</i> (2018))                                                                                                                                                           | 10       |

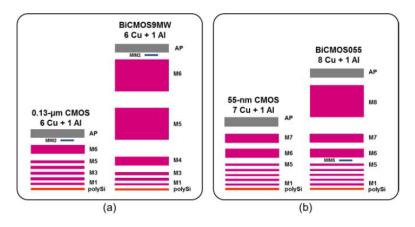

| 1.8    | BEOL modification in between digital CMOS and derived BiCMOS: 130 nm BiCMOS9MW (a), and 55 nm BiCMOS055 (b) (source: Chevalier <i>et al.</i> (2018))                                                                                                               | 12       |

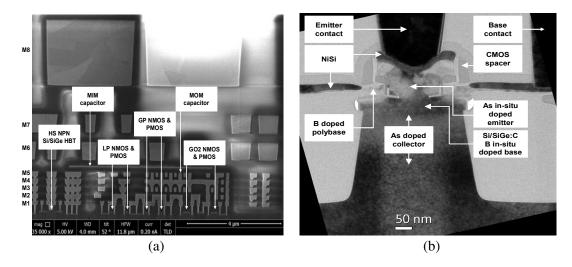

| 1.9    | SEM cross-section of the main devices with BEOL up to Metal 8 (a), and TEM cross-section (zoom in emitter-base part) of a 0.1 $\mu$ m $\times$ 4.9 $\mu$ m high-speed SiGe HBT fabricated in BiCMOS055 process technology (source: Chevalier <i>et al.</i> (2014)) | 13       |

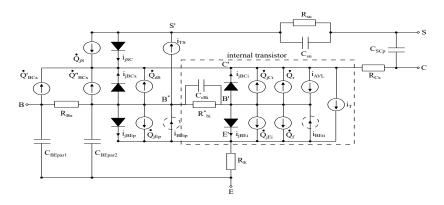

| 1.10   | Large-signal equivalent circuit of HICUM L2v2.4 compact model Schröt and Pawlak (2017)                                                                                                                                                                             | er<br>16 |

| 1.11   | European project TARANTO (ECSEL RIA): roadmap (a), and participating industry and academia (b) (source: TAR (2017-2020))                                                                                                                                           | 19       |

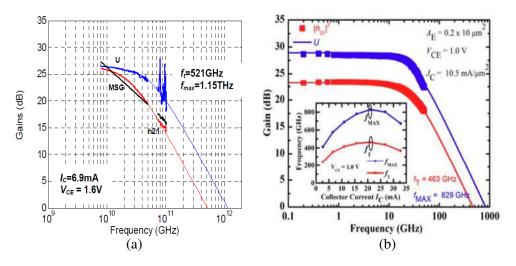

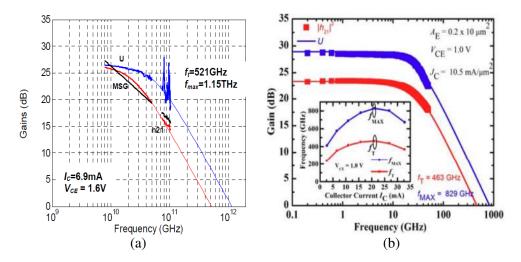

| 2.1    | Examples of $f_{MAX}$ extraction following the conventional process: U-based extrapolation Urteaga <i>et al.</i> (2011)(a), and single pole transfer function fitted on U Arabhavi <i>et al.</i> (2018)(b)                                                         | 23       |

| 3.1  | Examples of $f_{MAX}$ extraction following the conventional methods: RF gains of 0.13 $\mu$ m $\times$ 2 $\mu$ m InP HBT, from Urteaga <i>et al.</i> (2011) (a) and Short circuit current gain mag ( $h_{21}$ ) and Mason's unilateral gain $U$ from 2 to 50 GHz. $f_T$ and $f_{MAX}$ are extrapolated from a single pole transfer function (inset: dependence of $f_T$ on $I_C$ at $V_{CE}$ =1V), from Arabhavi <i>et al.</i> (2018) (b)  | 30 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

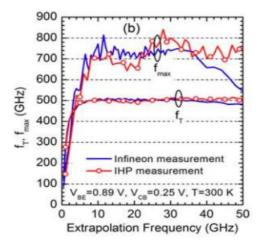

| 3.2  | Dependence of $f_T$ and $f_{MAX}$ on extrapolation frequency for the same HBT measured at IHP and Infineon. SOLT calibration with an impedance standard substrate (ISS) is applied from Heinemann <i>et al.</i> (2016)                                                                                                                                                                                                                     | 31 |

| 3.3  | Cycle of scientific modeling (source: Bryden (2007))                                                                                                                                                                                                                                                                                                                                                                                       | 32 |

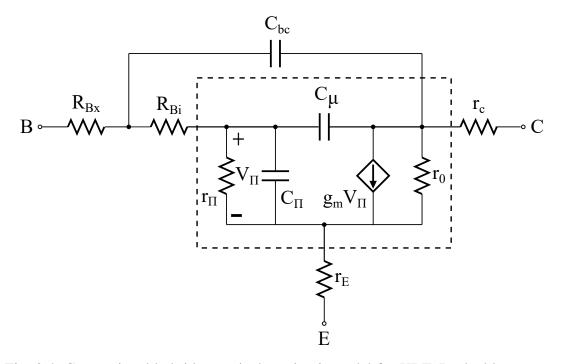

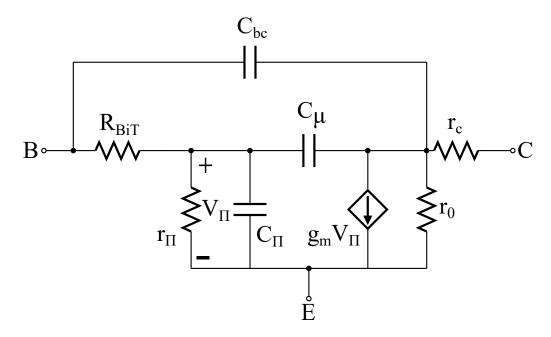

| 3.4  | Conventional hybrid $\pi$ -equivalent circuit model for HBT. Dashed box represents the intrinsic transistor model                                                                                                                                                                                                                                                                                                                          | 33 |

| 3.5  | Simplified hybrid $\pi$ -model of HBT                                                                                                                                                                                                                                                                                                                                                                                                      | 33 |

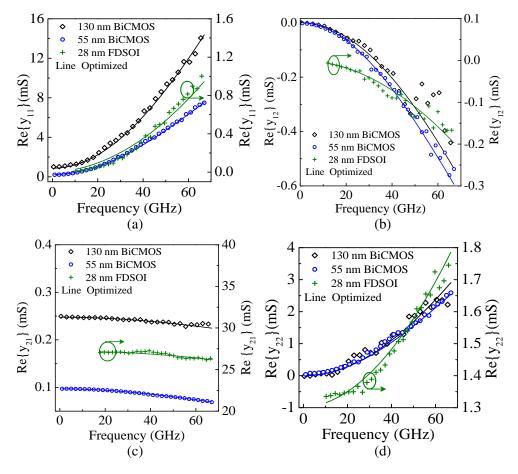

| 3.6  | Frequency-dependent real of admittance parameters for 130 nm BiC-MOS SiGe HBT (0.105 $\mu$ m $\times$ 1 $\mu$ m) biased at $V_{BE}$ = 0.89 V and $V_{CB}$ = 0.25 V and 55 nm BiCMOS SiGe HBT (0.09 $\mu$ m $\times$ 4.8 $\mu$ m) biased at $V_{BE}$ = 0.88 V and $V_{CB}$ = 0.5 V and 28 nm FDSOI MOS transistor (on right y-axis) biased at $V_{GS}$ = 0.6 V and $V_{DS}$ = 1 V                                                           | 38 |

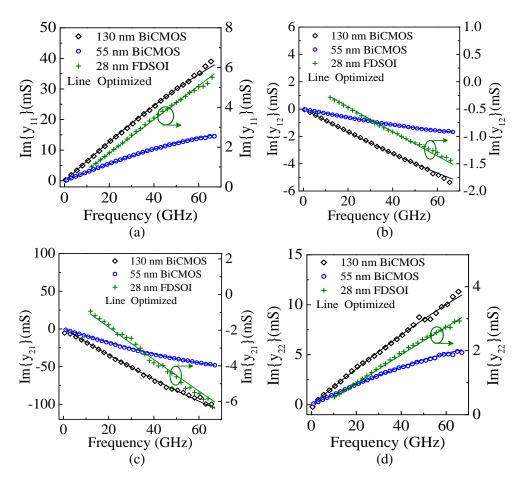

| 3.7  | Frequency-dependent imaginary of admittance parameters for 130 nm BiCMOS SiGe HBT (0.105 $\mu$ m $\times$ 1 $\mu$ m) biased at $V_{BE}$ = 0.89 V and $V_{CB}$ = 0.25 V and 55 nm BiCMOS SiGe HBT (0.09 $\mu$ m $\times$ 4.8 $\mu$ m) biased at $V_{BE}$ = 0.88 V and $V_{CB}$ = 0.5 V and 28 nm FDSOI MOS transistor (on right y-axis) biased at $V_{GS}$ = 0.6 V and $V_{DS}$ = 1 V                                                       | 39 |

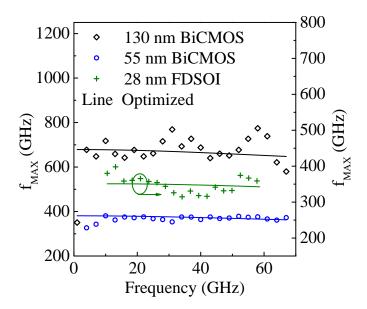

| 3.8  | Maximum oscillation frequency as a function of frequency for different flavors of various transistor technologies (symbols) and the least square regraded optimized $f_{MAX}$ (solid line)                                                                                                                                                                                                                                                 | 40 |

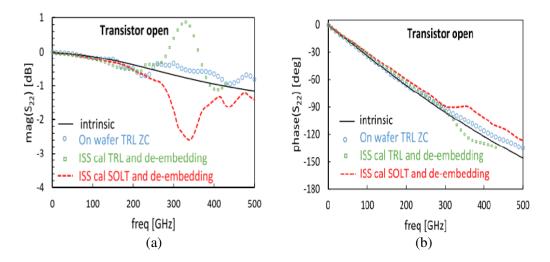

| 3.9  | EM simulation prediction of the transistor-open magnitude (a) and phase (b) of $S_{22}$ parameter versus frequency. Included results are for SOLT ISS calibration with pad-open pad-short de-embedding (red dashed line); TRL ISS calibration with pad-open pad-short de-embedding (green square) on-wafer TRL calibration (blue circle) and intrinsic simulation without pad and probe (black line) (from Fregonese <i>et al.</i> (2019)) | ;  |

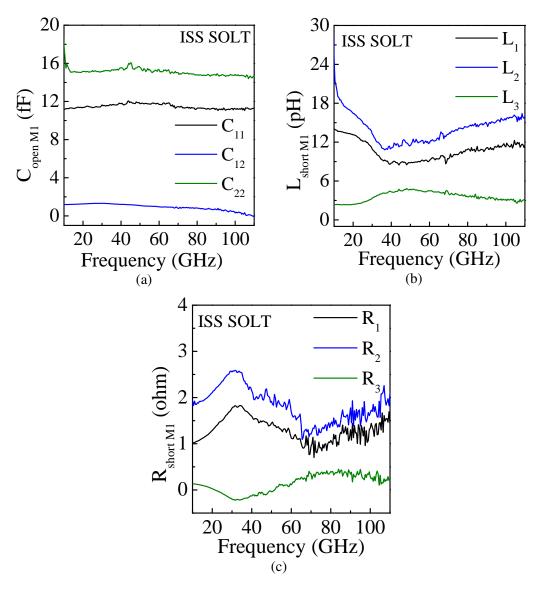

| 3.10 | Capacitances (a), inductances (b) and resistances (c) of OPEN-SHORT de-embedding structures; measurements from the B55 technology from ST Microelectronics                                                                                                                                                                                                                                                                                 | 42 |

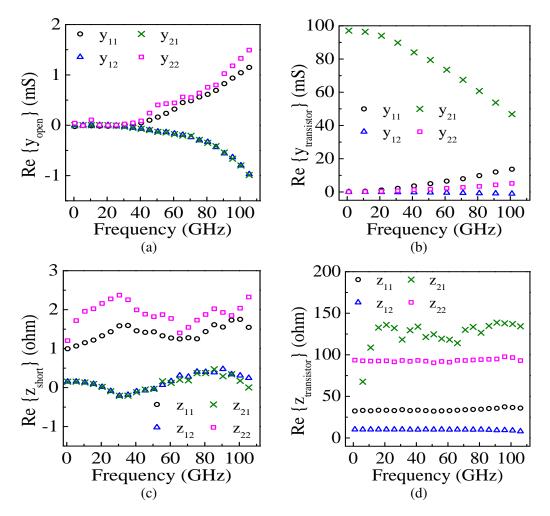

| 3.11 | Real parts of admittance or $y$ -parameters for OPEN de-embedding structure (a) and with transistor (b) and real parts of impedance or $z$ -parameters for SHORT de-embedding structure (c) and with transistor (d)                                                                                                                                                                                                                        | 44 |

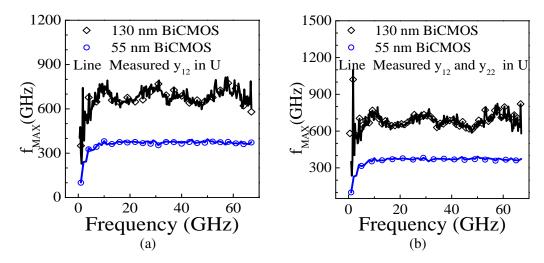

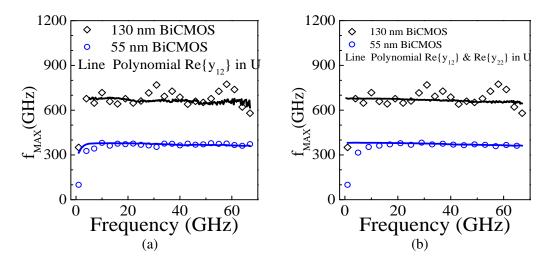

| 3.12 | $f_{MAX}$ as a function of frequency showing dominance impact of specific measured y-parameter; only $y_{12}$ (a) and both $y_{12}$ and $y_{22}$ (b) with other interpolated y-parameters in the Mason's gain formula                                                                                                                                                      | 45 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13 | $f_{MAX}$ as a function of frequency showing dominance impact of specific interpolated y-parameter; only $y_{12}$ (a) and both $y_{12}$ and $y_{22}$ (b) with other measured y-parameters in the Mason's gain formula                                                                                                                                                      | 46 |

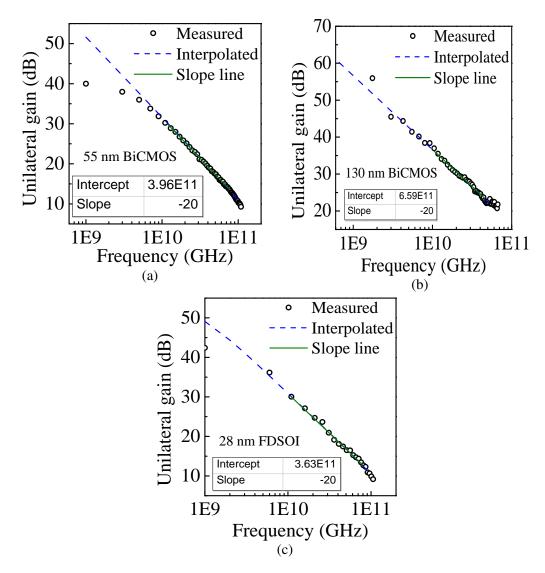

| 3.14 | Justification of predicted $f_{MAX}$ from optimized U(f) with slope of -20 dB/decade for 55 nm BiCMOS (a), 130 nm BiCMOS (b) and 28 nm FDSOI (c) technology                                                                                                                                                                                                                | 48 |

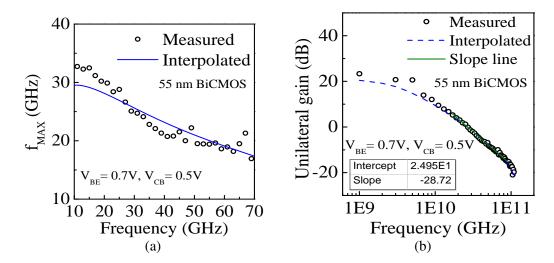

| 3.15 | Measured and interpolated $f_{MAX}$ as a function of frequency (a) and extracted from measured $U(f)$ characteristics (b) biased at $V_{BE} = 0.7$ V and $V_{CB} = 0.5$ V for 55 nm BiCMOS process                                                                                                                                                                         | 49 |

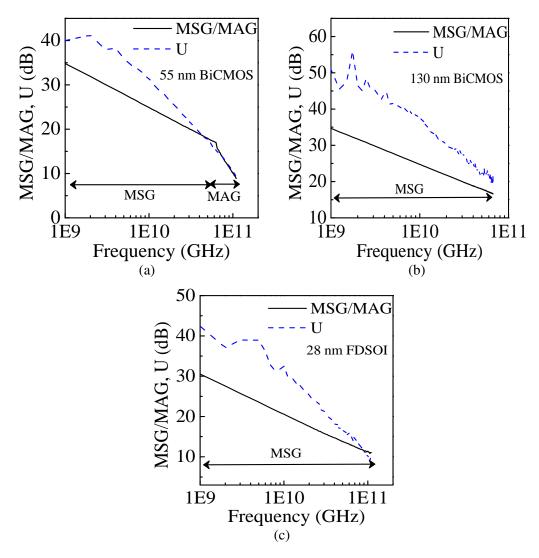

| 3.16 | MSG/MAG(f) and U(f) for three technologies: 55 nm BiCMOS (a), 130 nm BiCMOS (b) and 28 nm FDSOI (c)                                                                                                                                                                                                                                                                        | 50 |

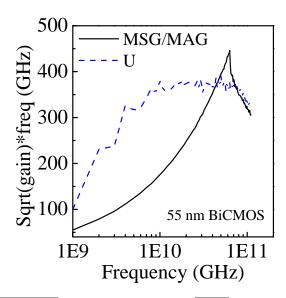

| 3.17 | $\sqrt{MSG/MAG(f)} \times frequency \text{ and } \sqrt{U(f)} \times frequency \text{ for 55 nm}$ BiCMOS technology                                                                                                                                                                                                                                                         | 51 |

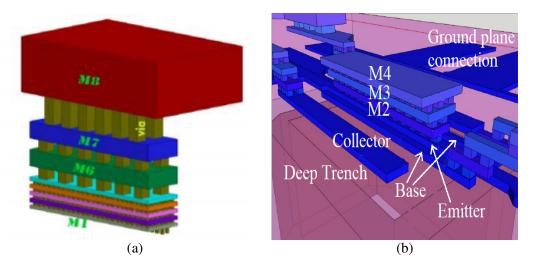

| 3.18 | Back-end-of-line (BEOL) contact configuration: cross-sectional view of eight (8) metal layers architecture (a) and 3D representation of the $M_{4wide}$ test structure with drawn emitter window 5 $\mu m \times$ 0.34 $\mu m$ (b) used in work                                                                                                                            | 53 |

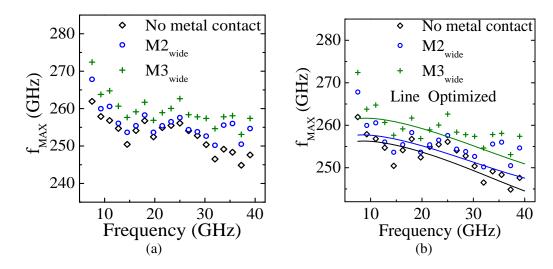

| 3.19 | Frequency-dependent $f_{MAX}$ for the different BEOL contact configurations (a) and obtained by interpolated $y$ -parameters represented by solid line (b)                                                                                                                                                                                                                 | 53 |

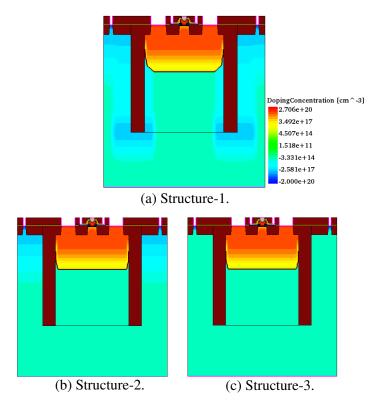

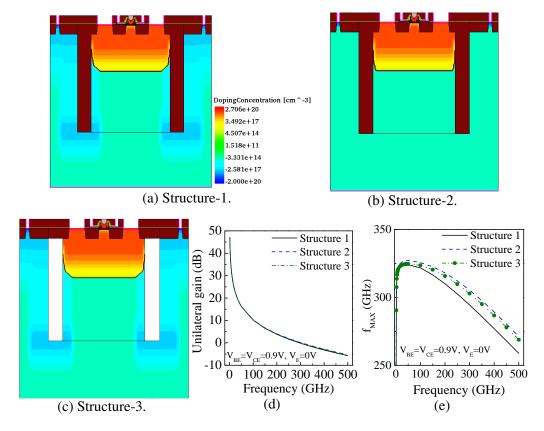

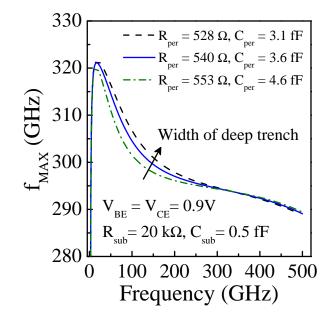

| 4.1  | Different collector-substrate-based TCAD structures: full calibrated structure (a), structure without stop channel and surround doped region (b), and structure without heavily doped substrate (c)                                                                                                                                                                        | 57 |

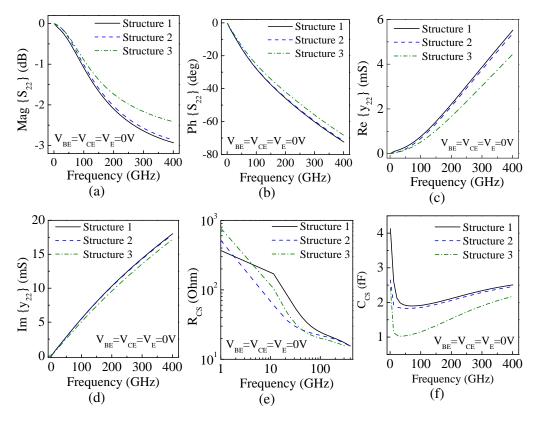

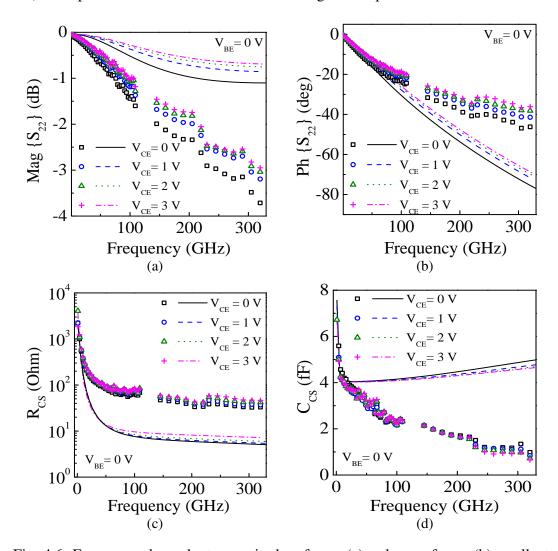

| 4.2  | Frequency-dependent characteristics: magnitude of $s_{22}$ (a), phase of $s_{22}$ (b), real part of $y_{22}$ (c) imaginary part of $y_{22}$ (d), collector-substrate resistance $R_{CS}$ =Re $(y_{22}+y_{21})^{-1}$ (e), and collector-substrate capacitance $C_{CS}$ =1/ $(\omega \text{Im}(y_{22}+y_{21})^{-1})$ (f) for the different TCAD structures shown in Fig. 4.1 | 58 |

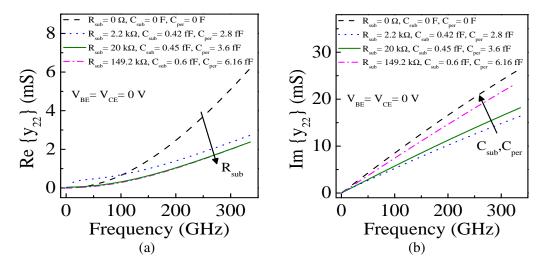

| 4.3  | Frequency-dependent output admittance showing intra-device substrate coupling: real (a) and imaginary (b) for different set of substrate parameters                                                                                                                                                                                                                        | 60 |

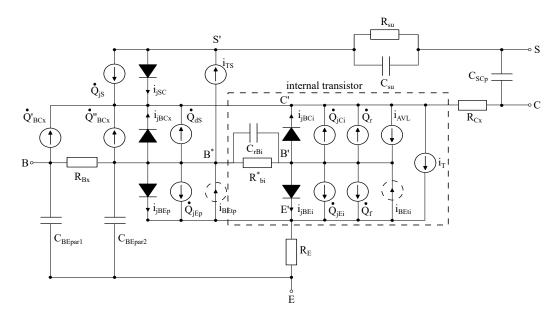

| 4.4  | Large-signal equivalent circuit of HICUM L2v2.4 compact model Schröter and Pawlak (2017)                                                                                                                                                                                                                                                                                   | 61 |

| 45   | Collector-substrate network of state-of-the-art HICLIM I 2v2 4                                                                                                                                                                                                                                                                                                             | 61 |

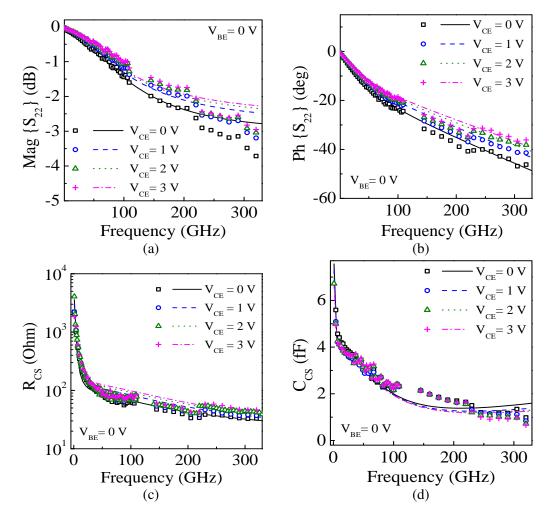

| 4.6  | Frequency-dependent magnitude of $s_{22}$ (a), phase of $s_{22}$ (b), collector-substrate resistance $R_{CS}=\text{Re}(y_{22}+y_{21})^{-1}$ (c) and collector-substrate capacitance $C_{CS}=1/(\omega \text{Im}(y_{22}+y_{21})^{-1})$ (d) for $0.09~\mu m \times 4.8~\mu m$ SiGe HBT: comparison between measurement (symbols) and HICUM L2v2.4 (lines)                                                                                                              | 62 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

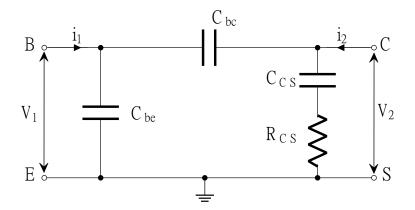

| 4.7  | A simple cold transistor model in common-emitter configuration for determination of the substrate parameters                                                                                                                                                                                                                                                                                                                                                         | 63 |

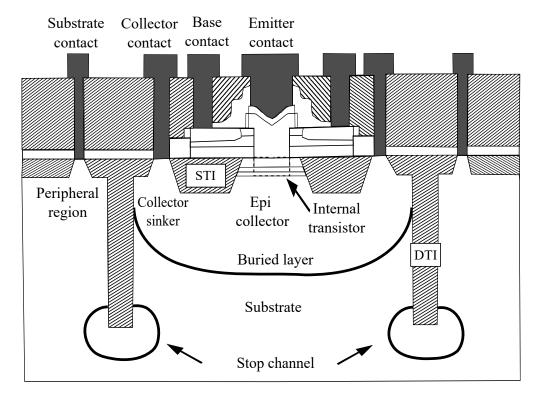

| 4.8  | Cross-sectional view of B55 device structure                                                                                                                                                                                                                                                                                                                                                                                                                         | 65 |

| 4.9  | Symmetric half-structure of the investigated HBT : different portions in the collector-substrate region (a) and equivalent SPICE circuit implemented in the collector-substrate region (b)                                                                                                                                                                                                                                                                           | 65 |

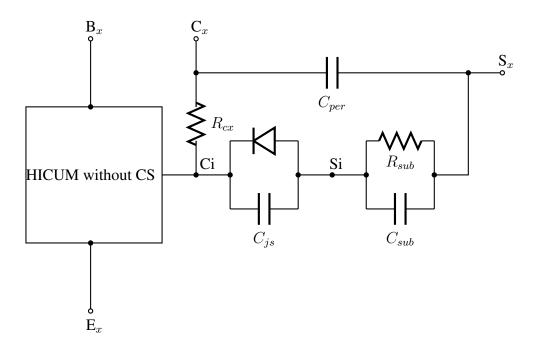

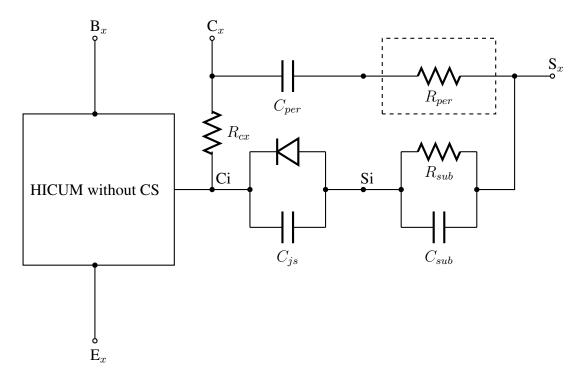

| 4.10 | Improved substrate network with the element inside the dashed box has been incorporated in HICUML2                                                                                                                                                                                                                                                                                                                                                                   | 68 |

| 4.11 | Frequency-dependent magnitude (a), phase (b) of $s_{22}$ , collector-substrate resistance $R_{CS}=\text{Re}(y_{22}+y_{21})^{-1}$ (c) and collector-substrate capacitance $C_{CS}=1/(\omega \text{Im}(y_{22}+y_{21})^{-1})$ (d) for $0.09~\mu m \times 4.8~\mu m$ SiGe HBT: comparison between measurement (symbols) and proposed collector-substrate model that is implemented in L2v2.4 (lines)                                                                     | 69 |

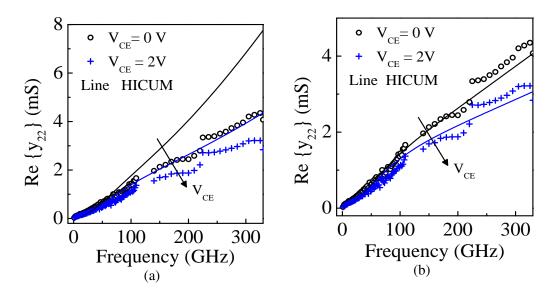

| 4.12 | Real of frequency-dependent output conductance $(y_{22})$ : without substrate network $R_{sub}$ , $C_{sub}$ (a) and with substrate network (b) in HICUM.                                                                                                                                                                                                                                                                                                             | 70 |

| 4.13 | Dependence of substrate doping and deep trench material on $f_{MAX}$ following different TCAD structures: full calibrated structure (a), structure without heavy doped substrate (b), deep trench with air (c), frequency dependent unilateral gain (d) and $f_{MAX}$ (e)                                                                                                                                                                                            | 72 |

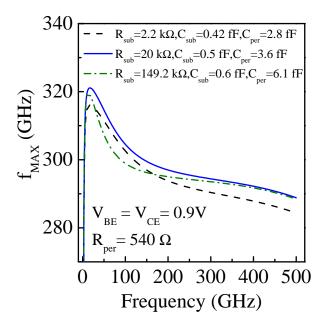

| 4.14 | Impact of different time constant of $R_{sub}$ - $C_{sub}$ on $f_{MAX}$ at peak $f_T$ bias condition of $V_{BE} = V_{CE} = 0.9$ V in HICUM                                                                                                                                                                                                                                                                                                                           | 73 |

| 4.15 | Observation of different $R_{sub}$ - $C_{sub}$ with same time-constant on $f_{MAX}$ at peak $f_T$ bias condition of $V_{BE}$ = $V_{CE}$ = 0.9V in HICUM                                                                                                                                                                                                                                                                                                              | 74 |

| 4.16 | Impact of change in deep trench width on $f_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                   | 75 |

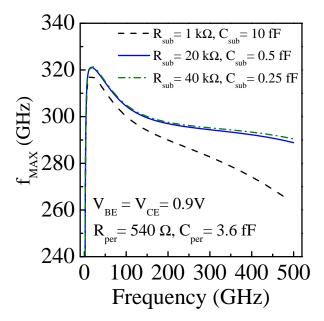

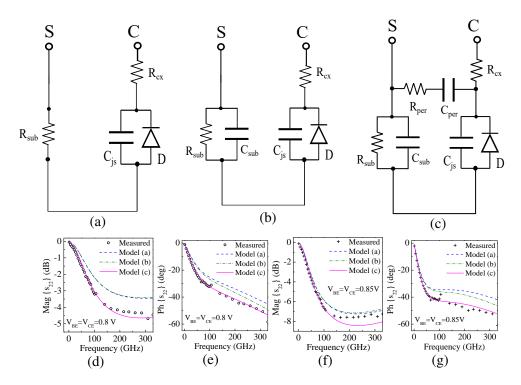

| 4.17 | Comparison with measured data in the forward bias following step-by-step incorporation of the collector-substrate model components in the HICUM: only $R_{sub}$ with the internal collector (a), only $R_{sub}$ and $C_{sub}$ with the internal collector (b), complete collector-substrate network (c), magnitude (d) and phase (e) at bias $V_{BE}=V_{CE}=0.8V$ and magnitude (f) and phase (g) at bias $V_{BE}=V_{CE}=0.85V$ of the $s_{22}$ parameter of the in- |    |

|      | vestigated HBT                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76 |

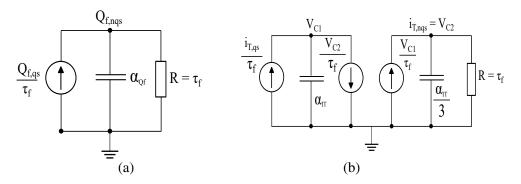

| 5.1  | VNQS models incorporated in the state-of-the-art HICUM L2v2.4: input VNQS (a), and output VNQS (b) (source: Schröter and Pawlak (2017))                                                                                                                                                                                                                                                                                                                              | 80 |

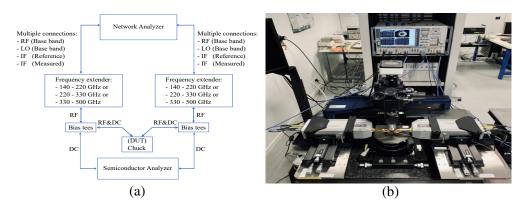

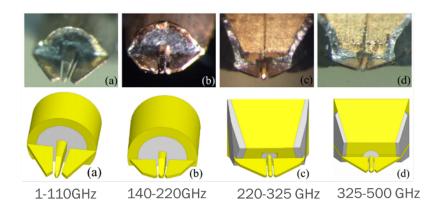

| 5.2  | photograph of the probe station for the 140 to 500 GHz measurement set-up (a), and the photograph of the probe station for the 140 to 500 GHz measurements (b) (source: Cabbia (2021))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.3  | Frequency band specific probes geometry used for high-frequency measurement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81 |

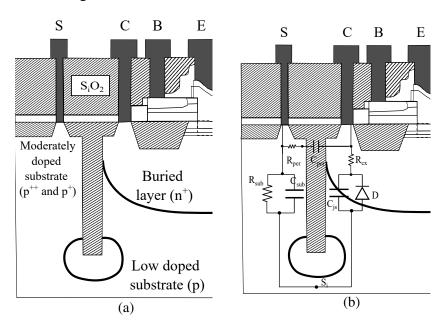

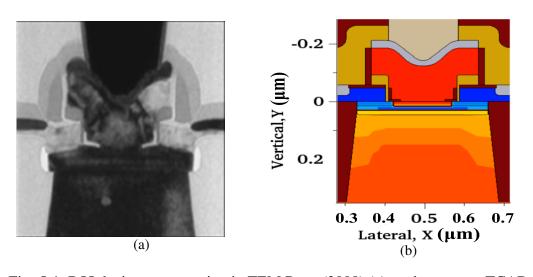

| 5.4  | B55 device cross-section in TEM Raya (2008) (a), and sentaurus TCAD (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82 |

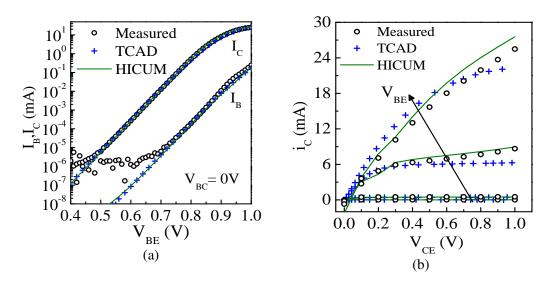

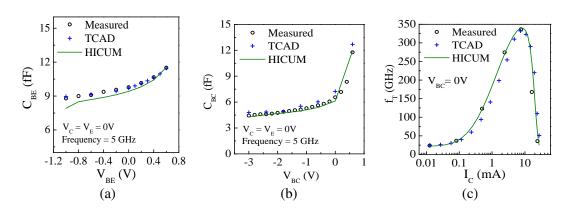

| 5.5  | Bias-dependent gummel plots (a), and output characteristics (b) for 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT: comparison between measured data ("o" symbol), calibrated TCAD simulation ("+" symbol) and HICUM model (solid lines)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 84 |

| 5.6  | Bias-dependent cold base-emitter capacitance (a), base-collector capacitance (b), and transit frequency characteristics (c) for 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT: comparison between measured data ("o" symbol), calibrated TCAD simulation ("+" symbol) and HICUM (solid lines)                                                                                                                                                                                                                                                                                                                                                                                                             | 84 |

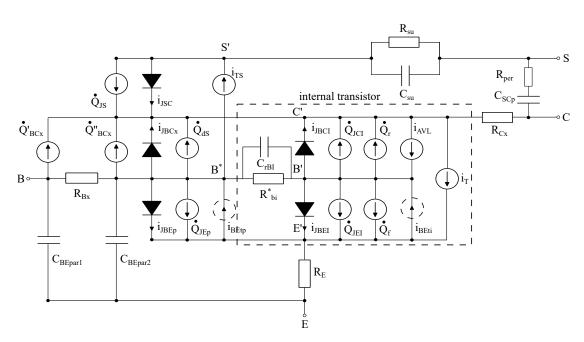

| 5.7  | Large-signal equivalent circuit of HICUM with an improved substrate network Saha <i>et al.</i> (2019)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85 |

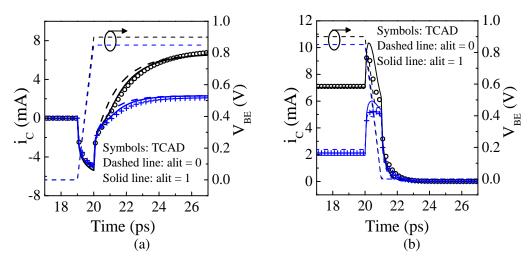

| 5.8  | Turn-on (a), and turn-off (b) characteristics for the collector current $i_C(t)$ : comparison between TCAD (symbols) and HICUM (solid line with $alit$ =1, and dashed line with $alit$ =0) for a 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT biased at constant $V_{CE}$ =0.9 V (circles) and 0.85V (plus). $V_{BEs}(t)$ have been shown as a dashed-dot line to the right $Y$ -axis                                                                                                                                                                                                                                                                                                                    | 86 |

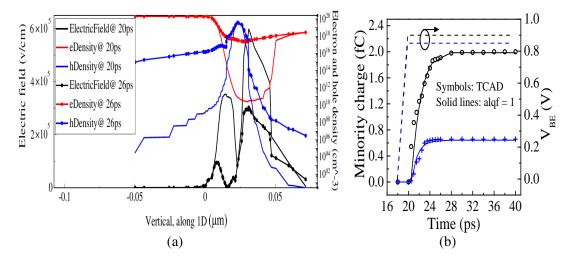

| 5.9  | Variation of electric field (left axis) and carrier density (right axis) captured at 20 ps (solid line) and 26 ps (solid line with symbols). The bias voltages $V_{BE} = V_{CE}$ are ramped up from 0 V to 0.9 V at 18 ps with a rise time of 2 ps. The value '0' in the X-axis refers to the position where poly-emitter and mono-emitter meet (a), and time dependent turn-on stored minority charge (in the emitter and base): comparison between TCAD (symbols) and HICUM (solid line with $alqf=1$ ) for the 0.09 $\mu$ m × 4.8 $\mu$ m SiGe HBT biased at $V_{BE}=0.9$ V (circle) and $V_{BE}=0.85$ V (plus), $V_{BC}=0$ V. $V_{BEs}(t)$ have been shown as a dashed line to the right $Y$ -axis | 87 |

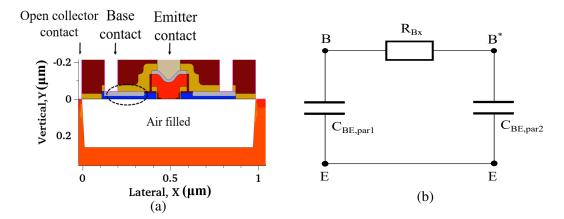

| 5.10 | Customized TCAD structure (grey: silicite, blue: p-type poly-Si) (a), and RC equivalent circuit representing the circled region in (a) for the determination of base-emitter parasitic capacitance partitioning factor ( $fbepar$ ). Here $B$ denotes the external base node (b)                                                                                                                                                                                                                                                                                                                                                                                                                       | 89 |

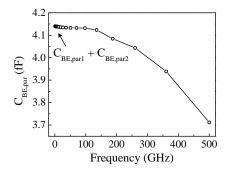

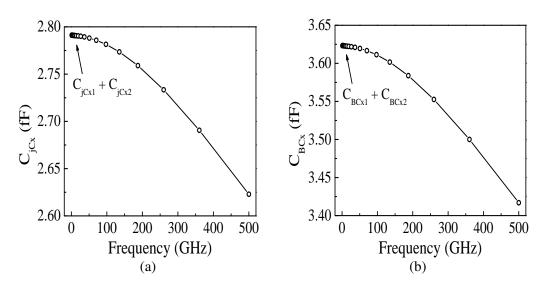

| 5.11 | Frequency-dependent capacitance characteristic for <i>fbepar</i> extraction following the customized TCAD structure shown in Fig. 5.10a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80 |

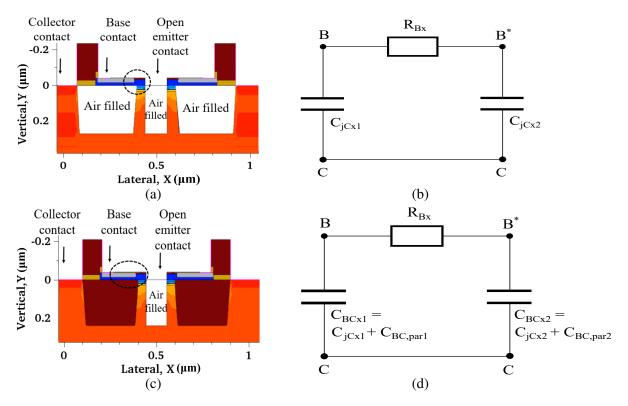

| 5.12 | Customized TCAD structure (a) and RC equivalent circuit (b) representing the left circled region for the determination of $C_{jCx}$ , and the same (in (c) and, (d) respectively) for the determination of $C_{BCx} = C_{jCx} + C_{BC,par}$ . B denotes the external base node                                                        | 91 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.13 | Frequency-dependent capacitance characteristic following the customized TCAD structure shown in Fig. 5.12a (a) and 5.12c (b) for $fbcpar$ extraction                                                                                                                                                                                  | 91 |

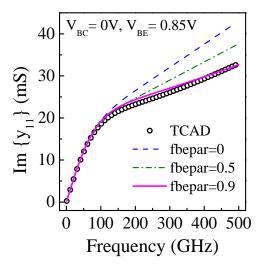

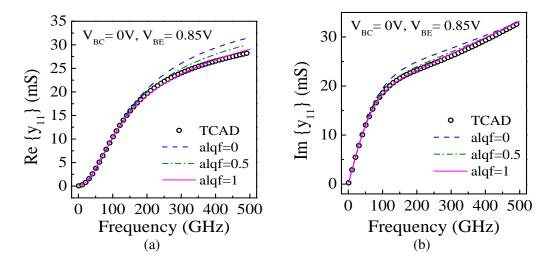

| 5.14 | Sensitivity of $fbepar$ on frequency-dependent ${\rm Im}\{y_{11}\}$ for the 0.09 $\mu{\rm m}$ $\times$ 4.8 $\mu{\rm m}$ SiGe HBT biased at $V_{BC}$ = 0 V with $V_{BE}$ = 0.85 V: comparison between TCAD (circles) and Hicum L2v2.4 (lines)                                                                                          | 92 |

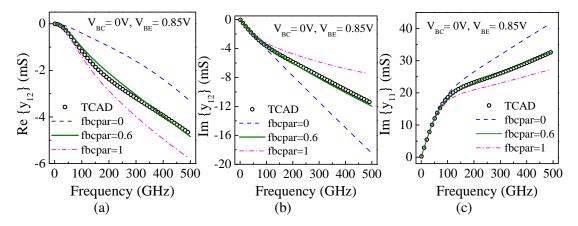

| 5.15 | Sensitivity of $fbcpar$ on frequency-dependent $\operatorname{Re}\{y_{12}\}$ (a), $\operatorname{Im}\{y_{12}\}$ (b) and $\operatorname{Im}\{y_{11}\}$ (c) for the 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT biased at $V_{BC}$ = 0 V with $V_{BE}$ = 0.85 V: comparison between TCAD (circles) and Hicum L2v2.4 (lines)              | 93 |

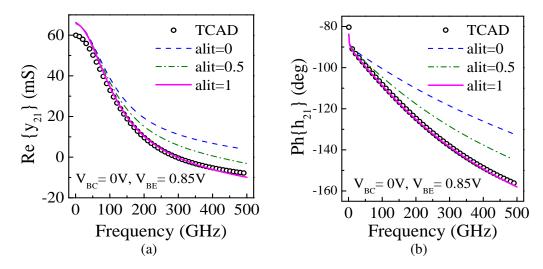

| 5.16 | Sensitivity of $alit$ on frequency-dependent $Re\{y_{21}\}$ (a), and $Ph\{h_{21}\}$ (b) for the 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT biased at $V_{BC}$ = 0 V with $V_{BE}$ = 0.85 V: comparison between TCAD (circles) and Hicum L2v2.4 (lines)                                                                                | 94 |

| 5.17 | Sensitivity of $alqf$ on frequency-dependent $\operatorname{Re}\{y_{11}\}$ (a) and $\operatorname{Im}\{y_{11}\}$ (b) for the 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT biased at $V_{BC}$ = 0 V with $V_{BE}$ = 0.85 V: comparison between TCAD (circles) and Hicum L2v2.4 (lines)                                                   | 94 |

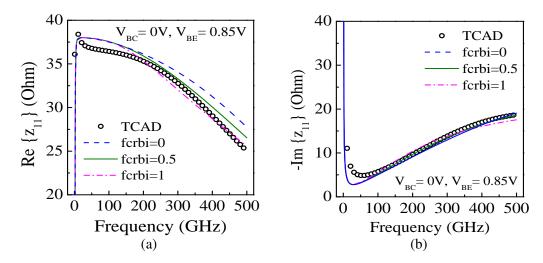

| 5.18 | Sensitivity of $fcrbi$ on frequency-dependent $Re\{z_{11}\}$ (a) and $Im\{z_{11}\}$ (b) for the 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT biased at $V_{BC}$ = 0 V with $V_{BE}$ = 0.85 V: comparison between TCAD (circles) and Hicum L2v2.4 (lines)                                                                                | 95 |

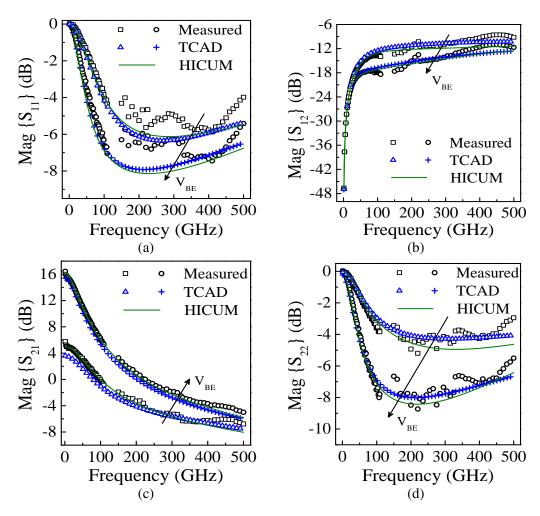

| 5.19 | Frequency-dependent magnitude of scattering parameters for the 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT biased at $V_{BC}$ = 0V with $V_{BE}$ = 0.8 V and 0.85 V: comparison between measured data (rectangles and circles), TCAD (triangle and cross) and HICUM (solid lines)                                                      | 96 |

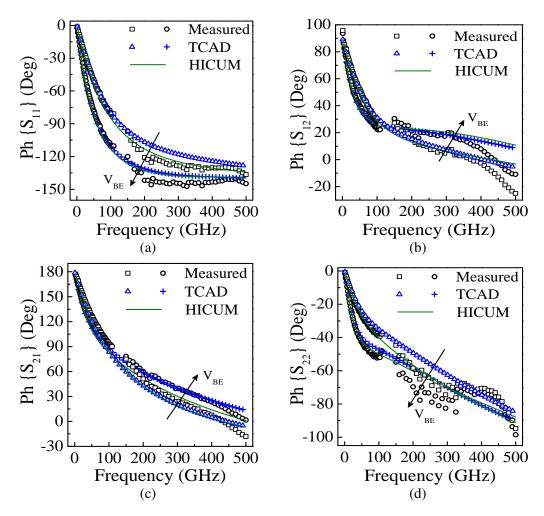

| 5.20 | Frequency-dependent phase of scattering parameters for the 0.09 $\mu$ m $\times$ 4.8 $\mu$ m SiGe HBT biased at $V_{BC}$ = 0V with $V_{BE}$ = 0.8 V and 0.85 V: comparison between measured data (rectangles and circles), TCAD (triangle and cross) and HICUM (solid lines)                                                          | 97 |

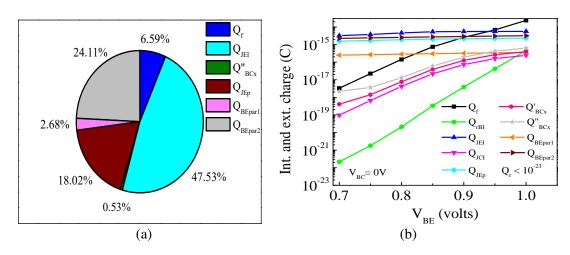

| 5.21 | Two-dimensional $\pi$ -chart showing the distribution for the charge amounts in each charge elements (having more than 0.5% share) in HICUM equivalent circuit at bias $V_{BE} = 0.85$ V and $V_{BC} = 0$ V (a), and $V_{BE}$ -dependent comparative variations of different charges assigned to deplaced HICUM charges also gets (b) | 00 |

|      | ployed HICUM charge elements (b)                                                                                                                                                                                                                                                                                                      | 99 |

## **ABBREVIATIONS**

AC Alternating Current

ADC Analog to Digital Converter

BC Base-Collector

BE Base-Emitter

BEM Boundary Element Method

BEOL Back-End-Of-Line

BiCMOS BIpolar Complementary Metal Oxide Semiconductor

BJT Bipolar Junction Transistor

CB Common Base

CC Common Collector

CE Common Emitter

CMC Compact Model Coalition

DAC Digital to Analog Converter

DC Direct Current

DEMUX Demultiplexer

DTI Deep Trench Isolation

DUT Device Under Test

EDA Electronic Design Automation

EM Electro Magnetic

EU European Union

FDSOI Fully Depleted Silicon On Insulator

FEM Finite Element Method

FET Field Effect Transistor

FoM Figure of Merit

GICCR Generalized Integral Charge Control Relation

HBT Heterojunction Bipolar Transistor

HF High Frequency

HICUM HIgh CUrrent Model

HICUM L2 HIgh CUrrent Model Level2

IRDS International Roadmap for Device and System

ISS Impedance Standard Substrate

LAN Local Area Network

LNQS Lateral Non-Quasi-Static

MAG Maximum Available Gain

MUX Multiplexer

MSG Maximum Stable Gain

NF Noise Figure

NQS Non-Quasi-Static

PAN Personal Area Network

PDK Process Design Kit

QS Quasi-Static

RF Radio Frequency

SGPM SPICE Gummel Poon Model

SiGe Silicon-Germanium

SNR Signal-to-Noise-Ratio

SoC System on Chip

SOLT Short-Open-Load-Through

SPICE Simulation program with Integrated Circuit Emphasis

ST STMicroelectronics

STI Shallow Trench Isolation

TCAD Technology Computer Aided Design

TEM Transmission Electron Microscope

TRL Thru-Reflect-Line

VNQS Vertical Non-Quasi-Static

WLAN Wireless Local Area Network

## **NOTATION**

| Physical co         |                                                                                        |

|---------------------|----------------------------------------------------------------------------------------|

| k                   | Boltzmann's constant (= $1.38 \times 10^{-23} \text{ JK}^{-1}$ )                       |

| q                   | Electronic charge (= $1.602 \times 10^{-19}$ C)                                        |

| $\epsilon_0$        | Permittivity of the free space (= $8.85 \times 10^{-12} \text{ C}^2/\text{Nm}$ )       |

| English Sy          | mbols                                                                                  |

| B', C', E'          | Internal base, collector, and emitter nodes respectively in HICUM                      |

| $B^*$               | External base node in HICUM                                                            |

| $BV_{CEO}$          | Open base collector emitter breakdown voltage                                          |

| $\Delta E_C$        | Conduction band offset                                                                 |

| $\Delta E_G$        | Bandgap difference                                                                     |

| $\Delta E_V$        | Valence band offset                                                                    |

| $C_{BC}$            | Base collector capacitance                                                             |

| $C_{BCx}$           | External base collector capacitance                                                    |

| $C_{JCx}$           | External base collector junction capacitance                                           |

| $C_{BE}$            | Base emitter capacitance                                                               |

| $C_{\mu}$           | Base collector capacitance of the small-signal hybrid- $\pi$ model                     |

| $C_{j0}$            | Zero bias collector substrate diode junction capacitance                               |

| $C_{js}$            | Collector substrate diode junction capacitance                                         |

| $C_{per}$           | Collector substrate peripheral capacitance                                             |

| $C_{RBi}$           | Internal base shunt capacitance in HICUM                                               |

| $C_{BE,par}$        | Base emitter parasitic capacitance in HICUM                                            |

|                     | f Effective base emitter parasitic capacitance                                         |

| $C_{BC,par}$        | Base collector parasitic capacitance in HICUM                                          |

| $d_C$               | Buried layer and depth of collector substrate space charge region                      |

| f                   | Operating frequency                                                                    |

| $f_C$               | Cut-off frequency                                                                      |

| $f_T$               | Unity current gain transit frequency                                                   |

| $f_{MAX}$           | Unity power gain transit frequency or maximum oscillation frequency                    |

| $g_m$               | Transconductance                                                                       |

| $g_{m0}$            | DC Transconductance                                                                    |

| $i_{AVL}$           | Base collector avalanche current                                                       |

| $I_C$               | Collector Current                                                                      |

| $i_{BEti}$          | Internal base emitter tunneling current                                                |

| $i_{jBEi}, i_{jBC}$ | v <sub>i</sub> Internal base emitter and base collector junction currents respectively |

| $i_T$               | Transfer current                                                                       |

| $J_C$               | Collector Current density                                                              |

| K                   | Stability factor                                                                       |

| $Q_f$               | Forward minority charge                                                                |

| $Q_r$               | Inverse minority charge                                                                |

$Q_{jEi}, Q_{jCi}$  Internal base emitter and base collector junction charge respectively

$Q_{rBI}$  Charge across internal base resistance

$Q_{JEp}$  Peripheral base emitter charge  $Q_{BE,par}$  Parasitic base emitter charge

$r_b$  Base resistance

$R_{bi}^*$  Internal base resistance in HICUM External base resistance in HICUM

$R_{BiT}$  External and internal base resistance in small-signal hybrid- $\pi$  model

$R_{per}$  Collector substrate peripheral resistance

$r_c$  Collector resistance

$r_{\pi}, C_{\pi}$  Internal base emitter resistance and capacitance of the small-signal hybrid- $\pi$

model

$r_0$  Collector emitter resistance of the small-signal hybrid- $\pi$  model  $R_{su}, C_{su}$  Substrate resistance and capacitance respectively in HICUM

$V_A$  Early voltage

$egin{array}{lll} V_{BC} & {

m Base-collector\ voltage} \ V_{BE} & {

m Base-emitter\ voltage} \ T & {

m Thermal\ voltage} \ U & {

m Unilateral\ gain} \ v_{sat} & {

m Saturation\ velocity} \ \end{array}$

$W_{BC}$  Base collector depletion region width

#### **Greek Symbols**

$\beta$  Current gain in the common emitter configuration

$au_b$  Base transit time  $au_d$  Overall delay time  $au_e$  Emitter transit time

$\rho$  Resistivity  $\epsilon$  Permittivity

$\omega$  Angular frequency

#### Miscellaneous

$\tilde{\gamma}$  Position-averaged quantities across the base profile

$\tilde{\eta}$  Minority electron diffusivity ratio  $\beta_i$  Function of small-signal parameters

$c_i$  Function of  $\beta_i$

$\alpha_i$  Normalization function of  $c_i$

## **CHAPTER 1**

# PRINCIPLES OF BIPOLAR TRANSISTOR AND EVALUATION OF BICMOS TECHNOLOGY

Promising progress has been made in the field of semiconductor technology today, due to the revolutionary invention of the transistor. In its early days, Germanium was used to manufacture transistors. However, Germanium was quickly replaced by Silicon due to reliability issues and operation at high temperatures. Texas Instruments invented the first Silicon-based transistor in 1954, and its mature of technology, low cost, and mass integration capabilities made Silicon the basis for manufacturing transistors for industrial and commercial purposes. Today, the number of transistors in a chip from leading smartphone manufacturers such as Apple, Huawei, etc. exceeds 10 billion.

Mostly the semiconductor market is dominated by one type of transistors, the field-effect transistor (FET). However, for specific applications related to very high frequencies, the bipolar transistor (BJT) is still the corner stone and it is primarily responsible for the rapid development in the last decade of ultra-high data transfer systems. Moreover, it was long time employed for the output stage of mobile phones and is considered as the key element for next 6G generation and finally it will be the heart of the long distance radar systems for autonomous car drive.

The progress in frequency is mainly due to the continuous changes and applications of the various semiconductor devices. These changes can be broadly divided into two categories: (i) structural changes and (ii) technological changes. In structural modification, heterojunctions were introduced after considering a suitable material from the periodic table (mainly group III, IV or V). Following this idea, IBM first demonstrated the result of a SiGe HBT at the IEDM conference in 1987 Iyer *et al.* (1987). Technological modifications, on the other hand, merge different technologies into a single platform. Complementary metal-oxide semiconductors (CMOS) are known for their low power dissipation due to the complementary switching process. Coupling CMOS with the

bipolar technology results in the BiCMOS technology which combines the advantages of both technologies: High integration density, low power and high speed.

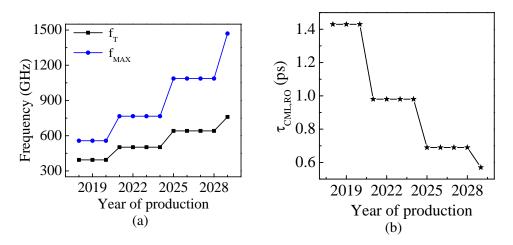

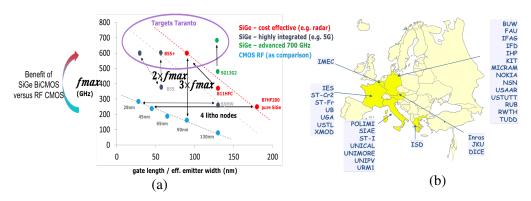

In the last decade, various EU countries have contributed to improve the performance of SiGe-HBT technology. For example, IHP reported a maximum oscillation frequency  $(f_{MAX})$  of up to 500 GHz Heinemann *et al.* (2010) in the DOTFIVE project and 720 GHz Heinemann *et al.* (2016) in the DOTSEVEN project, which is considered the highest  $f_{MAX}$  value for SiGe-HBTs. It has been predicted that the performance of the transistor may be even more aggressive in the coming years due to the continuous downsizing of the device dimensions. The IRDS (International Roadmap for Device And Systems) community has predicted the future performance metrics of SiGe-HBTs (Figs. 1.1). Based on the progress in the SiGe technology, it is expected that the SiGe HBTs will be able to overcome the THz-limit.

Fig. 1.1: High-speed SiGe HBT  $f_T$  and  $f_{MAX}$  roadmap (a), and ring oscillator gate delay (b) versus year of production (source: ird (2020)).

## 1.1 Basic of bipolar transistor device physics

## 1.1.1 Bipolar junction transistor

The term 'bipolar' in the bipolar junction transistor reflects the fact that both types of carriers, namely electrons and holes, are involved in the operation. Although minority carrier diffusion plays a critical role. The sections in a BJT are the emitter, base, and collector with the alternate doping concentration i.e. the complete device structure is

either n-p-n or p-n-p. As electrons have greater mobility than holes, n-p-n transistors are often used to offer greater trans-conductance and speed. As per the application point of view, a transistor can be operated in four possible regions of operations (Table. 1.1) with any one of possible circuit configurations (Table. 1.2). Commercially a transistor is mainly used as an amplifier so we discuss here the forward active mode of operation.

Table 1.1: Possible regions of operation and application of bipolar transistor.

| Possible region | Applied                        | Application      |  |

|-----------------|--------------------------------|------------------|--|

| of operation    | bias (n-p-n)                   |                  |  |

| Forward active  | $V_{BE} > 0$ V, $V_{BC} < 0$ V | analog amplifier |  |

| Inverse active  | $V_{BE}$ < 0V, $V_{BC}$ > 0V   | resonator        |  |

| Saturation      | $V_{BE} > 0$ V, $V_{BC} > 0$ V | digital circuits |  |

| Cut-off         | $V_{BE}$ < 0V, $V_{BC}$ < 0V   | digital circuits |  |

Table 1.2: Possible circuit configuration for bipolar transistor.

| Possible circuit      | Input    | Output           | Common    |

|-----------------------|----------|------------------|-----------|

| configuration         | terminal | terminal termina |           |

| common emitter (CE)   | Base     | Collector        | Emitter   |

| common base (CB)      | Emitter  | Collector        | Base      |

| common collector (CC) | Base     | Emitter          | Collector |

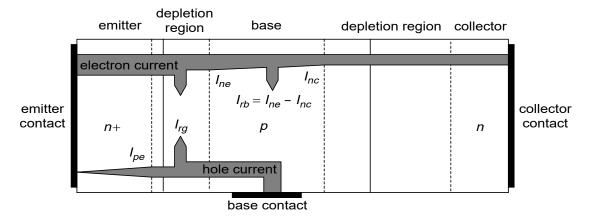

As shown in Table. 1.1, in forward active mode, the base-emitter junction is forward biased while the base-collector junction is reverse biased. A large number of electrons (for n-p-n transistor) are thus injected from the emitter into the base. Then diffusion of electrons from the base to the collector occurs as a result of the formation of a concentration gradient in the base. Of course, the width of the neutral base region should be considered equal to or smaller than the diffusion length of the electrons otherwise, a significant recombination current will generate and no electrons will reach the edge of the base-collector space charge region. In the other case, upon reaching the base-collector space charge region and due to the presence of a large electric field, electrons are quickly swept across the space charge region and become available in the collector region. On the other hand, the majority of holes from the base inject into the emitter generating base current. To minimize the base current (for sustaining the total current gain), emitter doping can be increased compared to base doping. The current flow com-

ponents for a n-p-n transistor under a forward active mode of operation are shown in Fig. 1.2.

Fig. 1.2: Current components inside the n-p-n bipolar transistor operating in the forward active mode (source: Ashburn (2003)).

#### 1.1.2 The SiGe HBT transistor

Following the general design procedure, a silicon BJT hardly manages to operate at cutoff frequencies higher than 50 GHz. This is mainly because of the considerable base

transit time of minority carriers. Therefore, in order to reduce the base transit time, a

narrow heavily doped base should be considered. Note that a heavily doped base results

in low base resistance. However, at the same time, the base current increases, thus

reducing the total current gain. The trade-off in between gain and base transit time is

so-called *bandgap engineering*. This methodology was introduced in BJTs to improve

their performance.

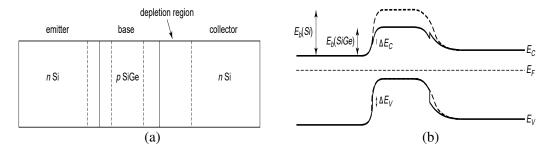

Heterojunction bipolar transistor (HBT) is a kind of bipolar transistor in which one of the two junctions (or both) can be formed with a different kind of semiconductor material. In general, a narrow bandgap and a wide bandgap material are used in the base and emitter, respectively to form such heterojunction. This results in a lower energy barrier for the carriers moving from emitter to base and higher for the carriers moving towards the emitter. Since SiGe has a lower bandgap than silicon, a thin epitaxial layer of SiGe is grown on the base of silicon BJT (Fig. 1.3a). The energy band diagram, in Fig. 1.3b, shows that the conduction band barrier is much smaller in SiGe HBT than in

Fig. 1.3: Basic cross-sectional view of a SiGe HBT structure (a), and comparison of energy band diagram in between silicon BJT (dashed line) and a SiGe HBT (solid line) (b) (source: Ashburn (2003)).

Si BJT. This low barrier height in SiGe HBT results in a much higher collector current to silicon BJT at the same operating point. In addition to having desired gain, the base resistance of HBT can be reduced to decrease input power consumption. High current gain with low base resistance helps to achieve high input signal-to-noise (SNR) ratio leading to a low noise figure (NF $_{min}$ ).

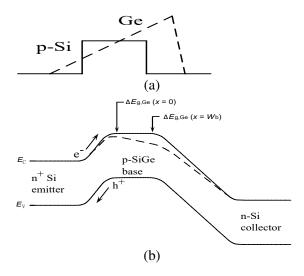

In modern *bandgap engineering*, instead of using box type germanium (Ge) profile in the base, a graded profile is used. This means that the Ge content is linearly graded from 0% near the base-emitter junction to some maximum value of Ge content near the collector-base junction than rapidly ramped down to 0% Ge. Unlike the constant baseband lowering, as shown in Fig. 1.3b, graded Ge profile lowers most of the base bandgap at the collector side. Moreover, the built-in electric field further reduces the base transit time. A triangular Ge-profile and resulting non-uniform change in the base bandgap are shown in Figs. 1.4a and 1.4b respectively.

Due to the incorporation of graded Ge profile in the base, it leads to positive influences in both DC and AC operation. They are summarized as follows:

- (a) Since both the base-emitter and base-collector junctions bandgaps become narrower, for the same applied  $V_{BE}$ , more electrons inject into the base resulting in higher collector current and gain, provided base current remain unchanged. In fact, the presence of Ge gives a new order of freedom to adjust the current gain, which is only dependent on the base doping in the conventional BJT. This is the added flexibility to customize the base resistance with the same current gain.

- (b) Since the Ge content at the base-collector junction is finite (generally high com-

Fig. 1.4: Triangular Ge profile for a graded base SiGe HBT (a), and energy band diagram showing silicon BJT (solid line) and a SiGe HBT (dashed line) (b) both biased at forward active mode with low injection operation (source: Cressler (2008)).

pared to the base-emitter junction in Fig. 1.4a), it restrains the base-collector space charge region to move further into the quasi-neutral base region with increasing  $V_{BC}$ . This results in higher early voltage and output conductance compared to silicon BJT.

(c) The dynamic operation in silicon BJT is limited due to the substantial basic transit time. However, an HBT with a graded Ge profile can efficiently handle this issue by featuring a higher built-in field such that this field accelerates all the injected minority carriers across the base. Hence base transit time is decreased significantly.

Considering such graded Ge incorporated bandgap engineering, the normalized DC figure-of-merits (gain  $\beta$ , early voltage  $V_A$ , transit time  $\tau_b$ ) are summarized as follows Cressler (2008):

$$\frac{\beta_{SiGe}}{\beta_{Si}} = \left\{ \frac{\tilde{\gamma}\tilde{\eta}\Delta E_{g,Ge}(grade)/kT e^{\Delta E_{g,Ge}(0)/kT}}{1 - e^{-\Delta E_{g,Ge}(grade)/kT}} \right\}$$

(1.1)

$$\frac{V_{A,SiGe}}{V_{A,Si}} = e^{\Delta E_{g,Ge}(grade)/kT} \left\{ \frac{1 - e^{-\Delta E_{g,Ge}(grade)/kT}}{\Delta E_{g,Ge}(grade)/kT} \right\}$$

(1.2)

$$\frac{\tau_{b,SiGe}}{\tau_{b,Si}} = \frac{2}{\tilde{\eta}} \frac{kT}{\Delta E_{g,Ge}(grade)} \left\{ 1 - \frac{kT}{\Delta E_{g,Ge}(grade)} \left[ 1 - e^{-\Delta E_{g,Ge}(grade)/kT} \right] \right\}$$

(1.3)

The AC figure-of-merits are also positively influenced. The unity gain cut-off frequency  $(f_T)$  and maximum oscillation frequency  $(f_{MAX})$  can be written Cressler (2008):

$$f_T = \frac{1}{2\pi} \left[ \frac{kT}{qI_C} (C_{BE} + C_{BC}) + \tau_b + \tau_e + \frac{W_{BC}}{2v_{sat}} + r_c C_{BC} \right]^{-1}$$

(1.4)

$$f_{MAX} = \sqrt{\frac{f_T}{8\pi C_{BC} r_b}} \tag{1.5}$$

The transit time improvement results in an increase of  $f_T$  and thus an improvement of  $f_{MAX}$  also.

## 1.2 Micrometer to THz waves and application

Silicon offers integration capabilities on a very large-scale and the miniaturization of the device geometries makes it possible to obtain high cut-off frequencies. These two benefits along with Ge's integration make SiGe HBT capable of capturing the RF wireless communication market and become one of the contenders relatively in a short period of time. For those key reasons, SiGe HBT can cover a wide variety of applications. Below we have classified the different applications into the respective frequency spectrum.

Fig. 1.5 shows the electromagnetic spectrum primarily with a focus from microwaves to THz waves. Although there is no stated convention about the range of the frequency spectrum, we do categorize the various applications in the respective bands. Generally, the spectrum from 300 MHz to 30 GHz term as microwave spectrum which mainly serves the purpose of ground wave long-distance communication. The next range is from 30 GHz to 300 GHz and is termed as a millimeter (mm) wave spectrum where high-speed and radar applications have taken place. Following mm-wave, the spectrum from 300 GHz to 3 THz is known as sub-millimeter (sub-mm) range (or THz range) which is primarily used for imaging and sensing applications.