# Assessment of Edge Machine-Learning Systems under Radiation-Induced Effects

Matheus Garay Trindade

#### ▶ To cite this version:

Matheus Garay Trindade. Assessment of Edge Machine-Learning Systems under Radiation-Induced Effects. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2021. English. NNT: 2021GRALT063. tel-03525899

# HAL Id: tel-03525899 https://theses.hal.science/tel-03525899v1

Submitted on 14 Jan 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# **DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES**

Spécialité : Nano Electronique et Nano Technologies (NENT)

Arrêtée ministériel : 25 mai 2016

Présentée par

#### **Matheus GARAY TRINDADE**

Thèse dirigée par Rodrigo POSSAMAI BASTOS

préparée au sein du Laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés (TIMA) dans l'École Doctorale Electronique, Electrotecnique, Automatique & Traitement du Signal (EEATS)

# Assessement of Edge Machine-Learning Systems under Radiation-Induced Effect

Thèse soutenue publiquement le **30 Septembre 2021**, devant le jury composé de :

#### Dr. Rodrigo POSSAMAI BASTOS

Maître de Conférences, Université Grenoble Alpes, Directeur de thèse

#### **Dr. Laurent ARTOLA**

Ingénieur de recherche, ONERA, Examinateur

#### Pr Sergio CUENCA ASENSI

Professeur d'université, Universidad d'Alicante, Rapporteur

#### Pr. Alberto Bosio

Professeur d'université, École Centrale Lyon, Rapporteur

#### Dr. Patrick Girard

Directeur de Recherche, Université Grenoble Alpes, Président

| "Quem tem um rumo de rancho pras quatro pato |

|----------------------------------------------|

|                                              |

| Bota seu mundo na estrada batendo água       |

| Luiz Mareno                                  |

|                                              |

|                                              |

# Acknowledgements

First, I would like to thank Dr. Laurent Artola, Dr. Alberto Bosio, Dr. Sergio Cuenca Asensi and Dr. Patrick Girard for agreeing to be part of my thesis committee. I would also like to thank you for all the remarks and questions that have been posed during the review and defense of the manuscript.

I would also like to thank my advisor Dr. Rodrigo Possamai Bastos, who has accepted me as his Ph.D. student and who throughout the development of the thesis has spared no efforts in guiding me and providing me with access to state-of-the-art radiation test equipment. I can say that I was a very privileged student when it came to radiation campaigns during my thesis.

Moreover, I would like show gratitude to the advisors that I had during my undergraduate studies at the Universidade Federal de Santa Maria. Dr. Osmar Marchi dos Santos, who accepted a very inexperienced 17 years old me into his research group and advised me throughout my five years of undergraduate studies. You have helped me even when I was in England, during my exchange year, helping me getting into a research group. When I came back, in no time I was placed by you in a project that has been one of the most exciting projects that I have participated: the Astros project. It was, as far as I know, the best project in the University to be at the time. I am really grateful for everything. Dr. Andrei Legg, you are also someone who was really important for me during my undergraduate studies. You were always there for everything that I needed and who helped guiding me on my final year graduation project (and there were some good laughs that came out of it!). Also, I remember when you came to me and said "I have heard of an opportunity in France, and while I do not want to lose you as a student, I believe it is a great opportunity for you and if you want to go, I will help with that the best I can". Thanks. It really meant a lot. I would also like to thank Dr. Simone Ceolin and Dr. Renato Machado, who have been of immense help during my time on the Astros project and who have trusted in my work. I really enjoyed working with you.

Ph.D. is hard, no questions about it, but it is easier when you have colleagues that make your day better, and I sure had that. Ricardo, you were much more than a colleague, you are real friend that I made during the thesis. And when I say real friend, I really mean it. We have published papers together, learned to ski together, went drinking beer together

and built a Viking city together (yeah reader, you heard it right). Whenever I needed, I felt that I could count on you, and I have no words for that. I hope that you know that you can always count on me; Thiago, you are another great friend that I have made on my thesis. You are probably one of the funniest people I have ever met, and it is amazing the amount of stuff that you have helped me with and I am really grateful for everything. The greatest thing is that I can continue working with you after my thesis!; Leonel, my first lab roommate! I can say that we had some good laughs and celebrations, especially when our team won the Libertadores; Rodrigo Iga, I really miss our discussions at coffee time and the great ski weekends that we have done together. Furthermore, I would like to thank Alexandre, Yoan, Mohammed, Gregoire, Jérémy, Nils, Assia, Liège and Tarso. You were great colleagues to have. I miss the environment at TIMA!

During my thesis, I have also made some really good friends outside the lab too. I would like to thank Luiza, you were the first person that I met (in a quite funny way) when I got in Grenoble and you have definitely made adapting to such a huge amount of change easier. You are a great friend. I would like to thank Katyanne. Is there a better guest than one that stays in your house and randomly cooks you a shrimp risotto? I also want to acknowledge Paola, Rafael, Raup, Natalia, Renato and Cocotas.

Good friendships can withstand distance and time. I want to acknowledge my friends (ODS!!!) from Santa Maria. I have met these guys when I was in school and while I now live an ocean away from them, whenever I step in Brazilian soil, they are eager to see me. Guto, I can honestly say that you are one the best friends that I have and I miss our long drives discussing politics, Grêmio, parties and plenty of legendary stories that we have been through, all of that while listening to some good ol' Pitbull. Rafael, man, we have done some stuff, right? Looking forward to a good barbecue that only the guys from the "border" know how to do. Bruno, curiously enough, you were one of the first people I met when I moved to Santa Maria, and we did not seem to have much in common, but we definitely become great friends. Beto, I really enjoy our discussions regarding a huge variety of games and I surely miss going out with you or even just chilling and playing some Magicka.

Finally, I would like to address the most important acknowledgements of this thesis. I would like to thank my parents, my dad Alcino and my mom Rosangela. I believe that to make justice of how thankful I am, I would need to write a whole other manuscript

explaining the multitude of ways that I am grateful. You have always encouraged me to do anything that I wanted. And really, ANYTHING. I believe that it must have been hard enduring me learning how to play the guitar, for instance! You pushed me to study foreign languages, and guess what, I am now using English and French every day, and both have been primordial for my studies. You have made sure that I would have access to the best education possible, and this has definitely played a major role in everything that I have achieved. Also, even though I was far away, I always felt safe and I never felt alone. I was always sure that you were on my side. I know that it is cliche, but I do have the best parents in the world and I love you. I would also like to thank my grandmother Maria, my cousins Rafaela, Maria Eduarda, Mariana and Fernanda, my uncle Pires and my Aunts Mariangela and Denise. I am grateful for all the good energy that you have sent towards me, for believing in me and for always receiving me so well when I visit you. An honorable mention as well is my dog Prince. He was a real companion that I had, who would curl up on my lap while I would study and try to cheer me up when I was feeling down.

It has been quite a ride. Now, let's see what is waiting for me in the future.

# Contents

|    | Ackı  | nowledg   | gements                                  | i  |

|----|-------|-----------|------------------------------------------|----|

| In | trodu | ction     |                                          | 1  |

| 1  | Rad   | iation te | esting of Components and Systems         | 7  |

|    | 1.1   | Soft E    | rror Taxonomy                            | 9  |

|    |       | 1.1.1     | Single-Bit Upset (SBU)                   | 9  |

|    |       | 1.1.2     | Multiple-Bit Upset (MBU)                 | 10 |

|    |       | 1.1.3     | Single-Event Transient (SET)             | 10 |

|    |       | 1.1.4     | Single-Event Functional Interrupt (SEFI) | 10 |

|    |       | 1.1.5     | Single-Event Latch-up (SEL)              | 10 |

|    | 1.2   | Metric    | s                                        | 11 |

|    |       | 1.2.1     | Particle Flux                            | 11 |

|    |       | 1.2.2     | Fluence                                  | 11 |

|    |       | 1.2.3     | Cross-section                            | 12 |

|    |       | 1.2.4     | Soft Error Rate (SER)                    | 13 |

| 2  | Revi  | sion on   | Machine Learning                         | 14 |

|    | 2.1   |           | tions                                    | 16 |

|    |       | 2.1.1     | Dataset                                  | 16 |

|    |       | 2.1.2     | Input Sample                             | 16 |

|    |       | 2.1.3     | Feature                                  | 16 |

|    |       | 2.1.4     | Supervised Learning                      | 17 |

|    |       | 2.1.5     | Unsupervised Learning                    |    |

|   |      | 2.1.6    | Classification                                             | 18 |

|---|------|----------|------------------------------------------------------------|----|

|   |      | 2.1.7    | Regression                                                 | 19 |

|   | 2.2  | Artific  | cial Neural Networks (ANN)                                 | 19 |

|   | 2.3  | Suppo    | rt Vector Machine (SVM)                                    | 21 |

|   |      | 2.3.1    | Multiclass SVM                                             | 23 |

|   | 2.4  | Rando    | om Forest                                                  | 23 |

| 3 | Sup  | port Ve  | ctor Machine under Radiation Effects                       | 26 |

|   | 3.1  | Introd   | uction                                                     | 28 |

|   | 3.2  | Case-S   | Study Support Vector Machine (SVM) Architecture            | 29 |

|   |      | 3.2.1    | State-of-the-Art SVM in Hardware                           | 29 |

|   |      | 3.2.2    | SVM Architecture Design                                    | 30 |

|   |      | 3.2.3    | Set of Input Vectors                                       | 30 |

|   | 3.3  | SVM A    | Architecture Assessment Through Fault Emulation Campaign   | 31 |

|   |      | 3.3.1    | Device Under Test (DUT)                                    | 31 |

|   |      | 3.3.2    | Assessment metrics                                         | 32 |

|   |      | 3.3.3    | Fault Emulation Method                                     | 33 |

|   |      | 3.3.4    | Results of the Fault Emulation Campaign                    | 35 |

|   | 3.4  | Radiat   | tion Test Experiment and Results                           | 37 |

|   |      | 3.4.1    | Radiation Test Set-Up                                      | 38 |

|   |      | 3.4.2    | Radiation Test Method                                      | 38 |

|   |      | 3.4.3    | Assessment of Radiation Test Results                       | 39 |

|   |      | 3.4.4    | Comparison with State-of-the-Art Works                     | 44 |

|   | 3.5  | Conclu   | usions                                                     | 44 |

| 4 | Effe | cts of T | hermal Neutron Radiation on a Hardware-Implemented Machine | )  |

|   | Lea  | rning A  | lgorithm                                                   | 46 |

|   | 4.1  | Introdu  | uction                                                     | 48 |

|   | 4.2  | Case-S   | Study SVM Architectures                                    | 48 |

|   |      | 4.2.1    | Binary SVM Architecture Design                             | 48 |

|   |      | 4.2.2    | Multiclass SVM Architecture Design                         | 49 |

|   |      | 4.2.3    | Set of Input Vectors for the Multiclass SVM                | 49 |

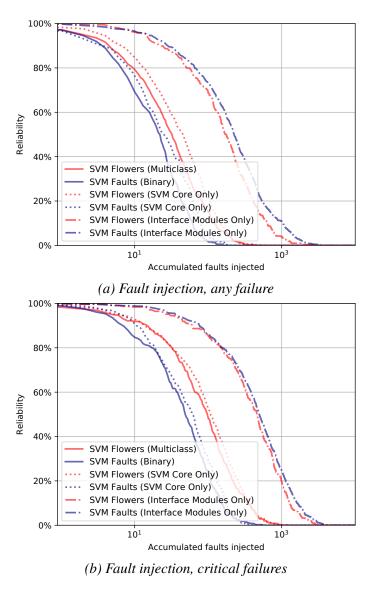

|   | 4.3  | SVM l    | Reliability Assessment Through Emulated Fault Injection    | 49 |

|   |      | 4.3.1    | Fault Injection Set-up                                        | 50 |

|---|------|----------|---------------------------------------------------------------|----|

|   |      | 4.3.2    | Assessment Metrics                                            | 51 |

|   |      | 4.3.3    | Fault Injection Methodology                                   | 52 |

|   |      | 4.3.4    | Results                                                       | 54 |

|   | 4.4  | Radiat   | ion Test Experiment and Results                               | 56 |

|   |      | 4.4.1    | Radiation Test Set-Up                                         | 56 |

|   |      | 4.4.2    | Radiation Test Method                                         | 57 |

|   |      | 4.4.3    | Radiation Test Results for the Binary SVM                     | 58 |

|   |      | 4.4.4    | Radiation Test Results for the Multiclass SVM                 | 58 |

|   |      | 4.4.5    | Assessment of Results and Comparison of the SVM Architectures | 59 |

|   |      | 4.4.6    | Comparison with State-of-the-Art Works                        | 60 |

|   | 4.5  | Conclu   | nsions                                                        | 61 |

| 5 | Asse | essment  | of Machine Learning Algorithms for Near-Sensor Computing      |    |

|   | Thro | ough Fa  | ult Emulation                                                 | 63 |

|   | 5.1  | Introdu  | action                                                        | 65 |

|   | 5.2  | Case-S   | Study ML Algorithm Models                                     | 65 |

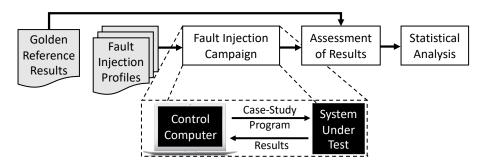

|   | 5.3  | Fault I  | njection-Based Assessment Method                              | 66 |

|   | 5.4  | Fault I  | njection-Based Assessment                                     | 69 |

|   |      | 5.4.1    | Description of Experiments                                    | 69 |

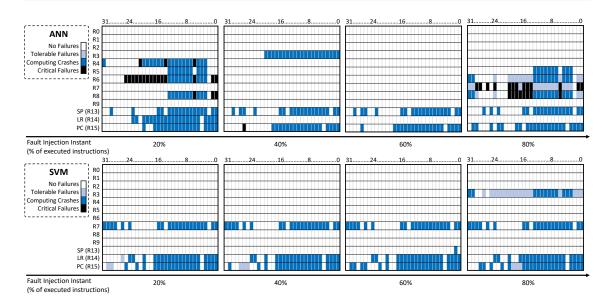

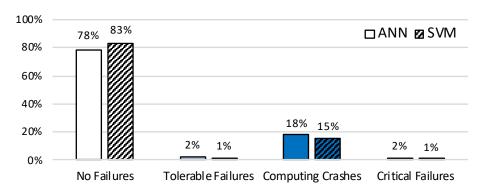

|   |      | 5.4.2    | Analysis of Results by Register                               | 70 |

|   | 5.5  | Radiat   | ion Test-Based Assessment                                     | 71 |

|   | 5.6  | Conclu   | isions                                                        | 72 |

| 6 | Asse | essment  | of Machine Learning Algorithms for Near-Sensor Computing      |    |

|   | unde | er Radia | ation Soft Errors                                             | 74 |

|   | 6.1  | Introdu  | action                                                        | 75 |

|   | 6.2  | Case-S   | Study Machine Learning Models                                 | 75 |

|   | 6.3  |          | mented Case-Study <i>Machine Learning</i> (ML) Algorithms     | 75 |

|   | 6.4  |          | ion Test Assessment                                           | 77 |

|   |      | 6.4.1    | Radiation Test Set-Up                                         | 77 |

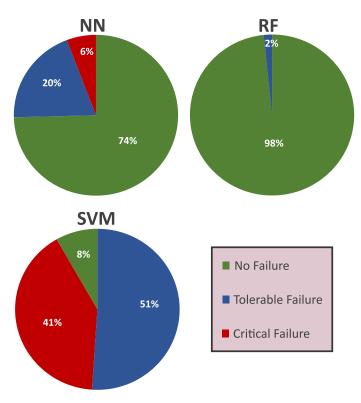

|   |      | 6.4.2    | Radiation Test Results                                        |    |

|   | 6.5  | Conclu   | isions                                                        |    |

# Contents

| 7                    | Deve             | elopment of a Fault Emulation Tool                       | 83  |  |  |

|----------------------|------------------|----------------------------------------------------------|-----|--|--|

|                      | 7.1 Introduction |                                                          |     |  |  |

| 7.2 State-of-the-Art |                  |                                                          |     |  |  |

|                      | 7.3              | Implemented Solution                                     | 85  |  |  |

|                      | 7.4              | Proofs of Concept                                        | 86  |  |  |

|                      |                  | 7.4.1 STM32 Nucleo Target                                | 86  |  |  |

|                      |                  | 7.4.2 Raspberry Pi Target                                | 87  |  |  |

|                      | 7.5              | Conclusions                                              | 91  |  |  |

| 8                    | Con              | clusions                                                 | 93  |  |  |

|                      | 8.1              | Contributions to FPGA implementation of Machine Learning | 94  |  |  |

|                      | 8.2              | Contributions on Low-Power Processor                     |     |  |  |

|                      |                  | Implementations of Machine Learning                      | 96  |  |  |

|                      | 8.3              | Perspectives: Reliable Machine Learning                  | 98  |  |  |

| Bil                  | oliogr           | raphy                                                    | 100 |  |  |

| Lis                  | st of H          | ligures                                                  | 108 |  |  |

| Lis                  | st of T          | <b>Cables</b>                                            | 112 |  |  |

| Lis                  | st of F          | Publications and Presentations                           | 114 |  |  |

| 9                    | List             | of Publications and Presentations                        | 114 |  |  |

|                      | 9.1              | International Journals                                   | 115 |  |  |

|                      | 9.2              | Conferences                                              | 115 |  |  |

| Gl                   | ossar            | y                                                        | 118 |  |  |

| 10                   | Acro             | onym List                                                | 118 |  |  |

# Introduction

Ankind marvels at *Artificial Intelligence* (AI) date back to as early as the antiquity. For instance, in the greek mythology, Talos is described as an automaton made of bronze that is tasked to protect Europa, the mother of King Minos, in the island of Crete. In the ancient Chinese *Liezei* Taoist book, an "artificer" builds a human-shaped automaton that could be mistaken by a live human. Mary Shelly's *Frankeintein* is an example of AI depicted in more recent literature, but that still pre-dates one of the biggest steps in mankind history that has since shaped our understanding (and expectations) of AI: the computer.

With the computational power yielded by the development of computers during the Second World War, computer scientists started to theorize the feasibility of true AI and what it should be like. The prestigious computer scientist Alan Turing even published a paper describing a method to identify if a machine is thinking: the famous Turing Test. Later advances in symbolic processing allowed by computers in the early 50s culminated in the recognition of AI as field with the Darthmouth Workshop in 1956. The years that followed were marked by great enthusiasm by the community, with a multitude of AI applications being developed, such as natural language processing and problem solving algorithms. However, due to hardware limitations, the development hit a barrier and, in 1974, started what is now know was "AI winter", a period where interest was decreased due to disbelief of community in the capabilities of such systems. While some spikes of interest have happened in the 80s, AI would only be regarded with enthusiasm again decades later.

Contemporary to the first developments in AI and later AI winter was the Cold War. This period was marked by constant dispute between the Western Bloc, i.e., Capitalist bloc, and the Eastern bloc, i.e., Communist bloc. These two blocs were in a constant arms race in a variety of domains in order to assert their political ideology and influence. Results of this dispute were, for example, proxy wars in what were known as Third World

countries, nuclear weapon development, and, notably for this thesis, the Space Race. Following the ballistic developments motivated by the second world war, one of the ways that both blocs started to display power was through space exploration. Notable achievements were the launch of the first artificial satellite (Sputinik 1) and the first human in space (Yuri Gagarin) by the *Union of Soviet Socialist Republics* (USSR) and the manned expeditions to the Moon (Apollo program) by the *United States of America* (USA). With the interest in spaceflight came many scientific and engineering questions. In this thesis, the focus is on the problem that was first described in [1]. The development of *Integrated* Circuit (IC)s started in the late 50s and were of great importance for space exploration. In fact, the ICs were used in the Apollo Guidance Computer (AGC), responsible for guidance and control of the Apollo spacecrafts. However, as stated [1], the space environment was not only hazardous to humans, but to ICs as well. Communication satellites were showing unexpected behaviors as their circuitry was triggering in an anomalous fashion. The authors, through an experiment using an electron microscope, showed that ionizing particles could indeed provoke unintended triggering of the IC, effectively causing softerrors, i.e. non-permanent errors in which bits of the system have their value inverted (bitflips). They also showed that the expected error rate extracted from their experiments agrees with the error rate observed in a satellite in orbit, corroborating the claim that the faults were caused by cosmic rays.

From that point on, it was evident that space posed an additional challenge due to the way it affects electronics. This raised the question of whether such effects could happen inside the Earth atmosphere. Later, in 1996 [2], E. Normand showed that, in fact, the same effects observed in space could happen at ground level. The difference resides in the type of particles that cause these effects. Earth's atmosphere and magnetic field work together to shield the planet from cosmic radiation. However, when cosmic rays collide with particles in the Earth's atmosphere, neutrons are released at different levels of energy. These neutrons are capable of producing bitflips, just as cosmic rays.

While research on the effects of radiation developed through the late 70s and 80s, AI was stagnated and still facing some disbelief. It was not until the 90s that the enthusiasm would came back. Developments in semiconductor technology made computers reach a new height in terms of processing power. This allowed for some major breakthroughs, such as the development of an AI that beat the chess grandmaster Garry Kasparov [3]. In

the early 2000s, also pushed by the developments in processing power, ML has started to gain more notoriety. ML is a branch of AI in which the focus is to develop algorithms that learn from data. As more and more people started to gain access to the internet, the amount of usable data skyrocketed opening many opportunities for ML applications. For instance, it was at this time that web companies started to analyze their user's data to provide personalized experiences, i.e., the first development of recommender systems. Furthermore, various entities promoted competitions to instigate researchers and encourage the development of ML applications. For instance, the company Netflix, at the time an online DVD-rental company - held an open competition, namely The Netflix Prize, in which the goal was to predict the rating a user would give for a movie based on the previous ratings he/she has assigned to other movies. Also at this time, The American *Defense Advanced Research Projects Agency* (DARPA) held multiple self-driven cars competitions [4].

During the 2000s and the 2010s, as technology was getting more and more ubiquitous, so was machine learning. During this time, making calls became just minor functionalities of smartphones as they evolved into very capable devices. Home automation devices, such as Amazon Alexa and the Google Home, reached the selves. Even websites evolved into personalized experiences tailored towards each of its user. ML was behind all these advances. However, these solutions often require hefty processing power, which these devices cannot provide. The solution, in these cases, is to forward the data to be analyzed to the cloud. While this solution is acceptable in these cases, not all applications can rely on a connection to a server. For instance, self-driven cars relying on internet connection would be disastrous. Thus, there has been movements towards edge-AI. The idea is to embedded the ML computation to the devices closer to the sensors that capture data, i.e. the ML is placed on the edge. Works have been conducted to port the models over to platforms that are candidates to for edge processing, such as *Graphic Processor Unit* (GPU)s, *Field-Programmable Gate Array* (FPGA)s and microcontrollers.

Edge-AI has also started to find its way in space applications. The Perseverance Mars rover, launched in July 2020 and which landed on Mars in February 2021, implements Edge-AI. Embedded in the rover is the *Planetary Instrument for X-ray Lithochemistry* (PIXL), an equipment designed to look for traces of ancient microscopic life. AI models are used to better point the instrument to the intended location [5]. The rover also used

AI to help on its landing. This is especially important as the distance between Mars and Earth makes that a signal takes from 5 to 20 minutes to travel between the planets, making it impossible to pilot the craft remotely from Earth. Apart from the rover, companies and universities have been investigating the usage of AI in nanosatellites. An example is the Lockheed Martin joint project with the University of Southern California for the development of the La Jument nanosatellites, specifically for testing ML implementations in space.

Critical systems are systems in which a failure may lead to catastrophic or costly results. For instance, a failure in a self-driven vehicle may cause the loss of a human life. A failure on a rover on Mars may turn billions of dollars in investment into a very expensive robotic decoration to the landscape of Mars. As ML is being embedded in such systems, and they are subject to radiation induced faults, be it at ground level, avionic altitudes and on space, it is important to understand how these faults affect these systems. In this sense, the objective of this thesis is to evaluate the reliability of machine learning models implemented in different hardware platforms.

In this work, the reliability of three popular ML models against radiation induced faults was studied. These models are: Artificial Neural Network (ANN), SVM and Random Forest (RF). To estimate their reliability, two approaches were used. The first was fault emulation. As mentioned, radiation induced faults may result in bitflips. To evaluate how these bitflips affect the algorithms, they are implemented on a device and the memory of such device is manipulated to artificially invert the values of bits. In doing so, it is possible to evaluate the impact of such faults on the system while also identifying which parts of the system are the most sensitive. The second method used was accelerated testing. As the time expected for a fault to happen is long, the target devices containing the ML algorithms are placed in front of artificial radiation sources that surpasses natural fluxes by various orders of magnitudes. This way, months or even years of real-life system exposure is simulated in a fraction of the time, allowing for an estimation of fault rate and behavior of the system in the real environment. In terms of the devices used, two SVM models were implemented using FPGA. Furthermore, implementations of the three ML models in microcontrollers were also studied. All these solutions were also tested using fault injection as a complimentary study.

This thesis is organized as follows: Chapter 1 describes the terminology related to the

radiation testing of components and systems. Chapter 2 contains a review on ML and the algorithms used in this work. Chapter 3 presents the first evaluation of the reliability of a SVM under the effect of fast neutrons. The algorithm was implemented in FPGA and tested using a fast neutron source and fault emulation techniques. Chapter 4 complements this work by testing two SVM models implemented in FPGA under the effect of thermal neutrons by also performing an accelerated test using a radiation source and a fault emulation campaign. Chapter 5 analyses the effect of fast neutrons in microcontroller implementations of ANN, SVM and RF using a custom fault emulator. In Chapter , the same ML algorithms are tested using a neutron source. Chapter 7 introduces a custom fault emulator implemented to serve as tool in this thesis. Chapter 8 presents the final remarks.

1

# Radiation testing of Components and Systems

# Contents

| 1.1 | Soft E | rror Taxonomy                            |

|-----|--------|------------------------------------------|

|     | 1.1.1  | Single-Bit Upset (SBU)                   |

|     | 1.1.2  | Multiple-Bit Upset (MBU)                 |

|     | 1.1.3  | Single-Event Transient (SET)             |

|     | 1.1.4  | Single-Event Functional Interrupt (SEFI) |

|     | 1.1.5  | Single-Event Latch-up (SEL)              |

| 1.2 | Metri  | cs                                       |

|     | 1.2.1  | Particle Flux                            |

|     | 1.2.2  | Fluence                                  |

| Chapter 1. Radiation testing of Components and Systems |                       |  |  |  |

|--------------------------------------------------------|-----------------------|--|--|--|

| 1.2.3                                                  | Cross-section         |  |  |  |

| 1.2.4                                                  | Soft Error Rate (SER) |  |  |  |

In this Chapter, a review on radiation testing of components and systems is presented. The terminology and definitions used in this thesis are discussed.

# 1.1 Soft Error Taxonomy

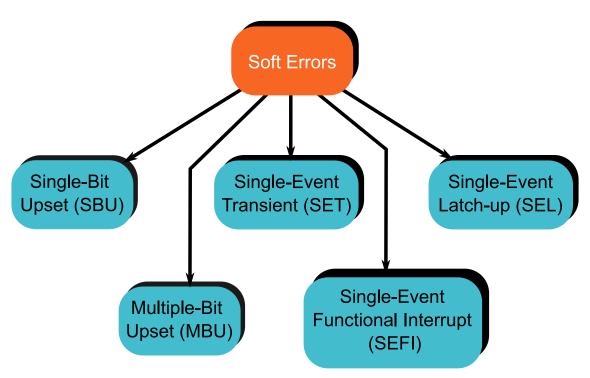

As defined in the JESD89A standard [6], soft errors are any type of non-destructive functional disruption of a system normal execution induced by any type of radiation. A taxonomy of soft errors is present in Figure 1.1. Each type of Soft Error is described in the sequence.

Figure 1.1: Taxonomy of Soft Errors, according to [6]

# **1.1.1** Single-Bit Upset (SBU)

A Single-Bit Upset (SBU) is when a particle causes a bit of a memory element to change from its expected. Examples of memory elements are Random Access Memories (RAMs), latches and registers. It is worth nothing that no permanent damage is done to the components, i.e., the memory still operates correctly but it holds an erroneous value. If the erroneous value is overwritten before being used, the system will not present an unexpected behavior.

### **1.1.2** Multiple-Bit Upset (MBU)

With the ever-increasing miniaturization of devices, memory cells are getting physically close to each other with every new technological step. This makes so that a single particle may be capable to cause bit upsets in multiple memory cells, causing a Multiple-Bit Upset (MBU). It is important to notice that MBU refers to a single event causing multiple bits to flip, and not multiple events each causing a bit to change.

#### **1.1.3** Single-Event Transient (SET)

When a particle hits a semiconductor device, it may transfer energy to it, causing transient pulse in the circuit. In analog systems, this can be very problematic, as disturbances in a signal may cause the system to fail, e. g. the pulse may be amplified by an operational amplifier. In digital system, SET may interfere with the combinational logic of the circuit. This disturbance may be capture by a memory element, possibly leading to unwanted behavior [7].

# 1.1.4 Single-Event Functional Interrupt (SEFI)

A Single Event Functional Interrupt (SEFI) is a soft error which causes the system to lose its functionality. For example, a soft error may attack a control bit, making the system reset, hang or malfunction. The system must be recoverable without power cycling for the event to be considered a SEFI. Also, no permanent damage incurs in the circuit.

# 1.1.5 Single-Event Latch-up (SEL)

Similar to a SEFI, a *Single Event Latch-Up* (SEL) is a soft error that causes the system to lose its functionality, but different than a SEFI, it is only recoverable through power cycling, i.e. turning the system off and back on. It happens when a particle passes through a sensitive part of the circuit, creating an abnormal high-current state. As noted in [6], a common example is when a particle induces the creation of parasitic bipolar (p-n-p-n), effectively shorting power to ground.

### 1.2 Metrics

In this Section, the metrics related to radiation testing are presented and discussed.

#### 1.2.1 Particle Flux

The particle flux  $(\phi)$ , commonly referred to simply as flux in the context of radiation testing, is the rate in which particles reach a component per unit of area. As so, it is expressed in  $particle/s/cm^2$ . In whichever physical environment a component is executing, be it ground level, avionic altitudes or in space, it is constantly being bombarded with a spectrum of particles at multiple energies, each environment having it is own characteristics. For instance, in space, cosmic rays contribute the most to particle spectrum, which in turn makes the flux of protons, alpha particle and heavy ions the highest. At ground and avionics level, due to Earth's natural protection, the flux of cosmic ray-related particles is lower. However, secondary particles are generated when cosmic rays collide with oxygen and nitrogen atoms in the atmosphere releasing neutrons, which are in turn the most common particles at ground and avionics altitude [8].

Knowing the particle flux of an environment allows for the design of experiments to simulate it. Particle accelerators are great tools to not only mimic a environment (even though partially) but to perform accelerated testing. They can provide fluxes that are orders of magnitude higher than natural fluxes, allowing for the emulation of months (or even years) of the real environment. For example, for some of the experiments described in this work, the GENEPi2 [9] 14 MeV accelerator from the Laboratoire de physique subatomique et de cosmologie de Grenoble (LPSC) has been used, in which we have used fluxes of roughly  $10^6$  neutrons/s/cm<sup>2</sup>. The natural flux of 14 MeV neutrons at ground level is roughly  $5*10^{-2}$ neutrons/s/cm<sup>2</sup> [10], with the GENEPi2 flux being  $2*10^7$  times larger than it. Thus, 1 hour of testing in the GENEPi2 equipment is equivalent to 2.281 years in the real environment.

#### 1.2.2 Fluence

Fluence  $\Phi$  represents the total number of particles per  $cm^2$  that have traversed an environment in a time interval  $\Delta t$ . It is represented as the integral of the flux over time, described in Equation 1.1:

$$\Phi = \int_{t_0}^{t_f} \phi(t)dt \tag{1.1}$$

where  $\Delta t = t_0 - t_1$  are the initial and final time of the interval being measurement, respectively, and  $\phi(t)$  represents the flux as a function of time. As it is a product between flux  $(particle/s/cm^2)$  and time, the result measuring unit is  $particle/cm^2$ . Fluence is particularly useful to define further metrics, such as cross-section *Failure in Time* (FIT), to be described in the sequence.

#### 1.2.3 Cross-section

Cross-section is a useful tool to quantify the radiation effects on a hardware platform or system. It describes the probability of a single particle causing a failure in the system. Thus, it is expressed as shown in Equation 1.2:

$$\sigma = \frac{N_f}{\Phi} \tag{1.2}$$

where  $N_f$  is the number of failures identified during the irradiation with the fluence  $\Phi$ . Assuming that a fault is a result of a single particle interacting with the component, the measurement unit for the cross-section is  $cm^2$ .

It is common to distinguish between static and dynamic cross-sections. Static cross-section measures the sensitivity of a hardware platform agnostic of an application. For example, static cross-section of a *Dynamic Random Access Memory* (DRAM) memory is the probability of a particle to cause a bit flip in a cell. In this case, a way to measure the static cross-section is to load a pattern on the memory, irradiate it, count the number of failures and use Equation 1.2. On the other hand, dynamic cross-section represents the probability of a particle to cause a fault when a application is being run on a platform, e. g. a machine learning algorithm running on an FPGA. It takes into account that the application itself may mask some faults, e.g., faults outside the memory space being used may not need to a failure, providing a metric that represents the system as whole.

While the dynamic cross-section is the most useful when it comes to the final implementation of system. Measuring the dynamic cross-section is expensive due to the cost of radiation campaign. To overcome this, it is possible to estimate the it from the static cross-section, which may be provided by the platform vendor. They can be related by

Equation 1.3.

$$\sigma_{dynamic} \approx \sigma_{static} * \theta_{system}$$

(1.3)

with  $\theta_{system}$  being the probability of a fault becoming a failure, which can be estimated through fault injection campaigns.

### 1.2.4 Soft Error Rate (SER)

Soft Error Rate (SER) is the rate of soft error observed in a system in a given environment [7]. A popular way to express it is through FIT. 1 FIT is equivalent to 1 failure per 1 billion hours. It is calculated using Equation 1.4:

$$FIT = \sigma * \phi_{env} * 10^9 \tag{1.4}$$

where  $\sigma$  is the system cross-section and  $\phi_{evn}$  is the environment flux expressed in  $particle/cm^2/h$ .  $10^9$  represents 1 billion hours, as per the definition of FIT.

# 2

# Revision on Machine Learning

# Contents

| 2.1 | Definit | tions                     |

|-----|---------|---------------------------|

|     | 2.1.1   | Dataset                   |

|     | 2.1.2   | Input Sample              |

|     | 2.1.3   | Feature                   |

|     | 2.1.4   | Supervised Learning       |

|     | 2.1.5   | Unsupervised Learning     |

|     | 2.1.6   | Classification            |

|     | 2.1.7   | Regression                |

| 2.2 | Artific | ial Neural Networks (ANN) |

| 2.3 | Suppo   | rt Vector Machine (SVM)   |

|     | 2.3.1   | Multiclass SVM            |

| 2.4 | Random Forest |  |  |  |  |  |  |  |  |  |  |  |  | 22 |  |

|-----|---------------|--|--|--|--|--|--|--|--|--|--|--|--|----|--|

In this Chapter, the ML terminology and techniques are described. Furthermore, a review of the algorithms studied is presented.

#### 2.1 Definitions

#### 2.1.1 Dataset

A dataset is a collection of data of a particular problem. An example of a famous dataset is the Fisher's Iris flower dataset [11]. The dataset is a collection of measurements, sepal and petal length and width, of multiple specimen of Iris flowers, a flower genus, of three different species: *Setosa*, *Virginica* and *Versicolor*. The data was collected by E. Anderson and became famous when R. Fisher [11] used statistical learning techniques to design a classifier capable to predict the species of an Iris flower from its measurements. Other examples of datasets are shown in [12].

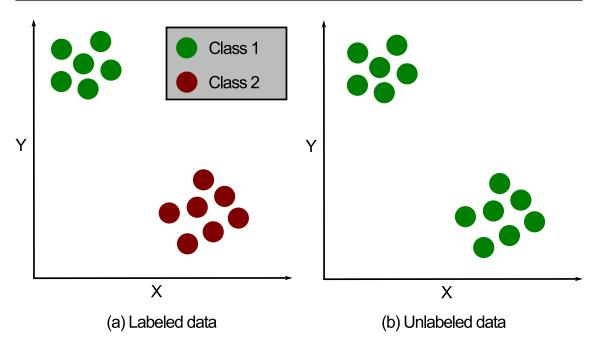

A dataset may be labelled or unlabeled. A labeled dataset contains the expected output of its samples. For instance, the Fisher Iris dataset, the class of each specimen is known. This allows for the training of machine learning models to be used to infer an output over a sample whose class is unknown. On the other hand, an unlabeled dataset is not annotated. This type of dataset is often used for clustering problems. Figure 2.1 shows an example of labeled and unlabeled datasets.

# 2.1.2 Input Sample

An input sample is a single instance that follows the structure of the dataset of which some information is unknown and a machine learning technique is going to be used to predict this information. For example, for the Fisher Iris dataset, an input sample is the measurements of a flower whose class is unknown. The goal of the machine learning algorithm is to predict the class of this input sample.

#### 2.1.3 Feature

A feature is one of the dimensions of a sample. For example, as mentioned, the Iris flower dataset is a set of measurements of multiple specimens of Iris flowers. These

Figure 2.1: (a) Illustrative example of a labeled dataset. (b)Illustrative example of an unlabeled dataset.

measurements are sepal length, sepal width, petal length and petal width. Each of these measurements is a feature, i.e., each sample is composed of 4 features/dimensions.

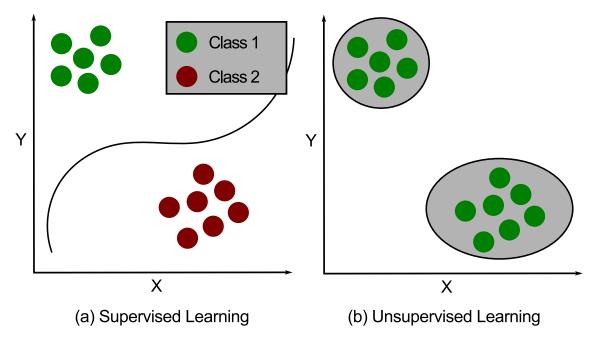

## 2.1.4 Supervised Learning

Supervised Learning is a subset of the machine learning algorithm that performs the learning over a labeled dataset. The workflow of supervised learning algorithms is often divided in two distinct phases: learning and classification. During the learning phase, a training algorithm to generate a mathematical model that maps samples of a dataset to their expected labels. The dataset used for this learning phase is referred to as training dataset. In the classification phase, the generated model is used to classify samples whose labels are unknown. For instance, for self-driving cars, a dataset of road pictures (samples) associated with the action that should be taken, such as breaking or turning (label) could be used to train a model. On a real-life environment, a camera could be mounted on a car, input pictures to the model (input samples), which would output the action that should be taken. Please note that this is an oversimplification of the self-driving car application and it is used only with illustrative purpose. An illustration of a supervised learning is shown inf Figure 2.2-(a).

### 2.1.5 Unsupervised Learning

Different than supervised learning, unsupervised learning algorithm performs learning on unlabeled datasets. For examples, a machine learning design may have access to a dataset of emails and want to develop a model that is capable of distinguishing between spam and regular mail. However, the dataset is unlabeled, meaning that the mails are not identified as spam or not. To goal of an unsupervised learning algorithm is to identify the underlying structure of data and group them accordingly, i.e., find clusters of data. Unsupervised learning is illustrated in Figure 2.2-(b).

Figure 2.2: (a) Illustrative example of a labeled dataset. (b)Illustrative example of a unlabeled dataset.

#### 2.1.6 Classification

The goal in a classification problem is to derive a function  $X \to Y$ , s.t.  $X \in \mathbb{R}^n$ , n being the number of features in the input dataset, Y being a discrete set. For instance, the Iris Flower problem [11] is an example of classification problem. The output set Y is defined as  $\{setosa, virginica, versicolor\}$ . In a more semantic definition, a classification consists predicting the class of an unknown sample based on its characteristics.

#### 2.1.7 Regression

A regression problem, similar to a classification problem, also consists in finding a  $X \to Y$  function, s.t.  $X \in \mathbb{R}^n$ , n being the number of features in the input dataset, but differently than classification, Y is a continuous value. An example is the Boston housing problem [13]. The dataset contains information concerning housing in the Boston Mass, U.S.A. The goal is to estimate the value of real-state based on this information. As "value" is a continuous variable, this is a regression problem.

# 2.2 Artificial Neural Networks (ANN)

ANN is a classical machine learning technique, with its first dating to the 40s, with the work of McCulloch and Pitts [14]. In their paper, the authors mention that due to the characteristics of biological neurons, their behavior could be treated as propositional logic. At that moment, the idea was embraced by the community and other related works exploring the technique were developed. However, the research on the topic reached a plateau at the end of the 60s due to limited processing power at the time. The interest resurged in the mid-80s [15] with the rise of parallel processing and, in recent years, their popularity only grew, being implemented in platforms such as GPUs [16, 17] and FPGA [18].

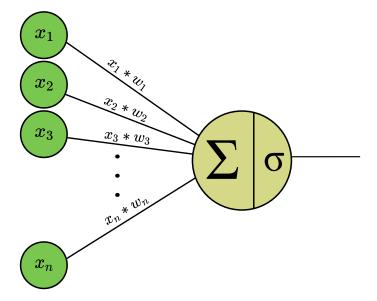

Figure 2.3: Structure of a Perceptron/Neuron

As mentioned, the idea of the ANN is inspired on the way biological neurons be-

have. In biology, neurons receive a series of inputs (neurotransmitters) on their dendrite, and, depending on what was received, forwards neurotransmitters over its axon. The analogous "artifical" neuron is shown in Figure 2.3. The neuron receives a set of inputs  $\{x_1, x_2, ..., x_n\}$ . Each input is multiplied with a weight  $\{w_1, w_2, ..., w_n\}$  and the results are summed. This process is also known as *Multiply-ACcumulate* (MAC) operation. The result is then evaluated on an activation function  $\sigma$ . A structure composed of a single neuron as portrayed in Figure 2.3 is called a Perceptron. While limited, a Perceptron works a binary classifier, i.e., a classifier capable of distinguishing between two classes. For example, let's take a dataset with only two classes  $\{A, B\}$ . A perceptron can be trained to output positive values for samples of the class A, while outputting negative values for samples belonging to the class B by carefully selecting a proper activation function. A possible candidate to achieve this behavior is a using the  $\sigma(x) = tanh(x)$ .

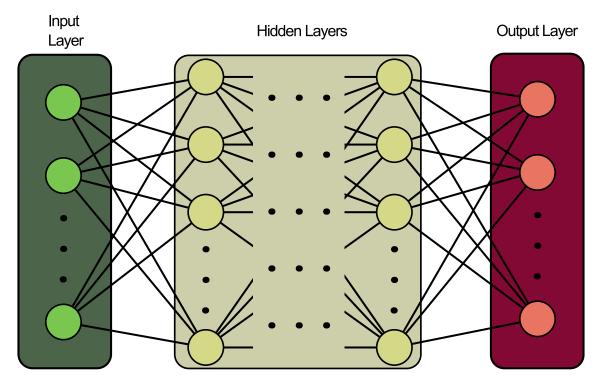

As discussed, the perceptron is somewhat limited, being restricted to binary problems. Furthermore, it was shown in [19] that a perceptron is incapable of learning the XOR function. To overcome this, the idea of multi-layer networks was introduced. The neurons are organized in a layered manner, as shown in Figure 2.4. The general idea is that a neuron is going to receive the outputs of the neurons in the preceding layer, perform the MAC operations and forward to the next layer, hence why this topology is also known as feed-forward neural network. The structure is divided in three segments: the input layer, the hidden layers and the output layer. The neurons in the input layer are solely responsible to inject the inputs to the neurons of the next layer. The number of neurons in this layer is exactly the number of dimensions, i.e., features, of the dataset. The majority of the learning often takes place in the hidden layers. The number of layers as well as the number of neurons per layers are variable, to be defined the neural network designer. The output layer, similar to the input layer, has its size tied to the dataset being used. The number of neurons is exactly the number of classes of the problem at hand, each neuron specifically representing one of the classes, which makes a neural network intrinsically capable of performing multiclass classification.

Figure 2.4: Structure of a Artificial Neural Network

# 2.3 Support Vector Machine (SVM)

SVM is a classification algorithm belonging to the group of supervised machine learning techniques [20]. The algorithm addresses the problem of binary classification, i.e., a problem in which an observation (herein an input vector) has to be classified in one of two possible classes. Being a supervised machine learning technique, its workflow requires two phases, each one performed with a different algorithm: one for training *Sequential Minimal Optimization* (SMO) algorithm) and another for classification (SVM algorithm).

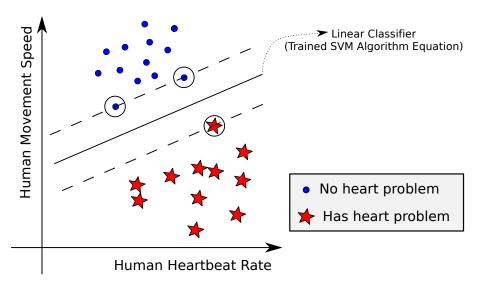

Figure 2.5 presents an application of a SVM-based classification able to indicate whether an astronaut reaches a risky condition to have a cardiac problem – for instance, according to her/his heartbeat rate while moving or speeding on a treadmill in a space station.

An input vector for the SVM algorithm is a pair (*heartbeatrate*, *speed*), which are referred to as features or dimensions. The set of all measured pairs (*heartbeatrate*, *speed*) is defined as a feature space. In order to train the SVM algorithm, i.e. to model the SVM algorithm equation, a set of input vectors – herein called training vectors – is required. The training vectors are indeed a subset of the feature space, however, the class of them are known beforehand, e.g., input vectors from people whose cardiac conditions are known.

Figure 2.5: An SVM algorithm equation (linear classifier) trained to classify the heartbeat condition. The horizontal axis represents the human heartbeat rate, while the vertical axis represents the human movement speed.

At the training phase, the SMO algorithm uses the training vectors to calculate the weights of the linear function that better separates input vectors from the two classes, for example in Fig. 2.5: class "No heart problem" and class "Has heart problem", and the training vectors respectively represented by blue dots and red stars. The calculated weights, therefore, model a linear classifier dividing the elements of the two classes, i.e. they model the SVM algorithm equation.

Formally, a tuple  $(\vec{x_i}, y_i)$  defines a training vector, in which the support vector  $\vec{x_i} \in \mathbb{R}^2$  in the example: heartbeat rate and speed features – both belonging to the set of real numbers – that are measurements performed on a person i. Moreover, the class  $y_i \in \{-1,1\}$ , and in the example: -1 and 1 represent respectively the class "No heart problem" and the class "Has heart problem".

At the classification phase, the trained SVM algorithm is able to classify an input vector whose class is unknown, e.g., if the heartbeat rate and speed of an astronaut running on a treadmill indicate either "No heart problem" or "Has heart problem". The SVM algorithm equation to classify an input vector  $\vec{x}$  with an unknown class is thus defined as:

$$score(\vec{x}) = \sum_{i=1}^{n} \alpha_i y_i(\vec{x}_i \cdot \vec{x}) + b$$

(2.1)

Each  $\alpha_i$  is a weight, found at the training phase and associated with its respective training vector  $(\vec{x_i}, y_i)$ . The weights  $\alpha_i$  shape the linear classifier (i.e. the SVM algorithm

equation). At the training phase, the SMO algorithm also calculates the bias factor b. The sign of the  $score(\vec{x})$  determines the class of the input vector  $\vec{x}$ , in the example: positive for "Has heart problem" and negative for "No heart problem".

#### 2.3.1 Multiclass SVM

Even though, originally, SVM was created to perform binary classification. However, it may be extended to fit multiclass problems. This is achieved by dividing the dataset into subsets so it is possible to use binary classification. The two most popular techniques are One-vs-One and One-vs-All. In this work, we made use of One-vs-One, which is explained in the sequence. One-vs-All was left out for the sake of brevity.

In the One-vs-One approach, a binary classifier is trained for each pair of classes. For instance, if there are three possible classes, e.g.  $\{A,B,C\}$ , a classifier is trained only with samples from classes  $\{A,B\}$  in order to classify unknown samples between classes A and B. Another one is trained with samples from classes  $\{A,C\}$  to classify an unknown simple into either A or C. A classifier for  $\{B,C\}$  is also trained. To infer a class for an unknown sample, it is evaluated on the three trained SVMs, each one inferring one class. The class that is the most inferred is chosen as the final class. For example, if SVM  $\{A,B\}$  outputs A, SVM  $\{A,C\}$  outputs A and SVM  $\{B,C\}$  outputs B, as A has been inferred twice whereas B was only inferred once and C has not been inferred, the final class is A

# 2.4 Random Forest

RF is a supervised learning algorithm that performs the learning by building a collection *Binary Decision Trees* (BDT). To understand its model, it necessary to discuss the workflow of BDTs.

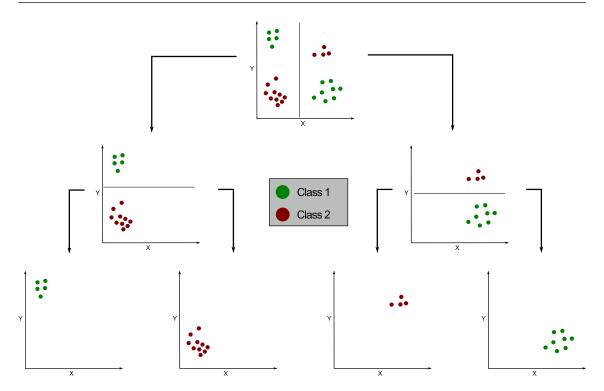

The idea of a BDTs is to partition the training dataset in two, trying to group elements of the same class together. The same process is then applied to each of these partitions recursively, up until the partitions have only examples of a single class. This process can be represented using binary trees, as illustrated in Figure 2.6. Each non-leaf node contains the partitioning function, while the leafs contain only an identifier representing the class of the elements it contains. To classify an input sample using a BDT, the input sample

Figure 2.6: Example of partitioning performed by BDT

is evaluated in the partitioning function of the root node, which will direct it to either the left or right child node. This process is repeated recursively until a leaf is reached. The class assigned to the input sample is the class represented by the leaf reached.

While BDTs work by themselves as supervised learning algorithms, they are prone to overfitting the data. As mentioned, the partitioning is done until they contain members of a single class. This is particularly problematic for datasets that contain outliers, i. e. samples of class that differ from other elements of the same class, or noisy data. The algorithm will try to accommodate these examples in the partitioning process, which may create a BDT that does not generalise well over the training dataset. A way to try to overcome this is building a "forest", i.e. a collection of BDTs. Each tree is trained over slightly modified versions of the dataset generated using bagging, also known as bootstrap sampling. Each new dataset is generated by performing uniform sampling with replacement on the original dataset. The number of datasets and, consequentially the number of BDTs trained is defined by the machine learning designer and varies from case to case. To classify an input sample using the forest generated, it is first classified all the trees generated then, the most common class among the results is the final classification of the RF.

# 3

# Support Vector Machine under Radiation Effects

# **Contents**

| 3.1 | Introd | luction                                                  | 28 |

|-----|--------|----------------------------------------------------------|----|

| 3.2 | Case-S | Study SVM Architecture                                   | 29 |

|     | 3.2.1  | State-of-the-Art SVM in Hardware                         | 29 |

|     | 3.2.2  | SVM Architecture Design                                  | 30 |

|     | 3.2.3  | Set of Input Vectors                                     | 30 |

| 3.3 | SVM A  | Architecture Assessment Through Fault Emulation Campaign | 31 |

|     | 3.3.1  | Device Under Test (DUT)                                  | 31 |

|     | 3.3.2  | Assessment metrics                                       | 32 |

|     | 3.3.3  | Fault Emulation Method                                   | 33 |

|     | 3.3.4 | Results of the Fault Emulation Campaign |

|-----|-------|-----------------------------------------|

| 3.4 | Radia | tion Test Experiment and Results        |

|     | 3.4.1 | Radiation Test Set-Up                   |

|     | 3.4.2 | Radiation Test Method                   |

|     | 3.4.3 | Assessment of Radiation Test Results    |

|     | 3.4.4 | Comparison with State-of-the-Art Works  |

| 3.5 | Concl | usions                                  |

#### 3.1 Introduction

Machine learning algorithms have been increasing in popularity in both academic and industry because of their capacity to learn from existing data, and to predict future outcomes. Those two features, learning and predicting, have motivated the use of this type of algorithm in many applications such as medical diagnostics [21], robot intelligence [22], and geoscience/aerospace domain [23]. What all these application have in common is the need to identify a pattern – in a raw amount of data – and to decide which action has to be taken based on the pattern classification.

Among machine learning algorithms, the SVM, described in Section 2.3, has been extensively used over the past years for pattern recognition and data mining. The SVM has high generalization capacity and robustness in both data classification and regression. SVMs are more commonly used in classification problems because they are based on the idea of finding a hyperplane that best divides a dataset into classes. In other words, SVM separates the elements of a dataset in classes that have similar properties. However, since the amount of data are increasing in size and complexity, the necessity of providing some alternatives to accelerate the performance of the SVM classification is still a current issue.

In the sense of accelerating the SVM classification, this algorithm has been implemented in FPGAs [24]. Nevertheless, FPGAs are considered sensitive to radiation effects [25], especially *Static Random Access Memory* (SRAM)-based FPGAs on which particle-induced transient faults may corrupt their configuration memory in a effect also known as *Single Event Upset* (SEU)s. Transient faults are indeed able to change three elements in an FPGA: the configuration of a routing connection; the configuration of a *Look-Up Table* (LUT); and the data inside of an embedded *Block RAM memory* (BRAM). As the effects might be persistent, a new bitstream must be loaded to the FPGA to correct it. Furthermore, a transient fault is able to invert a *Flip-Flop* (FF) of a *Configuration Logic Block* (CLB) of the user's sequential logic. In this case, the next load of the FF may correct this fault.

Recent works have studied the effects of radiation-induced transients faults on hardware implementations of machine learning algorithms, such as ANNs and Convolutional Neural Networks [26–28] and Bayesian machines [29]. To the best of our knowledge, however, no related work has been studied the radiation effects on SVM. In this Chapter,

we present the first assessment of an FPGA-implemented SVM architecture under radiation effects by looking at how induced transient faults affect its behavior. An extensive fault emulation campaign and experimental radiation tests with a 14-MeV neutron generator beam have been carried out to analyze SVM responses. The radiation test campaign has been performed in GENEPi2 neutron accelerator [9] using an Artix-7 FPGA.

# 3.2 Case-Study SVM Architecture

Depending on the application, a software-implemented SVM algorithm is continuously demanded to classify input vectors  $\vec{x}$ , consuming energy and occupying computational resources that could be reallocated to other tasks. A hardware-implemented SVM algorithm is an effective alternative solution to accelerate the computation and to save the energy of systems.

Training and SVM-based classification phases have been implemented in hardware as an *Application-Specific Integrated Circuit* (ASIC) in [30, 31] and by using an FPGA in [24, 32] to speed up the SVM algorithm execution. Furthermore, related works have also implemented in hardware only the SVM-based classification phase [31] [24], conducting the training phase in software platforms such as MATLAB or LibSVM [33], and enabling further energy savings in ASICs used to make preliminary offline inference.

#### 3.2.1 State-of-the-Art SVM in Hardware

Several solutions have been proposed for implementing SVM classification in hardware [24,30,31]. The implementation in [31] multiplies the *Support Vector* (SV)s with an input vector all in parallel. This has been done to achieve maximum performance to suit their application (voltage-droop prediction), which demands a very fast classification time. The limitation of this approach is being able to generate only linear and second-order polynomial classifiers. To overcome this limitation, works [24] and [30] have implemented non-linear classification by using a *Coordinate Rotation DIgital Computer* (CORDIC) algorithm, which requires solely hardware-friendly functions (e.g., shift and sum operations) to approximate the calculations over some clock cycles. Likewise in [31], the operations with the SVs and an input vector are also performed in parallel in [24] and [30]. The

CORDIC algorithm-based implementations have higher memory requirements in comparison with [31] because look-up tables are used to approximate exponential functions and more clock cycles are needed to output an answer. However, they generate more complex classifiers.

#### 3.2.2 SVM Architecture Design

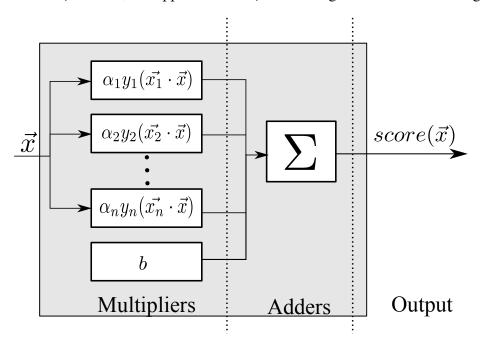

As our dataset is linearly separable, further described in Subsection 3.2.3, we opted for the approach in [31] with a first order, i.e. linear, classifier to explore its benefits in terms of memory requirements and performance. Figure 3.1 shows the case-study SVM architecture. In addition, we have calculated the  $\alpha_i y_i$  products beforehand, reducing one multiplication for each SV  $\vec{x_i}$ , and further optimizing the SVM architecture. The final implementation is completely combinatorial. The circuit is composed by three main parts: the Multipliers, the Adders and the Output, as illustrated in Figure 3.1.

The SVM architecture adopted a 16-bit fixed-point representation, 8 bits being dedicated to representing the real part, following the ideas in [24,30,31]. Through simulations, we have confirmed that the representation is enough to avoid possible overflows and also to maintain sufficient precision. The primary inputs are composed of 32 bits (16 for each dimension of the input vector). The primary outputs are composed of 49 bits to maintain the calculation precision.

# 3.2.3 Set of Input Vectors

The target set of input vectors (dataset) has been obtained from Monte-Carlo simulations representing current peaks and global delays obtained from golden ICs and faulty ICs [34]. The input vector is 2-dimensional, and 150 input vectors have been obtained from golden IC samples and 150 input vectors from faulty IC samples. The dimensions are thus:

• **Dimension 1**: global delay

• **Dimension 2**: current peak

This set of input vectors is sufficient to distinguish faulty asynchronous IC samples from fault-free asynchronous IC samples [34]. The set of input vectors has been parti-

tioned into 2 subsets of the same size, one for training and another for classification, each one with 75 golden IC samples and 75 faulty IC samples. A SVM model has been generated by using MATLAB. From this model, we have obtained the  $\alpha$ 's and their respective support vectors  $\vec{x_i}$ . In total, 50 support vectors  $\vec{x_i}$  have been generated at the training phase.

Figure 3.1: Overview of the hardware-implemented SVM architecture design.

# 3.3 SVM Architecture Assessment Through Fault Emulation Campaign

This section assesses the ability of the case-study SVM architecture to tolerating transient faults. We have used a fault-injection method able to emulate transient faults in an FPGA-implemented SVM architecture.

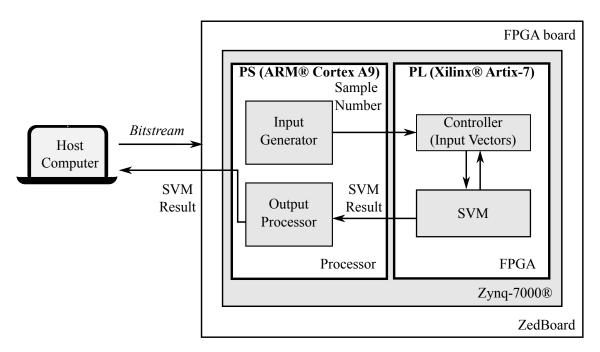

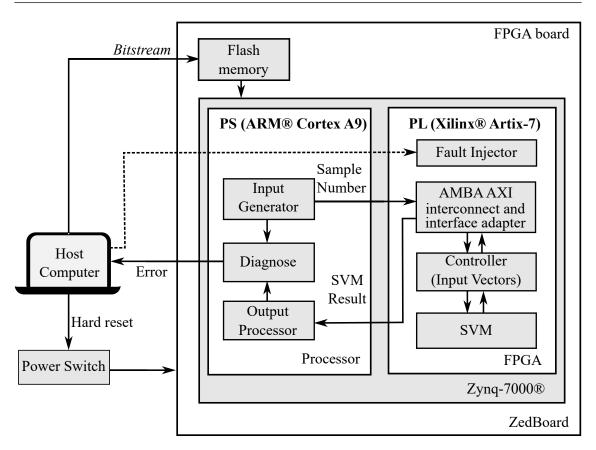

# 3.3.1 Device Under Test (DUT)

The DUT is a fully combinational SVM architecture design using fixed-point representation for its support vectors  $\vec{x_i}$  and wights  $\alpha_i$  (cf. section 3.2). The target platform is a Zynq-7000 [35], which is composed of two main parts: the Processing System (PS), consisting of an ARM Cortex-A9, and the Programmable Logic (PL), a Xilinx Artix-7 FPGA. The Zynq-7000 has been used on the ZedBoard development board The SVM

architecture was implemented in PL part by using VHDL. The resource utilization of the PL is shown in Table 3.1.

The SVM algorithm depends fundamentally on multiplications, cf. section 2.3. Most modern FPGAs, including the Artix-7, have Digital Signal Processing units (DSPs), which implement multiplications in dedicated hardware. All the multiplications of the DUT have been mapped in the DSPs, which is the reason why DSP resources are prominent in Table 3.1.

| Resource                               | Utilization | Elements |

|----------------------------------------|-------------|----------|

| Flip-Flops (FFs)                       | 1.65 %      | 1751     |

| Digital Signal Processing units (DSPs) | 40%         | 88       |

| Look-Up Tables (LUTs)                  | 7.24%       | 3854     |

*Table 3.1: Resource utilization of the PL (Artix-7)*

#### 3.3.2 Assessment metrics

We have assessed the case-study SVM architecture under transient faults by stimulating different input vectors  $\vec{x}$  at its primary inputs, observing the related results  $score(\vec{x})$  at its primary outputs, and classifying them into three types:

- **No Failure:** the result at the primary outputs of the SVM architecture does not differ from the golden reference (i.e. fault-free output vector);

- Tolerable Failure: there is a mismatch between the result at the SVM primary outputs and the golden reference, however, the resulting class is correct, i.e. the sign of the result at the primary outputs is equal to the sign of the golden reference;

- **Critical Failure:** there is a mismatch between the result at the SVM primary outputs and the golden reference, and the resulting class is not correct.

In order to assess the rate of critical failures provoked by the emulation of a single transient fault on a node n of the SVM architecture design, we define the following metric:

$$CriticalFailureRate(n) = \frac{\#CriticalFailures(n)}{\#InputVectors}$$

(3.1)

in which # *CriticalFailures*(n) is the total number of critical failures provoked by a single transient fault injected at node n of the SVM architecture design, and # *InputVectors* is the total number of vectors tested at the primary inputs of the SVM architecture with the node n under the same fault emulation.

#### 3.3.3 Fault Emulation Method

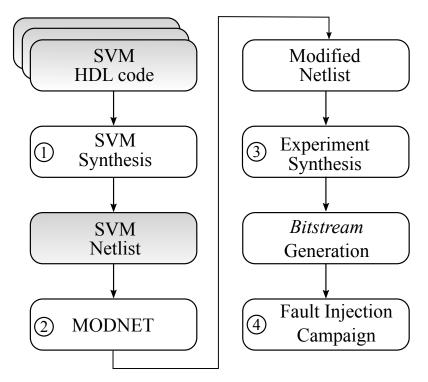

Figure 3.2 illustrates the workflow proposed to apply the fault emulation method on SVM architecture. The method emulates transient faults based on an in-house tool proposed in [36–38]. Initially, the HDL description of the SVM is used to obtain the first synthesis in Step ①. In this step, the synthesis of the SVM is targeted for a specific FPGA (an Artix-7 in our proposed architecture). We consider Synplify FPGA synthesis software as it allows exporting a netlist, which is necessary in further steps.

Figure 3.2: Workflow of the FPGA-based fault emulation method

In Step ②, the netlist is used as input for the *MODify NETlist* (MODNET) tool [38]. The output of MODNET is a modified (but functionally equivalent) Netlist with a large number of extra input signals used to access all memory cells and logic blocks of the design to inject faults in the SVM. The resulting synthesis of the modified netlist includes some additional combinational circuitry to the design.

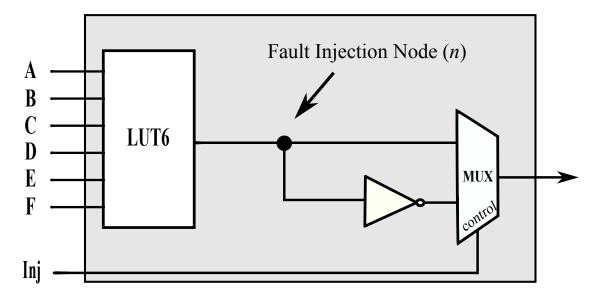

MODNET tool adds a multiplexer at the outputs of the LUTs and logic gates of the netlist to either enable faults at these nodes or disable them by using the signal *INJ*, cf. Figure 3.3.

Figure 3.3: Structure of the fault injection node

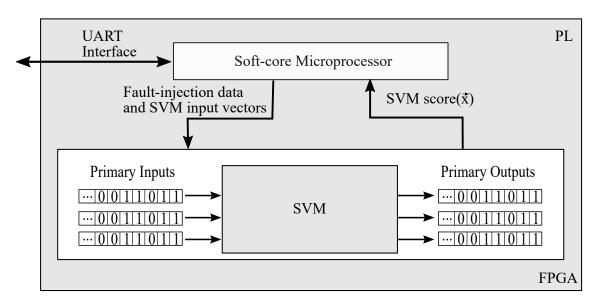

In Step ③, a campaign controller is integrated within the modified Netlist for the target FPGA. The campaign controller is implemented in a soft-core processor that is in charge of managing the transient fault emulation campaign by being directly wired to the SVM architecture modified by MODNET. To this end, the netlist obtained in Step ② is synthesized in the *Electronic Design Interchange Format* (EDIF) and then attached to the processor via a direct interface. The resulting *bitstream* implementing the complete circuit (controller and SVM) is thus generated and implemented in the target FPGA.

Finally, the FPGA-based experiment in Step 4 can be directly executed from the soft-core processor without requiring additional or external hardware support. Indeed, the whole fault emulation campaign (including the post-processing of the results), are conveniently encoded in the processor software. By accessing high-speed interfaces connecting the SVM, the software executes several iterations of fault-injection experiments with different data inputs and fault nodes. The MicroBlaze processor uses an UART to communicate with the outside to report the status of the experiment and its final results.

In summary, Figure 3.4 shows the framework of the method that we have applied to perform the fault emulation campaign, which is integrated into a single FPGA where the SVM and the experiment controller are instantiated and connected by an *Advanced eX*-

the transient fault emulations in the components already intervened by MODNET (*INJ* signals), as well as to configure the input and read the output values of the SVM. In this particular case, the MicroBlaze processor (campaign controller) is a master, whereas the SVM is a slave. The results of the fault emulation campaign are presented in subsection 3.3.4.

Figure 3.4: Framework of the method used to perform the fault emulation campaign.

#### 3.3.4 Results of the Fault Emulation Campaign

The fault emulation campaign has been configured to extensively analyze the behavior of the SVM architecture in the presence of faults. The MODNET tool (step ② in Figure 3.2) has identified in the SVM architecture 1350 nodes to be assessed through a transient fault emulation campaign. For each node, a fault has been injected successively for the set of 150 input vectors. It is important to note that the node holds the fault over the entire clock cycle. For each fault emulation, the primary outputs of the SVM architecture have been compared with the correct result (golden), and each observed failure has been logged in the campaign controller.

It is worth mentioning that 58.8% of the faults have been injected on the outputs of the LUTs connected at the DSP outputs (the Multipliers), while 29.3% of the faults have been injected on the outputs of the LUTs that are in charge of computing the Adders part. The rest of the faults (approximately 11.9%) have been injected on the outputs of the

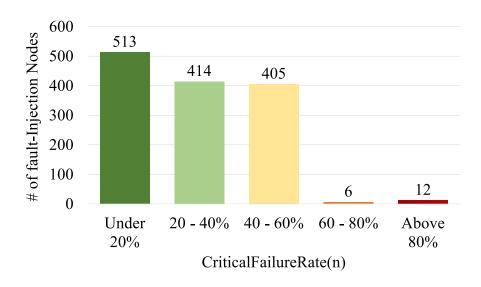

LUTs used by the configuration signals of the SVM architecture. After an extensive fault emulation campaign covering several nodes of the SVM architecture, encompassing a total of 202,500 faults injected in the SVM architecture, results show that more than 29% of emulated single transient faults provoked a critical failure in the SVM architecture. It means that 71% of the fault emulations led to either tolerable failure or no failure. Figure 3.5 presents the histogram of the rates of critical failures (Equation 3.1) provoked by the emulation of single transient faults on the nodes of the SVM architecture design. The results indicate that most nodes are quite sensitive to transient faults (critical failure rates between 20% and 60%), and only a small number of them has a critical failure rate higher than 60%. Such considerable critical failure rates on several nodes suggests that the fault masking effects are low due to the parallel configuration of the operators and the short path between the primary inputs and outputs of the SVM architecture. Selective mitigation techniques could be applied to make more robust such nodes with high critical failure rate.

Figure 3.5: Histogram of the critical failure rate of the injection nodes on the SVM architecture as given by Equation 3.1

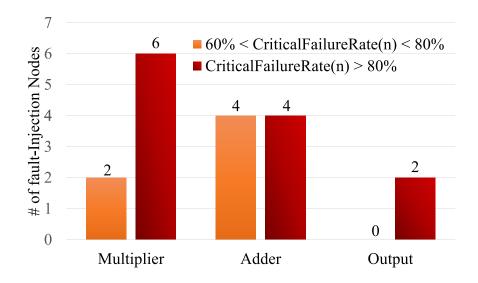

Figure 3.6 shows the correlation among the most critical failure rate nodes and their relative position in the SVM's circuitry. It is worth mentioning that those nodes were extracted from the FPGA LUTs, and their relative positions are logically represented into the Figure 3.1. The results plotted in the Figure 3.6 correspond to the 18 nodes with a *CritiaclFailureRate* > 60%. As indicate in the figure, the most critical faults are distributed in the SVM architecture. In regard to the multipliers, all the eight critical

components are positioned in the first logical level of the multiplier, i.e., they are LUTs that receive the first computation of the DSPs with most significant bits. Analyzing the region of the Adders, we can see that eight other faults/nodes can be classified as critical. Unlike the multiplier results, where critical faults are significantly positioned in the first logical level of the SVM architecture, failures in the Adders are diffused in the circuit. It means that the critical failures can occur in different stages of the combinational Adders' circuitry. When the fault injections are performed in Output, only faults happening close or on the actual sign bit cause critical failures. Even though the most susceptible LUTs are spread out in the architecture, they can be mapped. The very small number of LUTs with a high *CriticalFailureRate*, as shown by Figure 3.6, suggests that hardening could be done on these LUTs to improve the SVM fault tolerance with low area overhead.

Figure 3.6: Histogram representing the correlation among the most critical failure rate (Equation 3.1) nodes and their position relative to the SVM's circuitry implemented in a FPGA.

# 3.4 Radiation Test Experiment and Results

This section describes the radiation experiments conducted with a neutron source and an analysis of the obtained and assessed results.

#### 3.4.1 Radiation Test Set-Up

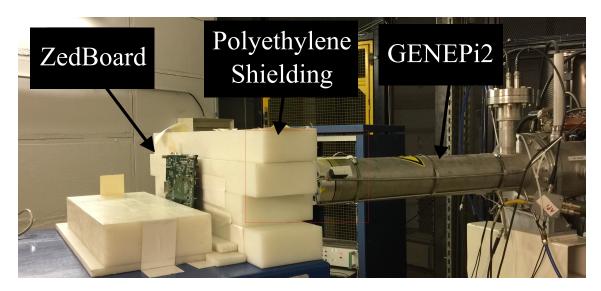

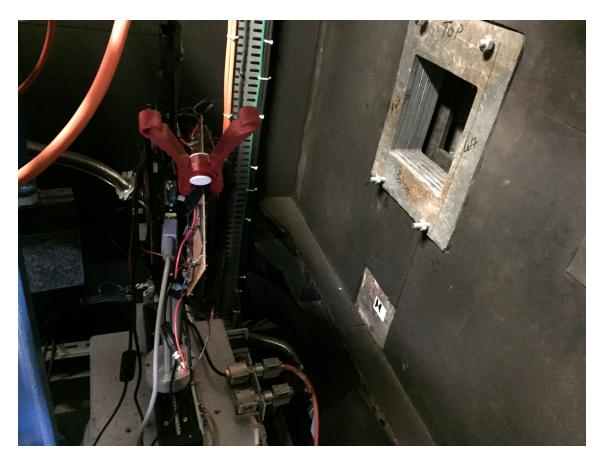

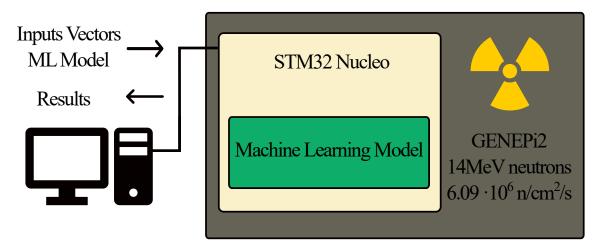

A radiation campaign has been performed at the GENEPi2 neutron source, at the *Laboratory of Subatomic Physics & Cosmology* (LPSC), in Grenoble (France) [9]. Unlike the LANSCE neutron beam, which ranges from 10-MeV to 750-MeV having a flux that is  $10^6$  higher than the natural neutron flux of this spectrum at 40,000 ft. [10], the GENEPi2 is a 14-MeV neutron generator with a maximum flux that exceeds the natural flux of 14-MeV neutrons at 40,000 ft. by a factor of  $10^{10}$ . The board was irradiated for 6 hours and 45 minutes, yielding a total neutron fluence of  $1.944*10^{10}$   $n*cm^{-2}$  and an average flux of  $8*10^5$   $n*cm^{-2}/s$ . Note that we did not use the maximum flux of the accelerator. with an environment temperature of  $18^{\circ}$ C. A polyethylene shielding with a hole was placed in front of the ZedBoard to protect parts other than the Zynq-7000.

The architecture used for the radiation test has a minor difference from the one used in Section 3.3 and is shown in Figure 3.7. While in the fault emulation campaign the FPGA has been driven by MicroBlaze, in this radiation test experiment we adopted the ARM as controller for the SVM. However, the SVM architecture design on the PL remained unchanged. In order to reduce the number of input bits sent from the ARM to the SVM architecture, we instantiated a small controller that had 32-bit wide to store the set of input vectors tested on the FPGA. The controller fetches the data from the memory and forwards it to the SVM. It then retrieves the output and exposes it through an AXI interconnect. Figure 3.8 shows a picture of the test set-up.

The ARM processor provides the controller on the FPGA with the index of the input vector to be tested, as the input vectors are stored in a ROM in the PL, and reads the result. It then forwards the result through the serial port. The L2 cache of the ARM processor has been disabled to reduce the probability of faults affecting the PS [39].

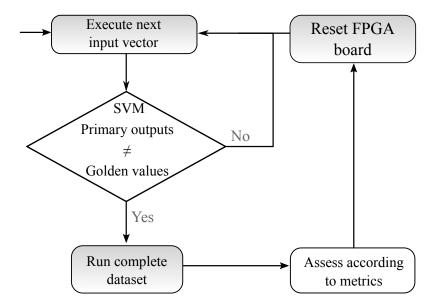

#### 3.4.2 Radiation Test Method

Figure 3.9 presents the method we have used during the radiation test experiment. The set of input vectors is continuously running in the FPGA. The radiation is able to alter the configuration SRAM, which contains the FPGA bitstream, i.e. it is able to create an error. This error may then lead to an alteration of the SVM calculation structure, mathematically changing the classification function. The score of an input vector evaluated in this

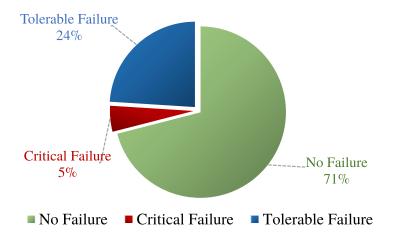

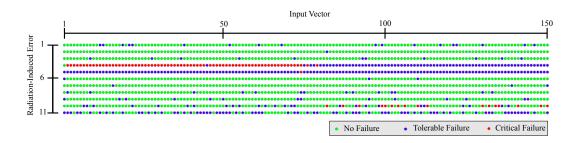

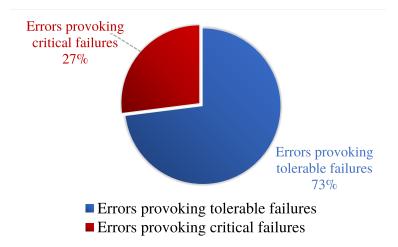

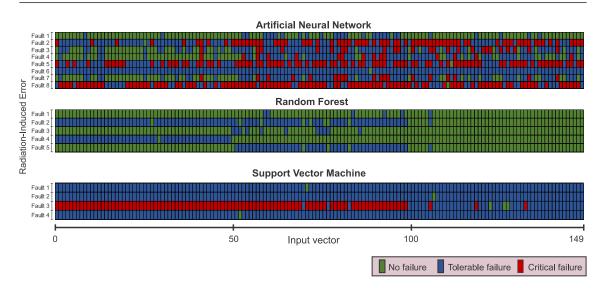

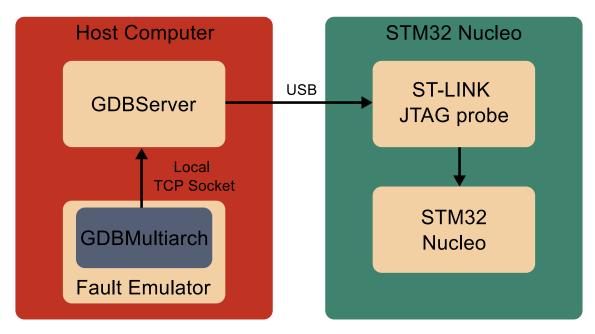

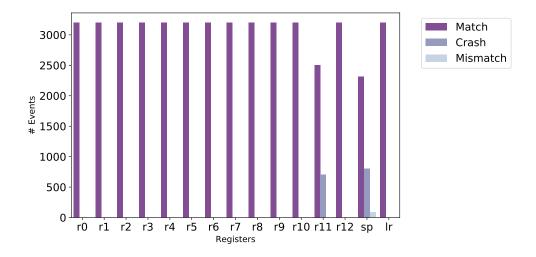

faulty SVM may deviate from its expected result, i.e., we analyze the primary outputs of the SVM architecture, and then we compare them with a golden reference. We use this property to identify when an error has happened. Whenever an error has been identified, we rerun the entire set of input vectors on the faulty SVM to classify each input vector according to the metrics in Subsection 3.3.2, and finally, we log the results. When it is done rerunning the input vectors, the FPGA is reset to erase the error, and the process is restarted. It is worth noting that the errors detected during the radiation test could be either from SEUs or Single Event Multiple Upsets (SEMU), the latter becoming more important in recent technology nodes. A SEMU happens when a single particle affects more than one adjacent memory elements, which is becoming more likely with the shrinking of transistor size [40].