# Toward the Next generation of Non Volatile Phase-Change Memory Targeting Ultra-Low Power Consumption

Anna Lisa Serra

## ► To cite this version:

Anna Lisa Serra. Toward the Next generation of Non Volatile Phase-Change Memory Targeting Ultra-Low Power Consumption. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2021. English. NNT: 2021GRALT030. tel-03527519

# HAL Id: tel-03527519 https://theses.hal.science/tel-03527519v1

Submitted on 16 Jan 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITE GRENOBLE ALPES

Spécialité : **Nano-Electronique et Nano-Technologie** Arrêté ministériel : 25 mai 2016

Présentée par

# Anna Lisa SERRA

Thèse dirigée par Véronique SOUSA, CEA-LETI

préparée au sein du Laboratoire des composants mémoires du CEA-LETI dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Nouvelle génération de mémoire à changement de phase non volatile pour des applications à très basse consommation

Thèse soutenue publiquement le **5 Mars 2021**, devant le jury composé de :

M. Daniele IELMINI Professeur, Politecnico di Milano (Rapporteur) M. Lambert ALFF Professeur, TU Darmstadt (Rapporteur) M. Abdelkader SOUFI Professeur, INSA de Lyon (Président) M. Roberto SIMOLA Ingénieur de recherche, ST Microelectronics (Examinateur) M. Andrzej KUSIAK Professeur Associé, Université de Bordeaux (Examinateur) M. Gabriele NAVARRO Ingénieur de recherche, CEA-LETI (Encadrant de thèse) Mme. Véronique SOUSA Ingénieur de recherche, CEA-LETI (Directrice de thèse)

# Contents

| Co | Contents   |         |                                                                                              |    |  |  |

|----|------------|---------|----------------------------------------------------------------------------------------------|----|--|--|

| Li | st of a    | Symbols | 3                                                                                            | 7  |  |  |

| Gl | Glossary 9 |         |                                                                                              |    |  |  |

| In | trodu      | ction   |                                                                                              | 1  |  |  |

| 1  | Pha        | se-Chan | ge Memory                                                                                    | 7  |  |  |

|    | 1.1        |         | change materials and phase-change mechanism                                                  | 8  |  |  |

|    |            | 1.1.1   | Crystalline structure and phase transition                                                   | 8  |  |  |

|    |            | 1.1.2   | Crystallization mechanism                                                                    | 10 |  |  |

|    |            | 1.1.3   | Conduction mechanism in amorphous and crystalline phase                                      | 11 |  |  |

|    |            | 1.1.4   | Threshold switching                                                                          | 14 |  |  |

|    | 1.2        | Phase-  | change memories                                                                              | 15 |  |  |

|    |            | 1.2.1   | Electro-thermal analysis                                                                     | 17 |  |  |

|    |            |         | 1.2.1.1 Device functionality $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 17 |  |  |

|    |            |         | 1.2.1.2 Electo-thermal properties                                                            | 22 |  |  |

|    | 1.3        | Chapte  | er summary                                                                                   | 25 |  |  |

| 2  | Pha        | se-Chan | ge Memory challenges                                                                         | 27 |  |  |

| _  | 2.1        |         | engineering targeting low power consumption                                                  | 28 |  |  |

|    |            | 2.1.1   | Device structure engineering and scaling                                                     | 29 |  |  |

|    |            | 2.1.2   | Phase-Change material encapsulation                                                          | 32 |  |  |

|    |            |         | 2.1.2.1 Bottom Electrodes engineering                                                        | 33 |  |  |

|    |            |         | 2.1.2.2 Top electrode engineering                                                            | 34 |  |  |

|    |            |         | 2.1.2.3 Dielectric engineering                                                               | 35 |  |  |

|    |            | 2.1.3   | Phase-change material engineering                                                            | 36 |  |  |

|    | 2.2        | PCM f   | or aerospace applications                                                                    | 39 |  |  |

|    | 2.3        | Chapte  | er summary                                                                                   | 41 |  |  |

| 3  | The        | rmal co | nductivity of dielectric and conductive layers                                               | 43 |  |  |

|    | 3.1        |         | nal conductivity measurements by the $3\omega$ method                                        | 44 |  |  |

|    |            | 3.1.1   | The $3\omega$ method $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 44 |  |  |

|    |            | 3.1.2   | Models for thermal conductivity measurements                                                 | 46 |  |  |

|    |            | 3.1.3   | Experimental setup                                                                           | 49 |  |  |

|    |            | 3.1.4   | Device structure optimization                                                                | 50 |  |  |

|   |      | 3.1.4.1 Electrode size optimization                                                                         | 50  |

|---|------|-------------------------------------------------------------------------------------------------------------|-----|

|   |      | 3.1.4.2 Electrode material optimization                                                                     | 51  |

|   |      | 3.1.4.3 Characterization of the temperature coefficient of resis-<br>tance                                  | 53  |

|   |      |                                                                                                             |     |

|   |      | 3.1.5 Identification of the best workflow for $k_{th}$ evaluation                                           |     |

|   |      | 3.1.6 Measurement at room temperature                                                                       |     |

|   |      | 3.1.7 Results at high temperature                                                                           |     |

|   | 2.0  | 3.1.7.1 Dielectric layer engineering                                                                        |     |

|   | 3.2  | Thermal conductivity measurements by MPTR                                                                   |     |

|   |      | 3.2.1 Method description                                                                                    |     |

|   |      | 3.2.2 Measurements on GST and GGST                                                                          |     |

|   |      | 3.2.2.1 Measurements at I2M in Bordeaux                                                                     |     |

|   |      | 3.2.2.2 Measurements at LNE in Paris                                                                        |     |

|   | 3.3  | $3\omega$ method vs MPTR results comparison                                                                 |     |

|   | 3.4  | Chapter summary                                                                                             | 65  |

| 4 | Elec | ctro-thermal simulations                                                                                    | 67  |

|   | 4.1  | Geometry and mesh                                                                                           | 68  |

|   | 4.2  | Stationary electro-thermal model                                                                            | 69  |

|   |      | 4.2.1 Electrical conductivity                                                                               | 70  |

|   |      | 4.2.2 Thermal conductivity                                                                                  | 71  |

|   | 4.3  | Parametric study                                                                                            | 72  |

|   |      | 4.3.1 Discussions and conclusions                                                                           | 80  |

|   | 4.4  | Optimization of the electrical conductivity model                                                           | 81  |

|   | 4.5  | Chapter summary                                                                                             | 84  |

| 5 | PCI  | M current reduction and thermal optimization                                                                | 85  |

|   | 5.1  | Electrical characterization                                                                                 | 86  |

|   |      | 5.1.1 Devices                                                                                               | 86  |

|   |      | 5.1.2 Test set-up $\ldots$ | 87  |

|   |      | 5.1.3 Testing protocols                                                                                     | 89  |

|   | 5.2  | Encapsulation layer effect on PCM performance                                                               |     |

|   |      | 5.2.1 Electric test                                                                                         |     |

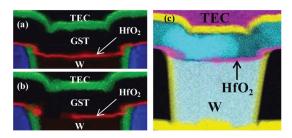

|   |      | 5.2.2 Electro-thermal simulations and TEM/EDX analyses                                                      |     |

|   |      | 5.2.3 Electro-thermal theoretical analysis and discussions                                                  |     |

|   |      | 5.2.4 Discussions and conclusions                                                                           |     |

|   | 5.3  | GeN interfacial layer                                                                                       | 102 |

|   | 0.0  | 5.3.1 Electric test                                                                                         |     |

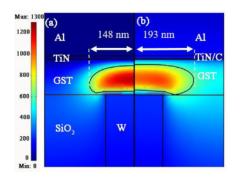

|   |      | 5.3.2 Electro-thermal simulations                                                                           |     |

|   |      | 5.3.3 Discussions and conclusions                                                                           |     |

|   | 5.4  | PCM for aerospace applications: tolerance to radiation                                                      |     |

|   | 0.4  | 5.4.1 Radiation effect on GST alloys structure                                                              |     |

|   |      | 5.4.2 Radiation effect on 4kb PCM                                                                           |     |

|   |      | 5.4.3 Irradiations conclusions                                                                              |     |

|   | 5.5  |                                                                                                             |     |

|   |      | TiTe/GST based PCM                                                                                          |     |

|   | 5.6  | Chapter summary                                                                                             | 116 |

\_\_\_\_\_

| Conclusions and perspectives                 | 119 |

|----------------------------------------------|-----|

| List of publications associated to this work | 125 |

| References                                   | 127 |

| Abstract                                     | 143 |

# List of Symbols

| Symbol             | Measure Unit                      | Designation                                                            |

|--------------------|-----------------------------------|------------------------------------------------------------------------|

| $ec{E}$            | $[V  m^{-1}]$                     | Electric field vector                                                  |

| E                  | $[V m^{-1}]$                      | Electric field intensity                                               |

| $h_a$              | [m]                               | Amorphous thickness                                                    |

| $I_m^u$            | $\begin{bmatrix} A \end{bmatrix}$ | Melting current                                                        |

| $I_0$              | [A]                               | AC current amplitude                                                   |

| $I_{cell}$         | [A]                               | Current in the cell                                                    |

| $I_R$              | [A]                               | RESET current                                                          |

| $I_R$<br>$\vec{J}$ | $[A m^{-2}]$                      | Current density vector                                                 |

|                    | $[A m^{-2}]$                      | Current density intensity                                              |

|                    | $[A m^{-2}]$                      | RESET current density                                                  |

| $k_{th}$           | $[W m^{-1} K^{-1}]$               | Thermal conductivity                                                   |

| $k_{th,eff}$       | $[W m^{-1} K^{-1}]$               | Effective thermal conductivity                                         |

| P                  | [W]                               | Electrical power                                                       |

| $P_l$              | [Wm]                              | Power per length unit                                                  |

| q                  | $[W m^{-2}]$                      | Thermal flux                                                           |

| Q                  | $[W  m^{-3}]$                     | Power density                                                          |

| $R_0$              | $[\Omega]$                        | Line resistance                                                        |

| R                  | $[\Omega]$                        | Resistance value                                                       |

| $R_i$              | $[\Omega]$                        | Interfacial resistance                                                 |

| $R_{Load}$         | $[\Omega]$                        | Load resistance                                                        |

| $R_{ON}$           | $[\Omega]$                        | Resistance of the cell in the ON-state                                 |

| $R_{RESET}$        | $[\Omega]$                        | RESET resistance of the device                                         |

| $R_{SET}$          | $[\Omega]$                        | SET resistance of the device                                           |

| $R_{th}$           | $[KW^{-1}]$                       | Thermal resistance                                                     |

| $t_{ox}$           | [m]                               | Dielectric layer thickness                                             |

| $T_g$              | [s]                               | Glass temperature                                                      |

| $T_m$              | [K]                               | Melting temperature                                                    |

| $T_C$              | [K]                               | Crystallization temperature                                            |

| $v_g$              | $[m  s^{-1}]$                     | Growth speed                                                           |

| $V_0$              | [V]                               | AC voltage amplitude                                                   |

| $V_{\omega}$       | [V]                               | Amplitude of the voltage first harmonic                                |

| $V_{3\omega}$      | $\begin{bmatrix} V \end{bmatrix}$ | Amplitude of the voltage third harmonic                                |

| $V_{cell}$         | $\begin{bmatrix} V \end{bmatrix}$ | Voltage drop on the cell                                               |

| $V_H$              | $\begin{bmatrix} V \end{bmatrix}$ | Holding voltage                                                        |

| $V_I$              | $\begin{bmatrix} V \end{bmatrix}$ | Initialization voltage                                                 |

| $V_{pulse}$        | $\begin{bmatrix} V \end{bmatrix}$ | Voltage applied                                                        |

| $V_{TH}$           | [V]                               | Threshold voltage<br>Coordinate at which $T = 930$ K is reached in the |

| $z_{melt}$         | [m]                               | coordinate at which $I = 950$ K is reached in the phase-change layer   |

| $z_{heater}$       | [m]                               | Coordinate at which $T = 930$ K is reached in the heater               |

| $\alpha$      | $[K^{-1}]$   | Temperature coefficient of resistance   |

|---------------|--------------|-----------------------------------------|

| $\Delta T_0$  | [K]          | Amplitude of temperature oscillations   |

| ρ             | $[\Omega m]$ | Resistivity                             |

| $\sigma$      | $[S m^{-1}]$ | Electrical conductivity                 |

| $\sigma_r$    | $[S m^{-1}]$ | Electrical conductivity during READ     |

| $\sigma_{ON}$ | $[S m^{-1}]$ | Electrical conductivity of the ON-state |

| ω             | $[s^{-1}]$   | Angular frequency                       |

# Glossary

| Acronym       | Designation                                  |

|---------------|----------------------------------------------|

| BEOL          | Back End Of Line                             |

| BL            | Bit Line                                     |

| CVD           | Chemical Vapor Deposition                    |

| CMOS          | Complementary Metal Oxide Semiconductor      |

| FEM           | Finite Element Method                        |

| FDSOI         | Fully Depleted Silicon on Insulator          |

| EDX           | Energy-Dispersive X-ray Spectroscopy         |

| GST           | $Ge_2Sb_2Te_5$                               |

| GGST          | Ge-rich $Ge_2Sb_2Te_5$                       |

| НСР           | High Current Population                      |

| HXPES         | Hard X-ray PhotoEmission Spectroscopy        |

| IV            | Current vs Voltage curve                     |

| IGS-PCM       | Inter Granular Switching Phase-Change Memory |

| IL-PCM        | Interfacial Layer Phase-Change Memory        |

| LCP           | Low Current Population                       |

| MPTR          | Modulated PhotoThermal Radiometry            |

| NMOS          | Negative Metal Oxide Semiconductor           |

| PCM           | Phase-Change Memory                          |

| PCL           | Phase-Change Layer                           |

| PECVD         | Plasma Enhanced Chemical Vapour Deposition   |

| QLC           | Quad-Level Cell                              |

| RI            | Resistance vs Current curve                  |

| RT            | Room Temperature                             |

| SNC PCM       | Self-Nano Confined Phase-Change Memory       |

| SEE           | Single Event Effect                          |

| SET-opt       | Optimized SET pulse                          |

| SET-FT        | SET pulse with Fall Time                     |

| SLL           | SuperLattice-Like                            |

| TBR           | Thermal Boundary Resistance                  |

| TCR           | Thermal Coefficient of Resistance            |

| TDTR          | Time Domain Thermo Reflectance               |

| TID           | Total Ionization Dose                        |

| TEM           | Transmission Electron Microscopy             |

| VBM           | Valence Band Minimum                         |

| $\mathbf{WL}$ | Word Line                                    |

| XRD           | X-Ray Diffraction                            |

| XRR           | X-Ray Reflectometry                          |

# Introduction

## Context

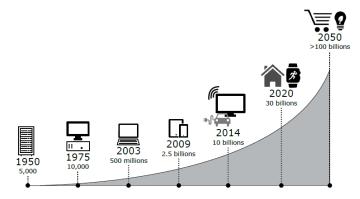

During the last decades, the number of objects connected has drastically increased and more than hundreds of billions of devices are expected to be connected in 2050 (Fig. 1). In this scenario, storing a large amount of information in a small space represents a primary necessity, leading to a growing interest in the development of memory systems suitable for the new generation of electronic devices featuring high scaling.

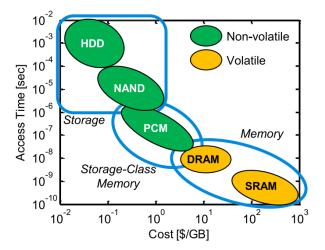

Nowadays, all the electronic accessories have a memory system based on a von-Neumann architecture, with the computing and the storage units physically separated and organized according to a specific hierarchy. The top of the hierarchy is occupied by the working memory, which is used to perform the logic operations. This memory is represented by the Static or Dynamic Random Access Memory units (SRAM and DRAM, respectively) which are fast, expensive and volatile. While, the bottom of the hierarchy, is occupied by NAND Flash and NAND Solid State Drives as well as by Hard Disk Drives (HDD), which are slow, cheap and non-volatile, hence able to store the information even when the power is off, unlike the volatile ones. Therefore, storage memories are used to store the data not directly used, allowing an easier access to them when needed. The gap between the top and the bottom of the hierarchy consists in a three order of magnitude difference in terms of access time and one order of magnitude in cost (Fig. 2). Nevertheless, despite the difference in tasks and requirements fulfilled, they both rely their functionality on charge storage, making them not suitable to satisfy the scaling requirements demanded by the market. Indeed, different studies report an impact on data sensing and data retention when reducing the size of charge-based devices [1, 2]. Moreover, Flash memories present low radiation tolerance, ruling out the possibility to use them for aerospace applications.

The scaling limit in charge based technology can be solved either with sophisticated design solutions (as in the 3D NAND supported by Samsung, Micron and Toshiba) or with the use of microcontrollers and error correction codes. Nevertheless, these improvements could not provide a memory featuring high scalability along with low power consumption at reduced cost and ensuring radiation hardness. With this aim, innovative memory technologies were developed, namely the resistive non-volatile memories (NVM). These are two-terminal devices were the information storage relies on the change of the resistive state in an active material, sandwiched between two electrodes. The NVMs are able to combine the accessibility of DRAM with the non-volatility of Flash, filling the gap between working and storage memories (Fig. 2), and making them the ideal candidate for Storage Class Memory (SCM) applications.

The resistive non-volatile memories are classified according to their working principles.

Fig. 1. Timeline of the number of connected objects. More than 100 billions objects are estimated to be connected in 2050 [3].

The most promising solutions include:

- Resistive Memories (RRAM) which are based on a reversible dielectric breakdown mechanism;

- Magnetic Memories (MRAM) which store the information in magnetic domains;

- Phase-Change Memories (PCM) where a chalcogenide material is used to store the bit by a reversible switching from the amorphous to the crystalline state.

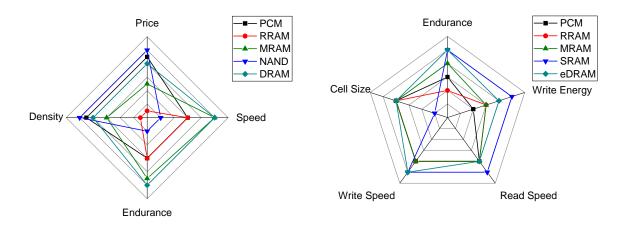

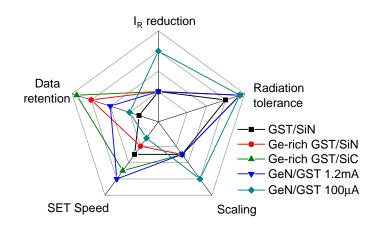

These memory technologies can be implemented in both embedded and stand-alone applications. The comparison of the new generation NVMs performance with respect to the charge based stand-alone and embedded counterpart is reported in Fig. 3 and Fig. 4, where the best performance for each feature is represented by the higher value on the respective axis on the chart. Some of the parameters used in the comparison are:

- *write/read speed*, which refers to the time needed to save/have access to the information;

Fig. 2. Access time as a function of the cost for both volatile and non-volatile memories. Emerging NVMs, like PCM, can fill the performance gap [4].

- write energy, which accounts for the energy needed to save an information;

- *endurance*, which refers to the number of program/erase operations before facing the device degradation.

In terms of stand-alone applications, PCM ensures lower costs and higher density compared to RRAM and MRAM competitors. More precisely, PCM became the leading technology after the commercialization of the 3DXPoint by Intel in 2017. This stateof-the-art PCM technology is characterized, in fact, by a latency one thousand times higher than NAND flash and by a density ten times higher than DRAM. Moreover, its non-volatility guarantees a reduction in the amount of DRAM needed to maintain a high bandwidth (i.e., rate at which the processor read/store the data in the memory), hence reducing the cost and the power used by the whole system [5]. This has been witnessed in 2019 when the Intel Optane memory H10 with SSD came into commercialization. It co-integrates a 3DXPoint with a Quad-Level Cell (QLC) 3DNAND (i.e.,4 bit per cell) ensuring high performance at low latency and cost. Further improvements on the Optane memory are ongoing in order to achieve a higher density and storage performance. In particular, IBM is developing a three-bit per cell PCM chip; while a second generation of Optane (expected for the end of 2020) will be based on a four layer stack used to replace the two layered version already on the market.

In terms of embedded applications, the emerging NVM have still limited market. As described in Fig. 4, among the new generation of NVM, MRAM owns the best features with high endurance and low writing energy. However, the cost and the reliability at high temperature are also two crucial factors to take into account for industrialization, positioning PCM as the main MRAM competitor. Indeed, the better thermal stability achieved in PCM by the chalcogenide material engineering [6] brought to the development of a PCM device based on a 28 nm FDSOI by STMicroelectronics, which is supposed to get in the market at the beginning of next year. Therefore, PCM represents the undeniable breakthrough in the present storage scenario featuring properties of both DRAM and Flash, presenting an advanced state in terms of development and industrialization in SCM [7] as well as in embedded PCM-based microcontrollers for

**Fig. 3.** Performance comparison of different NVM technologies with respect to NAND and DRAM for stand-alone applications.

**Fig. 4.** Performance comparison of different NVM technologies with respect to SRAM and eDRAM for embedded applications.

automotive applications [8]. Furthermore, since the discovery of phase-change materials and PCM, a high radiation tolerance was foreseen [9] expanding the fields of application for this technology.

## **Objectives of this work**

Since all the electronic based systems need a power supply to assure their functionality, the development of low power devices is the main target of the modern technology. This represents a big challenge for PCM since this technology is characterized by the higher writing energy among the emerging NVM (see Fig. 4). Indeed, the lowest programming current demonstrated in PCM is of 30  $\mu$ A on 256 Mb [10], to be compared with less than 10  $\mu$ A achieved at array level in both RRAM [11] and MRAM [12].

In this scenario, the objective of this thesis is to contribute to the development of the next generation Non-Volatile PCM targeting ultra-low power consumption. Since PCMs rely on Joule Heating, the thermal optimization of the device represents a key point for investigation. In this work, the thermal optimization of the cell is carried out by the interplay of three different aspects:

- The thermal conductivity characterization of both dielectric and conductive materials that i) are currently integrated, ii) present interesting properties and are potential candidates for integration in next generation PCM devices;

- 3D electro-thermal simulations of PCM devices, allowing to describe the temperature profile in the memory cell and to further investigate the main parameters to be tuned in order to improve the thermal performances of the cell;

- The electrical characterization of PCM devices (e.g., programming current, speed, endurance) to define the performance of different state-of-the-art PCM configurations and their ability to reach low-power operations.

In Chapter 1, the basic working principle of Phase-Change Memories will be introduced. Then an overview of the approaches proposed to reduce the programming current in PCM will be described in Chapter 2.

Chapter 3 will focus on the measurement of material thermal conductivity. At first, theoretical models will be presented. Then, the setup of a  $3\omega$  method and its optimization will be described. Furthermore, the validation of the measurements on a set of materials will be reported, comparing the resulting thermal conductivity values to those obtained by another method (Modulated Photothermal Radiometry) at the Institut de Mecanique et d' Ingenierie (I2M) de Bordeaux and at the Laboratoire National de Metrologie et d'essais (LNE) in Paris.

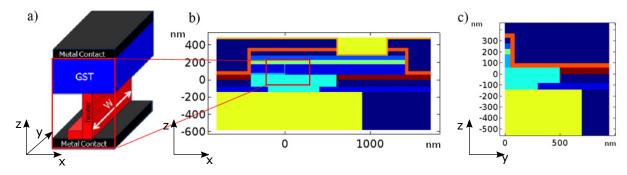

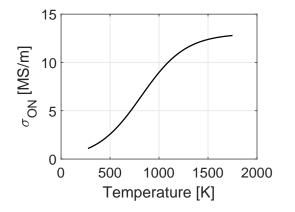

The measured thermal conductivity values were exploited in a numerical model, based on finite-element simulations. A parametric study on the Wall-based PCM will be presented in Chapter 4. In particular, the electro-thermal response of the PCM device subjected to an external voltage pulse will be described, and the influence of the material and geometrical properties will be investigated to identify the optimal conditions for low-power PCM applications.

Chapter 5 reports the results obtained via the electric tests performed on different

low power solutions. The results will involve a discussion on the PCM performances by coupling the electric test with the device electro-thermal simulations and physicochemical analysis performed on the programmed devices. We will mainly focus on i) the importance to tune the encapsulation layer thermal conductivity in Wall based PCM; ii) the 50  $\mu$ A and size-independent RESET current achieved thanks to an interfacial GeN layer on 4kb matrice and its potentiality to be further scaled; iii) the possibility of alternative current reduction solutions for PCM low power performance and iv) the impact of material and architecture engineering on PCM radiation hardness. Finally, potential future directions of investigation will be provided.

# Chapter 1 Phase-Change Memory

The Phase Change Memory functionality relies on the reversible switching from a high resistive state to a low resistive state of the phase-change material deposited between the two electrodes. Therefore, PCM performance depends on the phase-change material properties.

In this chapter, the main features of phase-change materials are introduced, dealing with an analysis on the crystalline structure and of the nature of the crystallization mechanism taking place during the amorphous-to-crystalline transition. The difference in the conduction mechanism between the two phases is also addressed.

We than move our focus on the Phase-Change Memory device and first introduce the strategy to write/erase an information in a device. The electro-thermal model driving the device functionality is then introduced to trigger possible path for PCM optimization.

# 1.1 Phase-change materials and phase-change mechanism

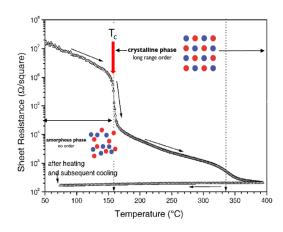

During the 1960s, Ovshinsky first presented the existence of a switching mechanism when a phase-change material is subjected to an external voltage [15]. This mechanism causes the transition from a high resistive state (amorphous phase) to a low resistive state (crystalline phase), introducing the concept of information storage in the two phases of the material. The transition between the amorphous and the crystalline phase is evidenced by a characteristic resistance vs temperature curve (Fig. 1.1): as soon as the crystallization temperature ( $T_c$ ) is reached, the material electrical resistivity suddenly drops. In this section, we will present at first the phase-change materials chemical composition. After that, we will focus on their crystalline structures and on the principle underling the atomic rearrangement, which enables the crystalline-toamorphous and amorphous-to-crystalline phase transitions.

#### **1.1.1** Crystalline structure and phase transition

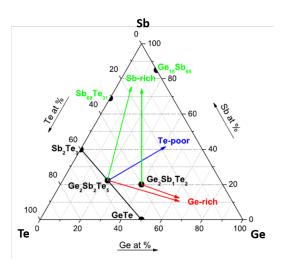

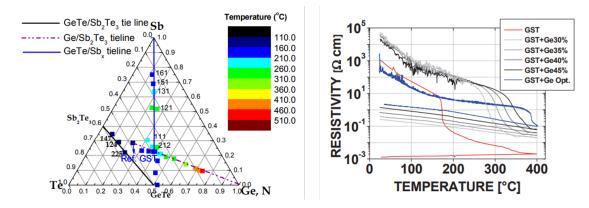

Phase-change materials belong to the family of chalcogenides, which are compounds of chalcogens (e.g. sulphur, selenium or tellurium) with electropositive elements or organic radicals. The most used phase change materials are ternary chalcogenides based on a Ge-Sb-Te alloy. The ternary diagram of a Ge-Sb-Te system is shown in Fig. 1.2 where each of the three apexes represents one of the elements composing the alloy. Each point of the diagram is referred to a specific Ge-Sb-Te composition, defined by the correspondent atomic percentage value reported along the three axis. Modifying the material composition, it is possible to tune its properties and, consequently, the performance of the device in which it will be integrated. From the application point

Fig. 1.1. Characteristic resistance vs temperature curve for a phase-change material. When the crystallization temperature  $(T_c)$  is overcome, the material reorganizes in a crystalline phase, resulting in a drop of the electrical resistance [13].

Fig. 1.2. Ternary Ge-Sb-Te phase diagram [14].

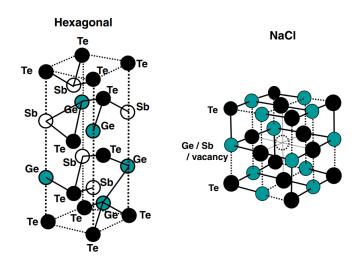

Fig. 1.3. Representation of the hexagonal crystal structure and the metastable NaCl structure [17].

of view, compounds characterized by high crystallization temperature and speed are desired [16]. Materials belonging to the GeTe-Sb<sub>2</sub>Te<sub>3</sub> pseudobinary system (indicated by the black line in Fig. 1.2) present this features. In particular, the most used chalcogenides for non-volatile memories applications are GeTe and Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST).

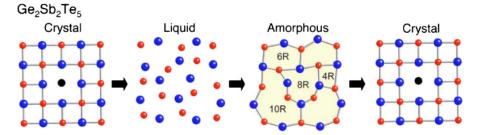

The crystalline structure of phase-change materials can be either hexagonal (hcp) or face-centered cubic (fcc). As an example, the schematic representation of these two structures is reported in Fig. 1.3 for GST. The GST hexagonal structure is made up of three unit cells, characterized by a rhombic top and bottom plane with vertex angles of  $60^{\circ}$  and  $120^{\circ}$ . The major covalent bonds in the unit cell are arranged in even-numbered rings and are represented in the schematic as black lines connecting the atoms. The non uniform arrangement of the atoms requires a long heating time to allow the material to rearrange its atoms in the hexagonal configuration. On the contrary, by heating up the material in a small time range (i.e., nanoseconds to microseconds), the most probable crystalline arrangement is the metastable NaCl-like structure [17] (Fig. 1.3). When  $Ge_2Sb_2Te_5$  is in this metastable NaCl-like structure, the Te atoms take the place of Cl sites while Ge and Sb randomly occupy the Na sites with 20% of vacancies. In the unit cell of the metastable NaCl-like structure, the vacancy site is highlighted by the dashed circle situated at the center of the cubic cell. Therefore, when the GST undergoes the phase transition, it organizes at first into a face centered cubic (fcc) structure, then into the hexagonal one. A description of the atomic rearrangement taking place during the phase transformation is reported in Fig. 1.4. The transition from the crystalline to the amorphous phase occurs only if the material is melted via Joule heating and then rapidly quenched back to room temperature. On the contrary, to recover the crystalline state, the material faces the threshold switching phenomenon. At this point, the Joule heating generated in the material allows the crystallization if the temperature achieved in the system favors the atomic reorganization.

The optimal condition to get the amorphous to crystalline phase-change depends on the material composition, hence on the type of crystallization mechanism driving the resistive transition, as will be described in more details in the next section.

Fig. 1.4. Description of the phase-change transition. At first, crystallne material has to undergo a melting process. Setting a sufficiently high cooling rate, the amorphous phase is then obtained. On the contrary, the crystalline state can be achieved exclusively with a specific temperature profile which favor the atomic reorganization [17].

#### 1.1.2 Crystallization mechanism

The crystallization mechanism in chalcogenide materials follows the classical nucleation theory developed by Gibbs [18] and is based on the thermodynamic description of a system made up of a crystalline cluster evolving in an amorphous matrix. At the beginning of the crystallization mechanism the created clusters are small and unstable (i.e., crystal nucleation) until some of them are able to increase their radius above a critical dimension at which they become stable nuclei and can grow to macroscopic crystals (i.e., crystal growth). The time needed to reach the critical size is called transient or incubation period. Therefore, a long transient period inhibits the material crystallization.

Dependending on the mechanism dominating the phase transition, chalcogenides are classified in nucleation dominated or growth dominated materials. In nucleationdominated materials, the crystalline state is achieved when the nucleation rate (number of critical nuclei formed per unit time in a unit volume of the material) is high enough to fill the entire volume, leading to an increase of the material conductivity. The nucleation is defined as homogeneous when the probability of nucleus formation is constant in the entire volume under investigation; while it is defined as heterogeneous when the presence of interfaces, boundaries or defects can favor the nucleation in these regions. Therefore, melt-quenching or thermal pre-treatment could modify the crystallization speed [5, 19].

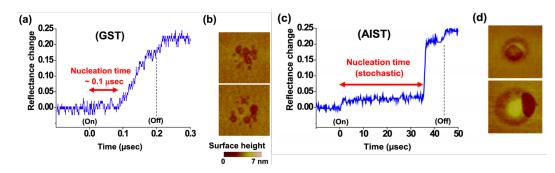

In growth-dominated materials, both nucleation and growth occur but the nucleation rate is small enough to do not significantly contribute to the crystallization mechanism. Growth is associated to the possibility of the atoms to reorganize at the interface between the amorphous and the crystalline region. The amorphous to crystalline transition takes place only if each atom is able to overcome a certain energy barrier, resulting in a reduction of the overall energy of the system. The growth speed  $(v_g)$  can be determined by considering a combination of the probability of the atom to remain in its amorphous state and the probability for it to undergo the phase transformation. The two crystallization mechanisms has been studied in phase-change materials. Particularly, Lee et al. [19] exploit the difference in reflectance between the crystalline and amorphous phase to monitor the crystallization process by pump-probe laser measurements and Atomic Force Microscopy (AFM). In this study, two materials were investigated and compared: GST and AgInSbTe (AIST). As shown in Fig. 1.5 a, the

Fig. 1.5. a) Reflectance change of GST obtained with a laser spot diameter of around  $1 \mu m$ . A reflectance change is observed after 0.1  $\mu s$ , b) Atomic Force Microscopy (AFM) analysis of the GST sample after laser exposure, shows the multiple supercritical nuclei growing individually. c) Reflectance change of AIST obtained with a laser beam diameter of 2  $\mu m$ . In AIST, the nucleation time is stochastic and longer than GST (tens of  $\mu s$ ). d) AFM measurements on AIST highlights the growth phenomenon from a single supercritical nucleus [19].

GST reflectance remains constant during a nucleation time of 0.1  $\mu$ s. After that, it increases monotonically, indicating the formation of multiple super-critical nuclei which grow up separately as can be observed in Fig. 1.5 b. The area is not completely filled with nuclei since the crystallization has been interrupted by turning off the pump-laser before the full crystallization of the layer. For AIST, instead, the nucleation time is ten times higher than in GST. During this time, the material try to generate some nucleus in a stochastic way before facing a rapid crystallization, as witnessed by the abrupt change in reflectance reported in Fig. 1.5 c. The AFM analysis on the sample is reported in Fig. 1.5 d where the growth from a single supercrytical nucleus is evidenced.

#### **1.1.3** Conduction mechanism in amorphous and crystalline phase

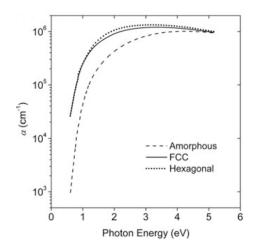

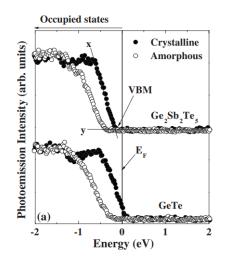

In 1976 the discovery of localized states in the energy gap of amorphous chalcogenide materials [22] paved the way for the study of the conduction mechanism in both the amorphous and crystalline state by the quantum semiconductor theory. Furthermore, the investigation of both the optical and electrical properties of phase-change materials gave the possibility to predict the band structure of the two phases. The absorption coefficient of GST as a function of the photon excitation energy is reported in Fig. 1.6. The steep reduction of the absorption coefficient at lower energy is an evidence of the band edge. In particular, the optical gap evaluated for the amorphous phase has been associated to the presence of Urbach tails, decaying exponentially due to the presence of localized states generated by the disorder in the amorphous matrix, as stated by the Anderson theory [20]. The position of the Fermi level has been, instead, investigated by Hard x-ray photoemission spectroscopy (HXPES) which allows to detect the density of state in the valence band with respect to the Fermi level. The HXPES spectra of the amorphous and crystalline phase as a function of the energy are reported in Fig. 1.7 for both GST and GeTe. The energy zero along the x-axis coincides with the Fermi level. The valence band minimum (VBM) is closer to the Fermi level in the crystalline phase with respect to the amorphous for both the materials. This is in accordance with the higher electrical conductivity typical of the crystalline state. The deep valence band in

crystalline GST indicates the possibility to have an almost metallic conduction (i.e., degenerate semiconductor). On the other end, the amorphous phase presents a bandgap of 0.8 eV (i.e., a VBM at 0.4 eV), as an evidence of its intrinsic semiconductor nature characterized by a Fermi level pinned at midgap. Further studies evaluated the hole concentration in crystalline GST by the measure of the Hall coefficient [20] [23], demonstarting an acceptor-like band in accordance with the 20% of vacancies typical of the fcc GST.

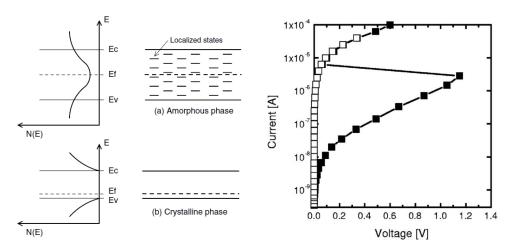

The density of state and band schematic argued from the previous studies is reported in Fig. 1.8 along with the current vs voltage curve associated to both phases of the material. The crystalline phase is represented as a degenerate semiconductor since the Fermi energy lies between a defect band and the maximum of the valence band with low density of free carriers even at low temperature  $(10^{19}-10^{20} \text{ cm}^{-3} \text{ at } \text{T} = 5 \text{ K} [20])$ highlighting the tiny energy difference between valence and defects band. Hence, as soon as the temperature is increased, the amount of carriers involved in conduction increases drastically giving rise to a metallic conduction mechanism. This behavior is reported in the IV curve, where a typical Ohmic (V = RI) trend is evidenced for a crystalline material. In the amorphous phase, instead, the material can be considered as an intrinsic semiconductor with the Fermi level in the middle of the gap. This is mainly due to the presence of band tails in the valence band caused by lone-pairs or other defects, such as dangling or distorted bonds (e.g. Ge-Ge bonds in GST), which generate localized states in the material. Therefore, the conduction mechanism of an amorphous material is completely different from the crystalline one. This is evidenced in the experimental IV curve where the amorphous characteristic is firstly non-linear.

Fig. 1.6. Measured absorption coefficient  $\alpha$  as a function of photon energy for amorphous and crystalline GST [20]. The presence of a band edge is evidenced by the steep reduction of the absorption coefficient at low energy.

Fig. 1.7. HXPES spectra for GST (top) and GeTe (bottom) in the amorphous and crystalline phases [21], highlighting that the Valence Band Minimum (VBM) is closer to the Fermi level (Energy = 0 eV) for crystalline phase with respect to the amorphous

Fig. 1.8. (left) Density of state and band schematic for a chalcogenide material in a) amorphous phase and b) crystalline phase [23]. (right) Current vs voltage characteristic associated to both the crystalline (empty squares) and the amorphous (filled squares). The IV obtained for a RESET state presents a snap back, hence a threshold voltage at 1.2 V [26].

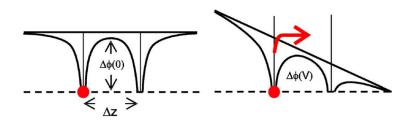

Fig. 1.9. Representation of the trap-limited conduction mechanism. The traps states modeled as potential wells with height  $\Delta \phi(V)$  and distance  $\Delta z$  are reported (left) at zero applied voltage (V = 0) and (right) under an external voltage. The latter induces a barrier lowering and a consequent increase of the hopping probability to a neighbor cell when a small thermal excitation is induced in the system [23].

Indeed, the current increases following an exponential law until the onset of the threshold switching phenomenon, where the curve evidences a snap-back. After that, the two curves get superimposed (i.e., ON-state) as an effect of the phase transition. The conduction mechanism associated to the non-ohmic region before the threshold switching (i.e., OFF-state) can be ascribed to different phenomena [24]. Nevertheless, the one that is most commonly attributed to a high trap density material is the Poole-Frenkel mechanism. This is based on the electronic hopping generated by the thermal excitation between two trap states, usually modeled as a potential well with a height  $\Delta \phi$  and distance  $\Delta z$  (Fig. 1.9). When an external voltage is applied to the system, the hopping probability increases exponentially giving rise to a current [25]:

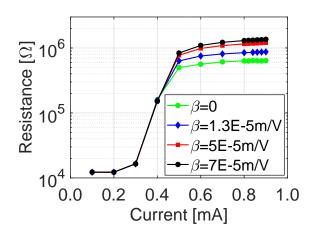

$$I = I_0 e^{\beta V} \tag{1.1}$$

where  $\beta$  and  $I_0$  are constants depending on the trap distance and barrier height. When a potential is applied to a system with high density of traps (small  $\Delta z$ ), the barrier height reduces to  $\Delta \phi(V)$  in accordance with the following relation:

$$\Delta\phi(V) = \Delta\phi(0) - qF\frac{\Delta z}{2} = -qV\frac{\Delta z}{2u_a}$$

(1.2)

with  $\Delta \phi(0)$  being the energy barrier when no external voltage is applied to the system (Fig. 1.9), q the elementary charge, F the electric field and  $u_a$  the amorphous chalcogenide thickness.

#### 1.1.4 Threshold switching

The IV curve of an amorphous chalcogenide (Fig. 1.8), described in the previous section, shows an instantaneous change in the material conductivity at a specific voltage ( $V_{th}$ ). It represents the onset of the threshold switching phenomenon, which leads to have two different currents values associated to the same applied voltage. These two values are referred to the OFF and ON-state of the material.

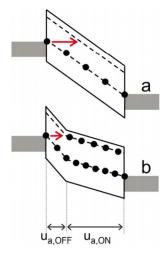

The threshold voltage  $V_{th}$ , represents the transition between these two states. The origin of the threshold switching mechanism was longly debated in the years. Recently, Ielimini et al. [26] described the threshold switching as based on the non-equilibrium distribution generated by a relatively high electric field applied to the system. In particular, in this conditions, the electrons can access traps states at higher energies due to tunneling or thermal emission or energy gained by the external field. In general, the relaxation process counterbalances the gain in kinetic energy keeping the system in the equilibrium state. Nevertheless, in a system with trapped electrons, the relaxation process can involve phonon emission and impurity ionization (i.e., a high-energy carrier can transfer part of its energy to a carrier trapped at a deep level). Hence, the kinetic energy is shared among more exited electrons, leading to a non-equilibrium distribution of carriers. This scenario is reported in Fig. 1.10, where  $u_{a,OFF}$  is the region where the Fermi level represents the highest occupied trap state at equilibrium. This is

Fig. 1.10. Potential profile and electrons energy distribution in an amorphous chalcogenide material a) below and b) above threshold switching. At low current, the system is in equilibrium (OFF), while at high current a non-equilibrium condition takes place in a part of the layer characterized by an increase in the conductivity  $(u_{a,ON})$  [26].

Fig. 1.11. Current vs voltage characteristic measured for devices characterized by an amorphous volume of different thickness  $(u_a)$ . The thickness and resistance increase induces a decrease of the subthreshold slope (STS), leading to an increase of the threshold voltage [27].

considered as an OFF layer since the population is still controlled by the equilibrium statistic (i.e., no conduction switching is possible). Along the thickness  $u_{a,ON}$ , instead, the non-equilibrium distribution results in a high conductive regime. Therefore, the two regions are characterized by different electric fields even if the same current is flowing into them. This gives rise to the voltage drop in Fig. 1.8. In particular, the applied voltage is splitted in the two regions as:

$$\phi = F_{OFF} u_{a,OFF} + F_{a,ON} u_{a,ON} \tag{1.3}$$

with  $F_{OFF}$  and  $F_{ON}$  respectively the electric field in the OFF and ON layers. Furthermore,  $u_{a,OFF}$  is independent from the amorphous layer thickness since it obeys the following relation:

$$u_{a,OFF} = \frac{E_{T2} - E_{T1}}{qF_{OFF}}$$

(1.4)

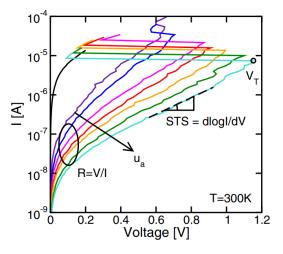

where  $E_{T2}$  is the energy of the deep trap aligned with the Fermi level and  $E_{T2}$  is a shallow trap close to the conduction band edge. Therefore, an increase in the overall amorphous thickness will not impact  $u_{a,OFF}$ . It will cause, instead, the increase in  $u_{a,ON}$ and the decrease in the voltage across it. As a consequence, the gap between  $F_{OFF}$  and  $F_{ON}$  will be enhanced, resulting in a higher  $V_{th}$ . The IV curves associated to devices having different amorphous thicknesses are reported in Fig. 1.11. This highlights the threshold voltage increase with the amorphous thickness as well as it evidences the increase of the resistance and the decrease of the ratio between the current and the voltage variation (i.e., dlogI/dV), defined as the sub-threshold slope (STS). The correlation between the  $V_{th}$  and the amorphous thickness represents a parameter of valuable interest especially when the chalcogenide material is integrated in a device, as it will be presented later in this work.

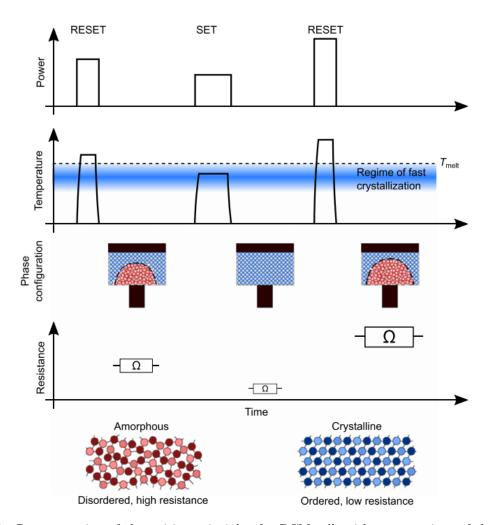

## **1.2** Phase-change memories

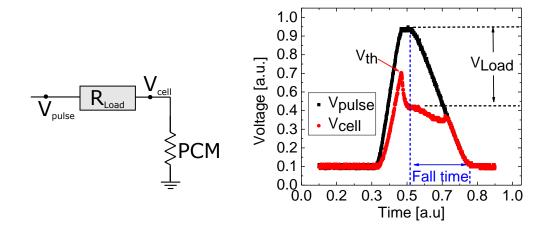

Phase-Change Memories (PCM) are two terminal devices where a phase-change material layer is sandwiched between two electrodes and the difference in resistivity between the two phases is used to store the information. In general, the amorphous phase is associated to the logic state 0 (RESET) while the crystalline phase corresponds to the logic state 1 (SET). The information is stored with a write operation that induces a resistance switch in the material through the application of an external voltage pulse. The SET and RESET write operations are schematized in Fig. 1.12. The amorphization is ensured by a voltage pulse high enough to induce the melting of the phase-change material inside the device (T >  $T_{melt}$ , where  $T_{melt}$  is generally around 650 °C) and with sharp pulse edges to maintain the disordered atom arrangement, achieved during melting, even when the material is cooled down back to room temperature. Indeed, during the fast quenching the atoms mobility is small enough to prevent the atomic rearrangement. To switch the material from the amorphous to the crystalline phase, instead, the voltage pulse should be able to keep the temperature in the fast crystallization regime long enough to ensure the re-crystallization of the whole amorphous region. Therefore, the crystallization process is characterized by a longer pulse edge (i.e., fall time) with respect to the amorphisation. Hence, the temperature profile control inside

Fig. 1.12. Representation of the writing principle of a PCM cell, with a comparison of the power, temperature profile, phase configuration and resistance during the SET and RESET programming conditions. The RESET pulse heats the material above the melting temperature and it leads the memory in an high resistive state (amorphous phase) when rapidly quenched back to room temperature. By tuning the power used during the programming pulse, the final RESET resistance can be modulated. The SET pulse, instead, heats the material up to the crystallization temperature and cool the system down with a specific speed which enable the atomic reorganization to a low resistive state [28].

the cell is fundamental to achieve an accurate storage of the information. To be noted that during the writing operation the voltage pulse need to have an amplitude higher than the threshold voltage (V >  $V_{th}$ ).

The programmed state can then be read through a read operation. This step retrieves the information stored in the cell (i.e., amorphous or crystalline state). The read operation consists in the application of a voltage pulse low enough to do not modify the memory state: the voltage amplitude should be smaller than  $V_{th}$ . Nevertheless, even if a V < V<sub>th</sub> is used, the information retrieved by a read operation can assume different values dependently on the time and temperature at which the measurement is performed. This effect mainly occurs in material being in the amorphous phase. Indeed, when the material is in this phase, it can face a structural relaxation, which macroscopically leads to the resistance drift towards higher values, due to the thermally activated nature of the electric transport, typical of the materials in these phase. At room temperature, the resistance (R) evolution in time (t) is described by a power low as follows:

$$R = R_0 \left(\frac{t}{t_0}\right)^{\nu} \tag{1.5}$$

were  $R_0$  represents the resistance at t = 0 ( $t_0$ ) and  $\nu$  is the drift coefficient, which is material dependent.

Moreover, the pulse used to SET the memory cell is not always capable to completely crystallize the material. Therefore, most of the time, the SET state is referred to a poly-crystalline state of the material. In this condition, the structural relaxation can occur at the grain boundaries between crystalline grains [29]. Furthermore, it has been demonstrated that the drift coefficient is temperature dependent. It increases linearly with temperature [30] until nucleation and growth take place, leading the resistance to decrease back to the starting value [29]. To be noted that, unlike the RESET state, the SET drift could cause the resistance window to reduce, hindering the programming of the cell.

#### **1.2.1** Electro-thermal analysis

The PCM working principle is based on the coupling between i) an *electric* contribution, due to the voltage applied and the current flowing in the device and ii) a *thermal* contribution, associated with the temperature rise in the system due to the Joule heating.

#### **1.2.1.1** Device functionality

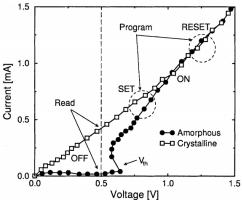

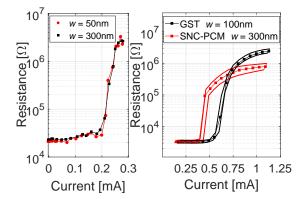

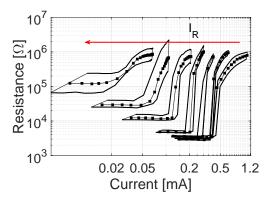

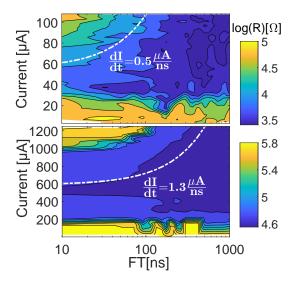

The typical IV and RI (resistance vs current) characteristics of a PCM cell are reported in Fig. 1.13 and Fig. 1.14, respectively. The curves are reported for both a PCM device initially in the crystalline phase (empty markers) and amorphous phase (filled markers). When the material is crystalline, the IV curve follows a ohmic behavior for low applied voltages. Increasing the voltage, the material is heated up by Joule

RESET state (filled black dots) [31].

Fig. 1.13. Current as a function of voltage for a PCM device in SET state (empty squares) and for a PCM device in

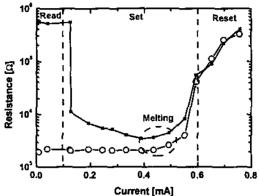

Fig. 1.14. Resistance as a function of current for a PCM device in SET state (empty cyrcle) and RESET state (filled black squares) [32].

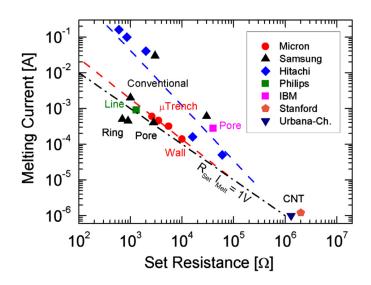

Fig. 1.15. Melting current as a function of the SET resistance compared for different architectures presented in literature, showing a linear correlation between the two parameters. [33]

heating. As a consequence, its atomic arrangement get drastically modified when the melting temperature is reached. This induces the onset of the ON-state, evidenced by a change of slope in the IV curve. The PCM resistance at this stage is called ON resistance ( $R_{ON}$ ). In general, it represents the bottom electrode resistance since the melted phase-change layer contributes marginally to  $R_{ON}$ . After melting, the material can reach the amorphous phase through a rapid quencing. It is important to notice that in a PCM device, the abrupt cooling will not always result in a resistance increase: if the interface between the chalcogenide and the bottom electrode is not completely covered by the melted region, the residual crystalline zones play the role of conductive paths, thus contributing the most to the final resistance value (i.e., in the equivalent electric circuit, the conductive paths are modeled by a resistance in parallel to the melted region one).

On the contrary, when the initial state of the material is amorphous, the IV characteristic follows the non-ohmic behavior according to Eq. 1.1, until the onset of the threshold switching  $(V_{th})$ . This will result in an abrupt reduction of the resistance, as reported in Fig. 1.14. At this point, the material reaches the ON-state, where the device can partially SET, if the active material achieves a temperature in the range of favorable crystallization. At this stage of the programming operation, the crystalline order achieved depends on the shape of the pulse used to program the cell. Therefore, the measured resistance could be higher than the SET value, as it is shown, for example, in the SET region of Fig. 1.14. Independently from the initial state, when the full region above the bottom electrode is melted, the material can be either programmed in RESET or in SET, depending on the shape of the applied pulse: a short fall time will RESET the device (as in Fig. 1.14) while a long fall time will SET it.

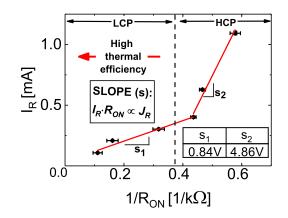

The PCM can be described by looking at two parameters controlling its functionality:

- the melting current  $(I_m)$ , which is directly related to the device power consumption

- the SET resistance  $(R_{SET})$ , which refers to the material conductance in the crys-

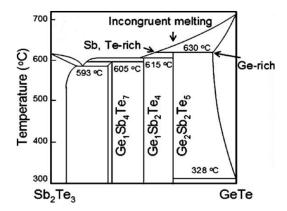

Fig. 1.16. Phase diagram along the tie-line  $Sb_2Te_3$ -GeTe [34]

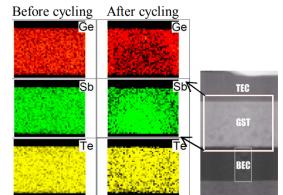

Fig. 1.17. Comparison of Energy Dispersive X-ray spectroscopy (EDX) performed before and after cycling. The analysis shows that after cycling the Sb atoms are pulled down to the bottom electrode/GST interface and the Ge is placed in the surrounded area [35]

talline state. This resistance is also associated with the contact area between the chalcogenide material and the bottom electrode when devices with the same active layer are compared.

The relation between  $I_m$  and the SET resistance for different PCM cell architectures is reported in Fig. 1.15 [33]. The trend evidences that the higher is the SET resistance, the lower is the current needed to melt the material. Therefore, device scaling is a suitable solution to reduce the melting current in PCM. As a matter of fact, shrinking all the device dimensions by a factor k, the electrical and thermal resistance (defined in the next section) increase of k, while  $I_m$  should decrease of the same factor, enabling better power performances [33]. In addition, using a low current to induce the phase change is particularly advantageous for the chalcogenide material aging. Indeed, the use of high programming current can be detrimental for the material upon multiple programming of the memory state, since it generates a non-uniform reorganization of the material inside the programmed region. This phenomenon is known as material segregation.

#### Phase segregation

Studying the behavior of a GST based PCM after a programming cycle at temperature higher than  $T_{c,GST}$  [34], S. W. Nam et al. demonstrated that the GST faced a phase separation into a Sb-Te-rich region and a Ge-rich one. Considering the pseudobinary phase diagram between Sb<sub>2</sub>Te<sub>3</sub> and GeTe reported in Fig. 1.16, the phase separation can be explained by a non-congruent melting in the ternary compound: at 630 °C a Sb-Terich phase begins to melt, while the Ge-rich phase is solid between 630 °C and 650 °C. Furthermore, a poor electrical contact between the electrode and GST can further enhance the heat generation, pulling the Ge atoms away from the liquid region. The same behavior has been observed by comparing EDX images on GST based PCM [35]. As shown in Fig. 1.17, the material reorganization results in:

- a Sb-rich region close to the bottom electrode contact, which improves the contact

area with the phase-change layer and can potentially induce a reduction in the SET resistance along cycling;

- a Ge-rich region moving towards the external part of the Sb-rich region;

- an almost unchanged Te distribution in the overall layer.

Further studies demonstrated that the material segregation is dependent on the polarity applied to the device [36]. When the cell is subjected to a standard forward bias condition, the Sb-rich region locate in contact with the bottom electrode and it is surrounded by Ge-rich region, as described above. Crespi et al. [37] developed an atomic migration model based on Wall structure PCM which is in accordance with the experimental behaviour: the Ge and Sb segregation is a result of the themal diffusion, while the Te atom displacement is electrif field driven.

Materials not belonging to the stoichiometric tie-line face phase segregation as well. In particular, Ge-rich GST starts to segregates during its re-crystallization. In this case, first a GST or Sb-rich phase (i.e Ge<sub>1</sub>Sb<sub>4</sub>Te<sub>7</sub> or the Ge<sub>1</sub>Sb<sub>2</sub>Te<sub>4</sub>) is formed due to its lower  $T_c$ ; then, further crystallization induces a Ge-rich residual amorphous with a composition more similar to Ge<sub>3</sub>Sb<sub>2</sub>Te<sub>6</sub> or the Ge<sub>4</sub>Sb<sub>2</sub>Te<sub>7</sub>, which is known to have a higher crystallization temperature (see Fig. 1.16 and Fig. 1.2) [38]. Whereas, in Sb-rich GST [39], the Sb in excess does not fill up the vacancies of the NaCl-type structure: the material is quite similar to GST and the Sb in excess remains amorphous by increasing its concentration at the grain boundaries.

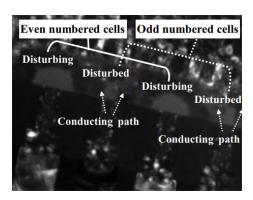

However, this undesirable phenomenon is not always detrimental for the device. In fact, when the cell faces a stable elemental segregation, the device performance can be improved, particularly the endurance. As an example, Sb-rich confined PCM demonstrated the highest endurance in PCM, reaching 2  $10^{12}$  cycles. In this case, a complete material segregation occurs in the first set of ten switching operations. As a result, a Sb-rich region is located close to the bottom electrode and it does not evolve throughout the cycling, avoiding both voids generation and further material segregation, ensuring the higher endurance [40]. The material segregation has also been exploited to develop Inter-Granular Switching PCM (IGS PCM) featuring both low power (i.e., programming current of 30  $\mu$ A) and high endurance ( $10^{11}$  cycles) [10]. Unlike conventional memories, the IGS PCM is a multi-grained structure where the phase-change spreads only in the inter-grain regions. Therefore, the programmed volume is limited and the write energy reduced.

In conclusion, the material segregation is a phenomenon taking place in all the PCM devices. Nevertheless, by tuning the material composition, it can be finely controlled and exploited to improve the PCM performance depending on the target application.

#### Exploting segregation: from $Ge_2Sb_2Te_5$ to Ge-rich GST

The most commonly used phase-change material is  $Ge_2Sb_2Te_5$ . Nevertheless, it is not suitable for all the possible applications that PCM can fulfill. As an example, the use of PCM for automotive applications requires a stability of the amorphous phase for 10 years at 150 °C. This target cannot be attained by GST, due to its low crystallization temperature (around 150 °C). For this reason, different materials lying on the Sb<sub>2</sub>Te<sub>3</sub>-GeTe tie-line gained the attention of the scientific community. Some of

**Fig. 1.18.** (left) Crystallization temperatures  $T_x$  as a function of compositions in the Ge-Sb-Te ternary phase diagram [41].(right) Resistivity versus temperature for Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> and Ge-rich GST thin films, showing the increase of the crystallization temperature with increasing Ge content [42].

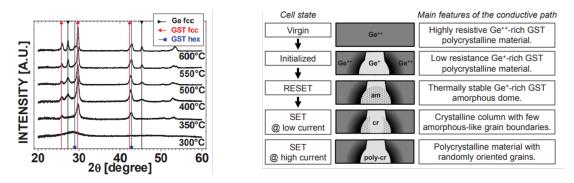

Fig. 1.19. X-ray diffraction (XRD) spectra of GST+Ge45% film after annealing at different temperatures, showing the phase separation of Ge and GST. Schematic of the composition and shape of the active volume during the programming of Ge-rich GST. [41].

the materials investigated are reported in Fig. 1.18, along with their crystallization temperature. It is evident that the Ge content can increase the crystallization temperature with respect to GST. This is further confirmed by the resistivity vs temperature analysis performed on different compositions obtained by increasing the Ge content in GST. In fact, the alloy with the higher Ge content demonstrates a crystallization temperature increase of more than 100 °C (which ensures a better thermal stability) as well as an increase of the crystalline state resistivity. These two features of Gerich GST compositions are advantageous when targeting automotive applications [43]. The higher crystallization temperature is explained by the increase of the tetrahedral Ge-Ge bonds induced in Ge-rich alloys [44] [45]. As a result, the material has a more disordered structure, leading to a higher material resistivity and a slower crystallization mechanism [46].

XRD spectra performed at different temperature on GST enriched with 45% of Ge is reported in Fig. 1.19. These show that the material crystallizes at 350 °C and segregates in crystalline GST (fcc or hcp) and fcc Ge. An evidence of the material segregation induced in programmed PCM devices is reported in Fig. 1.19, where the phase-change material reorganization results quite similar to the one observed in GST (Fig. 1.17). At first, the highly resistive Ge-rich material is initialized: part of the Ge is moved out from the active area, while the rest is kept inside it, therefore, the programmed

region is still made up of a Ge-rich alloy. Consequently, the RESET state presents a high thermal stability, differently from the GST-based PCM. The Ge-rich composition achieved a data retention up to 10 years at 185 °C, which is above the requirements for automotive applications. The SET state of Ge-rich PCM, instead, is characterized by amorphous-like grain boundaries/randomly oriented grains (Fig. 1.19), resulting in the increase of the SET resistance drift coefficient with respect to GST based devices.

#### **1.2.1.2** Electo-thermal properties

The electro-thermal behavior of the cell can be described by a classical heat transfer model in stationary conditions:

$$\nabla \cdot q = Q \tag{1.6}$$

where q is the thermal flux which obeys the Fourier's law of heat transfer:

$$q = -k_{th} \nabla T \tag{1.7}$$

and Q is the power density represented by the Joule heating induced by the external voltage applied to the cell:

$$Q = \vec{J} \cdot \vec{E} \tag{1.8}$$

In the previuos equations,  $k_{th}$  represents the thermal conductivity and  $\vec{E}$  is the electric field ( $\vec{E} = \vec{J}/\sigma$ ). Both the thermal and electrical conductivity are temperature dependent in the phase-change layer. By coupling Eq. 5.13 with Eq. 5.13 and Eq. 5.13, it is possible to predict the temperature achieved in a specific position of the memory thanks to the following expression:

$$\nabla^2 T = -\frac{J^2}{k_{th}\sigma} \tag{1.9}$$

Furthermore, it is possible to define the thermal resistance  $(R_{th})$  of a PCM cell by considering the simplified Fourier equation:

$$\Delta T = P_{cell} R_{th} \tag{1.10}$$

where  $\Delta T$  is the temperature achieved in the system with respect to room temperature and  $P_{cell}$  is the power injected in the system to obtain a specific  $\Delta T$ , defined as:

$$P_{cell} = R_{ON} I^2 \tag{1.11}$$

where I is the current flowing in the system. The evaluation of  $R_{th}$  provides a quantitative estimation of the thermal efficiency of a PCM cell. Therefore, from Eq. 1.10 follows that the higher is  $R_{th}$ , the smaller the power needed to achieve a specific temperature in the cell. Hence, the variation in temperature inside the device can mainly be ascribed to: i) the thermal resistance of the device, which is dependent on the temperature variation of  $k_{th}$  and  $\sigma$  for the active layer and the material in contact with it ii) the device geometry, since the current required to achieve the melting at a specific J depends on the SET resistance. Consequently, the thermal conductivity of the materials used in the PCM as well as the device structure have a crucial role on the PCM performances. These aspects will be describe in detail later in this work, respectively

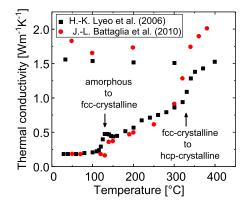

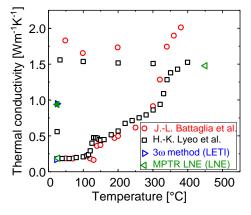

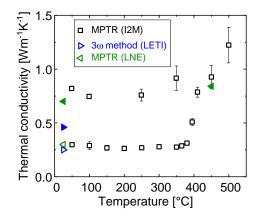

Fig. 1.20. Temperature dependent thermal conductivity values measured by TDTR by Lyeo et al. [47] and TDTR by Battaglia et al. [48]

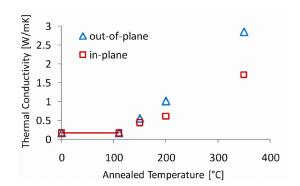

Fig. 1.21. In-plane and out-of-plane thermal conductivity values for GST at different annealing temperatures. The coefficient of thermal anysotropy is one for the amorphous GST, while it increases with annealing time, reaching for both a cubic and hexagonal GST a value of 0.6 [49].

in the next paragraph and in Ch.2.

#### Thermal conductivity characterization

The thermal conductivity of the phase-change materials and of those being in direct contact with it, plays a key role in the device functionality. Indeed, a small variation in  $k_{th}$  can cause a significant change of the temperature profile inside the cell, affecting the device performance. For this reason, the interest to characterize the thermal conductivity of the materials involved in the PCM devices has increased. In particular, the measured thermal conductivity value can enable an accurate electro-thermal modeling of the memory [50], that can be exploited both to predict the device performance and to propose innovative solutions to improve it.

The two most used methods to evaluate the thermal conductivity of conductive and non-conductive layers are: the  $3\omega$  method and the Modulated Photothermal Radiometry (MPTR). The former is based on an electric measurement performed via the contact of the probes on an electrode heater deposited on top of the tested material. The latter, is a contactless method. It is based on the optical measure of the radiation emitted by the sample, in response to a photothermal excitation by a laser beam.

In the first studies, the out-of plane thermal conductivity of phase-change materials has been evaluated at room temperature and a thermal annealing was used to carry the material either in the crystalline or in the amorphous phase before their characterization [51]. Lately, the test procedure have been improved and the thermal conductivity measurements has been performed under a continous temperature increase, allowing the thermal conductivity characterization during the phase transition. The GST thermal conductivity evaluated with the  $3\omega$  method showed a  $k_{th} \sim 0.14$  Wm<sup>-1</sup>K<sup>-1</sup> in the crystalline phase and  $k_{th} \sim 0.39$  Wm<sup>-1</sup>K<sup>-1</sup> for the amorphous one [50].

In the same way, H.-K. Lyeo et al. [47] and J.-L. Battaglia et al. [48] used noncontact methods (time-domain termoreflectance (TDTR) and Photo-Thermal Radiometry, respectively) to measure the thermal conductivity evolution in temperature for  $Ge_2Sb_2Te_5$ . The results, reported in Fig. 1.20, present comparable trend, with a first  $k_{th}$  increase in correspondence of the amorphous to crystalline transition and a second one at around 350 °C, in line with the fcc to hcp-crystalline transition. Furthermore, in both cases, the thermal conductivity remains stable at 1.6 Wm<sup>-1</sup>K<sup>-1</sup>, when the material is characterized at room temperature after the same annealing thermal budget. These results are comparable with other works reporting the thermal conductivity on both amorphous GST ( $k_{th} \sim 0.2 \text{ Wm}^{-1}\text{K}^{-1}$ ) [51] [52] and fcc-crystalline GST ( $k_{th} \sim 0.5 \text{ Wm}^{-1}\text{K}^{-1}$ ) [51] [53]. Moreover, the transition temperatures from amorphous to crystalline and crystalline to hexagonal are consistent with the one observed in resistivity versus temperature measurements [54].

The small differences in the amorphous  $k_{th}$  values, follow the minimum thermal conductivity approximation [55] [47]. It assert that in disordered crystals the presence of structural defects does not impact the thermal conductivity value obtained by modeling phonon transport as a system of localized oscillators. In addition, this is in accordance with the hypothesis of phonon driven thermal transport for amorphous GST [56]. Therefore, the small  $k_{th}$  variation observed can only be addressed to the partial re-crystallization of the amorphous [57] or to the presence of thermal boundary resistance (when the effective thermal conductivity is measured [58]). On the contrary, the crystalline phase transport is mainly dominated by electrons [56]. Furthermore the low  $k_{th}$  glass like values obtained for the crystalline GST are not surprising. Indeed, these are typical values for materials having a high concentrations of vacancies [55], which is the case in crystalline GST, as observed by Kolobov et al. [59]. Fig. 1.20 further shows that, unlike the amorphous to fcc transition, the fcc to hcp is really gradual. Lyeo et al. ascribed the phenomena to an evolving mixture of cubic and hexagonal GST, in the range of temperature investigated.

However, it is important to underline that all the presented works, independently from the method used, do not investigated temperatures higher than 400 °C, while the melting temperature of GST is around 600 °C. The impossibility to reliably test at high temperature is caused by the thermal diffusion effect, which can impact the temperature profile [60] or cause the sublimation of the layer along with the electrode cracking [61]. Recently, with the optimization of the device structure and the development of highly scaled devices based on different thermal propagation mechanisms, raised the interest in the evaluation of the in-plane thermal conductivity. A first study performed on GST shows that the thermal conductivity anysotropy (i.e., ratio between in-plane and out-of plane  $k_{th}$ ) in crystalline GST assumes values within 0.65 and 0.8 (Fig. 1.21). The phenomena is currently ascribed to the columnar grain structure of GST generated during the material annealing [62] [63] [49]. Nevertheless, further investigation are on-going to confirm this hypothesis.

#### Thermal boundary resistance

Another factor influencing the thermal properties of the PCM cell is the thermal boundary resistance (TBR). This arises from the partial transmission of heat carriers across an interface [65] and, importantly, it is not negligible with respect to the thermal resistance of the material itself. As an example, the TBR at the GST/Si interface ( $10^{-7}$  $\text{Km}^2\text{W}^{-1}$ ) is comparable to the  $R_{th}$  of a 100 nm thick hcp-GST [64]. In addition, the

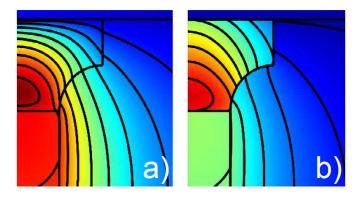

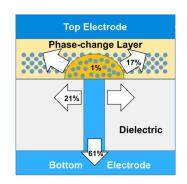

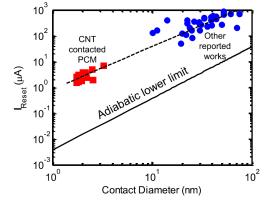

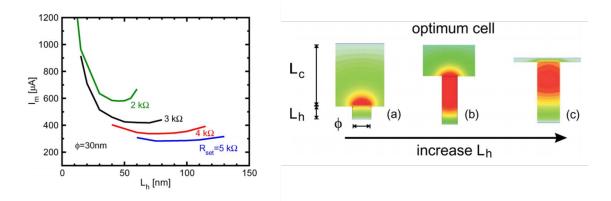

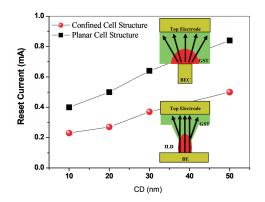

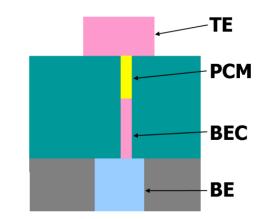

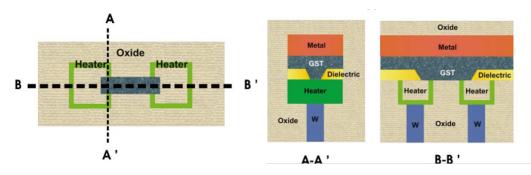

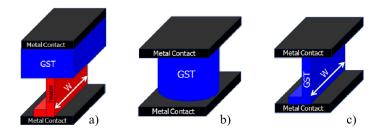

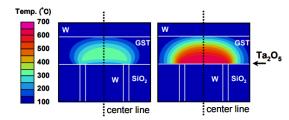

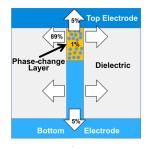

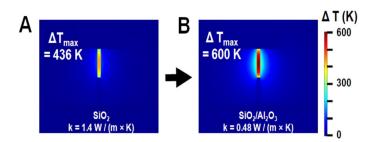

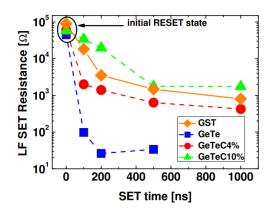

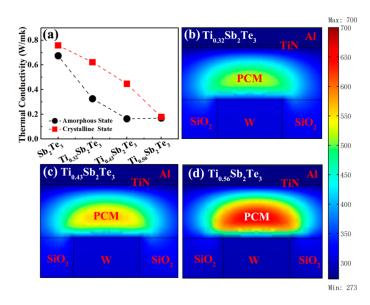

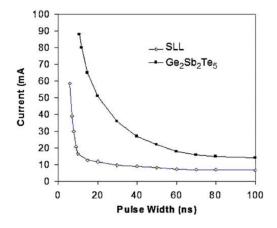

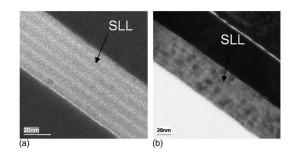

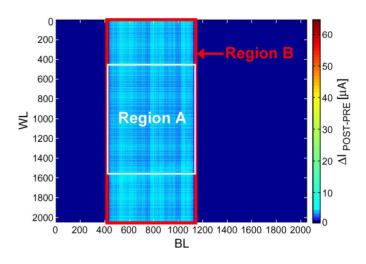

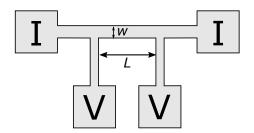

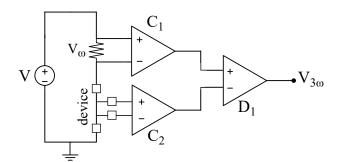

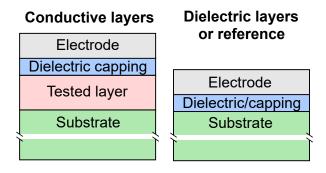

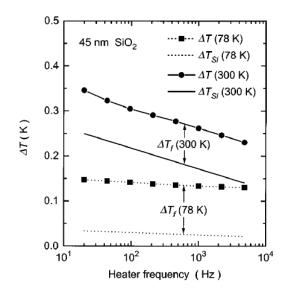

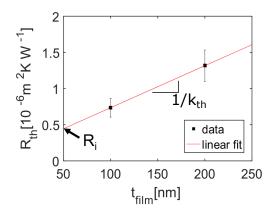

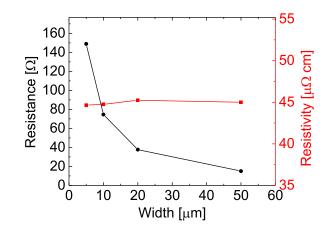

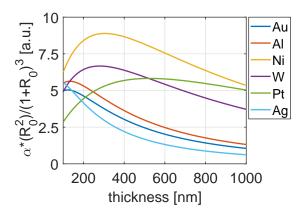

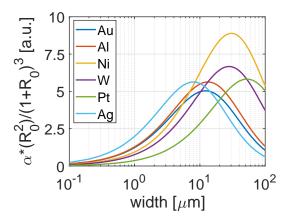

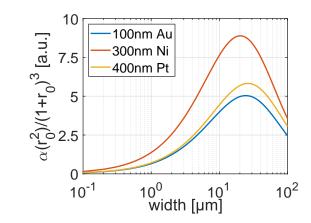

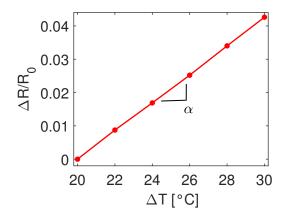

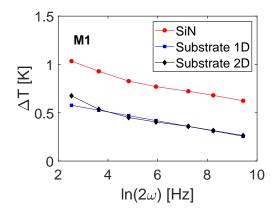

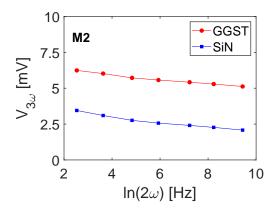

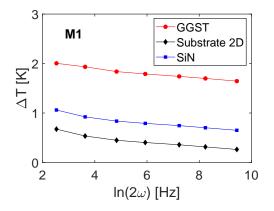

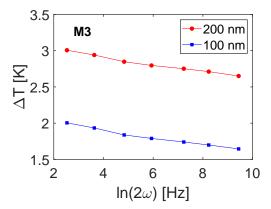

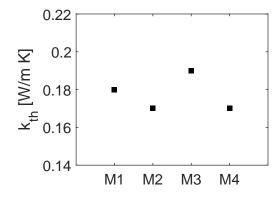

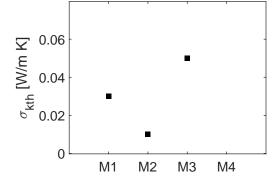

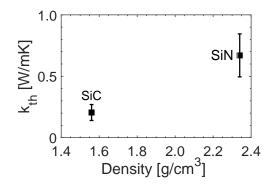

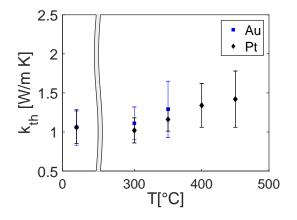

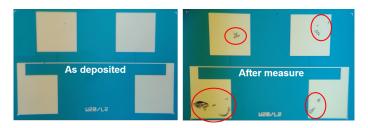

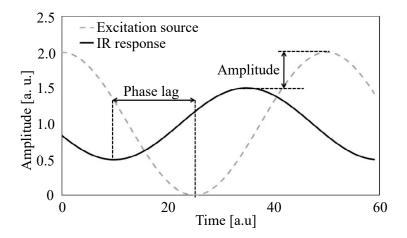

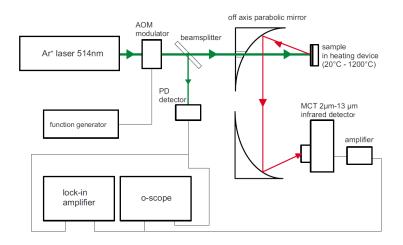

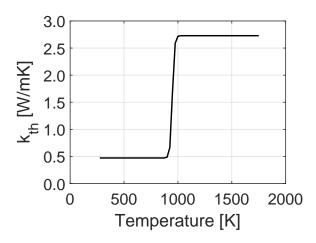

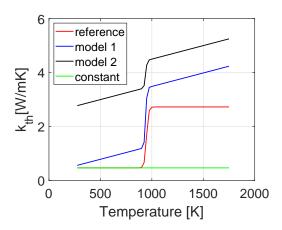

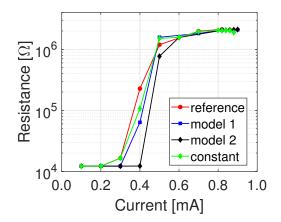

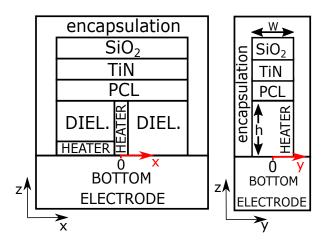

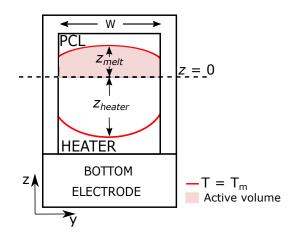

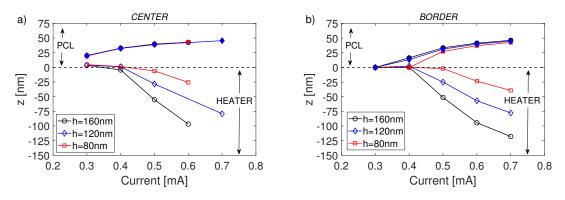

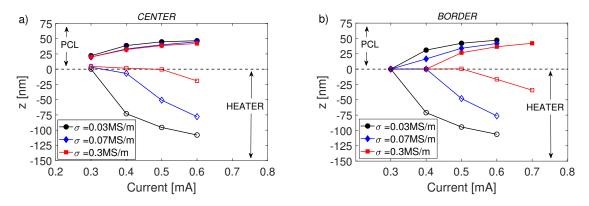

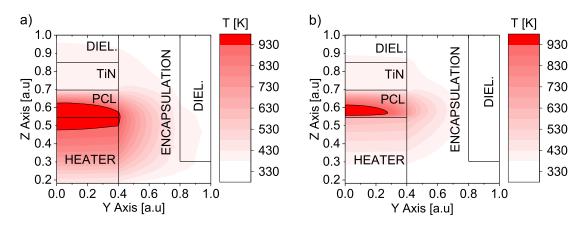

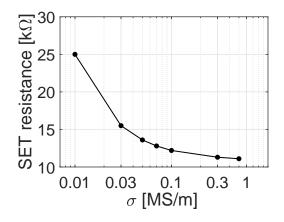

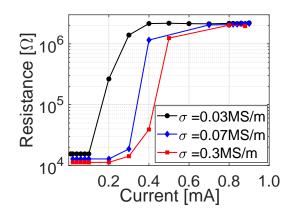

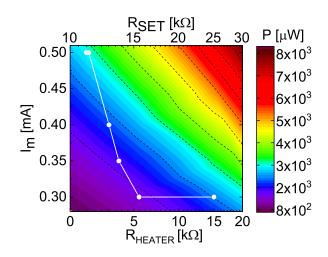

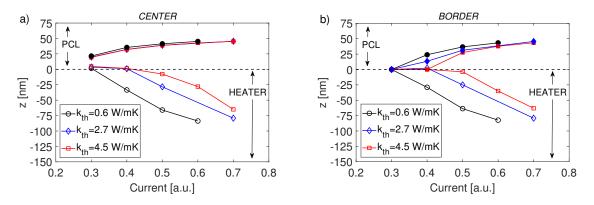

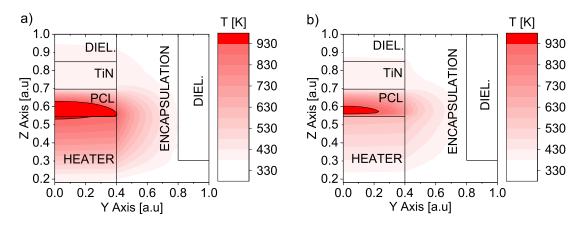

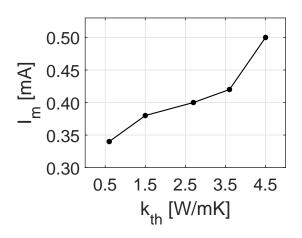

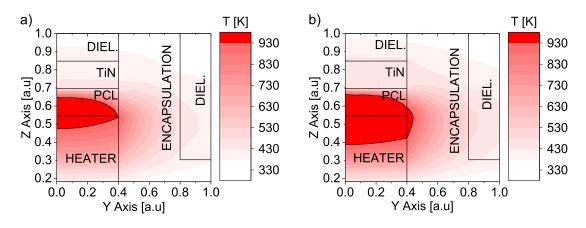

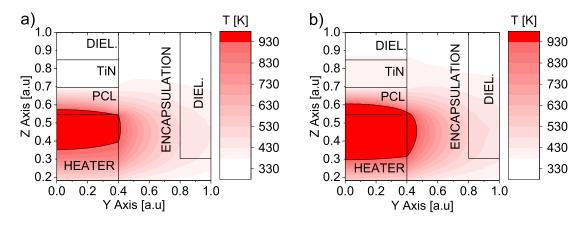

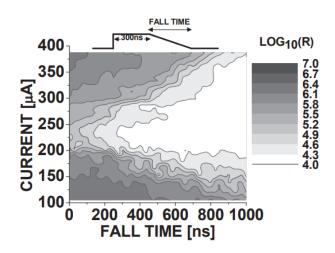

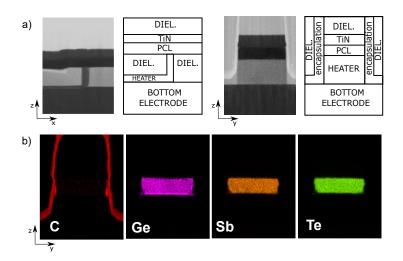

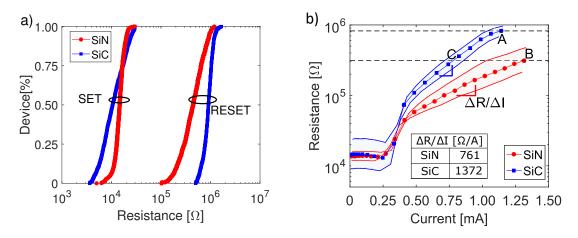

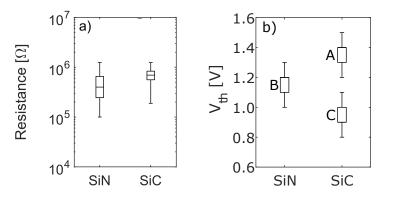

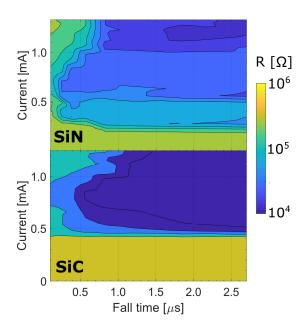

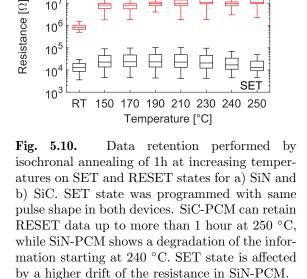

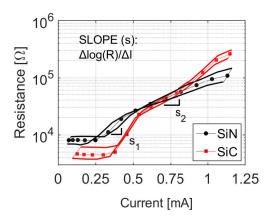

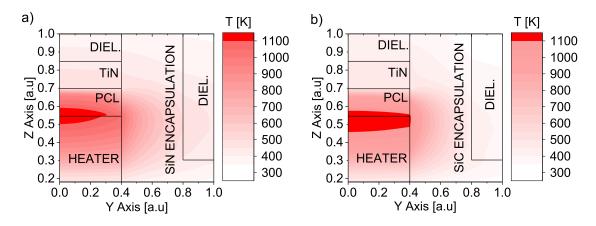

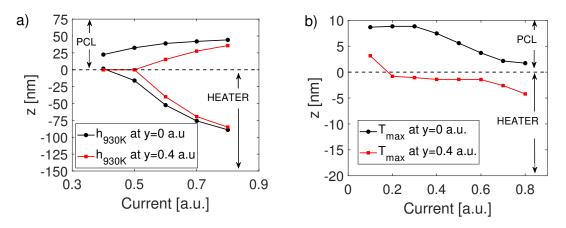

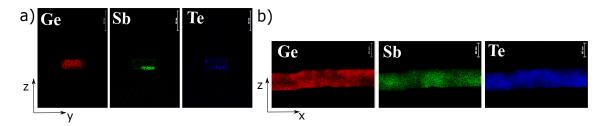

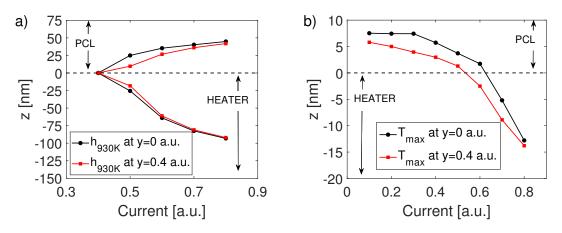

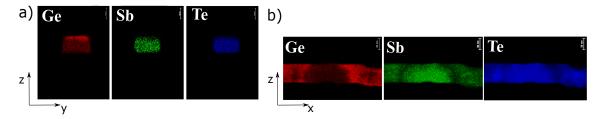

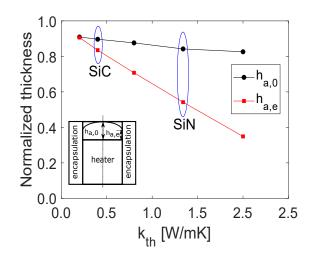

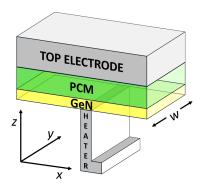

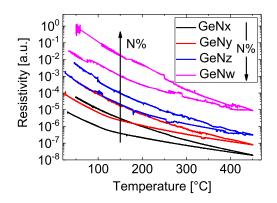

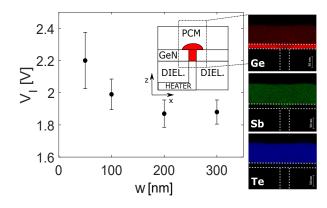

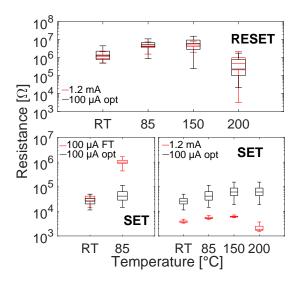

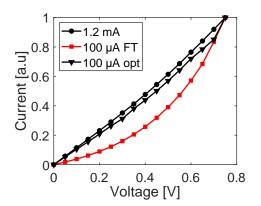

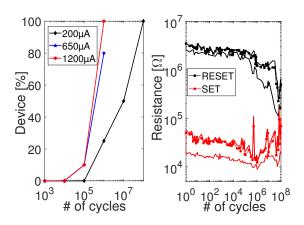

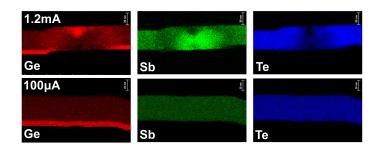

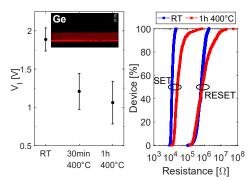

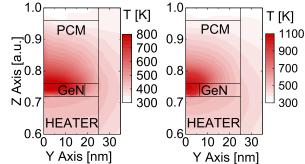

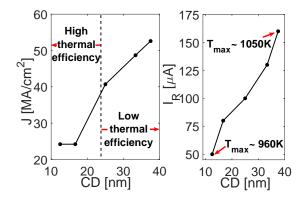

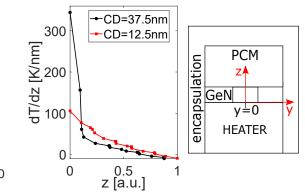

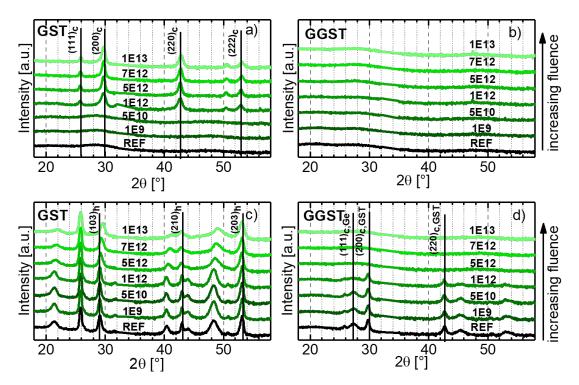

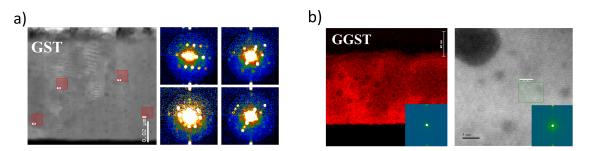

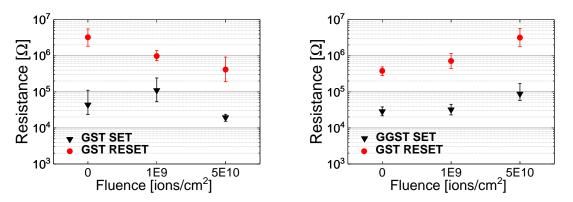

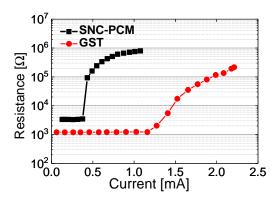

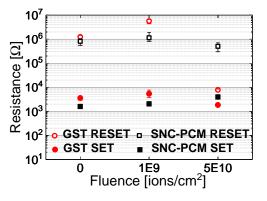

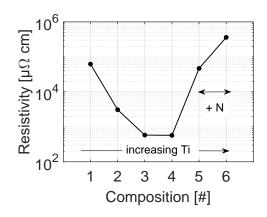

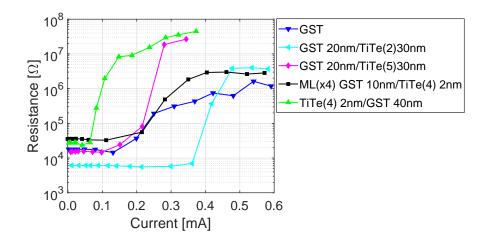

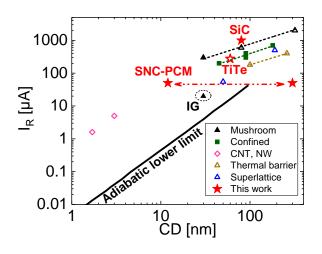

Fig. 1.22. Comparison of the temperature profile reached inside a memory cell a) with and b) without Thermal Boundary Resistance (TBR). When the TBR is taken into account, the temperature is more concentrated at the heater/chalcogenide interface [64]