# Nanvix: A Distributed Operating System for Lightweight Manycore Processors

Pedro Henrique Penna

## ▶ To cite this version:

Pedro Henrique Penna. Nanvix: A Distributed Operating System for Lightweight Manycore Processors. Embedded Systems. Université Grenoble Alpes [2020-..]; Pontifícia universidade católica de Minas Gerais (Brésil), 2021. English. NNT: 2021GRALM027. tel-03545212

## HAL Id: tel-03545212 https://theses.hal.science/tel-03545212v1

Submitted on 27 Jan2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

Pour obtenir le grade de

DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

préparée dans le cadre d'une cotutelle entre l'*Université Grenoble Alpes et la Pontifícia Universidade Católica de Minas Gerais*

Spécialité: Informatique

Arrêté ministériel: le 6 janvier 2005 – 25 mai 2016

Présentée par

## Pedro Henrique DE MELLO MORADO PENNA

Thèse dirigée par Jean-François MÉHAUT et Henrique FREITAS

préparée au sein des Laboratoires d'Informatique de Grenoble

dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

## Nanvix: Un Système d'Exploitation Distribué pour les Processeurs Manycore Légers

Thèse soutenue publiquement le **23 Septembre 2021** devant le jury composé de:

Abdoulaye GAMATIÉ Directeur de Recherche, CNRS/LIRMM, Président Pierre SENS Professeur, Sorbonne Université, Rapporteur Rodolfo AZEVEDO Professeur, Universidade de Campinas, Rapporteur Benoît DINECHIN Ingéniur Docteur, Kalray Inc, Examinateur François BROQUEDIS Maître de Conferénce, Université Grenoble Alpes, Examinateur Márcio CASTRO Professeur Associé, Universidade Federal de Santa Catarina, Examinateur Carlos Augusto MARTINS Professeur, Pontifícia Universidade Católica de Minas Gerais, Invité

## PONTIFÍCIA UNIVERSIDADE CATÓLICA DE MINAS GERAIS Programa de Pós-Graduação em Informática

Pedro Henrique de Mello Morado Penna

## NANVIX A Distributed Operating System for Lightweight Manycore Processors

Belo Horizonte 2021

Pedro Henrique de Mello Morado Penna

## NANVIX A Distributed Operating System for Lightweight Manycore Processors

Doctorate thesis presented to the Graduate Program in Informatics of the Pontifícia Universidade Católica de Minas Gerais as partial requirements for earning the PhD degree in Informatics.

Advisor: Prof. Dr. Henrique Cota de Freitas (PUC Minas) Advisor: Prof. Dr. Jean-François Méhaut (UGA)

Belo Horizonte 2021

Pedro Henrique de Mello Morado Penna

## NANVIX A Distributed Operating System for Lightweight Manycore Processors

Doctorate thesis presented to the Graduate Program in Informatics of the Pontifícia Universidade Católica de Minas Gerais as partial requirements for earning the PhD degree in Informatics.

Prof. Dr. Jean-François Méhaut - UGA (Advisor)

Prof. Dr. Henrique Freitas - PUC Minas (Advisor)

Prof. Dr. Abdoulaye Gamatié – LIRMM (Examining Committee)

Prof. Dr. Pierre Sens - Sorbonne Université (Examining Committee)

Prof. Rodolfo Azevedo - UNICAMP (Examining Committee)

Dr. Benoît Dinechin - Kalray Inc (Examining Committee)

Prof. Dr. Carlos Augusto Martins - PUC Minas (Examining Committee)

Prof. Dr. François Broquedis - UGA (Examining Committee)

Prof. Dr. Márcio Castro – UFSC (Examining Committee)

Belo Horizonte 2021

#### ABSTRACT

Lightweight Manycore (LW Manycore) processors were introduced to deliver performance scalability with low-power consumption. To address the former aspect, they rely on specific architectural characteristics, such as a distributed memory architecture and a rich Network-on-Chip (NoC). To achieve low-power consumption, they are built with simple low-power Multiple Instruction Multiple Data (MIMD) cores, they have a memory system based on Scratchpad Memories (SPM) and they exploit heterogeneity by featuring cores with different capabilities. Some industry-successful examples of these processors are the Kalray MPPA-256, the PULP and the Sunway SW26010. While this unique set of architectural features grant to LW Manycore performance scalability and energy efficiency, they also introduce multiple challenges in software programmability and portability. First, the high density circuit integration turns dark silicon into reality. Second, the distributed memory architecture requires data to be explicitly fetched/offloaded from remote memories to local ones. Third, the small amount of on-chip memory forces the software to partition its working data set into chunks and decide which of them should be kept local and which should be offloaded to remote memory. Fourth, the on-chip interconnect invites software engineers to embrace a message-passing programming model. Finally, the *on-chip* heterogeneity makes the deployment of applications complex. One approach for addressing these challenges is by means of an Operating System (OS). This type of solution craves to bridge intricacies of an architecture, by exposing rich abstractions and programming interfaces, as well as handling resource allocation, sharing and multiplexing. Unfortunately, existing OSes struggle to fully address programmability and portability challenges in LW Manycore, because they were not designed to cope with architectural features of these processors. In this context, the main goal of this work boils down to propose a novel OS for LW Manycore that specifically copes with these uncovered challenges. The main contribution of this work is a distributed OS that advances the resource management in LW Manycore processors. On the one hand, from the scientific perspective this main contribution may be unfolded in three specific contributions. First, a comprehensive Hardware Abstraction Layer (HAL) that makes the development and deployment of a fully-featured OS for LW Manycore easier, as well as it enables the portability of an OS across multiple of these processors. Second, a rich memory management approach that is based on Distributed Paging System (DPS). This is a novel system-level solution that we devised for managing memory of a LW Manycore. Third, a lightweight communication facility that manages the on-chip interconnect and exposes primitives with hardware channel multiplexing. On the other hand, as a technical contribution, this work introduces Nanvix. This is a concrete implementation of an OS for LW Manycore processor that features the aforementioned scientific advancements. Nanvix supports multiple architectures (Bostan, x86, OpenRISC, ARMv8 and RISC-V), runs on baremetal processors, exposes rich abstractions and high-level programming interfaces.

Keywords: Distributed Operating Systems. Lightweight Manycore Processors.

#### **RESUMO**

Processadores LW Manycore foram introduzidos para fornecer escalabilidade de desempenho a um baixo consumo de energia. Para abordar o primeiro aspecto, eles contam com características arquiteturais específicas, como uma arquitetura de memória distribuída e um rede-em-chip. Para atingir baixo consumo de energia, esses processadores são construídos com núcleos simples e de baixo consumo de energia, têm um sistema de memória baseado em SPM e exploram heterogeneidade. Alguns exemplos de sucesso desses processadores são o Kalray MPPA-256, o PULP e o Sunway SW26010. Embora este conjunto único de recursos arquiteturais conceda a LW Manycore desempenho escalabilidade e eficiência energética, eles também apresentam vários desafios na programação e portabilidade do software. Primeiro, a integração do circuito *de alta densidade* transforma o problema de *dark silicon* em realidade. Em segundo lugar, a arquitetura de memória distribuída requer que os dados sejam explicitamente buscados / descarregados de memórias remotas para memórias locais. Terceiro, a pequena quantidade de memória on-chip força o software a particionar seu conjunto de dados de trabalho em blocos e decidir qual deles deve ser mantido local e deve ser descarregado para a memória remota. Quarto, a interconexão on-chip convida engenheiros de software a abraçar um modelo de programação de passagem de mensagens. Finalmente, a heterogeneidade no chip torna complexa a implantação de aplicações. Uma abordagem para enfrentar esses desafios é por meio de um sistema operacional (SO). Esse tipo de solução anseia por superar as complexidades de uma arquitetura, por expor abstrações ricas e interfaces de programação, bem como manipular alocação, compartilhamento e multiplexação de recursos. Infelizmente, os sistemas existentes lutam para resolver totalmente a programabilidade e desafios de portabilidade em LW Manycore, porque eles não foram projetados para lidar com características arquitetônicas desses processadores. Nesse contexto, o principal objetivo deste trabalho se resume em propor um SO para LW Manycore que lida especificamente com esses desafios. A principal contribuição deste trabalho é um SO distribuído que avança o gerenciamento de recursos em processadores LW Manycore. Por um lado, do ponto de vista científico, esta contribuição principal pode ser desdobrada em três contribuições específicas. Em primeiro lugar, uma HAL abrangente que torna o desenvolvimento e implantação de um SO totalmente caracterizado para LW Manycore mais fácil, bem como permite a portabilidade de um SO em vários desses processadores. Em segundo lugar, uma abordagem de gerenciamento de memória rica que se baseia em DPS, uma nova solução em nível de sistema que criamos para gerenciar a memória de um LW Manycore. Terceiro, uma facilidade de comunicação leve que gerencia o on-chip interconecta e expõe primitivas com multiplexação de canal de hardware. Por outro lado, como contribuição técnica, este trabalho apresenta o Nanvix. Esta é uma implementação concreta de um processador SO para LW Manycore que apresenta os avanços científicos mencionados. Nanvix suporta múltiplos arquiteturas é executado em processadores baremetal, expõe abstrações ricas e programação de alto nível interfaces.

Palavras-chave: Sistemas Operacionais Distribuídos. Processadores Manycore leves.

### LIST OF FIGURES

| Figure 1 – An extended taxonomy for single-chip manycore architectures      | 24 |

|-----------------------------------------------------------------------------|----|

| Figure 2 – Manycore accelerators.    2                                      | 25 |

| Figure 3 – Manycore processors.    2                                        | 26 |

| Figure 4 – A LW Manycore processor with 67 cores.                           | 27 |

| Figure 5 – A possible architecture for an OS                                | 30 |

| Figure 6 – Popular architectures for an OS.       Sector                    | 31 |

| Figure 7 – Memory partitioning techniques                                   | 32 |

| Figure 8 – Memory allocation techniques                                     | 33 |

| Figure 9 – Memory virtualization techniques                                 | 35 |

| Figure 10 – States diagram for a process.                                   | 38 |

| Figure 11 – Possible organizations for a file                               | 14 |

| Figure 12 – File allocation schemes                                         | 45 |

| Figure 13 – A possible layout for a file system.                            | 46 |

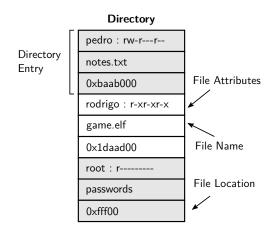

| Figure 14 – Structure of a directory                                        | 47 |

| Figure 15 – Architectures for distributed OSes.                             | 47 |

| Figure 16 – Communication mechanisms for distributed systems.               | 18 |

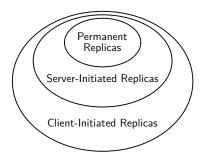

| Figure 17 – Replica placement in a distribute system                        | 53 |

| Figure 18 – Operating systems for single-chip manycore architectures        | 67 |

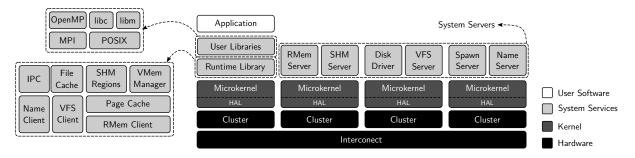

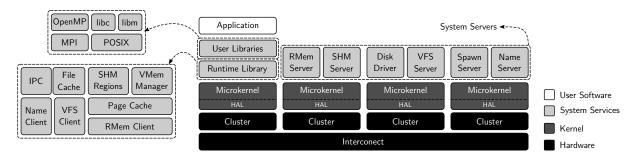

| Figure 19 – A structural overview of Nanvix                                 | 70 |

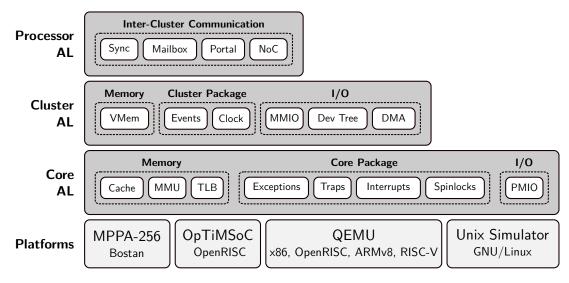

| Figure 20 – Structural overview of the HAL of Nanvix                        | 72 |

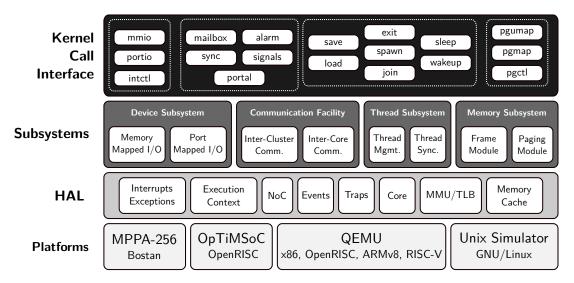

| Figure 21 – Structural overview of the Nanvix microkernel.                  | 76 |

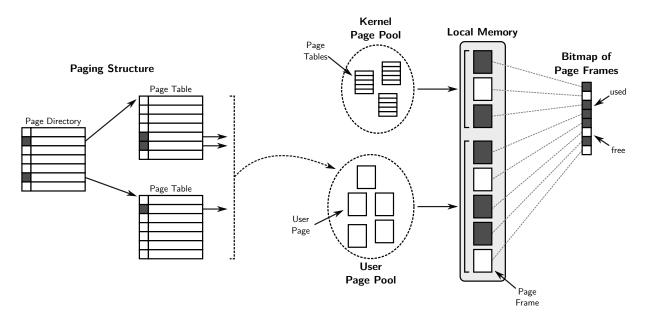

| Figure 22 – Memory system module.                                           | 77 |

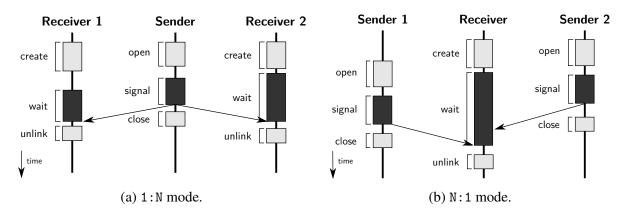

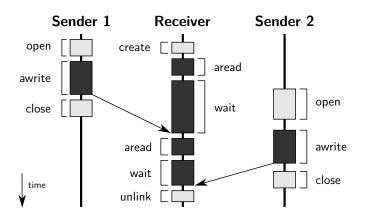

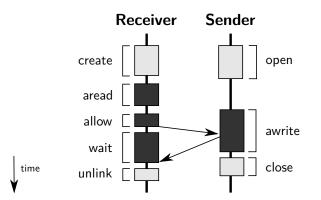

| Figure 23 – Execution flow of <i>sync</i> abstraction                       | 81 |

| Figure 24 – Execution flow of <i>mailbox</i> abstraction (N:1)              | 32 |

| Figure 25 – Execution flow of <i>portal</i> abstraction (1:1)               | 32 |

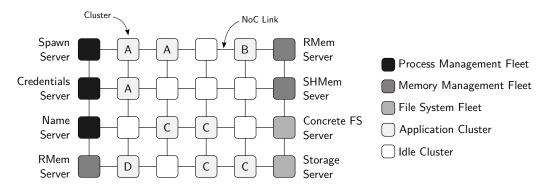

| Figure 26 – Services of Nanvix running on a lightweight manycore processor. | 34 |

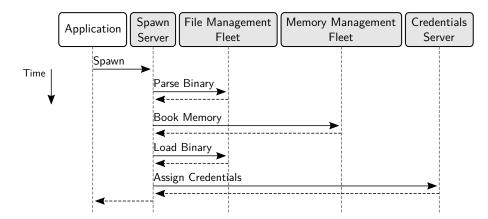

| Figure 27 – Process spawn in Nanvix                                         | 36 |

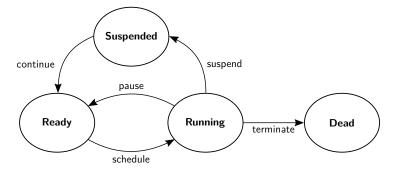

| Figure 28 – States of a process in Nanvix                                   | 87 |

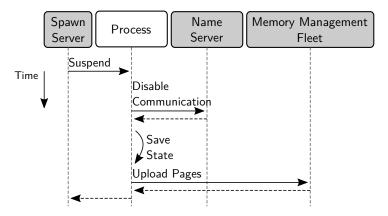

| Figure 29 – Process migration in Nanvix                                     | 88 |

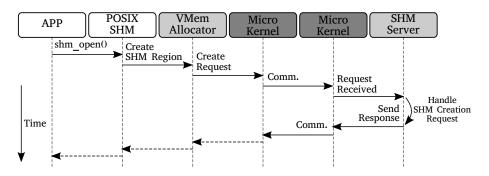

| Figure 30 – Shared memory region creation in Nanvix.                        | 92 |

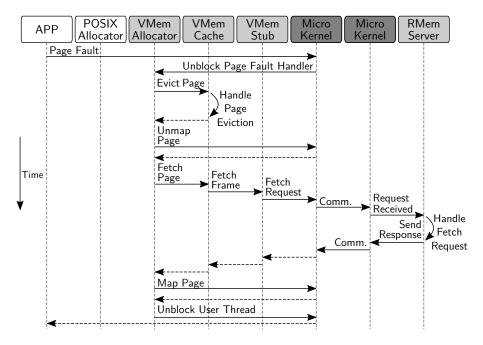

| Figure 31 – Remote page fetch in Nanvix                                     | 93 |

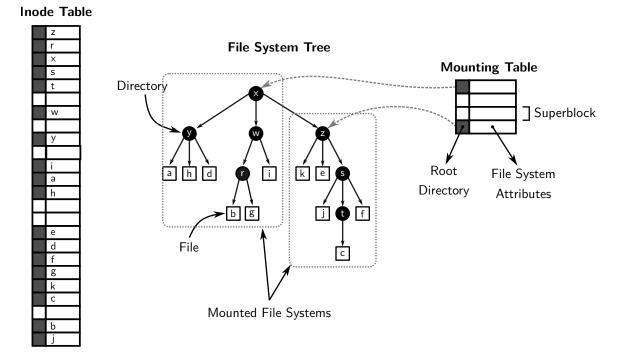

| Figure 32 – Virtual file system of Nanvix                                   | 94 |

| Figure 33 – Architectural overview of the MPPA-256 LW Manycore processor 10 | )5 |

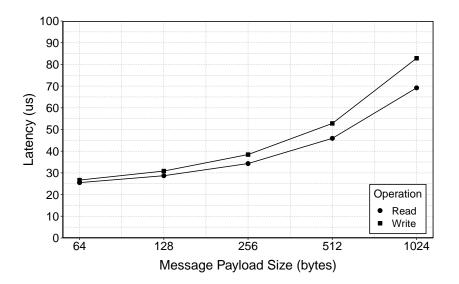

| Figure 34 – Mailbox latency when varying message size                       | )9 |

| Figure 35 – Mailbox throughput for fixed-size messages                      | 10 |

| Figure 36 – Sync latency scalability for synchronization signals.           | 10 |

| Figure 37 – Portal bandwidth scalability for dense data transfers                            |

|----------------------------------------------------------------------------------------------|

| Figure 38 – Mailbox and portal throughput when varying transfer size                         |

| Figure 39 – Uncached read/write bandwidth                                                    |

| Figure 40 – Cached read/write bandwidth                                                      |

| Figure 41 – Execution breakthrough for local kernel calls                                    |

| Figure 42 – Execution breakthrough for remote kernel calls                                   |

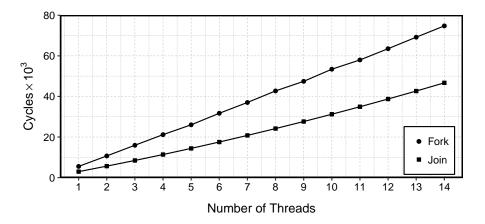

| Figure 43 – Performance scalability for creating and terminating threads                     |

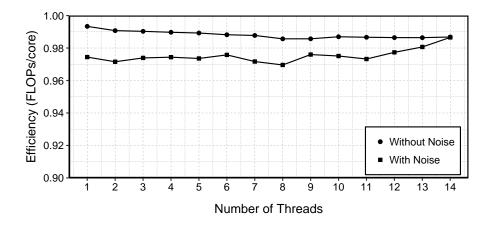

| Figure 44 – Execution efficiency for the knoise Benchmark                                    |

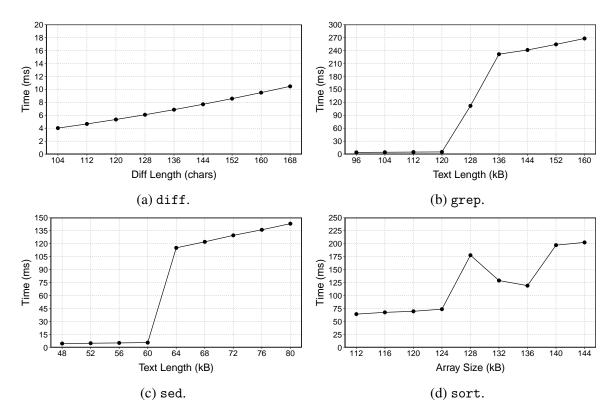

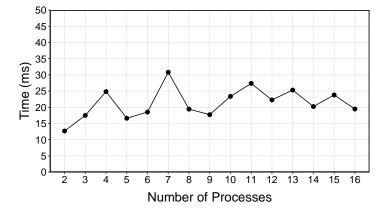

| Figure 45 – Performance for system utilities                                                 |

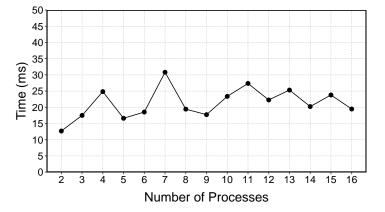

| Figure 46 – Performance of Nanvix under heavy-load                                           |

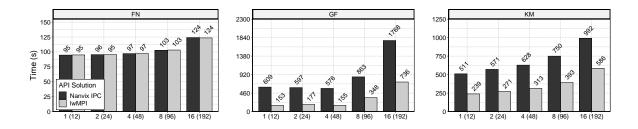

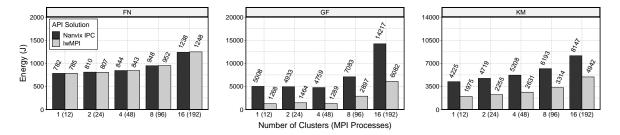

| Figure 47 – Execution times for fn, gf and km                                                |

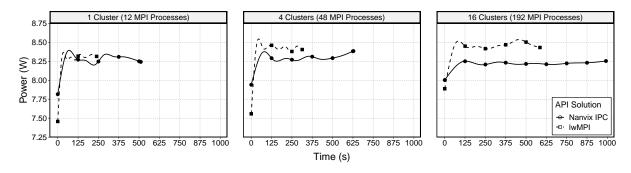

| Figure 48 $-$ Power consumption for km when varying the number of clusters/problem sizes.124 |

| Figure 49 – Energy consumption for fn, gf and km                                             |

| Figure 50 – Architectural overview of the MPPA-256 LW Manycore processor 147                 |

| Figure 51 – Uma taxonomia estendida para arquiteturas manycore de chip único 155             |

| Figure 52 – Uma possível arquitetura para um sistema operacional                             |

| Figure 53 – Arquiteturas para sistemas operacionais distribuídos                             |

| Figure 54 – Sistemas operacionais para arquiteturas multicore de chip único                  |

| Figure 55 – Uma visão geral estrutural de Nanvix                                             |

| Figure 56 – Visão geral da arquitetura do processador MPPA-256 LW Manycore 165               |

| Figure 57 – Desempenho para utilitários do sistema                                           |

| Figure 58 – Desempenho do Nanvix sob carga pesada                                            |

| Figure 59 – Une taxonomie étendue pour les architectures multicœurs à puce unique 178        |

| Figure 60 – Une architecture possible pour un OS                                             |

| Figure 61 – Architecture pour les systèmes d'exploitation distribués                         |

| Figure 62 – Systèmes d'exploitation pour architectures multicœurs à puce unique 184          |

| Figure 63 – Un aperçu structurel de Nanvix                                                   |

| Figure 64 – Présentation architecturale du processeur MPPA-256 LW Manycore 188               |

| Figure 65 – Performance pour les utilitaires système                                         |

| Figure 66 – Performance de Nanvix sous forte charge                                          |

### LIST OF TABLES

| Table 1 – Summary of popular scheduling algorithms.    38                          |

|------------------------------------------------------------------------------------|

| Table 2 – List of IPC abstractions and primitives commonly found in OSes.       42 |

| Table 3 – Common operations on files.    42                                        |

| Table 4 – Distributed OSes for network environments vs LW Manycore.       58       |

| Table 5 – Interface exposed by the Core Abstraction Layer.    73                   |

| Table 6 – Interface exposed by the Cluster Abstraction Layer.    74                |

| Table 7 – Interface exposed by the Processor Abstraction Layer.    74              |

| Table 8    – Experimental programs used for assessing Nanvix                       |

| Table 9 – Performance of memory management protocols.    110                       |

| Table 10 – Performance of process management protocols.    120                     |

| Table 11 – Design space for cores in OpTiMSoC.    149                              |

| Table 12 – Programas experimentais usados para avaliar Nanvix       164            |

| Table 13 – Programmes expérimentaux utilisés pour évaluer Nanvix       18'         |

|                                                                                    |

### TABLE OF CONTENTS

| 1     | INTRODUCTION                                                 | 17 |

|-------|--------------------------------------------------------------|----|

| 1.1   | Motivation                                                   | 18 |

| 1.2   | Problem                                                      | 19 |

| 1.3   | Goals                                                        | 20 |

| 1.4   | Contributions                                                | 20 |

| 1.5   | Thesis Outline                                               | 21 |

| 2     | BACKGROUND                                                   | 23 |

| 2.1   | Single-Chip Manycore Processors                              | 23 |

| 2.1.1 | Manycore Accelerators                                        | 24 |

| 2.1.2 | Manycore Processors                                          | 25 |

| 2.1.3 | Lightweight Manycore Processors                              | 26 |

| 2.2   | Runtime Systems for Parallel and Distributed Programming     | 28 |

| 2.3   | Operating Systems                                            | 29 |

| 2.3.1 | Overview                                                     | 29 |

| 2.3.2 | Operating System Construction                                | 30 |

| 2.3.3 | Memory Management                                            | 32 |

| 2.3.4 | Process Management                                           | 37 |

| 2.3.5 | File System Management                                       | 42 |

| 2.4   | Distributed Systems                                          | 46 |

| 2.4.1 | System Architecture                                          | 47 |

| 2.4.2 | Communication                                                | 48 |

| 2.4.3 | Coordination                                                 | 49 |

| 2.4.4 | Replica Management                                           | 53 |

| 2.4.5 | Data Consistency                                             | 54 |

| 2.5   | Lightweight Manycores and Distributed Operating Systems      | 56 |

| 3     | RELATED WORK                                                 | 59 |

| 3.1   | Runtime Systems for Single-Chip Manycore Processors          | 59 |

| 3.1.1 | Vendor Specific Libraries                                    | 59 |

| 3.1.2 | Templates Programming Libraries                              | 60 |

| 3.1.3 | Message Passing Interface (MPI) Libraries                    | 60 |

| 3.1.4 | Partitioned Global Address Space (PGAS) Libraries            | 61 |

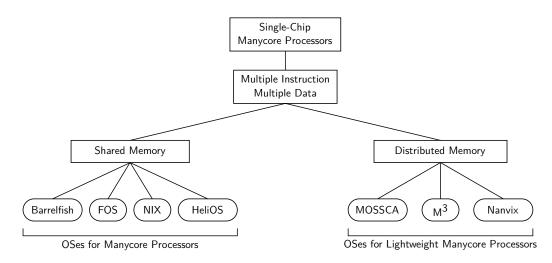

| 3.2   | <b>Operating Systems for Single-Chip Manycore Processors</b> | 61 |

| 3.2.1 | Operating Systems for Manycore Processors                    | 62 |

| 3.2.2 | Operating Systems for Lightweight Manycore Processors        | 64 |

| 3.3   | Discussion                          |

|-------|-------------------------------------|

| 4     | THE NANVIX OPERATING SYSTEM         |

| 4.1   | Design Requirements and Goals       |

| 4.2   | System Overview                     |

| 4.3   | Hardware Abstraction Layer          |

| 4.3.1 | Design Goals                        |

| 4.3.2 | Overview                            |

| 4.3.3 | Core Abstraction Layer              |

| 4.3.4 | Cluster Abstraction Layer           |

| 4.3.5 | Processor Abstraction Layer         |

| 4.4   | Asymmetric Microkernel              |

| 4.4.1 | Design Goals                        |

| 4.4.2 | Overview                            |

| 4.4.3 | Memory System Module                |

| 4.4.4 | Thread System Module    78          |

| 4.4.5 | Inter-Kernel Communication Facility |

| 4.5   | System Services                     |

| 4.5.1 | Design Goals                        |

| 4.5.2 | Overview                            |

| 4.5.3 | Process Management Fleet            |

| 4.5.4 | Memory Management                   |

| 4.5.5 | File Management    93               |

| 4.6   | Libraries and Runtimes              |

| 4.7   | Implementation Insights             |

| 4.8   | Concluding Remarks                  |

| 5     | EVALUATION METHODOLOGY 101          |

| 5.1   | Evaluation Goals                    |

| 5.2   | Experimental Programs               |

| 5.2.1 | Synthetic Programs                  |

| 5.2.2 | System Utilities                    |

| 5.2.3 | Scientific Programs                 |

| 5.3   | Experimental Platform               |

| 5.4   | Evaluation Methods                  |

| 6     | EXPERIMENTAL RESULTS                |

| 6.1   | Communication System                |

| 6.1.1 | Programmability and Portability     |

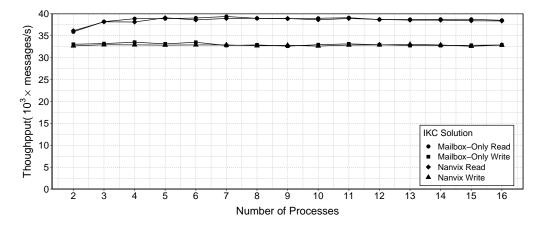

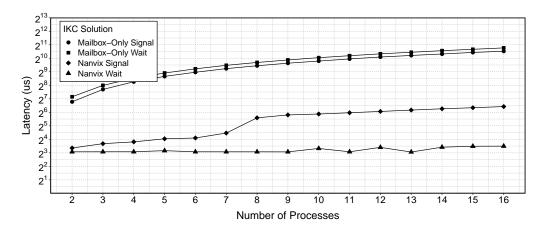

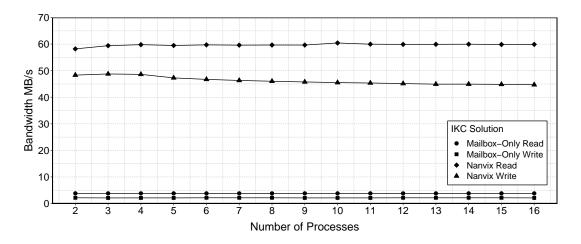

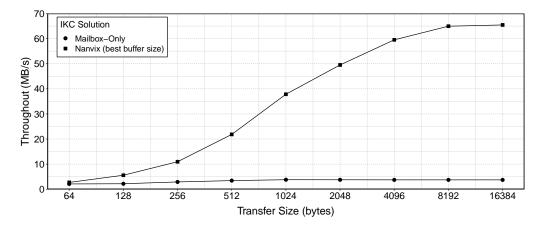

| 6.1.2 | Performance                         |

| 6.2        | Memory System                                    |

|------------|--------------------------------------------------|

| 6.2.1      | Programmability and Portability                  |

| 6.2.2      | Performance                                      |

| 6.3        | Process System                                   |

| 6.3.1      | Programmability and Portability                  |

| 6.3.2      | Performance                                      |

| 6.4        | User Applications                                |

| 6.4.1      | System Utilities                                 |

| 6.4.2      | Scientific Programs                              |

| 6.5        | Concluding Remarks                               |

| 6.5.1      | Programmability and Portability with Nanvix      |

| 6.5.2      | Performance in Nanvix                            |

| 7          | CONCLUSIONS                                      |

| 7.1        | Contributions                                    |

| 7.1.1      | Scientific Contributions                         |

| 7.1.2      | Technical Production                             |

| 7.1.3      | Academic Supervisions                            |

| 7.2        | Future Works                                     |

|            | REFERENCES                                       |

|            | APPENDIX A – SUPPORTED PLATFORMS 145             |

| A.1        | QEMU                                             |

| A.2        | Unix Simulator                                   |

| A.3        | MPPA-256 Bostan                                  |

| A.4        | <b>OpTiMSoC</b>                                  |

|            | APPENDIX B – EXTENDED ABSTRACT IN PORTUGUESE 151 |

| <b>B.1</b> | Introdução                                       |

| B.1.1      | Motivação                                        |

| B.1.2      | Problema                                         |

| B.1.3      | Objetivos                                        |

| B.1.4      | Contribuições                                    |

| <b>B.2</b> | Referencial Teórico                              |

| B.2.1      | Processadores Manycore Single-Chip               |

| B.2.2      | Ambientes de Execução                            |

| B.2.3      | Sistemas Operacionais                            |

| B.2.4      | Sistemas Distribuídos                            |

| <b>B.3</b> | Trabalhos Relacionados                           |

| <b>B.4</b> | O Sistema Operacional Nanvix                     |

| <b>B.4.1</b> | Objetivos de Projeto                     |

|--------------|------------------------------------------|

| B.4.2        | Arquitetura do Sistema                   |

| <b>B.5</b>   | Metodologia de Avaliação                 |

| B.5.1        | Programas de Experimentação              |

| B.5.2        | Plataforma Experimental                  |

| B.5.3        | Projeto Experimental                     |

| <b>B.6</b>   | Resultados Experimentais                 |

| B.6.1        | Programabilidade e Portabilidade         |

| B.6.2        | Desempenho de Utilitários de Sistema     |

| <b>B.7</b>   | Conclusões                               |

| B.7.1        | Contribuições Científicas                |

| B.7.2        | Produção Técnica                         |

|              | APPENDIX C – EXTENDED ABSTRACT IN FRENCH |

| C.1          | Introduction                             |

| C.1.1        | Motivation                               |

| C.1.2        | Problème                                 |

| C.1.3        | Contributions                            |

| C.2          | Background                               |

| C.2.1        | Processeurs à puce unique Manycore       |

| C.2.2        | Environnements d'exécution               |

| C.2.3        | Systèmes Opérationnels                   |

| C.3          | Travaux Connexes                         |

| C.4          | Le système d'Exploitation Nanvix         |

| C.4.1        | Objectifs du Projet                      |

| C.4.2        | Architecture du Système                  |

| C.5          | Méthodologie d'évaluation                |

| C.5.1        | Programmes d'expérimentation             |

| C.5.2        | Plateforme expérimentale                 |

| C.5.3        | Conception expérimentale                 |

| C.6          | Résultats expérimentaux                  |

| C.6.1        | Programmabilité et portabilité           |

| C.6.2        | Performances des utilitaires système     |

| C.7          | Conclusion                               |

| C.7.1        | Contributions scientifiques              |

| C.7.2        | Production Technique                     |

#### **1 INTRODUCTION**

The scientific and industry communities are constantly seeking and developing solutions to address the ever-increasing performance demands of software applications. These solutions are often tailored to particular intricacies of a target application and platform, and they range from the software-level and compiler support (KAMIL et al., 2010), to the runtime system (BROQUEDIS et al., 2010) and the underlying hardware architecture (DINECHIN et al., 2013). In this way, specialized techniques may be applied and thus cutting-edge performance achieved.

On the one hand, in software-level, programming techniques are employed to optimally handle domain-specific properties (FRANCESQUINI et al., 2015). For instance, in graph-traversal applications, fine-grain locking schemes are widely employed to enable maximum concurrency and parallelism to the graph itself (MERRILL et al., 2012). Alternatively, in N-Body Simulations, density-guided domain decomposition is often used to minimize load imbalance, exploit data locality and enable faster simulation algorithms to be applied (BARNES; HUT, 1986). On the other hand, at compile time, code optimizations are employed, so that execution time, memory footprint and power usage are tuned. Some techniques such as Instruction Scheduling and Auto-Vectorization are architecture dependent and thus are required to be employed for extracting maximum performance from the hardware. In contrast, other techniques such as Register Allocation and Loop Unrolling are architecture independent, but they may significantly increase instruction throughput in a portable fashion.

Performance improvements in the runtime system level target challenges on the interactions between the application and the underlying platform. For instance, to overcome communication overheads, thread mapping heuristics (CRUZ et al., 2014), data placement techniques (DIENER et al., 2016) and asynchronous communication primitives (PASCOLO et al., 2016) are often employed. In this way, communication latencies between threads may be mitigated and overlapped with computation. Alternatively, to address processing heterogeneity and inherent load imbalance, runtime systems heavily rely on scheduling strategies (AUGONNET et al., 2011). Most often, these features are exported through a framework or an Application Programming Interface (API), and hence may be seamlessly invoked by applications (GROPP et al., 1996; DAGUM; MENON, 1998).

Finally, in hardware-level, tailored approaches are adopted to push even further performance bounds. To improve instruction throughout in a single core, techniques such as Instruction Pipelining, Superescalar Out of Order (OoO) execution and Very Long Instruction Word (VLIW) are widely used. Alternatively, thread-level parallelism and code acceleration are tackled with application-specific architectural solutions, such as multicore and manycore processors, Graphics Processing Unit (GPU), and more recently manycores and Field Programmable Gate Array (FPGA). Finally, there are solutions such as distributed memory architecture and Network-on-Chip (NoC) to enable a massive scalability on the number of cores in a single chip. Specifically on the hardware-level efforts, Lightweight Manycore (LW Manycore) processors (ISHII et al., 2017) emerged as a promising alternative to deliver performance scalability with low-power consumption. To enable these features, these processors rely on a selected set of architectural characteristics:

- They are designed to cope with Multiple Instruction Multiple Data (MIMD) workloads.

- They integrate up to thousands of low-power cores in a single chip.

- They have their cores disposed in tightly-coupled groups called clusters.

- They feature a distributed memory architecture with multiple address spaces.

- They present a constrained memory, with small (few kB per core) and private local memories.

- They rely on NoC for fast and reliable message-passing communication.

- They have a heterogeneous configuration in terms of I/O and/or computing capabilities.

Some industry-successful examples of LW Manycore are the Kalray MPPA-256 (DINECHIN et al., 2013), the PULP (ROSSI et al., 2017), and the Sunway SW26010 (ZHENG et al., 2015), being the latter employed in Sunway TaihuLight (FU et al., 2016), currently the fourth most powerful supercomputer in the world, according to TOP500 raking<sup>1</sup>.

#### 1.1 Motivation

While a unique set of architectural features grant to LW Manycore high-performance and energy efficiency, they also introduce multiple challenges in programmability and software portability. First, the *high density circuit integration* turns dark silicon into reality (HAGHBAYAN et al., 2017). If all the cores of such type of a processor are powered on at the same time, the output heat cannot be effectively dissipated and the hardware may malfunction. Therefore to tackle this physical barrier, software is required to implement thermal-aware scheduling strategies.

Second, the *distributed memory architecture* leads to a non-trivial software design. To access and manipulate data across multiple physical address spaces, software should explicitly fetch/offload data from remote memories to local ones (FRANCESQUINI et al., 2015). Furthermore, the *small amount of on-chip memory* requires the software to partition its working data set into chunks and decide which chunks should be kept local and which should be offloaded to memory, at a given time. Furthermore, to achieve this efficiently, software should handle by its own data caching, replication and prefetching (CASTRO et al., 2016).

Third, the *on-chip interconnect* invites engineers to embrace a message-passing programming model and thus work on significant refactor on their software (SOUZA et al., 2017). Additionally, hardware exposes mechanisms for asynchronous programming and explicit message

<sup>&</sup>lt;sup>1</sup> Available at: <https://www.top500.org>.

routing, which engineers should also handle. The former is a fundamental requirement when aiming at communication and computation overlapping (HASCOËT et al., 2017). The latter should be strongly considered in order to guarantee uniform communication latencies (DINECHIN et al., 2014).

Finally, the *on-chip heterogeneity* makes the deployment of applications in LW Manycore complex (BARBALACE et al., 2015). On the one hand, clusters of LW Manycore may feature different processing capabilities, and thus processor allocation should account for this factor, in order to extract the most of hardware. Allocating a cluster to a process that will not make use of all the hardware features that are available may negatively impact the overall system performance. On the other hand, clusters may also differ in respect to their connectivity to external devices, and thus application placement should also consider this aspect.

#### 1.2 Problem

There are two main approaches for addressing software programmability and portability challenges in an architecture: baremetal runtime systems and Operating Systems (OSes). The first aims to expose a programming environment of top of the hardware to address the needs of a specific architecture (HO et al., 2015; Mohr; Tradowsky, 2017). In contrast, the second approach craves to bridge intricacies of the hardware in a broader sense, by exposing rich abstractions and programming interfaces, as well as handling resource allocation, sharing and multiplexing.

In the context of LW Manycore processors, unfortunately as of today, neither of the two previous approaches provide a complete solution to tackle programmability and portability challenges. On the one hand, existing baremetal runtime systems that aim these emerging processors (VARGHESE et al., 2014; RICHIE; ROSS; INFANTOLINO, 2017) inherently lack on covering all the issues that we stated in previously (Section 1.1). For instance, some runtime systems do provide rich abstractions to tackle on-chip communication (DINECHIN et al., 2013; AUBRY et al., 2013; HO et al., 2015), but overlook challenges that concern the distributed memory architecture. On the other hand, existing OSes do not to cope with architectural intricacies of LW Manycore as follows.

a) At the one end of the spectrum, centralized OSes intrinsically face important barriers:

- They have scalability problems (WENTZLAFF; AGARWAL, 2009).

- They do not cope with increasingly diverse hardware (BARBALACE et al., 2015).

- They are not feasible for the context due to the small amount of on-chip memory.

- b) On the other end of the spectrum, distributed OSes miss some architectural constraints of LW Manycore processors (PENNA et al., 2021), and thus it is not possible to deploy these OSes in the aforementioned architectures without a complete redesign and/or significant changes to their source code. The rationale for this lies in the following points:

- They do not rely on a decentralized view of the hardware. For instance, they assume that hardware resources are visible to all cores of the underlying processor.

- Although they do feature a distributed software organization, they do not cope with the multiple physical address spaces. They rely on shared memory areas to either transfer software messages and move data from one core to another.

- They do not have as one of their primary constraints their memory footprint, and thus inherently do not cope with small on-chip memories of LW Manycore.

- They overlook rich the on-chip interconnects and do not exploit additional features that are often available in LW Manycore, such as asynchronous message passing through Direct Memory Access (DMA) and message routing.

Based on these observations, we formulate the following problem, which remains unanswered by the state-of-the-art in Operating Systems:

How to design an operating system so as to address programmability and portability issues in lightweight manycore processors?

#### 1.3 Goals

Seeking for an answer to the previously stated problem, the main goal of this thesis boils down to *bridge architectural characteristics of lightweight manycore processors*. To this end, we propose a novel distributed OS that specifically aims the following:

- *Programmability*: to provide rich system abstractions for LW Manycore, such as process, files, virtual memory and communication primitives; as well as to enable resource sharing, multiplexing and isolation in these emerging architectures.

- *Portability*: to expose standard programming interfaces so as to enable existing software to be ported to LW Manycore processors.

#### 1.4 Contributions

The main contribution of this thesis is a distributed OS that advances the resource management in LW Manycore processors. On the one hand, from the scientific perspective this main contribution may be unfolded in following specific contributions:

• A comprehensive Hardware Abstraction Layer (HAL) for LW Manycore (PENNA; FRAN-CIS; SOUTO, 2019) that: (i) bridges architectural differences across multiple architectures; and (ii) cope with key issues that are often encountered when designing an OS for these processors. With this abstraction layer, the development and deployment of a fully-featured OS becomes easier not only to a particular LW Manycore, but also the portability of an OS itself across multiple of these processors.

- A rich memory management approach that is based on a Distributed Paging System (DPS). This is a novel solution that we devised for managing memory of a LW Manycore processor and it works as follows. The local memories of a LW Manycore processor are considered page caches that can store data of whichever processes. Based on this, the OS manages this page cache by: (i) placing those pages that are being heavily used by a process in local memories; and (ii) swapping out those pages that are not used by a process to remote memories. Overall, this solution enables transparent data accessing and manipulation, as well as data sharing and coherence in LW Manycore. We believe that these issues are importantly related to programmability and portability challenges that we aim at overcoming.

- A lightweight communication facility that manages the on-chip interconnect and exposes rich primitives (PENNA et al., 2021). Overall, this facility exposes three communication abstractions: (i) syncs, for enabling a process to signal and unlock another process remotely; (ii) mailboxes, for sending fixed-size messages with low latency; and (iii) portals, for handling dense data transfers with high bandwidth. This communication infra-structure effectively enables the efficient implementation of our OS.

On the other hand, we highlight that this thesis also introduces an important technical contribution to the community:

Nanvix, a concrete implementation of an OS that features the aforementioned scientific advancements for LW Manycore processors. Nanvix supports multiple architectures (i.e., k1b, x86, OpenRISC, ARMv8 and RISC-V), runs on silicon LW Manycore processors, as well as it exposes rich abstractions and high-level programming interfaces.

#### 1.5 Thesis Outline

The remaining chapters of this thesis are organized as follows:

- Chapter 2 reviews the background of this work. We cover single-chip many core processors and precisely highlight the unique features of LW Manycore processors. We present an overview of the main aspects related to the design of OSes. We discuss about principles and problems in distributed systems.

- Chapter 3 discusses related work. We discuss about runtime systems and how they improve

programmability by exposing API for narrowed domains. We present existing OSes for

manycore processors and how they leverage software development in these architectures.

We argue on what points these solutions lack for answering the problem stated in this thesis,

and we summarize why our work advances the state-of-the-art on the programmability and

portability of LW Manycore.

- Chapter 4 details the design of Nanvix and discusses how it addresses the programmability and portability challenges of LW Manycore.

- Chapter 5 presents the evaluation methodology that we employed to evaluate our OS. We relied on an experimental-based approach based on synthetic programs, system utilities and scientific programs.

- Chapter 6 presents and discuss the experimental results that we obtained. We evaluated several aspects of Nanvix in Kalray MPPA-256, a 288-core silicon LW Manycore processor.

- Chapter 7 presents our conclusions and perspectives for future works. We highlight the contributions of this thesis, as well as we stress three main follow-up research topics: kernel bypassing, process migration and hardware/software co-design.

- Appendix A presents an overview discussion on the platforms that are currently supported by Nanvix. We give insights on architectural intricacies of each of these platforms and how Nanvix was designed to cope with this challenges.

#### 2 BACKGROUND

In this chapter we cover the foundations of our thesis. First, we take an in-depth look on single-chip manycore architectures and their main characteristics (Section 2.1). Next, we introduce runtime systems (Section 2.2). Then, we discuss about OSes (Section 2.3) and brief about distributed systems (Section 2.4). Finally, we conclude this chapter by positioning our work on this ground (Section 2.5).

#### 2.1 Single-Chip Manycore Processors

During the past decades, performance improvements of computing platforms were mostly driven by techniques that aimed to increase instruction throughput in a single Central Processing Unit (CPU) (FRANCESQUINI et al., 2015). On the microarchitecture level, superescalar pipelines and speculative execution heuristics were employed to boost execution streaming. Conversely, on the electronic level, operating frequency increase was applied to effectively accelerate instruction execution. Unfortunately however, these techniques rapidly reached a scalability barrier on the material level known as the *Power Wall* (CASTRO et al., 2016). This problem comes down to the fact that instruction throughput in a single CPU cannot increase indefinitely because the output heat cannot be dissipated out of the circuit. As a side effect, the temperature of the processor sharply increases thus causing it to first malfunction and eventually get damaged.

Parallel processors were introduced to overcome this physical barrier. Instead of turning up instruction throughput in a single CPU, the alternative idea was to increase the actual number of cores in a CPU. This way, multiple execution streams could run at the same time, and thread level parallelism could be exploited to achieve performance scalability in an application. In this context, a well known categorization was proposed by Flynn (FLYNN, 1972), in which architectures may be grouped according to their instruction and data streams:

- Single Instruction Single Data (SISD): a single processor executes a single instruction stream to operate on data stored in a single memory.

- Single Instruction Multiple Data (SIMD): a single machine instruction controls the simultaneous execution of a number of processing elements on a lockstep basis. Each processing element has an associated data memory, so that each instruction is executed on a different set of data by the different processors.

- Multiple Instruction Single Data (MISD): a sequence of data is issued to a set of processors, each of which executes a different instruction sequence.

- MIMD: a set of processors simultaneously execute different instruction sequences on different data sets.

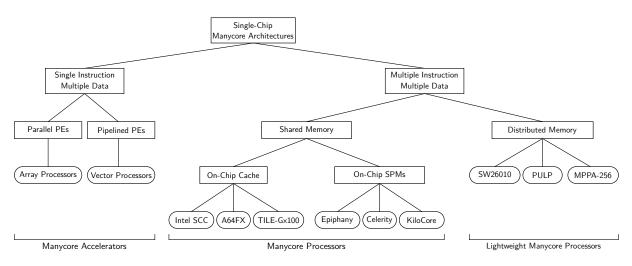

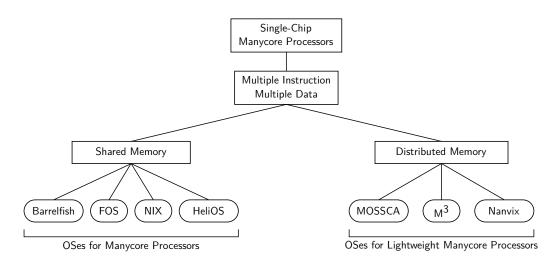

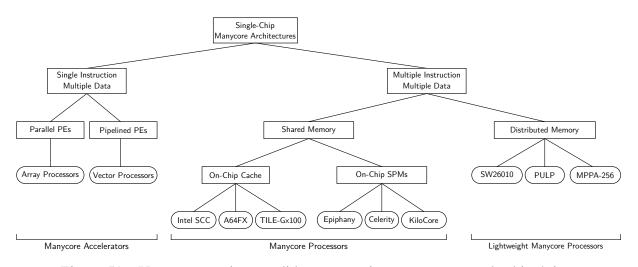

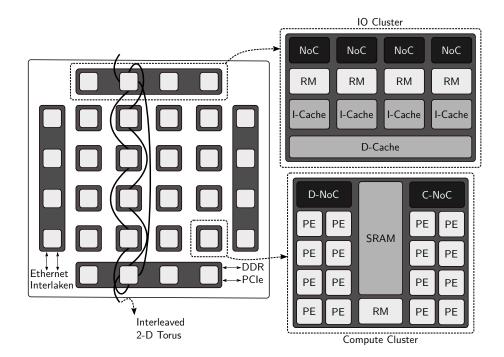

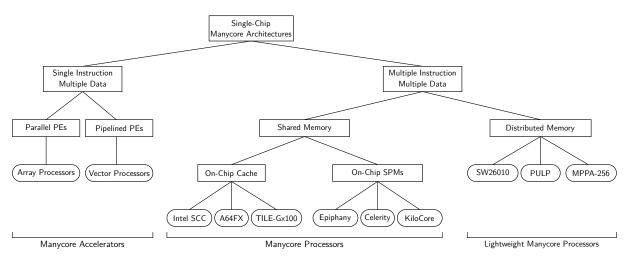

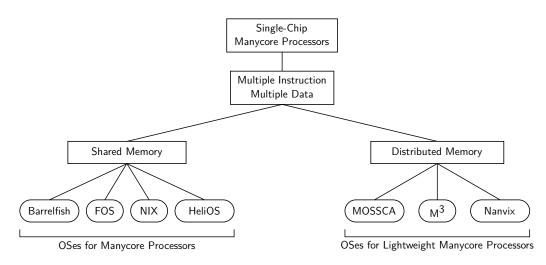

Figure 1 – An extended taxonomy for single-chip manycore architectures.

Despite the fact of being a solid taxonomy, with the recent increase of cores in architectures, one could also argue on extra architectural characteristics that may be accounted to categorize single-chip manycore processors. This extended classification is outlined in Figure 1 and it adds to Flynn's approach aspects concerning the memory system of single-chip manycore architectures. Based on this additional characteristic, we highlight three organizations that are relevant to the understanding of this thesis: *manycore accelerators, manycore processors* and *LW Manycore processors*. In the next sections, we present and discuss each of these classes.

#### 2.1.1 Manycore Accelerators

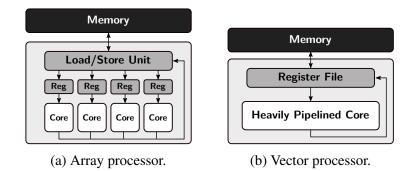

Manycore accelerators were the first class of single-chip manycore processors to arise. They comprise those architectures that are narrowed for specific workloads, such as vector processing, computer vision and artificial intelligence. Overall, manycore accelerators often feature a SIMD organization and for this reason are often coupled to a general purpose processor to construct a heterogeneous system. Among manycore accelerators, we highlight two subclasses that differ in the way cores are organized: *array processors* and *vector processors*. These two approaches are outlined in Figure 2 and discussed next.

Array processors have several cores attached to a shared control unit and a common wide register file (a.k.a. vector register). All cores have the same internal configuration, but each of them operate on a different subword of the vector register. Figure 2a shows the execution flow for a set of instructions in an array processor. In this example, there are four different cores executing one instruction on a vector register file. At each clock cycle, all cores execute the same instruction, but each of them operate on a different range of the vector register. Array processors have the major advantage of being easy to implement, but at the same time, they face a limitation on the bit-width of operands. Typically, array processors are embedded in the same package of general purpose architectures, to accelerate some specific workloads such as those from multimedia domain (PELEG; WEISER, 1996). Some examples of standalone manycore accelerators of this subclass are discussed by (ISHIGAKI et al., 2015) and Shi (SHI et al., 2014).

Figure 2 – Manycore accelerators.

Vector processors take an orthogonal approach to array processors. Instead of implementing SIMD instructions with an array of identical cores and a vector register, vector processors bundle in the same chip several stream cores, each of which featuring several specialized functional units that run micro-operations on a vector throughout multiple consecutive cycles. With this alternative organization, the length of vector operands not only may be arbitrarily large, but also may they dynamically change. The execution flow in a vector processor is presented in Figure 2b. Some examples of vector processors are Nvidia Pascal (FOLEY; DANSKIN, 2017) and ARA (CAVALCANTE et al., 2020)

#### 2.1.2 Manycore Processors

Manycore processors address the general-purpose High Performance Computing (HPC) domain and are often used as basic building blocks for supercomputers. These processors feature a shared memory system in which all cores may transparently read/write using common load/store instructions. Ultimately, manycore processors do not require great programming paradigm shifts and thus are currently the most known class among single-chip manycore architectures. Some examples of manycore processors are Intel Single-Cloud Computer (HOWARD et al., 2011), Tilera TILE-Gx100 (RAMEY, 2011), Adapteva Epiphany (OLOFSSON; NORDSTROM; UL-ABDIN, 2014), Celerity (DAVIDSON et al., 2018), Fujitsy A64FX (YOSHIDA, 2018) and Manticore (ZARUBA; SCHUIKI; BENINI, 2020).

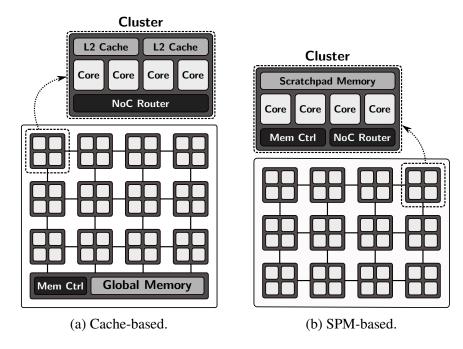

Specifically concerning manycore processors, we highlight two different organizations that are often embraced. The first one is presented in Figure 3a. In this organization, cores are physically grouped in physical units called clusters (or tiles), which are altogether interconnected with the global shared memory system through a NoC. Cores in the same cluster are tightly coupled to a local memory controller, a local cache and a NoC router. Memory controllers enable transparent access to the global shared memory by forwarding load/store requests through the NoC. Furthermore, these memory controllers also provide cache coherence support, by either implementing it in hardware or exposing special instructions that enable this in software-level.

Figure 3b outlines a second organization for a manycore processor. Likewise in the previous approach, in this one cores are grouped into clusters which are interconnected through a NoC. Differently however, the memory system does not rely on a caching scheme. Instead, cores

Figure 3 – Manycore processors.

in the same cluster share access to a local Scratchpad Memory (SPM) module. Moreover, the global address space is this statically partitioned across the several SPM and memory controllers forward remote memory accesses to the concerning SPM module.

Both organizations have their own advantages and disadvantages. On the one hand, cachebased manycore processors often feature larger physical address spaces than their counterparts. This is because memory modules are disposed outside the chip, and thus they may be as large as possible. However, as drawback, cache coherence becomes the main performance bottleneck in the system, once the number of cores in this type of design increases. On the other hand, SPM-based manycore processors do not face scalability issues concerning coherency traffic, but they do have a much more limited address space, once all memory modules are disposed on-chip.

#### 2.1.3 Lightweight Manycore Processors

LW Manycore processors have an endeavor to deliver high performance with energy efficiency. To this end, they mostly rely on a distinguished set of architectural features. Overall, LW Manycore can be seen as "clusters on a chip" and present the following main characteristics:

- They are designed to cope with MIMD workloads.

- They integrate up to thousands of low-power cores in a single chip.

- They have their cores disposed in tightly-coupled groups called clusters.

- They feature a distributed memory architecture with multiple address spaces.

- They present a constrained memory, with small (few kB per core) and private local memories.

- They rely on NoC for fast and reliable message-passing communication.

- They have a heterogeneous configuration in terms of I/O and/or computing capabilities.

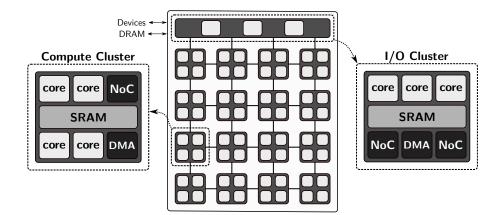

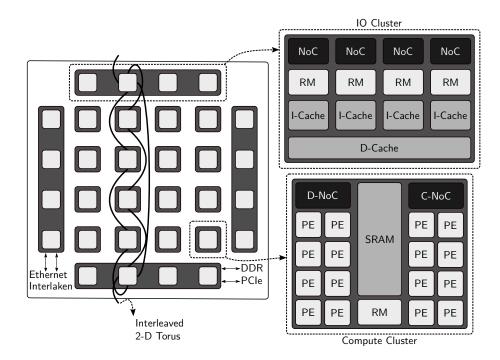

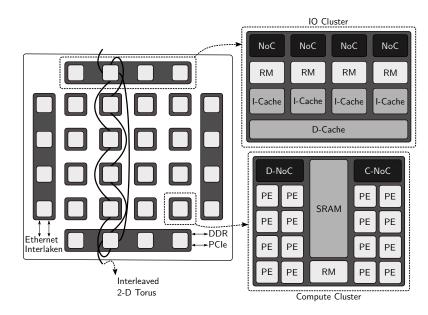

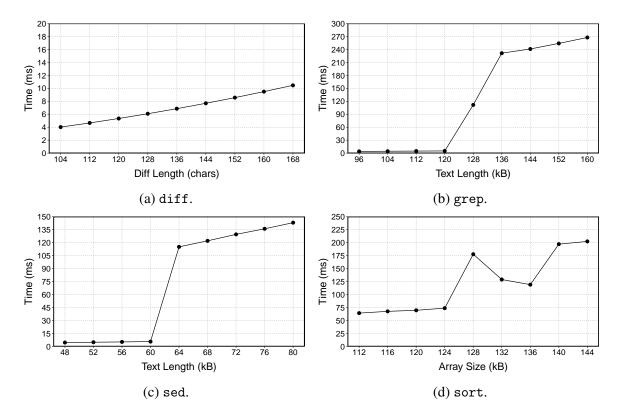

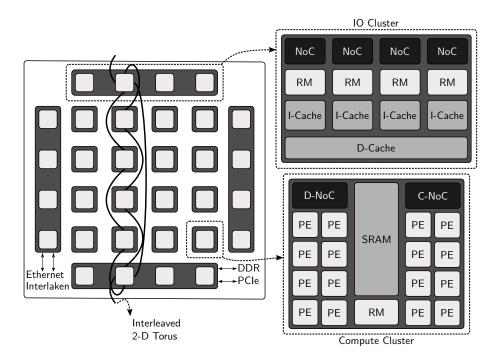

To exemplify these features, we consider a discussion on a concept processor (Figure 4). Noteworthy, this narrative applies to existing LW Manycore, such as PULP (ROSSI et al., 2017), Kalray MPPA-256 (DINECHIN et al., 2013) and Sunway SW26010 (ZHENG et al., 2015). This concept processor integrates 67 cores grouped into 17 clusters. In a cluster, cores share some local hardware resources, such as a Static Random Access Memory (SRAM) and NoC interfaces, and have uniform access latencies to these components. Clusters may have different characteristics, like processing power, local memory sizes, and communication capabilities, to better address different computing needs. For instance, in this concept processor, there are 16 Compute Clusters having 4 cores each and that are meant for computing workloads. In contrast, the I/O Cluster features connectivity to external devices as well as two NoC interfaces, thereby being intended to handle IO workloads.

Clusters have different address spaces, and they may communicate with one another by explicitly exchanging hardware-level messages through the NoC. Therefore, to write to external devices and the Dynamic Random Access Memory (DRAM) attached to the I/O Cluster, Compute Clusters must tile in software the output data into hardware-level messages and transfer them through the NoC to the I/O Cluster. Conversely, if two threads running on different Compute Cluster want to exchange information, they should do the same.

So far in this chapter, we discussed about sing-chip manycore processors and highlighted how LW Manycore processors are positioned in this context. In the next sections, we unveil software-related aspects that concern this thesis. First, we present an overview of runtime systems for parallel and distributed programming, which are often found in LW Manycore. Then, we cover the background on OSes and distributed systems, which we believe that are the key to enable rich resource management of LW Manycore. Finally, in the end of this chapter, we conclude about the aspects of OSes and distributed systems that are relevant for addressing portability and programmability in LW Manycore.

Figure 4 – A LW Manycore processor with 67 cores.

#### 2.2 Runtime Systems for Parallel and Distributed Programming

Runtime systems provide rich programming environments for a particular execution model. To accomplish this, they expose specific API to applications; and they may interact directly with the hardware, OS and/or compiler. Some well-known examples of runtime systems are the crt0, the Android Runtime Environment (ART), and the Java Runtime Environment (JRE). These systems primarily enable a general-purpose programming environment for applications, by exposing routines and abstractions for manipulating resources such as data streams, software signals/exceptions and heap memory. Notwithstanding, in the context of this work, we next discuss about runtime systems that focus on manycore processors. Overall, the existing alternatives mostly concern parallel and distributed programming frameworks.

Parallel programming environments expose an infrastructure for applications to create, manipulate and synchronize multiple execution flows within a program. This way, an application may thoroughly exploit the performance that is provided by a parallel architecture. We highlight three environments that are often available for manycore architectures: POSIX Threads (PThreads), OpenMP (DAGUM; MENON, 1998) and OpenCL (MUNSHI, 2009). The first encapsulates an execution flow in an abstraction called *thread*, and it exposes a set of routines that enable applications to manipulate threads. The PThreads environment enables maximum flexibility in parallel programming and are typically available as a statically-linked library. Next, the OpenMP runtime focus on a transparent support for the fork-join parallel programming model. To this end, the runtime system interacts with the compiler infrastructure to enable the software engineer to annotate the source code in order to create parallel regions. Then, when building the application from an annotated source code, the compiler links low-level routines to spawn and terminate threads at the begin and end of a parallel region, respectively. Finally, the OpenCL environment aims at parallel programming in heterogeneous architectures. It defines a structure for writing programs where the application kernel executes in the OpenCL device, whereas the remainder portion of the code executes in the host device. To accomplish this, OpenCL works with the compiler infrastructure to generate code for both architectures, as well as it interacts with the hardware/OS to download/offload binary and data from/to the devices.

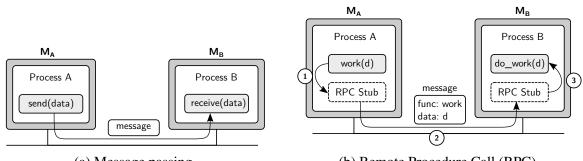

Distributed programming environments enable a complete exploitation of distributed architectures by focusing on providing communication abstractions between multiple computing nodes in a platform. We note two distributed programming environments that are typically encountered in manycore architectures: Message Passing Interface (MPI) (GROPP et al., 1996) and Partitioned Global Address Space (PGAS) (De Wael et al., 2015). The first exposes a set of routines that enable arbitrary data to be send/received using abstractions called messages. Messages can have a single or multiple recipients and may be send/received synchronously and/or asynchronously. On the other hand, PGAS enable one-sided communication by maintaining a global address space that is partitioned and spread across the several peers of the application. Peers may read/write data to this address space though special functions put/get, and the runtime system ensures that coherence is maintained.

#### 2.3 Operating Systems

An Operating System (OS) is a software layer that lies on top of baremetal hardware, manages computing resources and provides common services for programs. Without an OS, engineers would have to handle hardware intricacies by their own, thereby increasing software complexity and development cost. An OS has two important roles in a computing platform:

- (i) Abstract Resources: extend the functionalities of the hardware and expose to user programs services and rich API that are easier to deal with.

- (ii) Manage Resources: multiplex access to hardware and software resources, ensuring data protection and integrity, as well as enforcing administration protocols and policies.

In this section, we take an in-depth look on the fundamentals of OSes. First, we present an overview on the main components of an OS (Section 2.3.1). Then, we discuss about the internals of each of these component (Section 2.3.2 to Section 2.3.5).

#### 2.3.1 Overview

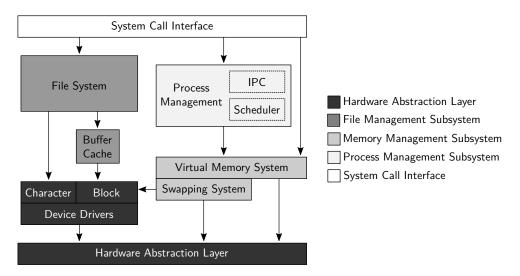

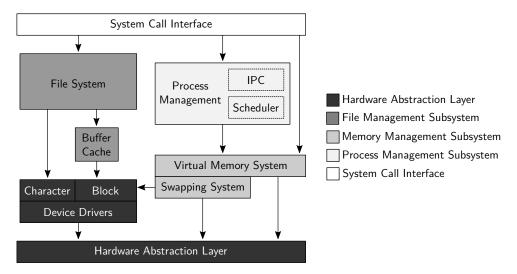

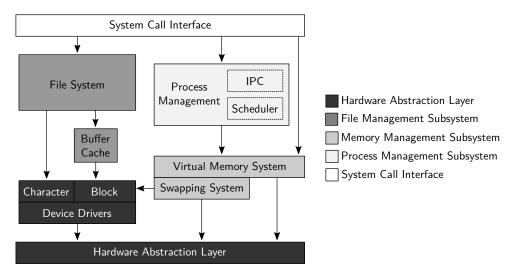

Figure 60 presents a schematic of an OS. It is composed by multiple components that interact with each other to provide rich resource abstraction and management. Noteworthy, there are many ways to couple these components. Therefore, in the following paragraphs we focus on discussing their roles, and in Section 2.3.2, we give insights on how they may be tighten together.

The HAL is the lowest-level component of an OS. It directly interacts with the hardware and exposes a common API for dealing with baremetal structures, such as interrupt vectors and Memory Management Unit (MMU) tables. The main role of this component is to hide as much as possible all hardware intricacies, as well as to provide a standard interface across multiple architectures. This way, the overlying OS components become less complex and easier to be ported from one hardware to another.

The Memory Management Subystem (MMS) provides a view of the underlying memory system. It typically does so by having two modules working together: the swapping and virtual memory modules. The first deals with paging, keeping in memory those pages that are more frequently used, and swapping out to secondary storage those that are not. The virtual memory system, on the other hand, relies on the paging module to enable advanced features such as shared memory regions, on-demand loading, lazy copying and page pinning. We further discuss the internals of a MMS in Section 2.3.3.

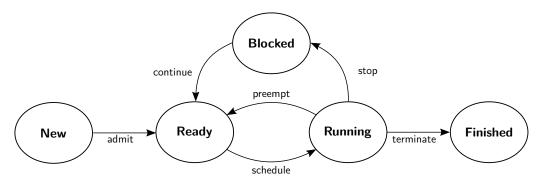

The Process Management Subsystem (PMS) handles all tasks that involves programs. To do this, it relies on an abstraction called process, which encapsulates the execution flow and the set of resources used by a program. Overall, the PMS exposes routines for creating, terminating and scheduling processes, as well as abstractions that allow processes to exchange information with one another and synchronize their activities. We present a detailed discussion of a PMS in Section 2.3.4.

Figure 5 – A possible architecture for an OS.

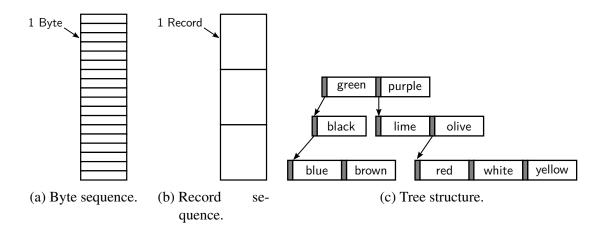

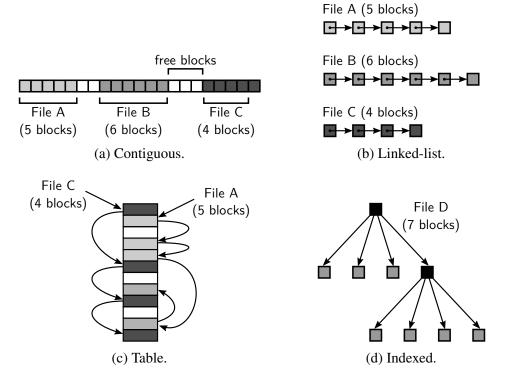

The File Management Subsystem (FSM) provides a uniform interface for programs to store and retrieve data from secondary data storage, as well as to manipulate hardware devices and software resources. To accomplish this, it creates and maintains the file abstraction. Files may be organized into directories, can be accessed through a unique pathname, and may be shared among several processes transparently. We discuss about this component in Section 2.3.5.

The system libraries lie on top of all the components and expose to user programs a collection of routines known as system calls. This is a well-defined interface in which user programs rely on to interact with the system. Overall, system libraries do not do much work than sanity checking parameters and ensuring protection. Typically, user libraries wrap around system libraries to provide interfaces and abstractions that are even more friendly to software engineers.

#### 2.3.2 Operating System Construction

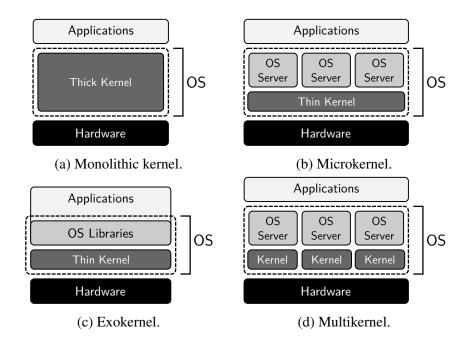

In the previous section we presented a possible structure for an OS, but indeed such systems may be constructed in several different ways. In a nutshell, the structure of an OS is defined by the way in which their different subsystems and components are disposed and interact. Each structure has its own advantages and disadvantages, and in the next paragraphs we cover the major aspects of the most popular variants.

In a monolithic kernel OS (Figure 6a), the system is built as a single component that provides most system functionalities and runs entirely in privileged mode. Subsystems are implemented as a collection of procedures and data structures which are linked altogether into a single and large executable binary. The major advantage of a monolithic kernel system lies in the simplicity of its implementation. However, since it is constructed as a single unit it faces from both poor fault tolerance and scalability problems (BOYD-WICKIZER et al., 2010). This approach is typically embraced by commodity OSes, such as GNU/Linux, BSD and Windows.

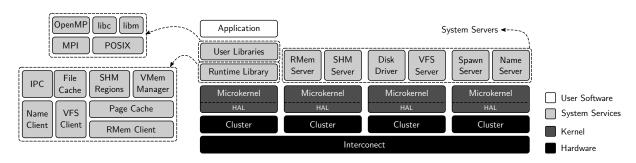

In contrast to monolithic kernels, microkernel OSes factor the system in multiple components, as it is outlined in Figure 6b. On the one hand, there is a kernel component that runs in privileged mode and ships bare minimum primitives for manipulating hardware resources (LIEDTKE, 1995). On the other hand, system servers run in unprivileged mode as stand alone programs and provide rich system functionalities, like process, memory and device management. A microkernel OS is challenging to implement, but it has two important advantages. First, it enforces a modular system structure, thereby improving fault tolerance and scalability. Second, it is flexible, because services may be narrowed to specific purposes, as well as multiple API and policies may coexist in the system. Examples of such OSes are L4 (LIEDTKE, 1995), Tornado (GAMSA et al., 1999) and K42 (APPAVOO et al., 2005).

Exokernel OSes take one step further towards minimalism and aim at a strong separation between security and abstraction. In this design (Figure 6c), the kernel is also the only software component that runs in privileged mode, but it does nothing more than partitioning the hardware and ensuring the secure multiplexing of these partitions(ENGLER; KAASHOEK; O'TOOLE, 1995). Unprivileged components run on top of these partitions and may either be user-applications, subsystems implementing common services or entire OSes. Exokernel OSes are complex to design, because their interface should be drawn so as to be comprehensive and flexible. The upside of this design lies on the fact that it enables programs to make efficient and intelligent use of hardware resources. Examples of exokernels are MIT's Exokernel (ENGLER; KAASHOEK; O'TOOLE, 1995) and Corey (BOYD-WICKIZER et al., 2008).

Multikernel OSes embrace a fully distributed design (Figure 6d). The system is factored in a set of independent OS kernels which are deployed across the cores of the underlying processor. These kernels communicate with one another via message-passing only; and they collaboratively implement traditional OS subsystems. Noteworthy, several designs for a multikernel are possible, once each OS kernel instance may follow either of the previous designs. The design and

Figure 6 – Popular architectures for an OS.

implementation of a multikernel OS stands outs in high complexity. However, from all the current approaches known for OS construction, it achieves higher scalability, and for this reason it is increasingly under research, in the context of multicore and manycore systems. The multikernel approach is embraced by Barrelfish (BAUMANN et al., 2009), FOS (WENTZLAFF; AGARWAL, 2009), MOSSCA (KLUGE; GERDES; UNGERER, 2014), M<sup>3</sup> (ASMUSSEN et al., 2016) and Nanvix (PENNA et al., 2019).

#### 2.3.3 Memory Management

In a computing system, memory is the resource that is intended to accommodate running programs. In this context, the role of the OS is to: (i) keep track of which parts of memory are in use; (ii) allocate memory to programs; (iii) multiplex memory among programs; (iv) ensure protection on portions of memory that are owned by a program. These tasks are carried out by the Memory Management Subystem (MMS), and their efficient accomplishment is essential for the overall performance of a system. To this end, the MMS relies on a special abstraction called memory partition, which models a portion of physical memory. On top of this, the MMS provides four mechanisms: partitioning, memory allocation, virtualization and reallocation. In the next sections, we take a look on each of these mechanisms.

#### **Partitioning**

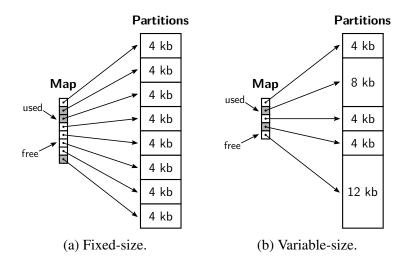

Partitioning comes down to dividing the physical memory in several sections, in order to either accommodate portions of running programs or programs themselves. Thanks to this mechanism, multiprogramming and virtualization are made possible. Overall, there are two approaches for partitioning: fixed-size partitions and dynamic partitioning. We outline these approaches in Figure 7 and detail them next.

In fixed-size partitioning, memory is statically divided into several sections that cannot grow nor shrink across execution. To keep track of partitions, the OS relies on a map data

Figure 7 – Memory partitioning techniques.

structure that records whether or not a partition is in use. Fixed-size partitioning eases memory allocation, but it introduces internal fragmentation. If a given partition is not entirely used, memory is wasted within a partition. In current architectures, fixed-size partitioning is natively supported by underlying hardware paging. Later in this section, we discuss how this technique is employed to implement paging.

In variable-size partitioning, memory is dynamically divided into several sections which can grow and shrink across execution. To keep track of variable size partitions, the OS relies on a map data structure that stores the location and size of partitions, as well as what is loaded into them. Variable size partitioning improves memory utilization, but it turns memory allocation into a more complex and expansive operation. In order to avoid external fragmentation (i.e., unused memory between partitions), the OS needs to constantly move partitions around and compact them. As a consequence, processor time is wasted. In current architectures, variable-size partitioning is natively supported by underlying hardware segments.

#### Allocation

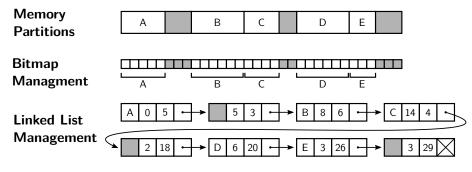

Memory allocation concerns the strategy that the OS uses to allocate memory partitions. This is triggered whenever a new program is launched or when a running program requests for memory. To manage memory allocation, two approaches are commonly used: bitmaps and linked lists. These are outlined in Figure 8 and detailed in the next paragraphs.

The bitmap approach relies on an array of bits to keep track of which memory partitions are in use and which are free. With this representation, allocation of a single partition is straightforward: find the bit in the bitmap that is unset, set it to one and return the corresponding partition. Conversely, deallocation comes down to finding the corresponding bit in the bitmap and clearing it to zero. Bitmaps are suitable for managing fixed-size partitions and handling requests one at a time. In this scenario, the allocation procedure takes linear time, whereas the deallocation step takes constant time. Unfortunately however, if memory partitions have dynamic size the bitmap structure is not enough for storing the required information. Furthermore, if multiple partitions should be allocated at once, the complexity of this operation increases substantially, because the bitmap would need to be traversed several times to find a suitable place for allocation.

Memory management with linked lists is more adequate when either variable partitions

Figure 8 – Memory allocation techniques.

are in use or allocation requests have arbitrary sizes. In this alternative approach, the idea is to maintain a linked-list that stores in the information about free partitions, such as its base address and size. At system startup, this structure has a single node which starts at address zero and spans over the whole memory. Then, when an allocation is requested: (i) the list is searched for a free partition that is large enough; and (ii) the selected partition is resized accordingly.

On the other hand, when a partition is released, it is put back into the linked-list. Noteworthy, since allocation requests may have arbitrary sizes and partitions are resized during this operation, partitions that are too small are likely to appear in the linked list of free partitions. As a consequence, over the time, there will not be enough large partitions to fulfill allocation requests and the system starves. This problem is known as fragmentation and may be mitigated by coupling two orthogonal approaches. First, whenever a partition is released and is about to be placed backed in the linked list of free partitions, the memory allocator may attempt to merge unused partitions into larger ones. To this end, the system checks if either of the adjacent partitions are free, and if so it merges then. Second, when allocating partitions a suitable strategy may be employed, depending on the load characteristics in which the system is subjected. Some popular strategies are discussed below.

- **First-Fit** The first memory partition that is large enough to fulfill the allocation request is returned. This favors performance and generates large fragments in average.

- **Best Fit** The memory partition that best fulfills the request is returned. This has a slightly worse performance than First-Fit and generates small fragments in average.

- **Quick Fit** Free memory partitions are hierarchically grouped into sublists according to their size. When a memory partition is requested, the concerned list is searched. Noteworthy, each sublist may have its own allocation policy. Overall, quick fit delivers the best performance but it imposes extra complexity for merging free partitions.

# Virtualization

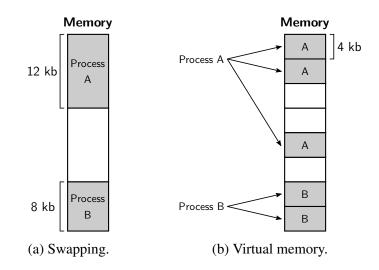

Virtualization enables programs to address more memory than there is physically available. To this end, the OS uses non-volatile storage devices to temporarily store unused memory portions of programs. There are two main approaches for virtualization, namely swapping and virtual memory. Both are outlined in Figure 9 and discussed in the next paragraphs.

In swapping, programs are placed in their entirety in physical memory and swapped back and forth from/to non-volatile storage. When a new program is launched, the OS first scans the physical memory for some unused partition that is large enough to accommodate the program. If such a partition can be promptly allocated, the new program is stored there and it starts executing. Otherwise, the new program is placed in the non-volatile storage until further space in physical memory becomes available. Later on during execution, whenever a running program gets preempted or terminates, the OS searches the non-volatile storage for another program to be brought into physical memory.

Figure 9 – Memory virtualization techniques.

The main advantage of swapping lies on its simplicity. No special hardware is required, although current architectures do leverage swapping support with segment registers. Furthermore, the OS may manage partitions by itself using any combination of the approaches that we discussed previously for memory partitioning and allocation. Unfortunately however, swapping has an important limitation that prevents it from delivering a full virtualization solution by its own. For instance, if a single program requires more memory than there is available in the underlying platform, it cannot run even if there is no other program running in the system. Indeed, some OSes address this issue by applying the swapping approach only to program segments (i.e., stack, heap and code), but the problem still remains unsolved.

The second approach (virtual memory) provides a complete virtualization solution and works as follows. Physical memory is divided in fixed-size partitions, called frames. Conversely, programs are split into fixed-size partitions of same size, known as pages. Based on this, the OS takes care of: (i) assigning pages to frames; (ii) keeping in memory those pages that are currently in use; and (iii) swapping out to the non-volatile storage those pages that are not (currently) in use. Unlike swapping, virtual memory requires support from the underlying hardware and a tight cooperation with the OS. On the one hand, the OS maintains a special data structure, known as page table, that provides the mapping of pages. On the other hand, the hardware relies on this structure to dynamically translate page addresses into frame addresses.

In virtual memory, the main challenge that the OS faces concerns the decision of which pages it should keep in memory. Indeed, if physical memory is large enough, this is trivially handled, because there are more frames than pages. However, this is not the base case scenario. Often, physical memory operates under pressure, and the OS should constantly offload unused pages to non-volatile storage and bring in to memory those pages that are needed. This is known as page replacement and effectively happens whenever a program tries to access a page that is not currently mapped in physical memory. In this event, the hardware triggers a page fault exception and traps execution flow to the OS. In turn, the OS locates the target page in the underlying non-volatile storage and selects some in-memory page to be replaced. Overall, the replacement

algorithm has an important impact in the performance of the system and for this reason it is a wide subject of research. Among the various algorithms that exist, we highlight below those that are the most relevant to this work.

- **First-in First-Out (FIFO)** This algorithm relies on the idea that pages that were accessed longer ago have less chance to be accessed in the near future. Pages are kept in a queue structure, which is sorted according to their arrival time in memory. Whenever a page should be swapped out to non-volatile memory, the head page in the queue is chosen to be replaced (i.e., the page that was first brought in). This algorithm is simple to implement, but often presents the anomaly of swapping out heavily-used pages.

- **Second Chance** This is an improved version of FIFO page replacement. Likewise, in-memory pages are kept in a queue structure according to their arrival time. However, before selecting a page, the algorithm checks if that candidate was accessed since the last run of the algorithm. If this was the case, then the candidate page is put back in the queue and the search continues. As soon as a valid candidate is found, such page is selected. In the worst case, all in-memory pages are processed and Second Chance degenerates to FIFO.

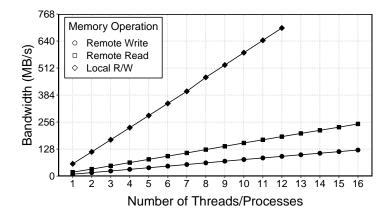

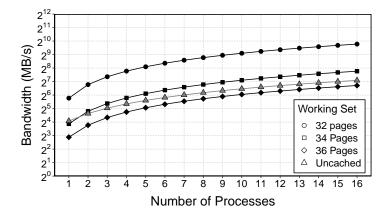

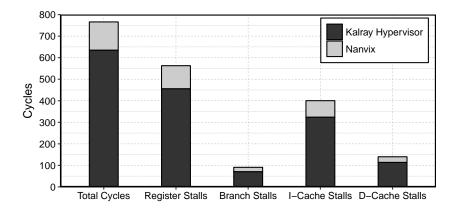

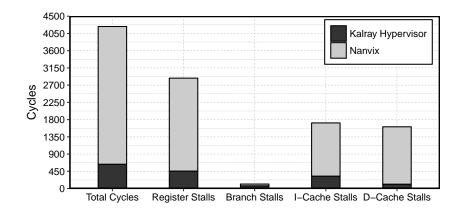

- Least Recently Used (LRU) This algorithm embraces the idea that pages that were heavilyused recently will likely be used in the near future. Conversely, those that were not heavily used for longer, will unlikely be used next. Based on this, whenever a replacement decision is triggered, the algorithm selects the page that was not used for longer. This strategy yields to near optimal solution, but faces an important challenge concerning performance. Effectively, to select the least recently used page, in-memory pages would have to be placed in a priority queue structure that is sorted according to the number of times that each page was accessed. Noteworthy, the hardware would need to update this structure at each memory reference, which is clearly prohibitive in terms of complexity and performance.