# Hardware implementation of cell-inspired computational models

Zeyi Shang

#### ► To cite this version:

Zeyi Shang. Hardware implementation of cell-inspired computational models. Bioinformatics [q-bio.QM]. Université Paris-Est; Southwest Jiaotong University, 2020. English. NNT: 2020PESC0088. tel-03545599

### HAL Id: tel-03545599 https://theses.hal.science/tel-03545599v1

Submitted on 27 Jan2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### UNIVERSITÉ PARIS-EST CRÉTEIL VAL DE MARNE

DOCTORAL THESIS

# Hardware implementation of cell-inspired computational models

Author: Zeyi Shang Jury President: Lynda Mokdad Supervisor: Gexiang Zhang Sergey Verlan

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in

COMPUTER SCIENCE

## **Declaration of Authorship**

I, Zeyi SHANG, declare that this thesis titled, "Hardware implementation of cellinspired computational models" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

Signed:

Date:

"L'archer à cheval de la steppe a régné sur l'Eurasie pendant treize siècles parce qu'il était la création spontanée du sol même, le fils de la faim et de la misère, le seul moyen pour les nomades de ne pas entièrement périr les années de disette."

René Grousset

L'empire des steppes

### Abstract

#### Zeyi Shang

#### Hardware implementation of cell-inspired computational models

Parallelism, non-determinism and large scale are the three characters of biological and ecological systems which are transmitted to bio-inspired computing models enlightened by these bio- or/and eco- systems. Imitating bio-inspired computing models on general purpose computers by designing high level programming language codes is the common approach to simulate these unconventional computing models for its accessibility. However, this approach is inappropriate to cope with the three characters mentioned above, especially for the parallelism on a large scale. From the perspective of hardware, CPU of computers executes software codes which simulate bio-inspired computing models. More precisely, integrated circuits inside CPUs or other processing devices perform operations defined by software codes which mimic these models. Software codes emulating bio-inspired computing models can get expected results, but it is not guaranteed that the CPU executes operations in line with what models do. If the parallel performance provided by target CPU is not enough to support parallel processing, some parallel procedures will be serialized. And because that the process of CPU is not transparent, we cannot know whether the CPU carry out operations in accordance with that of models or not. To state the main works more clearly, the notion of implementation and simulation should be distinguished. If a hardware emulates bio-inspired computing models in strict accordance with procedures defined by the models, such type of emulation is termed as "implementation". While if processing procedures of target hardware are not consistent with models, although expected outcomes obtained, such kind of emulation is entitled as "simulation".

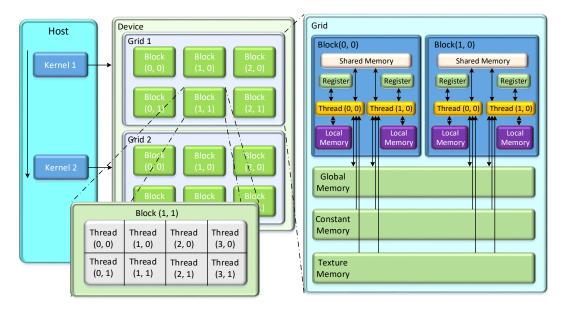

A more preferable approach to imitate bio-inspired computing models is to design model-specific hardware platform to implement other than simulate them for the simulation will do harm for some advantages of these models, for instance, the large scale parallelism. The hardware implementation method of bio-inspired computing models imitates models with (digital) circuits directly instead of software codes since circuits are the principal part comprising a variety of processors such as CPUs and GPUs. On the contrary, if a processor is powerful enough to execute models as exactly the theoretical procedures, this emulation is called software implementation. High-end GPUs with computing unified device architecture (CUDA) belong to such type of hardware so many parallel algorithms are implemented on them. This thesis concentrate on hardware implementation of two bio-inspired computing models: reaction systems and numerical P systems. Variants of these two models were implemented on the reconfigurable hardware-field programmable gate array (FPGA). The prominent strength of hardware implementation comparing with software implementation is its high performance rooted in the tailored parallel hardware architectures.

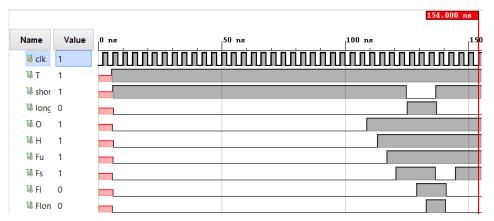

Reaction systems is a theoretical framework for investigating biochemical reactions and their interactions in biological cells. It is a qualitative parallel computing model for reactions and their interactions taking place concurrently. There are investigations on CPU software simulation and GPU software implementation of reaction systems. For the simulation of large-scale reaction systems, the processing speed of these two methods is not adequate. Hence, it is worthwhile to investigate their implementation using hardware circuits. To conceive the FPGA implementation method of reaction systems, the relationship between reaction systems and synchronous circuits is studied at first. It is found that the dynamics of a reaction system corresponds to the dynamics of a Mealy or Moore automaton of some synchronous circuit, and the qualitative characteristics of reaction system can be expressed by the value of binary variables. Based on these observations, an FPGA implementation method for reaction systems is devised. According to this method, the reaction system of intermediate filaments self-assembly and heat shock response reaction system are implemented on FPGA, which verify the correctness of this method. The calculation speed is up to  $2 \times 10^8$  step per second (the frequency is 200 MHz). A binary counter constructed with a reaction system is implemented on FPGA as well, exhibiting the expressibility of reaction systems that can be used to build a quantitative model.

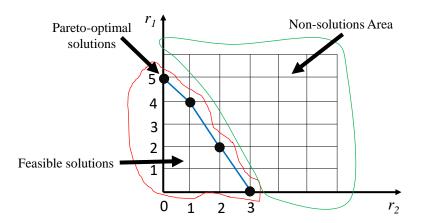

Membrane computing is a parallel quantitative computing paradigm inspired by the membrane structure of biological cells and biochemical reactions inside. Membrane computing models are called P systems. Due to the limited parallel processing capability of CPU, software simulation of P systems cannot leverage their maximal parallelism. Like reaction systems, implementing P systems on parallel hardware circuits is more reasonable. When hardware resources are sufficient, theoretical parallelisms can be fully exploited. In this thesis, FPGA implementations of the celllike symbol object P systems are summarized, and existing FPGA implementation methods are expounded at length. The qualitative and quantitative comparisons of various methods are formulated. Object distribution problem (ODP, choosing which rules to apply) is the core problem of hardware implementation of symbol object P systems. Because of the maximal parallelism and non-determinism of this class of P system, ODP is NP hard. In order to calculate the solutions (available rule sets) of ODP, a method based on multi-criteria optimization and integer linear programming is proposed.

This thesis also considers on a special type of cell-like P system, called numerical P system (NPS), focusing on its FPGA implementation and applications in robot control and path planning. The relationship between NPS and system of difference equations is studied, and it is found that NPS is another form of the latter. Considering that a difference equation and a differential equation can be transformed to each other, NPS can model systems modeled by differential equations. Enzymatic numerical P system (ENPS) is a variant of NPS having better modeling capacity for the function of enzyme-like variables. However, the rule usability predicate form is not uniform, and there is only one discriminant, which limits its application scope. In order to expand the application field of (E)NPS and facilitate FPGA implementation, they are extended to generalized numerical P system (GNPS). The rule applicability discriminants of GNPS are generalized to Presburger arithmetic.

The FPGA implementation method of GNPS's rules, called *FPGA step-wise parallel implementation of program* (FSPIP) implementation method, is proposed. According to this method, the robot membrane controller based on NPS, ENPS and GNPS are implemented. Since GNPS is a superset of (E)NPS, the FSPIP approach also compatible to (E)NPS. Compared with software simulation, the acceleration ratio obtained by the three NPSs implemented on FPGA is the order of 10<sup>4</sup>. Considering the data input and output in practical applications, an UART serial communication module was designed for the NPS membrane controller to receive data from the robot sensors and to transmit the computation results to actuators. A object multiset rewriting rule of symbol object P system can be disassembled as a set of NPS programs. Programs updating multiplicity of the same object can be combined together. The function of combined programs are equivalent to rewriting rules in the same membrane.

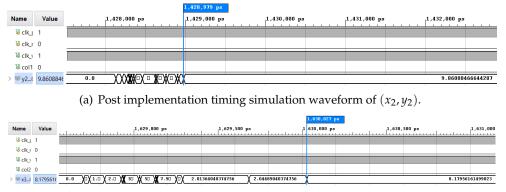

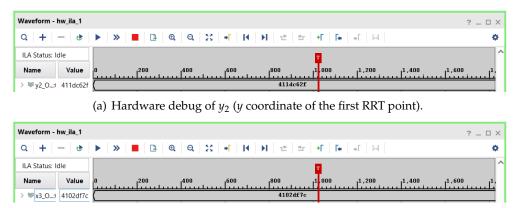

The maximal parallelism of GNPS is suitable to accelerate computationally intensive algorithms. The rapidly-exploring random tree (RRT) algorithm is modeled in the framework of GNPS, obtaining a RRT-GNPS model in which all parallel operations are calculated simultaneously, while sequential procedures are processed serially. The RRT-GNPS model is implemented on FPGA in line with the GNPS FPGA implementation method. In consideration of future applications in large-scale maps, variables in RRT-GNPS are expressed in IEEE 754 single-precision floating point format, which is different from fixed-point number representation used in the implementation of membrane controllers. Floating-point adder, multiplier and reverse square root units are designed. A sequential triggering method based on edge detection is designed to trigger operations according to the applicability of rules and the order of arithmetic operation priority. Compared with software simulation, the FPGA hardened RRT-GNPS achieves a speedup of  $3.20195 \times 10^4$ .

### Résumé

Le non-déterminisme et le parallélisme à grande échelle sont deux propriétés importantes des systèmes biologiques et écologiques. Il est donc naturel qu'elles soient héritées par les modèles de calculs bio-inspirés, c.-à-d. dont le fonctionnement est inspiré par des processus biologiques. Pour utiliser ces modèles en pratique, ou juste pour mieux comprendre leur comportement, il est important de pouvoir simuler leur fonctionnement. L'approche standard pour le faire consiste dans la réalisation des simulateurs logiciels, exécutées sur des ordinateurs conventionnels. Cependant, l'architecture de ces derniers n'est pas de tout compatible avec les propriétés essentielles des systèmes visés, plus particulièrement avec le parallélisme à grande échelle. Même si le résultat final est correct, l'exécution des modèles ne corresponde pas à leur inspiration biologique et leur définition mathématique, la plupart des opérations parallèles étant effectuées en séquence. On parle alors de simulation, qui traite le modèle considéré comme une boite noire en fournissant une entrée et en produisant la bonne sortie après un certain temps. Cette simulation peut être séquentielle (sur un processeur), ou parallèle (sur un processeur multicœur ou une carte graphique ayant plusieurs processeurs spécialisés). En revanche, l'implémentation (ou la simulation forte), demande additionnellement que le comportement du modèle original soit respecté lors de l'exécution.

Pour obtenir une implémentation d'un modèle de calcul bio-inspiré il est possible d'utiliser des composants biologiques, directement liés au phénomène dont le modèles est inspiré. Cette approche, réalisable dans certains cas, est bornée par les limites actuelles de la biotechnologie. Une autre possibilité repose sur le parallélisme inhérent des circuits logiques. Il est possible de construire une plateforme matérielle in silico dont les circuits vont correspondre aux composants du modèle tout en gardant le fonctionnement parallèle à grande échelle. Pour faciliter le développement on utilise généralement des circuits logiques matériels reconfigurables, appelés FPGA, qui permettent un prototypage rapide des circuits matériels.

Cette thèse s'articule autour de l'implémentation matérielle de deux modèles de calcul bio-inspirés : systèmes à réaction (RS) et des systèmes à membranes numériques (NPS). Nous avons implémenté différentes versions de ces modèles sur FPGA et nous avons comparé les résultats obtenus avec les simulations logicielles et matérielles (en utilisant les GPUs) existantes. Afin d'avoir des exemples non-triviaux, nous avons également proposé la traduction des différents problémes liées au contrôle du mouvement robotique dans le formalisme NPS.

Les systèmes à réaction sont une formalisation théorique des réactions biochimiques. C'est un modèle de calcul qualitatif et parallèle qui se concentre sur les relations causales entre les entités en ignorant les quantités (ou les concentrations). La dynamique du modèle repose sur la promotion et l'inhibition d'un réactant par des autres. Le principe de non-permanence assure la présence des réactants dans le système uniquement s'ils viennent d'être produits ou introduits. Il existe plusieurs logiciels de simulation des systèmes à réaction, ainsi que des simulations matérielles à l'aide des GPU. Cependant, aucune implémentation matérielle n'a pas été reporté dans la littérature. Pour des circuits de petite taille cela ne pose aucun problème particulier, car les temps de simulation logicielle sont suffisamment petits. Par contre, le passage à l'échelle et l'utilisation des modèles de grande taille nécessite une approche différente.

Dans cette thèse on s'est intéressé à l'implémentation matérielle des systèmes à réaction à l'aide des FPGA. Premièrement, on a étudié le lien entre les systèmes à réaction et les circuits de commutation synchrones (qui sont un sous-ensemble des circuits Booléens), ainsi que les modèles connexes des automates de Mealy et Moore (qui sont des automates finis avec des entrées/sorties). Nous avons trouvé que les deux modèles sont très proches et nous avons donné des algorithmes de traduction entre les systèmes à réaction et les circuits de commutation synchrones qui préservent la même dynamique pas à pas. Cela a permis par le passage de trouver une forme normale pour les systèmes à réaction ayant des propriétés intéressantes et de proposer de nouvelles possibilités de conception de ces derniers à l'aide des outils bien connus comme des automates de Mealy.

Les circuits de commutation peuvent être traduits naturellement vers FPGA. Cela permet donc de traduire un système à réaction vers un circuit FPGA tout en gardant son comportement dynamique pas à pas, en obtenant donc une implémentation. Pour tester notre approche nous avons implémenté des systèmes à réaction proposés pour la modélisation de la croissance des filaments intermédiaires et de la réponse au choc thermique dans les bactéries. Ensuite, nous avons développé un compilateur qui permet d'automatiser la traduction en appliquant les algorithmes proposés. Cela nous a permis d'effectuer des mesures de performance de notre approche sur des systèmes de grande taille: nous avons effectué l'implémentation du modèle du transduction du signal du récepteur ErbB dans les cellules épithéliales humaines qui comprend 620 réactions et 246 entités. Cette implémentation a permis d'atteindre la vitesse de calcul de 108 étapes/seconde et d'avoir une accélération de l'ordre 2.5 × 10<sup>5</sup> par rapport aux meilleurs simulateurs GPU existants.

Les autres modèles de calcul considérés dans ce mémoire relèvent du domaine du calcul à membranes qui est un paradigme de calcul parallèle et quantitatif inspiré par la structure et le fonctionnement des cellules vivantes. Le fonctionnement du modèle sous-entend un parallélisme massif, sa simulation sur des ordinateurs conventionnels ou même GPU ne permet pas de tirer profit de cette propriété. En revanche, une implémentation à l'aide des FPGA permet d'obtenir un fonctionnement plus proche de la sémantique du modèle et d'avoir par conséquent un gain de vitesse.

Dans ce mémoire de thèse nous donnons un aperçu des méthodes d'implémentation existantes des différentes variantes des systèmes à membranes à l'aide des FPGA. Afin de pouvoir comparer les approches, nous avons représenté le problème calculatoire principal de ces implémentations (le calcul des règles applicables pour une configuration donnée) sous forme d'un problème d'optimisation multicritères. Nous avons montré que les différentes solutions existantes correspondent à des scalarisations particulières du problème d'optimisation.

La suite du mémoire se concentre sur une variante particulière des systèmes à membranes, appelée systèmes à membranes numériques (NPS). C'est un modèle qui comprend plusieurs compartiments chacun possédant des variables numériques. Les règles du modèle sont des fonctions qui calculent une valeur numérique à partir des variables présentes dans un compartiment, ainsi que dans les compartiments voisins et puis la distribuent vers d'autres variables en utilisant des pondérations. Le modèle NPS et son extension ENPS, ou l'applicabilité des règles est contrôlée par une valeur seuil, ont des applications importantes dans le contrôle robotique et la planification du chemin.

Nous avons montré des liens inattendus entre les NPS et les systèmes d'équations en différences finies en montrant comment transformer les modèles l'un dans l'autre sans perdre la dynamique. Plus précisément, la relation entre les NPS et les systèmes d'équations des différences finies est de même nature que celle entre les systèmes à réaction et les circuits de commutation. De plus, les systèmes à réaction peuvent être vues comme des versions simplifiées de NPS ou les variables ont des valeurs booléennes (à la place des valeurs numériques). Cela nous a conduit naturellement vers une nouvelle notion d'automates de Mealy opérant sur des vecteurs de nombres en entrée/sortie.

Nous avons également proposé une nouvelle extension du modèle (E)NPS, appelée GNPS, qui a pour but l'optimisation du codage des problèmes de contrôle robotique et qui en même temps admet une implémentation efficace à l'aide des FPGA. En effet, dans GNPS l'application des règles est contrôlée par des prédicats arithmétiques écrits en arithmétique de Presburger (avec une signature optionnelle). Cela permet à la fois de faciliter l'écriture des contrôleurs et d'avoir une implémentation directe sur FPGA. En se fondant sur les résultats théoriques ci-dessus, nous avons conçu une méthode d'implémentation des GNPS à l'aide des FPGA. Cette implémentation peut être faite avec deux représentations différentes des nombres: en point fixe et en format IEEE 754. Dans le premier cas des accélérations importantes ont été obtenues, car les opérations d'addition, soustraction, multiplication par constante et test sont facilement représentables en FPGA. Nous avons développé un contrôleur robotique à l'aide de GNPS et nous l'avons implémenté sur FPGA en utilisant la méthode proposée. En comparant avec une simulation sur GPU, notre implémentation a une accélération de l'ordre 10<sup>4</sup>. Nous avons également rajouté un module de communication UART pour récupérer les données des capteurs et de contrôler le mouvement des roues en temps réel.

Comme le modèle GNPS est par définition parallèle et comme son implémentation en FPGA préserve cette propriété, il devient intéressant de l'utiliser pour la résolution des algorithmes demandant beaucoup de calculs. Nous avons modélisé l'algorithme RRT pour la planification du mouvement. Cela a demandé également de concevoir des modules de calcul des diverses fonctions arithmétiques utilisant des nombres encodés au format IEEE 754. D'après les tests, l'accélération obtenue est de l'ordre 10<sup>4</sup>.

Organisation du mémoire :

Chapitre 1 contient l'introduction, ainsi que la description des notions principales utilisés dans la thèse.

Chapitre 2 donne les définitions des modèles considérés (systèmes à réaction, systèmes à membranes et systèmes à membranes numériques). Ce chapitre présente également comment on peut représenter une étape de calcul à l'aide d'un problème d'optimisation multicritères.

Chapitre 3 contient une introduction aux GPU et CUDA et présente un aperçu des implémentations matérielles existantes dans le domaine.

Chapitre 4 étudie les liens entre les systèmes à réaction et les circuits de commutation et présente l'implémentation des systèmes à réaction sur FPGA.

Chapitre 5 analyse les liens entre NPS et les systèmes d'équations des différences finies. Le modèle GNPS y est également introduit.

Chapitre 6 présente l'implémentation de 3 contrôleurs de mouvement robotique en utilisant GNPS et les méthodes développées.

Chapitre 7 présente une implémentation de l'algorithme RRT de planification du mouvement d'un robot. L'encodage des valeurs numériques utilise le standard IEEE

754. Plusieurs modules FPGA ont été crées pour gérer les opérations non-linéaires, comme par exemple la racine carrée. Chapitre 8 présente les conclusions.

### Acknowledgements

First and foremost, I would like to express my special thanks to my two supervisors: professor Zhang Gexiang and Sergey Verlan. The research subject of my doctoral phase is a new field for me. Professor Zhang chose the research direction for me based on my academic experiences. Due to the insufficient accumulation of relevant knowledge, I encountered many problems and difficulties in the early stage of my research. Professor Zhang answered questions and solved problems I raised. To provide more chances for me to learn cutting-edge knowledge, Professor Zhang contacted several high-level international scholars to give guidance to me. He helped me to get the chance to be a joint supervising PhD student. Professor Zhang provided very good hardware equipment which I need in my research, which ensured that the project progress went with a swing. In the monthly academic summary meeting, Professor Zhang suggested many forward-looking opinions and constructive guidance for my research and guided me to overcome difficulties. Professor Zhang's rigorous scientific research attitude deeply influenced me, which made me adapt to the high-intensity scientific research work gradually. Professor Zhang also gave me considerate care in my ordinary life. Because of my dietary custom, Professor Zhang always prepare extra dishes for me at every dinner party, so that I could eat well. With his words and deeds, Professor Zhang taught me how to conduct scientific research and how to face the difficulties in life and work positively. Under the guidance of Professor Zhang, I am able to set sail in my academic career.

Sincere gratitude from the bottom of my heart is also given to my supervisor Sergey Verlan for all things you have done to me. I would never forget that it is you who helped me involving in the joint supervision project, enrolling in Université Paris-Est and gaining scholarship so that I can study in Créteil nearly one year. Bio-inspired computing and FPGA development were totally new to me and I was completely at a loss what to do at beginning. From studying reaction system and its Verilog design, you guide me in the scene. Almost every week in Créteil you resolve problems raised by me, giving the detailed derivations so that I can understand entirely. You help me renting a studio, opening a bank account and starting living in France. To pick me up in the Charles de Gaulle airport at 6:30 am, you get up very early. You have no idea how moved I was to see you in the airport lobby. Under your guidance, I learn how to do research and how to write academic papers. I am deeply grateful to you for these things. I am quite lucky to meet you and it is my honor to be your student.

It behaves me to express my special thanks to Professor Gheorghe Păun. In the autumn of Wuhan, 2016, it was my first time to meet a member of European Academy of Science coming from Romania. I was excited and nervous to shake hands with you. After 5 days of listening your lectures about formal languages and P systems, I got some fundamental concepts in the membrane computing field. I bought a Chinese version of your monograph *Membrane Computing: An Introduction*. I would like your autograph but I dare not to walk to you. At last I got the strength to walk to the podium, saying what I want. You agreed nicely and wrote on the flyleaf "Happy computing–Gheorghe Păun". Your words encourage me to get through adversities in front of me. The book with your hand-writing is a treasure for me.

To Ignacio, you are such a kindhearted man. I would never forget the hotpot you treat me in Seville. It is you who take me to visit the magnificent Royal Alcázar, and to look around the lovely city. You picked me up in the airport when I came to Seville to attend the brainstorming week of Membrane Computing and drove me to the airport again in the early morning. You explained me how the RRT algorithm works so that I can implemented it on FPGA. Thank you so much for your kindness and consideration for me.

To Junior, you are a gentleman with heartiness. You introduce me to Xiangxiang, who is a caring girl helping me a lot to make a living in Créteil. You help to get the gym card of our university so I have a place to do physical exercise so to keep healthy. To Xiangxiang, although we never ever meet, you were the only Chinese people I can talk to at the first time I came to France. You warned me to stay alert in subway and told where to find a room close to our university with good price. Thank your goodness and wish happiness for you and your family. To Steve, you do a great favor for me to get my long term pass card in the prefecture hall. I remember that it was a cold winter morning you came to help me for my french is too poor to handle this. In fact during that time you did not know me well, but you still got up and braved the cold to support me. Your kindness touches my heart all the time. I thank Paul for his heart-warming smile every time entering our working room. I enjoy the conversations about my home town and academic discussions with you. Thank your help to deal with my inscription. To Tau, a enthusiastic and generous man. Your jasmine tee and other scented tee are always on time in the morning which fresh my mind, reminding me the ancient tradition of east Asia. To Alex, a cordial man. I enjoy the academic discussions with you. Thank you, Paul and Tau to hold the farewell party by the lake of Créteil for me. You guys bought cakes, snacks and beers. We talked a lot over beer. It is a good memory for me.

To Wenya, your culinary skill is very good. I miss chives pancakes and steam breads you made. They are so delicious. I am appreciative to be a house mate of you. Wish you all the best. To Mengmeng, thank your benevolence and patience to listen to my grievances about life. The Pixian broad bean paste you bought from Chinese supermarket for me saved my life. I am grateful to know you. Wish you a bright future.

I am grateful to Université Paris-Est for providing a good laptop computer to me. It is quite helpful to do FPGA developments because post implementation timing simulation requires very good CPU performance and large RAM.

I express my appreciation to my wife, Yongli, for her support, dedication and love. During my worst time you give me warm family, a cute baby. You bring up our child while I work in Chengdu far away from you. I owe you a lot. Many thanks to my sister in law, Yongmei, for your support and consideration.

Last but not certainly not least, thank my grand parents and my parents who raised and cultivated me. My grandmother was the one who love me most in the world. I grew up with her endless love which helps me struggling through the hardest time. My mother scratch a living to devote the energies of her lifetime to my education. My younger brother experienced all the difficulties and happiness with me. Because the love and support from all of you, I gain enough courage to fight against fate.

## Contents

| Declara                                                                       | ation of Authorship                                                                                                                                                                                                                                                                                          | iii                                        |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Abstra                                                                        | ct                                                                                                                                                                                                                                                                                                           | vii                                        |

| Résum                                                                         | é                                                                                                                                                                                                                                                                                                            | xi                                         |

| Acknow                                                                        | wledgements                                                                                                                                                                                                                                                                                                  | xv                                         |

| Conten                                                                        | its                                                                                                                                                                                                                                                                                                          | cvii                                       |

| List of                                                                       | Figures                                                                                                                                                                                                                                                                                                      | xxi                                        |

| List of                                                                       | Tables xx                                                                                                                                                                                                                                                                                                    | cvii                                       |

| 1 Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7                       | oductionBiological cell: foundation of lifeBiological system modellingReaction systemsMembrane computingFPGA based reconfigurable computingThesis statement1.6.1Main research contents1.6.2ContributionsThesis organization                                                                                  | 1<br>2<br>3<br>4<br>5<br>6<br>6<br>8<br>10 |

| <ul> <li>2 Def</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ul> | initionsReaction systemsP systems2.2.1Symbol object cell-like P system2.2.2Network of cellsReduction the computation of P systems to multi-criteria optimization2.3.1Preliminaries2.3.2Rule choice as integer multi-criteria linear optimization problem2.3.3Tentative solutionsWrap-up                      | 22                                         |

| <ul> <li>3 Ove</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> </ul>              | Prview of hardware implementation of reaction systems and P systemsGPU presentationFPGA presentation3.2.1FPGA architecture3.2.2FPGA development flowSoftware simulation and implementation of reaction systems: an overvie3.3.1CPU simulation of reaction systems3.2.2GPU implementation of reaction systems | 27<br>28<br>30<br>30<br>34                 |

### xviii

|   | 3.4         | Background of hardware implementations of P systems                  | 38  |

|---|-------------|----------------------------------------------------------------------|-----|

|   | 3.5         | General ideas about hardware implementations of P systems            |     |

|   |             | 3.5.1 Data organization                                              |     |

|   |             | 3.5.2 Object Distribution Problem and Non-Determinism                |     |

|   | 3.6         | Literature review of existing P system FPGA implementations          | 42  |

|   |             | 3.6.1 Region-based implementation                                    |     |

|   |             | Petreska and Teuscher implementation                                 |     |

|   |             | Nguyen simulation                                                    |     |

|   |             | 3.6.2 Rule-based implementations                                     | 45  |

|   |             | Nguyen implementation                                                |     |

|   |             | Verlan and Quiros implementation                                     |     |

|   | 3.7         | Micro-controller based implementation of P systems                   |     |

|   | 3.8         | Wrap-up                                                              |     |

|   | 0.0         | ••••••••••••••••••••••••••••••••••••••                               | 00  |

| 4 | FPG         | A implementation of reaction systems                                 | 55  |

|   | 4.1         | Relations between reaction systems and synchronous circuits          | 55  |

|   |             | 4.1.1 From reaction systems to switching circuits                    |     |

|   |             | 4.1.2 From switching circuits to reaction systems                    | 59  |

|   |             | 4.1.3 General ideas for FPGA implementation of reaction systems      | 61  |

|   | 4.2         | FPGA implementation of self-assembly intermediate filaments reac-    |     |

|   |             | tion systems                                                         | 62  |

|   | 4.3         | FPGA implementation of heat shock response reaction systems          |     |

|   | 4.4         | FPGA implementation of reaction system binary counter                | 69  |

|   |             | 4.4.1 Reaction system binary counter design                          |     |

|   |             | 4.4.2 UART-RS counter design and implementation                      |     |

|   | 4.5         | Wrap-up                                                              |     |

| _ |             |                                                                      |     |

| 5 |             | oretical investigations of numerical P systems                       | 79  |

|   | 5.1         | Numerical P system and enzymatic numerical P system                  | 80  |

|   | 5.2         | The relationship between (E)NPS and system of difference equations . |     |

|   |             | 5.2.1 From (E)NPS to system of difference equations                  |     |

|   |             | 5.2.2 From system of difference equations to (E)NPS                  |     |

|   | 5.3         | Binary and unary normal form of (E)NPS                               |     |

|   | 5.4         |                                                                      |     |

|   | 5.5         | Generalized Numerical P Systems                                      |     |

|   | 5.6         | FPGA implementation of GNPS                                          |     |

|   | 5.7         | Case studies                                                         |     |

|   |             | 5.7.1 Case study 1                                                   | 94  |

|   |             | 5.7.2 Case study 2                                                   | 96  |

|   | 5.8         | Wrap-up                                                              | 100 |

| 6 | БЪ <b>С</b> | A implementation of robot membrane controller                        | 101 |

| U | 6.1         | •                                                                    | 101 |

|   | 6.1<br>6.2  | FPGA implementation of membrane controller based on ENPS             |     |

|   | 6.2         | FPGA implementation of membrane controller based on GNPS             |     |

|   | 6.4         | UART communication of NPS                                            |     |

|   | 6.5         |                                                                      |     |

|   | 0.0         | Wrap-up                                                              | 117 |

| 7  | FPGA Architecture for Generalized Numerical P System modeled Rapidly- |                                                                      |      |

|----|-----------------------------------------------------------------------|----------------------------------------------------------------------|------|

|    | expl                                                                  | loring Random Tree Algorithm                                         | 121  |

|    | 7.1                                                                   | Rapidly-exploring random tree algorithm                              | 121  |

|    | 7.2                                                                   | Floating point arithmetic units design                               | 125  |

|    |                                                                       | 7.2.1 Basics of IEEE 754 single precision floating point standard    | 125  |

|    |                                                                       | 7.2.2 Sequential triggered IEEE 754 compliant adder                  | 128  |

|    |                                                                       | 7.2.3 Sequential triggered IEEE 754 compliant multiplier and FP com- |      |

|    |                                                                       | parator                                                              | 129  |

|    |                                                                       | 7.2.4 Inverse square root unit                                       |      |

|    |                                                                       | 7.2.5 Floating point random number                                   |      |

|    | 7.3                                                                   | GNPS arranged RRT register transfer level model design               | 132  |

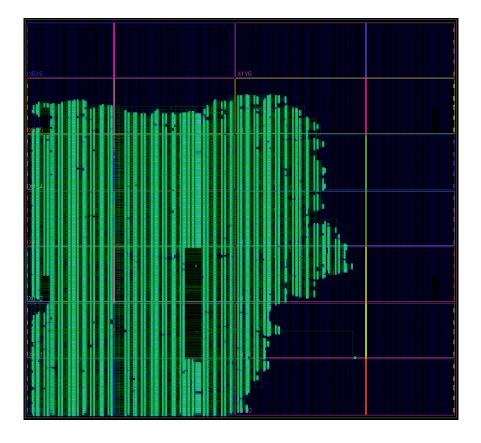

|    | 7.4                                                                   | FPGA implementation of RRT-GNPS                                      | 135  |

|    | 7.5                                                                   | Wrap-up                                                              | 137  |

| 0  | Com                                                                   | alered a ma                                                          | 1.11 |

| 8  | Con                                                                   | clusions                                                             | 141  |

| Α  | Ass                                                                   | ociated figures of reaction systems                                  | 145  |

| B  | Ass                                                                   | ociated figures of GNPS                                              | 149  |

| Bi | Bibliography 1                                                        |                                                                      | 155  |

| Pu | Publications by the author 179                                        |                                                                      | 179  |

# **List of Figures**

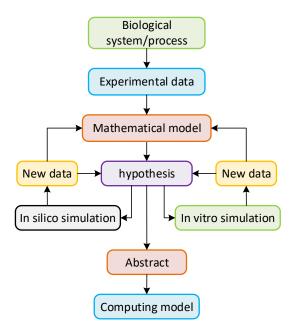

| 1.1        | Biological system or process modelling and biological computing. The comprehensive investigation of biological systems or processes is enlightening for theoretical computer scientists as well, resulting in bio-                                                                             |          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

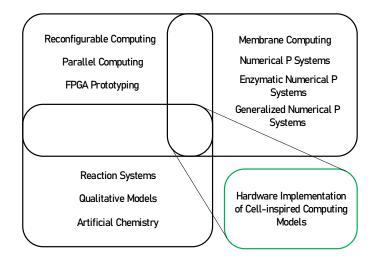

| 1.2        | logical computing a cross-discipline filed                                                                                                                                                                                                                                                     | 3        |

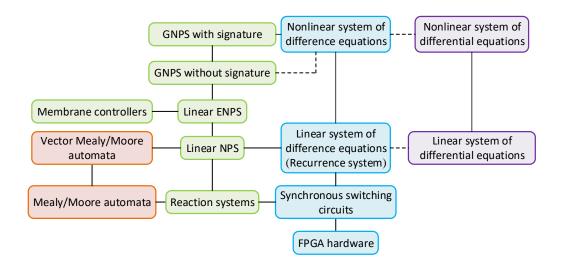

| 1.3        | be implemented on FPGAs as reconfigurable computing instances Relations of main research topics                                                                                                                                                                                                | 7<br>9   |

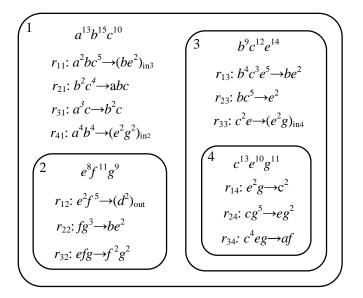

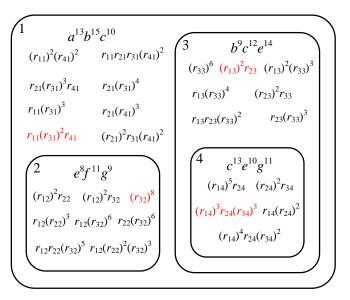

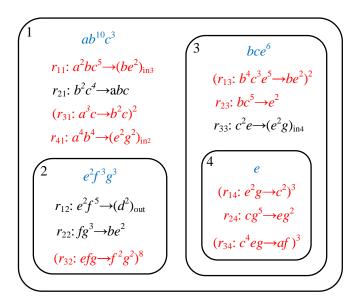

| 2.1        | An example of a P system with two membranes. Membrane 1 con-<br>tains a object multiset $a^5b^8c^6$ and four rules. Membrane 2 encom-                                                                                                                                                          |          |

| 2.2        | passes a object multiset $b^8c^{1}1e^9$ and three rules                                                                                                                                                                                                                                        | 15       |

| 2.3        | which can dissolving or creating membranes                                                                                                                                                                                                                                                     | 17       |

| 2.4        | cable rule multisets are highlighted in red                                                                                                                                                                                                                                                    | 18       |

| 2.5        | in blue                                                                                                                                                                                                                                                                                        | 18<br>21 |

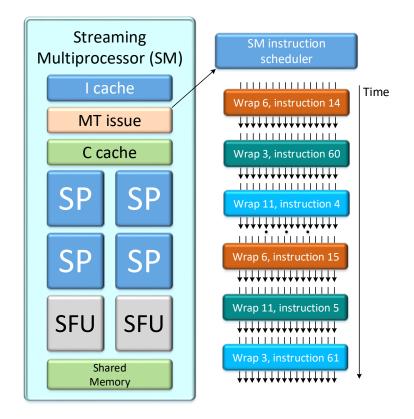

| 3.1<br>3.2 | (left) CUDA execution model, (right) CUDA memory model [110]<br>A SM is composed of an array of SPs, shared memory and a couple of<br>caches. A Multiple-Thread tissue module contains a SM instruction                                                                                        | 29       |

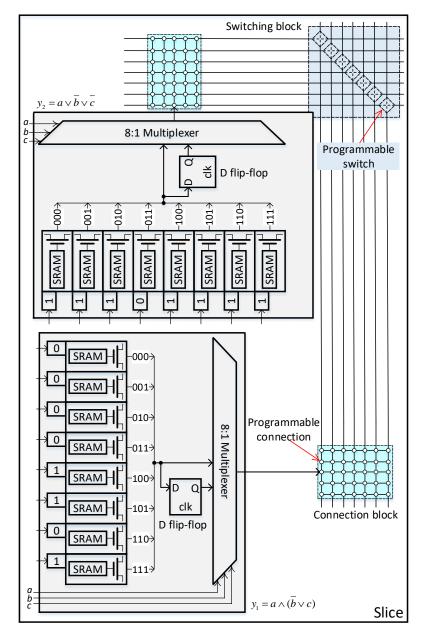

| 3.3<br>3.4 | scheduler which conducts instruction flows [112]                                                                                                                                                                                                                                               | 29<br>30 |

|            | $a \wedge (\bar{b} \vee c)$ and $y_2 = a \vee \bar{b} \vee \bar{c}$ respectively.                                                                                                                                                                                                              | 32       |

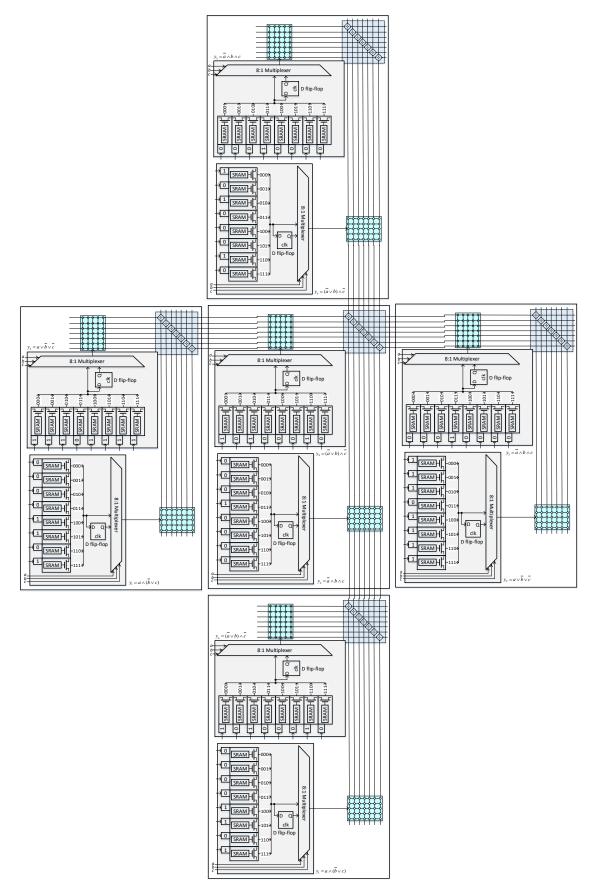

| 3.5        | The interconnection of 5 slices. Connection blocks (CBs) and switch-<br>ing blocks (SBs) impart highly flexibility for FPGAs to reconfigure<br>their architectures to perform various functions. The CB and SB can<br>contain much more intersection points than that depicted in this figure. | 33       |

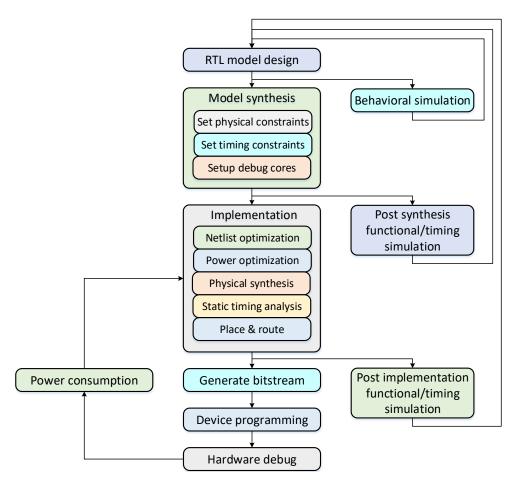

| 3.6        | Vivado FPGA development flow.                                                                                                                                                                                                                                                                  | 36       |

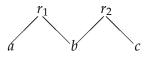

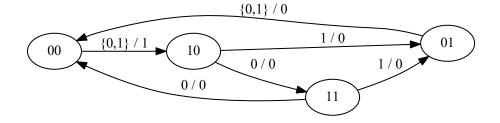

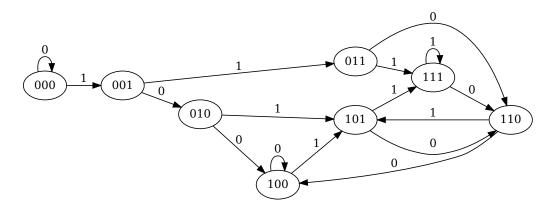

| 4.1        | The Mealy automaton for the circuit described by Equation (4.2). The label of the state corresponds to the value of the vector $(q_1, q_2)$ . The label of the transition corresponds to the value of the input variable <i>x</i> and output <i>y</i> .                                        | 57       |

|            | ouipui y                                                                                                                                                                                                                                                                                       | 57       |

#### xxii

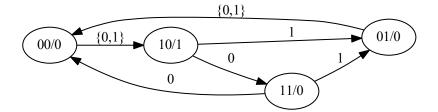

| 4.2        | The Moore automaton for the circuit described by Equation (4.2). The label of the state corresponds to the value of the vector $(q_1, q_2)/y$ . The la-         |          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | bel of the transition corresponds to the value of the input variable $x$ .                                                                                      | 58       |

| 4.3        | Moore machine for Example 4.6. The state label corresponds to the                                                                                               |          |

|            | values of the vector $(F, H, O)$ and the transitions are labeled by the                                                                                         |          |

|            | value of <i>T</i> . The output is the label of the state.                                                                                                       | 59       |

| 4.4        | Mealy machine for the 1101 sequence detector. It outputs 1 when the                                                                                             | 0,       |

| 1.1        | corresponding sequence is encountered as input. The state label cor-                                                                                            |          |

|            | responds to the vector $(q_2, q_1)$                                                                                                                             | 60       |

| 4.5<br>4.6 | Waveform comparison of interactive process of $\mathcal{R}_{ifl1} = (B_1, A_1)$ Waveform comparison of interactive process of $\mathcal{R}_{ifl2} = (B_2, A_2)$ | 64<br>65 |

| 4.7        | Physical constraints settings of two intermediate filaments reaction systems. Gray circles with wide orange bars are pins allocated to RTL                      |          |

|            | model ports.                                                                                                                                                    | 66       |

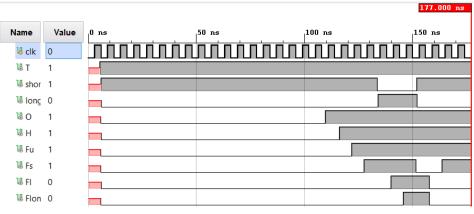

| 4.8        | Post implementation timing simulation of $\mathcal{R}_{ifl1}$ .                                                                                                 | 67       |

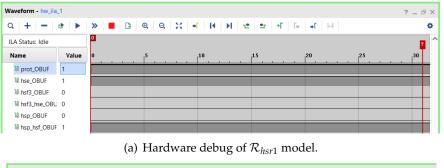

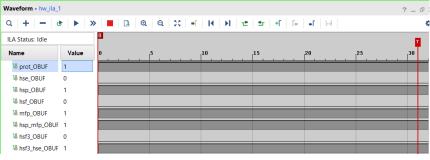

| 4.9        | Hardware debug of two intermediate filaments RSs.                                                                                                               | 68       |

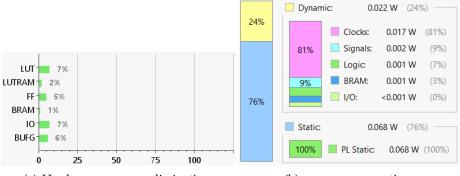

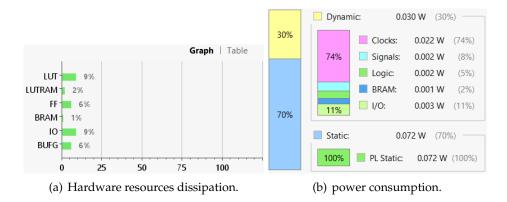

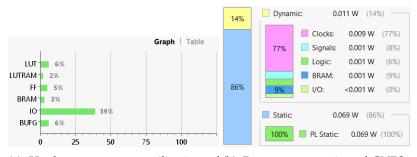

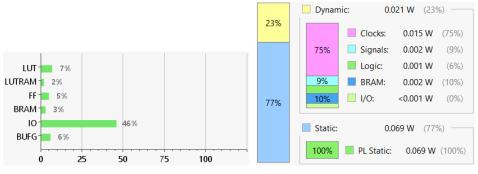

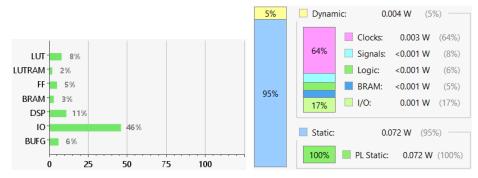

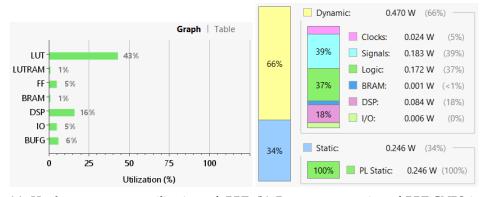

|            | Hardware resources dissipation and power consumption of $\mathcal{R}_{ifl1}$                                                                                    | 68       |

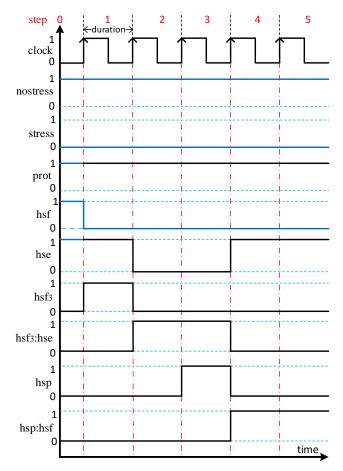

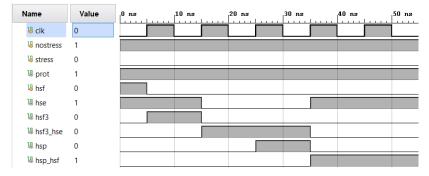

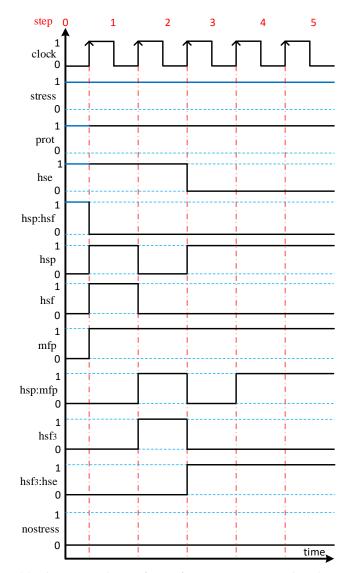

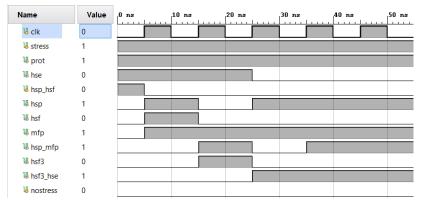

|            | Waveform comparison of interactive process 1 of $\mathcal{R}_{hsr} = (B_3, A_3)$ .                                                                              | 70       |

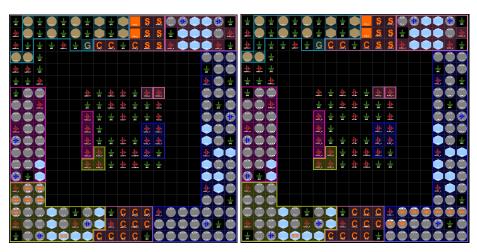

|            | Hardware debug of two heat shock response RSs. $\dots \dots \dots \dots \dots \dots$                                                                            | 71       |

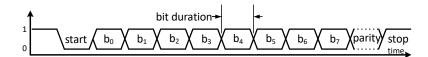

|            | UART data frame with 8 bits data, 1 bit EOF. Parity bit is optional                                                                                             | 73       |

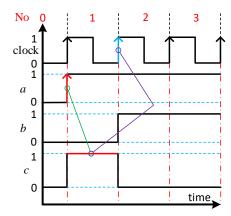

|            | Rising edge detection. The edge detection method can generate a high                                                                                            | 10       |

| 4.14       | level signal lasting for 1 clock cycle after the red rising edge. It is used                                                                                    |          |

|            | in combination with the clock rising edge highlighted in blue as the                                                                                            |          |

|            | trigger signal for other operations.                                                                                                                            | 74       |

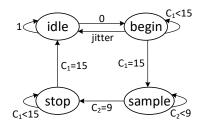

| 115        |                                                                                                                                                                 | 74<br>74 |

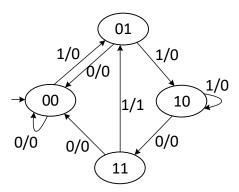

|            | State transition diagram of UART receiver $R_1$                                                                                                                 | 74       |

|            | State transition diagram of UART transmitter $T_1$ RTL model block diagram of UART-RS counter. $Cs_1$ to $Cs_4$ are clock                                       | 75       |

| 4.17       |                                                                                                                                                                 | 70       |

| 1 1 0      | synthesis module producing desired clock frequencies Behavioral simulation of UART-RS counter RTL model                                                         | 76<br>77 |

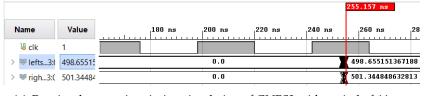

|            |                                                                                                                                                                 | //       |

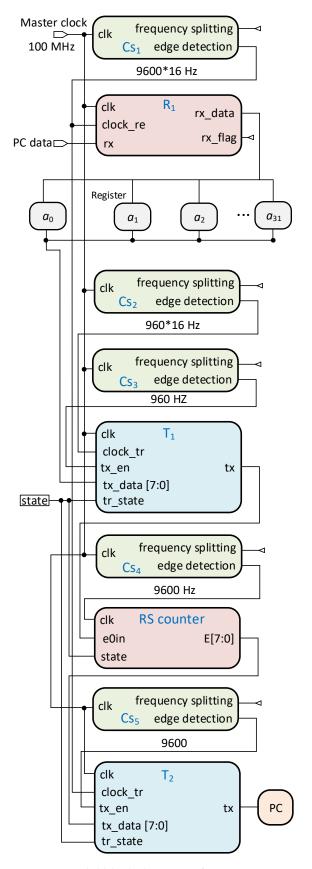

| 4.19       | Communication experiment between host computer and FPGA hard-                                                                                                   |          |

|            | ened UART-RS counter. The last E1 is an end mark signifying the                                                                                                 |          |

|            | completeness of counting.                                                                                                                                       | 77       |

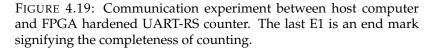

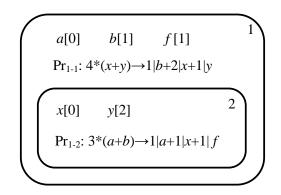

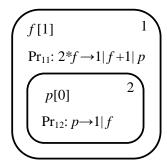

| 5.1        | Target numerical P system. The nested (membrane) structure is rep-                                                                                              |          |

| 0.1        | resented by a Venn diagram; the variables and the rules are placed in                                                                                           |          |

|            | corresponding locations; the initial value of variables follow them in                                                                                          |          |

|            | square brackets.                                                                                                                                                | 82       |

| 5.2        | Target enzymatic numerical P system.                                                                                                                            | 83       |

| 5.3        | The numerical P system generating Fibonacci sequence.                                                                                                           | 84       |

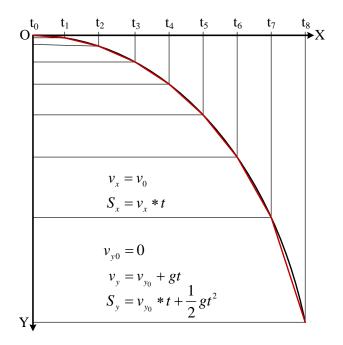

| 5.4        | The projectile motion. The red solid line is the piecewise-linear ap-                                                                                           | 01       |

| 5.4        | proximation of the non-linear trajectory.                                                                                                                       | 85       |

| 5.5        | The NPS corresponding to the system of difference equations given in                                                                                            | 05       |

| 5.5        |                                                                                                                                                                 | 85       |

| <b>E</b> 6 |                                                                                                                                                                 | 00       |

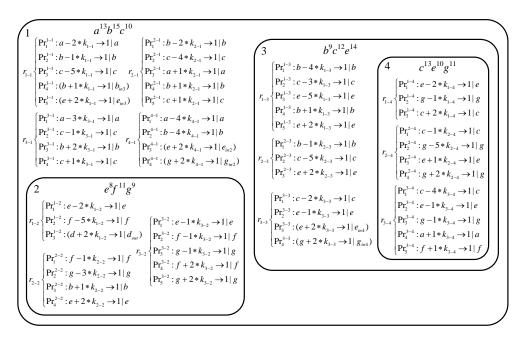

| 5.6        | The symbol object P system described in NPS form. A rewriting rule is                                                                                           |          |

|            | translated in a set of programs in which programs involving subtrac-                                                                                            |          |

|            | tion denote $obm_l$ and programs involving addition signify $obm_r$ . Pro-                                                                                      |          |

|            | grams in parentheses are executed in membranes indicated by their                                                                                               | ~-       |

|            | subscripts, not in membranes containing them.                                                                                                                   | 87       |

| 5.7        | The effect of rules is equivalent to the set of programs in each mem-                                                                                           |          |

|            | brane, where $k_{i-j}$ denotes instance of rule $r_{i-j}$ . Once $k_{i-j}$ have com-                                                                            | 0.5      |

|            | puted, these programs are used to update multiplicity of objects                                                                                                | 88       |

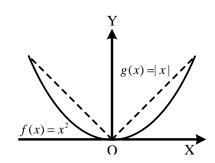

| 5.8   | Linear approximation of $f(x) = x^2$ by $g(x) =  x $                                | 90  |

|-------|-------------------------------------------------------------------------------------|-----|

| 5.9   | The predator-prey GNPS. A predicates and its associated rule are placed             |     |

|       | in two rows in a brace to show them more explicitly                                 | 90  |

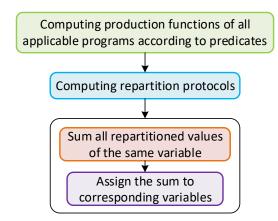

|       | Main procedures of FSPIP method                                                     | 92  |

| 5.11  | GNPS system from Example 5.7. The predicate for each program is                     |     |

|       | taken to a separate line before it. Variables in red and blue indicate              |     |

|       | input and output variables respectively. Others are intermediate vari-              |     |

|       | ables                                                                               | 93  |

| 5.12  | GNPS model for case study 1. It implements the core computations of                 |     |

|       | Sobel image edge detection algorithm. The predicate $P_i$ and program               |     |

|       | $Pr_i$ are written in two lines to render them better. GNPS1 has a skin             |     |

|       | membrane containing 4 programs and 19 real-value variables. Input                   |     |

|       | variables are highlighted in red. Output variables are highlighted in               |     |

|       | blue.                                                                               | 94  |

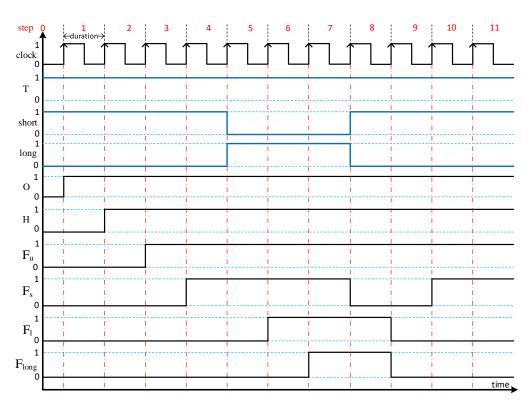

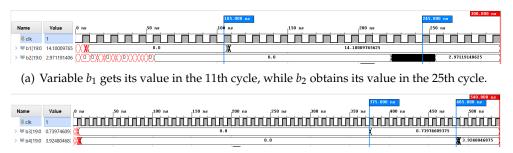

| 5.13  | Post implementation timing simulation of GNPS1. Port $b_1$ , $b_3$ and              |     |

|       | $b_4$ obtain their steady output value after the eleventh rising edge of            |     |

|       | clock, indicating it costs 110 ns to get results. For $b_2$ , its steady output     |     |

|       | value emerges after sixteenth rising edge, costing 160 ns to compute                | 07  |

| E 14  | outcome                                                                             | 96  |

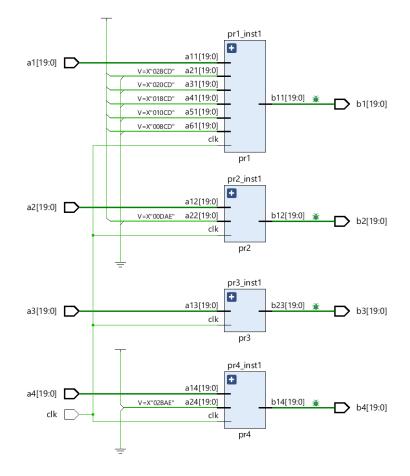

| 5.14  | step to stop. There is no one-to-one correspondence between a clock                 |     |

|       | cycle and a GNPS step. For complex arithmetic computations, one                     |     |

|       | step of GNPS requires more than one clock cycle                                     | 96  |

| 5 1 5 | Hardware debug of GNPS1. Input variables cannot be debugged so                      | 70  |

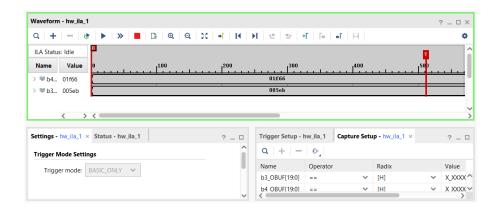

| 0.10  | there is no clock signal. Values are represented in hexadecimal, 01f66              |     |

|       | is 8038 in decimal. $8038 \div 2^{11} = 3.9248046875$ , which is the value of       |     |

|       | $b_4$ . 005eb is 1515 in decimal, $1515 \div 2^{11} = 0.73974609375$ , which is the |     |

|       | value of $b_3$                                                                      | 97  |

| 5.16  | GNPS model for case study 2 is numbered as GNPS2. The equations                     |     |

|       | inside are the core computations of Sobel image edge detection al-                  |     |

|       | gorithm. GNPS2 has 5 membranes and evolves 4 steps to reach halt                    |     |

|       | condition. Programs in each membrane compute concurrently while                     |     |

|       | each membrane execute serially.                                                     | 98  |

| 5.17  | Post implementation timing simulation of GNPS2. The real timing of                  |     |

|       | $b_2$ and $b_3$ is a little different than expected                                 | 98  |

| 5.18  | Software simulation of GNPS2. It is assumed that GNPS2 evolves four                 |     |

|       | steps to stop. CPU of the host computer costs 0.009306 s to get results.            | 99  |

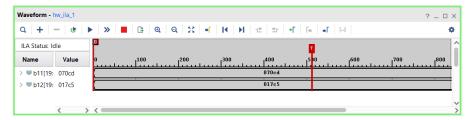

| 5.19  | Hardware debug of GNPS2. Values are represented in hexadecimal,                     |     |

|       | 070cd is 28877 in decimal. $28877 \div 2^{11} = 14.10009765625$ , which is          |     |

|       | the value of $b_1$ . 17c5 is 6085 in decimal, $6085 \div 2^{11} = 2.97119140625$ ,  |     |

|       | which is the value of $b_2$ .                                                       | 99  |

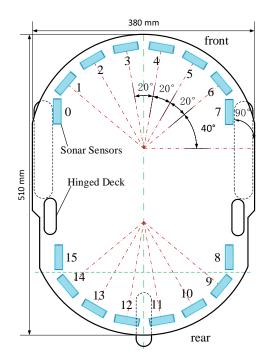

| 6.1   | This is a plan view of Pioneer 3 DX robot which is covered by a hinged              |     |

| 0.1   | deck on the top. The 16 rectangles in light blue are the sonar sensors              |     |

|       | surrounding the robot, just beneath the hinged deck. Sensors are ar-                |     |

|       | ranged in two arrays in the front and in the rear. The layout of sensors            |     |

|       | in two arrays is identical.                                                         | 103 |

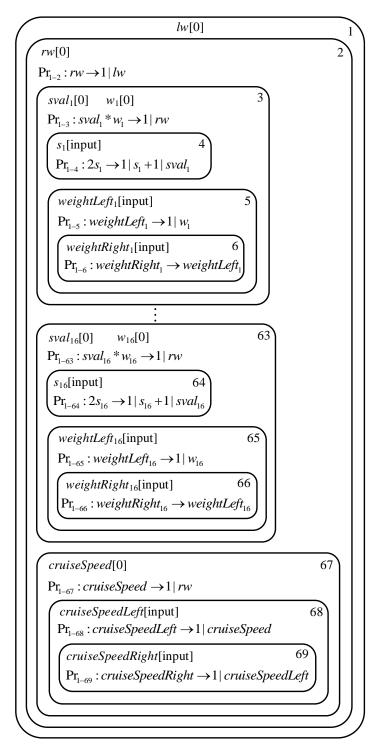

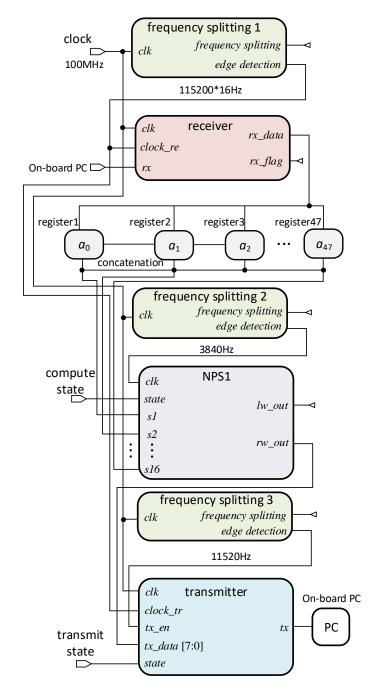

| 6.2   | The NPS controller performing control law of Formula 6.1, which will                |     |

|       | be implemented in FPGA. This numerical P system is called NPS1                      |     |

|       | below                                                                               | 104 |

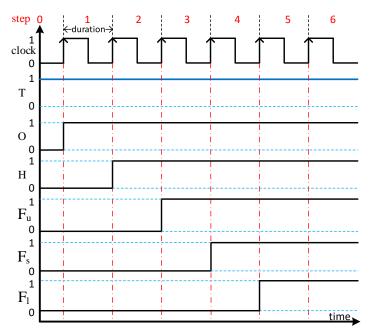

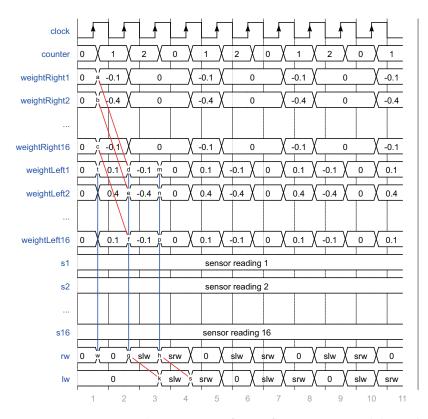

| 6.3  | Expected timing waveform of NPS1 RTL model. Red lines indicate value transfers from $weightRight_i$ to $weightLeft_i$ and from $rw$ to $lw$ .<br>Blue lines signifies parallel computing of programs in associated mem- |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | branes                                                                                                                                                                                                                  |

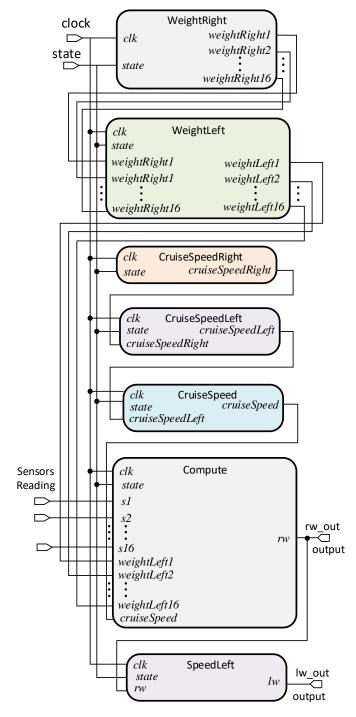

| 6.4  | RTL model of NPS1 consists of 7 modules, although NPS1 has 69 membranes. There is a one-to-one correspondence between mem-                                                                                              |

|      | branes and programs inside. This correspondence transforms the im-                                                                                                                                                      |

|      | plementation of a membrane to implementation a set of programs                                                                                                                                                          |

|      | inside. Programs can be synchronized in one module with parallel                                                                                                                                                        |

|      | constructs of Verilog. This is the reason why the number of modules                                                                                                                                                     |

|      | can be reduced substantially. A <i>state</i> port is added to NPS1 so that it                                                                                                                                           |

|      | possesses idle and busy state                                                                                                                                                                                           |

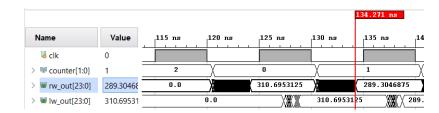

| 6.5  | Waveform of behavioral simulation of NPS1. The values of $weightLeft_i$                                                                                                                                                 |

|      | alternate as expected when <i>counter</i> loops its value. Sensors' readings                                                                                                                                            |

|      | $s_i$ take the value in the last row of Table 6.1 which are abridged from                                                                                                                                               |

|      | waveform for the sake of taking a screenshot including computing                                                                                                                                                        |

| ( (  | results $rw$ -out and $lw$ -out                                                                                                                                                                                         |

| 6.6  | Results of <i>PeP</i> simulation of NPS1. It costs 0.011703 seconds to obtain results.                                                                                                                                  |

| 6.7  | results                                                                                                                                                                                                                 |

| 6.8  | Hardware debug of NPS1. Numbers are represented in hexadecimal. 110                                                                                                                                                     |

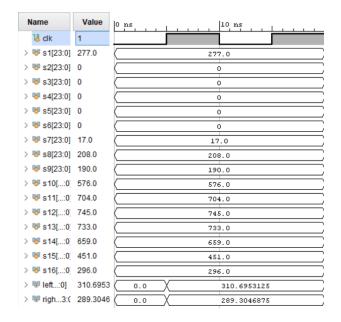

| 6.9  | Enzymatic numerical P system ENPS1. The value of enzyme <i>e</i> is larger                                                                                                                                              |

| 0.7  | than that of <i>f</i> in membrane 1, so these two programs can take place.                                                                                                                                              |

|      | Enzymes $e_i$ have greater values than weight values so the 16 programs                                                                                                                                                 |

|      | in membrane 2 can execute in parallel                                                                                                                                                                                   |

| 6.10 | Waveform of behavioral simulation of ENPS1. Left and right wheel                                                                                                                                                        |

|      | speed variables gain their expected values after the first rising edge 111                                                                                                                                              |

| 6.11 | PeP simulation results of ENPS1. It costs 0.002993 seconds to obtain                                                                                                                                                    |

|      | results                                                                                                                                                                                                                 |

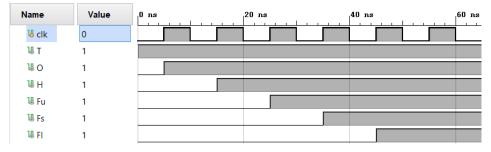

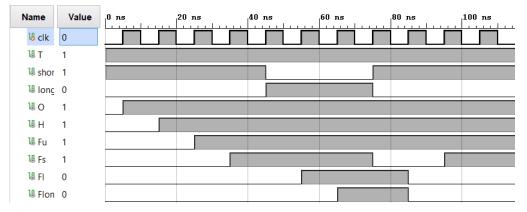

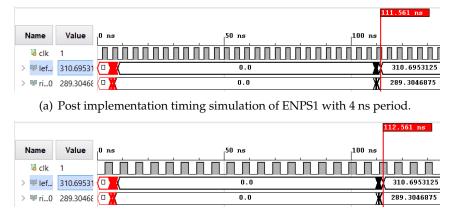

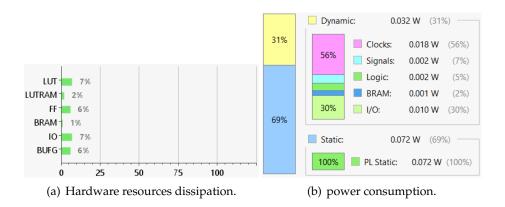

| 6.12 | Post implementation timing simulation waveform of ENPS1. 112 ns                                                                                                                                                         |

|      | is regarded as the elapsed time to get results. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $112$                                                                                                                               |

|      | Hardware debug of ENPS1                                                                                                                                                                                                 |

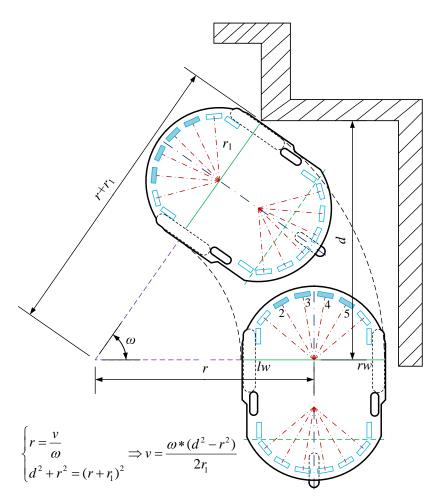

|      | Obstacle avoidance kinetics analysis of Pioneer 3 DX robot 113                                                                                                                                                          |

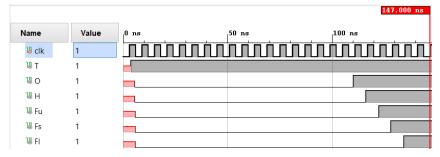

|      | GNPS3 which carrys out control law 2                                                                                                                                                                                    |

| 6.16 | Post implementation timing simulation of GNPS3. The implemented                                                                                                                                                         |

|      | clock period is 45 ns whose half period cannot defined so 44 ns and                                                                                                                                                     |

|      | 46 ns are set as periods. So the elapsed time is the mean time which is                                                                                                                                                 |

| ( 17 | 260.657 ns                                                                                                                                                                                                              |

|      | <i>PeP</i> simulation of GNPS3. It costs 0.020997 s to output results 115<br>Hardware debug of CNPS2. Numbers are represented in heyedosimel. 115                                                                       |

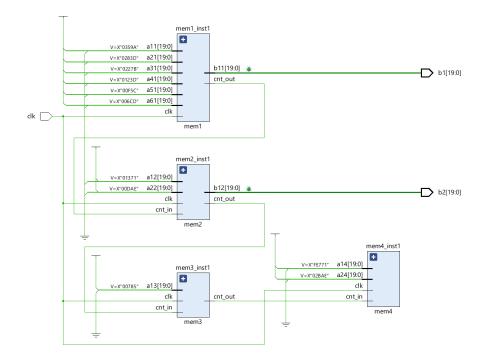

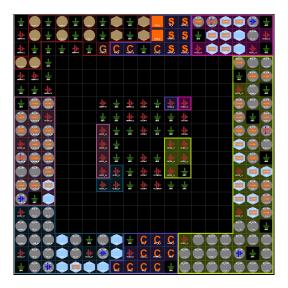

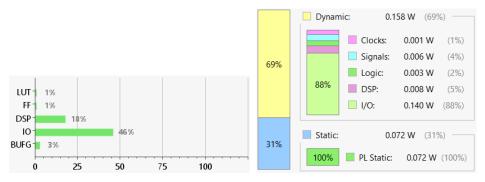

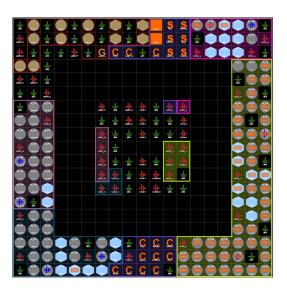

|      | Hardware debug of GNPS3. Numbers are represented in hexadecimal. 115<br>RTL model of UART-NPS1                                                                                                                          |

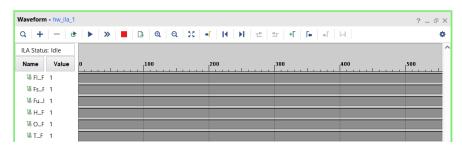

|      | Numbers are in hexadecimal for real numbers are represented in fixed                                                                                                                                                    |

| 0.20 | point binary numbers. These data repeats 00 00 00, 26 D6 40 and 24 29                                                                                                                                                   |

|      | C0. Two digits of hexadecimal correspond to 8 bits in binary so three                                                                                                                                                   |

|      | dual hexadecimal pairs comprise a 24-bit binary number. These three                                                                                                                                                     |

|      | repeated data strings are 0, 310.6953125 and 289.3046875 in decimal,                                                                                                                                                    |

|      | which are the desired three outcomes of $rw$ of NPS1                                                                                                                                                                    |

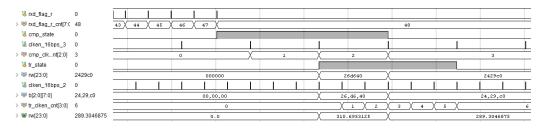

| 6.21        | When input counter counts from 0 to 47, sensor readings are received into NPS1. Computing signal <i>cmp-state</i> converts from 0 to 1 to trigger computing. When left wheel speed are outputted, transmitting signal <i>tr-state</i> shifts from 0 to 1 to trigger transmitting. At the time when transmitting counter signal <i>tr-clken-cnt</i> has value of 5, <i>tr-state</i> switches its value to terminate transmitting | 118  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

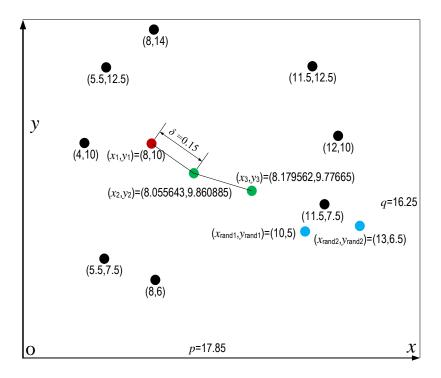

| 7.1         | Graphical representation of the target RRT. Black points indicates ob-<br>stacle points and the red point denotes robot initial point. Blue points                                                                                                                                                                                                                                                                              |      |

| 7.2         | are random points and green points are generated RRT points<br>The RRT-GNPS designed to execute RRT algorithm which generates<br>two RRT points in eight obstacle points. It consists of 34 membranes                                                                                                                                                                                                                           |      |

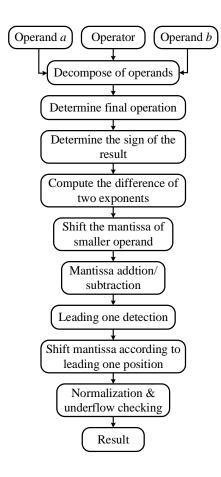

| 7.3         | including the skin membrane                                                                                                                                                                                                                                                                                                                                                                                                     |      |

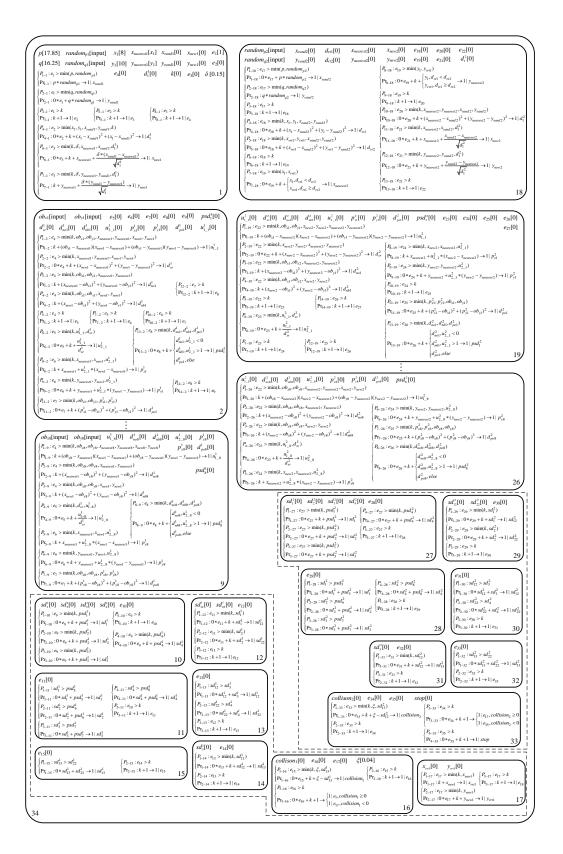

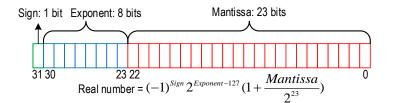

| 7.4         | s to get results. The results of <i>PeP</i> save 2 significant digits. $\dots$ The dynamic range is represented using radix 2 as well as radix 10.                                                                                                                                                                                                                                                                              |      |

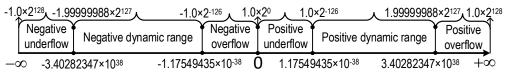

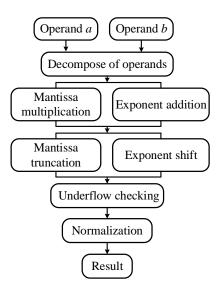

| 7.5         | Zero is denoted by $1.0 \times 2^0$ , $-\infty$ by $-1.0 \times 2^{128}$ and $+\infty$ by $1.0 \times 2^{128}$ . Procedure diagram of the adder. This is a composite unit which can                                                                                                                                                                                                                                             |      |

|             | perform addition and subtraction.                                                                                                                                                                                                                                                                                                                                                                                               |      |

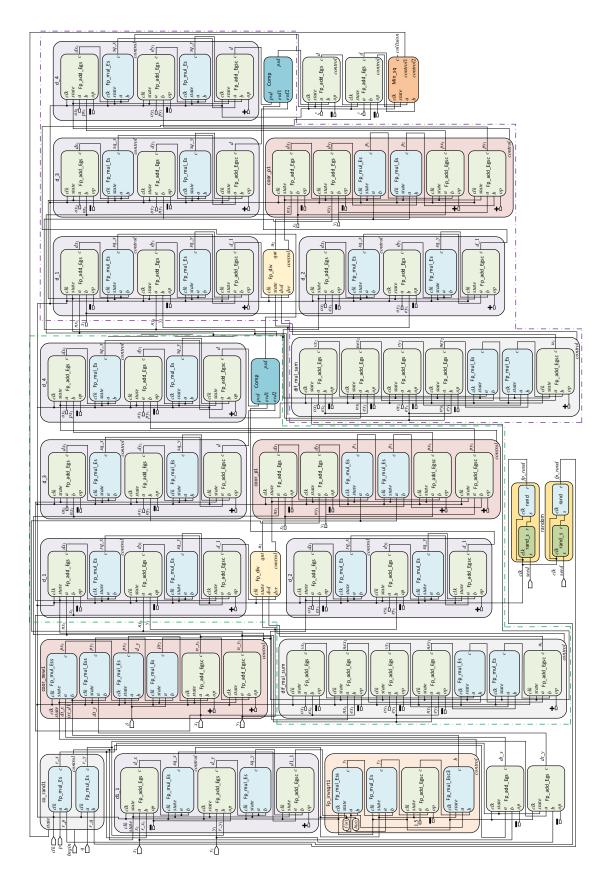

| 7.6         | Procedure diagram of the multiplier.                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 7.7         | RTL model of the RRT-GNPS generating the first RRT point                                                                                                                                                                                                                                                                                                                                                                        | 134  |

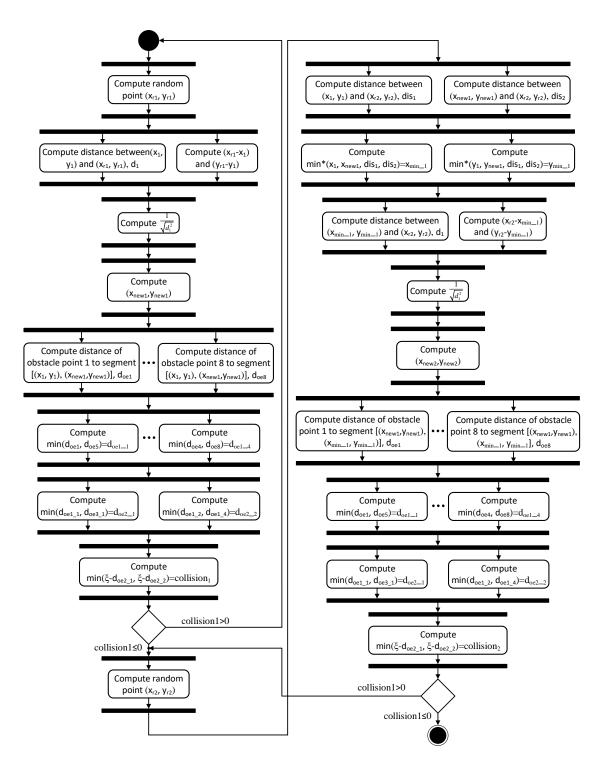

| 7.8         | The whole process of RRT-GNPS RTL model characterized by UML                                                                                                                                                                                                                                                                                                                                                                    |      |

|             | activity diagram.                                                                                                                                                                                                                                                                                                                                                                                                               | 136  |

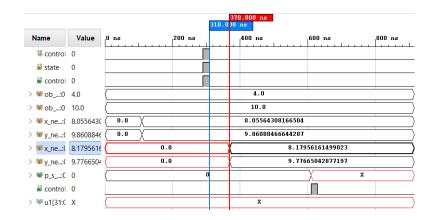

| 7.9         | The behavioral simulation waveform of RRT-GNPS RTL model. The                                                                                                                                                                                                                                                                                                                                                                   |      |

|             | red waveforms are caused by the lack of initial values of variables.                                                                                                                                                                                                                                                                                                                                                            |      |

|             | This phenomenon can be eliminated by assigning initial values to <i>reg</i>                                                                                                                                                                                                                                                                                                                                                     |      |

|             | variables.                                                                                                                                                                                                                                                                                                                                                                                                                      | 137  |