# Towards Efficient Reuse of Software Programmable Streaming Coarse Grained Reconfigurable Architectures

Elias Barbudo Franco

#### ▶ To cite this version:

Elias Barbudo Franco. Towards Efficient Reuse of Software Programmable Streaming Coarse Grained Reconfigurable Architectures. Hardware Architecture [cs.AR]. Université Gustave Eiffel, 2021. English. NNT: 2021UEFL2014. tel-03551361

## HAL Id: tel-03551361 https://theses.hal.science/tel-03551361

Submitted on 1 Feb 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## École doctorale nº 532 : Mathématiques et Sciences et Technologies de l'Information et de la Communication (MSTIC)

# THÈSE

pour obtenir le grade de docteur délivré par

## UNIVERSITE GUSTAVE EIFFEL

présentée publiquement par

### Elias Barbudo Franco

## Towards Efficient Reuse of Software Programmable Streaming Coarse Grained Reconfigurable Architectures

| Jury           |                           |                       |

|----------------|---------------------------|-----------------------|

| Prof.,         | Alejandro Castillo Atoche | Rapporteur            |

| Prof.,         | Jean-François Nezan       | Rapporteur            |

| Prof.,         | Michel Paindavoine        | Examinateur           |

| Prof.,         | Carlos Valderrama         | Examinateur           |

| Prof. Associé, | Thierry Grandpierre       | Co-directeur de thèse |

| Prof.,         | Eva Dokladalova           | Directrice de thèse   |

|                |                           |                       |

T----

LIGM, Univ Gustave Eiffel CNRS, ESIEE Paris, F-77454 Marne-la-Vallée

### Abstract

Coarse-Grained Reconfigurable Architectures (CGRA) are designed to deliver high performance while drastically reducing the latency of the computing system. There are several types of CGRA according to the structure, application, type of resources, and memory infrastructure. We focus our work on a subset of CGRA designs that we call Software Programmable Streaming Coarse-Grained Reconfigurable Architectures (SPS-CGRA). An SPS-CGRA is a more or less complex array of coarse-grained heterogeneous hardware resources with a coarser granularity than the classical. An SPS-CGRA can perform spatial and temporal computations at low latency. Its stream-based processing provides high performance maintaining a level of flexibility. Although they are often highly domain-specifically optimized, they keep several levels of custom post-fabrication programmability, given by a set of parameters, so that they can be reused. However, their reuse is generally limited due to the complexity of identifying the best allocation of the processing tasks into the hardware resources. Another limiting point is the complexity of producing a reliable performance analysis for each new implementation since no mature tool exists.

To solve these problems, we propose a complete mapping and scheduling framework that targets SPS-CGRA. We introduce a generic hardware model allowing one to express these intrinsically custom levels of flexibility without neglecting data access and system configuration control. We also propose a performance estimation analysis based on resource latency description, allowing to obtain the upper bound of the computing cost. To complete, we present four different solutions for the mapping and scheduling problem: a List-based algorithm with backtracking, a Lookahead-based heuristic, a Bayesian-based heuristic and, a Q-Learning mapping algorithm. We evaluate and compare our solutions against an exhaustive approach in a real-life example and illustrate the benefits and efficiency of the proposed framework.

### Résumé

Les architectures reconfigurables à gros grains (CGRA) sont conçues pour offrir des performances élevées tout en réduisant considérablement la latence du système informatique. Il existe plusieurs types de CGRA en fonction de la structure, de l'application, du type de ressources et de l'organisation de la mémoire. Nous concentrons notre travail sur un sous-ensemble de conceptions CGRA que nous appelons les architectures gros grain, flot de données, reconfigurables et programmables (SPS-CGRA). Un SPS-CGRA est une grille plus ou moins complexe de ressources matérielles hétérogènes à gros grains avec une granularité plus grande que les architectures CGRA classiques. Un SPS-CGRA peut effectuer de grandes quantités de calculs avec une faible latence. Son principe de traitement orienté flot de données offre des performances élevées tout en maintenant un niveau élevé de flexibilité. Bien qu'ils soient souvent hautement optimisés pour un domaine spécifique, ils conservent plusieurs niveaux de programmation après la phase de configuration Cette programmation s'effectue par le biais de paramètres, rendant ainsi possible leur réutilisation. Cependant, cette réutilisation est généralement limitée en raison de la complexité de l'identification de la meilleure allocation des tâches de traitement sur les ressources matérielles. Un autre facteur limitant la réutilisation est la complexité à produire une analyse de performance fiable pour chaque nouvelle implémentation car généralement il n'existe aucun outil spécifique pour explorer et exploiter pleinement le potentiel des architectures ainsi produites.

Pour résoudre ces problèmes, nous proposons un cadre complet de distribution et d'ordonnancement qui cible les SPS-CGRA. Nous introduisons un modèle théorique et générique de l'architecture matérielle permettant d'exprimer ces niveaux de flexibilité intrinsèquement personnalisés, ainsi que l'accès aux données et le contrôle de la configuration du système, souvent négligés dans les travaux existants. Nous proposons également une analyse d'estimation des performances, basée sur la latence des ressources. Pour compléter, nous présentons quatre solutions différentes pour résoudre le problème de distribution et d'ordonnancement : un algorithme avec retour en arrière basé sur des listes, une heuristique basée sur les algorithme de type "lookahead", une heuristique basée sur un algorithme Bayésien et un algorithme d'ordonnancement basé sur le Q-learning. Pour finir, nous évaluons et comparons nos solutions sur des ensembles d'architectures et d'applications dont les paramètres sont générés aléatoirement, ainsi que sur deux applications réelles.

## Acknowledgements

First, I would like to express my gratitude to my director Eva Dokladalova, thank you for your guidance and support. I want to thank my co-director Thierry Grandpierre, it was a pleasure to benefit and learn from your knowledge.

I am very thankful to the reviewers of this thesis, Alejandro Castillo and Jean-François Nezan, your insights, and bits of advice are deeply appreciated. I also want to thank Michel Paindavoine and Carlos Valderrama for being part of my thesis jury. I am grateful for your advice and words towards this work.

I would like to thank CONACYT for financially support this work, and to the Université Gustave Eiffel, ESIEE Paris, and Laboratory Gaspard Monge, where this work was prepared.

To my parents, Ruddy and Elvira, I am deeply grateful for your support and love. To my sister Angelica, thank you very much for all your advice and help. To my brother Ruddy, thank you very much for your support. I thank all my family for being there for me. Special thanks to my lovely Noemi, who helped me through this entire journey.

I would like to thank Rosemberg Rodriguez for his friendship and support. My appreciation goes to all my friends from Mexico and France. I am deeply grateful that there was always someone to talk to and share my thoughts.

# Contents

| 1 | $\mathbf{Intr}$ | oduction 10                                                                    |

|---|-----------------|--------------------------------------------------------------------------------|

|   | 1.1             | Reusability of Time-Critical Systems                                           |

|   | 1.2             | State of the Art: Development Tools and Methodologies                          |

|   | 1.3             | Coarse-Grained Reconfigurable Architectures                                    |

|   | 1.4             | Software Programmable Streaming Coarse-Grained Reconfigurable Architectures 19 |

|   | 1.5             | Thesis Contributions                                                           |

|   | 1.6             | Thesis Outline                                                                 |

| Ι | Mo              | deling 28                                                                      |

| 2 | App             | olication Model 29                                                             |

|   | 2.1             | Introduction                                                                   |

|   | 2.2             | State of the Art                                                               |

|   |                 | 2.2.1 Dependence Graph                                                         |

|   |                 | 2.2.2 Task Model                                                               |

|   |                 | 2.2.3 Parallel Synchronous Task Model                                          |

|   |                 | 2.2.4 Digraph Real-Time Task Model                                             |

|   |                 | 2.2.5 Non Cyclic Recurrent Real-Time Task Model                                |

|   |                 | 2.2.6 Generalized Multiframe Task Model                                        |

|   |                 | 2.2.7 Recurring Real-Time Task Model                                           |

|   |                 | 2.2.8 3-Phase Model                                                            |

|   |                 | 2.2.9 Synchronous Dataflow Graph                                               |

|   |                 | 2.2.10 Algorithm Architecture Matching                                         |

|   |                 | 2.2.11 Directed Acyclic Graph                                                  |

|   |                 | 2.2.12 Directed Graph                                                          |

|   |                 | 2.2.13 Boolean Dataflow Graph                                                  |

|   |                 | 2.2.14 Others                                                                  |

|   |                 | 2.2.15 Discussion                                                              |

|   | 2.3             | Proposed Application Model                                                     |

|   | 2.4             | Formal Application Model                                                       |

|   | 2.5             | Examples of Real-Life Applications                                             |

|   |                 | 2.5.1 Alternated Sequential Filter                                             |

|   |                 | 2.5.2 Road Line Orientation Detection                                          |

|   | 2.6             | Conclusions                                                                    |

| 3 | Har             | dware Model 42                                                                 |

|   | 3.1             | Introduction                                                                   |

|   | 3.2             | State of the Art                                                               |

|   |                 | 3.2.1 Processor-Based Systems                                                  |

|   |                 | 3.2.2 Algorithm-Architecture Matching                                          |

|   |                 | 3.2.3 Multiprocessor System-on-Chip                                            |

|    |                  | 3.2.4 Network-on-Chip                                                       | 44 |

|----|------------------|-----------------------------------------------------------------------------|----|

|    |                  | 3.2.5 Coarse-Grained Reconfigurable Architectures                           | 45 |

|    |                  | 3.2.6 Field Programmable Gate Array                                         | 45 |

|    |                  | 3.2.7 Discussion                                                            |    |

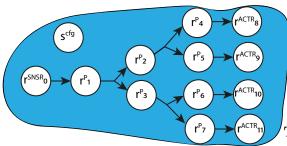

|    | 3.3              | Software Programmable Streaming Coarse Grained Reconfigurable Architectures | 47 |

|    |                  | 3.3.1 Architecture Resources                                                | 48 |

|    |                  | 3.3.2 Hardware Described Through Latency                                    |    |

|    | 3.4              | Formal Model                                                                |    |

|    |                  | 3.4.1 Set $S$ of SPS-CGRA Resources                                         |    |

|    |                  | 3.4.2 Sequencer Node $s^{CFG}$                                              |    |

|    |                  | R3.4.3 Hardware Resources $R$                                               |    |

|    |                  | $8.4.4$ Processing Resources Subset $\mathbb{R}^P$                          |    |

|    |                  | 3.4.5 Communication Resources Subset $R^C$                                  | 54 |

|    |                  | 3.4.6 Memory Resources Subset $R^M$                                         | 56 |

|    |                  | 3.4.7 Fork-Join Special Nodes                                               |    |

|    | 3.5              | •                                                                           |    |

|    | 5.5              | Examples                                                                    | 60 |

|    |                  | 3.5.1 Communication Resources $R^{WR}$ and $R^{RD}$                         | 61 |

|    |                  | 3.5.3 Memory Resources $R^M$                                                |    |

|    |                  | ·                                                                           |    |

|    |                  | 3.5.4 Fork-Join Special Nodes                                               |    |

|    | 2.0              | 3.5.5 The Morphological Co-Processor Unit                                   |    |

|    | 3.6              | Conclusions                                                                 | 69 |

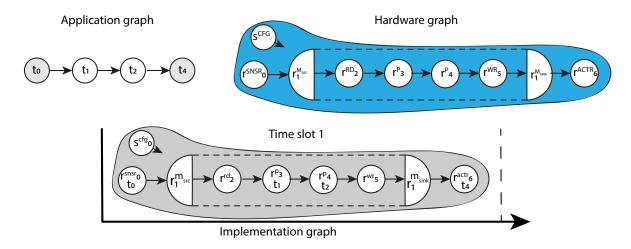

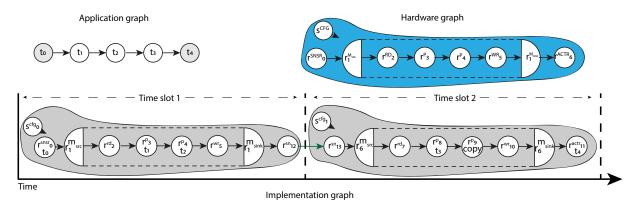

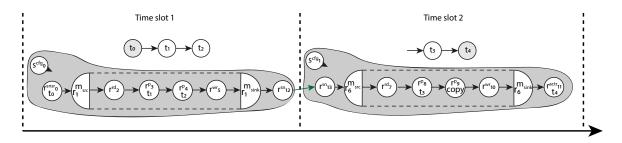

| 4  | Imp              | ementation Model                                                            | 70 |

| -  | 4.1              | Introduction                                                                |    |

|    | 4.2              | Proposed Implementation Model                                               |    |

|    | 4.3              | Formal Implementation Model                                                 |    |

|    | 4.0              | 4.3.1 Configuration Control Nodes $S^{cfg}$                                 |    |

|    |                  | 4.3.2 Processing Resources $R^p$                                            |    |

|    |                  | 4.3.3 Communication Resources $R^c$                                         |    |

|    |                  | 4.3.4 Memory Resources $R^m$                                                |    |

|    |                  |                                                                             |    |

|    |                  | 1.3.5 Data Dependency Resources $R^{sn}$                                    |    |

|    | 4 4              | 4.3.6 Examples                                                              |    |

|    | 4.4              | Performance Evaluation                                                      | 76 |

|    |                  | 4.4.1 State of the Art                                                      | 76 |

|    |                  | 4.4.2 Methodology                                                           |    |

|    |                  | 4.4.3 Examples                                                              | 80 |

|    | 4.5              | Conclusions                                                                 | 91 |

|    |                  |                                                                             |    |

| ΙΙ | $\mathbf{M}_{i}$ | pping Algorithms                                                            | 92 |

| =  | T4-              | duction                                                                     | ΩĐ |

| 5  |                  |                                                                             | 93 |

|    | 5.1              | State of the art                                                            | 94 |

|    |                  | 5.1.1 List-Based Scheduling Algorithms                                      |    |

|    |                  | 5.1.2 Linear Programming                                                    | 96 |

|    |                  | 5.1.3 Reinforcement Learning                                                | 96 |

|    |                  | 5.1.4 Others                                                                |    |

|    | 5.2              | Discussion                                                                  | 98 |

|    | 5.3              | Conclusions                                                                 | 99 |

| 6                |            | -Based Mapping Algorithms                                   | 100   |

|------------------|------------|-------------------------------------------------------------|-------|

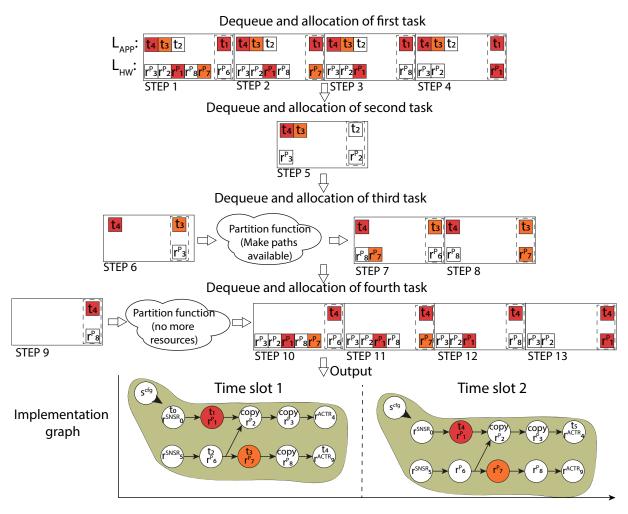

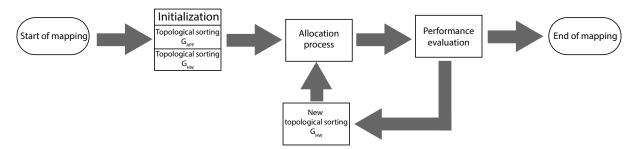

|                  | 6.1        | Single-Shot Mapping Algorithm                               |       |

|                  |            | 6.1.1 Methodology                                           |       |

|                  |            | 6.1.2 Discussion                                            | . 108 |

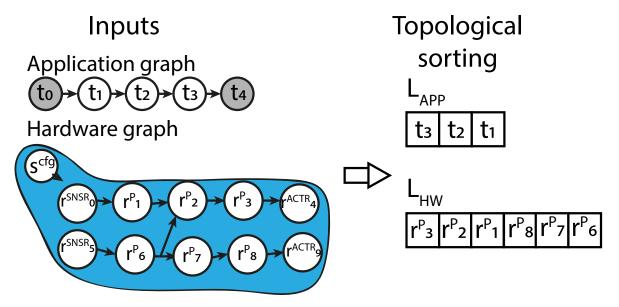

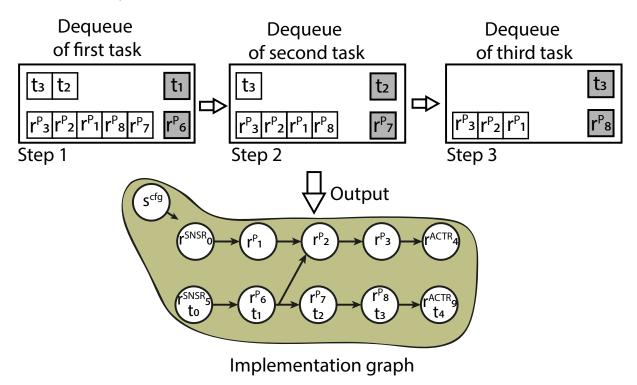

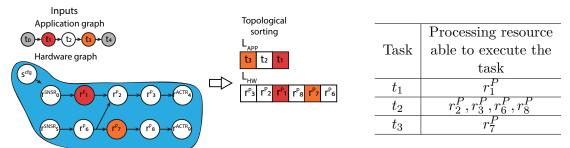

|                  | 6.2        | Topology-Aware Mapping Algorithm                            | . 108 |

|                  |            | 6.2.1 Methodology                                           |       |

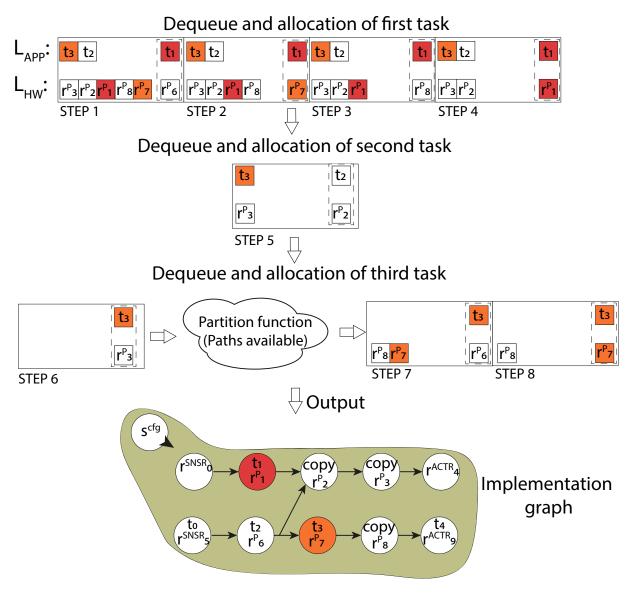

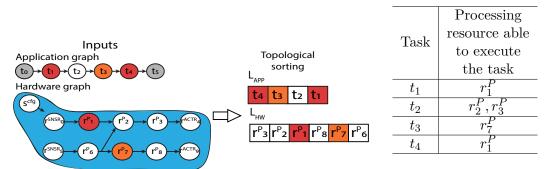

|                  |            | 6.2.2 Illustrations of the TA-MAP Principle                 | . 112 |

|                  |            | 6.2.3 Discussion                                            | . 118 |

|                  | 6.3        | Bayes-Based Heuristic Mapping Algorithm                     | . 119 |

|                  |            | 6.3.1 Bayes Theorem                                         | . 119 |

|                  |            | 6.3.2 Bayes Theorem Applied to the Mapping Problem          | . 120 |

|                  |            | 6.3.3 Illustration of the BB-MAP Principle                  | . 122 |

|                  | 6.4        | Conclusions                                                 | . 125 |

| 7                | Q-le       | earning Mapping Algorithm                                   | 126   |

| •                | 7.1        | Reinforcement Learning                                      |       |

|                  | 7.2        | Q-learning                                                  |       |

|                  | 7.3        | Q-learning Mapping and Scheduling Algorithm                 |       |

|                  | 1.0        | 7.3.1 Agent                                                 |       |

|                  |            | 7.3.2 Environment                                           |       |

|                  |            | 7.3.3 Rewards Policy                                        |       |

|                  |            | 7.3.4 Training                                              |       |

|                  |            | 7.3.5 Inference                                             |       |

|                  | 7.4        | Illustration of the Q-learning Principle                    |       |

|                  | 1.1        | 7.4.1 General Parameters and Policies                       |       |

|                  |            | 7.4.2 Example 1                                             |       |

|                  |            | 7.4.3 Example 2                                             |       |

|                  | 7.5        | Conclusions                                                 |       |

| 8                | Evn        | perimental Evaluation                                       | 140   |

| O                | 8.1        | Experimental Setup                                          |       |

|                  | 8.2        | Experimental Graphs                                         |       |

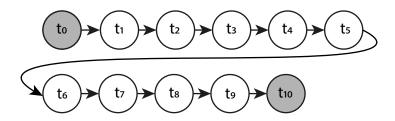

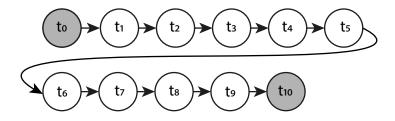

|                  | 0.2        | 8.2.1 Pipeline of Homogeneous Tasks                         |       |

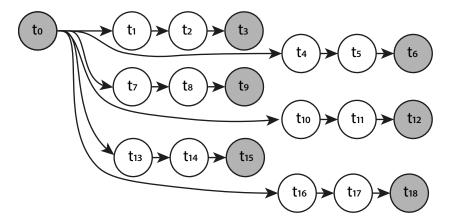

|                  |            | 8.2.2 Parallel Structure of Homogeneous Tasks               |       |

|                  |            | 8.2.3 Pipeline of Heterogeneous Tasks                       |       |

|                  |            | 8.2.4 Parallel and Hybrid Structures of Heterogeneous Tasks |       |

|                  | 8.3        | Pseudo-Random Graph Generator                               |       |

|                  | 0.0        | 8.3.1 Methodology                                           |       |

|                  |            | 8.3.2 Evaluation with Randomly Generated Graphs             |       |

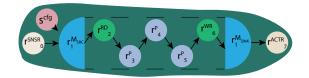

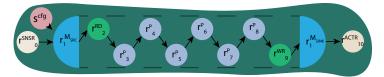

|                  | 8.4        | Real SPS-CGRA Example                                       |       |

|                  | 0.4        | 8.4.1 Hardware Model                                        |       |

|                  |            | 8.4.2 Application Graphs                                    |       |

|                  | 8.5        | Conclusions                                                 |       |

| 0                | <b>C</b> : | salusions and Danan actives                                 | 150   |

| 9                |            | Inclusions and Perspectives                                 | 170   |

|                  | 9.1        | Modeling                                                    |       |

|                  | 9.2        | Mapping Algorithms                                          |       |

|                  | 9.3        | Perspectives                                                | . 113 |

| P                | ublica     | ations and Communications                                   | 174   |

| $\mathbf{B}^{i}$ | bliog      | graphy                                                      | 175   |

# List of Figures

| 1.1  | Comparative study of hardware architectures from reusability point of view 11      |

|------|------------------------------------------------------------------------------------|

| 1.2  | Overall scheme of proposed modeling and mapping framework for SPS-CGRA 12          |

| 1.3  | Generic processing resource of a CGRA [1]                                          |

| 1.4  | Generic structure of a CGRA [1]                                                    |

| 1.5  | Logical structure of a CHESS processing element [2]                                |

| 1.6  | CHESS layout [2]                                                                   |

| 1.7  | Logical structure of a MorphoSys reconfigurable cell [3]                           |

| 1.8  | MorphoSys reconfigurable array [3]                                                 |

| 1.9  | Logical structure of a ADRES processing element [4, 5]                             |

| 1.10 | ADRES interconnection [4, 5]                                                       |

| 1.11 | Logical structure of a PipeRench processing element [6, 7]                         |

| 1.12 | PipeRench interconnection [6, 7]                                                   |

| 1.13 | Proposed microarchitectural classification of an SPS-CGRA                          |

| 1.14 | Architecture of the SPS-CGRA implementation of the standalone Lyra2REv2            |

|      | miner [8]                                                                          |

| 1.15 | Architecture of the SPS-CGRA proposed by Ngan et al. [9]                           |

|      | Architecture of the SPS-CGRA proposed by Ali et al. [10]                           |

|      | Simplified functional diagram of the P2IP [11]                                     |

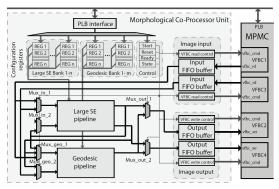

| 1.18 | Architecture of the MCPU [12]                                                      |

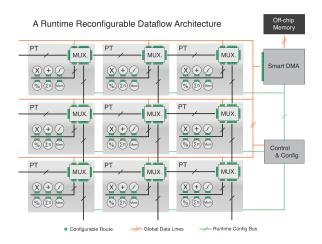

| 1.19 | Architecture of the NeuFlow                                                        |

|      | Architecture of the FlexFlow                                                       |

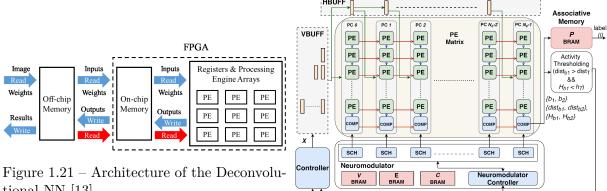

| 1.21 | Architecture of the Deconvolutional NN [13]                                        |

| 1.22 | Architecture of the a Life Long learning Convolutional NN [14]                     |

| 1.23 | Overview of the software solution for the easy reuse of SPS-CGRA 24                |

| 1.24 | General overview of the thesis                                                     |

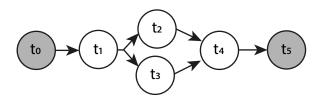

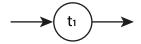

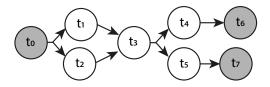

| 2.1  | Example of an application model hypergraph                                         |

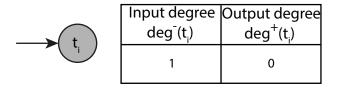

| 2.2  | Example of a single task                                                           |

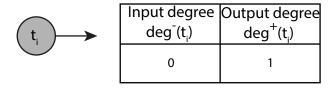

| 2.3  | Example of a single sensor                                                         |

| 2.4  | Example of a single actuator                                                       |

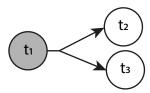

| 2.5  | Example of a task that broadcast is output data                                    |

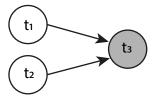

| 2.6  | Example of a task with input degree two                                            |

| 2.7  | Application model of the example $ASF^4$                                           |

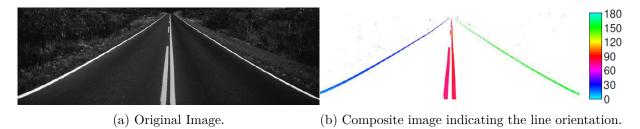

| 2.8  | Road line orientation detection [15]                                               |

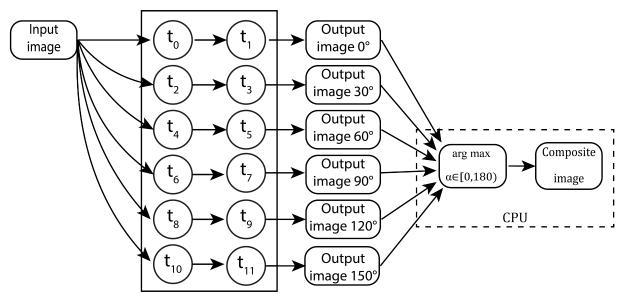

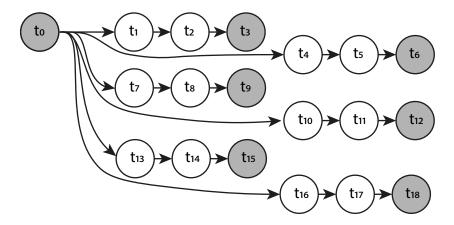

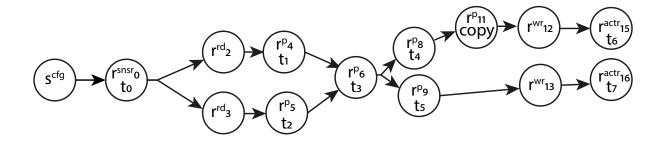

| 2.9  | Complete road line orientation detection                                           |

| 2.10 | Application model of the example of the road line orientation detection 40         |

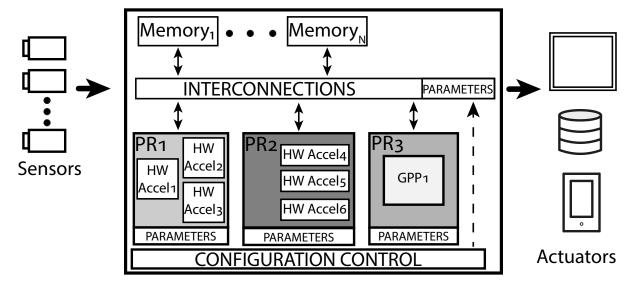

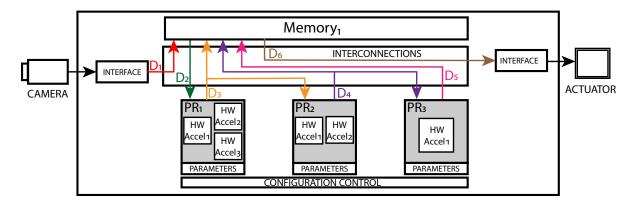

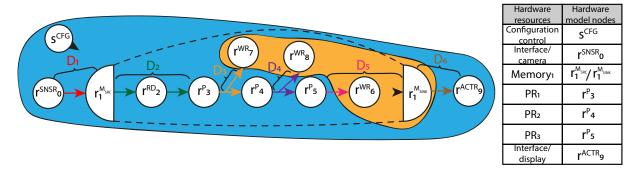

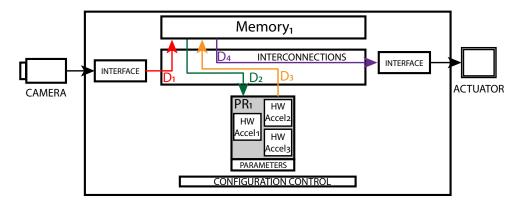

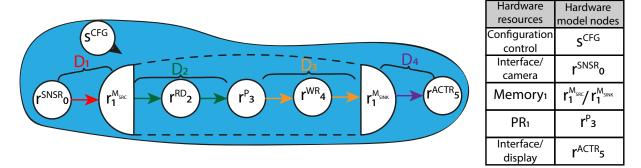

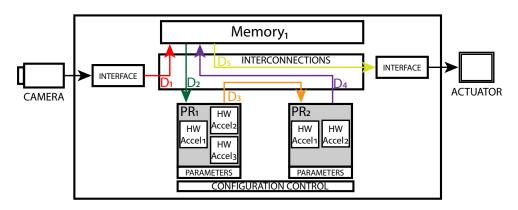

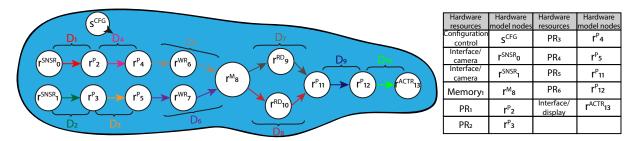

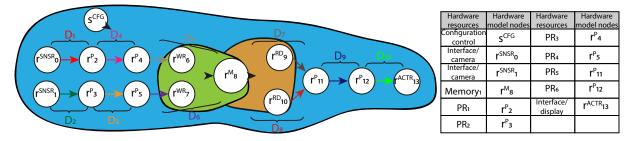

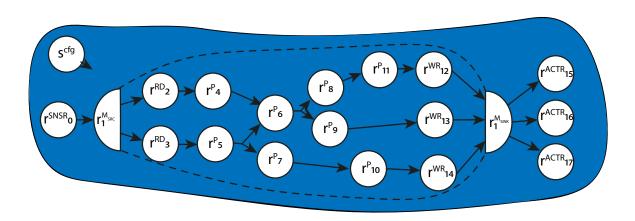

| 3.1  | Global architecture of an SPS-CGRA                                                 |

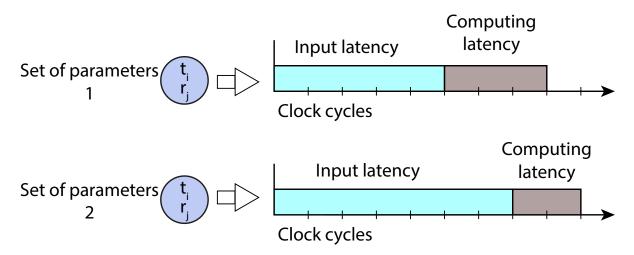

| 3.2  | Impact of the change of parameters on the latency of a resource                    |

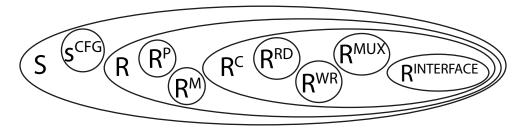

| 3.3  | Composition of the set $S$                                                         |

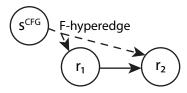

| 3.4  | Graphical representation of the connection of a $s^{CFG}$                          |

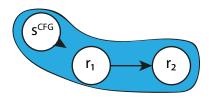

| 3.5  | Graphical representation of the connection of a $s^{CFG}$ through a solid plane 52 |

| 3.6  | Example of a single resource                                                       |

| 3.7  | Example of a single resource broadcasting its output                                      |

|------|-------------------------------------------------------------------------------------------|

| 3.8  | Example of single resource broadcasting its output without the connection to the          |

|      | configuration control node                                                                |

| 3.9  | An $r^{P}$ with two inputs and one output                                                 |

| 3.10 | Example of a $r_i^{sensor}$                                                               |

| 3.11 | Example of a $r_i^{actuator}$                                                             |

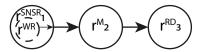

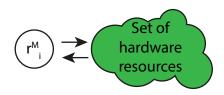

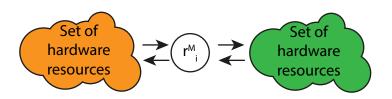

| 3.12 | Example of a node $r_2^M$ with $r_1^{SNSR}$ as predecessor and $r_3^{RD}$ as successor 57 |

| 3 13 | Example of a node $r_2^M$ with $r_1^{UR}$ as predecessor and $r_3^{ACTR}$ as successor 57 |

| 2 14 | Example of a node $r_2^M$ with $r_1^M$ as predecessor and $r_3^{RD}$ as successor 57      |

|      | Representation of a cyclic hardware model                                                 |

|      | ı v                                                                                       |

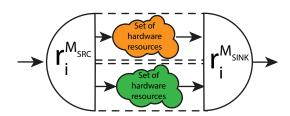

|      | Memory resource modelled by two connect memory nodes                                      |

|      | Representation of a cyclic hardware model                                                 |

| 3.18 | Memory resource modelled by two connect memory nodes with two independent                 |

|      | datapaths                                                                                 |

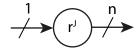

|      | Special join node                                                                         |

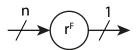

|      | Special fork node                                                                         |

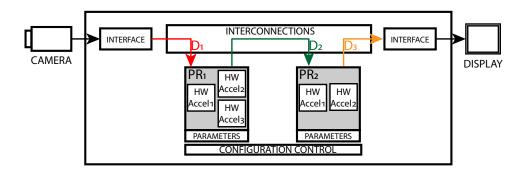

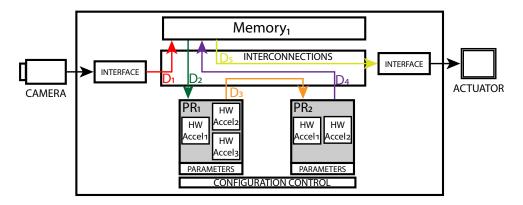

|      | SPS-CGRA example 1                                                                        |

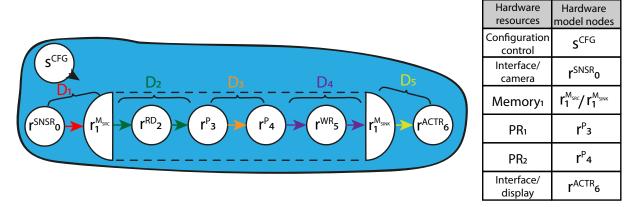

| 3.22 | Hardware model of SPS-CGRA example 1                                                      |

| 3.23 | SPS-CGRA example 2                                                                        |

| 3.24 | Hardware model of the SPS-CGRA example 2 61                                               |

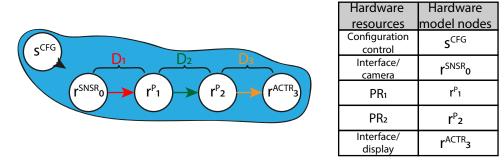

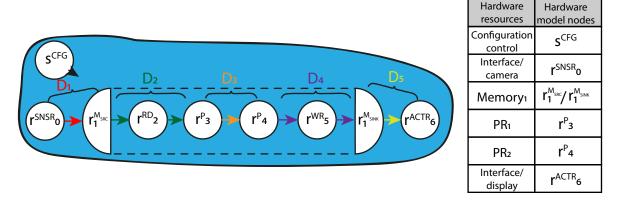

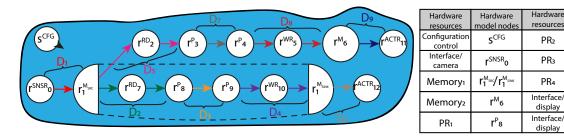

| 3.25 | SPS-CGRA example 3                                                                        |

| 3.26 | Hardware model of the SPS-CGRA example 3                                                  |

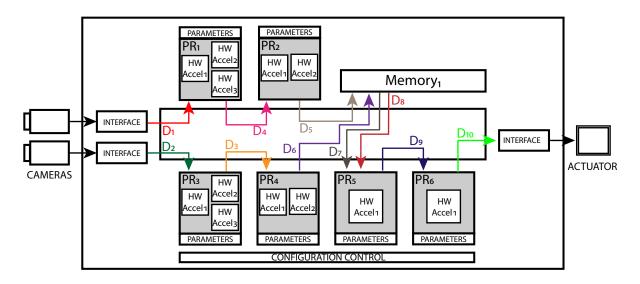

| 3.27 | SPS-CGRA example 4                                                                        |

|      | Hardware model of example 4                                                               |

|      | SPS-CGRA example 5                                                                        |

|      | Hardware model of example 5                                                               |

|      | SPS-CGRA example 6                                                                        |

|      | Hardware model of example 6                                                               |

|      | SPS-CGRA example 7                                                                        |

|      | hardware model of example 7                                                               |

|      | An equivalent hardware model of SPS-CGRA example 7                                        |

|      | SPS-CGRA example 8                                                                        |

|      |                                                                                           |

|      | Division of the regions of processing in example 8                                        |

|      | Hardware model of example 8 with the fork and join special nodes 67                       |

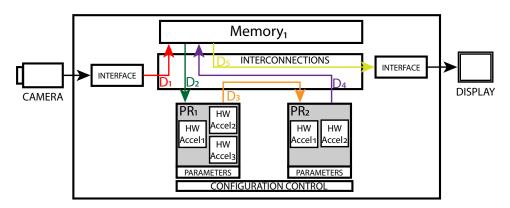

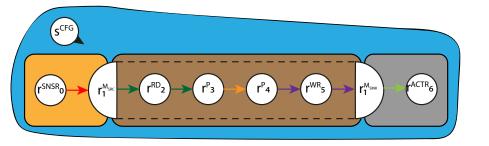

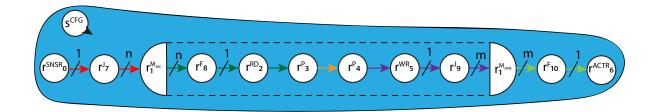

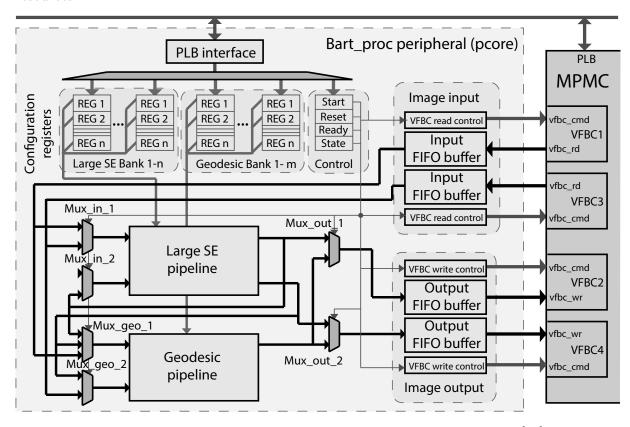

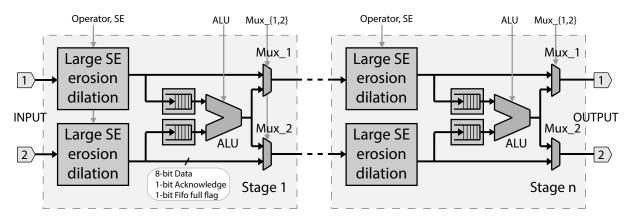

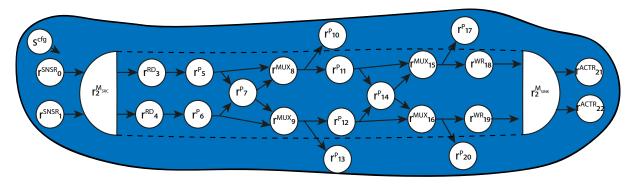

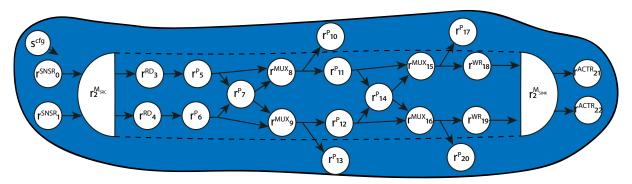

|      | Architecture of the Morphological Co-processor Unit [12]                                  |

|      | Large SE pipeline architecture                                                            |

| 3.41 | Hardware model of the MCPU                                                                |

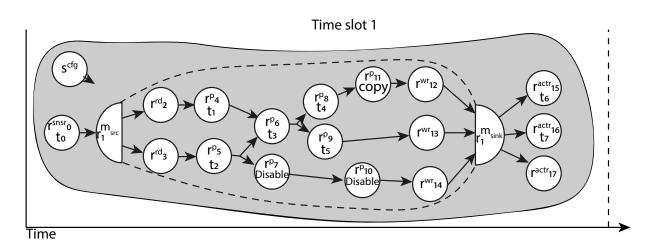

| 4.1  | Y-chart of a mapping and scheduling framework                                             |

| 4.2  | Example 1 of a generic implementation graph                                               |

|      |                                                                                           |

| 4.3  |                                                                                           |

| 4.4  | Inclusion of the data dependency resources between time slots                             |

| 4.5  | Inclusion of the data dependency resources between data-paths                             |

| 4.6  | Effects of the computing latency of a resource in the critical path                       |

| 4.7  | First implementation graph example                                                        |

| 4.8  | First evaluation graph example                                                            |

| 4.9  | Second implementation graph example                                                       |

| 4.10 |                                                                                           |

|      | Third implementation graph example                                                        |

| 4.12 | Third evaluation graph example                                                            |

| 4.13 | Fourth implementation graph example                                                       |

| 4.14 | Fourth evaluation graph example                                                           |

| 4.15 | Fifth implementation graph example                                                        |

| 4.16 | Fifth evaluation graph example                                                     | 82          |

|------|------------------------------------------------------------------------------------|-------------|

| 4.17 | Application graph for the performance evaluation example                           | 83          |

| 4.18 | Hardware graph for the performance evaluation example                              | 83          |

| 4.19 | Implementation graph for the performance evaluation example                        | 83          |

|      | Evaluation graph for performance evaluation example                                | 84          |

|      | Paths of the evaluation graph                                                      | 84          |

|      | Critical path of first set of parameters                                           | 85          |

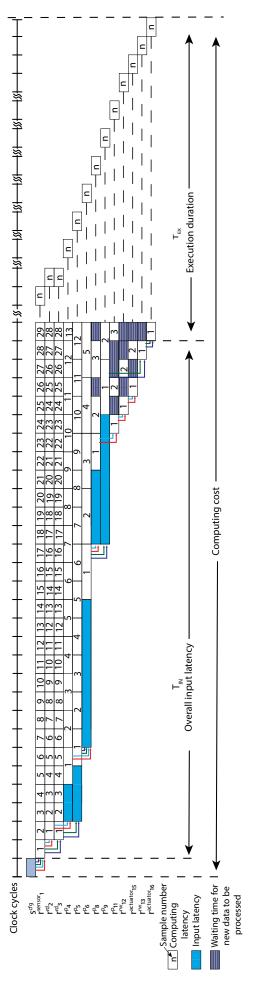

|      | Timing diagram of the first set of parameters                                      | 86          |

|      | Critical path for the second set of parameters                                     | 87          |

|      | Timing diagram for the second set of parameters.                                   | 88          |

|      | Critical path for the third set of parameters                                      | 89          |

|      | Timing diagram for the third set of parameters.                                    | 90          |

|      |                                                                                    |             |

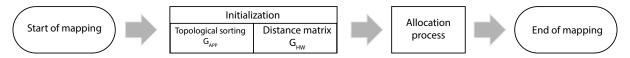

| 6.1  | Flow diagram of initialization                                                     |             |

| 6.2  | Allocation process                                                                 | .02         |

| 6.3  | Initialization process                                                             |             |

| 6.4  | Allocation process                                                                 |             |

| 6.5  | Initialization process                                                             | ۰06         |

| 6.6  | Allocation process                                                                 | .07         |

| 6.7  | Flow diagram of the SS-MAP algorithm (all topological sortings of $G_{HW}$ ) 1     | 108         |

| 6.8  | Flow diagram of the TA-MAP algorithm                                               |             |

| 6.9  | Graphical representation of the heuristic optimization                             |             |

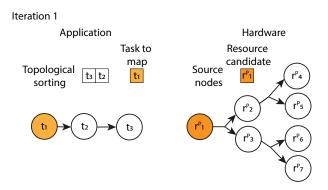

| 6.10 | Example application graph 1                                                        | .13         |

| 6.11 | Example hardware graph 1                                                           | .13         |

| 6.12 | First group of possible candidates for example 1                                   | 14          |

| 6.13 | Second group of possible candidates for example 1                                  | 14          |

| 6.14 | Third group of possible candidates for example 1                                   | ι15         |

| 6.15 | Application graph of example 2                                                     | ι15         |

| 6.16 | Hardware graph of example 2                                                        | 16          |

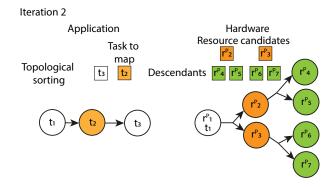

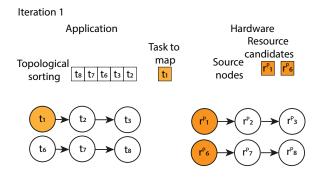

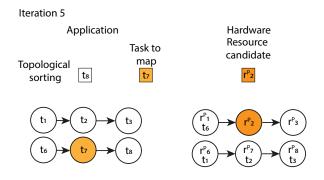

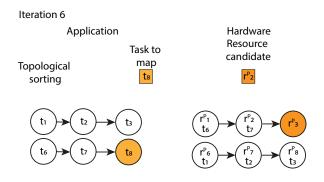

| 6.17 | First iteration for example 2                                                      | 16          |

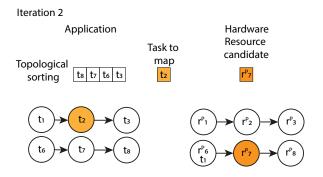

| 6.18 | Second iteration of example 2                                                      | 17          |

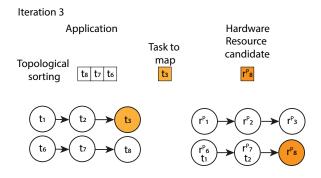

| 6.19 | Third iteration of example 2                                                       | 17          |

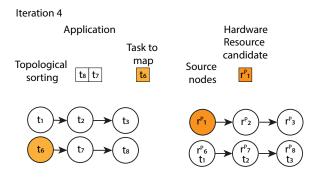

| 6.20 | Fourth iteration of example 2                                                      | 18          |

| 6.21 | Fifth iteration of example 2                                                       | 18          |

| 6.22 | Sixth iteration of example 2                                                       | 18          |

| 6.23 | Bayesian network                                                                   | 22          |

| 6.24 | Example application graph 1                                                        | 23          |

| 6.25 | Example hardware graph                                                             | 23          |

|      |                                                                                    |             |

| 7.1  | Basic principle of RL                                                              |             |

| 7.2  | Subgraphs and information given to the agent from the environment                  |             |

| 7.3  | Hardware graph of example 1                                                        |             |

| 7.4  | Application graph of example 1                                                     |             |

| 7.5  | Average rewards composition for example 1                                          | 138         |

| 7.6  | Hardware graph of example 2                                                        | 138         |

| 7.7  | Application graph of example 2                                                     |             |

| 7.8  | Average rewards composition for example 2                                          | 139         |

| 0 1  | First get of application around                                                    | 140         |

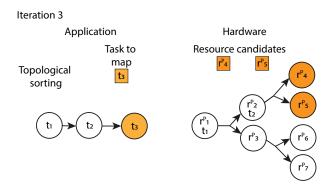

| 8.1  | First set of application examples                                                  |             |

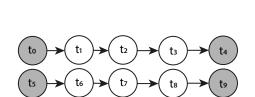

| 8.2  | 1                                                                                  | l43         |

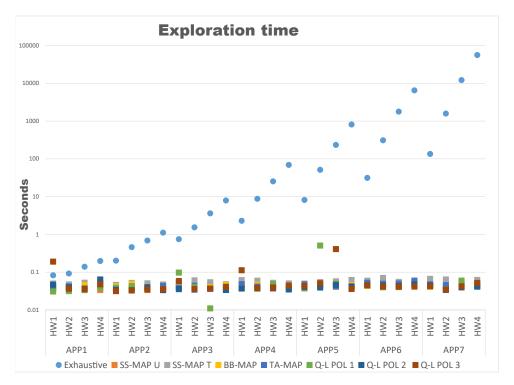

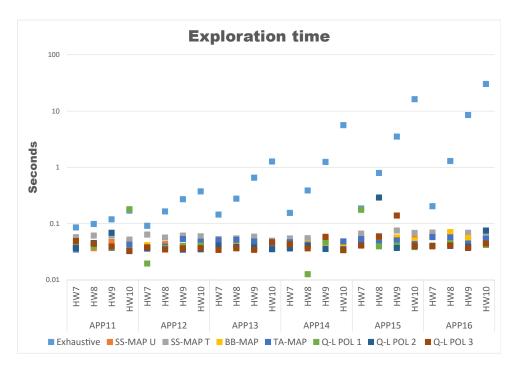

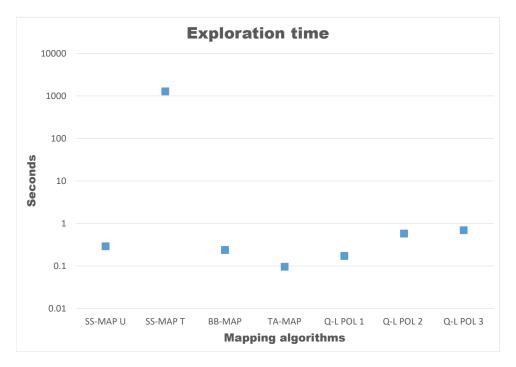

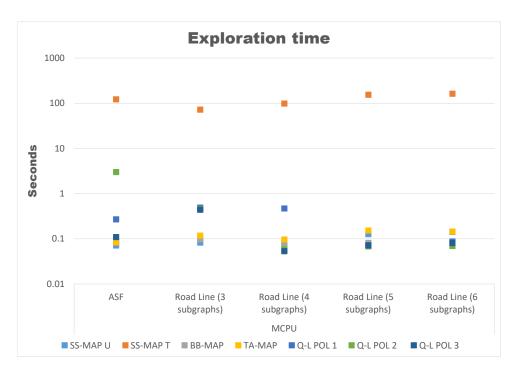

| 8.3  | Comparative study of the exploration time of the first set of applications and the | 1.4.4       |

| 0 1  | first set of hardware graphs                                                       |             |

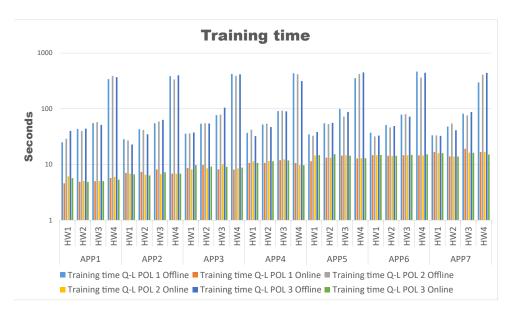

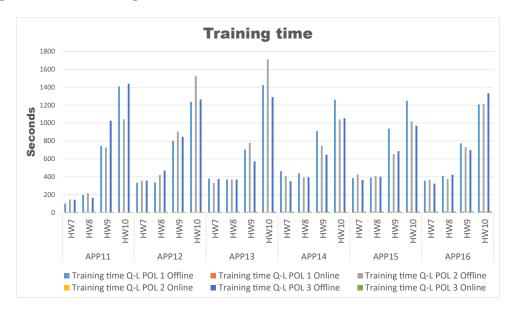

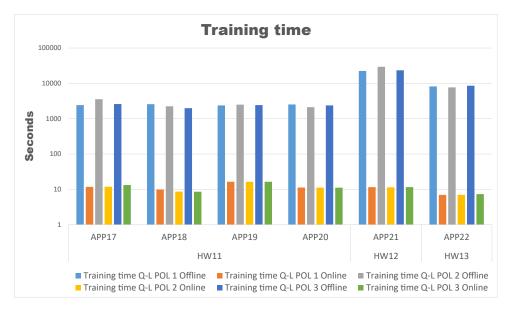

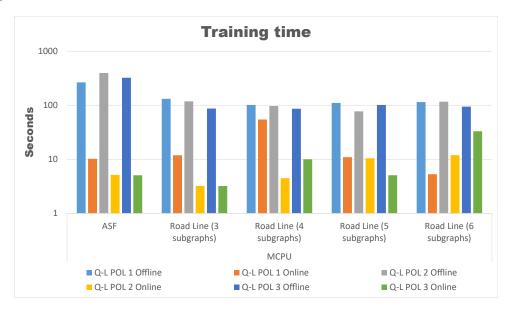

| 8.4  | Training time of the Q-learning approaches                                         | <b>.4</b> 0 |

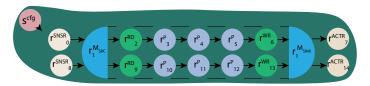

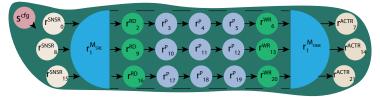

| 8.5  | Second set of application examples                                                 | 147 |

|------|------------------------------------------------------------------------------------|-----|

| 8.6  | Second set of hardware examples                                                    | 147 |

| 8.7  | Comparative of the exploration time of the second set of applications and the      |     |

|      | second set of hardware graphs.                                                     | 148 |

| 8.8  | Training time of the Q-learning approaches                                         | 148 |

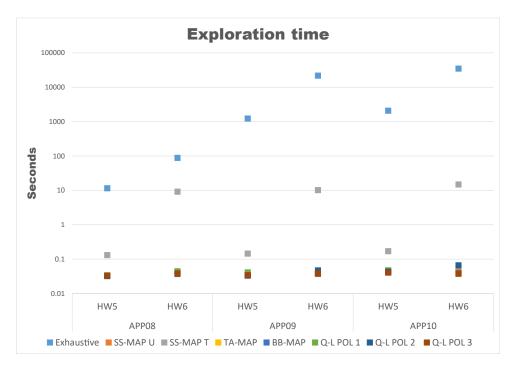

| 8.9  | Third set of application examples                                                  | 150 |

| 8.10 | Third set of hardware examples                                                     | 151 |

| 8.11 | Comparative of the exploration time of the third set of applications and the third |     |

|      | set of hardware graphs                                                             | 152 |

| 8.12 | Training time of the Q-learning approaches                                         | 152 |

|      | Fourth set of application examples                                                 | 154 |

| 8.14 | Fourth set of hardware examples                                                    | 155 |

| 8.15 | Comparative of the exploration time of the fourth set of applications and the      |     |

|      | fourth set of hardware graphs                                                      | 156 |

| 8.16 | Training time of the Q-learning approaches                                         | 156 |

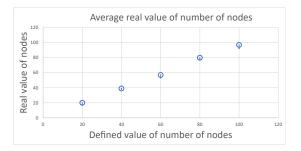

| 8.17 | Example of a random generated graph                                                | 159 |

| 8.18 | Comparison between expected values and real values for the number of nodes in      |     |

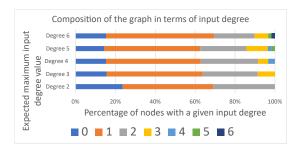

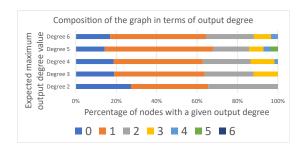

|      | the graph                                                                          | 159 |

| 8.19 | Comparison of the input degree of the nodes in a graph                             | 160 |

| 8.20 | Comparison of the input degree of the nodes in a graph                             | 160 |

| 8.21 | Process flow of the generation of an application graph                             | 161 |

| 8.22 | Example of the different structures                                                | 161 |

| 8.23 | Randomly generated hardware                                                        | 162 |

| 8.24 | Randomly generated application                                                     | 162 |

| 8.25 | Comparative of the exploration time of the first set of applications and the first |     |

|      | set of hardware graphs.                                                            | 163 |

| 8.26 | Training time of the Q-learning approaches                                         | 163 |

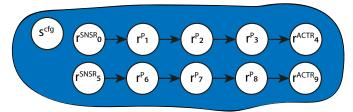

| 8.27 | Hardware model of the MCPU                                                         | 164 |

| 8.28 | Application model of the example $ASF^4$                                           | 165 |

| 8.29 | Application model of the example of the road line orientation detection            | 166 |

| 8.30 | Comparative of the exploration time of the first set of applications and the first |     |

|      | set of hardware graphs                                                             | 168 |

| 8.31 | Training time of the Q-learning approaches                                         | 168 |

|      |                                                                                    |     |

# List of Tables

| 2.1 2.2                                 | Descriptors of the tasks for the $ASF^4$ example                                                                                  | 38<br>40                        |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3.1<br>3.2                              | Hardware models state of the art summary                                                                                          | 46<br>69                        |

| 4.1<br>4.2<br>4.3<br>4.4                | Parameters of the application graph of the performance evaluation example First set of parameters of the hardware graph           |                                 |

| 6.1<br>6.2<br>6.3<br>6.4                | Correspondence between tasks and resources                                                                                        | 106                             |

| 6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10 | removed                                                                                                                           | 113<br>115<br>116<br>116<br>123 |

| 7.1<br>7.2                              | Rewards policies                                                                                                                  |                                 |

| 8.1<br>8.2<br>8.3                       | Reward policies                                                                                                                   | 143                             |

| 8.4                                     | sured in clock cycles (pipeline of homogeneous tasks)                                                                             | 146<br>149                      |

| 8.5                                     | Comparative between mapping approaches according to the computing cost measured in clock cycles (pipeline of heterogeneous tasks) |                                 |

| 8.6                                     | , ,                                                                                                                               | 157                             |

| 8.7                                     |                                                                                                                                   | 164                             |

| 8.8<br>8.9                              |                                                                                                                                   | $\frac{165}{167}$               |

|                                         |                                                                                                                                   |                                 |

### Acronyms

AAM Algorithm Architecture Matching methodology

ALU Arithmetic Logic Unit

**ARM** Advanced RISC Machines

ASIC Application-Specific Integrated Circuit

**ASIP** Application-Specific Intructions-Set Processor

**CGRA** Coarse-Grained Reconfigurable Architecture

CPU Control Processing Unit

**DAG** Directed Acyclic Graph

**DSE** Design Space Exploration

**DSP** Digital Signal Processor

FPGA Field Programmable Gate Array

**GPP** General-Purpose Processor

**GPU** Graphics Processing Unit

**HPC** High-Performance Computing

MCPU Morphological Co-Processing Unit

MPSoC Multiprocessor System on a Chip

**NoC** Networks-on-Chip

**RL** Reinforcement Learning

RRG Resource Routing Graph

SDF Synchronous Dataflow Graph

SFG Signal Flow Graph

SoPC System on Programmable Chip

SPS-CGRA Software Programmable Streaming Coarse Grained Reconfigurable Architecture

WCET Worst-Case Execution Time

VDHL VHSIC Hardware Description Language

XML Extensible Markup Language

# Chapter 1

## Introduction

Time-critical systems need to assure the accuracy of output while meeting hard timing constraints. This paradigm increases its importance with the advent of the industrial IoT, autonomous vehicles, drone-based applications, and smart grids. Often, these new applications must process a significant amount of data from a wide range of sensors. Furthermore, the data must be processed with maximal reactivity, respecting the capabilities of the hardware resources and ensuring a valid output. This creates a non-trivial problem for the latency optimization of processing systems.

To answer these constraints, an extensive number of hardware architectures have been proposed in the past, trying to find the best trade-off between efficiency and execution constraints. We can cite examples going from General-Purpose Processors (GPPs), Digital Signal Processors (DSPs), and Graphics Processing Units (GPUs) up to Application-Specific Intructions-Set Processors (ASIPs), Field Programmable Gate Array (FPGAs), Coarse-Grained Reconfigurable Architectures (CGRAs), and Application-Specific Integrated Circuit (ASIC).

### 1.1 Reusability of Time-Critical Systems

The increasing complexity of time-critical systems and their applications make designers lean towards the reuse of parts of hardware blocks and systems. Since time-to-market constraints are often an industrial priority, and to design a new hardware block from scratch takes a considerable amount of time, the best option is to exploit the already developed platforms' programmable or configurable blocks.

Reusability is the attribute of a system that allows to use it in different applications. It is the use of pre-designed and pre-verified platforms or hardware blocks that reduces time-to-market and ensures a previously known performance [16]. The level of reusability of a given platform includes the following [17]:

- Hardware features: programmability and parametrization of the hardware blocks, the complexity of the target applications, type of interfaces.

- Software tools: programming software and support, simulation environments.

- Standardization support (norms and protocols): documentation of parameters, requirements, and restrictions.

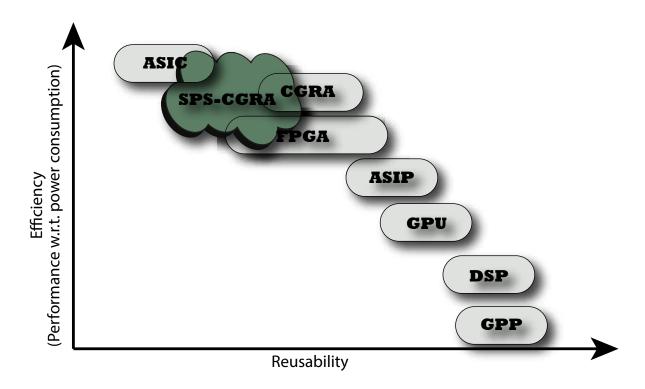

In Figure 1.1, we compare the efficiency with respect to the reusability exploitation of different platforms used for implementing time-critical systems. Efficiency is the relation of performance with regard to power consumption, as reported in the literature [18, 19]. There, we can observe that GPPs, DSPs, and GPUs have a broad support structure and can be used for many applications. However, their performance is lower than an FPGA and an ASIC. ASIPs are better than GPUs and GPPs in terms of efficiency, given the frequent addition of custom instructions

and functional units. However, they remain below FPGAs and ASICs, in terms of efficiency, due to their completely specialized execution engines [19, 20]. FPGAs offer high performance with low consumption and with a significant support environment. Nonetheless, this architecture's management usually requires low-level knowledge, and its performance is lower than the ASICs. ASICs offer the best efficiency, but they require a very rare low-level knowledge and a costly design process. Therefore their reusability is severely reduced. Finally, in the above-mentioned context, Coarse-Grained Reconfigurable Architectures (CGRAs) provide the best ratio between the increase of the overall performance while decreasing computing latency and minimizing the energy budget [21]. Their reuse capability depends on a degree of programmability provided by a set of parameters, often custom and positioned between general-purpose and fixed-function, defining the possibility of their "on-line or off-line re-programming" [18].

Figure 1.1 – Comparative study of hardware architectures from reusability point of view.

Effectively, CGRAs are optimized for a given application domain. There is a large diversity of CGRAs types. Their processing elements are not so generic as the ones of GPPs or DSPs. Usually, a CGRA consists of a set of ALU-like processing resources organized according to some well-defined topology for a dedicated application [22]. Hence, their interconnections and granularity have a reduced complexity than those of FPGAs. Also, their memory infrastructure allows decreasing the overall memory transactions compared to a GPU.

Based on these re-programming capabilities, we can distinguish an inner CGRA family that we call Software Programmable Streaming Coarse-Grained Reconfigurable Architecture (SPS-CGRA). An SPS-CGRA is a systolic, highly pipelined array of heterogeneous hardware resources. It is a spatially-configured overlay [23], based on an FPGA, can be realized as ASIC or be a part of a System on Programmable Chip (SoPC). Its hardware resources are defined by an initial "off-line" structural reconfiguration [24]. After this step, a degree of programmability is provided through reconfigurable or reprogrammable parameter sets, called configuration contexts [25]. Each hardware resource may be equipped with multiple contexts that may be individually switched through its internal registers' modification. An SPS-CGRA is a data-driven platform that may perform not only loops but entire applications at low latency. Its stream-based processing provides high performance while maintaining a level of flexibility.

The use of SPS-CGRAs is widespread across numerous fields. In the cryptocurrency domain, the implementation of hashing algorithms requires a massive amount of computational power. This may be solved using an FPGA-based SPS-CGRA, as depicted in Tetu et al. [8] where an implementation of the Lyra2REv2 algorithm, a standard in cryptocurrency, is presented. Mathematical algorithms can also take advantage of the systolic structure of an SPS-CGRA. For example, we can cite the FPGA-based implementation of an Algebraic Multigrid Solver presented by Haghi et al. [26]. Sound field rendering models the behavior of sound wave propagation in spatial and time domain using numerical methods, and its implementation and efficiency are crucial for several engineering application fields. Tan et al. [27, 28] proved that SPS-CGRA solutions offer better performance than a GPP implementation. In the computer vision domain, SPS-CGRAs are used to enhance the performance of image processing systems. Examples of these architectures are the FPGA-based SPS-CGRAs presented by Ngan et al. [29] and by Isavudeen et al. [10]; and also the ASIC-based SPS-CGRA introduced by Dokladalova et al. [30]. Deep Learning is another field where the use of SPS-CGRA is growing. Since a Neural Network (NN) is modeled as a Directed Acyclic Graph (DAG) and its dataflow is unidirectional, an SPS-CGRA is a perfect candidate to be used as an implementation platform. We can cite, for example, the ASIC-based Neuflow [31], and FlexFlow [32], the FPGA-based implementations of a Deconvolutional NN presented by Chang et al. [13], a Life Long learning Convolutional NN by Piyasena et al. [14] and a Randomly Wired NN develop by Kuramochi and Nakahara [33]. Some of these examples will be detailed in Section 1.4.

Unfortunately, despite the high performance that an SPS-CGRA can deliver while decreasing latency of processing, its reuse is not generalized due to the lack of generic tools or frameworks. This problem is inherited from the CGRA, based on manual or custom programming frameworks, that can not be easily transferred (or adapted) to other CGRA-based systems [11, 12].

Consequently, the programming and compiling frameworks remain immature. Hence, the mapping of any application onto an SPS-CGRA is often manual, requiring expert knowledge of both inner hardware mechanisms and application specificity. This reuse task could become overwhelming, leading to the rare reuse of these powerful SPS-CGRA platforms.

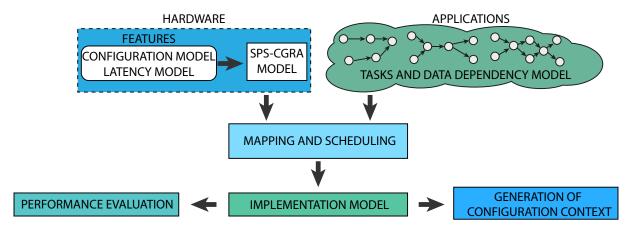

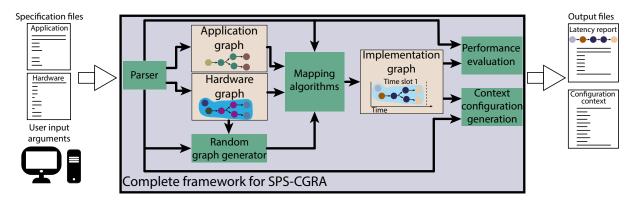

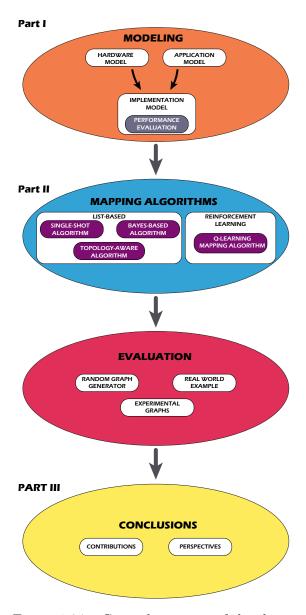

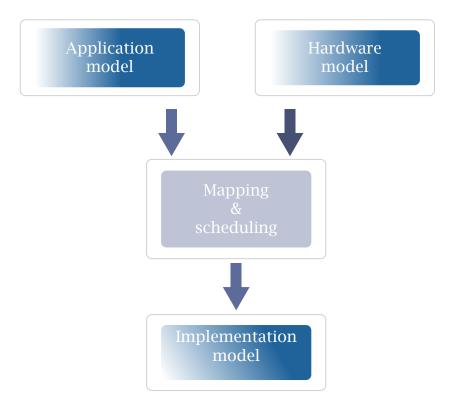

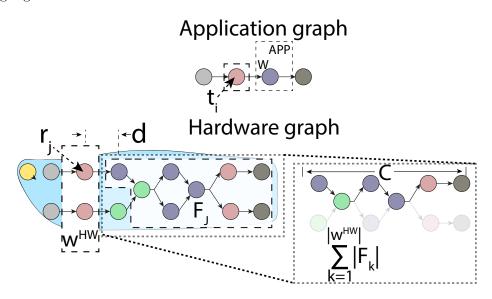

To face these issues, we propose a generic automated mapping and scheduling framework that targets most of the existing SPS-CGRA (Fig. 1.2).

Figure 1.2 – Overall scheme of proposed modeling and mapping framework for SPS-CGRA.

Such a framework must be based on a model that allows describing the heterogeneity of any SPS-CGRA hardware element programming models. Simultaneously, this model has to be generic enough to match the maximum of SPS-CGRAs variants in granularity and application fields. Also, considering the need to optimize the system's reactivity, it has to provide an accurate, near-to-real performance latency estimation. Additionally, such a framework should offer mapping assistance to help the designer exploit this type of hardware architecture's inherent parallelism. Finally, the mapping assistance should aim to decrease the computing cost, a critical

metric in these systems.

In this context, the main contributions of this thesis are:

- A unified modeling framework that includes application, hardware and selected implementation.

- We propose to use processing latency as a metric of computing cost to be optimized. The latency can be described as a function of the hardware block programming parameters.

- A computation model to estimate the upper bound of the computing cost of the implementation selected by the mapping algorithm.

- We propose and evaluate four different mapping approaches.

- 1. A List-based algorithm equipped with backtracking.

- 2. A Topology-aware mapping heuristic.

- 3. A Bayes-based mapping heuristic.

- 4. A Q-learning-based mapping algorithm.

To complete, we evaluate the algorithms in terms of exploration time and computing cost of the implementation.

Additionally, we introduce a complete benchmark framework with the previous items, including a configuration control generator.

The remainder of the chapter is divided as follows. In Section 1.2, we review state of the art on development tools and methodologies. Section 1.3 describes in detail the characteristics of a CGRA. Section 1.4 introduces the concept of SPS-CGRA. Section 1.5 presents the thesis contributions. Section 1.6 presents the outline of the thesis.

### 1.2 State of the Art: Development Tools and Methodologies

As introduced previously, reusability is the attribute of a system that allows one to use it in different applications. This aspect directly impacts time-to-market and provides the opportunity to use already developed and tested tools or frameworks. As stated in Section 1.1, reusability includes three aspects: hardware, software, and documentation. However, most of the designers of SPS-CGRA focus only on the hardware aspect, providing a set of programmable parameters to allow the use in different applications. Thus, we can observe a lack of tools and methodologies that could provide the software support. In this context, tools like Design Space Exploration (DSE) are often used to bridge this reuse technique gap.

A DSE is the systematic evaluation process of the different implementations (mappings) of an application onto a hardware system to determine optimal or best-suited hardware. This process can be manual, automatic, or hybrid. In a manual DSE, the engineer is in full charge to find the optimal implementation, while in an automatic DSE, the framework takes the implementation decision. In a hybrid DSE, the framework takes the decisions with a fine tunning from the engineer. This evaluation process may generate many possibilities due to the size of the design space. As the number of possible implementations increases, a complete, exhaustive exploration may be prohibitive. For this reason, several works propose different approaches for efficient DSE.

Giannopoulou et al. [34] presented a DSE framework for many/multicores, part of the Certification of Real-Time Applications designed for mixed-criticality (CERTAINTY) project, aiming at avionics applications. It uses a mixed-critically task application model with multiple critical levels and different task activation patterns and a platform model that allows to abstract of the memory and the communications of the system. A mixed-critically scheduling policy is

used, where only equal critical tasks can be executed in parallel. Finally, the implementation is evaluated using a response time analysis based on the Worst-Case Execution Time (WCET).

Grandpierre and Sorel [35] presented a prototyping methodology and a software tool (Syn-DEx) that aims to optimize implementations of real-time image and signal processing onto heterogeneous multiprocessors architectures. This methodology has been extended to integrated circuits [36, 37], VHDL code generation [38], and it has been the subject to improvements in terms of power consumption [39].

Jalier et al. [40] introduced a DSE framework for Multiprocessors System on Chip (MPSoCs). Their framework targets telecom applications. The application and hardware model are based on a SystemC description and specified using an XML standard. The modelization and the mapping are manual. However, the performance estimation is done automatically. Metrics such as application throughput, maximum latency, the utilization rate of resources, transient effects are used.

Castrillon et al. [41] presented the MPSoC Application Programming Studio (MAPS), a framework focusing on MPSoCs. The application model is described in C for Process Networks (CPN) and modeled as Kahn Process Networks (CPN). The architecture model is described with Extensible Markup Language (XML). The authors propose several heuristics for mapping and scheduling. The performance evaluation is a composability analysis, where the goal is to determine if a set of applications may be run in parallel.

Jovanovic et al. [42] presented a memory-aware mapping optimization tool for MPSoCs (MAMOT). The application model is a thread-based task graph. A memory-aware evolutionary algorithm is used as a mapping algorithm and is evaluated using performance and energy consumption as metrics.

Dauphin et al. [43] presented Ordonanceur DYNamique (Odyn), an approach for scheduling and memory management that targets Non-Uniform Memory Architecture (NUMA) platforms. The inputs are a Synchronous Data-Flow and a generic logical architecture. The scheduling aims to prevent deadlocks, using a static analysis of Memory Exclusion Graphs.

Suriano et al. [44] presented a framework that integrates the framework Parallel and Real-time Embedded Executives Scheduling Method (PREESM) [45] and the Xilinx SDSoC tool for Zynq devices. It aims to automatize the design and implementation of heterogeneous multicore multi-hardware accelerators. The framework uses PREESM to generate code, and then this code is manually adapted to be used within the Xilinx SDSoC software.

Bruneel et al. [46] introduced a tool for mapping applications to an FPGA. This tool allows a post-mapping reconfiguration by leaving a set of parameters that can be reconfigured on runtime. The applications are expressed as Boolean functions, and the main module of this tool is TMAP, a reconfigurability-aware technology mapper that produces a tunable LUT circuit.

Fricke et al. [47] presented an automatic tool-flow for an application-specific CGRA, called Virtual Coarse-Grained Reconfigurable Array (VCGRA). The architecture consists of layers of processing elements with virtual channels (switches) between them. The framework takes a data flow graph as an application model and produces a binary file used as a configuration context.

Peyret et al. [48] introduced a generic method for mapping application onto CGRA architectures. A Control Data Flow Graph is the application model, and the mapping is a combination between a heuristic and an exact method.

Chin et al. [49] presented CGRA Modelling and Exploration (CGRA-ME), a DSE framework for CGRAs. It includes modeling, mapping, and physical implementation. CGRA-ME modeling does not provide the descriptors for heterogeneous resources or latency because it only considers ALU-like processing resources. The framework offers two options for mapping: a simulated annealing approach and an integer linear programming. The mapping success of these approaches is directly proportional to the flexibility of the hardware fabric. The more flexible the platform, the higher is the mapping success rate. The resource's layout uses a mesh-type pattern, where the number of columns and rows requires to be specified and should be higher than one. Irregular structures are not allowed. Canesche et al. [50] introduced TRAVERSAL, a

graph-based greedy heuristic that provides a flexible, fast, and adaptive placement and routing for CGRAs. It's based on a novel traversal method called ZigZag. It exceeds the performance of CGRA-ME in terms of execution run-time, due to its execution on GPU. Li et al. [51] presented ChordMap, it focus on automated mapping of streaming applications, represented as Synchronous Dataflow graphs, onto a CGRA. Using modulo scheduling, it aims to exploit the parallelism of an application by partitioning it and using the notion of divide and conquer to map all the resulting partitions. Targeting High Processing Computing (HPC), Tan et al. [52] introduced ARENA, a DSE that generates specialized CGRA accelerators. The authors proposed to build CGRA clusters connected by a fast ring network, to increase the performance of the generated system. Shent et al. [53] opted for a different approach. The authors focus on the optimization of the FPGA routing. They proposed to divide the nets into three subsets: a subset of possible dependant nets and two subsets of possible independents. They showed that their approach speedup current approaches by 1.8x.

Even with the large number of works and frameworks dedicated to the reuse problem, to the extent of our knowledge, none can be directly applied to the SPS-CGRA. The inner mechanisms and the latency features can not be captured by the models used for many/ multicores or MPSoCs frameworks. Furthermore, the mapping and scheduling algorithms are not aware of the complexity of both the application and the hardware. Thus, the resulting mapping or implementation will not be near-optimal. Similar works, such as CGRA-ME, use code generation techniques to build hardware blocks according to the application. They may not be capable of reusing an already deployed system's parameters.

### 1.3 Coarse-Grained Reconfigurable Architectures

Initially, the introduction of the CGRA was motivated to solve development bottlenecks of the FPGA-based systems. Despite its high performance, the FPGA granularity (bitwise logic) imposed a significant challenge for the designers. Additionally, the synthesis-time could take hours or days to finish.

The coarser granularity allows designing more specialized processing resources. This, in turn, increases the performance. Additionally, the new granularity decreased the synthesis time, and the possibility of multiple contexts was introduced. The new type of architecture was named Coarse-Grained Reconfigurable Architecture.

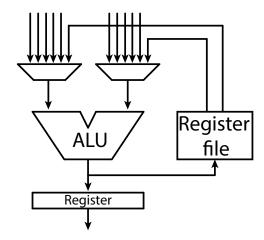

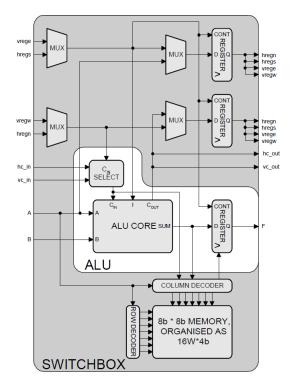

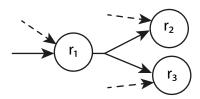

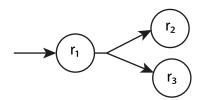

There are many variations of CGRAs. Depending upon the type of interconnections or processing resources, the structure and application of a CGRA may change. Despite these variations, the usual basic processing element of a CGRA consists of interconnections, a register file, and an ALU block [22, 1]. Figure 1.3 illustrates a generic processing resource. The variations of the processing resources may cover the addition of several register files, different types of processing modules. Also, the internal structure of a processing element can be completely different from the one shown in Figure 1.3, with only one processing module or without a register file.

Figure 1.3 – Generic processing resource of a CGRA [1].

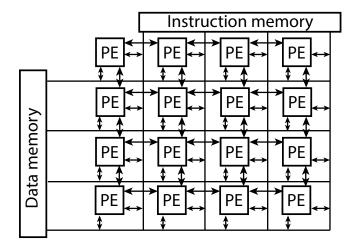

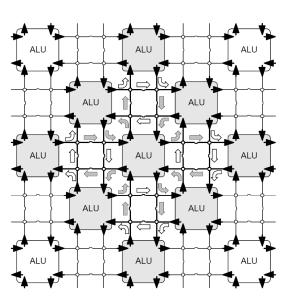

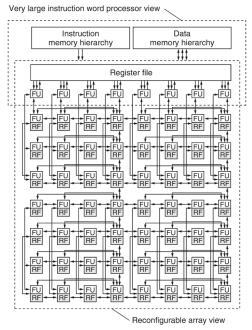

In terms of interconnection structure, the typical configuration is a mesh of processing resources. In Figure 1.4 a generic structure is showed, where we can see the mesh of processing resources with the addition of the data and instruction memory. Other types of interconnections may be torus, linear array, or ring.

Figure 1.4 – Generic structure of a CGRA [1].

The main role of a CGRA is to perform the computational-demanding inner loops of an application. A CGRA may process the input data in stream-based processing at low latency. Due to this, a CGRA acts as a hardware accelerator inside a system controlled by the main processor. The coupling of the main processor and the CGRA may be tight or loose. In a loose coupling, the CGRA is connected directly to the main memory and may execute code concurrently with the main processor. On the other hand, a tight coupling means that the CGRA shares resources with the main processor and can not execute code in parallel [22].

The last but not least advantage of a CGRA is the context switching time. Specifically the possibility to switch contexts in a very short time. The implementation of an application onto a CGRA may result in several configuration contexts. Each configuration context represents a part of the application and contains the resources' configuration and one or more addresses to the next configuration context. The time needed to request and gather a configuration context and deploy it to the resources to start the new processing process is the context switching time [54]. This feature opens the door to a temporal execution, as the configuration time is short enough to allow the use of multiple contexts.

#### Examples

A large number of CGRAs have been developed during the last 30 years. Most of them show similarities regarding the type of processing resources. According to the type of topology, we can distinguish two categories: mesh-based and linear-based CGRAs.

Within the category of mesh-based topology, Marshall et al.[2] introduced CHESS. CHESS is a 4-bit ALU-based system, one of the first CGRA that allowed the use of its processing elements as a scratchpad. Figure 1.5 shows a CHESS processing element and Figure 1.6 the interconnection. An evolution of this CGRA is the Elixent D-Fabrix Reconfigurable Algorithm Processor (RAP) [55], where the functionality of the CHESS switch-boxes are improved.

Figure 1.6 – CHESS layout [2].

Figure 1.5 – Logical structure of a CHESS processing element [2].

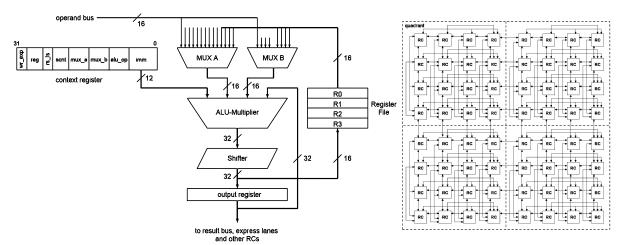

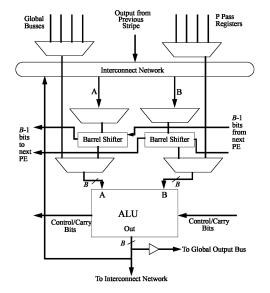

MorphoSys [3, 56] is a reconfigurable platform that includes a CGRA and a RISC processor loosely coupled. As illustrated in Figure 1.7 the basic processing element tasks also include a multiplier. Additionally, it allows multiple configuration contexts and dynamic reconfiguration. The interconnection network consists of quadrants that allow three hierarchical levels of interconnectivity (Figure 1.8). The first level is the nearest neighbor, which is the interconnectivity between a hardware resource and its direct neighbors. The second level is the intraquadrant connectivity, which enables the interconnection between hardware resources that belongs to a quadrant. The last level is the interquadrant connectivity that allows the interconnectivity between quadrants. These levels of interconnectivity increase the parallelism of the system and its performance. This platform has been improved to allow floating-point operation and implemented in silicon [57].

Figure 1.7 – Logical structure of a MorphoSys reconfigurable cell [3].

Figure 1.8 – MorphoSys reconfigurable array [3].

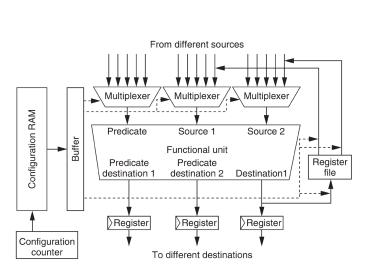

The Architecture for Dynamically Reconfigurable Embedded Systems (ADRES) [4, 5] features a mesh of heterogeneous processing elements (Figure 1.10) and is widely used for research. These heterogeneous processing elements feature a functional unit that supports multiple operations and a distributed register file (Figure 1.9). The main advantage of this platform is its flexibility and easy-to-use framework.

Figure 1.9 – Logical structure of a ADRES processing element [4, 5].

Figure 1.10 – ADRES interconnection [4, 5].

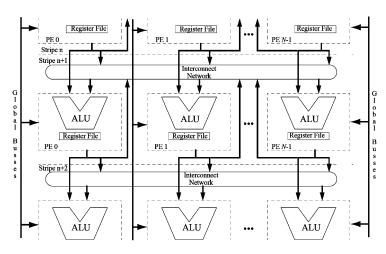

PipeRench [6, 7] is a CGRA with a linear interconnection. The basic structure of its processing element is shown in Figure 1.11, as we can notice it is an ALU-based element with an interconnection layer. The interconnection layer is the main feature of this CGRA, as its structure is based on independent layers interconnected by the interconnection layer (Figure 1.12). This structure allows for implementing independent applications in each layer. This increases the parallelism of this platform.

Figure 1.11 – Logical structure of a PipeRench processing element [6, 7].

Figure 1.12 – PipeRench interconnection [6, 7].

Most of the current work on CGRA development applies the same principles as the previous CGRA examples. They use the same type of connectivity, and the processing elements perform ALU-like operations. Nonetheless, there have been some improvements in the use of the register file, different internal structures, the addition of scratchpads, processing elements heterogeneity. A significant development is in the part of the granularity of the processing elements. We can observe and corroborate the heterogeneity of resources that will impact the processing latency and final computing cost. As previously stated, the CGRA was a solution for the FPGA development process bottlenecks. However, its performance may still be improved. For this, the designers chose to increase even more the granularity of the processing elements and use a stream-based interconnection. These new systems can perform time-critical tasks and shown an increase in the performance of several applications. In the following section, we will introduce such architectures.

# 1.4 Software Programmable Streaming Coarse-Grained Reconfigurable Architectures

An SPS-CGRA is a specific subset of CGRAs that consists of a systolic array of heterogeneous processing resources. To better understand the features of this type of architecture, we can use several classification methods. Liu et al. [18] propose a CGRA multidimensional taxonomy based on the models of programming, computation, execution, and micro-architecture. According to the programming model, an SPS-CGRA belongs to the category of the parallel programming model. Usually, an application for an SPS-CGRA consists of a sequence of expressions that describe its behavior with partially implicit parallelism. The aim of the mapping tool is to completely identify and abstract the parallelism to exploit it and provide an efficient implementation. The second classification is based on the computation model, where the SPS-CGRA falls in the category of multiple configurations, multiple data (MCMD). However, an SPS-CGRA can switch between configurations and allows a dynamic parameter-based reconfiguration on runtime. The third classification is based on the execution model. An SPS-CGRA belongs to the category of static-scheduling sequential execution where the mapping tool is in charge of the initiation and mechanism of the reconfiguration.

In the work of Wijtvliet et al. [22] a CGRA classification is proposed using four main elements, structure, control, integration, and tooling. According to this paper, structurally, an SPS-CGRA is a multi granular direct connection network with a cache memory hierarchy. The

granularity may be coarser than ALU-based operations. In terms of the control, SPSP-CGRA scheduling is done at compile-time, where the mapping tool creates the spatial and temporal scheduling. Still, both the resources and network's reconfiguration can be done at run-time using a pre-defined configuration. It also allows custom operations since the granularity of the resources is higher than the usual CGRA operations. Regarding the integration, SPS-CGRAs are usually used as co-processors (hardware accelerators) with loose coupling and no resource sharing. The last element of the classification, tooling, claims that the compiler is usually based on a mix of dataflow/custom language, as each SPS-CGRA has different types of operations. The framework of an SPS-CGRA does not consider the place and route since the architecture is usually already deployed, and only a design space exploration is done to find the best mapping possible.

Hartenstein [58] proposes different classification. The author uses the type of architecture, granularity, fabrics, mapping, and the intended target application to distinguish between CGRAs. According to this classification, an SPS-CGRA would be a multi granular 1-D array. Both the fabrics and the target application may vary. The mapping in these types of architectures is described as scheduling. Tehre and Kshirsagar [59] propose a similar classification to [58]. However, the authors added the category of reconfiguration model, which for an SPS-CGRA is dynamic.

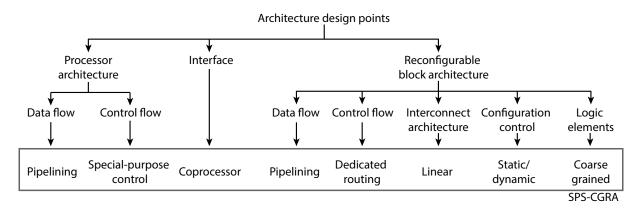

Chattopadhyay [60] proposes a taxonomy based on three axes, the design choices, the class, and the modeling and design space exploration tools. The design choices refer to three aspects, the microarchitectural view, the programming model, and the platform type. In Figure 1.13, we summarize the different microarchitectural view categories applied to our SPS-CGRA target. An SPS-CGRA is usually used as a special-purpose co-processor. Its pipelining interconnection architecture allows a data-driven flow. It typically consists of a linear array of coarse-grained resources that may be configurable statically/dynamically.

Figure 1.13 – Proposed microarchitectural classification of an SPS-CGRA.

According to Chattopadhyay [60], an SPS-CGRA belongs to Class III: custom processing and reconfigurability. The broad range of possible structures and architectures make this family of accelerators a good candidate for various real-time applications, although it increases the complexity for a general framework that could cover all types. The last axis of Chattopadhyay is the modeling and design space exploration tools. Usually, the tools that target SPS-CGRA allow only the modification/optimization of the (software parameters) implementation, and they are highly specialized for a given platform.

As stated previously, there are several types of SPS-CGRA. They share similarities in architecture and properties, but the tools and their frameworks are custom. This aspect overburdens its use and also the possibility to apply tools from one SPS-CGRA to another. A seamless design with accurate latency estimation and exploration capability is required to increase the use of this type of architecture and exploit all its benefits.

#### Examples

As quickly presented in the introduction, an extensive number of SPS-CGRAs have been developed for research and commercial purposes. They belong to different fields, and they are application-specific. Due to the higher level of granularity of these architectures, reusability within the application field may be narrow, but it is compensated by the high performance and low latency that can provide.

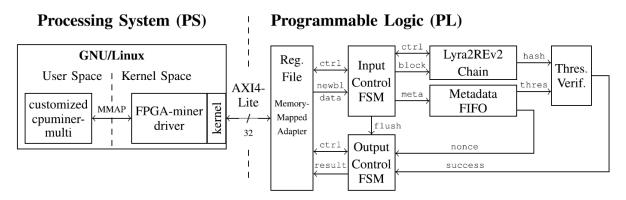

Hashing is an algorithm that calculates a fixed-size bit string value from a file. Within the cryptocurrency domain, hashing algorithms ensure the integrity of the transactions. The implementation of hashing algorithms requires a huge amount of computational power. In this regard, Tetu et al. [8] propose an SPS-CGRA-based implementation of the Lyra2REv2 hashing algorithm (Figure 1.14). It features a pipelined stream-based architecture, and it is loosely coupled to an ARM processor.

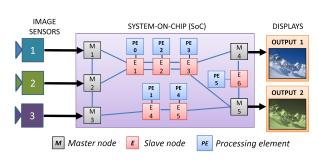

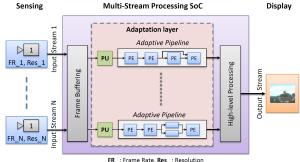

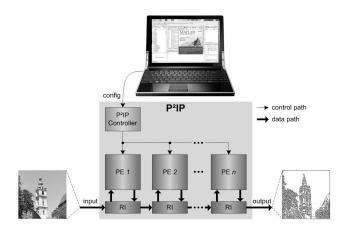

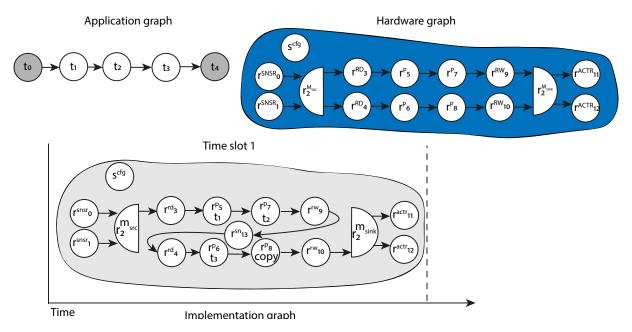

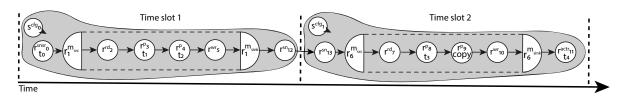

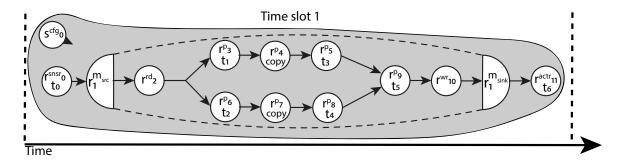

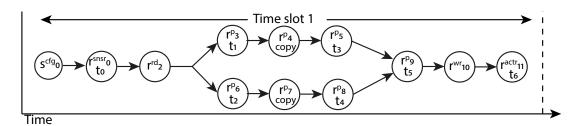

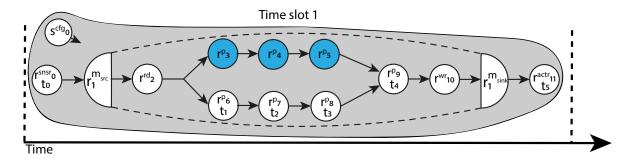

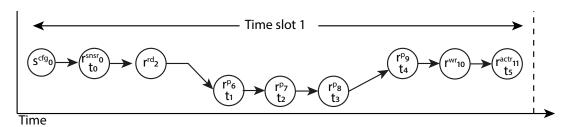

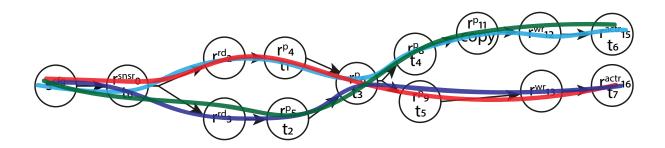

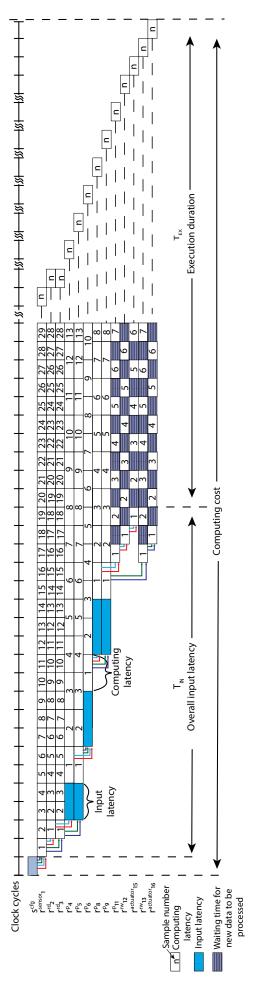

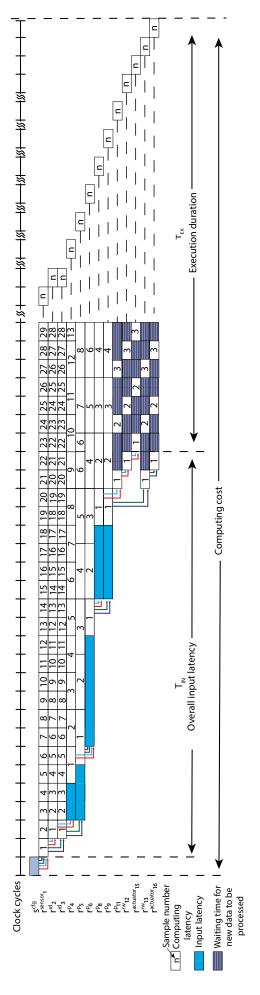

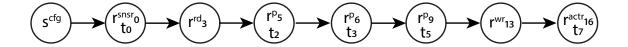

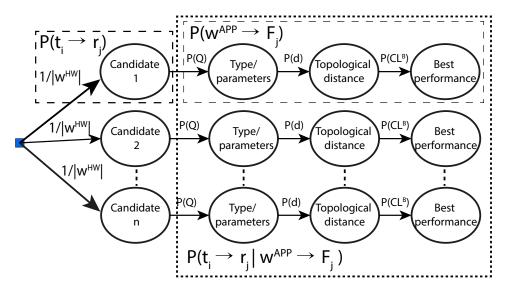

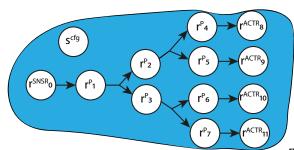

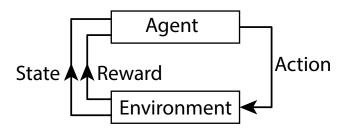

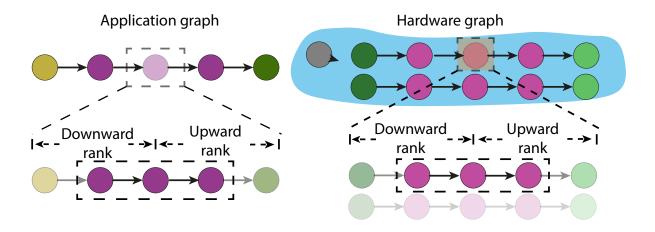

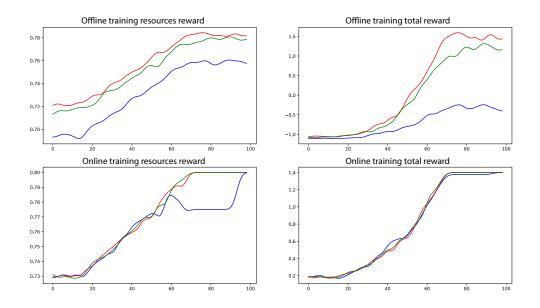

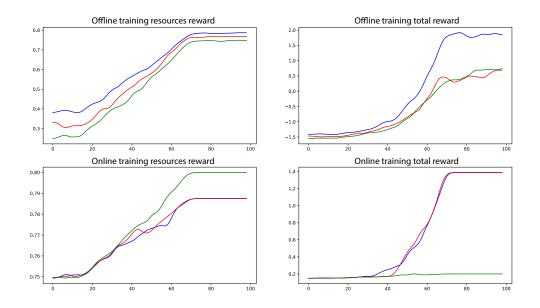

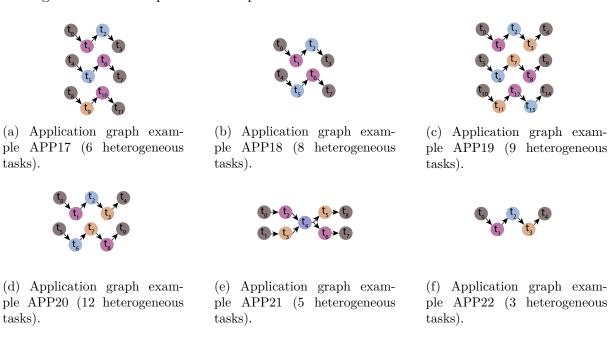

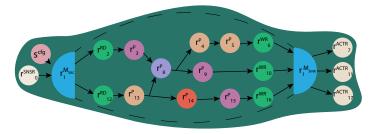

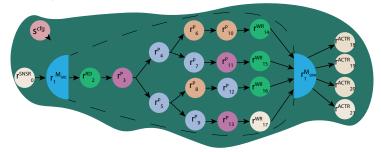

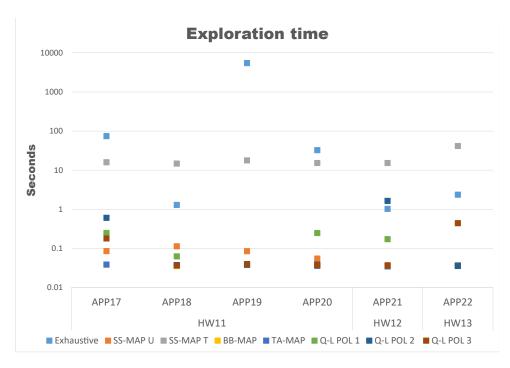

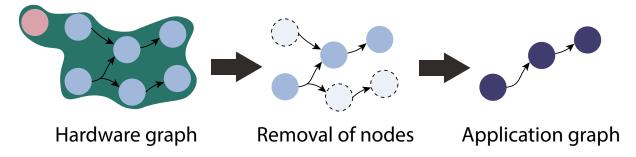

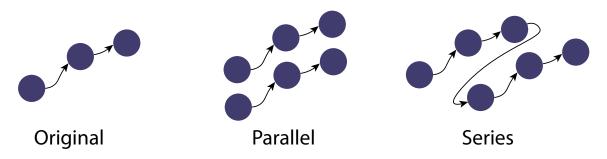

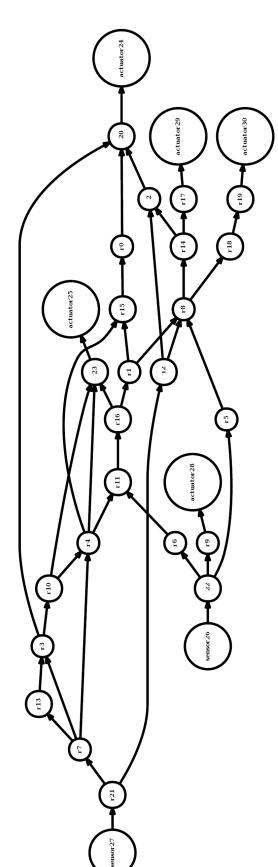

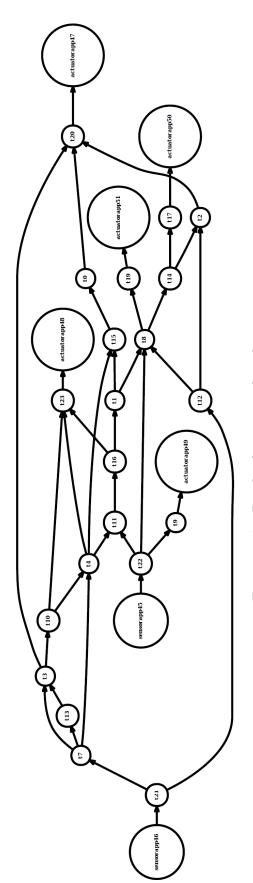

Figure 1.14 – Architecture of the SPS-CGRA implementation of the standalone Lyra2REv2 miner [8].