### Design of a continuous time Delta-Sigma modulator for energy measurement using diamond detectors

Abderrahmane Ghimouz

### ▶ To cite this version:

Abderrahmane Ghimouz. Design of a continuous time Delta-Sigma modulator for energy measurement using diamond detectors. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2021. English. NNT: 2021GRALT069. tel-03553846

### HAL Id: tel-03553846 https://theses.hal.science/tel-03553846

Submitted on 3 Feb 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITE GRENOBLE ALPES

Spécialité : **NANO ELECTRONIQUE ET NANO TECHNOLOGIES** Arrêté ministériel : 25 mai 2016

Présentée par

### Abderrahmane GHIMOUZ

Thèse dirigée par Olivier ROSSETTO, MAITRE DE CONFERENCE, Université Grenoble Alpes et codirigée par Fatah-Ellah RARBI, INGENIEUR DE RECHERCHE, CNRS/IN2P3/UGA/LPSC

préparée au sein du Laboratoire de Physique Subatomique et Cosmologie de Grenoble (LPSC) dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Conception d'un modulateur Delta-Sigma à temps continu pour la mesure d'énergie utilisant des détecteurs diamant

# Design of a continuous time Delta-Sigma modulator for energy measurement using diamond detectors

Thèse soutenue publiquement le **28 octobre 2021**, devant le jury composé de :

### Monsieur Sylvain BOURDEL

PROFESSEUR, Grenoble INP, Président

### **Monsieur Dominique DALLET**

PROFESSEUR, Bordeaux INP, Rapporteur

#### Monsieur Wilfried UHRING

PROFESSEUR, Université de Strasbourg, Rapporteur

### Monsieur Christophe DE LA TAILLE

INGENIEUR DOCTEUR, CNRS/IN2P3 OMEGA, Examinateur

#### Monsieur Olivier ROSSETTO

MAITRE DE CONFERENCE, Université Grenoble Alpes, Directeur de Thèse

### Monsieur Fatah-Ellah RARBI

INGENIEUR DE RECHERCHE, Laboratoire de physique subatomique et de cosmologie, Co-encadrant

|   | "To the courage of my Dad                                                         |

|---|-----------------------------------------------------------------------------------|

|   | The wisdom of my Mum The ambitions of my Brothers nat is living within all of us" |

| , | S V                                                                               |

|   |                                                                                   |

### Acknowledgments

Throughout the writing of this dissertation, I have received a great deal of support and assistance. Our prophet Mohammed (peace be on him) said: He, who does not thank people, does not thank Allah (narrated by Ahmad and Tirmidhi).

I would first like to thank my advisors, Doctor Fatah-Ellah RARBI and Professor Olivier ROSSETTO, your expertise was invaluable in formulating the research questions and methodology. Your insightful feedback pushed me to sharpen my thinking and brought my work to a higher level. I am grateful to have the opportunity to work with both of you; I will never forget all your advises, discussions, jokes and moments of challenges, you made me love science more and more.

Besides my advisors, I would like to thank the rest of my thesis committee: Professor DALLET Dominique, Professor UHRING Wilfried, Professor BOURDEL Sylvain and Doctor DE LA TAILLE Christophe, for their insightful comments and encouragements, but also for the original questions, which incented me to widen my research from various perspectives.

My sincere thanks also goes to Doctor Marie-Laure GALLIN-MARTEL, Engineer Laurent GALLIN-MARTEL, Doctor Denis DAUVERGNE, and all theirs students and PhD candidates for the great discussions and clear explanations about Diamond detectors.

I would like to acknowledge my colleagues from the electronics departments in the LPSC, for their wonderful collaboration. I would particularly like to single out Mahfoud YAMOUNI, Emmanuel TOURBA, Jean-pierre SCORDILIS, Nicolas PONCHANT, Joel BOUVIER, Germain BOSSON, Yvan ODIEVRE, and Thierry DESCOMBES. Without you, things would not be that interesting, is not it?

I would also like to thank the youngsters in our department; the new engineers Julien BOUNMY and Oumaima JAAFOURA. Those who went for new adventures; Theo MABILON and Lucas TRIBOUILLOY (We still playing online games, right?).

In addition, my warmth thanks to all the students and colleagues from the administration and other departments (Special thanks to Thierry LAMY, Denis GRONDIN, Emmanuelle VERNAY, Audrey COLAS and Christine SERVOZ-GAVIN), my PhD candidate mates from the BIDUL Club and the communication department of CNRS ALPES and UGA Grenoble.

Moreover, I would like to thank my parents for their wise counsels and sympathetic ear. You are always there for me; your words never let me down in the hardest moments, thank you! To my brothers Hocine, Taqi-Eddine and BENBOUDIAF Merwan, I believe in you as much as you believe in me! Finally, I could not have completed this dissertation without the support of my friends, here in Grenoble: Mustapha TOUHAMI, Wissam BENJILALI, Mounder KOUICEM, Abdel-mounain AHMINE, Mohamed ZELOUFI, Hamza RIHANI, Housseyne NADOUR, Nassim LOUKKASS, Hadj MAHBOUBI and his wife, YOU ARE MY FAMILY HERE! My friends in others cities and countries Rafik SAAD, Younes AGGOUN (This man took the plane and came to my defence from TUNISIA! Man you made my day!), BOUCHAMA Abdelbari, BOKHARI Lamine, LYAMSI Ismail, MANSER Belkacem, Yacine and finally to the spirit of imagination, love and laugh D.A.R Aggy. All of you provided stimulating discussions as well as happy distractions to rest my mind outside of my research (w kess JUS).

I would not forget all the great people who keep inspiring me and making me enjoying the adventure of science: Nicola TESLA, Isaac NEWTON, Albert EINSTEIN, Carl Friedrich GAUSS, Muhammad Ibn Mūsā AL-KHUWĀRIZMĪ, Leonardo da VINCI, Behzad RAZAVI, Boris MURMANN, and the entire curious scientists from different eras who are seeking the knowledge through hard work and effort: "If I have seen further it is by standing on the shoulders

| Acknowledgments           |  |  |

|---------------------------|--|--|

| of Giants." <sup>1</sup>  |  |  |

| or Grands.                |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

|                           |  |  |

| <sup>1</sup> Isaac Newton |  |  |

# Conception d'un modulateur Delta-Sigma passe bas à temps continu pour la mesure d'énergie en utilisant des détecteurs diamant

### Résumé

La conception des convertisseurs analogique numérique de type Delta-Sigma à temps continu est souvent considérée comme complexe et difficile. Elle nécessite des connaissances, de l'intuition, de la créativité et de l'expertise technique. Jusqu'à présent, ce type d'architecture n'apparaît pas dans le domaine de la conception des circuits électroniques intégrées pour la détection de particules. Pourtant, nous pensons qu'il peut apporter des solutions intéressantes, comme nous allons le montrer dans le cas des systèmes de mesure d'énergie.

Ce travail de thèse s'inscrit dans le cadre d'un projet de recherche intitulé DIAMASIC. Le but est de développer une électronique de lecture intégrée d'un système de détection hodoscope utilisant des détecteurs diamant dans le cadre de monitorage de faisceaux pour le traitement de tumeurs par hadronthérapie. Ce système doit permettre un étiquetage spatio-temporel des particules utilisées connu sous le nom « hadron » pour garantir la sécurité du patient pendant ce type de traitement. Cette électronique est composée de deux parties : un système de mesure de temps et un système de mesure d'énergie. Le design de ce dernier nécessite la conception d'un CAN.

Ce manuscrit synthétise les travaux de modélisation, conception et simulation d'un modulateur Delta-Sigma passe-bas à temps continu avec une bande passante de 10MHz (Peut atteindre 40 MHz) et visant une résolution de 8bits avec une consommation raisonnable. Dans un premier temps, nous avons réalisé une analyse des architectures possibles des différents modulateurs pour arriver à garantir le cahier des charges voulu. Suite à cette étude, nous avons proposé une topologie d'un modulateur de type CRFF "Cascaded Resonator Feed-Forward" du cinquième ordre avec un quantificateur interne d'une résolution de 3bits et un taux de sur-échantillonnage de 8. Pour valider ces choix et étudier l'impact des imperfections liées à chaque bloc, nous avons développé une méthodologie de modélisation basée sur le paradigme connu sous le nom du Model-Based Design (MBD) via des modèles graphiques SIMULINK et des scripts MATLAB. Cette approche nous a permis de spécifier les performances de chaque partie du modulateur et aussi de faire des optimisations en termes de complexité, stabilité et consommation. Les données extraites de la partie de modélisation sont utilisées dans la phase d'implémentation en technologie CMOS 130nm. Le dimensionnement théorique des transistors est réalisé en utilisant la méthodologie gm/ld. Les détails de cette méthode sont discutés pour la conception des amplificateurs utilisés dans le filtre de la boucle. Les résultats de différentes simulations électriques sont présentés, elles montrent que l'architecture proposée atteint une résolution de 8bits dans une bande passante de 10 MHz.

Finalement, une comparaison entre les résultats de modélisation et les différentes simulations électriques sur CADENCE a été présentée et l'écart de performance est discuté avec des propositions d'amélioration avant la fabrication du circuit.

**Mots clés**: Hodoscope, Diamant, détection des particules, circuit analogique, CAN, Delta-Sigma, temps continu, MBD.

# Design of a continuous time low-pass Delta-Sigma modulator for energy measurement using diamond detectors

### **Abstract**

The design of continuous-time Delta-Sigma analog-to-digital converters is often considered complex and difficult. It requires knowledge, intuition, creativity and technical expertise. Up to now, this type of architecture does not appear in the field of designing integrated electronic circuit for particle detection. However, we believe that it can provide interesting solutions, as we will show here in the case of energy measurement systems.

This thesis work is part of a research project entitled DIAMASIC. The aim is to develop an integrated readout electronics of a hodoscope detection system using diamond detectors in the context of beam monitoring for the treatment of tumors using hadrontherapy. This system must allow a spatio-temporal tagging of the used particles known as "hadron" to guarantee the safety of the patient during the treatment. This electronics is composed of two parts: a time measurement system and an energy measurement system. The design of the latter requires an ADC.

This manuscript synthesizes the modeling, design and simulation of a continuous-time low-pass Delta-Sigma modulator with a bandwidth of 10MHz (can reach 40 MHz) and targeting a resolution of 8bits with a reasonable power consumption. The first step was to analyze the possible architectures of different modulators in order to guarantee the desired specifications. Following this study, we proposed a topology for a fifth order CRFF (Cascaded Resonator Feed-Forward) modulator with an internal quantizer of 3 bits resolution and an oversampling rate of 8. In order to validate these choices and to study the impact of the imperfections linked to each block (non-idealities), we have developed a modeling methodology based on the paradigm known as Model-Based Design (MBD) through the use of SIMULINK graphical models and MATLAB scripts. This approach permitted us to specify the capabilities of each part of the modulator and also to make optimizations in terms of complexity, stability and power consumption. The data extracted from the modeling part are used in the implementation phase in a 130nm CMOS technology. The theoretical sizing of the transistors is done using the gm/ld methodology. The details of this method are discussed for the design of the amplifiers used to build the integrators of the loop filter. The results of different electrical simulations are presented, they show that the proposed architecture reaches a resolution of 8bits in a bandwidth of 10MHz.

Finally, a comparison between the modeling results and the different electrical simulations on CADENCE has been presented and the performance gap is analyzed and some solutions are proposed aiming for improvements before the fabrication of the circuit.

**Keywords:** Hodoscope, Diamond, particle detection, analog circuit, ADC, Delta-Sigma, Continuous time, MBD.

### Contents

|    | Ack   | nowledgments                                                    | i      |

|----|-------|-----------------------------------------------------------------|--------|

|    | Con   | tents                                                           | vii    |

|    | List  | of figures                                                      | X      |

|    | List  | of tables                                                       | ΧV     |

|    |       |                                                                 | vii    |

|    | List  | of Actolytis                                                    | . V 11 |

| In | trodu | action                                                          | 1      |

| 1  | Ove   | rview of the application                                        | 4      |

|    | 1.1   | Hadrontherapy                                                   | 5      |

|    |       | 1.1.1 Principles and challenges                                 | 5      |

|    |       | 1.1.2 Online beam monitoring                                    | 7      |

|    | 1.2   | CVD diamond detectors                                           | 9      |

|    |       | 1.2.1 Diamond as a material                                     | 9      |

|    |       | 1.2.2 CVD diamond for particle detection                        | 9      |

|    |       | 1.2.3 CVD diamond Hodoscope                                     | 12     |

|    | 1.3   | Read-out electronics for diamond detector                       | 14     |

|    |       | 1.3.1 Contribution to the design of the time measurement system | 15     |

|    |       | 1.3.2 The energy measurement system                             | 26     |

|    | 1.4   | Motivation                                                      | 27     |

|    | 1.5   | Summary                                                         | 27     |

| 2  | Intr  | oduction to analog to digital conversion                        | 32     |

|    | 2.1   | ADC Performance Metrics                                         | 33     |

|    |       | 2.1.1 Quantization                                              | 33     |

|    |       | 2.1.2 Dynamic parameters                                        | 34     |

|    |       | 2.1.3 Static parameters                                         | 36     |

|    |       | 2.1.4 The figure of merit FoM                                   | 39     |

|    | 2.2   | Class of architectures                                          | 40     |

|    |       | 2.2.1 Nyquist-Rate Converters                                   | 40     |

|    |       | 2.2.2 Over-sampling converters                                  | 43     |

|    | 2.3   | More about Delta Sigma ADC                                      | 46     |

|    |       | 2.3.1 Fundamental parameters: L, N, OSR                         | 46     |

|    |       | 2.3.2 Discrete-time vs Continuous-Time Delta Sigma modulator    | 47     |

|    |       | 2.3.3 High order Delta Sigma modulator                          | 48     |

|    | 2.4   | Summary                                                         | 52     |

| 3  | Syst  | tem level modeling                                              | 55     |

|    | 3.1   | Choice of topology                                              | 56     |

|    | 3.2   | System-level simulation                                         | 57     |

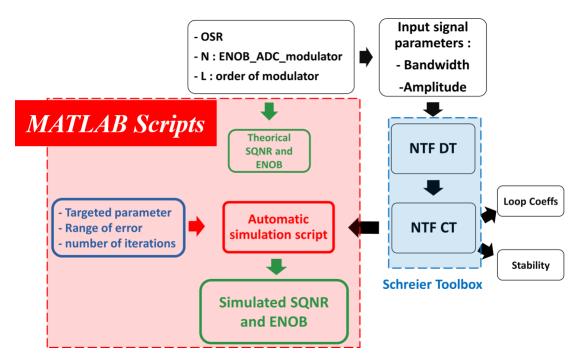

|    |       | 3.2.1 Model-Based Design approach                               | 58     |

### Contents

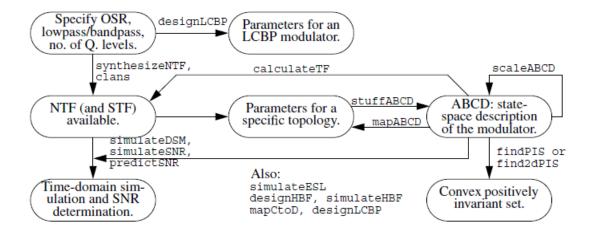

|    |       | 3.2.2       | Integration of Schreier's toolbox                                      | 60  |

|----|-------|-------------|------------------------------------------------------------------------|-----|

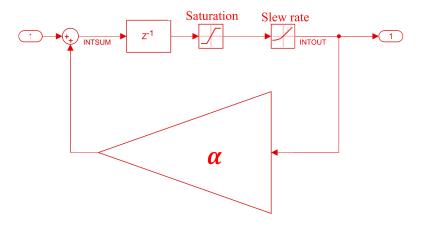

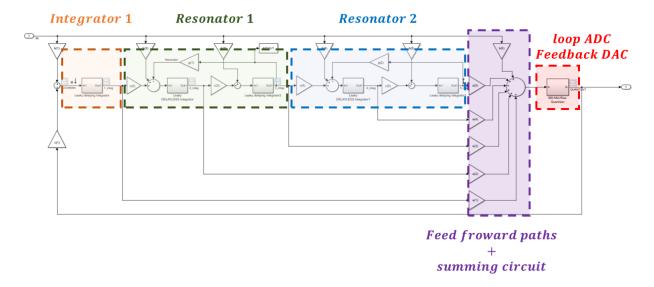

|    |       | 3.2.3       | SIMULINK model                                                         | 61  |

|    | 3.3   | Simula      | tions and results                                                      | 64  |

|    |       | 3.3.1       | The script to synthesize the modulator                                 | 64  |

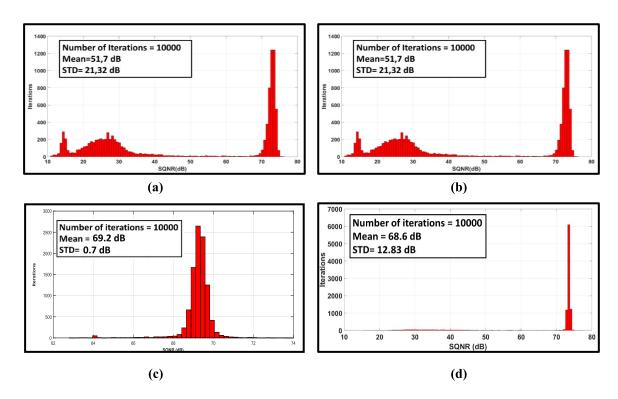

|    |       | 3.3.2       | The script of component dispersion effect                              | 69  |

|    |       | 3.3.3       | The script of the amplifiers DC gain optimization                      | 73  |

|    |       | 3.3.4       | Simulation of the ADC/DAC non-idealities                               | 75  |

|    |       | 3.3.5       | Simulation of the Excess Loop Delay (ELD)                              | 77  |

|    | 3.4   | Summa       | ary                                                                    | 78  |

| 4  | Circ  |             | el Implementation                                                      | 81  |

|    | 4.1   | $g_m/I_d$ d | design methodology for sizing transistors                              | 82  |

|    |       | 4.1.1       | Why the $g_m/I_d$ design methodology?                                  | 82  |

|    |       | 4.1.2       | Implementation of $g_m/I_d$ design methodology via Precomputed LUTs in |     |

|    |       |             | the design flow                                                        | 84  |

|    |       | 4.1.3       | Amplifier topology                                                     | 85  |

|    |       | 4.1.4       | Example of amplifier sizing                                            | 87  |

|    | 4.2   | Loop fi     | ilter                                                                  | 90  |

|    |       | 4.2.1       | Integrators sizing                                                     | 91  |

|    |       | 4.2.2       | Resonators sizing                                                      | 94  |

|    |       | 4.2.3       | Electrical simulation of the loop filter                               | 96  |

|    | 4.3   | Summi       | ng circuit                                                             | 97  |

|    |       | 4.3.1       | Amplifier topology and Sizing                                          | 98  |

|    |       | 4.3.2       | Electrical simulations and results                                     | 98  |

|    | 4.4   | Loop C      | Ouantizer                                                              | 99  |

|    |       | 4.4.1       | Quantizer Architecture                                                 | 100 |

|    |       | 4.4.2       | Simulations and results                                                | 101 |

|    | 4.5   | Feedba      | ick DAC                                                                | 103 |

|    |       | 4.5.1       | DAC Architecture                                                       | 104 |

|    |       | 4.5.2       | Simulations and results                                                | 104 |

|    | 4.6   | Full mo     | odulator Simulations                                                   | 107 |

|    |       | 4.6.1       | Electrical simulations                                                 | 108 |

|    |       | 4.6.2       | Results discussion                                                     | 109 |

|    | 4.7   |             | ary                                                                    | 111 |

| Co | nclus | sion and    | future work                                                            | 115 |

## List of Figures

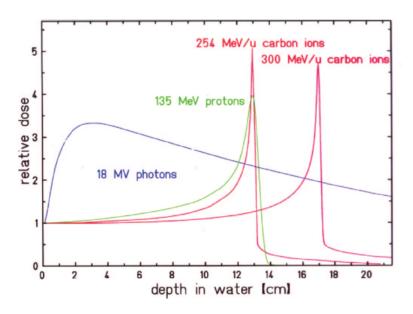

| 1.1  | Comparison of the deposited dose yield of different ions in depth, extracted from [1]                                                                                                                                                                                                                                                                                                                                   | 4        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

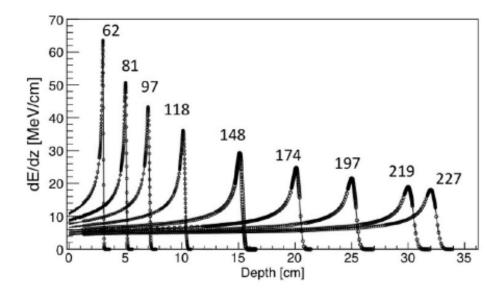

| 1.2  | Evolution of the Bragg peak depth as a function of the initial energy (in MeV) of                                                                                                                                                                                                                                                                                                                                       | ٠        |

|      | protons in water, extracted from [2]                                                                                                                                                                                                                                                                                                                                                                                    | 6        |

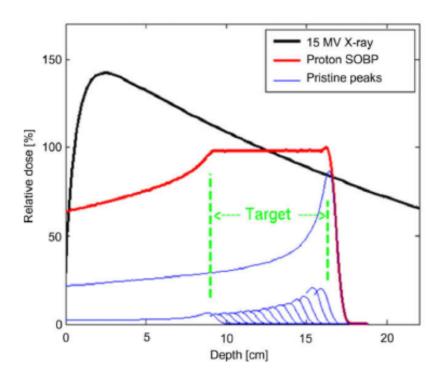

| 1.3  | Illustration of the implementation of the spread-out Bragg peak, extracted from [3].                                                                                                                                                                                                                                                                                                                                    | 6        |

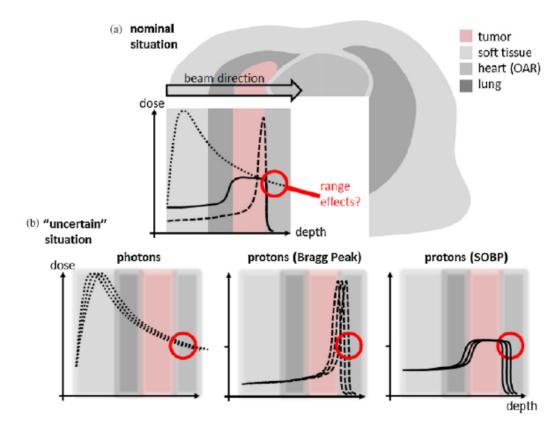

| 1.4  | Exemple of the impact of uncertainties on the dose deposit for both conventional radiotherapy and hadrontherapy, extracted from [4]                                                                                                                                                                                                                                                                                     | 7        |

| 1.5  | Schematic diagram of the contribution of spatial and temporal tagging provided by a beam hodoscope in the case of compton imaging for hadrontherapy                                                                                                                                                                                                                                                                     | 8        |

| 1.6  | Photo of the hodoscope with scintillating fibers coupled to PMTs                                                                                                                                                                                                                                                                                                                                                        | 8        |

| 1.7  | Concept diagram of a solid state ionization chamber based on a diamond detector.                                                                                                                                                                                                                                                                                                                                        | 10       |

| 1.8  | Summary diagram of the current induced in a diamond detector by a passing charged particle, extracted from [20]: (a)A particle uniformly ionizes the medium along its path and the free charges begin to drift under the effect of the electric field; (b)The drift of the two charge carriers induces a current of the same sign on the considered electrode; (c)The total induced current on the electrode is the sum | 1.1      |

| 1.0  | of the currents of the two charge carriers.                                                                                                                                                                                                                                                                                                                                                                             | 11       |

| 1.9  | Concept diagram of the CVD double-side stripped metallized diamond beam hodoscope: (a)The metallization by strips of large diamonds (left) or mosaic assembly of smaller diamonds (right); (b)The coupling of the strips to their dedicated electronics on both sides of diamond.                                                                                                                                       | 10       |

| 1 10 | dedicated electronics on both sides of diamond.                                                                                                                                                                                                                                                                                                                                                                         | 13<br>14 |

| 1.10 | r · r                                                                                                                                                                                                                                                                                                                                                                                                                   | 15       |

| 1.11 | FEE diagram for radiation detectors, extracted from [24].                                                                                                                                                                                                                                                                                                                                                               | 15       |

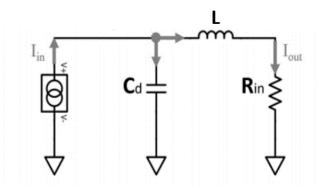

|      | Equivalent electrical model of the input stage circuit.                                                                                                                                                                                                                                                                                                                                                                 | 16       |

|      | Precise equivalent electrical model of the input stage circuit with bonding wire inductance $L$ .                                                                                                                                                                                                                                                                                                                       | 17       |

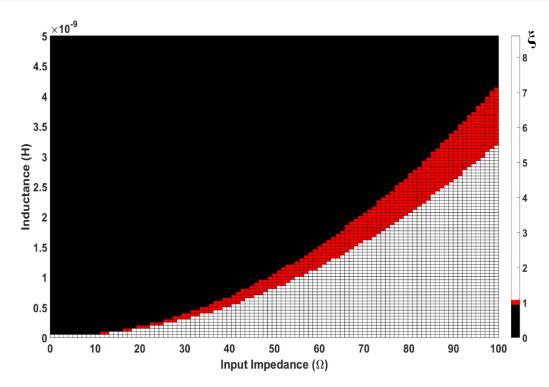

| 1.15 | Values of the damping factor for different values of input impedance and parasitic inductance.                                                                                                                                                                                                                                                                                                                          | 18       |

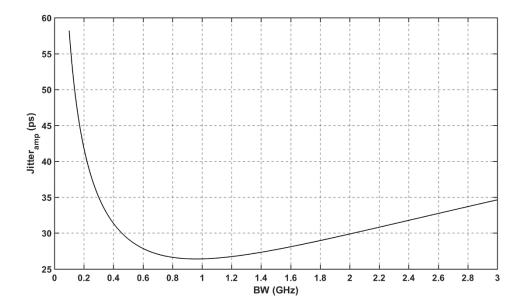

| 1.16 | Timing jitter function according to the specs of the FEE                                                                                                                                                                                                                                                                                                                                                                | 20       |

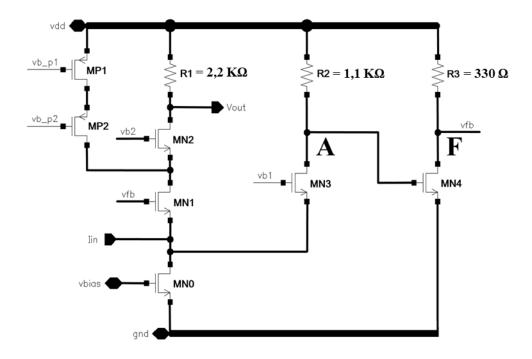

|      | Common Gate Feedforward TIA architecture                                                                                                                                                                                                                                                                                                                                                                                | 21       |

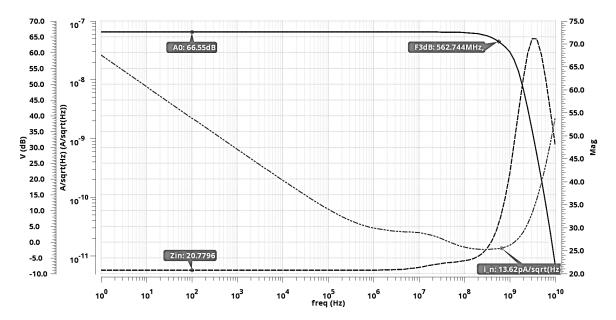

|      | AC and noise extracted simulation results                                                                                                                                                                                                                                                                                                                                                                               | 22       |

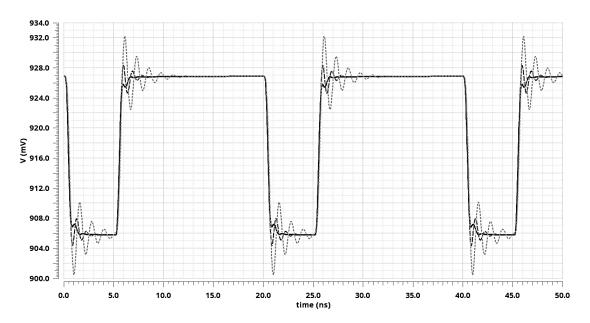

| 1.19 | Extracted transient simulation of the TIA output with $R_{in} = 20 \Omega$ and several inductance values (5 $nH$ (solid), $10 nH$ (dashed) and $20 nH$ (doted))                                                                                                                                                                                                                                                         | 23       |

| 1.20 | Extracted transient simulation of the TIA output with $R_{in} = 50 \Omega$ and several inductance values (5 $nH$ (solid), 10 $nH$ (dashed) and 20 $nH$ (doted))                                                                                                                                                                                                                                                         | 24       |

| 1.21 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 24       |

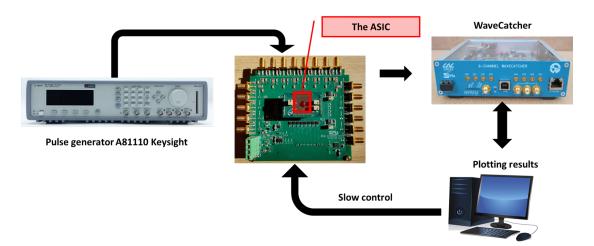

|      | The testing setup for the measurements of the timing jitter                                                                                                                                                                                                                                                                                                                                                             | 25       |

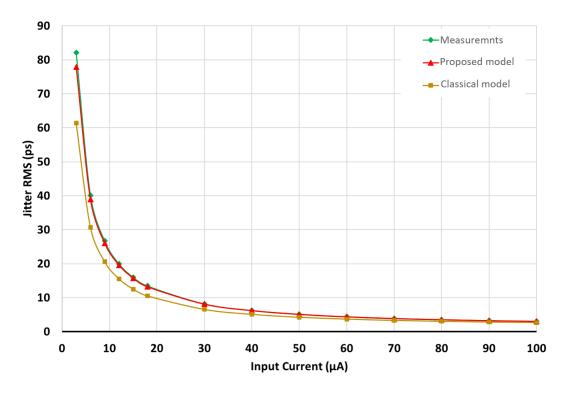

|      |                                                                                                                                                                                                                                                                                                                                                                                                                         | 25       |

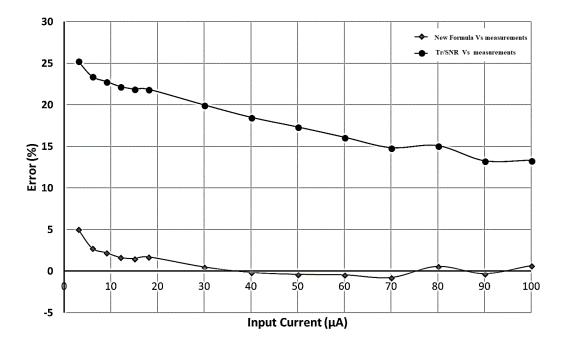

| 1.24 | Comparison of the precision of the two formulas based on measurement results                                                                                                                                                                                                                                                                                                                                            | 26       |

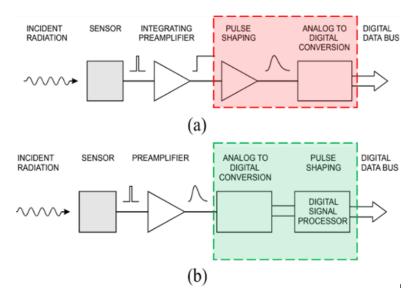

| 1.25 | (a) Simplified diagram of the classical systems; (b) Simplified diagram of the novel systems, extracted from [33].                                                                                                                                                                                                                                                                                                      | 26       |

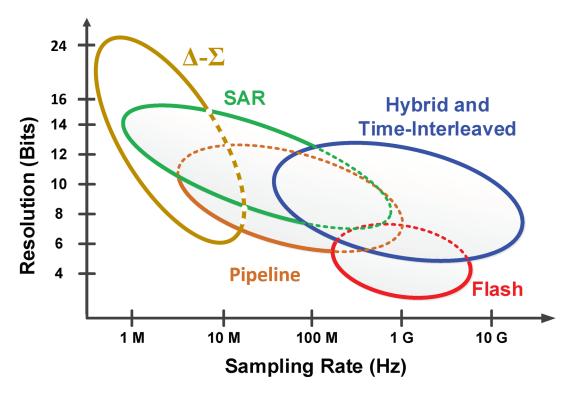

| 2.1    | Overview of different ADC architectures operating ranges, edited from [2]                    | 33 |

|--------|----------------------------------------------------------------------------------------------|----|

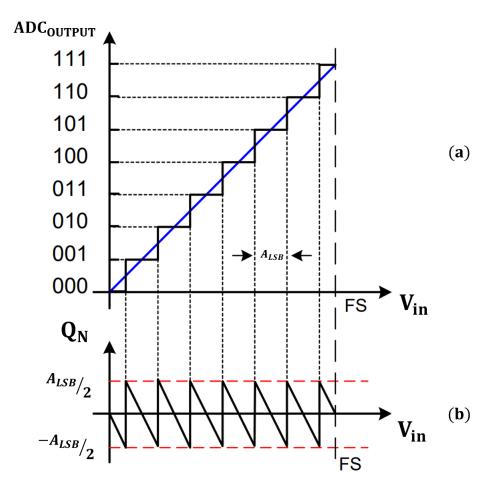

| 2.2    | (a) Transfer function of a 3-bit ideal ADC; (b) Quantization error of a 3-bit ideal          |    |

|        | ADC, edited from [3]                                                                         | 34 |

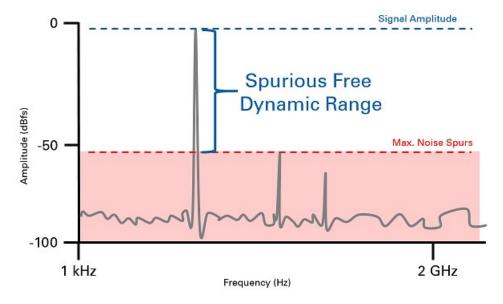

| 2.3    | Exemple of the SFDR                                                                          | 36 |

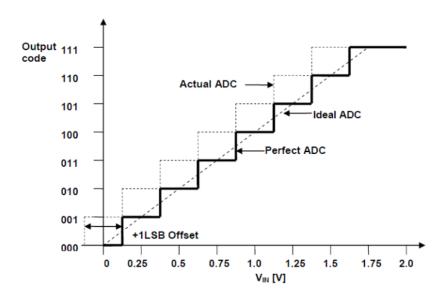

| 2.4    | Exemple of the offset error, extracted from [7]                                              | 36 |

| 2.5    | Exemple of the gain error, extracted from [7]                                                | 37 |

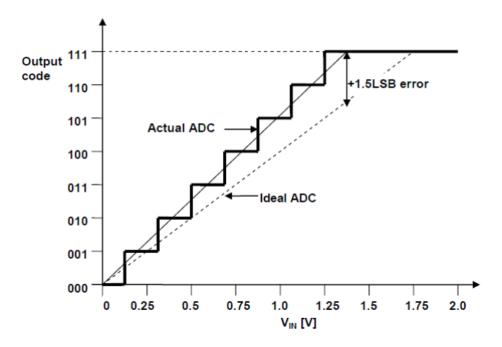

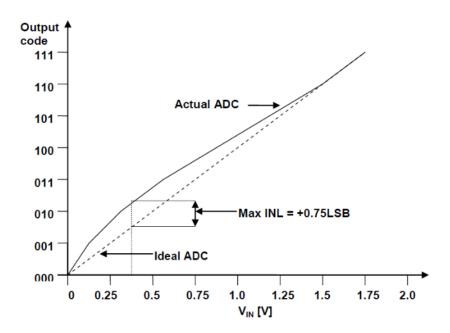

| 2.6    | Exemple of the DNL, extracted from [7]                                                       | 38 |

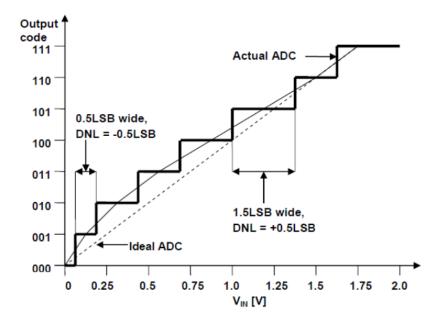

| 2.7    | Exemple of the INL, extracted from [7]                                                       | 38 |

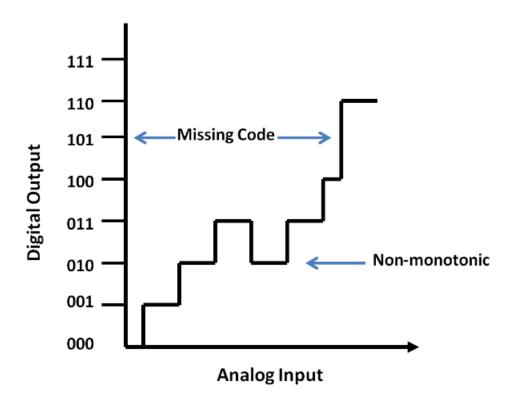

| 2.8    | Exemple of the monotonicity of a 3 bit ADC                                                   | 39 |

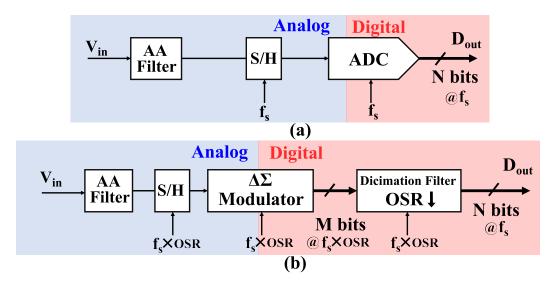

| 2.9    | (a): Block diagram of a Nyquist-rate ADC; (b): Block diagram of an oversampling              |    |

|        | ADC                                                                                          | 4  |

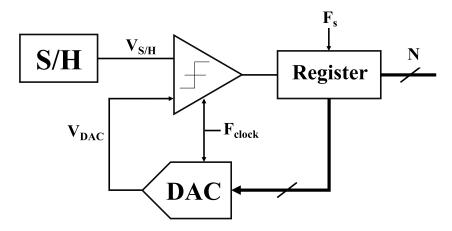

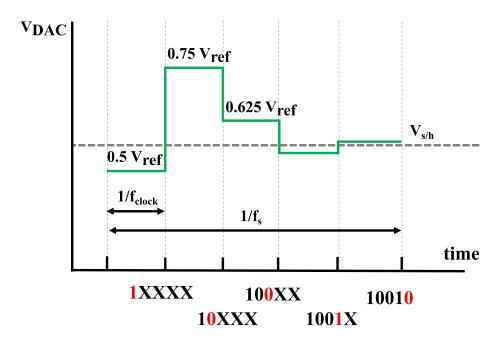

| 2.10   | Block diagram of SAR ADC architecture                                                        | 4  |

|        | Exemple of an approximation sequence of a SAR ADC                                            | 4  |

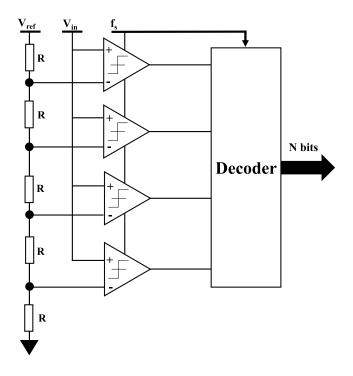

|        | Block diagram of a FLASH ADC Architecture.                                                   | 42 |

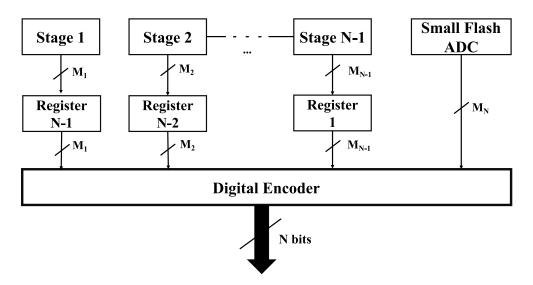

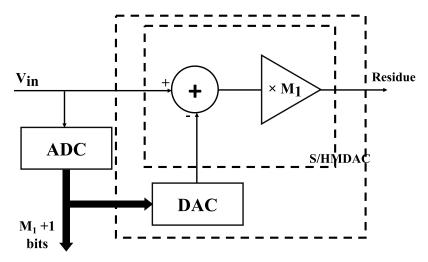

|        | Block diagram of a PIPELINE ADC Architecture                                                 | 42 |

|        | Block diagram of a MDAC                                                                      | 4  |

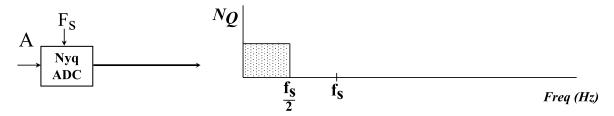

|        | Power spectral density of quantization noise in Nyquist-rate ADC                             | 4  |

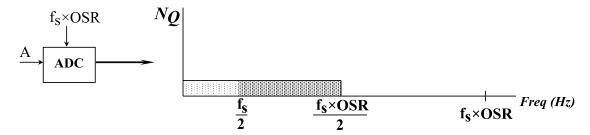

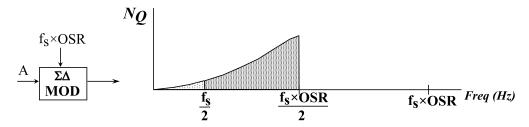

|        | Power spectral density of quantization noise with oversampling                               | 4  |

|        | Power spectral density of quantization noise with oversampling and noise shaping.            | 4. |

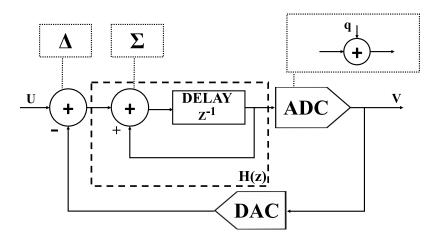

|        | Block diagram of a $\Delta\Sigma$ ADC                                                        | 4: |

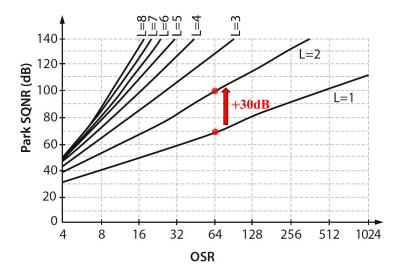

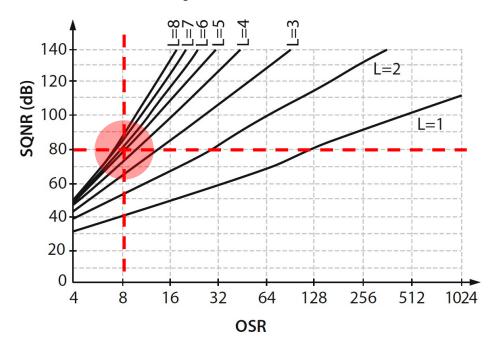

|        | SQNR values for different orders of noise shaping and OSR value                              | 4  |

|        | Implementation of a $\Delta\Sigma$ modulator with: (a): DT loop filter; (b): CT loop filter; | •  |

| 2,20   | (c): Hybrid DT/CT loop filter                                                                | 4  |

| 2 21   | Example of implementation of a third order $\Delta\Sigma$ modulator: (a): Single loop        | •  |

| 2,21   | implementation; (b): 2-1 MASH implementation                                                 | 4  |

| 2. 22. | Block diagram of MASH Architecture                                                           | 5  |

|        | Different styles of compensation: (a): Feedforward loop filter; (b): Feedback loop           |    |

| _,     | filter; (c):Mixed feedforward-feedback loop filter.                                          | 5  |

|        |                                                                                              |    |

| 3.1    | A simplified block diagram of the proposed CT $\Delta\Sigma$ modulator                       | 5  |

| 3.2    | SQNR values for different key parameters                                                     | 5  |

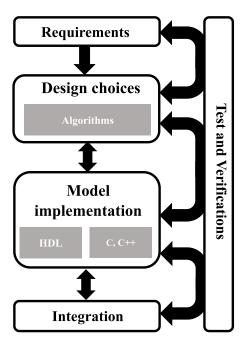

| 3.3    | A generic representation of the Model-Based Design workflow                                  | 5  |

| 3.4    | Flowchart of the implementation of Model-Based Design for ASIC design                        | 5  |

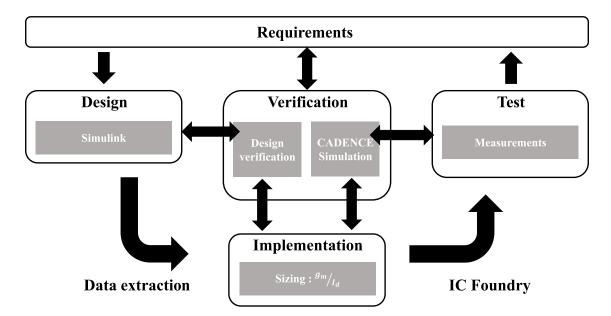

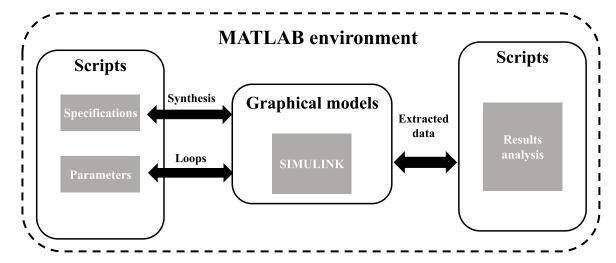

| 3.5    | A diagram of the interaction between MATLAB and SIMULINK in our workflow.                    | 6  |

| 3.6    | The integration of Schreier's toolbox in our proposed workflow                               | 6  |

| 3.7    | Flowchart of key Schreier's toolbox functions, extracted from [3]                            | 6  |

| 3.8    | Graphical model of the integrator in SIMULINK                                                | 6  |

| 3.9    | Graphical model of the Loop quantizer in SIMULINK                                            | 6  |

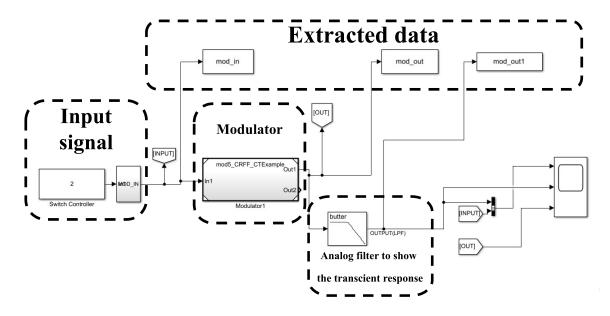

| 3.10   | Graphical model of the proposed modulator in SIMULINK                                        | 6  |

|        | Graphical model of the proposed benchmark model in SIMULINK                                  | 6  |

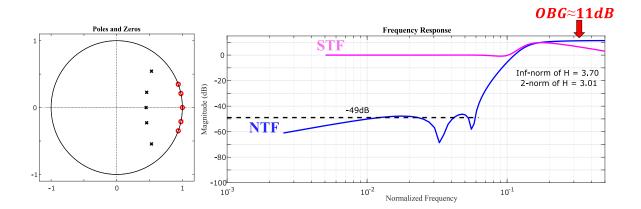

|        | The frequency response of the synthesized NTF and STF of the targeted modulator.             | 6  |

|        | An example of the predicted behavior of the system and the values of the SQNR                |    |

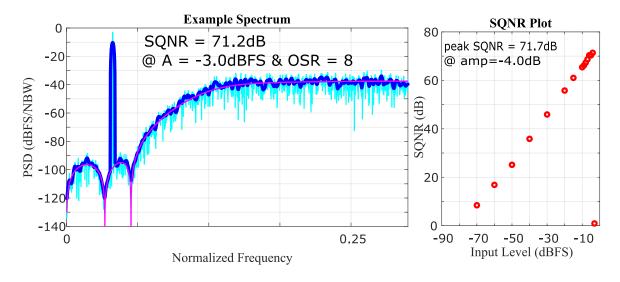

|        | for different amplitude levels                                                               | 6  |

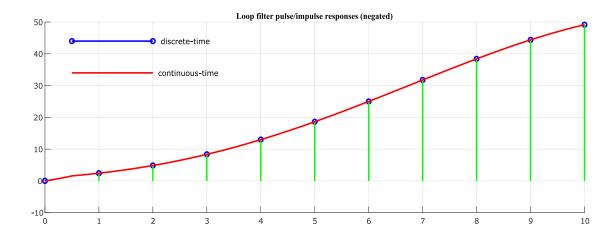

| 3.14   | The DT equivalent pulse response of the CT loop filter                                       | 6  |

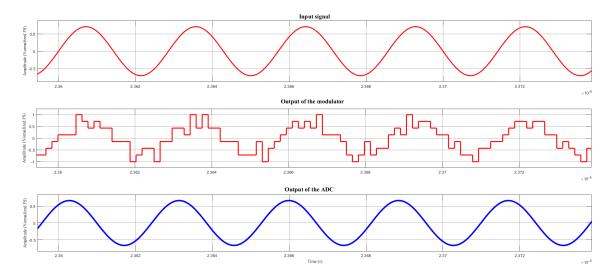

|        | Transient response of the synthesized modulator for a sinwave input signal                   | 6  |

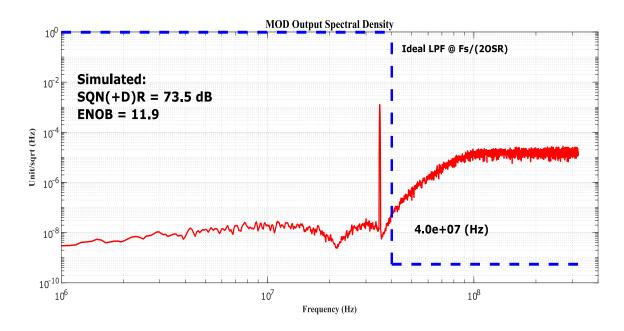

|        | PSD of the proposed architecture with a sinewave input.                                      | 6  |

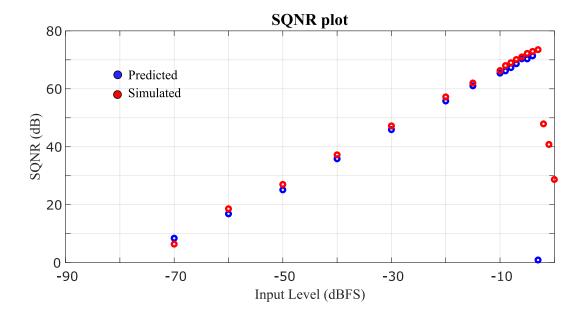

|        | The simulated behavior vs the predicted behavior of the modulator for different              |    |

|        | amplitude levels.                                                                            | 6  |

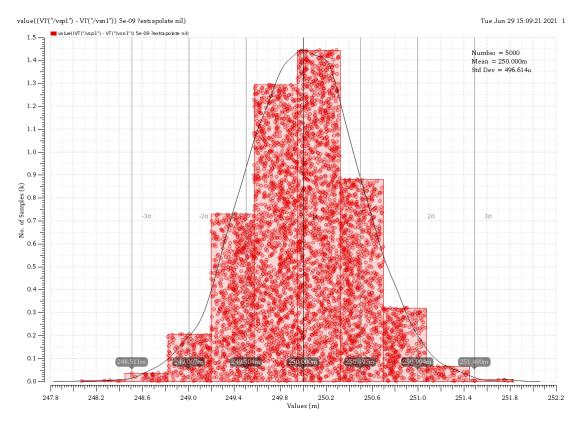

| 3.18 | Histogram representation of SQNR values for: (a): 10000 simulations with $\Delta p_i = 20\%$ and $\delta m_i = 1\%$ ; (b): 10000 simulations with $\Delta p_i = 20\%$ and $\delta m_i = 0\%$ ; (c): |          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | 10000 simulations with $\Delta p_i = 0\%$ and $\delta m_i = 1\%$ ; (d): 10000 simulations with                                                                                                      | 71       |

| 2 10 | $\Delta p_i = 10\%$ and $\delta m_i = 0.5\%$ for critical parameters.  Maximum output swing of the first integrator Vs SQNR for a dispersion of $\Delta p =$                                        | / 1      |

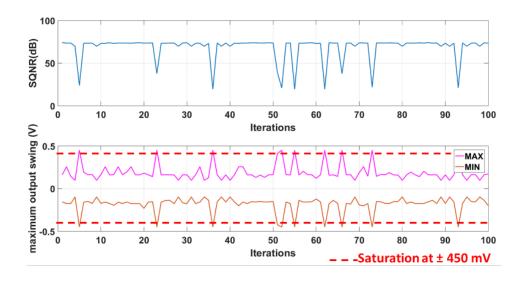

| 3.19 | 20%, $\delta m = 1\%$ of the coefficient $a_1, \ldots, a_m = 1$                                                                                                                                     | 72       |

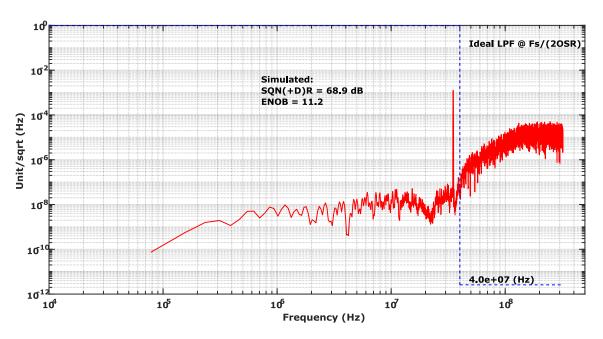

| 3 20 | PSD of the modulator using the obtained DC gains                                                                                                                                                    | 74       |

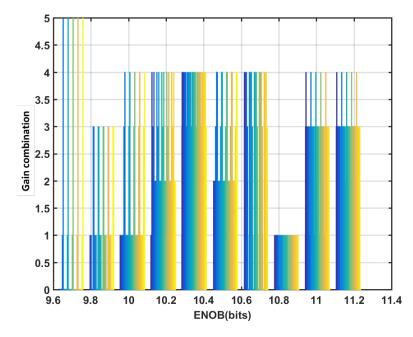

|      | Histogram of the ENOB values for all the combinations.                                                                                                                                              | 75       |

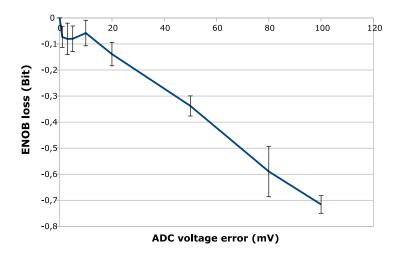

|      | The loss in ENOB for different values of the ADC voltage error.                                                                                                                                     | 76       |

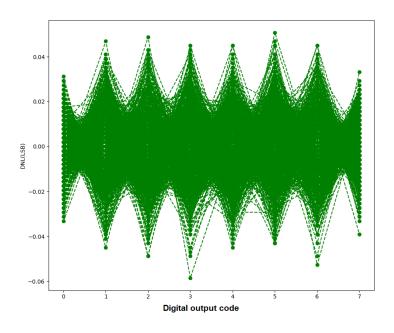

|      | Extracted DNL values for a 3 mV ADC voltage error.                                                                                                                                                  | 76<br>76 |

|      | The loss of the ENOB as a function of DAC DNL                                                                                                                                                       | 70<br>77 |

|      | Response of the modulator for different values of the ELD using different values                                                                                                                    | / /      |

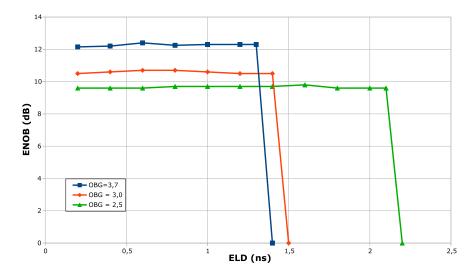

| 5.25 | of the OBG                                                                                                                                                                                          | 78       |

|      | of the OBG                                                                                                                                                                                          | 70       |

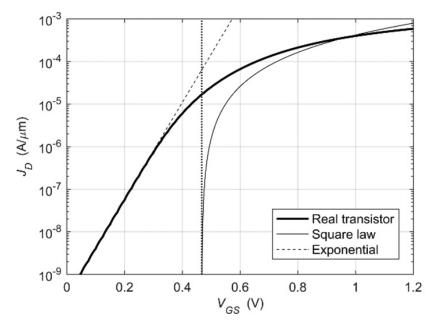

| 4.1  | Current density of a minimum-length n-channel device in 65-nm CMOS                                                                                                                                  |          |

|      | technology versus $V_{GS}$ . The dotted vertical line corresponds to the device's                                                                                                                   |          |

|      | threshold voltage, extracted from [1]                                                                                                                                                               | 82       |

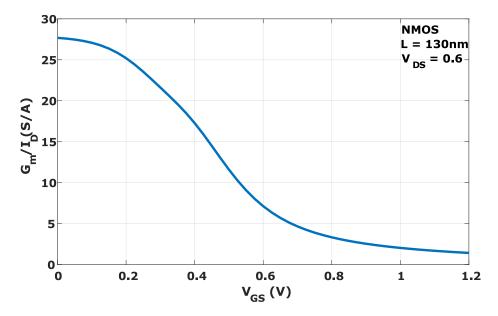

| 4.2  | The extracted $g_m/I_d$ values for different values of $V_{GS}$ of our used 130nm CMOS                                                                                                              |          |

|      | technology.                                                                                                                                                                                         | 83       |

| 4.3  | Block diagram of a single ended two stages NCFF opamp, extracted from [15]                                                                                                                          | 85       |

| 4.4  | A simplified diagram of the SIMULINK model of the proposed opamp                                                                                                                                    | 86       |

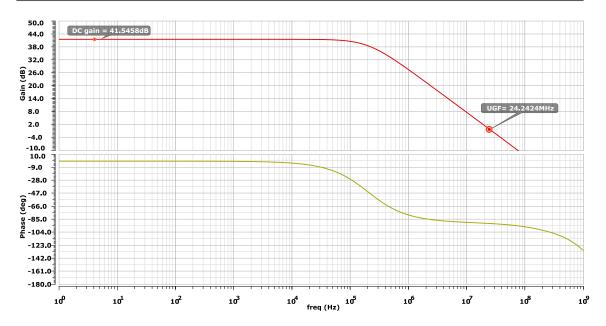

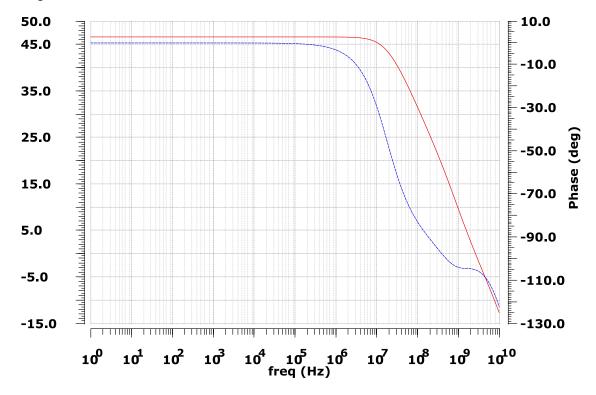

| 4.5  | The frequency response of the SIMULINK model using model-based design                                                                                                                               | 87       |

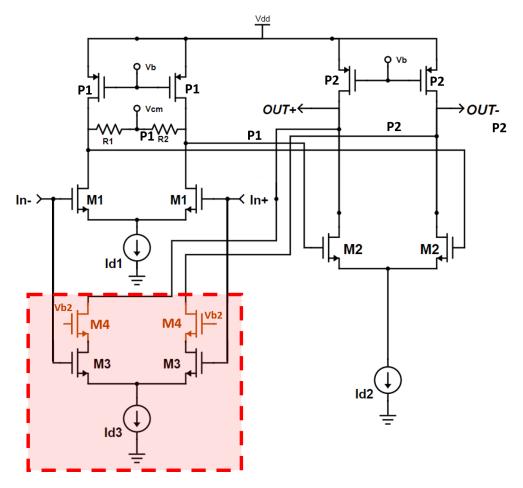

| 4.6  | Simplified schematic of the proposed two-stages NCFF opamp                                                                                                                                          | 88       |

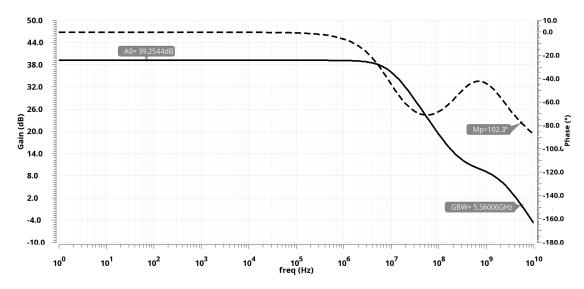

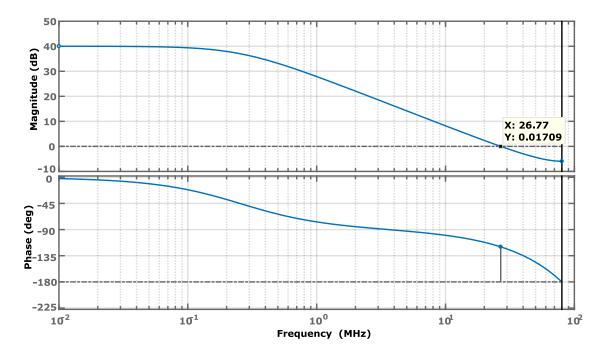

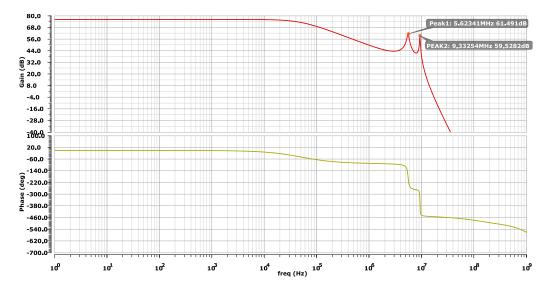

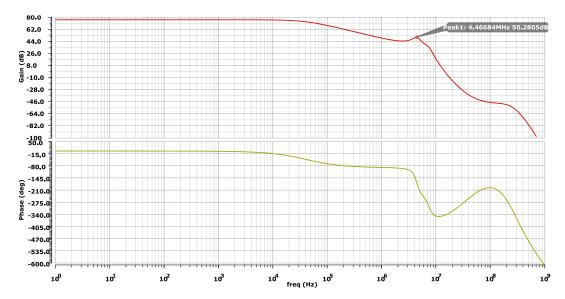

| 4.7  | The frequency response of the proposed opamp                                                                                                                                                        | 90       |

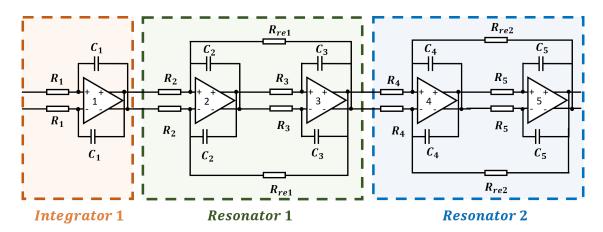

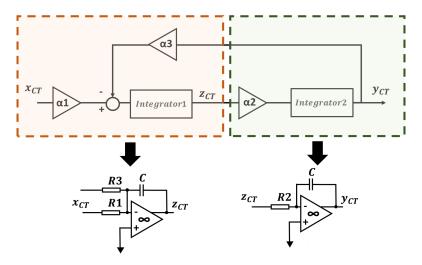

| 4.8  | Circuit level structure of the loop filter                                                                                                                                                          | 91       |

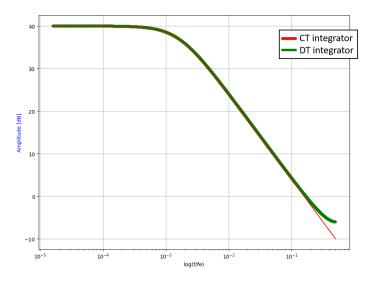

| 4.9  | Comparison between the response of CT integrator and DT integrator (with a finite                                                                                                                   |          |

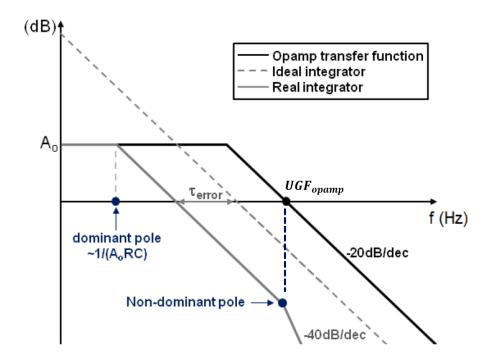

|      | DC gain of opamp = $40 dB$                                                                                                                                                                          | 91       |

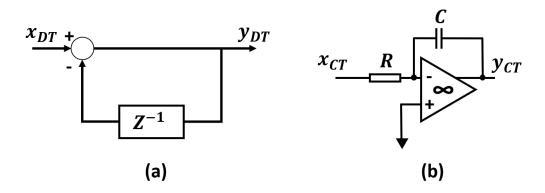

| 4.10 | Simplified structure of an ideal CT integrator and an ideal DT integrator                                                                                                                           | 92       |

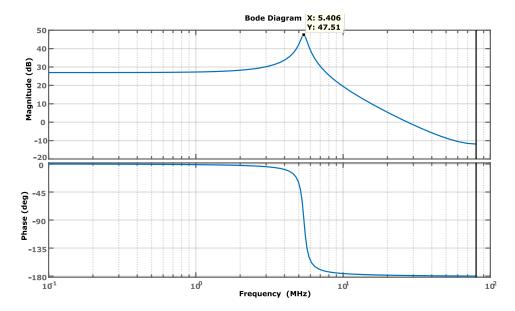

| 4.11 | The frequency response of the first DT integrator                                                                                                                                                   | 92       |

|      | The frequency response of the first circuit level CT integrator                                                                                                                                     | 93       |

| 4.13 | The frequency response of the first CT integrator, extracted from [12]                                                                                                                              | 93       |

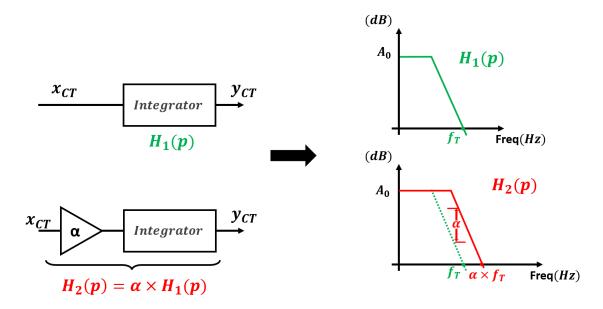

| 4.14 | Simplified diagram of the impact of an input coefficient on the frequency response                                                                                                                  |          |

|      | of an integrator                                                                                                                                                                                    | 94       |

|      | Simplified diagram of the implementation of the resonator                                                                                                                                           | 95       |

|      | The frequency response of the first DT resonator                                                                                                                                                    | 95       |

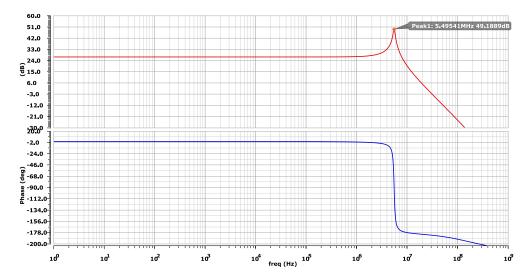

|      | Electrical simulation of the frequency response of the first CT circuit level resonate                                                                                                              |          |

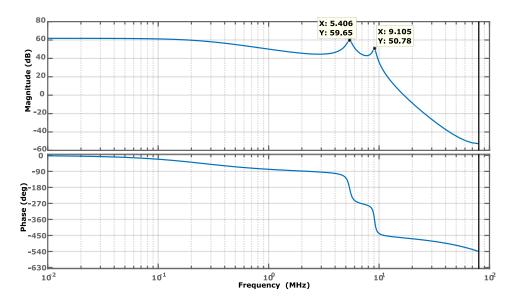

|      | The frequency response of the first DT loop filter                                                                                                                                                  | 96       |

|      | Electrical simulation of the frequency response of the CT circuit level loop filter.                                                                                                                | 97       |

|      | Simplified circuit level implementation of the summing stage                                                                                                                                        | 97       |

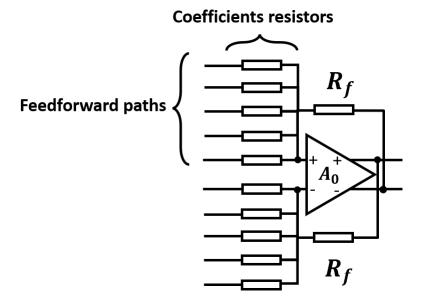

|      | Simplified schematic of the proposed summing opamp                                                                                                                                                  | 98       |

|      | The frequency response of the proposed summing opamp                                                                                                                                                | 99       |

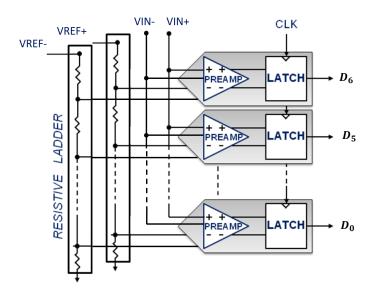

|      | Simplified schematic of the proposed differential flash ADC                                                                                                                                         | 100      |

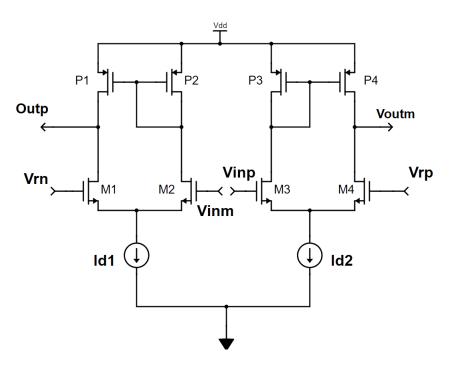

|      | Schematic of the preamplifier                                                                                                                                                                       | 100      |

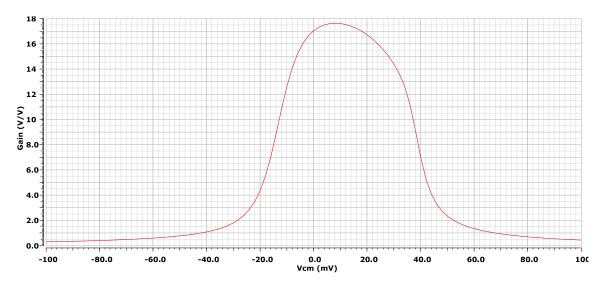

|      | Gain variation versus CM difference between input and reference signals                                                                                                                             | 101      |

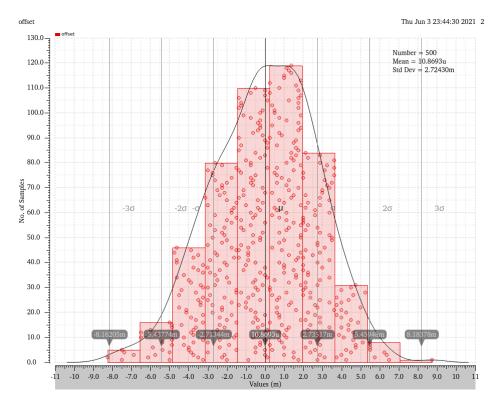

|      | Histogram of the Monte Carlo simulations of the offset of the comparator                                                                                                                            | 102      |

|      | Histogram of the Monte Carlo simulations of the precision of the reference voltage                                                                                                                  |          |

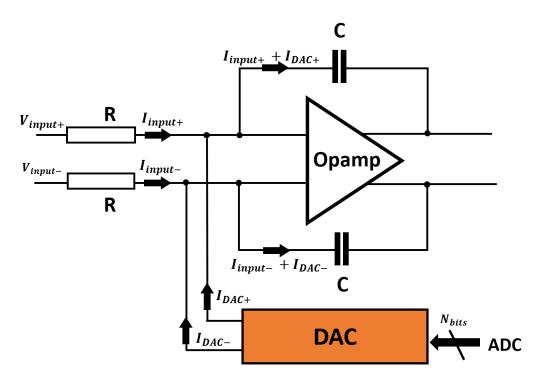

|      | Simplified diagram of the implementation of the feedback DAC.                                                                                                                                       | 103      |

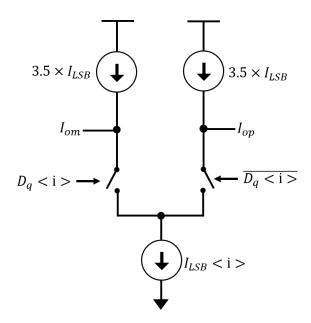

| 4.29 |                                                                                                                                                                                                     | 104      |

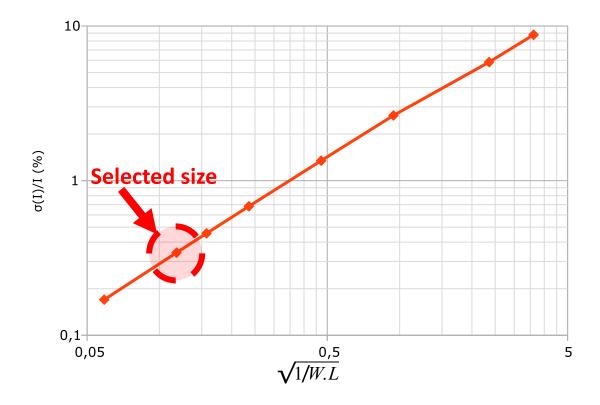

|      | Technology matching for NMOS current mirror.                                                                                                                                                        | 105      |

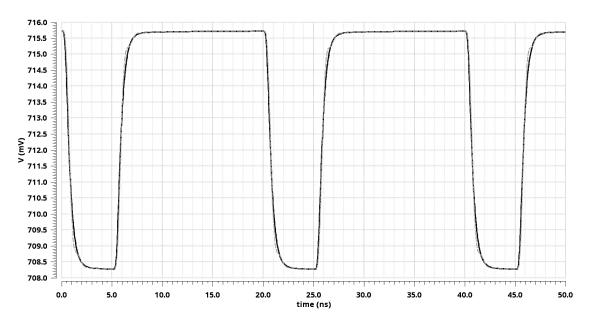

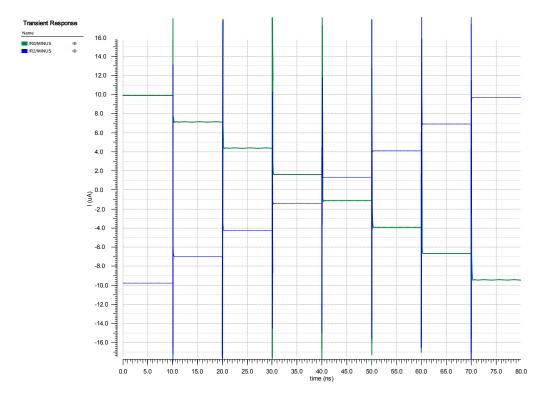

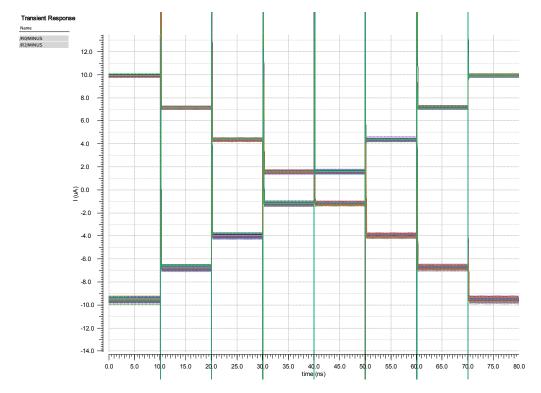

| 4.31 | The transient response of the proposed feedback DAC                                                                                                                                                 | 106      |

| 4.32 | The transient response of the proposed feedback DAC through Monte-Carlo             |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | simulations                                                                         | 106 |

| 4.33 | The values of the DNL for 500 runs.                                                 | 107 |

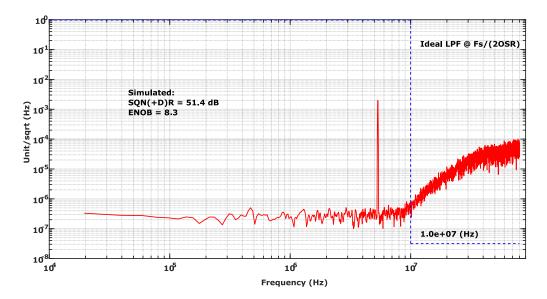

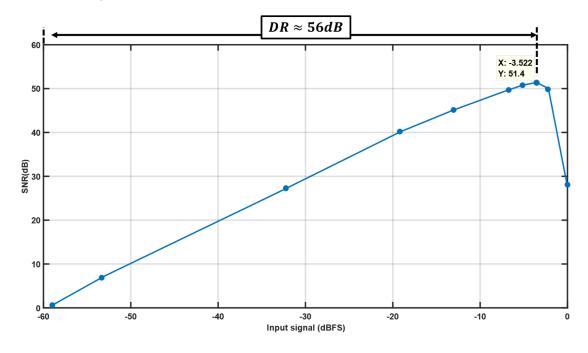

| 4.34 | Simulated output PSD of the modulator with a $-3 dBFS$ , 5.33 MHz input signal.     | 108 |

| 4.35 | Simulated SNR versus input signal power.                                            | 108 |

| 4.36 | The frequency response of the circuit level loop filter using the resistor in serie |     |

|      | with the feedback capacitor.                                                        | 109 |

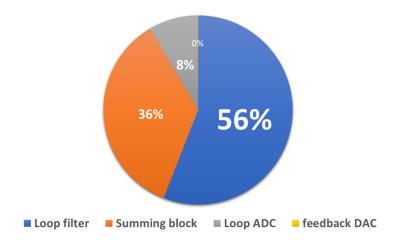

| 4.37 | Breakdown of the power consumption among the main blocks of the modulator           | 110 |

### List of Tables

| 1.1  | Properties of Diamond Vs Silicon, extracted from [12] | 9   |

|------|-------------------------------------------------------|-----|

| 1.2  | ENBW vs Filter order for low-pass filters             | 19  |

| 1.3  | Key parameters of the proposed TIA                    | 23  |

| 2.1  | Comparison of DT and CT $\Delta\Sigma$ modulation     | 48  |

| 3.1  | Proposed specifications of the CT $\Delta\Sigma$ ADC  | 56  |

| 3.2  | Coefficients of the loop filter                       | 66  |

| 3.3  | SQNR mean and STD for each coefficient simulation     | 71  |

| 3.4  | Optimized DC gain values of each integrator.          | 74  |

| 4.1  | Desired specifications of the proposed opamp          | 86  |

| 4.2  | Extracted parameters from SIMULINK model              | 87  |

| 4.3  | The sizing of transistors of the proposed topology    | 89  |

| 4.4  | Design specifications of the proposed opamp           | 90  |

| 4.5  | The sizing of transistors of the proposed topology    | 99  |

| 4.6  |                                                       | 101 |

| 4.7  |                                                       | 103 |

| 4.8  |                                                       | 107 |

| 4.9  |                                                       | 109 |

| 4.10 |                                                       | 110 |

| 4.11 |                                                       | 110 |

### List of Acronyms

$\Delta\Sigma$  delta-sigma

**AAF** anti-aliasing filter

**ADC** analog to digital converter

**CM** common mode

CMOS complementary metal-oxide-semiconductor

**CT** continuous time

**CT-DT** continuous time to discrete time

**CVD** chemical vapor deposition

**DAC** digital to analog converter

dB decibel

dBFS decibels relative to the full-scale input signal

**DEM** dynamic element matching

**DNL** differential non linearity

**DR** dynamic range

**DSP** digital signal processor

**DT** discrete time

**DWA** data weighted averaging

**ENOB** effective number of bits

**ELD** excess loop delay

**FFT** fast Fourier transform

**FoM** figure of merit

**FS** full scale signal range (peak-to-peak)

**GBW** gain bandwidth product

**HD** harmonic distortion

**IBN** in band noise

IC integrated circuit

**INL** integral non linearity

**LP** low pass

**LSB** least significant bit

MASH multistage noise shaping

MIP minimum ionizing particle

MSA maximum stable amplitude

MSB most significant bit

NMOS N-type metal-oxide-semiconductor

**NTF** noise transfer function

NRZ non return to zero

**OAR** organs at risk

**Opamp** operational amplifier

**OSR** oversampling ratio

**pCVD** polycrystalline CVD

**PDF** probability density function

**PMOS** P-type metal-oxide-semiconductor

**PSD** power spectral density

**PVT** power voltage temperature

**RMS** root mean square

**RZ** return to zero

**S/H** sample and hold

**SAR** successive approximation register

**sCVD** single crystal CVD

**SFDR** spurious free dynamic range

**SNR** signal to noise ratio

**SNDR** signal to noise and distortion ratio

**SQNR** signal to quantization noise ratio

**SR** slew rate

**STF** signal transfer function

**THD** total harmonic distortion

**TIA** Transimpedance amplifier

### Introduction

"If you want to find the secrets of the universe, think in terms of energy, frequency and vibration."

— Nikola Tesla, inventor and engineer

IAMOND is a large gap semiconductor material with very interesting physical properties for particle detection. This new generation of detectors is intended to be used for the design of a beam hodoscope with very high temporal resolution in the context of improving the performance of online monitoring systems in hadrontherapy. This latter is a novel cancer treatment method that proposes to use, in a number of clinical situations, light ion beams instead of X-ray beams as a means of irradiating tumors. It allows to generate advantageous dose deposition profiles compared to the X-ray beams used in the conventional radiotherapy. This dose deposition is described as a sharp profile in depth and called Bragg peak. Yet, this treatment method suffers from uncertainties about the actual path of the ions in the patient which is dangerous. Thus, various research groups are working to develop methods for online verification and monitoring of ion beams pathways.

In this context, the national collaboration CLaRyS¹ is developing detection methods for the online monitoring of ion pathways. The particularity of the work of this collaboration is that it proposes to add a beam hodoscope to the already developed gamma cameras. Its main goal is providing a spatial and temporal tagging of the used ion beams. Spatial tagging allows to obtain an image of the beam cross section and brings complementary information for the image reconstruction of the treatment. Temporal tagging enables an efficient rejection of the background noise caused by the detection of other secondary particles by the gamma cameras (mainly neutrons) by measuring the time difference between the moment of detection of the photon by the camera and that of the ion by the hodoscope. A temporal resolution of the order of 100 ps should be achieved to improve the efficiency and sensitivity of the monitoring system. This performance is not achievable with the classic scintillating fibers hodoscope. The collaboration has therefore chosen to develop a new hodoscope based on CVD (Chemical Vapor Deposition) diamond detectors.

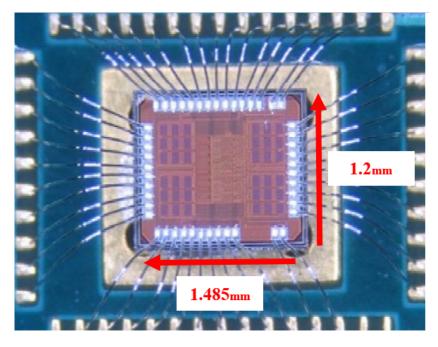

Within the framework of these developments, DIAMASIC project is founded to build the custom integrated read-out electronics of this CVD diamond hodoscope. The final circuit is a multichannel ASIC composed of two systems: a time measurement system with a timing resolution of less than 100 ps and an energy measurement system based on an innovative ADC architecture. The developments presented in this dissertation are a part of the DIAMASIC project, it was carried out in the electronic department of the Laboratory of Subatomic Physics and Cosmology (LPSC) of Grenoble. It focuses on the modeling and the design of an ADC based on a continuous time low-pass Delta-Sigma modulator for the energy measurement system with a

<sup>&</sup>lt;sup>1</sup>CLaRyS stands for "Contrôle en Ligne de la hAdronthérapie par détection de RaYonnements Secondaires", it is composed of four laboratories: le Laboratoire de Physique Subatomique et de Cosmologie (LPSC) de Grenoble, l'Institut des Deux Infinis de Lyon (IP2I Lyon), le Centre de Physique des Particules de Marseille (CPPM) et le Centre de Recherche en Acquisition et Traitement de l'Image pour la Santé (CREATIS) de Lyon.

bandwidth of 10 MHz (can reach 40 MHz), and targeting a resolution of 8 bits with a reasonable power consumption. This dissertation is organized as follows:

Chapter 1 describes the targeted medical application and the use of CVD diamond detectors. It starts with an introduction to the principles of hadrontherapy and the need of an hodoscope, followed by details about CVD diamond detectors and its response. The desired requirements of the ASIC are explained with emphasis on our contribution and results in the design of the timing measurement system. The chapter concludes with an explanation about the motivation to explore a new architecture for the energy measurement system.

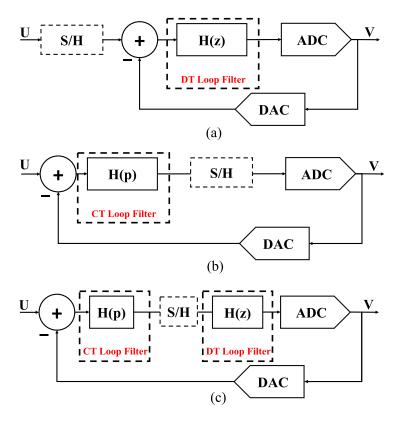

**Chapter 2** explains the basics of the analog to digital conversion and introduces the delta-sigma architecture and its features. At the beginning of this chapter, ADC performance metrics are illustrated followed by an analysis of its two classes: Nyquist-rate converters and over-sampling converters. After that, the principle of delta-sigma modulator is shown with a focus on its fundamental parameters. The two types of Delta-Sigma modulators, DT and CT, are then described and compared. The chapter concludes with a presentation of the different kinds of implementing high order modulators and the benefits of each one.

Chapter 3 deals with the system-level modeling and the use of the model-based design paradigm. A proposed workflow for the design of the CT modulator based on this approach is detailed and explained. At first, a block diagram of the chosen topology is introduced with the targeted specifications. Then, the integration of Schreier's toolbox is explained using a combination of MATLAB scripts and SIMULINK graphical models. Different scripts starting from synthesizing the modulator by calculating the various coefficients related to each stage, then followed by analyzing its behavior against different non-idealities of each building block are illustrated. The chapter concludes with an interpretation of the results of all these simulations.

Chapter 4 describes the transistor-level implementation using the  $g_m/I_d$  design methodology. It starts with an introduction of this methodology and its integration in our proposed workflow. An illustration of this step is discussed through the sizing of the amplifier used in building the various integrators of the modulator. Results of sizing and electric simulations of the loop filter in CADENCE are shown and discussed. The performances of the loop quantizer and the feedback DAC are analyzed as well. The chapter concludes with an examination of the performances of the proposed modulator and a comparison with the modeling results.

The dissertation ends with a general conclusion of the overall work performed during this thesis and makes suggestions for future work.

1

### Overview of the application

In this chapter, the medical application of the designed readout electronics and its specifications are introduced. Details about this therapy, the technology of the detector and both timing and energy measurement systems are presented.

### **Contents**

| 0011001105 |                                                                    |

|------------|--------------------------------------------------------------------|

| 1.1        | Hadrontherapy                                                      |

|            | 1.1.1 Principles and challenges                                    |

|            | 1.1.2 Online beam monitoring                                       |

| 1.2        | CVD diamond detectors                                              |

|            | 1.2.1 Diamond as a material                                        |

|            | 1.2.2 CVD diamond for particle detection                           |

|            | 1.2.3 CVD diamond Hodoscope                                        |

| 1.3        | Read-out electronics for diamond detector                          |

|            | 1.3.1 Contribution to the design of the time measurement system 15 |

|            | 1.3.2 The energy measurement system                                |

| 1.4        | <b>Motivation</b>                                                  |

| 1.5        | Summary                                                            |

### 1.1 Hadrontherapy

### 1.1.1 Principles and challenges

Cancer is an uncontrolled growth of cells, which can invade and spread to distant sites of the human body. Cancers have severe health consequences and are leading cause of death. Early detection, accurate diagnosis, and effective treatments are key issues for cancer survival rates.

The three treatment options available today are surgery, chemotherapy and radiotherapy. In conventional radiotherapy, X-ray photons are used to deposit an accurate dose to the tumor. The major constrain in radiotherapy, is to spare the healthy tissues of the patient from the radiation and target directly the cancerous cells. As we see in figure 1.1 [1](depth curves are generally used to compare different types of techniques, this illustrates the evolution of the dose deposition of different particle beams as a function of the depth of interaction in the tissue, here, in water). X-rays deposit their energy and release the dose close to the surface of the target, we notice as well that the shape of the relative dose is not selective. Photons of higher energy, 6 to 18 MeV have more relative dose and a better penetration in the patient's body. With the progress in the nuclear science, charged particles (protons and carbon ions) known also as hadrons are aimed to be used in cancer treatment. These particles have a better dosage deposit location by comparison with the photons. They leave maximum of their energy at the end of their trajectory, which is known as the Bragg peak.

Figure 1.1: Comparison of the deposited dose yield of different ions in depth, extracted from [1].

The position of this pic can be controlled through the initial energy of the ions as shown in figure 1.2 [2].

From this, hadrontherapy is defined as a non-invasive external radiotherapy technique using light ion beams as a means of irradiating tumors. Thus, although figure 1.1 shows that the Bragg peak can be defined at an exact point, it is never really the case because of the statistical fluctuations on the path of the ions. The ion beams suffer from a longitudinal and transverse spatial dispersion governed by the so-called *straggling* [2].

Also, it should be noted that if the Bragg peak generated by a monochromatic ion beam is defined on a small thickness, the tumor volume to be treated can be several centimeters in diameter. In order to be able to irradiate uniformly the whole tumor volume, a spread-out Bragg peak (SOBP) is used as shown in figure 1.3. Several ion beams with decreasing energies are used to scan the tumor in depth from the distal peak (blue Bragg peaks in the figure).

Figure 1.2: Evolution of the Bragg peak depth as a function of the initial energy (in MeV) of protons in water, extracted from [2].

Figure 1.3: Illustration of the implementation of the spread-out Bragg peak, extracted from [3].

Although hadrontherapy represents an alternative solution to conventional radiotherapy that can be very interesting from a clinical point of view, its concrete implementation is not so ideal as shown above. One of the main limitations of hadrontherapy, is that it is not used to its full potential because of uncertainties about the path of the ions in the patient. Some of these uncertainties are inevitable and/or systematic and others are subject to possible improvement. An example of this problematic is shown in figure 1.4. It is assumed here that a tumor has developed in the patient's lung, close to the heart, which is an organ at risk (OAR).

Figure 1.4: Exemple of the impact of uncertainties on the dose deposit for both conventional radiotherapy and hadrontherapy, extracted from [4].

As we can see, an error made in conventional radiotherapy treatment does not result in a major error in the dose deposition profile. Conversely, an error in the path of the ions in the patient can generate a double negative effect: an under-dosing of the tumor volume and an overdosing of the healthy tissue (so close to the OAR).

### 1.1.2 Online beam monitoring

At this level, it is obvious that the hadrons trajectory need to be carefully defined and specified for the safety of patients. The implementation of such control techniques is still an active research topic. Several ways are explored using different physical phenomena [4, 5, 6, 7].

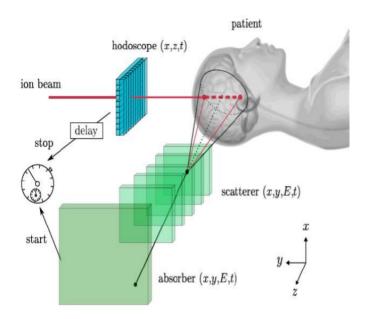

The Bragg peak must be located in the targeted cells. An online monitoring system is required for checking hadrons trajectories. During a treatment by hadron therapy, a part of ions undergoes one or few nuclear fragmentations and emit a secondary gamma radiation. Detection of these secondary gamma radiations is the basis of the method used to localize the dose deposition into the patient. In figure 1.5 we see a proposed system for the trajectory detection of the particles in hadrontherapy.

This configuration uses an hodoscope for labeling the incoming ions providing both transverse coordinates beam location and time measurements. The compton camera consists of diffusion detectors (scatterer) and an absorption detector (absorber), which detects the secondary gamma rays following the nuclear fragmentation of hadrons in the patient's tissues. Gamma rays can be associated to the corresponding ion using very sharp time coincidences (less than 100 ps). More details about the compton camera can be found in [8, 9, 10]. For this study, we will focus on the hodoscope part of the system. these detector should be able to ensure three essential qualities:

• It must be position sensitive;

- It must have a good temporal resolution (at least of the order of 1 ns);

- It must be sufficiently resistant to radiation over time without any prohibitive variation in its performances.

Figure 1.5: Schematic diagram of the contribution of spatial and temporal tagging provided by a beam hodoscope in the case of compton imaging for hadrontherapy.

Finally, it must be able to operate over a large dynamic range, from the detection of a single proton of 250 MeV to packets of a few hundred protons of 70 MeV (i.e., 29 of dynamic). The present hodoscope relies on an array of scintillating fibers which are coupled to multichannel photomultipliers tubes (PMT) as shown in figure 1.6. The performances of such a design are limited by the PMT admissible counting rate and the intrinsic radiation hardness of the scintillators which make it unsuitable for this application.

Figure 1.6: Photo of the hodoscope with scintillating fibers coupled to PMTs.

In order to overcome such difficulties, the CLaRyS collaboration has initiated different projects aiming to develop a new generation of hodoscopes using CVD (Chemical Vapor Deposition) diamond.

### 1.2 CVD diamond detectors

#### 1.2.1 Diamond as a material

In theory, diamond is only composed of carbon and its exceptional properties and characteristics come largely from its crystal structure [11, 12]. For diamond, the proximity of the atoms in the crystal and the important overlap of the orbitals of neighboring atoms participate in the generation of an important gap of energy  $E_g = 5.47 \, eV$ . Depending on the application, diamond is considered either as a large gap semiconductor or as an insulator. It also results in a very high displacement energy (43 eV) explaining the very high radiation resistance of diamond. Moreover, it is considered as an excellent thermal conductor, with a thermal conductivity of 2000  $W.m^{-1}.K^{-1}$ . In addition, it can be subjected to very high electric fields thanks to its dielectric strength of  $10^7 \, V.cm^{-1}$ . Diamond also has a very high resistivity (>  $10^{13} \, \Omega.cm$ , allowing it to produce detectors with a very low leakage current at room temperature (typically of the order of one pA).

Table 1.1 resumes a comparison of the properties of diamond and silicon:

| Property                            | Units       | Diamond            | Silicon           |

|-------------------------------------|-------------|--------------------|-------------------|

| Band Gap $E_g$                      | eV          | 5.47               | 1.12              |

| Electron mobility $\mu_e$           | $cm^2/V.s$  | 1700               | 1420              |

| Hole mobility $\mu_h$               | $cm^2/V.s$  | 2100               | 470               |

| Saturation velocity                 | cm/s        | $2 \times 10^7$    | $1.4 \times 10^7$ |

| Intrinsic carrier density           | $cm^{-3}$   | $< 10^{3}$         | $1.5^{10}$        |

| e/h pair energy                     | eV          | 13                 | 3.6               |

| Displacement energy                 | eV          | 37-47              | 15-20             |

| Density                             | $g cm^{-3}$ | 3.52               | 2.33              |

| Rad length X <sub>0</sub>           | cm          | 12.2               | 9.4               |

| Dielectric constant $\varepsilon_r$ | (relative)  | 5.7                | 11.9              |

| Breakdown E-Field                   | V/μ m       | 1000               | 30                |

| Resistivity                         | $\Omega/cm$ | > 10 <sup>15</sup> | $10^5 - 10^6$     |

Table 1.1: Properties of Diamond Vs Silicon, extracted from [12].

Finally, diamond is of great interest for the development of fast detectors. The mobility and the saturation speed of its charge carriers are among the highest of the semiconductors. They also have the advantage of being relatively close to each other [13]. In addition to that, its dielectric constant of 5.7 is relatively low, this allows diamond detectors to have a very low capacitance compared to other semiconductors (at a given geometry), and thus enable very fast timing measurements.

### 1.2.2 CVD diamond for particle detection

### a. Crystalline grades of diamond

Diamonds used to make particle detectors are often CVD diamonds. To date, three distinct crystalline grades of diamonds are produced by CVD and used for detector design:

### • Single-crystal CVD diamond (sCVD or sc-CVD)

They are made of a single homogeneous crystal, according to a precise crystallographic orientation (usually < 100 > for detectors). They are produced by homoepitaxy: the seed

used is generally an ultra-pure monocrystalline diamond. They are commercially available for sensitive areas up to  $4.5 \times 4.5 \ mm^2$ . Their small size together with their very high price represent the main limitation to their use [14].

### • Polycrystalline CVD diamond (pCVD or pc-CVD)

They are produced by heteroepitaxy. The use of substrates of a different chemical nature from diamond allows the production of much larger samples (up to  $120 \times 120 \text{ }mm^2$ ). They are commercially available from various providers at a much lower price per unit area than the sCVD diamonds.

#### · Heteroepitaxial diamond

The objective of heteroepitaxy on iridium (Diamond-On-Iridium: DOI) [15] is to allow the growth of large diamonds with electronic properties tending towards those of sCVD diamonds. This grade is still under development, early results show that there is still a large disparity in the quality of the samples produced, some DOI detectors have a response quality comparable to that of single crystal detectors. It was shown also that, in these DOI detectors, if the hole transport is realized with a very high quality, the electron transport is severely deteriorated. The cause of this deterioration of the electron signal is still unexplained [16].

#### b. Diamond as a solid state ionization chamber

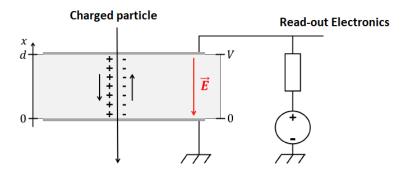

Nowadays, diamond detectors are almost exclusively used as solid state ionization chambers. The principle of operation of an ionization chamber is based on the collection of free charges generated by the passage of an ionizing particle in a detection volume. This particle will give up part of its initial energy in the detection volume, thus generating a certain amount of charges proportional to the total energy deposit of the particle in the volume. Without the application of an external electric field, these free charges are likely to be recombined very quickly in the detector. To go against this recombination and generate a usable signal, an electric field is applied to the detection volume in order to make these charges drift. The displacement of these charges induces a current signal on the polarization electrodes. Figure 1.7 shows a simplified diagram of this system.

Figure 1.7: Concept diagram of a solid state ionization chamber based on a diamond detector.

In an ionization chamber, the electric field only allows the charges generated by the ionization to drift and does not allow the charges to be multiplied by the generation of electronic cascades. There is therefore no internal amplification of the primary signal in this configuration. The polarization electric field of a diamond detector in this case is generally a few  $V.\mu m^{-1}$  (up to  $10~kV.cm^{-1}$ ). The measured signal corresponds in this case, to the signal induced by the displacement of charges under the effect of an electric field  $E = \frac{V}{d}$ , with V the value of the bias voltage and d the thickness of the diamond detector (case of a flat capacitor geometry). The induced signal can then be calculated using the Shockley-Ramo theorem [17, 18]. It states that

the current  $I_{ind}$  generated by the displacement of a free charge q at the drift speed  $v_q = \|\overrightarrow{v_q}\|$  and induced on an electrode subjected to a unit potential  $\phi_w$ :

$$I_{ind} = q\overrightarrow{v_q} \times \overrightarrow{E_w} \tag{1.1}$$

Where:  $\overrightarrow{E_w} = -\overrightarrow{grad(\phi_w)}$  is called the weighting field.

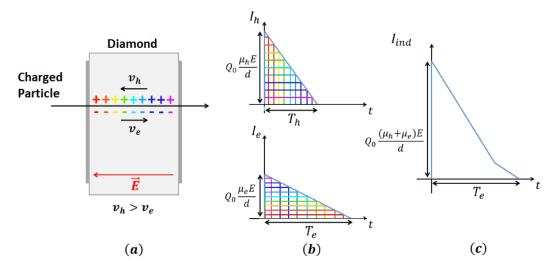

In the case of a free charge in a polarized plane capacitor, we can also express the evolution of the induced current in time  $I_{ind}(t)$ . The most important drift time is that of a charge created at a distance d from the considered electrode and drifting towards this same electrode. If we note this time as  $T_{e,h}$ , we find  $T_{e,h} = d/(\mu_{e,h}E)$ . Since  $v_h > v_e$  in CVD diamond, we distinguish then three temporal regimes [19]:

• When the two charge carriers drift ( $t < T_h < T_e$ ):

$$I_{ind}(t) = \frac{-Q_0 E^2}{2d^2} (\mu_h^2 + \mu_e^2)t + \frac{Q_0 E}{d} (\mu_h + \mu_e)$$

(1.2)

where  $Q_0$  is the inducted charge that corresponds to the Minimum Ionizing Particle (MIP).

• When only the electrons are still drifting  $(T_h < t < T_e)$ :

$$I_{ind}(t) = \frac{-Q_0 E^2}{2d^2} \mu_e^2 t + \frac{Q_0 E}{d} \mu_e$$

(1.3)

· When the two carriers have stopped drifting:

$$I_{ind}(t) = 0 (1.4)$$

A summary diagram of the inducted current generated by CVD diamond detectors is presented in figure 1.8.

Figure 1.8: Summary diagram of the current induced in a diamond detector by a passing charged particle, extracted from [20]:

(a)A particle uniformly ionizes the medium along its path and the free charges begin to drift under the effect of the electric field;

(b) The drift of the two charge carriers induces a current of the same sign on the considered electrode;

(c)The total induced current on the electrode is the sum of the currents of the two charge carriers.

The signal generated by particles passing through the diamond is therefore triangular in shape when the transport of charges is done without parasitic effects (recombination and polarization).

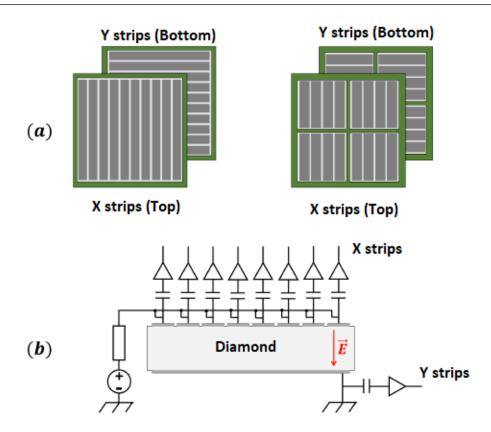

### 1.2.3 CVD diamond Hodoscope

### a. Specification of requirements

Within the framework of the CLaRyS-UFT project, a beam hodoscope demonstrator based on diamond CVD detectors is to be realized. To meet the objectives of the project, the demonstrator must meet the following specifications:

- A temporal resolution less than 100 ps;

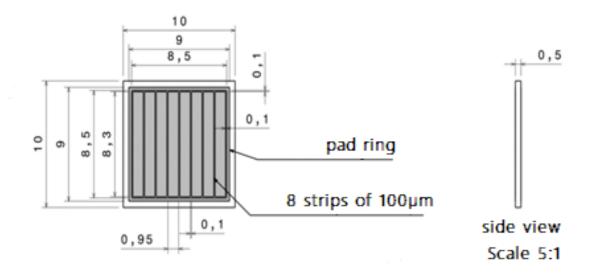

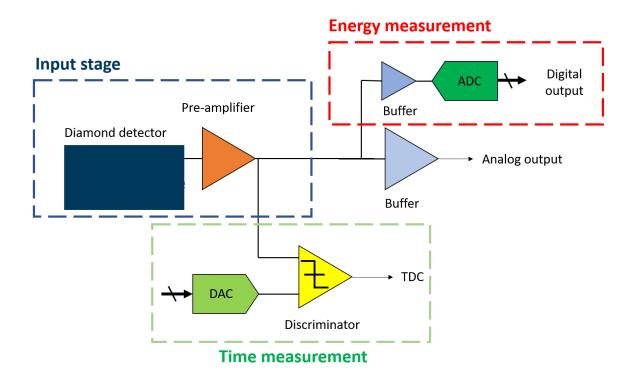

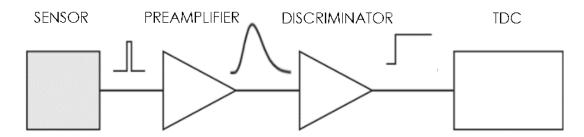

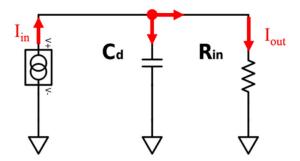

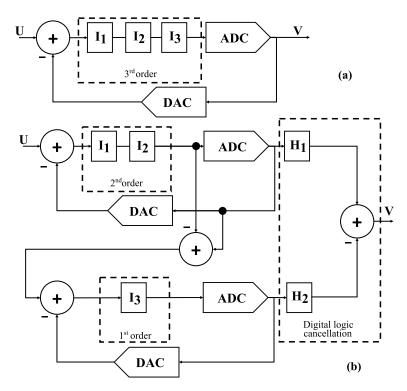

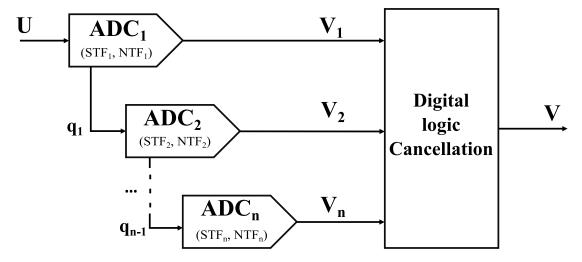

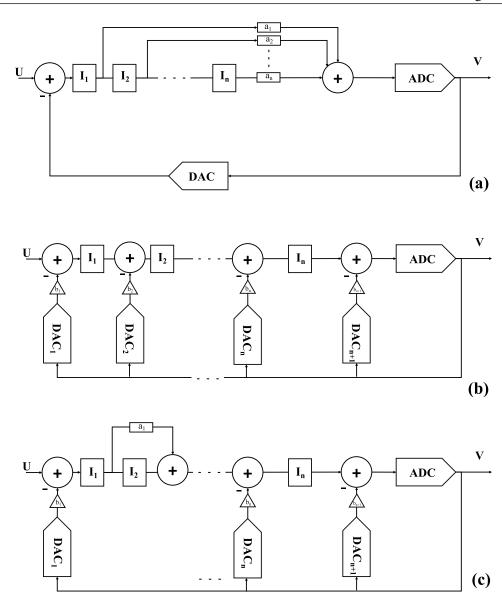

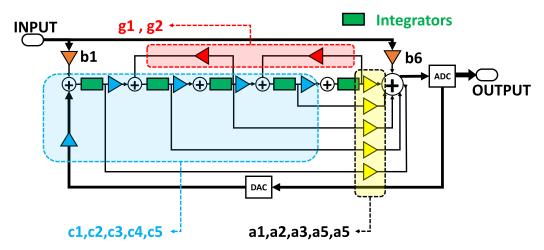

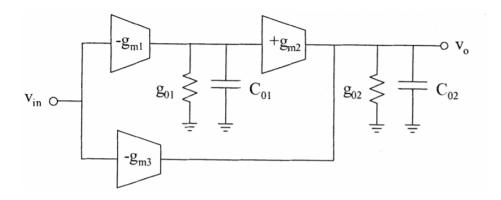

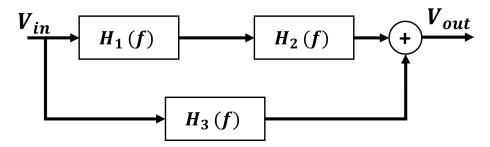

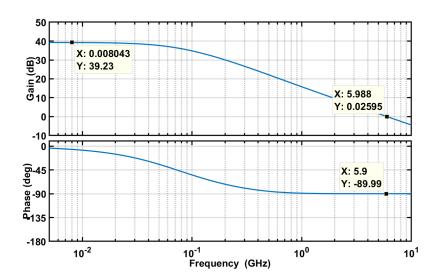

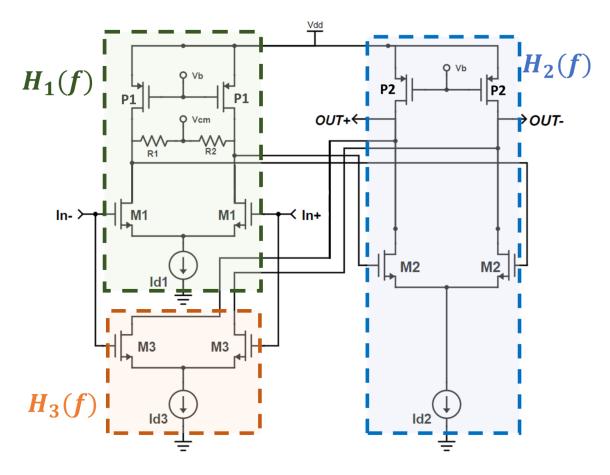

- An overall count rate that can reach the 100 MHz;