### A Temperature-Aware Framework for Analog Design Using a gm/ID Approach

João Roberto Raposo de Oliveira Martins

### ▶ To cite this version:

João Roberto Raposo de Oliveira Martins. A Temperature-Aware Framework for Analog Design Using a gm/ID Approach. Micro and nanotechnologies/Microelectronics. Université Paris-Saclay, 2021. English. NNT: 2021UPAST134. tel-03593607

### HAL Id: tel-03593607 https://theses.hal.science/tel-03593607v1

Submitted on 2 Mar 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Temperature-Aware Framework for Analog Design Using a $g_m/I_D$ Approach Une méthodologie de conception des circuits analogiques consciente de la température basée sur $g_m/I_D$

### Thèse de doctorat de l'université Paris-Saclay

École doctorale n° 575, Electrical, optical, bio-physics and engineering (EOBE) Spécialité de doctorat : Électronique et optoélectronique, nano et microtechnologies

> Graduate School : Sciences de l'ingénierie et des systèmes Référent : Faculté des Sciences d'Orsay

Thèse préparée dans l'unité de recherche Laboratoire de Génie Electrique et Electronique de Paris (Université Paris-Saclay, CentraleSupélec, CNRS), sous la direction de Francisco DE OLIVEIRA ALVES, Professeur des Universités, et le co-encadrement de Pietro M. FERREIRA, Maître de Conférences (HDR)

Thèse soutenue à Paris-Saclay, le 10 décembre 2021, par

# João Roberto RAPOSO DE OLIVEIRA MARTINS

### **Composition du jury**

Arnaud BOURNEL

Professeur des Universités, Université Paris-Saclay **Sylvain BOURDEL**

Professeur des Universités, Grenoble-INP

Formando SIIVEIDA

Fernando SILVEIRA

Professeur, Universidad de la Républica, Uruguay

Manohiaina GALAL-EL-DINE

Maître de Conférences, X-FAB France Corbeil-Essonnes

Francisco DE OLIVEIRA ALVES

Professeur des Universités, Directeur de l'IUT de Cachan

Président

Rapporteur & Examinateur

Rapporteur & Examinateur

Examinatrice

Directeur de thèse

#### **DOCTORAL SCHOOL**

Electrical, Optical, Bio: Physics and Engineering (EOBE)

**Titre:** Une méthodologie de conception des circuits analogiques consciente de la température basée sur  $g_m/I_D$

**Mots clés:** Electronique Analogique,  $g_m/I_D$ , Effets de Température, Physique des semiconducteurs

**Résumé:** La quatrième révolution industrielle et l'arrivée de l'Internet des Objets introduisent de nouveaux défis pour la conception de circuits fiables. Dans les nouveaux véhicules, les circuits doivent pouvoir fonctionner de manière fiable dans une plage de température étendue. Les caractéristiques des transistors sont connues pour être fortement dépendantes de la température. Pour minimiser ces effets de dérive thermique, l'utilisation de points de polarisation ZTC (Zero Temperature Coefficients) a déjà été proposée. Cependant, cette approche ZTC considère l'influence d'un seul transistor sur le comportement en température des différentes spécifications du circuit et ne permet pas une approche plus générale et méthodologique.

D'autre part, les techniques de conception tels que la  $g_m/I_D$  permettent une approche méthodologique pour la conception

analogique, sans possibilité d'analyse en température. Ce travail propose une extension de la méthodologie  $g_m/I_D$  en introduisant le concept de paramètres  $g_m/I_D$  normalisés en température. Ce paramètres permetent au concepteur de prendre en compte les effets de la température à un stade très précoce de la conception de la plupart des circuits analogiques, permettant ainsi une méthodologie unifiée pour la conception sensible à la température. Ces résultats sont validés à partir de données de simulation et de mesures de -40 °C à 200 °C avec la technologie XT018 de X-FAB. Trois exemples de conception différents sont également présentés dans cette thèse: circuit de référence de tension (Bandgap), Amplificateur à Transconductance (OTA), et oscillateur contrôlé par tension (VCO). Ces circuits présentent une meilleure performance en température comparable aux spécifications de l'état de l'art.

**Title:** A Temperature-Aware Framework for Analog Design Using a  $g_m/I_D$  Approach

**Keywords:** Analog Design,  $g_m/I_D$ , Temperature Effects, Semiconductor Physics

Abstract: The fourth industrial revolution and the Internet of things introduce new challenges to reliable circuit design. In this context, new transports circuits must be able to reliably work at an extensive temperature range. Transistor characteristics have been known to be highly temperature-dependent. Zero Temperature Coefficients (ZTC) bias points have already been proposed to minimize transistor's temperature drift effects. However, this ZTC approach considers the influence of a single transistor on the different circuit specifications' temperature behavior. Moreover, it does not allow and does not allow a more general and methodological approach.

On the other hand, design frameworks such as the  $g_m/I_D$  allow a methodological approach

for analog design, with no possibility of temperature analysis. This work proposes an extension of the  $g_m/I_D$  methodology by introducing the concept of temperature normalized  $g_m/I_D$  parameters. This concept allows the designer to take temperature effects in a very early design stage in most analog circuits, allowing a unified methodology for temperature-aware design. Those results are validated from simulation and measurement data from -40 °C to 200 °C on the XT018 technology node of X-FAB. Three different design examples are also presented in this thesis, being: a Band Gap voltage reference, an operational transconductance amplifier (OTA), and a voltage-controlled oscillator (VCO). Those circuits present a better presenting a better temperature performance comparable to the state-of-the-art specifications.

# Contents

| 1        | $\operatorname{Th}\epsilon$ | e need  | of Temperature-Aware Circuits                     | 3  |

|----------|-----------------------------|---------|---------------------------------------------------|----|

|          | 1.1                         | Circui  | its Reliability in Harsh Environments             | 4  |

|          | 1.2                         | Conte   | ext of Temperature Considerations in Circuits     | 5  |

|          | 1.3                         | Contr   | ibutions                                          | 6  |

|          |                             | 1.3.1   | Journal Papers                                    | 7  |

|          |                             | 1.3.2   | International Conferences                         | 7  |

|          |                             | 1.3.3   | National Colloquium                               | 7  |

|          |                             | 1.3.4   | Open Source Journals and Libraries                | 8  |

| <b>2</b> | Tra                         | nsistoi | r Temperature Effects                             | 9  |

|          | 2.1                         | Semic   | conductor Temperature Effects                     | 10 |

|          |                             | 2.1.1   | Band Gap Temperature dependency                   | 10 |

|          |                             | 2.1.2   | Carriers Concentration                            | 11 |

|          |                             | 2.1.3   | The Fermi Level                                   | 12 |

|          |                             | 2.1.4   | Doping                                            | 13 |

|          | 2.2                         | MOSI    |                                                   | 16 |

|          | 2.3                         | The N   | MOS Electrostatics                                | 16 |

|          |                             | 2.3.1   | Carriers Transport on MOSFETs                     | 19 |

|          |                             | 2.3.2   | MOSFET Models                                     | 22 |

|          |                             | 2.3.3   | The Effective Silicon Mobility                    | 24 |

|          |                             | 2.3.4   | The Charge Sheet Approximation                    | 25 |

|          |                             |         | Regional Approximations of the Charge Sheet Model | 26 |

|          |                             | 2.3.5   | $V_{th}$ Temperature effects                      | 27 |

|          |                             |         | $V_{FB}$ Temperature Variation                    | 28 |

|          |                             |         | $\phi_B$ Temperature Dependency                   | 29 |

|          |                             | 2.3.6   | Current ZTC Point                                 | 30 |

|          |                             | 2.3.7   | Small Channel Effects in Analog Design            | 32 |

|          |                             |         | Velocity Saturation                               | 32 |

|          |                             |         | Channel Length Modulation (CLM)                   | 34 |

|          |                             |         | Drain Induced Barrier Lowering (DIBL)             | 34 |

|          | 2.4                         | Trans   | istor Compact Models                              |    |

4 CONTENTS

|   |     | 2.4.1     | Symmetric Linearization Models                       | 36 |

|---|-----|-----------|------------------------------------------------------|----|

|   |     |           | Temperature Effects                                  | 38 |

|   |     | 2.4.2     | Inversion Charge Linearization Based Models          | 42 |

|   |     |           | Solutions to Charge Linearization Models             | 44 |

|   |     | 2.4.3     | The UICM model                                       | 46 |

|   |     | 2.4.4     | The BSIM 6 Model                                     | 48 |

|   | 2.5 | The $g_i$ | $I_m/I_D$ methodology                                | 48 |

|   |     |           | $g_m/I_D$ Temperature Modeling on Compact Models     | 50 |

|   |     | 2.5.1     | 9 -                                                  | 50 |

| 3 | АТ  | emper     | rature-Aware design Methodology                      | 53 |

|   | 3.1 | Zero 7    | Temperature Coefficients (ZTC) Point                 | 54 |

|   |     | 3.1.1     | The $g_m$ ZTC Bias                                   | 55 |

|   | 3.2 | Tempe     | 0 0 7 2                                              | 57 |

|   |     | 3.2.1     | Gate Transconductance Ratio                          | 58 |

|   |     | 3.2.2     | Parasitic Source/Drain Diodes                        | 64 |

|   |     | 3.2.3     |                                                      | 66 |

|   |     |           | Drain Induced Barrier Lowering                       | 66 |

|   |     |           | Velocity Saturation                                  | 69 |

|   |     |           | Channel Length Modulation                            | 70 |

|   |     |           | 5111/540                                             | 72 |

|   |     |           | Temperature Analysis                                 | 75 |

|   | 3.3 | Tempe     | erature Analysis of MOSFET Capacitances              | 76 |

|   |     | 3.3.1     | Varicap Temperature Analysis                         | 78 |

|   |     |           | Depletion and Inversion Analysis                     | 79 |

|   |     |           | Accumulation Mode Analysis                           | 80 |

|   |     | 3.3.2     | $C_{gs}$ Temperature analysis                        | 81 |

|   | 3.4 | Conclu    | usion                                                | 82 |

| 4 | АТ  | -         | ature-Aware Methodology Applications: A Study Case 8 |    |

|   | 4.1 | _         | gap Voltage Reference                                | 35 |

|   |     | 4.1.1     |                                                      | 87 |

|   |     | 4.1.2     |                                                      | 90 |

|   |     | 4.1.3     |                                                      | 92 |

|   | 4.2 |           | 1                                                    | 93 |

|   |     | 4.2.1     | y ,                                                  | 93 |

|   |     | 4.2.2     | 1                                                    | 94 |

|   |     | 4.2.3     |                                                      | 95 |

|   |     | 4.2.4     |                                                      | 96 |

|   |     | 4.2.5     | Temperature Sensitivity in Closed-Loop Operation     | 97 |

|   |     | 426       | Conclusion                                           | gg |

CONTENTS 5

|              | 4.3  | Active Inductance VCO                            |     |

|--------------|------|--------------------------------------------------|-----|

|              | 4 4  | 4.3.1 Active Inductance Temperature Analysis     |     |

|              | 4.4  | Results                                          |     |

|              | 4.5  | Conclusion                                       |     |

|              | 1.0  | Concretion                                       | 100 |

| 5            | Con  | clusion and Perspectives                         | 109 |

|              | 5.1  | Work Conclusions                                 |     |

|              | 5.2  | Research Perspectives                            |     |

|              |      | 5.2.1 Multi-Objective Optimization               |     |

|              |      | 5.2.2 System Level Optimization                  |     |

|              |      | 5.2.3 Technology Shrink                          | 110 |

| 6            | Rés  | umé Étendu en Français                           | 113 |

|              | 6.1  | Contexte                                         |     |

|              | 6.2  | Proposition                                      |     |

|              | 6.3  | Résultats                                        |     |

|              | 6.4  | Conclusion                                       |     |

| Ar           | open | dices                                            | 123 |

| -            | -    |                                                  |     |

| $\mathbf{A}$ |      | stal Structures Statistics                       | 125 |

|              | A.1  | Classical Statistical Mechanics                  | 129 |

| В            | Ferr | ni Distribution                                  | 133 |

|              |      | Fermi Level                                      |     |

| $\mathbf{C}$ | Drif | t-Diffusion Equation                             | 139 |

| O            |      | Scattering and the Relaxation Time Approximation |     |

|              |      |                                                  |     |

| D            |      | ctive Mobility and Matthiessen's Rule            | 143 |

|              | D.1  | Mobility with Multiple Scattering Mechanisms     | 144 |

| ${f E}$      | Sym  | metric Linearization Models                      | 147 |

# List of Symbols

### Acronyms

BJT Bipolar Junction Transistor

BSIM Berkley Short-channel IGFET Model

CAD Computer Aided Design

CLM Channel Length Modulation

CTAT Complementary to Absolute Temperature

DIBL Drain Induced Barrier Lowering

GaN Gallium Nitrite

GCA Gradual Channel Approximation

IoT Internet of Things

MOSFET Metal Oxide Silicon Field Effect Transistor

MTS Mean Temperature Sensitivity

NTC Negative Temperature Coefficient

PTAT Proportional to Absolute Temperature

RF Radio Frequency

SCCT Self-Cascode Composite Transistor

SiC Silicon Carbide

SOI Silicon Over Insulator

SRAM Static Random Access Memory

### UICM Unified Current Control Model

### ZTC Zero Temperature Coefficient

### **Physics Constants**

| $k_b$           | Boltzman Constant                                  | $8.617333262 \cdot 10^{-5}$ . $eV/K$ |

|-----------------|----------------------------------------------------|--------------------------------------|

| q               | Elementary Charge                                  | $1.60217662 \cdot 10^{-19}$ . $C$    |

| $\varepsilon_0$ | Vacum Permitivity                                  | $8.85418782 \cdot 10^{-14}$ . $F/cm$ |

| Tran            | sistor Parameters                                  |                                      |

| $g_m/g_d$       | s Transistor Self-Gain                             | 1/V                                  |

| $g_m/I_I$       | Drain Current to Drain to Gate Transconductar      | ace ratio $1/V$                      |

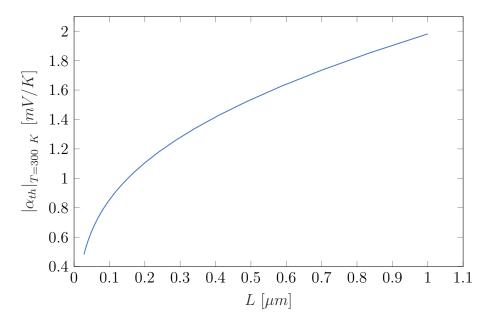

| $\alpha_{th}$   | Treshold Voltage Linear Temperature Coefficient    | V/K                                  |

| $eta_{\mu}$     | Carriers Mobility Temperature Coefficient          |                                      |

| $\chi_{si}$     | Semiconductor Vacum Energy                         | V                                    |

| $\eta$          | Non-Ideality Factor                                |                                      |

| $\mu_n$         | Electrons Mobility                                 | $cm^2/Vs$                            |

| $\mu_p$         | Holes Mobility                                     | $cm^2/Vs$                            |

| $\mu_{eff}$     | Effective Mobility of Carriers at the Inversion La | yer $cm^2/Vs$                        |

| $\phi_m$        | Metal Workfunction Voltage                         | V                                    |

| $\phi_T$        | Thermal Voltage                                    | V                                    |

| $\psi$          | Electric Potential                                 | V                                    |

| $\psi_B$        | Bulk Electric Potential                            | eV                                   |

| $\psi_p$        | Pintch-off Electric Potential                      | V                                    |

| $\psi_s$        | Electric Potential at Semiconductor Surface        | V                                    |

| $\psi_{sa}$     | Surface Potential Approximation at Depletion ar    | d Accumulation $V$                   |

| $\sigma(L)$     | DIBL Coefficient                                   | V/V                                  |

| $\Theta_D$         | Debye Temperature                                           |                     | K        |

|--------------------|-------------------------------------------------------------|---------------------|----------|

| $\varepsilon_{si}$ | Silicon Permitivity                                         | 1                   | F/cm     |

| ξ                  | - Electric Field                                            | 7                   | V/cm     |

| $C_p$              | Specific Heat Capacity at Constant Pressure                 | $J \cdot Kg^{-1}$ · | $K^{-1}$ |

| $C_{ds}$           | Drain to Source Capacitance                                 |                     | F        |

| $C_{gb}$           | Gate to Bulk Capacitance                                    |                     | F        |

| $C_{gd}$           | Gate to Drain Capacitance                                   |                     | F        |

| $C_{gg}$           | Total Gate Capacitance                                      |                     | F        |

| $C_{gs}$           | Gate to Source Capacitance                                  |                     | F        |

| $C_{ox}$           | Capacitance Density from Oxide                              | F                   | $c/cm^2$ |

| $C_{si}$           | Silicon Capacitance                                         |                     | F        |

| $E_A$              | Ionization Energy for the Acceptor                          |                     | eV       |

| $E_C$              | Conduction Band Energy                                      |                     | eV       |

| $E_D$              | Ionization Energy for the Acceptor                          |                     | eV       |

| $E_F$              | Fermi Level Energy                                          |                     | eV       |

| $E_i$              | Intrinsic Fermi Level Energy                                |                     | eV       |

| $E_V$              | Valence Band Energy                                         |                     | eV       |

| $E_G$              | Semiconductor Band Gap                                      |                     | eV       |

| $E_{sat}$          | Minimum Electric Field for Mobility Saturation              |                     |          |

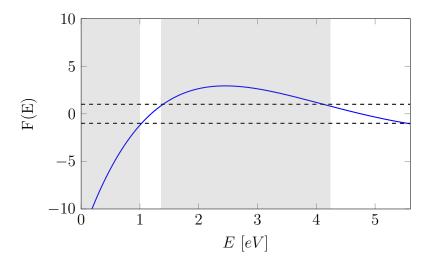

| $F(\psi)$          | Kingston Function                                           |                     |          |

| $g_m$              | Drain to Gate Transconductance                              |                     | S        |

| $G_p$              | Equivalent Parallel Conductance                             |                     | S        |

| $G_{comp}$         | Compensation Conductance                                    |                     | S        |

| $G_{d_{ZTC}}$      | Normalized Drain $g_m/I_D$ parameter Zero Temperature point | Coefficient         | Bias     |

| $G_{g_{ZTC}}$  | Normalized Gate $g_m/I_D$ parameter Zero Temperature Coefficient Bia | as point  |

|----------------|----------------------------------------------------------------------|-----------|

| $g_{m_{ZTC}}$  | Gate Transconductance Zero Temperature Coefficient Bias Point        |           |

| $I_B$          | Bulk Current                                                         | A         |

| $I_D$          | Drain Current                                                        | A         |

| $i_f$          | Normalized Forward Current                                           |           |

| $i_r$          | Normalized Reverse Current                                           |           |

| $I_{DS_{ZTC}}$ | Drain to Source Current ZTC Bias Point                               |           |

| $I_{DS}$       | Drain to Source Current                                              | A         |

| $J_n$          | Electrons Current Density                                            | A/cm      |

| $J_p$          | Holes Current Density                                                | A/cm      |

| $L_{eq}$       | Equivalent Inductance                                                | H         |

| n              | Electrons Concentration                                              | $cm^{-3}$ |

| $N_A$          | Acceptor Doping Concentration                                        | $cm^{-3}$ |

| $N_A^-$        | Ionized Acceptor Doping Concentration                                | $cm^{-3}$ |

| $N_C$          | Effective Density of States at the Conduction Band                   | $cm^{-3}$ |

| $N_D$          | Donnors Doping Concentration                                         | $cm^{-3}$ |

| $N_D^+$        | Ionized Donnors Doping Concentration                                 | $cm^{-3}$ |

| $n_i$          | Intrinsic Carriers Concentration                                     | $cm^{-3}$ |

| $n_q$          | Equivalent Non-Ideality Factor                                       |           |

| $N_V$          | Effective Density of States at the Valence Band                      | $cm^{-3}$ |

| p              | Holes Concentration                                                  | $cm^{-3}$ |

| $q_b$          | Normalized Bulk Charge                                               |           |

| $Q_d$          | Inversion Charge at the Drain                                        | C         |

| $Q_i$          | Invertion Charge                                                     | C         |

| $q_i$         | Normalized Inversion Charge                             |          |  |

|---------------|---------------------------------------------------------|----------|--|

| $Q_s$         | Inversion Charge at the Source                          | C        |  |

| $Q_s(\psi_s)$ | ) Surface Charge as a Function of the Surface Potential | C        |  |

| $q_{id}$      | Normalized Inversion Charge at Drain                    |          |  |

| $q_{im}$      | Normalized Inversion Charge at Channel Midle Point      |          |  |

| $q_{is}$      | Normalized Inversion Charge at Source                   |          |  |

| $R_s$         | Equivalent Series Resistance                            | $\Omega$ |  |

| $S_x^{y(x)}$  | Sensitivity of y in relation to x                       |          |  |

| $T_{C_{eqq}}$ | Equivalent Temperature Coefficient                      |          |  |

| $V_p$         | Pintch-off Voltage                                      | V        |  |

| $V_{ch}$      | Quasi-Fermi Level at the Channel                        | eV       |  |

| $V_{D_{sat}}$ | Minimum Drain Source for Mobility Saturation            | V        |  |

| $V_{DS}$      | Drain to Source Voltage                                 | V        |  |

| $V_{FB}$      | Flatband Voltage                                        | V        |  |

| $V_{GB}$      | Gate to Bulk Voltage                                    | V        |  |

| $V_{SB}$      | Source to Bulk Voltage                                  | V        |  |

| $V_{th}$      | Transistor Threshold Voltage                            | V        |  |

| $Z_{in}$      | Input Impedance                                         | $\Omega$ |  |

| $Z_{out}$     | Output Impedance                                        | $\Omega$ |  |

| L             | Drawing Channel Length                                  | $\mu m$  |  |

| W             | Drawing Channel Width                                   | $\mu m$  |  |

|               |                                                         |          |  |

# List of Figures

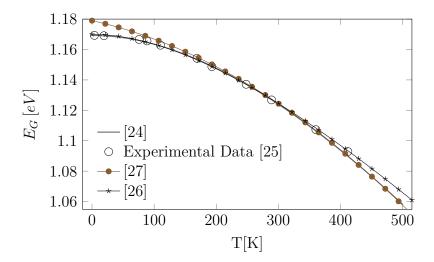

| 2.1  | Bandgap temperature model comparison to experimental data from [36]                                                                                                                                                                                                                    | 11       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

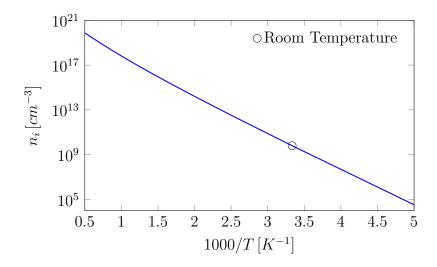

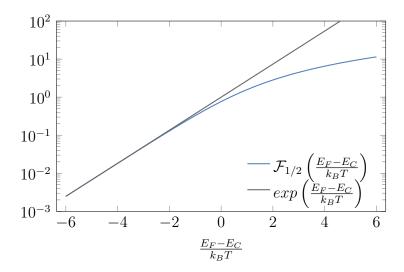

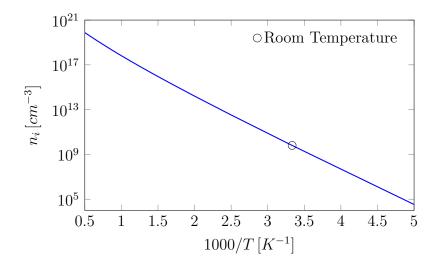

| 2.2  | Intrinsic carrier concentration relation with inverse temperature using Fermi-Dirac distribution                                                                                                                                                                                       | 12       |

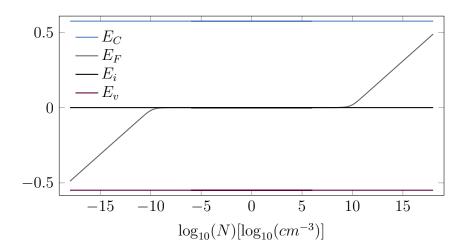

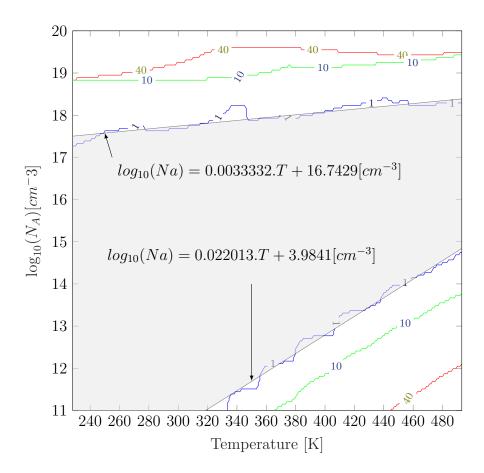

| 2.3  | Fermi-level position due to doping concentration, negative values are for P-doped silicon and positive for N-doped Silicon                                                                                                                                                             | 14       |

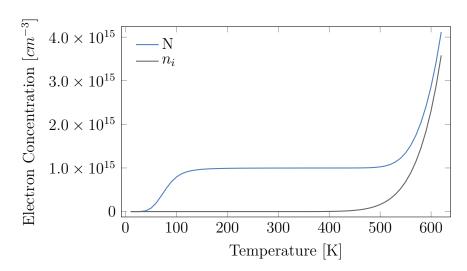

| 2.4  | Electrons concentration for a N doped Silicon with doping concentrations of $10^{-15}~cm^{-3}$ and $E_a=0.044~eV$                                                                                                                                                                      | 15       |

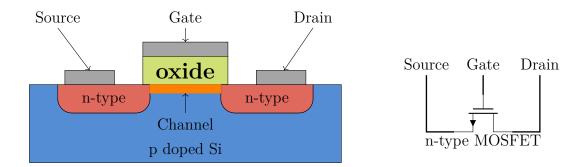

| 2.5  | MOSFET structure and electrical symbol                                                                                                                                                                                                                                                 | 16       |

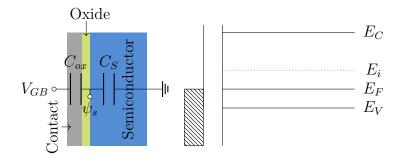

| 2.6  | Physical structure and Band Diagram on the y axis of a MOS Struc-                                                                                                                                                                                                                      |          |

|      | ture                                                                                                                                                                                                                                                                                   | 17       |

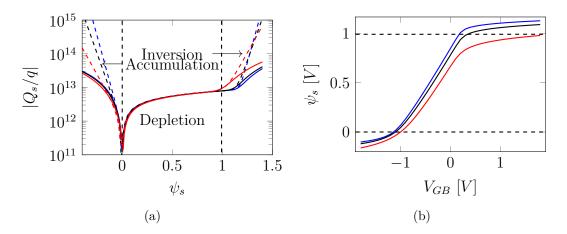

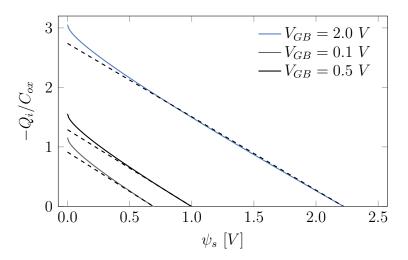

| 2.7  | Surface Charge of a P-type Silicon with the assumptions of [29] (dashed) and [30] (solid) (a) and the surface potential (b) for an with P-type dopant concentration of $5 \cdot 10^{18} \ cm^{-3}$ considering a Boron doping with $E_a = 0.044 \ eV$ at three different temperatures: | 1.5      |

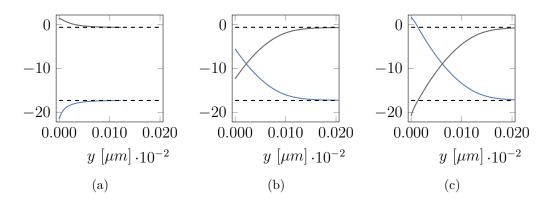

| 2.8  | -40 °C (blue), 27 °C (black) and 175 °C (red)                                                                                                                                                                                                                                          | 17<br>18 |

| 2.9  | (c). Analytical expressions for total gate capacitance and the silicon and                                                                                                                                                                                                             | 10       |

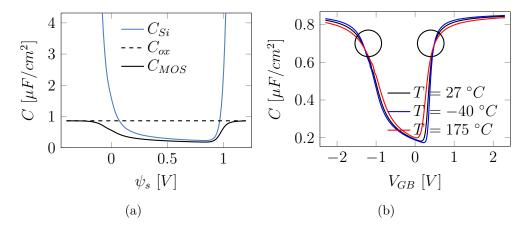

| 2.9  | Analytical expressions for total gate capacitance and the sincon and $C_{ox}$ capacitance                                                                                                                                                                                              | 19       |

| 2.10 |                                                                                                                                                                                                                                                                                        | 10       |

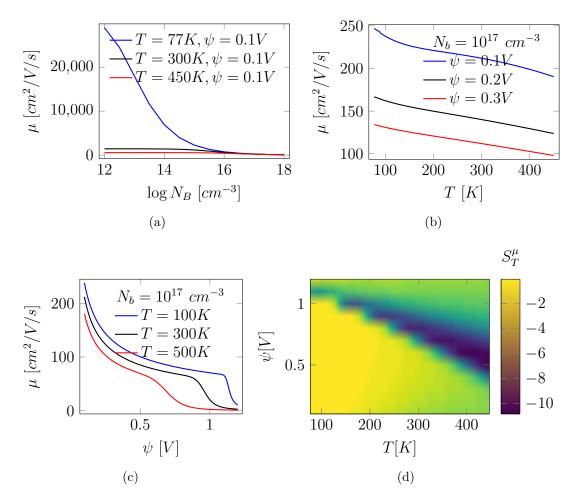

| 2.10 | ture, doping concentration and electric potential                                                                                                                                                                                                                                      | 21       |

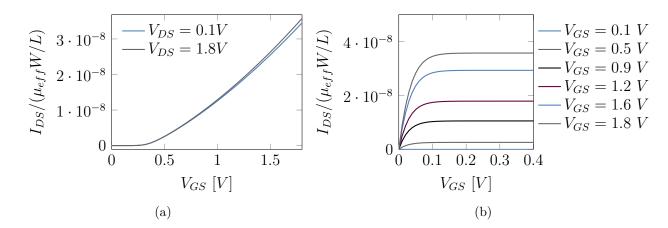

| 2.11 | Pao-Sah Current model numerical calculations                                                                                                                                                                                                                                           | 24       |

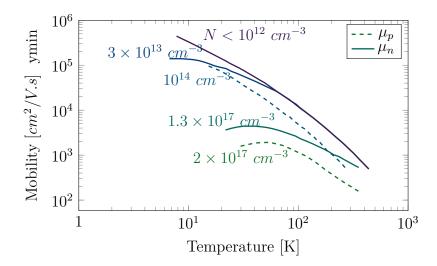

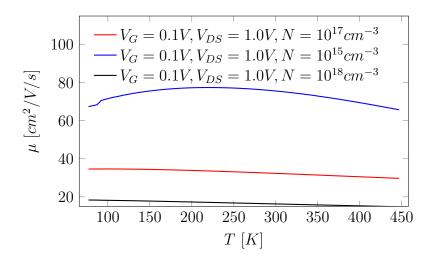

| 2.12 | Effective Mobility Temperature dependency extracted from measurement data, for holes $(\mu_p)$ and electrons $(\mu_n)$ for different doping                                                                                                                                            |          |

|      | concentrations extracted from [39]                                                                                                                                                                                                                                                     | 25       |

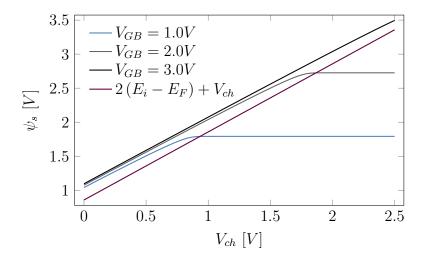

| 2.13 | Brews approximation for the surface potential as a function of                                                                                                                                                                                                                         |          |

|      | $V_{ch}$ and $V_{GB}$                                                                                                                                                                                                                                                                  | 27       |

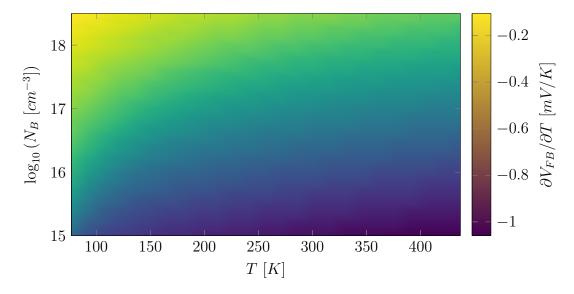

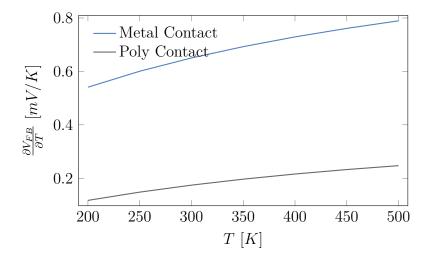

| 2.14 | $V_{FB}$ temperature coefficient of in $mV/K$ for different doping profiles and temperatures using Fermi distribution and non-ionized acceptors with $F_{FB} = 0.044$ eV and aluminum rate centers.                                                                                                                                                                                                                                                                                                                                 | ച  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28 |

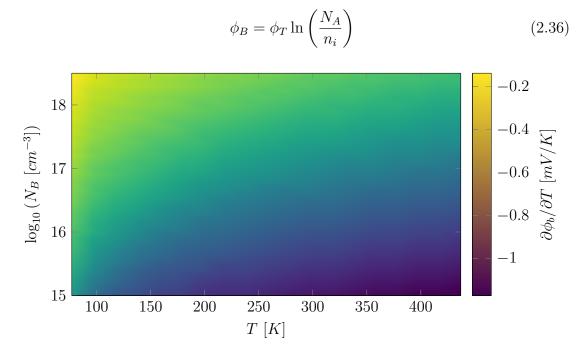

| 2.15 | Bulk potential temperature coefficient at different temperatures and doping concentrations                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29 |

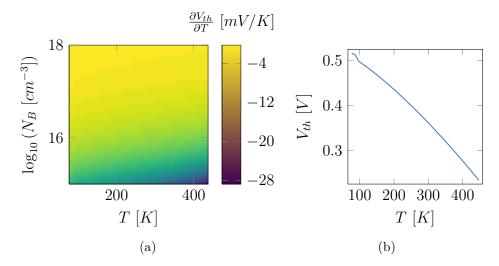

| 2.16 | Threshold voltage temperature coefficient at different temperatures and doping concentrations, and threshold voltage temperature behavior for a $N_B = 5 \cdot 10^{18} cm^{-3}$ , $t_{ox} = 4 nm$ transistor                                                                                                                                                                                                                                                                                                                        | 30 |

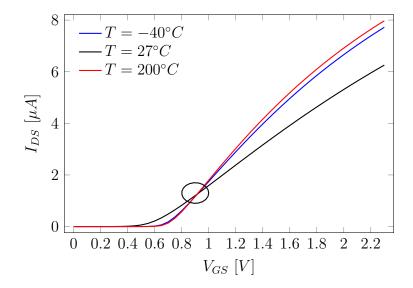

| 2.17 | Drain do source current of a PMOS transistor calculated numerically at different temperatures using Pao-Sah model                                                                                                                                                                                                                                                                                                                                                                                                                   | 31 |

| 2.18 | Measured Drain do source current of a PMOS transistor at different                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31 |

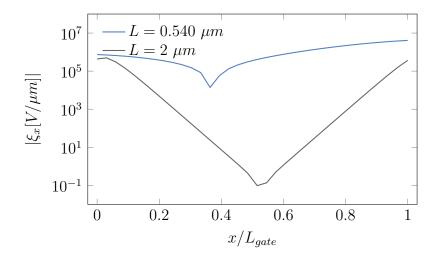

| 2.19 | Longitudinal electric field calculated numerically [43] using a finite volume method whit 5151 grid points, no recombination and generation phenomena with Shaffered-Gummel flux, of two NMOS with bulk dopping of $5.7 \cdot 10^{17}~cm^{-3}$ , a source/drain dopping of $6 \cdot 10^{16}~cm^{-3}$ with an Alluminum gate and a gate oxide of $4~nm$ at two different gate lengths $(0.54~\mu m, 2.0~\mu m)$ with an lattice temperature of 300 $K$ at a 0.9 $nm$ distance from the silicon-oxide interface.                      |    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33 |

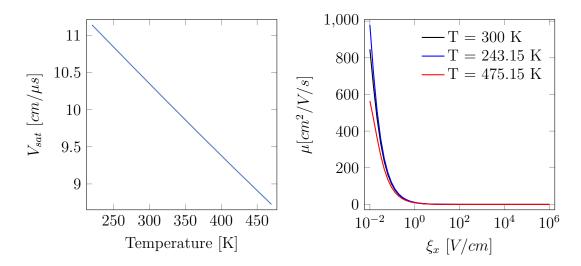

| 2.20 | Temperature behavior of the saturation velocity and the saturated mobility given by the Swarts Model                                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |

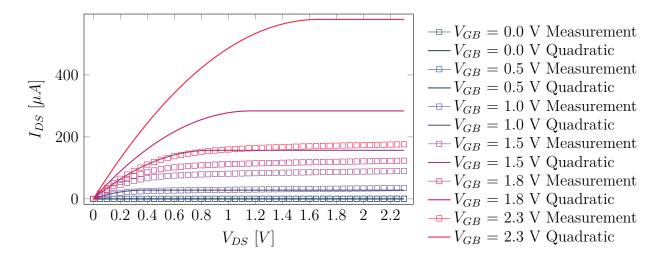

| 2.21 | Comparison between the quadratic model drain current and measurement data of a NMOS transistor                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35 |

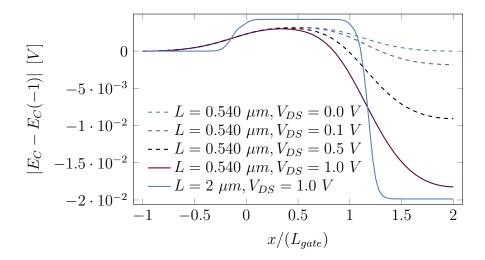

| 2.22 | Electric potential from source to drain calculated numerically using a finite volume method with 5151 grid points, no recombination and generation phenomena with Shaffered-Gummel flux, of two NMOS with bulk dopping of $5.7 \cdot 10^{17}$ cm <sup>-3</sup> , a source/drain dopping of $6 \cdot 10^16$ cm <sup>-3</sup> with an Alluminum gate and a gate oxide of $4 nm$ at two different gate lenghts $(0.54 \ \mu m, 2.0 \ \mu m)$ with an lattice temperature of 300 Kat a 0.9 nm distance from the silicon-oxide interface | 36 |

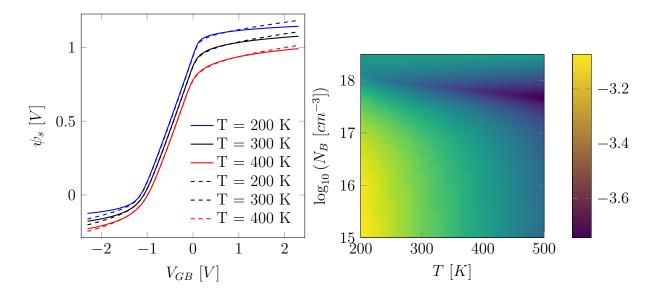

| 2.23 | Comparison between PSP approximation for the surface potential (solid) and numerical results considering Fermi-Dirac distribution (dashed) and maximum absolute error on the approximation for                                                                                                                                                                                                                                                                                                                                      | 38 |

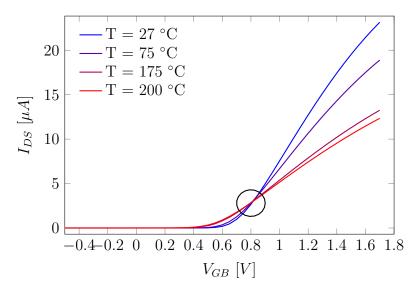

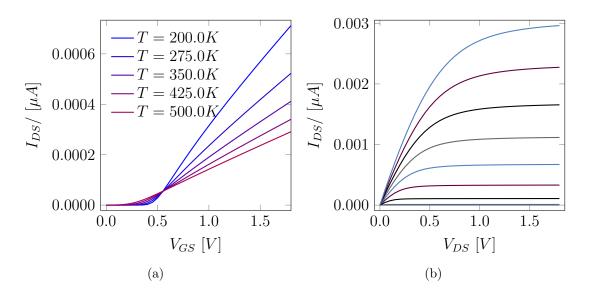

| 2.24 | $I_D \times V_{GB}$ Characteristics of long channel MOSFET calculated using                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39 |

| 2.25 | Comparison of flat-band temperature coefficient theoretical calcu-                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39 |

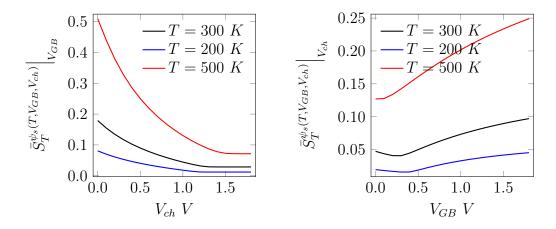

| 2.26 | Mean Temperature Sensitivity of the surface potential by averaging                                                                                                                                                                                                                                                                           |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | on the $V_{GB}$ voltage and the $V_{ch}$ voltage                                                                                                                                                                                                                                                                                             | 40  |

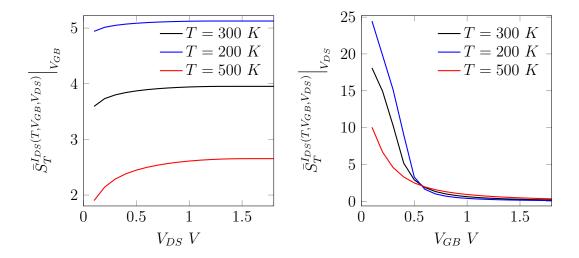

| 2.27 | Drain to source current mean temperature sensitivities by averaging                                                                                                                                                                                                                                                                          |     |

|      | on the $V_{GB}$ voltage and the $V_{DS}$ voltage                                                                                                                                                                                                                                                                                             | 41  |

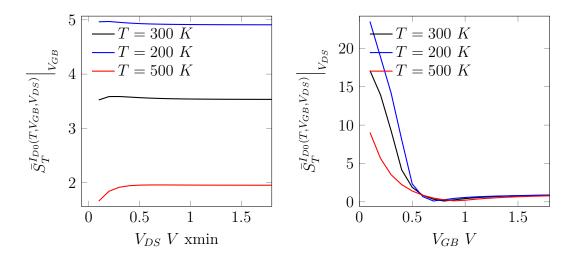

| 2.28 | Mean Temperature Sensitivity of the drain current when considering                                                                                                                                                                                                                                                                           |     |

|      | (first row) and not considering mobility temperature dependency by                                                                                                                                                                                                                                                                           |     |

|      | averaging on the $V_{GB}$ voltage and the $V_{DS}$ voltage                                                                                                                                                                                                                                                                                   | 41  |

| 2.29 | Theoretical inversion charge given by (2.52) (solid lines) charge linearization approximation (dashed lines) for different gate to bulk                                                                                                                                                                                                      |     |

|      | voltages                                                                                                                                                                                                                                                                                                                                     | 42  |

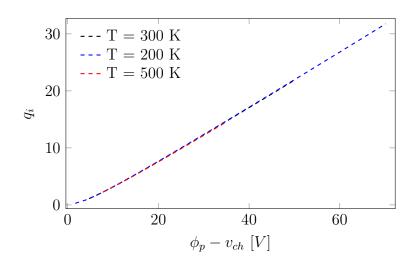

| 2.30 | Normalized Inversion Charge over three different temperatures given as function of the normalized pitch off surface potential and normal-                                                                                                                                                                                                    |     |

|      | ized channel potential difference                                                                                                                                                                                                                                                                                                            | 44  |

| 2.31 | The EKV approximation for the charge linearisation model for a large transistor considering multiple bias points and temperatures.                                                                                                                                                                                                           | 45  |

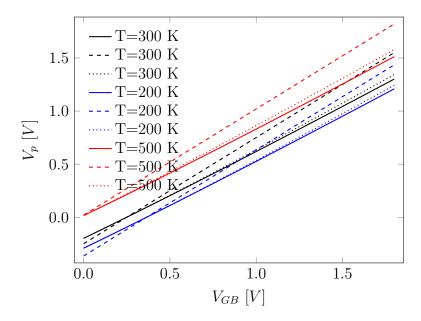

| 2.32 | Pitch-Off voltage approximation, overdrive voltage (dashed), indroduction of $n_q$ (doted) and numerical calculation (solid) at multiple                                                                                                                                                                                                     |     |

|      | temperatures                                                                                                                                                                                                                                                                                                                                 | 46  |

| 2.33 |                                                                                                                                                                                                                                                                                                                                              |     |

|      | large transistor considering multiple bias points and temperatures                                                                                                                                                                                                                                                                           | 47  |

| 2.34 | The BSIM6 approximation for the charge linearisation model for a                                                                                                                                                                                                                                                                             |     |

|      | large transistor considering multiple bias points and temperatures.                                                                                                                                                                                                                                                                          | 49  |

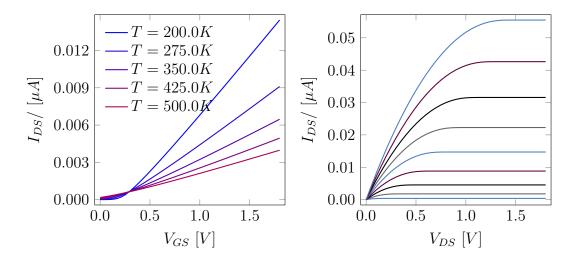

| 2.35 | $g_m/I_D$ calculated from measurement data for different transistor                                                                                                                                                                                                                                                                          |     |

|      | dimensions.                                                                                                                                                                                                                                                                                                                                  | 50  |

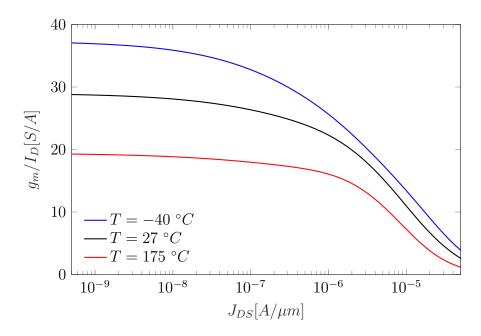

| 2.36 | $g_m/I_D$ calculated from measurement data for different transistor                                                                                                                                                                                                                                                                          |     |

|      | temperatures                                                                                                                                                                                                                                                                                                                                 | 51  |

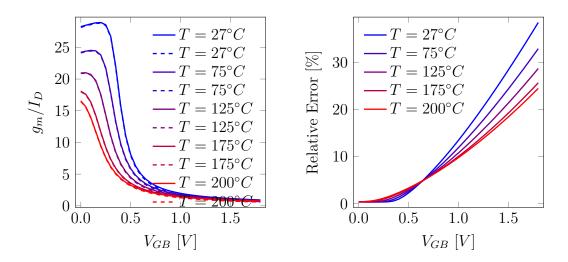

| 2.37 | $g_m/I_D$ characteristics obtained by a third order central difference                                                                                                                                                                                                                                                                       |     |

|      | method when considering the CVN mobility model (dashed lines)                                                                                                                                                                                                                                                                                |     |

|      | and constant mobility (solid lines) and their relative error                                                                                                                                                                                                                                                                                 | 52  |

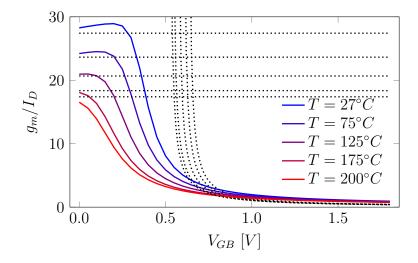

| 2.38 | $g_m/I_D$ characteristics obtained by a third order central difference                                                                                                                                                                                                                                                                       |     |

|      | method when considering the CVN mobility model (solid lines) and                                                                                                                                                                                                                                                                             |     |

|      | Brew's model assymptotes (dashed lines)                                                                                                                                                                                                                                                                                                      | 52  |

| 0.1  |                                                                                                                                                                                                                                                                                                                                              |     |

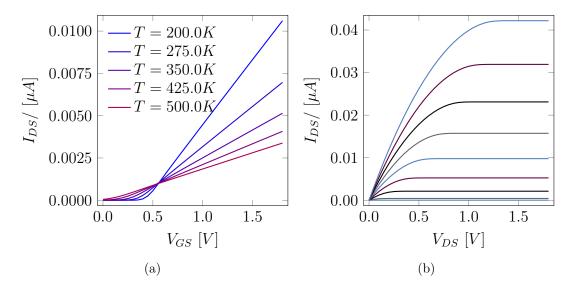

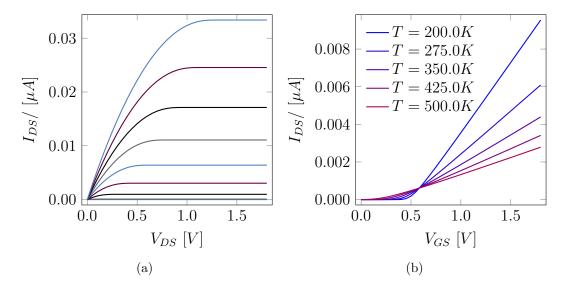

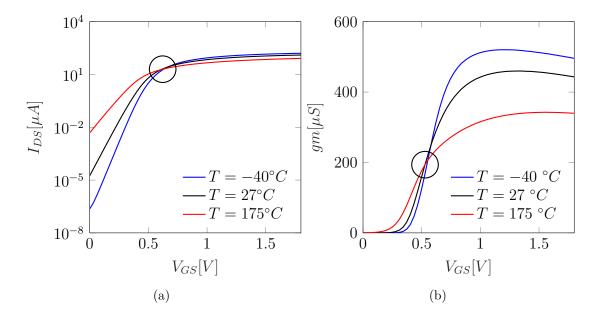

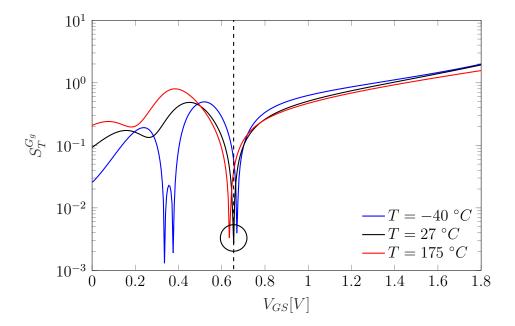

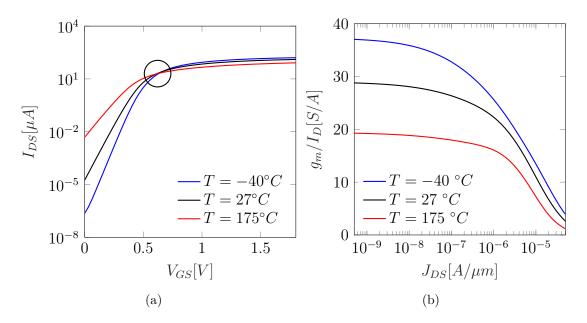

| 3.1  | Electric Simulation of (a) $I_D \times V_{GS}$ , $V_{DS} = 1.8 \text{ V}$ , (b) $g_m \times V_{GS}$ , $V_{DS} = 1.8 \text{ V}$ for a $10 \times 0.22 \ \mu m^2$ low $V_{th}$ NMOS transistors of XT018. One may observe in Fig. 3.1(a) and Fig. 3.1(b) present a ZTC bias point around 0.6 V and 0.5 V, respectively. Both figures are taken |     |

|      | at -40 °C (blue), 27 °C (black), and 175 °C (red), which lies on the                                                                                                                                                                                                                                                                         | ~ 4 |

|      | temperature range in which the process design kit is validated                                                                                                                                                                                                                                                                               | 54  |

|      |                                                                                                                                                                                                                                                                                                                                              |     |

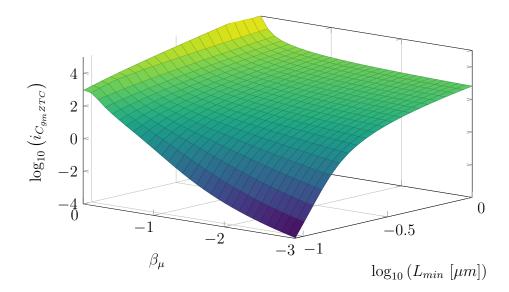

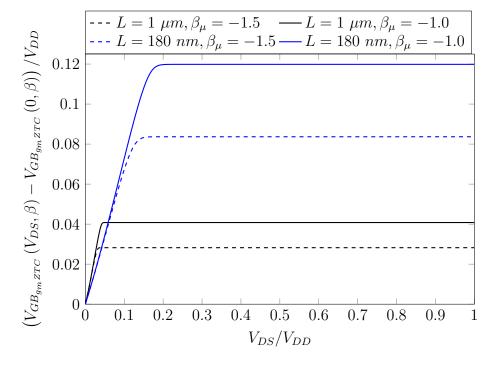

| 3.2  | Inversion Coefficient of the $g_{m_{ZTC}}$ calculated numerically using the UICM model for different $\beta_{\mu}$ as a function of $L_{min}$ using Denard's scalling rule. [64]                                               | 56       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.3  | Overdrive voltage to threshold voltage ratio at $g_{m_{ZTC}}$ for two different transistors sizes at 300 K and two different mobility temperature exponent                                                                     | 56       |

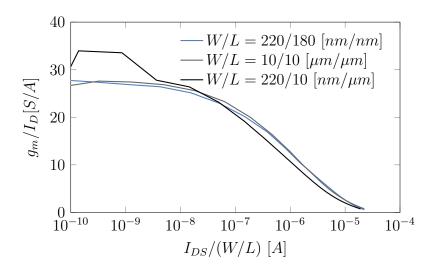

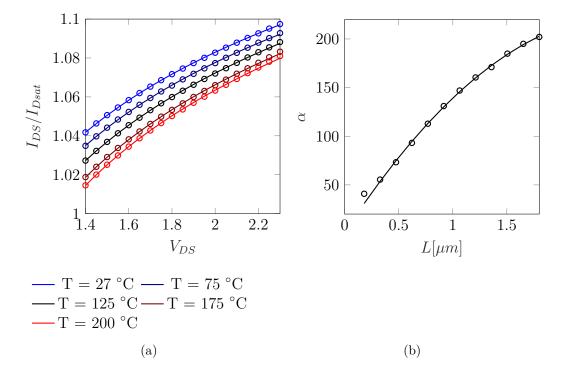

| 3.4  | Electric Simulation of $g_m/I_D \times V_{GS}$ , $V_{DS} = 0.1$ V, low $V_{th}$ NMOS transistors of XT018 taken at -40 °C (blue), 27 °C (black), and 175 °C (red), which lies on the temperature range in which the process    |          |

| 3.5  | design kit is validated                                                                                                                                                                                                        | 58       |

| 3.6  | of the Fermi level                                                                                                                                                                                                             | 60       |

| 3.7  | ferent transistor sizes                                                                                                                                                                                                        | 62<br>63 |

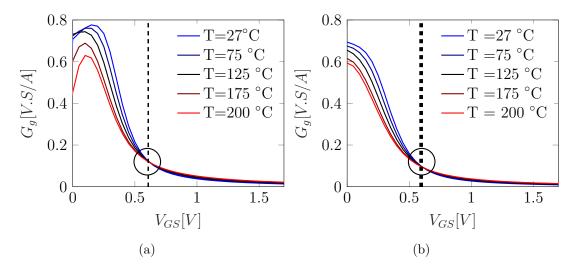

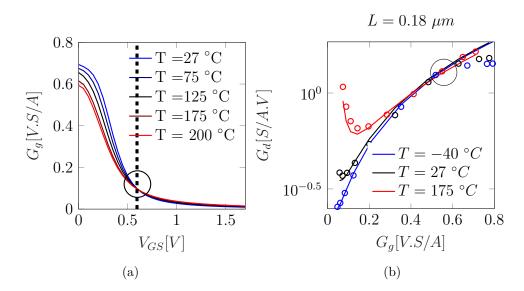

| 3.8  | The $G_g$ parameter extracted from measurement data from a Low VT NMOS transistor at 27, 75, 125, 175, 200°C (from blue to red) with dimensions (a) $10 \times 10 \ \mu m^2$ and (b) $10 \times 0.18 \ \mu m^2$ with $V_s = 0$ |          |

|      | and $V_D = 0.1 \ V$                                                                                                                                                                                                            | 64       |

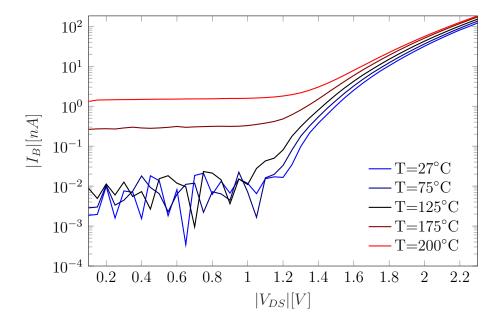

| 3.9  | NMOS low VT transistor bulk current at $V_{GS} = 0.5 \text{ V.} \dots$                                                                                                                                                         | 65       |

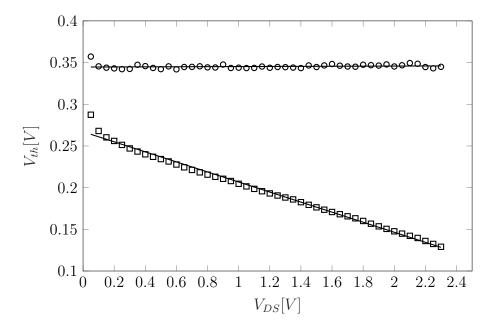

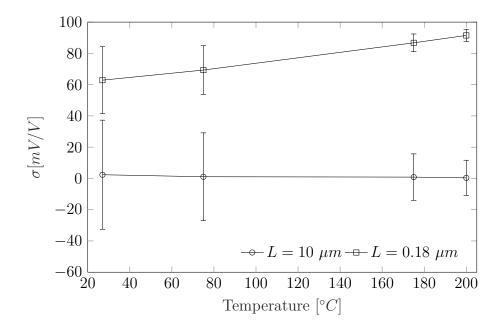

| 3.10 | Estimated DIBL from measurement data for a Low VT NMOS transistor with $L=0.18\mu m$ (squares), $L=10\mu m$ (circles), and the fitted                                                                                          | a=       |

| 3.11 | data (solid lines)                                                                                                                                                                                                             | 67       |

| 3.12 | data (solid lines)                                                                                                                                                                                                             | 68<br>68 |

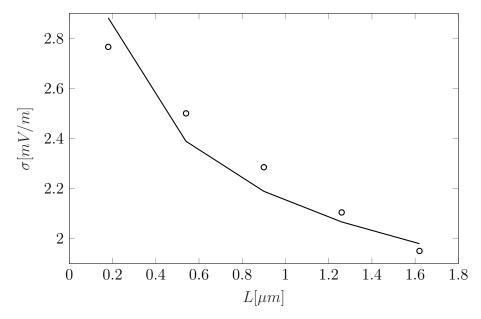

| 3.13 | $V_{D_{sat}}$ Extraction, in (a) the extracted $V_{D_{sat}}$ is highlighted with circles at different $V_{GS}$ , (b) shows the extracted model based on (3.24) for                                                             |          |

| 3.14 | $L=10\mu m$ (circles) and $L=0.18\mu m$                                                                                                                                                                                        | 69       |

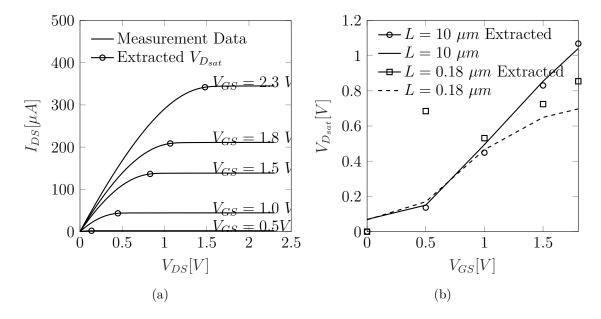

| 3.15 | and lines the proposed models                                                                                                                                                                                                  | 71       |

|      | $V_{DS} = 0.6$ V                                                                                                                                                                                                               | 72       |

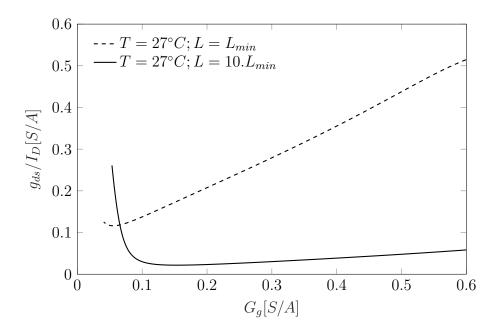

| 3.16 | $g_{ds}/I_D \times G_g$ plot obtained from BSIM model for different L and                                                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $V_{DS} = 0.6 \text{V}. \dots \dots$ | 73 |

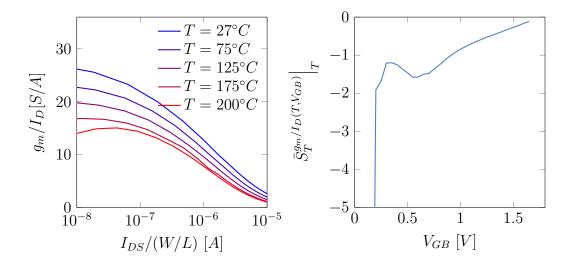

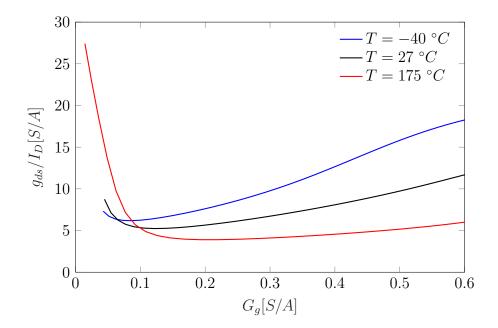

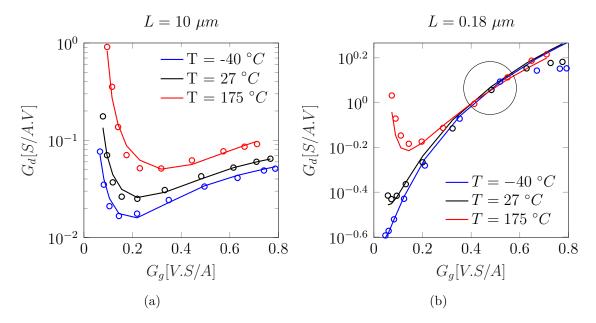

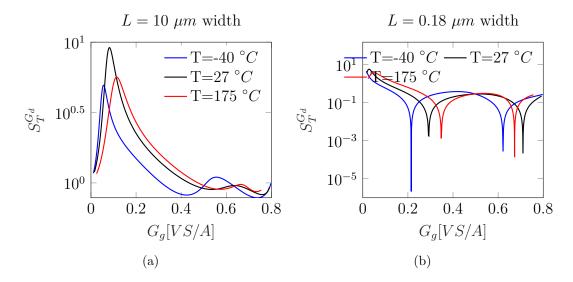

| 3.17 | Proposed temperature normalized parameters extracted from for (a)                                                                          |    |

|      | $L=10~\mu m$ and (b) $L=0.18~\mu m$ for temperatures -40, 27 and 175                                                                       |    |

|      | $^{\circ}C$ (from blue to red) obtained from simulated data                                                                                | 74 |

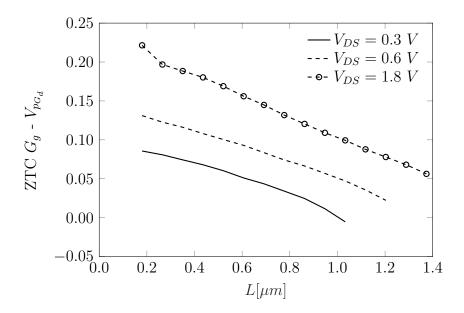

| 3.18 | Extracted pinch-off voltage at $G_{d_{ZTC}}$ for different $V_{DS}$ and channel                                                            |    |

|      | lengths                                                                                                                                    | 76 |

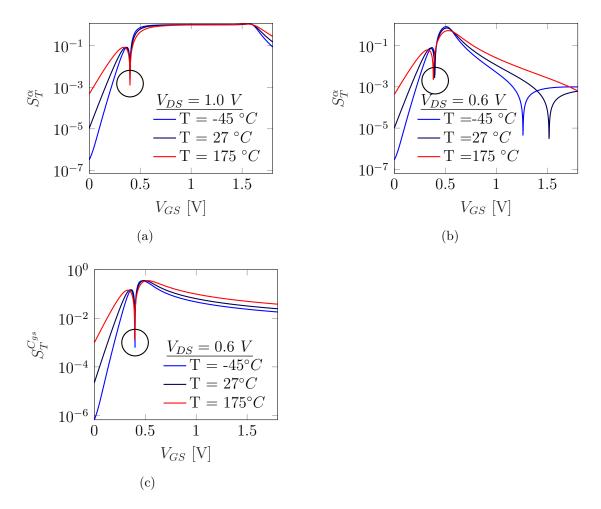

| 3.19 | Extracted sensitivities for long channel $(L = 10\mu m)$ (a) and short                                                                     |    |

|      | channel $(L = 0.18 \mu m)$ (b) at -40°C (Blue); 27°C (Black); 175°C                                                                        |    |

|      | (Red)                                                                                                                                      | 77 |

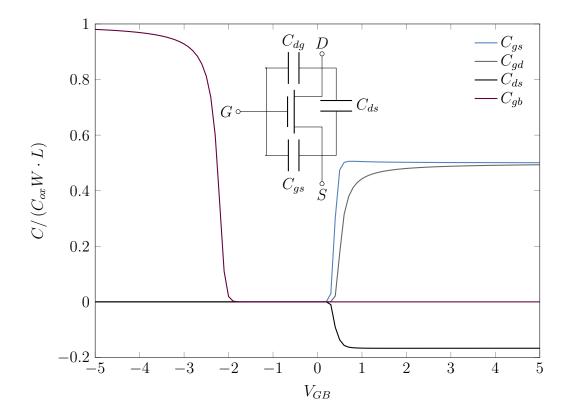

| 3.20 | MOSFET capacitances on a three terminal transistor (a) and nu-                                                                             |    |

|      | merical calculations of them using the UICM model                                                                                          | 78 |

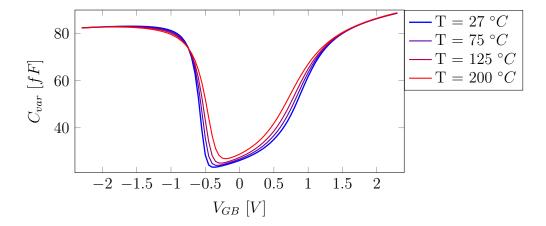

| 3.21 | Measurement Data of a $100\mu m \times 100\mu m$ NMOS varicap capacitance                                                                  |    |

|      | at $27^{\circ}C$ , $75^{\circ}C$ , $125^{\circ}C$ and $200^{\circ}C$                                                                       | 79 |

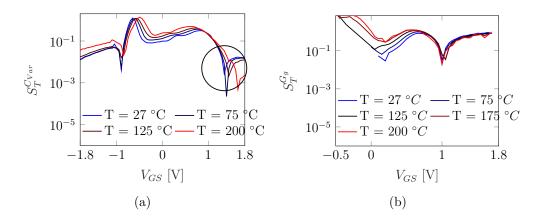

|      | Extracted sensitivity from measurement data for $C_{var}$ (a) and $G_g$ (b).                                                               | 80 |

| 3.23 | Extracted sensitivity from UICM model for transistors presenting                                                                           |    |

|      | the same physical parameters as low $V_{th}$ transistor for (a) $\alpha$ at $V_D$                                                          |    |

|      | = 1 V, (b) $\alpha$ at $V_D = 0.6$ V and (c) $C_{gs}$ at $V_D = 0.6$ V                                                                     | 83 |

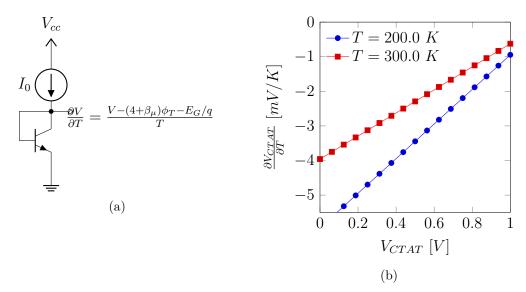

| 4.1  | Traditional CTAT Voltage Generation and the theoretical temper-                                                                            |    |

| 1.1  | ature coefficient at different temperatures for $\beta_{\mu} = -1.5.$                                                                      | 86 |

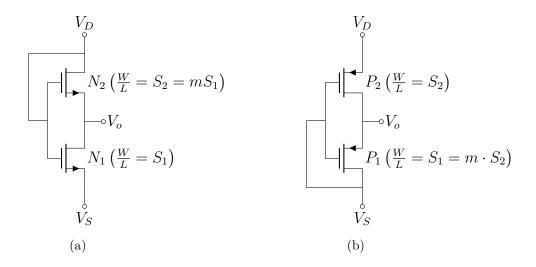

| 4.2  | Self-Cascode Composite Transistor in NMOS (a) and PMOS (b)                                                                                 |    |

|      | versions                                                                                                                                   | 87 |

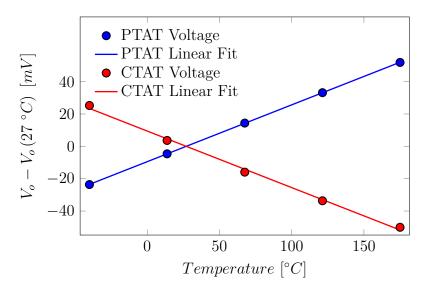

| 4.3  | PTAT and CTAT voltages when designed for maximum linearity                                                                                 | 88 |

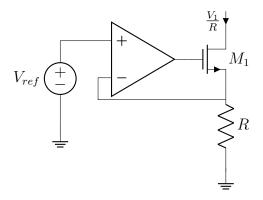

| 4.4  | Voltage to Current Converter                                                                                                               | 89 |

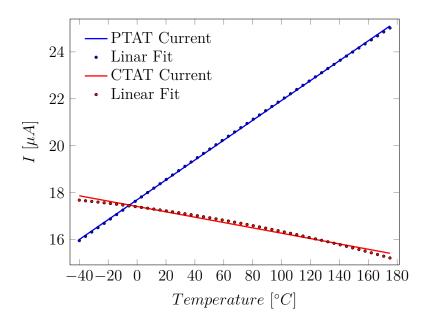

| 4.5  | PTAT and CTAT Currents after the voltage to current converters                                                                             | 89 |

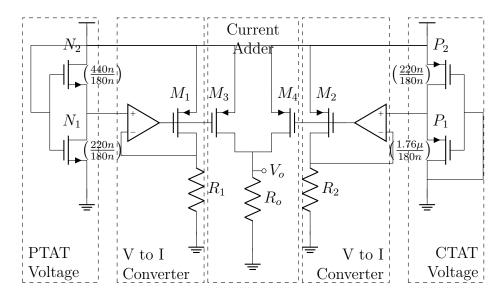

| 4.6  | Proposed bandgap circuit                                                                                                                   | 90 |

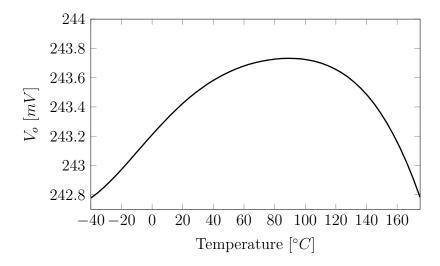

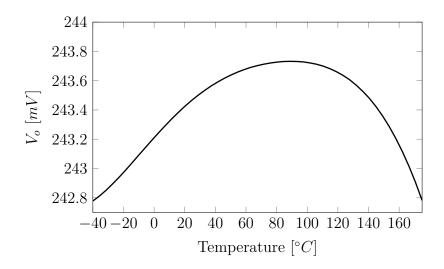

| 4.7  | Simulated bandgap reference voltage from -40 $^{\circ}C$ to 175 $^{\circ}C$                                                                | 91 |

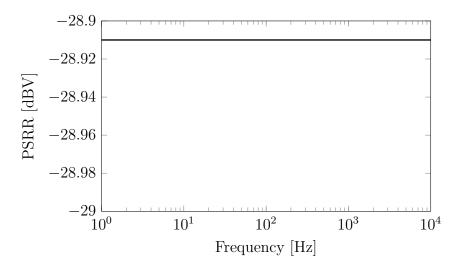

| 4.8  | Simulated Power Supply Rejection Ratio                                                                                                     | 91 |

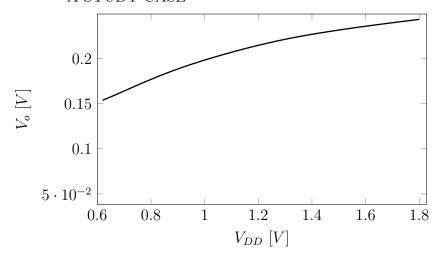

| 4.9  | Output Voltage Dependency to power supply voltage                                                                                          | 92 |

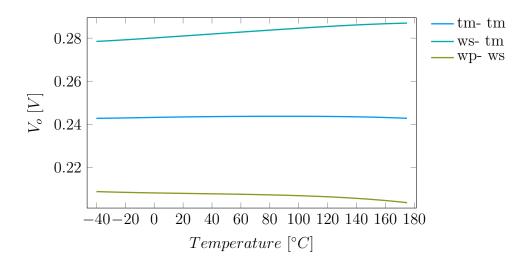

| 4.10 |                                                                                                                                            |    |

|      | corner corresponds to the transistors corner and second to the re-                                                                         |    |

|      | sistors                                                                                                                                    | 92 |

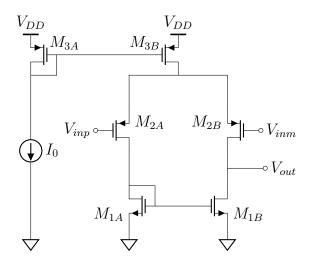

| 4.11 | PMOS differential pair with active load                                                                                                    | 93 |

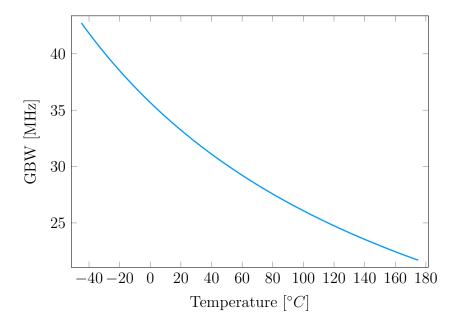

| 4.12 | GBW from the proposed amplifier, as estimated by (4.15) and sim-                                                                           |    |

|      | ulated at spectre<br>(To Do) from -45 °C to 175 °C                                                                                         | 95 |

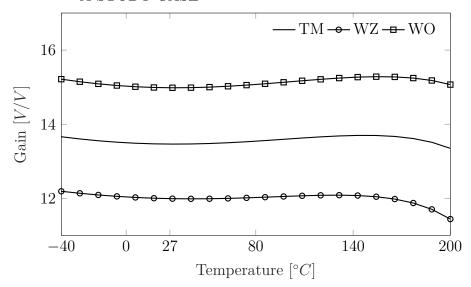

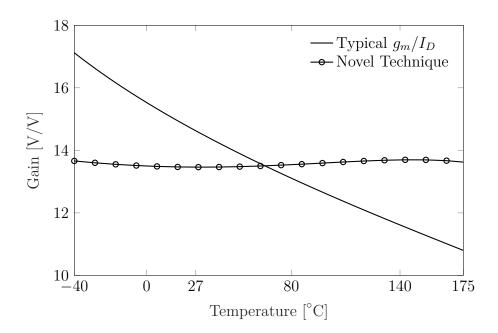

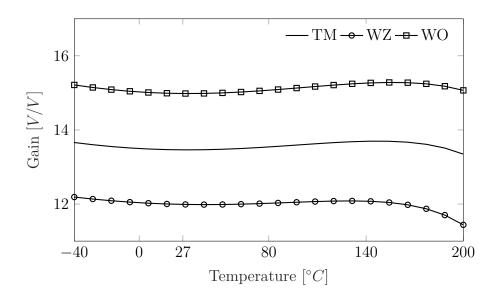

| 4.13 | Gain variation over temperature in different corners of the amplifier                                                                      |    |

|      | design with the novel methodology                                                                                                          | 96 |

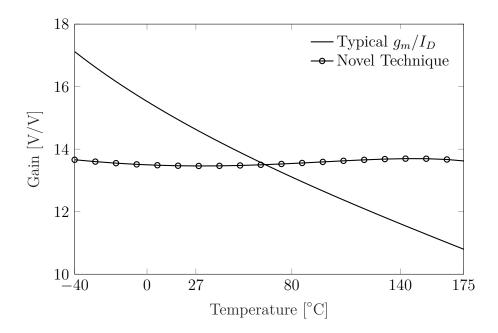

| 4.14 | Comparison with gain over temperature using typical strong inver-                                                                          |    |

|      | sion and the proposed in TT corner                                                                                                         | 97 |

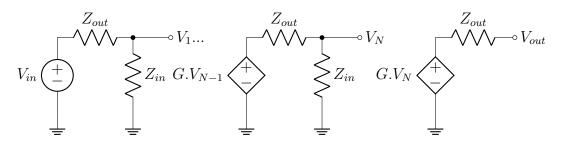

| 4.15 | Multiple Stage Amplifier Model                                                                                                             | 98 |

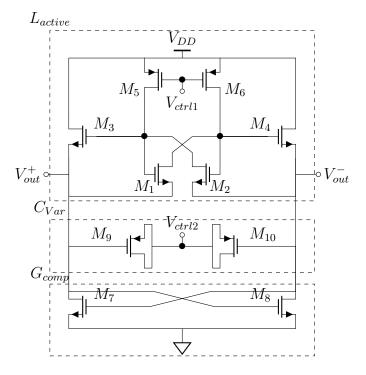

| 4.16       | Active Inductor Based VCO                                                                                                                                                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

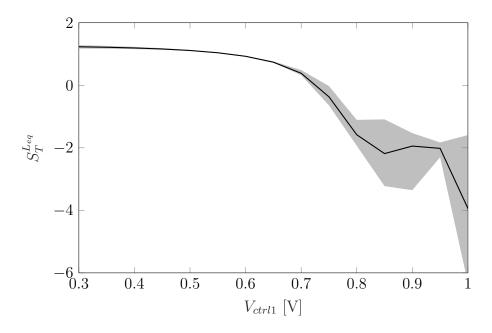

| 4.17       | Active Inductance equivalent inductance range (gray) and mean(solid)                                                                                                                  |

|            | at different control voltages and temperature from -40 $^{\circ}C$ to 200 $^{\circ}C$ . 103                                                                                           |

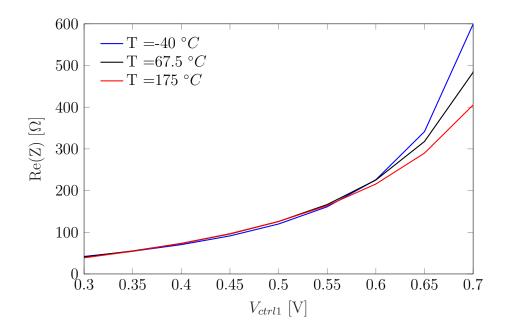

| 4.18       | PSL Real Part from active inductance impedance for $V_{ctrl1}$ at the                                                                                                                 |

|            | tuning range and different temperatures                                                                                                                                               |

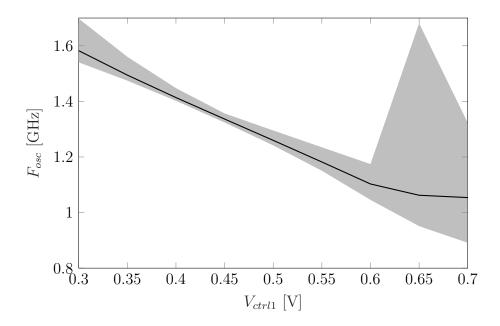

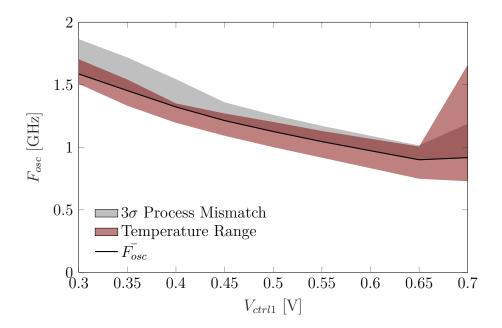

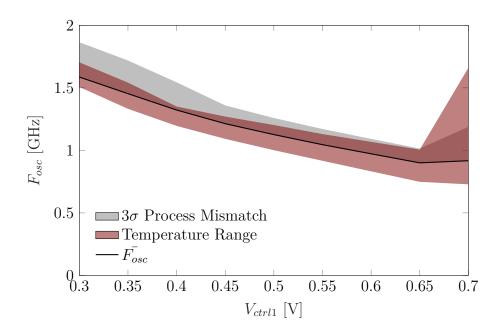

| 4.19       | PSL Oscillation frequency range (gray) and mean(solid) at different                                                                                                                   |

|            | control voltages and temperature from -40 $^{\circ}C$ to 175 $^{\circ}C$ 105                                                                                                          |

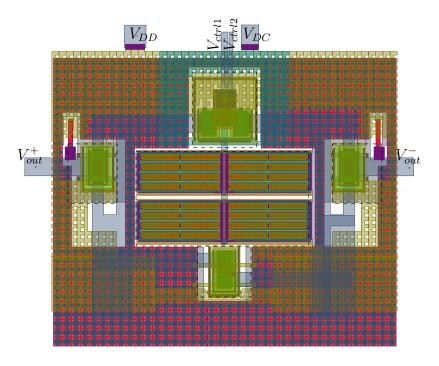

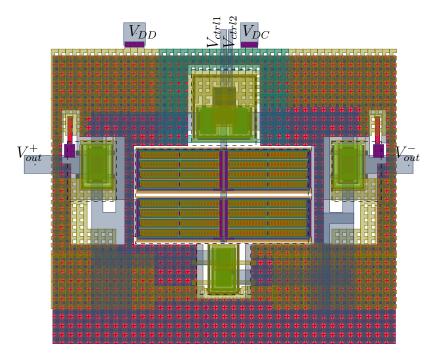

| 4.20       | Temperature-Aware VCO Layout presenting an area of 163.5 x 190                                                                                                                        |

|            | $\mu m^2$                                                                                                                                                                             |

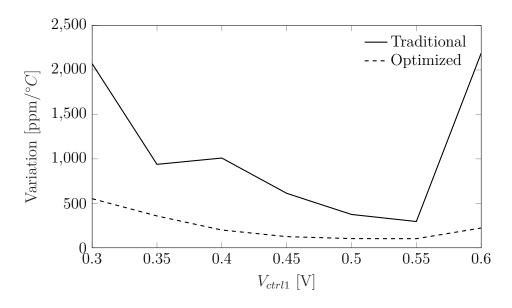

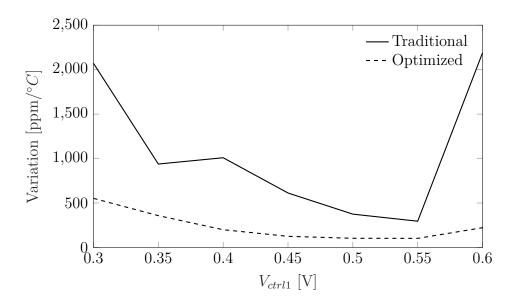

| 4.21       | Frequency Temperature coefficient comparison between [10] and this                                                                                                                    |

|            | work                                                                                                                                                                                  |

| 4.22       | Monte Carlo Results for the oscillation Frequency of the proposed                                                                                                                     |

|            | VCO                                                                                                                                                                                   |

| <i>C</i> 1 | Circulation (lastrians (a) I w I/ I/ I I I I I I I I I I I I I I I                                                                                                                    |

| 6.1        | Simulation électrique (a) $I_D \times V_{GS}$ , $V_{DS} = 1.8 \text{ V}$ , (b) $g_m \times V_{GS}$ ,                                                                                  |

|            | $V_{DS} = 1.8 \text{ V}$ and (c) $g_m/I_D$ , $V_{DS} = 1.8 \text{ V}$ for a $10 \times 0.22 \mu\text{m}^2$ low $V_{th}$ d'un transistor NMOS. Sub-figures (a) et (b) présentent un ZT |

|            | C, lorsque (c) ne le présente pas                                                                                                                                                     |

| 6.2        | Caractéristiques des paramètres proposés pour un transistor low-VT                                                                                                                    |

| 0.2        | avec 180 $nm$ de longueur de canal (a) $G_q$ (b) $G_d$                                                                                                                                |

| 6.3        | Tension de reference du bandgap proposé de -40 °C à 175 °C 117                                                                                                                        |

| 6.4        | Comparaison entre le gain d'un amplificateur conçu avec $q_m/I_D$                                                                                                                     |

| 0.1        | traditionnelle et la proposition $\dots \dots \dots$                                  |

| 6.5        | Variation du gain de l'amplificateur proposé à différentes tempéra-                                                                                                                   |

| 0.0        | tures                                                                                                                                                                                 |

| 6.6        | Variation du gain de l'amplificateur proposé à différentes tempéra-                                                                                                                   |

|            | tures                                                                                                                                                                                 |

| 6.7        | Layout du VCO proposé avec une surface de 163.5 x 190 $\mu m^2$ 119                                                                                                                   |

| 6.8        | Résultats Monte Carlo de la fréquence généré par l'oscillateur proposé. 120                                                                                                           |

|            |                                                                                                                                                                                       |

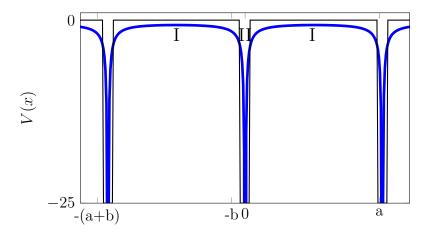

|            | The Kronig-Penney model potential energy approximation 125                                                                                                                            |

| A.2        | Right hand side of Kronig-Penney model solution                                                                                                                                       |

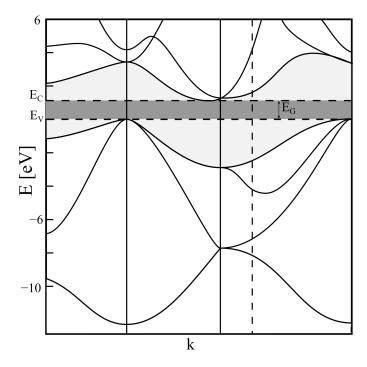

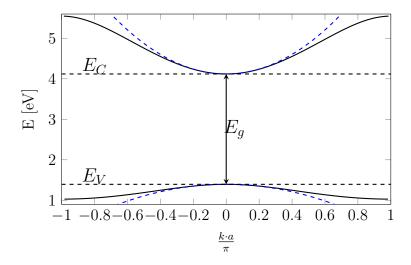

| A.3        | Silicon Energy, wave vector relation on intrinsic silicon 127                                                                                                                         |

| A.4        | Test                                                                                                                                                                                  |

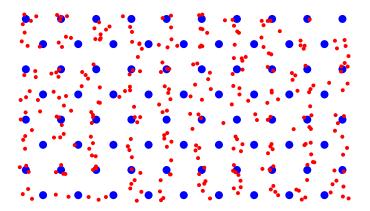

| A.5        | Representation of a crystal lattice                                                                                                                                                   |

| A.6        | System Subdivisions                                                                                                                                                                   |

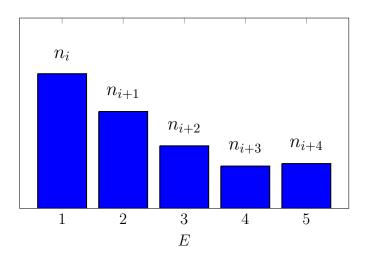

| A.7        | Energy binning histogram                                                                                                                                                              |

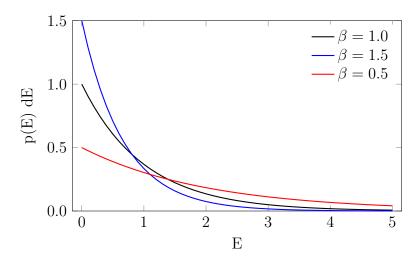

| A.8        | The Boltzmann Distribution                                                                                                                                                            |

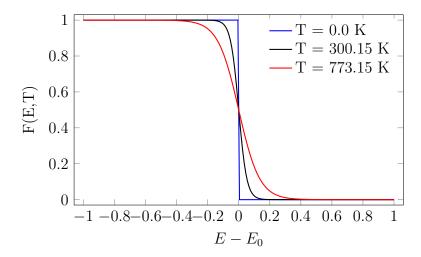

| B.1        | Fermi-Dirac distribution function at different temperatures 134                                                                                                                       |

| B.2 | Comparison Between Fermi-Dirac integral and Boltzmann approx-         |     |

|-----|-----------------------------------------------------------------------|-----|

|     | imation                                                               | 135 |

| B.3 | Intrinsic carrier concentration relation with inverse temperature us- |     |

|     | ing Fermi-Dirac distribution                                          | 136 |

|     |                                                                       |     |

| D.1 | Numerical calculations of the effective mobility over temperature at  |     |

|     | different doping concentrations                                       | 144 |

# List of Tables

| 2.1 | Default Caughey Thomas Mobility model default parameters used in ATLAS                        | 22 |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | Linearity Comparison Between Current and Voltage Generators Circuit Dimensions and Parameters |    |

## Acknowledgement

Even though a little bit cliché is still true that if I have seen further, it is by standing on the shoulders of Giants and for them I would like to thank:

- My Director Prof. Francisco de Oliveira Alves and Prof. Pietro Maris Ferreira whom I consider my Co-Director. For all the support given during my thesis. And helped me to grow not only as a scientist but also as a human and a professional

- Prof. Philippe Benabes, Prof. Jerome Juillard, Mr. Francis Trelin, and Prof. Emilie Avignon for the support and very interesting conversations during those three years.

- For their time and extremely valuable feedback, my dissertation committee members, Prof. Fernando Silveira, Prof. Sylvain Bordel, Dr. Manohiaina Galal-El-Dine, and Prof. Arnaud Bournel.

- X-FAB employees and now my colleagues Dr. Rachid Harmani and Mr. Pascal Louis for the very fruitful collaboration and acquired measurements.

- Dr. Ali Mostafa for being a great friend and colleague and for the discutions, ideas and papers together.

- All my friends who helped and encouraged me during this periods, but whom I could not fit in here.

- To my teachers Ms. Silvana Martins Bayma, Ms. Gloria Vianna, Ms. Gilda Leventhal, Mr. Germano Nogueira Prado and the institution Colégio Pedro II for being eternalized in me.

- To my professors Prof. Carlos Fernando Teodósio Soares, Prof. Fernando A. P. Barúqui, Dr. Antonio Petraglia, Prof. Luiz Wagner Pereira Biscainho and Prof. Prof. Antonio Carlos Moreirão de Queiroz (in memorian) that ignigithed the passion for electronics on me.

2 CONTENTS

• My family, especially my mother Rita de Cassia Raposo de Oliveira Martins and godmother Marcia Lucia Raposo Calixto, raised me, supported me, and prioritized my education.

• And last but not least to my girlfriend Justine Chollet and her family for all the love, encouragement and support during this period.

# Chapter 1

# The need of Temperature-Aware Circuits

According to Professor Jeremy Rifkin, all significant economic changes in history originate from a paradigm change over three leading technologies: communication, transport, and energy [11]. In the first industrial revolution, the steam printing press and the telegraph joined with charcoal, and railroads allowed the beginning of modern urban society and industry. Some decades after, telephone and radio communications powered by a centralized electricity system, mostly based on fossil fuels and cars, allowed urban and industrial growth to the present state.

In the last few years, the most significant advancement in communication is that the internet is now arriving in transport and energy through the Internet of Things (IoT) framework. The exponential advances in circuits, processing power, and the internet deeply affected our relationship with technology and reshaped our society. Those innovations, promoted in the latest decades, now arrive at objects with Big Data, allowing better performance in data analytics and the Internet of Things (IoT), shortening the time to acquire information, and allowing real-time control and analysis of processes [1].

As with the previous industrial revolutions, Industry 4.0 starts to deeply affect our way to design, manufacture and consume new products. In his book entitled Entropy [11], Professor Rifkin discusses the productivity paradox present in our society. Even though technology and education standards have known and massive growth, producing better performance machines and workers, productivity has been declining in the last 20 years. This paradox is later discussed in his book and explained by introducing thermodynamical inspired modeling of economics, showing that the major efficiency losses in the production phases are due to our inability to control our processes closely.

The Industry 4.0, the productivity paradox is solved using the IoT framework, where connected machines and sensors are used to gain better knowledge and have

better decisions through the process. In this context, it becomes critical to access real-time, accurate, and reliable information to monitor and control any process included in the IoT framework.

To achieve this goal, circuits and sensors must work reliably, have low production costs and environmentally sustainable materials. According to the Boston Consulting Group [2], the fast spread of IoT is mainly limited by production and maintenance costs. Circuit reliability is a complex task and should be considered through the whole design and manufacturing process. Since IoT circuits need to be placed inside machines, vehicles, and portable devices, they can be submitted to extreme and harsh environments.

### 1.1 Circuits Reliability in Harsh Environments

With the increasing demand for sensors to monitor performance, the readout circuits must reliably work under the different environmental conditions they are surrounded by. Those external perturbations must not deteriorate their ability to provide fast and accurate measurements. Temperature, pressure, and radiation impacts on circuit reliability have to been studied since the early stages of electronics development [12].