# Synthèses de fréquence à bas bruit basées sur des oscillateurs opto-électroniques couplés intégrées en technologie BiCMOS SiGe 130 nm

Arnaud Collet

#### ▶ To cite this version:

Arnaud Collet. Synthèses de fréquence à bas bruit basées sur des oscillateurs opto-électroniques couplés intégrées en technologie BiCMOS SiGe 130 nm. Electromagnétisme. Université Paul Sabatier - Toulouse III, 2021. Français. NNT: 2021TOU30103. tel-03603746

#### HAL Id: tel-03603746 https://theses.hal.science/tel-03603746

Submitted on 10 Mar 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

## En vue de l'obtention du DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par l'Université Toulouse 3 - Paul Sabatier

#### Présentée et soutenue par Arnaud COLLET

Le 22 juillet 2021

Synthèses de fréquence à bas bruit basées sur des oscillateurs opto-électroniques couplés intégrées en technologie BiCMOS SiGe 130nm

Ecole doctorale : **GEETS - Génie Electrique Electronique, Télécommunications et Santé : du système au nanosystème**

Spécialité : Electromagnétisme et Systèmes Haute Fréquence

Unité de recherche :

LAAS - Laboratoire d'Analyse et d'Architecture des Systèmes

Thèse dirigée par **Éric TOURNIER**

Jury

Mme Florence PODEVIN, Rapporteure

M. Bruno BARELAUD, Rapporteur

M. Olivier LLOPIS, Examinateur

M. Kamel ACHOUR, Invité

M. Éric TOURNIER, Directeur de thèse

### Remerciements

Ce mémoire présente mes travaux de recherche effectués au Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) à Toulouse, unité propre du Centre National de la Recherche Scientifique (CNRS), au sein du groupe Microondes et Opto-microondes pour Systèmes de Télécommunications (MOST). Je tiens à remercier M. Liviu Nicu, directeur du LAAS, de m'avoir accueilli au sein de ce laboratoire et de m'avoir permis d'évoluer dans d'aussi bonnes conditions de travail. Je souhaite également remercier l'ensemble des partenaires de ce projet : Thalès Alénia Space (TAS), Thalès Research and Technology (TRT), le Laboratoire Aimé Cotton (LAC) et en particulier le Centre National d'Etudes Spatiales (CNES) et la région Occitanie d'avoir préservé ma rémunération malgré l'arrêt prématuré du projet. Je souhaite remercier mon directeur de thèse, M. Éric Tournier, pour les nombreuses connaissances et compétences qu'il a su me transmettre. Je le remercie de s'être toujours assuré que je dispose de tous les outils nécessaires pour mener à bien mes recherches et de m'avoir guidé jusqu'à l'accomplissement de cette thèse malgré les quelques embûches que nous avons rencontrées. Je voudrais ensuite remercier les membres du jury de m'avoir fait bénéficier de leur expertise pour l'évaluation de mes travaux. Mme Florence Podevin et M. Bruno Barelaud, en tant que rapporteurs du manuscrit, d'avoir pu me remettre leur rapports détaillés et précis malgré un délai très bref. M. Kamel Achour, invité, d'avoir partagé son expertise et sa passion pour la conception de circuits et M. Olivier Llopis, examinateur et président du jury, pour les nombreuses connaissances qu'il m'a apportées lors de cette thèse. Je vous remercie sincèrement pour vos retours, pour la justesse de vos questions et pour les discussions que nous avons eues. Je tiens à remercier l'ensemble de l'équipe MOST pour ses conseils et les discussions enrichissantes que nous avons pu avoir lors de cette thèse. Je tiens à remercier M. Alexandre Rumeau et M. Damien Saugnon pour leur aide précieuse lors de la caractérisation expérimentale des circuits. Je remercie Mme Hassna Hameur, stagiaire au LAAS qui a contribué à cette thèse, pour sa rigueur, sa curiosité scientifique et sa bonne humeur immuable. Un grand merci aux différents collègues du bureau G24 pour les moments que nous avons partagés : Napoléon, la force tranquille, François, la sagesse incarnée, Pierre, l'original, Alexandre, le bon vivant et Jordi, la bouffée d'air frais de la fin de thèse. J'envoie une rafale de mercis à la team Bang<sup>TM</sup>: Lya, Sylvain, Vincent, Fabien, Damien, David et William. Merci pour les moments de détente et de rire. Je remercie également tous les doctorants, post-doctorants et membres du LAAS pour leurs conseils et leur bonne humeur: Aliou, Boris, Audrey, Alexis, Bastien, Lucas, Nicolas, Lilian, Jordi et tous les autres que j'oublie. Je remercie les amis qui m'ont accompagné et soutenu : Pascal, sans qui je n'aurais pas fait cette thèse, et Carole, pour les bons moments passés ensemble ces dernières années. Hugo, que je remercie sincèrement d'avoir lu ce manuscrit, et Myriam, pour votre bonne humeur réconfortante. Aude, pour tous les moments passés ensemble durant nos thèses respectives à se soutenir mutuellement. Un énorme merci à ma famille pour leur soutien et leur amour : mes parents qui ont toujours voulu le meilleur pour moi, qui ont tout fait pour, et que j'ai voulu rendre fiers. Mes frères, Antoine et Alexandre, et leur dulcinée, Anaïs et Orlane, et ma petite sœur Anaïs pour leur soutien et les bons moments que l'on partage régulièrement. Une pensée pour Odile et Nimchi, nos deux chats pleins de tendresse et d'affection. Enfin, je ne pourrais jamais assez remercier Anaïs, qui partage ma vie depuis quatre années et qui a du supporter une deuxième thèse après la sienne. Merci pour ta patience qui a été mise à rude épreuve par moment, merci pour ta bienveillance constante, merci pour tout ce que tu as fait pour me faciliter la vie, merci pour tes précieux conseils tout au long de la thèse... Tu es exceptionnelle et je mesure chaque jour la chance que j'ai de t'avoir à mes côtés.

Merci.

## Table des matières

#### Remerciements

| In | trodu | ction gé | énérale                                                               | 1  |

|----|-------|----------|-----------------------------------------------------------------------|----|

| 1  | Mét   | hodes d  | le synthèse de références hyperfréquences                             | 11 |

|    | Intro | duction  |                                                                       | 11 |

|    | 1.I   | La syn   | thèse par multiplication de fréquence                                 | 12 |

|    |       | 1.I.1    | Principe                                                              | 12 |

|    |       | 1.I.2    | Bruit de phase dans la PLL                                            | 13 |

|    |       | 1.I.3    | État de l'art de la PLL                                               | 16 |

|    | 1.II  | La syn   | thèse par division de fréquence                                       | 18 |

|    |       | 1.II.1   | Principe                                                              | 18 |

|    |       | 1.II.2   | Oscillateurs opto-électroniques couplés                               | 19 |

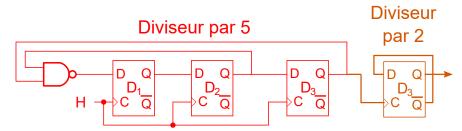

|    |       | 1.II.3   | Diviseurs de fréquence numériques                                     | 21 |

|    |       |          | 1.II.3.a Principe                                                     | 21 |

|    |       |          | 1.II.3.b Diviseurs synchrones                                         | 26 |

|    |       |          | 1.II.3.c Diviseurs asynchrones                                        | 27 |

|    |       |          | 1.II.3.d Diviseurs entiers fixes                                      | 28 |

|    |       |          | 1.II.3.e Diviseurs entiers programmables                              | 29 |

|    |       |          | 1.II.3.f Diviseurs dans la PLL                                        | 32 |

|    |       |          | 1.II.3.g État de l'art diviseurs numériques                           | 37 |

|    |       | 1.II.4   | Diviseurs analogiques                                                 | 39 |

|    |       |          | 1.II.4.a Principe                                                     | 39 |

|    |       |          | 1.II.4.b Diviseurs entiers à verrouillage par injection               | 40 |

|    |       |          | 1.II.4.c Diviseurs entiers et fractionnaires régénératifs             | 41 |

|    |       |          | 1.II.4.d État de l'art des diviseurs analogiques ILFD et régénératifs | 43 |

|    | Con   | clusion  |                                                                       | 46 |

| 2 | Synt       | thèse pa | ar division entière                                             |     |            |   | 61  |

|---|------------|----------|-----------------------------------------------------------------|-----|------------|---|-----|

|   | Intro      | duction  | 1                                                               |     |            |   | 61  |

|   | <b>2.I</b> | Divise   | eurs numériques                                                 |     |            |   | 62  |

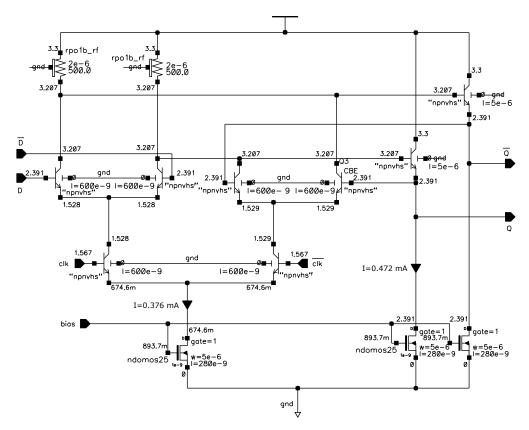

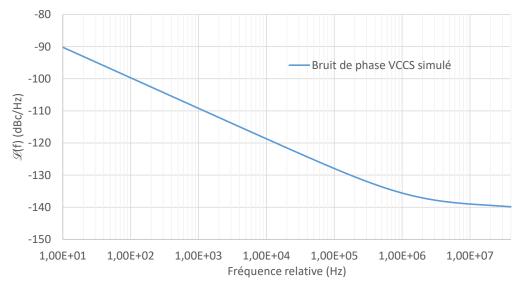

|   |            | 2.I.1    | Diviseur par 2 ECL numérique VCCS                               |     |            |   | 62  |

|   |            |          | 2.I.1.a Présentation                                            |     |            |   | 62  |

|   |            |          | 2.I.1.b Conception et résultats de simulations                  |     |            |   | 63  |

|   |            | 2.I.2    | Diviseur par 2 ECL numérique VCVS                               |     |            |   | 69  |

|   |            |          | 2.I.2.a Présentation                                            |     |            |   | 69  |

|   |            |          | 2.I.2.b Conception et résultats de simulations                  |     |            |   | 71  |

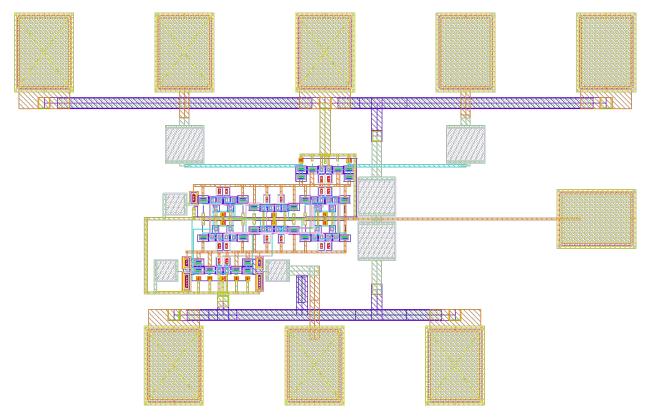

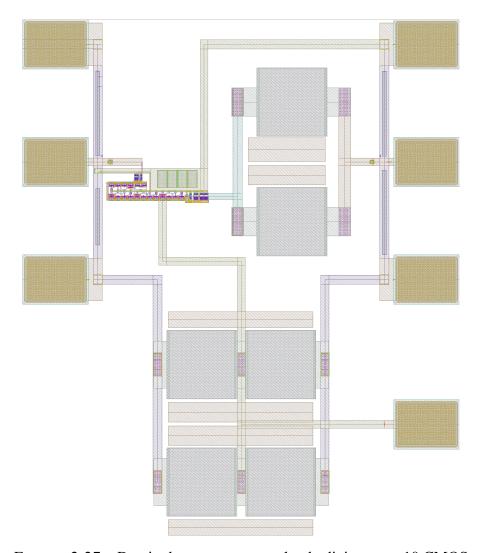

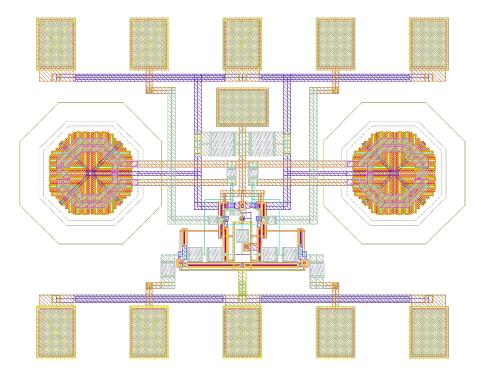

|   |            |          | 2.I.2.c Dessin des masques du diviseur                          |     |            |   | 72  |

|   |            |          | 2.I.2.d Protocole et résultat de mesures                        |     |            |   | 75  |

|   |            | 2.I.3    | Diviseur par 3 ECL numérique                                    |     |            |   | 78  |

|   |            |          | 2.I.3.a Présentation                                            |     | , <b>.</b> |   | 78  |

|   |            |          | 2.I.3.b Conception et résultats de simulations                  |     | , <b>.</b> |   | 80  |

|   |            |          | 2.I.3.c Dessin des masques du diviseur                          |     |            |   | 82  |

|   |            |          | 2.I.3.d Protocole et résultat de mesures                        |     |            |   | 83  |

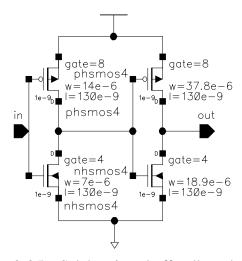

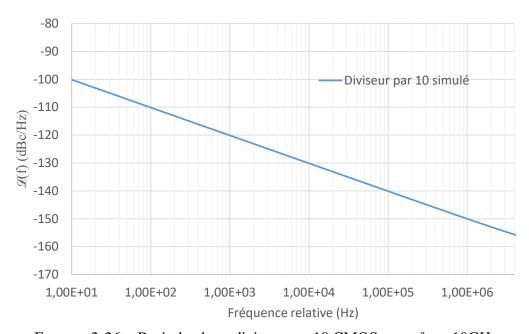

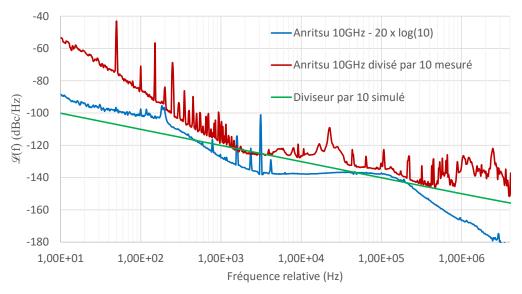

|   |            | 2.I.4    | Diviseur par 10 CMOS numérique                                  |     |            |   | 84  |

|   |            |          | 2.I.4.a Présentation                                            |     |            |   | 84  |

|   |            |          | 2.I.4.b Conception et résultats de simulations                  |     |            |   | 85  |

|   |            |          | 2.I.4.c Protocole et résultat de mesures                        |     |            |   | 85  |

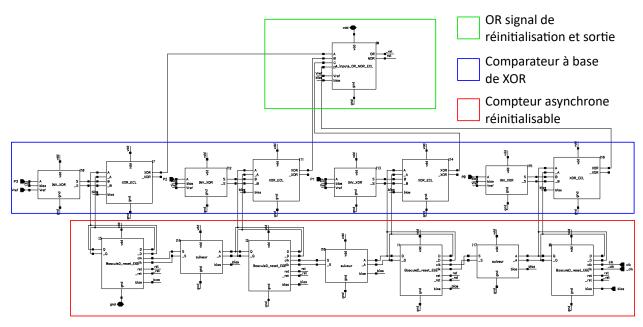

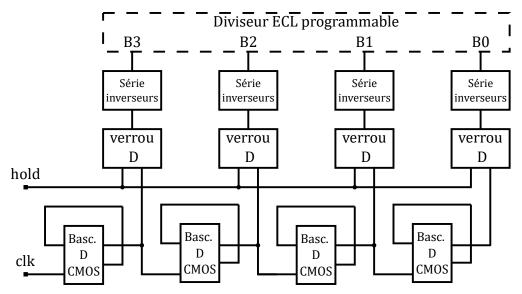

|   |            | 2.I.5    | Diviseur numérique ECL programmable sur 4 bits basé sur un déco | omp | teu        | r |     |

|   |            |          | asynchrone                                                      |     |            |   | 90  |

|   |            |          | 2.I.5.a Présentation                                            |     |            |   | 90  |

|   |            |          | 2.I.5.b Conception et résultats de simulations                  |     |            |   | 91  |

|   |            | 2.I.6    | Diviseur numérique ECL programmable sur 4 bits basé sur un déco | omp | teu        | r |     |

|   |            |          | synchrone                                                       |     |            |   | 93  |

|   |            |          | 2.I.6.a Présentation                                            |     |            |   | 93  |

|   |            |          | 2.I.6.b Conception et résultats de simulations                  |     |            |   | 94  |

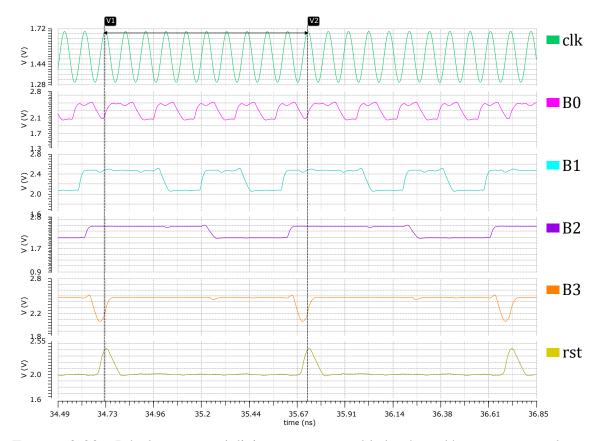

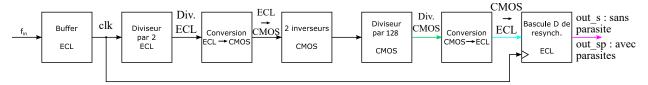

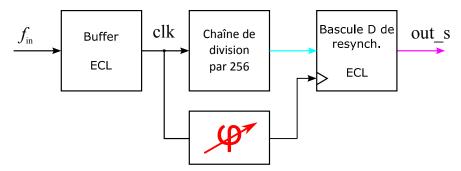

|   |            | 2.I.7    | Circuit test de la technique de resynchronisation               |     |            |   | 95  |

|   |            |          | 2.I.7.a Présentation                                            |     |            |   | 95  |

|   |            |          | 2.I.7.b Conception et résultats de simulations                  |     |            |   | 95  |

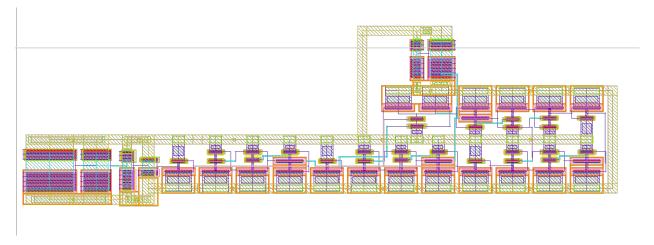

|   |            |          | 2.I.7.c Dessin des masques du diviseur                          |     |            |   | 100 |

|   |            |          | 2.I.7.d Protocole et résultat de mesures                        |     |            |   | 100 |

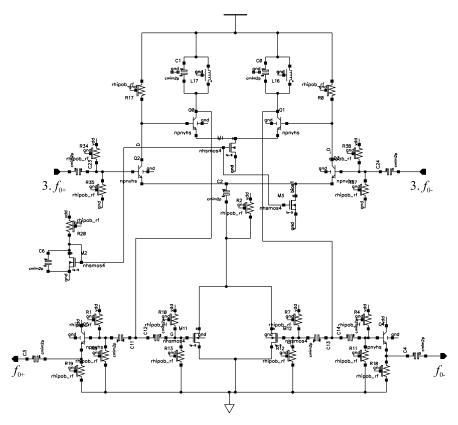

|   | 2.II       | Divise   | eurs analogiques                                                |     |            |   | 104 |

|   |            | 2.II.1   | Diviseur par 3 à verrouillage par injection                     |     |            |   | 104 |

|   |            |          | 2.II.1.a Présentation                                           |     |            |   | 104 |

|    |       |         | 2.II.1.b Conception et résultats de simulations      | 105   |

|----|-------|---------|------------------------------------------------------|-------|

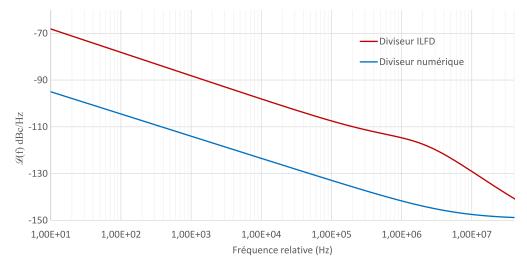

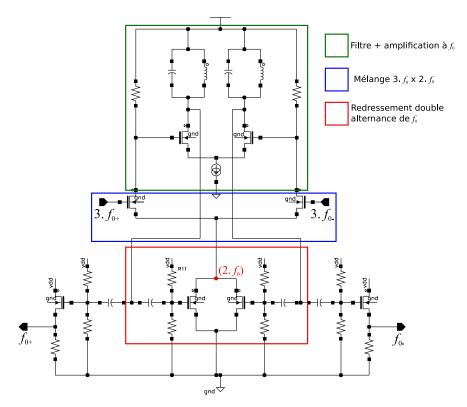

|    |       | 2.II.2  | Diviseur par 3 avec second harmonique régénératif    | 106   |

|    |       |         | 2.II.2.a Présentation                                | 106   |

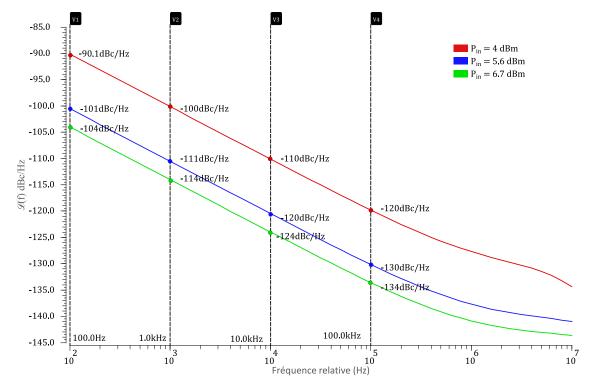

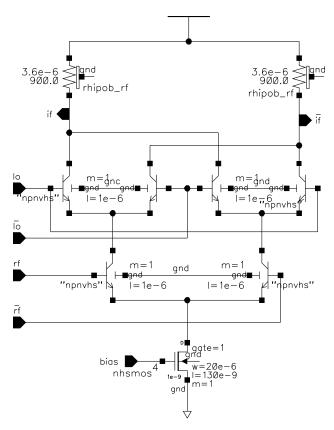

|    |       |         | 2.II.2.b Conception et résultats de simulations      | 109   |

|    |       |         | 2.II.2.c Dessin des masques du diviseur              | 110   |

|    |       |         | 2.II.2.d Protocole et résultat de mesures            | 111   |

|    | Conc  | clusion |                                                      | . 112 |

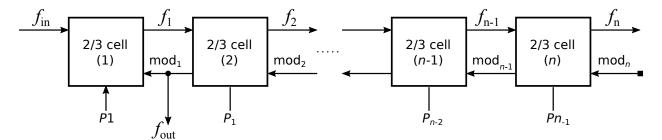

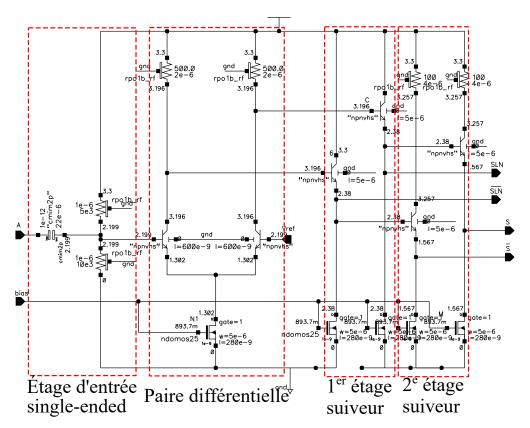

| 3  | Synt  | hèse pa | r division fractionnaire régénérative                | 117   |

|    | 3.I   | Introdu | ection                                               | 117   |

|    | 3.II  | Présent | tation et démarche                                   | 118   |

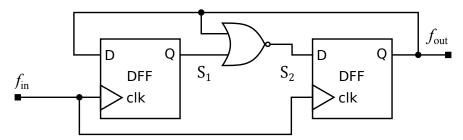

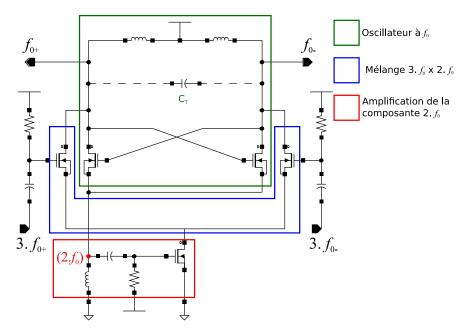

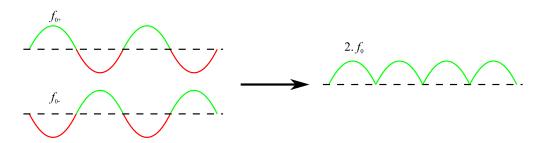

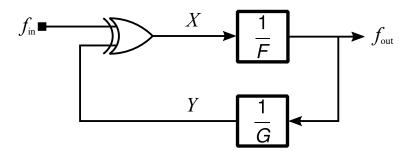

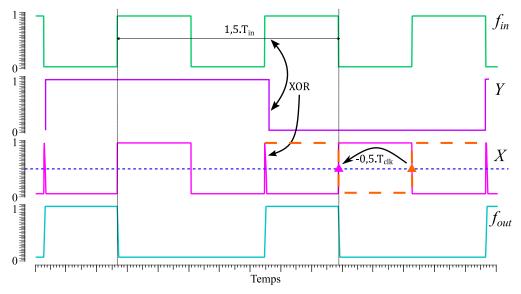

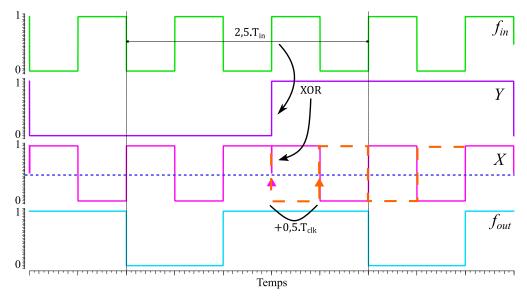

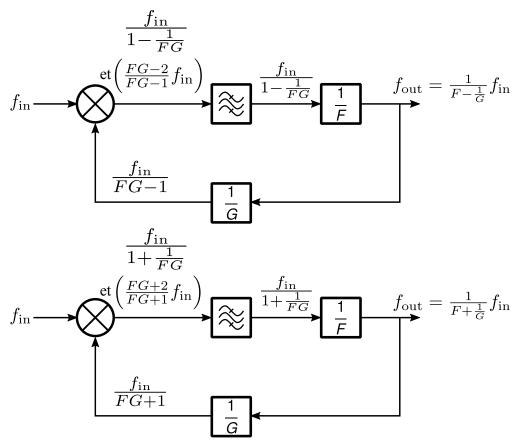

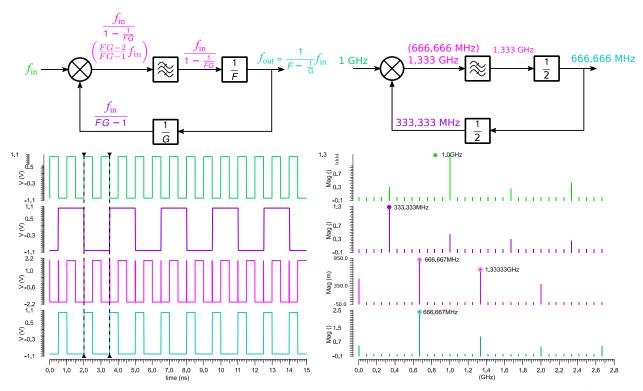

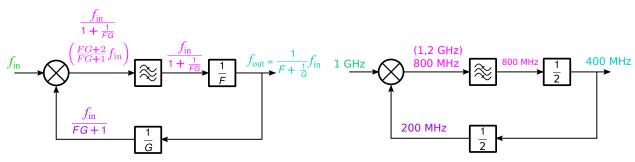

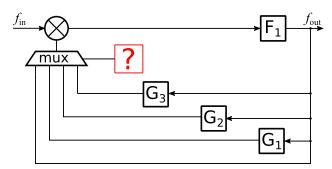

|    |       | 3.II.1  | Approche avec un XOR en entrée                       | 119   |

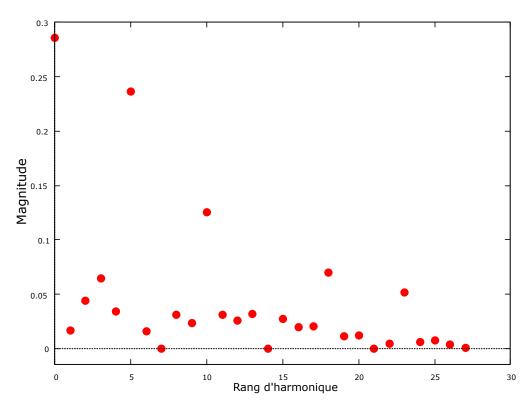

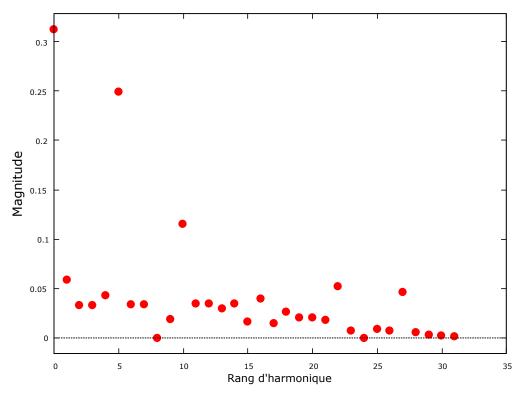

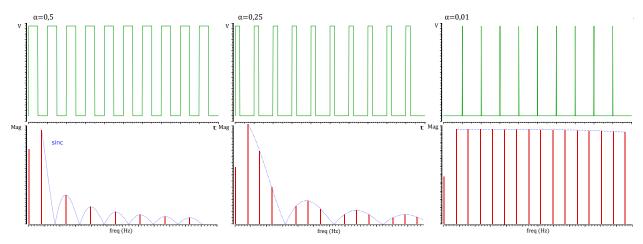

|    |       | 3.II.2  | Spectre du diviseur fractionnaire                    | 120   |

|    |       | 3.II.3  | Approche avec un mélangeur en entrée                 | 125   |

|    | 3.III | Divise  | ırs régénératifs fractionnaires par 1,25, 2,5 et 4,5 | 129   |

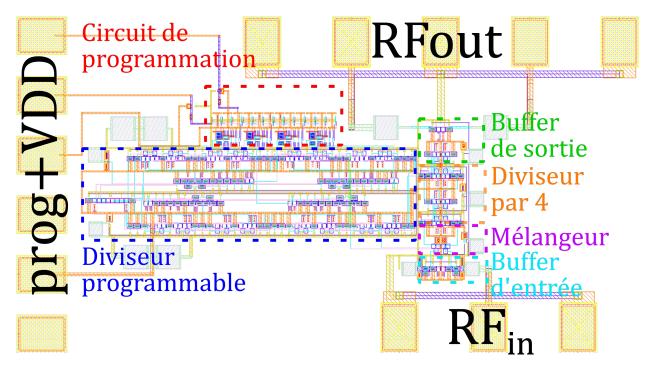

|    |       | 3.III.1 | Présentation                                         | 129   |

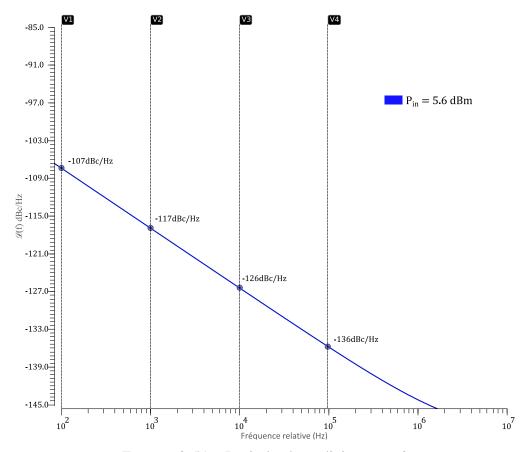

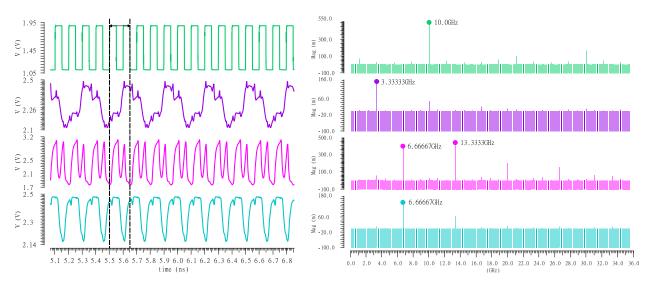

|    |       | 3.III.2 | Conception et résultat de simulation                 | 130   |

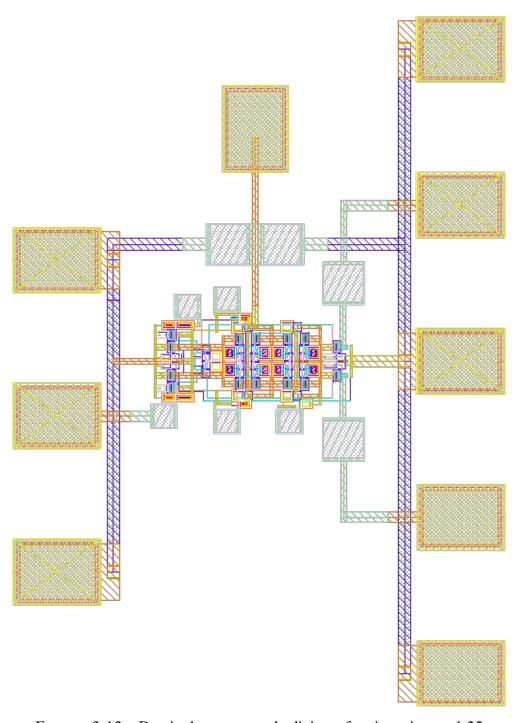

|    |       | 3.III.3 | Dessin des masques du circuit                        | 132   |

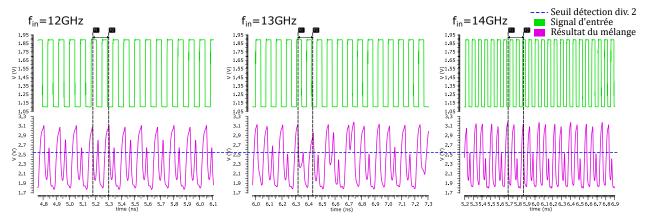

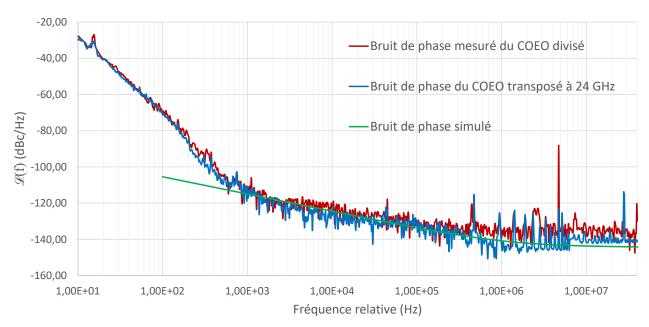

|    |       | 3.III.4 | Protocole et résultats de mesures                    | 132   |

|    | 3.IV  | Divise  | ır régénératif fractionnaire programmable            | 140   |

|    |       | 3.IV.1  | Présentation                                         | 140   |

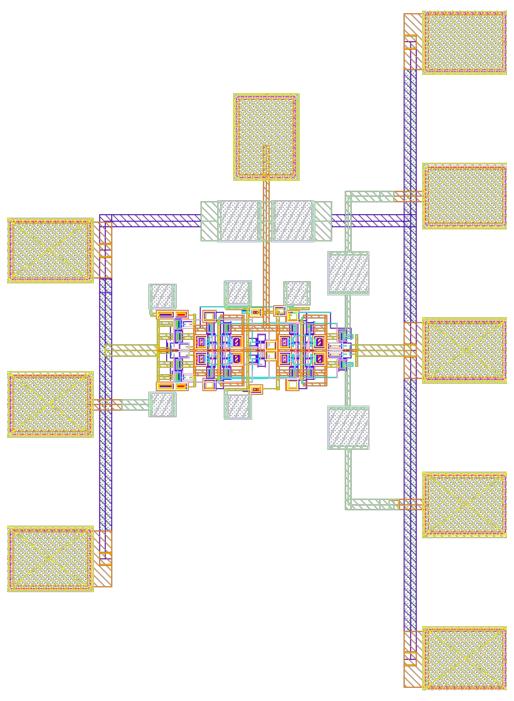

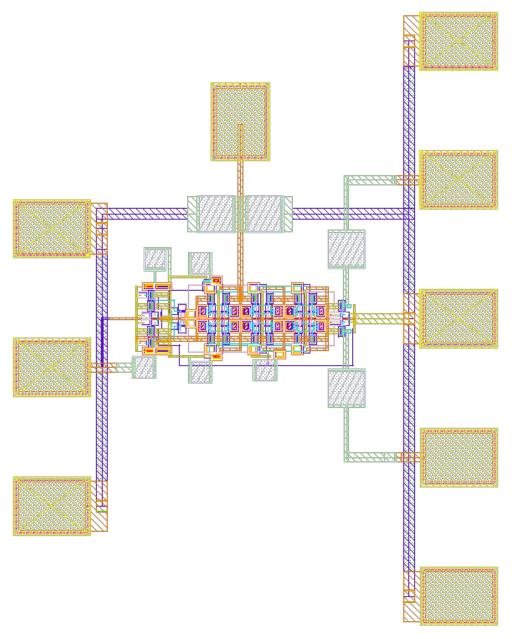

|    |       | 3.IV.2  | Conception et résultat de simulation                 | 140   |

|    |       | 3.IV.3  | Dessin des masques du circuit                        | 143   |

|    |       | 3.IV.4  | Protocole et résultats de mesures                    | 144   |

|    | Conc  | clusion |                                                      | 148   |

| Co | nclus | ion gén | ér <mark>ale</mark>                                  | 151   |

| Pe | rspec | tives   |                                                      | 153   |

| An | nexes | S       |                                                      | 155   |

|    | I     | Transp  | osition et comparaison avec la technologie BiCMOS55  | 155   |

|    |       | I.1     | Diviseur numérique par 2 VCCS                        | 155   |

|    |       | I.2     | Diviseur numérique par 3                             | 156   |

|    |       | I.3     | Diviseur numérique par 10 CMOS                       | 157   |

|    |       | I.4     | Diviseur par 3 ILFD                                  | 158   |

|    |       | I.5     | Diviseur par 3 avec second harmonique régénératif    | 158   |

## Introduction générale

Les signaux hyperfréquences (ou micro-ondes) sont les ondes électromagnétiques dont la gamme de fréquence généralement admise est comprise entre 1 GHz et 300 GHz [1]. Les gammes de fréquence auxquelles ce qualificatif est appliqué ne sont pas définies précisément et peuvent varier d'un auteur à l'autre [2-4]. Cette gamme hyperfréquence est comprise entre celle des radiofréquences et celle des infrarouges dans le spectre électromagnétique [5, 6]. Ces signaux jouent un rôle indispensable dans le domaine des télécommunications, que ce soit pour la téléphonie mobile, la télévision, le Wi-Fi [7] ou encore la transmission satellitaire [8, 9]. Pour l'ensemble de ces applications omniprésentes dans la société actuelle, ce sont les signaux hyperfréquences qui vont servir de porteuses pour transmettre l'information sur de plus ou moins longues distances.

Les signaux hyperfréquences sont également utilisés dans le domaine de la radiodétection pour détecter la présence, la localisation ou même la vitesse d'un objet [10, 11]. Pour cela, la propriété de réflexion des ondes électromagnétiques est exploitée : lorsqu'une onde électromagnétique change de milieu ou rencontre une surface, l'onde est alors, au moins partiellement, réfléchie. Ce signal réfléchi peut être mesuré et analysé pour déterminer la présence d'un objet, et même calculer sa vitesse ou la distance à laquelle il se trouve.

Enfin, un dernier domaine qui illustre l'importance des signaux hyperfréquences est celui de la médecine. Ils sont notamment utilisés pour la détection de tumeurs cancéreuses [12, 13] et pour le traitement de certaines pathologies [14].

Les signaux hyperfréquences sont donc omniprésents dans le monde qui nous entoure, au point que cela en devienne problématique. En effet, même si le spectre des hyperfréquences s'étale de 1 GHz à 300 GHz, certaines fréquences sont plus adaptées pour certaines applications, et il est généralement plus simple technologiquement de travailler à basse fréquence, si bien que beaucoup d'applications utilisent encore des fréquences inférieures à 6 GHz [15-17]. Ainsi, la bande de fréquence de 1 à 6 GHz, appelée « Sub-6 », est particulièrement prisée en grande partie en raison des caractéristiques de propagation des signaux à ces fréquences. En effet, dans cette bande de fréquence, les ondes peuvent toujours se propager à travers certaines surfaces, notamment les murs, ce qui peut être indispensable pour certaines applications. De plus, les signaux de cette bande de fréquence ne subissent pas d'atténuation importante par temps de pluie, contrairement à des si-

gnaux de fréquence plus élevée [18].

En outre, utiliser la même fréquence pour différentes applications peut générer des problèmes d'interférences [19]. Il faut donc répartir les différentes gammes de fréquences entre les différents domaines d'utilisation et mettre en place des normes pour que les communications puissent s'établir sans se perturber mutuellement. Pour l'ensemble de ces raisons, le domaine des hyperfréquences fait actuellement face à un encombrement important des bandes de fréquence inférieures à 6 GHz [20] et un de ses défis majeurs sera de trouver des solutions à cette saturation. Une des solutions étudiées est l'utilisation de gammes de fréquences plus élevées [21-23]. Cependant, cela demande de relever certains défis technologiques liés notamment à la génération de références hyperfréquences. Effectivement, la méthode de génération de signaux hyperfréquences la plus répandue actuellement est la boucle à verrouillage de phase (ou Phase locked-loop) (PLL) [24]. Elle réalise une multiplication d'une fréquence de référence basse par un certain facteur N. Mais il y a un inconvénient lié à cette méthode de synthèse : dans la plupart des applications, il est primordial de conserver autant que possible la qualité du signal hyperfréquence, c'est-à-dire sa pureté spectrale. Une des grandeurs physiques qui permet d'évaluer cette pureté spectrale est le bruit de phase [25]. Or dans le cas d'une multiplication idéale d'une fréquence par un facteur N, son bruit de phase théorique augmente proportionnellement à  $N^2$ , soit de  $20 \cdot \log N$  en dB [26, 27]. À cette inévitable augmentation du bruit de phase vient s'ajouter le bruit des différents éléments du système de synthèse de fréquence. Synthétiser une fréquence élevée en multipliant une référence de fréquence basse par un facteur important impacte donc négativement la pureté du signal généré de façon inéluctable. Les oscillateurs générant la fréquence basse de référence sont généralement des oscillateurs à quartz, les plus répandus étant ceux de type Oven Controlled X-tal(Crystal) Oscillator (OCXO) qui fournissent des signaux de fréquences de l'ordre de la dizaine à quelques centaines de mégahertz [28-34].

Une autre technologie d'oscillateurs, appelée Surface Acoustic Wave (SAW) tend à se démocratiser. Ils génèrent des signaux de fréquences compris entre quelques centaines de mégahertz à plusieurs gigahertz à haute pureté spectrale [35-37]. Enfin, d'autres méthodes de génération à haute pureté spectrale sont également utilisées comme les Bulk Acoustic Wave (BAW) [38-40] ou les oscillateurs à saphir [41-43].

Quoi qu'il en soit, concernant les oscillateurs les plus communs, c'est-à-dire les OCXO, des facteurs multiplicatifs de l'ordre de plusieurs centaines doivent être mis en œuvre pour atteindre des fréquences dépassant les 6 GHz, ce qui impacte négativement le bruit de phase.

Pour cette raison, cette thèse vise à étudier les perspectives et approfondir les recherches sur la méthode de synthèse de fréquence basée non plus sur la multiplication d'une référence basse mais sur la division d'une référence haute. Elle est intégrée dans le cadre du projet Division de Fréquence d'Oscillateurs Opto-éLectroniques (DIFOOL) débuté en mars 2016, qui portait sur la

synthèse de fréquence par division de oscillateur opto-électronique couplé (ou Coupled OptoElectronic Oscillator) (COEO). Le projet DIFOOL s'est cependant terminé prématurément au début de l'année 2018, soit un an et demi après le début de la thèse, suite à la liquidation judiciaire de l'une des entreprises partenaires, ce qui a fortement impacté la thèse : le projet devait financer les runs technologiques des circuits conçus. Un deuxième projet, Oscillateurs opto-éLectroniques dI-Visés Électroniquement (OLIVE), devait prendre la suite du projet DIFOOL mais n'a finalement démarré qu'en début d'année 2020, la plupart des runs présentés dans la thèse se sont donc faits sur les finances de mon équipe de recherche, limitant de fait les surfaces envisageables pour les différents circuits conçus.

Les partenaires du projet DIFOOL étaient le Laboratoire Aimé Cotton, Thalès Alenia Space, Thales Research and Technology, OSAT et enfin le LAAS où j'ai réalisé ma thèse. Une partie du projet était orientée sur l'étude des COEO, qui sont des oscillateurs haute fréquence à haute pureté spectrale, et une autre partie concerne la division faible bruit de ces oscillateurs, sur laquelle porte cette thèse.

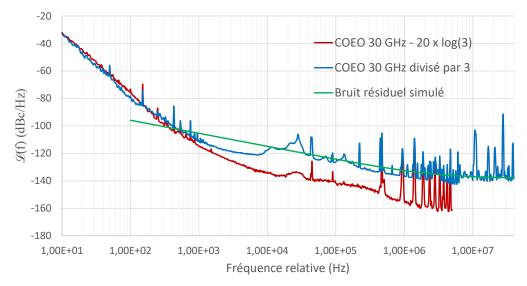

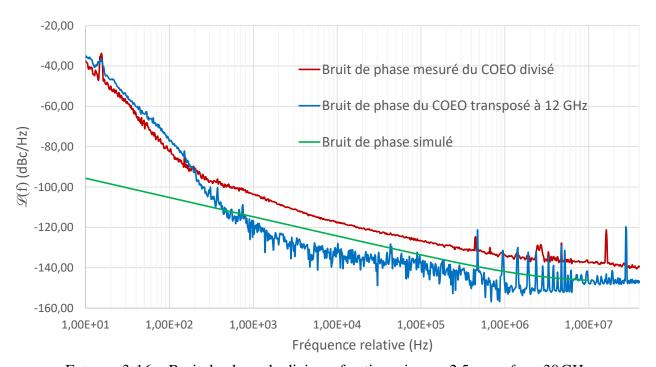

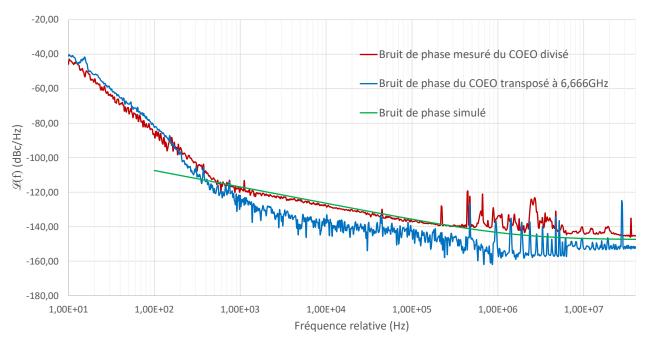

Deux COEO générant des signaux à 30 GHz [44] et à 10 GHz, conformément au cahier des charges du projet DIFOOL, sont utilisés comme références pour les diviseurs présentés dans ce manuscrit. Ainsi, contrairement à une PLL où un facteur de l'ordre de la centaine est nécessaire pour arriver aux 6 GHz au-delà desquels l'encombrement en fréquence nous amène à travailler, une simple division par 5 du COEO à 30 GHz permet déjà d'atteindre les 6 GHz.

À partir de la référence de fréquence à 30 GHz, l'objectif du projet était alors d'être capable de générer plusieurs fréquences inférieures à 30 GHz et éventuellement aussi basse que 1 GHz pour comparer les performances du signal synthétisé avec celles d'un signal généré par un oscillateur de référence standard à cette fréquence. Cela signifie qu'à fréquence équivalente, le bruit de phase du COEO transposé à 1 GHz doit être meilleur que ceux de ces oscillateurs à 1 GHz. Nous avons notamment étudié la division fixe par trois à 30 GHz, puisque nous travaillons également avec un COEO à 10 GHz, cela nous permettait ensuite de mutualiser les méthodes de synthèse en dessous de 10 GHz.

Ces signaux synthétisés à partir de la référence à 30 GHz doivent en conserver autant que possible la pureté spectrale. Pour cela, nous travaillons sur la conception de diviseurs à très faible bruit de phase résiduel tout en offrant la possibilité de réaliser des rapports de division fractionnaires et mêmes programmables. En effet, des applications telles que la 5G en France utiliseront massivement à terme des fréquences proches de 26 GHz, donc du même ordre de grandeur que le COEO à 30 GHz utilisé ici, et d'autres proches de 3,5 GHz [45]. Par conséquent, un diviseur à haute pureté spectrale, programmable et fractionnaire permettrait d'avoir accès à l'ensemble des fréquences nécessaires en utilisant la fréquence la plus élevée en tant que référence. Un des objectifs de cette thèse est donc d'étudier les performances de différentes méthodes de division de

fréquence et de proposer des solutions performantes et innovantes basées sur de la division plutôt que de la multiplication.

Ce document s'articule autour de trois chapitres : dans le premier, les principales méthodes de synthèses hyperfréquences existantes et les caractéristiques intrinsèques de chacune sont présentées, puis un état de l'art est réalisé. Un des deux sujets majeurs abordé au cours de ce chapitre est celui de la PLL, méthode de synthèse à laquelle nous souhaitons proposer une alternative. Le deuxième sujet majeur traité dans ce chapitre est la synthèse par division de COEO, comprenant une présentation de différentes méthodes de division.

Dans un deuxième chapitre, nous présentons les différents diviseurs de fréquences entiers que nous avons conçus et leurs résultats de simulations et de mesures. Ils sont présentés dans deux catégories distinctes : les diviseurs numériques et les diviseurs analogiques. Ce sont pour commencer des diviseurs relativement simples, qui serviront de base pour des diviseurs plus complexes que nous présenterons par la suite. Ils permettent d'estimer les meilleures performances que l'on peut espérer obtenir avec des diviseurs car leur simplicité bénéficie généralement au bruit de phase. Les différents choix de conception et de dimensionnement de ces diviseurs sont expliqués dans ce chapitre et les résultats de simulations et de mesures y sont discutés.

Enfin, dans un troisième et dernier chapitre, le développement et la conception d'une topologie innovante de diviseur régénératif fractionnaire sont présentés. Basée sur le principe du diviseur régénératif de Miller, nous avons mis au point une topologie utilisant des diviseurs numériques fixes dans un premier temps pour évaluer les performances, notamment en bruit de phase, de ce type de diviseur. Ayant obtenu des résultats convaincants, une version avec un diviseur programmable a par la suite été implémentée. Il s'agit, à notre connaissance, du premier diviseur régénératif fractionnaire programmable réalisé ainsi. La conception et les résultats de mesures de ces différents circuits sont présentés au cours de ce chapitre.

### **Bibliographie**

- [1] IEEE Standard Letter Designations for Radar-Frequency Bands. IEEE. URL: https://ieeexplore.ieee.org/document/8999849/(cf. p. 1).

- [2] R. SORRENTINO et G. BIANCHI. *Microwave and RF Engineering*. 2010. URL: https://nbn-resolving.org/urn:nbn:de:101:1-201410313207 (cf. p. 1).

- [3] NATIONAL ASSOCIATION OF BROADCASTERS, E. A. WILLIAMS et G. A. JONES. *Engineering handbook*. Amsterdam: Focal Press, 2007 (cf. p. 1).

- [4] R. T. HITCHCOCK. *Radio-Frequency and Microwave Radiation*. Avec la coll. d'A. I. H. ASSOCIATION. 3rd ed. Nonionizing Radiation Guide Series. Fairfax, Va: American Industrial Hygiene Association, 2004. 51 p. (cf. p. 1).

- [5] ANFR. Qu'est-ce que le spectre ? 18 juin 2020. URL : https://www.anfr.fr/l-anfr/quest-ce-que-le-spectre/(cf. p. 1).

- [6] Spectre Électromagnétique Commission Européenne. URL: https://ec.europa.eu/health/scientific\_committees/opinions\_layman/artificial-light/fr/glossaire/pqrs/spectre-electromagnetique.htm (cf. p. 1).

- [7] Microwave Link Networks ETHW. URL: https://ethw.org/Microwave\_Link\_Networks (cf. p. 1).

- [8] V. AKAN et E. YAZGAN. "Antennas for Space Applications: A Review". In: Advanced Radio Frequency Antennas for Modern Communication and Medical Systems (18 août 2020).

URL: https://www.intechopen.com/books/advanced-radio-frequency-antennas-for-modern-communication-and-medical-systems/antennas-for-space-applications-a-review (cf. p. 1).

- [9] Microwave Applications | 2018-08-01 | Microwave Journal. URL: https://www.microwavejournal.com/articles/29922-microwave-applications?page=1 (cf. p. 1).

[10] S. DILL et al. "A Drone Carried Multichannel Synthetic Aperture Radar for Advanced Buried Object Detection". In: 2019 IEEE Radar Conference (RadarConf). 2019 IEEE Radar Conference (RadarConf19). Boston, MA, USA: IEEE, avr. 2019, p. 1-6. URL: https://ieeexplore.ieee.org/document/8835814/(cf. p. 1).

- [11] P. SINGH et al. "Motion Detection and Tracking Using Microwave Sensor for Eliminating Illegal Mine Activities". In: 2018 3rd International Conference on Microwave and Photonics (ICMAP). 2018 3rd International Conference on Microwave and Photonics (ICMAP). Dhanbad: IEEE, fév. 2018, p. 1-5. URL: https://ieeexplore.ieee.org/document/8354484/ (cf. p. 1).

- [12] M. ELSDON et al. "Early Stage Breast Cancer Detection Using Indirect Microwave Holography". In: 2006 European Microwave Conference. 2006 European Microwave Conference. Manchester, UK: IEEE, sept. 2006, p. 1256-1259. URL: http://ieeexplore.ieee.org/document/4058057/(cf. p. 1).

- [13] M. PERSSON et al. "Microwave Based Diagnostics and Treatment in Practice". In: 2013 IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-BIO). 2013 IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-BIO). Singapore, Singapore: IEEE, déc. 2013, p. 1-3. URL: http://ieeexplore.ieee.org/document/6756231/ (cf. p. 1).

- [14] G. BEALE. "Improving Patient Safety in Microwave Ablation Treatments". In: 2014 IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-Bio2014). 2014 IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-BIO). London, United Kingdom: IEEE, déc. 2014, p. 1-1. URL: http://ieeexplore.ieee.org/document/7032421/ (cf. p. 1).

- [15] 5G-The Microwave Perspective | Analog Devices. URL: https://www.analog.com/en/technical-articles/5g-the-microwave-perspective.html (cf. p. 1).

- [16] M. ZADA, I. A. SHAH et H. YOO. "Integration of Sub-6-GHz and Mm-Wave Bands With a Large Frequency Ratio for Future 5G MIMO Applications". In: *IEEE Access* 9 (2021), p. 11241-11251 (cf. p. 1).

- [17] Spectrum of Interest Spans Sub-6-GHz Cellular Frequencies to mmWave Radar. Evaluation Engineering. 30 juin 2020. URL: https://www.evaluationengineering.com/applications/rf-microwave-test/article/21140649/spectrum-of-interest-spans-sub6ghz-cellular-frequencies-to-mmwave-radar (cf. p. 1).

[18] 6GHz Archives. Microwave Link. URL: https://www.microwave-link.com/tag/6ghz/(cf. p. 2).

- [19] NASA. Spectrum 101 An Introduction to National Aeronautics and Space Administration Spectrum Management. 2016. URL: https://www.nasa.gov/sites/default/files/atoms/files/spectrum\_101.pdf (cf. p. 2).

- [20] G. ZHOU, J. A. STANKOVIC et S. H. SON. "Crowded Spectrum in Wireless Sensor Networks". In: (), p. 5 (cf. p. 2).

- [21] T. WANG et al. "Spectrum Analysis and Regulations for 5G". In: 5G Mobile Communications (2017), p. 27-50. URL: https://link-springer-com-s.docadis.ups-tlse.fr/chapter/10.1007/978-3-319-34208-5\_2 (cf. p. 2).

- [22] E. COMMISSION. 5G for Europe: An Action Plan. URL: http://ec.europa.eu/newsroom/dae/document.cfm?doc\_id=17131 (cf. p. 2).

- [23] F. Khan et Z. Pi. "mmWave Mobile Broadband (MMB): Unleashing the 3GHz;300GHz Spectrum". In: 34th IEEE Sarnoff Symposium. 2011 34th IEEE Sarnoff Symposium. Princeton, NJ, USA: IEEE, mai 2011, p. 1-6. URL: http://ieeexplore.ieee.org/document/5876482/(cf. p. 2).

- [24] B. TARANTO. Bruno TARANTO RF Phase-Locked Loop (PLL) Synthesizer Loop Bandwidth Optimization. 19 mai 2020 (cf. p. 2).

- [25] "IEEE Standard Definitions of Physical Quantities for Fundamental Frequency and Time Metrology—Random Instabilities". In: *IEEE Std Std 1139-2008* (fév. 2009), p. c1-35 (cf. p. 2).

- [26] J. CHEN et al. "Does LO Noise Floor Limit Performance in Multi-Gigabit Millimeter-Wave Communication?" In: *IEEE Microwave and Wireless Components Letters* 27.8 (août 2017), p. 769-771. URL: http://ieeexplore.ieee.org/document/7987033/(cf. p. 2).

- [27] I. THOMPSON et P. BRENNAN. "Phase Noise Contribution of the Phase Frequency Detector in a Digital PLL Frequency Synthesiser". In: *IEE Proceedings Circuits, Devices and Systems* 150.1 (2003), p. 1. URL: https://digital-library.theiet.org/content/journals/10.1049/ip-cds\_20030221 (cf. p. 2).

- [28] OCXO | Microsemi. URL: https://www.microsemi.com/product-directory/high-reliability-rugged-oscillators/4847-ocxo (cf. p. 2).

- [29] Oven Controlled OCXO Oscillators | Farnell UK. URL: https://uk.farnell.com/c/crystals-oscillators/oscillators/oven-controlled-ocxo-oscillators (cf. p. 2).

[30] OCXO Oven Controlled Crystal Oscillators - Microchip Technology | Mouser. URL: https://www.mouser.fr/new/microchip/vectron-ocxo-oscillators/(cf. p. 2).

- [31] N. F. CONTROLS. Low Phase Noise 1 GHz OCXO in 36x27 Mm "Europack" (Datasheet) (cf. p. 2).

- [32] K. IRIE et al. "High Stability Ultra-Miniature Size OCXO Operating within Wide Temperature Range: Using ASIC with Built-in Oven for OCXO". In: 2020 Joint Conference of the IEEE International Frequency Control Symposium and International Symposium on Applications of Ferroelectrics (IFCS-ISAF). 2020 Joint Conference of the IEEE International Frequency Control Symposium and International Symposium on Applications of Ferroelectrics (IFCS-ISAF). Keystone, CO, USA: IEEE, juill. 2020, p. 1-4. URL: https://ieeexplore.ieee.org/document/9234922/ (cf. p. 2).

- [33] R. BORODITSKY et J. GOMEZ. "Micro-Miniature, SMD, Ultra Low Phase Noise, High Frequency OCXO". In: 2014 European Frequency and Time Forum (EFTF). 2014 European Frequency and Time Forum (EFTF). Neuchatel, Switzerland: IEEE, juin 2014, p. 360-362. URL: https://ieeexplore.ieee.org/document/7331510 (cf. p. 2).

- [34] M. B. REDDY et al. "High Frequency OCXO for Space Applications". In: 2012 IEEE International Frequency Control Symposium Proceedings. 2012 IEEE International Frequency Control Symposium (FCS). Baltimore, MD: IEEE, mai 2012, p. 1-5. URL: https://ieeexplore.ieee.org/document/6243649/ (cf. p. 2).

- [35] SAW (Surface Acoustic Wave) Oscillators. URL: https://www.rfglobalnet.com/doc/saw-surface-acoustic-wave-oscillators-0001 (cf. p. 2).

- [36] RF/Microwave SAW Oscillators | Microsemi. URL: https://www.microsemi.com/product-directory/rf-microwave-saw-products/3880-rf-microwave-saw-oscillators#parametric-search (cf. p. 2).

- [37] High Frequency Ultra Low Phase Noise SAW Oscillator VS-401 VCSO. URL: https://www.vectron.com/products/vcso/vs-401.htm (cf. p. 2).

- [38] E. MARIGO et al. "Monolithic BAW Oscillator with Conventional QFN Packaging". In: 2019 Joint Conference of the IEEE International Frequency Control Symposium and European Frequency and Time Forum (EFTF/IFC). 2019 Joint Conference of the IEEE International Frequency Control Symposium an European Frequency and Time Forum (EFTF/IFC). Orlando, FL, USA: IEEE, avr. 2019, p. 1-2. URL: https://ieeexplore.ieee.org/document/8855999/ (cf. p. 2).

[39] G. PILLAI et al. "3-GHz BAW Composite Resonators Integrated with CMOS in a Single-Chip Configuration". In: 2016 IEEE International Frequency Control Symposium (IFCS). 2016 IEEE International Frequency Control Symposium (IFCS). New Orleans, LA, USA: IEEE, mai 2016, p. 1-4. URL: http://ieeexplore.ieee.org/document/7563593/(cf. p. 2).

- [40] P. GUILLOT et al. "A 2GHz 65nm CMOS Digitally-Tuned BAW Oscillator". In: 2008 15th IEEE International Conference on Electronics, Circuits and Systems. 2008 15th IEEE International Conference on Electronics, Circuits and Systems (ICECS 2008). St. Julien's, Malta: IEEE, août 2008, p. 722-725. URL: https://ieeexplore.ieee.org/document/4674955 (cf. p. 2).

- [41] E. VAILLANT et al. "Frequency Synthesis from Cryogenic Sapphire Oscillator". In: IEEE, avr. 2016, p. 1-4. URL: http://ieeexplore.ieee.org/document/7477773/ (cf. p. 2).

- [42] N. NAND et al. "Radio Frequency Signals Synthesised from Independent Cryogenic Sapphire Oscillators". In: *Electronics Letters* 50.4 (13 fév. 2014), p. 294-295. URL: http://digital-library.theiet.org/content/journals/10.1049/el.2013.3481 (cf. p. 2).

- [43] N. R. NAND et al. *Ultra Stable and Very Low Noise Signal Source Using a Cryocooled Sapphire Oscillator for VLBI*. 20 avr. 2011. arXiv:1104.4146 [astro-ph, physics:physics]. URL: http://arxiv.org/abs/1104.4146 (cf. p. 2).

- [44] A. Ly et al. "Highly Spectrally Pure 90-GHz Signal Synthesis Using a Coupled Optoelectronic Oscillator". In: *IEEE Photonics Technology Letters* 30.14 (15 juill. 2018), p. 1313-1316. URL: https://ieeexplore.ieee.org/document/8376022/ (cf. p. 3).

- [45] Tableau de bord des expérimentations 5G en France. Arcep. URL: https://www.arcep.fr/cartes-et-donnees/nos-publications-chiffrees/experimentations-5g-en-france/tableau-de-bord-des-experimentations-5g-en-france.html (cf. p. 3).

## Chapitre 1

## Méthodes de synthèse de références hyperfréquences

#### Introduction

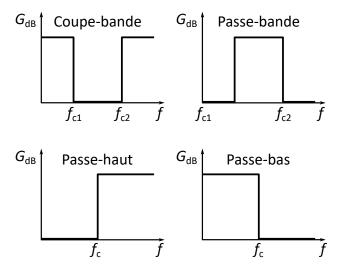

Nous présentons dans cette première partie un état des lieux des principales méthodes de synthèses de signaux de références hyperfréquences, puis un état de l'art est établi.

Dans une première partie, nous discutons de la synthèse par multiplication de fréquence qui, dans le domaine des hyperfréquences, est le plus souvent réalisée avec une PLL. Nous présentons son principe de fonctionnement ainsi que les éléments qui la constituent. Nous pointons en particulier les inconvénients que l'on souhaite contourner en changeant d'approche avec la synthèse par division de fréquence.

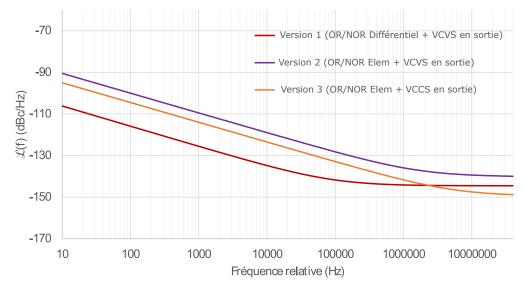

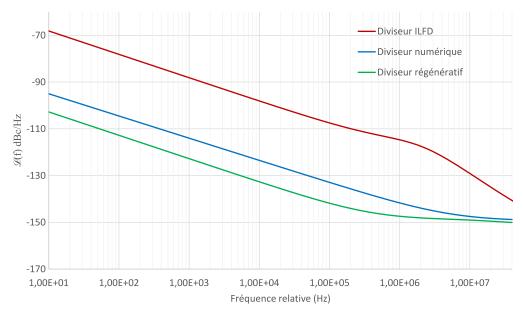

Dans une seconde partie, nous discutons de cette synthèse par division, et nous détaillons plus particulièrement la méthode de synthèse que nous proposons : la division de fréquence de COEO. Différentes topologies de diviseurs faisant partie de trois grandes familles sont présentées. Ces familles sont : les diviseurs numériques, les diviseurs de fréquence à verrouillage par injection (ou Injection-Locked Frequency Dividers) (ILFD) et les diviseurs régénératifs. Nous déterminons dans ce chapitre les avantages et inconvénients de chacune de ces familles au regard de nos objectifs avec, par conséquent, comme contrainte principale, le bruit de phase. D'autres caractéristiques vis-à-vis des objectifs du projet sont également à considérer, notamment la programmabilité et la possibilité de mettre en œuvre des rapports fractionnaires.

#### 12

#### 1.I La synthèse par multiplication de fréquence

#### 1.I.1 Principe

Comme son nom l'indique, la synthèse par multiplication de fréquence consiste à générer, à partir d'une référence de fréquence basse, un multiple de cette fréquence. La méthode la plus répandue pour la multiplication de fréquence est la PLL. La fréquence de référence utilisée dans les PLL est généralement issue d'un oscillateur à haute pureté spectrale, les plus répandus étant les oscillateurs à quartz qui génèrent des fréquences de l'ordre de la dizaine à quelques centaines de mégahertz [1-7].

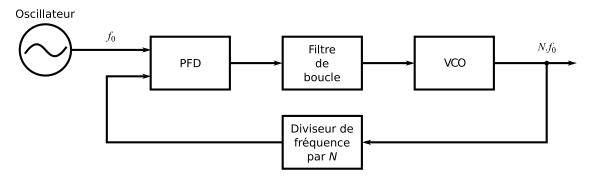

La PLL, utilisée comme un synthétiseur de fréquence dont le schéma de principe est donné sur la figure 1.1, est constituée d'un détecteur phase/fréquence (ou Phase/Frequency Detector) (PFD), d'un filtre de boucle, d'un oscillateur contrôlé en tension (ou Voltage Controlled Oscillator) (VCO) et d'un diviseur de fréquence [8].

FIGURE 1.1 – Schéma de principe de la PLL

La PLL est un système qui asservit la fréquence de sortie à celle d'entrée, ainsi, le principe qui régit le fonctionnement d'une PLL est de comparer les phases, et éventuellement la fréquence, du signal d'entrée et du signal de sortie dont la fréquence a été divisée par le diviseur de contre-réaction. Tant que ces deux signaux ne sont pas en phase, le PFD va, au moyen d'une pompe de charge et d'un filtre de boucle, faire varier la tension de commande du VCO pour modifier la fréquence de sortie de telle sorte que, une fois divisée par le diviseur de contre-réaction, elle tende vers la fréquence d'entrée. On parle d'asservissement de phase. La PLL tend alors naturellement vers un état d'équilibre où les deux signaux en entrée du PFD sont en phase, la PLL est alors verrouillée [8, 9].

Pour décrire plus en détail le fonctionnement de la PLL, le comparateur, au moyen d'une pompe de charge [10], injecte ou draine des charges en fonction du déphasage entre les deux signaux à ses entrées. Le filtre de boucle permet de déterminer les caractéristiques de l'asservissement de phase : amortissement, bande passante... Il atténue également les produits d'intermodulation indé-

sirables issus du PFD. Ces produits d'intermodulation sont des composantes fréquentielles parasites apparaissant lors de phénomènes non-linéaires. Le VCO génère un signal dont la fréquence est proportionnelle à la tension continue à l'entrée du VCO et qui, lorsque la PLL est verrouillée, est le signal de sortie dont la fréquence sera le multiple souhaité de la fréquence d'entrée. Enfin, le diviseur de fréquence génère une fréquence de sortie inférieure à sa fréquence d'entrée [11], il peut être entier ou fractionnaire. C'est lui qui fixe le rapport de multiplication de la PLL, puisqu'en divisant la fréquence du signal de sortie par un certain rapport de façon à ce qu'elle soit la même que la fréquence d'entrée, le rapport du diviseur de la chaîne de contre-réaction est égal au facteur de multiplication de la PLL.

Soit  $f_{\text{ref}}$  la fréquence de référence générée par l'oscillateur de référence et N la valeur du diviseur de la boucle de contre-réaction, la fréquence  $f_{\text{out}}$  du signal synthétisé par la PLL est :

$$f_{\text{out}} = N \times f_{\text{ref}} \tag{1.1}$$

La PLL permet donc de multiplier une fréquence de référence par le facteur du diviseur. Il est possible de réaliser une multiplication soit entière soit fractionnaire, en fonction du type de diviseur utilisé dans la boucle de contre-réaction.

Un des défauts de la PLL est de présenter une bande passante limitée. Elle présente plusieurs plages de fonctionnement. Tout d'abord la plage de capture, qui comprend les fréquences pour lesquelles la PLL passe d'un état non-verrouillé à verrouillé. Ensuite la plage de maintien, qui correspond aux fréquences pour lesquelles une PLL déjà verrouillée reste verrouillée. Par définition, la plage de maintien englobe la plage de capture. Lorsqu'une PLL sort de sa plage de maintien, un phénomène de décrochage est observé, c'est-à-dire qu'elle se déverrouille, et le VCO retrouve sa fréquence libre. Deux causes peuvent être à l'origine de ce décrochage : soit une saturation du VCO, soit une saturation du PFD. Concernant le VCO, la plage de maintien correspond à la plage de fonctionnement du VCO, donc la plage où il peut fournir une fréquence proportionnelle à sa tension d'entrée. Pour ce qui est du PFD, si les deux fréquences en entrée deviennent trop différentes l'une de l'autre, il ne peut pas drainer ou fournir suffisamment de charges pour que le VCO corrige cette différence, la PLL décroche alors.

Maintenant que le principe de fonctionnement de la PLL a été présenté, nous allons introduire une notion importante pour la suite : le bruit de phase dans la PLL.

#### 1.I.2 Bruit de phase dans la PLL

Comme évoqué dans l'introduction générale, le bruit de phase est une des grandeurs physiques permettant d'évaluer la pureté spectrale d'un signal. Nous l'exprimons en dBc/Hz puisqu'il exprime un rapport de puissance entre la puissance du signal à la porteuse (« carrier » en anglais d'où

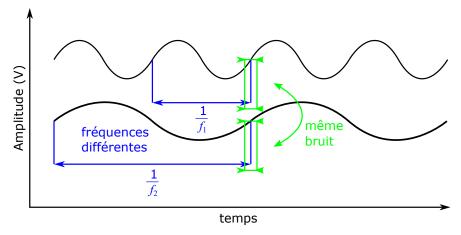

FIGURE 1.2 – Illustration des grandeurs impliquées dans le calcul du bruit de phase

le dBc) et la puissance du signal dans une bande de 1 Hz relativement à la porteuse, comme illustré sur la figure 1.2. Pour préciser cette distance à la porteuse, nous utilisons la notation suivante pour exprimer un bruit de phase : XdBc/Hz@YHz avec X la valeur de bruit de phase et Y la distance à la porteuse.

On voit également sur la figure 1.2 qu'il y a deux bandes latérales symétriques de part et d'autre de la porteuse. Le bruit de phase peut être exprimé en fonction d'une seule (Single-SideBand (SSB)) ou des deux bandes latérales (Double-SideBand (DSB)). La définition IEEE du bruit de phase est celle du bruit de phase SSB, c'est donc celle-ci que nous utilisons par la suite. Il est également important de comprendre qu'un bruit de phase est toujours donné en fonction de la fréquence du signal et de la distance à celle-ci, comme on peut le comprendre en regardant la figure 1.2 : le bruit de phase proche de la porteuse n'est pas le même que celui loin de la porteuse. D'un point de vue temporel, cette dégradation de bruit de phase se traduit en partie par une fluctuation plus importante des fronts par rapport à un front idéal. C'est ce que l'on appelle la gigue ou encore le « jitter » en anglais. Ainsi, même si sur le long terme, la période moyenne reste la même, d'une période à l'autre, le moment où un front a lieu peut varier de manière importante si la gigue est prononcée. Cela impacte grandement la qualité du signal, car pour servir de référence de fréquence, il est important d'avoir une période quasi-identique d'une période à l'autre, et donc d'avoir une gigue la plus faible possible. De plus, la représentation temporelle d'une même gigue pour deux signaux de fréquences différentes, présentée sur la figure 1.3, nous permet de comprendre pourquoi il est important d'exprimer un bruit de phase en donnant la fréquence du signal étudié. En effet, pour la même gigue, le signal de fréquence la plus élevée sera d'autant plus impacté, car la gigue est plus importante par rapport à une période du signal. Avec une période plus grande, la gigue dégrade moins la qualité générale du signal.

FIGURE 1.3 – Illustration d'une gigue équivalente pour deux signaux de fréquences différentes

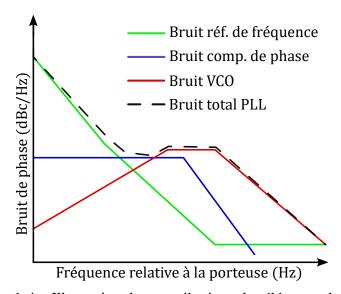

FIGURE 1.4 – Illustration des contributions des éléments de la PLL

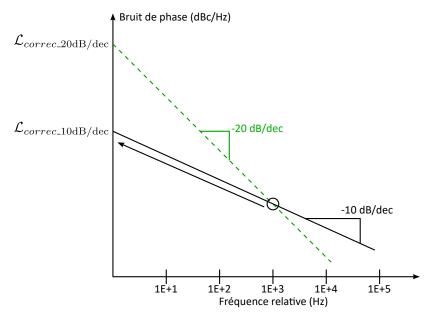

Maintenant que la notion de bruit de phase a été présentée, nous détaillons plus spécifiquement le bruit de phase de la PLL. Lorsque la fréquence d'un signal est multipliée par un facteur N, le bruit de phase est rehaussé de  $20 \times \log N$ . Cette augmentation est inéluctable car nous venons de voir que le calcul du bruit de phase d'un signal est directement lié à la fréquence de ce signal [12]. Il faut ensuite prendre en compte le bruit résiduel des différents éléments de la PLL qui se cumulent et participent à des degrés divers au bruit de phase global [8], comme présenté sur la figure 1.4. C'est sur ce bruit de phase résiduel que des optimisations pourront être apportées, dans une certaine mesure. Ainsi, au plus proche de la porteuse, c'est le bruit de la référence multipliée (donc le bruit de la référence auquel s'ajoute les  $20 \times \log N$ ) qui est prédominant. Très loin de la porteuse, le bruit de la PLL rejoint le plancher de bruit. Entre les deux, les différents éléments de la PLL contribuent plus ou moins au bruit total en fonction de la distance à la porteuse et du design du circuit. Les éléments de la PLL participant majoritairement au bruit de phase sont généralement le PFD et le

Nous allons à présent établir un état de l'art de la PLL afin de comparer les performances de ces dernières.

#### 1.I.3 État de l'art de la PLL

Un état de l'art au sujet des PLL est pertinent puisqu'un des objectifs de la thèse est d'offrir une alternative à celles-ci, et nos résultats sont en partie voués à être comparés à ceux des PLL. La caractéristique la plus étudiée est le bruit de phase puisque l'objectif principal est d'offrir, pour les fréquences très élevées, une alternative plus performante sur cet aspect que les PLL. Nous utiliserons comme facteur de mérite (ou Figure of Merit) (FoM) celui issu de la définition suivante, souvent utilisé dans les publications sur les synthétiseurs de fréquence :

$$FoM = \left| \mathcal{L}(\Delta f_{BdP}) - 20 \cdot \log \left( \frac{f_{ref}}{(\Delta f_{BdP})} \right) + 10 \cdot \log \left( \frac{P_{DC}}{1 \text{mW}} \right) \right|$$

(1.2)

où  $\mathcal{L}(\Delta f_{\text{BdP}})$  représente le bruit de phase mesuré à  $\Delta f_{\text{BdP}}$ , fréquence relative à la porteuse (généralement à 1 MHz pour les PLL). fref représente la fréquence centrale de la plage de fréquences synthétisée par la PLL et P<sub>DC</sub> la puissance dissipée par le circuit. Nous prenons la valeur absolue de la valeur obtenue pour simplifier l'explication, ainsi un FoM plus élevé traduit de meilleures performances. Nous utilisons ce FoM pour la plupart des synthétiseurs de fréquence par la suite car en contrepartie de sa simplicité, il est utilisable pour n'importe quel synthétiseur de fréquence dont on connaît la fréquence synthétisée, la consommation et le bruit de phase. Les performances des PLL peuvent ainsi être comparées avec celles des diviseurs. De plus, le fait de diviser  $f_{\rm ref}$  par  $\Delta f_{\rm BdP}$  permet de comparer plusieurs FoM entre eux, même si le bruit de phase n'est pas mesuré à la même distance de la porteuse (à condition toutefois que le bruit de phase ait une pente de -20 dB/dec). Bien entendu, de par sa simplicité, ce FoM occulte bon nombre d'autres paramètres pertinents de synthétiseurs de fréquences, mais il donne une bonne indication de leurs performances en bruit de phase en fonction de leur consommation, qui sont les deux principaux critères sur lesquels reposent les conceptions de nos diviseurs de fréquences. Les caractéristiques de PLL à facteurs entiers sont présentées dans le tableau 1.1 et celles de PLL à facteurs fractionnaires sont présentées dans les tableaux 1.2 et 1.3. Elles sont toutes relativement récentes, datant de 2013 à 2020, et sont assez représentatives de la diversité existante parmi les PLL, avec des finesses de gravure différentes, des caractéristiques fréquentielles variées et des topologies diverses.

Les points communs que l'on peut cependant noter sont que l'ensemble des PLL présentées ici synthétisent des signaux hyperfréquences, qu'elles sont réalisées en technologie CMOS (sauf une) et qu'elles sont, pour la plupart, présentées comme « faible bruit » dans les articles correspondants.

Références [14] [13] [15] [16] [17] [18]  $6\overline{5}$ Technologie (nm) 28 65 65 65 180 Bande-passante (%) 5,3 5,9 17,2 8 21,7 14 2 Fréquence centrale (GHz) 27,9 2,3 54,65 20,025 10,33 Bruit de phase@1 MHz (dBc/Hz) -96 -105 -125,2-113,5-102-136500 Référence de fréquence (MHz) N/A 2280 45 50 50 -67Référence « Spur » (dBc) N/A N/A -61<-40 N/A Puissance dissipée (mW) 10 23,6 126 33,6 3,7 39 Surface puce (mm²) 0,19 3,04 1,48 0,56 0,36 0,55 FoM (dBc/Hz) 180 174,35 181 178,65 186,5 176,5

TABLE 1.1 – État de l'art de PLL entières

TABLE 1.2 – État de l'art de la PLL fractionnaires

| Références                    | [19]  | [20] | [21] | [22]  |

|-------------------------------|-------|------|------|-------|

| Technologie (nm)              | 65    | 28   | 40   | 65    |

| Bande-passante (%)            | 17    | 28   | 64,5 | 26,6  |

| Fréquence centrale (GHz)      | 3,5   | 6,4  | 2,5  | 3     |

| Bruit de phase@1 MHz (dBc/Hz) | -109  | -118 | -110 | -115  |

| Référence de fréquence (MHz)  | 78    | 104  | 50   | 40    |

| Référence « Spur » (dBc)      | -69   | -70  | N/A  | N/A   |

| « Spur » fractionnaire (dBc)  | <-65  | <-54 | N/A  | N/A   |

| Puissance dissipée (mW)       | 6,9   | 18,9 | 10,7 | 13,3  |

| Surface puce (mm²)            | 0,24  | 0,5  | 0,5  | 0,21  |

| FoM (dBc/Hz)                  | 171,5 | 181  | 168  | 173,3 |

TABLE 1.3 – État de l'art de la PLL fractionnaires (suite)

| Références                   | [23]   | [24]  | [25]      | [26]  |

|------------------------------|--------|-------|-----------|-------|

| Technologie (nm)             | 65     | 65    | SiGe bip. | 65    |

| Bande-passante (%)           | 20,6   | 13    | 30        | 93    |

| Fréquence centrale (GHz)     | 29     | 4,64  | 80        | 3,75  |

| Bruit de phase@1MHz (dBc/Hz) | -112,6 | -120  | -94       | -96   |

| Référence de fréquence (MHz) | 78     | 40    | 1000      | 50    |

| Référence « Spur » (dBc)     | N/A    | -70,8 | N/A       | N/A   |

| « Spur » fractionnaire (dBc) | N/A    | -59,2 | N/A       | N/A   |

| Puissance dissipée (mW)      | 26,9   | 6,2   | 1557      | 4     |

| Surface puce (mm²)           | 0,28   | 0,2   | 1         | 0,084 |

| FoM (dBc/Hz)                 | 187    | 188,3 | 160       | 162,5 |

Une première chose plutôt générale à noter est que le bruit de phase de la PLL est mesuré loin de la porteuse, ici 1 MHz, puisque proche de la porteuse, c'est le bruit de la référence qui prévaut et qui n'apporte donc pas d'information sur la PLL elle-même. En effet, dans la littérature,

le bruit de phase des PLL est généralement donné à cette distance de la porteuse. C'est pour cela que dans le FoM utilisé, la fréquence centrale du synthétiseur est divisée par la fréquence relative à la porteuse à laquelle le bruit de phase est mesuré. Cela permet de mettre en exergue les synthétiseurs ayant un bon bruit de phase proche de la porteuse. Comme évoqué dans l'introduction générale, il apparaît que la plupart des références de fréquences utilisées dans ces PLL génèrent des signaux de quelques dizaines à quelques centaines de mégahertz. Ensuite, nous voyons qu'il est aujourd'hui possible de générer des fréquences élevées avec les technologies les plus fines tout en conservant un niveau correct de bruit de phase pour une PLL [13]. Il semble également ressortir de ce tableau que générer des fréquences plus élevées a un impact négatif sur le bruit de phase. En effet, si l'on essaye de relever une tendance, il semble que pour une finesse de gravure identique, plus la fréquence centrale d'une PLL est élevée, plus son FoM est détérioré. Or, une fréquence centrale élevée devrait en théorie correspondre à un FoM moins élevé (donc meilleur), cela veut donc dire que cette augmentation de la fréquence centrale entraîne une dégradation importante d'une autre caractéristique de la PLL, comme le bruit de phase ou la consommation. De plus, on constate d'après ces tableaux que la synthèse fractionnaire dégrade davantage le bruit de phase que la synthèse entière, ce qui s'explique en partie par une complexité accrue des diviseurs fractionnaires, ce qui implique un plus grand nombre de composants utilisés donc plus de contributeurs en bruit. Enfin, pour tenter de généraliser sur l'aspect qui nous intéresse le plus, on peut avancer qu'en ramenant les bruits de phase des différentes PLL entières à une fréquence de 10 GHz (avec la formule  $20 \times \log N$ ), ils sont compris entre 105 dBc/Hz@1 MHz et 122 dBc/Hz@1 MHz. Pour les PLL fractionnaires, en transposant mathématiquement leur bruit de phase à une fréquence de 10 GHz, ils vont de 87,5 dBc/Hz@1 MHz à 121 dBc/Hz@1 MHz. Pour le reste, nous estimons qu'il est complexe d'extraire des tendances précises sur une caractéristique précise de ces PLL puisque toutes les caractéristiques sont généralement interdépendantes et que c'est principalement l'application pour une PLL donnée qui détermine laquelle des caractéristiques sera favorisée.

Maintenant que les PLL ont été décrites en détail, nous allons présenter la méthode de synthèse alternative au centre de nos recherches, à savoir la synthèse par division de fréquence.

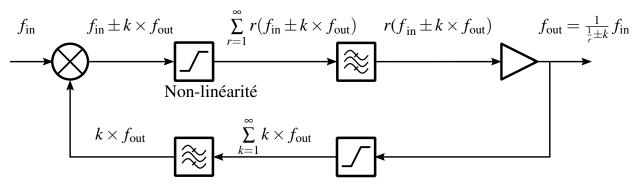

#### La synthèse par division de fréquence **1.II**

#### 1.II.1 **Principe**

Comme présenté lors de l'introduction générale, la multiplication d'une fréquence par une PLL entraîne une augmentation du bruit de phase théorique du signal synthétisé, par rapport à celui de la référence, de  $20 \times \log N$ , N étant le facteur de multiplication. Comme détaillé dans le § 1.I.2, à cette augmentation de bruit de phase inévitable s'ajoute le bruit de phase résiduel des éléments de la PLL [27]. À l'inverse, diviser une référence de fréquence par un facteur N diminue théoriquement le bruit de phase du signal synthétisé de  $20 \times \log N$  par rapport à celui de la référence. Nos travaux portent sur la division de fréquence qui, à l'inverse de la PLL, utilise une référence de fréquence élevée. Cette référence à haute fréquence et à haute pureté spectrale est divisée par des diviseurs à faible bruit de phase résiduel pour tenter d'en conserver la pureté spectrale. Du fait de leur complexité, les références à haute fréquence et haute pureté spectrale restent encore peu répandues comparées aux références basses fréquences.

Dans notre cas, la référence utilisée est un COEO. Différents diviseurs de fréquences sont réalisés pour opérer une division directe du signal généré par cette référence. L'objectif principal est d'obtenir un bruit de phase résiduel aussi faible que possible pour ces diviseurs, puisque c'est sur cet aspect que l'on souhaite avoir un avantage important comparé à une PLL. Ensuite, la possibilité d'obtenir des rapports fractionnaires et/ou programmables a également été au centre de nos préoccupations. Enfin, les derniers aspects auxquels nous avons porté une attention particulière, une fois les spécifications précédentes satisfaites, sont la consommation de puissance et l'encombrement du circuit.

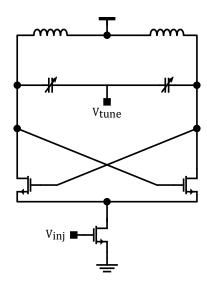

#### 1.II.2 Oscillateurs opto-électroniques couplés

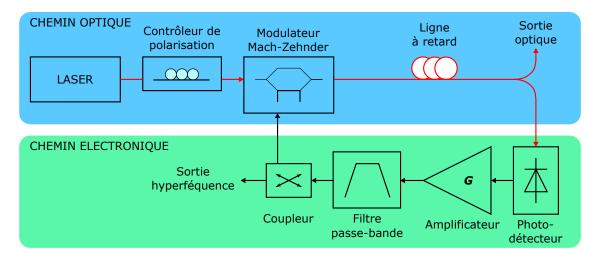

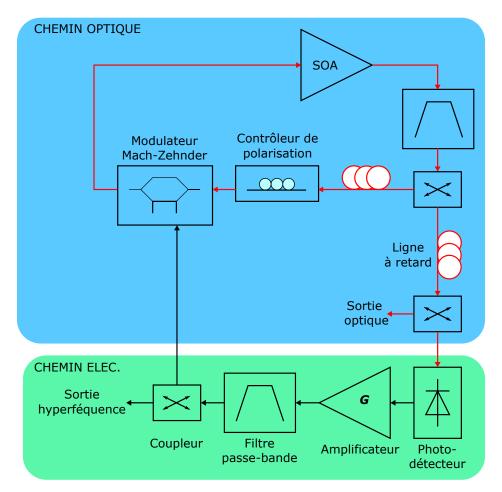

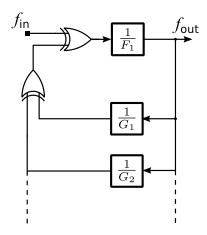

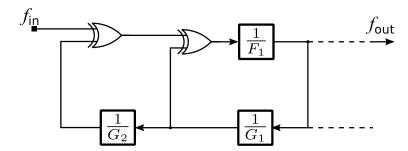

Présenté pour la première fois en 2000 [28], le COEO est un système oscillant permettant la génération de signaux de fréquences de la dizaine à quelques dizaines de gigahertz à haute pureté spectrale. Son principe repose sur le couplage d'une oscillation opto-électronique et d'une oscillation optique. Il est important de ne pas confondre le COEO avec l'oscillateur opto-électronique (ou OptoElectronic Oscillator) (OEO) [29-31]. En effet, bien qu'ils présentent des similarités puisque pour l'OEO, la lumière d'un laser est utilisée dans une boucle à contre-réaction opto-électronique pour générer une oscillation hyperfréquence comme présenté sur la figure 1.5, le COEO réinjecte l'oscillation opto-électronique dans une boucle optique qui génère elle-même un signal optique comme illustré sur la figure 1.6.

Ainsi, contrairement à l'OEO où le signal optique est issu d'un laser totalement décorrélé de l'onde hyperfréquence, le COEO génère lui-même un signal optique pulsé, avec une fréquence de répétition des impulsions égale à la fréquence de la boucle micro-onde. La génération optique est obtenue grâce à un amplificateur optique. Cet amplificateur peut être un Semiconductor Optical Amplifier (SOA) ou un Erbium-Doped Fiber Amplifier (EDFA).

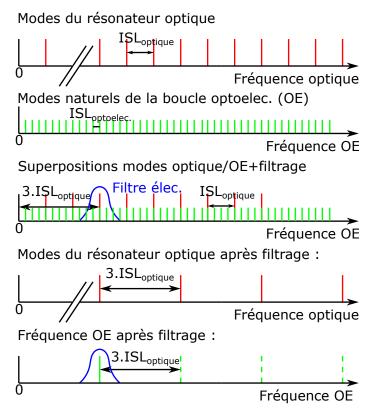

Cette partie optique du montage est un type de source laser particulière appelée laser à blocage de modes (cadre « CHEMIN OPTIQUE » sur la figure 1.6). Comme l'illustre la figure 1.7, ce laser génère différents modes correspondant à l'ensemble des modes autorisés par la boucle. Ces modes sont espacés d'un Intervalle Spectral Libre (ISL) constant, qui est lié à la longueur de la cavité.

FIGURE 1.5 – Schéma de principe d'un OEO

FIGURE 1.6 – Schéma de principe d'un COEO

Ensuite, la partie opto-électronique (cadres « CHEMIN OPTIQUE » et « CHEMIN ELEC. » combinés de la figure 1.6) possède elle-même son propre ISL. Il existe alors plusieurs fréquences pour lesquelles l'oscillation optique et l'oscillation opto-électronique sont accordées. Une de ces

FIGURE 1.7 – Principe de fonctionnement d'un COEO

fréquences est sélectionnée à l'aide du filtre de la partie électronique. Ce filtrage, à travers la contre-réaction, fixe l'harmonique choisi sur lequel le laser oscille et par conséquent la fréquence du signal électrique en sortie du COEO. Il génère alors un signal micro-onde de fréquence fixe à haute pureté spectrale en sortie de la partie électronique. C'est ce signal qui sert de référence pour les différents diviseurs que nous allons maintenant présenter. Ces COEO sont le fruit du travail d'autres chercheurs au LAAS et je n'ai pas travaillé sur les COEO eux-mêmes, mais je m'en suis servi comme référence de fréquence pour les diviseurs que j'ai conçus.

#### 1.II.3 Diviseurs de fréquence numériques

#### 1.II.3.a Principe

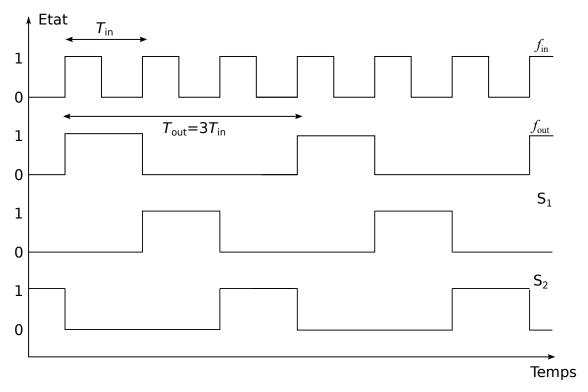

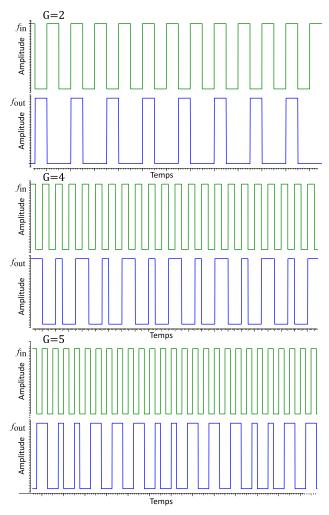

Un diviseur numérique a pour principe de réaliser un comptage logique des fronts actifs d'un signal d'horloge, et de générer un front en sortie pour *N* fronts actifs d'horloge.

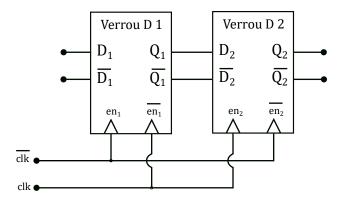

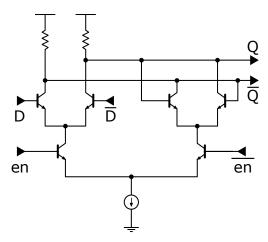

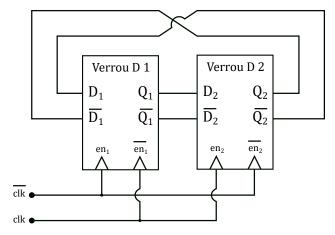

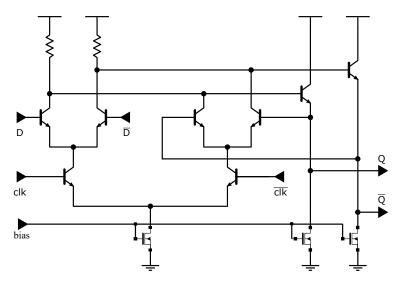

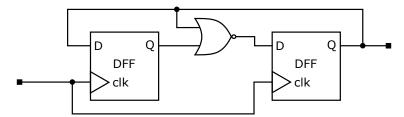

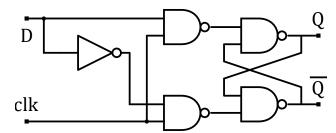

Une des briques élémentaires permettant la mise en œuvre de diviseurs numériques est la bascule D. Elle recopie le niveau logique de l'entrée D sur la sortie Q lors d'un front actif d'horloge (montant, descendant ou les deux selon la bascule). Elle est constituée de deux verrous D comme présenté sur la figure 1.8.

FIGURE 1.8 – Deux verrous D constituant une bascule D

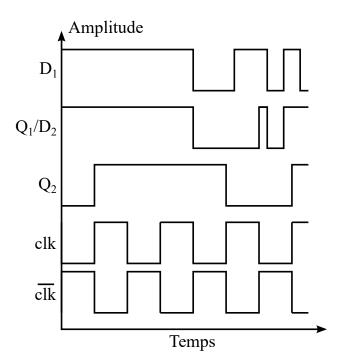

Un verrou recopie l'entrée D sur sa sortie Q pendant le niveau actif de l'horloge (haut ou bas) et mémorise l'état de la sortie sur l'autre niveau. C'est en mettant en série deux verrous réagissant sur des niveaux complémentaires de l'horloge que l'on crée la bascule. Par exemple, sur le niveau bas de l'horloge, le premier verrou laisse passer le signal en position intermédiaire pendant que l'autre verrou mémorise la sortie précédente, puis sur le niveau haut qui suit, le premier verrou fige la valeur intermédiaire qui est recopiée en sortie par le deuxième verrou. Tout se passe alors comme si l'ensemble réagissait sur un front montant (en fait en deux temps) en créant une bascule équivalente. Le chronogramme présenté sur la figure 1.9 illustre le fonctionnement de la bascule, avec le détail de chaque verrou.

FIGURE 1.9 – Chronogramme d'une bascule D avec le détail de chaque verrou

Il existe ensuite de nombreuses technologies pour concevoir le verrou D en fonction de l'appli-

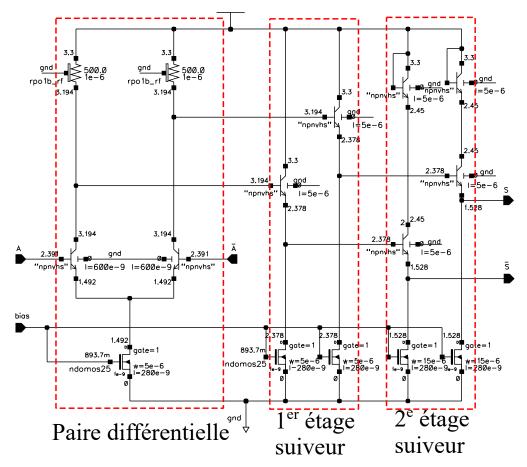

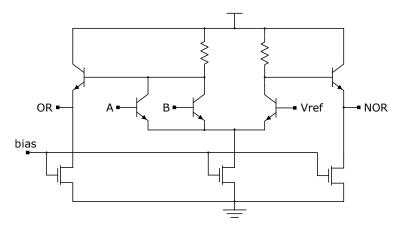

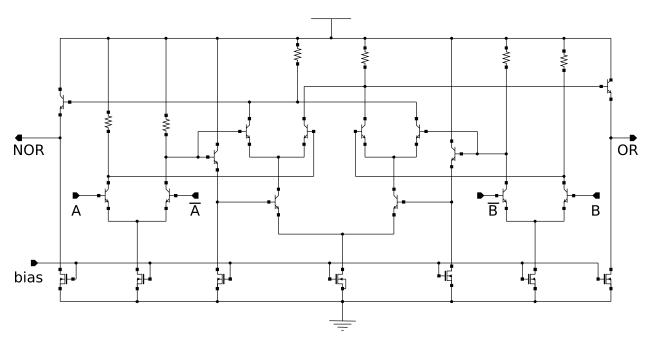

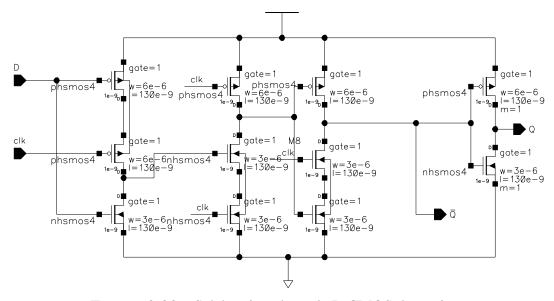

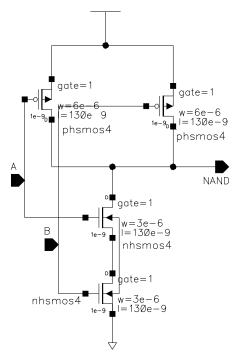

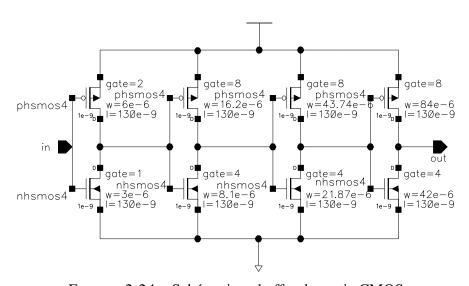

FIGURE 1.10 – Topologie verrou D en CML

cation visée. Certaines utilisent des transistors bipolaires et d'autres des transistors MOS, certaines sont adaptées aux hautes fréquences d'autres ne le sont pas, etc. Lors de la conception des circuits, nous avons principalement utilisé la technologie Emitter Coupled Logic (ECL), elle-même issue d'une logique de conception appelée Current-Mode Logic (CML) basées sur des transistors bipolaires et plus précisément sur des paires différentielles. Cette logique permet d'atteindre des fréquences de fonctionnement élevées en utilisant de faibles excursions en tension et en empêchant le transistor de travailler dans en régime saturé. Le principal inconvénient de ces logiques est leur consommation importante, mais cette caractéristique est secondaire dans la conception de nos circuits. Les paires différentielles permettent d'activer une branche ou l'autre de la paire en fonction des niveaux logiques de commande. La plupart de nos circuits sont conçus en ECL qui est semblable à la CML, à la différence près que des montages émetteurs suiveurs sont ajoutés en sortie des circuits CML pour devenir des circuits ECL. Ces collecteurs communs ont l'avantage de garantir un courant suffisant pour piloter des charges de faibles impédances en sortie et de maintenir les transistors de la paire différentielle en régime linéaire. Ces techniques de conception permettent d'atteindre des vitesses de fonctionnement plus élevées comparées à celles du CMOS grâce à l'utilisation de transistors bipolaires et leur faible excursion de tension en sortie.

Une topologie de verrou D CML est présentée sur la figure 1.10.

Le verrou D permet de recopier sur la sortie  $\mathbf{Q}$  l'état de l'entrée  $\mathbf{D}$  tant que le signal d'activation  $\mathbf{e}\mathbf{n}$  est à l'état haut. Ainsi en cascadant deux verrous D et en inversant les signaux d'activation des deux verrous, on obtient une bascule D comme présenté sur la figure 1.8. Les signaux d'activation étant inversés sur les deux verrous, la bascule ne change d'état que sur les fronts montants du signal d'horloge  $\mathbf{clk}$ . Ainsi, lors d'un front descendant, le premier verrou recopie  $\mathbf{D}_1$  sur  $\mathbf{Q}_1$  tandis que  $\mathbf{Q}_2$  conserve l'état dans lequel il était précédemment. Ensuite, au front montant suivant, le verrou 1 désolidarise cette valeur de son entrée, en la mémorisant dans cette position intermédiaire, et le verrou 2 la recopie sur sa sortie. On comprend alors l'intérêt de la bascule D : elle permet une

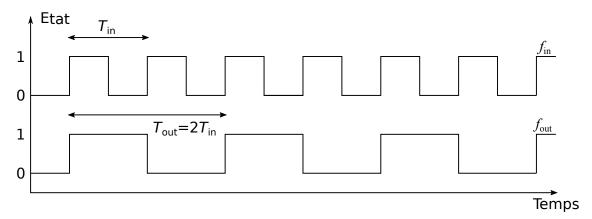

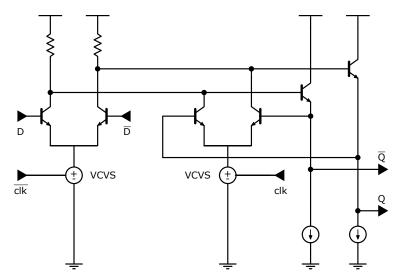

FIGURE 1.11 – Diviseur par 2 numérique

FIGURE 1.12 – Chronogramme d'une division numérique par 2

mémorisation d'un état sur un front actif d'horloge. Nous parlerons désormais de front d'horloge pour les fronts actifs d'horloge afin de simplifier la lecture.

Si l'on a bien saisi le fonctionnement de la bascule D, on comprend alors qu'il est aisé de réaliser un diviseur par deux en utilisant une bascule D. En effet, comme présenté sur la figure 1.11, en bouclant la sortie inverseuse de la bascule sur son entrée non inverseuse, nous obtenons un diviseur par deux. Cela est dû au fait que l'état de la sortie soit inversé à chaque front montant du signal d'horloge, ce qui équivaut à diviser la fréquence par deux comme le montre la figure 1.12.

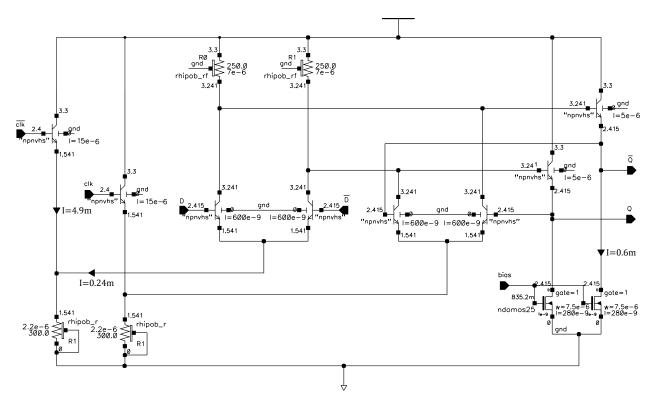

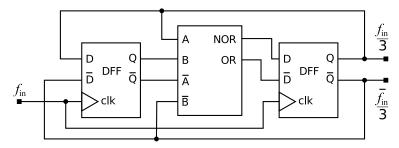

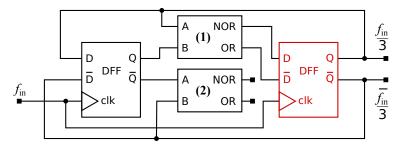

Sur ce même principe, on rajoute ensuite des portes logiques pour « sauter » un certain nombre de fronts de l'horloge afin d'augmenter le rapport de division. Par exemple, une topologie de diviseur par 3 numérique est présentée sur la figure 1.13

On obtient pour ce diviseur par 3 le chronogramme présenté en figure 1.14.

Nous utilisons ici comme état initial le cas où les sorties des deux bascules D sont à l'état bas (deux autres états initiaux sont possibles avec la sortie de l'une ou l'autre des bascules D à l'état haut). Les deux entrées de la porte NOR sont donc à l'état bas, sa sortie est à l'état haut. Au

FIGURE 1.13 – Diviseur par 3 numérique

FIGURE 1.14 – Chronogramme d'une division numérique par 3

premier front d'horloge, la sortie de la bascule D de droite passe à l'état haut, celle de la bascule D de gauche reste à l'état bas. La porte NOR a alors une entrée à l'état haut et l'autre à l'état bas, sa sortie passe à l'état bas. Au second front d'horloge, la sortie de la bascule D de droite passe donc à l'état bas, celle de la bascule D de gauche passe à l'état haut. La porte NOR a toujours une entrée à l'état haut et l'autre à l'état bas, sa sortie reste à l'état bas. Au troisième front d'horloge, les sorties des deux bascules sont à l'état bas. La sortie de la porte NOR est à l'état haut, nous sommes revenus dans l'état initial au bout de trois fronts d'horloge et un seul front montant a été généré en sortie, une division par 3 a donc été réalisée. Nous obtenons alors  $f_{\text{out}} = \frac{f_{\text{in}}}{3}$ .

C'est le principe de base qui régit la division numérique : on utilise des portes logiques pour masquer plus ou moins de fronts et régler ainsi le rapport de division.

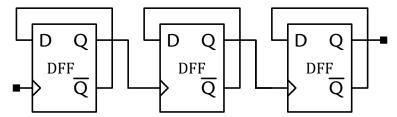

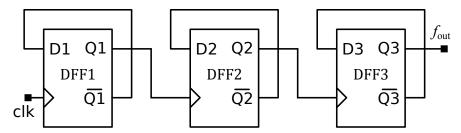

#### 1.II.3.b Diviseurs synchrones

Les bascules d'un diviseur synchrone partagent toutes la même horloge et changent donc d'état simultanément sur un même front d'horloge [32].

Comme expliqué précédemment dans le § 1.II.3, le principe est de réaliser un comptage de fronts du signal d'horloge pour générer un front en sortie tous les N fronts d'horloge, réalisant ainsi une division par N. Par exemple, le diviseur par 3 présenté précédemment est un diviseur synchrone 1.13.

Cette simultanéité permet de travailler sereinement en interdisant des états parasites dus aux temps de propagation entre bascules. En contrepartie, leur complexité s'accroît rapidement avec le rapport de division qu'ils réalisent : il faut davantage de portes logiques pour réaliser un rapport de division plus élevé que pour des diviseurs asynchrones. En revanche, ils présentent un avantage du point de vue du bruit de phase : c'est la bascule D en sortie qui détermine majoritairement le bruit de phase du signal synthétisé. En effet, [33] explique qu'entre un diviseur par 4 synchrone et un diviseur par 4 asynchrone, une différence de bruit de phase de 3 dB est attendue car seul le bruit de phase de la seconde bascule est significatif pour le diviseur synchrone. Cela peut s'expliquer par le fait que chaque bascule n'évolue qu'à partir d'un même front d'horloge qui sert donc de référence de phase pour toutes leurs sorties. Et donc chaque bascule « efface » le bruit de la précédente en se resynchronisant sur cette horloge unique, en particulier la bascule de sortie qui devient la seule à contribuer au bruit de sortie.. Pour un diviseur synchrone, il faut donc apporter un soin particulier au bruit de phase de la bascule de sortie car c'est elle qui sera déterminante pour le bruit de phase du signal synthétisé.

## 1.II.3.c Diviseurs asynchrones

Les diviseurs asynchrones sont réalisés sans se soucier de n'utiliser qu'une seule horloge pour toutes les bascules. La fréquence générée par un premier diviseur peut ainsi servir d'horloge au diviseur suivant. Un exemple de diviseur asynchrone est présenté sur la figure 1.15. Il s'agit d'un diviseur par  $2^n$ , n étant le nombre de bascules D utilisées en diviseur par 2. Ainsi, en cascadant trois bascules D réalisant chacune une division par deux, on réalise un diviseur par  $2^3 = 8$ .

FIGURE 1.15 – Diviseur par  $2^3 = 8$  asynchrone

Ce type de diviseur est assez simple à mettre en œuvre, mais il présente plusieurs inconvénients : tout d'abord, les temps de propagation dans chaque bascule s'accumulent si bien qu'à fréquence élevée, des problèmes de synchronisation entre l'horloge principale et le signal synthétisé peuvent apparaître. Cela ne pose pas de problème en soi si l'on s'intéresse uniquement au signal synthétisé. En revanche, si ce signal synthétisé est utilisé pour réaliser une opération avec un autre signal synthétisé à partir de l'horloge principale, ce déphasage peut impacter le fonctionnement du circuit. De plus, les bruits de phase de chacune des bascules s'accumulent également au fur et à mesure, si bien que le signal synthétisé peut présenter un bruit de phase important si de nombreuses bascules s'enchaînent. Il existe cependant un moyen d'améliorer en partie ce bruit de phase par une technique de resynchronisation.

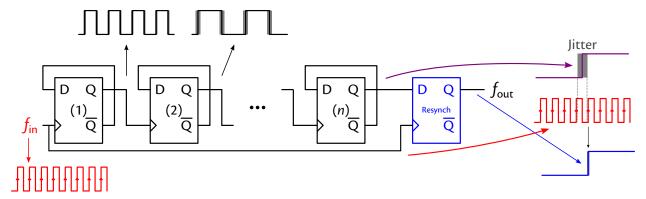

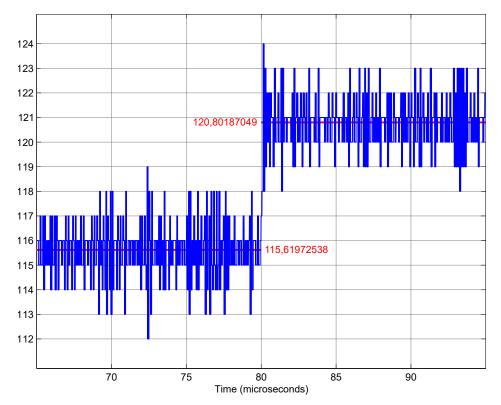

### 1.II.3.c. i Technique de resynchronisation

Le fait d'utiliser des diviseurs asynchrones en cascade entraîne une dégradation progressive du bruit de phase du signal qui accumule les détériorations de la chaîne de diviseurs.

Sur la figure 1.16, cette technique de resynchronisation est illustrée pour un diviseur en 2<sup>n</sup> mais elle est valable pour tout diviseur asynchrone aussi compliqué soit-il. La resynchronisation consiste à utiliser une bascule D synchronisée avec l'horloge de départ à la suite de la chaîne de diviseurs. Ainsi, la gigue accumulée au cours de la chaîne de diviseurs est éliminée en recalant les fronts de signal synthétisé sur ceux, propres, du signal d'horloge de départ. On parle alors de resynchroniser le signal de sortie sur l'horloge d'entrée, ce qui permet d'obtenir une amélioration significative du bruit de phase [34, 35].

FIGURE 1.16 – Illustration de la technique de resynchronisation

Un des soucis principaux de cette technique est lié au problème d'accumulation de temps de propagation dans les différentes bascules. Il peut entraîner un décalage important entre le front d'horloge qui a déclenché la division et le front généré en sortie. Ainsi, le signal synthétisé en sortie sera bien un sous-multiple de la fréquence d'entrée mais à cause des temps de propagation accumulés, il se peut qu'au moment de la resynchronisation, il y ait eu davantage de périodes sur le signal d'entrée que sur le signal de sortie. Cela n'est problématique que dans le cas où l'on utilise un circuit en parallèle du circuit resynchronisé ayant la même horloge. Par exemple, avec deux diviseurs asynchrones différents en parallèle utilisant la même horloge, un même front va déclencher le début de la division, mais l'accumulation de temps de propagation ne sera pas la même dans les deux diviseurs. Une fois resynchronisé (individuellement), il peut exister un décalage entre les deux signaux synthétisés. Il faut donc être prudent à ce sujet si l'on souhaite réaliser des opérations fréquentielles utilisant ces signaux. En revanche, cela importe peu pour la resynchronisation d'un circuit dont la sortie n'est pas comparée à celle d'un circuit en parallèle puisque c'est uniquement la position relative du front de resynchronisation par rapport au signal resynchronisé qui va être importante. Un décalage d'une ou plusieurs périodes du signal d'entrée par rapport au signal resynchronisé n'a pas d'impact sur la resynchronisation. En revanche, sur une période du signal à resynchroniser, l'instant où a lieu le front de resynchronisation est important. En effet, si celui-ci advient sur un front montant ou descendant du signal à resynchroniser, une partie du bruit peut être transmise sur le signal resynchronisé. Il peut donc s'avérer bénéfique d'ajouter un délai réglable sur le signal de resynchronisation de façon à pouvoir décaler un front de resynchronisation sur un état établi du signal à resynchroniser.

#### 1.II.3.d Diviseurs entiers fixes

Les diviseurs entiers fixes ne comportent que des portes logiques qui ne présentent aucune programmabilité, c'est-à-dire que le diviseur n'est capable de réaliser qu'un seul rapport de division. Ces diviseurs ont donc des topologies simples et épurées en faisant un sacrifice sur la flexibilité.

Ils permettent donc d'estimer les performances, notamment en bruit de phase, qu'il est possible d'atteindre avec une technologie donnée, en particulier celle du diviseur par deux qui est le plus simple d'entre tous.

#### 1.II.3.e Diviseurs entiers programmables

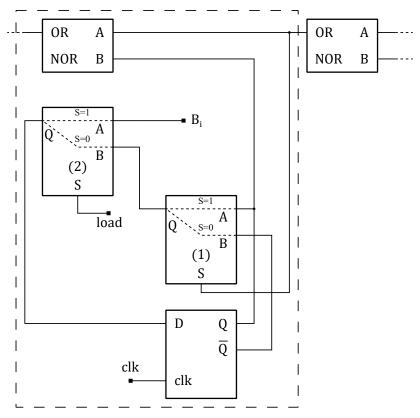

Un diviseur programmable est un diviseur dont le rapport peut être codé par un mot binaire indiquant le rapport à programmer.

Il existe diverses méthodes pour réaliser un diviseur programmable. Un exemple de diviseur programmable est le diviseur N/N+1.

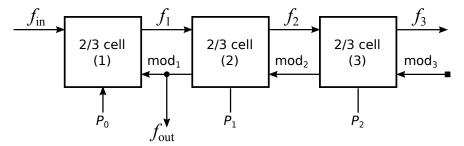

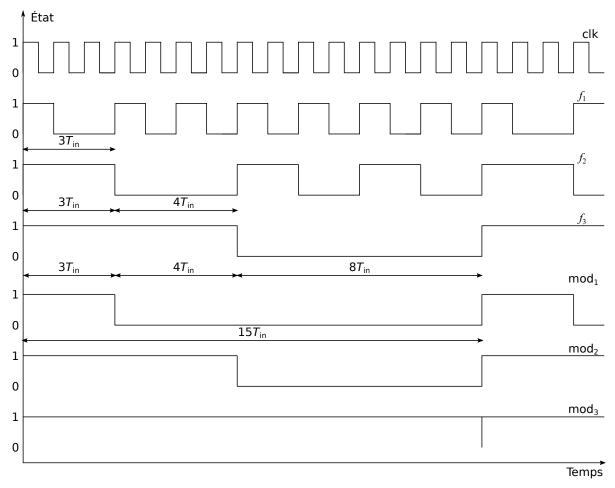

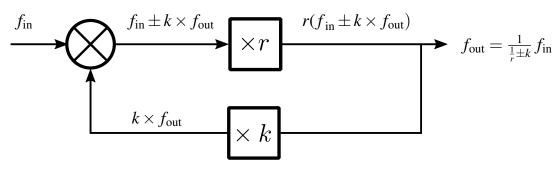

## 1.II.3.e. i Diviseurs N/N+1

Comme leur nom l'indique, ils permettent de réaliser une division par deux rapports différents consécutifs au choix mais souvent avec  $N = 2^n$ . Ils sont généralement réalisés en logique rapide (CML ou ECL) en tant que prédiviseur vers un diviseur plus complexe réalisé en logique CMOS, plus lent mais plus facilement programmable. Ils sont réalisés à partir de bascules D et de portes logiques, et leur programmation reste simple (entre N et N+1 donc sur un seul bit). Différentes topologies de ce type de diviseurs pour différents rapports peuvent être trouvés dans la littérature [36].

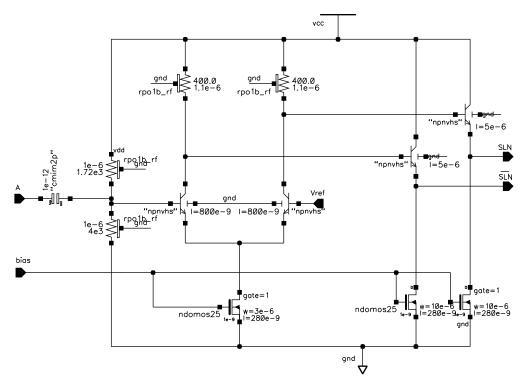

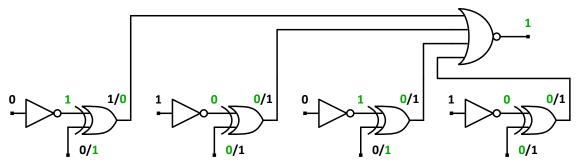

#### 1.II.3.e. ii Diviseurs programmables à comparateur

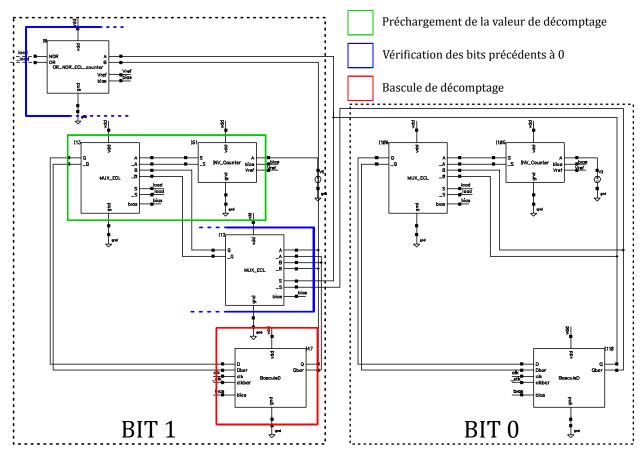

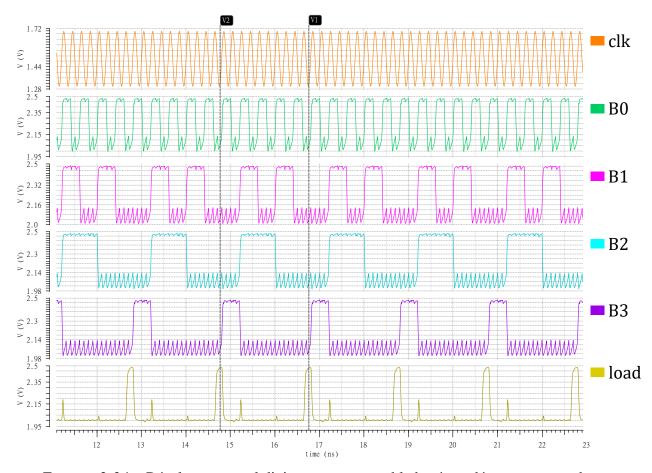

Une autre méthode pour réaliser des diviseurs programmables est de comparer la valeur d'un compteur ou d'un décompteur à une consigne et, d'à la fois générer un front et réinitialiser le (dé)comptage une fois la consigne atteinte. Il existe ensuite différentes méthodes pour concevoir le (dé)compteur, réaliser la comparaison et faire la réinitialisation. Nous présentons ici deux méthodes basées sur des décompteurs, un synchrone et un asynchrone. Le plus performant est utilisé par la suite dans un diviseur plus complexe.

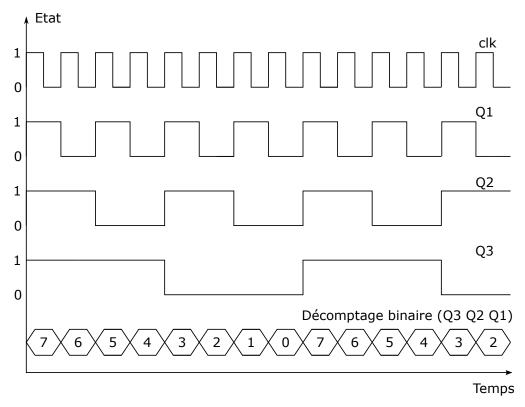

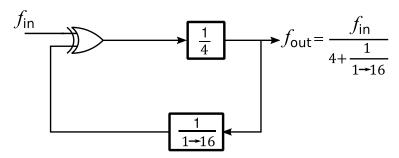

Tout d'abord, nous utilisons les diviseurs asynchrones basés sur les diviseurs par 2 en cascade évoqués plus haut. En effet, nous avons établi que ce type de montage réalisait une division par  $2^n$  où n est le nombre de bascules utilisées. Nous avons également expliqué que faire une division de fréquence numérique équivaut à compter un nombre de fronts et à en générer un en sortie tous les N fronts d'entrée pour faire une division par N. Or c'est exactement ce que réalise ce circuit, il opère un décomptage binaire entre  $2^{n-1}$  et 0. Chacun des signaux en sortie des bascules représentent un bit de ce comptage binaire. La sortie de la première bascule D correspond au bit de poids faible, le signal en sortie de la bascule D suivante correspond au bit de poids plus fort et ainsi de suite. Prenons l'exemple d'un décompteur à N0 présenté dans la figure N1. Nous obtenons alors le

FIGURE 1.17 – Schéma décompteur numérique à 8

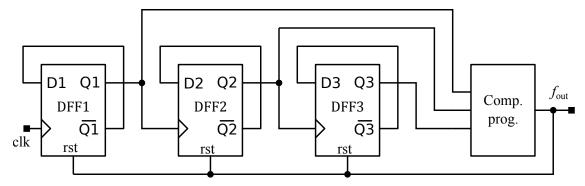

FIGURE 1.18 – Chronogramme décompteur numérique à 8

chronogramme de la figure 1.18. Un décomptage de 7 à 0 est bien opéré sur les sorties Q3, Q2 et Q1. Afin de rendre ce décompteur programmable, il suffit d'utiliser un comparateur programmable sur chacun des bits en sortie des bascules D et de remplacer les bascules par des bascules D à reset (**rst**) comme présenté sur la figure 1.19. Le comparateur programmable génère un front montant lorsque la valeur du mot binaire qu'il a en entrée atteint la consigne qui a été implémentée. Les bascules D **rst** retournent dans leur état initial dès qu'il y a un front montant sur l'entrée **rst**. Ainsi, une valeur à laquelle arrêter le décomptage est implémentée dans le comparateur et lorsque cette valeur est atteinte, les bascules D sont réinitialisées pour que le décomptage recommence de la valeur initiale. Par exemple, pour une division par 5, il faut programmer le comparateur à la valeur 2. En effet, il faut cinq coups d'horloge pour décompter de 7 à 2, le comparateur génère donc un front montant tous les cinq coups d'horloge, ce qui réalise une division par 5, et ce signal sert

FIGURE 1.19 – Décompteur 3 bits avec comparateur et bascule D à reset

```

B0:1010101010101010

B1:110011001100