# Fabrication et caractérisation du HEMT InP pour amplification faible bruit THz

Mohammed Samnouni

#### ▶ To cite this version:

Mohammed Samnouni. Fabrication et caractérisation du HEMT InP pour amplification faible bruit THz. Micro et nanotechnologies/Microélectronique. Université de Lille, 2019. Français. NNT: 2019LILUI103. tel-03611230v1

### HAL Id: tel-03611230 https://theses.hal.science/tel-03611230v1

Submitted on 17 Mar 2022 (v1), last revised 17 Mar 2022 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

# Présentée à l'Université de Lille École Doctorale Sciences Pour l'Ingénieur

Pour obtenir le grade de :

# DOCTEUR DE L'UNIVERSITÉ

Spécialité: ÉLECTRONIQUE, MICROÉLECTRONIQUE, NANOÉLECTRONIQUE ET MICRO-ONDES

### Par

## **Mohammed SAMNOUNI**

# Fabrication et caractérisation de HEMT InP pour amplification faible bruit THz

Soutenue le 16 décembre 2019 devant la commission d'examen

#### Membres du Jury:

| Dr. Xavier Wallart    | IEMN, Univ. Lille     | Président du jury  |

|-----------------------|-----------------------|--------------------|

| Pr. Hassan Maher      | LN2, Univ. Sherbrooke | Rapporteur         |

| Pr. Jean-Guy Tartarin | LAAS, Univ. Toulouse  | Rapporteur         |

| Pr. Nathalie Malbert  | IMS, Univ. Bordeaux   | Examinatrice       |

| Dr. Nicolas Wichmann  | IEMN, Univ. Lille     | Co-encadrant       |

| Pr. Sylvain Bollaert  | IEMN, Univ. Lille     | Directeur de thèse |

|                       |                       |                    |

#### Remerciements

Ce travail a été effectué à l'Université de Lille au sein de l'Institut d'Électronique, de Microélectronique et de nanotechnologie (IEMN) dirigé par Monsieur Lionel Buchaillot et plus particulièrement dans l'équipe ANODE dirigé par Monsieur Mohammed Zaknoune. Il est évidemment assez difficile de citer toutes les personnes qui ont contribué à la réalisation de cette thèse, alors en espérant n'oublier personne ....

Je souhaite tout d'abord remercier mes encadrants Sylvain Bollaert et Nicolas Wichmann d'avoir dirigé et encadré ces travaux de thèse, je les remercie pour leurs disponibilités, leurs investissements, leurs patiences ainsi que leurs encouragements durant ces années.

J'adresse mes sincères remerciements à Monsieur Xavier Wallart (IEMN) qui me fait l'honneur de présider la commission d'examen, je lui suis grandement reconnaissant également pour sa disponibilité, les discussions à propos des optimisations des structures épitaxiales et l'accroissance des couches HEMT avec Monsieur Christophe Coinon.

Je remercie sincèrement Monsieur Jean-Guy Tartarin (LAAS) et Monsieur Hassan Maher (LN2) d'avoir jugé ce travail en tant que rapporteurs. Je leur suis très reconnaissant de l'intérêt qu'ils ont porté à mes travaux. Je remercie également Madame Nathalie Malbert (IMS) d'avoir accepté d'examiner ce travail au sein de la commission d'examen.

Je remercie sincèrement tout le personnel de l'IEMN la centrale de nanofabrication : B. Grimbert, F. Vaurette, M. François, Y. Deblock, J-L Codron, S. Ouendi, P. Tilmant, C. Boyaval M. Dewitte, A. Fattorini, D. Troadec, J-L ainsi que le personnel de la centrale de caractérisation : S. Lepilliet, V. Avramovic, E. Okada et S. Eliet.

Je tiens maintenant à remercie les membres du groupe ANODE et EPIHY ainsi que PhotoniqueTHz particulièrement Monsieur Guillaume Ducournau pour sa contribution aux caractérisations à très Hautes fréquences. Mes remerciements vont également à Monsieur Ahmed Addad pour ces images TEM et à Monsieur Gilles Dambrine pour son aide dans la partie bruit.

Un immense merci aussi aux personnes que j'ai côtoyées durant ces années de thèse les exdoctorants, les doctorants, les post doctorants, ingénieurs ainsi que tous les collègues pour leur sympathie et les moments conviviaux passés ensemble : Aurélien, Vinay, Matej, Yoann, Khadim, Alexandre, Jawad, Elias, Giuseppe, Hugo, Soukaina, Fatima, Cybelle, Kévin, Charbel, Mahmoud, Reda et autres...

Enfin, je remercie mes parents, mes frères et ma sœur, ainsi que ma chère épouse pour leurs soutiens et leurs encouragements durant toute cette période.

#### Résumé -

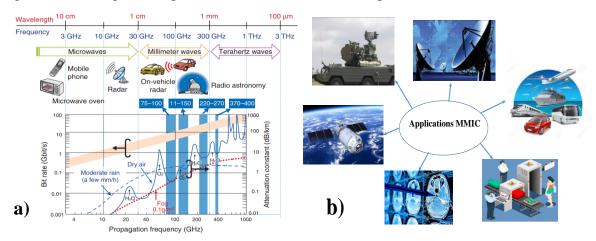

Les avancées des technologies III-V permettent aujourd'hui de concevoir des composants électroniques fonctionnant en gammes millimétrique et submillimétrique (fréquences Terahertz) pour répondre aux besoins émergents du marché des télécommunications et de l'électronique à destination de différents secteurs industriels. L'électronique THz trouve des débouchées importantes dans les applications d'imagerie, entre autres pour la sécurité et les communications sans fils ultra haut débit (5G plus).

La technologie des transistors HEMT InP a connu ces dernières années un progrès remarquable dans la réalisation des circuits intégrés à très hautes fréquences (fréquence de fonctionnement à 1 THz) et de faible bruit. Peu d'acteurs mondiaux de la microélectronique (aucun en France) ont établi des performances atteignant ces fréquences THz. Nous proposons de développer une technologie répondant à cette demande.

Dans ces travaux de thèse, nous proposons de développer des HEMT InAlAs /InGaAs/InAs sur substrat d'InP de fréquence de coupure THz pour amplification faible bruit dans les systèmes de réception-détection THz. Nous avons pour cela optimisé la structure semiconductrice utilisée afin d'obtenir un meilleur compromis mobilité/charges électroniques. Nous avons également apporté des modifications géométriques (longueur de grille, taille du recess et espacements des électrodes du transistor) qui ont permis d'augmenter considérablement les fréquences de fonctionnement du transistor. Nous avons réalisé des mesures de paramètres S jusque 750 GHz et en bruit jusque 110 GHz, afin de valider les optimisations technologiques apportées à la structure HEMT.

Mots clés : HEMT, InP, InAlAs/InGaAs/InAs, recess asymétrique, hyperfréquence, fréquence maximale d'oscillation et facteur minimum de bruit.

#### Abstract—

Progress of III-V technologies are now making it possible to design electronic components operating in the millimeter and sub-millimeter wave range (THz) are facing the needs of the telecommunications and electronics market for various industrial sectors. The technology of InP High Electron Mobility Transistor (HEMT) allowed in recent years a remarkable progress in the realization of integrated circuits at very high frequencies (operating frequency at 1 THz) and low noise. Few world players in microelectronics (none in France) have established performances reaching these THz frequencies. We propose to develop a technology that meets this demand.

We propose to develop InAlAs /InGaAs/InAs HEMT with THz cutoff frequency and low noise, mainly for reception-detection THz electronic system. The work will therefore focus on the determination of an optimal epitaxial structure using InAlAs/InGaAs/InAs materials by performing Hall effect measurements of several heterostructures, in order to determine the layer offering a better mobility / electronic charges tradeoff. The modifications of the transistor geometry (gate length, recess size and the spacings of the electrodes of the transistor) made it possible to considerably increase the operating frequency of the transistor. We achieved the characterizations of S-parameters up to 750 GHz and noise up to 110 GHz, in order to validate the technological optimizations.

Key words: HEMT, InP, InAlAs/InGaAs/InAs, asymmetric gate recess, high frequency, maximum oscillation frequency, noise-figure.

# Table des matières

| Remerciements                                                                            | i       |

|------------------------------------------------------------------------------------------|---------|

| Liste des figures                                                                        | viii    |

| Liste des tableaux                                                                       | xii     |

| Introduction générale                                                                    | 1       |

| Chapitre I : Introduction et performances des HEMTs InAlAs/InGaAs                        | 5       |

| I. Introduction du chapitre I                                                            |         |

| II. Filières technologiques du transistor à effet de champ                               | 6       |

| II.1. Histoire et évolution des HEMTs                                                    | 6       |

| II.2. Hétérojonction et formation du gaz bidimensionnel                                  | 7       |

| II.3. Transistor à effet de champ HEMT                                                   | 8       |

| II.3.1. Filières technologiques de HEMT à base de matériaux III-V                        | 9       |

| II.3.2. Évolution des technologies de HEMTs                                              | 12      |

| III. État de l'art statique, dynamique et en bruit de HEMT                               | 16      |

| III.1. Définition des caractéristiques électriques du transistor                         | 16      |

| III.1.1. Grandeurs statiques                                                             | 16      |

| III.1.2. Grandeurs dynamiques (Gain hyperfréquences et fréquences de transitions)        | 17      |

| III.1.3. Grandeur de bruit                                                               | 22      |

| III.2. Filière de transistors pour les applications millimétriques et sub-millimétriques | 23      |

| III.3. Paramètres ayant un impact sur les caractéristiques de HEMT (InAlAs/ InGaAs)      | 27      |

| III.3.1. Impact de $L_g$                                                                 | 27      |

| III.3.2. Impact du recess asymétrique                                                    | 28      |

| III.3.3. Impact de l'espacement drain-source                                             | 30      |

| IV. Circuits et Applications en bande millimétriques et sub-millimétriques               | 30      |

| IV.1. Circuits et applications MMICs                                                     | 30      |

| IV.2. État de l'art en bruit (transistors et circuits)                                   | 32      |

| V. Conclusion du chapitre I                                                              | 35      |

| Chapitre II : Réalisation et optimisation technologiques de HEMT de la                   | filière |

| InAlAs/InGaAs/InAs à canal composite sur un substrat d'InP                               |         |

| I. Introduction du chapitre II                                                           | 38      |

| II. Structure épitaxiale : Simulations et études expérimentales                          | 38      |

| II.1. Structure épitaxiale                                                               | 38      |

| II.2. Simulations et études expérimentales                                               | 40      |

| II.2.1. Potentiel de surface                                                             | 40      |

| II.2.2. Épaisseur de la couche « cap »                                                   | 42      |

|                                                                                                                                                                                                                                                                                                                                                                                                             | 43           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| II.2.4. Optimisation du contact ohmique                                                                                                                                                                                                                                                                                                                                                                     | 48           |

| II.2.5. Passivation de la structure                                                                                                                                                                                                                                                                                                                                                                         | 51           |

| II.2.6. Dénitruration de la structure                                                                                                                                                                                                                                                                                                                                                                       | 54           |

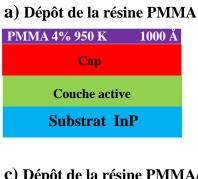

| III. Procédés et optimisations technologiques                                                                                                                                                                                                                                                                                                                                                               | 55           |

| III.1. Procédés de fabrication de HEMT                                                                                                                                                                                                                                                                                                                                                                      | 55           |

| III.2. Premier procédé de fabrication                                                                                                                                                                                                                                                                                                                                                                       | 59           |

| III.2.1. Marques d'alignement                                                                                                                                                                                                                                                                                                                                                                               | 59           |

| III.2.2. Mésa d'isolation                                                                                                                                                                                                                                                                                                                                                                                   | 60           |

| III.2.3. Contacts ohmiques                                                                                                                                                                                                                                                                                                                                                                                  | 60           |

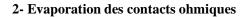

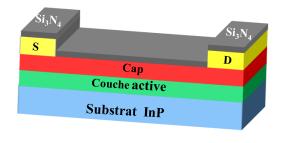

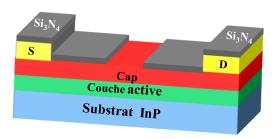

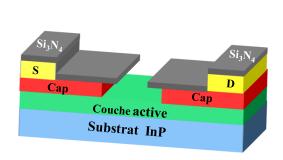

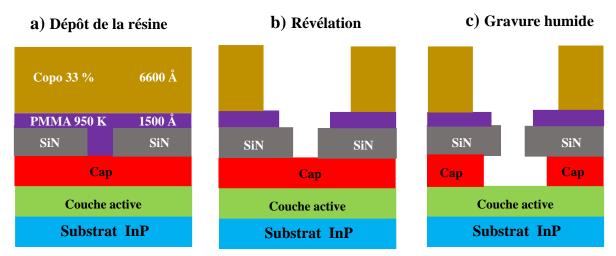

| III.2.4. Dépôt de Si <sub>3</sub> N <sub>4</sub> et gravure plasma RIE                                                                                                                                                                                                                                                                                                                                      | 62           |

| III.2.5. Recess et réalisation de la grille                                                                                                                                                                                                                                                                                                                                                                 | 64           |

| III.2.6. Plots d'épaississement                                                                                                                                                                                                                                                                                                                                                                             | 66           |

| III.2.7. Résultats et discussions du procédé 1                                                                                                                                                                                                                                                                                                                                                              | 67           |

| III.3. Deuxième procédé de fabrication                                                                                                                                                                                                                                                                                                                                                                      | 68           |

| III.3.1. Réalisation du recess et de l'électrode de grille                                                                                                                                                                                                                                                                                                                                                  | 70           |

| IV. Réajustement des accès coplanaires en 25 µm de pitch                                                                                                                                                                                                                                                                                                                                                    | 71           |

| V. Conclusion du chapitre II                                                                                                                                                                                                                                                                                                                                                                                | 73           |

| Chapitre III : Caractérisation de HEMT : Mesures statiques, dynamic                                                                                                                                                                                                                                                                                                                                         | miques et en |

| bruit                                                                                                                                                                                                                                                                                                                                                                                                       | 75           |

| I. Introduction du chapitre III                                                                                                                                                                                                                                                                                                                                                                             | 76           |

| II. Caractérisations des transistors des procédés 1 et 2                                                                                                                                                                                                                                                                                                                                                    | 76           |

| III. Caractérisations en régime statique                                                                                                                                                                                                                                                                                                                                                                    | 77           |

|                                                                                                                                                                                                                                                                                                                                                                                                             | 77           |

| III.1. Caractérisations statiques du procédé 1                                                                                                                                                                                                                                                                                                                                                              | / /          |

| III.1. Caractérisations statiques du procédé 1                                                                                                                                                                                                                                                                                                                                                              |              |

| • •                                                                                                                                                                                                                                                                                                                                                                                                         | 80           |

| III.2. Caractérisations statiques du procédé 2                                                                                                                                                                                                                                                                                                                                                              | 80<br>84     |

| III.2. Caractérisations statiques du procédé 2  IV. Outils de caractérisations en régime dynamique                                                                                                                                                                                                                                                                                                          |              |

| III.2. Caractérisations statiques du procédé 2                                                                                                                                                                                                                                                                                                                                                              |              |

| III.2. Caractérisations statiques du procédé 2  IV. Outils de caractérisations en régime dynamique  IV.1. Étalonnage Off-wafer  IV.2. Étalonnage On-wafer                                                                                                                                                                                                                                                   |              |

| III.2. Caractérisations statiques du procédé 2  IV. Outils de caractérisations en régime dynamique  IV.1. Étalonnage <i>Off-wafer</i> IV.2. Étalonnage <i>On-wafer</i> V. Caractérisations dynamiques jusque 110 GHz.                                                                                                                                                                                       |              |

| III.2. Caractérisations statiques du procédé 2  IV. Outils de caractérisations en régime dynamique  IV.1. Étalonnage <i>Off-wafer</i> IV.2. Étalonnage <i>On-wafer</i> V. Caractérisations dynamiques jusque 110 GHz  V.1. Caractérisations dynamiques du procédé 1                                                                                                                                         |              |

| III.2. Caractérisations statiques du procédé 2  IV. Outils de caractérisations en régime dynamique  IV.1. Étalonnage <i>Off-wafer</i> IV.2. Étalonnage <i>On-wafer</i> V. Caractérisations dynamiques jusque 110 GHz  V.1. Caractérisations dynamiques du procédé 1  V.1.1. Comparaison de la couche cap                                                                                                    |              |

| III.2. Caractérisations statiques du procédé 2  IV. Outils de caractérisations en régime dynamique  IV.1. Étalonnage Off-wafer  IV.2. Étalonnage On-wafer  V. Caractérisations dynamiques jusque 110 GHz  V.1. Caractérisations dynamiques du procédé 1  V.1.1. Comparaison de la couche cap  V.1.2. Impact de l'espacement drain-source L <sub>SD</sub>                                                    |              |

| III.2. Caractérisations statiques du procédé 2  IV. Outils de caractérisations en régime dynamique  IV.1. Étalonnage Off-wafer  IV.2. Étalonnage On-wafer  V. Caractérisations dynamiques jusque 110 GHz  V.1. Caractérisations dynamiques du procédé 1  V.1.1. Comparaison de la couche cap  V.1.2. Impact de l'espacement drain-source L <sub>SD</sub> V.1.3. Impact de longueur de grille L <sub>g</sub> |              |

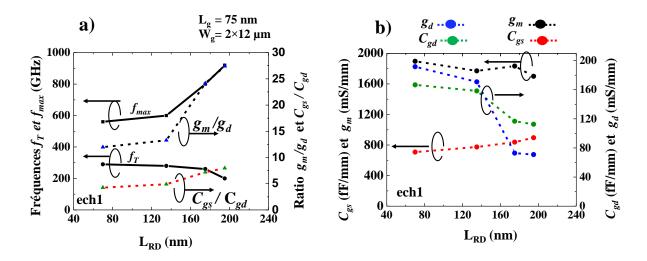

| VI.1. Origines du bruit dans un HEMT                                    | 96  |

|-------------------------------------------------------------------------|-----|

| VI.1.1. Bruit d'un quadripôle                                           | 97  |

| VI.1.2. Modèles de bruit de HEMT et méthodes de mesure                  | 99  |

| VI.1.3. Description du Banc de mesure                                   | 102 |

| VI.1.4. Étalonnage du banc de mesure                                    | 104 |

| VI.2. Mesure de bruit jusque 110 GHz                                    | 106 |

| VI.2.1. Épluchage des accès coplanaires                                 | 106 |

| VI.2.2. Mesure de NF <sub>50</sub>                                      | 107 |

| VI.2.3. Méthode d'extraction                                            | 108 |

| VI.2.3.1. Détermination du schéma équivalent                            | 108 |

| VI.2.3.2. Détermination de $T_{out}$                                    | 109 |

| VI.2.3.3. Extraction des quatre paramètres de bruit                     | 110 |

| VII. Conclusion du chapitre III                                         | 112 |

| Chapitre IV : Mesure et deembedding au-delà de 110 GHz et perspectives  | 113 |

| I. Introduction du chapitre IV                                          | 114 |

| II. Mesures et épluchage des transistors HEMTs                          | 114 |

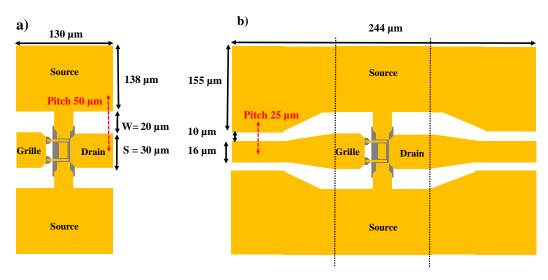

| II.1. Topologie des accès coplanaires du transistor                     | 114 |

| II.2. Mesure des étalons d'épluchage « Open-Short »                     | 116 |

| II.3. Mesure du transistor                                              | 118 |

| III. Étude des lignes coplanaires en large bande                        | 122 |

| III.1. Influence de la topologie des lignes coplanaires                 | 122 |

| III.2. Méthode d'extraction des caractéristiques des lignes coplanaires | 124 |

| III.3. Mesure et extraction des caractéristiques de ligne coplanaire    | 126 |

| IV. Conclusion du chapitre IV                                           | 131 |

| Conclusion générale et perspectives                                     | 133 |

| Annexes                                                                 | 137 |

| Liste des publications                                                  | 145 |

| Références                                                              | 147 |

# Liste des figures

| Figure-Intro. 1-Photographie du HEMT en coupe transversale de $L_g = 25$ nm et b) Circuit TMIC                                                         |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| réalisé                                                                                                                                                | 1 |

| Figure-Intro. 2-a) Photographie du HEMT en coupe transversale de $L_g=75\mathrm{nm}$ et b) Gains mesurés                                               | 2 |

| Figure I.1-Structure épitaxiale du MESFET                                                                                                              | 7 |

| Figure I.2-Comparaison de la structure de bande d'une hétérojonction entre un matériau de petit-gap e                                                  |   |

| de grand-gap                                                                                                                                           |   |

| Figure I.3-Structure épitaxiale du HEMT                                                                                                                |   |

| Figure I.4- Alignement des bandes de conduction et de valence en fonction du paramètre de maille                                                       | フ |

| [11]                                                                                                                                                   | 1 |

| Figure I.5-Evolution du marché des applications de type MMIC à base de technologie HEMT [15] 1                                                         |   |

| Figure I.6-Difference de la structure de bande du HEMT entre un canal simple et composite                                                              |   |

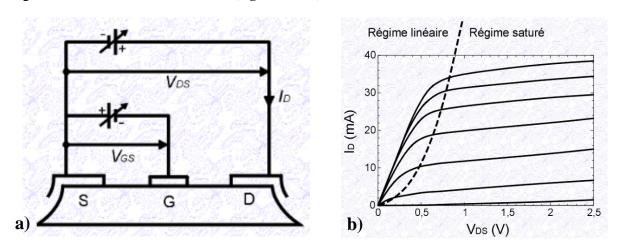

| Figure I.7- a) Polarisation d'un transistor à effet de champ. b) caractéristiques $I_D(V_{DS})$ [26]                                                   |   |

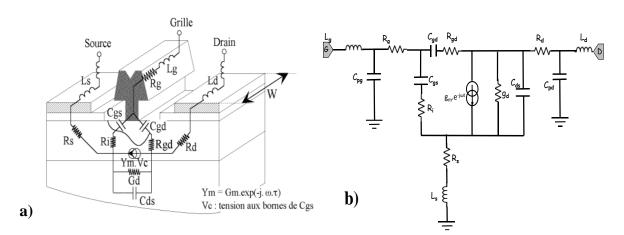

| Figure I.8-a) Localisation physique des éléments du schéma équivalent [10]. b) schéma équivalent                                                       | U |

| petit signal du transistor HEMT                                                                                                                        | g |

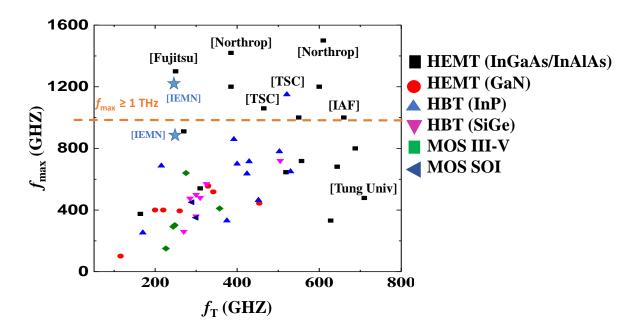

| Figure I.9-Etat de l'art de figure de mérite de couple $f_T/f_{\text{max}}$ , des transistors à base de matériaux III-V e                              |   |

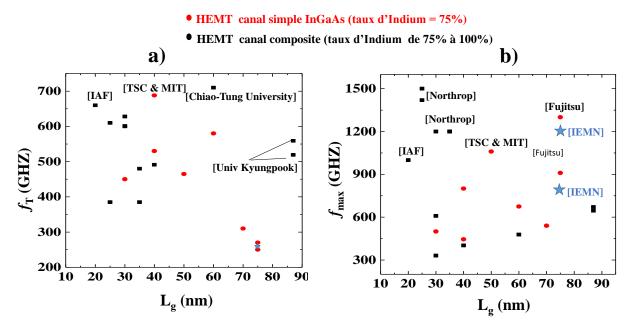

| Silicium de différents laboratoires et industries                                                                                                      |   |

| Figure I.10-Etat de l'art de figures de mérites $f_T$ et $f_{max}$ en fonction de $L_g$ pour deux types du canal 2                                     |   |

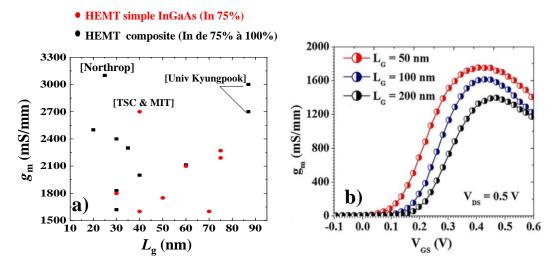

| Figure I.11-Impact de longueur de grille $L_g$ sur les caractéristiques de HEMT : (a) état de l'art de $g_m$ et                                        |   |

| fonction de $L_g$ , (b) impact de Lg sur gm d'un In <sub>0.70</sub> Ga <sub>0.3</sub> As PHEMT, (b : [77])                                             |   |

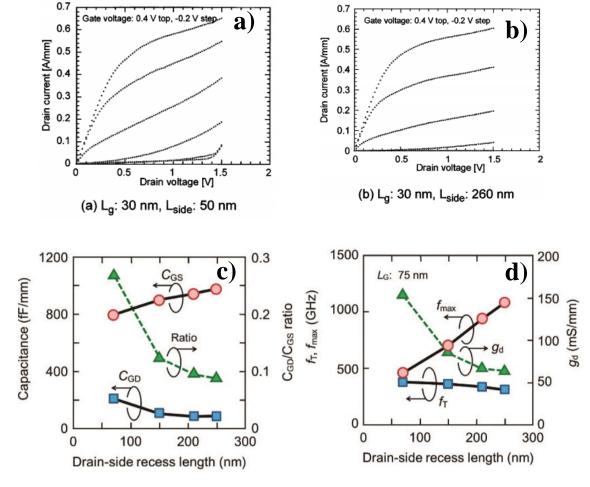

| Figure I.12-Impact de $L_{side}$ sur les caractéristiques du HEMT (a) et (b) dans [79], (c) et (d) dans [20] 2                                         |   |

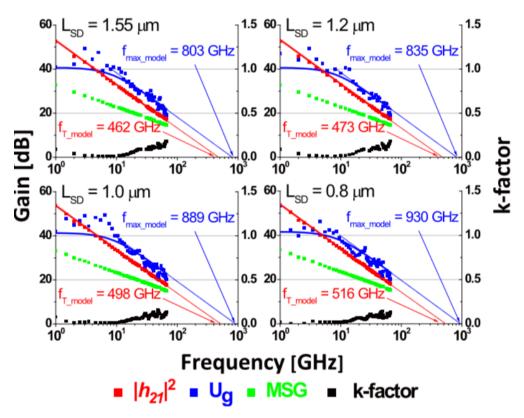

| Figure I.13-Impact de l'espacement drain-source $L_{SD}$ sur les caractéristiques du HEMT [48]                                                         |   |

| Figure I.14Diversité des applications millimétriques et sub-millimétriques des MMICs [81] 3                                                            |   |

| Figure I.15-Photographie de LNA à base d'un MHEMT à 600 GHz développé par IAF                                                                          |   |

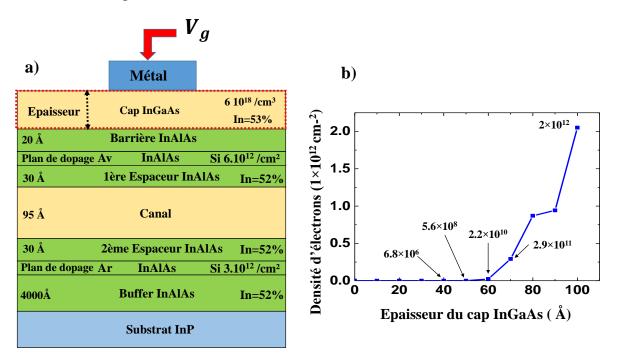

| Figure II.1-Structure épitaxiale initiale du HEMT à double-plan de dopage                                                                              |   |

| Figure II.2-Présentation des bandes de conduction et de valence des matériaux III-V en fonction 4                                                      |   |

| Figure II.3- Potentiel de surface et tension $V_g$ d'un Bulk d'InGaAs : a) expérimental et b) simulation 4                                             |   |

| Figure II.4-Densité d'électrons dans le cap InGaAs en fonction de son épaisseur                                                                        |   |

| Figure II.5-Structure épitaxiale du HEMT à double-plan de dopage : a-Structure de départ et b-                                                         |   |

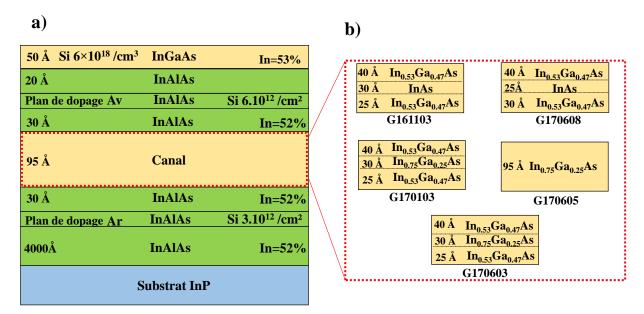

| différentes architectures de canal                                                                                                                     | 3 |

| Figure II.6-Structure épitaxiale du HEMT à différent double-plan de dopage : a-Structure à canal                                                       |   |

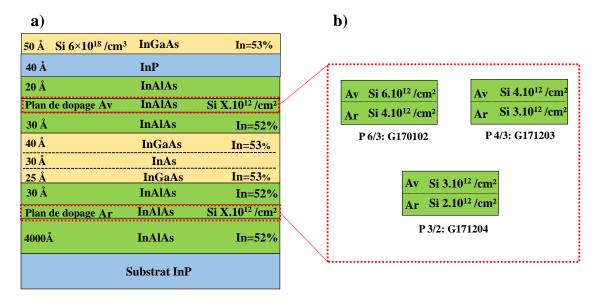

| optimisé b-trois combinaisons de dopage4                                                                                                               | 7 |

| Figure II.7-Méthode TLM appliquée sur la structure HEMTs à cap composite                                                                               |   |

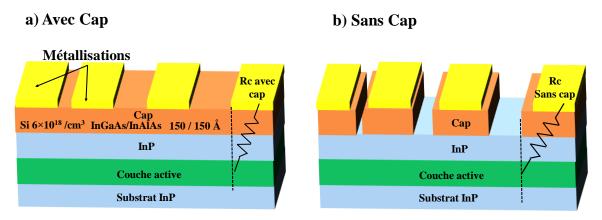

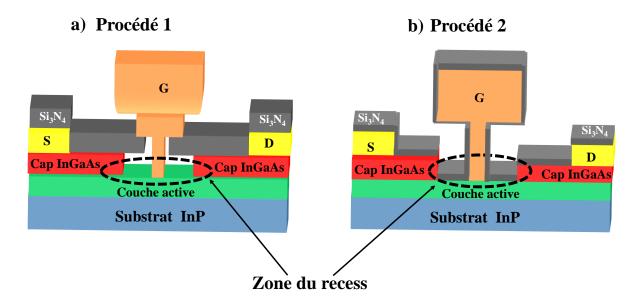

| Figure II.8-Passivation de zone du recess pour les deux procédés de fabrication                                                                        | 2 |

| Figure II.9-a-Structure épitaxiale, b- schéma représentatifs des échantillons mesurés par effet Hall 5                                                 | 3 |

| Figure II.10- Principales étapes du premier procédé pour la réalisation du HEMT                                                                        | 7 |

| Figure II.11-Principales étapes du deuxième procédé pour la réalisation du HEMT5                                                                       | 8 |

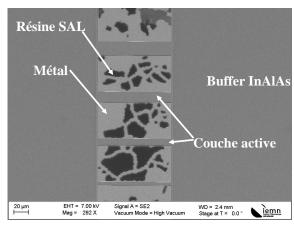

| Figure II.12-Problème du résidu de la résine SAL 601 sur les contacts ohmiques                                                                         | 9 |

| Figure II.13-(a), (b), (c), et (d) schémas représentatifs des étapes de la gravure humide de mésa                                                      |   |

| d'isolation, (e) et (f) images MEB d'une couche active du transistor                                                                                   | 0 |

| Figure II.14- Observation au MEB du problème d'effet de proximité en fonction du développement et                                                      |   |

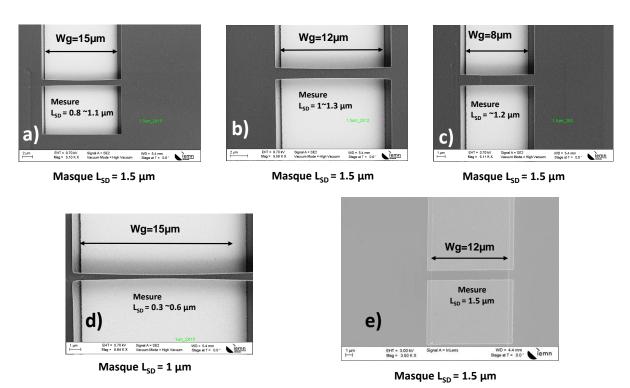

| de la distance $L_{SD}$ 6                                                                                                                              | 1 |

| Figure II.15-a) Schéma représentatif du contact ohmique, b) images MEB de réalisation des contacts                                                     |   |

| ohmiques Ti/Pt/Au6                                                                                                                                     |   |

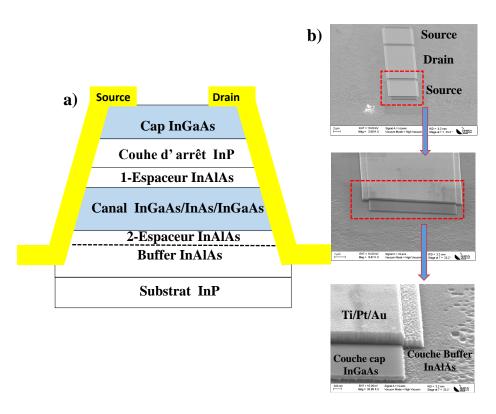

| Figure II.16- Schéma représentatif :a) dépôt de 30 nm de Si <sub>3</sub> N <sub>4</sub> et b) ouverture de Si <sub>3</sub> N <sub>4</sub> par plasma 6 | 2 |

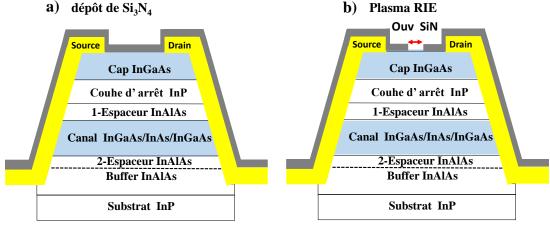

| Figure II.17-Images MEB des ouvertures obtenues à travers le nitrure                                                                                                              | . 63 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

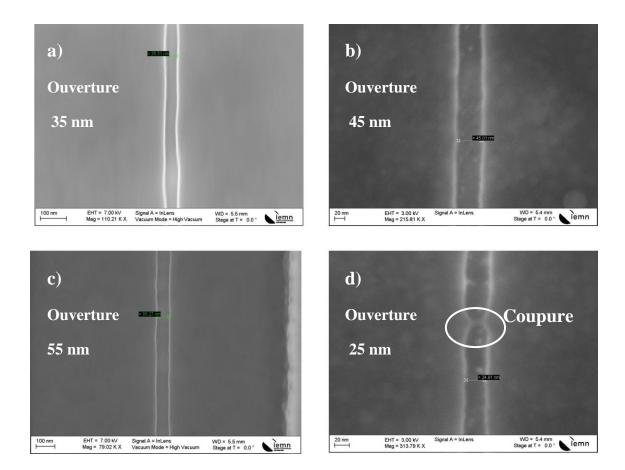

| Figure II.18-Etape de définition du recess de grille                                                                                                                              | . 64 |

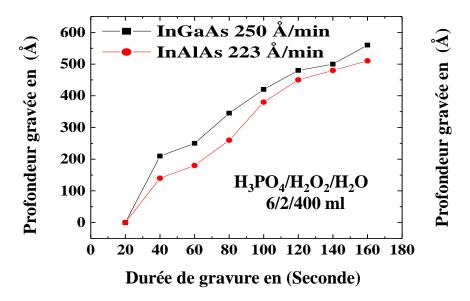

| Figure II.19-Vitesse de gravure des matériaux In <sub>0.53</sub> Ga <sub>0.47</sub> As et In <sub>0.52</sub> Al <sub>0.48</sub> As par la solution H <sub>3</sub> OP <sub>4</sub> | . 65 |

| Figure II.20-Gravure d'un cap composite In <sub>0.53</sub> Ga <sub>0.47</sub> As / In <sub>0.52</sub> Al <sub>0.48</sub> As par la solution H <sub>3</sub> OP <sub>4</sub>        | . 65 |

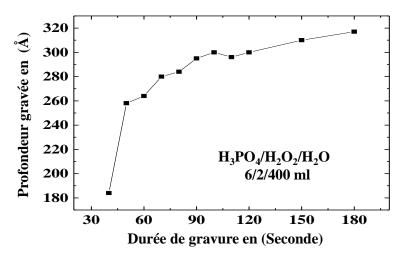

| Figure II.21- a) Schéma représentatif du transistor après dépôt de la grille- b), c) et d) Images MEB                                                                             |      |

| d'un transistor à deux doigts de grille                                                                                                                                           | . 66 |

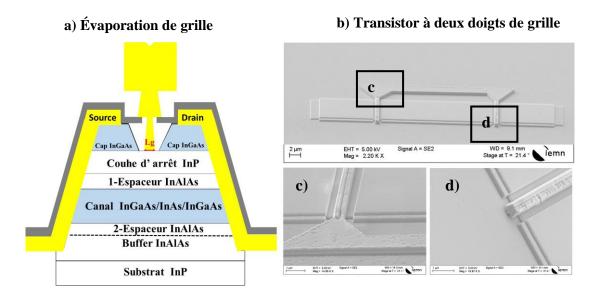

| Figure II.22- Images MEB de a) position des zones de nitrure à graver avant le dépôt des plots, b)                                                                                |      |

| transistor après gravure du nitrure dans les zones de contact source et drain et c) transistor aprè                                                                               | ès   |

| dépôt des plots d'épaississement                                                                                                                                                  | . 67 |

| Figure II.23-Images MEB de différentes longueurs de grille du premier procédé                                                                                                     | . 68 |

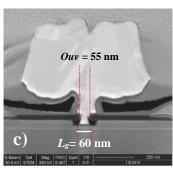

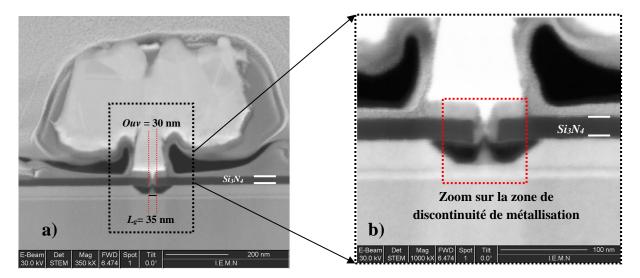

| Figure II.24-Images MEB représentantes le problème de discontinuité de métallisations a) ouverture                                                                                |      |

| de nitrure de 30 nm et b) zoom sur la zone de discontinuité                                                                                                                       |      |

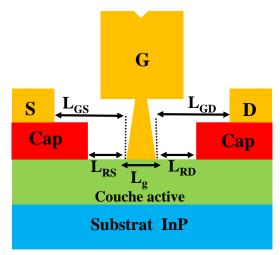

| Figure II.25-Schéma représentatif des principales longueurs définissent le deuxième procédé de                                                                                    |      |

| fabrication                                                                                                                                                                       | . 69 |

| Figure II.26-Etapes de réalisation du recess et de grille du deuxième procédé                                                                                                     |      |

| Figure II.27-Imges FIB pour deux transistors avec recess : a) symétrique et b) asymétrique                                                                                        |      |

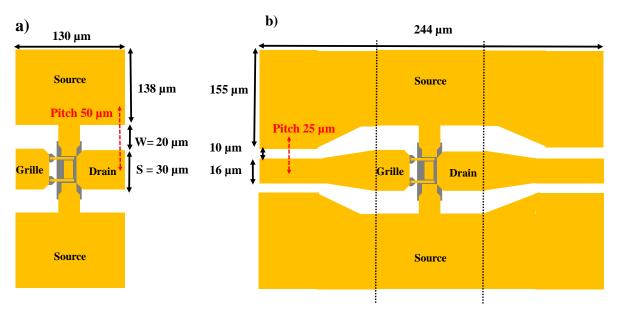

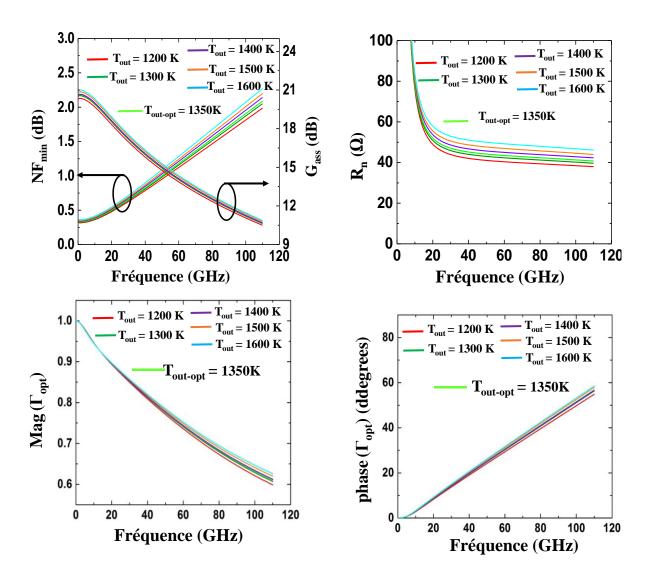

| Figure II.28-Adaptation du pitch des accès coplanaire : a) transistor initial de 50 µm de pitch ; b)                                                                              |      |

| transistor après réajustement de pitch à 25µm                                                                                                                                     | . 72 |

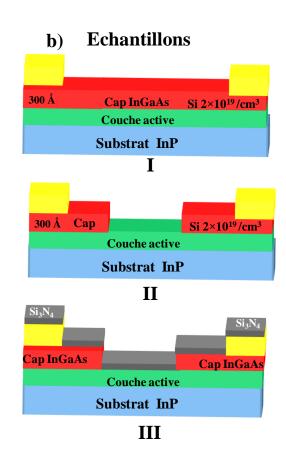

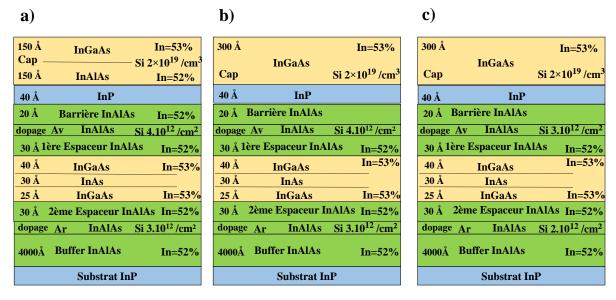

| Figure III.1-Structures épitaxiales utilisées pour concevoir les transistors HEMT du procédé 1 et 2                                                                               |      |

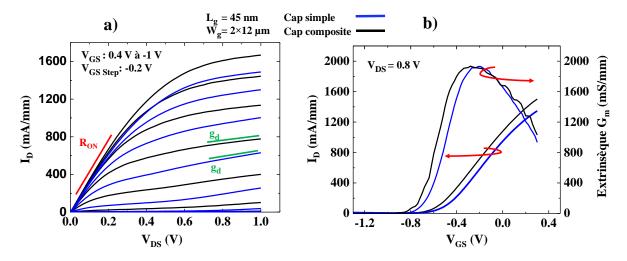

| Figure III.2-Caractéristiques de sortie et de transfert pour deux composants de $L_g = 45$ nm et $W_g = 25$                                                                       |      |

| μm                                                                                                                                                                                |      |

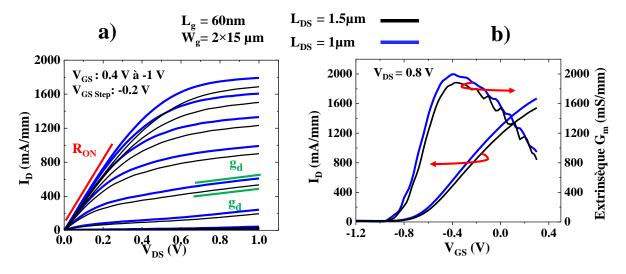

| Figure III.3-Caratéristiques de sortie et du transfert de deux composants avec $L_g = 60$ nm et $W_g = 2x$                                                                        |      |

| μm                                                                                                                                                                                |      |

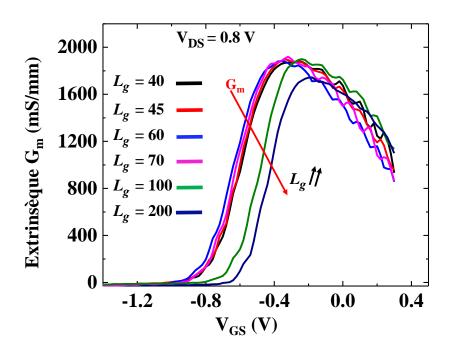

| Figure III.4-Effet de longueur de grille sur la transconductance des transistors de $W_g = 2 \times 15 \mu\text{m}$                                                               |      |

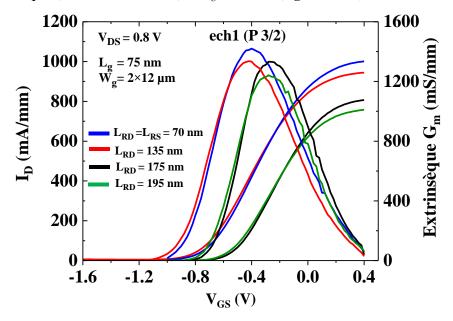

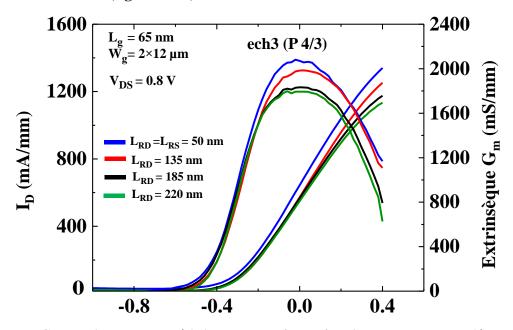

| Figure III.5-Comparaison des caractéristiques de transfert en fonction du recess $L_{RD}$ de l'échantillon                                                                        |      |

| Tigure time Comparation des caracteristiques de transfert en fonction du recess E <sub>RD</sub> de l'estation en                                                                  |      |

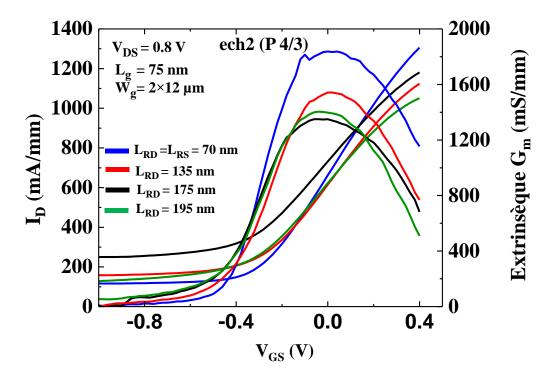

| Figure III.6- Comparaison des caractéristiques de transfert en fonction du recess $L_{RD}$ de l'échantillor                                                                       |      |

| Tigure 11.0 Comparation des caracteristiques de transfert en fonction du recess $D_{RD}$ de l'echantimor                                                                          |      |

| Figure III.7- Comparaison des caractéristiques de transfert en fonction du recess $L_{RD}$ de l'échantillor                                                                       |      |

| Tigure III. Comparation des caracteristiques de transfert en fonction du fecess $E_{RD}$ de l'echantimor                                                                          |      |

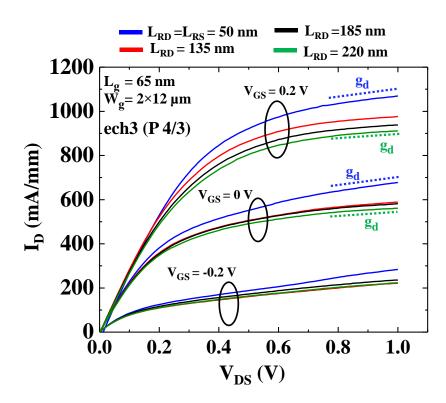

| Figure III.8-Comparaison des caractéristiques de sorties en fonction de la longueur du recess $L_{RD}$ de                                                                         |      |

| 1'échantillon 3 avec (P4/3)                                                                                                                                                       |      |

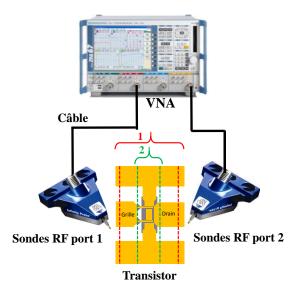

| Figure III.9-Synoptique d'un banc de mesure de paramètres S [250 MHz – 110 GHz]                                                                                                   |      |

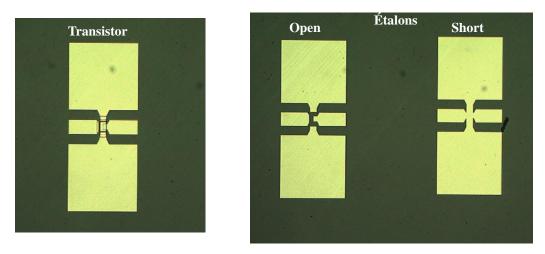

| Figure III.10-Topologie de lignes coplanaires du transistor et les étalons d'épluchage associés de 50                                                                             |      |

| µm de pitch                                                                                                                                                                       |      |

| Figure III.11-Procédure d'épluchage des accès par la technique Open-Short                                                                                                         |      |

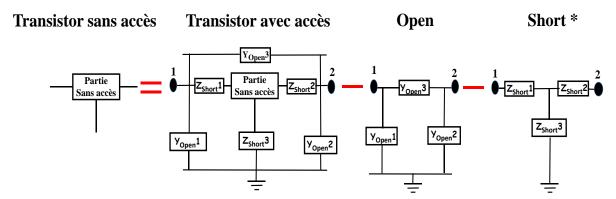

| Figure III.12-Méthode de calcul de paramètres de Short*                                                                                                                           |      |

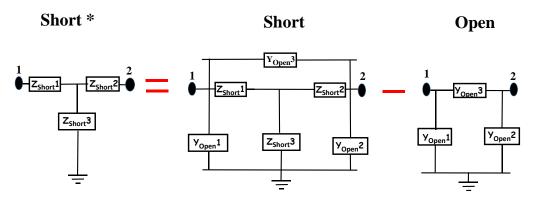

| Figure III.13-Evolution fréquentielle des gains ; a) gain unilatéral de Mason U et b) gain en courant                                                                             |      |

| $h21^2$ pour deux transistors de couche cap simple et composite                                                                                                                   |      |

|                                                                                                                                                                                   | . 00 |

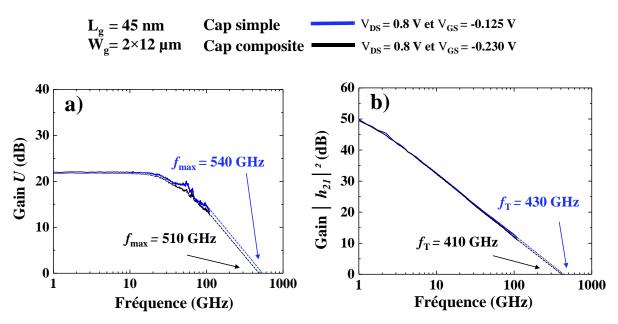

| Figure III.14-Comparaison des paramètres S mesurés et modélisés sous ADS pour le transistor à                                                                                     | 00   |

| couche cap simple.                                                                                                                                                                | . 90 |

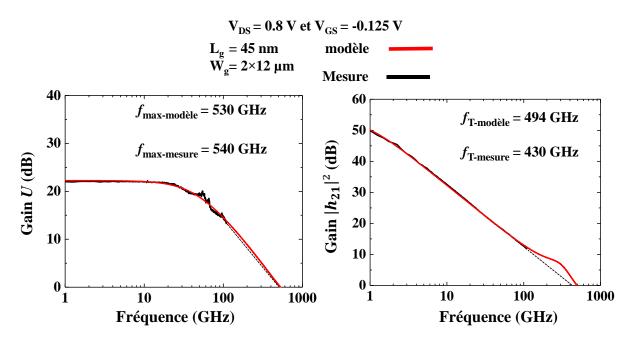

| Figure III.15-Évolution fréquentielle des gains $U$ et $h21^2$ mesurés et modélisés sous ADS pour le                                                                              | 00   |

| transistor à couche cap simple                                                                                                                                                    |      |

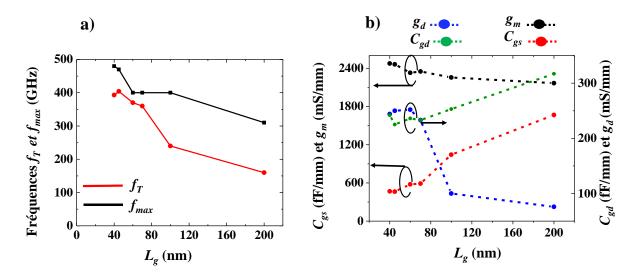

| Figure III.16-Impact de longueur de grille $L_g$ sur les performances du transistor                                                                                               |      |

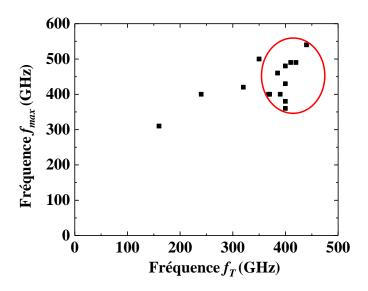

| Figure III.17-Recapitulatif du couple $f_T/f_{\text{max}}$ obtenues sur des composants du premier procédé                                                                         | . 93 |

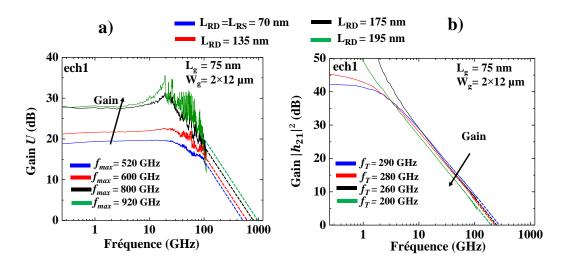

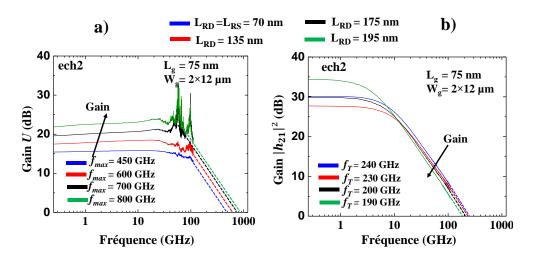

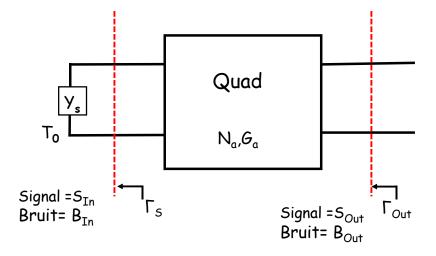

| Figure III.18-Évolution fréquentielle des Gains mesurés de « l'ech1 » en fonction de $L_{RD}$ pour des                                                                            |      |

| transistors de $L_g = 75$ nm et $Wg = 2 \times 12 \mu \text{m}$                                                                                                                   | . 94 |

| Figure III.19- Évolution fréquentielle des Gains mesurés de « l'ech2 » en fonction de $L_{RD}$ pour des         |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| transistors de $Lg = 75$ nm et $Wg = 2 \times 12 \mu \text{m}$                                                  | 94 |

| Figure III.20- Évolution fréquentielle des Gains mesurés de « l'ech3 » en fonction de $L_{RD}$ pour des         |    |

| transistors de $L_g = 65$ nm et $Wg = 2 \times 12 \mu \text{m}$                                                 | 94 |

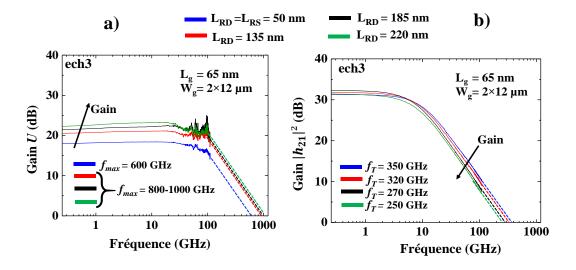

| Figure III.21-Evolution de paramètres du schéma équivalent petit signal et fréquences fmax des                  |    |

| composants de « ech1 » en fonction de longueur $L_{RD}$                                                         | 96 |

| Figure III.22-Description de bruit dans un quadripôle                                                           | 98 |

| Figure III.23-Modèle bruit de type Van Der Ziel d'un TEC avec deux sources de bruit en courant 1                | 00 |

| Figure III.24-modèle de bruit de Pospieszalski                                                                  | 01 |

| Figure III.25-Modèle bruit <i>NF</i> <sub>50</sub> d'un HEMT avec deux sources de bruit                         | 02 |

| Figure III.26- Photographie du banc de mesure du facteur de bruit sous 50 $\Omega$ en bande [6 GHz – 42         |    |

| GHZ]1                                                                                                           | 03 |

| Figure III.27- Synoptique du banc de mesure du facteur de bruit sous $50 \Omega$ en bande [6 GHz $-42$          |    |

| GHz]1                                                                                                           | 03 |

| Figure III.28- Photographie du banc de mesure du facteur de bruit sous 50Ω en bande W [75 GHz –                 |    |

| 110 GHZ]1                                                                                                       | 04 |

| Figure III.29- Synoptique du banc de mesure du facteur de bruit sous $50\Omega$ en bande W [75 GHz –            |    |

| 110 GHZ]1                                                                                                       | 04 |

| Figure III.30-Synoptique du banc de mesure du facteur de bruit sous 50 $\Omega$                                 | 05 |

| Figure III.31- Évolution fréquentielle des gains du transistor représentatif de « ech1 »                        | 06 |

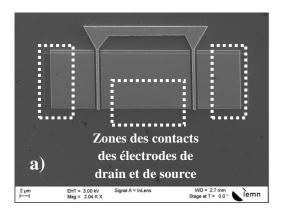

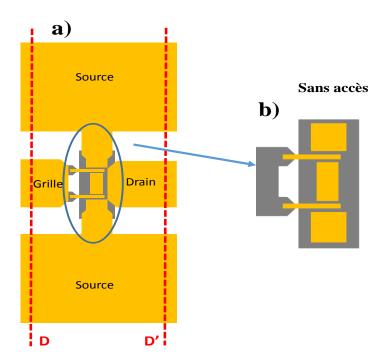

| Figure III.32-Photographie du transistor a) avec accès et b) sans accès coplanaires                             | 07 |

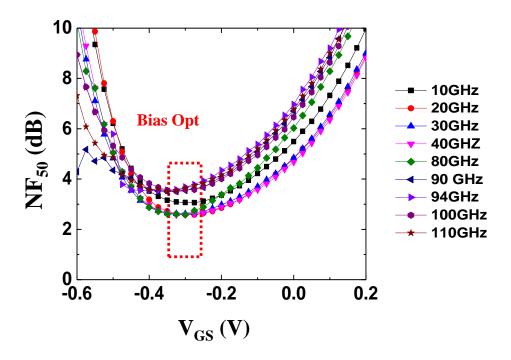

| Figure III.33-Mesure de $NF_{50}$ en fonction de la tension $V_{GS}$ à $V_{DS}$ =1V pour plusieurs fréquences 1 | 08 |

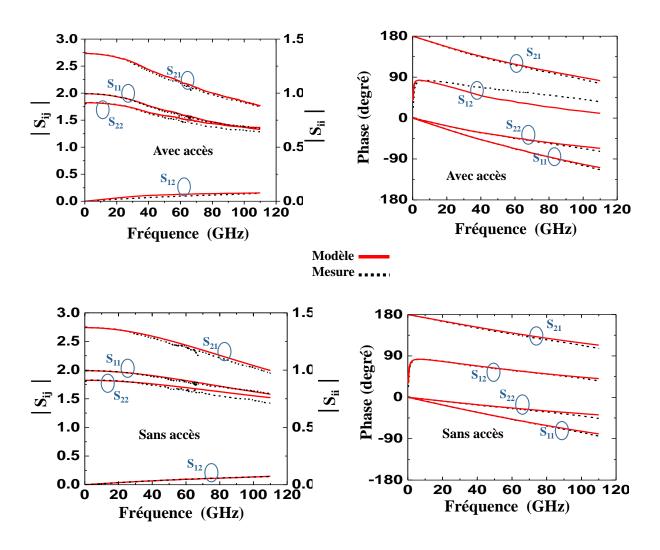

| Figure III.34-Comparaison de paramètres S mesurés et simulés à partir d'un schéma équivalent petit              |    |

| signal avec et sans accès coplanaires du transistor                                                             | 09 |

| Figure III.35-Facteur de bruit NF50 mesuré et simulé jusque 110 GHz à $T_{out}$ variable d'un transistor        | de |

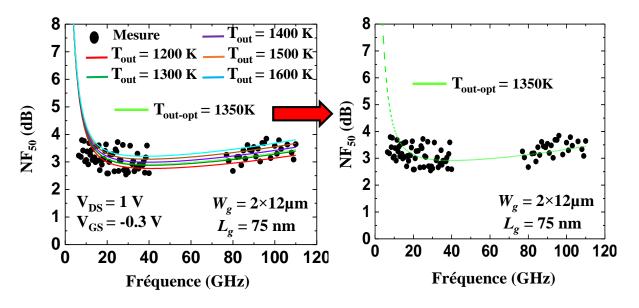

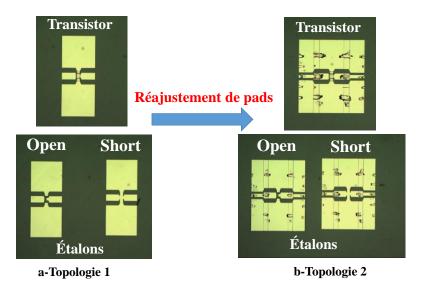

| Wg= 2×12 μm et Lg= 75 nm du deuxième procédé « ech1 »                                                           | 10 |

| Figure III.36-Extraction des quatre paramètres de bruit jusque 110 GHz à Tout variable d'un transisto           | r  |

| de $Wg=2\times12~\mu m$ et $L_g=75~nm$ du deuxième procédé                                                      | 11 |

| Figure IV.1-Adaptation du pitch des accès coplanaire : a) transistor initial de 50 µm de pitch et b)            |    |

| transistor après le réajustement du pitch à 25µm1                                                               | 15 |

| Figure IV.2-Topologies 1 et 2 des transistors et les étalons d'épluchage associés de a) 50 µm de pitch          | l  |

| et b) 25 µm de pitch                                                                                            | 15 |

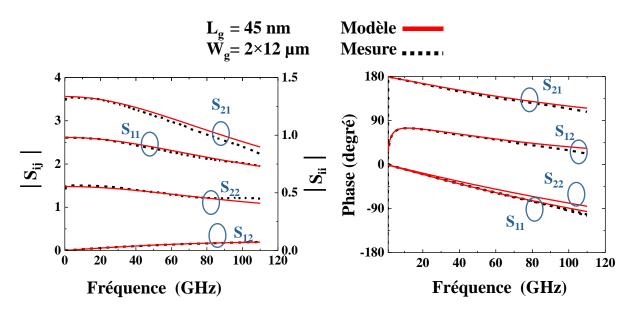

| Figure IV.3-Paramètres S de l'étalon Open                                                                       | 16 |

| Figure IV.4-Paramètres S de l'étalon Short                                                                      | 17 |

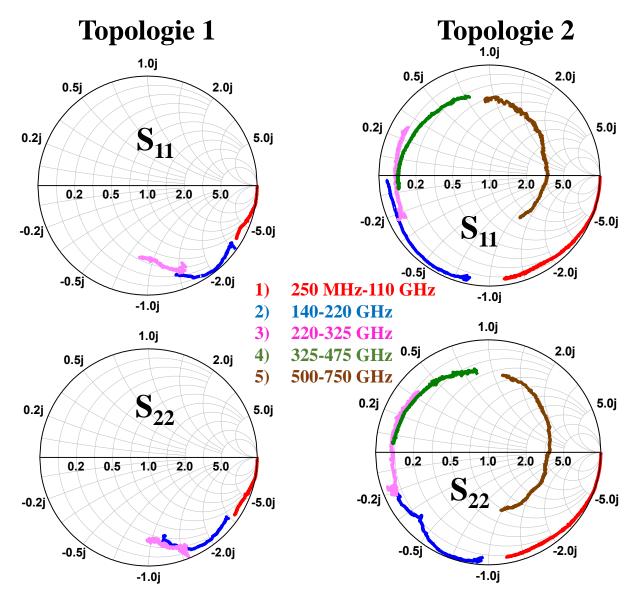

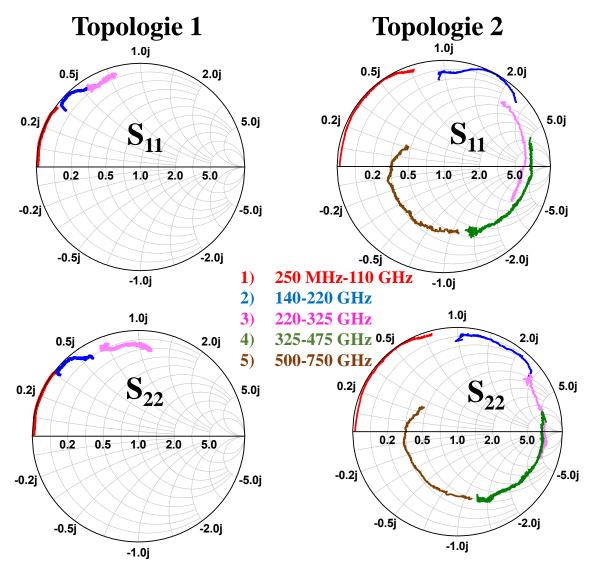

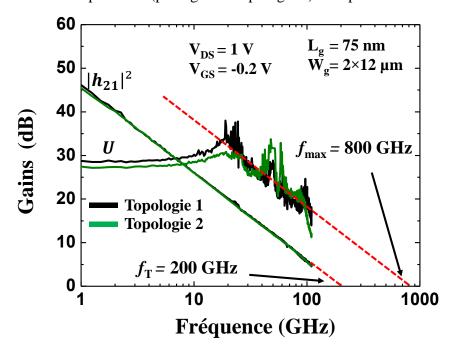

| Figure IV.5-Evolution fréquentielle des gains U et  h21  ² dans la bande [250 MHz – 110 GHz] de                 |    |

| transistors avec recess asymétrique ( $L_{RS}$ = 70 nm et $L_{RD}$ = 195 nm) pour les deux topologies 1         | 18 |

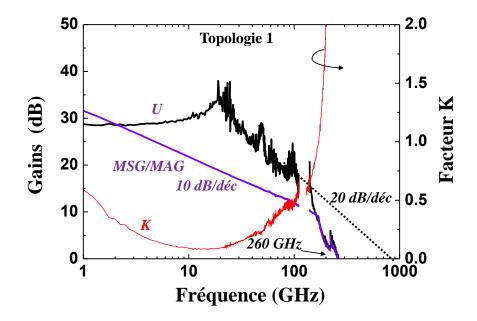

| Figure IV.6-Evolution fréquentielle des gains <i>U, MSG/MAG</i> et du facteur de stabilité K dans les           |    |

| bandes [250 MHz – 110 GHz], [140 GHz – 220 GHz] et [220 GHz – 325 GHz] du transistor de                         | ,  |

| la topologie 1                                                                                                  | 19 |

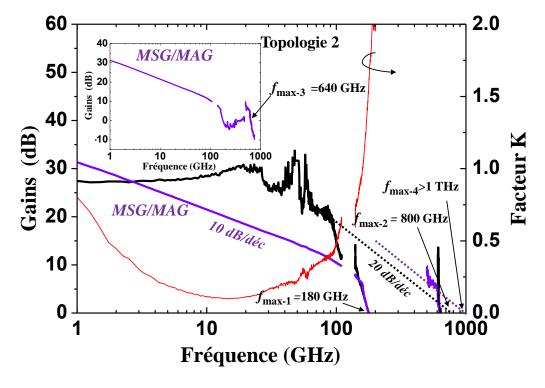

| Figure IV.7-Evolution fréquentielle des gains <i>U, MSG/MAG</i> et du facteur de stabilité K du transistor      |    |

| de la topologie 2 dans toutes les bandes (250 MHz jusqu'à 750 GHz)1                                             | 19 |

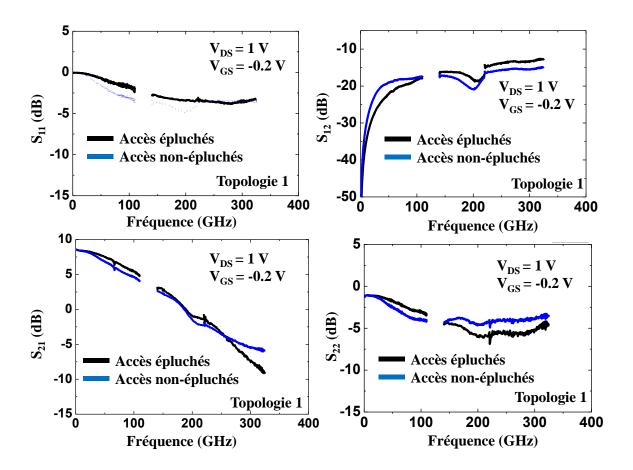

| Figure IV.8-Paramètres S du transistor de la topologie 1 avec et sans correction                                |    |

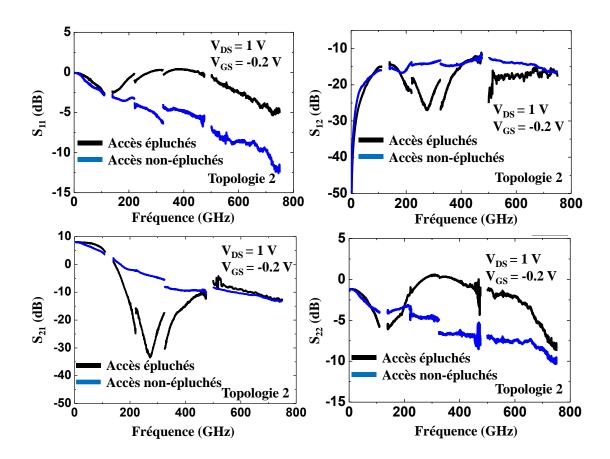

| Figure IV.9-Paramètres S du transistor de la topologie 2 avec et sans correction                                | 22 |

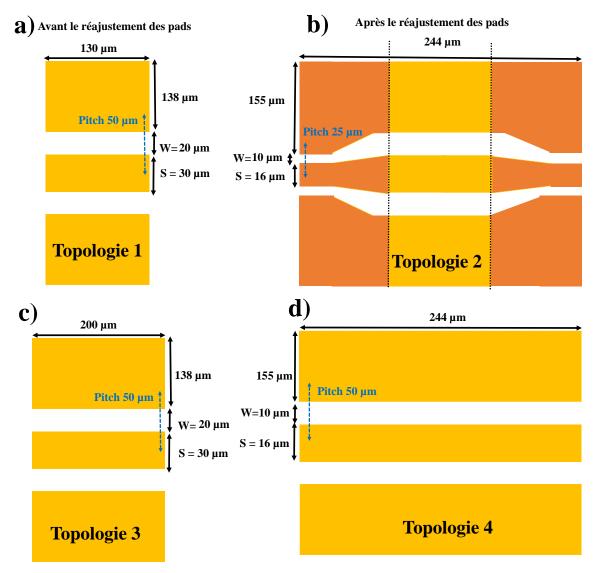

| Figure IV.10- Topologies de lignes coplanaires correspondant aux transistors mesurés. a) Topologie              | 1  |

| identique à celle des accès du transistor, b) topologie 2 accès du transistor avec réajustement de              |    |

| la distance inter-masse, c) topologie 3 et d) topologie 4                                                       |    |

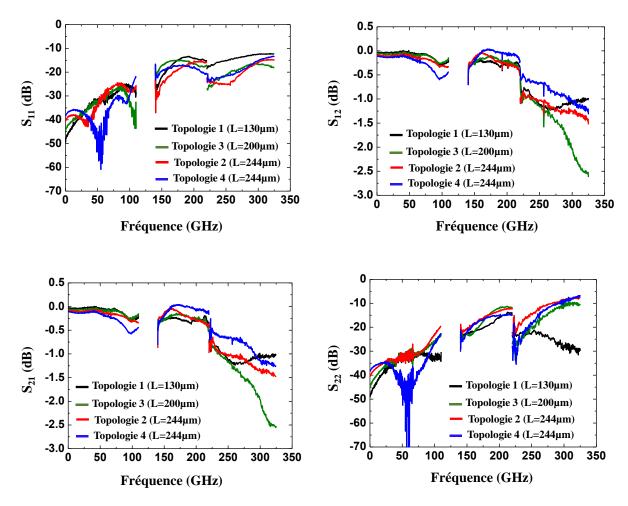

| Figure IV.11- Évolution fréquentielle de quatre paramètres S de 250 MHz jusque 325 GHz pour les                 |    |

| quatre topologies                                                                                               | 27 |

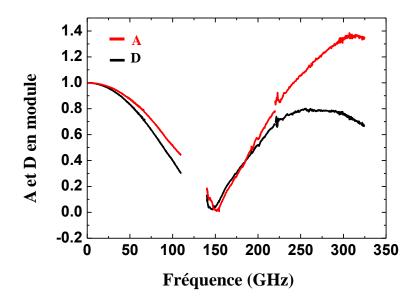

| Figure IV.12- Comparaison des éléments A et D de la matrice chaine                             | 128     |

|------------------------------------------------------------------------------------------------|---------|

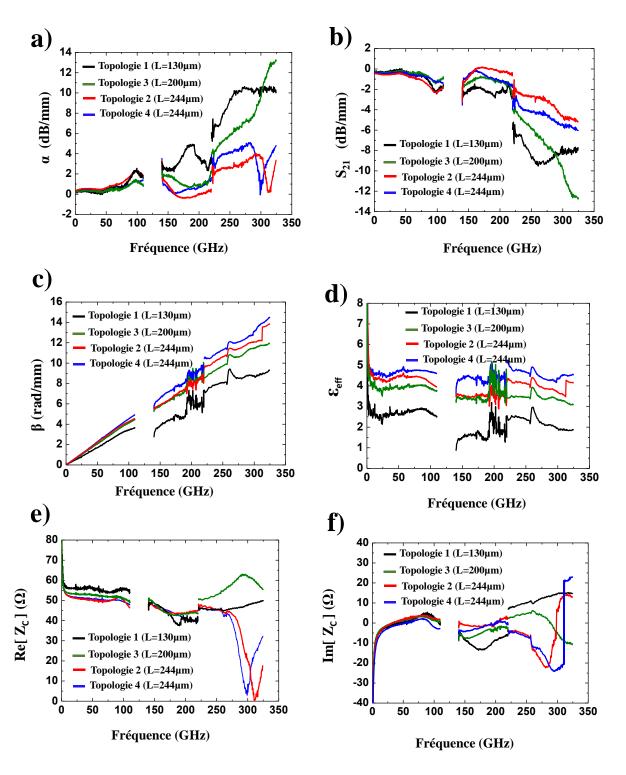

| Figure IV.13- Évolution fréquentielle de quatre paramètres de propagation de 250 MHz jusque    | e 325   |

| GHz pour les quatre topologies                                                                 | 130     |

| Figure-Conc. 1Images MEB pour un transistor a grille décentré de 200 nm et b) évolution        |         |

| fréquentielle des gains $U$ et $ h_{21} ^2$                                                    | 135     |

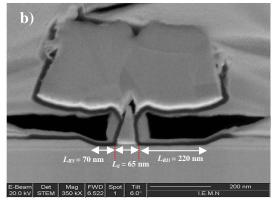

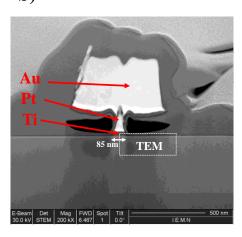

| Figure. 1-Coupe transversale de la structure HEMT : a) la structure épitaxiale ; (b) image MEI | 3 de la |

| grille en T; c) une coupe TEM                                                                  |         |

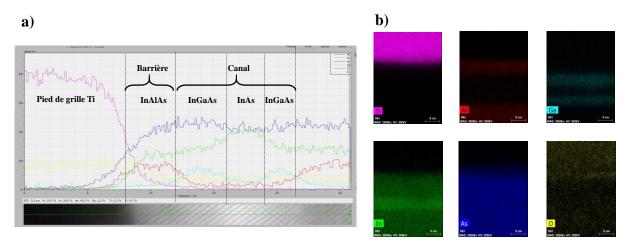

| Figure. 2-Images EDX de la coupe transversale de la structure HEMT                             | 138     |

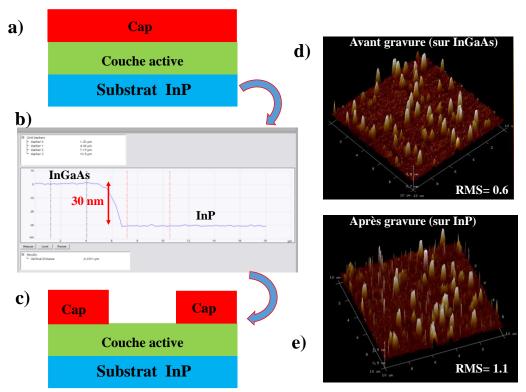

| Figure. 3-Étude de la rugosité de surface sur InGaAs et InAlAs par AFM                         |         |

| Figure. 4-Synoptique d'talonnage des ports                                                     | 142     |

| Figure. 5-Synoptique d'étalonnage du banc de mesure de quadripôles d'entrée et de sortie       | 142     |

| Figure. 6-Modèle du transistor sans accès coplanaires                                          | 143     |

| Figure. 7-Épluchage des accès : a-Paramètres de l'open et b-Paramètres du short                | 144     |

| Figure. 8-Modèle du transistor avec accès coplanaires                                          | 144     |

## Liste des tableaux

| Tableau I-1 Propriétés de matériaux III-V, GaN et Si [12]                                                              |

|------------------------------------------------------------------------------------------------------------------------|

| Tableau I-2.<br>Etat de l'art de couple $\mu$ Hall / NHall du HEMT-InP pour différents types de canaux 15              |

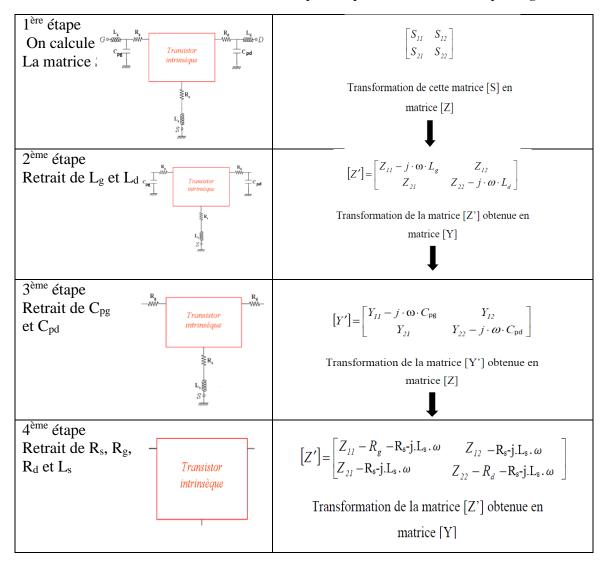

| Tableau I-3. Extraction de la matrice intrinsèque Yi à partir de la méthode d'épluchage [28] 20                        |

| Tableau I-4. Références bibliographiques des couples fT/fmax présentés sur la figure I.9 de différents                 |

| laboratoires et industries                                                                                             |

| Tableau I-5. Références bibliographiques entre 2007 et 2019 des couples $f_T/f_{max}$ et gm présentés sur la           |

| figure I.10-a et b                                                                                                     |

| Tableau I-6. État de l'art en bruit des transistors HEMTs et HBTs [1990-2019]                                          |

| Tableau I-7. État de l'art en bruit des amplificateurs LNA [2008-2018]                                                 |

| Tableau II-1. Densités d'électrons Ni simulées selon couches associées à leur mobilité respective μi.                  |

| La densité d'électrons et la mobilité de Hall calculées sont comparées aux valeurs expérimentales                      |

| Tableau II-2. Comparaison des paramètres de Hall calculés et mesurés des cinq architectures de canal                   |

| à double-plan de dopage fixe P 6/3                                                                                     |

| Tableau II-3 Répartition des charges dans la couche canal pour les cinq architectures à double-plan de                 |

| dopage fixe P 6/3                                                                                                      |

| Tableau II-4. Répartition des charges dans la couche canal pour les trois paires de dopage à couche                    |

| canal fixe InGaAs/InAs/InGaAs (40/30/25Å)                                                                              |

| Tableau II-5. Comparaison des paramètres de Hall calculés et mesurés des trois paires de dopage à                      |

| couche canal fixe InGaAs/InAs/InGaAs (40/30/25Å)                                                                       |

| Tableau II-6. Mesure électrique de TLM pour une structure HEMT avec et sans cap composite                              |

| InGaAs/InAlAs50                                                                                                        |

| Tableau II-7. Mesure électrique de TLM pour deux structures HEMT à cap composite et simple 50                          |

| Tableau II-8. L'effet de la passivation sur les propriétés de transport électronique du HEMT 54                        |

| Tableau II-9 L'impact de la gravure plasma $SF_6$ sur les mesures de Hall                                              |

| Tableau II-10. Ouvertures obtenues à travers le diélectrique de $Si_3N_4$                                              |

| Tableau III-1.Description des échantillons réalisés de procédé 1                                                       |

| Tableau III-2. Éléments du schéma équivalent petit signal pour des transistors à cap simple et ( $L_g = 45$            |

| nm et $W_g = 2 \times 12 \mu \text{m}$ ). Extraction réalisée au point de polarisation indiqué sur la figure III.13 89 |

| Tableau III-3. Schéma équivalent petit-signal pour deux transistors de $L_{SD}$ =1.5 $\mu$ m et 1 $\mu$ m91            |

| Tableau III-4. Paramètres du schéma équivalent petit signal et fréquences de transition des composants                 |

| de « ech1 » en fonction de longueur $L_{RD}$                                                                           |

| Tableau III-5. Eléments du schéma équivalent petit signal ( $V_{DS} = 1$ V et $V_{GS} = -0.3$ V) sans accès            |

| coplanaires du transistor ( $L_g = 75$ nm et $W_g = 2 \times 12 \mu$ m)                                                |

| Tableau III-6. Extraction des quatre paramètres de bruit du transistor                                                 |

| Tableau IV-1.Description des bandes de fréquences disponibles à l'IEMN                                                 |

## Introduction générale

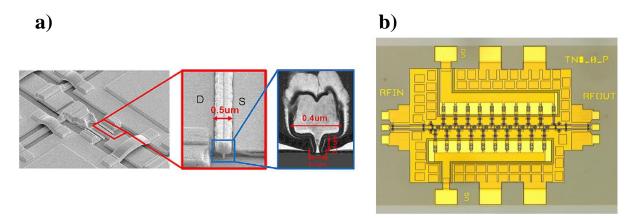

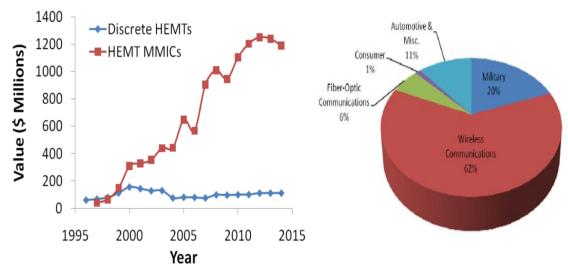

Les HEMTs (High Electron Mobility Transistors) utilisant des matériaux III-V à petite bande interdite pour le canal conducteur, tel que le matériau InGaAs, restent encore aujourd'hui les meilleurs transistors pour les applications millimétriques voire sub-millimétriques (le THz), en particulier pour les modules de réception en télécommunication ou dans les systèmes de détection. Bien que la concurrence se fait rude, en particulier par l'émergence des technologies silicium mais aussi les transistors à base de matériaux nitrurés, les HEMTs sont encore aujourd'hui les meilleurs candidats pour les applications de télécommunication, en imagerie passive ou pour la radioastronomie. En effet, ces applications requièrent des amplificateurs faible bruit. Le circuit intégré monolithique micro-onde (MMIC : Microwave Monolithique Integrated Circuit) de la filière HEMT InGaAs présente les plus faibles facteurs de bruit en gamme millimétrique et surtout en gamme sub-millimétrique. La bande de longueur d'onde sub-millimétrique, qui correspond à des fréquences THz, est un domaine que peu d'acteurs mondiaux ont exploré. On peut citer les travaux du MIT [1], de l'IAF [2] et surtout ceux de Northrop Grumman qui ont établi le record mondial de fréquence maximale d'oscillation  $f_{max}$  à 1.5 THz [3]. Ce dernier résultat a été confirmé par la fabrication d'un MMIC ou d'un TMIC (Térahertz MIC) de type amplificateur faible bruit (Low Noise Amplifier LNA) à 1 THz de fréquence de fonctionnement [3]. La figure 1 présente une photographie du circuit ainsi qu'une coupe transversale du HEMT utilisé. Le HEMT consiste en une hétérostructure InAlAs/InGaAs/InAs et de longueur de grille  $L_g$  atteint 25 nm.

Figure-Intro. 1-Photographie du HEMT en coupe transversale de  $L_g=25$  nm et b) Circuit TMIC réalisé

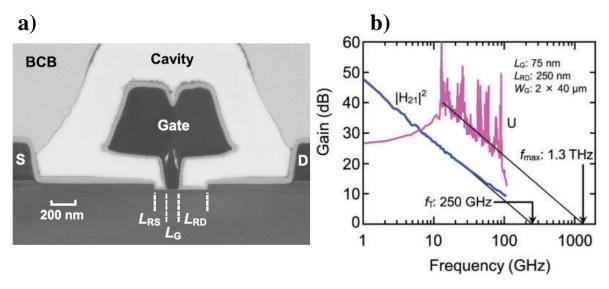

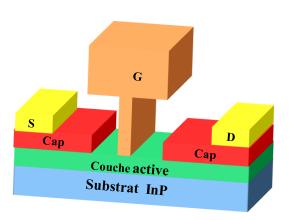

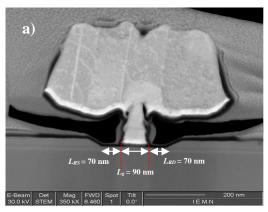

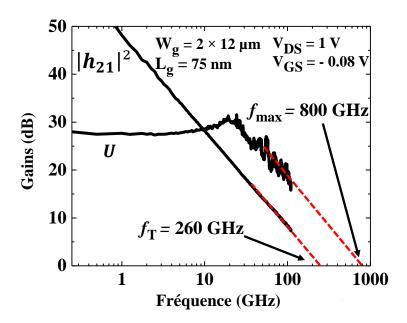

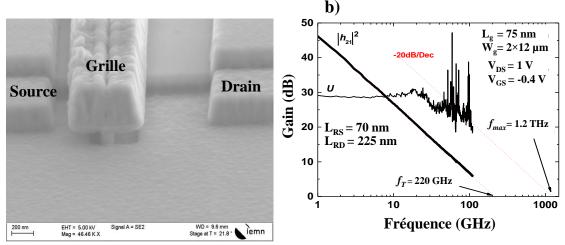

Plus récemment, les travaux de Fujitsu nous ont interpelés. En effet, ceux-ci ont reporté une fréquence maximale d'oscillation  $f_{max}$  de 1.3 THz en utilisant les mêmes types de matériaux que Northrop Grumman, mais avec une longueur de grille beaucoup plus élevée, 75nm. Les **figures 2-a** et **2-b**, présentent respectivement une photographie du HEMT en coupe transversale et les gains mesurés. Cette excellente fréquence a été obtenue en optimisant les propriétés de l'hétérojonction InAlAs/InGaAs, en utilisant une gravure de fossé de grille (recess) asymétrique et par réduction de l'espace entre les électrodes de source et de drain. Cette topologie s'avère prometteuse, car elle évite la réduction de la longueur de grille à quelques dizaines de nanomètres. Une longueur de grille, dont le profil est en forme de T, est plus simple à réaliser

au-delà de 50 nm. De plus, cette dimension relâchée est un atout pour l'uniformité, la reproductibilité et le rendement des technologies HEMTs.

Figure-Intro. 2-a) Photographie du HEMT en coupe transversale de  $L_g$  = 75 nm et b) Gains mesurés

C'est pourquoi, nous proposons dans ce travail de thèse d'explorer les potentialités pour le THz, de HEMTs InAlAs/InGaAs/InAs sur substrat d'InP avec des longueurs de grille d'environ 75 nm.

Ce travail de thèse se décompose en quatre principaux chapitres :

Le premier chapitre de ce manuscrit présente le contexte général de la thèse et la description du transistor HEMT. L'état de l'art des transistors à effet du champ et principalement des HEMTs à base de matériaux III-V. Nous allons comparer les différentes filières technologiques de HEMT réalisées au cours de ces dix dernières années. Nous présentons également leurs performances en statique, en dynamique et en bruit. Nous décrivons l'état de l'art actuel des HEMTs InGaAs/InAlAs sur InP avec recess de grille asymétrique et des HEMTs à différentes longueurs de grille. Nous présentons brièvement l'état de l'art de différents types de transistor (HBT, HEMT à base de GaN et GaAs, MOSFET...) afin de justifier les motivations du choix du transistor HEMT à hétérostructure InAlAs/InGaAs/InAs sur substrat d'InP. Nous finissons ce chapitre en présentant les différentes applications des HEMTs pour les circuits MMICs.

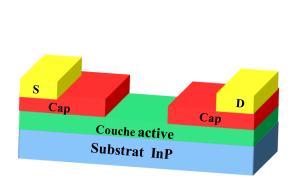

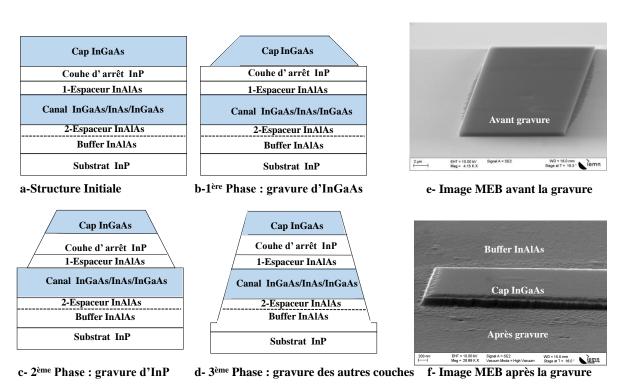

Le second chapitre sera consacré à la fabrication de HEMT de la filière InAlAs/InGaAs/InAs sur un substrat d'InP, nous présentons les étapes de fabrication de deux procédés, plus particulièrement les étapes technologiques critiques (gravure du fossé de la grille symétrique et asymétrique, contact ohmique). Une grande partie de ce chapitre sera dédiée aux optimisations apportées à la structure semiconductrice pour améliorer les propriétés de transport électronique et la qualité des contacts ohmiques. L'accent sera notamment porté sur plusieurs tests effectués qui nous ont permis d'améliorer le procédé de fabrication et de mettre en place de nouvelles méthodes simples à la réalisation et à la caractérisation de HEMT.

Le troisième chapitre quant à lui sera dédié à la présentation des résultats obtenus à partir des mesures statique, dynamique et en bruit effectuées jusqu'à la fréquence 110 GHz. Les deux procédés de fabrication seront étudiés en fonction de figure de mérite  $f_T$  et  $f_{max}$ . La modélisation

et l'extraction du schéma équivalent petit-signal seront présentées et validées jusqu'à la fréquence 110 GHz. Pour étudier le bruit du transistor dans un premier temps, nous décrivons la méthode utilisée ainsi que le modèle à deux sources de bruit de G. Dambrine. Ensuite, nous présentons les résultats de mesure de bruit ainsi que les résultats de l'extraction des quatre paramètres de bruit sur trois bandes différentes [6 GHz – 20 GHz], [20 GHz – 42 GHz] et [75 GHz – 110 GHz].

Finalement, le dernier chapitre sera consacré aux mesures de paramètres S du transistor et des éléments passifs, étalons et lignes coplanaires, au-delà de 110 GHz. Les bandes de fréquences explorées s'étendent de 250 MHz jusqu'à la fréquence de 750 GHz. Dans un premier temps, nous présentons les résultats obtenus dans les bandes G [140 GHz – 220 GHz] et J [220 GHz – 325 GHz]. Ensuite, un réajustement de l'espacement entre le plot de masse et le plot de signal d'une ligne coplanaire (pitch) a permis de réaliser des mesures avec le nouveau banc de mesures des paramètres S sur substrat, récemment acquis par l'IEMN, au-delà de 325 GHz [325 GHz – 750 GHz]. Par ailleurs, nous avons constaté que les topologies actuelles présentes des pertes importantes au-delà de 110 GHz notamment en band G, J et [325 GHz – 500 GHz]. Ce qui nécessite le travail avec de nouvelles lignes adaptées à ces bandes de fréquences plus élevées.

Chapitre I: Introduction et performances des HEMTs InAlAs/InGaAs

### I. Introduction du chapitre I

Afin de comprendre le contexte de nos travaux présentés dans ce manuscrit, nous rappelons brièvement dans ce premier chapitre le principe de fonctionnement de transistor HEMT (High Electron Mobility Transistor), son évolution et ces différentes filières technologiques en fonction des années. Dans un premier temps, nous rappelons les avantages et les inconvénients de chaque filière, nous présentons par la suite les propriétés physiques de matériaux III-V. Notamment, la mobilité électronique des électrons ( $\mu$ ), le paramètre de maille et d'autres propriétés physiques intrinsèques aux matériaux (masse effective d'électrons et conductivité thermique...).

Dans le cadre de l'évolution de HEMT, la première partie de l'état de l'art sera consacrée aux attentes du marché des semiconducteurs. Ensuite, nous comparons les différents types de canaux du HEMT et l'influence du taux d'Indium sur la mobilité et la densité d'électrons. Dans la deuxième partie de l'état de l'art, nous définissons l'ensemble des grandeurs caractéristiques du HEMT en régime statique et dynamique, notamment les figures de mérite  $f_T/f_{max}$  et de quatre paramètres de bruit afin de clarifier et comprendre la suite de ce manuscrit.

De plus une présentation globale sera dédiée principalement à la comparaison de HEMT et des transistors de la même famille III-V : MOSFET et HBT, ainsi que d'autres filières concurrentes de HEMT à base de GaN et de Silicium. Après avoir abordé les caractéristiques de différentes technologies, nous comparons par la suite les figures de mérites  $f_T/f_{\text{max}}$  obtenues au cours de ces dernières années.

Par ailleurs, nous décrivons l'impact géométrique du composant sur l'évolution des caractéristiques de HEMT. Principalement, l'impact de la longueur de grille  $L_g$ , la couche canal et le type de contact Schottky, puis la topologie du transistor.

Finalement, nous présentons des circuits intégrés MMICs (Monolithic Microwave Integrated Circuit) ainsi que leurs applications en bandes de fréquences millimétriques et sub-millimétriques. Nous allons aborder également l'état de l'art de bruit des transistors et des circuits démonstrateurs de type LNA (Low Noise Amplifier).

# II. Filières technologiques du transistor à effet de champ

#### II.1. Histoire et évolution des HEMTs

Tout a commencé en 1947, les trois physiciens américains John Bardeen, William Shockley et Walter Brattain, ont réalisé le premier dispositif à semi-conducteur nommé par « Transistor » [4]. Quelques années plus tard, en 1966 la fabrication de transistor à effet de champ MESFET (Metal Semiconductor Field Effect Transistor) a connu de grands progrès technologiques permettant de concevoir des composants à des hautes performances. Des fréquences importantes ont été démontrées à environ 15 GHz [5].

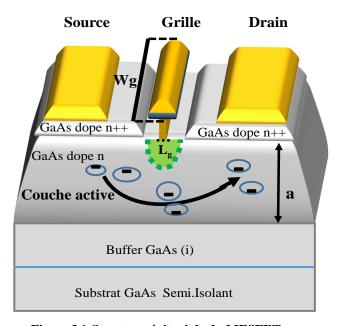

La figure. I-1, illustre la structure d'un MESFET, elle se compose de deux contacts. Le premier est ohmique et est formé à partir d'une jonction métal-semiconducteur (métal-GaAs n++); les deux électrodes associées sont appelées « drain » et « source ». Le deuxième contact (métal-semiconducteur dopé n) est de type Schottky et formé à partir d'une jonction métal-semiconducteur (métal-GaAs n); l'électrode associée à ce contact est nommée « grille ». Les limitations des MESFET se présentent lors de la réduction de la longueur de l'électrode de grille «  $L_g$  ». En effet, la réduction de la longueur de grille doit s'accompagner d'une réduction de l'épaisseur de la couche active 'a', ce qui nécessite d'augmenter le dopage de la couche active pour maintenir la même valeur du courant. Ainsi, la nécessité de conserver un bon rapport d'aspect (  $\frac{L_g}{a} > \sim 5$ ), entraîne une dégradation des propriétés de transport dans le canal liée à l'augmentation de dopage. Ceci limite par conséquent, les performances fréquentielles du transistor. D'où la nécessité de mettre au point d'autres structures de transistor.

Figure I.1-Structure épitaxiale du MESFET

### II.2. Hétérojonction et formation du gaz bidimensionnel

L'évolution des transistors à effet de champ connaîtra une autre dimension à la fin des années 70, grâce aux résultats apportés par R. Dingle et ses collègues [6]. La première démonstration de l'hétérojonction à modulation de dopage a été effectuée en utilisant les matériaux AlGaAs/GaAs par croissance par jet moléculaire MBE (Molecular Beam Epitaxy), les premiers résultats obtenus de mobilité ( $1000 - 2500 \, \text{cm}^2/\text{V.s}$ ) et de discontinuité des bandes de conduction  $\Delta E_C = 0.3 \, \text{eV}$  étaient assez faibles.

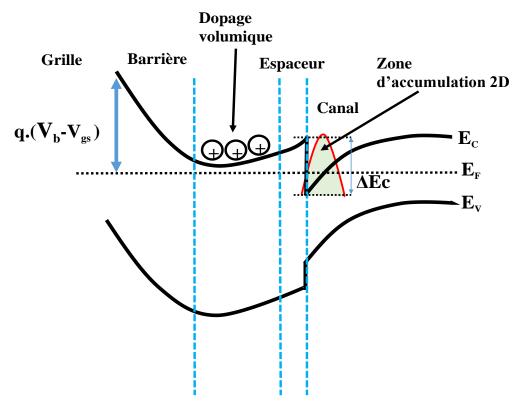

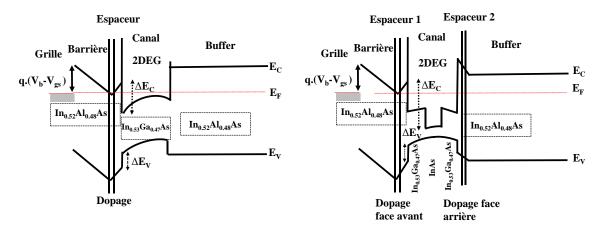

L'hétérojonction est basée sur la mise en contact d'un matériau à grand gap dopé et d'un autre à petit gap non dopé. Cette hétérojonction induit la création d'une discontinuité de bande de conduction  $\Delta E_C$  entre les deux matériaux (**figure I.2**). L'alignement des niveaux de Fermi entraîne un transfert d'électrons de la couche donneuse dopée vers le matériau non dopé. Une zone de puits bidimensionnel, appelée « 2DEG : Two Dimensionnel Electron Gas » constituée à l'interface de l'hétérostructure, accumule des électrons séparés de leurs atomes donneurs

ionisés. Ces électrons sont localisés dans une couche non dopée et bénéficient donc quasiment des propriétés de transport électronique d'un matériau non dopé.

Figure I.2-Comparaison de la structure de bande d'une hétérojonction entre un matériau de petit-gap et de grand-gap

### II.3. Transistor à effet de champ HEMT

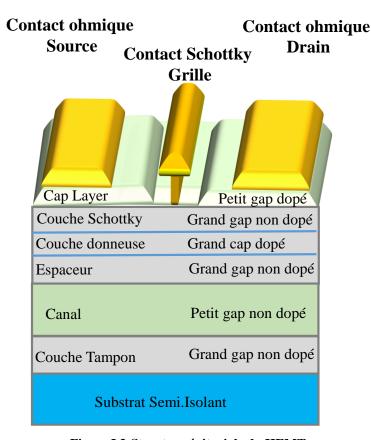

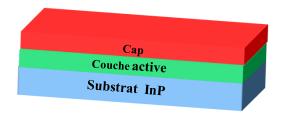

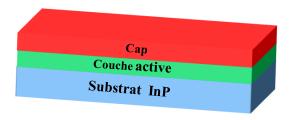

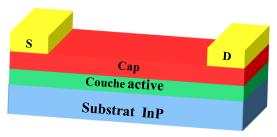

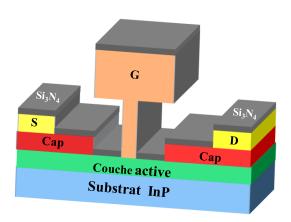

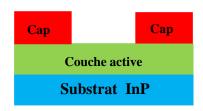

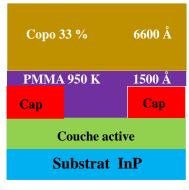

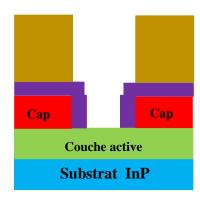

Grâce à la croissance atomique de l'épitaxie, l'optimisation des transistors à effet de champ n'a cessé de croitre. En 1980, Mimura et ses collègues du laboratoire Fujitsu [7] ont présenté pour la première fois un transistor basé sur le concept de dopage par modulation mis au point par Dingle. Il est basé sur le principe de l'hétérojonction d'un matériau grand gap dopé et d'un autre matériau à petit gap non dopé, la séparation spatiale des atomes ionisés des porteurs libres introduits dans le HEMT permet d'éviter les limitations du MESFET et l'augmentation de porteurs de charges dans le puits 2DEG. Pour mieux comprendre le rôle de chacune des couches de la structure HEMT, et leur impact sur les performances de transport électronique ainsi que les caractéristiques électriques du transistor, la **figure I.3** illustre l'ensemble des couches épitaxiales du HEMT. Elles sont constituées principalement de deux matériaux l'un à grand gap InAlAs et l'autre à petit gap InGaAs déposés sur un matériau semi isolant (le substrat).

Le premier matériau à grand gap (InAlAs) est utilisé pour : la couche Schottky, un contact formé à partir d'un semiconducteur non dopé assure le contrôle des électrons par effet de champ électrique ; la couche donneuse, relativement dopée fournit des électrons libres au canal ; la couche espaceur, a pour but de séparer les électrons libres du canal aux atomes donneurs ; la couche tampon (buffer), améliore le confinement des électrons dans le canal.

Le deuxième matériau à petit gap (InGaAs) est utilisé pour : la couche de contact ohmique nommée « cap layer », a pour rôle de constituer des zones de contacts de source et de drain. Ce matériau fortement dopé permet la réalisation d'un contact ohmique de type N et la réduction des résistances d'accès de source et de drain ; la couche « canal », l'une des principales couches d'un transistor à effet de champ (HEMT), dans laquelle se situe le gaz 2DEG.

Figure I.3-Structure épitaxiale du HEMT

#### II.3.1. Filières technologiques de HEMT à base de matériaux III-V

Des avancées en techniques de croissance de matériaux de haute qualité cristalline ont ouvert de nouvelles perspectives pour l'ingénierie de la structure de bande, et ont permis d'améliorer les caractéristiques des hétérojonctions. Il devient envisageable de concevoir des alliages de matériaux capables d'améliorer les caractéristiques électroniques, notamment la mobilité et la densité des électrons. Il existe plusieurs alliages possibles à travers de nombreux matériaux composés. Particulièrement, des éléments des colonnes III et V du tableau de Mendeleïev qui peuvent être binaires (GaAs, InP, InAs...), ternaires (InGaAs, InAlAs, InAlP, GaAsSb...) voire même quaternaires (InGaAsP, InGaAsSb...) et permettent la réalisation des hétérostructures. L'objectif est de proposer des alliages permettant de créer des hétérostructures qui sont capables de présenter une discontinuité de bande de conduction la plus élevée possible. En effet, la formation d'un puits de potentiel profond tend à améliorer la densité d'électrons du 2DEG. Enfin, on choisira pour le canal conducteur un matériau à forte mobilité électronique. La plus grande contrainte provient de la croissance de l'hétérojonction et plus particulièrement du paramètre de maille cristalline. En effet, lors de la croissance d'un matériau III-V sur un

autre matériau III-V quelle que soit la technique MBE ou MOCVD (metalorganic chemical vapor deposition), les paramètres de maille cristalline doivent être identiques voire assez proches (quelques pourcents sur des épaisseurs de quelques dizaines de nanomètres). Dans le cas contraire, il y'a l'apparition de dislocations qui vont induire une dégradation des propriétés physiques du matériau (la mobilité par exemple), des pièges, des difficultés lors de la fabrication des composants et une baisse de la fiabilité du composant final.

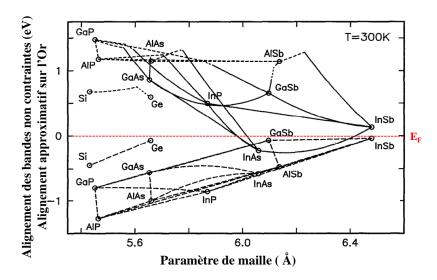

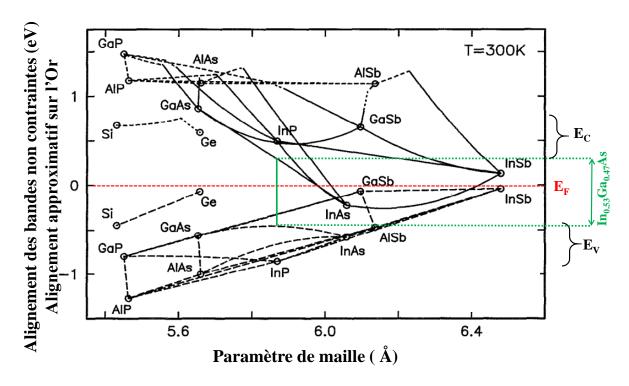

La croissance se fait généralement sous forme de trois structures et va dépendre des paramètres de maille cristalline des matériaux (**figure I.4**).

**Structure adaptée en maille (Lattice Matched) :** cette structure est obtenue lorsque les matériaux ont le même paramètre de maille que le substrat. Ces matériaux ont souvent la composition chimique différente, mais présentent le même paramètre de maille cristalline.

**Structure pseudomorphique :** Lorsque le matériau en croissance et le substrat ont un paramètre de maille peu diffèrent (quelques pourcents). Dans le régime de croissance pseudomorphique, la couche épitaxiale sera contrainte (en extension ou en compression) afin que sa maille cristalline soit identique à celle du substrat. Exemple : la croissance d'InGaAs sur un substrat GaAs. Au-dessus d'une épaisseur critique, il y'a aura apparition de dislocations, non souhaitées pour la fabrication des composants.

**Structure métamorphique :** L'épitaxie métamorphique est une forme de croissance dans laquelle on part du paramètre de maille du substrat vers le paramètre de maille désiré. Le matériau final sera quasiment relaxé. On utilise un buffer métamorphique, dans lequel on va par exemple introduire un graduel de concentration, ou un super réseau, ou une couche tampon qui bloquera les dislocations. Le buffer métamorphique a une épaisseur aux alentours du micron. Un exemple en HEMT est l'hétérojonction In<sub>0.52</sub>Al<sub>0.48</sub>As/In<sub>0.53</sub>Ga<sub>0.47</sub>As adaptée en maille sur InP réalisée sur substrat de GaAs.

Le diagramme de la **figure I.4** représente l'alignement des bandes de conduction et de valence de différents matériaux III-V en fonction de paramètre de maille. Il est donc important pour concevoir des transistors avec des discontinuités et des mobilités importantes de bien choisir les hétérostructures permettant un bon confinement des électrons.

Aujourd'hui, les technologies à base des principaux substrats InP et GaAs, sont devenues matures pour les applications millimétriques mais restent pour le sub-millimétrique (ou THz) assez confidentielles (on verra cela dans la partie état de l'art). Le taux d'Indium dans la couche canal de type  $In_xGa_{1-x}As$  a tendance à croitre ces dernières années avec des valeurs très élevées de l'ordre de x = 53%, 70%, 80% et 100% et permet d'atteindre jusqu'à des dizaines de milliers de cm²/V.s; nous pouvons citer le cas de l'InAs (30000~40000 cm²/V.s). De plus, un taux d'Indium accru s'accompagne d'une augmentation de la discontinuité de bande de conduction ( $\Delta E_c$ ) et donc de la densité du 2DEG. La classification des filières a été longuement discutée dans les travaux de thèse réalisés à l'IEMN de N. Wichmann [8], I. Duszynski [9] et T. Parenty [10].

Figure I.4- Alignement des bandes de conduction et de valence en fonction du paramètre de maille [11]

Dans la physique des semiconducteurs, la mobilité est définie comme la vitesse des porteurs de charges par unité de force du champ électrique, elle caractérise la rapidité avec laquelle un électron peut se déplacer à travers un métal ou un semi-conducteur. Lorsqu'un champ électrique E (V/cm) est appliqué sur un morceau de matériau, les électrons répondent en se déplaçant avec une vitesse moyenne  $v_d$  (cm/s) appelée vitesse de dérive. La distance parcourue par un électron sans interaction avec le réseau cristallin est nommée le libre parcours moyen. Ce déplacement est lié à la mobilité qui dépend à son tour de toute modification intervenue dans le réseau cristallin. La mobilité des électrons est donnée par la relation suivante :

$$\mu = \frac{v_d}{E} \text{ [cm}^2/\text{V.s]}$$

Eq-I.1

Elle peut être définie également en fonction de la masse effective de l'électron  $\mathbf{m}^*$ , le temps moyen entre deux collisions  $\boldsymbol{\tau}$  et la charge  $\boldsymbol{q}$  par l'équation ci-dessous :

$$\mu = \frac{q.\tau}{m^*}$$

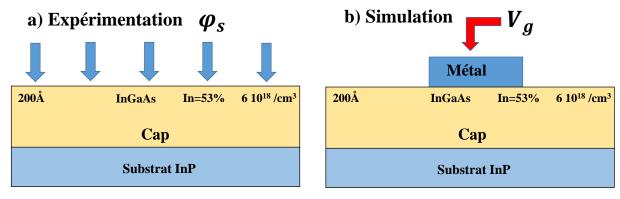

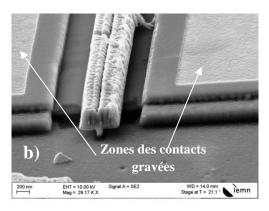

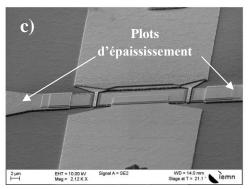

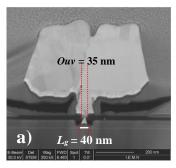

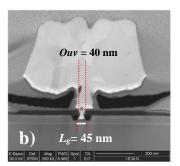

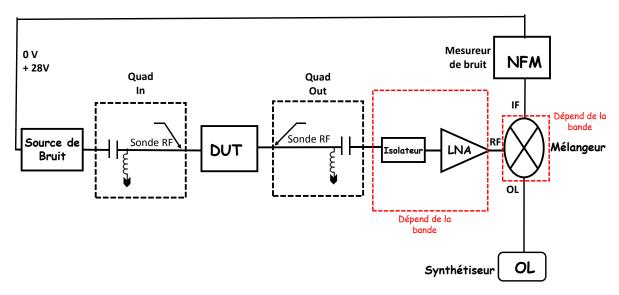

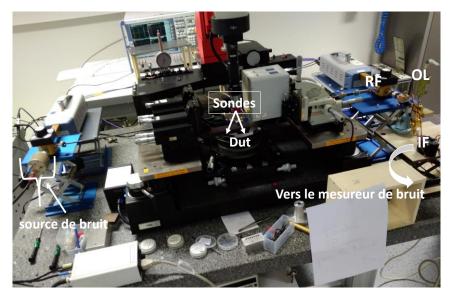

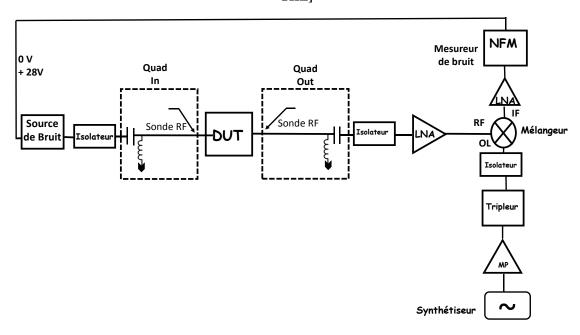

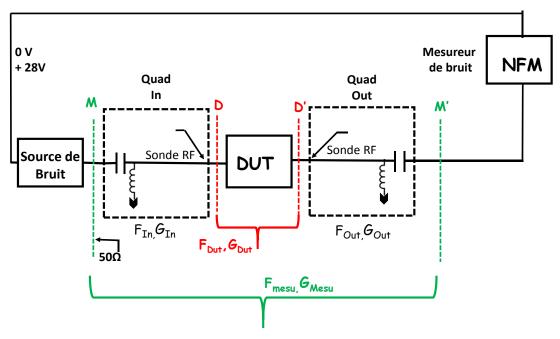

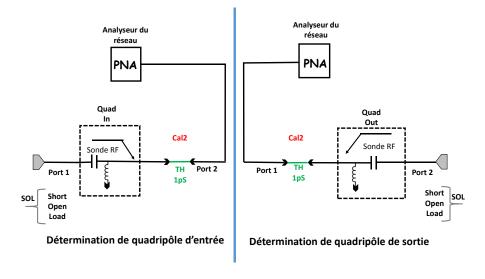

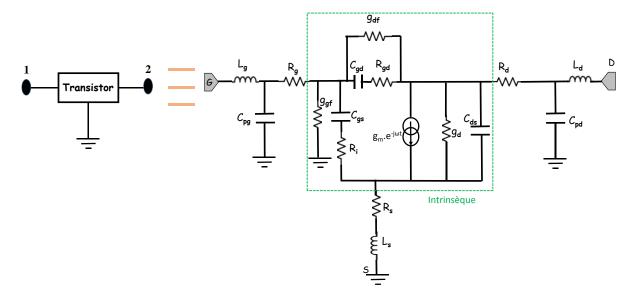

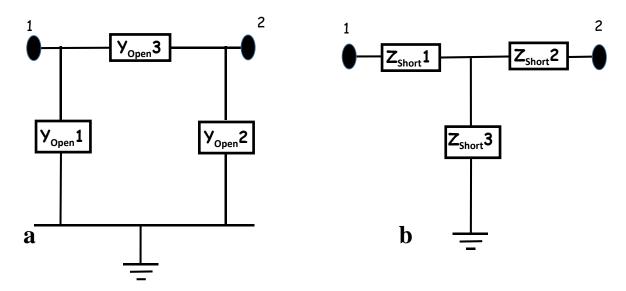

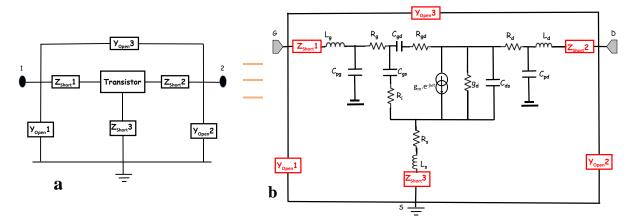

Eq-I.2