## Study of an integrated pre-processing architecture for smart-imaging-systems, in the context of lowpower computer vision and embedded object detection

Luis Cubero Montealegre

### ► To cite this version:

Luis Cubero Montealegre. Study of an integrated pre-processing architecture for smart-imagingsystems, in the context of lowpower computer vision and embedded object detection. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2021. English. NNT: 2021GRALT091. tel-03612476

### HAL Id: tel-03612476 https://theses.hal.science/tel-03612476

Submitted on 17 Mar 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Communauté UNIVERSITÉ Grenoble Alpes

# THÈSE

Pour obtenir le grade de

### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano-Electronique et Nano-Technologies

Arrêté ministériel : 25 mai 2016

Présenté par

## Luis Angel CUBERO MONTEALEGRE

Thèse dirigée par **Gilles SICARD**, Ingénieur de recherche, HDR, encadrée par **Arnaud PEIZERAT**, Ingénieur de recherche et **Dominique MORCHE**, Ingénieur de recherche, HDR.

préparée au sein du CEA-LETI dans l' Ecole Doctorale d'Electronique, Automatisme et Traitement du signal (EEATS).

Etude d'une architecture intégrée de prétraitement du signal pour les imageurs intelligents, dans le contexte de la vision embarquée pour la détection des objets.

Study of an integrated pre-processing architecture for smart-imaging-systems, in the context of lowpower computer vision and embedded object detection

Thèse soutenue publiquement le **16/12/2021**, devant le jury composé de :

Pr. Alice CAPLIER GIPSA-Lab, Grenoble INP, Grenoble, France, Présidente Dr. Ricardo CARMONA GALAN Chercheur, Instituto de Microelectrónica de Sevilla, IMSE-CNM, Séville, Espagne, Rapporteur Pr. Dominique GINHAC Laboratoire ImViA – Université de Bourgogne, Dijon, France, Rapporteur Dr. Gilles SICARD Ingénieur de recherche HDR, CEA-LETI, Grenoble, France, Directeur de thèse Dr. Arnaud PEIZERAT Ingénieur de recherche, CEA-LETI, Grenoble, France, co-encadrant, invité Dr. Dominique MORCHE Ingénieur de recherche HDR, CEA-LETI, Grenoble, France, co-encadrant, invité

To my grandmothers.

### Abstract

Embedded Computer vision, as many applications of artificial intelligence and edge computing, is subjected to hardware and power constraints. For instance, the object detection problem, consisting in finding different objects of specific classes (types) in an image, turns out to be quite complicated to embed near the image sensor as two complex tasks are required: multi-scale localization and multi-class classification (i.e. identifying bounding boxes that perfectly enclose each object, whatever its size, and labeling the type of the detected object). Today these tasks are often performed on general-purpose desktop machines. Nevertheless, attractive applications like autonomous-driving, augmented reality or video surveillance are urging the need for low-power, low-latency and compact low power devices.

The state of the art has approached this challenge by optimizing specific sections of the complete processing-pipeline for a comparable object detection performance. A typical example in the last decade corresponds to minimizing the computing precision, hence the power, to a minimal value. Diminishing the bit-depth or image size has then been studied while implementing pre-processing steps that increase robustness against the loss in bit and image resolution. An algorithm that does not require that kind of pre-processing stage to be programmable is obviously desirable in order to simplify its implementation (e.g. no memory access to learned weights). Another strategy has been to reduce power due to I/O communications amongst different chips or devices thanks to a more exhaustive integration of specialized circuitry and thanks to more efficient memory accesses and mathematical operations.

In that context of near-sensor computing, this work points towards a more energy efficient detection pipeline. We target several specific key aspects:

1. We try to assess if a dedicated-class-agnostic region proposal algorithm, based on preprocessed low-level features, could replace the typical sliding window approach for object localization in integrated smart imaging systems, allowing to target more efficiently objects in the image. Then, we propose a pipeline that takes into account near image sensor features extraction for Region Proposals with an embedded version of an algorithm called Edge-Boxes.

2. We try to assess an optimal type of pre-processing (based on an efficient architecture) that would allow extracting low level features (oriented gradients), and give the best trade-off between power consumption, hardware complexity and object detection performance. Specifically, while being this architecture fully compatible with region proposal algorithms beyond the sliding window.

3. Finally, we try to assess if non-standard, or neuromorphic, image acquisition techniques can be exploited in order to further increase the detection efficiency in real case scenarios.

Our methodology relies on behavioral simulations carried out thanks to a custom framework written in Python and C++ code. We propose a hierarchical model (and code architecture) of different image acquisition and processing techniques, and we study their performance through specific metrics related to runtime, memory usage, hardware complexity, I/O data-rate, localization performance and classification performance. We provide comparison with the state of the art and several benchmarks giving guidance to choose one or another architecture depending on the specific needs, and we conclude by stating which one would give, from our perspective, the best trade-offs.

### Table of contents

| Abstract                                                |   |

|---------------------------------------------------------|---|

| Table of contents                                       |   |

| List of figures                                         | 7 |

| List of tables                                          |   |

| Chapter 1. Introduction                                 |   |

| Chapter 2. State of the art                             |   |

| 2.1. CMOS Image sensors                                 |   |

| 2.1.1. Typical system architecture                      |   |

| 2.1.2. Pixel types                                      |   |

| 2.1.3. Typical design parameters                        |   |

| 2.2. Smart CMOS image sensors                           |   |

| 2.2.1. Frame-based smart-image-sensors                  |   |

| 2.2.2. Edge or Oriented Gradients extraction            |   |

| 2.2.3. Embedded CNN-like features extraction            |   |

| 2.2.4. 3D-IC Smart Image Sensors                        |   |

| 2.2.5. Event-based imaging-systems                      |   |

| 2.3. Object detection pipelines                         |   |

| 2.3.1. HOG and linear SVM                               |   |

| 2.3.2. HOG and DPM                                      |   |

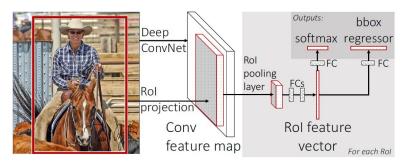

| 2.3.3. Fast R-CNN                                       |   |

| 2.3.4. Faster R-CNN                                     |   |

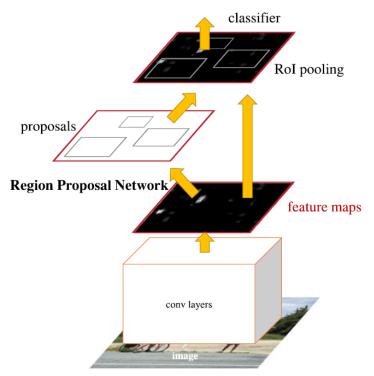

| 2.3.5. SDD and YOLO                                     |   |

| 2.4. Conclusions of chapter 2                           |   |

| Chapter 3. Our simulation Framework                     |   |

| 3.1. EdgeTon main architecture                          |   |

| 3.1.1. Imager models structure                          |   |

| 3.1.2. Imager model module                              |   |

| 3.1.3. Simulation engine loop                           |   |

| 3.2. Imager model examples                              |   |

| 3.2.1. Ideal 8-bit-depth Sobel oriented-edges extractor |   |

| 3.2.2. Analog linear oriented gradient extractor        |   |

| 3.2.3. Digital linear oriented gradient extractor       |   |

| 3.2.4. Logarithmic oriented gradients extractor         |   |

| 3.2.5. Relative edge extractor                              | 52  |

|-------------------------------------------------------------|-----|

| 3.2.6. Dynamic vision imagers                               | 52  |

| 3.3. Conclusions of chapter 3                               | 54  |

| Chapter 4: Region proposals pipeline design                 | 55  |

| 4.1. ROI proposals vs. typical sliding window approaches    | 56  |

| 4.2. Selecting a ROI detection algorithm                    | 58  |

| 4.2.1. EdgeBoxes decortication                              | 62  |

| 4.2.2. Preliminary memory estimation                        | 68  |

| 4.3. Embedding oriented gradients generation                | 69  |

| 4.3.1. Canny Edge Detection                                 | 70  |

| 4.3.2. Our edge detection pipeline description              | 75  |

| 4.3.3. Dynamic range improvement                            | 79  |

| 4.4 Conclusions of chapter 4                                | 80  |

| Chapter 5: Embedded Edge Extraction Circuitry               | 81  |

| 5.1. Circuit stages                                         | 82  |

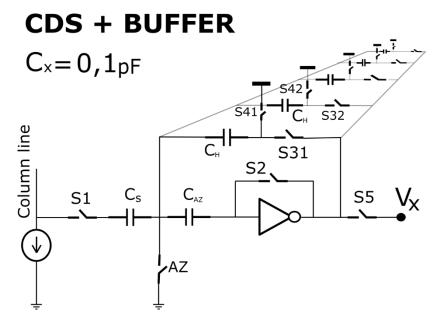

| 5.1.1. Correlated double sampling and first buffer          | 82  |

| 5.1.2. Low Pass Filter                                      | 83  |

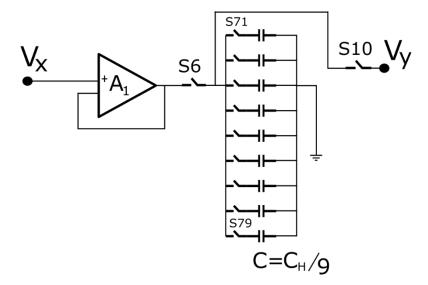

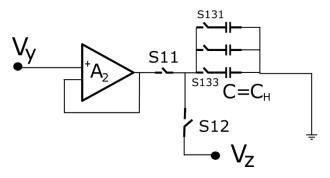

| 5.1.3. Second buffer                                        | 84  |

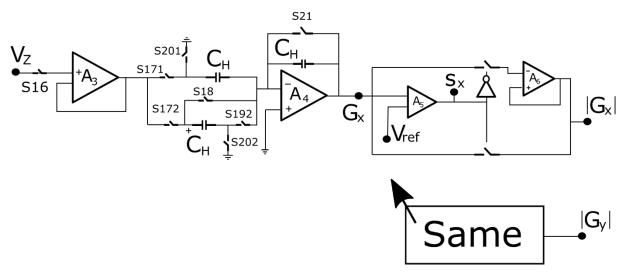

| 5.1.4. Difference and absolute value                        | 85  |

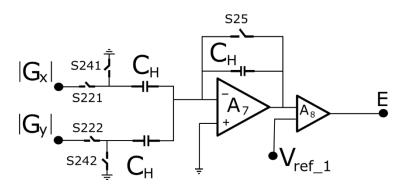

| 5.1.5. Summation and quantization                           | 86  |

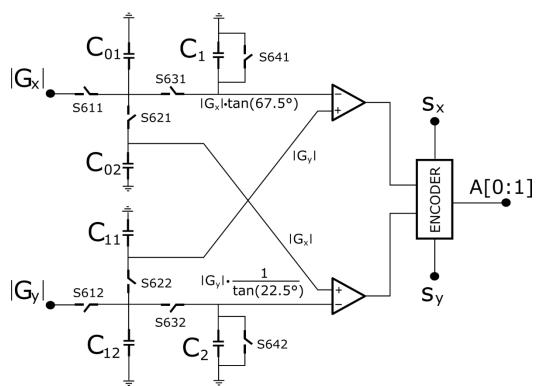

| 5.1.6. Angular computation                                  | 87  |

| 5.2. Condensing power into a single formula                 | 89  |

| 5.3. Estimation of the bias current                         | 90  |

| 5.3.1. Band-width constraints on biasing current            | 90  |

| 5.4. Noise analysis                                         | 93  |

| 5.5. Conclusions of chapter 5                               |     |

| Chapter 6. Object Localization benchmarks                   |     |

| 6.1. Localization characterization methodology              | 100 |

| 6.1.1. Simulation Flow with EdgeTon                         | 102 |

| 6.1.2. Edge extraction with a smart imager behavioral model | 103 |

| 6.1.3. Localization with Edge-Boxes                         | 104 |

| 6.1.4. Intersection over union metrics calculation          | 104 |

| 6.2. Benchmarks                                             | 105 |

| 6.2.1 Global ABIoU along jobs for each architecture         | 105 |

| 6.2.2 Memory estimation                                     | 112 |

| 6.2.3 Runtime estimation                                    | 118 |

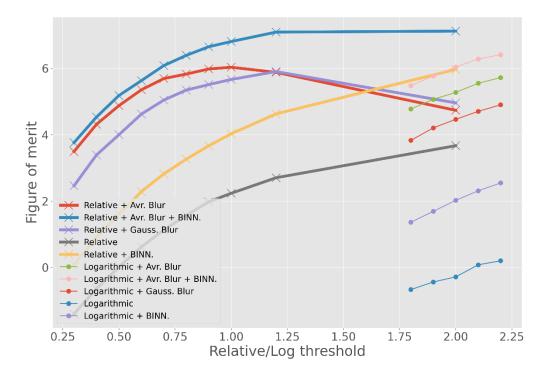

| 6.3. Empiric Figure of Merit                                  | 121 |

|---------------------------------------------------------------|-----|

| 6.4. Conclusions of chapter 6                                 | 125 |

| Chapter 7. Dynamic Vision Pre-processing                      | 127 |

| 7.1. Event-base data for object detection                     | 128 |

| 7.2. Synthetic dataset generation                             | 130 |

| 7.2.1. Polygon dataset                                        | 131 |

| 7.2.2. Three spheres over ground dataset                      | 133 |

| 7.3. From circuit schematic to behavioral simulations         | 137 |

| 7.4. Pre-processing improvement for data-throughput reduction | 139 |

| 7.5. Using dynamic vision for ROI proposals                   | 145 |

| 7.6. Conclusions of chapter 7                                 | 150 |

| Chapter 8. Conclusion                                         | 152 |

| References                                                    | 155 |

| List of Publications                                          | 160 |

| Patents                                                       | 160 |

# List of figures

| FIGURE 1 : DIFFERENT APPROACHES FOR PIXELS PRE-PROCESSING AND/OR READ-OUT. "(A) SERIAL ARCHITECTURE; (B) COLUMN-      |      |

|-----------------------------------------------------------------------------------------------------------------------|------|

| parallel architecture; (c) pixel-parallel architecture." (Takayanagi and Nakamura 2013)                               | . 15 |

| FIGURE 2 : ILLUSTRATION OF THE PASSIVE PIXEL IN CMOS TECHNOLOGY (THEUWISSEN 2007).                                    | . 16 |

| FIGURE 3 : ILLUSTRATIONS OF THE ACTIVE 3T (TOP) AND 4T (BOTTOM) PIXELS (EL GAMAL AND ELTOUKHY 2005)                   | . 17 |

| FIGURE 4 : ILLUSTRATION OF THE IN 1.75T ARCHITECTURE (EL GAMAL AND ELTOUKHY 2005)                                     | . 18 |

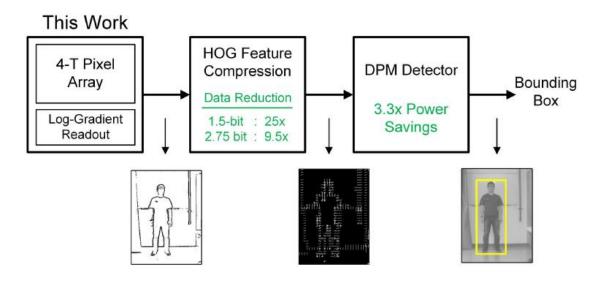

| FIGURE 5 : LOGARITHMIC GRADIENTS OBJECT DETECTION PIPELINE (YOUNG ET AL. 2019).                                       | . 21 |

| FIGURE 6 : DISTRIBUTION OF POWER CONSUMPTION FOR THE IMPLEMENTED CIRCUIT FROM (YOUNG ET AL. 2019)                     | . 21 |

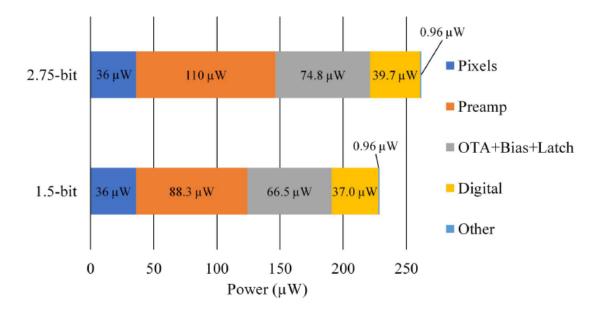

| FIGURE 7 : CIRCUIT SCHEMATIC FOR LOGARITHMIC GRADIENTS EXTRACTION (YOUNG ET AL. 2019)                                 | . 22 |

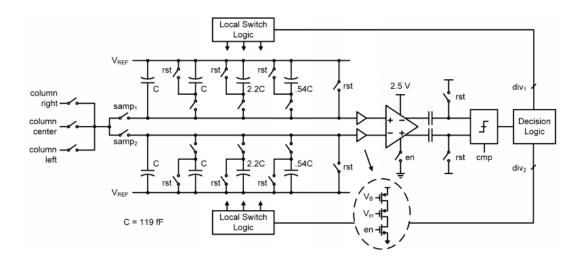

| FIGURE 8 : CIRCUIT SCHEMATIC FOR SOBEL-LIKE EDGE-MAGNITUDE-EXTRACTION (SOELL ET AL. 2016)                             | . 22 |

| FIGURE 9 : "(A) CONVENTIONAL FACE RECOGNITION SYSTEM (B) PROPOSED RECOGNITION SYSTEM" (JH. KIM ET AL. 2019)           | . 26 |

| FIGURE 10 : SYSTEM OVERVIEW OF THE PWM PIXELS-MATRIX AND PROGRAMMABLE PRE-PROCESSING (HSU ET AL. 2021)                | . 27 |

| FIGURE 11 : DIAGRAM OF THE IMPLEMENTED PRE-PROCESSING FOR MAC AFTER PWD READ-OUT (HSU ET AL. 2021)                    | . 28 |

| FIGURE 12 : ILLUSTRATION OF THE IN PIXEL-MAC ARCHITECTURE (BOSE ET AL. 2019)                                          | . 29 |

| FIGURE 13 : ILLUSTRATION OF THE 3D-IC SMART-IMAGE SENSOR (MILLET ET AL. 2018)                                         | . 29 |

| FIGURE 14 : DIAGRAM OF THE UNITS IMPLEMENTED IN THE BOTTOM LAYER (MILLET ET AL. 2018)                                 | . 30 |

| FIGURE 15 : ILLUSTRATION OF THE PRINCIPLE OF FUNCTIONING OF THE DYNAMIC VISION SENSOR (POSCH ET AL. 2014)             | . 32 |

| FIGURE 16 : EXAMPLE OF THE EVENT-BASED READ-OUT "(A) BLOCK DIAGRAM. (B) TIMING FOR A COMMUNICATION CYCLE FOR A        |      |

| SINGLE ON EVENT" (LICHTSTEINER, POSCH, AND DELBRUCK 2008)                                                             | . 33 |

| FIGURE 17 : PRINCIPLE OF FUNCTIONING OF THE TIME-TO-FIRST-SPIKE PIXEL (GUO, QI, AND HARRIS 2007)                      | . 34 |

| FIGURE 18 : EXAMPLE OF A WEIGHTED AVERAGE CIRCUIT IN SPIKE-DOMAIN (RAVINUTHULA AND HARRIS 2004)                       | . 34 |

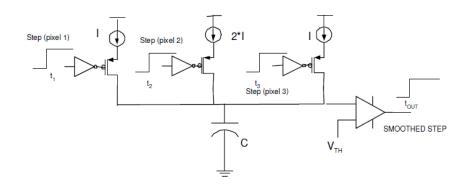

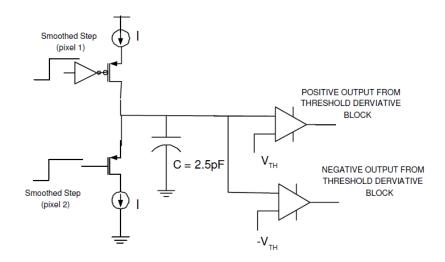

| FIGURE 19 : EXAMPLE OF A SUBTRACTION AND THRESHOLDING CIRCUIT IN SPIKE DOMAIN (RAVINUTHULA AND HARRIS 2004)           | . 35 |

| FIGURE 20 : EXAMPLE OF AN OBJECT DETECTION PIPELINE WITH HOG AND SVM (DALAL AND TRIGGS 2005)                          | . 35 |

| FIGURE 21 : ILLUSTRATION OF THE PRINCIPLE OF FUNCTIONING OF THE DMP MODEL. "(A) A COARSE FILTER, (B) SEVERAL HIGHER   |      |

| RESOLUTION PART FILTERS, AND (C) A SPATIAL MODEL FOR THE LOCATION OF EACH PART RELATIVE TO THE ROOT" (P. F.           |      |

| Felzenszwalb et al. 2010)                                                                                             | . 36 |

| FIGURE 22 : DIAGRAM OF THE FAST R-CNN PIPELINE: " AN INPUT IMAGE AND MULTIPLE REGIONS OF INTEREST (ROIS) ARE INPUT    | Т    |

| INTO A FULLY CONVOLUTIONAL NETWORKS. EACH ROI IS POOLED INTO A FIXED-SIZE FEATURE MAP" (GIRSHICK 2015)                | . 37 |

| FIGURE 23 : ILLUSTRATION OF THE "FASTER R-CNN" PIPELINE (REN ET AL. 2017)                                             | . 38 |

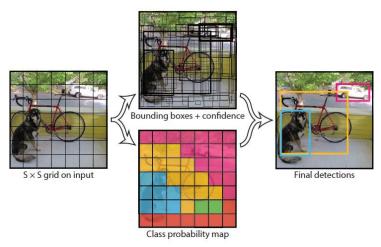

| FIGURE 24 : ILLUSTRATION OF THE PRINCIPLE OF THE YOLO-PIPELINE: "IT DIVIDES THE IMAGE INTO AN S X S GRID AND FOR EACH | I    |

| GRID CELL PREDICTS B BOUNDING BOXES, CONFIDENCE FOR THOSE BOXES, AND C CLASS PROBABILITIES" (REDMON ET AL.            |      |

| 2016)                                                                                                                 |      |

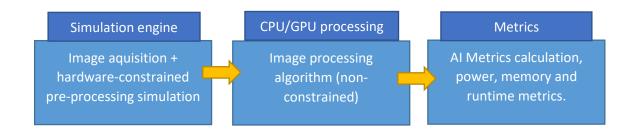

| FIGURE 25 : MAIN EDGETON ALGORITHM                                                                                    |      |

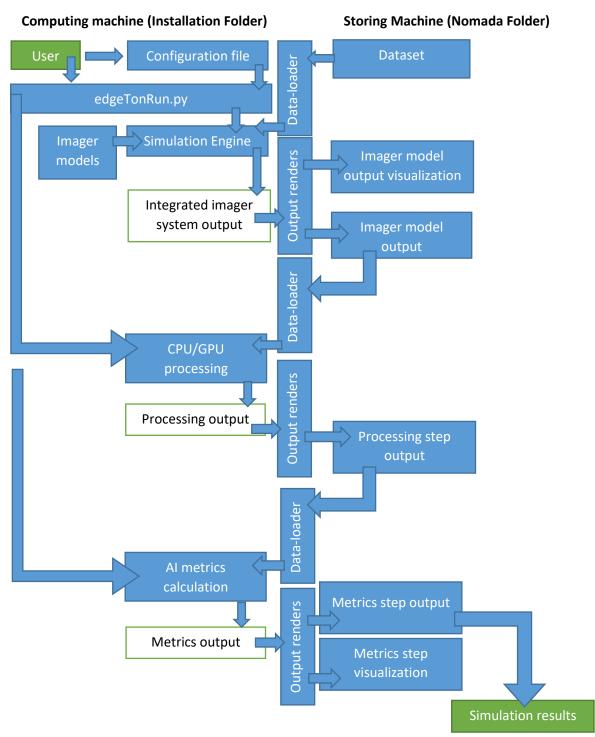

| FIGURE 26 : DIAGRAM OF EDGETON FRAMEWORK ARCHITECTURE FOR SIMULATING COMPLETE PROCESSING PIPELINES.                   | . 43 |

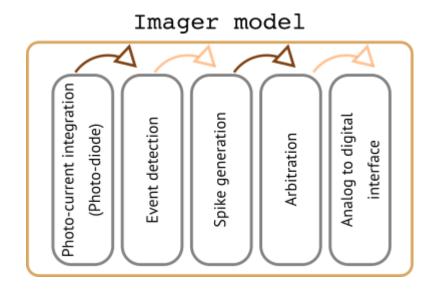

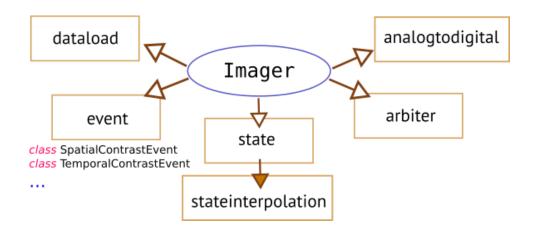

| Figure 27 : Imager model (Cubero et al. 2019)                                                                         | . 44 |

| FIGURE 28 : EXAMPLE OF THE IMAGER MODEL IMPLEMENTED IN PYTHON MODULES (CUBERO ET AL. 2019)                            |      |

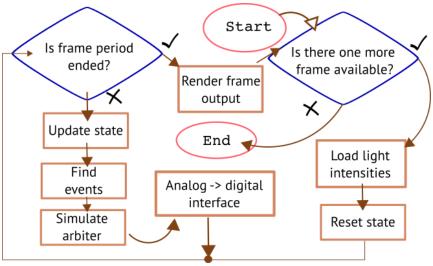

| FIGURE 29 : SIMULATION LOOP (CUBERO ET AL. 2019)                                                                      |      |

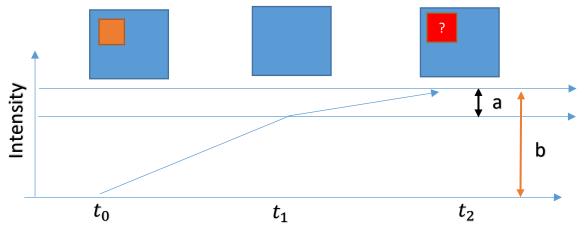

| Figure 30 : example image of how an event at time step $Ti$ can depend on a time step simulation $Tt-2$               |      |

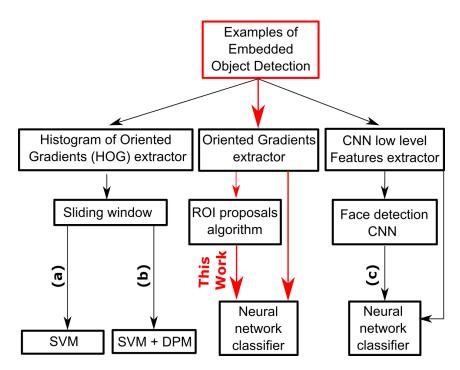

| FIGURE 31 : EXAMPLE OF DIAGRAMS OF PIPELINES FOR EMBEDDED INTEGRATED DEVICES                                          |      |

| FIGURE 32 : "(A) CONVENTIONAL FACE RECOGNITION SYSTEM (B) PROPOSED FACE RECOGNITION SYSTEM" (JH. KIM ET AL. 2019      | 9).  |

|                                                                                                                       |      |

| FIGURE 33 : (A) OD IN GENERAL. (B) OD WITH EMBEDDED AND DIGITAL PRE-PROCESSING. (C) THEIR INNOVATIVE APPROACH WITH    |      |

| EMBEDDED DIGITAL AND ANALOG PRE-PROCESSING. (OMID-ZOHOOR ET AL. 2018)                                                 |      |

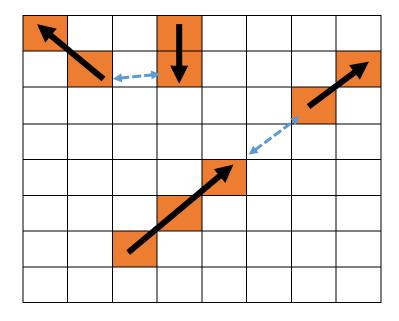

| FIGURE 34 : PRINCIPLE OF FUNCTIONING OF EDGE-BOXES (ZITNICK AND DOLLAR 2014).                                         |      |

| FIGURE 35 : EXAMPLE OF HOW EDGE-BOXES RELATES DISCONNECTED SEGMENTS.                                                  |      |

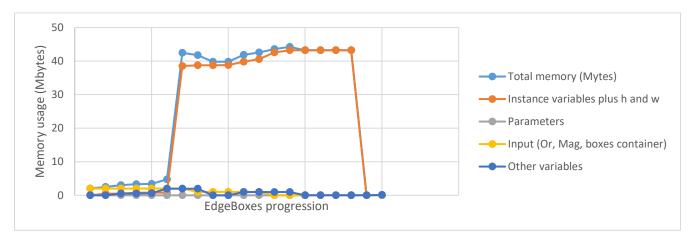

| FIGURE 36: EDGE-BOXES MEMORY ESTIMATION WHILE PROCESSING ONE IMAGE                                                    |      |

| FIGURE 37: EDGE-BOXES INSTANCE VARIABLES SIZE ESTIMATION                                                              |      |

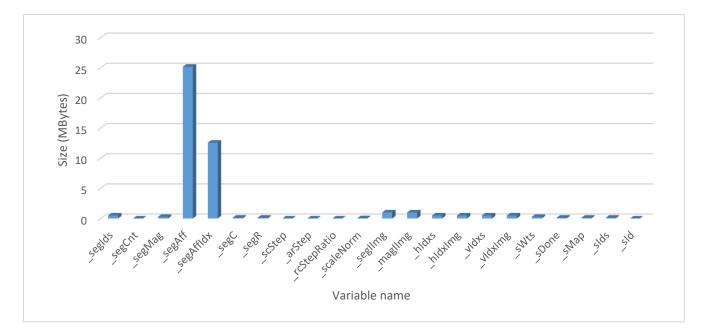

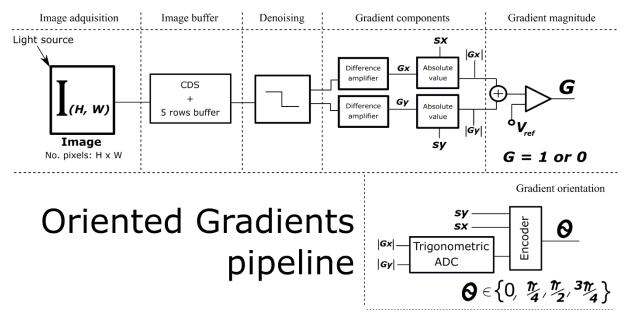

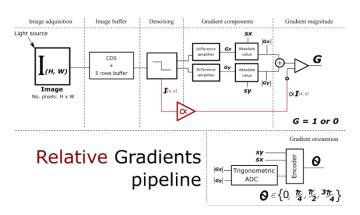

| FIGURE 38: OUR PROPOSED COLUMN PARALLEL PRE-PROCESSING PIPELINE FOR GRADIENT COMPUTATION.                             |      |

| FIGURE 39: ILLUSTRATION OF WHY A SIMPLE GRADIENT COMPUTATION DEPENDS UPON 25 ORIGINAL-IMAGE-VALUES.                   | . 77 |

| FIGURE 40 : ADAPTATION FROM FIGURE 38 FOR RELATIVE GRADIENTS. THE ARCHITECTURE SEGMENTS ADDED ARE COLORED IN REL      | o.80 |

| FIGURE 41 : CORRELATED DOUBLE SAMPLING AND BUFFER CIRCUITRY PROPOSED BY (YOUNG ET AL. 2019)                          | 82   |

|----------------------------------------------------------------------------------------------------------------------|------|

| FIGURE 42 : IMAGE SPATIAL-LOW-PASS (BLUR) FILTER WITH AN AVERAGING KERNEL.                                           | 83   |

| FIGURE 43: INTERMEDIARY BUFFER SCHEMATIC                                                                             | 84   |

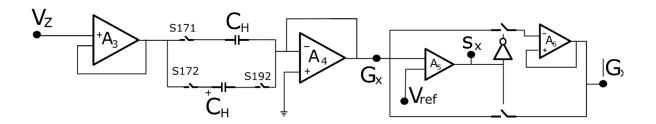

| FIGURE 44 : SCHEMATIC FOR COMPUTED GRADIENT MAGNITUDE COMPONENTS                                                     | 85   |

| FIGURE 45 : EQUIVALENT DIFFERENCE AND ABSOLUTE VALUE CIRCUIT FROM FIGURE 44 IN SAMPLING PHASE                        | 86   |

| FIGURE 46 : EQUIVALENT DIFFERENCE AND ABSOLUTE VALUE CIRCUIT FROM FIGURE 44 IN AMPLIFICATION STAGE                   | 86   |

| FIGURE 47: CIRCUIT SCHEMATIC FOR THE SUMMATION AND QUANTIZATION STAGE.                                               | 86   |

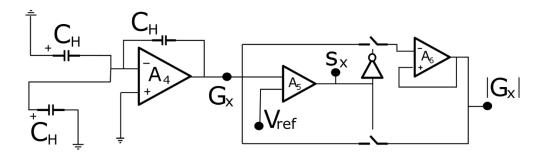

| FIGURE 48 : SIMPLIFIED CIRCUIT RESPECT TO THE ONE FROM (CHOI ET AL. 2014) FOR ANGULAR COMPUTATION                    | 88   |

| FIGURE 49 : LOGICAL EXPRESSIONS AND RELATED TRUTH TABLES FOR ANGULAR COMPUTATION WITH THE CIRCUIT FROM FIGURE 48     | 8.89 |

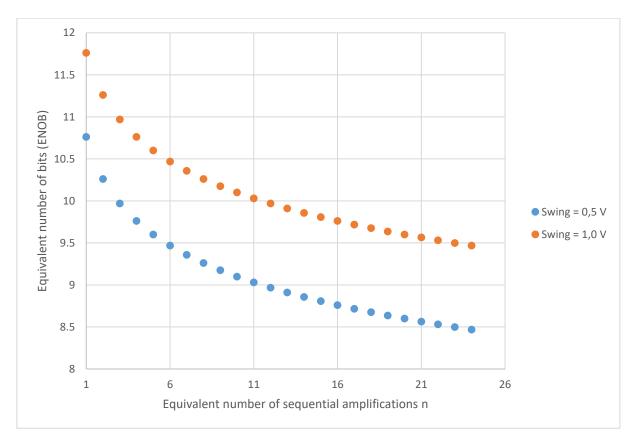

| Figure 50 : Equivalent number of bits for two different pixel-intensity-voltage-swings V_sig=V_R, as a function      | OF   |

| THE EQUIVALENT NUMBER OF SEQUENTIAL SIGNAL AMPLIFICATIONS N. C_H=100 FF,T=300 K                                      | 96   |

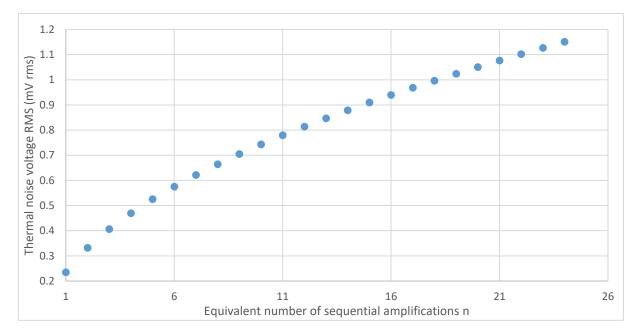

| Figure 51 : RMS Thermal noise voltage ( $v(\Sigma^2)$ ), as a function of the equivalent number of sequential signal |      |

| AMPLIFICATIONS N. C_H=100 FF,T=300 K.                                                                                | 97   |

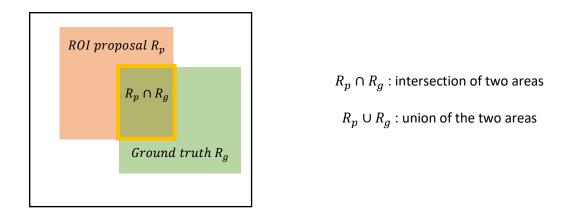

| FIGURE 52 : ILLUSTRATION OF THE IOU SHOWING THE ROI PROPOSAL, GROUND-TRUTH-BOX, AND INTERSECTION AREAS. THE UNI      | ON   |

| AREA IS DELIMITED BY BORDERS OF BOTH RECTANGLES WITHOUT TAKING INTO ACCOUNT BORDERS OF THE INTERSECTION              |      |

| RECTANGLE                                                                                                            | 100  |

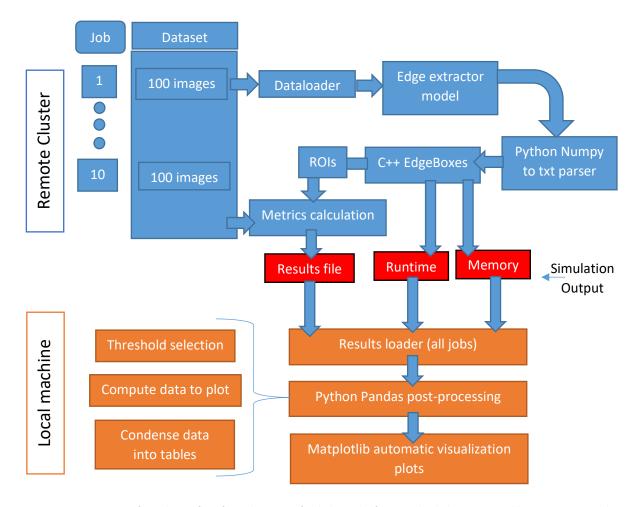

| FIGURE 53 : DIAGRAM OF SIMULATION FLOW FROM DATASET TO FINAL PLOTS. THE FIGURE IS DIVIDED IN UPPER AND BOTTOM        |      |

| SECTIONS. THE FIRST ONE WAS COMPUTED IN A CLUSTER, WITH $10$ JOBS (AVAILABLE TO RUN IN PARALLEL AND SCALABLE TO      |      |

| more jobs) of $100$ images each. The second (bottom) one corresponded to the post-processing made to                 |      |

| GENERATE THE FINAL PLOTS                                                                                             | 102  |

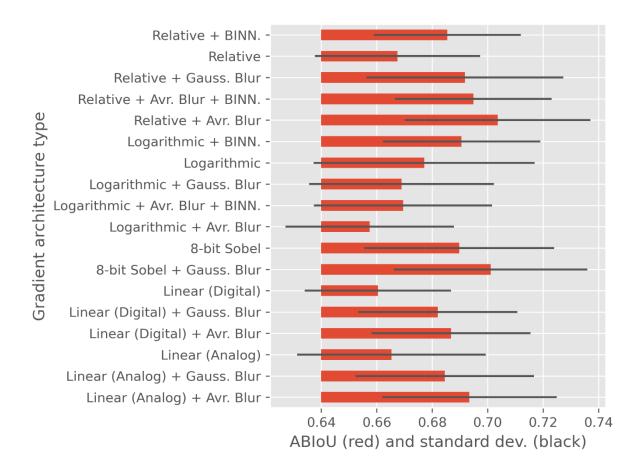

| FIGURE 54 : AVERAGE GLOBAL ABIOU OBTAINED WITH 10 JOBS.                                                              | 106  |

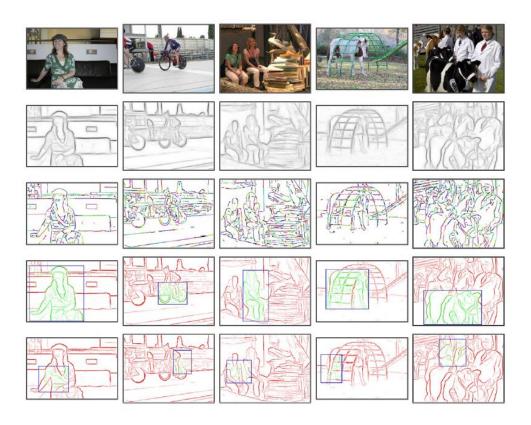

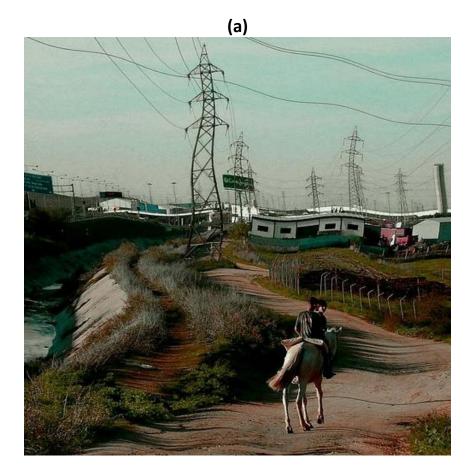

| FIGURE 55 : EXAMPLE OF AN INPUT IMAGE FROM PASCAL VOC2007 DATASET (M. EVERINGHAM ET AL. N.D.; N.D.; MARK             |      |

| EVERINGHAM ET AL. 2015), AND CORRESPONDING REPRESENTATIONS OF THE ORIENTED EDGES MAP OUTPUTS FROM THREE              | Ξ    |

| DIFFERENT EDGE-EXTRACTORS. THE GRAY/RED BOXES REPRESENT THE BEST ROI PROPOSALS AFTER RUNNING EDGE-BOXES O            | ЛС   |

| THE EDGES-MAPS. GREEN MEANS THAT THE OBJECT WAS CORRECTLY INCLUDING IN THE ROI, WHILE RED MEANS THAT THE             |      |

| OBJECT WAS NOT FOUND (E.G. ALL ROIS WHERE SUCH THAT THEIR IOU < 0.5)                                                 | 108  |

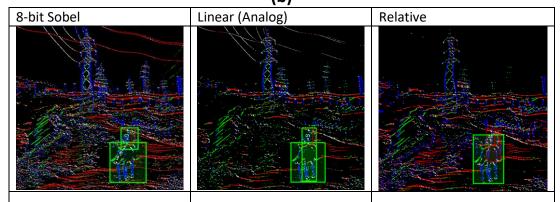

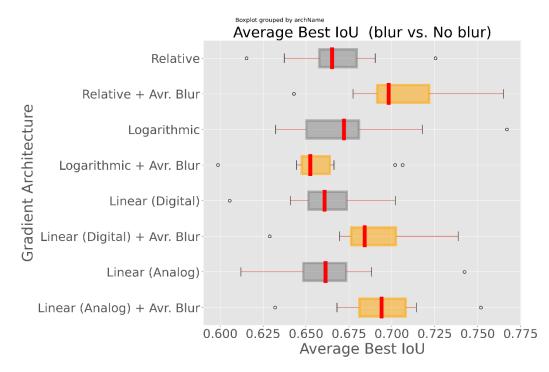

| FIGURE 56 : GLOBAL AVERAGE BEST IOU COMPARISON FOR ARCHITECTURES USING AND NOT USING DE-NOISING.                     |      |

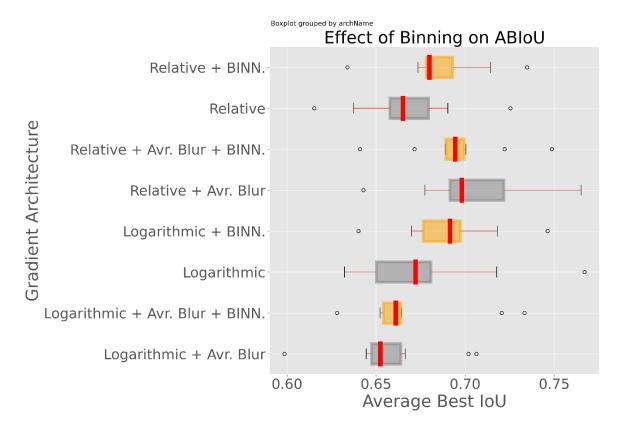

| FIGURE 57 : GLOBAL AVERAGE BEST IOU COMPARISON FOR ARCHITECTURES USING AND NOT USING 2X2 BINNING.                    | 110  |

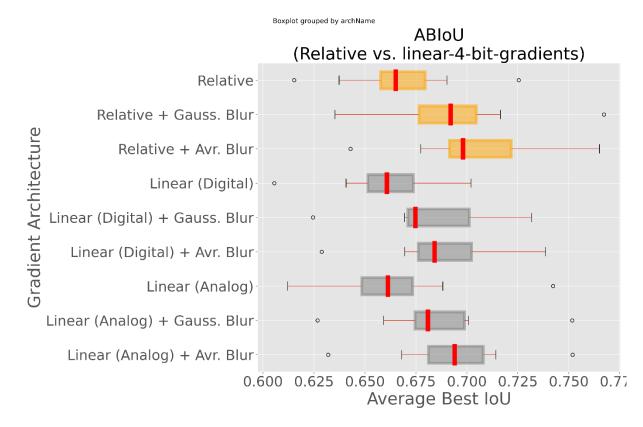

| FIGURE 58 : GLOBAL AVERAGE BEST IOU COMPARISON FOR ARCHITECTURES USING RELATIVE AND SIMPLE LINEAR GRADIENTS (4       |      |

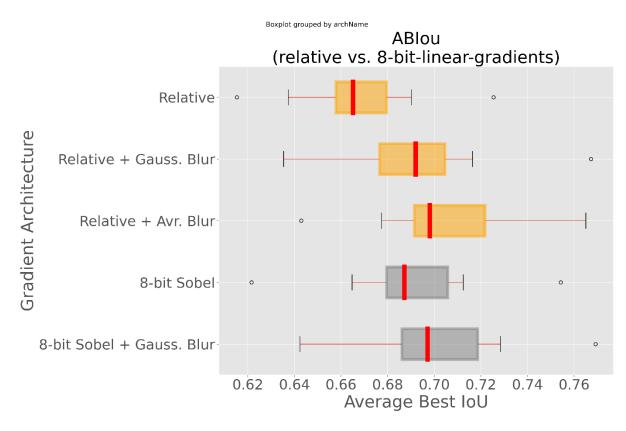

| ENOB)                                                                                                                | 111  |

| FIGURE 59 : GLOBAL AVERAGE BEST IOU COMPARISON FOR ARCHITECTURES USING RELATIVE AND SIMPLE LINEAR GRADIENTS (4       |      |

| ENOB)                                                                                                                |      |

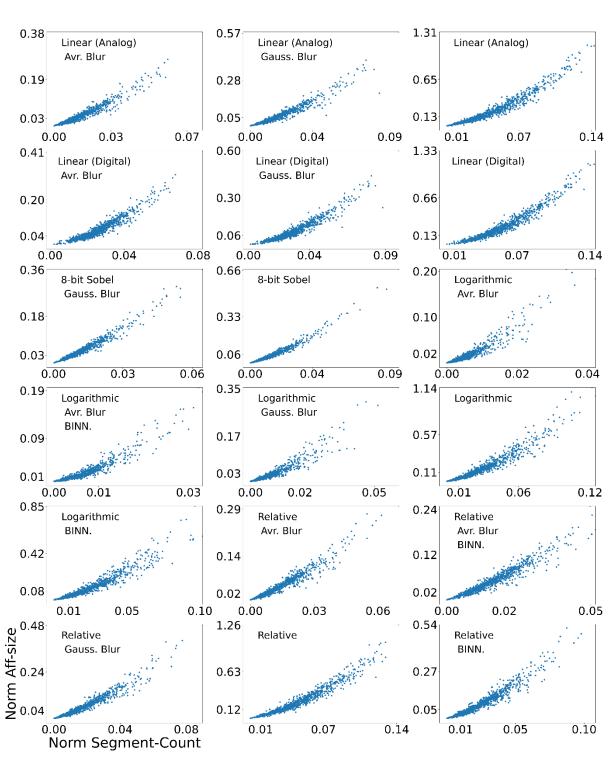

| FIGURE 60 : NORMALIZED AFFINITIES VARIABLE SIZE AS A FUNCTION OF THE NORMALIZED NUMBER OF EGDE-CLUSTERS (SEGMENTS    |      |

| FOR DIFFERENT ARCHITECTURES. ALL PLOTS SHOW A POSITIVE CORRELATION BETWEEN THE TWO VARIABLES.                        | 113  |

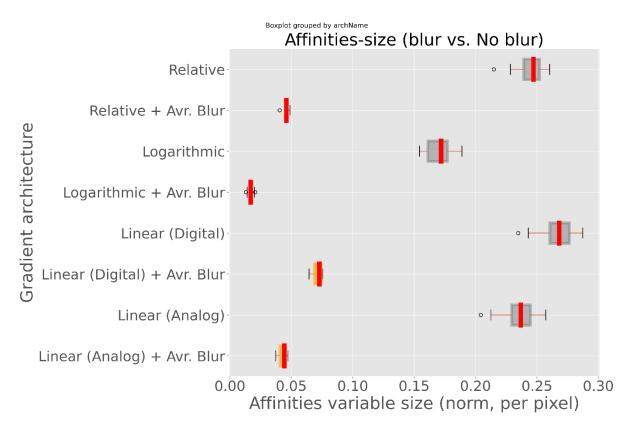

| FIGURE 61 : AFFINITIES-VARIABLE-SIZE COMPARISON FOR ARCHITECTURES USING AND NOT USING DE-NOISING.                    | 114  |

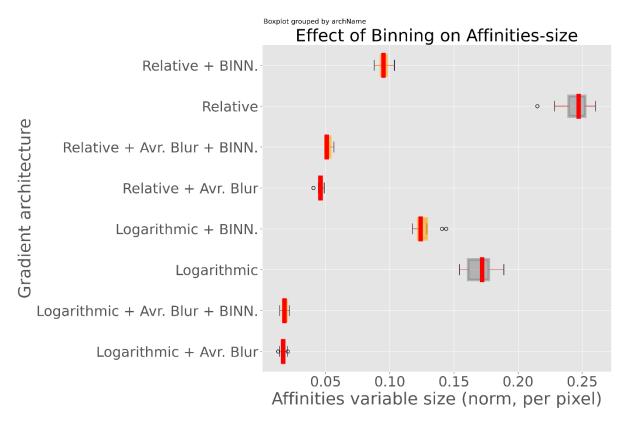

| FIGURE 62 : AFFINITIES-VARIABLE-SIZE COMPARISON FOR ARCHITECTURES USING AND NOT USING 2x2 BINNING                    | 115  |

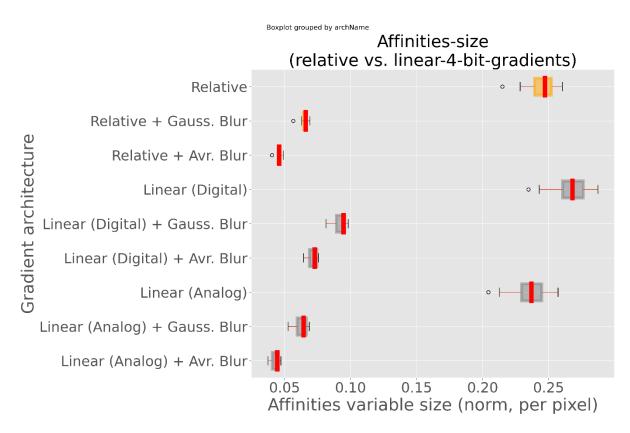

| FIGURE 63 : AFFINITIES-VARIABLE-SIZE COMPARISON FOR ARCHITECTURES USING RELATIVE AND SIMPLE LINEAR GRADIENTS (4 ENC  | ЭΒ). |

|                                                                                                                      | 116  |

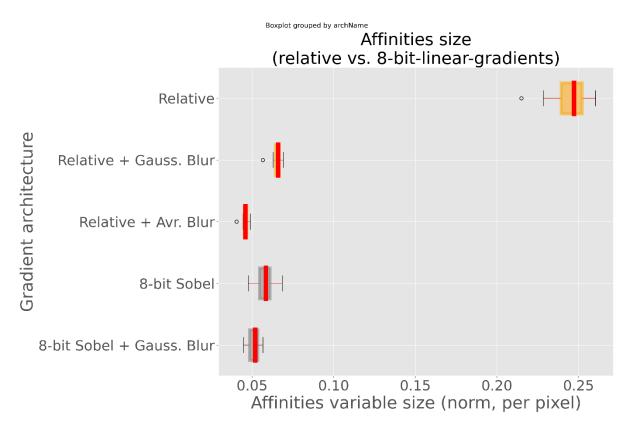

| FIGURE 64 : AFFINITIES-VARIABLE-SIZE COMPARISON FOR ARCHITECTURES USING RELATIVE LINEAR GRADIENTS (8 ENOB)           | 117  |

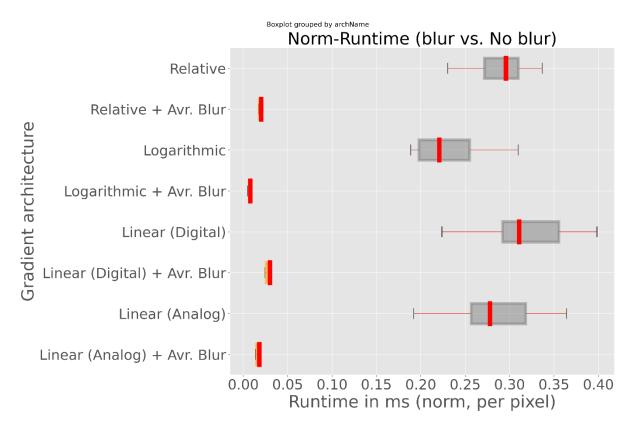

| FIGURE 65 : NORMALIZED-RUNTIME COMPARISON FOR ARCHITECTURES USING AND NOT USING DE-NOISING.                          | 119  |

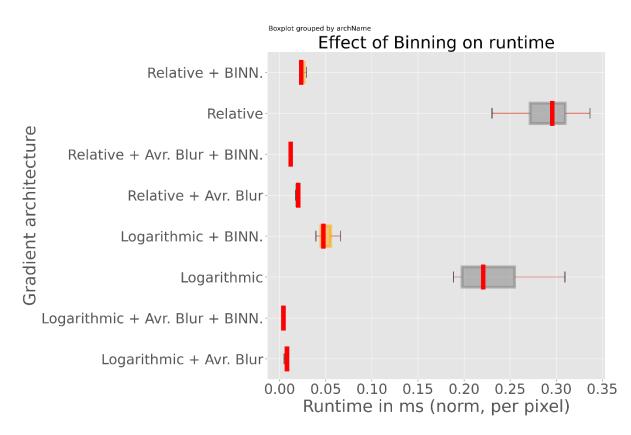

| FIGURE 66 : NORMALIZED-RUNTIME COMPARISON FOR ARCHITECTURES USING AND NOT USING 2x2 BINNING                          | 119  |

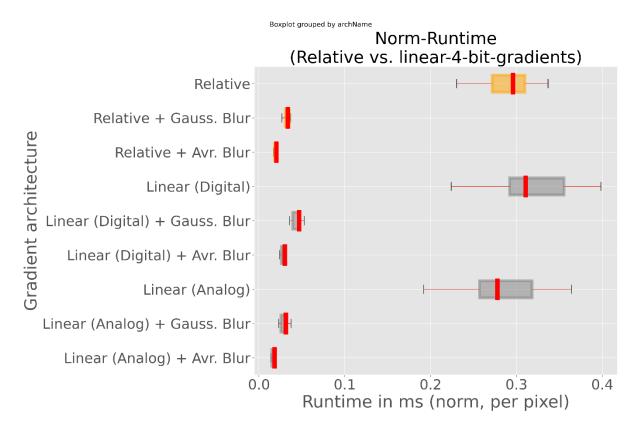

| FIGURE 67 : NORMALIZED-RUNTIME COMPARISON FOR ARCHITECTURES USING RELATIVE AND SIMPLE LINEAR GRADIENTS (4 ENOP       | 3).  |

|                                                                                                                      | 120  |

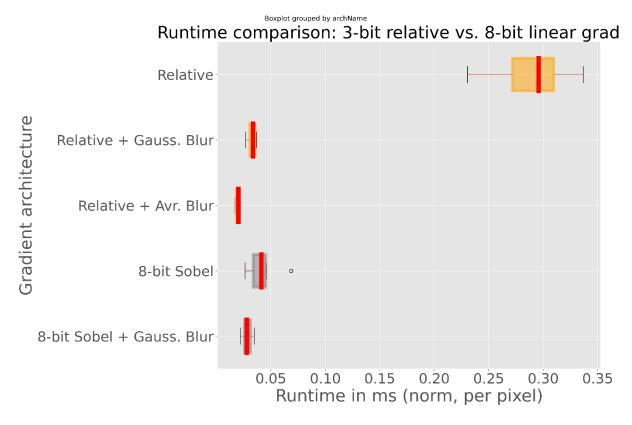

| FIGURE 68 : NORMALIZED-RUNTIME COMPARISON FOR ARCHITECTURES USING RELATIVE AND 8-BIT LINEAR GRADIENTS.               | 121  |

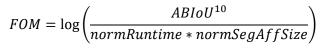

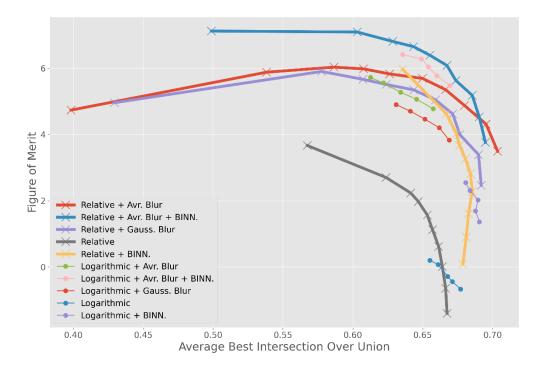

| FIGURE 69 : FIGURE OF MERIT FOR DIFFERENT ARCHITECTURES AT SELECTED THRESHOLDS (FROM TABLE []).                      | 122  |

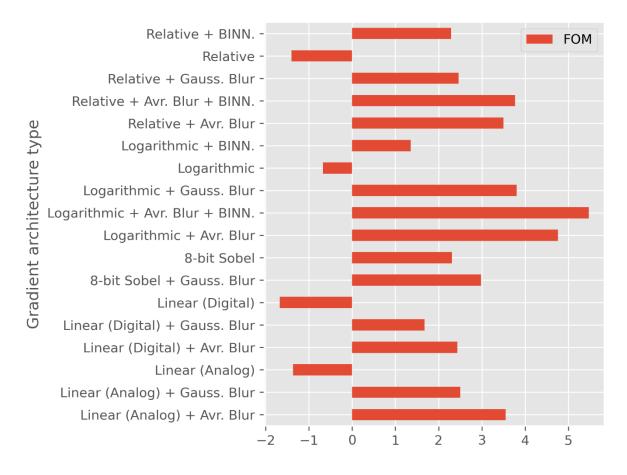

| FIGURE 70 : GLOBAL ABIOU DEPENDANCE UPON THE GRADIEND THRESHOLD FOR DIFFERENT ARCHITECTURES                          |      |

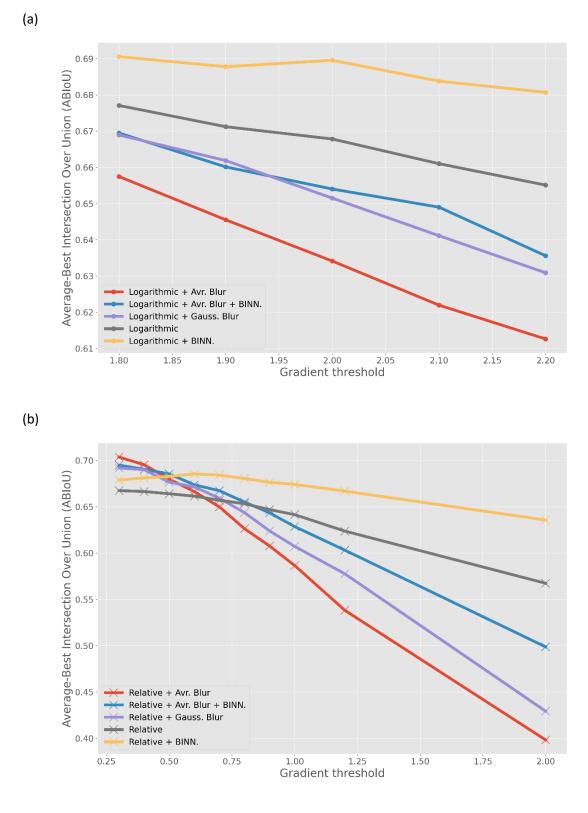

| FIGURE 71 : FIGURE OF MERIT AS A FUNCTION OF THE RELATIVE/LOG THRESHOLD FOR DIFFERENT ARCHITECTURES.                 | 124  |

| FIGURE 72 : DEPENDANCE OF THE FIGURE OF MERIT UPONG THE ABIOU FOR DIFFERENT ARCHITECTURES (BOTH QUANTITIES ARE       |      |

| PARAMETRIC FUNCITONS OF THE ARCHITECTURE THRESHOLDS).                                                                |      |

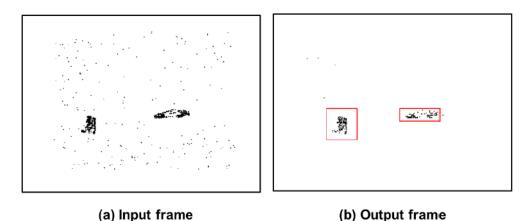

| FIGURE 73 : EXAMPLE OF REGIONS PROPOSALS GENERATED IN (B) FROM (A) (ACHARYA, PADALA, AND BASU 2019).                 | 128  |

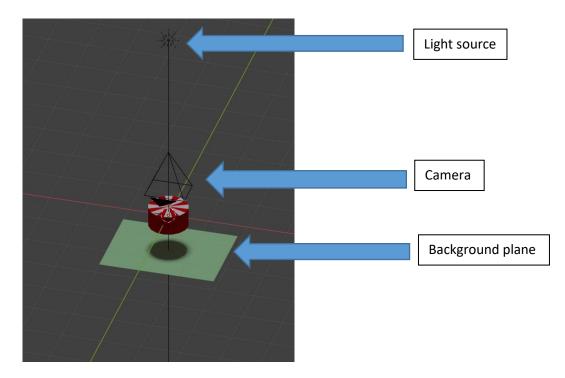

| FIGURE 74 : OUR ANIMATION SETUP FOR GENERATING OUR FIRST SYNTHETIC DATASET.                                          |      |

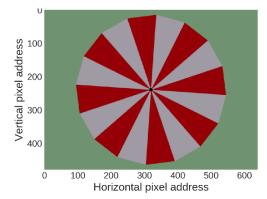

| FIGURE 75 : EXAMPLE OF A RENDERED IMAGE FROM THE VIDEO SEQUENCE GENERATED WITH THE SIMULATION SETUP FROM FIGUR       |      |

| (CUBERO ET AL. 2020)                                                                                                 | 132  |

| FIGURE 76 : LIGHT INTENSITY EVOLUTION FOR TWO PIXELS WHEN A COLOR-EDGE IS PASSING THROUGH. THE GRAY PLOT CORRESP     | ONDS  |

|----------------------------------------------------------------------------------------------------------------------|-------|

| TO A PIXEL FAR AWAY FROM THE POLYGON CENTER, WHEREAS THE RED ONE CORRESPONDS TO A PIXEL CLOSER TO THE CEN            | TER   |

| (CUBERO ET AL. 2020)                                                                                                 | 132   |

| FIGURE 77 : OUR ANIMATION-SETUP FOR OUR SECOND DATASET GENERATED.                                                    | 133   |

| FIGURE 78 : FIRST (A) AND LAST (B) FRAMES RENDERED FROM THE VIDEO SEQUENCE RELATED TO THE SETUP IN FIGURE 74.        | 133   |

| FIGURE 79 : EXAMPLE OF A RENDERED FRAME FROM THE OUTPUT OF THE RELATIVE-EDGES EXTRACTOR. COLORS INDICATE THE         |       |

| DETECTED EDGE DIRECTION (BLUE: 90 DEG, RED: 0 DEG, YELLOW: 45 DEG, GREEN: 135 DEG)                                   | 134   |

| FIGURE 80 : EXAMPLE OF HOW THE IMAGE PLANE IS PLACED INTO THE WORLD COORDINATE SYSTEM.                               | 135   |

| FIGURE 81 : EXAMPLE OF TWO RENDERED FRAMES WHEN ANIMATING A MOVING CHESS-BOARD PATTERN IN THE SCENE.                 | 136   |

| FIGURE 82 : RESULT FROM OPENCV FUNCTION FOR DETECTING THE CHESSBOARD PATTERN CORNERS AT FRAME 10 (A) AND AT F        | RAME  |

| 20 (в)                                                                                                               | 136   |

| FIGURE 83 : EXAMPLE OF THE FIRST (A) AND LAST (B) RENDERED FRAME FROM THE ANIMATION-SETUP FROM FIGURE 77, AND W      | /ITH  |

| GROUND-TRUTH BOUNDING-BOXES GENERATED WITH THE METHOD PREVIOUSLY DESCRIBED.                                          | 137   |

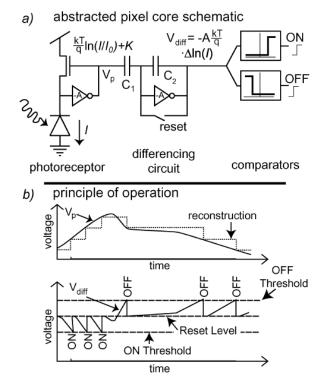

| FIGURE 84 : "(A) ABSTRACTED PIXEL SCHEMATIC. (B) PRINCIPLE OF OPERATION. IN (A), THE INVERTERS ARE SYMBOLS FOR SINGL | E-    |

| ended inverting amplifiers." (Lichtsteiner, Posch, and Delbruck 2008)                                                | 138   |

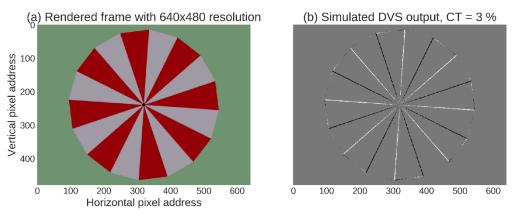

| FIGURE 85 : (A) EXAMPLE OF A RENDERED FRAME FROM OUR FIRST (VIDEO-SEQUENCE) SYNTHETIC DATASET, AND (B) EXAMPLE OF    | )F A  |

| RENDERED FRAME AFTER BEHAVIORAL SIMULATIONS OF A DVS (CUBERO ET AL. 2020)                                            |       |

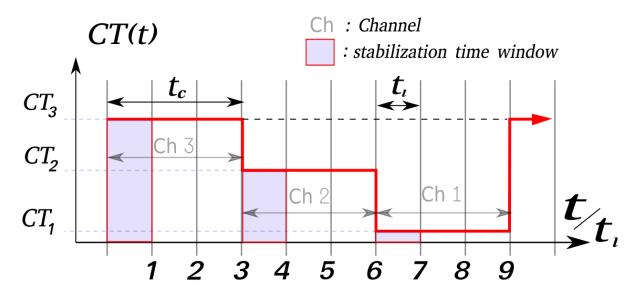

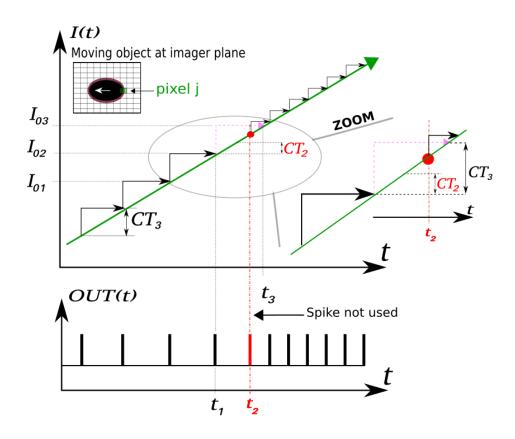

| FIGURE 86 : OUR PROPOSED MODULATION SCHEME (CUBERO ET AL. 2020)                                                      | 140   |

| FIGURE 87 : ILLUSTRATION OF HOW AN ABRUPT CHANGING IN CT TRIGGERS UNDESIRED SPIKES AT THE MOMENT OF THE CHANGIN      |       |

| (CUBERO ET AL. 2020)                                                                                                 | 141   |

| FIGURE 88 : DVS ORIGINAL SCHEMATIC (A) FROM (LICHTSTEINER, POSCH, AND DELBRUCK 2008) AND (B) OUR PROPOSED            |       |

| MODIFICATION FOR INCLUDING THE MODULATION PRESENTED IN FIGURE 86, AND PUBLISHED IN (CUBERO ET AL. 2020)              | 143   |

| FIGURE 89 : EXAMPLE OF OUTPUTS FROM THE THREE CHANNELS DURING ONE MODULATION PERIOD (CUBERO ET AL. 2020)             | 144   |

| FIGURE 90 : INSTANTANEOUS DATA THROUGHPUT FOR THE ORIGINAL DVS AND FOR OUR THREE MODIFICATIONS. THE TABLE AT         | THE   |

| TOP PRESENTS THE AVERAGE DATA THROUGHPUT                                                                             | 144   |

| FIGURE 91 : OUR DYNAMIC FEATURES EXTRACTION METHOD COMPARED WITH THE STATE OF THE ART.                               | 145   |

| FIGURE 92 : DIAGRAM ILLUSTRATING THE PRINCIPLE OF FUNCTIONING FOR EXTRACTING DYNAMIC FEATURES FROM TWO SUBSEQUE      |       |

| FEATURE MAPS                                                                                                         | -     |

| FIGURE 93 : SIMULATION OUTPUT FROM THE DFVS (LEFT) AND A STANDARD DVS WITH CT = 3 % (RIGHT), AT TWO DIFFERENT        | TIMES |

| OF THE VIDEO SEQUENCE FROM THE THREE-SPHERES-OVER-GROUND DATASET                                                     |       |

| FIGURE 94 : DIAGRAM SHOWING HOW WE MODIFIED EDGEBOXES IN ORDER TO INCLUDE DYNAMIC FEATURES IN THE ROI PROPO          |       |

| GENERATION                                                                                                           |       |

| FIGURE 95 : AVERAGE RUNTIME PER IMAGER FOR DIFFERENT ARCHITECTURES, SHOWING THE GAIN IN RUNTIME WHEN USING DYN       | VAMIC |

| FEATURES ALONGSIDE WITH EDGEBOXES                                                                                    | 150   |

### List of tables

| TABLE 1 : COMPARISON OF THE HYBRID-CNN IMPLEMENTATION AND PREVIOUS WORKS (JH. KIM ET AL. 2019).                             |          |

|-----------------------------------------------------------------------------------------------------------------------------|----------|

| TABLE 2 : THE HYBRID-CNN IMPLEMENTATION VERSUS PREVIOUS WORKS (JH. KIM ET AL. 2019).                                        | 60       |

| TABLE 3 : BENCHMARK OF PERFORMANCES FOR DIFFERENT REGION PROPOSALS ALGORITHMS: " FOR IOU THRESHOLD OF 0.                    | 7.       |

| METHODS ARE SORTED BY INCREASING AREA UNDER THE CURVE (AUC). ADDITIONAL METRICS INCLUDE THE NUMBER                          | OF       |

| proposals needed to achieve 25%, 50% and 75% recall and the maximum recall using 5000 boxes" (Zi                            | TNICK    |

| and Dollar 2014).                                                                                                           | 61       |

| TABLE 4 : MOST-RELEVANT-VARIABLES SIZE-ESTIMATION FOR THE FIRST EDGEBOXES STAGE; SEGMENTS = $2int = 216$ (w                 |          |

| CASE)                                                                                                                       | 66       |

| TABLE 5 : MOST-RELEVANT-VARIABLES SIZE-ESTIMATION FOR THE SECOND EDGE-BOXES STAGE; H = W = 500 PIXELS.                      | 67       |

| TABLE 6: TRUTH TABLE SUGGESTED BY (YOUNG ET AL. 2019) FOR APPROXIMATING LOGARITHMIC 2-BIT GRADIENT-COMPONE                  | ENTS 79  |

| TABLE 7: POWER ESTIMATION WHEN TAKING $Vi = 1,5 V, I1 = 1 \mu A, H = W = 500 pixels$ , and $fps = 60 fram V = 500 pixels$ . | ıes/s.   |

|                                                                                                                             | 90       |

| TABLE 8 : EXAMPLE OF VALUES CALCULATED FOR $ID$ when $CH = 100  fF$ , $Nc = 1$ and $H = 500  rows$                          | 92       |

| TABLE 9 : UPDATED POWER CURRENT ESTIMATION WHEN TAKING V_AMPDD=1,5 V,C_H=100FF,H=W=500 PIXELS,V_R=                          | 1 V, AND |

| FPS = 60                                                                                                                    | 92       |

| TABLE 10 : UPDATED POWER ESTIMATION WHEN TAKING V_DD=1,5 V,C_H=100FF,H=W=500 PIXELS, AND FPS = 60                           | 93       |

| TABLE 11 : CLASSES FOUND IN THE PASCAL VOC 2007 DATASET(M. EVERINGHAM ET AL. N.D.; N.D.; MARK EVERINGHAM ET                 | ΓAL.     |

| 2015), AND ONE EXAMPLE IMAGE WITH TWO CATS                                                                                  | 101      |

| TABLE 12 : DIFFERENT TYPES OF LIGHT-INTENSITY ORIENTED GRADIENT EXTRACTORS TYPES CONSIDERED IN OUR LOCALIZATION             | 1        |

| BENCHMARK.                                                                                                                  | 103      |

| TABLE 13 : SELECTED THRESHOLDS VALUES ISSUED FROM SIMULATION (SELECTED AS DESCRIBED IN CHAPTER 3).                          | 107      |

| TABLE 14 : NORM-NUMBER-OF SEGMENTS, NORM-SEGAFFSIZE, AND GLOBAL-ABIOU FOR THE RELATIVE ORIGRAD WITH AVE                     | ₹. DE-   |

| NOISING AND BINNING                                                                                                         | 118      |

| TABLE 15 : CUMMULATIVE TIME IN SECONDS PER IMAGE                                                                            | 149      |

| TABLE 16: SUMMARY OF SYNTHETIC IMAGES RESOLUTION                                                                            | 150      |

# Chapter 1. Introduction

Computer vision and artificial intelligence have opened a new range of applications. For instance, machines have become able to solve complex problems for object localization and classification, and also with high resolution images. That is, even if challenging characteristics such as high dynamic range, occlusion and significant affine/projective transformations are present. Moreover, most recent algorithms, based on deep convolutional neural networks (CNNs), have shown capacity to classify objects from an elevated amount of different classes.

Nevertheless, some of those new applications are simply incompatible with desktop-machine computations and/or servers: typical limitations in latency, autonomy, size, weight and financial cost constraint the computational unit to be compact and portable. Probably, one of the most common use-case scenarios are mobile phones. In addition, other examples where such limitations are present are drones, autonomous vehicles, video surveillance and wearable devices, among others. The aforementioned means that such smaller devices are logically less equipped, and thus it is common to say that they are under "hardware and power constraints".

Regarding the last sentence, power consumption restrictions typically arise when devices are not connected to a "permanent" energy source, but they rather depend on a battery. Of course, for being smaller, the battery size has to be reduced too, and thus its lifetime (before re-charging) as well. Yet, computer vision tasks are often related to computationally intensive operations, and, for instance, CNNs are not an exception. In parallel, each computation implies energy, and the faster the system goes, the more power is drained from the battery. In the other hand, sending data out from the system to a remote server is possible, but the energy cost of this I/O bus is significant and often unsuitable if the data-rate is too high.

Last paragraphs sets motivations for one entire research field: one that is focused on computer vision and/or artificial intelligence on hardware/power constrained devices. The set of problems addressed commonly cannot be reduced to simply "take" the exact same algorithm and then "run it" on an embedded device. Typical reasons for that are that embedded devices have, for example, less memory available, a reduced instruction set (e.g. summation, subtraction, bit-shifting, etc...), and less energy compared to desktop computers or servers. Those reasons are why efforts are made in optimizing, simplifying and/or adapting algorithms and hardware, so even embedded systems can perform more complex computer vision tasks.

Continuing with last ideas, our work focuses on optimizing the power versus AI performance trade-off for object detection. Object detection is a known problem in artificial intelligence and computer vision: the problem is giving bounding-boxes for objects in a still image as the algorithm output, along with class labels for each object inside each bounding box. Moreover, as other groups do, our approach is to include more complex/adapted operations on the same integrated chip, so the I/O data-rate with remote servers and/or other chips is reduced. Furthermore, as other groups do as well, we optimize the algorithm/hardware to make it more energy-efficient. We take into account the development of newer microfabrication technologies allowing 3D-IC staking for justifying the addition of more complex circuitry.

More specifically, we tackle the last mentioned problem by optimizing the region-proposals stage and the low-level-features generation in the object detection pipeline. We explore the inclusion

of circuitry specialized on generating low-level hand-crafted features for region proposals. We also explore both frame-based (classic) and asynchronous/neuromorphic (non-classic) pixel topologies for achieving it. We believe that region proposals can replace other typical IC implementations that rely on the older sliding window approach, and for energy efficiency. That is, since the computational complexity of the sliding window makes it inefficient or even unsuitable for solving problems with a high-scale-range or with high-resolution images. Indeed, with the so-called sliding window, embedded object detection can be constrained to "small" images only, and with objects in positions and/or scales that are relatively "easy" to solve, or in other works, incompatible with real-case/outdoors scenarios.

This work has been made in a laboratory called CEA-LETI/L3I: a group specialized in CMOS image-vision-sensor development, and also in integrated, low-power image pre-processing electronic architectures. The laboratory is located in Grenoble, France, and it forms a part of a bigger entity called the Commissary of Atomic Energy and Renewable Energies (CEA). The CEA counts with different laboratories in a wide range of fields, from fundamental sciences to applied electronics.

Our manuscript is composed of eight chapters (counting the introduction and conclusion). Chapter two gives a brief view of the state of the art in CMOS image-sensors, smart-imagers and object detection algorithms. Chapter three presents our simulation and modeling methodology, which we use to derive conclusions for the electronic-architecture design. Chapter four explains which kind of object detection pipeline we propose to use for embedded applications. Chapter five presents the low-level features architecture that we propose to use for region-proposals-generation. Chapter six presents a series of benchmarks that show (at simulation level) that our pipeline is suitable for region-proposals-generation on constrained devices. Finally, chapter seven presents further models and simulation results regarding the implementation of non-classic, neuromorphic pixels for optimizing the region proposals generation as well.

# Chapter 2. State of the art

Chapter 2 describes the main theoretical concepts for the general understanding of this thesis. We present a synthesis of our State of Art review, so the reader can find here a (non-exhaustive) list of related works. The first principal subject mentioned is "CMOS" Image sensors: we cover from photogeneration to digital-image-output. We do so for different light-sensing types, and for several pixel architectures. However, we do not go into details, as we only cite relevant ideas for later in this work. The second principal subject is what a "smart-image-sensor" is. We explain it by signaling key differences with classic architectures, and by citing illustrative examples in the state of the art. The final subject covered here is the "object-detection" problem: it comes from the fields of Artificial Intelligence, Machine-learning and Computer-vision. We describe its formal definition, and later we relate it with applications and implementations in the embedded-IC case-scenario.

#### 2.1. CMOS Image sensors

The term « CMOS » is an acronym for « complementary metal oxide semiconductor » (El Gamal and Eltoukhy 2005). The name describes a specific type of electronics-related technology and physics knowledge, allowing creating devices known as CMOS transistors. CMOS transistors are useful to create simple or complex circuits, as switches, amplifiers and digital-processors, among many others. During advances in imaging techniques, CMOS technology became attractive for devices that generate a static image of a scene. In order to achieve that, transistors, combined with light-sensing devices (photo-transductors), have been used for locally transforming impinging light into an electric signal. This setup is known as a "pixel". Pixels arranged into matrices are capable of generating an image. For the present work, one needs to understand how the signal goes from photo-generation to a digital image. In addition, the reader should know the behavior (operation) of the basic pixel types.

#### 2.1.1. Typical system architecture

Classic CMOS image-sensors typically relate to a matrix of pixels. Each pixel transforms the local impinging light into an electric signal. In this work, we refer to an imaging-system as the combination of the image-sensor (including the pixels matrix), the optics that set how light rays are directed to pixels, and the read-out that outputs a digital-image. Another aspect is how such signal goes from the pixel to next stages. Indeed, this signal corresponds to a photo-generated electric-charge stored into a capacitance -at each pixel. This charge gives rise to an output voltage for each pixel, which directly relates to the amount of impinging light -into each pixel. For recovering the whole image, the read-out stage, after the imaging-part, has to output the voltage read at all pixels. Nevertheless, later stages normally are digital-based, whereas voltage-signals from pixels are analog values. Then, after reading each pixel voltage, the image-sensor has to "transform" analog values to digital ones (e.g. the analog-to-digital conversion). This process can be achieved in several manners, as shown in Figure 1.

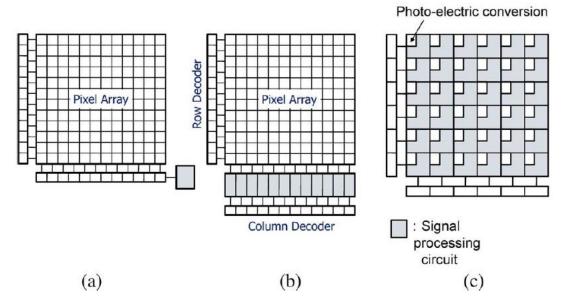

Figure 1 : different approaches for pixels pre-processing and/or read-out. "(a) serial architecture; (b) column-parallel architecture; (c) pixel-parallel architecture." (Takayanagi and Nakamura 2013)

In Figure 1, authors (Takayanagi and Nakamura 2013) explain three different image readout and/or pre-processing schemes. Figure 1 takes into account signal-processing and read-out, but for now we take only the read-out into account (letting more complex pre-processing types for section 2.2): one possibility (Figure 1 a) is to read pixels one by one, while using only one unit for carrying-out the A-D conversion. Here, transistors are used as switches for selecting which pixel value goes to the ADC. Typically, a digital controller circuit selects a row of pixels and allows them to store their values in a column analog part. This part stores, "de-noises" and amplifies pixel values. Then, another digital controller-circuit selects these pixel values, one by one, and sends them to the ADC. Another possibility (Figure 1 b) is to have one ADC per column: a digital-controller selects only the row to convert, and then all pixels of the selected row are read in parallel (with a stack of parallel ADCs). This architecture is the current one in industry of image-sensors. Another possibility (Figure 1 c), is to perform the A-D conversion at the pixel level by implementing one single ADC for each pixel. Notice that the name "Signal processing circuit", used in Figure 1, illustrates that more (pre-) processing can be performed near sensor (or matrix of sensors). That can be done even without and/or beyond the standard A-D conversion. In next section, we go a bit deeper into the inner structure of pixels, and we briefly explain several of the most common variants.

#### 2.1.2. Pixel types

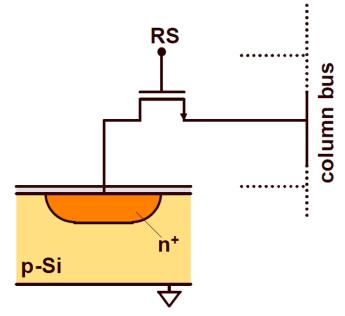

In previous part, we have cited the overall (frame-based) image-sensor architecture(s). Here, we go deeper into detail about pixel configurations and the main aspects for choosing amongst them. Figure 2 shows one simple pixel: it consists in a p-n junction in reverse-biasing conditions, a RS (row-select) switch, and a column bus (shared by all pixel on the same column). The reverse p-n junction is the photo-sensitive area (i.e. where impinging photons give rise to photo-generated electron-hole pairs). Holes drift to ground, and electrons cumulate in the junction capacitance. This charge generates an electric signal that is temporarily stored in the junction-capacitance until the read. For reading one

pixel, the row is selected by the RS switch, while the corresponding column bus is addressed, for instance, by a column-decoder. For this particular case (called the passive pixel sensor PPS), when the signal is read, charges "escape" from the junction capacitance, and thus the reading process is "destructive". The PPS has the advantages of being simple and compact, thus favoring the easiness of higher fill factors. Nevertheless, it typically suffers from poor performances (e.g. regarding noise) respect to later topologies (Theuwissen 2007).

Figure 2 : illustration of the passive pixel in CMOS technology (Theuwissen 2007).

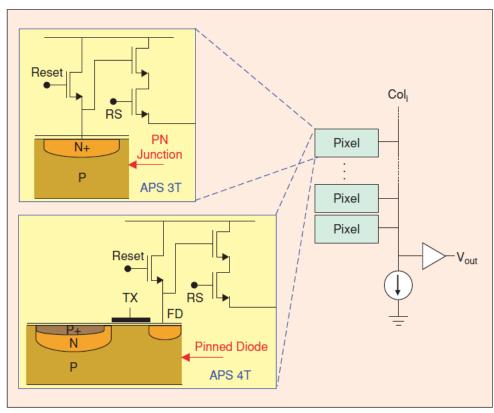

After the PPS, CMOS imaging was improved with the introduction of the so-called "Active Pixel Sensor" or APS, illustrated in Figure 3. We base our explanation from (El Gamal and Eltoukhy 2005), which gives a good overview. The term "active" comes from the amplifier (buffer) between the electric signal (the photodiode voltage) and the column bus. In this case, the readout is non-destructive. Moreover, one reset switch controls when photo-generated charges, which are stored in the junction capacitance, are discarded. The intermediate buffer-amplifier adds 1 transistor respect to the PPS, and the Reset adds another extra transistor. This is why this pixel configuration is known as the 3T-APS. This configuration allows improving the SNR respect to the PPS (El Gamal and Eltoukhy 2005), but still presents an important noise contribution from the "reset-noise". In order to circumvent that, a forth transistor allows performing the so-called "correlated-doubled-sampling (CDS)" (El Gamal and Eltoukhy 2005). The 4T-APS is shown in Figure 3, bottom. Then, this pixel is known as the 4T-APS. This fourth transistor is, however, less conventional respect to the others in the pixel, since one of its terminals can be made of the so-called "pinned-photodiode" (El Gamal and Eltoukhy 2005). The pinned photodiode is the current industrial-standard pixel structure. Moreover, its dark-current is less important with respect to non-pinned junction. In addition, and regarding Figure 3 (bottom), signal TX allows splitting the photo-generated signal from the reading node FD. Thus, the reset signal is sampled at FD (almost) immediately before the photo-generated signal "passes" to FD (thus enabling CDS). This readout process is also non-destructive. Moreover, CDS can be set aside for the 4T-APS if a "globalshutter" readout scheme is desired. Until now, pixels are read "one by one", but photo-currentintegration is still happening during read time as well (a method known as the "rolling-shutter" reading scheme). In general, this effect is not desired. For instance, one way for letting away the rolling-shutter technique is by passing all photo-generated charges to the sensing node FD at once. That means that photo-current-integration stops at the same time for all pixels. This strategy is the so-called globalshutter in the literature.

Figure 3 : illustrations of the active 3T (top) and 4T (bottom) pixels (El Gamal and Eltoukhy 2005).

The last example we present is the 1.75T-APS (Figure 4). We base our description from (El Gamal and Eltoukhy 2005). This pixel allows performing neighboring-pixels-binning and at pixel level. Binning is important for us, since we want to assess the optimal image size for object localization / classification, and the impact of image binning on algorithms performances (e.g. object localization).

Figure 4 : illustration of the in 1.75T architecture (El Gamal and Eltoukhy 2005).

In next section, we explain some important image-sensor design parameters that we mention often during this work.

#### 2.1.3. Typical design parameters

We base our explanation of typical design parameters from the work of (El Gamal and Eltoukhy 2005). (El Gamal and Eltoukhy 2005) explain several performance measures, and non-ideal-effects that are often mentioned in this work. They separate those non-ideal-effects into "temporal" and "fixed-pattern-noise (FPN)". As its name suggests, temporal noise depends on time, and thus it can make the signal to change between successive readings (instead of keeping steady until the reset). On the other hand, FPN does not depend on time, but on space: it corresponds to differences in amplifiers offsets and gains across (for instance) different pixels. In addition, (El Gamal and Eltoukhy 2005) explain that temporal noise sources are (without being exhaustive) "shot noise, pixel reset circuit noise, readout circuit thermal and flicker noise, and quantization noise" (El Gamal and Eltoukhy 2005).

(El Gamal and Eltoukhy 2005) also mention important design parameters, such as the "signalto-noise-ratio" (SNR) and the "dynamic-range" (DR). The SNR is 10 times the base-10 logarithm of the ratio of signal power and noise power:

$$SNR = 10 \cdot \log\left(\frac{P_{sig}}{P_{noise}}\right)$$

Equation 1

Where  $P_{sig}$  is the signal power and  $P_{noise}$  is the noise power. The higher the SNR, the greater is the signal respect to the noise. Moreover, the DR states the range of illumination (photons) that the image-sensor can collect and read from each pixel, settling a minimum and a maximum value. Mathematically the DR is 20 times the base-10 log of the ratio of maximum photo-current and the minimum photo-current (El Gamal and Eltoukhy 2005). The last parameter cite here from (El Gamal and Eltoukhy 2005) is the "spatial resolution".

So far we have mentioned classic architectures and parameters of image-sensors. In next section, we introduce newer ideas, which try to include more complex signal (pre-) processing schemes.

#### 2.2. Smart CMOS image sensors

Smart-image-sensors differentiate from classic approaches due to the inclusion of integrated signal (pre-) processing. These kind of devices go beyond the typical scheme of in-pixel buffer-amplifier, column read/amplification and signal A-D conversion. The aim of integrated "smart" capabilities can be further improving design parameters (SNR, DR, etc), and at the cost of an increasing on-chip complexity. Another objective can be integrating ("embedding") artificial-intelligence algorithms, in order to optimize performance at the system level, e.g. allowing for higher speed and/or attaining lower power consumption. This work is concerned by the second case scenario, related to embedded/integrated artificial intelligence for computer vision applications.

There are several reasons for which "integrated-smart" capabilities are attractive. In the context of internet of things, distributed sensor networks, mobile robots, wearable devices, etc, devices have a limited battery that should last as long as possible without recharging. This rises the interest for "low-power" devices, which can perform artificial-intelligence-related tasks but without "draining" the battery. Reducing power has been tackled in different ways in the literature. Some trends (without being exhaustive) are reducing inter-chip data throughput by including pre-processing steps in the same chip as the image-sensor. For instance, (Verdant et al. 2020) integrated the full object-recognition pipeline into one chip with an innovative (low-power) read-out. Other strategies have been optimizing the ADC by reducing its bit-depth output, and by changing the image codification as done by (Young et al. 2019). In addition, other works have tried performing more complex computations in the analog domain (so the ADC workload is significantly reduced), such as CNN-layers, like in (J.-H. Kim et al. 2019).

In this work, we focus on two main types of smart-image-sensors: namely, frame-based (FB) image-sensors and event-based image-sensors. So far, concepts introduced apply for FB image-sensors, whereas event-based image-sensors are just briefly explained in sub-section (2.2.2). We go more into details about event-based-imaging in chapter 7.

#### 2.2.1. Frame-based smart-image-sensors

Frame based (FB) image-sensors are characterized by a deterministic read-out scheme. In other words, the pixel readout sequence is always the same and the frame rate is constant. Moreover, each output is an image, which is acquired by two main stages: integration, and read-out. During integration time, all pixels start sensing impinging photons. Then, during read-out, pixels voltages are read by any of the schemes shown in Figure 1. For the case of FB smart-image-sensors, a (pre-) processing stage can be included to the frame-time. In next subsections, we explain some topologies in the literature following the latter idea. Notice that integration examples we found (in relation to our work) were typically related to edges or oriented gradients extraction (and/or related pipelines).

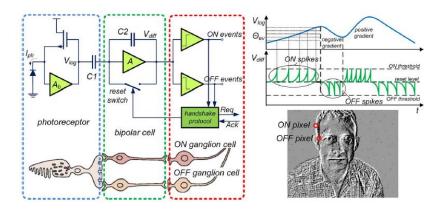

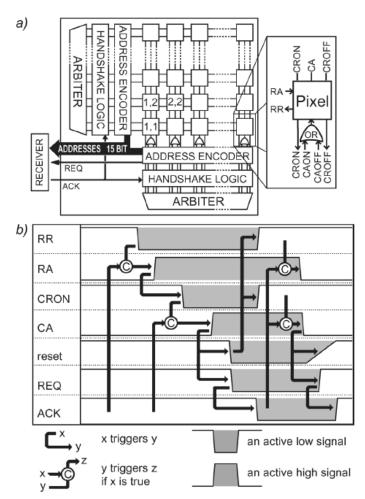

#### 2.2.2. Edge or Oriented Gradients extraction

Edge-extraction<sup>1</sup> consists in computing image intensity gradients, followed by a "thresholding" operation: only pixels with a gradient magnitude higher than a certain threshold are kept. This kind of task has been included in the ADC, and some examples are (H.-J. Kim et al. 2017) and (Young et al. 2019). For instance, (H.-J. Kim et al. 2017) implemented a read-out scheme for outputting both 5-level edges data and a light-intensity-image. Furthermore, they reported a figure of merit of 70 pJ/pix/frame. For the case of (Young et al. 2019), they proposed an ADC capable of outputting logarithmic light intensity gradients on the fly. Their proposed complete system (see Figure 5) allowed detecting objects from different classes, such as humans. The logarithmic-gradients-output from their smart-imaging-system allowed better robustness under illumination conditions (e.g. high dynamic range). That was, even under strong quantization of the log-gradients, and which they linked to the logarithm-based gradients (related to pixel-intensities ratios instead of differences). In their pipeline, logarithmic-gradients were the input for another computing stage (only simulated). There, they computed the HOG features (Dalal and Triggs 2005), which derived from the oriented-gradients image. They used those with an object-detection framework and algorithm called the Deformable-Parts-Model (P. F. Felzenszwalb et al. 2010) or DPM. The later uses a strategy based on pictorial structures, and Support-Vector-Machines, to localize and classify objects in an image.

<sup>&</sup>lt;sup>1</sup> We take the convention of calling "edges" the image-gradients whose magnitude is higher to any threshold.

Figure 5 : logarithmic gradients object detection pipeline (Young et al. 2019).

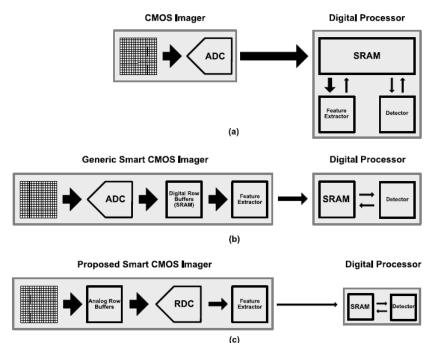

Figure 6 : distribution of power consumption for the implemented circuit from (Young et al. 2019)

Figure 6 shows their (Young et al. 2019) power consumption decorticated for their implementation. Notice that they implemented only the pixels-array and the logarithmic ADC (called "RDC" by them). From that figure, we observe that the orange, gray and yellow blocks are related to the log-gradients ADC, which was capable of computing log-oriented gradients on the fly. Their reported power per pixel per frame was of **99 pJ/pix/frame** (including the blue block) in Figure 6. Their log-gradients ADC is shown in Figure 7: Their circuit was capable of sampling two pixels from which the local log-gradient was obtained. The circuit used a successive approximation strategy for addressing each gradient-component magnitude and sign.

*Figure 7 : circuit schematic for logarithmic gradients extraction (Young et al. 2019)*

Other edge extractors have been proposed, which typically implement linear versions of the gradient approximation (instead of log), and at the bottom-of-the-column level. For instance, (Soell et al. 2016) proposed an analog edge-extraction circuitry for a matrix of 200x200 pixels that consumed (in simulation) 5.5 mW@75 fps (2097 pJ/pix/frame). Their work was interesting for us since they show clever circuit ideas for analog implementation (showed in Figure 8). Their architecture was based on computing both gradient components with a Sobel kernel. Then, they used both components for approximating their respective absolute value, and finally the magnitudes-sum. If the sum of both absolute-values was higher than a reference threshold, then the 1-bit output was set to "high" (indicating the present of an edge). One of the main drawbacks we found from this architecture was that no angular information was output.

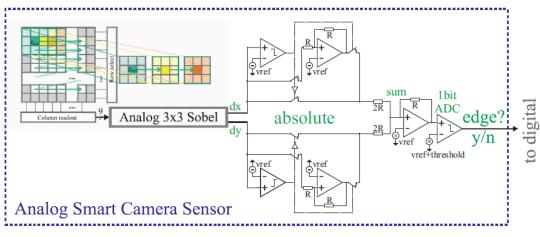

Figure 8 : circuit schematic for Sobel-like edge-magnitude-extraction (Soell et al. 2016)

Other edge extractors have computed gradients and angles in the digital side (after the ADC). For instance, (Suleiman and Sze 2014). However, as mentioned by (Omid-Zohoor et al. 2018), digital computations with the ASIC proposed by (Suleiman and Sze 2014) could imply using a standard CMOS image sensor for extracting image intensities with 8-bit resolution images, which would consume more power for the ADC than for the feature extraction. One argument can be that 8-bit intensity images

are not really necessary, and that a reduced bit depth is possible. However, (Omid-Zohoor et al. 2018) also shows that reduced-bit-depth-linear-gradients are more prone to fail under high dynamic-range conditions. Another digital implementation of the edge extraction, after the ADC, was proposed by (Jin et al. 2020): their implementation had 1920 x 1440 pixels and consumed 9,4 mW@60fps (**57 pJ/pix/frame**). However, their work does not address how to cope with high-dynamic-range conditions, neither how power would change if the angular information is needed. (Choi et al. 2014) proposed a digital block right after the A-D conversion, which can also calculate orientations. Moreover, their implementation also computes HOG features right after oriented gradients calculation. Their reported FOM was **51.94 pJ/pix/frame**, *but it cannot directly be compared* with other examples, since it also includes the HOG features generation from the oriented gradients. In the other hand, they did not take into account high-dynamic range optimizations.

Indeed, when comparing the work of (Soell et al. 2016) (2097 pJ/pix/frame) with respect to (Jin et al. 2020) (57 pJ/pix/frame) and (Young et al. 2019) (99 pJ/pix/frame), the increased power of the analog Sobel implementation can be explained by several reasons : firstly, they read pixels several times directly from the pixels matrix, implying the usage of amplifiers able to drive the column capacitances. One possible improvement, already applied by other works such as (Young et al. 2019), is buffering pixel values that are required more than once. Moreover, the Sobel filter mask is rather complicated in comparison with, for example, the mask used by (Young et al. 2019), which only requires 2 pixels per component computation. Finally, from their publication (Soell et al. 2016), we understood that the analog Sobel computing unit was shared and not parallelized at the bottom-of-the-column level. This increases significantly the bandwidth requirements for this unit, increasing the power consumption. However, we still find the schematic from Figure 8 important since it gives an insight of implementation and potential optimizations.

Other edge extractors have included corresponding electronics in pixel. Typically, the gain happens potentially in latency or power, since signals do not have to be transmitted before being processed. For example, (Valenzuela et al. 2021) proposed a smart-pixel array capable of computing pixel differences, and in order to generate a kind of feature (related to gradients) proposed by them: the Ringed Local Binary Patterns (Valenzuela et al. 2021). However, we did not find in their publication the power related for the smart-pixels-array, and for the analog-to-digital conversion. Another example is the work from (C. Lee et al. 2015): their implementation was able to detect edges, and with a power consumption of 8 mW@30fps over a 105 x 92 pixels matrix (27605 pJ/pixel/frame). In addition, (Yin, Chiu, and Hsieh 2016, 14) implemented an array of pixels with PWM read-out, and with in-pixel circuitry for Imaging, edge-extraction and multi-point tracking. As an example, the edgeextraction was based on pixel-intensity-comparisons (of a central pixel with its neighbors). This comparison was made with in pixel-logic, and whose output was either 1 or 0 for reflecting the edge magnitude. Their implementation consumed 34.4  $\mu$ W@2160 fps for an array of size 64 x 64, giving a FOM for edge extraction of ~3.89 pJ/pix/frame. Interestingly, in imaging mode, their implementation consumed 154  $\mu$ W@30 fps, giving a FOM of ~1253 pJ/pix/frame. The latter example reflects the gain of three orders of magnitude after exchanging the image codification from intensity to edges. This work is interesting from the point of view of having a very good FOM for edge extraction mode. However, several drawbacks limit our interest about their approach: firstly, the pixel complexity, containing 26 transistors per pixel, would be challenging to scale to bigger resolutions, and could show very poor fill factors. Secondly, the way edges are extracted reflects a rather simplistic logic, which is not justified to work in more complex computer vision algorithms. Finally, they do not output orientation information if an edge is detected.

One interesting question is how reported FOMs compare to a FPGA implementation. We found an example of a Canny Edge Detection algorithm implementation on FPGA (J. Lee, Tang, and Park 2018). The Canny Edge Detection algorithm runs on standard desktop computers with libraries such as OpenCV ("OpenCV, Canny Edge Detector" 2021). Continuing with last example, (J. Lee, Tang, and Park 2018) reported an optimized algorithm and implementation (on FPGA) of the Canny-Edge-Detection algorithm. It consumed 5.48 mW@50 fps for a UHD image (3840 x 2160 pixels, giving a FOM of **13.1 pJ/pix/frame**). This illustrates that features/edges computations is not necessary the most consuming part. Moreover, last examples show as well that analog computations are not necessarily less power consuming than, for instance, the more standard pipeline Image-array -> 8-bit ADC -> processing ASIC. One example supporting this argument is the work from (Choi et al. 2014), and which had a good FOM of ~52 pJ/pix/frame. Nevertheless, even though the work of (Young et al. 2019) has not the best FOM (99 pJ/pix/frame), they are the only example we found that address high-DR for feature extractors along with aggressive quantization, and that proves (with benchmarks) the interest for Object Detection.

From last examples, we observed certain trends that served us as starting point: firstly, low power optimizations seem to benefit most from near matrix-of-pixels integration of custom-ADCs. In addition, they benefit from specialized circuitry for features extraction. From examples we have found, we did not observe a conclusive reason to say that an analog or a digital implementation is more performant. The work from (Choi et al. 2014) made us wonder if computing the edge-extraction at the analog-side (and thus eliminating the need for 8-bit ADCs for A-D conversion of pixel-intensities) would lead to a significant gain in power. Moreover, from the work of (Young et al. 2019), we observed that column-parallel computations gave a much better significant FOM, and even for more complex processing (of log-gradients) with respect to the work of (Soell et al. 2016). In our work, we wonder if log-gradients could be implemented differently if we could implement another architecture which potentially gives a better FOM for oriented-edges-extraction. We did not find any particular interest in on-pixel edge-extraction, based on cited examples from the state of the art. Examples we found, like (C. Lee et al. 2015; Yin, Chiu, and Hsieh 2016, 5) were related to at least a subset of issues such as: relatively high power consumption, high pixel complexities, poor fill factors, and limited pre-processing capabilities because of the on-pixel size constraints.

We also observed relevant aspects regarding implemented algorithms for object localization or classification based on gradient-like features. Typically, different works choose a specific type of computer vision problem (e.g. face detection, identity verification, classification / recognition, etc...) and then they benchmark their implementation with a particular dataset (made by them or not). Nevertheless, most of the works we found only focus on processing images with only one object centered in them, like (Verdant et al. 2020). This might not be suitable for real case ("outdoors / out of lab") scenarios. In this work, we have chosen the Object Detection (OD) problem (localization + classification), since it is still challenging due to its complexity, and because it may have a wide range of applications that could be used in more specific contexts (autonomous driving, gaming, surveillance, etc...). The work from (Omid-Zohoor et al. 2018) (Young et al. 2019) took such approach, and they also chose OD for benchmarking the output from their imager. They used an algorithm called the Deformable Parts Model (P. Felzenszwalb, McAllester, and Ramanan 2008) (DPM), which is further explained in section 2.3.2. Nevertheless, in our work we wonder if there is a better pipeline respect to the DPM model, which, for example, would be suitable for more modern algorithms such as low-power CNNs.

Coming back to the work from (Verdant et al. 2020), their work is interesting for us, since they implemented an end-to-end image-acquisition and object recognition on chip. For the image

acquisition, they changed the standard image read-out for one that they called "Fastscan" (Verdant et al. 2020), and then they fed the image to a quantized SVM to compute binary classification "on the fly". Their reported figure of merit for image acquisition plus object recognition was **53-59 pJ/pix/frame** for "intra-frame processing" (Verdant et al. 2020). Thus, they achieved a good figure of merit even with respect to works that only include the feature extraction. However, there are questions that, from our point of view, are yet to be clarified: firstly, the problem they solve (object recognition) is significantly simpler that problems tackled by, for example (Choi et al. 2014), and (Young et al. 2019). That is, since they targeted multi-scale and multi-class object detection. Then, it is not clear if the good FOM reported by (Verdant et al. 2020) comes from their read-out scheme and quantized SVM implementation, or just from the more simplistic machine learning problem. Secondly, and related to last sentence, there is not enough insight in the dataset they used. Therefore, we do not know how difficult the dataset is (e.g. presence of high dynamic range, variation in object's position, occlusion, etc...). Finally, it is not clear if the edge-extraction performed on-the-fly can actually profit from the full imaging-system-DR of 36 - 88.3 dB (Verdant et al. 2020), as targeted for example by (Omid-Zohoor et al. 2018) with their logarithmic features.

So far we have cited examples for edge-extractors. Those architectures are part of a bigger family of features called in the literature "hand-crafted-features". That is, they are human-made and tuned. The opposite corresponds to algorithms that only "impose" shapes of operations performed on data, but they do not set fixed coefficients that appear during the (pre-) processing. Instead, many of those coefficients (and the logic behind them) are "learned" under a data-driven training-process, known in the literature as "supervised learning" and explained in (Khan et al. 2018) (i.e. the algorithm is trained by using example data, where each example is labeled with ground-truth annotations). In next subsection, we cite several examples of smart-imaging-systems which implement one specific kind of trained-algorithms: the so-called "Convolutional Neural Networks".

#### 2.2.3. Embedded CNN-like features extraction

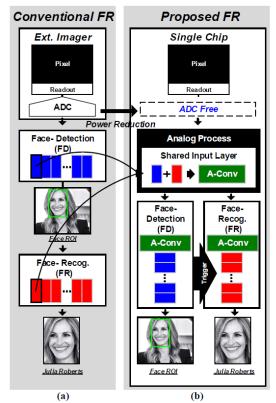

(J.-H. Kim et al. 2019) proposed a smart-imaging-system including a convolutional neural network (CNN). CNNs typically require multiply-accumulation (MAC) operations for subsequent cross-correlations of different kernels with the image. Moreover, the need memory access for kernel-coefficients (weights) loading and for intermediary operations. Finally, they require units capable of performing the activation-function (e.g. ReLu). In their work, (J.-H. Kim et al. 2019) implemented a CNN distributed between the analog and the digital domain. One particularity of such approach, is that no ADC is needed.

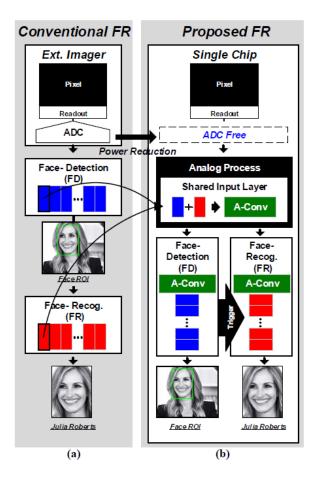

Figure 9 illustrates the difference between more classic face recognition approaches and theirs. The ADC is not present, and instead, an analog unit computes the first convolution stage. The output is a 2-bit low-level-features map (after a ternary quantizer), which is used by two CNNs in the digital domain. One CNN is "always-on", and it is in charge of finding faces. In one face is detected, then another CNN is "woken-up" for the identity verification process.

Figure 9 : "(a) Conventional face recognition system (b) Proposed recognition system" (J.-H. Kim et al. 2019).

|            | JSSC'17 [4]              | JSSC'18 [5]        | This Work                    |

|------------|--------------------------|--------------------|------------------------------|

| Technology | TSMC 40nm                | Samsung 65nm       | Samsung 65nm                 |

| Algorithm  | FD: Haar-like            | FD: Haar-like      | FD&FR :                      |

| Algorithm  | FR: PCA+SVM              | FR: CNN            | Analog-digital<br>hybrid CNN |

| Accuracy   | 81% @ 32-class in<br>LFW | 97% @ whole<br>LFW | 96.18% @ whole<br>LFW        |

| Resolution | HD                       | QVGA               | QVGA                         |

| Power      | 23mW                     | 0.62mW             | 0.6198mW                     |

Table 1 shows that the work from (J.-H. Kim et al. 2019) is viable of face detection and identity verification at 96,18 % in their tests. Moreover, their implementation only consumed 0,6198 mW@1 fps for 320 x 240 pixels, from which  $10.17 - 18.75 \mu$ W where due to the analog multiply accumulation unit. *The total analog part (imaging + convolution)* was 0,0588 mW, giving a FOM of **765,5 pJ/pix/frame**. This FOM was approximately one order of magnitude higher than the case of edge-detectors like (Young et al. 2019). Moreover, we observe, from Table 1, that the CNN implementation was not significantly better in power respect to a similar solution based on Haar-like features (for only the face-detection). In addition, their reported accuracy was slightly lower for the CNN. For those two

reasons, we do not observe a particular interest for going deeper into trainable kernels for low-level features extraction, which have to handle memory access and functions such as max-poling, activation and MAC with variable coefficients.

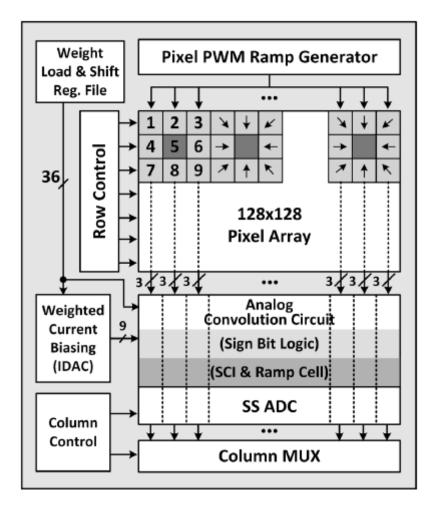

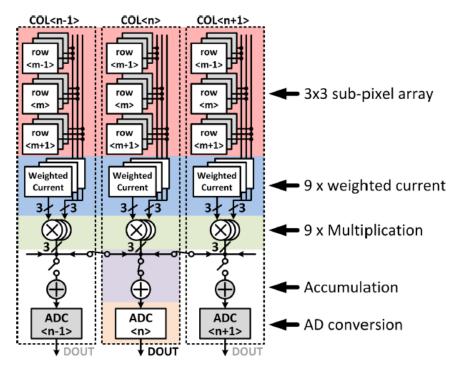

In addition to last example, (Hsu et al. 2021) implemented a PWM pixel array and an analog convolution unit allowing 3 x 3 MAC operations (for applying the first layer of a CNN, or other kernels such as the ones needed for edge extraction). The architecture allows programmability of the kernel coefficients encoded in 4-bit weights (including the sign bit). The overall architecture is shown in Figure 10.

Figure 10 : system overview of the PWM pixels-matrix and programmable pre-processing (Hsu et al. 2021)

The architecture from Figure 10 allowed reading, from the pixels-matrix, 9 neighboring pixels (with a PWM scheme). Then, those pixels could be multiplied by programmable-coefficients and accumulated on the fly in the analog domain. The processing steps applied by this architecture are in Figure 11.

Figure 11 : diagram of the implemented pre-processing for MAC after PWD read-out (Hsu et al. 2021)

Figure 11 shows the sequence of operations performed on the image to achieve a 3x3 programmable kernel convolution with the input image. This architecture achieved a FOM of 9.8 pJ/pix/frame for imaging, and 14.8 pJ/pix/frame for the convolution, giving a total FOM of 9.8 + 14.8 = 24.6 pJ/pix/frame. This implementation achieved a significantly better (~ 10x) FOM than the work of (J.-H. Kim et al. 2019). This might suggest that a PWM read-out plus analog-convolutions with current-integration logic is a good approach for low-power feature extractors. Nevertheless, we observe the fill factor was relatively low (36 %), which probably came from their more complex pixel. In contrast, (Young et al. 2019) reported a fill factor of 60.4 % after using a more simple pixel type. Moreover, also related with the last argument, the dynamic range was 52.3 dB, which was lower than the one reported by (Young et al. 2019): 59.3 dB. Another potential drawback of this implementation is that they did not take into account big changes in scene illumination and their impact in the reported accuracy, as done by (Omid-Zohoor et al. 2018). That could suggest that this kind of linear pre-processing along with an aggressive quantization could suffer from scenes that are not uniformly illuminated.

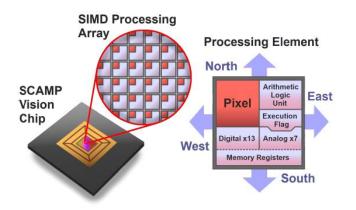

Another example of works for integrating CNNs is given by (Bose et al. 2019): they proposed an implementation of "Pixel processor arrays" (Bose et al. 2019) for computing ternary convolutions on the focal plane. Each pixel contained basic hardware, as illustrated by them in Figure 12, for computing addition, subtraction and bit-shifting. In their work, they explain how to represent ternary CNN convolutions with the limited hardware available.

Figure 12 : illustration of the in pixel-MAC architecture (Bose et al. 2019)

In last paragraphs we have cited different works that show interesting applications of integrated image pre-processing. One common trend is the increased circuit complexity, either at pixel level or at the periphery. In next section, we cite examples that use 3D-IC technologies for integrating relatively complicated and highly parallelized pre-processing algorithms.

In our work, we preferred to tackle hand-crafted near-matrix-of-pixels feature extractors before going into more complicated implementations without having clear if they are really justified.

#### 2.2.4. 3D-IC Smart Image Sensors

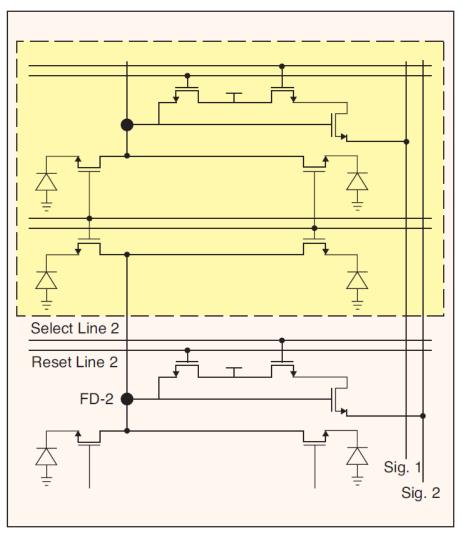

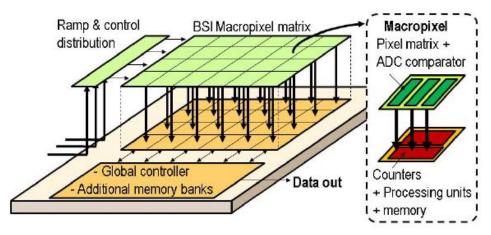

(Millet et al. 2018) implemented a 3D-IC smart-image-sensor chip with two tiers (layers). Their microfabrication technology allowed them to parallelize communications between the two layers, as shown in Figure 13.

Figure 13 : illustration of the 3D-IC smart-image sensor (Millet et al. 2018)

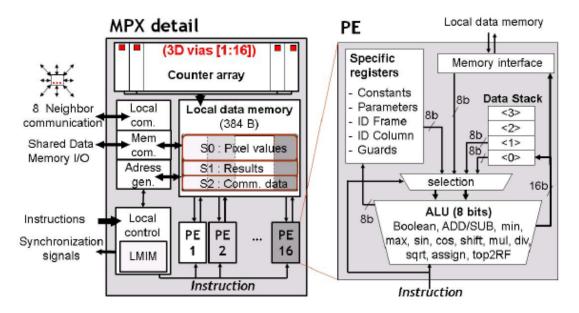

Figure 13 shows the system overview implemented by (Millet et al. 2018): the top layer (tier) included an array of what they called "macropixels", which include a 16 x 16 arrays of pixels, plus an

ADC. Each macropixel could communicate with a processing unit located right underneath, so local operations could be performed with improved latency and with a high degree of parallelization. Figure 14 shows each processing-unit-architecture. Indeed, this same Figure 14 indicates that one unit was dedicated for interfacing the pure computational unit (right) with the pixels on the top tier. Their processing unit (called "PE" for processing element), contained hardware capable of 8-bit computation of rather complicated functions (for near-sensor ICs) such as sinus, cosine and square root.

Figure 14 : diagram of the units implemented in the bottom layer (Millet et al. 2018)

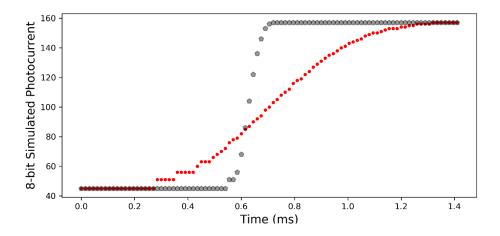

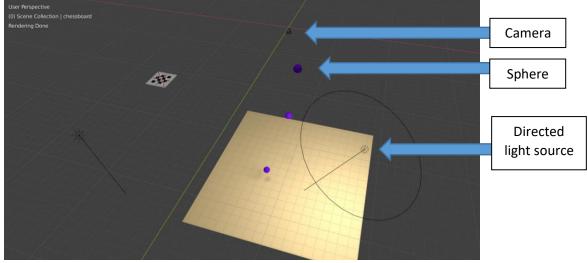

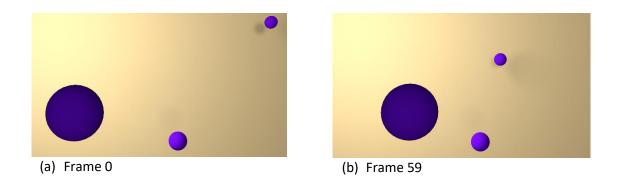

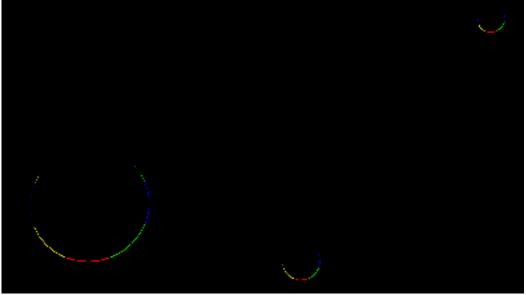

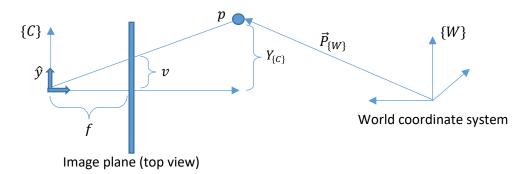

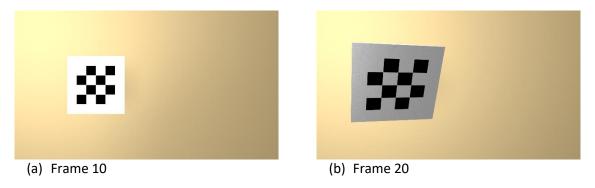

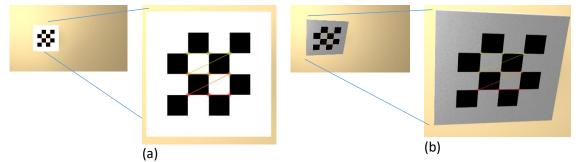

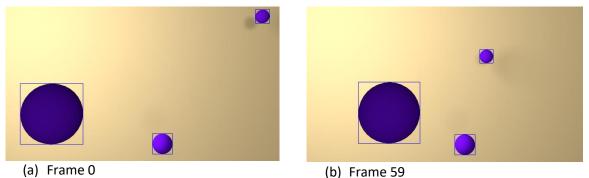

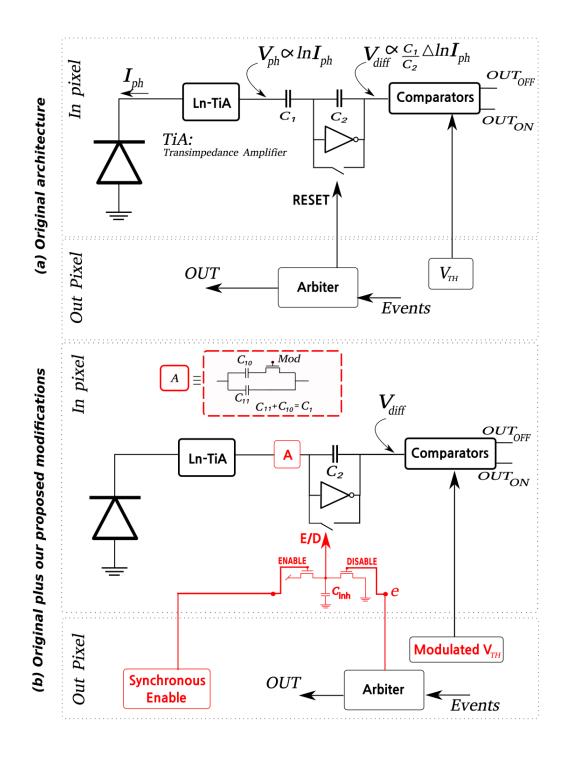

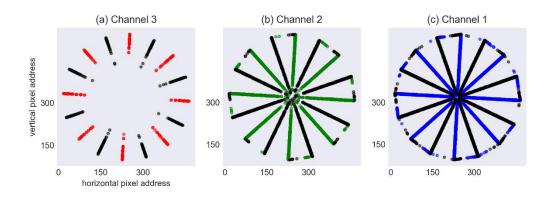

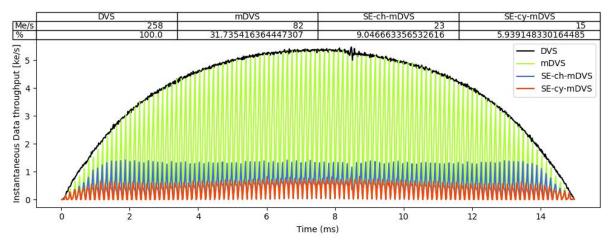

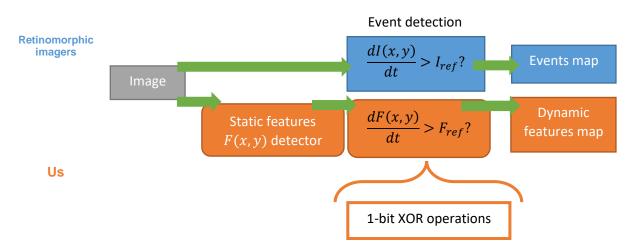

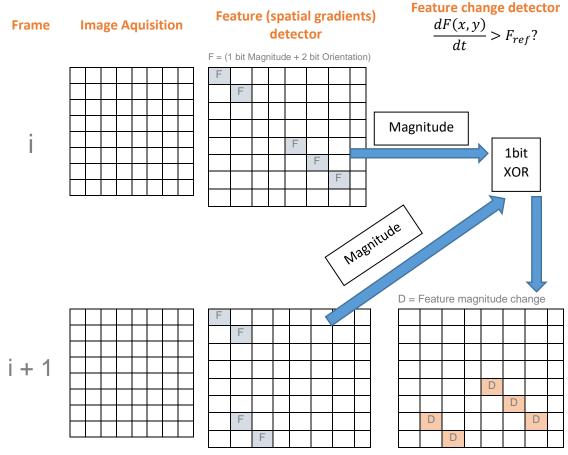

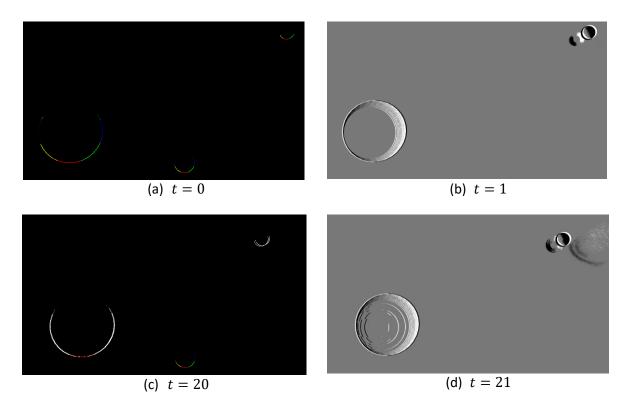

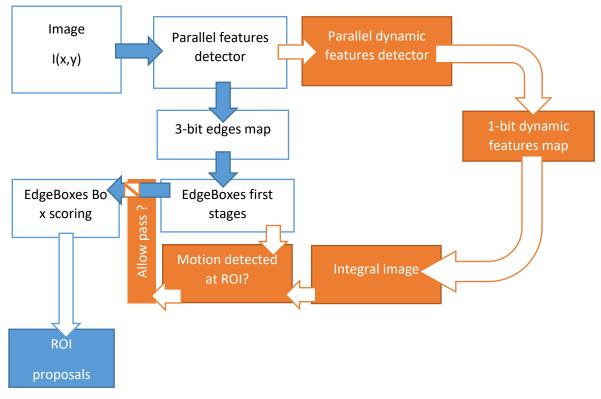

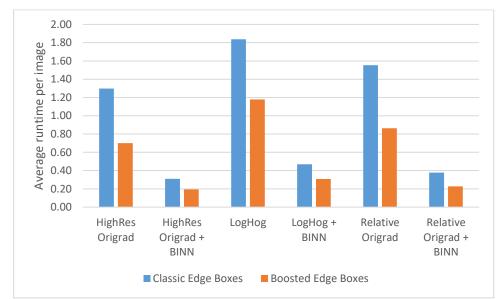

The implementation from (Millet et al. 2018) allowed interesting figures of merit, especially regarding latency : for an array resolution of 0.05 Mpixels with a 9 bit-depth encoding and a frame rate of 5500 fps. However, power-wise, the consumption for this arrangement was 720 mW, giving a FOM of ~**166.5 pJ/pix/frame**. This figure of merit is significantly less attractive than other works already cited before, also considering that it only takes into account image acquisition. Moreover, for low power applications, it is not clear for us how this system would benefit of such elevated frame rate without prohibitive power consumption from data I/O.