# Theoretical and experimental evaluation of the Integrated gate-commutated thyristor (IGCT) as a switch for Modular Multi Level Converters (MMC)

Arthur Boutry

#### ▶ To cite this version:

Arthur Boutry. Theoretical and experimental evaluation of the Integrated gate-commutated thyristor (IGCT) as a switch for Modular Multi Level Converters (MMC). Electronics. Université de Lyon, 2021. English. NNT: 2021LYSEI095 . tel-03613187v2

## HAL Id: tel-03613187 https://theses.hal.science/tel-03613187v2

Submitted on 18 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre NNT: 2021LYSEI095

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de INSA de Lyon

Ecole Doctorale N°160 Électronique, Électrotechnique, Automatique de Lyon

Spécialité/discipline de doctorat : Génie Électrique

Soutenue publiquement le 16/12/2021, par : Arthur BOUTRY

Theoretical and experimental evaluation of the Integrated gate-commutated thyristor (IGCT) as a switch for Modular Multi Level Converters (MMC)

#### Devant le jury composé de :

| Ladoux, Philippe     | Professeur des Universités | Univ. Toulouse      | Examinateur,       |

|----------------------|----------------------------|---------------------|--------------------|

|                      |                            |                     | Président          |

| Dieckerhoff, Sibylle | Professor                  | TU Berlin           | Rapporteure        |

| Dujic, Drazen        | Associate Professor EPFL   |                     | Rapporteur         |

| Batut, Nathalie      | Maitre de conférences, HDF | RUniv. Tours        | Examinatrice       |

| Buttay, Cyril        | Directeur de recherches    | INSA de Lyon        | Directeur de thèse |

| Vagnon, Eric         | Maitre de conférences      | Centrale Lyon       | Co-directeur       |

| Lefebvre, Bruno      | Docteur                    | SuperGrid Institute | Invité             |

| Dong, Dong           | Assistant Professor        | CPES, Virginia Tech | Invité             |

| Vemulapati,          | Docteur                    | Hitachi             | Invité             |

| Umamaheswara         |                            |                     |                    |

## Département FEDORA – INSA Lyon - Ecoles Doctorales

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                      | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                                                                                                         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON  https://www.edchimie-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage secretariat@edchimie-lyon.fr                                                         | M. Stéphane DANIELE C2P2-CPE LYON-UMR 5265 Bâtiment F308, BP 2077 43 Boulevard du 11 novembre 1918 69616 Villeurbanne directeur@edchimie-lyon.fr                                                                                                                                          |

| E.E.A.    | ÉLECTRONIQUE, ÉLECTROTECHNIQUE, AUTOMATIQUE  https://edeea.universite-lyon.fr Sec.: Stéphanie CAUVIN Bâtiment Direction INSA Lyon Tél: 04.72.43.71.70 secretariat.edeea@insa-lyon.fr | M. Philippe DELACHARTRE INSA LYON Laboratoire CREATIS Bâtiment Blaise Pascal, 7 avenue Jean Capelle 69621 Villeurbanne CEDEX Tél: 04.72.43.88.63 philippe.delachartre@insa-lyon.fr                                                                                                        |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME, MICROBIOLOGIE, MODÉLISATION  http://e2m2.universite-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 secretariat.e2m2@univ-lyon1.fr  | M. Philippe NORMAND Université Claude Bernard Lyon 1 UMR 5557 Lab. d'Ecologie Microbienne Bâtiment Mendel 43, boulevard du 11 Novembre 1918 69 622 Villeurbanne CEDEX philippe.normand@univ-lyon1.fr                                                                                      |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTÉ  http://ediss.universite-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 secretariat.ediss@univ-lyon1.fr                 | Mme Sylvie RICARD-BLUM Institut de Chimie et Biochimie Moléculaires et Supramoléculaire (ICBMS) - UMR 5246 CNRS - Université Lyon 1 Bâtiment Raulin - 2ème étage Nord 43 Boulevard du 11 novembre 1918 69622 Villeurbanne Cedex Tél: +33(0)4 72 44 82 32 sylvie.ricard-blum@univ-lyon1.fr |

| INFOMATHS | INFORMATIQUE ET MATHÉMATIQUES  http://edinfomaths.universite-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage Tél: 04.72.43.80.46 infomaths@univ-lyon1.fr                  | M. Hamamache KHEDDOUCI Université Claude Bernard Lyon 1 Bât. Nautibus 43, Boulevard du 11 novembre 1918 69 622 Villeurbanne Cedex France Tél: 04.72.44.83.69 hamamache.kheddouci@univ-lyon1.fr                                                                                            |

| Matériaux | MATÉRIAUX DE LYON  http://ed34.universite-lyon.fr Sec.: Yann DE ORDENANA Tél: 04.72.18.62.44 yann.de-ordenana@ec-lyon.fr                                                             | M. Stéphane BENAYOUN Ecole Centrale de Lyon Laboratoire LTDS 36 avenue Guy de Collongue 69134 Ecully CEDEX Tél: 04.72.18.64.37 stephane.benayoun@ec-lyon.fr                                                                                                                               |

| MEGA      | MÉCANIQUE, ÉNERGÉTIQUE, GÉNIE CIVIL, ACOUSTIQUE  http://edmega.universite-lyon.fr Sec.: Stéphanie CAUVIN Tél: 04.72.43.71.70 Bâtiment Direction INSA Lyon mega@insa-lyon.fr          | M. Jocelyn BONJOUR INSA Lyon Laboratoire CETHIL Bâtiment Sadi-Carnot 9, rue de la Physique 69621 Villeurbanne CEDEX jocelyn.bonjour@insa-lyon.fr                                                                                                                                          |

| ScSo      | https://edsciencessociales.universite-lyon.fr<br>Sec.: Mélina FAVETON<br>INSA: J.Y. TOUSSAINT<br>Tél: 04.78.69.77.79<br>melina.faveton@univ-lyon2.fr                                 | M. Christian MONTES Université Lumière Lyon 2 86 Rue Pasteur 69365 Lyon CEDEX 07 christian.montes@univ-lyon2.fr                                                                                                                                                                           |

melina.faveton@univ-lyon2.fr

\*ScSo: Histoire, Géographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

# Abstract

This manuscript investigates the potential of Integrated Gate-Commutated Thyristors (IGCT) for Modular Multi-Level Converters (MMC). After a theoretical analysis of the advantages of IGCTs regarding losses, we investigate their switching operation experimentally. In particular, we focus on di/dt limiting inductance and RCD-clamp reduction/suppression using plastic module silicon (Si) fast recovery diodes and silicon carbide (SiC) diodes in an MMC submodule. This study aims to explore improvements for the MMC, focusing on using different semiconductors in the MMC submodule.

#### This Ph.D. manuscript contains:

- An analysis of existing HVDC MMC Submodules and their technologies.

- A review on the IGCT: semiconductor structure, types and features.

- An assessment of the interest of the IGCT in HVDC MMC Submodules and losses comparison with IGBTs, using MMC-specific figures-of-merit created in this thesis.

- An assessment of the works on limiting di/dt inductor size reduction.

- A double pulse test design with specific structure imitating an MMC submodule.

- A review and an analysis of the PiN diode failure modes.

- Double pulse tests with fast recovery diode in plastic module with successful attempts to reduce and suppress the limiting di/dt inductor (up to 2400V/1800A and 2000V/2400A).

- The packaging of High-Voltage (10kV) High-Current (50A) SiC PiN diode dies (1cm<sup>2</sup>), test with IGCT in the same setup, with successful attempts to reduce and suppress the limiting di/dt inductor (up to 2400V/100A and 2000V/150A), and analysis of the specificities of the SiC diode in that setup.

# Résumé

Ce manuscrit étudie le potentiel des thyristors de type IGCT pour les convertisseurs multiniveaux modulaires (MMC). Après une analyse théorique des avantages des IGCTs au regard de leurs niveaux de pertes, nous étudions leur fonctionnement en commutation de manière expérimentale. En particulier, nous nous concentrons sur la réduction/suppression de l'inductance de limitation di/dt pour IGCTs et du clamp RCD en utilisant des diodes rapides en silicium (Si) et des diodes en carbure de silicium (SiC) dans les sous-modules MMC. Cette étude vise à explorer les pistes d'amélioration pour le MMC, en se concentrant sur l'utilisation de différents semi-conducteurs dans le sous-module MMC.

Ce manuscrit de thèse de doctorat contient :

- Une analyse des sous-modules de MMC HVDC existants.

- Une revue de l'IGCT : structure du semi-conducteur, types et caractéristiques.

- Une évaluation de l'intérêt des IGCTs dans les sous-modules MMC HVDC et comparaison des pertes avec les IGBT, en utilisant des facteurs de mérite spécifiques aux MMC créés dans cette thèse.

- Une évaluation des travaux sur la réduction de la taille des inductances limitant le di/dt.

- Un design de banc d'essais test à double pulse avec une structure spécifique imitant un sous-module MMC.

- Une revue et une analyse des modes de défaillance des diodes PiN.

- Des tests en double pulse avec diode à récupération rapide dans un module plastique pour tenter de réduire et supprimer l'inductance limitant le di/dt.

- Packaging de puces de diodes SiC PiN à haute tension et courant élevé, test avec IGCT dans le même montage, pour tenter de réduire et supprimer l'inductance limite di/dt, et analyser les spécificités de la diode SiC dans ce montage.

# Remerciements / Acknowledgements

Ces remerciements seront en Français et en Anglais, la langue utilisée correspond à celle des personnes remerciées/These acknowledgements will be in French and English, the language used corresponds to the one of the thanked persons.

Je veux tout d'abord remercier Cyril Buttay, mon directeur de thèse. J'ai énormément appris auprès de lui, techniquement bien sûr, méthodologiquement assurément, mais humainenement aussi. C'est dans ses valises que j'ai atteri à Blacksburg en Virginie, et cette expérience a été très importante pour moi. Il m'a toujours soutenu, du début de la thèse où le démarrage a été difficile, à la fin où le rush d'expériences, d'écriture/correction a été intense, en passant par le milieu où le covid, les douanes et les explosions de diodes se sont mélées au reste. Au delà de l'aspect scientifique, j'ai appris avec lui la plomberie en connectant mon banc de test, l'application de mastic en appliquant la pâte d'argent, la découpe, le perçage... Comme quoi ma thèse sera utile pour les travaux domestiques, merci encore Cyril.

Je veux ensuite remercier Bruno Lefebvre. Bruno a toujours été un support important dans cette thèse : il a toujours suivi et supporté les travaux de la thèse avec entousiasme mais aussi gentillesse. Sa confiance durant la thèse m'a permis d'avancer le plus sereinement possible. Je veux aussi remercier Eric Vagnon, même si j'aurais aimé travailler plus étroitement avec lui, le sujet de la thèse ayant divergé de sa spécialité, son ouverture et sa bonne humeur ont aidé en particulier à la fin de la thèse avec les répétitions de soutenance.

I want to thank all the people in CPES for their warm welcome and their help through this year I spent as a visiting scholar. In particular I want to thank Dushan Boroyevich, Dong Dong, Rolando Burgos for allowing me to be part of this lab and start my experimental work there. Despite that thyristors were not part of their research fields, they have always been curious, shown interest and have been good advisors during my time in Virginia Tech. I want to thank in particular Jian and Lakshmi that helped me set up my experience. There is also Slavko, Joseph, Vladimir, John, Gibong that I want to thank for all the good interactions we had over this year, you are awesome guys.

I would like to thank the Fulbright Program (and in particular the French Fulbright Commission) and their staff that made the year in Virginia Tech possible and easy. Your dedication and niceness were incredible.

J'aimerais remercier tous mes collègues de SuperGrid Institute et du laboratoire Ampère pour leur aide et leur camaraderie. Merci Diego, Rayane, Alexandre, Alexis, Somya, Cédric, Luong-Viêt, Dominique, Pascal, Hervé, Joël, Hugo, Besar, Joseph, Hadiseh, Quentin, Arnaud, Christophe, Juan, Piotr, Daniel, Joan, Martin, Jilani, Loïc, Caroline, Pierre-Baptiste, Florent

et tous les autres pour tous votre aide et ces bons moments.

I want to thank Doug, also known as William Douglas Hartley II, for being the roommate that I never thought I could meet on Craigslist. I do not regret sending \$ 500 overseas to an unknown man on Craigslist, this was the best stupid idea I had during 3 years. I hope Remi replaced my goofiness at your home and I am looking forward to spend some time with you again my friend. Your family was incredibly nice to me, and I consider you folks like my American family, with who I spend my first Thanksgiving.

I would like to thank the VT rugby team for this incredible adventure with you guys. On top of winning the conference and going to the national play offs, being part of this team was awesome. I hope I was your little french lucky charm during this season and the seasons to come. Without you guys, my year would have been way less crazy. And as you love to say, burn your boats.

J'aimerais remercier ma famille, qui m'a soutenu dans tous mes projets avec amour et bienveillance, même s'ils ne comprenaient pas toujours mes travaux ou pas toujours pourquoi j'allais au fin fond de la Virginie. Je voulais aussi remercier tous mes amis, tous mes camarades, qui me suivent et me supportent (dans tous les sens du terme) depuis si longtemps, avec qui j'ai parcouru beaucoup de chemin. Ceux de Carquefou, ceux de Nantes, ceux de Lyon, ceux de Nouvelle-Zélande et ceux d'ailleurs.

Lastly but most importantly, I want to thank Lauren. Your love and your support every single day made me a better man through these tough years, whether it was pandemic time, moving back to France, the customs losing my PhD experiment, the manuscript redaction... I could go on and make a huge list out of all the moments you have helped me and also all the good times I have spent with you all around America, Europe and France. I am happy to say that I can finally spend time with you, without having to finish a PhD, and I am looking forward to all the new adventures ahead of us. If I was able to pull off this 200 pages thesis manuscript, it is mainly thanks to you. The patience that you have shown was a gift. For this and all the rest, thank you my love.

# Contents

| A            | bstra | act     |                                                                          | 5  |

|--------------|-------|---------|--------------------------------------------------------------------------|----|

| $\mathbf{R}$ | ésum  | ıé      |                                                                          | 7  |

| $\mathbf{R}$ | emer  | cieme   | ${ m nts} \; / \; { m Acknowledgements}$                                 | 10 |

| 1            | Rev   | view of | f MMC-submodule technology                                               | 15 |

|              | 1.1   | Introd  | luction to the Modular Multilevel Converter Topology and its Submodule . | 15 |

|              |       | 1.1.1   | Voltage Source Converters                                                | 15 |

|              |       | 1.1.2   | The MMC Submodule                                                        | 18 |

|              |       | 1.1.3   | MMC Definitions, Design, and existing MMCs                               | 24 |

|              |       | 1.1.4   | Overstress and Dimensioning Situations                                   | 27 |

|              |       | 1.1.5   | Insulation Co-ordination                                                 | 30 |

|              | 1.2   | Comp    | onents of a Submodule                                                    | 35 |

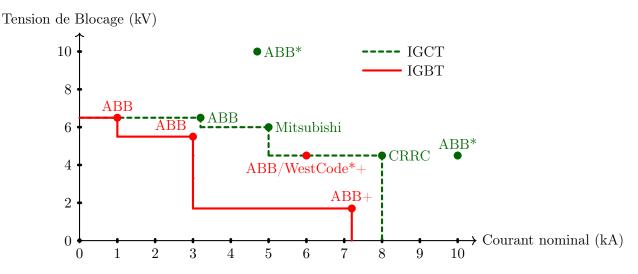

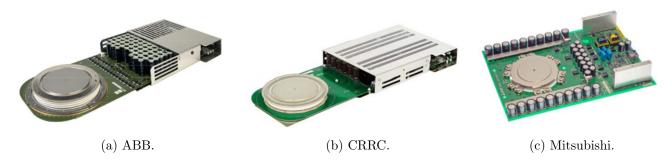

|              |       | 1.2.1   | Power Switches and Diodes                                                | 36 |

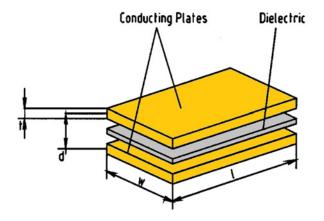

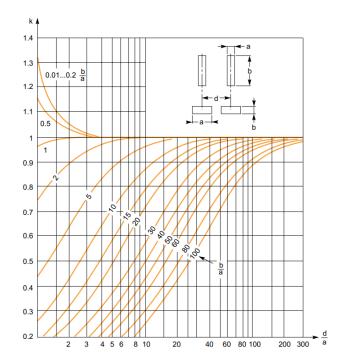

|              |       | 1.2.2   | Capacitors                                                               | 40 |

|              |       | 1.2.3   | Interconnections                                                         | 47 |

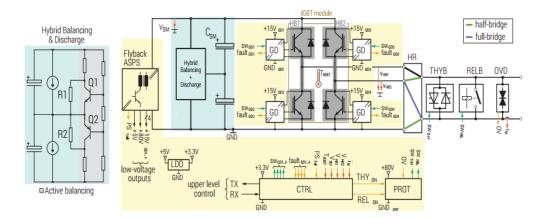

|              |       | 1.2.4   | Auxiliary Circuits                                                       | 50 |

|              |       | 1.2.5   | Protections Systems                                                      | 53 |

|              |       | 1.2.6   | Cooling                                                                  | 56 |

|              | 1.3   | Revie   | w of Existing Submodules                                                 | 57 |

|              |       | 1.3.1   | Alstom Grid / GE Grid                                                    | 57 |

|              |       | 1.3.2   | Fraunhofer Institute IISB                                                | 57 |

|              |       | 1.3.3   | Siemens                                                                  | 58 |

|              |       | 1.3.4   | ABB                                                                      | 59 |

|   |     | 1.3.5              | Submodule designs from scientific literature                                                       | 60 |

|---|-----|--------------------|----------------------------------------------------------------------------------------------------|----|

|   | 1.4 | Conclu             | asion of this review and research axes                                                             | 65 |

| 2 |     | CT in I<br>es stud | MMC Submodule – State of the Art, comparison with IGBTs and ly                                     | 67 |

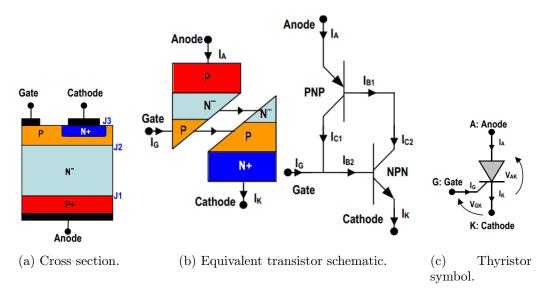

|   | 2.1 | Thyris             | stors semiconductor structures – evolution from SCR to GCT                                         | 67 |

|   |     | 2.1.1              | Thyristor (SCR)                                                                                    | 68 |

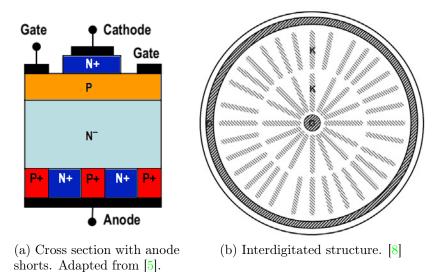

|   |     | 2.1.2              | GTO                                                                                                | 68 |

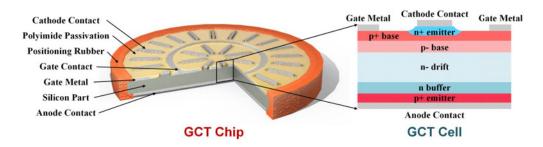

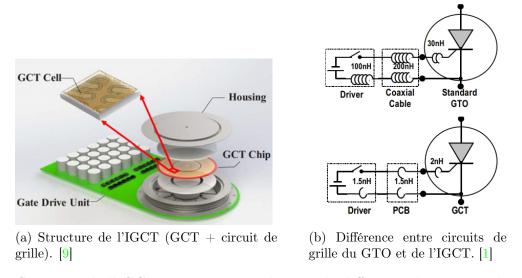

|   |     | 2.1.3              | GCT                                                                                                | 69 |

|   | 2.2 | The I              | GCT – types and functioning                                                                        | 72 |

|   |     | 2.2.1              | GCTs Types                                                                                         | 72 |

|   |     | 2.2.2              | Gate Drive Circuit functions and parts                                                             | 76 |

|   | 2.3 | Comp               | arison of IGCTs and IGBTs in MMCs – a literature review                                            | 77 |

|   |     | 2.3.1              | General considerations and features to compare                                                     | 77 |

|   |     | 2.3.2              | Losses studies in literature                                                                       | 79 |

|   |     | 2.3.3              | A focus on the turn-on snubber and the associated literature                                       | 80 |

|   |     | 2.3.4              | Conclusions and limits on this literature review                                                   | 85 |

|   | 2.4 | Develo<br>Figure   | oping a comparison between IGCTs and IGBTs through the creation of s-of-Merit and a current metric | 87 |

|   |     | 2.4.1              | Current Metric for comparison of current ratings                                                   | 87 |

|   |     | 2.4.2              | Figures-of-merit to compare losses                                                                 | 91 |

|   | 2.5 | Losses             | simulation to validate the Figures-of-Merit                                                        | 92 |

|   |     | 2.5.1              | Model                                                                                              | 92 |

|   |     | 2.5.2              | Results                                                                                            | 95 |

|   |     | 2.5.3              | Conclusion on the Figures-of-Merit                                                                 | 96 |

|   | 2.6 | Possib             | le investigations on the IGCT for MMC applications                                                 | 97 |

|   |     | 2.6.1              | Snubberless IGCTs                                                                                  | 97 |

|   |     | 2.6.2              | Improving the gate driver                                                                          | 98 |

|   |     | 2.6.3              | Other research topics                                                                              | 99 |

|   | 2.7 | Conclu             | usion on the use of IGCT in MMC submodules and perspectives                                        | 99 |

| 3 | Dou | ıble Pı            | ılse Test of IGCT with fast recovery diodes – a test bench Design1                                 | 01 |

|   | 3.1 | Exper              | iment objective, functioning of the double pulse test setup                                        | 01 |

|   |                | 3.1.1                                                                           | Experiment objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | UΙ                                                                   |

|---|----------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

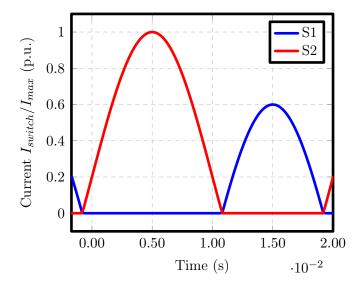

|   |                | 3.1.2                                                                           | Double pulse test setup description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 01                                                                   |

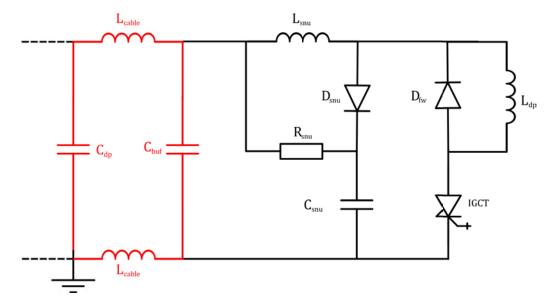

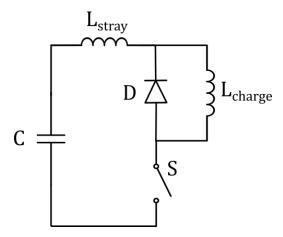

|   |                | 3.1.3                                                                           | Presentation of the circuit of the test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 02                                                                   |

|   | 3.2            | Designand co                                                                    | n of the test circuit part imitating the structure of an MMC submodule emponent selection                                                                                                                                                                                                                                                                                                                                                                                                                                 | 04                                                                   |

|   |                | 3.2.1                                                                           | Choice of semiconductors – IGCT, freewheeling and snubber diode 10                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 05                                                                   |

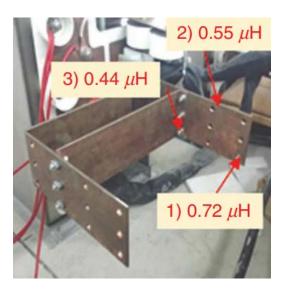

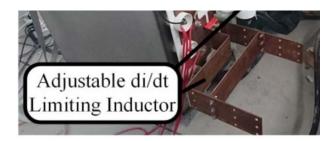

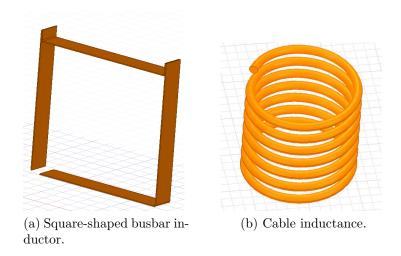

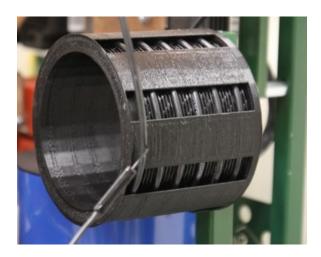

|   |                | 3.2.2                                                                           | Snubber inductor design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80                                                                   |

|   |                | 3.2.3                                                                           | Snubber capacitor and resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12                                                                   |

|   |                | 3.2.4                                                                           | Analysis of the snubber volume                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                   |

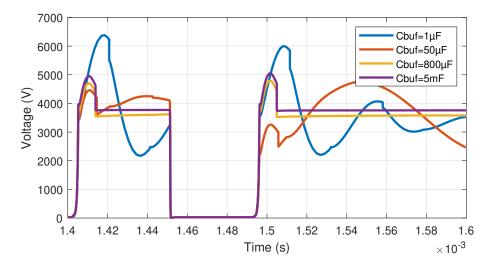

|   |                | 3.2.5                                                                           | Buffer capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                                   |

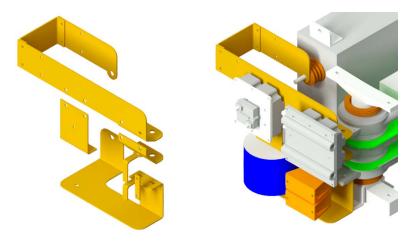

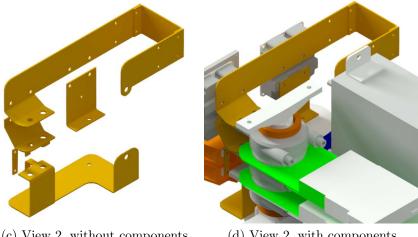

|   |                | 3.2.6                                                                           | Busbar design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                   |

|   | 3.3            | Imple                                                                           | mentation of the rest of the test circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19                                                                   |

|   |                | 3.3.1                                                                           | Capacitor bank and Charge Inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19                                                                   |

|   |                | 3.3.2                                                                           | Temperature control System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21                                                                   |

|   |                | 3.3.3                                                                           | Protection elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                                   |

|   | 3.4            | Finalis                                                                         | sed setup and conclusion on the test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                                                                   |

|   |                |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 4 | Con            | nmuta                                                                           | tion of an IGCT with fast Silicon diodes 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                                   |

| 4 | <b>Con</b> 4.1 |                                                                                 | tion of an IGCT with fast Silicon diodes  ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| 4 |                |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                                   |

| 4 |                | Litera                                                                          | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26                                                             |

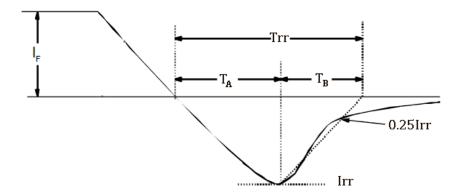

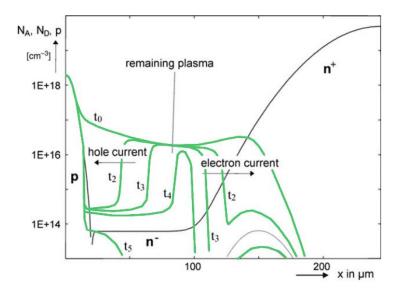

| 4 |                | Litera 4.1.1                                                                    | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27                                                       |

| 4 |                | Litera 4.1.1 4.1.2                                                              | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28                                                 |

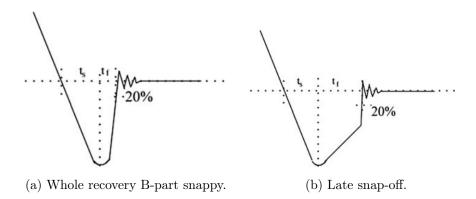

| 4 |                | Litera 4.1.1 4.1.2 4.1.3                                                        | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28<br>32                                           |

| 4 |                | Litera<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                      | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28<br>32<br>35                                     |

| 4 |                | Literal<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                            | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28<br>32<br>35<br>38                               |

| 4 |                | Literal<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7          | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28<br>32<br>35<br>38<br>39                         |

| 4 | 4.1            | Literal<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7          | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28<br>32<br>35<br>38<br>39                         |

| 4 | 4.1            | Literal<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>Exper | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28<br>32<br>35<br>38<br>39<br>40                   |

| 4 | 4.1            | Literal 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 Exper 4.2.1                   | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28<br>32<br>35<br>38<br>39<br>40<br>41             |

| 4 | 4.1            | Literal 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 Exper 4.2.1 4.2.2             | ture review on reverse recovery and its destructive modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>26<br>27<br>28<br>32<br>35<br>38<br>39<br>40<br>41<br>46       |

| 4 | 4.1            | Literal 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 Exper 4.2.1 4.2.2 4.2.3       | ture review on reverse recovery and its destructive modes 12  Useful definitions 12  Types of diodes in Power Electronics 12  Reverse Recovery 12  A focus on snappy recovery 13  Dynamic avalanche 13  Conclusion on destructive modes during reverse recovery 13  Design trade-offs on PiN Silicon Diodes 13  iment on IGCT and quick Silicon diode commutation at high di/dt 13  Summary of the experimental plan 14  Overview of typical waveforms 14  Operational parameters influence on the snap-off phenomenon 14 | 25<br>26<br>27<br>28<br>32<br>35<br>38<br>39<br>40<br>41<br>46<br>51 |

|    |       | 4.2.6  | Operation without RCD clamp                                                | . 155 |

|----|-------|--------|----------------------------------------------------------------------------|-------|

|    |       | 4.2.7  | Snubber reduction impact on losses                                         | . 157 |

|    |       | 4.2.8  | Conclusion on the experiment with fast silicon diodes                      | . 157 |

| 5  | IGO   | CT Sw  | itching with SiC PiN diodes at high $\mathrm{di}/\mathrm{dt}$              | 165   |

|    | 5.1   | SiC P  | iN diodes                                                                  | . 165 |

|    |       | 5.1.1  | Difference with Silicon PiN diodes                                         | . 165 |

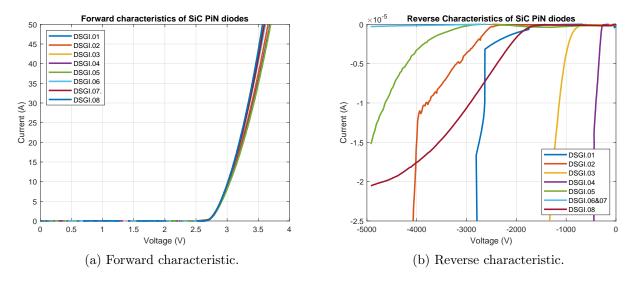

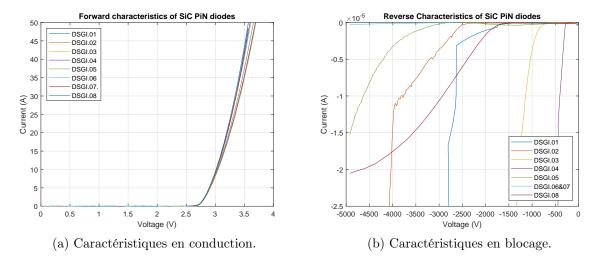

|    |       | 5.1.2  | Description of the SiC diode dies                                          | . 166 |

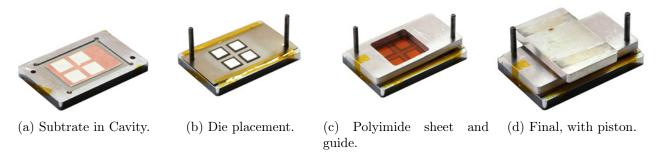

|    | 5.2   | Packa  | ging of the SiC dies                                                       | . 168 |

|    |       | 5.2.1  | Constraints to be considered                                               | . 168 |

|    |       | 5.2.2  | Package design                                                             | . 170 |

|    |       | 5.2.3  | Packaging process                                                          | . 175 |

|    |       | 5.2.4  | Characterisation of the obtained diodes sub-packages                       | . 179 |

|    |       | 5.2.5  | Conclusion on the packaging of the SiC diodes                              | . 180 |

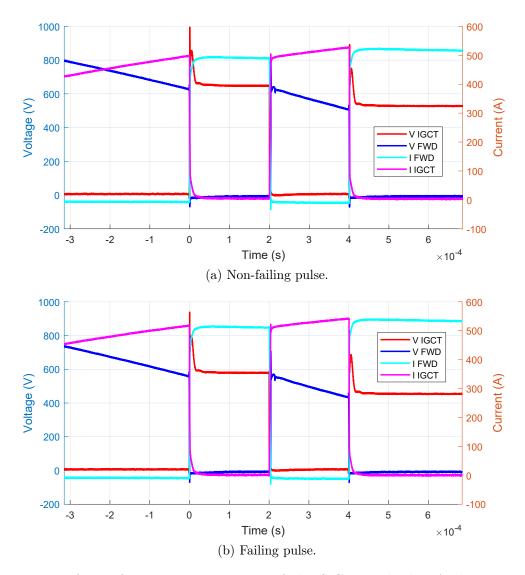

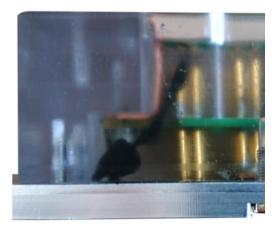

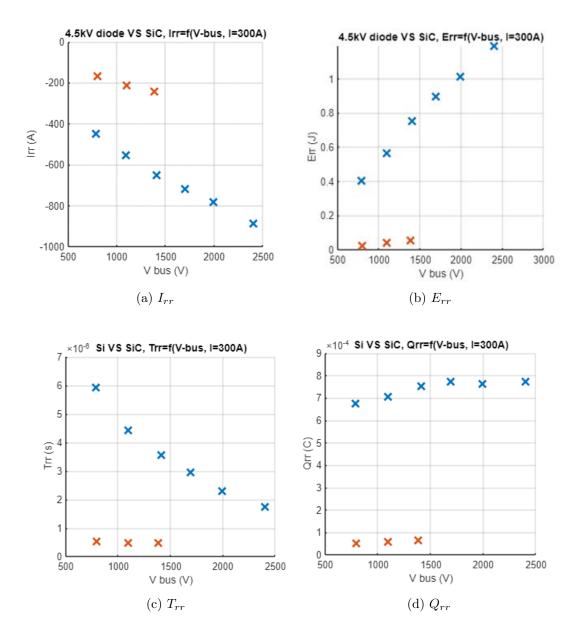

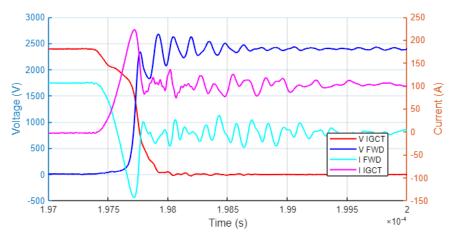

|    | 5.3   | Doubl  | e pulse with IGCT                                                          | . 180 |

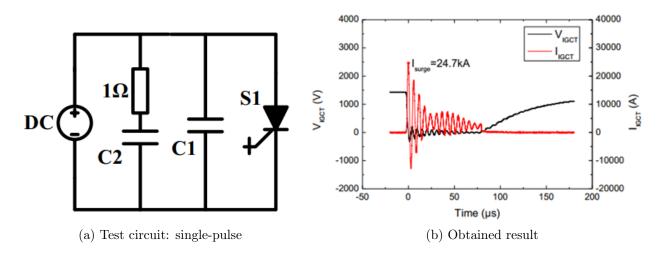

|    |       | 5.3.1  | Current surge test                                                         | . 180 |

|    |       | 5.3.2  | Double pulses with snubber                                                 | . 183 |

|    |       | 5.3.3  | Without snubber and RCD clamp                                              | . 194 |

|    | 5.4   | Concl  | usion on the packaging and the use of HV SiC diodes with IGCTs $ .  .  . $ | . 197 |

| G  | enera | al Con | clusion                                                                    | 199   |

| Ré | ésum  | ié com | plet français                                                              | 220   |

# Chapter 1

# Review of MMC-submodule technology

In this chapter, the MMC submodule technology will be assessed. In a first section, the MMC and its design will be presented before going into the details of the submodules themselves (components and design rules) in a second section, and concluding with a review of the existing submodule realisations (industrial and litterature submodules) in a third section.

The goal of this chapter is to expose the submodule design rules and their typical features and values.

# 1.1 Introduction to the Modular Multilevel Converter Topology and its Submodule

## 1.1.1 Voltage Source Converters

The Modular Multilevel Converter (MMC) is a Voltage Source Converter (VSC) developed and used for Medium or High Voltage Direct Current (MVDC or HVDC) applications. This is a reversible, AC/DC Converter. A simple type of VSC is the two-level converter and its understanding helps to identify the advantages of the Modular Multilevel Converter.

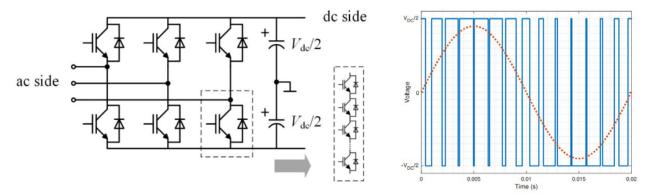

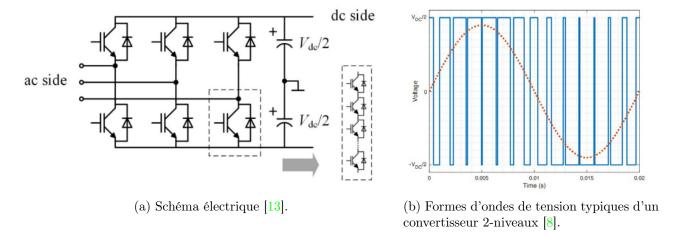

#### 1.1.1.1 The two-level converter

The two-level converter is presented in fig. 1.1a, and the corresponding waveforms on the AC side are given in fig. 1.1b. Because only 2 levels of voltage can be applied on each terminal of the AC side, the AC/DC conversion relies on high-frequency switching, with for example the Pulse Width Modulation method – using a sinusoidal reference signal, and the filtering of high-frequencies. This strategy has its main drawbacks: high switching frequency implies large switching losses, and requires filtering to remove the high frequency harmonics. Because the power semiconductor devices have a limited voltage ratings – up to 10kV, it is necessary to connect many of them in series (as illustrated in figure 1.1a) to sustain the MVDC or HVDC

(a) Circuit Diagram [105], each arm is composed of series-connected(b) Typical voltage waveform of a 2-level switches.

Figure 1.1: Circuit diagram and typical voltage waveform of a 2-level converter.

DC voltage – from tens of kVs to hundreds of kV. Such connection is complex to ensure balanced voltage distribution as well as simultaneous switching of all the semiconductor components.

#### 1.1.1.2 The Modular Multilevel Converter

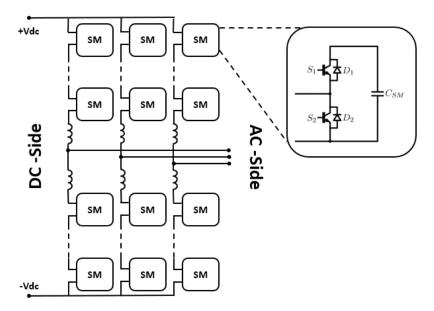

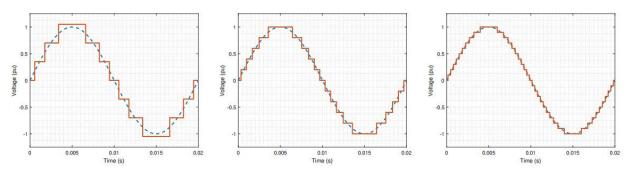

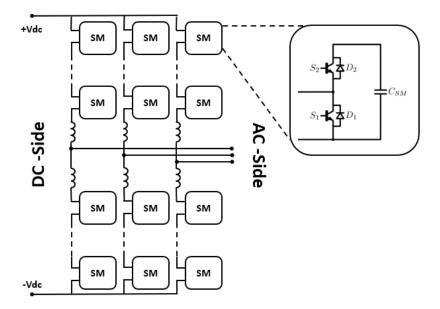

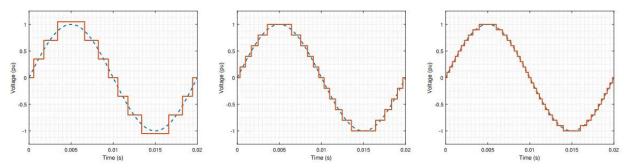

The Modular Multilevel Converter (fig. 1.2a) is based on submodules, its elementary unit. Formed by power semiconductors (switches and diodes) and a capacitor, a submodule can be seen as a small voltage source, that can be inserted or not (depending on the switching sequence and the current sign along the submodules). This structure permits to function as a rectifier or an inverter. The number of submodules can be high – up to hundreds, allowing a good sinusoidal waveform to be generated (see figure 1.2b), even without filtering. The quality of the signal is measured with the total harmonic distortion (THD). The MMC topology is also easily scalable: for a given submodule, different MMCs can be built (a 100 kV MMC and a 400 kV MMC can be built with the same submodule). The way the converter works, the switching frequency of each individual submodule is lower than the one for a two-level converter, and so switching losses are lower as well. The switching frequency of a submodule is generally between 100Hz and 300Hz. It has also a good failure management, a larger number of submodules than the minimum number needed is used inside an MMC to have redundancy in the converter. When a submodule fails, it is bypassed and this permits the converter to continue working.

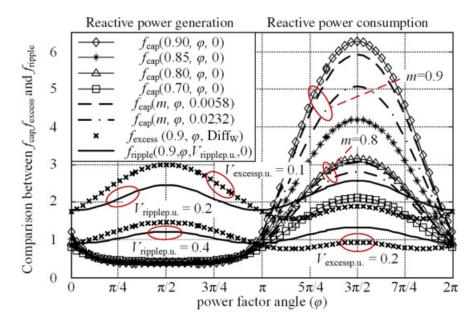

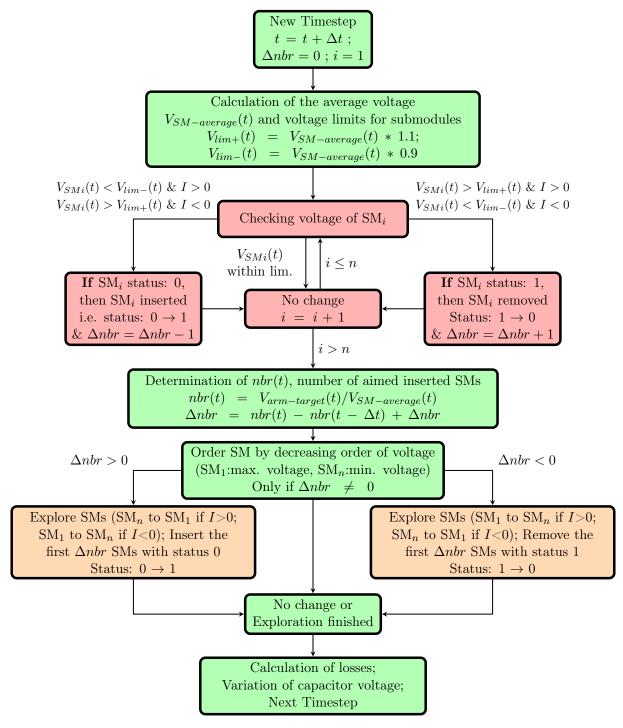

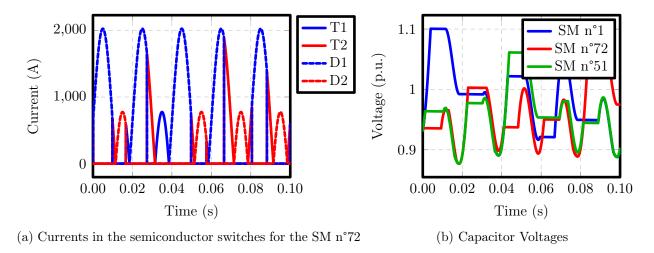

Operation and main parameters Submodules are inserted or removed from the circuit to obtain the desired voltage waveform, the capacitor acting like a voltage source. While inserted, capacitors either charge or discharge, depending on the sign of the current. The control of the MMC is aiming to generate the desired voltage waveform but is also aiming to control the state of charge of the capacitors. The typical submodule selection process is divided into two parts: first the number of submodules that have to be inserted to generate the voltage is calculated, and then a balancing control algorithm (BCA) selects which submodule will be inserted or removed – depending on the capacitor voltage level and the voltage limits that are set. This algorithm is very important because it influences the losses of the whole converter, the voltage ripple of the capacitors, the quality of the signal... Typically, this kind of algorithm ranks the

(a) Circuit Diagram of the modular multilevel converter and if one of its submodules (SM)

(b) Typical voltage waveform of an MMC with different number of submodule per arm [50], from the left to the right, larger number of submodules.

Figure 1.2: Circuit Diagram and typical voltage waveform of an MMC

submodules according to the voltage levels of their capacitor, and depending on the voltage level and the current direction, it chooses which capacitor has to be inserted or removed. Allowing a large voltage swing in the capacitors lowers the losses in the submodule (because the switching is less frequent). But for the same capacitor, a higher voltage ripple will accelerate its ageing. This would force the submodule manufacturer to oversize the capacitor, leading to extra cost and extra volume.

The MMC is converting power from DC to AC (or the opposite). Its operation depends on the voltages on the AC and DC sides, and the transmitted powers. It must also create or absorb reactive power. The operation point can be defined as a combination of the modulation factor (see equation (1.2)) – the ratio between AC and DC-voltage, the power factor on the AC-side, and the transmitted active power.

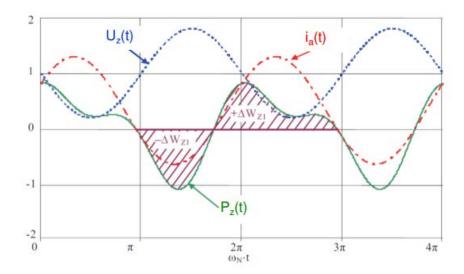

In the hypotheses of a sinusoidal signal, the voltage across an arm is:

$$V_{arm}(t) = \frac{V_{dc}}{2} - V_{ac}.cos(\omega t + \phi)$$

(1.1)

$$= \frac{V_{dc}}{2} - \frac{V_{dc}}{2}.m.cos(\omega t + \phi)$$

(1.2)

With m, the modulation factor defined as  $\frac{2V_{ac}}{V_{dc}}$ , with  $V_{ac}$  the amplitude of the AC-voltage,  $V_{dc}$  the DC-voltage,  $\omega$  the pulsation,  $\phi$  the power factor.

**Examples of MMCs implementations for HVDC** A list of HVDC projects based on MMCs can be found in Table 1.1. This list describes the different ratings (voltages, power) as well as the submodule topologies (see 1.1.2.2), the applications (GC stands for Grid Connection, OWF for offshore wind farm) and the manufacturers. This table is based on manufacturer documentation [1, 4, 32, 99], publications and presentations listing the projects [70, 53, 38]. It is, of course, non-exhaustive.

#### 1.1.2 The MMC Submodule

#### 1.1.2.1 Structure of an MMC Submodule

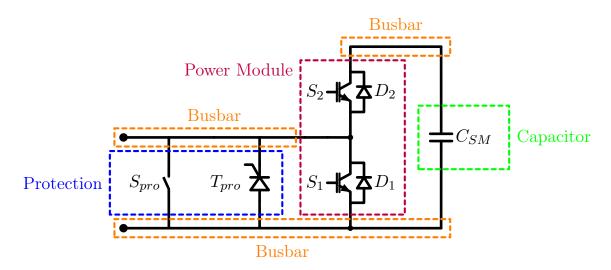

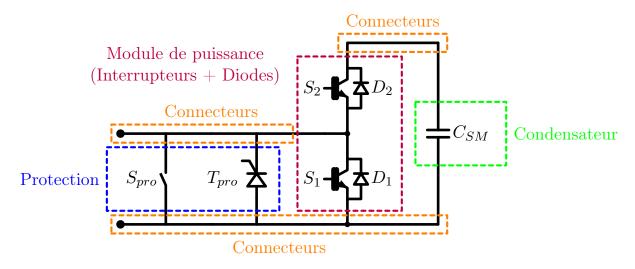

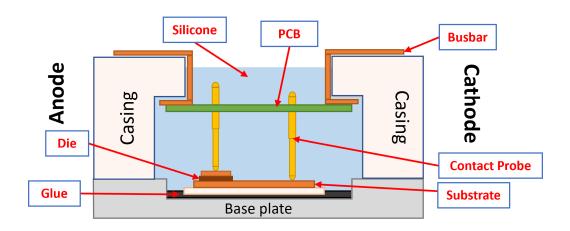

The different parts of a typical submodule, their role and characteristics are described below [24] (each of theses parts is then described in details in section 1.2). The table 1.2 and the figure 1.3 offer a quick overview of those parts.

• The power module houses the power switches with their anti-parallel diodes. This power module is the main source of losses in the MMC and one of the most expensive parts. The most used switch for HVDC MMCs is the silicon (Si) IGBT, due to a combination of its high voltage and high current ratings and its ease of control. Silicon carbide (SiC) MOSFETs are used in low current MMC (such as MVDC MMCs). IGCT, a component

Table 1.1: Table listing existing HVDC Projects based on MMCs, based on [4, 99, 32, 10]

| Project - date    | DC        | AC          | Power           | Topology | Application | Manufacturer |

|-------------------|-----------|-------------|-----------------|----------|-------------|--------------|

|                   | (kV)      | (kV)        | (MW)            | 2 00     |             |              |

| TransBay Cable    | ±200      | 115/230     | 400             | НВ       | GC          | Siemens      |

| - 2010            |           |             |                 |          |             |              |

| ULTRANET          | ±380      | 400         | 2000            | FB       | GC          | Siemens      |

| - 2020            |           |             |                 |          |             |              |

| SylWin1 - 2015    | $\pm 320$ | 155/300/380 | 864             | HB       | OWS         | Siemens      |

| INELFE - 2015     | $\pm 320$ | 400         | $2 \times 1000$ | HB       | GC          | Siemens      |

| Caithness Moray   | ±320      | 230/400     | 1200            | -        | GC          | ABB          |

| - 2018            |           |             |                 |          |             |              |

| Skagerrak 4       | 500       | 400         | 700             | -        | GC          | ABB          |

| - 2014            |           |             |                 |          |             |              |

| DolWin 1 - 2015   | ±320      | 155/380     | 800             | -        | OWS         | ABB          |

| DolWin 2 - 2017   | ±320      | 155/380     | 900             | -        | OWS         | ABB          |

| DolWin 3 - 2018   | ±320      | 380         | 900             | -        | OWS         | GE           |

| SydVästlänken     | ±300      | 400         | 2×600           | -        | GC          | GE           |

| (South-West Link) |           |             |                 |          |             |              |

| - 2016            |           |             |                 |          |             |              |

| Nan'ao Three-     | ±160      | 110         | T1:200          | T1: HB   | GC          | T1:RXPE      |

| terminals - 2013  |           |             | T2:100          |          |             | T2:XiDian    |

|                   |           |             | T3:50           |          |             | T3:NanRui    |

| Zhoushan Five-    | ±200      | T1-2:220    | T1:400          | -        | GC          | -            |

| terminals - 2014  |           | T3-4-5:110  | T2:300          |          |             |              |

|                   |           |             | T3-4-5:100      |          |             |              |

of the thyristor family, is being studied as a good alternative of the IGBT in HVDC MMC due to its lower losses and will be investigated in details in this thesis memoir. The different semiconductor switches are further developed in section 1.2.1.

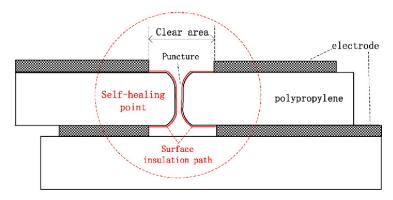

- The capacitor behaves in the MMC like a voltage source. All high power MMC submodules reported use of MPPF (Metallized PolyPropylene Film) capacitors because of their self-healing property, stability and cost. In [45], the energy storage requirements are calculated for a 4.5MVA MMC at 21kJ/MVA. The same calculation was done in [75], with a 20 MVA MMC and a 600 MVA MMC, and a value of 39kJ/MVA was found. As it can be guessed, these values depend on the MMC specifications, on the control etc. In [105], commercialised MPPF capacitors have been listed and studied. For the MMC ratings of [45, 75], the capacitor energy density would be around 350 J/L according to [105]. It would mean a capacitor volume of 60L/MVA or 111.4L/MVA, that is a total capacitor volume of 270L for the 4.5MVA MMC [45] and 66.8m³ for the 600MVA MMC of [75]. This represents one of the main source of volume of the converter. The review of capacitor technologies and dimensioning techniques are developed in section 1.2.2.

- The **busbar** is the electrical connexion between the elements of the submodule. It is subject to dielectric, thermal and mechanical stresses. It is further developed in section 1.2.3.

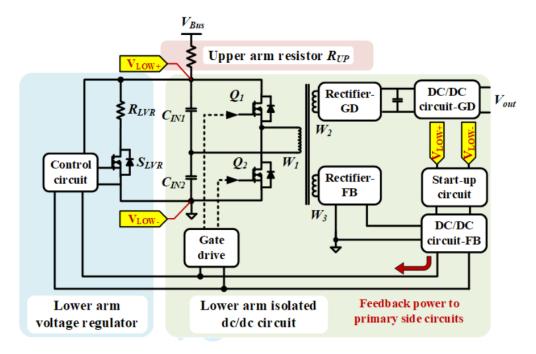

- The **control electronics** manage the interface with the main controller (fibre optic link) of the MMC converter: they receive switching orders for the IGBTs, and send status

Table 1.2: Table presenting an overview of the different parts of a submodule in an MMC.

| Part                                            | Role                                                     | General Design<br>Rules and Principles                                         |

|-------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|

| Power Module                                    | Inserts or removes the capacitor                         | Generate low losses, Able to withstand voltage, current, frequency constraints |

| Capacitor                                       | Voltage Source/<br>Energy Storage                        | Energy requirement, RMS Current, Voltage                                       |

| Busbars                                         | Electrical Connexion                                     | Low stray inductance,<br>low stray capacitance,<br>low resistance              |

| Protection Circuits<br>and Bypass<br>Components | Protect the SM<br>or the MMC                             | Short-Circuit, overvoltages, and other defined failure scenarii                |

| Auxiliary<br>Circuits                           | Acquire measures,<br>Control the SM,<br>Power Supply     | High reliability (regarding EMC), Isolation                                    |

| Cooling System                                  | Cools mainly the semiconductors                          | Cooling power and insulation requirements                                      |

| Mechanical Structure                            | Holds the SM parts<br>together, permit<br>valve assembly | Applied efforts,<br>insulation requirements,<br>possible to assemble           |

Figure 1.3: Typical Half-Bridge submodule structure.

feedback, as well as measurements of the capacitor voltage and of the submodule current. It also drives the protection circuits and bypass systems. This control system requires a low voltage power supply (with an external or internal power source). It is often a complex printed circuit board, with an important number of electronic components. This element is essential and is working in a harsh electromagnetic environment. Auxiliary circuits are developed in section 1.2.4.

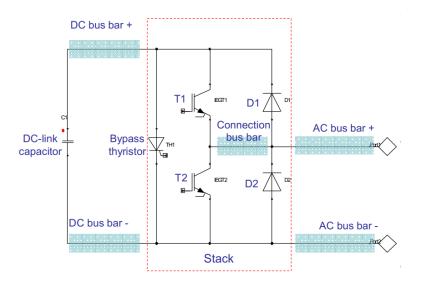

- Bypass components are necessary for mainly two reasons: a permanent and a temporary bypass. The permanent bypass is activated in case of fault in a submodule. It can be done by a mechanical switch or a switch in short-circuit a fail-to-short system. A temporary bypass can be needed either to protect the diodes from overcurrents or to help a mechanical switch, often too slow for the bypassing operation. Other protection circuits can be found and they vary from one submodule to another. Bypass components and other protection circuits are developed in section 1.2.5.

- A **cooling system** is designed to evacuate the losses, mostly from the power semiconductors, the main source of losses. This is done with liquid (often deionised water) or air cooling, with forced or natural convection. More details are given in section 1.2.6.

- The **mechanical structure** is holding together the different parts of the submodule. It must take into account the weight, but also that the submodule can be easily assembled, that different parts have different voltages and must be isolated from one another (insulation function, see section 1.1.5).

#### 1.1.2.2 Submodule Topologies

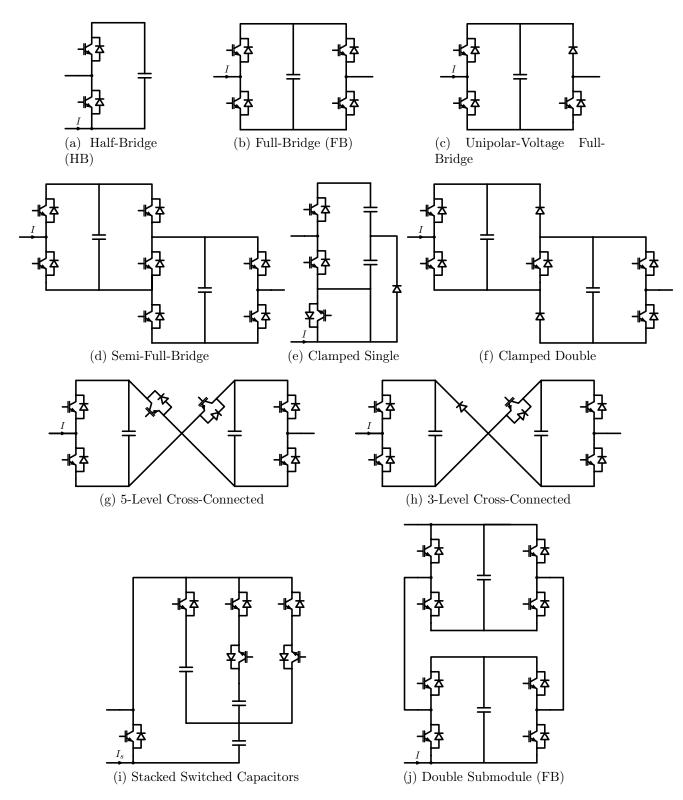

Many submodule circuits topologies have been introduced in the scientific literature. At the time this thesis is written, only two of them (the so-called "half-bridge" and "full-bridge") actually appear to be produced industrially for HVDC. They are presented in the next section. The remaining topologies may offer specific advantages, but their development is much less advanced.

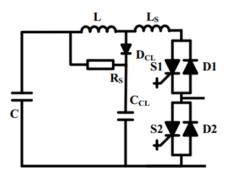

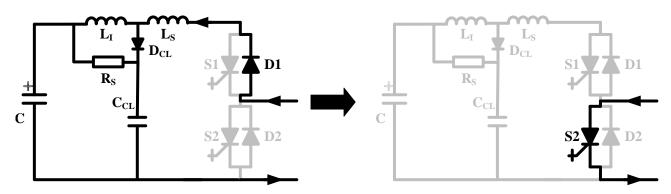

Half-Bridge (HB) The half-bridge structure (displayed in figure 1.4a) is the most common topology for MMC submodules. Its simplicity – only 2 switches – makes it easy to study, and limits the cost of the semiconductors. This topology has been intensively investigated [107, 56, 28, 16]. MMC converters based on Half-Bridge submodules have been designed and built by companies such as General Electric, Siemens, ABB, Mitsubishi, or Hyosung [12].

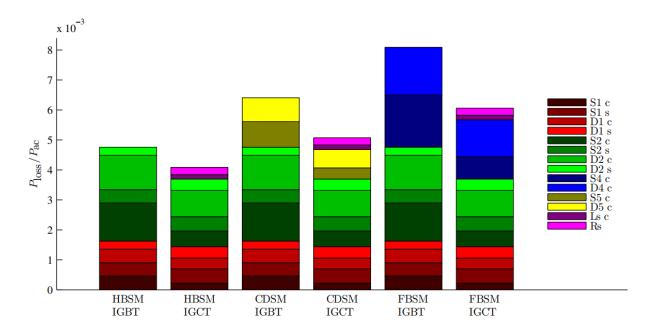

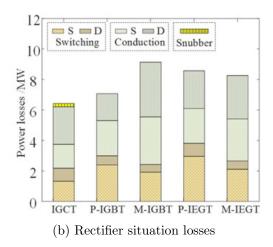

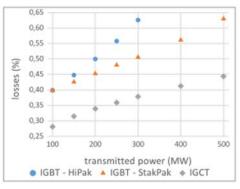

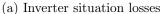

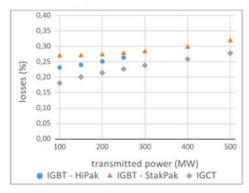

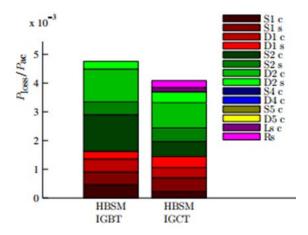

The Half-Bridge is the reference topology for losses as current flows through only one semiconductor switch at any given time, resulting in low conduction losses. An example of losses breakdown for half-bridge submodules (as well as for other topologies introduced below) can be found in figure 1.5.

The main problem with that topology is that it is unable to block a "pole to pole" DC short-circuit. Such short-circuit condition is described in the section about overstress situations (1.1.4). It implies that the MMC must be equipped with an AC or DC circuit breaker and that the anti-parallel diode of the switches must sustain large surge currents, or be assisted by a bypass thyristor.

Figure 1.4: Submodule topologies, see the corresponding table 1.3.

Figure 1.5: Example of losses breakdown for HB, FB and Double clamped submodule topologies using IGBT or IGCT switches, extracted from [76]

Another limitation of this topology is its lack of flexibility. Indeed, the modulation factor of the MMC cannot exceed 1, and in practice it is mostly used around 0.8 [68].

Full-Bridge (FB) The full-bridge topology (also called H-bridge, displayed in figure 1.4b) is composed of 4 switches. This makes this topology more expensive, more complex in terms of control. It also has more conduction losses (Fig. 1.5) [76, 68], as current has to flow through two switches connected in series at any given time. The two main advantages of this topology are: its capability of handling a DC-side short circuit (because the capacitors of the submodules are on the path of the short-circuit current), and a modulation factor higher than 1 (because negative voltage can be inserted).

To mitigate the drawbacks of the full bridge topology, a mixed MMC (i.e. including some FB submodules and some HB submodules) can be found in the literature. In [58], it is found that to handle the DC-side short-circuit, around 80 % FB submodules are needed, so 20 % of the submodules can have a HB topology. However, this kind of combination will not be investigated further in this thesis, because we will focus on the conception of one submodule – HB, FB or other topology – and not on the entire converter.

Other topologies and Comparison A summary of the different topologies which can be found in the literature is presented in table 1.3 and figure 1.4. These submodule topologies are only listed here for reference, and will not be discussed further. Only the HB and FB topologies appear to have been used in full-scale demonstrations.

As written in [69, 98], the half-bridge submodule is the topology with the lowest losses and the lowest cost – if we only take the price of the power semiconductors into account. In addition, most other topologies have only been described in publications using computer simulation or

Table 1.3: Comparison of the different submodule topologies, the circuits are displayed in Fig. 1.4

| SM Topology                         | Advantages                          | Drawbacks                          |

|-------------------------------------|-------------------------------------|------------------------------------|

| Half-Bridge [69, 68, 98]            | Simple, low losses, well-known      | Lack of flexibility, no negative   |

|                                     | and studied, few semiconduc-        | voltage possible, $k \leq 1$ , DC- |

|                                     | tors                                | short not controllable             |

| Full-Bridge [69, 68, 98]            | Negative voltage possible,          | Lots of semiconductors, high       |

|                                     | possibility of $k > 1$ , DC-short   | losses                             |

|                                     | controllable                        |                                    |

| Unipolar-Voltage FB [98]            | DC-short controllable               | No negative voltage, higher        |

|                                     |                                     | losses than HB (conduction         |

|                                     |                                     | only)                              |

| Semi-Full-Bridge [44, 69, 98]       | Reducing Capacitance a lot          | losses and perturbation due to     |

|                                     | (by reducing the ripple), $k >$     | current going from one capac-      |

|                                     | 1 possible, two switches rated      | itor to another                    |

| C1 1 C: 1 [00]                      | half of the other ones              | II. 1 4 IID                        |

| Clamped Single [98]                 | DC-short controllable, some         | Higher losses than HB              |

|                                     | device with lower blocking          |                                    |

| Clamped Double [98, 69]             | voltage  DC-short controllable, Re- | Slightly higher losses than        |

| Clamped Double [90, 09]             | duced arm inductance                | HB, complex mechanical de-         |

|                                     | duced arm inductance                | sign, $k \leq 1$                   |

| Five-Level Cross-Connected [69, 98] | Only 25 percent of the sub-         | 2  different submodule topolo-     |

| Tive Eever Cross Connected [65, 56] | modules to be efficient (rest       | gies required in the converter     |

|                                     | : HB), negative voltage, DC-        | gies required in the convertor     |

|                                     | short controllable                  |                                    |

| Three-Level Cross-Connected [98]    | Similar to 5-level                  | Similar to 5-level                 |

| Stacked Switched Capacitors [106]   | Reducing the ripple and then        | HB with added switches, more       |

| , ,                                 | the capacitors size, control        | losses                             |

|                                     | same as HB                          |                                    |

| Double Submodule (FB) [98]          | Same as for FB, plus reduced        | Same as FB, may be difficult       |

|                                     | capacitance                         | to assemble                        |

small-scale demonstrators. Meanwhile, the half-bridge topology is already implemented in real industrial applications. Full-bridge submodules may also be of interest, but in the current study (which focuses on the submodule design) they would only add costs to a demonstrator, without actually resulting in fundamental changes in the design procedure. As a consequence, in this thesis, we will focus on the Half-Bridge submodule topology.

## 1.1.3 MMC Definitions, Design, and existing MMCs

#### 1.1.3.1 Some MMC Definitions

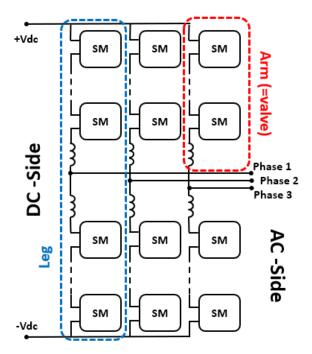

The MMC is divided into three <u>legs</u> and each leg is divided into two <u>arms</u> (six arms in total), as it can be seen in figure 1.6. The term <u>valve</u> is used to describe an association in series of parts of a converter (in a thyristor valve this is a series-connection of thyristor, in an MMC submodules in series). In thyristor-based converters, it corresponds to an entire thyristors

Figure 1.6: Definitions of arm, leg and valve in an MMC.

association conduction or blocking at the same time. In MMCs, it corresponds to an arm. The valve term is useful for technical issues covered in all types of converters (such as insulation coordination, in section 1.1.5).

#### 1.1.3.2 Considerations for the design of an MMC

An MMC must match a defined set of specifications. The first type of specifications is imposed by the project (voltage, current, power levels) and its physical location (volume, footprint); the second type of specifications is imposed by the network and its transmission system operators (TSO).

Specifications imposed by the project and its location One type of constraints is due to the location of the converter inside the electrical grid. This can impose the active power, the AC and DC voltages and therefore the current. Paralleling of converters can be achieved to reach the wanted current and power. But the AC voltage can be adapted with a transformer between the MMC and the AC-grid. Another type of constraint is due to the physical location of the converter. If the converter is located in the ocean or the sea, the weight and volume of the converter are critical.

**Specifications imposed by the network** When designing an MMC converter, some constraints are imposed by the local electrical network characteristics, its local TSO and its rules. For example, the European Union gives rules for voltage and reactive power ratings (allowed and imposed variations) [113]. The voltage ratings are described in the article 18 and annex III of [113] and the reactive power capability is described in the article 20 and annex IV of the

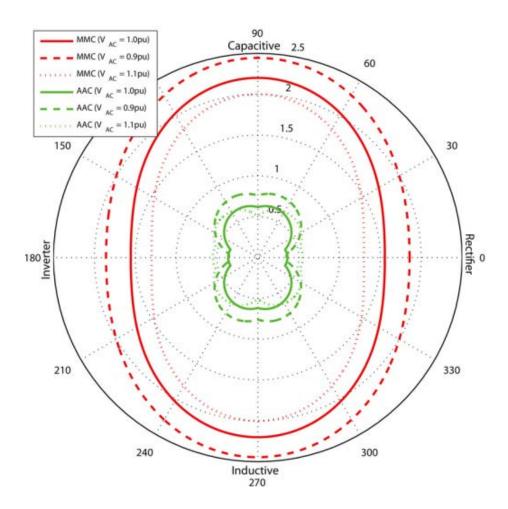

Figure 1.7: Requirements on reactive support proposed by ENTSO-E, extracted from [98]

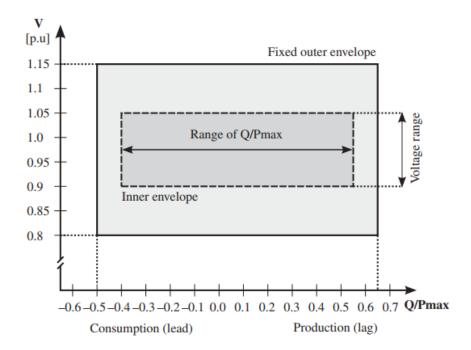

same regulation document. The pole-to-pole voltage can vary from 0.85 to 1.15 p.u. . But it depends on the region of Europe and some operating points (mainly voltages between 1.118 and 1.15 p.u.) have to be held for a limited amount of time only.

The reactive power capability is defined with a profile: a V-Q/Pmax profile with P the active power and Q the reactive power. An example of such a profile is given in figure 1.7, defined by the ENTSO-E (standing for European Network of Transmission System Operators). The regulation document of the European Union gives the outer envelope and the local TSO can draw any wanted profile inside of the outer envelope, not just rectangular shapes. Values for the inner region is available in the regulation document in the annex IV.

The frequency ranges are also defined in [113], and each range is associated to a time during which the converter still has to work. The converter has to work for an unlimited time between 49 and 51 Hz. The other ranges have to be specified by each TSO.

Global design parameters for the MMC Then an optimisation has to be done, mainly driven by global cost of the project, taking into account the efficiency and the overall cost of the station. If the submodule has to be designed from scratch, a submodule voltage is chosen. But most often, the submodule is chosen among available submodules in the market or the MMC building company. The inductance and the transformer have to be designed as well. The dimensioning process of the submodule is described in section 1.2.

The safety margin on the number of submodule is driven by the scheduled maintenance frequency (every 2 years typically), and seems to be around 5 to 10~% extra-modules for redundancy.

#### 1.1.4 Overstress and Dimensioning Situations

#### 1.1.4.1 Identified Cases of Overstress

There are plenty of overstress cases. They correspond to external or internal issues. It can be overvoltages, overcurrents, bad commutation of the switches, destruction of a part of the submodule (capacitor, switch...). The main problems that must be considered at design stage (as they affect the dimensioning of the submodule) are identified as the short-circuits, mainly on the DC-side, and the cosmic rays (which dictate the semiconductor switches operating voltage).

#### 1.1.4.2 Overcurrents

The different overcurrent cases that impact the MMC are developed in [131]. They are due either to short-circuits in the submodule with the erroneous firing of an IGBT for example, or to short-circuits outside of the submodule (AC-side short-circuit, DC-side short-circuit, short-circuit inside an MMC arm).

Internal short-circuits Two types of internal short-circuits are listed in [131]. The first is one IGBT going from off-state to short-circuit (Hard-Switch Fault) due to erroneous firing or due to the failure into short-circuit of the other IGBT. The other one is the IGBT going from on-state to short-circuit due to the break down of the IGBT or the erroneous firing of the other IGBT. This last one is called Fault under load (FUL) in [131]. Such internal short circuit causes the charged capacitance to be short-circuited by closing both IGBTs. [131] finds that this kind of fault causes fault current levels rising by 5kA to 20kA in a few µs – depending on the short-circuit situation inside the SM – for a 2.2 kV charged capacitor (value of capacitance none disclosed).

**DC-side Short-Circuits** Two types of DC-side short-circuits exist: the pole-to-ground short circuit and the pole-to-pole short-circuit. As their names indicate, the pole-to-ground is a short-circuit between one of the DC side terminal and the ground and the pole-to-pole between the two terminals of the DC side of the converter. A pole on the DC side is the negative or positive voltage terminal (-Vdc or +Vdc in figure 1.6).

According to [98], the most severe possible short-circuit for the components of the submodule is the DC-side short-circuit. It is hard to provide a probability or frequency of fault for these short-circuits, because they are specific to the converter, the cables and the grid around the converter. But the risk is high enough for the semiconductors in the submodules to consider installing a protection system. When the pole-to-pole fault occurs, the voltage on the DC side drops below the voltage on the AC side, allowing current to flow through the antiparallel diodes of the semiconductor switches in a HB submodule. Three main strategies exist to interrupt the short-circuit current [134]: having an AC-side breaker, having a DC-side breaker or having a topology able to withstand the short-circuit (i.e. a topology in which submodules can block current in both directions, such as a full-bridge). For topologies with uni-directional current control (such as the half-bridge), a bypass thyristor can be connected in parallel with the

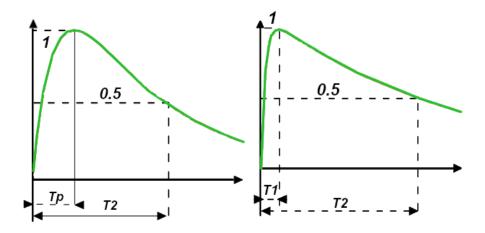

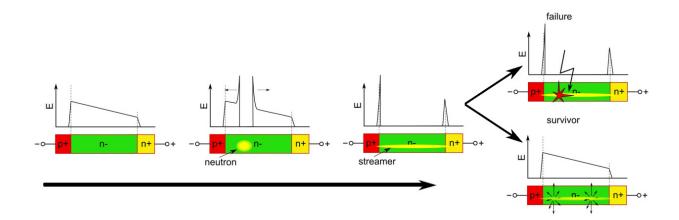

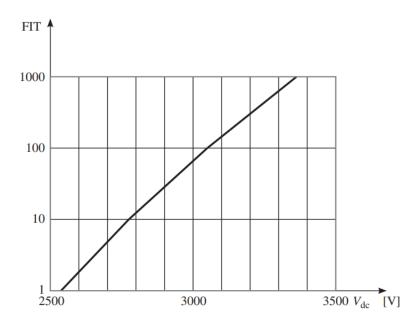

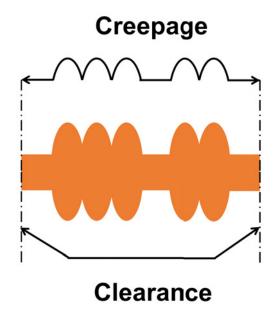

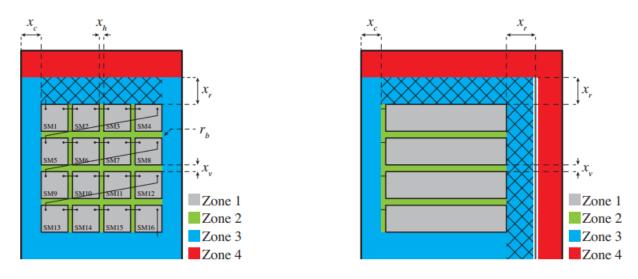

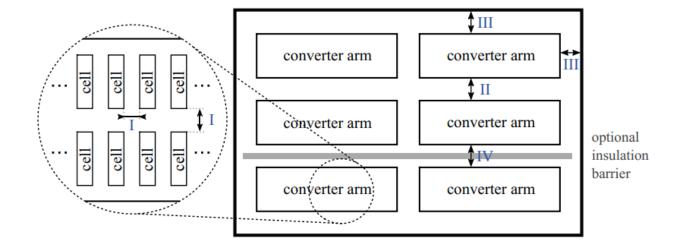

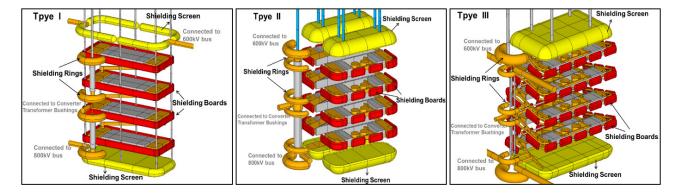

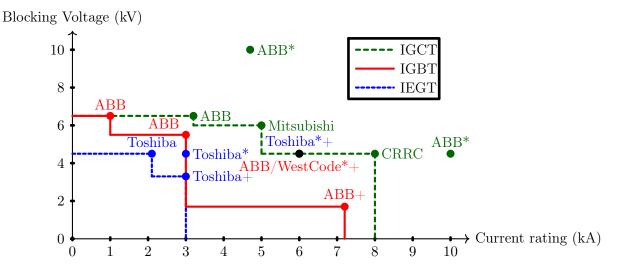

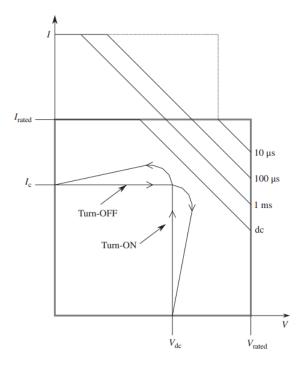

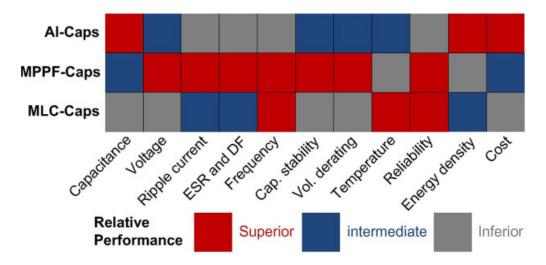

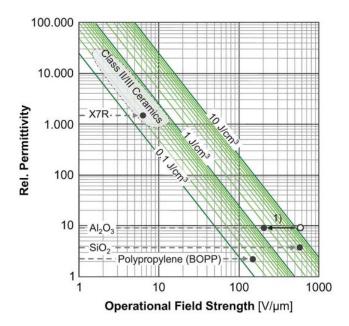

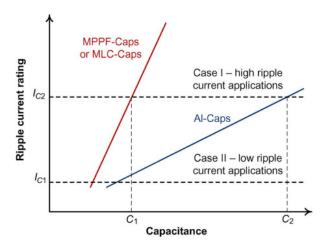

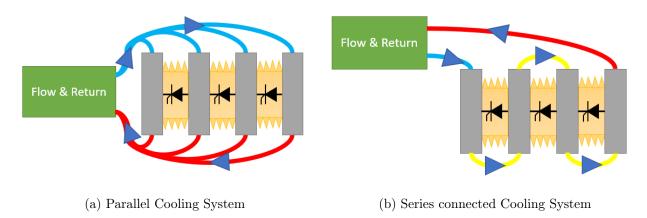

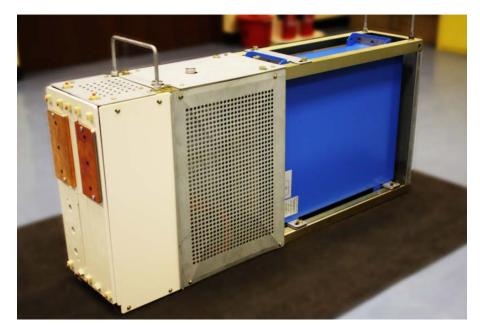

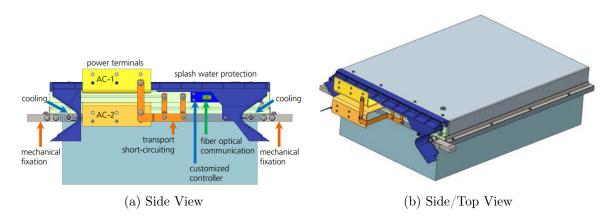

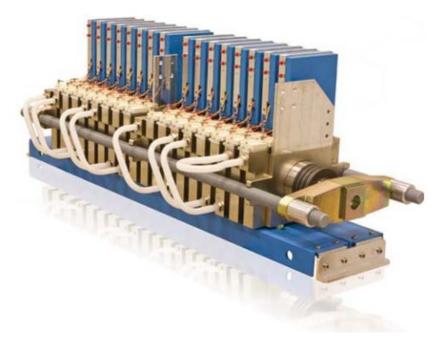

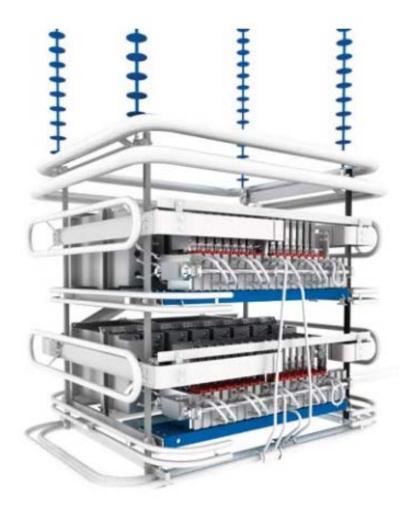

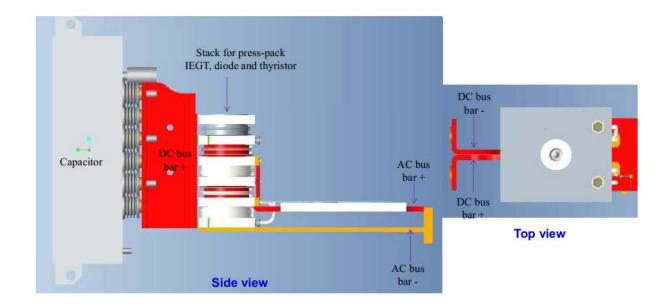

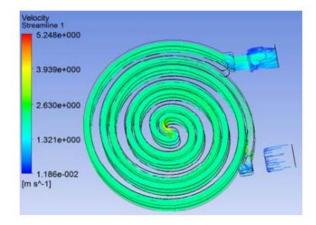

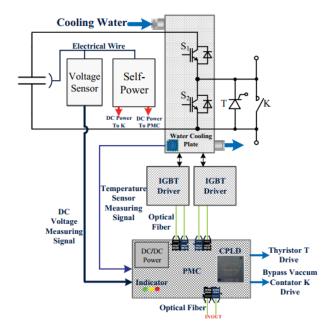

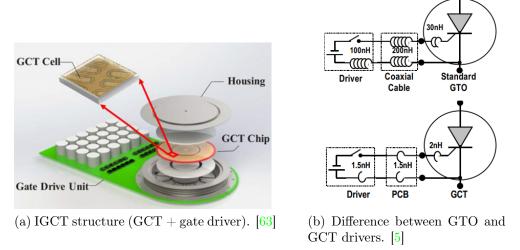

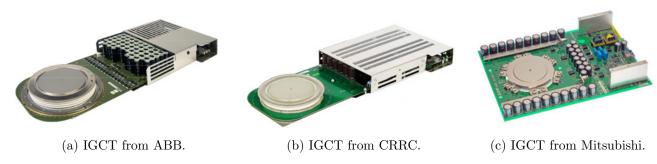

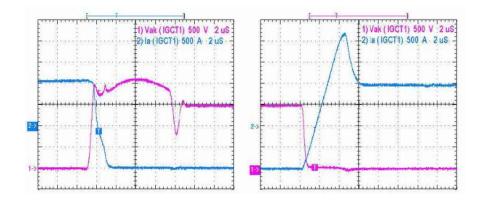

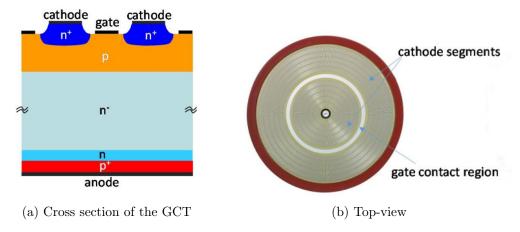

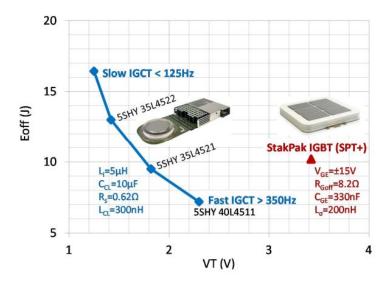

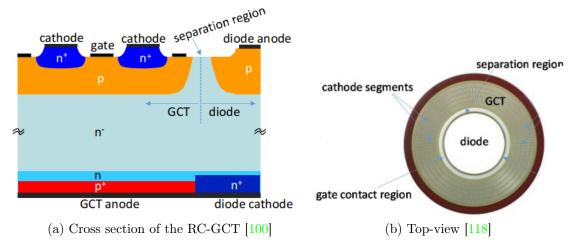

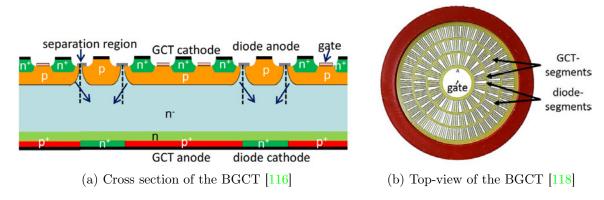

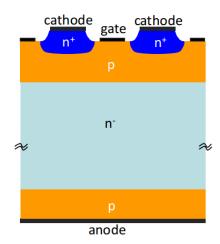

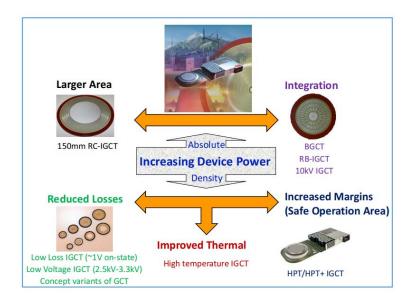

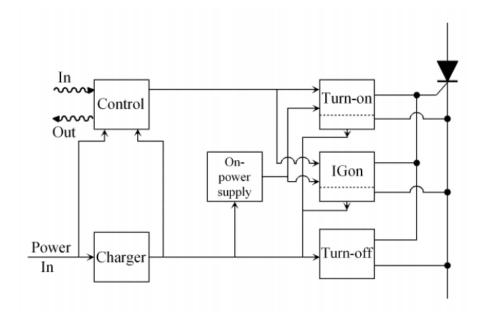

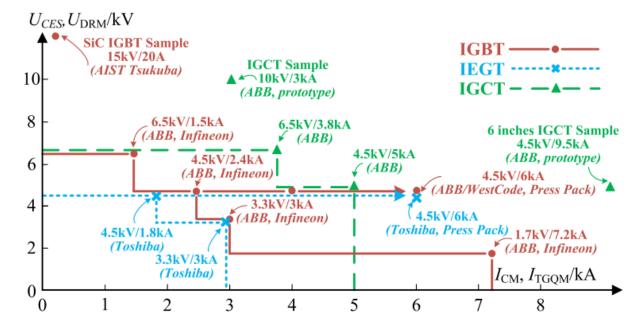

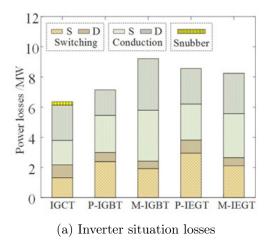

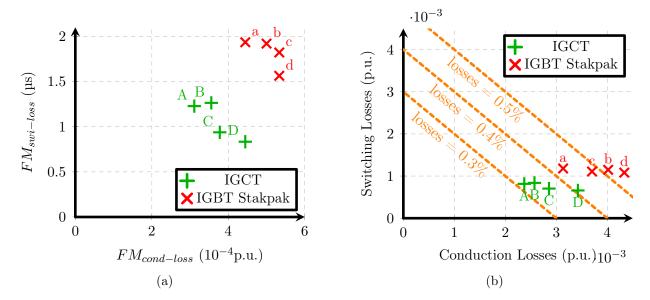

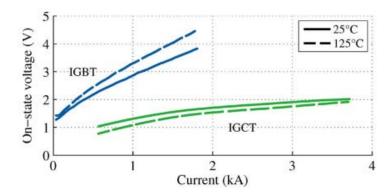

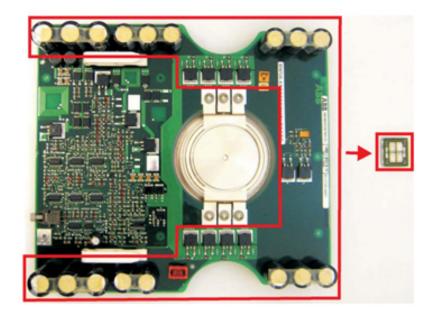

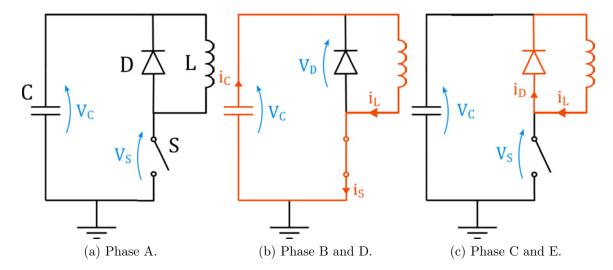

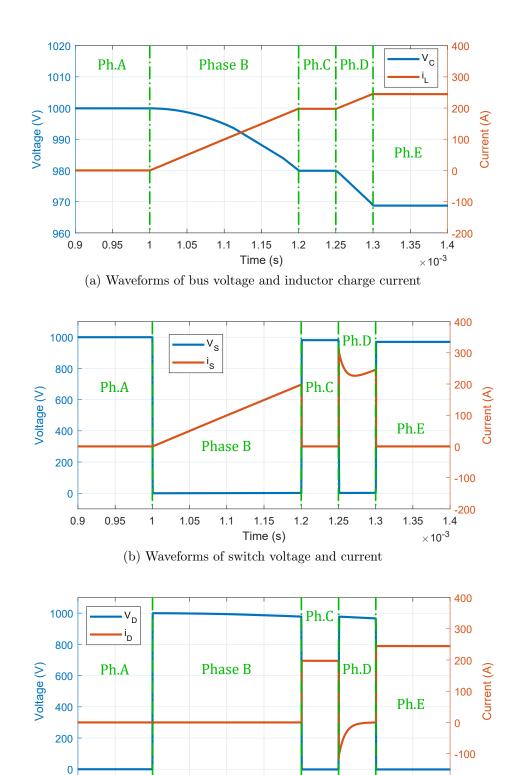

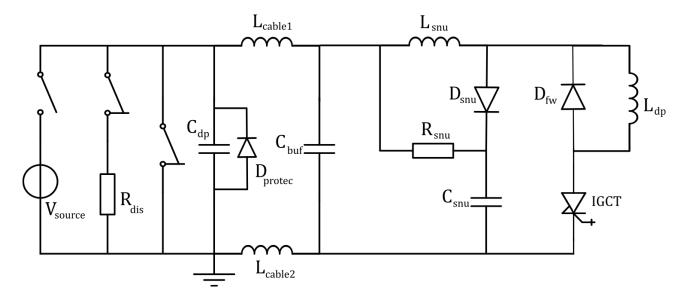

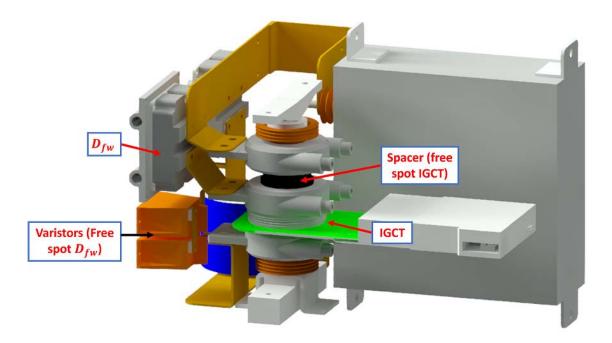

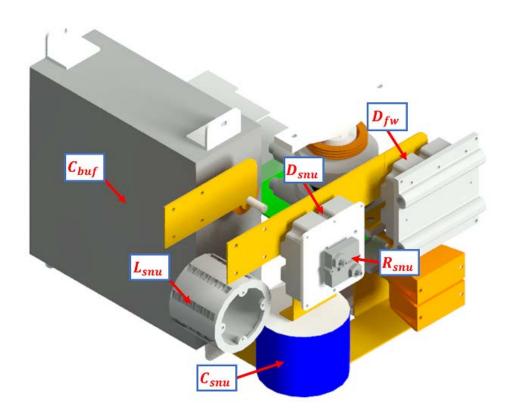

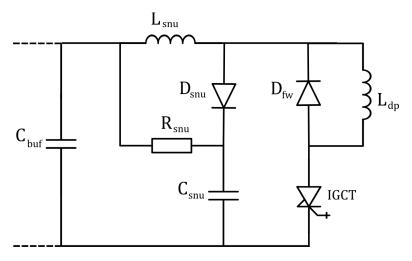

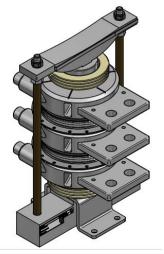

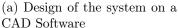

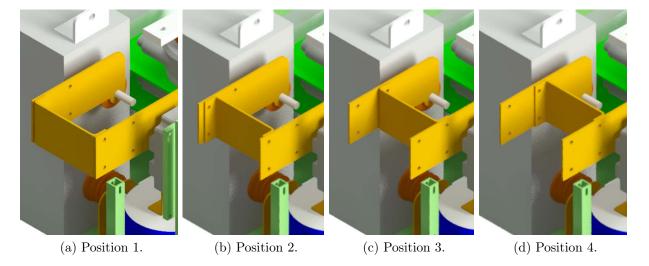

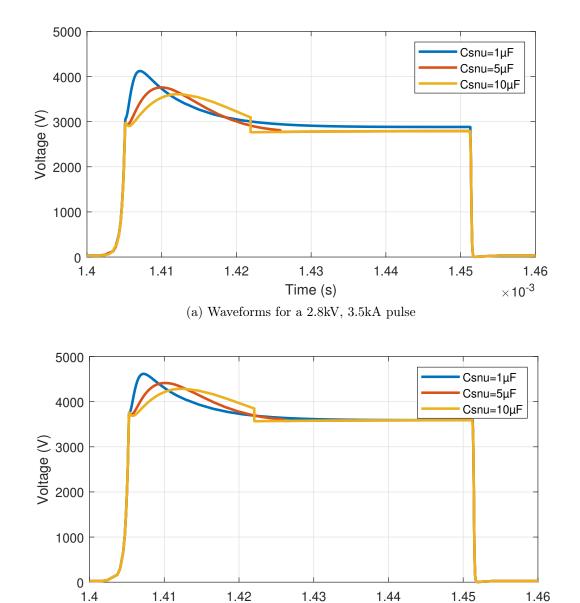

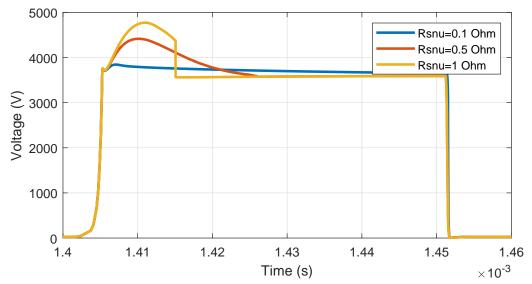

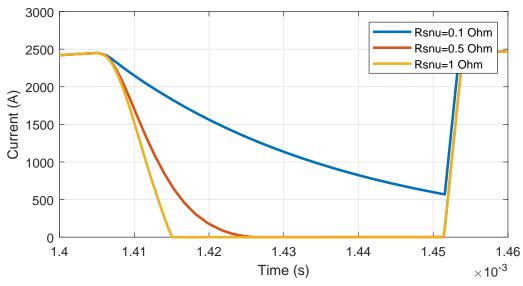

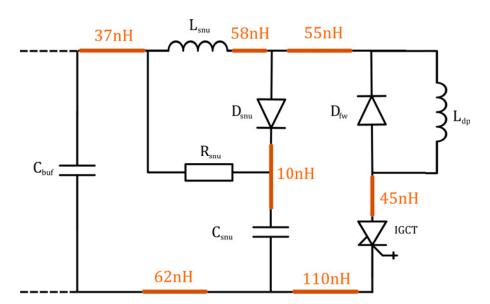

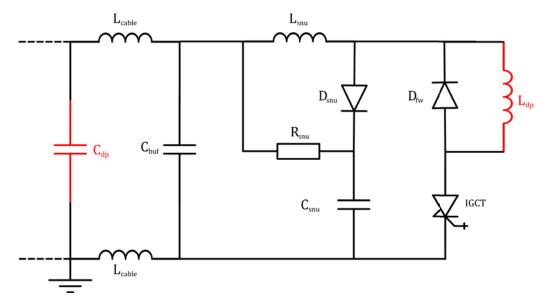

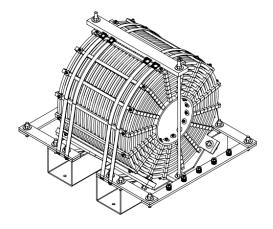

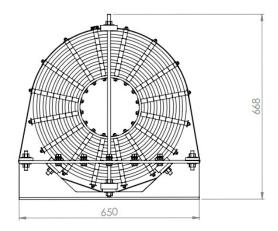

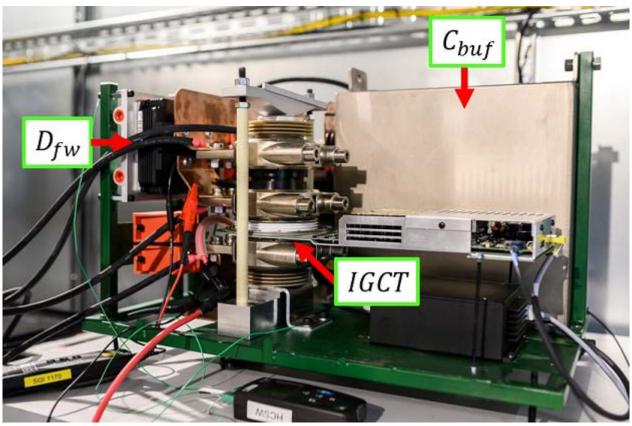

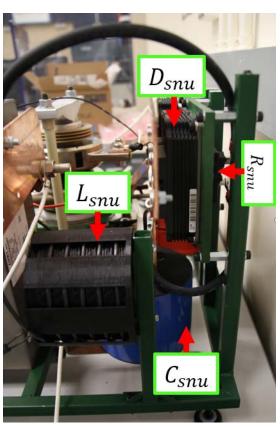

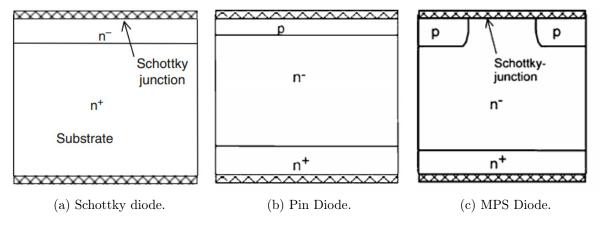

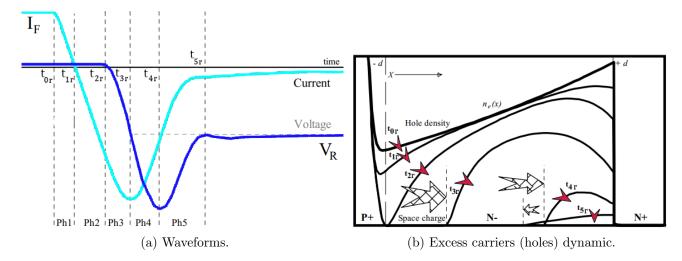

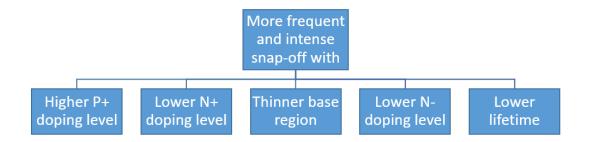

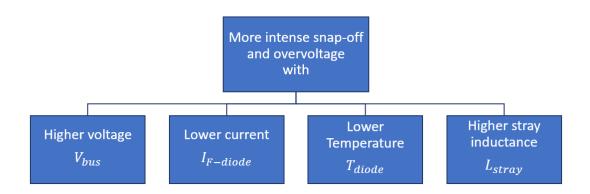

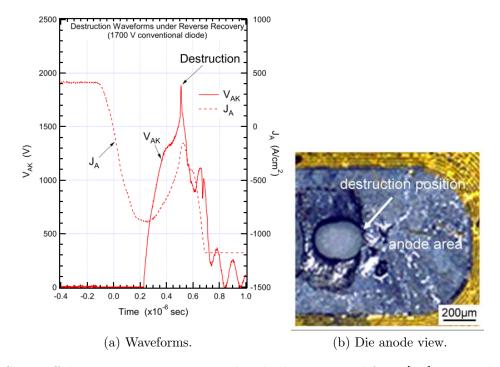

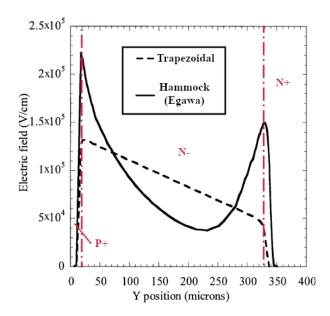

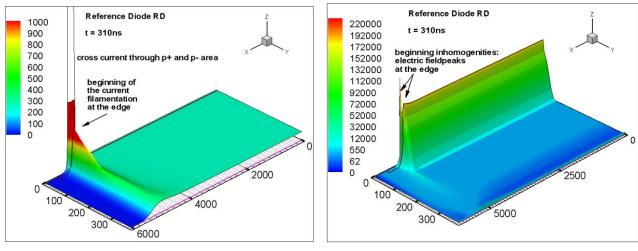

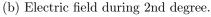

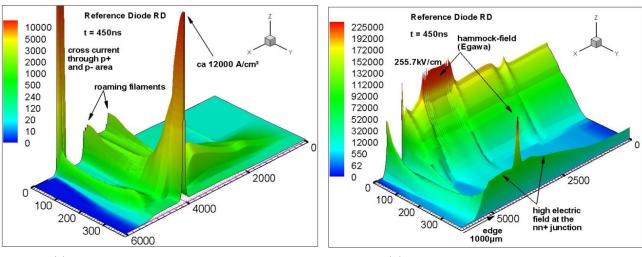

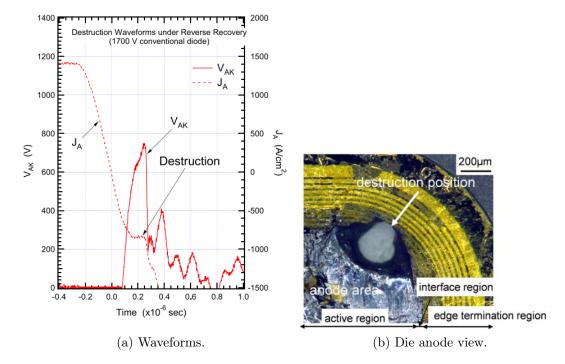

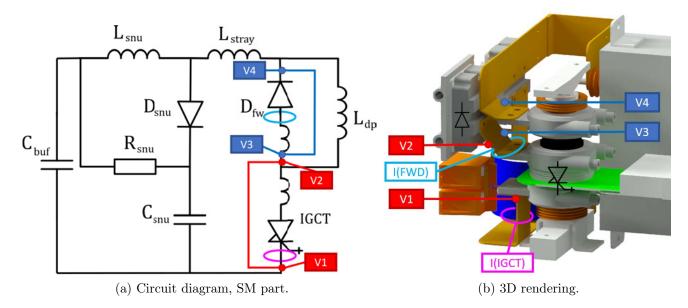

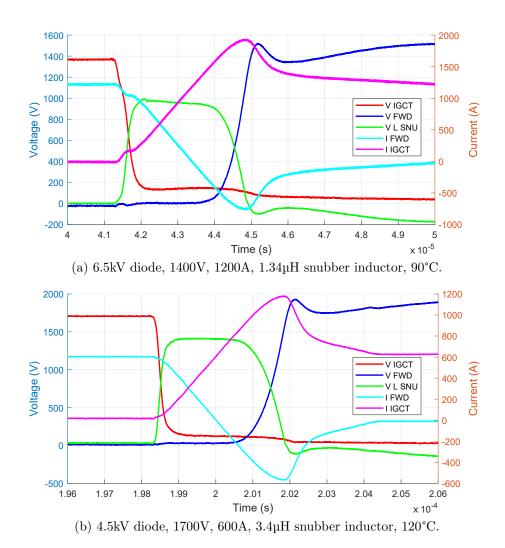

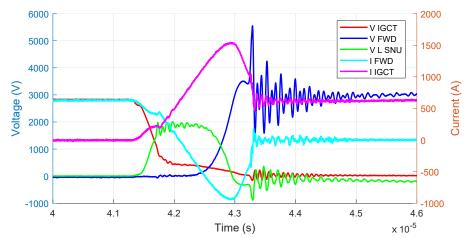

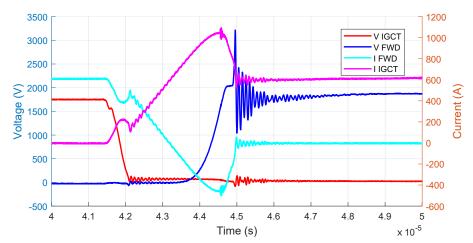

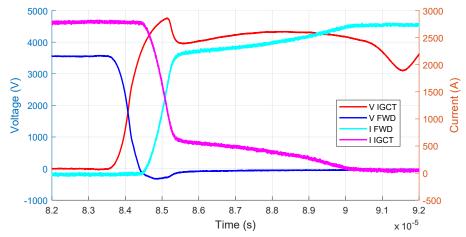

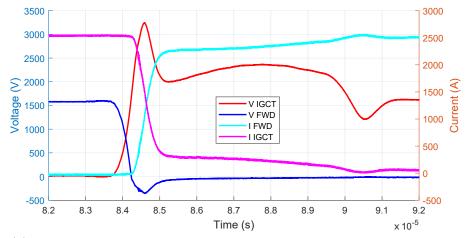

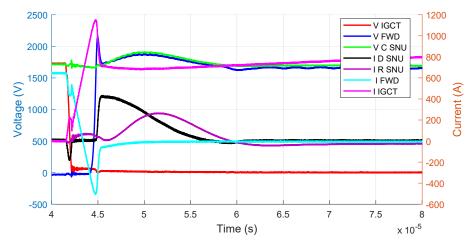

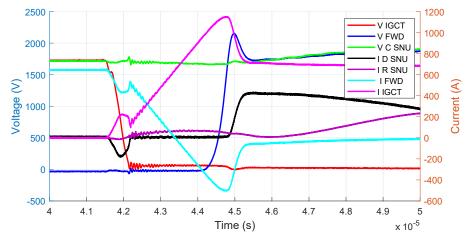

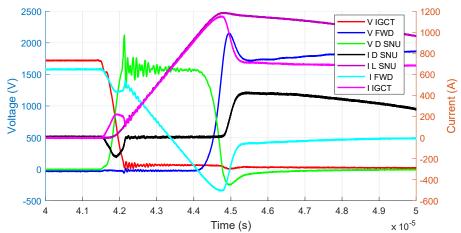

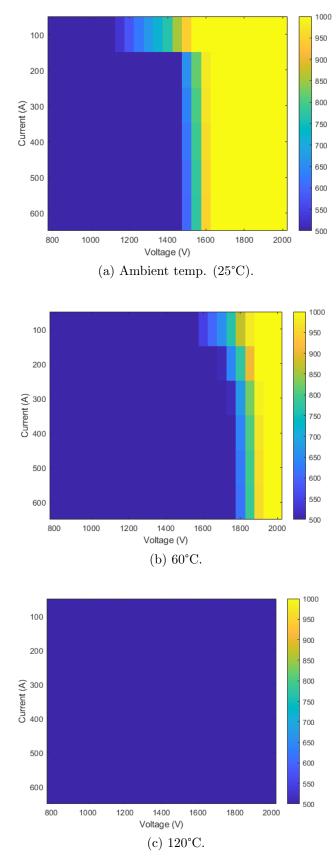

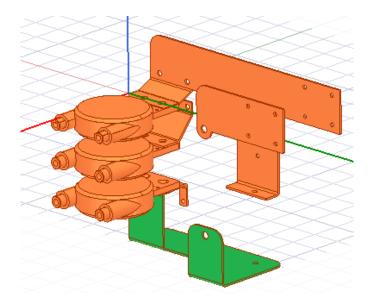

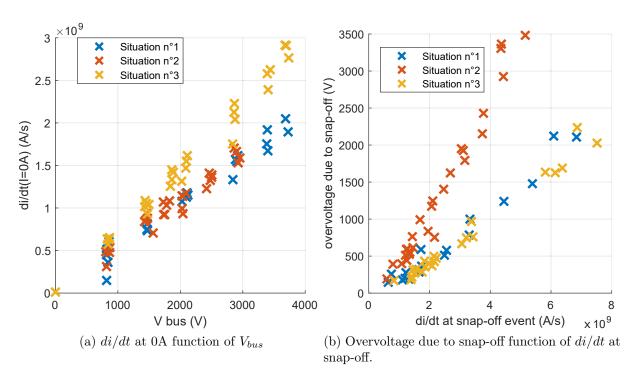

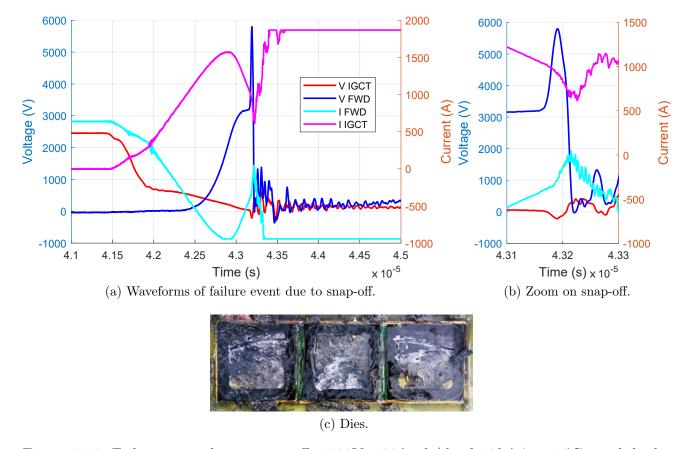

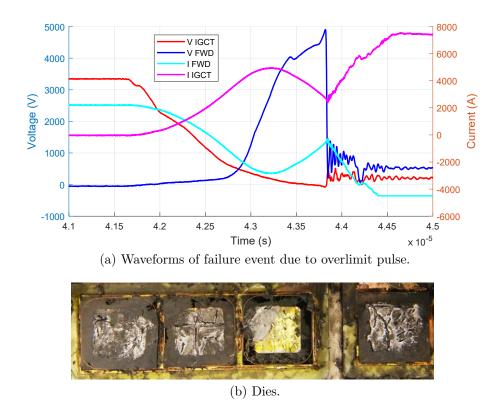

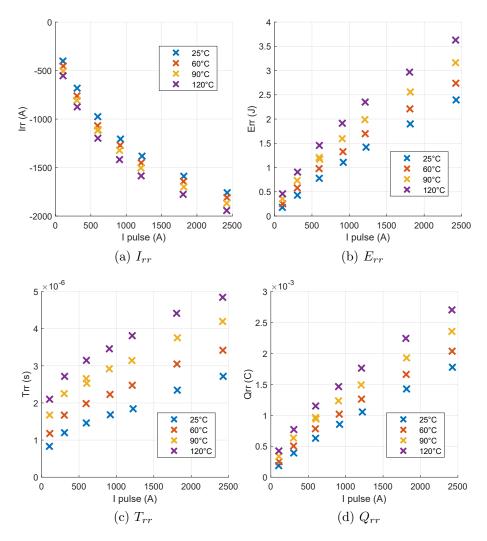

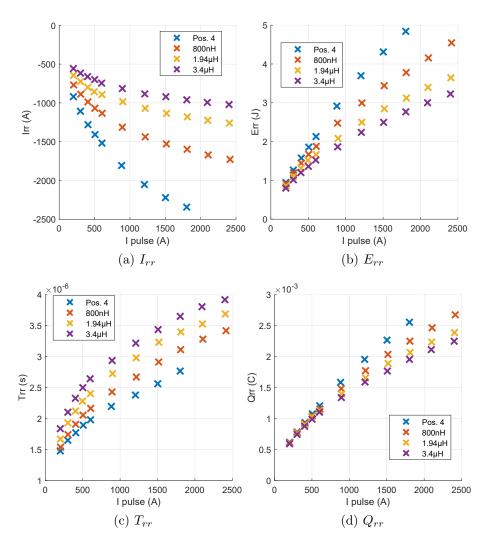

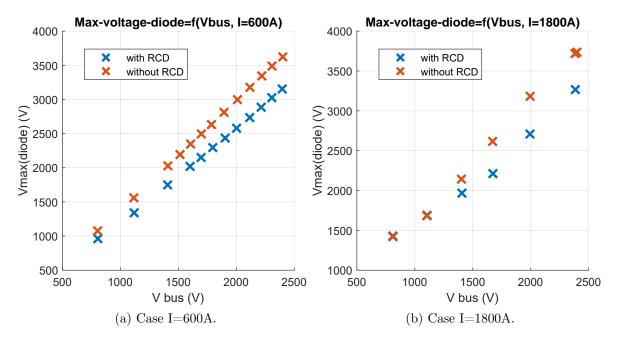

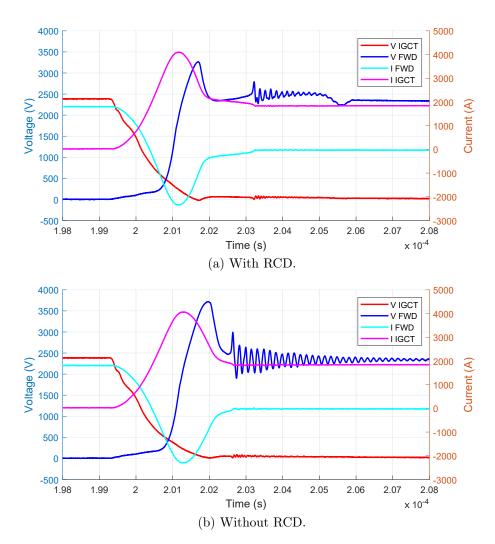

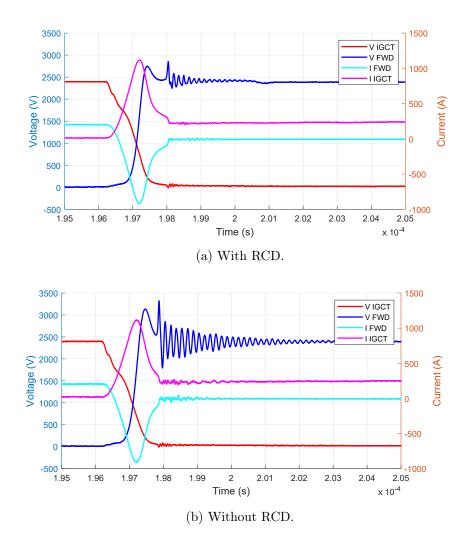

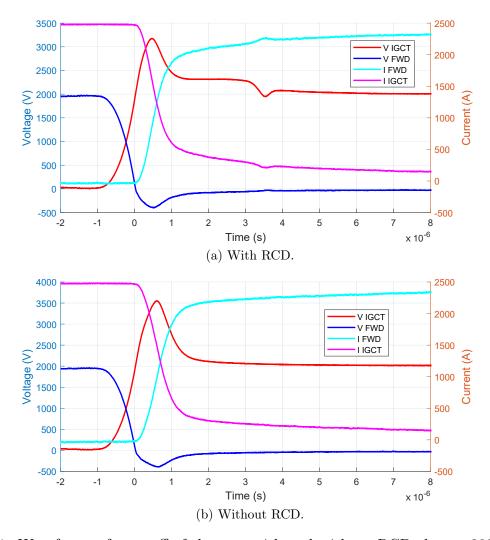

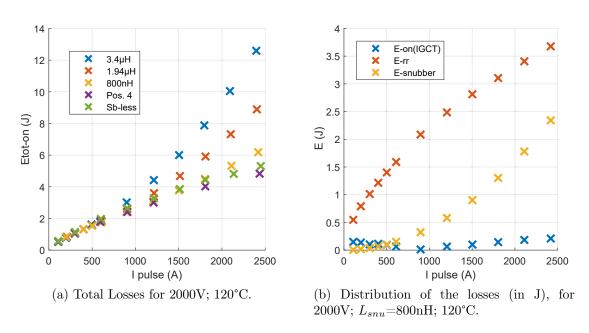

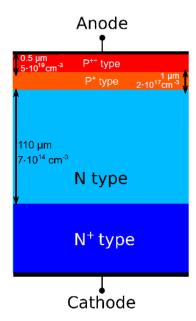

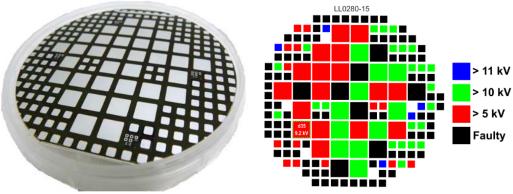

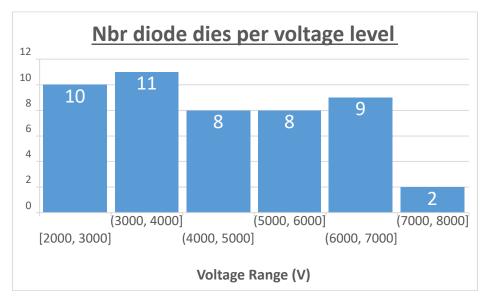

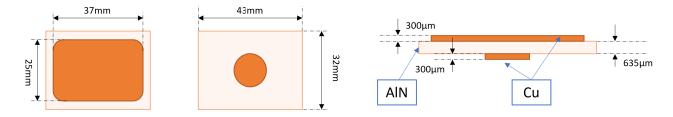

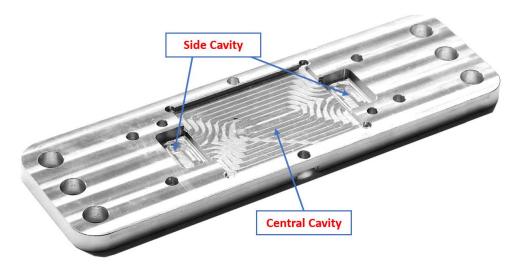

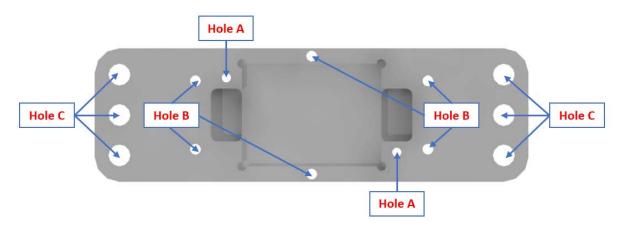

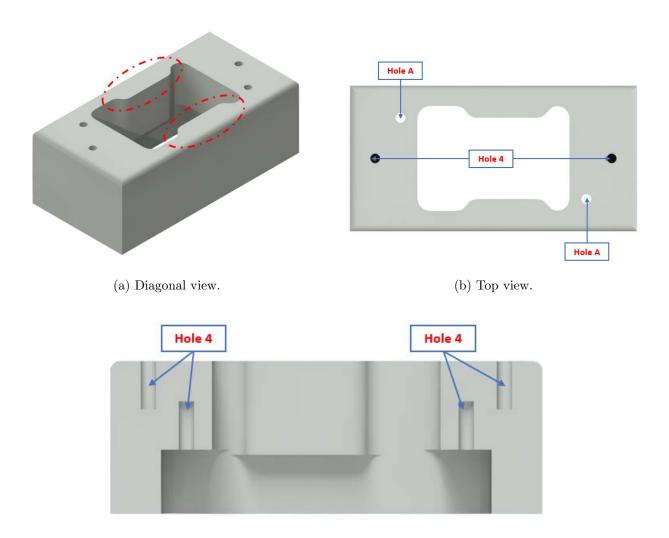

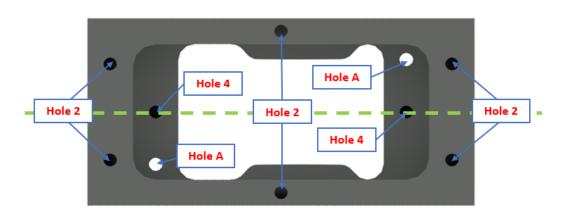

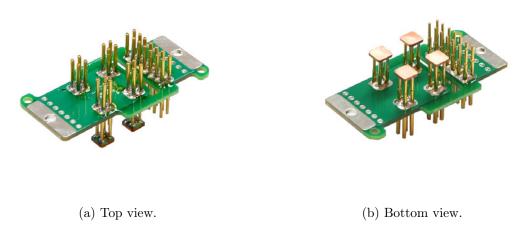

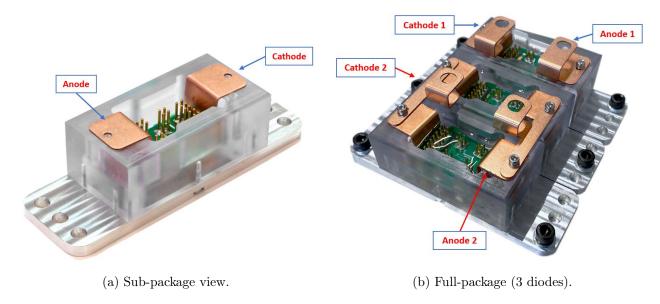

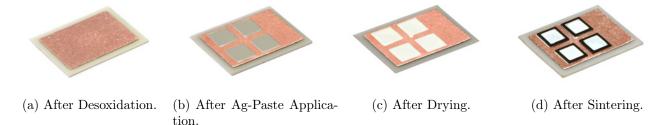

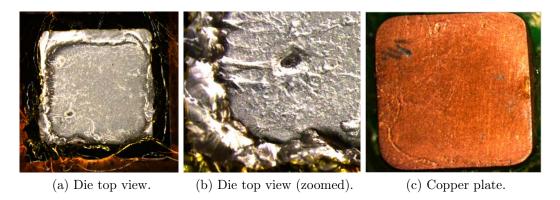

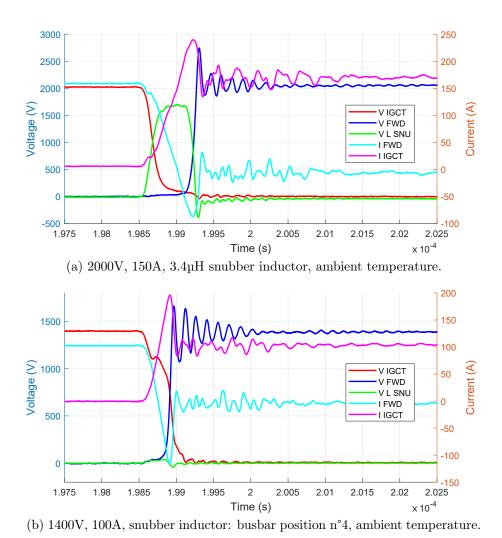

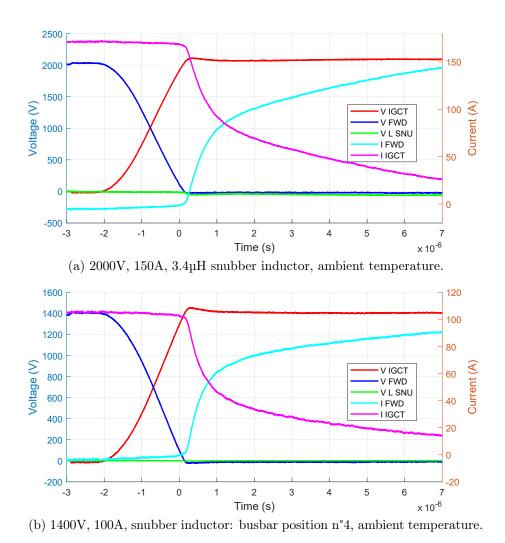

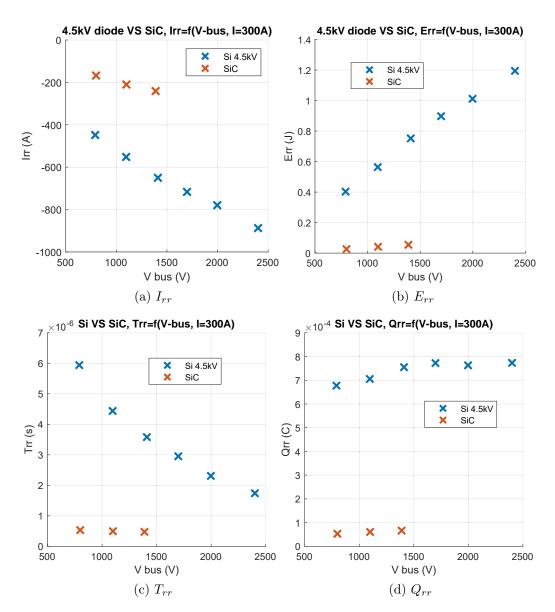

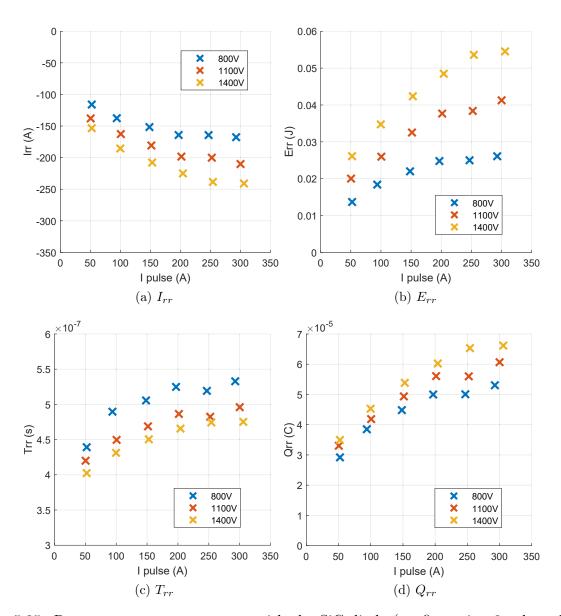

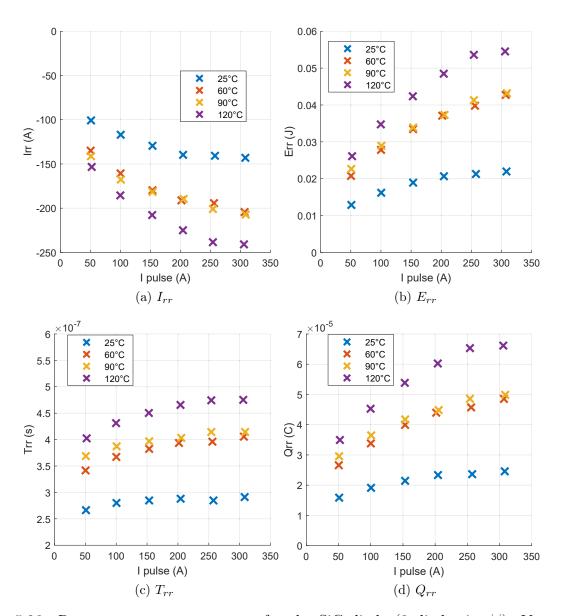

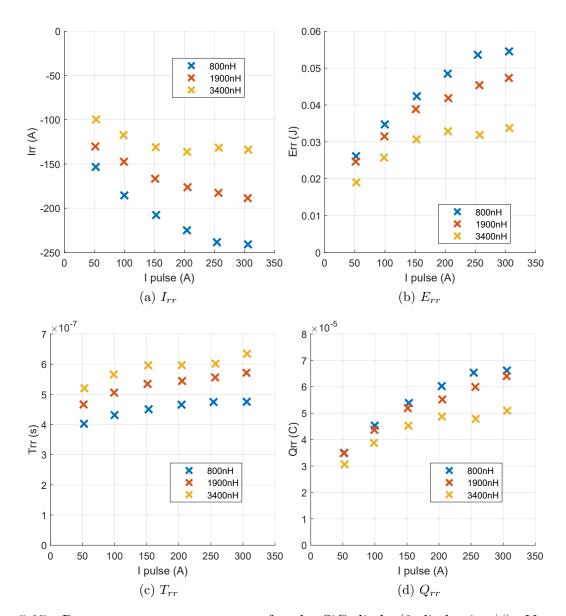

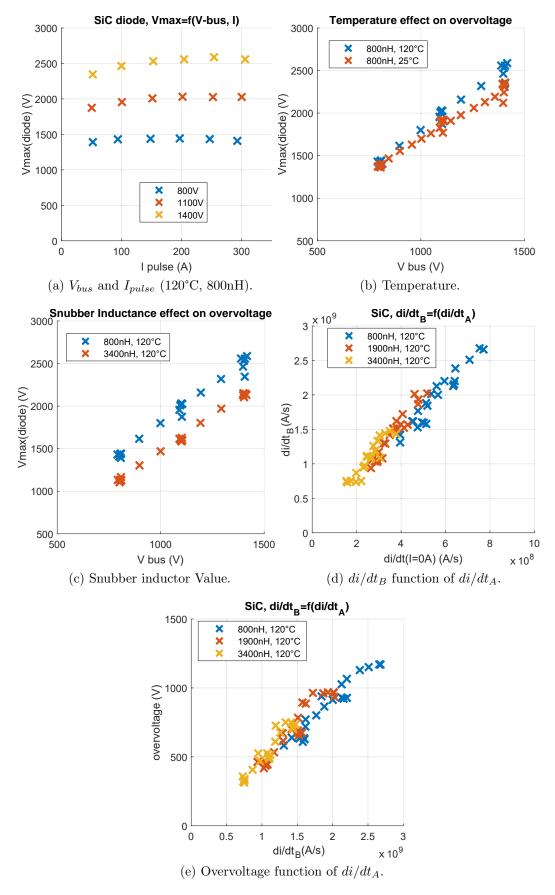

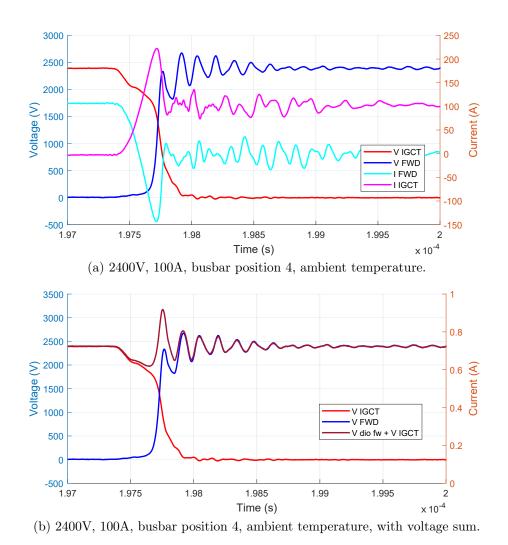

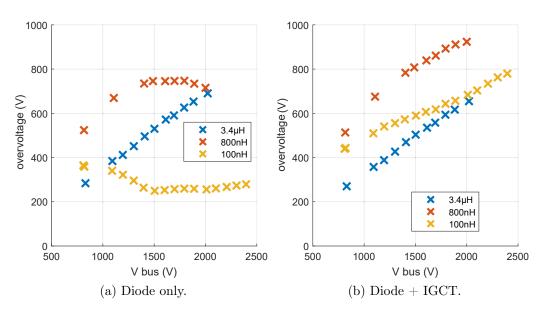

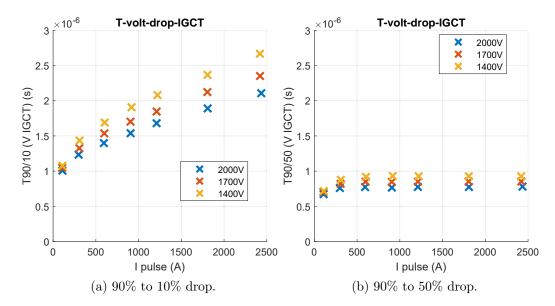

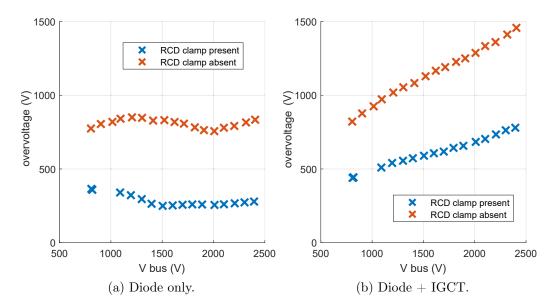

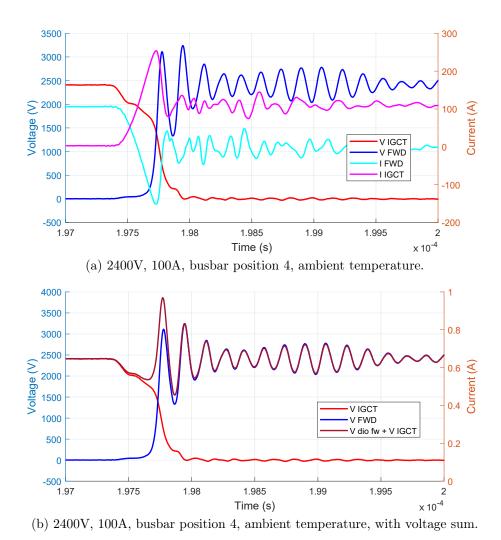

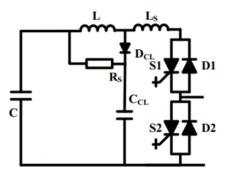

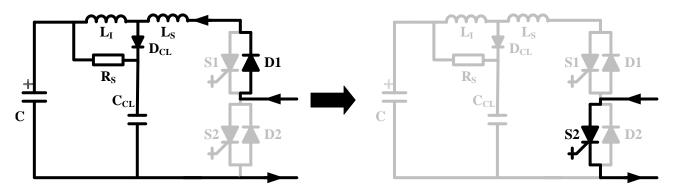

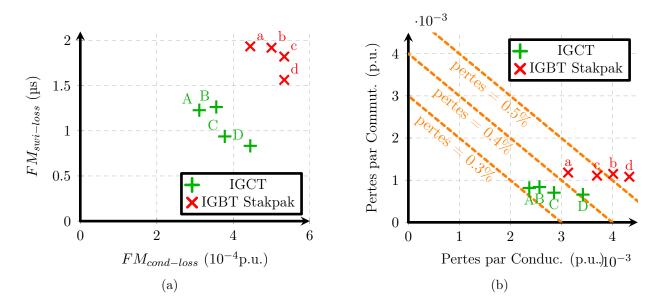

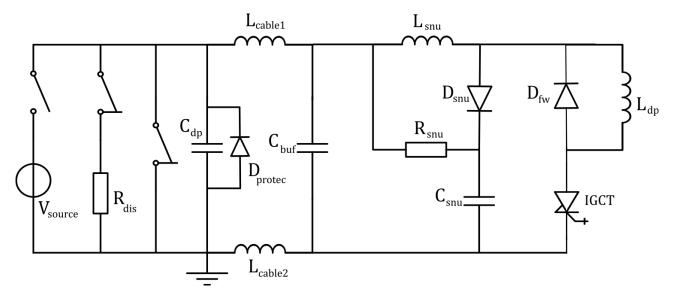

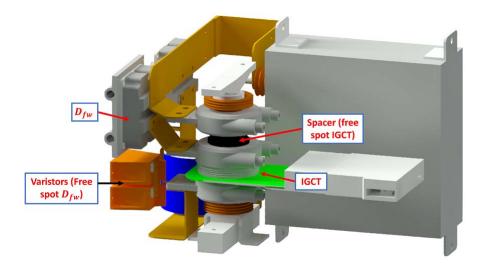

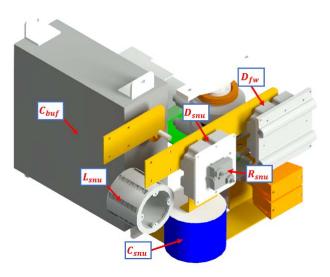

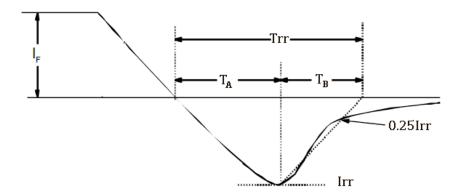

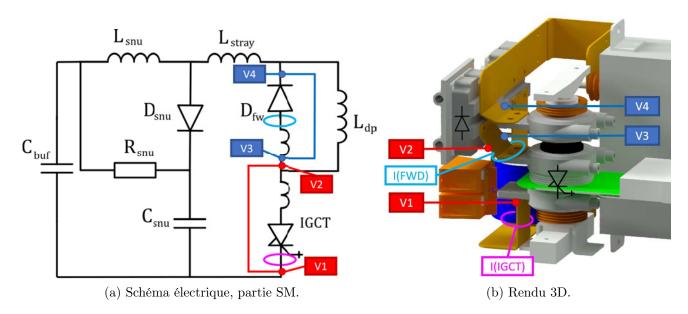

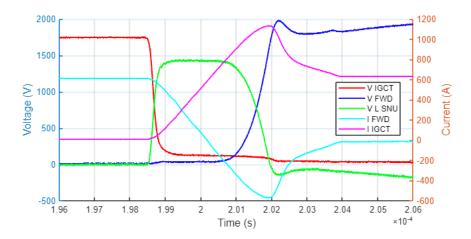

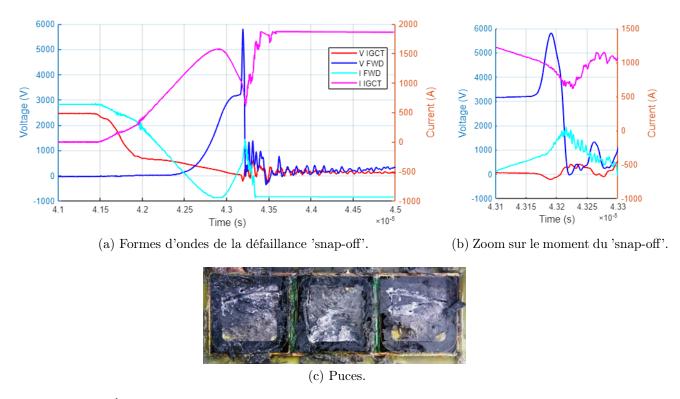

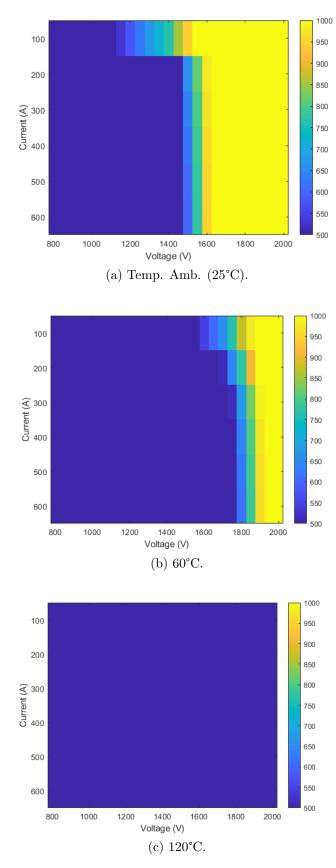

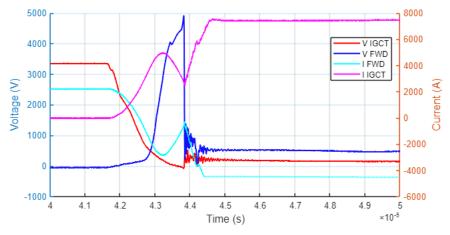

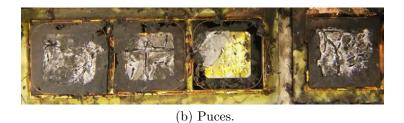

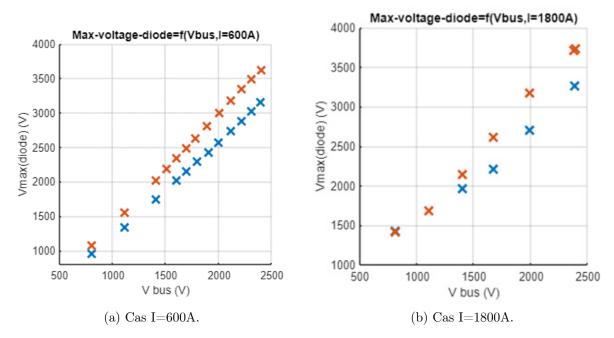

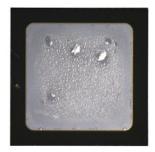

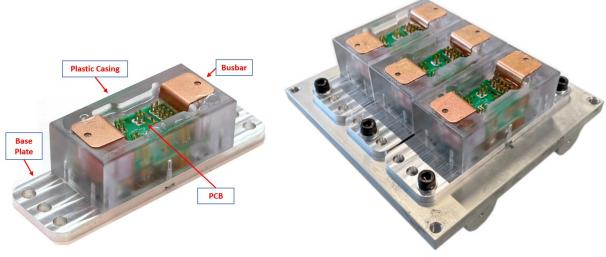

diodes, and triggered during the short-circuit. Such system allows to temporarily sustain the surge current (before the circuit breakers open), without using very large diodes which would increase switching losses due to their large recovery charge.