# Development and characterization of a thermoelectric harvester demonstrator using phonon engineered silicon membranes

Thierno-Moussa Bah

#### ▶ To cite this version:

Thierno-Moussa Bah. Development and characterization of a thermoelectric harvester demonstrator using phonon engineered silicon membranes. Micro and nanotechnologies/Microelectronics. Université de Lille, 2019. English. NNT: 2019LILUI036. tel-03622459

# HAL Id: tel-03622459 https://theses.hal.science/tel-03622459v1

Submitted on 29 Mar 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THESE**

Présentée à l'Université de Lille Ecole Doctorale des Sciences pour l'Ingénieur

Institut d'Electronique, de Microélectronique et de nanotechnologies de Lille STMicroelectronics Crolles

Pour obtenir le grade de : DOCTEUR DE L'UNIVERSITE

Spécialité: MICRO-NANO SYSTEMES ET CAPTEURS

Par

# Thierno Moussa BAH

# Développement et caractérisation d'un démonstrateur de générateur thermoélectrique à base de membranes de silicium couplées à de l'ingénierie phononique

Soutenue le 03 Juillet 2019 devant le Jury composé de :

Président du Jury Mr. Olivier BOURGEOIS, Directeur de Recherche CNRS, Institut Néel, Grenoble Rapporteur Mme. Sylvie HEBERT, Directrice de Recherche CNRS, CRISMAT, Caen Rapporteur Mme. Edith KUSSENER, Enseignant-Chercheur, ISEN-IM2NP, Toulon Examinateur Mr. Guillaume SAVELLI, Ingénieur R&D – Chef de Projets, CEA-Liten, Grenoble Examinateur Mr. Stéphane MONFRAY, Ingénieur R&D, STMicroelectronics, Crolles Co-encadrant de thèse Mr. Jean-François ROBILLARD, Enseignant-Chercheur, ISEN-IEMN, Lille Co-encadrant de thèse Mr. Thomas SKOTNICKI, Professeur, CEZAMAT-Univ. Polytech. Varsovie Co-Directeur de thèse Mr. Emmanuel DUBOIS, Directeur de recherche CNRS, ISEN-IEMN, Lille Directeur de thèse

# **THESE**

Présentée à l'Université de Lille Ecole Doctorale des Sciences pour l'Ingénieur

Institut d'Electronique, de Microélectronique et de nanotechnologies de Lille STMicroelectronics Crolles

Pour obtenir le grade de : DOCTEUR DE L'UNIVERSITE

**Spécialité: MICRO-NANO SYSTEMES ET CAPTEURS**

Par

# Thierno Moussa BAH

# Development and characterization of a thermoelectric harvester demonstrator using phonon engineered silicon membranes

Soutenue le 03 Juillet 2019 devant le Jury composé de :

| Mr. Olivier BOURGEOIS, Directeur de Recherche CNRS, Institut Néel, Grenoble | Président du Jury<br>Rapporteur |

|-----------------------------------------------------------------------------|---------------------------------|

| Mme. Sylvie HEBERT, Directrice de Recherche CNRS, CRISMAT, Caen             | Rapporteur                      |

| Mme. Edith KUSSENER, Enseignant-Chercheur, ISEN-IM2NP, Toulon               | Examinateur                     |

| Mr. Guillaume SAVELLI, Ingénieur R&D – Chef de Projets, CEA-Liten, Grenoble | Examinateur                     |

| Mr. Stéphane MONFRAY, $Ingénieur\ R\&D$ , STMicroelectronics, Crolles       | Co-encadrant de thèse           |

| Mr. Jean-François ROBILLARD, Enseignant-Chercheur, ISEN-IEMN, Lille         | Co-encadrant de thèse           |

| Mr. Thomas SKOTNICKI, Professeur, CEZAMAT-Univ. Polytech. Varsovie          | Co-Directeur de thèse           |

| Mr. Emmanuel DUBOIS, Directeur de recherche CNRS, ISEN-IEMN, Lille          | Directeur de thèse              |

#### **Mille Mercis**

Cette thèse a été effectué au sein du **l'Institut d'Electronique Microélectronique et Nanotechnologies de Lille (IEMN)** et financé par (convention CIFRE) par **STMicroelectronics Crolles** et a été possible grâce au concours de plusieurs personnes à qui je voudrais témoigner toute ma gratitude.

Je voudrais tout particulièrement adresser toute ma reconnaissance à mes directeurs de thèses, les **Dr. Emmanuel Dubois** et **Prof. Thomas Skotnicki**, ainsi qu'à mes co-encadrants, **Dr. Jean-François Robillard** et **Dr. Stephane Monfray** tout d'abord pour la confiance placée en moi en me confiant cette thématique de thèse. Mais encore plus pour leur patience, disponibilités et conseils, ... en somme pour m'avoir mis dans les meilleures conditions pour la réalisation de cette thèse.

Un grand merci aussi à Maciej Haras et Valeria Lacatena mes prédécesseurs sur cette thématique pour les travaux effectués avant et surtout pour leurs accompagnements et conseils durant mes premiers mois de thèse. Je remercie aussi le reste de l'équipe  $\mu E$  Si : Justine Philippe, Jean-Marc Boucaud, Mathieu Berthomé, Stanislav Didenko, Tianqi Zhu, Di Zhou, Jun Yin, Arun Bhaskar and Quentin Hivin pour l'aide qu'ils m'ont apporté sur l'utilisation des équipements ou la compréhension de technologies qui ne m'étaient pas familier(e)s ainsi que les suggestions et collaborations que j'ai pu effectuer avec certains d'entre eux. Un grand merci aussi à Jean-Michel Droulez qui a mis à ma disposition tous les outils informatiques indispensables à la réalisation de mes travaux et aussi à Florence Alberti pour avoir grandement facilité les différents déplacements effectués durant cette thèse, ainsi que l'organisation de la soutenance de thèse.

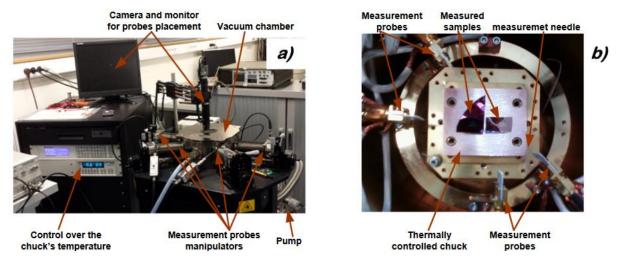

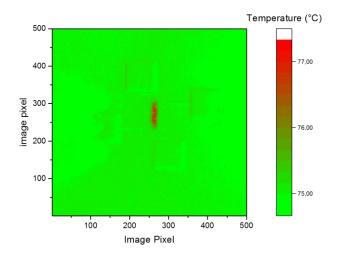

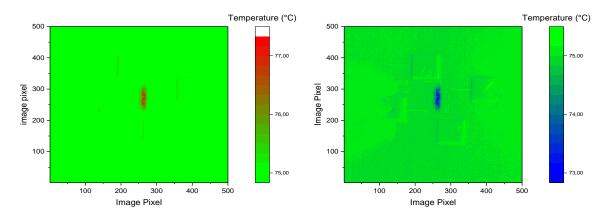

Les travaux effectués durant cette thèse et présentés dans les chapitres suivants ont été majoritairement effectués au sein de la centrale de micro et nano fabrication de l'IEMN, dont je souhaiterais remercier le directeur de l'IEMN Lionel Buchaillot et l'équipe de la centrale : François Vaurette, Marc François, Pascal Tilmant, Christiane Legrand, Dmitri Yarekha, Garrett Curley, Laurent Fugère, David Delcroix, Marc Dewitte, Annie Fattorini, Christophe Boyaval, Arnaud Pageau, Flavie Braud, Isabelle Roch-Jeune, Bertrand Grimbert et Guillaume Cochez pour les formations à l'utilisation des différents équipements qui ont été indispensables à la réalisation de mes travaux, aussi pour les opérations réalisées par leurs soins lorsque je n'en avais pas les compétences ou que les équipements n'étaient pas ouvert à tous les usagers. Après la réalisation des composants, les différentes étapes de caractérisations des composants réalisés ont été effectués au sein de la plateforme de caractérisation de l'IEMN. J'exprime ma gratitude à Sylvie Lepilliet pour son accompagnement tout au long de la caractérisation thermoélectrique des composants, Etienne Okada pour son aide lors de la réalisation des images infrarouges et son aide sur la caractérisation thermoélectrique lorsque Sylvie n'était pas disponible, ainsi que Sophie Eliet et Vanessa Avramovic.

Mes remerciements vont aussi à Fuanki Bavedila, Carlos Alberto Paragua, Malek Zegaoui, Vinay Kumar Chinni, Colin Mismer et Sara Bretin pour leurs aides « au quotidien » lorsque j'ai débuté mes travaux en centrale de micro-nano fabrication pour le développement de recettes de fabrications, l'utilisation de certains équipements. Je remercie également Adama, Kathia, Cybelle, Joao, khadim, Sidy, Boubacar, Hassimiou, Cheick, Ibrahima et Mohammed pour leur soutien, ainsi que pour m'avoir facilité l'installation sur Lille.

Enfin, Je remercie grandement ma famille, mes parents et notamment mon père **Boubacar Bah** qui malgré toutes les difficultés que cela représentait, a toujours insisté et tout mis en place afin que mes frères et moi puissions poursuivre nos études et réaliser nos ambitions. Je ne peux conclure ces remerciements, sans témoigner toute la gratitude que j'ai à l'égard de **Mr. Bernard Salvaing et toute sa famille** qui ont toujours soutenu et continuent à soutenir l'éducation de mes frères et moi.

| THESIS SUN                                                                                                                                                | 3.4.4.5.1/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| DECLIME DE                                                                                                                                                | MARY:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

|                                                                                                                                                           | TRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| HAPTER 1:                                                                                                                                                 | SILICON BASED THERMOELECTRIC HARVESTERS: PROBLEMATICS AND CHALLENGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

|                                                                                                                                                           | /IRELESS SENSORS NETWORKS AND POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

|                                                                                                                                                           | HERMOELECTRIC ENERGY HARVESTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

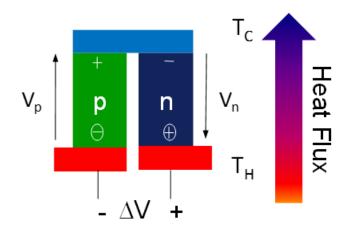

|                                                                                                                                                           | hermoelectric Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| 1.2.<br>1.2.                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| 1.2.<br>1.2.                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

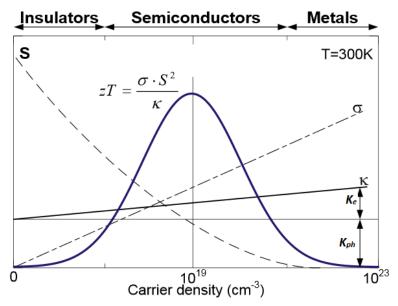

|                                                                                                                                                           | hermoelectric properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

| 1.2.2 1                                                                                                                                                   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

| 1.2.                                                                                                                                                      | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| 1.2.                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

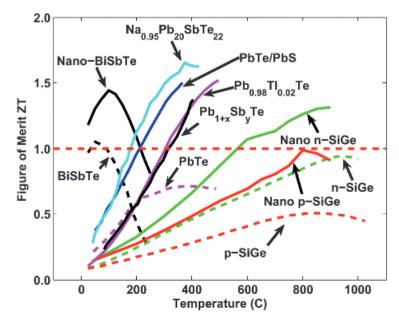

| 1.2.3 N                                                                                                                                                   | laterials choice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

|                                                                                                                                                           | LICON FOR THERMOELECTRIC HARVESTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

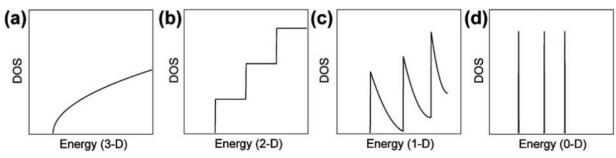

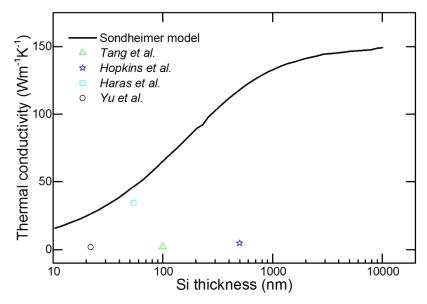

|                                                                                                                                                           | licon enhancement to an efficient thermoelectric material                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| 1.3.                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| 1.3.                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

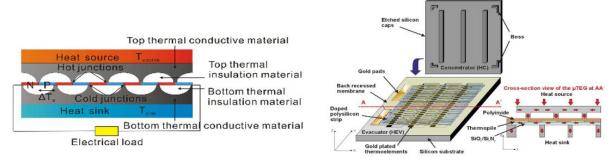

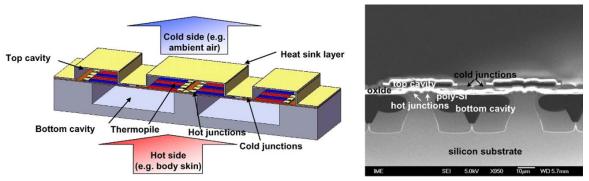

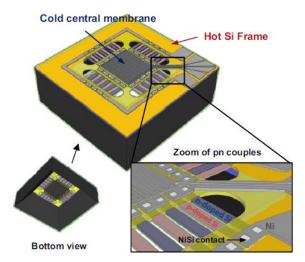

| 1.3.25                                                                                                                                                    | licon based micro-harvesters state of the art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                                       |

|                                                                                                                                                           | licon germanium based micro harvester                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

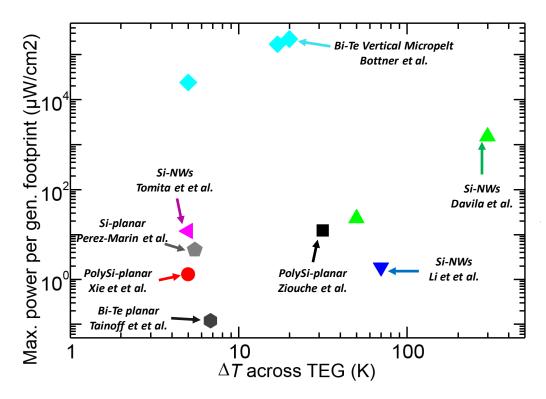

| 1.4 B                                                                                                                                                     | EST MICRO-HARVESTERS FOR NEAR ROOM TEMPERATURE APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                       |

| Conclusio                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41                                                       |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| 2.1 S                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

|                                                                                                                                                           | LICON TEG MODELING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43                                                       |

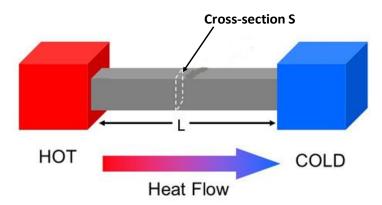

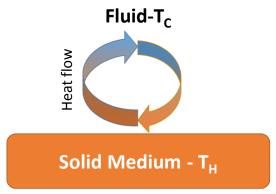

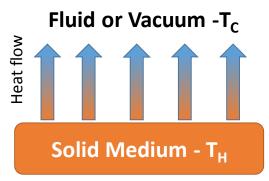

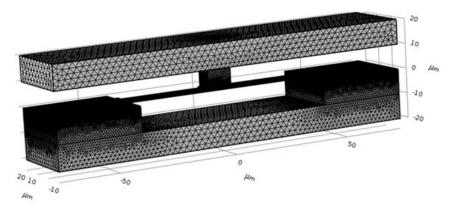

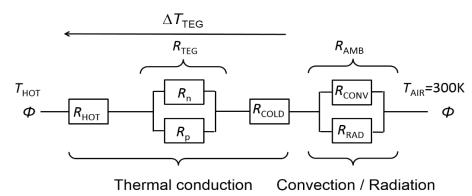

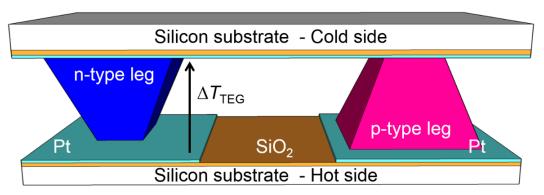

| 2.1.1 T                                                                                                                                                   | he model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43<br>44                                                 |

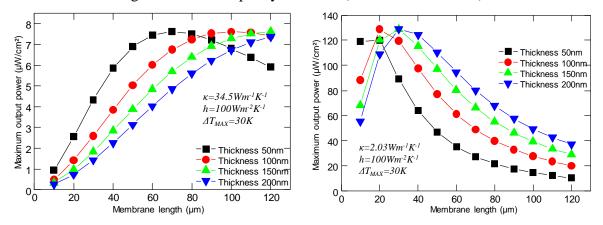

| 2.1.1 T<br>2.1.                                                                                                                                           | ne model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43<br>44<br>45                                           |

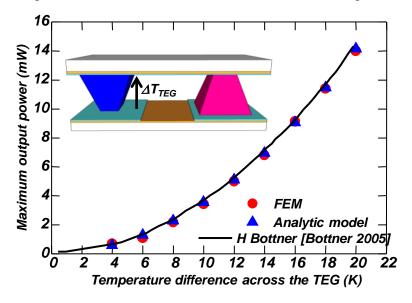

| 2.1.1 T<br>2.1.<br>2.1.                                                                                                                                   | ne model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43<br>44<br>45                                           |