# Substrate engineering using laser micromachining for improvement of RF devices and systems integrated in SOI-CMOS technology

Arun Bhaskar

## ▶ To cite this version:

Arun Bhaskar. Substrate engineering using laser micromachining for improvement of RF devices and systems integrated in SOI-CMOS technology. Micro and nanotechnologies/Microelectronics. Université de Lille, 2019. English. NNT: 2019LILUI057. tel-03622464

## HAL Id: tel-03622464 https://theses.hal.science/tel-03622464

Submitted on 29 Mar 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITE DE LILLE

Ecole doctorale : Sciences pour l'Ingénieur Laboratoire : Institut d'Electronique, de Microélectronique et de Nanotechnologie - IEMN

## THESE Présentée par

#### Arun BHASKAR

Pour obtenir le grade de Docteur de l'Université

Electronique, microélectronique, nanoélectronique et micro-ondes

# Ingénierie de substrat par micro-usinage laser pour l'amélioration des performances de composants et fonctions RF intégrées en technologie SOI-CMOS

Soutenue le 07/10/2019 devant le jury composé de :

Mme Florence GARRELIE Professeur, Université Jean Monnet, Saint-Etienne Rapporteur Mr Pierre BLONDY Professeur, Université de Limoges, XLIM Rapporteur Mr Olivier UTEZA Directeur de Recherche CNRS, LP3, Marseille Président Mme Christine RAYNAUD Marketing Manager RF Technologies, CEA-LETI, Grenoble Examinateur Mr Jean-François ROBILLARD Enseignant-Chercheur ISEN-IEMN, Lille Examinateur Mr Emmanuel DUBOIS Directeur de Recherche CNRS, IEMN, Villeneuve d'Asca Directeur de thèse Mr Christophe GAQUIERE Professeur, Université de Lille Co-directeur de thèse Mr Daniel GLORIA Ingénieur R&D STMicroelectronics, Crolles **Encadrant Industriel**

#### UNIVERSITY OF LILLE

Doctoral school : Sciences for engineering Laboratory : Institut d'Electronique, de Microélectronique et de Nanotechnologie - IEMN

## THESIS Presented by

#### Arun BHASKAR

For obtaining the grade of Doctor of University

Electronics, Microelectronics, Nanoelectronics and Microwave

## Substrate engineering using laser micromachining for improvement of RF devices and systems integrated in SOI-CMOS technology

Defended on 07/10/2019 in front of the jury composed of:

Mrs Florence GARRELIE Professeur, Université Jean Monnet, Saint-Etienne Rapporteur Mr Pierre BLONDY Professeur, Université de Limoges, XLIM Rapporteur Mr Olivier UTEZA Directeur de Recherche CNRS, LP3, Marseille Président Mme Christine RAYNAUD Marketing Manager RF Technologies, CEA-LETI, Grenoble Examinateur Mr Jean-François ROBILLARD Enseignant-Chercheur ISEN-IEMN, Lille Examinateur Mr Emmanuel DUBOIS Directeur de Recherche CNRS, IEMN, Villeneuve d'Ascq Directeur de thèse Mr Christophe GAQUIERE Professeur, Université de Lille, IEMN Co-directeur de thèse Mr Daniel GLORIA Ingénieur R&D STMicroelectronics, Crolles **Encadrant Industriel**

## Acknowledgements

I am very grateful for having got this opportunity to work on a challenging project which was multi-dimensional. I would like to thank my PhD supervisors Emmanuel, Daniel and Christophe for having constantly guided me. I have received good support and encouragement to try new ideas from all three of them. This has made the thesis a very memorable and cherished experience and I am thankful for that.

I would like to specially thank Emmanuel who had the oversight of my daily activities. His very approachable nature made it very easy for me to express my ideas and questions to him. He would always respond in an enthusiastic manner and spend adequate time to discuss the matter at hand. This constant support enabled me to stay motivated during the thesis.

It was great to work and also have social interactions with colleagues of my group over these years: Jean-François, Maciej, Valentina, Stanislav, Jean-Marc, Thierno, Quentin, Di, Tianqi, Justine, Jun, Pascale, Jean-Michel. I was also benefitted by a lot of technical help from other members of the lab. I would like to thank the cleanroom and RF characterization technical staff, Matthieu, Flavie, Etienne, and Vanessa for their valuable contributions at different phases of PhD.

Big thanks to all of my colleagues at ST Microelectronics and the RFSS team. I really liked the jovial morning coffee breaks and supportive working environment there and the team outings. A special mention of thanks to all the colleagues with their important contributions to the thesis: Cédric, Yohann, Simon, Vipin, Philippe, Jérome, Raphael.

I am in gratitude for my family who always encouraged me in my pursuits of education. Heartfelt thanks to my wife Deepthi, who has been a great source of motivation for me for well over two years now. She has enabled me to gain strength and help develop my overall personality. I would also like to express my thanks to all my good friends in Lille who I had a lot of memorable moments with: Gatien, Dev, Ragini, Ankita, Richa, Inder, Tanu, Naina, Shilpa, Piyush, Spurthi, and Ashwini.

I sincerely thank God who has given me knowledge that I have been blessed enough to receive. Heartfelt expressions of gratitude to my hero Swami Vivekananda and other great spiritual leaders whose words empower and embolden me to be who I am.

## Table of contents

| General Introduction                                                                            | 1  |

|-------------------------------------------------------------------------------------------------|----|

| Chapter 1: Synergy of laser processing and SOI technology for More than Moore advancements      | 5  |

| 1.0 Introduction                                                                                | 5  |

| 1.1 The semiconductor industry: An overview                                                     | 7  |

| 1.2 More than Moore: Introduction and recent advances                                           | 9  |

| 1.2.1 Motivation                                                                                | 10 |

| 1.2.2 SoC integration: Die level optimization                                                   | 11 |

| 1.2.3 Packaging: System level optimization                                                      | 13 |

| 1.3 Laser processing: An emerging driver for <i>More than Moore</i>                             | 17 |

| 1.3.1 The evolution of femtosecond laser                                                        | 17 |

| 1.3.2 Application of femtosecond laser processing in <i>More than Moore</i>                     | 18 |

| 1.3.2.1 Packaging and integration                                                               | 18 |

| 1.3.2.2 MEMS                                                                                    | 21 |

| 1.3.2.3 Microfluidics                                                                           | 23 |

| 1.3.2.4 Integrated photonics                                                                    | 25 |

| 1.4 SOI Technology: A platform for SoC integration                                              | 27 |

| 1.4.1 Memory and logic                                                                          | 29 |

| 1.4.2 RF/microwave circuits                                                                     | 30 |

| 1.4.3 Integrated photonic circuits                                                              | 34 |

| 1.4.4 MEMS                                                                                      | 36 |

| Concluding Remarks                                                                              | 37 |

| References                                                                                      | 39 |

| Chapter 2: Towards high-end RF electronics and laser material processing: State of t            |    |

| art                                                                                             |    |

| 2.0 Introduction                                                                                |    |

| 2.1 Micromachining of silicon                                                                   |    |

| 2.1.1 Overview of methods for silicon etching                                                   | 45 |

| 2.1.2 Femtosecond Laser processing: An unique tool for micro/nanostructuring of silicon         | 47 |

| 2.1.3 Laser micromachining: A potential candidate for high speed and large area silicon etching | 50 |

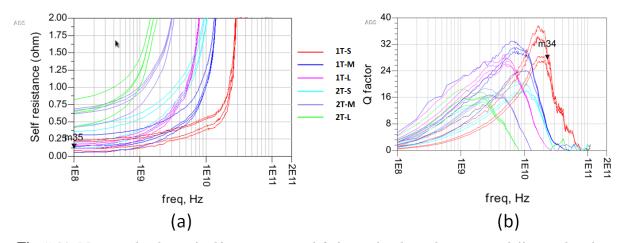

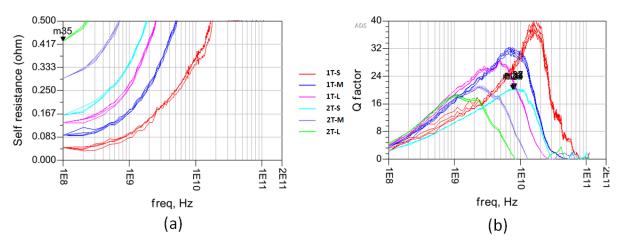

| 2.2 Inductors                                                                   | 52   |

|---------------------------------------------------------------------------------|------|

| 2.2.1 Factors affecting inductor performance                                    | 52   |

| 2.2.2 Inductors on SOI                                                          | 55   |

| 2.2.2.1 Q-factor using different substrate resistivities and BOX thickness      | 55   |

| 2.2.2.2 Inductor on commercial SOI and impact on device performance             | 57   |

| 2.2.3 Suspended inductors                                                       | 58   |

| 2.3 RF Switch                                                                   | 59   |

| 2.3.1 Overview of different implementations and technologies                    | 61   |

| 2.3.2 Performance comparison: Bulk vs. SOI                                      | 62   |

| 2.4 Low noise amplifier (LNA)                                                   | 65   |

| 2.4.1 LNA FoM: Bulk vs. SOI                                                     | 65   |

| 2.4.2 LNA performance comparison by optimization of passives                    | 66   |

| Concluding remarks                                                              | 69   |

| References                                                                      | 71   |

| Chapter 3: Laser processing applied to RF functions: Theoretical background and |      |

| experimental methodology                                                        | . 77 |

| 3.0 Introduction                                                                |      |

| 3.1 Laser processing: Essential concepts                                        |      |

| 3.1.1 Gaussian beam parameters                                                  | 79   |

| 3.1.2 Pulsed laser processing parameters                                        | 81   |

| 3.2 Laser processing: Description of physical processes and timescales          | 85   |

| 3.3 Effect of different parameters on laser processing of silicon               | 89   |

| 3.3.1 Ambient conditions                                                        | 90   |

| 3.3.1.1 Medium of ablation                                                      | 90   |

| 3.3.1.1 Substrate temperature                                                   | 91   |

| 3.3.2 Laser wavelength                                                          | 92   |

| 3.3.3 Laser pulse width                                                         | 94   |

| 3.3.3.1 Beam distortion effect                                                  | 94   |

| 3.3.3.2 Modification of ablation threshold                                      | 95   |

| 3.3.4 Polarization.                                                             | 96   |

| 3.4 Effect of ablation plume on laser processing                                | 97   |

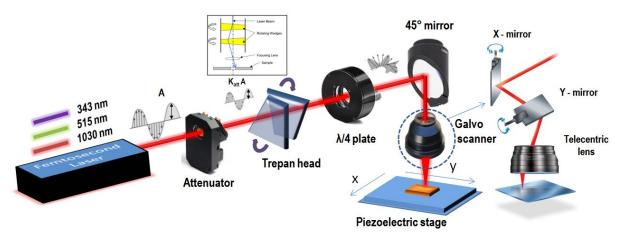

| 3.5 Laser processing: Description of system                                     | 100  |

| 3.5.1 Laser source and optics                                                   | 100  |

| 3.5.2 Optical attenuator                                                        | 101  |

| 3.5.3 Trepan head                                                               | 102  |

| 3.5.4 Galvanometric scanner                                                            | 102   |

|----------------------------------------------------------------------------------------|-------|

| 3.6 Laser processing: Experimental plan                                                | 102   |

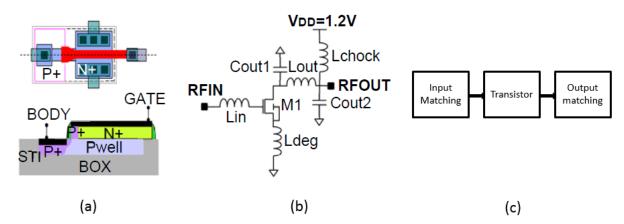

| 3.7 RF circuits: Description and theory                                                | 104   |

| 3.7.1 Isolation structures                                                             | 105   |

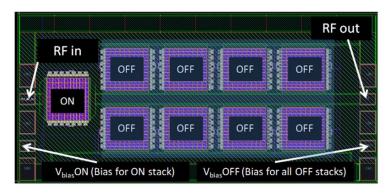

| 3.7.2 RF Switch                                                                        | 106   |

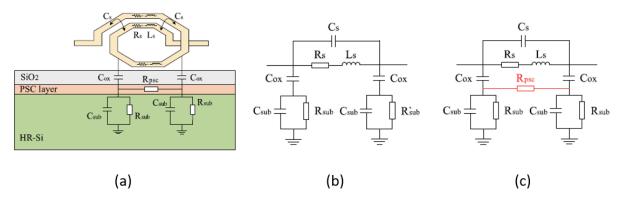

| 3.7.3 Inductors                                                                        | 108   |

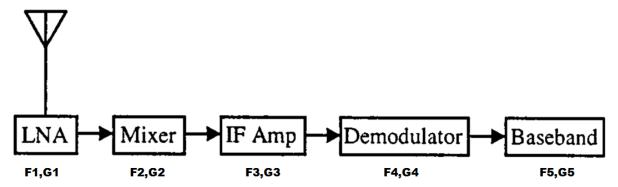

| 3.7.4 Low Noise Amplifier (LNA)                                                        | 109   |

| Conclusion                                                                             | 112   |

| References                                                                             | 113   |

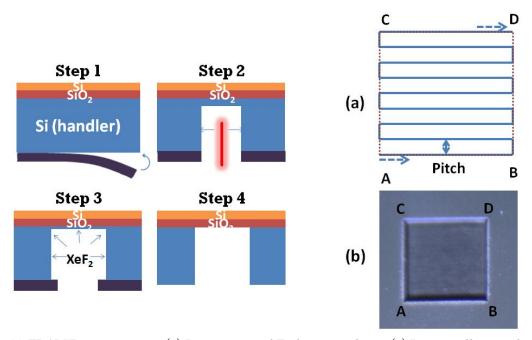

| Chapter 4: Femtosecond Laser Assisted Micromachining and Etch (FLAM).  CMOS technology |       |

| 4.0 Introduction                                                                       | 115   |

| 4.1 Determination of laser beam waist and threshold fluence                            | 117   |

| 4.2 Scribing of trenches in silicon                                                    | 119   |

| 4.2.1 Galvo stability: 343 nm and 1030 nm line                                         | 120   |

| 4.2.2 Study of trenches: 343 nm source                                                 | 121   |

| 4.2.2.1 Effect of speed                                                                | 121   |

| 4.2.2.2 Effect of fluence                                                              | 122   |

| 4.2.3 Study of trenches: 1030 nm source                                                | 123   |

| 4.2.3.1 Effect of speed                                                                | 124   |

| 4.2.3.2 Effect of fluence                                                              | 124   |

| 4.2.3 Detailed study of trench parameters for optimization of milling                  | 126   |

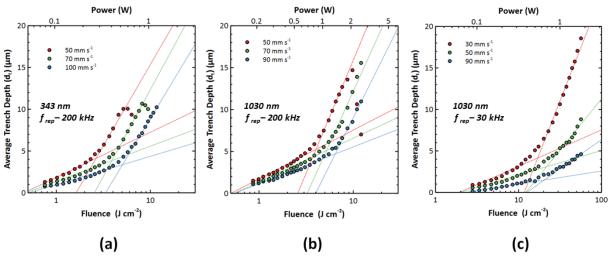

| 4.2.3.1 Average trench depth (d <sub>t</sub> )                                         | 127   |

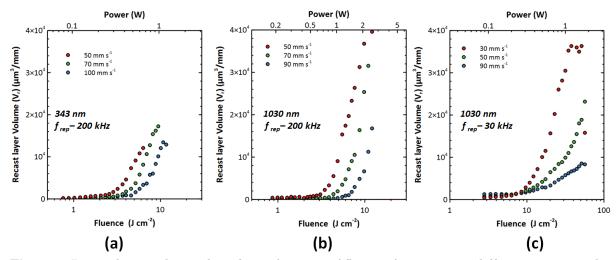

| $4.2.3.2$ Recast layer volume ( $V_r$ )                                                | 131   |

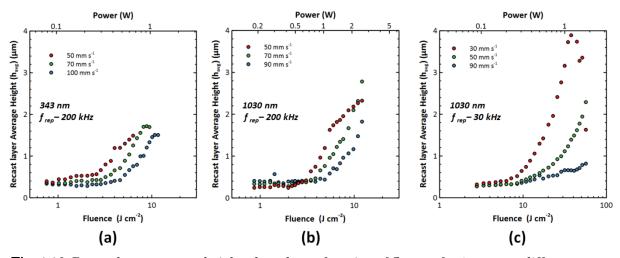

| 4.2.3.3 Recast layer average height (havg)                                             | 132   |

| 4.2.3.4 Average roughness of trench profile (R <sub>a</sub> )                          | 133   |

| 4.2.3.5 Trench width (W <sub>t</sub> )                                                 | 134   |

| 4.3 Laser milling                                                                      | 136   |

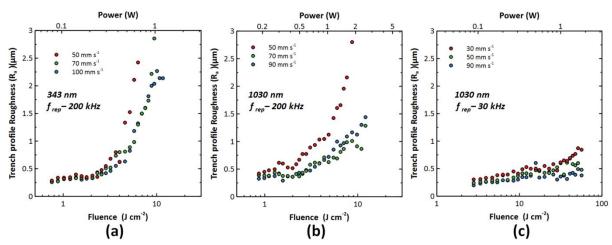

| 4.3.1 Choice of milling pitch                                                          | 136   |

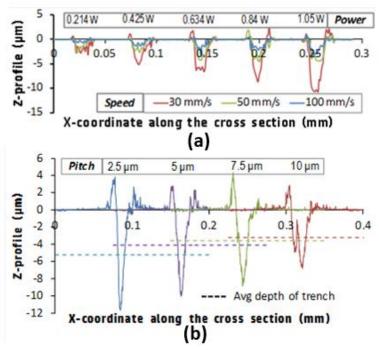

| 4.3.2 Determination of depth as a function of number of scans                          | 138   |

| 4.3.3 Effects of ablation plume and redeposition on laser milling                      | 139   |

| 4.3.3.1 Generation of particles                                                        | 140   |

| 4.3.3.2 Screening of laser radiation                                                   | 142   |

| 4.3.3 Analysis of milling quality                                                      | 146   |

| 4.4 Femtosecond Laser Assisted Micromachining and Etch (FLAME) proce                   | ss152 |

| Concluding Remarks                                           | 154 |

|--------------------------------------------------------------|-----|

| References                                                   | 155 |

| Chapter 5: FLAME membranes for high-performance RF frontends | 115 |

| 5.0 Introduction                                             | 157 |

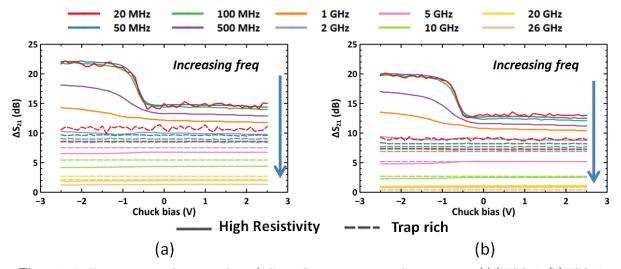

| 5.1 Isolation structures                                     | 159 |

| 5.1.1 FLAME process parameters                               | 159 |

| 5.1.2 S-parameter characterization                           | 159 |

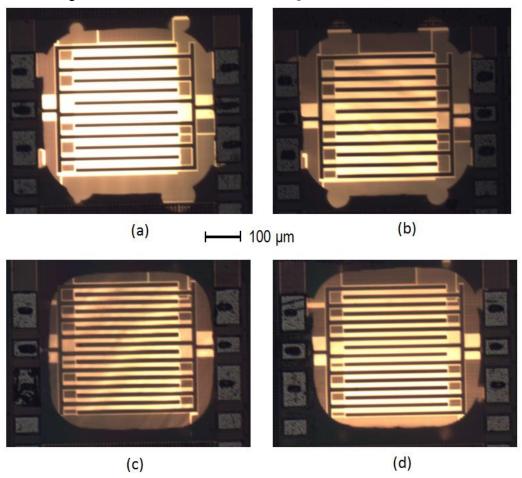

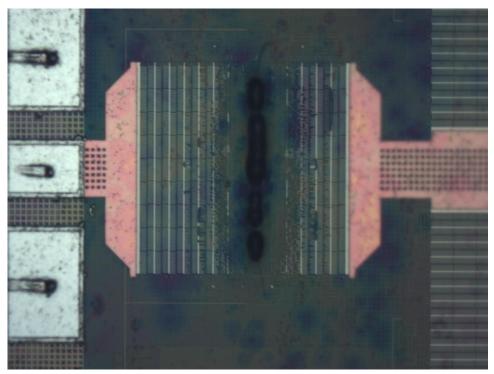

| 5.2 RF SP9T switch                                           | 163 |

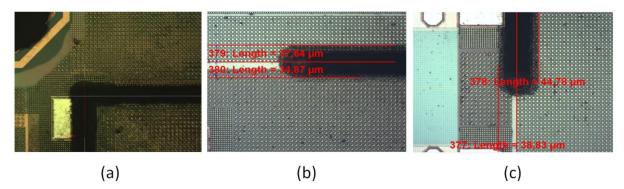

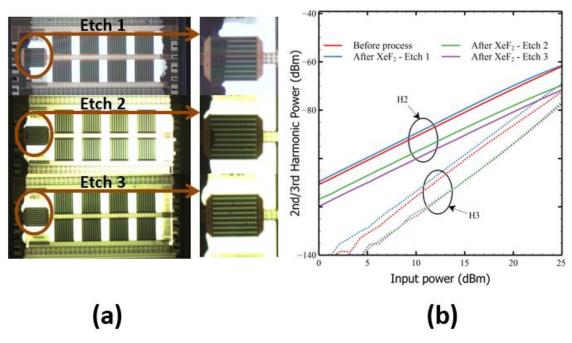

| 5.2.1 FLAME process parameters                               | 164 |

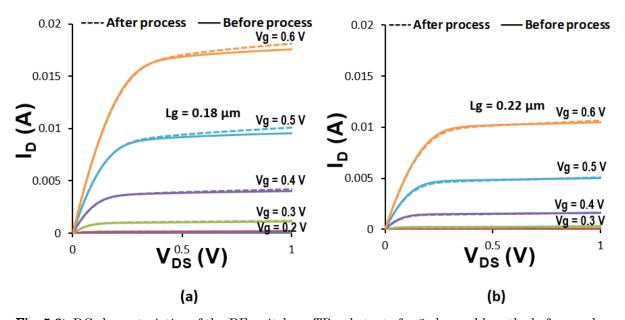

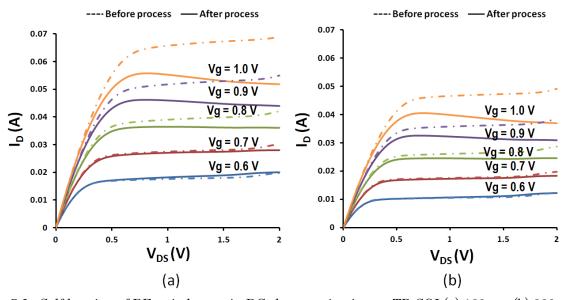

| 5.2.2 DC characterization                                    | 166 |

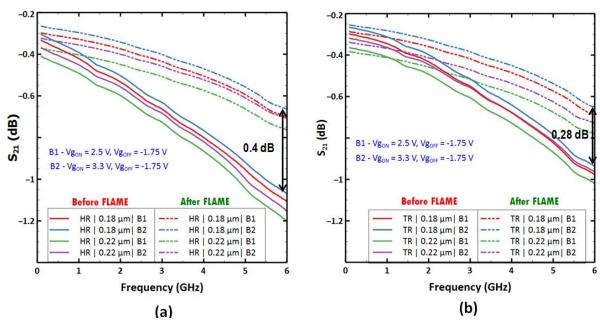

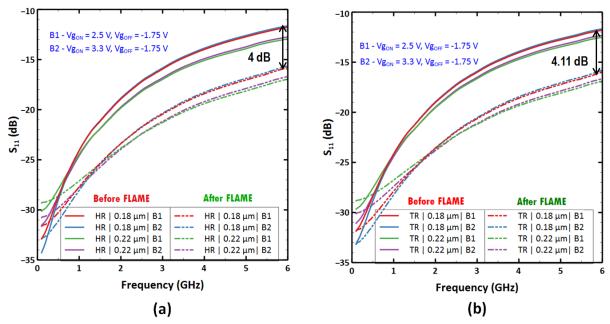

| 5.2.3 S-parameter characterization                           | 167 |

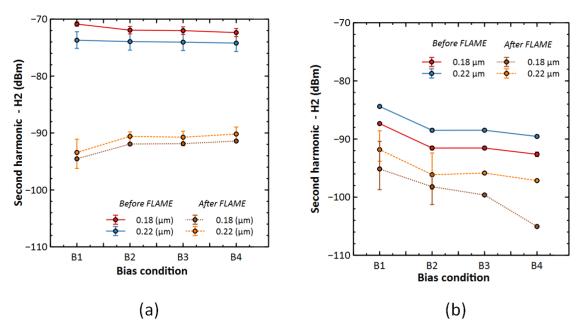

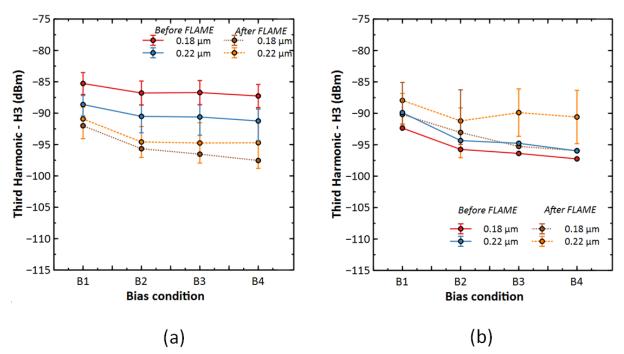

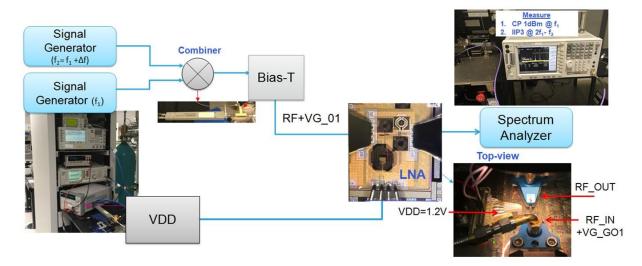

| 5.2.4 Large signal characterization                          | 170 |

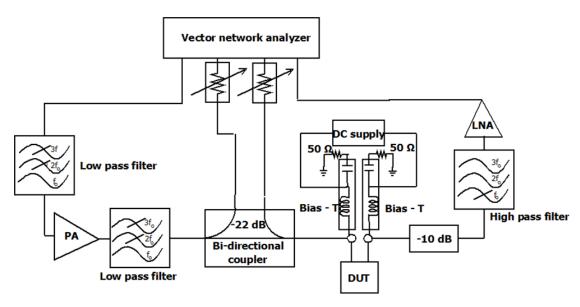

| 5.2.4.1 Measurement setup                                    | 170 |

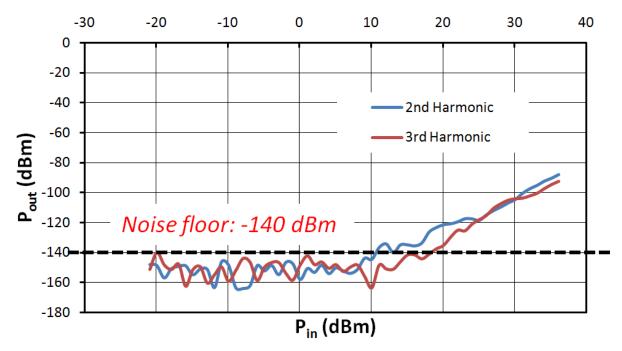

| 5.2.4.2 Results                                              | 172 |

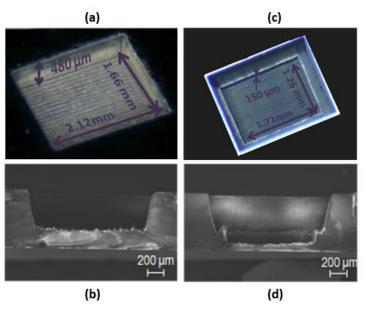

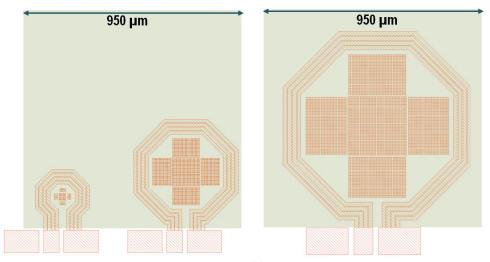

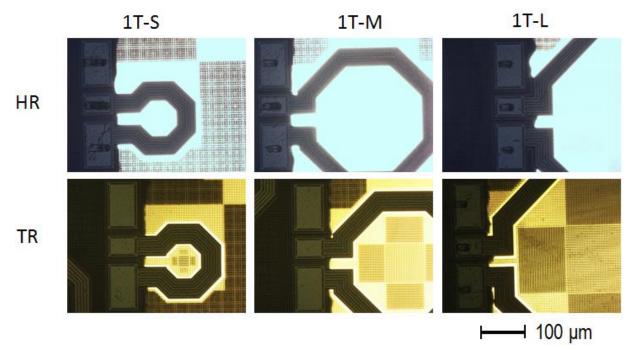

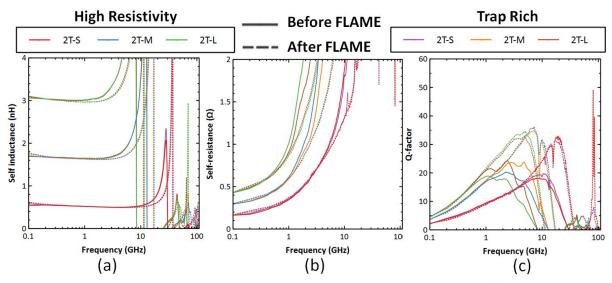

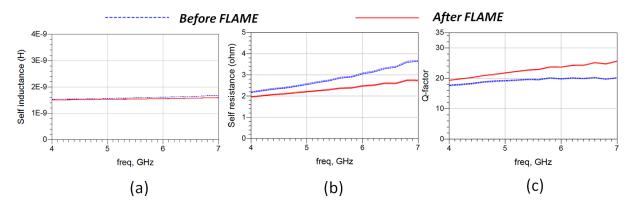

| 5.3 Inductors                                                | 176 |

| 5.3.1 FLAME process parameters                               | 176 |

| 5.3.2 S-parameter characterization                           | 177 |

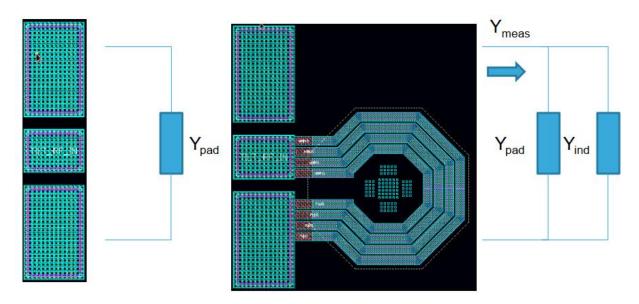

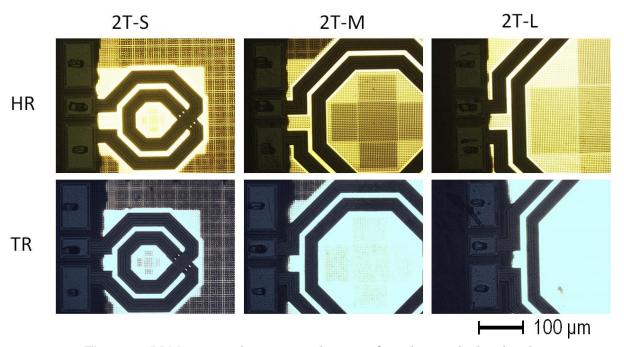

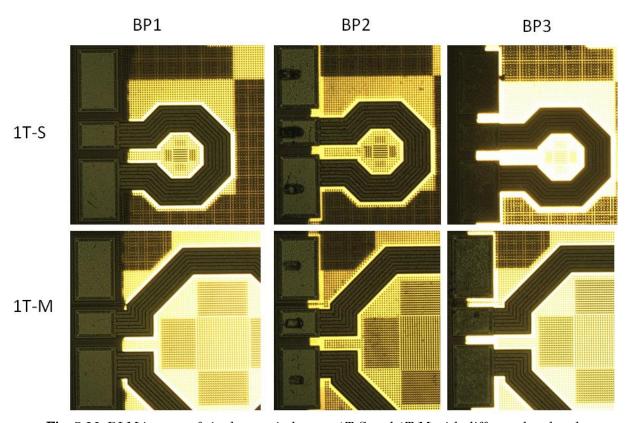

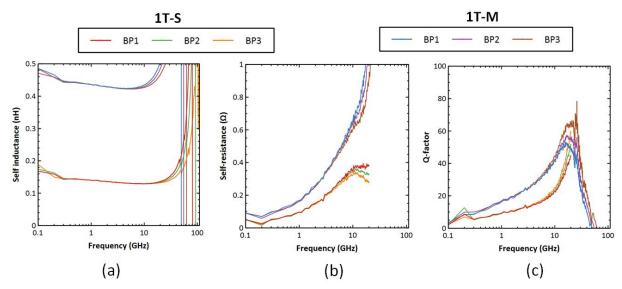

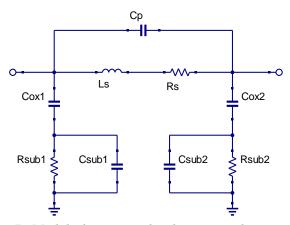

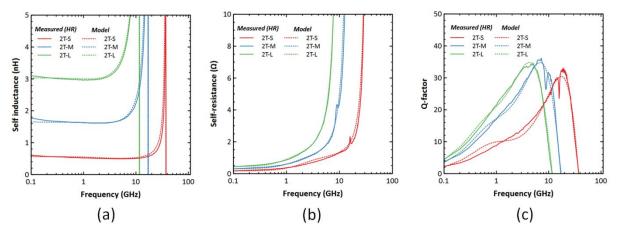

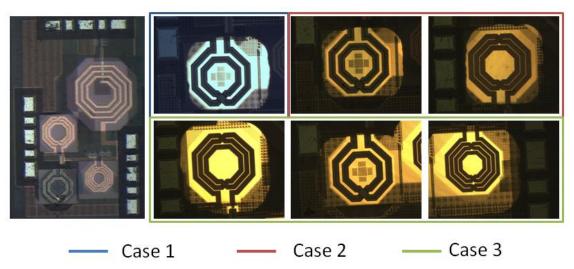

| 5.3.3 Modelling of inductors on membranes                    | 185 |

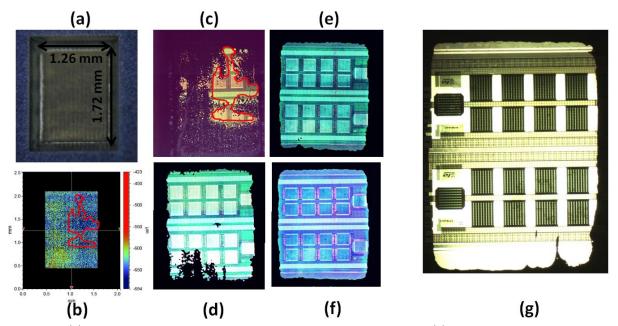

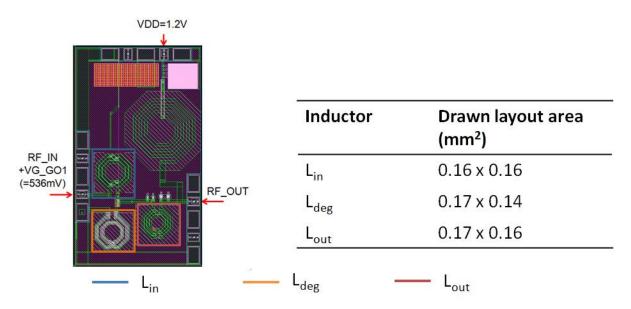

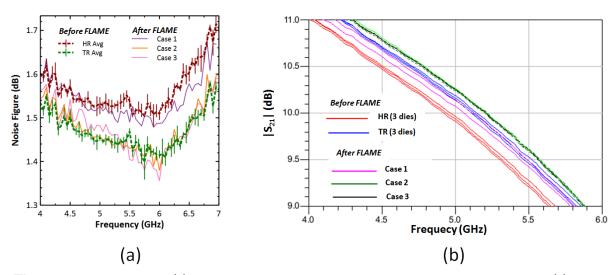

| 5.4 Low noise amplifier (LNA)                                | 189 |

| 5.4.1 FLAME process parameters                               | 189 |

| 5.4.2 Noise figure measurement                               | 190 |

| 5.4.3 Standalone input inductor measurement                  | 191 |

| 5.4.4 Linearity measurements                                 | 192 |

| Concluding Remarks                                           | 194 |

| References                                                   | 195 |

|                                                              |     |

| Conclusion and perspectives                                  | 197 |

| References                                                   | 200 |

## List of Figures

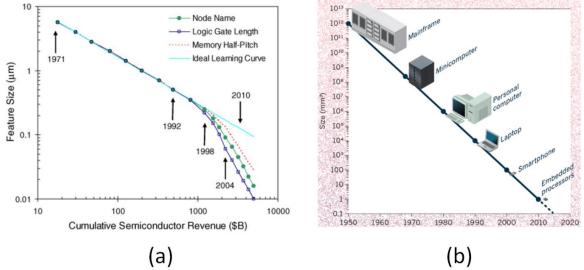

| Fig. 1.1: (a) Cumulative revenue generated as a result of continuous scaling of feature size of     |   |

|-----------------------------------------------------------------------------------------------------|---|

| semiconductor chips [3] (b) The end products of scaling at different points of time depicting the   |   |

| shift in high volume markets opened up as a result of Moore scaling [4]                             | 7 |

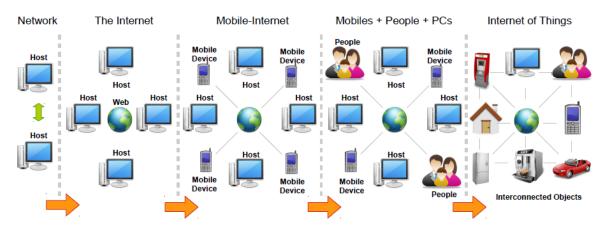

| Fig. 1.2: The emergence of different paradigms of connected devices: Beginning from local area      |   |

| networks (LAN) connecting two or more desktop stations in a localized geographical area, the        |   |

| internet was born connecting computers worldwide. Advent of social media, entertainment and         |   |

| communication platforms enabled massive entry of people on the web. The next phase that is          |   |

| emerging rapidly is the Internet of Things [11].                                                    | 3 |

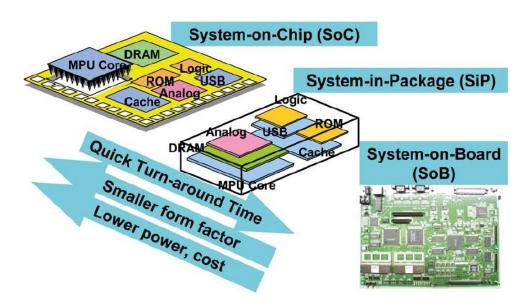

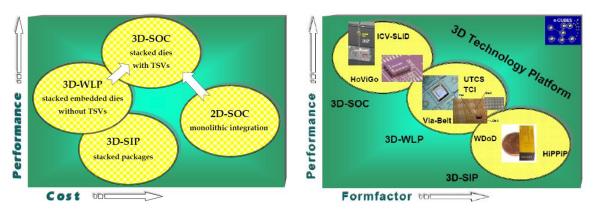

| Fig. 1.3: Schematic comparing the different methods of system integration [12]                      |   |

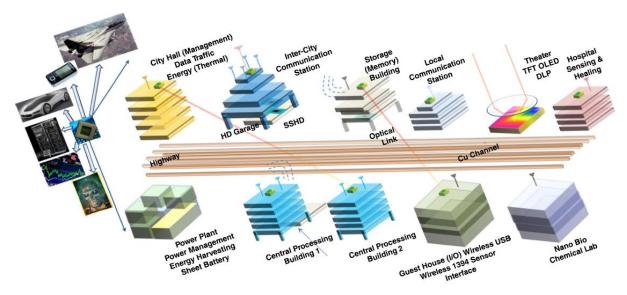

| Fig. 1.4: A real-world analogy of a system which is compared to a city. Just as different bodies of | , |

| the city need to interlink and communicate with each other, an electronic system needs to           |   |

| optimize its functioning between the interconnected components for efficiency. [13]                 | ) |

| Fig. 1.5: A comparison of different integration schemes and the tradeoffs obtained between cost,    |   |

| performance and form factor for each type of technology                                             |   |

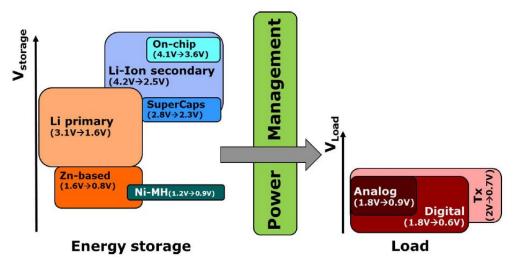

| Fig. 1.6: Power management scheme on a portable electronic device depicting the typical range of    |   |

| voltages on the storage side and the load side [14]                                                 | 2 |

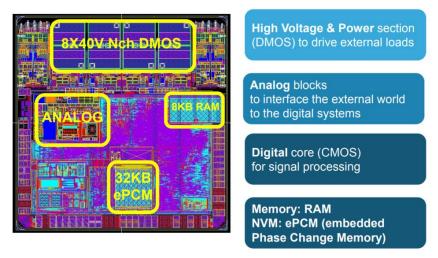

| Fig. 1.7: Chip realized on BCD platform containing digital, analog, memory and High Voltage         |   |

| blocks [15]                                                                                         | 2 |

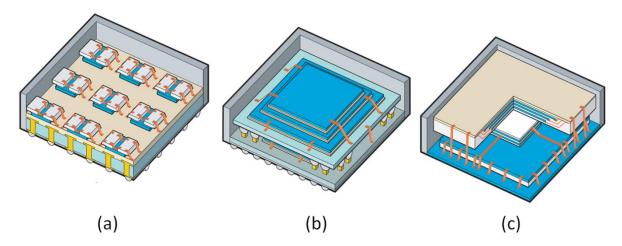

| Fig. 1.8: Different packaging integration schemes (a) SiP (b) PoP (c) PiP [16]                      | 3 |

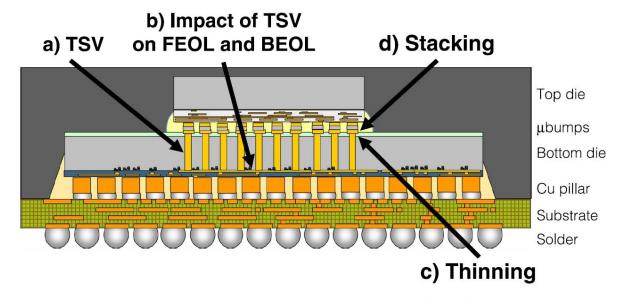

| Fig. 1.9: 3D stacking of two dies using Through-Silicon Vias (TSVs) for chip to chip                |   |

| interconnections. The four arrows point to the locations where the reliability concerns emerge in   |   |

| such a package. The final package is ready for board level integration using solder bumps           |   |

| connected to the substrate. [19]                                                                    | Į |

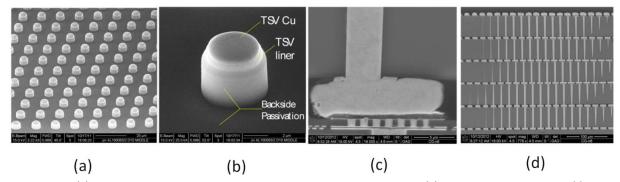

| Fig. 1.10: (a) Array of TSVs realized using via-middle process flow (b) Close-up view of via (c) Cu |   |

| interconnection by Cu-Cu TCB bonding (d) Cross section view of a 5 die stack [21]                   | 5 |

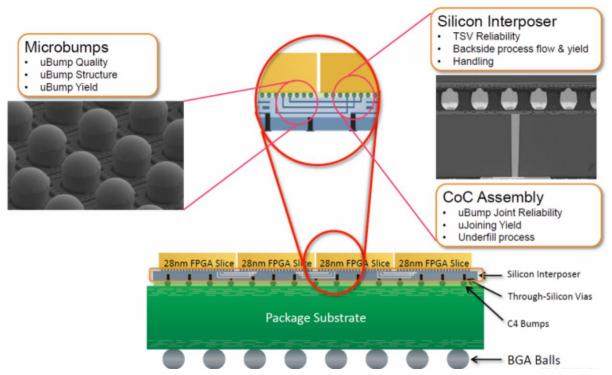

| Fig. 1.11: 2.5D packaging concept containing a silicon interposer for interconnection of dies. The  |   |

| demonstrated package here is a FPGA product developed by Xilinx [22]                                | ; |

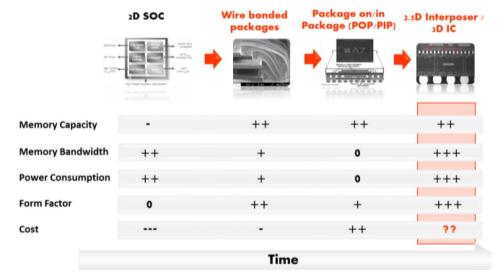

| Fig. 1.12: Comparison of different packaging technologies in terms of system performance            |   |

| metrics. [23]                                                                                       | ; |

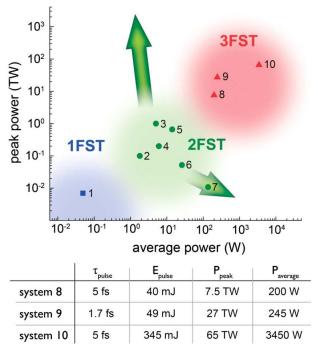

| Fig. 1.13: Comparison of 3 generations of femtosecond laser systems. Systems 1-7 have already       |   |

| been demonstrated. The systems $8-10$ were under development as of the publication date of the      |   |

| article [28]                                                                                        | 3 |

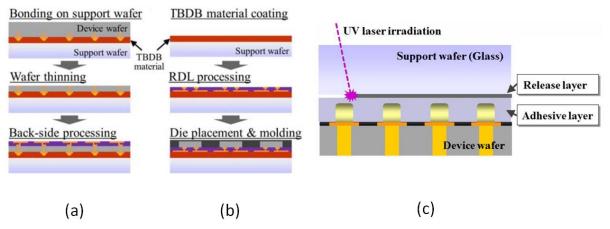

| Fig. 1.14: Use of temporary bonding in FO-WLP (a) For backside processing of wafer (b) For die      |   |

| placement and packaging (c) The release process of temporary bonding material using laser           |   |

| irradiation [31]                                                                                    | ) |

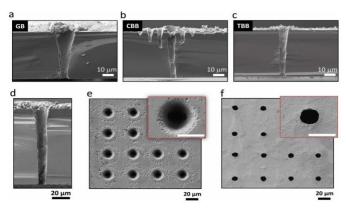

| Fig. 1.15: The use of femtosecond laser for through silicon vias (a) Gaussian beam (b)              |   |

| Conventional Bessel beam (c) Tailored Bessel beam (d) Vias in 100 µm silicon (d) Front side of      |   |

| TSV array (b) Rear side of TSV array [33]                                                           | ) |

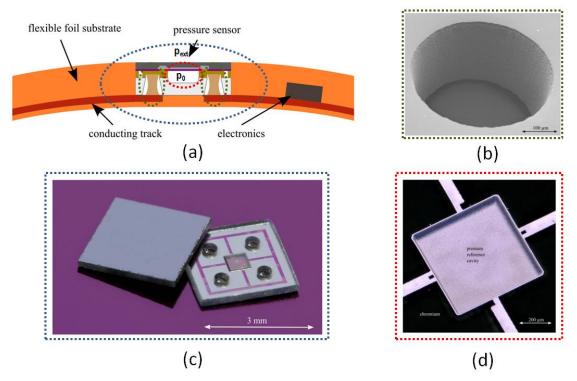

| Fig. 1.16: Surface passive pressure sensor integrated on a thin film foil (a) Finished package (b)  |   |

| TGV for sensor electrical connection (c) Bonded sensor front and back view (d) Cavity in glass to   |   |

| create chamber for pressure reference [34]                                                          | ) |

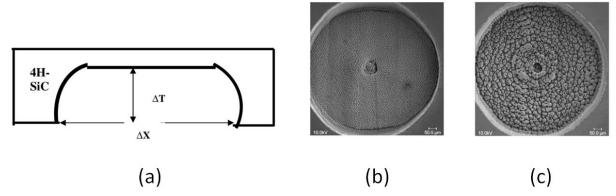

| Fig. 1.17: (a) Diaphragm in 4H-SiC substrate (b,c) SEM image of diaphragm milled with pulse         |   |

| energy 0.05 mJ and 0.15 mJ [35]                                                                     | L |

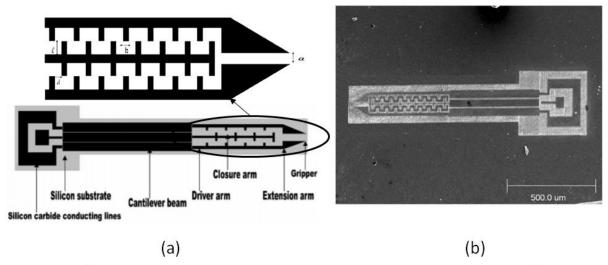

| Fig. 1.18: (a) Dimensions of the comb drive: a=20 μm, b=10 μm, l=21 μm, d=15 μm (b) SEM             |   |

| micrograph of machined microgripper [36]                                                            | 2 |

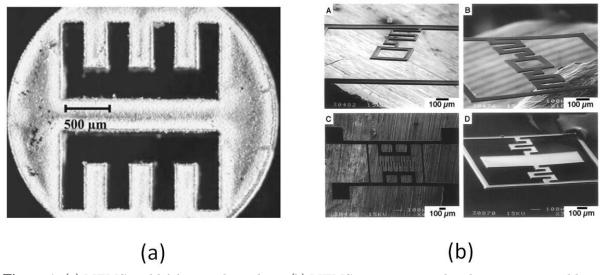

| Fig. 1.19: (a) MEMS mold fabricated in silicon (b) MEMS structures realized using micromolding      |   |

| of polymeric precursors [37], [38]                                                                  | 2 |

|                                                                                                     |   |

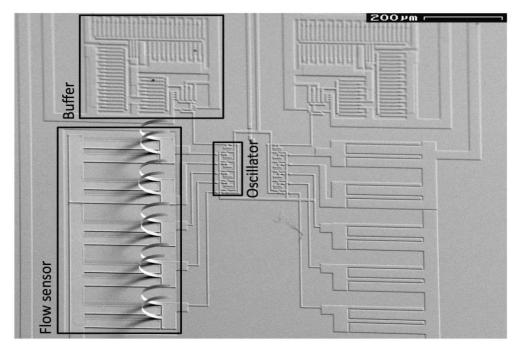

| Fig. 1.20: Micromachined MEMS cantilevers in silicon [39]                                                              |

|------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.21: (a) Micron sized particle filter using two photon polymerization (b) Filter matrix along                    |

| the microfluidic channel in fused silica using selective etching of femtosecond laser irradiated                       |

| areas in HF and KOH [40], [41]                                                                                         |

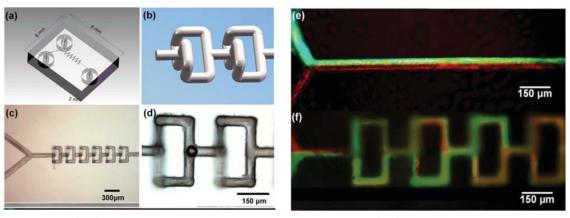

| Fig. 1.22: (a,b) Microfludic mixer schematic in fused silica (c,d) Microscope images of inscribed                      |

| mixing channels (e,f) Fluorescence microscopy to quantify mixing [42]                                                  |

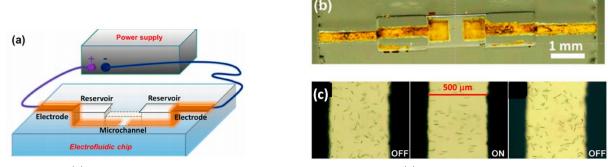

| Fig. 1.23: (a) Electrofluidic chip schematic with external supply (b) Fabricated electrofluidic chip                   |

| containing two electrodes which are baised using external supply (c) The alignment of Euglena                          |

| affected in the presence of external field. Turning off the field restores the random orientation of                   |

| cells [43]                                                                                                             |

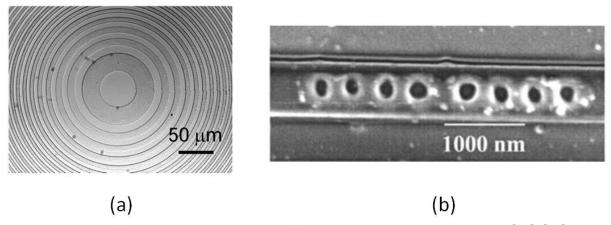

| Fig. 1.24: (a) BFL fabricated on PMMA (b) 1D photonic crystal on sapphire [45], [46]                                   |

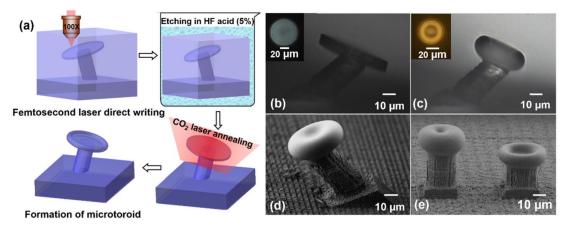

| Fig. 1.25: Fabrication of 3D high-Q resonator in fused silica with SEM images (a) Sequence of                          |

| steps (b) After laser direct write and HF etch (c) After laser annealing (d) Resonator with tilted                     |

| angle (e) Vertical resonator with different heights [47]                                                               |

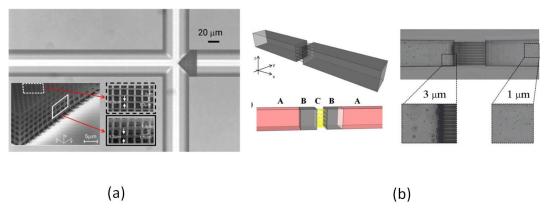

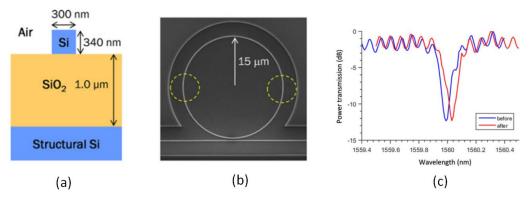

| Fig. 1.26: (a) Cross-sectional view of microring resonator (b) SEM image of the resonator (c)                          |

| Transmission characteristics of the resonator [48]                                                                     |

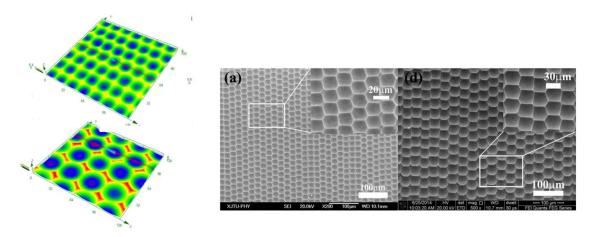

| Fig. 1.27: Large area microlens array fabricated on thin film silicon with average diameter (a) 20                     |

| μm (b) 30 μm with corresponding depth profiles shown on the left[49]                                                   |

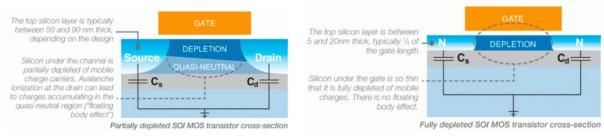

| Fig. 1.28: Transistor configurations for PD-SOI and FD-SOI [51]                                                        |

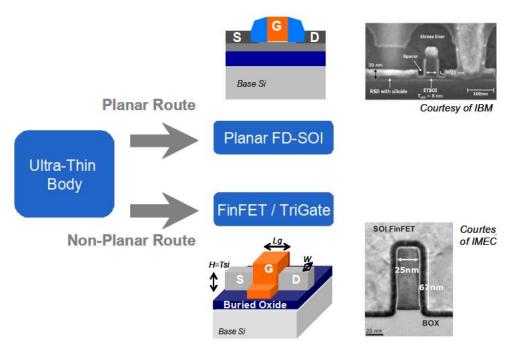

| Fig. 1.29: Ultra thin body scaling routes for FDSOI technology [52]                                                    |

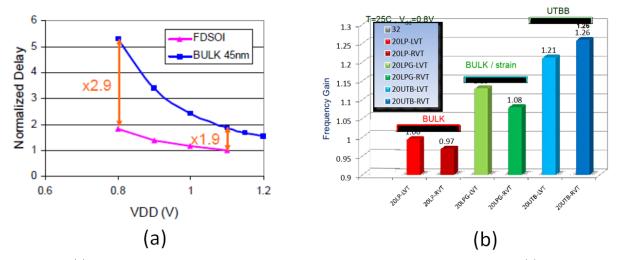

| Fig. 1.30: (a) SPICE simulation 16-bit adder circuit on bulk and FDSOI technology (b) Frequency                        |

| gain measured for LVT (low threshold voltage) and RVT (regular threshold voltage) for regular                          |

| bulk, strain engineered bulk and FDSOI technologies [52]                                                               |

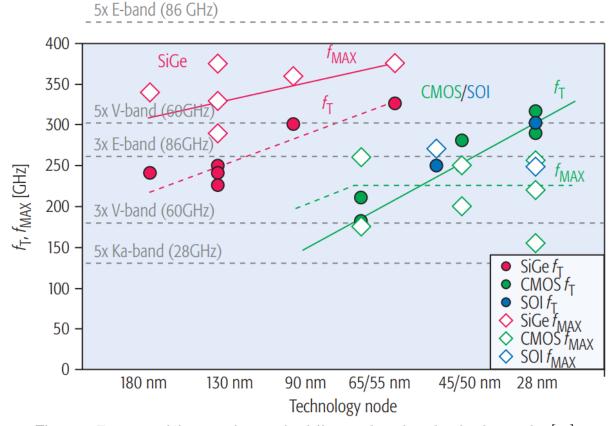

| Fig. 1.31: Transistor f <sub>t</sub> /f <sub>max</sub> specification for different silicon based technology nodes [55] |

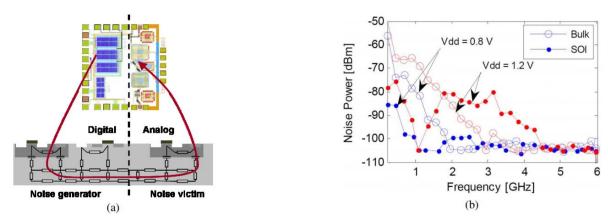

| Fig. 1.32: (a) Schematic of DSN measurement showing 8 inverter chains on digital side (b)                              |

| Measured noise power on the analog side at two different supply voltages [60]                                          |

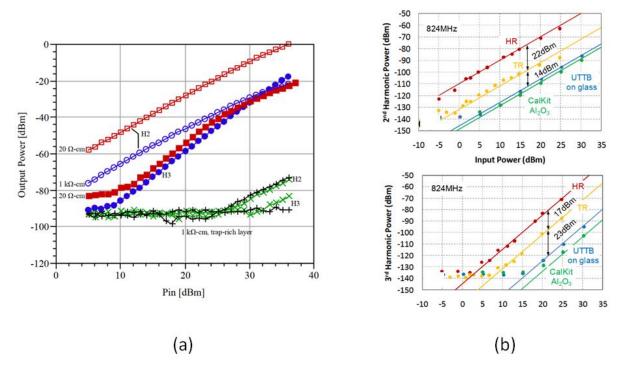

| <b>Fig. 1.33:</b> Linearity of a coplanar waveguide measured for different substrate types with                        |

| transmission line of length (a) 2.1 mm (b) 1 mm [61], [62]                                                             |

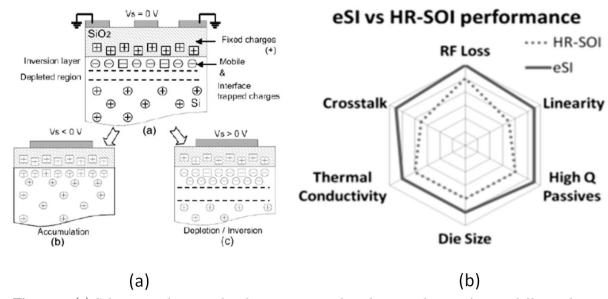

| <b>Fig. 1.34:</b> (a) Schematic showing the charge state at the silicon oxide interface at different bias              |

| conditions (b) Performance comparison between eSi and HR-SOI substrate [64]                                            |

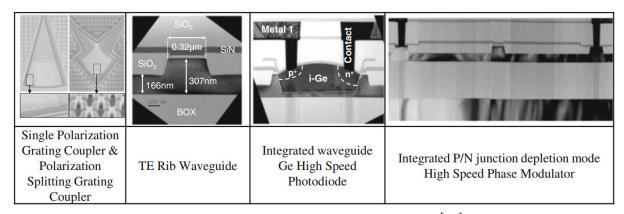

| Fig. 1.35: Optical functions on SOI substrate [67]                                                                     |

| Fig. 1.36: Mach Zehnder Interferometer and optical switch [69]                                                         |

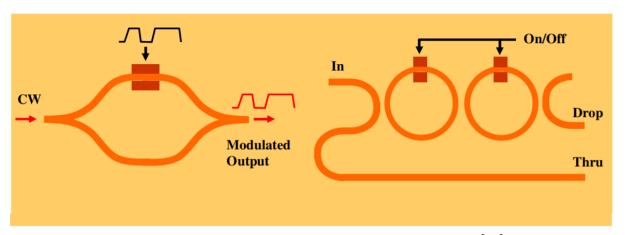

| Fig. 1.37: Pressure sensors on SOI membranes (a) N-MOSFET suspended on membrane of area                                |

| $250 \times 400 \mu\text{m}^2$ (b) A current source suspended on the edge of the membrane [71]                         |

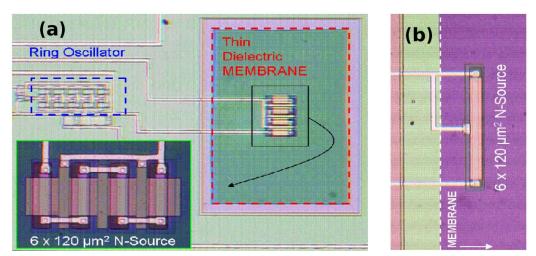

| Fig. 1.38: Self assembled 3D MEMS structures using CMOS compatible processes for temperature                           |

| and flow sensing applications [71]                                                                                     |

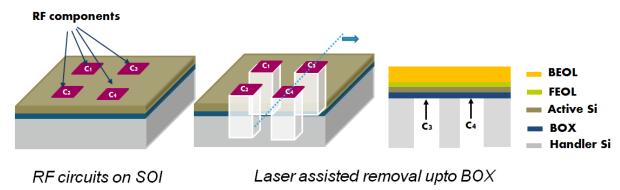

| Fig. 1.39: A route for RF performance enhancement by making use of local substrate removal for                         |

| alleviation of substrate effects                                                                                       |

|                                                                                                                        |

|                                                                                                                        |

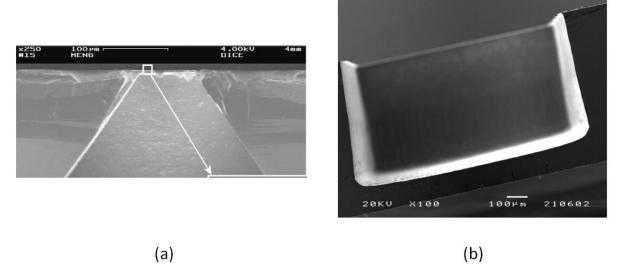

| Fig. 2.1: Example of macro-sized cavities etched in silicon using (a) TMAH: Etch Rate $-1.2~\mu m$                     |

| $min^{-1}$ [8] (b) Advanced silicon etching ,a variant of Bosch process: Etch Rate $-15~\mu m~min^{-1}$ [9]. 46        |

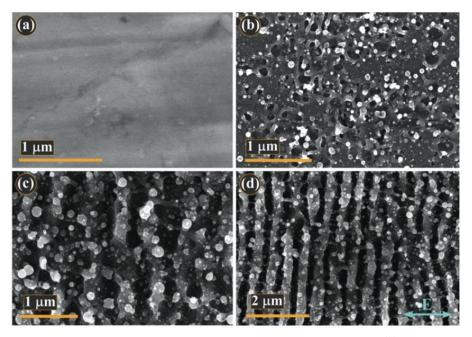

| Fig. 2.2: LIPSS on Titanium illustrated with SEM images taken after (a) Initial surface (b) 2                          |

| shots (c) 10 shots (d) 40 shots [10]                                                                                   |

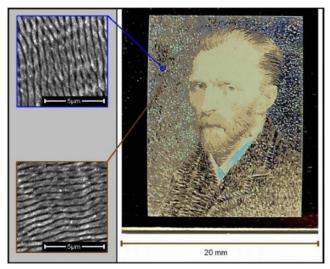

| Fig. 2.3: Color printing on stainless steel using LIPSS [11]                                                           |

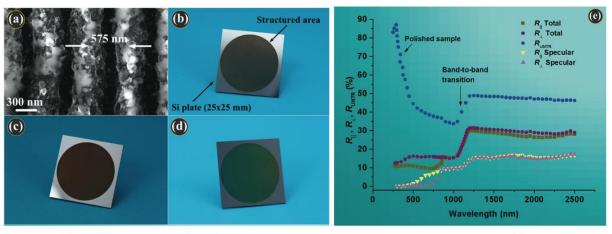

| Fig. 2.4: (a) LIPSS on silicon (b,c,d) Structured silicon views from different angles (e) Reflectance                  |

| measurements of microstructured silicon                                                                                |

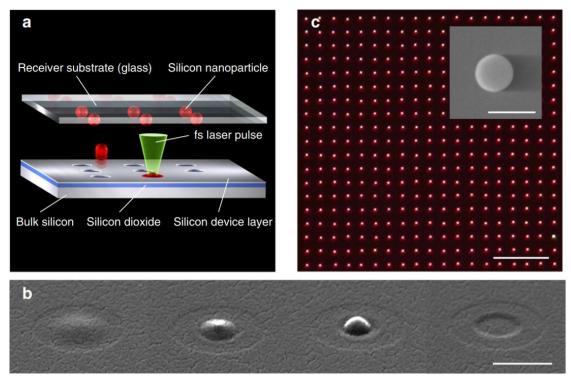

| Fig. 2.5: (a) Method of fabrication of nanoparticles array by ejecting nanoparticles from a parent                     |

| substrate to a host substrate (b) SEM images showing the formation of nanoparticle with the                            |

| application of higher laser fluences (c) Nanoparticle array fabricated on glass substrate with the                     |

| inset showing a single nanoparticles [15]                                                                              |

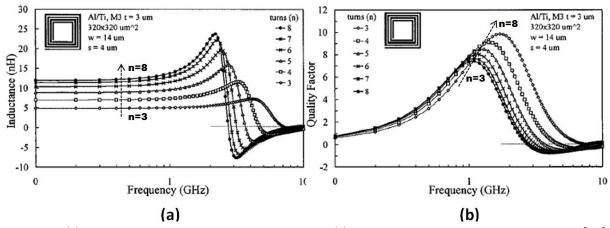

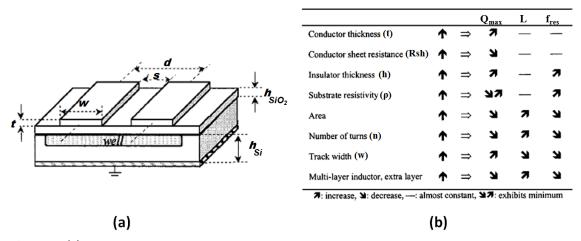

| _     | <b>2.8:</b> (a) Characteristic dimensions of an inductor showing segments of two neighbouring s (b) Variation of inductance, maximum quality factor and resonance frequency with                |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| varia | ation in different dimensions and design of the inductor [24]                                                                                                                                   |

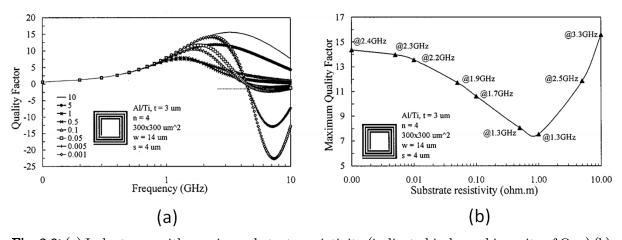

| Fig.  | <b>2.9:</b> (a) Inductance with varying substrate resistivity (indicated in legend in units of $\Omega$ .m)                                                                                     |

| Q-fa  | ctor for varying substrate resistivity [24]                                                                                                                                                     |

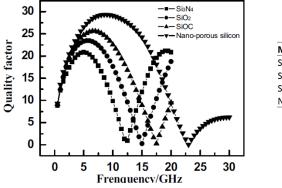

| Fig.  | 2.10: Quality factor obtained for the use of different dielectrics [26]                                                                                                                         |

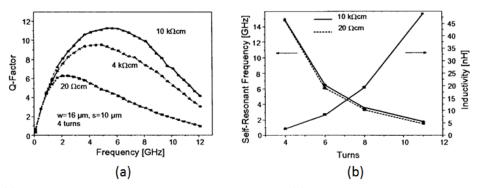

|       | 2.11: (a) Q-factor for different substrate resistivities (b) Self-resonance and inductance va                                                                                                   |

| for d | ifferent substrate resistivities [27]                                                                                                                                                           |

| Fig.  | 2.12: (a) Q-factor obtained for varying thickness of oxide layer (b) Inductance values obtain                                                                                                   |

| on b  | alk Si wafers with a oxide thickness of 25 μm [26], [28]                                                                                                                                        |

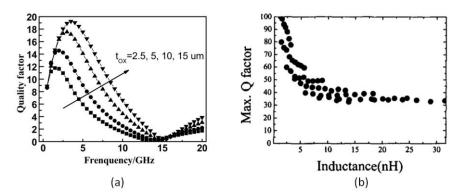

| Fig.  | 2.13: (a)Parallel stacking of metal lines to improve Q factor (b) Cross section of the induct                                                                                                   |

|       | -factor curves for varying number of parallelly stacked metal lines indicated in paranthes $(30-20 \ \Omega.cm)$ and HRS (>300 $(2.cm)$ ) substrate types. [29]                                 |

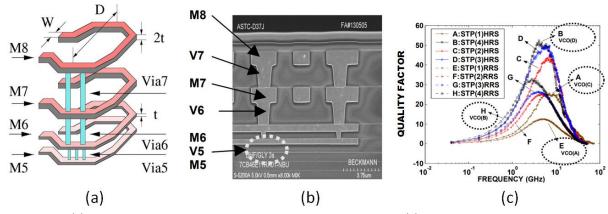

| Fig.  | <b>2.14:</b> (a) VCO circuit containing parallel LC tank circuit (b) Phase noise measured for                                                                                                   |

| _     | rent VCOs with varying Q-factor values (A) VCO-IV: $Q = 52,4$ -metal HRS (B) VCO-III: $Q$                                                                                                       |

| 22, 1 | -metal HRS (C) VCO-II: Q = 30, 4-metal RRS (D) VCO-I: Q = 11, 1-metal RRS                                                                                                                       |

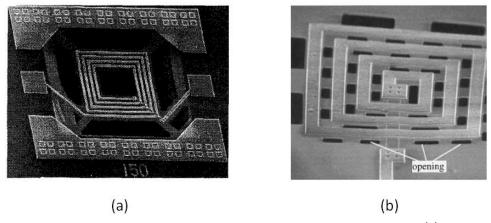

| Fig.  | 2.15: SEM micrographs of micromachined inductors on silicon showing (a) Full removal o                                                                                                          |

| subs  | trate (b) Partial removal of substrate [30], [31]                                                                                                                                               |

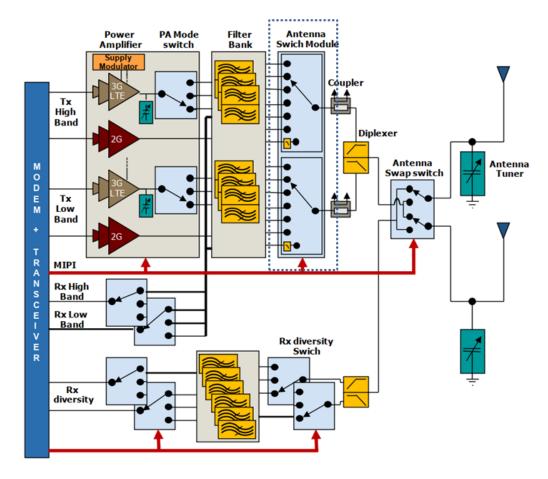

| Fig.  | 2.16: Front end module components for LTE with switch module outlined                                                                                                                           |

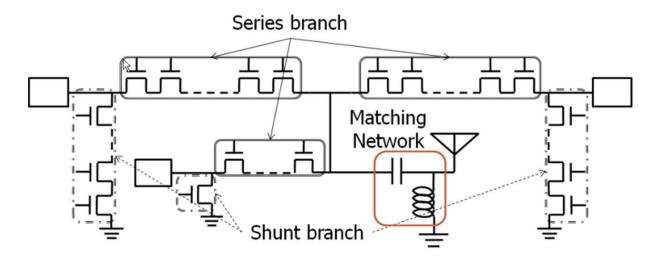

| Fig.  | 2.17: Series shunt implementation of the switch showing transistor stacking in the series                                                                                                       |

| shur  | t branches                                                                                                                                                                                      |

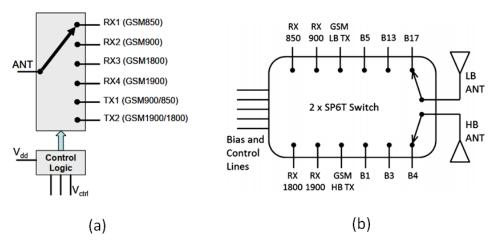

| Fig.  | 2.18: Examples of implementation of switch on SOI technology (a) S96T: GSM only (b)                                                                                                             |

| 2xSI  | P6T: GSM and LTE support [47], [48]                                                                                                                                                             |

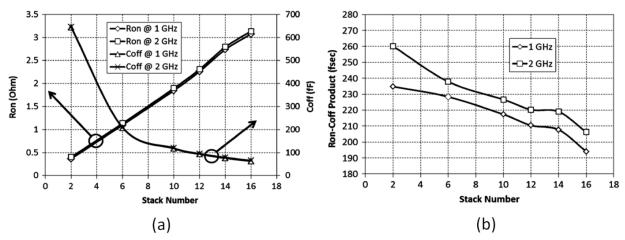

| Fig.  | <b>2.19:</b> (a) $R_{on}$ and $C_{off}$ as a function of stack number (b) $R_{on}$ * $C_{off}$ product as a function of sta                                                                     |

|       | ber. The switch is fabricated on 0.18 μm thin-film SOI technology [47]                                                                                                                          |

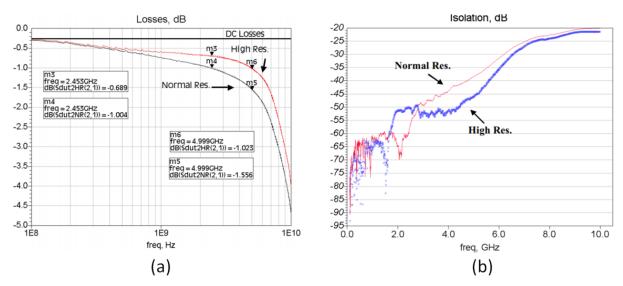

| _     | <b>2.20:</b> Switch characteristics comparison of bulk vs. SOI SPDT switch on 0.25 μm CMOS                                                                                                      |

| -     | ess (a) Insertion loss (b) Isolation [57]                                                                                                                                                       |

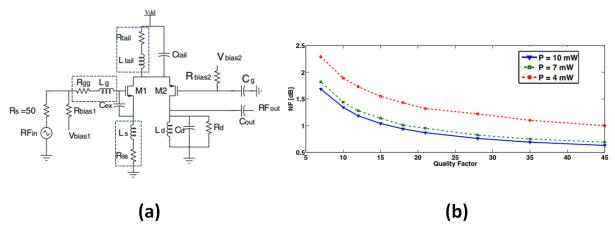

| _     | <b>2.21:</b> (a) Folded cascode architecture with outlined circuit components representing the                                                                                                  |

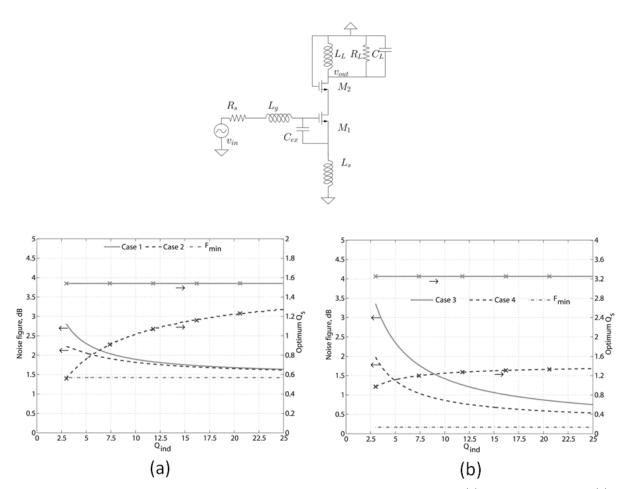

|       | rent inductors tuned in the design (b) Noise figure as a function of quality factor [73]                                                                                                        |

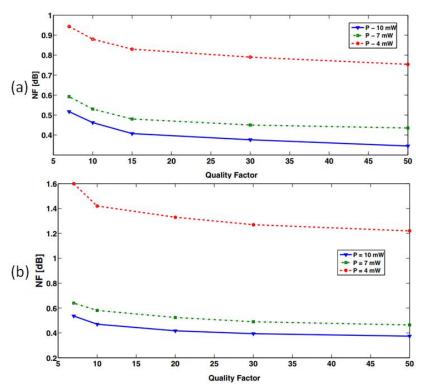

|       | <b>2.22:</b> Effect of (a) source degeneration and (b) tail inductor on noise figure of LNA circuit                                                                                             |

|       |                                                                                                                                                                                                 |

|       | 2.23: Effect of gate inductor quality factor on noise performance for (a) Constrained gain (                                                                                                    |

| Cons  | strained power optimization [22]                                                                                                                                                                |

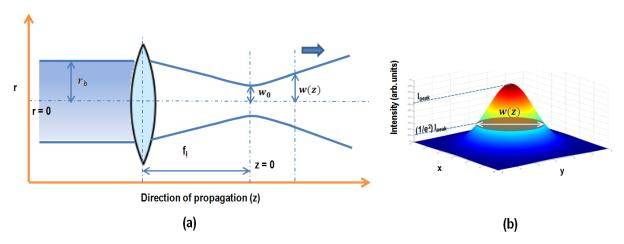

| Fig.  | 3.1: Gaussian beam description showing (a) the variation of beam width along the                                                                                                                |

|       | agation direction (b) The radial distribution of intensity at an arbitrary z-position                                                                                                           |

|       | <b>3.2:</b> Overlap of pulse energy between successive pulses shown for displacement along a                                                                                                    |

| _     | e direction of translation. The markers at $x = 0$ shows the fluence contributions from                                                                                                         |

|       | ious pulses and future pulses                                                                                                                                                                   |

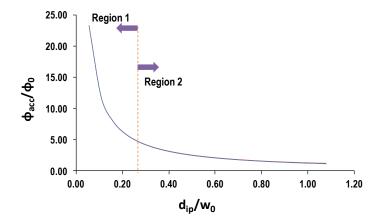

| -     | 3.3: Dependence of accumulated fluence on the ratio of interpulse distance and beam wais                                                                                                        |

|       | ring regions of high sensitivity (region 1) and low sensitivity (region 2)                                                                                                                      |

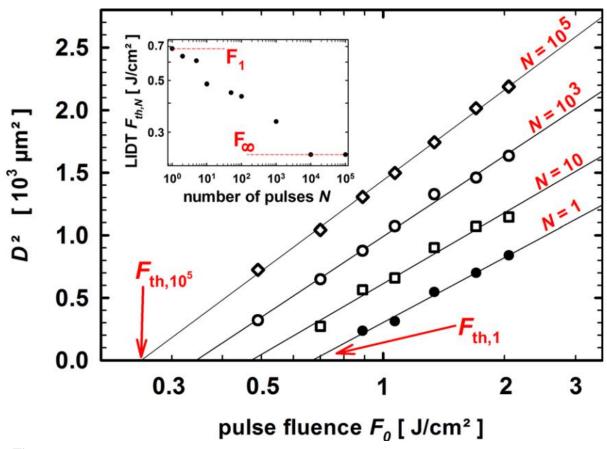

|       | 3.4: Squared diameter of crater plotted as a function of pulse fluence to estimate threshol                                                                                                     |

| _     | ace for different number of pulses on TiO <sub>2</sub> at repetition rate of 1 kHz. The inset shows the                                                                                         |

|       | nated threshold values as a function of number of pulses. [3]                                                                                                                                   |

| estir | ±                                                                                                                                                                                               |

|       | 3.5: Schematic representation of interaction between the electronic and lattice systems fo                                                                                                      |

| Fig.  | <b>3.5:</b> Schematic representation of interaction between the electronic and lattice systems fo to to second laser (b) Nanosecond laser (c) Normalized temperature profiles obtained for copy |

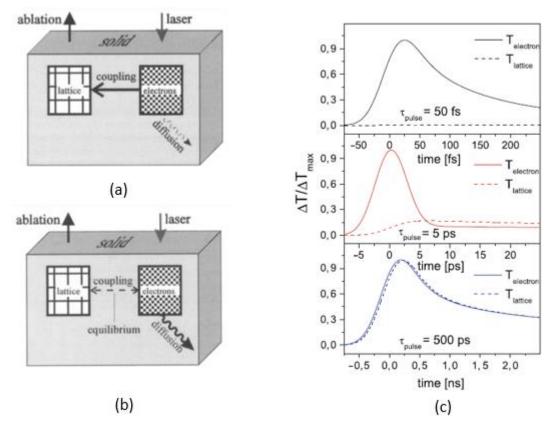

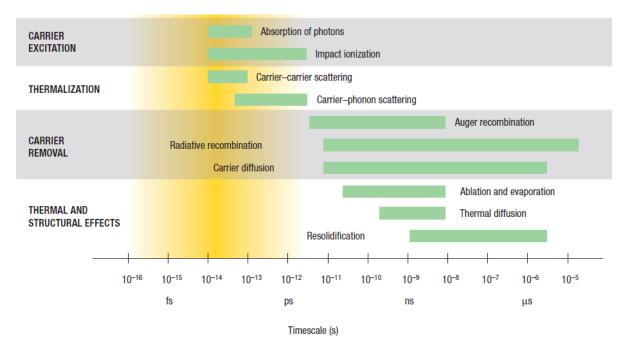

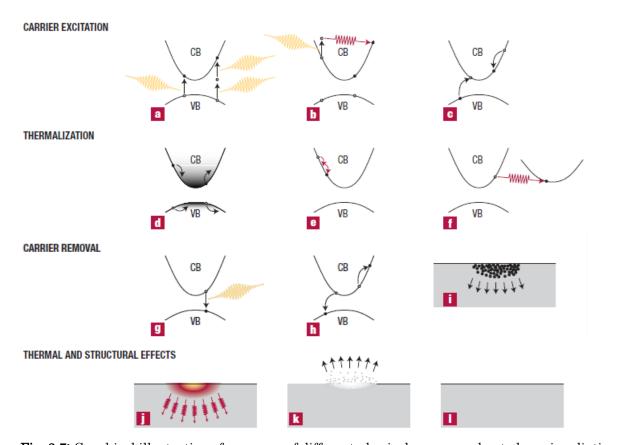

| Fig. 3.6: The summary of physical processes upon ultrashort laser irradiation and the typical timescales of these processes. The yellow region of the graph indicates the pulse duration [9] 87  Fig. 3.7: Graphical illustration of sequence of different physical processes due to laser irradiation on a semiconductor (a) Absorption (single and multiphoton) (b) Free carrier absorption/Inverse bremsstrahlung (c) Impact/Avalanche ionization (d) Non equilibrium carrier distribution after excitation (e) Electron —electron scattering (f) Emission of phonons (g) Radiative recombination (h) Auger recombination (i) Carrier diffusion (j) Thermal diffusion (k) Material ablation (l)  Condensation/resolidification [9] |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

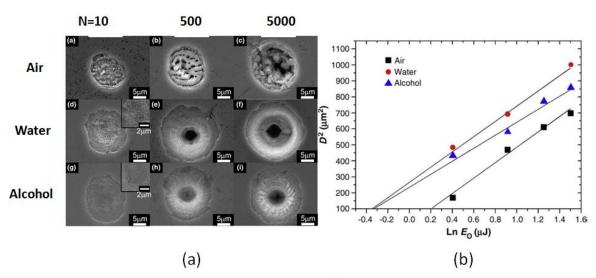

| <b>Fig. 3.8:</b> Ablation of silicon in air, alcohol and water (a) SEM micrograph of the obtained crater for different number of impulsions (b) Threshold fluence for Np=5000 for the 3 media by squared diameter regression method [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

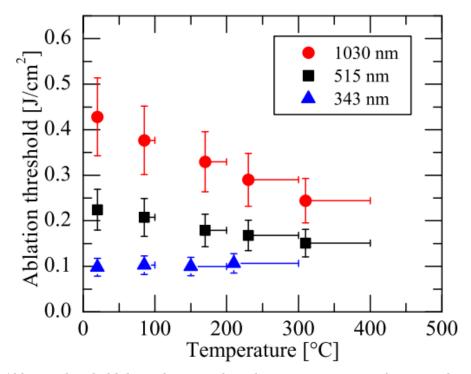

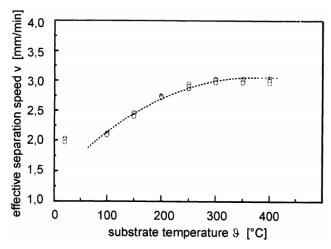

| Fig. 3.9: Ablation threshold dependence on the substrate temperature for 3 wavelengths [20] 91 Fig. 3.10: Influence of substrate temperature on effective cutting speed of wafer grade silicon [21]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

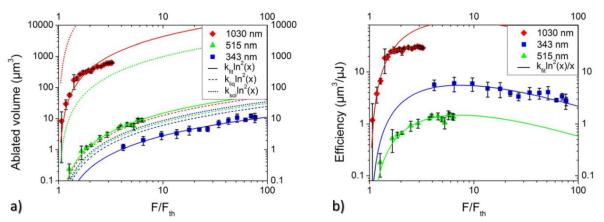

| <b>Fig. 3.11:</b> Ablated volume and efficiency as a function of peak fluence normalized to the threshold fluence for three different wavelengths [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

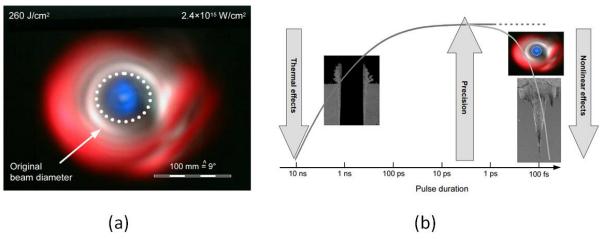

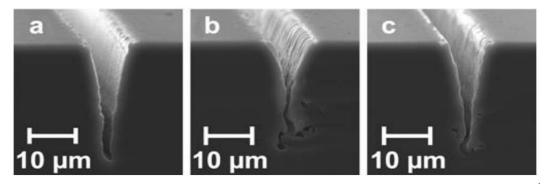

| Fig. 3.12: (a) Beam energy distribution taken after focusing of laser beam in air and measuring far-field intensity of the beam. The encircled region represents the outline of the original beam. (b) Different effects occurring at long and short pulse widths. At long pulse widths, melting is severe which causes redeposited slag and at short pulse widths non-linear effects results in non-gaussian energy deposition profiles and consequently enlarged ablation profiles. [17]                                                                                                                                                                                                                                            |

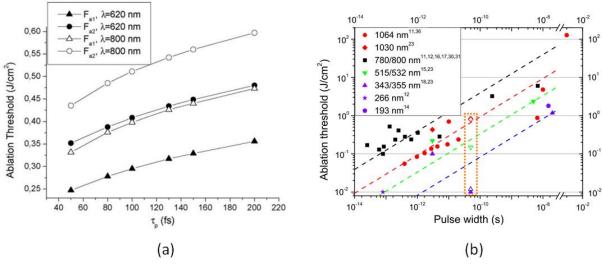

| (a), two ablation thresholds are mentioned. Here $F_{a1}$ refers to threshold for onset of ablation and $F_{a2}$ refers to threshold for complete surface ablation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

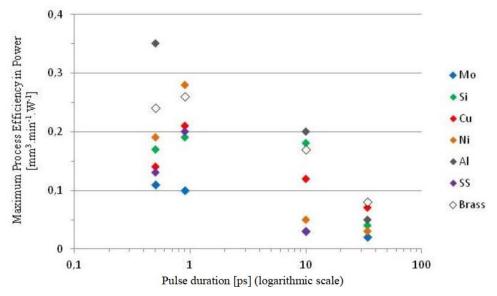

| <b>Fig. 3.14:</b> Ablation efficiency of different materials studied by making grooves using a Yb: YAG thin disc laser wavelength of 1030 nm and different pulse widths [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

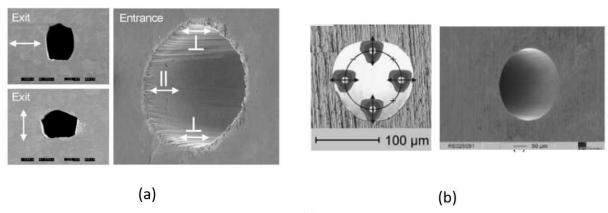

| Circular polarization [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

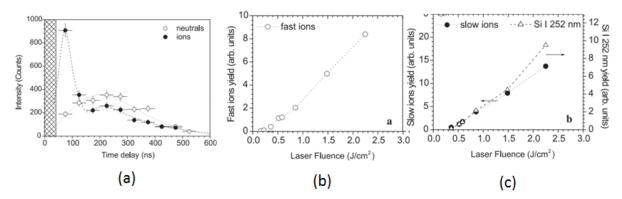

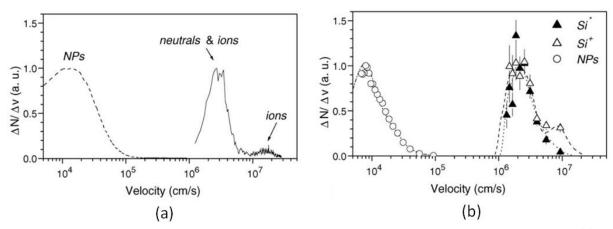

| laser fluence (c) Yield of slow ions as a function of laser fluence [30]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

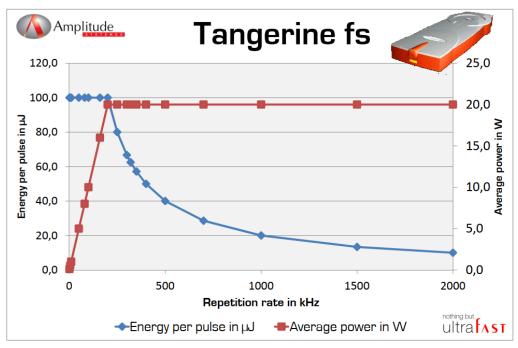

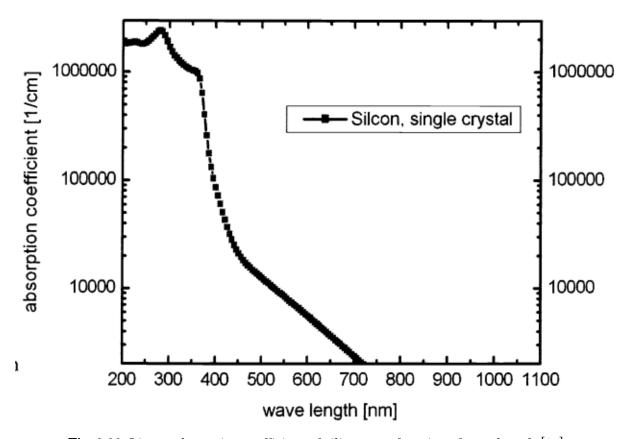

| Fig. 3.21: Variation of pulse energy and average power output as a function of repetition rate . 101  Fig. 3.22: Linear absorption coefficient of silicon as a function of wavelength [34]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

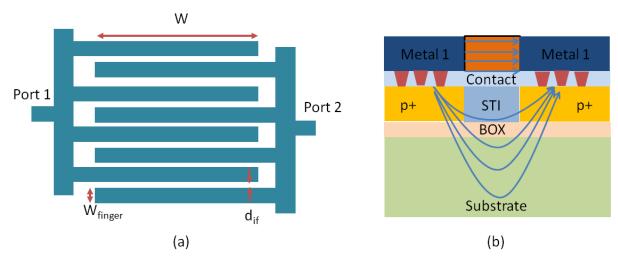

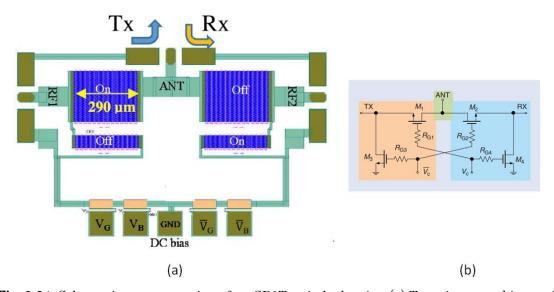

| Fig. 3.24: Schematic representation of an SP2T switch showing (a) Transistor stacking and relative sizes of series and shunt branches (b) Equivalent circuit of the switch [36], [37]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | cess.<br>tack<br>right.       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

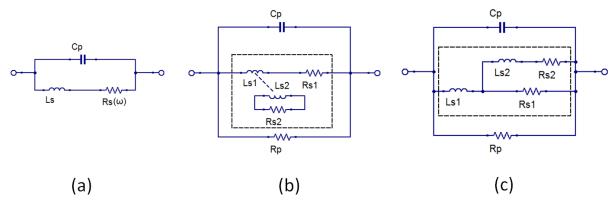

| Fig. 3.26: (a) Cross sectional schematic of an inductor fabricated on SOI wafer showing the or of different capacitances and resistances (b) Lumped circuit equivalent for TR-SOI (c) Lumped circuit equivalent for HR-SOI. Taken from [38]                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rigin<br>ed<br>109            |

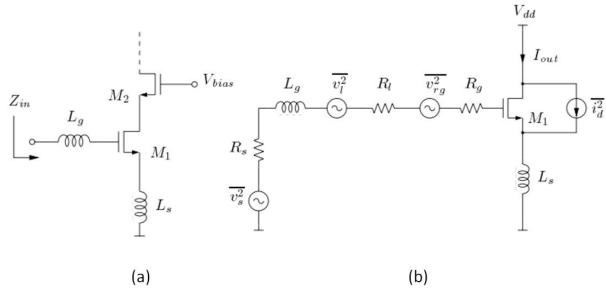

| and noise factors [39]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 110<br>110                    |

| Fig. 3.29: (a) Input stage of a common source LNA (b) Equivalent circuit for calculating the nat the input stage of LNA [41]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |

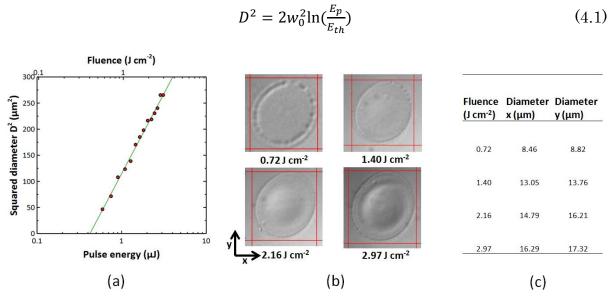

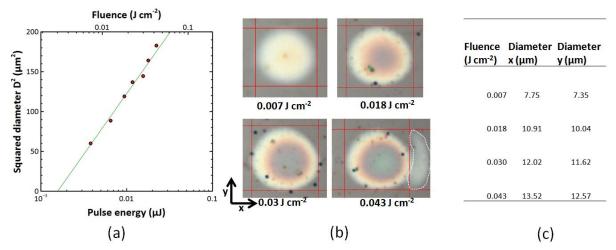

| <b>Fig. 4.1:</b> (a) Squared diameter (x) plotted as a function of pulse energy for 1030 nm source. Gline is the least squares fit of the experimental data (b) Optical micrographs of ablated area shown for 4 different fluences (c) Measured diameter in x and y direction for different fluence <b>Fig. 4.2:</b> (a) Squared diameter (x) plotted as a function of pulse energy for 343 nm source. Greline is the least squares fit of the experimental data (b) Optical micrographs of ablated area shown for 4 different fluences. Outlined region for 42.7 mJ cm <sup>-2</sup> shows the distortion of beam redistribution of incident energy (c) Measured diameter in x and y direction for different fluences. | es 117<br>een<br>and<br>ences |

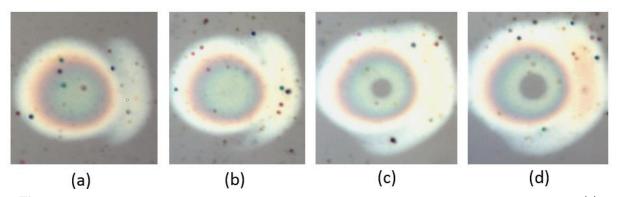

| Fig. 4.3: Optical micrographs depicting evolution of laser spot with increasing laser fluence (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | a)                            |

| 0.055 J cm <sup>-2</sup> (b) 0.067 mJ cm <sup>-2</sup> (c) 0.082 mJ cm <sup>-2</sup> (d) 0.097 mJ cm <sup>-2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |

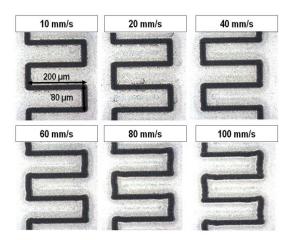

| Fig. 4.4: 2D laser scribing at different galvo speeds for 343 nm source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |

| Fig. 4.5: 2D laser scribing at different galvo speeds for 1030 nm source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |

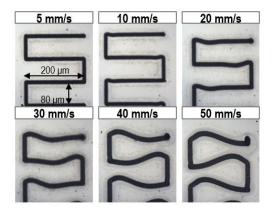

| <b>Fig. 4.6:</b> Profile of trenches taken along the centre of the trench for 343 nm source at fluence 4.2 J cm <sup>-2</sup> and repetition rate 200 kHz and scan speeds of (a) 25 mm s <sup>-1</sup> (b) 50 mm s <sup>-1</sup> (c) 75 m (d) 100 mm s <sup>-1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $m s^{-1}$                    |

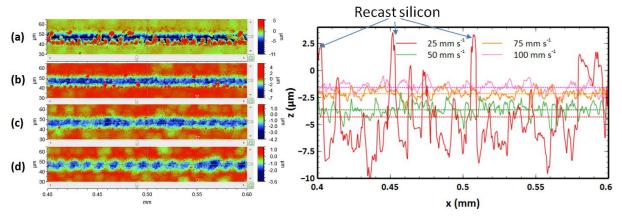

| <b>Fig. 4.7:</b> Profile of trenches along the centre of the trench for 343 nm source at scan speed of mm s <sup>-1</sup> and pulse repetition rate 200 kHz and fluence of (a) 3.7 J cm <sup>-2</sup> (b) 6 J cm <sup>-2</sup> (c) 9 J cm <sup>-2</sup> . microscope image shows the micro-holes at the bottom of the trench                                                                                                                                                                                                                                                                                                                                                                                            | 100<br>The                    |

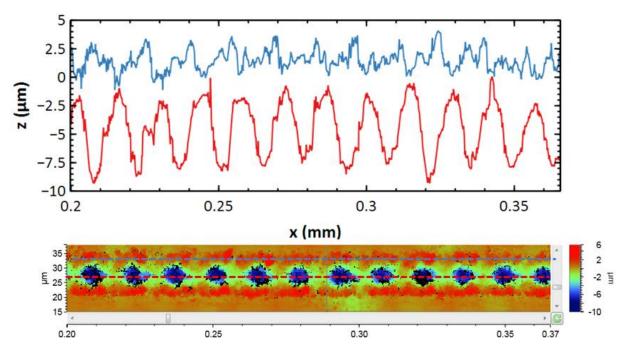

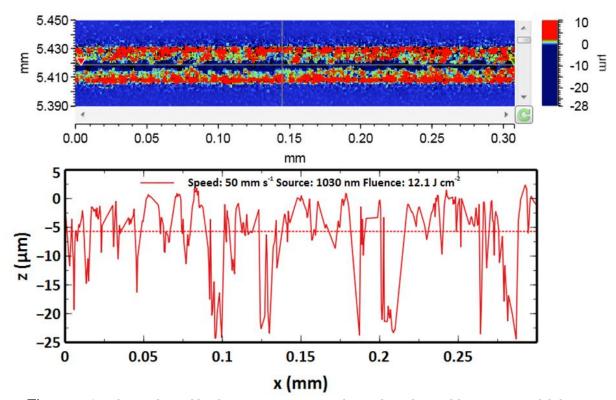

| Fig. 4.8: Profile of trench compared with the profile of recast layer for trench scribed at 6 J cr. The red line is the profile at trench centre while blue line represents the recast layer profile. Fig. 4.9: Profile of trenches along the centre of the trench for 1030 nm source at fluence of 13 cm <sup>-2</sup> and repetition rate 30 kHz and scan speeds of (a) 25 mm s <sup>-1</sup> (b) 50 mm s <sup>-1</sup> (c) 75 mm s <sup>-1</sup> (d) $\frac{1}{2}$                                                                                                                                                                                                                                                   | 123<br>3.6 J<br>d)            |

| 100 mm s <sup>-1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               |

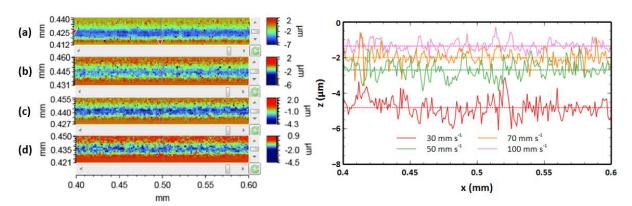

| <b>Fig. 4.10:</b> Profile of trenches along the centre of the trench for 1030 nm source at scan speed 100 mm s <sup>-1</sup> repetition rate 30 kHz and fluence of (a) 6.6 J cm <sup>-2</sup> (b) 19.9 J cm <sup>-2</sup> (c) 33.1 J cm <sup>-2</sup> 46.1 J cm <sup>-2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                           | (d)                           |

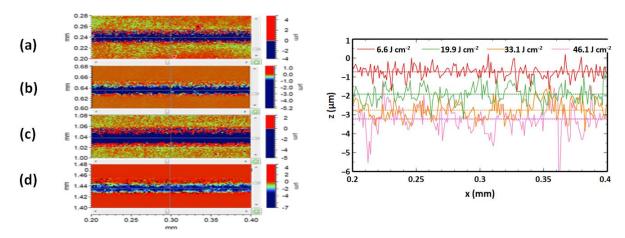

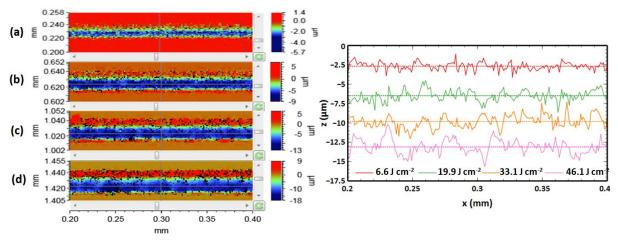

| Fig. 4.11: Profile of trenches along the centre of the trench for 1030 nm source at scan speed mm s <sup>-1</sup> repetition rate 30 kHz and fluence of (a) 6.6 J cm <sup>-2</sup> (b) 19.9 J cm <sup>-2</sup> (c) 33.1 J cm <sup>-2</sup> (d) cm <sup>-2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | of 30<br>46.1 J               |

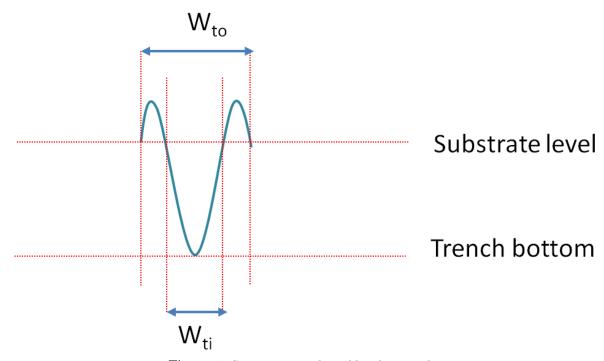

| Fig. 4.12: Cross sectional profile of a trench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 127                           |

| Fig. 4.13: Average trench depth plotted as a function of fluence for 3 cases at different scan s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                             |

| Fig. 4.14: Axial trench profile showing narrowing of trench and possible presence of debris                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |

| Fig. 4.15: Recast layer volume plotted as a function of fluence for 3 cases at different scan speeds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4.16: Recast layer average height plotted as a function of fluence for 3 cases at different scan peeds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 4.17: Average roughness of trench plotted as a function of fluence for 3 cases at different scan peeds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 4.18: Inner trench width plotted as a function of fluence for 3 cases at different scan speeds.  The error bars represent symmetric error of one standard deviation                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fig. 4.19: (a) Cross-sectional profiles of single trench as a function of varying laser power at lifferent scan speeds on 1030 nm source (b) Cross-sectional profiles for two lines scribed parallel o each other with varying pitch. Laser parameters: (i) Power: 0.26 W (ii) Scan speed: 20 mm s <sup>-1</sup> iii) Fluence: 6.4 J cm <sup>-2</sup>                                                                                                                                                                                                                                                                                    |

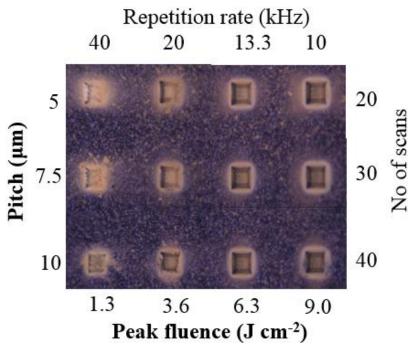

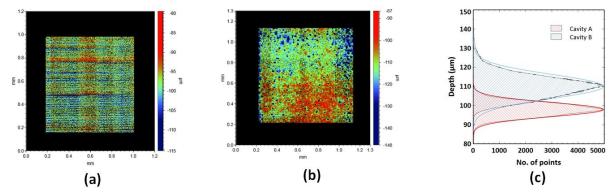

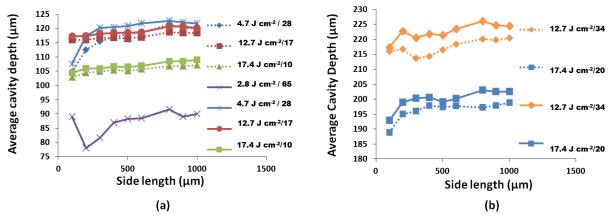

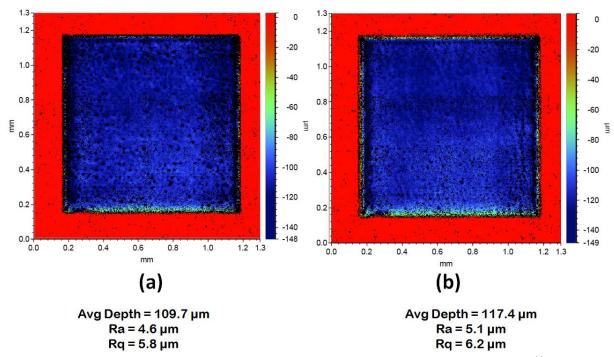

| Fig. 4.20: (a) Cavity depth obtained for different squares plotted as a function of square side. Milling parameters (i) Source: 1030 nm (ii) Scan speed: 5 mm s <sup>-1</sup> (iii) Repetition rate: 2 kHz (iv) Fluence: 56.8 J cm <sup>-2</sup> (v) Number of passes: 15 (b) Plot of depth as a function of different milling parameters for the two laser sources having average power of 1 W for square of side 1 mm 139 Fig. 4.21: Particle generation and redeposition as a function of laser fluence and pitch. Milling parameters (i) Source: 1030 nm (i) Area: 0.25 x 0.25 mm <sup>2</sup> (ii) Power: Column 1: 0.054 W, Column |

| : 0.072 W, Column 3: 0.085 W, Column 4: 0.09 W) (iii) Scan speed: 10 mm s <sup>-1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

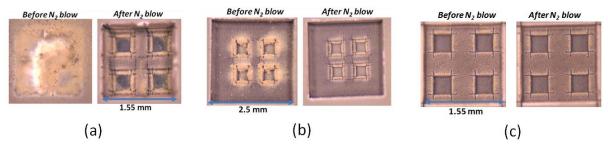

| leep cavity (b) Case 2: Wide opening, deep cavity (c) Case 3: Narrow opening, shallow cavity.  Large cavity milling parameters: Scan Speed - 50 mm s <sup>-1</sup> , Fluence - 61.5 J cm <sup>-2</sup> , No. of scans- 12.  Small cavity milling parameters: Scan speed - 10 mm s <sup>-1</sup> , Fluence - 7.1 J cm <sup>-2</sup> , No. of scans - 80                                                                                                                                                                                                                                                                                   |

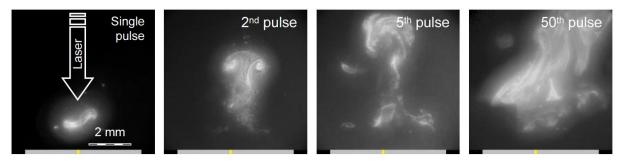

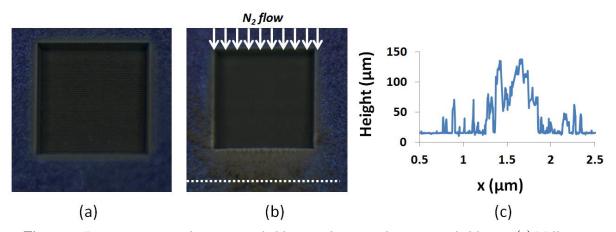

| Fig. 4.23: Demonstration of presence of ablation plume in the region of ablation (a) Milling process without air flow (b) Milling process with air flow (c) Depth profiling of particle aggregates along the white dotted line. Milling parameters (i) Scan speed: 50 mm s <sup>-1</sup> (ii) Fluence: 9.8 J cm <sup>-2</sup> (iii) Pulse repetition rate: 100 kHz (iv) No. of scans: 50                                                                                                                                                                                                                                                 |

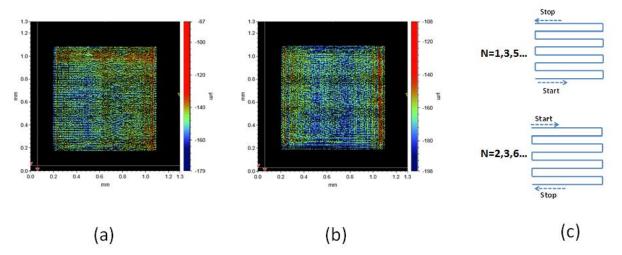

| b) 1 s (c) Two-way milling trajectory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

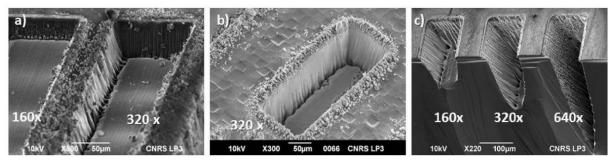

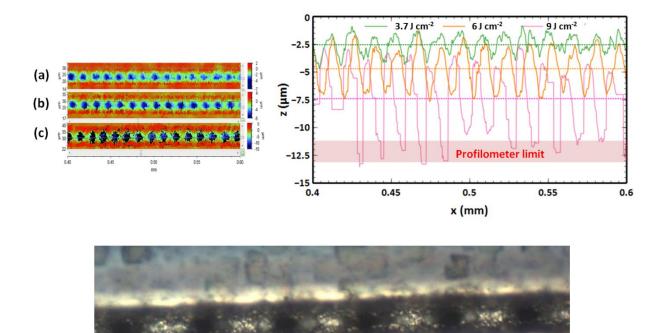

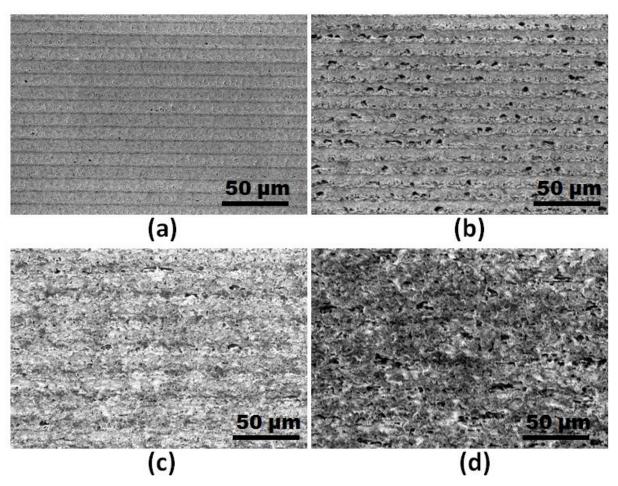

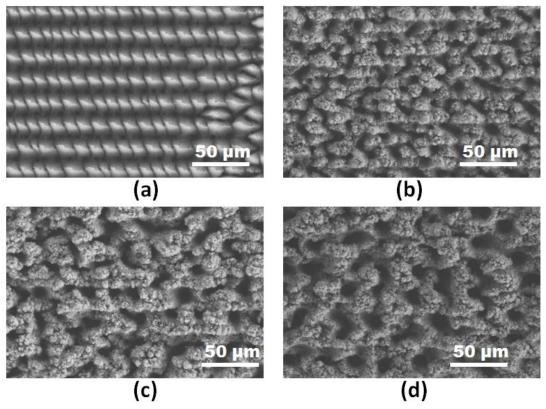

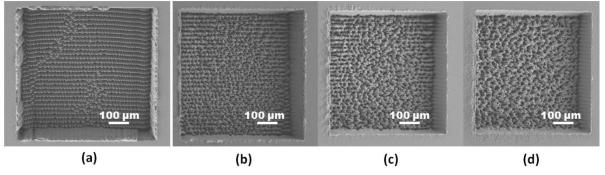

| <b>Fig. 4.30</b> : Cavity side walls after cleaning in ultrasonic bath. Milling parameters used are scan speed of 20 mm s <sup>-1</sup> and repetition rate of 30 kHz with fluence/ number of scans (a) 2.8 J cm <sup>-2</sup> /6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.7 J cm <sup>-2</sup> /28 (c) 12.7 J cm <sup>-2</sup> /17 (d) 17.4 J cm <sup>-2</sup> /10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 151 |

| <b>Fig. 4.31:</b> Reduction of holes by changing the focus for each pass. Milling parameters: (i) Speed mm s <sup>-1</sup> (ii) Repetition rate: 20 kHz (iii) Fluence: 51.1 J cm <sup>-2</sup> (iv) No. of scans: 8 (iv) Focus change after each scan (a) No focus change (b) 45 μm into the sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ge    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |