# Exploration of Direct Synchronization Approaches for a High-Level and Unified Simulation of Discrete-Event/Continuous-Time Systems

Breytner Joseph Fernandez Mesa

# ► To cite this version:

Breytner Joseph Fernandez Mesa. Exploration of Direct Synchronization Approaches for a High-Level and Unified Simulation of Discrete-Event/Continuous-Time Systems. Modeling and Simulation. Université Grenoble Alpes [2020-..], 2021. English. NNT: 2021GRALM047. tel-03625797

# HAL Id: tel-03625797 https://theses.hal.science/tel-03625797v1

Submitted on 31 Mar 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

# Présenté par

# Breytner Joseph FERNANDEZ MESA

Thèse dirigée par **Frédéric PETROT (MSTII)**, Professeur Grenoble INP/Ensimag, Université Grenoble Alpes et codirigée par **Liliana Lilibeth ANDRADE PORRAS**, Maître de conférence UGA / Polytech, Université Grenoble Alpes

préparée au sein du Laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés dans l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# Exploration des approches de synchronisation directes pour la simulation unifiée et de haut niveau des systèmes continus/discrets

# Exploration of Direct Synchronization Approaches for a High-Level and Unified Simulation of Discrete-Event/ Continuous-Time Systems

Thèse soutenue publiquement le **14 octobre 2021**, devant le jury composé de :

# **Florence Maraninchi**

Professeur des universités, Université Grenoble Alpes, France, Présidente **Christoph Grimm** Professeur, Technische Universität Kaiserslautern, Allemagne, Rapporteur **Robert de Simone** Directeur de recherche, INRIA Sophia Antipolis, France, Rapporteur **François Pêcheux** Professeur des universités, Sorbonne Université, LIP6, France, Examinateur **Nicolas Ventroux** Ingénieur HDR, Thales Research & Technology, France, Examinateur **Rainer Dömer** Professeur, University of California, Irvine, États-Unis, Examinateur **Frederic Pétrot**

Professeur des universités, Université Grenoble Alpes, Directeur de thèse

### Abstract

Current integrated cyber-physical systems combine digital and analog components that interact and create complex system behavior. The digital components can be hardware and software; the analog components can be electrical, mechanical, etc. Their integration has safety-critical applications in aerospace, automotive, defense, and other industries. Designers must assure safe and predictable functioning within constrained design budgets and short time-to-market intervals. To this end, they rely on modeling and simulation.

However, cyber-physical system simulation is prone to accuracy and speed problems. The simulation of digital components is based on discrete events (DE) and it progresses by discrete timesteps. The simulation of analog components is based on continuous-time (CT) differential equations and it progresses in a time continuum. Despite different time representations, data must be transmitted between both domains at precise instants (synchronization). One solution is fixed-step synchronization, which occurs at regular and statically user-defined timesteps. But it raises a dilemma: either the timestep is small, the simulation accurate but slow, or the timestep is large, the simulation possibly inaccurate, but fast. CT/DE synchronization has a vast impact on simulation accuracy and speed.

The purpose of this thesis is to accelerate the simulation of combined CT/DE models. To this aim, we propose a sequential direct CT/DE synchronization algorithm that makes the CT and DE domains interact by events. Synchronization takes place only at the event notification times, preserving accuracy and improving speed when compared to fixed-step approaches.

However, direct synchronization increases the modeling costs: it requires the CT components to communicate only by events. To address this issue, we also propose a modeling interface that can be automatically defined by a CT model of computation. This enables designers to specify models only by interconnecting primitives. Some primitives can consume and generate events. Such models take a graphical representation form, e.g., electrical circuits, and simulate on top of our algorithm with high accuracy and speed.

Last, based on our sequential approach, we propose a parallel direct CT/DE synchronization algorithm for the simulation of models containing multiple CT components. Our solution groups these components, synchronizes their execution, and simulates them in parallel. It improves simulation speed when compared to our sequential algorithm, which already shows an important speed-up when compared to fixed-step approaches.

Combined CT/DE modeling and simulation with high accuracy and speed is an aid to the design of high confidence and performant complex cyber-physical systems while maintaining short design cycles and reduced costs.

## Résumé

Les systèmes cyber-physiques intégrés actuels combinent des composants numériques et analogiques qui interagissent et permettent de créer des comportements de systèmes complexes. Les composants numériques peuvent être matériels et logiciels tandis que les composants analogiques peuvent être électriques, mécaniques, etc. Leur intégration a des applications critiques pour la sécurité dans l'aérospatiale, l'automobile, la défense et d'autres industries. Les concepteurs doivent assurer un fonctionnement prévisible dans le cadre de budgets de conception limités et de courts intervalles de mise sur le marché. À cette fin, ils s'appuient sur la modélisation et la simulation.

Cependant, la simulation de systèmes cyber-physiques est sujette à des problèmes de précision et de vitesse. La simulation des composants numériques est basée sur des événements discrets (ED) et elle progresse par pas de temps discrets. La simulation de composants analogiques est basée sur des équations différentielles en temps continu (CT) et progresse dans un continuum temporel. Malgré des représentations temporelles différentes, les données doivent être transmises entre les deux domaines à des instants précis (synchronisation). Une solution est la synchronisation à pas fixe, qui se produit à des pas de temps réguliers et statiquement définis par l'utilisateur. Mais cela pose un dilemme : soit le pas de temps est petit, la simulation précise mais lente, soit le pas de temps est grand, la simulation peut-être imprécise, mais rapide. La synchronisation TC et ED a un impact considérable sur la précision et la vitesse de la simulation.

L'objectif de cette thèse est d'accélérer la simulation de modèles combinés en TC et à ED. Dans ce but, nous proposons un algorithme de synchronisation séquentielle directe CT/DE qui fait interagir les domaines TC et ED par événements. La synchronisation n'a lieu qu'aux moments de notification des événements, préservant la précision et améliorant la vitesse par rapport aux approches à pas fixes.

Cependant, la synchronisation directe augmente les coûts de modélisation : elle oblige les composants en TC à communiquer uniquement par événements. Pour répondre à ce problème, nous proposons également une interface de modélisation qui peut être définie automatiquement par un modèle de calcul en TC. Cela permet aux concepteurs de spécifier des modèles uniquement en interconnectant des primitives dont certaines gèrent la communication par événements. De tels modèles prennent une forme de représentation graphique, par exemple, sous forme de circuits électriques, et sont simulés sur notre algorithme avec une précision et une vitesse élevées.

Enfin, sur la base de notre algorithme séquentiel, nous proposons un algorithme parallèle pour la simulation de modèles combinés contenant plusieurs composants en TC. Notre solution regroupe ces composants, synchronise leur exécution et les simule en parallèle. La vitesse de simulation est améliorée par rapport à notre algorithme séquentiel, qui fournit déjà une accélération importante par rapport aux approches à pas fixes.

La simulation en TC et à ED avec une précision et une vitesse élevées est une aide à la conception de systèmes cyber-physiques complexes hautement fiables et performants.

### Acknowledgements

I would like to express my profound appreciation to all those who have helped me to attain this goal. In particular, I would like to thank:

Prof. Christoph Grimm and Prof. Robert de Simone, for having accepted to report on this thesis and for their constructive comments during their revision.

Prof. Florence Maraninchi, Prof. François Pêcheux, Dr. Nicolas Ventroux, and Prof. Rainer Dömer, for having kindly taken part as members of the jury.

Frédéric Pétrot, for his trust, pertinence, and acuteness in the direction of this thesis.

Liliana Andrade, for the diligence and meticulousness of her supervision from the day we prepared my candidature to the present.

Olivier Müller, Laurence Pierre, Frédéric Rousseau, Arthur Perais, Marie Badaroux, Bruno Ferres, Arthur Vianès, and all other members of the System Level Synthesis team of TIMA Laboratory, for the warm working environment. Luc Michel, Clément Deschamps, and Damien Hedde, members and former members of GreenSoCs.

Gerard Paez, for his continuous advice since my early engineering school days and for his recommendation to Liliana and Fréderic to accept me as a Ph.D. student.

Claudia Gómez, Anna Patete, Mario Spinetti, Iñaki Aguirre, and Richard Márquez, members and former members of the Control Engineering department of the School of Systems Engineering of Universidad de Los Andes—Venezuela, for their rigorous instruction and for feeding my interest in teaching and research since the first semesters of my engineering degree.

My mother, Bertha Fernández, for her tenderness and care: you have taught me to give my best since I was little, this thesis is the fruit of your fervor in my education. I also praise my sisters and family, for all their love and support.

Thibaud Mautuit, for your noble temper, pristine spirit, and exquisite wit. Such rare integrity is a strength I cannot but cherish and wish to share.

To all those who have cared for me and whose name I leave unmentioned.

# Contents

| 1        | Intr | roduction                                                                      | 1  |

|----------|------|--------------------------------------------------------------------------------|----|

|          | 1.1  | Context                                                                        | 2  |

|          | 1.2  | Thesis Objective and Outline                                                   | 4  |

| <b>2</b> | Mo   | tivation and Definition of the Problem                                         | 5  |

|          | 2.1  | Introduction                                                                   | 6  |

|          | 2.2  | Modeling and Simulation in System Design                                       | 6  |

|          | 2.3  | Discrete-Event Modeling and Simulation                                         | 7  |

|          |      | 2.3.1 Levels of Behavioral and Structural Abstraction in Discrete-Event Models | 8  |

|          |      | 2.3.2 Simulation of Discrete-Event Models                                      | 9  |

|          | 2.4  | Continuous-Time Modeling and Simulation                                        | 9  |

|          |      | 2.4.1 Levels of Behavioral Abstraction in Continuous-Time Models $\ . \ . \ .$ | 9  |

|          |      | 2.4.2 Levels of Structural Abstraction in Continuous-Time Models 1             | 1  |

|          |      | 2.4.3 State-Space Representation of Continuous-Time Models                     | 4  |

|          |      | 2.4.4 Simulation of Continuous-Time Models                                     | 4  |

|          | 2.5  | The Problem of Synchronization in Continuous-Time and Discrete-Event Sim-      |    |

|          |      | ulation                                                                        | 5  |

|          | 2.6  | Parallel Simulation                                                            | 7  |

|          |      | 2.6.1 Parallel Discrete-Event Simulation                                       | 7  |

|          |      | 2.6.2 Parallel Continuous-Time Simulation                                      | 7  |

|          | 2.7  | Conclusions                                                                    | 8  |

| 3        | Sta  | te of the Art 1                                                                | 9  |

|          | 3.1  | Introduction                                                                   | 20 |

|          | 3.2  | Direct Continuous-Time and Discrete-Event Interactions                         | 20 |

|          | 3.3  | Model of Time                                                                  | 23 |

|          |      | 3.3.1 Superdense Time                                                          | 23 |

|          |      | 3.3.2 Implementation of a Superdense Time Model in a Digital Computer . 2      | 23 |

|          |      | 3.3.3 Difference between Discrete and Superdense Time                          | 24 |

|          | 3.4  | Continuous-Time and Discrete-Event Modeling and Simulation Approaches . 2      | 25 |

|          |      | 3.4.1 VHDL-AMS                                                                 | 25 |

|          |      | 3.4.2 Verilog AMS                                                              | 29 |

|   |      | 3.4.3     | Ptolemy II                                                               | 30              |

|---|------|-----------|--------------------------------------------------------------------------|-----------------|

|   |      | 3.4.4     | Discrete-Event System Specification Simulators                           | 34              |

|   |      | 3.4.5     | Synchronous Languages Based CT/DE Simulators                             | 35              |

|   |      | 3.4.6     | MATLAB/Simulink                                                          | 35              |

|   |      | 3.4.7     | Partial Conclusions                                                      | 36              |

|   | 3.5  | System    | nC-Based Modeling and Simulation Approaches                              | 36              |

|   |      | 3.5.1     | Modeling                                                                 | 36              |

|   |      | 3.5.2     | Model of Time                                                            | 37              |

|   |      | 3.5.3     | Simulation                                                               | 38              |

|   |      | 3.5.4     | Continuous-Time Modeling an Simulation Extensions                        | 39              |

|   |      | 3.5.5     | Partial Conclusions                                                      | 42              |

|   | 3.6  | Paralle   | el Simulation                                                            | 42              |

|   |      | 3.6.1     | Register-Transfer Level Approaches that Preserve Global Time $\ldots$    | 42              |

|   |      | 3.6.2     | Register-Transfer Level Approaches that Distribute Time $\ldots \ldots$  | 43              |

|   |      | 3.6.3     | General Transaction Level Modeling Approaches                            | 44              |

|   |      | 3.6.4     | Transaction Level Modeling Approaches that Increase the Number of        |                 |

|   |      |           | Runnable Processes                                                       | 45              |

|   |      | 3.6.5     | Other Transaction Level Modeling Approaches                              | 46              |

|   |      | 3.6.6     | Continuous-Time Approaches                                               | 46              |

|   |      | 3.6.7     | Partial Conclusions                                                      | 46              |

|   | 3.7  | Conclu    | usions                                                                   | 47              |

| 4 | Dire | act Car   | ntinuous-Time and Discrete-Event Synchronization                         | 49              |

| Ŧ | 4.1  |           | uction                                                                   | <b>49</b><br>50 |

|   | 4.2  |           | uous-Time Modeling Abstraction Suited for Direct Continuous-Time         | 00              |

|   | 1.2  |           | iscrete-Event Synchronization                                            | 50              |

|   |      | 4.2.1     | Implementation of the Superdense Time Model                              | 50              |

|   |      |           | Level of Abstraction Selected for Continuous-Time Models                 | 51              |

|   |      | 4.2.3     | Interface for Describing Continuous-Time and Discrete-Event Interactions | 51              |

|   | 4.3  |           | Continuous-Time and Discrete-Event Synchronization Algorithm             | 53              |

|   |      | 4.3.1     | Synchronization Algorithm Phases                                         | 53              |

|   |      | 4.3.2     | The Big Picture                                                          | 60              |

|   |      | 4.3.3     | Automatic Selection of an Integration Interval Size                      | 61              |

|   |      | 4.3.4     | Synchronization Algorithm Properties                                     | 65              |

|   | 4.4  |           | ments                                                                    | 67              |

|   |      | 4.4.1     | Comparison of Accuracy to Existing Approches                             | 68              |

|   |      | 4.4.2     | Handling State Discontinuities                                           | 72              |

|   |      | 4.4.3     | Handling Error Accumulation                                              | 75              |

|   |      | 4.4.4     | Discussion on the Integration Interval Size Effect on Simulation Speed   | 79              |

|   |      | 4.4.5     | Discussion on the Integration Interval Size Convergence and Adaptability | 80              |

|   | 4.5  | Conclu    | isions                                                                   | 81              |

|   | 1.0  | 0 0 0 - 0 |                                                                          |                 |

## CONTENTS

| <b>5</b> | 5 Direct Synchronization and Continuous-Time Models of Computation |         |                                                                                                  |     |  |  |

|----------|--------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------|-----|--|--|

|          | 5.1                                                                | Introd  | uction                                                                                           | 84  |  |  |

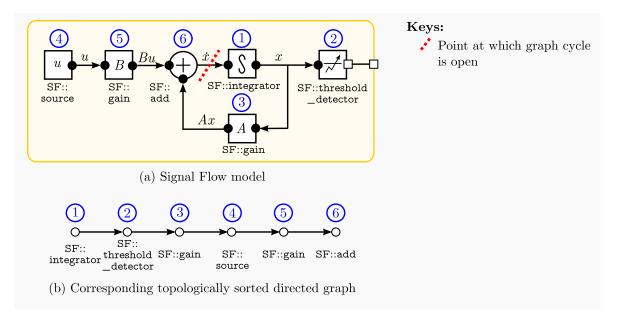

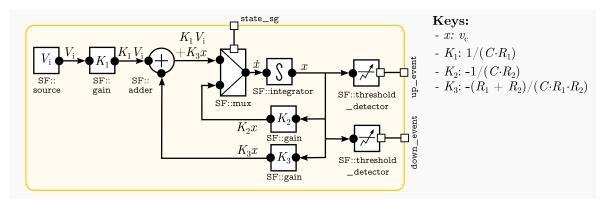

|          | 5.2                                                                | Signal  | Flow Model of Computation                                                                        | 84  |  |  |

|          |                                                                    | 5.2.1   | Modeling of Signal Flow Systems                                                                  | 85  |  |  |

|          |                                                                    | 5.2.2   | Elaboration of Signal Flow Models                                                                | 86  |  |  |

|          | 5.3                                                                | Ideally | V Switched Circuits Model of Computation                                                         | 89  |  |  |

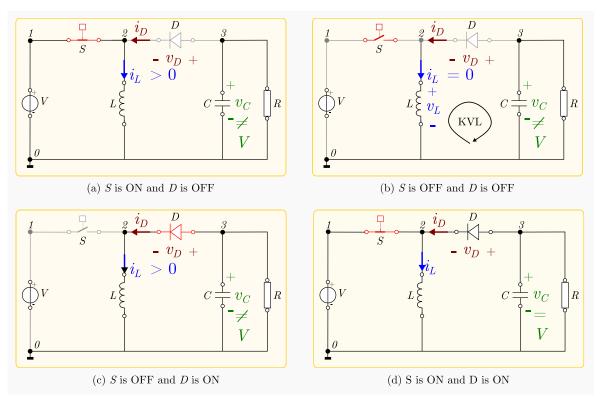

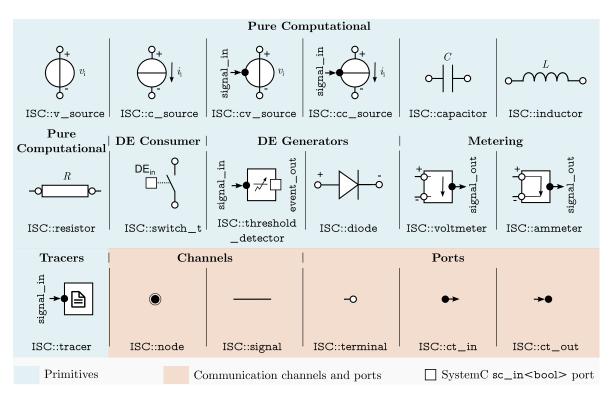

|          |                                                                    | 5.3.1   | Modeling of Ideally Switched Circuit Systems                                                     | 90  |  |  |

|          |                                                                    | 5.3.2   | Elaboration of Ideally Switched Circuit Models                                                   | 92  |  |  |

|          | 5.4                                                                | Remai   | rks about Modeling, Elaboration, and Simulation of Signal Flow and                               |     |  |  |

|          |                                                                    | Ideally | y Switched Circuit Systems                                                                       | 95  |  |  |

|          | 5.5                                                                | Exper   | iments                                                                                           | 96  |  |  |

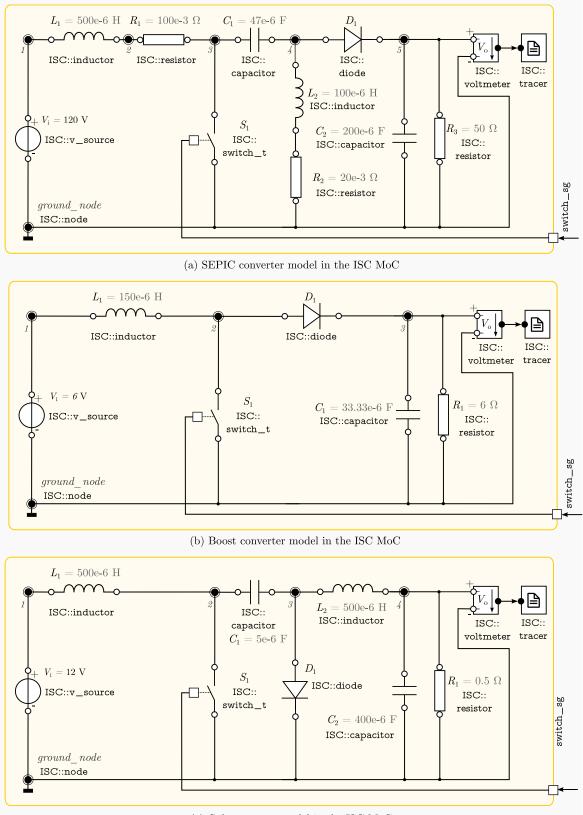

|          |                                                                    | 5.5.1   | Converter Systems and Models                                                                     | 96  |  |  |

|          |                                                                    | 5.5.2   | Simulation Results and Discussion                                                                | 99  |  |  |

|          | 5.6                                                                | Conclu  | usions                                                                                           | 101 |  |  |

| 6        | Par                                                                | allel D | irect Continuous-Time and Discrete-Event Synchronization                                         | 103 |  |  |

|          | 6.1                                                                | Introd  | uction                                                                                           | 104 |  |  |

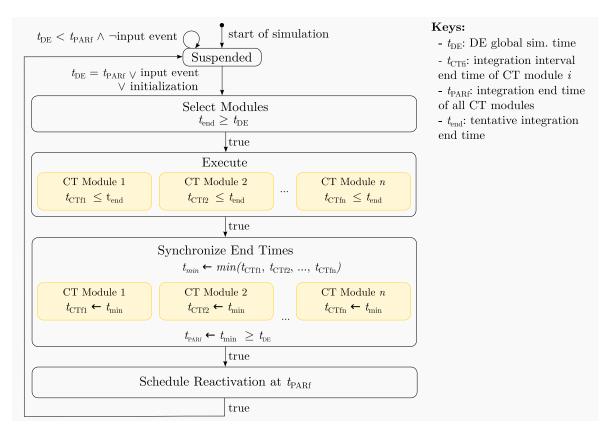

|          | 6.2                                                                | Algori  | thm $\ldots$    | 104 |  |  |

|          |                                                                    | 6.2.1   | Module Selection                                                                                 | 105 |  |  |

|          |                                                                    | 6.2.2   | Parallel Execution                                                                               | 107 |  |  |

|          |                                                                    | 6.2.3   | Synchronization of Continuous-Time Module Execution                                              | 108 |  |  |

|          |                                                                    | 6.2.4   | Reactivation Scheduling                                                                          | 110 |  |  |

|          | 6.3                                                                | Parall  | el Synchronization Algorithm Properties                                                          | 110 |  |  |

|          |                                                                    | 6.3.1   | Discussion on Causality and Completeness                                                         | 110 |  |  |

|          |                                                                    | 6.3.2   | Discussion on Liveness                                                                           | 112 |  |  |

|          | 6.4                                                                | Challe  | enges in Parallel Simulation                                                                     | 112 |  |  |

|          |                                                                    | 6.4.1   | Preservation of Causality                                                                        | 112 |  |  |

|          |                                                                    | 6.4.2   | Prevention of Race Conditions                                                                    | 112 |  |  |

|          |                                                                    | 6.4.3   | Efficient Use of Parallel Resources                                                              | 113 |  |  |

|          | 6.5                                                                | Exper   | iments                                                                                           | 114 |  |  |

|          |                                                                    | 6.5.1   | Model                                                                                            | 114 |  |  |

|          |                                                                    | 6.5.2   | Simulation Results and Discussion                                                                | 115 |  |  |

|          | 6.6                                                                | Conclu  | usions $\ldots$ | 118 |  |  |

| 7        | Conclusions                                                        |         |                                                                                                  |     |  |  |

|          | 7.1                                                                | Conclu  | usions                                                                                           | 120 |  |  |

|          | 7.2                                                                | Future  | e Works                                                                                          | 122 |  |  |

| Α        | СТ                                                                 | Mode    | ling Code Examples                                                                               | 125 |  |  |

| Pι       | ıblic                                                              | ations  |                                                                                                  | 129 |  |  |

| List of Acronyms | 131 |

|------------------|-----|

| Bibliography     | 133 |

# List of Figures

| 1.1  | Example of an automotive system integrating digital and analog components,                                                          |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

|      | adapted from $[1,2]$                                                                                                                | 2  |

| 2.1  | Discrete-event signals and systems                                                                                                  | 7  |

| 2.2  | Gajski Kuhn Y-chart: levels of abstraction in digital systems adapted from [3],                                                     |    |

|      | with the levels at which we place our contributions in blue                                                                         | 8  |

| 2.3  | Continuous-time signals and systems                                                                                                 | 9  |

| 2.4  | Graphical representations of continuous-time systems                                                                                | 12 |

| 2.5  | Numerical solution of an ordinary differential equation, adapted from $[4]$                                                         | 14 |

| 2.6  | Continuous-time and discrete-event synchronization through discrete-time sig-                                                       |    |

|      | nals                                                                                                                                | 16 |

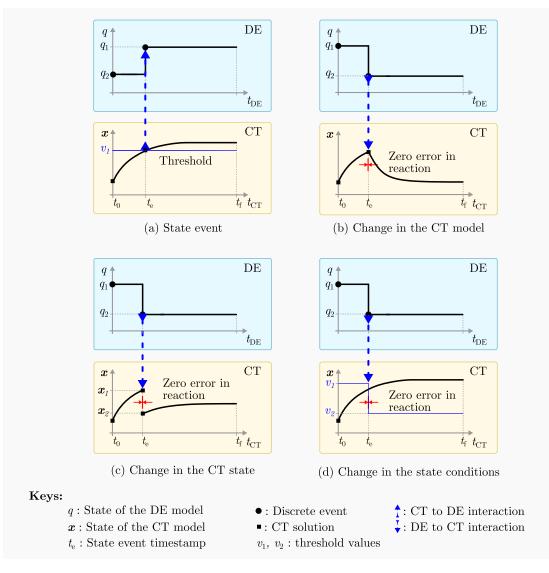

| 3.1  | Direct continuous-time and discrete-event interactions                                                                              | 21 |

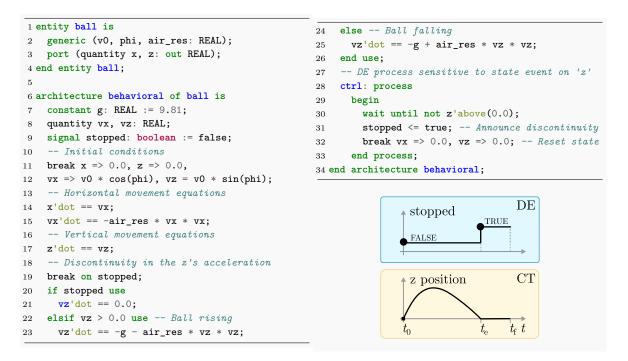

| 3.2  | VHDL-AMS model of a flying ball, adapted from [5]                                                                                   | 25 |

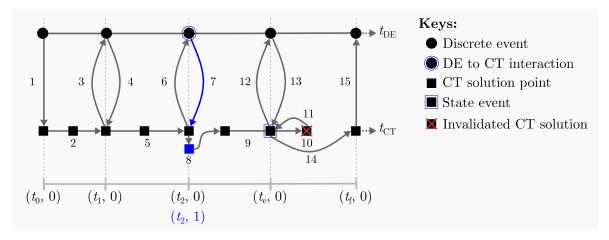

| 3.3  | VHDL-AMS continuous-time and discrete-event synchronization                                                                         | 27 |

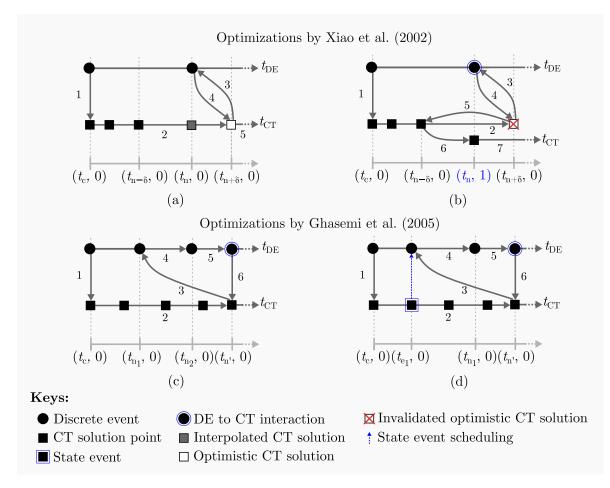

| 3.4  | Optimizations to VHDL-AMS synchronization, adapted from [6,7]                                                                       | 29 |

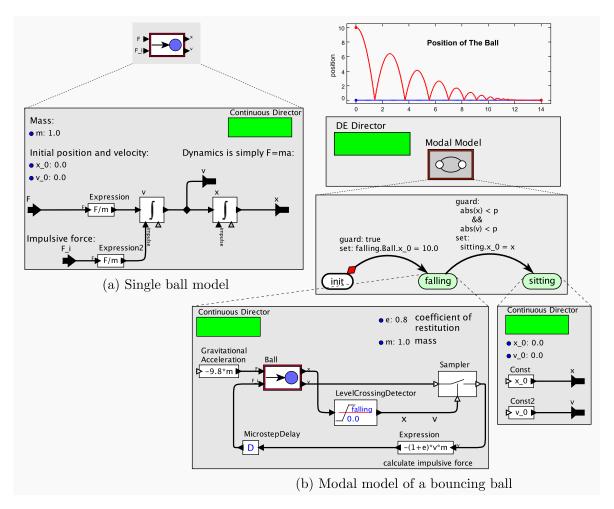

| 3.5  | Model of a bouncing ball in Ptolemy II, adapted from [8]                                                                            | 30 |

| 3.6  | Ptolemy II continuous-time and discrete-event synchronization                                                                       | 32 |

| 3.7  | Model of a boolean equation in SystemC and sample code of a module imple-                                                           |    |

|      | menting a logical not                                                                                                               | 37 |

| 3.8  | SystemC's scheduler, adapted from [9]                                                                                               | 38 |

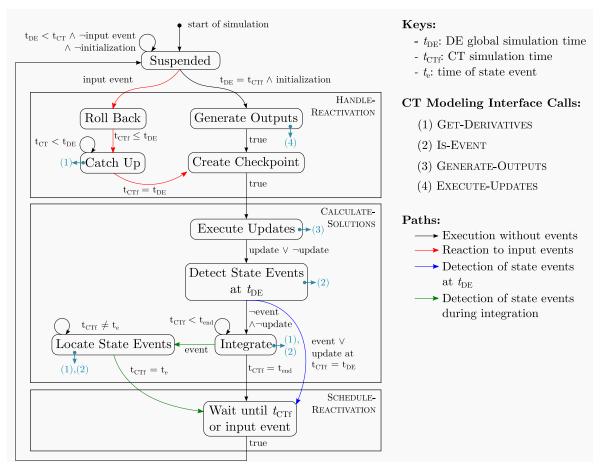

| 4.1  | Direct synchronization process overview                                                                                             | 54 |

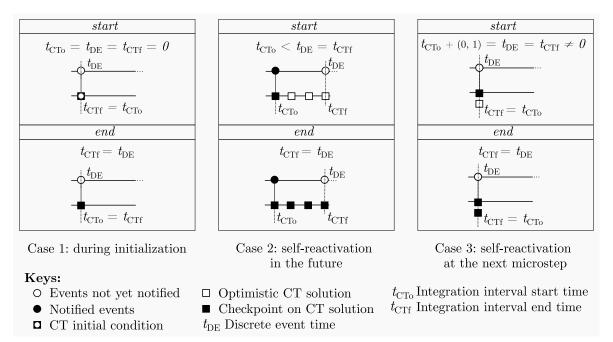

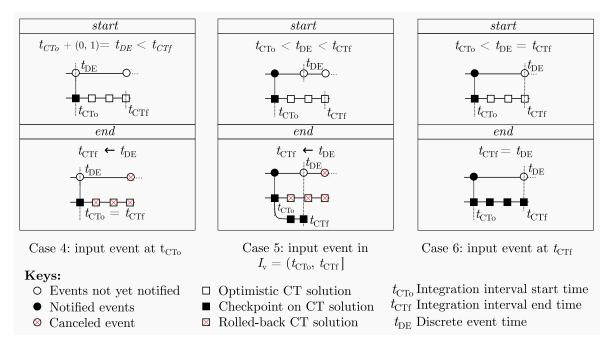

| 4.2  | Graphical representation of the first three cases of HANDLE-REACTIVATION $% \mathcal{A}^{(n)}$ .                                    | 55 |

| 4.3  | Graphical representation of the last three cases of HANDLE-REACTIVATION $% \mathcal{A} = \mathcal{A} = \mathcal{A} + \mathcal{A}$ . | 56 |

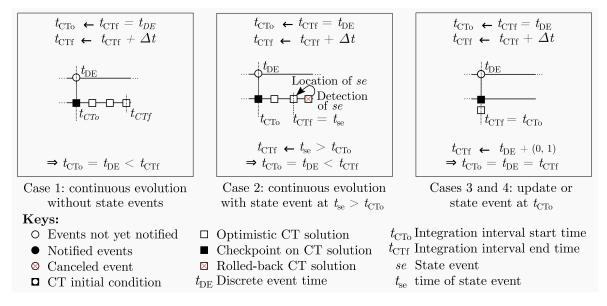

| 4.4  | Graphical representation of CALCULATE-SOLUTIONS                                                                                     | 58 |

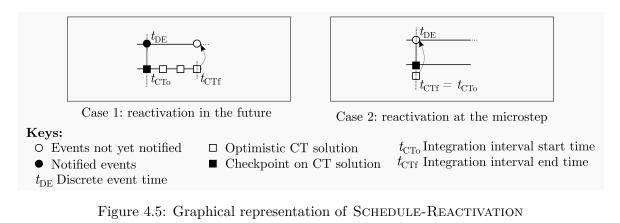

| 4.5  | Graphical representation of SCHEDULE-REACTIVATION                                                                                   | 60 |

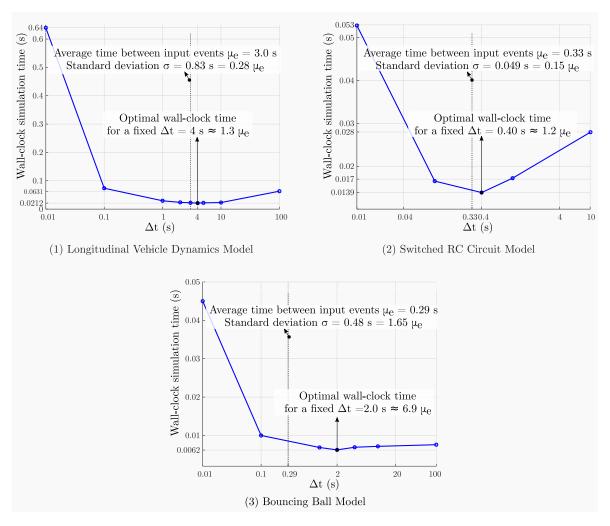

| 4.6  | Wall-clock simulation time vs. $\varDelta t$ for different case studies (log horizontal scale)                                      | 62 |

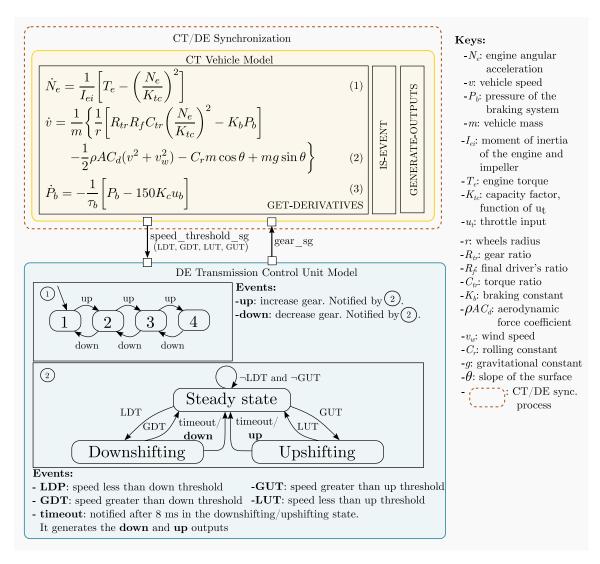

| 4.7  | Continuous-time and discrete-event longitudinal vehicle dynamics model                                                              | 69 |

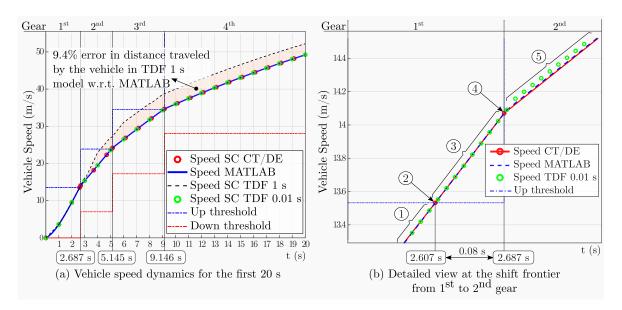

| 4.8  | Vehicle speed dynamics and gear shifts for a constant throttle input                                                                | 70 |

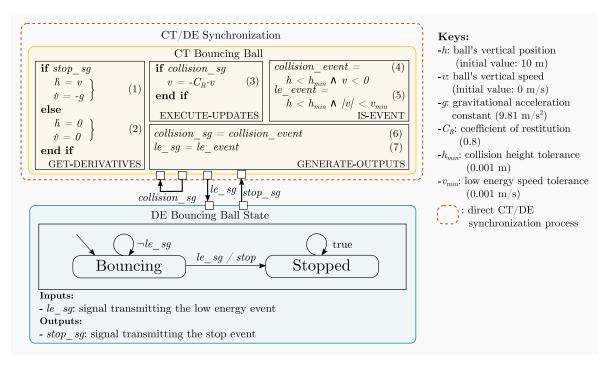

| 4.9  | Continuous-time and discrete-event bouncing ball model                                                                              | 73 |

| 4.10 | Continuous-time and discrete-event bouncing ball dynamics                                                                           | 75 |

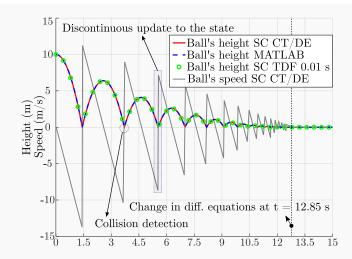

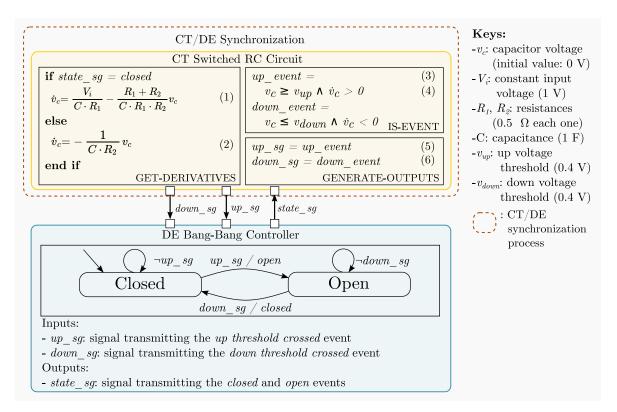

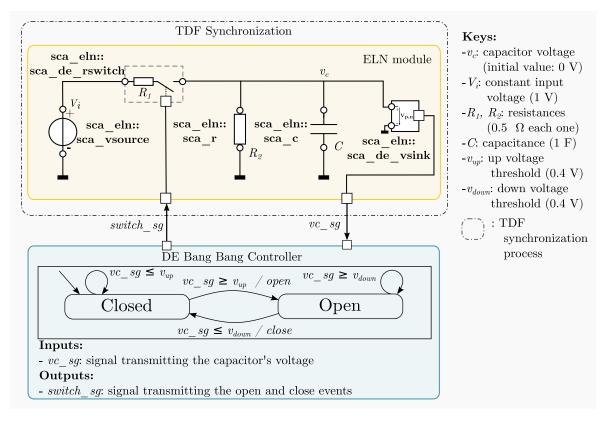

| 4.11 | Continuous-time and discrete-event switched BC circuit model                                                                        | 76 |

## LIST OF FIGURES

| 4.12 | SystemC AMS ELN switched RC circuit model                                                      | 77  |

|------|------------------------------------------------------------------------------------------------|-----|

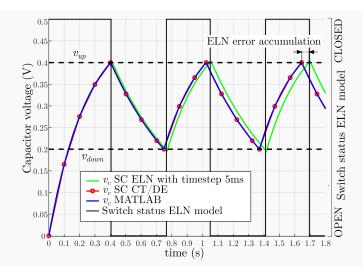

| 4.13 | Switched RC circuit dynamics                                                                   | 78  |

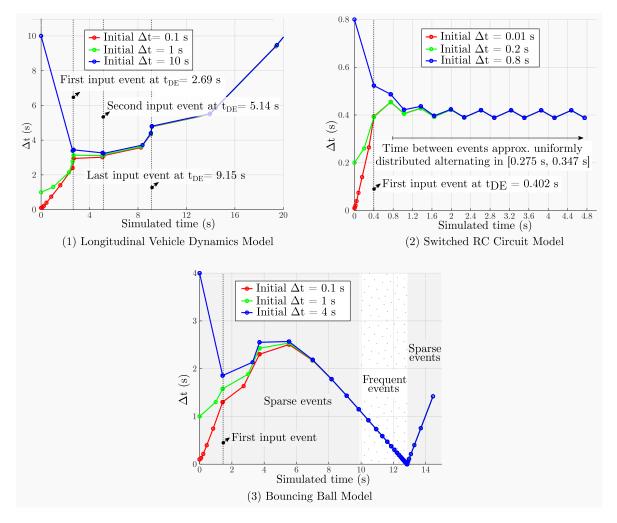

| 4.14 | Dynamics of the adaptive $\varDelta t$ w.r.t. the simulated time for different models $% dt$ . | 81  |

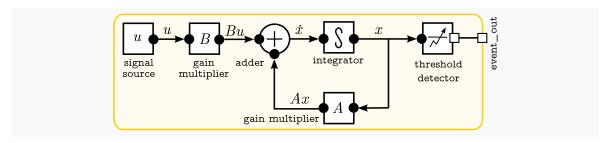

| 5.1  | Signal Flow model representing equation $\dot{x} = Ax + Bu$                                    | 85  |

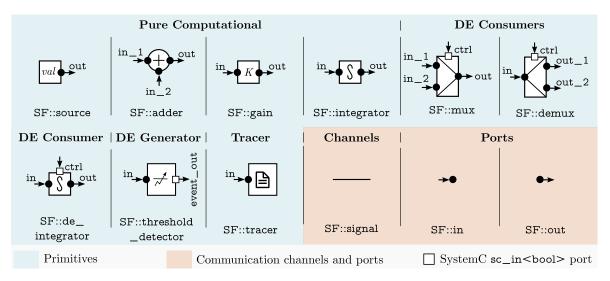

| 5.2  | Signal Flow modeling primitives                                                                | 85  |

| 5.3  | Signal Flow model and its execution schedule                                                   | 87  |

| 5.4  | Fly-back converter circuit topologies, adapted from [10]                                       | 90  |

| 5.5  | Ideally Switched Circuits modeling primitives                                                  | 91  |

| 5.6  | Power converter models in the Ideally Switched Circuits model of computation                   | 97  |

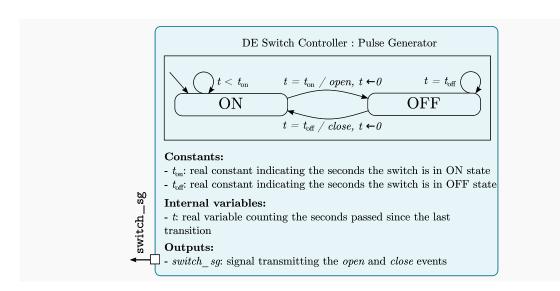

| 5.7  | Discrete-event switch controller model specified in SystemC                                    | 98  |

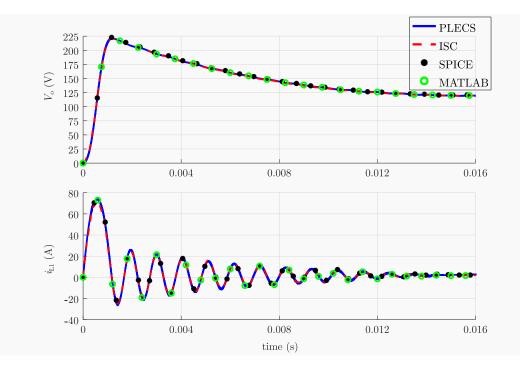

| 5.8  | SEPIC converter output voltage $V_{\rm o}$ and inductor $L_1$ current $i_{\rm L1}$             | 100 |

| 5.9  | Equivalent SF model of the RC circuit presented in Section 4.4.3                               | 100 |

| 6.1  | Parallel direct synchronization process overview                                               | 105 |

| 6.2  | Graphical representation of SELECT-MODULES                                                     | 106 |

| 6.3  | Graphical representation of SYNCHRONIZE-END-TIMES                                              | 108 |

| 6.4  | Graphical representation of SCHEDULE-REACTIVATION                                              | 110 |

| 6.5  | Synthetic model for parallel simulation experiments                                            | 114 |

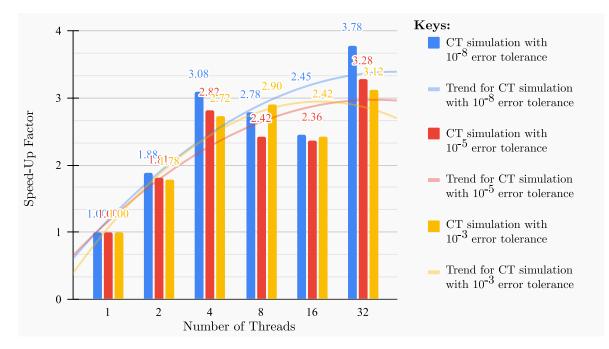

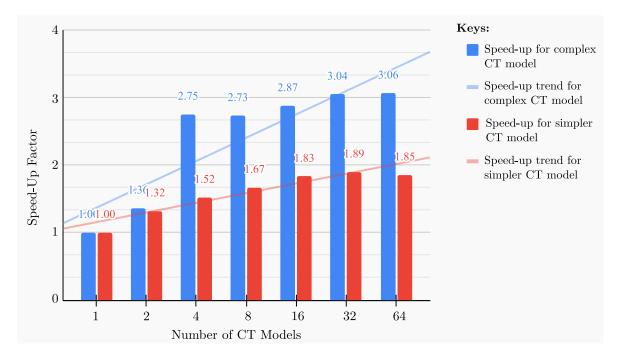

| 6.6  | Parallel simulation speed-up vs. number of threads                                             | 115 |

| 6.7  | Parallel simulation speed-up vs. number of continuous-time modules $\ldots$ .                  | 117 |

# List of Tables

| 4.1 | Longitudinal vehicle dynamics simulation accuracy and speed                                                                                                                                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2 | Simulation speed of the bouncing ball model                                                                                                                                                           |

| 4.3 | Simulation speed of the switched RC circuit model                                                                                                                                                     |

| 4.4 | Simulation speed for different $\Delta t$ selection strategies $\ldots \ldots \ldots$ |

|     | Wall-clock time for different power converter models                                                                                                                                                  |

| 6.1 | CPU utilization during simulation 116                                                                                                                                                                 |

# Chapter 1: Introduction

| 1.1 | Context                      | <b>2</b> |

|-----|------------------------------|----------|

| 1.2 | Thesis Objective and Outline | 4        |

Perhaps that is what the role of an artist relies on—giving a foretaste of something that could exist, and thus causing it to become imaginable. And being imagined is the first state of existence — Olga Tokarczuk, Nobel Lecture: The Tender Narrator

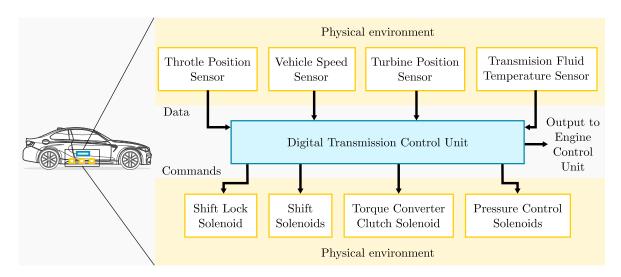

Figure 1.1: Example of an automotive system integrating digital and analog components, adapted from [1,2]

### 1.1 Context

Current integrated cyber-physical systems spread rapidly and promise to support major upcoming technological advances, e.g., the Internet of Things, the Smart Grid, Industry 4.0, etc. [11]. They combine digital and analog components to provide computation and networking in their physical environment, in which they sense data and command actuators [12]. Figure 1.1 shows the example of the transmission control unit of a vehicle: it senses positions, speeds, and temperatures; computes control actions digitally; and carries out these actions in their environment via actuators, such as shift, torque, and pressure control solenoids. It also communicates with other digital components, for instance, the engine control unit. In general, the digital components can be hardware and software, such as processors, firmware, and control algorithms. The analog components can be electrical (e.g., a power converter circuit), mechanical (e.g., a car suspension mechanism), chemical (e.g., a carbon monoxide detector), or from any other physical discipline. They interact and create complex system behavior.

Assuring safe component interaction is an unavoidable challenge for designers. These systems have safety-critical applications in the aerospace, automotive, defense, and other industries where small failures could cause great losses—human, economic, etc. In addition, their design, partitioning, manufacture, integration, and validation have to be achieved within constrained budgets and short time-to-market intervals. To meet these goals, *system designers* rely on modeling and simulation.

However, cyber-physical system simulation is prone to accuracy and speed problems. Digital components are typically modeled by processes that produce and consume *discrete events* (DE) in time order at variable timesteps; some DE languages and tools are VHDL [13], Verilog [14], and SystemC [15]. Conversely, analog components are typically modeled by *continuous-time* (CT) differential equations that are solved by symbolic or numerical integration algorithms over a continuous time interval; some CT languages and tools are MAT-LAB/Simulink [16] and Mathematica [17]. While CT simulation advances in a time continuum, DE simulation does so by discrete steps; the main difficulty of combined CT/DE simulation is to find suitable instants at which to transmit data between both *time domains* in an accurate and performant manner (*synchronization*).

There are two major views with respect to the integration of CT and DE simulation languages and tools: *co-simulation* and *unified simulation*. CT/DE co-simulation combines community-received tools following standards such as Functional Mockup Interface (FMI) [18] and High Level Architecture (HLA) [19]. But these tools were never conceived to interoperate and their integration requires intermediary mechanisms that add computation and communication overhead. Unified CT/DE simulation eliminates this overhead. It also enables designers to share a single language and modeling approach for all components. Although it might require converting models to a new language, unified simulation significantly reduces the simulation costs and proves useful in the long run.

Some unified CT/DE modeling and simulation languages and tools integrate both time domains, but their models are overly detailed for cyber-physical system design. For example, VHDL-AMS [20] and Verilog-AMS [21] work as extensions to the widely used hardware design languages VHDL [13] and Verilog [14], but their digital component models are at the *Register-Transfer Level* (RTL) of abstraction and take the form of registers, logical operations, and data transactions. This level of detail is likely too slow for system simulations containing many components that interact in intricate manners [22]. It is then necessary to support the simulation of models at a *high level of abstraction*, i.e., models that are just detailed enough to make complex system design a manageable task.

As an attempt to solve this problem, the Electronic System Level (ESL) design community has adopted the SystemC standard [15]. It supports high-level modeling and simulation of digital hardware and embedded software systems via its *Transaction Level Modeling* (TLM) extensions. It also supports high-level modeling and simulation of physical systems via its *Analog and Mixed-Signal* (AMS) extensions. However, SystemC AMS defines a CT/DE synchronization strategy based on statically user-defined simulation timesteps [23]. This strategy faces the designer with a dilemma: either the timestep is small, the simulation accurate but slow, or the timestep is large, the simulation possibly inaccurate but fast. As an alternative, *direct CT/DE synchronization* is based on events that are generated when the component variables meet certain conditions. Since the CT/DE synchronization strategy has a vast impact on the simulation accuracy and speed, we consider that proposing a direct strategy could help to circumvent the trade-off introduced by fixed-step approaches.

The implementation of a new direct CT/DE synchronization strategy in SystemC would extend this language to the modeling and simulation of combined CT/DE systems with high accuracy and speed to meet current cyber-physical integrated system design needs.

## 1.2 Thesis Objective and Outline

The purpose of this thesis is to accelerate the unified simulation of CT/DE models to support system design use cases that demand high simulation accuracy and speed. To this aim, we explore sequential and parallel direct synchronization algorithms.

After having defined in this chapter the context and purpose of our work, we organize this thesis as follows:

In Chapter 2, we review CT and DE modeling and simulation. We focus our attention on the problem of CT/DE synchronization and the accuracy and speed trade-off of fixed-step approaches. We also discuss and motivate parallel simulation. At the end of the chapter, we present our research questions on direct synchronization algorithms, their support for the simulation of models from different physical disciplines, and their parallel execution as the main axes guiding our work.

In Chapter 3, we review the state-of-the-art literature on the domain. We study direct CT/DE interactions and their modeling requirements, we describe some languages and tools for unified modeling and simulation, and we give an overview of parallel simulation. In this manner, we identify the available paths to answer our research questions.

In Chapter 4, we propose a sequential direct CT/DE synchronization algorithm. Synchronization takes place at the interaction event notification times. We demonstrate the causality, completeness, and liveness properties of our algorithm, important to ensure simulation correctness. We experimentally confirm that our solution speeds up simulation when compared to fixed-step approaches.

However, our algorithm requires the CT models to support direct interactions by events. We gather these requirements in a set of CT interface methods. In Chapter 5, we show that this interface can be automatically defined to facilitate the modeling and simulation of systems from different physical disciplines. We implement abstract-mathematical and electrical models and demonstrate their simulation on top of our algorithm with high accuracy and speed.

Then, based on our sequential solution in Chapter 4, we propose a parallel direct CT/DE synchronization algorithm for the simulation of models containing multiple CT components. It overcomes typical simulation challenges such as the preservation of causality, the prevention of race conditions, and the efficient use of parallel resources. It also preserves the causality, completeness, and liveness properties of the sequential algorithm. Our parallel solution further accelerates simulation.

Finally, in Chapter 7, we present our conclusions on direct CT/DE synchronization and our perspectives for future research.

# Chapter 2: Motivation and Definition of the Problem

#### Contents

| 2.         | 2.1 Introduction |                                                                          |    |  |

|------------|------------------|--------------------------------------------------------------------------|----|--|

| 2.         | 2 Mod            | leling and Simulation in System Design                                   | 6  |  |

| 2.         | 3 Disc           | rete-Event Modeling and Simulation                                       | 7  |  |

|            | 2.3.1            | Levels of Behavioral and Structural Abstraction in Discrete-Event        |    |  |

|            |                  | Models                                                                   | 8  |  |

|            | 2.3.2            | Simulation of Discrete-Event Models                                      | 9  |  |

| 2.         | 4 Con            | tinuous-Time Modeling and Simulation                                     | 9  |  |

|            | 2.4.1            | Levels of Behavioral Abstraction in Continuous-Time Models $\ . \ . \ .$ | 9  |  |

|            | 2.4.2            | Levels of Structural Abstraction in Continuous-Time Models $\ . \ . \ .$ | 11 |  |

|            | 2.4.3            | State-Space Representation of Continuous-Time Models $\ . \ . \ .$ .     | 14 |  |

|            | 2.4.4            | Simulation of Continuous-Time Models                                     | 14 |  |

| 2.         | 5 The            | Problem of Synchronization in Continuous-Time and                        |    |  |

|            | Disc             | rete-Event Simulation                                                    | 15 |  |

| <b>2</b> . | 6 Para           | allel Simulation                                                         | 17 |  |

|            | 2.6.1            | Parallel Discrete-Event Simulation                                       | 17 |  |

|            | 2.6.2            | Parallel Continuous-Time Simulation                                      | 17 |  |

| 2.         | 7 Con            | clusions                                                                 | 18 |  |

There is always a curious tie at some point between the fall and the creation. Taking this ghastly risk is the condition of there being life. You see, for all life is an act of faith and an  $act \ of \ gamble$

— Alan Watts, Falling in Love

## 2.1 Introduction

Current integrated systems mix up components from the discrete-event and continuous-time domains. Their industrial applications require high-confidence and performant systems with short design cycles and reduced costs. System modeling and simulation help to meet these goals. However, the combination of domains and tight coupling of components create complex behaviors that can compromise simulation accuracy and speed.

To identify the constraints and open possibilities to solve this issue, we begin in Section 2.2 by describing modeling and simulation and its use cases in system design. Then, we review modeling and simulation for discrete-event systems in Section 2.3 and continuous-time systems in Section 2.4; we emphasize the levels of abstraction in behavior and structure and the simulation algorithms, factors that affect simulation accuracy and speed. In Section 2.5, we expose fixed-step synchronization and we show how it introduces an accuracy and speed trade-off. In addition, in Section 2.6 we present parallel execution for simulation acceleration. Finally, we conclude our chapter in Section 2.7.

## 2.2 Modeling and Simulation in System Design

A major task in integrated system design is to maintain high confidence in these systems while working near to their performance limits [24]. Take, for example, safety-critical applications like automated avionics, robotic surgery, braking devices, etc; any failure can cause lives to be lost. The CT and DE domains have well-developed design methods to fulfill this task. However, the combination of domains and tight coupling of components make these isolated methods insufficient. Designers seek to study the system rather than the individual parts [25–27]. Unified modeling and simulation are a means to study system behavior.

A *model* is an abstraction of the system behavior. Simulation uncovers this behavior. System modeling and simulation should support different design use cases [28]:

- The creation of *executable specifications*, which are functional or algorithmic models of behavior. Designers specify the system requirements in executable specifications that are more rigorous, congruent, and unambiguous than what a paper description could be. Then, during development, designers refine the specifications to more detailed models or convert them into integration tests [28, 29].

- The development of *virtual prototypes*, which are high-level hardware models that enable the development and test of embedded software before the actual hardware is available. Designers need high simulation speed to handle complex prototypes.

- The exploration of architectures, which is the refinement of behavior to a set of architectural elements, communication interfaces, and channels. The detailed models include non-ideal properties and implementation constraints. To this aim, designer search for a satisfactory solution regarding the required behavior and constraints. This process is iterative and simulation must be fast [30].

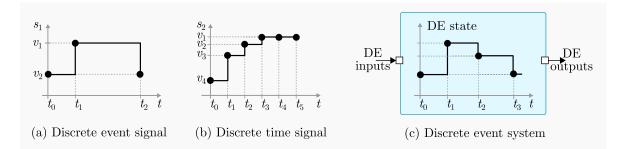

Figure 2.1: Discrete-event signals and systems

• Verification and validation, which refer to testing designs before and after tape-out, respectively [31]. Designers *verify* models during development to confirm functional correctness and other non-functional properties such as power consumption, security, safety, etc. Some verification methods include formal methods, FPGA prototyping, and simulation-based coverage-driven verification, which is currently the most commonly used [32]. After tape-out, designers *validate* component integration to guarantee that behavior meets expectations. Accurate interface modeling allows actual components to be coupled with simulated models to constitute real-time hardware-in-the-loop validation frameworks. Accuracy and speed are key.

Beyond the technical need for modeling and simulation, the business angle calls for it to shorten design cycles, risks, and costs.

DE and CT modeling and simulation have evolved independently and have given rise to unrelated languages and tools. Supporting both time domains under a unified, accurate, and fast simulation environment proves challenging.

### 2.3 Discrete-Event Modeling and Simulation

We deal with *dynamic systems* whose behavior evolves in time. They take a set of inputs, process them, update their state, and produce a set of outputs. Inputs, outputs, and states are valued functions in time, also known as *signals*. Time allows ordering behavior to distinguish between past, present, and future. Signals can be classified as discrete-event, discrete-time, and continuous-time depending on how time is modeled (*time base*).

In this section, we are interested in *discrete-event signals*, whose time base is the set of integer numbers—or any isomorphic set to the integers [33]. Figure 2.1 (a) is an example over the interval that starts at  $t_0$  and ends at  $t_2$ : the signal changes its value only in the discrete set of time points  $\{t_0, t_1, t_2\}$  (*timestamps*) that are irregularly spaced. We call each timestamp and value pair an *event*. These signals are typical of digital hardware and software, e.g., the value of a variable in a program and the content of a flip-flop in a digital circuit.

A related type are discrete-time (DT) signals, which are discrete-event signals in which the distance between time points is fixed [33]. Figure 2.1 (b) is an example. It changes its value only in the discrete set of time points  $\{t_0, t_1, ..., t_5\}$  that are regularly spaced. These

#### CHAPTER 2. MOTIVATION AND DEFINITION OF THE PROBLEM

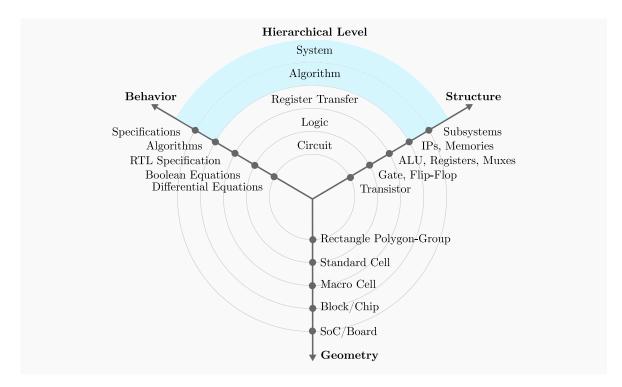

Figure 2.2: Gajski Kuhn Y-chart: levels of abstraction in digital systems adapted from [3], with the levels at which we place our contributions in blue

signals are typical of digital signal processing applications, where audio, image, and other signals are sampled at regular intervals.

*Discrete-event systems* are systems that take in DE inputs, process them, update their DE state, and produce DE outputs. Figure 2.1 (c) is an example. Discrete-event systems can process discrete-time signals because they are a special type of discrete-event signal. In cyber-physical systems, the digital components are discrete-event. These systems are *causal*, meaning that outputs depend only on past and present inputs, and not on future ones.

The behavior and structure of DE digital hardware and software models can be specified with more or less detail depending on the designer's goal.

## 2.3.1 Levels of Behavioral and Structural Abstraction in Discrete-Event Models

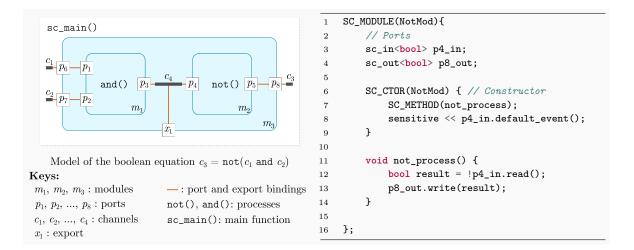

The Gajski Kuhn Y-chart in Figure 2.2 shows the levels of DE behavioral and structural abstraction [3]. Each level is defined in three axes: *behavior*—functioning in time—, *struc-ture*—constitutive elements and interconnections—, and *geometry*—size and shape properties relevant for physical placement. High-level modeling and simulation covers the system and algorithmic levels on the behavior and structure axes. In this thesis we deal with high-level DE models and their simulation.

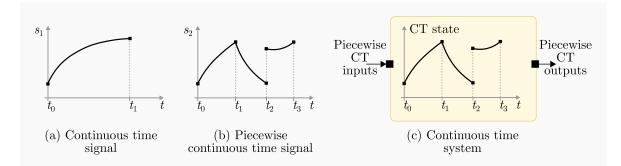

Figure 2.3: Continuous-time signals and systems

#### 2.3.2 Simulation of Discrete-Event Models

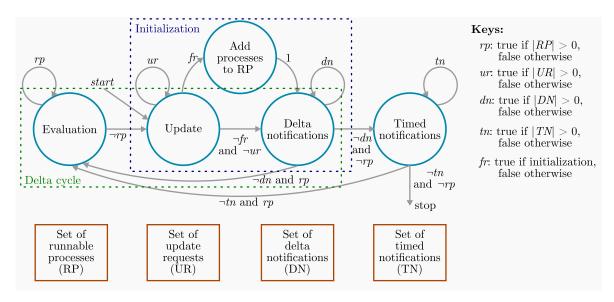

DE simulators monitor and maintain several variables: the DE simulation time  $(t_{\text{DE}})$ , the DE state, a list of pending events, and a map from the events to a set of *sensitive processes*. They advance time from event to event, processing first those with the earliest timestamp. An event triggers the execution of its sensitive processes. A process can update the system state and generate other events. The simulation ends when the list of events is empty. Execution in time order is critical to prevent *causality errors* where output events depend on future input events.

DE simulators do not advance time to intermediary points between events because, by definition, nothing happens between events. This is an important difference to continuous-time simulators, which divide the simulation intervals into steps to ensure accuracy, as we will see in Section 2.4.

We give more details on DE simulation based on specific languages and tools in Chapter 3.

### 2.4 Continuous-Time Modeling and Simulation

Continuous-time and discrete-event signals differ in their time bases. In *continuous-time* signals, the time base is the set of real numbers. Figure 2.3 (a) and (b) are two examples. Signal (a) is continuous over the interval that starts at  $t_0$  and ends at  $t_1$ . Signal (b) is piecewise continuous over the interval that starts at  $t_0$  and ends at  $t_3$ : it suddenly changes its tangent direction at  $t_1$  (corner) and its value at  $t_2$  (discontinuity).

*Continuous-time systems* are dynamic systems that take in a set of piecewise continuoustime inputs, process them, update their piecewise continuous-time state, and produce a set of piecewise continuous-time outputs. Figure 2.1 (c) is an example. In cyber-physical systems, the analog components are continuous-time. These systems are causal.

#### 2.4.1 Levels of Behavioral Abstraction in Continuous-Time Models

The electrical, mechanical, chemical, and other physical disciplines have each their particular design methods and tools. There is no agreed way to define the levels of behavioral and structural abstraction in CT systems as clearly as in DE systems. However, in general terms,

#### CHAPTER 2. MOTIVATION AND DEFINITION OF THE PROBLEM

we can classify their behavior as linear and nonlinear [34]. *Linear systems* are simple and meet the superposition principle: we can study their response to several simultaneous inputs by dealing with one input at a time. Nonlinear systems are more complex and fail to meet this principle. One example of linear systems are electronic filters that include only linear elements, such as ideal resistors, capacitors, and inductors; their mathematical models can be solved easily both analytically and by simulation. One example of nonlinear systems is fluid flows; their mathematical models, with a few exceptions, can only be solved by simulation with big computational cost. Whenever possible, designers abstract the behavior of physical systems by neglecting their nonlinearities.

The process depends to a big extent on the application and use case. Without consideration of these factors, designers are unable to decide which variables and relations are negligible and which are crucial [34, 35]. Some methods for the abstraction of behavior are:

#### 2.4.1.1 Linearization

Nonlinear systems can be considered linear around given operating points [36]. For example, classical tank models that relate the tank level from bottom to top to the rate of discharge of the tank's fluid are nonlinear. However, this relation is approximately linear around each level. For some applications, such as level regulation, it is possible to work with a linear model around the level of interest. Linearization works by approximation of the behavior.

#### 2.4.1.2 Macro-modeling

Designers can focus only on the major features and neglect part of the behavior [35]. If needed, they can later add these parts to the design. An electrical circuit model, for example, can comprise only linear electrical primitives and omit parasitic currents. Macro-modeling works by selection of the relevant behavior.

#### 2.4.1.3 Discrete-event abstraction

Some physical systems present fast physical phenomena, e.g., collisions in mechanical systems and switching in electrical circuits [8]. They give rise to nonlinear and stiff mathematical models whose parameters are often undetermined, unknown, and ununderstood. Designers can abstract away these phenomena by discrete events that split the model into two: one valid before and another valid after the phenomena. For example, instead of modeling the localized plastic deformations of two colliding balls, designers might model the collision as a discrete event in which the two balls transfer to each other the kinetic energy they had. The discrete-event abstraction works by zooming out the behavior.

These are not the only abstraction procedures, they can vary from domain to domain, and they do not always work, but when they do, they result in high-level models. These models are just accurate enough to let designers gain insight into the system rather than getting lost in the intricacies of its details. Besides, simpler models allow for performant simulations. As it is not always possible to obtain linear or simplified models, high-level simulation must support linear and nonlinear CT models and their discrete-event abstraction.

#### 2.4.2 Levels of Structural Abstraction in Continuous-Time Models

Given a behavior, designers describe the system structure with more or less granularity. Although there is little consensus on the levels of structural abstraction, we can list the mathematical and graphical representations that provide some structural information.

#### 2.4.2.1 Mathematical Representations

From the mathematical pespective, we can distinguish between models that only describe input/output relations and models that give information about the system state, internal constraints, and spatial distribution. The following representations are often used:

- **Transfer Functions**: they model input/output behavior. They are restricted to linear systems whose parameters do not vary with time (time-invariant). More formally, a transfer function is the ratio of the Laplace transform of the output of the system to the Laplace transform of the input of the system [34]. In this context, the Laplace transform is a mathematical transformation of a differential equation in time to an algebraic equation in frequency that is easier to analyze. However, transfer functions only relate inputs to outputs and omit information on the system structure. Different systems can have the same transfer function.

- State-Space Representation: it models not only the input/output behavior but also the internal system state [36]. It supports linear and nonlinear systems with time-invariant and time-varying parameters [34]; so it is more general and gives more information than transfer functions. This representation consists of a set of ordinary differential equations (ODEs) on the system state, and an output equation as a function of the state. There is a rich set of numerical methods to solve ODEs, which makes this representation ideal for simulation. We give their general form in Section 2.4.3.

- Differential Algebraic Equations (DAEs): they model the input/output behavior and the internal state in the form of implicit ODEs that describe the state dynamics. These ODEs are mixed with algebraic equations that describe physical or performance constraints on the system variables. They support linear and nonlinear time-invariant and time-varying systems. DAEs are easily obtained by applying physical laws and they are more general than ODEs, but they are also more difficult to simulate [37]. Whenever possible, ODEs are preferable.

- Partial Differential Equations (PDEs): they model the input/output behavior and the internal state not only as functions of time but also as functions of other variables, typically position. They give information about the effect of the spatial distribution of

(d) Bond graph of the mechanical spring-damper-mass system in the left

the system components on the system behavior. PDEs are more general than ODEs, but they are more complex and difficult to simulate.

• Partial Differential-Algebraic Equations (PDAEs): they model the input/output behavior and the internal state as a set of implicit PDEs and algebraic equations. They are to PDEs what DAEs are to ODEs. They are complex and difficult to simulate.

There are methods for going from a detailed representation to a less detailed one. These methods can either be manual or automatic. For example, to transform a PDE to an ODE, a designer can use the lumped matter abstraction [38]; to transform a DAE to an ODE, a computer can run Tarjan's or Pantelide's algorithms [37]. The state-space representation offers a good compromise between the level of details and ease of analysis, and we count with a rich set of numerical methods for their simulation.

#### 2.4.2.2 Graphical Representations

From the graphical representation perspective, models can reveal either the topological or the computational structure or both. Some representations are:

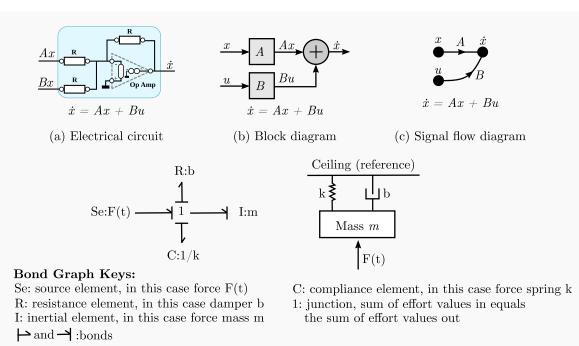

Electrical Circuit Diagrams: they model electrical systems in the form of graphs composed of electrical elements (resistors, capacitors, inductors, etc.) that are interconnected by wires that offer zero resistance, zero capacitance, and zero inductance [38]. Figure 2.4 (a) gives an example of a circuit that adds two signals A · x and B · x. Each element has an associated voltage (across quantity) and current (through quantity).

These diagrams model the topological system structure and they can be automatically transformed into a mathematical model by applying Kirchhoff's laws. Equivalent diagrams for mechanical and hydraulic systems exist and they can be analyzed by applying Newton's and fluid dynamic laws.

- Block Diagrams: they model the system as a set of functional blocks connected by directed signals (system variables). Figure 2.4 (b) gives an example of a block diagram equivalent to equation  $\dot{x} = A \cdot x + B \cdot x$ . Blocks apply mathematical operations on input signals to produce output signals. Each signal represents only an across, or a through quantity, but not both. Block diagrams model the computational but not the topological system structure. They can be transformed to transfer functions and state-space by using graph algorithms [39].

- Signal Flow Graphs: they are for the most part dual to block diagrams [39]: signals in block diagrams turn into nodes, and single input single output blocks turn into signals. Signal flow graphs are more restricted because they have no dual for blocks with multiple inputs and outputs. Nodes in signal flow graphs represent either an across or a through quantity, but not both. As block diagrams, they model the computational but not the topological system structure. Figure 2.4 (c) gives an example for equation x̂ = A ⋅ x + B ⋅ x. They are mostly used in control engineering and can be transformed to transfer functions and state-space by using Mason's rule [40].

- Bond Graphs: as opposed to the previous three, they model both, the computational and topological system structure. To this end, they represent systems by bonds that connect single port, double port, and multi-port elements. Each bond has one associated effort (across quantity) and flow (through quantity) variable that give the power (energy flow) of the system when multiplied together [39]. Bond graphs can represent physical systems and components from different disciplines based on energy analogies. Figure 2.4 (d) gives an example of a bond graph of a mechanical system. Bond graphs can be converted to state-space using graph algorithms.

These are not the only representations. Each physical discipline may model systems in one or more graphical forms. Going from a graphical to a mathematical model imposes additional computational costs.

Among these mathematical and graphical representations, the state-space representation is the most used because it is general enough to model relevant physical systems without omitting details about their internal structure. There is a rich set of numerical methods to solve state-space models. More detailed representations can be transformed to state-space either manually by the designer or automatically by the simulator. Let us define it more formally.

Figure 2.5: Numerical solution of an ordinary differential equation, adapted from [4]

#### 2.4.3 State-Space Representation of Continuous-Time Models

We are concerned with physical system models defined in the form [41]:

$$\begin{aligned} \dot{\boldsymbol{x}} &= f(\boldsymbol{x}, \boldsymbol{u}, t_{\text{CT}}) \\ \boldsymbol{y} &= g(\boldsymbol{x}, \boldsymbol{u}, t_{\text{CT}}) \\ \boldsymbol{x}(t_{\text{CT}_0}) &= \boldsymbol{x}_{\text{o}} \end{aligned}$$

(2.1)

where  $\boldsymbol{x} \in \mathbb{R}^n$  is the CT state, with  $n \in \mathbb{N}$  and n > 0,  $\dot{\boldsymbol{x}} \in \mathbb{R}^n$  is the derivative of the CT state,  $\boldsymbol{u} \in \mathbb{R}^p$  is the CT input, with  $p \in \mathbb{N}$ ,  $\boldsymbol{y} \in \mathbb{R}^q$  is the CT output, with  $q \in \mathbb{N}$ ,  $t_{\text{CT}} \in \mathbb{R}$  is the CT time, f and g are either linear or nonlinear functions,  $t_{\text{CT}_o}$  is the initial CT time,  $\boldsymbol{x}_o$  are the system initial conditions.

From Equation (2.1), we can compute the dynamics of the CT state and the CT outputs given the system inputs and initial conditions by using numerical integration methods.

#### 2.4.4 Simulation of Continuous-Time Models

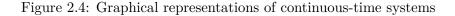

CT simulators monitor and maintain the CT simulation time  $(t_{\text{CT}})$  and state  $(\boldsymbol{x})$ . Given Equation (2.1), the task of a CT simulator executed on a digital computer is to compute a finite set of points  $\boldsymbol{w}_0, \boldsymbol{w}_1, \boldsymbol{w}_2, ... \boldsymbol{w}_N$  at the time instants  $t_0, t_1, t_2, ..., t_N$  that approximates the exact state evolution. The system output  $\boldsymbol{y}$  can be derived from it [42].

The numerical methods differ on how to approximate these points. The simplest of them is Euler's method, which defines the approximation sequence as:

$$w_0 = x_0$$

$$w_{i+1} = w_i + h \cdot f(w_i, u, t_i)$$

(2.2)

for i = 0, 1, ..., N - 1. Variable h is known as the *integration step*. Figure 2.5 (a) shows an example of the computation of the first step  $(\boldsymbol{w_1} = \boldsymbol{w_0} + h \cdot f(\boldsymbol{w_0}, \boldsymbol{u}, t_0))$  and Figure 2.5 (b) shows the approximated solution after computing N steps. In general, the smaller the

integration step, the more points in the interval  $[t_0, t_N]$  and the more precise the approximation but the longer it takes to compute.

While in DE simulation nothing happens between consecutive events, in CT simulation anything can happen in any non-zero length interval, so the CT simulators must divide these intervals into steps of size h to ensure accurate enough solutions.

Euler's method should not be used in practice because it introduces big errors in the approximation. Multiple other methods reduce the error. They differ on how to compute each step  $w_{i+1}$  [42]:

- Higher-order methods: based on Taylor series expansions, they use higher-order derivatives  $(\dot{f}, \ddot{f}, etc.)$  instead of just f. Runge-Kutta methods are an example.

- Varying step methods: they modify the step size *h* along with simulation depending on the error at each step. The Runge-Kutta Dormand-Prince method is an example.

- Multistep methods: they base the computation on multiple preceding steps ( $w_{i-1}$ ,  $w_{i-2}$ , etc.) instead of just  $w_i$ . The Adams-Moulton and Adams-Bashfort methods are two examples.

There is a rich set of numerical methods to solve ODEs and their selection depends on the application accuracy and speed needs.

# 2.5 The Problem of Synchronization in Continuous-Time and Discrete-Event Simulation

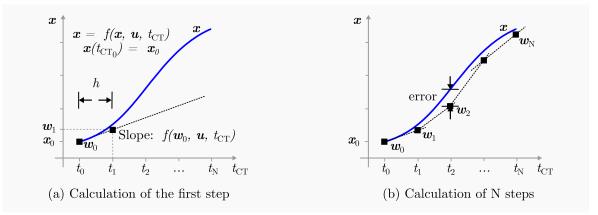

In cyber-physical systems and their simulations, the CT and DE parts interact to exchange data. But, as explained in Section 2.3 and Section 2.4, CT and DE signals are different. We need a way to convert one type of signal to the other. Sampling CT signals at fixed timesteps is common for signal conversion. Sampling results in DT signals. Figure 2.6 (a) shows the process. From bottom to top, the CT signal x is sampled at timepoints  $t_1$ ,  $t_2$ ,  $t_3$ , etc. that are separated by a timestep of size  $T_s$  to produce the DT signal x'. This signal is interpreted by the DE system, which can react to the sampled values by changing its state q, as it does at time  $t_2$ .

Similarly, a DE signal can be transformed to a DT signal from which a CT signal can be reconstructed. Figure 2.6 (b) shows the process. From top to bottom, signal q is sampled at timepoints  $t_1$ ,  $t_2$ ,  $t_3$ , etc. that are separated by a timestep of size  $T_s$  to produce the DT signal q'. This signal is interpreted by the CT system, which can react to the sampled values by changing the evolution of its state x, as it does at time  $t_2$ .

During simulation, these points allow the CT and DE parts to synchronize their local times ( $t_{\rm CT} = t_{\rm DE}$ ). Time synchronization allows a consistent global simulation time advance even if the CT and DE time bases are different. The global simulation time can be taken to be either  $t_{\rm DE}$  or  $t_{\rm CT}$  or other time depending on the simulation engine.

Figure 2.6: Continuous-time and discrete-event synchronization through discrete-time signals

However useful they might be, DT signals are a form of time abstraction and they can introduce accuracy problems. The fixed timesteps in DT signals constraint their capacity to encode important information in the original signals. Figure 2.6 (b) shows an example: an event in q occurs right after  $t_1$ , but it is not reflected in q' until  $t_2$ , and consequently, its intended effect on the evolution of x is delayed. Other examples of information that cannot be encoded are corners and discontinuities in piecewise continuous signals. In general, all that happens between timepoints is either omitted or delayed.

One way to reduce errors is to decrease the timestep. Figure 2.6 (c) shows that half the timestep creates a smaller delay in x's reaction. But this accuracy gain has a speed cost.

Small timesteps introduce too many synchronization points, as seen in Figure 2.6 (c). Most of these points are not useful, the only relevant information being the event between  $t_2$  and  $t_3$ . But each one of them has a computational cost that accumulates. DT signals bring in an accuracy/speed trade-off: either the timestep is small, the simulation accurate but slow, or the timestep is large, the simulation possibly inaccurate, but fast.

While the level of abstraction in models depends on the use case, synchronization depends on the simulation engine. The CT/DE synchronization plays a major role in simulation accuracy and speed.

## 2.6 Parallel Simulation

The complexity of the simulated systems and the ubiquity of networked processors and multi-threaded environments justify the study of parallel simulation algorithms for combined CT/DE simulation acceleration.

#### 2.6.1 Parallel Discrete-Event Simulation

The need to execute discrete events in time order to preserve system causality brings about sequential DE simulators. They are fast enough when processing few events. However, in complex models, the number of events can be very high. We can count by tens of thousands the instructions executed by a microprocessor model that runs a bare-metal control algorithm for a few seconds, for example [43]. Let alone simulations of real-time operating systems: executing millions of events sequentially is slow.

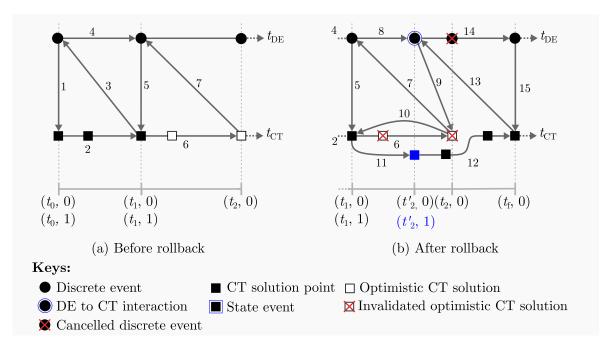

In parallel DE simulation, the goal is to process the events in parallel irrespective of their timestamps while preserving causality [44]. There are two major approaches to this aim. *Conservative* ones avoid causality errors by executing in parallel two events only if they do not affect each other; they require a way to identify the causality relations between events, which is difficult in general. *Optimistic* ones allow the execution of events in the future, detect the causality errors, and recover the simulation by rolling back the system state and remaking computations in the right order; they require to save the system state, which can be huge. Which strategy produces faster simulations depends on the application.

#### 2.6.2 Parallel Continuous-Time Simulation

Similar to DE simulation, the motivation of parallel CT simulation derives from system complexity: their models can be too big or take too long to execute on a single processor. These complex models may implement ODEs whose evaluation is expensive over long integration intervals and that may involve many state variables.

The problem of parallel CT simulation can be treated at multiple resolutions [45]: parallelism across the method, which parallelizes the computations required to perform a single integration step of a given numerical method; parallelism across the steps, which parallelizes the computation of several integration steps of a given numerical method; and parallelism across the system, which parallelizes the solution of the different parts of a CT model. The selected level depends on the application.

In general, parallel simulation works best when models show a degree of data parallelism or when the simulation algorithms consist of instructions that are independent of each other. But this is rarely the case. In Chapter 3, we study other more specific problems and the stateof-the-art parallel simulation strategies to use them for CT/DE simulation acceleration.

#### CHAPTER 2. MOTIVATION AND DEFINITION OF THE PROBLEM

# 2.7 Conclusions

In this thesis, our goal is to accelerate the modeling and simulation of cyber-physical systems to support system design use cases that demand high simulation accuracy and speed. These two aspects depend on many factors: the level of behavioral abstraction, the level of structural abstraction, the time abstraction, and the simulation and synchronization algorithms.

To this aim, we are interested in constraining the models of the different system components to be at high level of abstraction. In this context, DE models can be either at the system or algorithmic levels. CT models can be linear and nonlinear, they can abstract away fast physical phenomena by discrete events, and they are specified in state-space representation as it offers good structural details and ease of simulation. However, it is also important to consider the possibility of specifying CT graphical representations, as they ease modeling, are used in multiple physical disciplines, and can be automatically transformed to state-space.

Having defined the levels of behavioral and structural abstraction of our interest, we will focus on the exploration of the time abstraction, the simulation and synchronization algorithms, and the parallelization as possible spaces for the acceleration of high-level CT/DE simulation. In particular, we deal with the following questions:

- 1. What CT/DE synchronization strategies other than the intermediary discrete-time representations apply to high-level simulation and how can they be exploited to accelerate simulation?

- 2. How to support the simulation of models from particular physical disciplines in the form of electrical circuits and other graphical representations while still using a generic CT/DE simulation engine?

- 3. How to apply parallel simulation algorithms to accelerate CT/DE simulation?

# Chapter 3: State of the Art

## Contents

| 3.1        | Intr  | oduction                                                                                | <b>20</b> |

|------------|-------|-----------------------------------------------------------------------------------------|-----------|

| 3.2        | Dire  | ect Continuous-Time and Discrete-Event Interactions                                     | <b>20</b> |

| 3.3        | Mod   | lel of Time                                                                             | <b>23</b> |

|            | 3.3.1 | Superdense Time                                                                         | 23        |

|            | 3.3.2 | Implementation of a Superdense Time Model in a Digital Computer                         | 23        |

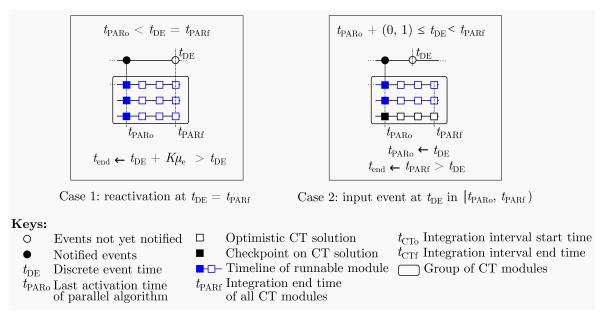

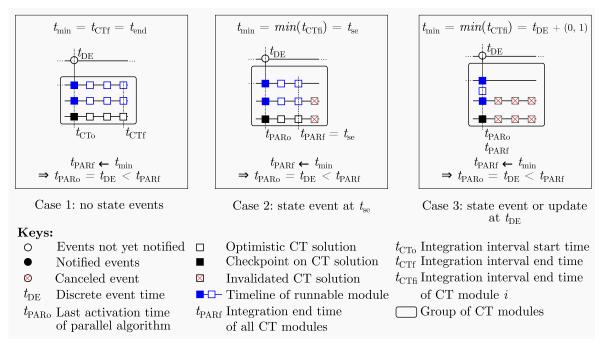

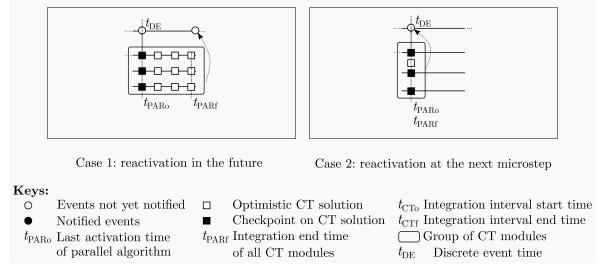

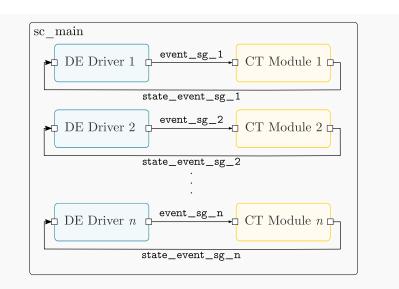

|            | 3.3.3 | Difference between Discrete and Superdense Time                                         | 24        |