# Performance optimization for the LHCb experiment

Arthur Hennequin

### ▶ To cite this version:

Arthur Hennequin. Performance optimization for the LHCb experiment. Hardware Architecture [cs.AR]. Sorbonne Université, 2022. English. NNT: 2022SORUS031. tel-03640612

## HAL Id: tel-03640612 https://theses.hal.science/tel-03640612

Submitted on 13 Apr 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

### Spécialité **Informatique**

École doctorale Informatique, Télécommunications et Électronique (Paris)

## Présentée par **Arthur Hennequin**

# Pour obtenir le grade de **DOCTEUR de SORBONNE UNIVERSITÉ**

Sujet de la thèse:

Performance optimization for the LHCb experiment

présentée le 31 Janvier 2022

devant le jury composé de:

| [Directeur de thèse] | Lionel   | LACASSAGNE | LIP6  | Sorbonne Université |

|----------------------|----------|------------|-------|---------------------|

| [Rapporteur]         | François | IRIGOIN    | CRI   | Mines ParisTech     |

| [Rapporteur]         | Denis    | BARTHOU    | INRIA | INRIA Bordeaux      |

| [Examinateur]        | Stef     | GRAILLAT   | LIP6  | Sorbonne Université |

| [Examinateur]        | Caroline | COLLANGE   | INRIA | INRIA Rennes        |

| [Examinateur]        | Vladimir | GLIGOROV   | LPNHE | Sorbonne Université |

## Abstract

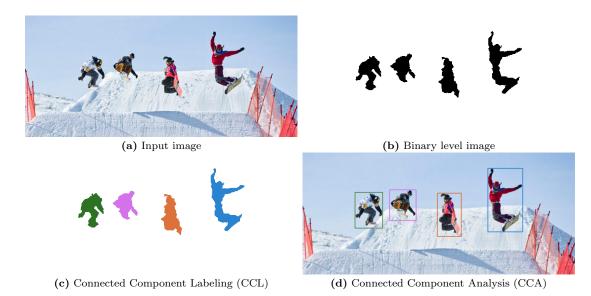

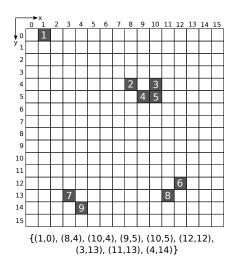

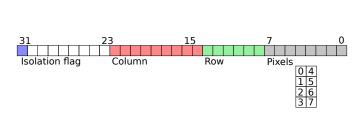

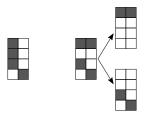

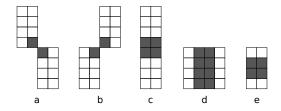

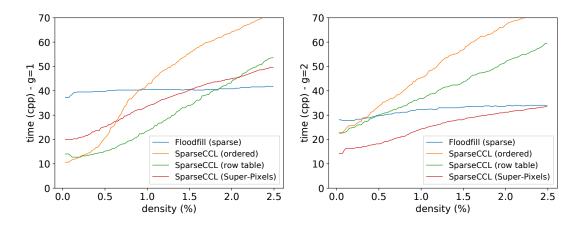

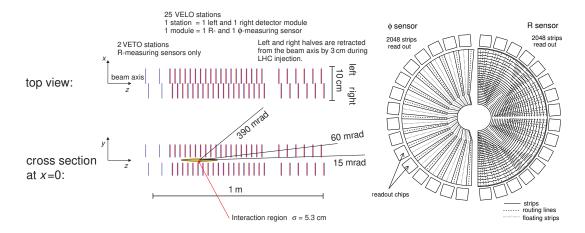

The LHCb experiment, at CERN, is preparing a major upgrade of its detector and a change from an hardware-based to a fully software-based trigger system. It is now facing the challenge of being able to process incoming events at a rate of 30 million events per second. To cope with this massive data input, the software must be optimized to use the processing power of the filtering farm more efficiently. This thesis focus on the first algorithm of LHCb's High Level Trigger software: the Vertex Locator (VELO) reconstruction algorithm. The VELO is the first detector encountered by particles, directly surrounding the interaction region. Its goal is to find the initial track candidate that are then followed through the other layers of the LHCb detector with a good enough resolution that they could also be used to locate the origin of the collisions. The first step of this algorithm is to prepare the data by grouping pixels of the silicon sensors into hits; this process is called connected component analysis (CCA). This thesis presents multiple new CCA algorithms for both CPU and GPU architectures. The first algorithm, HA4, was developed at the very start of this thesis and improved the state-of-the-art in connected component labeling on GPUs, as well as being the first efficient implementation of connected component analysis on GPUs. The second algorithm is a GPU port of the FLSL SIMD CPU algorithm, inspired by the LSL algorithm. FLSL on GPUs improved upon HA4 by reducing the memory accesses conflicts that are especially presents on new hardware with a lot of cores. Along with FLSL, two other optimisations aimed at further reducing conflicts are presented and evaluated. On CPU, two new algorithms were made for this thesis. The first one is a modification of the classic Rosenfeld algorithm to use SIMD. The second one is a new algorithm, named SparseCCL, which takes advantage of the sparsity of the input images. A new VELO reconstruction algorithm using SIMD is presented, that enable LHCb to process events in real time and improve the quality of the reconstruction. The SIMDWrapper library, developed for the new VELO algorithm, is now part of LHCb's software and is used in other algorithms.

# Acknowledgements

During my time as a CERN doctoral student I have often relied on the support and guidance of many people whom I would like to thank in the following:

Lionel Lacassagne for supervising my PhD thesis. I am particularly grateful for his detailed advices and encouragements during my master and PhD years.

François Irigoin and Denis Barthou for accepting to review this thesis manuscript and providing valuable suggestions.

Caroline Collange and Stef Graillat for being part of my jury.

Florian Lemaitre for his precious help and paving the way for efficient use of SIMD in LHCb's software.

Vladimir Gligorov, Ben Couturier and Sebastien Ponce for supervising my work in LHCb.

Gvozden Nešković from the Frankfurt Institute for Advanced Studies for lending me an AMD EPYC "Rome" 7742 system.

The Physics Data Processing group from Nikhef and in particular Tristan Suerink, for lending us the AMD EPYC "Rome" 7702 system used in VELO benchmarks.

E4, especially Marco Cicala, and Andrea Chierici from CNAF for lending me the AMD EPYC "Rome" 7302, 7452 systems as well as the Xeon Platinum 9242 system used in HLT benchmarks.

Eckardt Kehl, Rafael Kazumiti Morizawa, Lutz Weischer, Chris Derson, Frank Fijneman, Pierre Lagier and John Wagner from Fujitsu for giving me access to an A64FX and providing me with useful advices.

Christoph, Sascha, Niklas, Olli, Alex, Rosen, Marco, Victor, Conor, Louis, Andre, Michel, Laurent, Dominik, Claire, Niko, Concezio for welcoming me at CERN and all the useful discussions we had about the LHCb software.

Lastly, I would like to thank my family for their support, John for his help with the English of this manuscript and Clara for her patience during the writing of this manuscript and following me in this adventure.

# Contents

| In | ${f trod}{f u}$ | action                                   | 6  |

|----|-----------------|------------------------------------------|----|

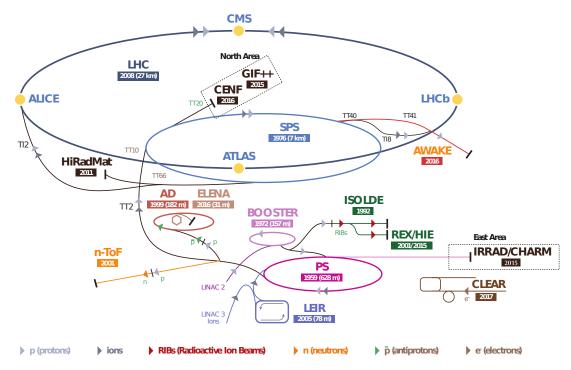

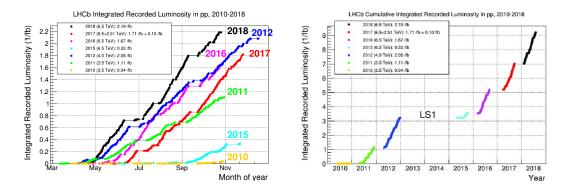

| 1  | The             | LHCb experiment                          | 8  |

|    | 1.1             | Introduction                             | 8  |

|    | 1.2             |                                          | 8  |

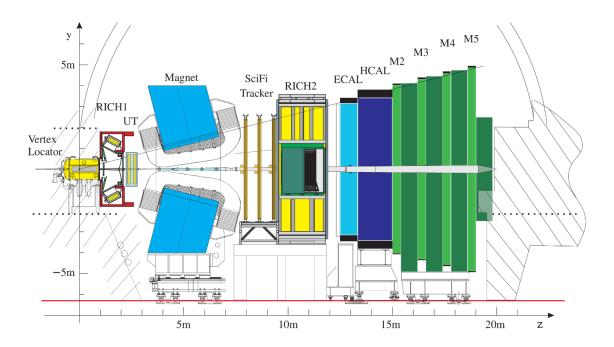

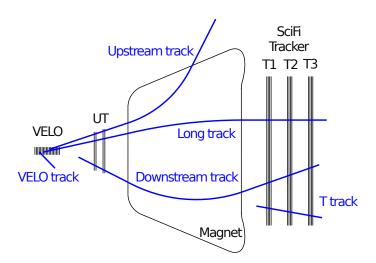

|    | 1.3             | The LHCb detector                        | 10 |

|    |                 |                                          | 13 |

|    |                 | 1.3.2 Upstream Tracker                   | 14 |

|    |                 | 1.3.3 Scintillating Fibre Tracker        | 15 |

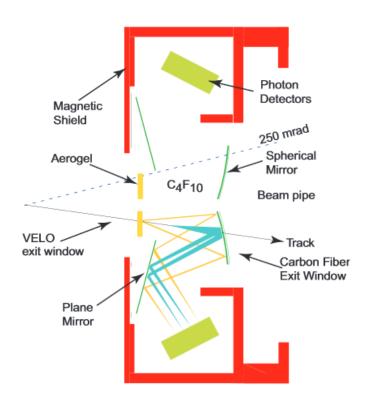

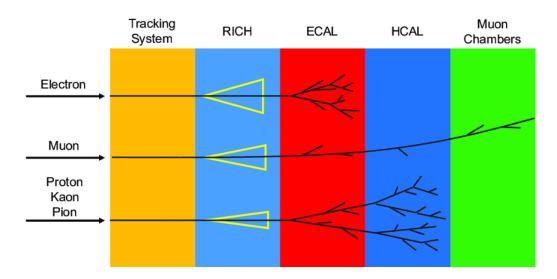

|    |                 | 1.3.4 Ring Imaging Cherenkov Detectors   | 17 |

|    |                 | 1.3.5 Calorimeters                       | 18 |

|    |                 | 1.3.6 Muon stations                      | 18 |

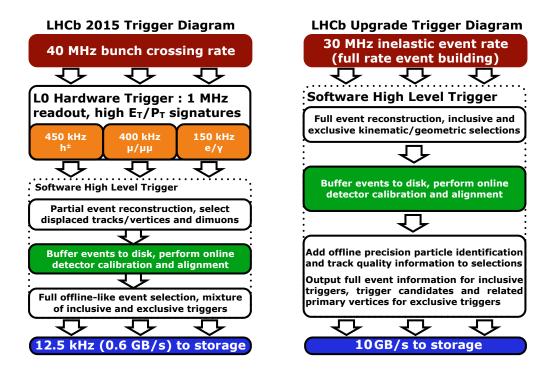

|    | 1.4             | The High Level Trigger                   | 19 |

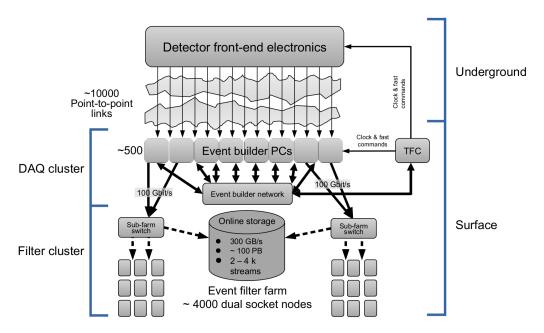

|    |                 | 1.4.1 Event Building                     | 20 |

|    |                 | 1.4.2 HLT1                               | 20 |

|    |                 | 1.4.3 HLT2                               | 21 |

|    |                 |                                          | 21 |

|    | 1.5             | Conclusion                               | 22 |

| _  | _               |                                          |    |

| 2  |                 |                                          | 23 |

|    | 2.1             |                                          | 23 |

|    | 2.2             |                                          | 23 |

|    |                 |                                          | 26 |

|    |                 | V                                        | 27 |

|    |                 | V                                        | 28 |

|    | 2.3             | 0                                        | 30 |

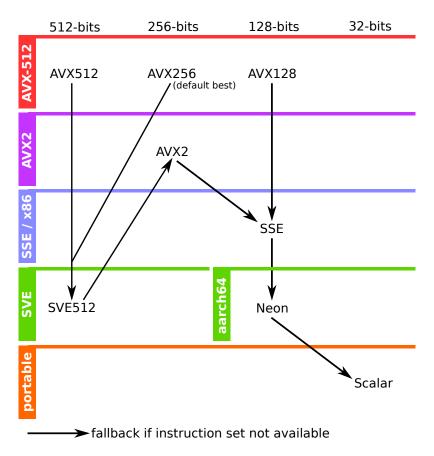

|    |                 | 2.3.1 Instruction sets                   | 32 |

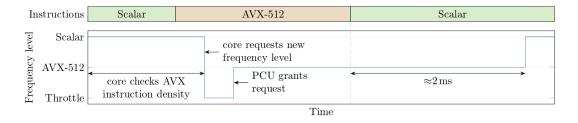

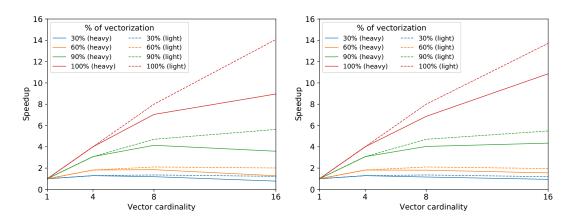

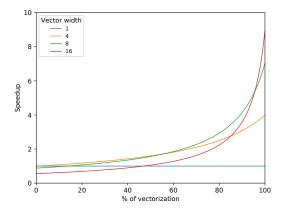

|    |                 | 2.3.2 SIMD speedup and frequency scaling | 35 |

|    | 2.4             |                                          | 36 |

|    |                 | $\circ$                                  | 36 |

|    |                 | 1                                        | 41 |

|    |                 | 2.4.3 Instruction emulation              |    |

|    | 2.5             | Conclusion                               | 42 |

| 3  | Para            | allelism on GPU                          | 44 |

| -  | 3.1             | Introduction                             | 44 |

|    | 3.2             |                                          | 44 |

|    | 3.3             |                                          | 46 |

|    | 3.4             |                                          | 49 |

| 3.5 | Shared memory optimisations                                                                           | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.6 | Warp-level programming                                                                                | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.7 | Conclusion                                                                                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Con | nected Component Analysis                                                                             | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                                                                       | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                                                                       | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7.2 | - •                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                                                                       | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                                                                       | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19  |                                                                                                       | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.5 | · - / -                                                                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | - ~                                                                                                   | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 0 0                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 9                                                                                                     | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 1                                                                                                     | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 0 1 1                                                                                                 | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4 4 | ±                                                                                                     | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.4 |                                                                                                       | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 1                                                                                                     | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                                                                       | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | · · · · · · · · · · · · · · · · · · ·                                                                 | 75<br>76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | ±                                                                                                     | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                                                                       | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.5 |                                                                                                       | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                                                                       | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                                                                       | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 8 8                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | <u> </u>                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | •                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.6 |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                                                                       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 1                                                                                                     | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | v -                                                                                                   | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | •                                                                                                     | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.7 | Conclusion                                                                                            | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VEI | LO reconstruction algorithm                                                                           | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.1 | Introduction                                                                                          | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

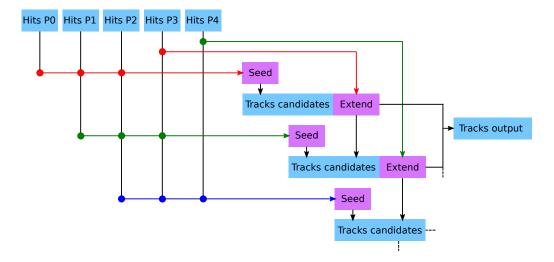

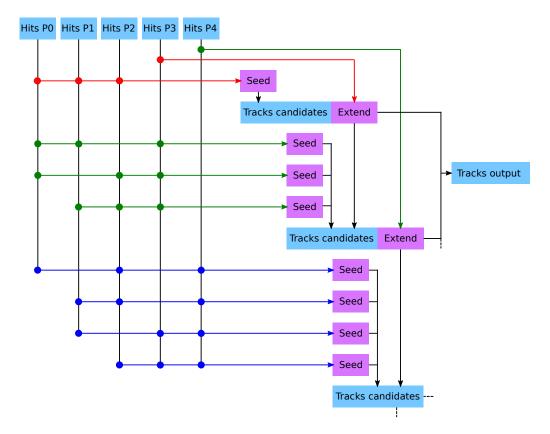

| 5.2 | Tracking algorithms                                                                                   | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.3 | Evolution of the VELO detector and algorithms                                                         | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 5.3.1 Reconstruction in the Run 1 and 2 VELO detector                                                 | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                                                                       | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.4 |                                                                                                       | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | · · · · · · · · · · · · · · · · · · ·                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

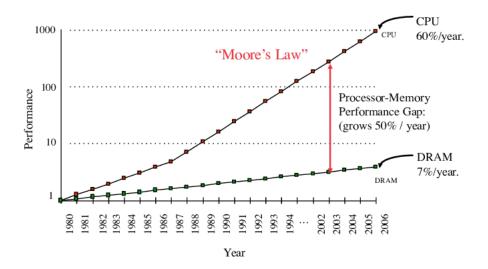

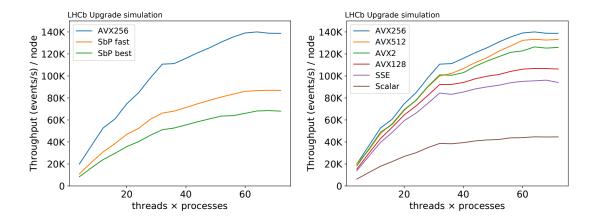

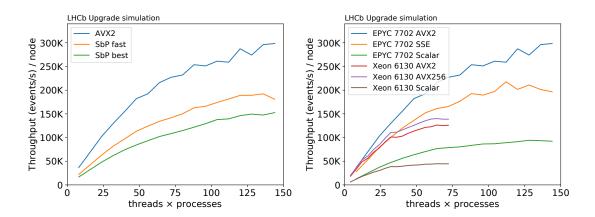

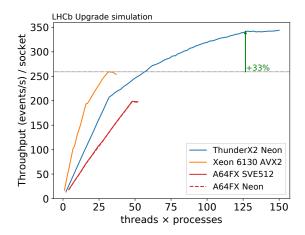

| 5.5 | Benchmarks                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |