# Analysis of space and atmospheric radiation-induced effects on memory devices

Lucas Matana Luza

#### ▶ To cite this version:

Lucas Matana Luza. Analysis of space and atmospheric radiation-induced effects on memory devices. Electronics. Université Montpellier, 2021. English. NNT: 2021MONTS100. tel-03641803

#### HAL Id: tel-03641803 https://theses.hal.science/tel-03641803

Submitted on 14 Apr 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

En Systèmes Automatiques et Microélectroniques

École doctorale : Information, Structures et Système (I2S)

Unité de recherche : Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier (LIRMM)

# Étude des Effets Induits par la Radiation Spatial et Atmosphérique sur des Mémoires Électroniques

(Analysis of Space and Atmospheric Radiation-Induced Effects on Memory Devices)

#### Présentée par Lucas MATANA LUZA Le 14 decembre 2021

Sous la direction de Luigi DILILLO

#### Devant le jury composé de

| Luigi DILILLO, Chargé de Recherche, Univ. Montpellier                 | Directeur de thèse |

|-----------------------------------------------------------------------|--------------------|

| Mihalis PSARAKIS, Professeur, Univ. Piraeus                           | Rapporteur         |

| Luis Alfonso ENTRENA ARRONTES, Professeur, Univ. Carlos III de Madrid | Rapporteur         |

| Lionel TORRES, Professeur, Univ. Montpellier                          | Président du jury  |

| Laurent DUSSEAU, Professeur, Univ. Montpellier                        | Examinateur        |

| Alberto BOSIO, Professeur, École Centrale de Lyon                     | Examinateur        |

| Edgar Ernesto SÁNCHEZ SÁNCHEZ, Professeur, Politecnico di Torino      | Examinateur        |

| Viyas GUPTA, Docteur, Agence Spatiale Européenne (ESA)                | Examinateur        |

#### Résumé

Le rayonnement est défini comme l'émission ou la transmission d'énergie sous forme d'ondes ou de particules, qui peuvent être ionisantes ou non ionisantes. L'interaction entre le rayonnement et la matière peut générer différentes réactions, qui peuvent varier en fonction des propriétés de la particule (type, énergie cinétique, masse et charge) et de la matière ciblée (semi-conducteurs dans le cadre de cette thèse). L'exposition de composants électroniques à des environnements avec une présence significative de rayonnement peut conduire à ce type d'interaction et, par conséquent, à une variété d'effets qui peuvent affecter considérablement la fiabilité des systèmes électroniques.

Lors de la conception de dispositifs et de systèmes électroniques, la prise en compte des effets des rayonnements est fondamentale pour les applications dans des environnements hostiles. Par exemple, dans les systèmes avioniques et spatiaux, ces effets sont largement étudiés pour garantir la haute fiabilité des composants et fournir les informations nécessaires pour les décisions de conception. Les préoccupations liées aux rayonnements ont commencé à être prises en compte au début de l'ère spatiale.

Les rayonnements ionisants peuvent induire des effets dans différents dispositifs, et plusieurs travaux ont montré que les mémoires électroniques sont l'une des principales causes d'erreur dans les systèmes. De plus, en raison de leur nature, les mémoires ont la capacité intrinsèque de stocker la trace des fautes induites par les rayonnements, comme le Single-Bit Upset (SBU), ce qui fait de ces dispositifs le meilleur candidat pour étudier les événements singuliers.

Le premier sujet introduit par la thèse est une étude sur les effets induits par les ions lourds sur une mémoire Flash de type NAND. Cette étude est basée sur plusieurs campagnes d'irradiation avec une large gamme d'énergies. Les résultats ont révélé différents mécanismes de défaillance, notamment des SBUs, des petits groupes d'erreurs, des fautes dans le registre et des fautes affectant une ou plusieurs colonnes de la mémoire. La section efficace a été calculée pour chaque type de faute, et leurs causes ont été discutées.

Ensuite, une étude sur les effets de la radiation neutronique (spectres thermiques et atmosphériques) sur une DRAM auto-rafraîchissante est présentée. Des méthodes de test statique et dynamique ont été utilisées pour définir la réponse du dispositif sous faisceau

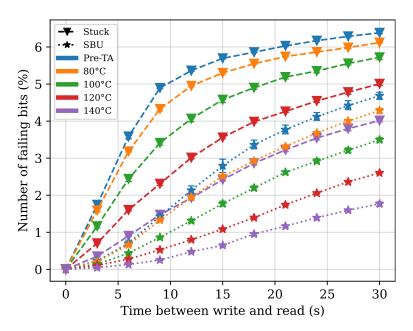

neutronique. Dans ce manuscrit, les résultats expérimentaux de deux campagnes de tests sont présentés, avec l'identification de différents modèles de faute, comme les SBUs, bits collés et blocs d'erreurs. Ces fautes ont été étudiées et caractérisées avec le calcule de la section efficace, du taux d'erreurs et l'étude des bitmaps. Une analyse du temps de rétention des cellules affectées a été réalisée, montrant une différence d'efficacité entre le mécanisme d'autorafraîchissement et une véritable opération de lecture. De plus, une corrélation du mécanisme de défaillance qui génère à la fois des SBUs et des bits collés est également proposée. Finalement, les effets de réparation du recuit à haute température ont été étudiés dans des tests post irradiation.

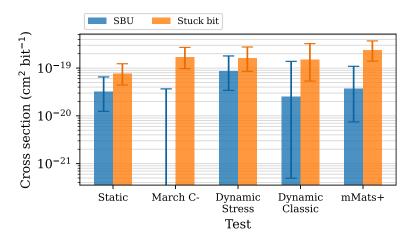

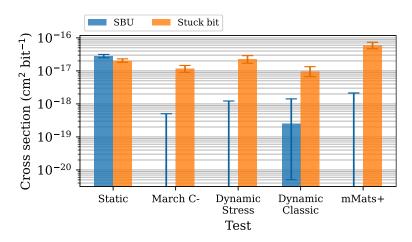

Après, ce manuscrit présente aussi une étude comparative sur les effets induits par les neutrons sur les SDRAM produites avec trois nœuds technologiques différents. Les résultats ont révélé la présence de SBUs et de bits collés dans les mémoires, montrant une sensibilité plus élevée pour la génération la plus ancienne et des résultats similaires pour les deux autres modèles étudiés.

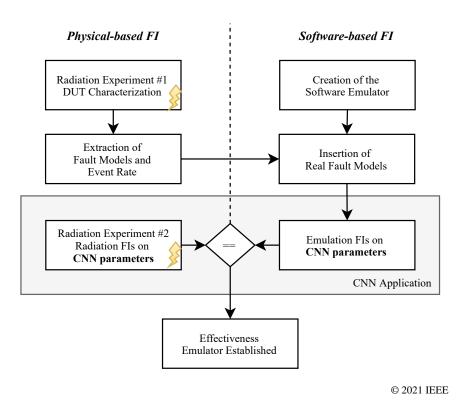

Enfin, une procédure est présentée afin d'évaluer la fiabilité des applications basées sur réseau de neurones convolutifs (CNN). Dans cette optique, cette étude propose d'utiliser des modèles de défauts réalistes extraits des tests de rayonnement comme entrée pour un émulateur logiciel qui effectue l'injection de défauts dans le système informatique dans lequel le CNN est implémenté.

**Mots-clés:** Radiation, effets singuliers, DRAM, mémoire Flash, injection de fautes, réseaux de neurones

#### **Abstract**

Radiation is defined as the emission or transmission of energy as waves or particles, which can be either ionizing or non-ionizing. The interaction between the radiation and the matter can generate different reactions, which may vary depending on the properties of the particle (type, kinetic energy, mass, and charge), and the target (semiconductors in this thesis scope). The exposition of electronics components to environments with a significant presence of radiation may lead to this kind of interaction and, consequently, to a variety of effects that can drastically affect the reliability of electronic systems.

When designing electronic devices and systems, considering radiation effects is fundamental for applications in harsh environments. For instance, in avionics and space systems, these effects are extensively studied to ensure the high reliability of the components and provide the needed insight for design decisions. The concerns related to radiation started to be noted at the beginning of the space era.

Ionizing radiation may induce effects in different types of devices, and many works have shown that memories are one of the highest contributors to soft errors in systems. Furthermore, due to their nature, memories have the intrinsic capability of storing radiation-induced fault tracks, e.g., Single-Bit Upsets (SBUs), making these devices the best candidate for studying soft errors.

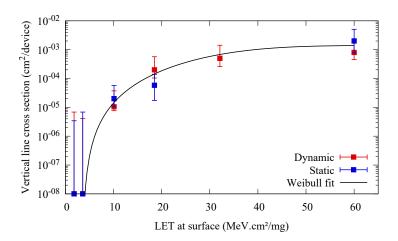

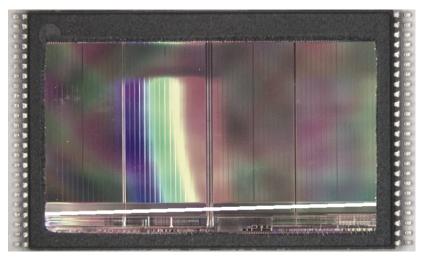

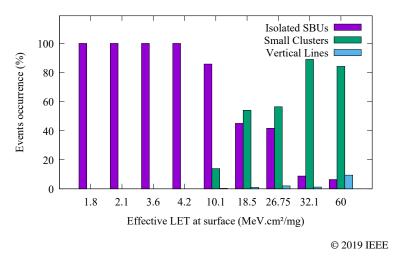

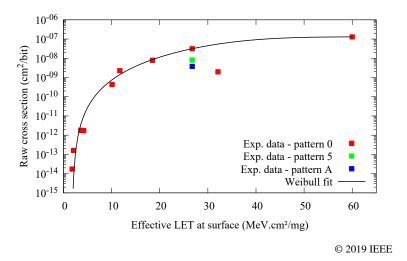

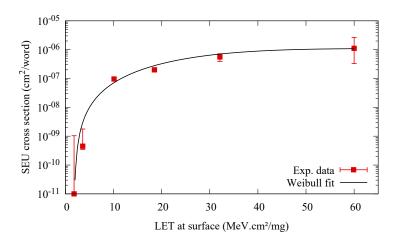

The first topic introduced by the thesis is a study on the heavy-ion induced effects on a Single-Level Cell NAND Flash. This study is based on several irradiation test campaigns with a wide range of heavy-ions energies. The results revealed different failure mechanisms, including Single-Event Upsets, small clusters of errors, data register upsets, and a columnwise failure mode. Cross section was calculated for each of these failure modes, and their causes were discussed.

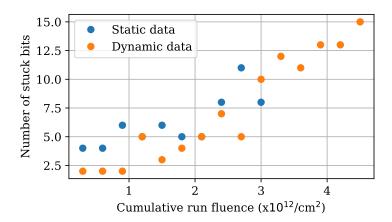

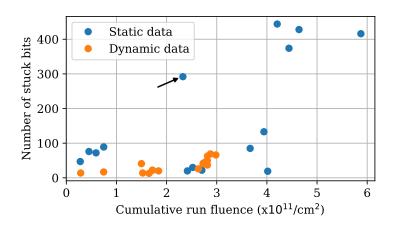

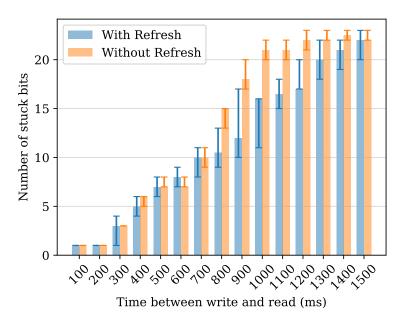

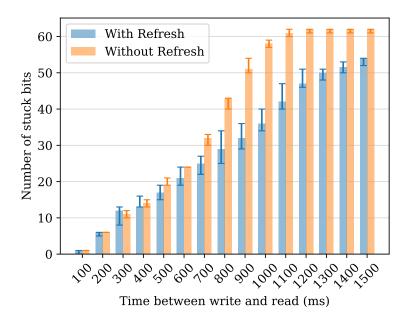

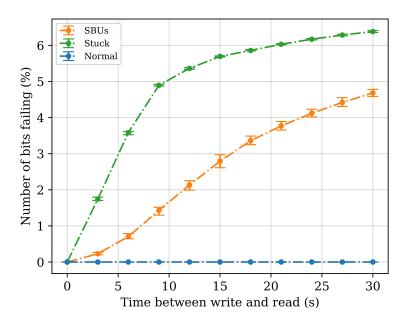

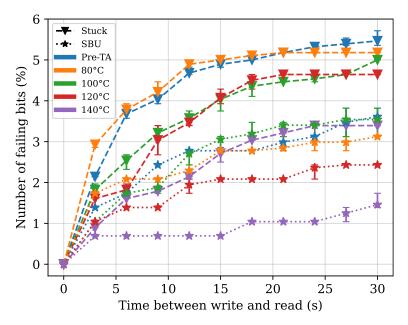

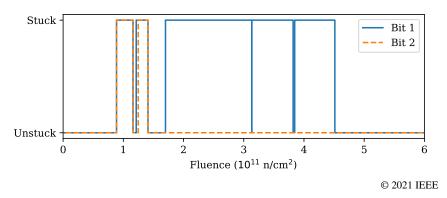

Then, a study on the effects of neutron irradiation (thermal and atmospheric-like spectra) on a self-refresh DRAM is presented. Static and dynamic test methods were used to define the response of the device under irradiation. In this manuscript, experimental results from two different test campaigns are presented, with the identification of SBUs, stuck bits, and block errors. These faults were investigated and characterized by event cross section, softerror rates, and bitmaps evaluations. An analysis of the damaged cells' retention time was

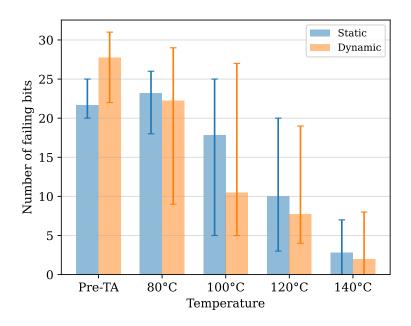

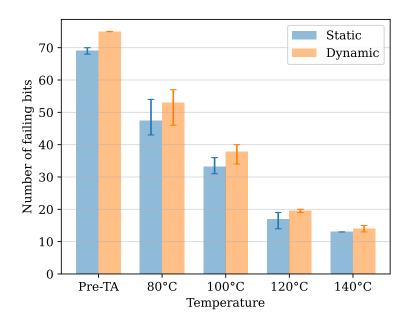

performed, showing a difference between the self-refresh mechanism and a read operation. Additionally, a correlation of the fault mechanism that generates both SBUs and stuck bits under neutron irradiation is also proposed. Furthermore, high-temperature annealing was studied in post-radiation tests.

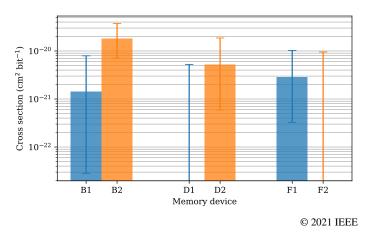

Following, this thesis presents a comparative study on the neutron-induced effects on SDRAMs produced with three different technology nodes. The results revealed the occurrence of SBUs and stuck-bits in the memories, showing higher sensitivity for the oldest generation and similar results for the other two models.

Finally, a framework is presented to assess the reliability of Convolutional Neural Network (CNN) applications. In this light, this study proposes using realistic fault models retrieved from radiation tests as input for a software emulator that performs fault injection in the computing system in which the CNN is implemented.

**Keywords:** Radiation, single-event effects, DRAM, Flash memory, fault injection, neural networks

#### Résumé Substantiel en Français

Le rayonnement est défini comme l'émission ou la transmission d'énergie sous forme d'ondes ou de particules, qui peuvent être ionisantes ou non ionisantes. L'interaction entre le rayonnement et la matière peut générer différentes réactions, qui peuvent varier en fonction des propriétés de la particule (type, énergie cinétique, masse et charge) et de la matière ciblée (semi-conducteurs dans le cadre de cette thèse). L'exposition de composants électroniques à des environnements avec une présence significative de rayonnement peut conduire à ce type d'interaction et, par conséquent, à une variété d'effets qui peuvent affecter considérablement la fiabilité des systèmes électroniques.

Le domaine des effets des rayonnements dans la recherche en électronique demande des investigations pour chaque nouveau composant et technologie. Lors de la conception de dispositifs et de systèmes électroniques, la prise en compte des effets des rayonnements est fondamentale pour les applications dans des environnements hostiles. Par exemple, dans les systèmes avioniques et spatiaux, ces effets sont largement étudiés pour garantir la haute fiabilité des composants et fournir les informations nécessaires pour les décisions de conception. Les préoccupations liées aux rayonnements ont commencé à être prises en compte au début de l'ère spatiale.

Les environnements radiatifs en naturels ou artificiels. Les milieux naturels comprennent l'espace et l'atmosphère. Les environnements artificiels sont, par exemple, les centrales nucléaires et les accélérateurs de particules. Chaque environnement est caractérisé par la présence de différents spectres de rayonnement.

L'aspect principal du rayonnement ionisant et de son interaction avec les dispositifs électroniques est le dépôt d'énergie dans le matériau. Les effets des rayonnements sont divisés en trois catégories principales : la dose ionisante totale (TID), les dommages par déplacement (DD) et les effets singuliers (SEE). Les SEE sont dus à une particule énergétique traversant le matériau semi-conducteur transférant son énergie par le biais d'interactions coulombiennes. Le passage de la particule ionisant crée des paires électrons-trous qui peuvent atteindre des endroits critiques du dispositif, entraînant différents types d'effets, par exemple, des bit flip dans la mémoire, des courantes parasites, des transitoires de tension sur les nœuds du circuit. TID et DD sont des effets cumulatifs causés par l'accumulation de rayonnements

ionisants entraînant une dégradation à long terme des paramètres du dispositif, par exemple une augmentation du courant de fuite et un décalage de la tension de seuil des transistors.

À mesure que les nœuds technologiques deviennent plus petits et les composants plus intégrés, le dépistage des effets induits par les rayonnements sur les composants devient encore plus important. Cette recherche joue un rôle crucial dans la compréhension de la fiabilité de chaque technologie, de ses mécanismes de défaillance et des techniques de durcissement qui peuvent être appliquées. Les effets des rayonnements peuvent différer lorsque l'on considère différents nœuds technologiques, par exemple, les SEEs par ionisation induits par les protons, ont une importance croissante pour les technologies les plus intégrées.

Comme mentionné plus haut, une seule particule ionisante passant à travers un dispositif semi-conducteur perd de l'énergie par les interactions coulombiennes et laisse une trace de paires électron-trou libres. L'excès créé de porteurs de charges mobiles atteignant les sites sensibles du dispositif peut conduire à des SEEs. Les parties les plus sensibles des composants électroniques sont généralement les jonctions p/n polarisées en inverse, car ces régions peuvent collecter efficacement les charges mobiles en raison de la présence d'un champ électrique élevé. Contrairement aux effets de dose, qui sont cumulatifs dans le temps, les SEEs sont des effets localisés dus à un impact d'une particule unique, provoquant un état transitoire pouvant conduire à des dommages temporels (soft errors) ou permanents (hard errors). Les erreurs temporelles sont celles qui peuvent être corrigées ou récupérées. Par exemple, une cellule de mémoire qui a perdu son information, une fois qu'elle sera réécrite, elle ne sera plus fautive. Les erreurs permanentes provoquent des dommages physiques irréversibles, par exemple, la rupture d'un diélectrique de grille. De plus, certaines fautes peuvent être classées comme temporelles ou permanents selon les effets qui les produisent. Par exemple, le Single-Event Latch-up peut provoquer une erreur permanent si la coupure d'alimentation n'est pas effectuée rapidement, ou simplement des effets transitoires.

Cette thèse est consacrée à l'étude des effets induits par les radiations, avec un focus particulier sur les SEEs dans les mémoires. L'utilisation de dispositifs commerciaux standards dans l'avionique, les missions spatiales ou les accélérateurs de particules nécessite une compréhension de leur comportement lorsqu'ils sont exposés à des environnements hostiles. Dans l'étude bibliographique, plusieurs travaux ont montré que les mémoires électroniques sont l'une des principaux contributrices aux défaillances des systèmes. En raison de leur nature, les mémoires sont capables de stocker des erreurs induites par les rayonnements en forme de *Single-Bit Upset* (SBU) ou *Multiple-Cell Upset* (MCU), ce qui fait de ce dispositif le meilleur candidat pour étudier ce type de faute. Ensuite, en mettant l'accent sur les environnements spatial et avionique (atmosphérique), cette thèse présent les résultats d'une

recherche de trois ans sur les effets de différentes sources de rayonnement sur plusieurs types de mémoires électroniques.

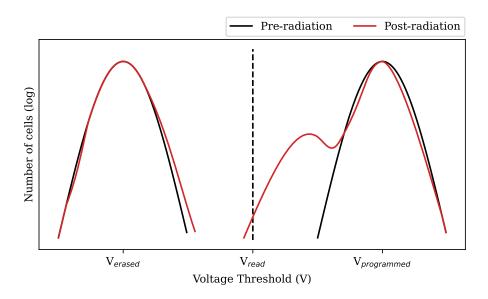

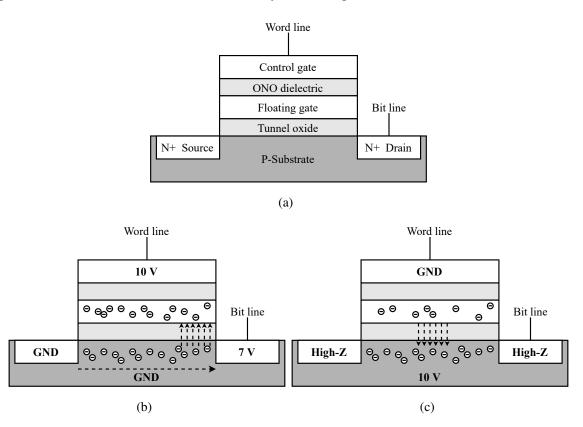

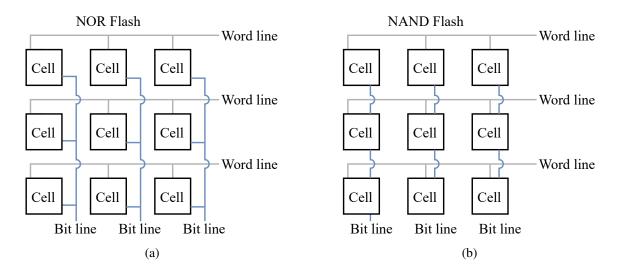

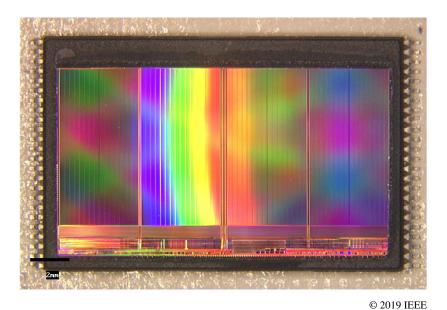

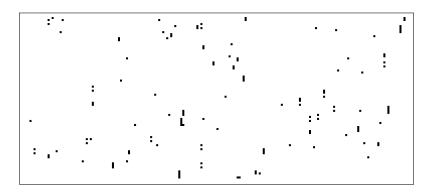

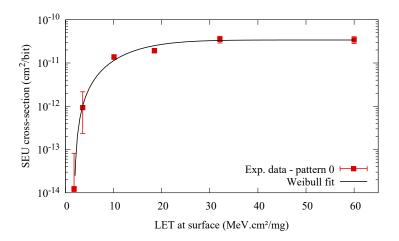

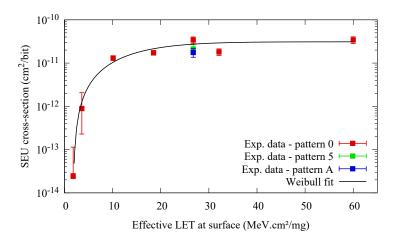

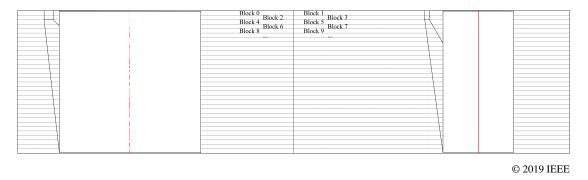

Le premier sujet introduit par la thèse est une étude sur les effets induits par les ions lourds sur une mémoire Flash de type NAND. La mémoire Flash est un type d'EEPROM (Electrically Erasable Programmable Read-Only Memory) basé sur une cellule à transistor unique à grille flottante (FG). Cette technologie a joué un rôle important sur le marché des mémoires non volatiles à semi-conducteurs, avec une tendance agressive à l'intégration. Dans la suite, la technologie à base la mémoire Flash et les effets induits par les rayonnements sont discutés. Une étude est présentée sur l'impact des ions lourds sur un dispositif de type Flash faisant partie de la mission MTCube (Memory Test CubeSat). Le projet MTCube a pour objectif principal de développer et tester en vol différentes mémoires commerciales et d'évaluer leur sensibilité à l'environnement spatial en comparant leur comportement dans l'espace avec des données de simulations et de test à l'aide de faisceaux de particules accélérées. L'étude de cette mémoire a conduit à l'identification de différents mécanismes de défaillance. Les plus simples entre eux sont les SBUs. Les bit-flips observés dans la mémoire Flash sont toujours produits par une transition de "0" à "1" logique, ce qui est attendu sur cette technologie puisqu'une grille flottante chargée est, par convention, normalement utilisée pour représenter le "0" logique. Une particule ionisante traversant une grille flottante chargée peut conduire à une décharge de la même, affectant la tension de seuil du transistor et affectant alors la lecture de la donne stockées. L'apparition de petits groupes d'erreurs, définis comme MCUs, a été identifiée, montrant un comportement similaire aux SBUs. Cela peut se produire en raison du partage de charge (charge sharing) dans la ligne de bit ou même de particules secondaires générées avec des angles. Ces tests révèlent également l'apparition de lignes d'erreurs verticales affectant tous les blocs du plan mémoire appartenant à une même colonne. Enfin, des tests spécifiques ont été effectués sur les registres de données de la mémoire. Ces tests ont révélé des SBUs, ainsi que des reset intempestifs des registres.

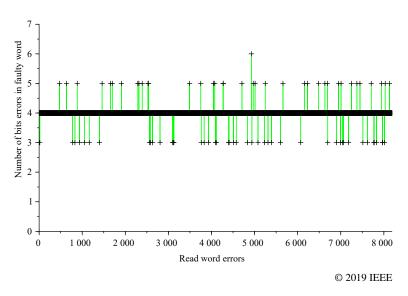

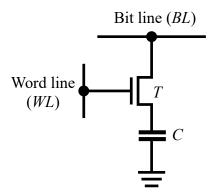

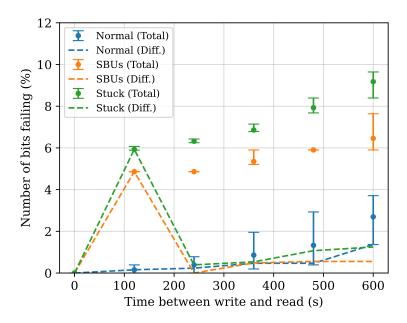

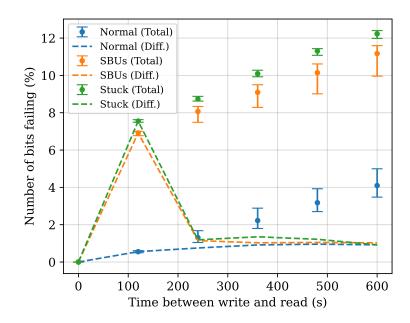

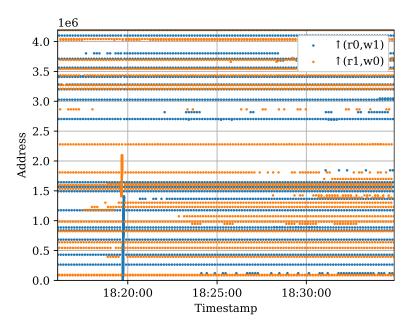

Ensuite, une étude sur les effets de la radiation neutronique (spectres thermiques et atmosphériques) sur différentes mémoires DRAM a été réalisée. La technologie DRAM est apparue dans les années 70 et reste une technologie importante de nos jours, avec de nouvelles architectures apportant des caractéristiques de haute performance et haute densité. La cellule DRAM est constituée d'un transistor d'accès et d'un condensateur utilisé comme élément mémoire. La charge stockée dans le condensateur définit l'état logique de la cellule, étant utilisée pour représenter un bit avec une valeur "0" ou "1" logique. Une pSRAM a été utilisée comme cible des expériences. La pSRAM est basée sur un plan mémoire de cellule DRAM. Ce type de cellules nécessite des opérations de rafraîchissement périodiques, et dans la pSRAM, l'opération de rafraîchissement est effectuée par un circuit logique embarqué

dans la puce, qui utilise l'opération de rafraîchissement en fonction de ses exigences de synchronisation et pendant que la mémoire n'est pas en cours de lecture ou d'écriture. Dans cette structure, puisque l'hôte n'a pas besoin de gérer d'opération de rafraîchissement, la mémoire se comporte comme un dispositif SRAM, qui est composé de cellules statiques qui ne nécessitent pas ce type de contrôle, d'où le nom pseudo SRAM (pSRAM). Dans cette étude, il est démontré qu'il existe une similitude entre le mécanisme de défaillance des SBUs et des bits collés. Les cellules présentant un SBU ou un bit collé ont été identifiées et étudiées dans des tests fonctionnels post-radiation où la capacité de rétention a été explorée. Les résultats de ces tests montrent que la dégradation de la rétention est déjà présente dans les cellules avec SBUs, mais elle est beaucoup plus prononcée dans les cellules qui présentent bit collé, c'est-à-dire que ces dernières sont tellement endommagées d'avoir une très faible capacité de rétention. Cependant, concernant le mécanisme physique de défaillance, l'interprétation la plus probable est un endommagement par déplacement qui affecte ou le transistor d'accès ou le condensateur de la cellule mémoire. Cette explication est aussi confirmée par le test de recuit thermique qui démontre une réduction des fautes permanentes et l'amélioration des propriétés de rétention des cellules affectées après exposition à des températures élevées. L'étude a également conduit à l'observation des fautes de type SEFI (Single-Effect Functional Interruption) sous la forme de blocs d'erreurs, avec, par exemple, une ligne verticale ou horizontale d'erreurs sur plusieurs adresses. Ces blocs d'erreurs peuvent constituer une menace réelle pour les applications critiques car la mise en œuvre de codes de correction d'erreurs ne sont pas en mesure de faire face à des erreurs de cette envergure.

Ensuite, une étude comparative sur trois nœuds technologiques différents (110 nm, 72 nm et 63 nm) est présentée pour le même dispositif SDRAM placé sous faisceau neutronique. La SDRAM est un type de DRAM dans laquelle les opérations sont effectuées en mode synchrone. Le mode synchrone fonctionne sur la base de signaux de contrôle qui doivent respecter les restrictions du temps d'accès de la mémoire. Les dispositifs SDRAM ont été soumis à un faisceau de neutron avec une spectre atmosphérique. Les résultats ont montré l'apparition de SBUs et de bits collés, comme pour la pSRAM. La comparaison entre les trois technologies a été faite sur la base des sections efficaces pour chaque type de faute, et elle a mis en évidence une sensibilité plus élevée pour la génération la plus ancienne (110 nm). Ceci montrant que les améliorations architecturales et matérielles face à la radiation dans ce cas sont prédominantes par apport à une sensibilité plus élevée induite par une intégration plus poussée (72 nm et 63 nm). Il est important de souligner que les changements exacts dans la structure, la conception et les matériaux utilisés entre les modèles ne sont pas accessibles au public, pour cela, l'analyse reste dans une perspective de haut niveau.

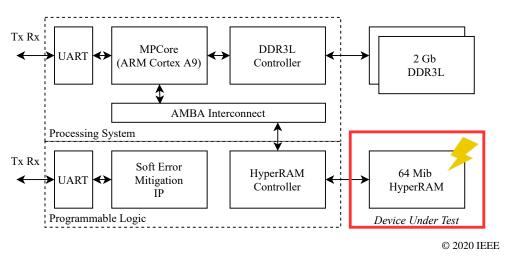

Les réseaux de neurones convolutifs (CNN) sont actuellement l'un des modèles prédictifs les plus utilisés en apprentissage automatique (*Machine Learning*). Des études récentes ont démontré que les défauts matériels induits par la radiation, y compris les rayonnements cosmiques, peuvent avoir un impact significatif sur l'inférence des CNNs conduisant à des prédictions erronées. Par conséquent, garantir la fiabilité des CNNs est crucial, en particulier, lorsqu'ils sont déployés dans des applications critiques, telles que la robotique, l'aéronautique et la conduite autonome. Dans cette thèse, un cas d'étude est présenté avec l'objectif d'évaluer l'impact des radiations sur la fiabilité des systèmes où des CNNs ont été implantés. A cette fin, l'étude se base sur des campagnes d'injection de fautes réalistes qui sont extraites dans des campagnes de test par irradiation. Dans ce contexte, les modèles de faute étudiés précédemment dans la mémoire pSRAM ont été utilisés, en particulier les fautes de type SBU, bit collé et bloc d'erreurs, en tenant compte de leur fréquence d'apparition calculée dans les expériences.

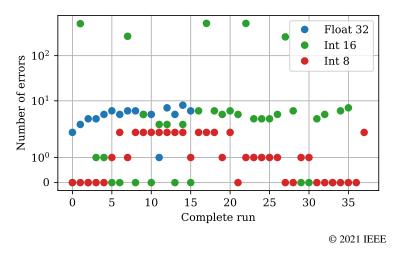

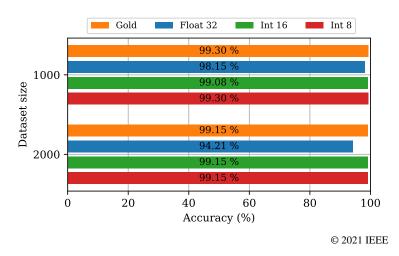

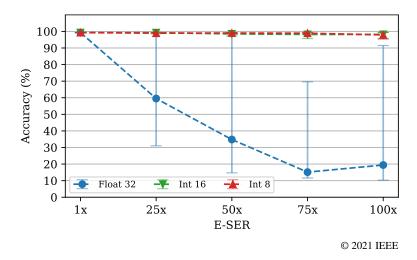

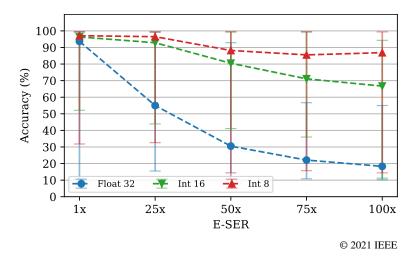

Dans cette étude, trois représentations de données ont été exploitées pour créer trois versions du même modèle CNN. Ces versions (*Float 32*, *Int 16* et *Int 8*) ont été implémentées dans un système embarqué utilisant la pSRAM étudiée étudie auparavant. L'un des objectifs de cette étude était d'évaluer la fiabilité de différentes représentations des données, montrant, que la moins sensible est celle qui utilise une représentation de type *integer* sur 8 bits. Le deuxième objectif, comme mentionné avant, était d'explorer l'utilisation des modèles réalistes de fautes pour définir un émulateur capable d'injecter les fautes les plus proche de la réalité représentant un certain environnement et qui pourrait être généralisé pour d'autres types d'application.

En conclusion, l'évolution technologique, qui comporte une meilleure intégration des transistors et l'utilisation de nouveaux matériaux, nous amène à reconduire de nouvelles études pour comprendre l'impact des radiations sur les dispositifs électroniques. Les travaux présentés dans cette thèse contribuent à l'avancement de ces connaissances et évaluent impact des radiations non seulement au niveau des dispositifs mais également d'un point de vue des applications au niveau système. De plus, l'approche présentée dans le cas d'étude des réseaux de type CNNs apporte une méthodologie complète pour évaluer la fiabilité des systèmes par la méthode expérimentale e par simulation/émulation.

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of University of Montpellier's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License from RightsLink. If applicable, University Microfilms and/or ProQuest Library, or the Archives of Canada may supply single copies of the dissertation.

#### Acknowledgements

I would like to thank my supervisor Dr. Luigi Dillilo for the opportunity of working under his guidance, for the knowledge transmitted, and for the attention received during this work. Also, I would express my gratitude for the exceptional work environment that was provided at the *Laboratoire d'Informatique*, de Robotique et de Microélectronique de Montpellier (LIRMM).

I would like to thank all my family, my closest and loved ones, which sustained me during this long path with immeasurable support and love even at a long distance from Brazil. I would also like to thank all my colleagues at LIRMM, mainly the ones within our research group, that I had the privilege to share extraordinary experiences and countless liters of coffee. Also, I would like to extend this mention to those I had the opportunity to spend my free time with great joy and friendship. These three years' journey was full of challenging and stunning moments, and their support was crucial to accomplish this path. Furthermore, I would like to thank all my co-authors, who supported this work with excellent knowledge.

This research has been achieved thanks to the financial support of the VAN ALLEN Foundation (Contract No. UM 181387) and the Region Occitanie (Contract No. UM 181386).

# **Contents**

| Lı | st of A | Author'       | s Publicati | lons                                            | XXI    |

|----|---------|---------------|-------------|-------------------------------------------------|--------|

| Li | st of l | Figures       |             |                                                 | xxvii  |

| Li | st of T | <b>Tables</b> |             |                                                 | xxxiii |

| No | omeno   | clature       |             |                                                 | XXXV   |

| 1  | Intr    | oductio       | n           |                                                 | 1      |

|    | 1.1     | Radiat        | ion Enviro  | nments                                          | . 2    |

|    |         | 1.1.1         | Space Ra    | diation                                         | . 2    |

|    |         |               | 1.1.1.1     | Solar Particles                                 | . 2    |

|    |         |               | 1.1.1.2     | Galactic Cosmic Rays                            | . 3    |

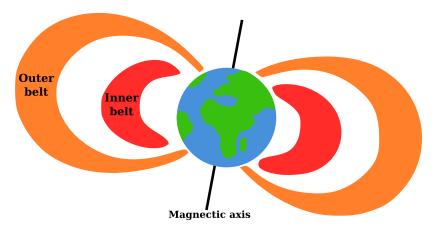

|    |         |               | 1.1.1.3     | Trapped Radiation                               | . 3    |

|    |         | 1.1.2         | Atmosph     | eric Radiation                                  | . 5    |

|    |         | 1.1.3         | Artificial  | Radiation Environments                          | . 5    |

|    | 1.2     | Radiat        | ion Effects | in Electronics                                  | . 6    |

|    |         | 1.2.1         | Total Ion   | izing Dose                                      | . 6    |

|    |         | 1.2.2         | Displace    | ment Damage                                     | . 7    |

|    |         | 1.2.3         | Single-Ev   | vent Effects                                    | . 7    |

|    |         |               | 1.2.3.1     | Single-Event Upset                              | . 8    |

|    |         |               | 1.2.3.2     | Single-Event Transient                          | . 8    |

|    |         |               | 1.2.3.3     | Single-Event Functional Interruption            | . 9    |

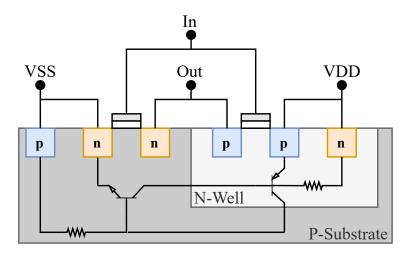

|    |         |               | 1.2.3.4     | Single-Event Latch-up                           | . 9    |

|    | 1.3     | Thesis        | Outline .   |                                                 | . 10   |

| 2  | Stud    | ly of Si      | ngle-Event  | Upsets in a Single-Level Cell NAND Flash Memory | 13     |

|    | 2.1     | Flash         | Memories    |                                                 | . 13   |

|    |         | 2.1.1         | Cell Struc  | cture and Memory Architecture                   | 14     |

#### **Contents**

|   | 2.2  | Radiat    | ion Effects on Flash Memories                                   |

|---|------|-----------|-----------------------------------------------------------------|

|   | 2.3  | Experi    | mental Setup                                                    |

|   |      | 2.3.1     | The Device Under Test                                           |

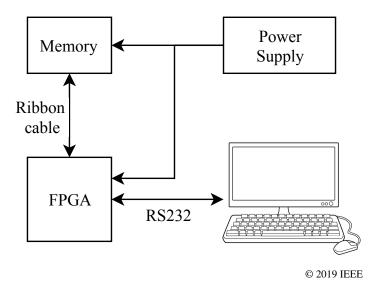

|   |      | 2.3.2     | Test Setup                                                      |

|   |      | 2.3.3     | Test Modes                                                      |

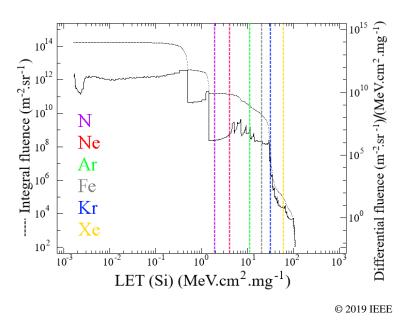

|   |      | 2.3.4     | Test Facilities                                                 |

|   | 2.4  | Result    | s and Discussion                                                |

|   |      | 2.4.1     | Static and Dynamic Mode                                         |

|   |      |           | 2.4.1.1 Single-bit Upsets and Small Clusters                    |

|   |      |           | 2.4.1.2 Vertical Lines                                          |

|   |      |           | 2.4.1.3 Events Impact and Discussion                            |

|   |      | 2.4.2     | Static Data Register Test                                       |

| 3 | Neu  | tron-In   | duced Impact on a Pseudo-Static RAM 33                          |

|   | 3.1  | Dynan     | nic Random Access Memory                                        |

|   | 3.2  | Pseudo    | o-Static RAM                                                    |

|   | 3.3  | Neutro    | on-Induced Effects on DRAMs                                     |

|   | 3.4  | Experi    | mental Setup                                                    |

|   |      | 3.4.1     | Device Under Test                                               |

|   |      | 3.4.2     | Test Facilities                                                 |

|   |      | 3.4.3     | Test Setup                                                      |

|   | 3.5  | Test M    | Todes                                                           |

|   | 3.6  | Result    | s and Analysis                                                  |

|   |      | 3.6.1     | SBUs and Stuck Bits                                             |

|   |      | 3.6.2     | Cells' Retention Time                                           |

|   |      | 3.6.3     | Fault Mechanism of the Stuck Bits and SBUs                      |

|   |      | 3.6.4     | Thermal Annealing Tests                                         |

|   |      | 3.6.5     | Block Errors                                                    |

|   |      | 3.6.6     | Overall Event Cross Section and SER                             |

|   | 3.7  | Conclu    | asion and Discussion                                            |

| 4 | Stud | ly on a S | Synchronous Dynamic RAM 61                                      |

|   | 4.1  | Synchi    | conous Dynamic RAM                                              |

|   | 4.2  | Heavy     | -ion-induced Effects                                            |

|   | 4.3  | Electro   | on-induced Effects                                              |

|   | 4.4  | A Con     | nparative Study of the Technology Impact on the Neutron-induced |

|   |      | Effects   | 64                                                              |

|     |                                                |                                                                                                                                                                                                                                                      | Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ntents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 4 4 1                                          |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <i>(5</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |                                                |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                                                | •                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                                                | -                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 4.4.4                                          | Results and discussion                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 4.4.5                                          | Comparison among the different technology nodes                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.5 | Conclu                                         | asion                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| An  | Applica                                        | tion Case Study: Reliability on Approximate Computing Sys                                                                                                                                                                                            | stem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.1 | Assess                                         | sing the reliability through fault injections campaigns                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2 | Relate                                         | d Works                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

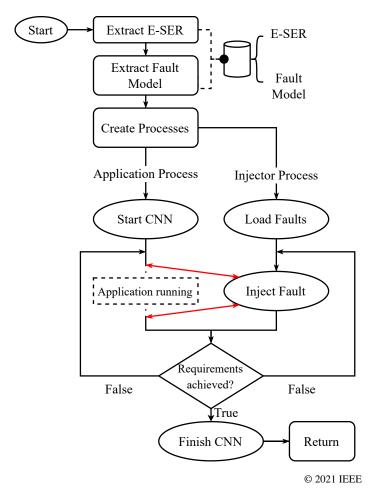

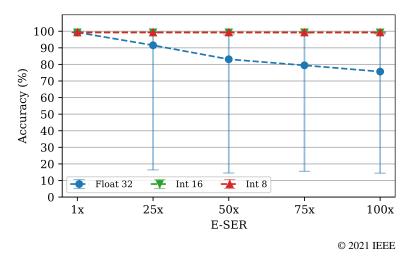

| 5.3 | Propos                                         | sed Approach                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.4 | Radiat                                         | ion Experiments                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 5.4.1                                          | DUT Characterization                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 5.4.2                                          | Radiation Tests on the CNN Application                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                                                | 5.4.2.1 CNNs Implementation                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                                                | 5.4.2.2 Test Procedure                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                                                | 5.4.2.3 Test Results                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 5.4.3                                          | Execution Soft-Error Rate                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.5 | Emula                                          | tor                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.6 | Result                                         | s Analysis                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 5.6.1                                          | SBUs and Stuck Bits                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

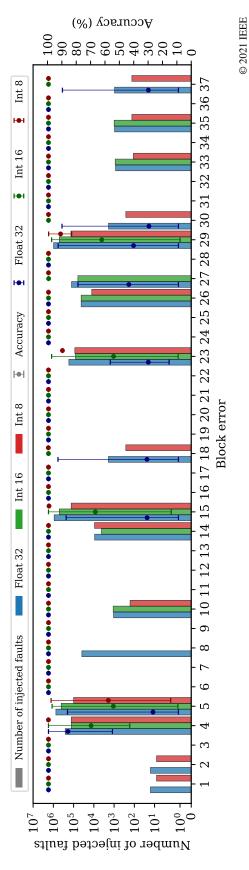

|     | 5.6.2                                          | Block Errors                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.7 | Conclu                                         |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Sum | ımary a                                        | and Conclusions                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | An 7<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | <ul> <li>4.5 Conclu</li> <li>An Applica</li> <li>5.1 Assess</li> <li>5.2 Relate</li> <li>5.3 Propos</li> <li>5.4 Radiat</li> <li>5.4.1</li> <li>5.4.2</li> <li>5.4.3</li> <li>5.5 Emula</li> <li>5.6.1</li> <li>5.6.2</li> <li>5.7 Conclu</li> </ul> | 4.4.2 Test facility 4.4.3 Test procedures and setup 4.4.4 Results and discussion 4.4.5 Comparison among the different technology nodes 4.5 Conclusion  An Application Case Study: Reliability on Approximate Computing Sys 5.1 Assessing the reliability through fault injections campaigns 5.2 Related Works 5.3 Proposed Approach 5.4 Radiation Experiments 5.4.1 DUT Characterization 5.4.2 Radiation Tests on the CNN Application 5.4.2.1 CNNs Implementation 5.4.2.2 Test Procedure 5.4.2.3 Test Results 5.4.3 Execution Soft-Error Rate 5.5 Emulator 5.6 Results Analysis 5.6.1 SBUs and Stuck Bits 5.6.2 Block Errors | 4.4.1 Devices under test 4.4.2 Test facility 4.4.3 Test procedures and setup 4.4.4 Results and discussion 4.4.5 Comparison among the different technology nodes 4.5 Conclusion  An Application Case Study: Reliability on Approximate Computing System 5.1 Assessing the reliability through fault injections campaigns 5.2 Related Works 5.3 Proposed Approach 5.4 Radiation Experiments 5.4.1 DUT Characterization 5.4.2 Radiation Tests on the CNN Application 5.4.2.1 CNNs Implementation 5.4.2.2 Test Procedure 5.4.2.3 Test Results 5.4.3 Execution Soft-Error Rate 5.5 Emulator 5.6 Results Analysis 5.6.1 SBUs and Stuck Bits 5.6.2 Block Errors 5.7 Conclusion |

105

**Bibliography**

### **List of Author's Publications**

This doctoral thesis is based in part on the following peer-reviewed publications, the number used in this reference list is self-contained and is not related to thesis main matter.

#### **Journals**

- [JO-1] **L. Matana Luza**, A. Ruospo, D. Söderström, C. Cazzaniga, M. Kastriotou, E. Sanchez, A. Bosio and L. Dilillo, "Emulating the Effects of Radiation-Induced Soft-Errors for the Reliability Assessment of Neural Networks" in *IEEE Transactions on Emerging Topics in Computing*, Oct. 2021. DOI: 10.1109/TETC.2021.3116999. [Early access]. © 2021 IEEE

- **Contribution:** The author contributed with the conceptualization, methodology, validation, formal analysis, investigation, and writing. Also, the author had a major role in the experiment's software and hardware development, took part in the test campaigns.

- [JO-2] **L. Matana Luza**, D. Söderström, H. Puchner, R. G. Alía, M. Letiche, C. Cazzaniga, A. Bosio and L. Dilillo, "Neutron-Induced Effects on a Self-Refresh DRAM" in *Microelectronics Reliability*, vol. 128, pp. 114406, Nov. 2021, DOI: 10.1016/j.microrel.2021.114 406.

- **Contribution:** The author contributed with the conceptualization, methodology, validation, formal analysis, investigation, and writing. Also, the author had a major role in the experiment's software and hardware development, took part in the test campaigns.

- [JO-3] A. Ruospo, **L. Matana Luza**, A. Bosio, L. Dilillo, R. Mariani, M. Traiola, and E. Sanchez, "A Survey on Artificial Neural Networks Reliability Assessment Methodologies," in *ACM Computing Surveys*. [Under review].

- **Contribution:** The author contributed with the conceptualization, methodology, formal analysis, writing, review and editing.

- [JO-4] G. Bricas, G. Tsiligiannis, A. Touboul, J. Boch, M. Kastriotou, C. Cazzaniga, C. D. Frost, L. Dilillo, L. Matana Luza, "On the Evaluation of FPGA Radiation Benchmarks" in *Microelectronics Reliability*, vol. 126, pp. 114276, Nov. 2021. DOI: 10.1016/j.microrel.2021.114276.

- **Contribution:** The author contributed with the writing, review and editing.

- [JO-5] D. A. Santos, **L. Matana Luza**, L. Dilillo, C. A. Zeferino, and D. R. Melo, "Reliability Analysis of a Fault-Tolerant RISC-V System-on-Chip," in *Microelectronics Reliability*, vol. 125, pp. 114346, Oct. 2021, DOI: 10.1016/j.microrel.2021.114346.

- **Contribution:** The author contributed with the conceptualization, methodology, and formal analysis.

- [JO-6] D. Söderström, L. Matana Luza, H. Kettunen, A. Javanainen, W. Farabolini, A. Gilardi, A. Coronetti, C. Poivey, and L. Dilillo, "Electron-Induced Upsets and Stuck Bits in SDRAMs in the Jovian Environment," in *IEEE Transactions on Nuclear Science*, vol. 68, no. 5, pp. 716–723, May 2021, DOI: 10.1109/TNS.2021.3068186. © 2021 IEEE

**Contribution:** The author contributed with the conceptualization, methodology, and formal analysis. Also, the author had a role in the experiment's software and hardware development.

#### **International Events**

- [IE-1] A. Ruospo, **L. Matana Luza**, A. Bosio, M. Traiola, L. Dilillo and E. Sanchez, "Pros and Cons of Fault Injection Approaches for the Reliability Assessment of Deep Neural Networks" in *2021 IEEE 22nd Latin American Test Symposium (LATS)*, Oct. 2021, pp. 1-5, DOI: 10.1109/LATS53581.2021.9651807. © 2021 IEEE

- **Contribution**: The author contributed with the conceptualization, methodology, validation, formal analysis, investigation, and writing.

- [IE-2] L. Matana Luza, D. Söderström, A. M. P. de Mattos, E. A. Bezerra, C. Cazzaniga, M. Kastriotou, C. Poivey and L. Dilillo, "Technology Impact on Neutron-Induced Effects in SDRAMs: A Comparative Study," in 2021 16th International Conference on

*Design & Technology of Integrated Systems in Nanoscale Era (DTIS)*, 2021, pp. 1-6, DOI: 10.1109/DTIS53253.2021.9505143. © 2021 IEEE

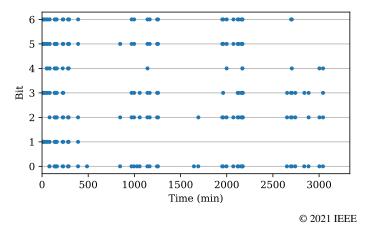

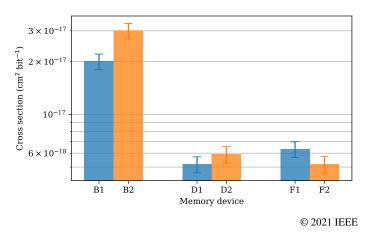

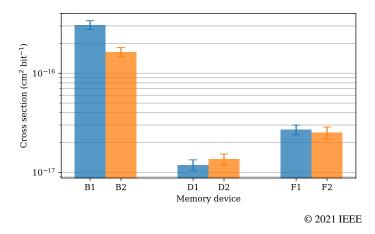

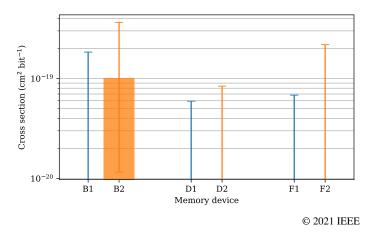

**Contribution**: The author contributed with the conceptualization, methodology, validation, formal analysis, investigation, and writing. Also, the author had a major role in the experiment's software and hardware development, took part in the test campaigns.