## Fault Injection Attacks on Embedded Applications: Characterization and Evaluation

Zahra Kazemi

### ▶ To cite this version:

Zahra Kazemi. Fault Injection Attacks on Embedded Applications : Characterization and Evaluation. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2022. English. NNT : 2022GRALT006 . tel-03659627

## HAL Id: tel-03659627 https://theses.hal.science/tel-03659627v1

Submitted on 5 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE ALPES

Préparée dans le cadre d'une cotutelle entre

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES Arrêté ministériel : 25 mai 2016

Présentée par Zahra KAZEMI

Thèse dirigée par **Vincent BEROULLE, Professeur, Université Grenoble Alpes** et codirigée par **David HÉLY, Maitre de Conférence, Université Grenoble Alpes**

préparée au sein des Laboratoire de Conception et d'Intégration des Systémes (LCIS)

dans les École Doctorale d'Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS) et le Département d'Ingénierie Électrique

## Attaques par injection de fautes sur les applications embarquées : caractérisation et évaluation

Fault Injection Attacks on Embedded Applications: Characterization and Evaluation

Thèse soutenue publiquement le **3 Février, 2022**, devant le jury composé de :

### Monsieur Jean-Max DUTERTRE

Professeur, Ecole des Mines, Rapporteur

Monsieur Pascal BENOIT

MCF HDR, Université de Montpellier, Rapporteur

### Monsieur Lilian BOSSUET

Professeur, Université de Saint Etienne, Président du jury

### Madame Noémie BÉRINGUIER-BOHER

Hardware Security Expert, Brightsight SGS, Examinatrice

### Monsieur Ioannis PARISSIS

Professeur, Université de Grenoble Alpes, Examinateur

### Monsieur Mahdi FAZELI

Professeur, Université de Halmstad, Suéde, Invité

### ACKNOWLEDGMENTS

First, i would like to sincerely thank my thesis directors, Prof.Vincent Beroulle and Dr.David Hély, for their time, help, and support during these years. It would take another dissertation to describe their positive effects on my work and my life in France. Their integrity and meticulousness have greatly influenced me as a researcher and an individual. This work would not have been possible without their continuous encouragement, guidance, and enthusiasm for my research.

In addition, i express special thanks to my co-advisor, Dr. Mahdi Fazeli, for his help, support, and fruitful discussions throughout my Ph.D. journey. He taught me the skills of a professional researcher, such as exposing a scientific problem and approaching it from different perspectives. Thank you for enlightening my life and supporting me like a brother through these years. Likewise, I would like to acknowledge Dr. Thanos Papadimitriou for being an exemplary mentor to start my Ph.D. This was an excellent opportunity to work with him and learn immensely from him.

I must express my gratitude to the jury members for their useful and productive questions and discussions. I would like to thank Prof. DUTERTRE and Dr. Pascal Benoit for all the time and effort that they put on carefully reading the thesis and writing an accurate and detailed report.

I also want to take this opportunity to thank the SERENE-IoT project, the Laboratoire de Conception et d'Integration des Systémes (LCIS) Laboratory, the Grenoble EEATS doctoral school, Grenoble Alpes Cybersecurity Institute, and IDEX for financially supporting this work, the conferences, and all travel.

I am deeply grateful to Dr. Peyman Pouyan for his generous encouragements and help during my Ph.D. journey. Also, i would like to give a special thanks to one of my best friends Dr. Ionela Prodan for supporting me like a sister, even in the most challenging moments. Last but not least, i would like to thank all my friends, colleagues, and labmates. I feel quite fortunate to meet and working many brilliant people at LCIS. Thank you, Jennyfer Duberville, Carole Seyvet, Caroline Palisse, Raphael Tavares De Alencar, Ehsan Aerabi, Amir Alipour, Ashkan Azarfar, Amin Norollah, Mahdi Talebi, Afef Kchaou, Baptiste Pestourie, Cyril Bresch, Johan Laurant, and Zishan Ali. Finally, I would not forget my family for their continuous love and support throughout all these years.

"This thesis is dedicated to my beloved parents, Farhad Kazemi and Elham Choolabi, for their unconditional love and support throughout all these years."

# Abstract

The security assessment of IoT devices against potential software and hardware-based threats is now a necessary task for embedded software developers. Having physical access to the target devices makes hardware security a significant concern to consider in IoTs. Among the hardware security attack techniques, fault injection attacks such as clock glitching are one of the most practical attacks which are non-invasive and low-cost. They can interfere with the expected operations and cause serious malfunctions in the targeted device. Regarding this, an efficient security assessment framework and methodology against fault injection attacks are needed to properly evaluate the embedded devices.

It is often difficult for the software developer to use a fault injection platform correctly. Therefore, this thesis focuses on designing an easy-to-use platform dedicated to clock glitching attacks in order to evaluate the vulnerabilities of embedded software applications. This work proposes an open-source evaluation platform followed by high-level assessment methodologies. Then, a characterization process based on a preliminary simulation approach is presented to improve the experimental fault injection parameters. Finally, the impacts of the injected faults are analyzed and studied in an open-source medical application (Sec-Pump) as a case study. The platform and the methodology proposed in this thesis can successfully identify the security vulnerabilities in an embedded application and guide the software developer to mitigate such attacks.

Keywords- Hardware Security, Embedded Systems, Fault Injection Attacks, Clock Glitching

# Résumé

L'évaluation de la sécurité des appareils IoT contre les menaces logicielles et matérielles potentielles est désormais une tâche nécessaire pour les développeurs de logiciels embarqués. Avoir un accés physique aux appareils cibles fait de la sécurité du matériel une préoccupation importante à prendre en compte dans les IoT. Parmi les techniques d'attaque de sécurité matérielle, les attaques par injection de fautes telles que les problémes d'horloge sont l'une des attaques les plus pratiques, non invasives et peu coûteuses. Ils peuvent interférer avec les opérations attendues et provoquer de graves dysfonctionnements dans l'appareil ciblé. À cet égard, un cadre d'évaluation de la sécurité efficace et une méthodologie contre les attaques par injection de fautes sont nécessaires pour évaluer correctement les dispositifs embarqués.

Il est souvent difficile pour le développeur de logiciels d'utiliser correctement une plate-forme d'injection de fautes. Par conséquent, cette thése s'est concentrée sur la conception d'une plateforme facile à utiliser dédiée aux attaques par défaut d'horloge afin d'évaluer les vulnérabilités des applications logicielles embarquées. Ce travail propose une plateforme d'évaluation open source suivie de méthodologies d'évaluation de haut niveau. Ensuite, un processus de caractérisation basé sur une approche de simulation préliminaire est présenté pour améliorer les paramétres expérimentaux d'injection de fautes. Enfin, les impacts des failles injectées sont analysés et étudiés dans une application médicale open source (Sec-Pump) en tant qu'étude de cas. La plate-forme et la méthodologie proposées dans cette thése peuvent identifier avec succés les vulnérabilités de sécurité dans une application embarquée et guider le développeur de logiciels pour atténuer de telles attaques.

*Mots clés*— Sécurité matérielle, Systémes Embarqués, Attaques par Injection de Fautes, Glitch d'horloge

# CONTENTS

| Li                       | st of   | Figures                                           | κv |

|--------------------------|---------|---------------------------------------------------|----|

| Li                       | st of ' | Tables x                                          | ix |

| List of Abbreviations xx |         |                                                   | xi |

| 1                        | Intr    | roduction                                         | 1  |

|                          | 1.1     | Basic Concepts of Hardware Attacks                | 3  |

|                          |         | 1.1.1 Side-Channel Attacks                        | 4  |

|                          |         | 1.1.2 Fault Injection Attacks                     | 6  |

|                          | 1.2     | Thesis Statement and Main Objectives              | 9  |

|                          | 1.3     | Thesis Contributions                              | 11 |

|                          | 1.4     | Organization of the Dissertation 1                | 12 |

| 2                        | Stat    | te of The Art                                     | 15 |

|                          | 2.1     | A Basic Setup for a FIA Platform I                | 15 |

|                          | 2.2     | Clock-Based FIAs                                  | Ι7 |

|                          |         | 2.2.1 Concepts of Clock FIAs                      | Ι7 |

|                          |         | 2.2.2 Clock Glitching Attack Examples             | 20 |

|                          |         | 2.2.3 Clock Glitch Generator Characteristics      | 20 |

|                          | 2.3     | Voltage-Based FIAs                                | 22 |

|                          |         | 2.3.1 Concepts of Voltage FIAs                    | 22 |

|                          |         | 2.3.2 Voltage Glitching Attack Examples           | 25 |

|                          |         | 2.3.3 Voltage Glitch Generator Characteristics    | 26 |

|                          | 2.4     | A Review of Fault Generators                      | 27 |

|                          |         | 2.4.1 Clock Glitch Generators in the literature   | 27 |

|                          |         | 2.4.2 Voltage Glitch Generators in the Literature | 35 |

|                          | 2.5     | Conclusion                                        | 41 |

| 3                        | Har     | rdware Security Evaluation Platform 4             | 13 |

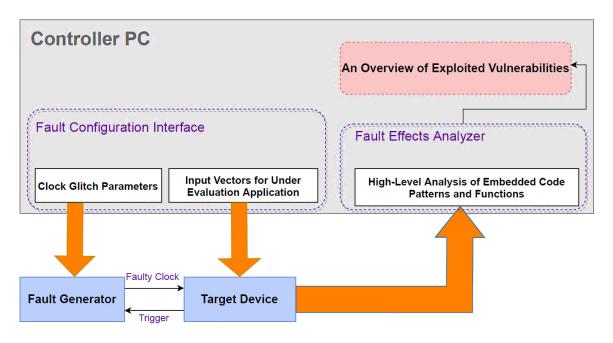

|                          | 3.1     | The Framework of a Practical Evaluation Platform  | 43 |

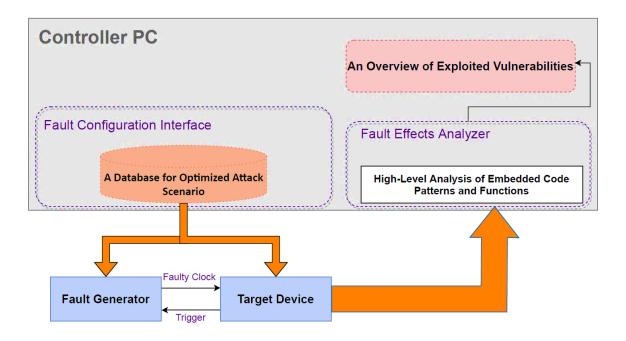

|                          | 3.2     | Fault Configurator Interface    4                 | 15 |

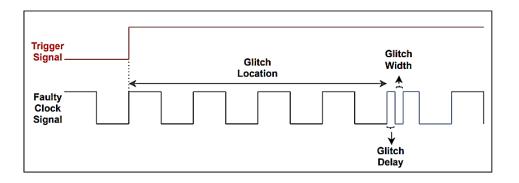

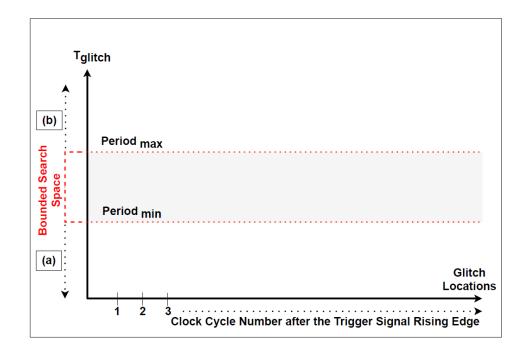

|   |      | 3.2.1   | Key Parameters for Clock Glitch Configuration                                        | 45  |

|---|------|---------|--------------------------------------------------------------------------------------|-----|

|   |      | 3.2.2   | Clock Glitch Configurator Interface                                                  | 46  |

|   | 3.3  | Fault   | Generator                                                                            | 47  |

|   |      | 3.3.1   | FPGA Implementation of the Clock Glitch Generator                                    | 48  |

|   |      | 3.3.2   | Experimental Comparison of Clock Glitch Generator Designs, CDC vs. CDCF:             |     |

|   |      |         | Attacking AES Algorithm                                                              | 51  |

|   |      | 3.3.3   | Design of an Efficient and Automated Clock Glitch Generator                          | 57  |

|   | 3.4  | Fault   | Effect Analyzer                                                                      | 59  |

|   |      | 3.4.1   | Main Control Flow Patterns and Their Evaluation Methods                              | 59  |

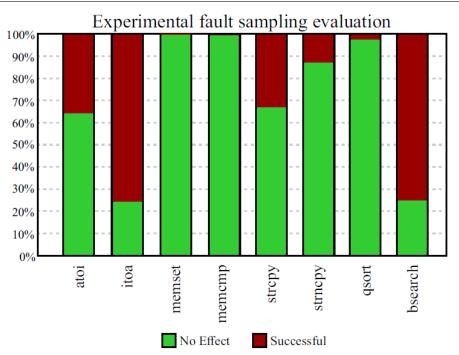

|   |      | 3.4.2   | Main Standard C-Functions and Their Evaluation Methods                               | 61  |

|   | 3.5  | Concl   | lusion                                                                               | 64  |

| 4 | Har  | dware   | Security Assessment By Utilizing The Hardware Evaluation Platform                    | 67  |

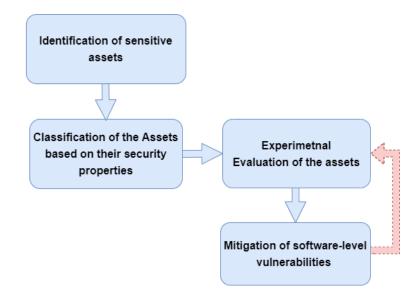

|   | 4.1  | ICEM    | Assessment Methodology                                                               | 68  |

|   |      | 4.1.1   | Identification of sensitive assets                                                   | 68  |

|   |      | 4.1.2   | Classification of the Assets based on their security properties                      | 69  |

|   |      | 4.1.3   | Experimental Evaluation of the Assets                                                | 69  |

|   |      | 4.1.4   | Mitigation of Software-Level Vulnerabilities                                         | 70  |

|   | 4.2  | Evalu   | ation of a Medical Embedded Application against Clock Glitching FIA: A Case          |     |

|   |      | Study   | ·                                                                                    | 70  |

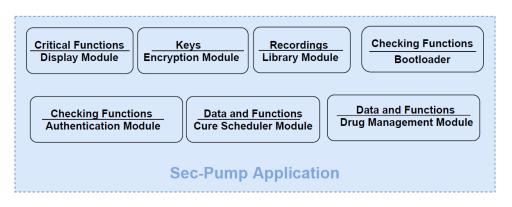

|   |      | 4.2.1   | Identifying the Sec-Pump Assets                                                      | 71  |

|   |      | 4.2.2   | Classifying the Sec-Pump's Assets based on their Security Properties $\ldots \ldots$ | 72  |

|   |      | 4.2.3   | Experimental Evaluation of the Sec-Pump                                              | 72  |

|   |      | 4.2.4   | Vulnerability Mitigation for the Sec-Pump Application                                | 82  |

|   | 4.3  | Concl   | lusion                                                                               | 85  |

| 5 | Opt  | imizin  | g the FIA Evaluation Process by Utilizing Simulation-based Analysis and Sym-         |     |

|   | boli | ic Asse | rtion                                                                                | 87  |

|   | 5.1  | Enha    | ncing the Experimental FIA Through Simulation-based Pre-Injection Analysis $\ .$     | 88  |

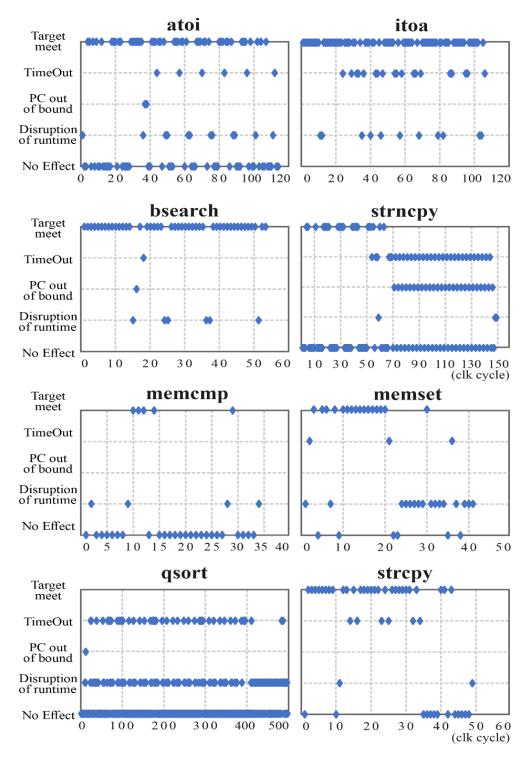

|   |      | 5.1.1   | Non-Exhaustive Experimental Evaluation of C-Functions                                | 88  |

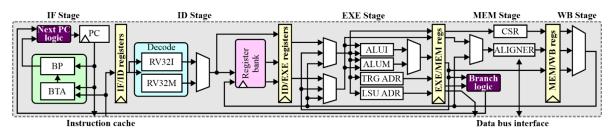

|   |      | 5.1.2   | Fault Effects on A RISC-V Micro-Architecture                                         | 89  |

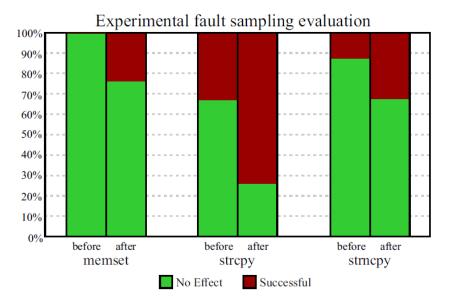

|   |      | 5.1.3   | Simulation-based Evaluation Results                                                  | 94  |

|   |      | 5.1.4   | Fine Tuned Experimental Attack                                                       | 95  |

|   | 5.2  | An Of   | ffline Hardware Security Assessment Approach using Symbolic Assertion and            |     |

|   |      | Code    | Shredding                                                                            | 97  |

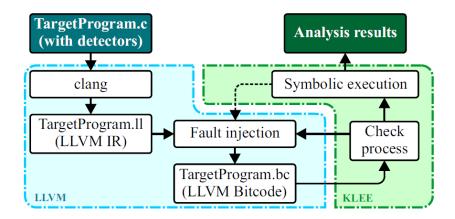

|   |      | 5.2.1   | Background of the Symbolic Fault Injection                                           | 97  |

|   |      | 5.2.2   | Precise Fault Injection Using Symbolic Execution                                     | 98  |

|   |      | 5.2.3   | A Case-Study                                                                         | 99  |

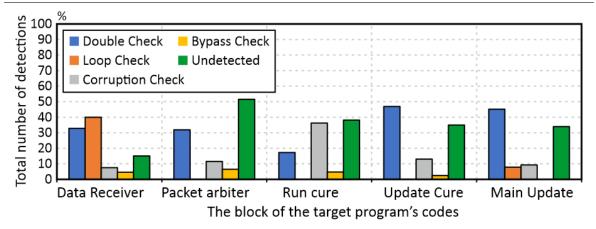

|   |      | 5.2.4   | Experiments and Results                                                              | 100 |

|    | 5.3 Conclusion | . 105 |

|----|----------------|-------|

| 6  | Conclusions    | 107   |

| 7  | Perspectives   | 111   |

| 8  | Publications   | 113   |

| Bi | bliography     | 117   |

# LIST OF FIGURES

| 1.1  | The Abstract Machine of an Embedded Systems                                                 | 3  |

|------|---------------------------------------------------------------------------------------------|----|

| 1.2  | An Example of Traditional Assumption for Crypto-analysis Attacks against an Encryp-         |    |

|      | tion Machine                                                                                | 4  |

| 1.3  | Taxonomy of Physical Attacks                                                                | 5  |

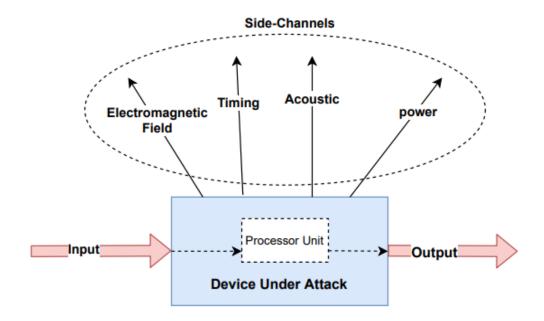

| 1.4  | Side-Channels from an Embedded Device                                                       | 5  |

| 1.5  | Fault propagation through different layers, (1) Fault Injection, (2) Fault Manifestation,   |    |

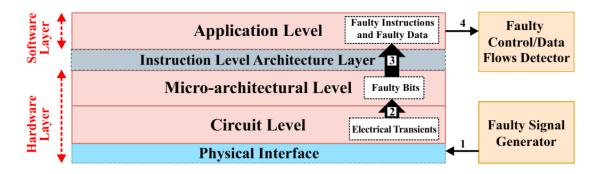

|      | (3) Fault Propagation, (4) Fault Exploitation                                               | 7  |

| 1.6  | The road map for the dissertation                                                           | 13 |

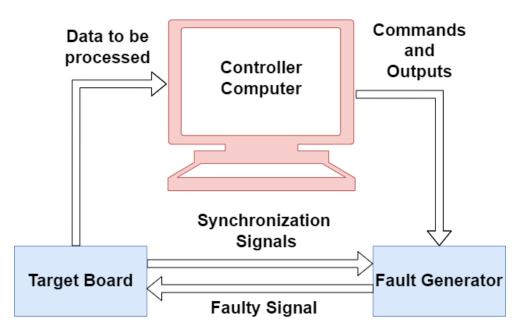

| 2.1  | General Fault Injection Attack Setup                                                        | 16 |

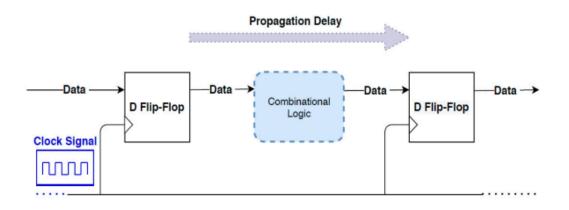

| 2.2  | Synchronous Representation of Digital ICs [55]                                              | 17 |

| 2.3  | Violating Critical Path Delay by Insertion of Additional Positive Clock Edge                | 18 |

| 2.4  | Representation of Clock Glitch and Fault Injection [64]                                     | 19 |

| 2.5  | Experimental Setup of Clock Fault Attack                                                    | 20 |

| 2.6  | Inverter Circuit and $T_{PHL}$ , $T_{PLH}$ Parameters in Response Waveforms                 | 23 |

| 2.7  | Negative Supply Voltage Glitch                                                              | 24 |

| 2.8  | Fault Injection Setup for Voltage Fault Attack                                              | 25 |

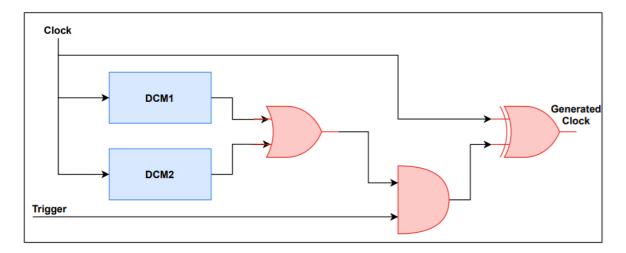

| 2.9  | Different Methods for Generating Clock Glitch(es)                                           | 28 |

| 2.10 | Faulty Clock Generation Using Two Shifted Signals                                           | 29 |

| 2.11 | Experimental Environment                                                                    | 29 |

| 2.12 | Glitch Generator in [57]                                                                    | 30 |

| 2.13 | Glitch Generation Using High-Frequency Signal                                               | 31 |

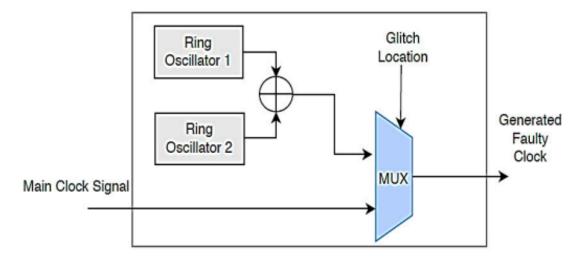

| 2.14 | Glitch Insertion Circuitry Using Two Ring Oscillators [54]                                  | 31 |

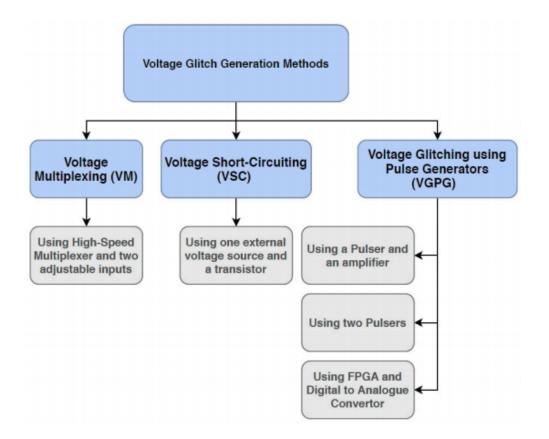

| 2.15 | Different Methods for Generating Voltage Glitches                                           | 36 |

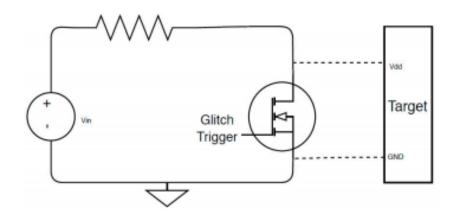

| 2.16 | Voltage Generator Set-Up in [51]                                                            | 37 |

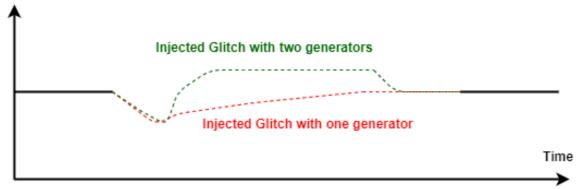

| 2.17 | Comparing Generated Voltage Signal with One and Two Voltage Generators [68]                 | 37 |

| 3.1  | The architecture of the proposed evaluation platform                                        | 44 |

| 3.2  | Clock Glitch FIA Parameters                                                                 | 46 |

| 3.3  | Glitch Period's Search Space Bounds                                                         | 47 |

| 3.4  | The improved architecture of the proposed evaluation platform $\ldots \ldots \ldots \ldots$ | 48 |

| 3.5  | A Clock Glitch Generator Based on the CSC Method                                          | 49 |

|------|-------------------------------------------------------------------------------------------|----|

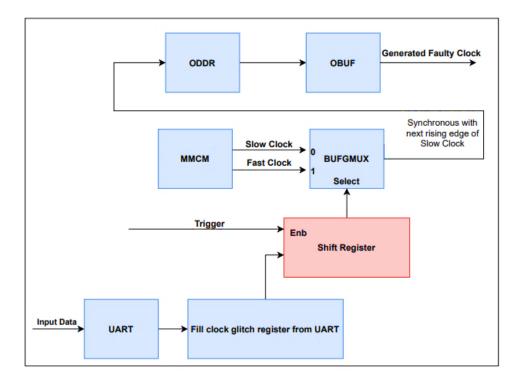

| 3.6  | Glitch Generator based on the CDCF Method                                                 | 50 |

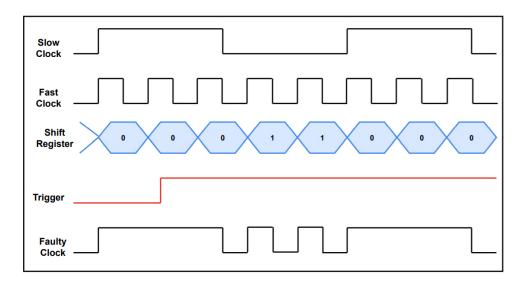

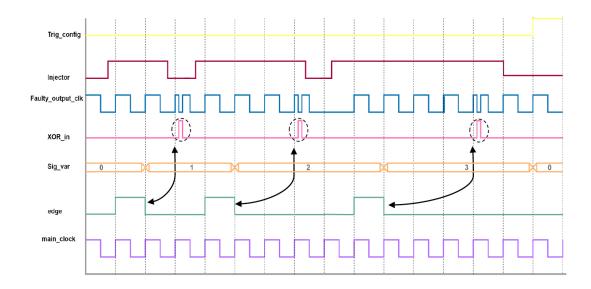

| 3.7  | An example of faulty clock generation based on the CDCF method                            | 51 |

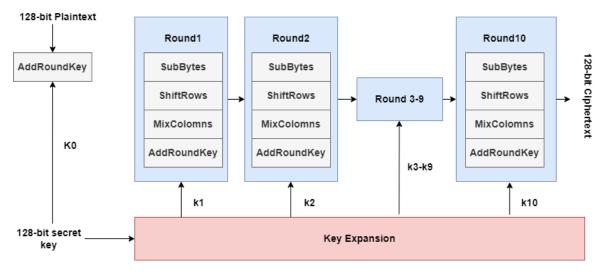

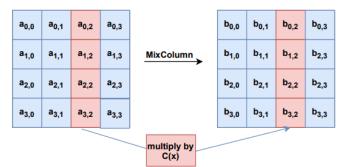

| 3.8  | Structure of AES [83]                                                                     | 52 |

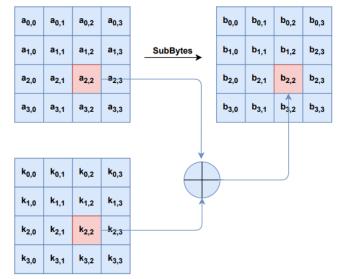

| 3.9  | SubBytes in AES 128                                                                       | 53 |

| 3.10 | ShiftRows in AES 128                                                                      | 53 |

| 3.11 | MixColumn in AES 128                                                                      | 53 |

| 3.12 | AddRoundKey in AES 128                                                                    | 53 |

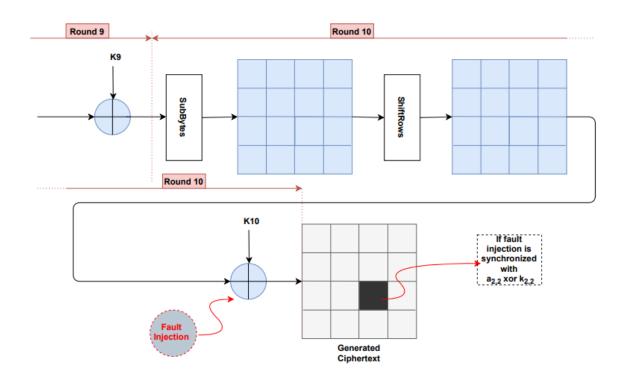

| 3.13 | Fault Injection on a single byte of an AES-128 bit                                        | 54 |

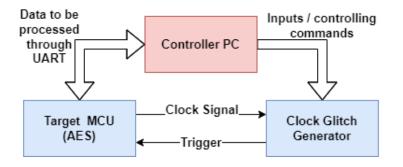

| 3.14 | The Clock Glitching FIA Setup                                                             | 54 |

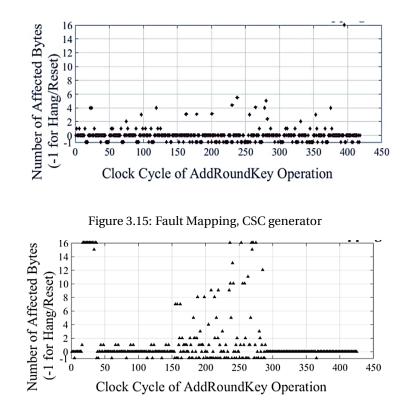

| 3.15 | Fault Mapping, CSC generator                                                              | 55 |

| 3.16 | Fault Mapping, CDCF generator                                                             | 55 |

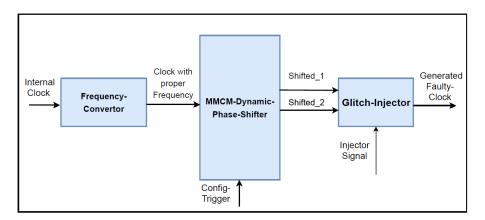

| 3.17 | General Architecture of the Clock Glitch Generator                                        | 57 |

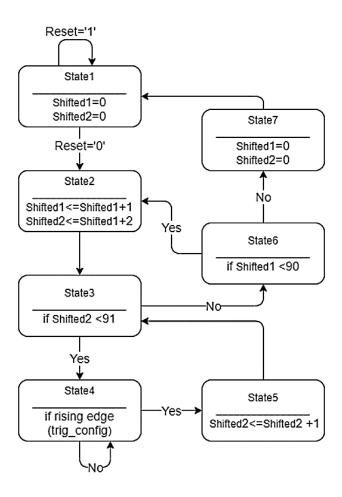

| 3.18 | The State Machine for Updating the Phase Shifts                                           | 58 |

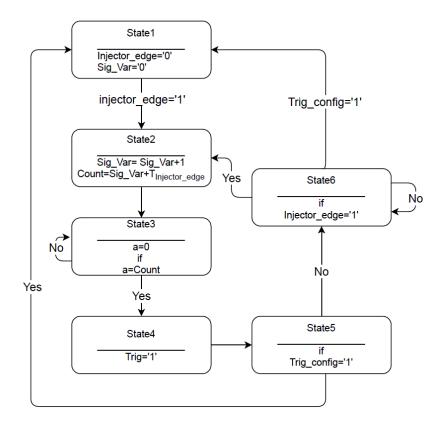

| 3.19 | The State Machine for Updating the Glitch Location                                        | 58 |

| 3.20 | An Example of the Generated Faulty Clock                                                  | 59 |

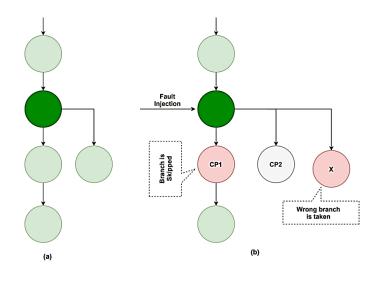

| 3.21 | Control Flow Evaluation for Unconditional Branch                                          | 61 |

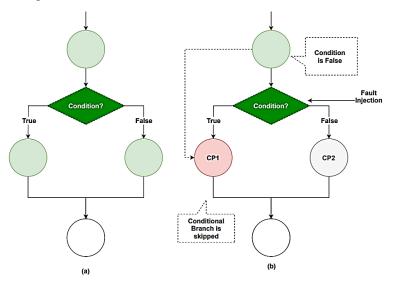

| 3.22 | Control Flow Evaluation of Single Conditional Branch                                      | 61 |

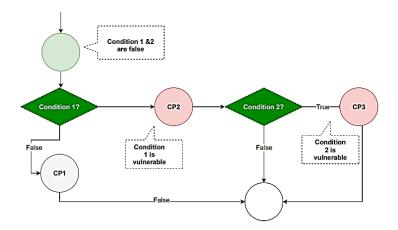

| 3.23 | Control Flow Evaluation for Nested Condition                                              | 62 |

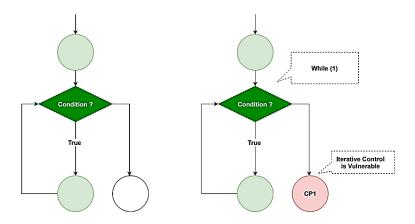

| 3.24 | Control Flow Evaluation of an Iterative Control                                           | 62 |

| 4.1  | ICEM Assessment Methodology                                                               | 68 |

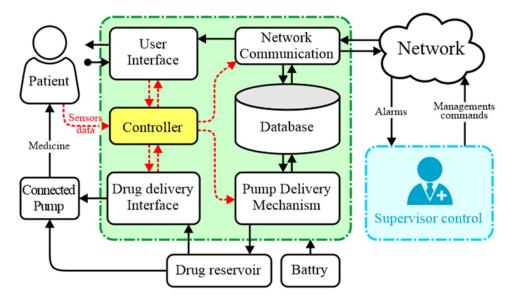

| 4.2  | Infusion Pump Physical Architecture                                                       | 70 |

| 4.3  | Critical Assets in Sec-Pump                                                               | 71 |

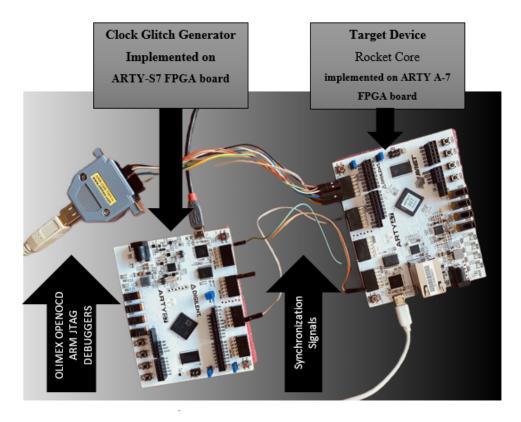

| 4.4  | The Experimental Setup                                                                    | 73 |

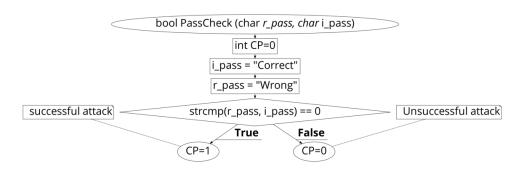

| 4.5  | Sec-Pump Authentication Evaluation Process                                                | 75 |

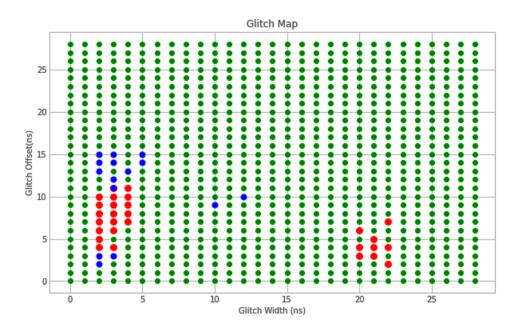

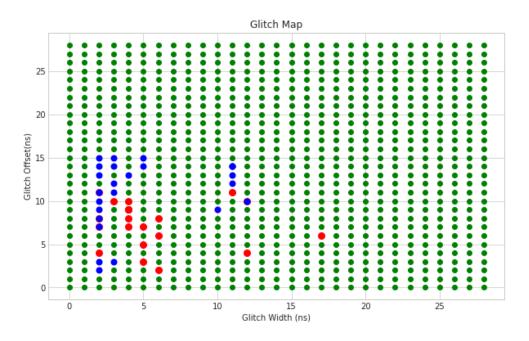

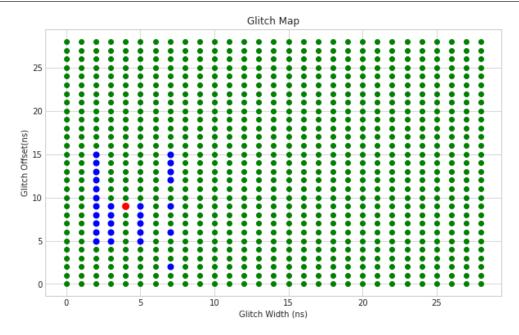

| 4.6  | Glitch Map for Single-Step Authentication (RED: Successful FIA, BLUE: Target Reset) .     | 75 |

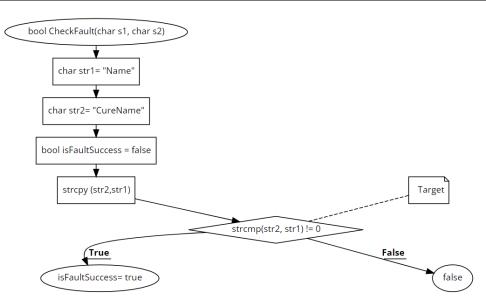

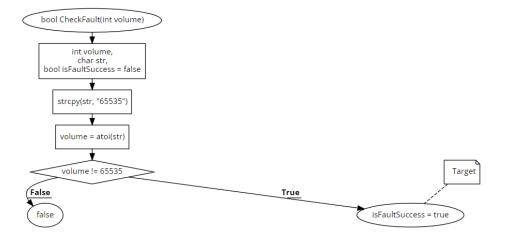

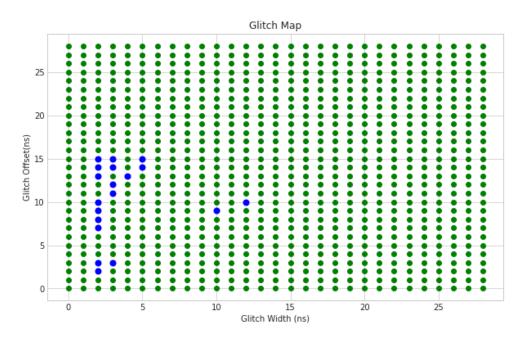

| 4.7  | Sec-Pump Drug Management Module Evaluation Process (strcpy function)                      | 77 |

| 4.8  | Glitch Map for <i>strcpy</i> function in Drug Management Module (RED: Successful FIA,     |    |

|      | BLUE: Target Reset)                                                                       | 78 |

| 4.9  | Sec-Pump Drug Management Module Evaluation Process ( <i>atoi</i> function)                | 78 |

| 4.10 | Glitch Map for <i>atoi</i> function in Drug Management Module (RED: Successful FIA, BLUE: |    |

|      | Target Reset)                                                                             | 79 |

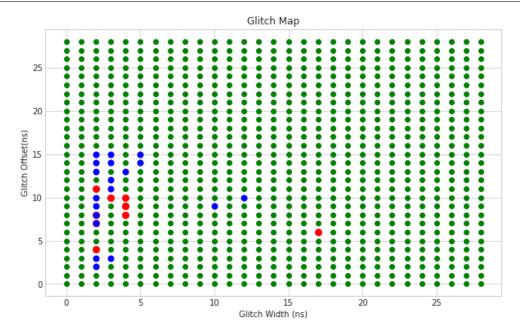

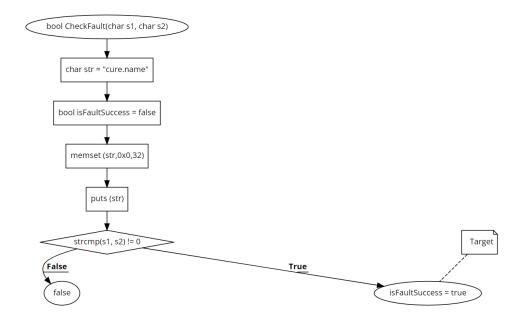

| 4.11 | Sec-Pump Drug Management Module Evaluation Process ( <i>memset</i> function)              | 80 |

| 4.12 | Glitch Map for memset function in Drug Management Module (RED: Successful FIA,            |    |

|      | BLUE: Target Reset)                                                                       | 81 |

| 4.13 | Glitch Map for Nested Conditional Authentication (RED: Successful FIA, BLUE: Target       |    |

|      | Reset)                                                                                    | 82 |

| 5.1 | Experimental-Based Evaluation Results With Combinatorial Glitch Parameters $\ldots$   | 89  |

|-----|---------------------------------------------------------------------------------------|-----|

| 5.2 | A 5-stage RISC-V CPU implementation                                                   | 90  |

| 5.3 | RISC-V based instruction formats                                                      | 90  |

| 5.4 | Simulation results of different functions                                             | 96  |

| 5.5 | Fine Tuned Experimental Evaluation Results for memset, strcpy, and strncpy $\ldots$ . | 97  |

| 5.6 | The architecture for our approach                                                     | 98  |

| 5.7 | The percentage of the successful attacks for each block considering our utilized de-  |     |

|     | tection patterns                                                                      | 104 |

# LIST OF TABLES

| 2.1 | Clock Fault Injection Techniques and Characteristics                                          | 19  |

|-----|-----------------------------------------------------------------------------------------------|-----|

| 2.2 | Supply Voltage Fault Injection Techniques and Characteristics                                 | 24  |

| 2.3 | Review of Previously Proposed Clock Glitch Generators                                         | 33  |

| 2.4 | Review of Previously Proposed Clock Glitch Generators                                         | 39  |

|     |                                                                                               |     |

| 3.1 | Glitch Generator Comparison of Affected Bytess                                                | 56  |

| 3.2 | Fault Multiplicity of Single-Byte Faults                                                      | 56  |

| 3.3 | Important Control Flow Statements                                                             | 59  |

| 3.4 | The behavior of different high-level C-functions                                              | 63  |

|     |                                                                                               |     |

| 4.1 | Different Asset Categories of Sec-Pump                                                        | 72  |

| 4.2 | Potential FIA Threats for Sec-Pump                                                            | 74  |

|     |                                                                                               |     |

| 5.1 | Propagated fault effects based on different instruction types                                 | 93  |

| 5.2 | The calculation of vulnerability factor for Sec-Pump's software blocks $\ldots \ldots \ldots$ | 103 |

|     |                                                                                               |     |

## LIST OF ABBREVIATIONS

- **IoT** The Internet of Things

- IoMT Internet of Medical Things

- **IIoT** Industrial Internet of Things

- **SCA** Side Channel Attack

- **FIA** Fault Injection Attack

- CF Control Flow

- DF Data Flow

- **CSC** Combine Shifted Clocks

- CDCF Combine Different Clock Frequencies

- VM Voltage Multiplexing

- VSC Voltage Short Circuiting

- VGPG Voltage Glitching using Pulse Generator

- **DCM** Digital Clock Manager

- MMCM Mixed-Mode Clock Manager

- **DRP** Dynamic Reconfigurable Port

## 1 INTRODUCTION

#### Contents

| 1.1 | Basic Concepts of Hardware Attacks   | 3  |

|-----|--------------------------------------|----|

|     | 1.1.1 Side-Channel Attacks           | 4  |

|     | 1.1.2 Fault Injection Attacks        | 6  |

| 1.2 | Thesis Statement and Main Objectives | 9  |

| 1.3 | Thesis Contributions                 | 11 |

| 1.4 | Organization of the Dissertation     | 12 |

The Internet of Things (IoT) connects objects and devices of all types over the Internet, either wired or wireless. This technology has transformed many aspects of our daily lives, and there are many useful applications for these devices. For instance, IoTs help to make smarter, safer, more comfortable, and energy-efficient homes [1]. Moreover, they have a high potential to improve and automate healthcare services. The Internet of Medical Things (IoMT) has already been employed at home and in hospitals to enhance the safety and efficiency of medical services [2]. The banking sector and other financial areas are also striving to make use of IoT and benefit from it. This way, the customers can always stay in touch with their bank, which makes it possible to gather more data about their behavior and preferences [3]. Additionally, IoTs are employed in industrial sectors such as manufacturing, energy, mining, and transportation [4]. These intelligent devices in the industry, so-called Industrial IoT (IIoT), are usually connected to a central system that can monitor, collect, exchange, and analyze the gathered data.

Despite all of these applications and achievements for IoTs, their rapid technology usage comes with various security challenges. The security attacks against them can result in dangerous and costly outcomes, i.e., it can reveal personal information in public [5,6]. The attacks can be launched against any IoT assets and facilities. They can potentially damage or disable a system's regular operation, which can cause severe economic damage to the owners/users. An example includes an attack on medical IoT systems and taking control of the monitoring mechanisms [7]. Moreover, the personal data from an embedded sensor inside or close to the patient's body can be collected and transferred to the adversary. Regarding this, performing security assessments against real examples like medicine injection pumps is required to demonstrate the potential risks of numerous security flaws of life-critical medical IoTs [8, 9]. As an example, an attacker can maliciously modify the functionality of a pump and target running software and raise the amount of the injected insulin over time [9].

In general, the attacks against IoT embedded devices can be classified into three main categories, including 1) Network, 2) Software, and 3) Hardware Attacks. In practice, an attack can employ any or all of these approaches. In principle, the Network-based Attacks could be applied remotely at any point of the interconnected IoTs. There are various studies that show IoTs are susceptible to Network Attacks such as Denial of Service and Spoofing [10]. The second class of security attacks against IoTs is applied at the software level. They can be applied at various software abstraction layers, such as in high level and low level. For instance, some High-level Software Attacks are brute force attacks that target an application that consists of a pair of input/output to get authenticated or to reveal the information. Other examples aim to inject malware or manipulate the machine-level code at lower levels and hijack the application's execution flow [11]. Besides software attacks, numerous security threats exist against the user-accessible targets named Hardware Attacks [7, 12]. These attacks become critical when the attacker can have direct physical access to measure the device operating parameters (e.g., power and propagation delay signal) or can tamper with the external inputs of the targeted embedded device.

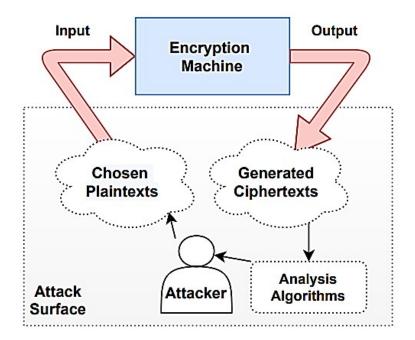

There are various techniques to apply Hardware Attacks against embedded systems. Two of the main techniques which are considered in this thesis are the Side-Channel Attacks (SCA) and the Fault Injection Attacks (FIA). One can perform SCAs to extract useful information (e.g., cryptographic key) by observing the physical characteristics such as power consumption or electromagnetic emissions while the device is executing a specific operation. In FIAs, the attacker tries to manipulate the device's input or emit different energy rays to circumvent the security checks (e.g., user authentication) or execute an arbitrary code that causes unintended behavior of the target (i.e., by changing the application's control flow). There are also multiple combinations of FIA and SCA, where the SCA takes advantage of fault impacts on the targeted device. For example, in [13,14], a FIA reduces the number of rounds of a cryptographic algorithm, and the SCA can extract the pass key faster.

To design a secure embedded system, one needs to follow a set of assessment procedures against different types of threats in the three domains of network, software, and hardware. The first two fields have been investigated and extensively analyzed over the past years [15]. Subsequently, numerous countermeasures are proposed and employed to secure the systems against such vulnerabilities [16, 17, 18]. However, securing the system against network and software attacks is often inadequate to achieve the desired security protection, especially in easily accessible targets. Thus, it is required to consider the hardware security and to include different evaluation processes against physical threats. To design an efficient hardware evaluation methodology, one first needs to understand the fundamentals of these attacks. Regarding that, the background and concepts of the Hardware Attacks are described in the following.

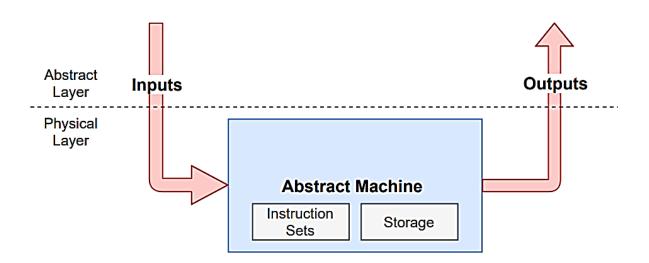

Figure 1.1: The Abstract Machine of an Embedded Systems

### 1.1 BASIC CONCEPTS OF HARDWARE ATTACKS

Embedded systems, at the beginning of their emergence and early developments, were not studied in terms of security as of today. They were mainly considered as models called abstract machines. Figure 1.1 shows an example of such abstract machines, including the inputs, the outputs, and the relevant operation sets, usually at the high level of the system. In this case, it was assumed that an attacker could only access and compromise the input and output of this system model [19, 20]. Figure 1.2 shows an example of an encryption machine in which the attacker can choose plain texts freely, observe the generated cipher texts, and mathematically break a cryptography algorithm (to reveal the key). Similar attacks can be applied against different designs to discover their internal executive algorithm and extract secret information. These attacks, as they were mostly utilized to hack the cryptography systems, were termed Crypto-Analysis attacks. Since then, the ability and success rate of many cases in classical crypto-analysis attacks have been reported [21].

Along with the classical analysis attacks, the implementation-specific characteristics of the embedded systems, which are referred to as side-channels, became an important concern in the field of security. In this regard, the vulnerabilities of the newfangled category were reported in security systems in which they were considered very secure from the mathematical point of view. The NSA, for example, pointed to signs of detected vulnerabilities in encrypted and teletyped messages by a conventional oscilloscope [22]. Besides, in the 1990s, N. Kocher et al. presented a new topic called Hardware Attacks, which officially came alongside the conventional attacks of that time [20,23]. In these attacks, vulnerabilities related to the hardware layer of the target system were analyzed in a more specific way compared to the classical attacks. Since then, Hardware Attacks have emerged as a new and powerful approach for attackers to compromise the accessible embedded systems and their security [6].

A Hardware Attack is based on the interactions of an embedded system with its external en-

Figure 1.2: An Example of Traditional Assumption for Crypto-analysis Attacks against an Encryption Machine

vironment [6]. Figure 1.3 shows the taxonomy of Hardware Attacks. Depending on the goal of the attacker (e.g., to change the expected behavior of the system or to obtain encrypted information), the appropriate attack model and method must be determined [6,24]. Accordingly, two of the most important approaches including 1) Side-Channel Attacks; 2) Fault Injection Attacks, are studied, where the main focus in this thesis has been on FIA.

### 1.1.1 SIDE-CHANNEL ATTACKS

Side-Channel Attacks are based on gathering the target's produced unintentional outputs, physical characteristics, or observable signals while executing the software. They usually do not require manipulation of the target device, and the attacker can passively evaluate the system interactions [19,25]. An attacker can take advantage of these available side-channel parameters, such as the power consumption [20], the electromagnetic emanation [26], and the thermal signature [27], to mount an SCA in order to obtain the critical data and to leak the secrets from an embedded device [7]. Figure 1.4 depicts some common side-channel parameters, including Electromagnetic emissions, Timing information, Acoustic leakage, and Power signals, which have leaked from a target device during data processing. All types of discovered side-channels have been reviewed in [19].

The SCA's most basic instances have been performed against cryptographic machine implementations to extract their secret key [28,29]. The subsequent works employed a similar approach on various side-channels and targeted implemented ciphers (e.g., DES, AES, and RSA) inside the

Figure 1.3: Taxonomy of Physical Attacks

Figure 1.4: Side-Channels from an Embedded Device

smart-cards, mobile phones, personal computers, dedicated ASICs, and different microprocessor architectures. These examples demonstrate that SCAs can pose a significant challenge to the security of IoT devices.

SCAs are performed in two phases:1) Interaction phase, 2) Exploitation phase. The first phase is to find an observable and measurable physical characteristic of a target and monitor that, generally without any modification or opening up the chip (usually during the normal operational mode). Note that this step often needs full access to the device for the attacker, who can run it iteratively several times. Occasionally, based on the level of control an attacker may have on a device, the SCA can be performed with the appropriate input vectors to get optimized results [25]. The exploitation phase analyzes the collected data to extract the important physical information related to the non-functional and internal operations. Although different SCAs may have their unique interaction phase (way of data measurement), they all follow a very similar approach to their exploitation phase [30].

### **1.1.2** FAULT INJECTION ATTACKS

Fault attacks are the noticeable type of physical attacks, in which the expected and secure behavior of the targeted devices is liable to be jeopardized.Fault Injection Attacks have been designed and introduced in various methods, such as 1) By manipulating the inputs of the device (such as clock or voltage); 2) By stressing the target through changing its surrounding conditions (such as raising the temperature); 3) By emitting energy rays (such as electromagnetic or laser). They can either modify the process of software execution or the stored values inside the memory locations. FIAs can be classified into three categories, namely: 1) Invasive, 2) Non-invasive, and 3) Semi-invasive [31].

Invasive attacks are the type of intrusions performed by de-packaging the Integrated Circuit (IC) and modifying the physical properties to do some probing. Invasive attacks, such as Microprobing, laser, or optical fault injection, are the strongest physical attacks without imposing any restrictions on accessing the inside of the chips [32]. These kinds of attacks are very powerful in precise space-time positioning, and they can reveal considerable secret information from internal parts of the chip to the attackers. However, they are expensive, mostly irreversible, and complicated. In addition, they have to be performed by qualified specialists in laboratories equipped with special devices. They are usually applied against very secure devices such as smart-cards or complex Commercial Off-The-Shelves (COTS) components, in which the target is in the form of industrial products, and the attacker usually has more features and knowledge [33]. Nonetheless, in some cases, such attacks are not appropriate methods for individual IoT hackers because they are too costly for them, and also, they do not have access to wide-range facilities.For the consumer IoTs, the attack would be in most cases too costly for the gain.

The semi-invasive attack is a type of FIA that stands between invasive and non-invasive at-

tacks [34,35]. This type of attack can involve de-packaging the IC layers to gain access to the internal surface of the target, but normally, the passivisation layer remains unimpaired. For instance, optical fault injection is a semi-invasive attack in which the protection layer of the device has to be ruined [34].

Finally, non-invasive attacks are the type of non-destructive attacks that can be accomplished by only utilizing pin-probing or bus-snooping without damaging the package [32]. Two of the simplest non-invasive fault attacks are tampering with the device clock signal and/or the supply voltage, the so-called clock and voltage glitch attacks [36].

Among those different kinds of FIAs, this thesis considers the non-invasive FIAs against secured embedded applications because there are more threatening than invasive attacks for IoT devices. This is for three main reasons:

- They do not require any physical tampering; refer to the owner of the targeted device might not notice the attack and trust in functionality and security.

- They can be reproduced and updated by using low-cost and easy-to-access equipment, even in a small laboratory [37].

- They have proven that a high success rate can be achieved in a short time [38].

Since such threats can jeopardize embedded software, it is necessary for software developers to evaluate the potential vulnerabilities due to FIAs. Therefore, there should be a systematic security assessment approach to identify the security assets in terms of important functions and data, discover the vulnerabilities, define risks, and illustrate the probability and consequences of the potential successful Hardware Attacks. Discovering the impacts of physical FIA is not always straight forward. So, one needs to understand the FIA effects and their propagation through different levels. Figure 1.5 shows an example of the propagation of an injected fault through layers of an embedded system along with its effects on the target.

These effects can be classified into different categories:

Figure 1.5: Fault propagation through different layers, (1) Fault Injection, (2) Fault Manifestation, (3) Fault Propagation, (4) Fault Exploitation

- Faults at Circuit-Level: The physical stress on any target interface leads to transient electrical faults like transient voltage glitches or current spikes at the circuit level resulting in gate faulty behavior.

- Faults at Micro-Architectural Level: Transient electrical faults might be captured by the latches and flip-flops in the system's data or control paths, resulting in erroneous micro-architectural states or data.

- Faults at Software/Application Level: Faulty values captured by different micro-architectural blocks would cause errors in the control or data flow of the running software. In other words, a fault at the micro-architectural level manifests itself as a deviation in the correct instruction flow or as a faulty operand or opcode at the software level. Note that the faults at the software level can be exploited in different manners.

In general, the exploited vulnerabilities at application level can be modeled as 1) Control-Flow Corruptions (CF-Corrupt) and/or 2) Data-Flow Corruptions (DF-Corrupt) at the application level. The CF-Corrupt can occur by disrupting the intended order of instructions, branches, or statements of the embedded software. Accordingly, several works have shown that even non-invasive FIAs such as clock/voltage glitching attacks can lead to CF-Corrupt by skipping or repeating one instruction or by replacing that with another instruction [39, 40]. Other CF-Corrupt instances happen when the evaluation step of a conditional branch has been skipped, and the incorrect branch is taken [41]. FIAs can alter the conditional branch instructions, which are used to implement loops and change conditions in security checks of embedded software.

DF-Corrupt happens when the attacker compromises the integrity or confidentiality of processed data by disturbing the targeted MCU. For example, they can corrupt a single bit, a single byte, multiple bytes, or a single word of a security-critical variable in various ways (e.g., flip, set, reset, random) [42,43]. Furthermore, one can exploit the vulnerable arithmetical/logical instructions to generate intermediate or final faulty results. By repeating this procedure and obtaining more erroneous computational values, it is possible to leak secret and sensitive information [44]. On the other hand, FIAs can affect the memory operations such as load, store, and copy instructions and lead to DF-Corrupt [45]. These manipulated values can directly affect the system behavior, mainly while other computational or condition evaluation instructions are using them.

Considering the mentioned vulnerabilities, the security specialists aim to mitigate the destructive consequences of FIA by developing a set of software and hardware level defensive countermeasures. For example, redundancy-based protection methods are one of the most utilized softwarebased methods, in which one important instruction is repeated, and its result is compared; Then, one detects the mismatch and runs the error management routine (if necessary) [46]. Another approach is named the duplication method without comparing and fault detection steps [47]. The signature-based protection is another approach to counter-based protection, and that assigns a unique identifier to all of the basic blocks inside the control flow graph. Then, it verifies the identifier/signature by every control-flow transfer. Basic examples of hardware-based countermeasures are applied in different ways, such as utilizing passive shields to cover the vulnerable part of the chip and using specific logic such as autonomous frequency detectors that can detect the glitches in the clock signal [48].

The software-based countermeasures have significant performance overhead, and they cannot guarantee complete code integrity against fault injection attacks. However, in many noncritical cases, they can provide a good trade-off between hardware cost and security. Accordingly, hardware-level countermeasures can be applied for safety-critical embedded devices to protect the design against stronger FIAs. Moreover, hardware-based mechanisms have better performance than software solutions since fewer processor cycles need to be spent on performing the security checks. The main drawback of the hardware-based countermeasures is their cost for embedded devices.

### **1.2 THESIS STATEMENT AND MAIN OBJECTIVES**

Embedded software evaluation against hardware-based security attacks has recently gained compelling attention in industry and academia. Although several assessment tools and platforms have been developed, choosing the right hardware platform is not always easy and depends on many parameters. In response, the first objective of this thesis is to review some of the existing assessment tools, specifically against non-invasive fault injection attacks, and to classify them according to their specifications and features. This study helps to determine the important factors of an hardware evaluation platform by considering the budget and the design effort.By budget, the aim is to use low-cost devices and chips and by design effort, the aim is to have a easily configurable platform. The way that IoT products are developed today - especially with their reduced" time to market"- does not always give time to perform a third-party hardware security evaluation. Nowadays, developers get more involved in performing the evaluations by themselves. The existing commercial evaluation tools have been simplified and matured considerably to satisfy the developers' needs; however, they are dependent on the use of specific hardware, closed-source, not accessible to deploy for the low-cost IoTs and not easy to exploit the software-level vulnerabilities. On the other hand, very little research has been conducted to determine whether the hardware security analysis instruments fulfill the embedded software developers need to secure their code. Accordingly, the second objective is to provide one open-source and low-cost hardware evaluation tool, which is highly important in the embedded software development stage.

When such a tool is available, the target users (e.g., non-security specialists or embedded software developers) must be guided properly to apply the practical experiments. Unfortunately, the previous research works have only focused on the in-depth evaluation of low-level specific instructions, and these isolated approaches cause inefficiency for a broad evaluation purpose. So, this research's next objective is to define comprehensive and function-level evaluation methods to be executed in order to detect the embedded software vulnerabilities. Combining these scenarios and the open-source platform designed in this thesis can significantly simplify the evaluation process at the development phase.

The introduced hardware platform in this thesis, can efficiently apply fault injection attack into an embedded system; however, it still requires significant time and analysis effort to detect the vulnerabilities of a target. In practice, the evaluation time plays an essential role in the embedded software design step, and one cannot ignore or just accept it as "that is how long it takes." Likewise, this approach lacks information about the root causes of the revealed vulnerabilities and cannot guide the target user to fix these issues or add proper countermeasures. Accordingly, this thesis improves the evaluation process's critical factors (e.g., accuracy, coverage, and time).

The proposed experimental FIA platform along with its associated tools and the defined methodologies in this thesis work construct an evaluation framework, to be used by embedded developers. Accordingly this framework is verified in a case study to have a qualitative study. Among various attention-demanding case studies, this thesis focuses on a medical IoT application named Sec-Pump, which is also in the context of the SERENE IoT project. The SERENE IoT project (Secured EneRgy EfficieNt hEalth-care solutions for IoT market) aims at developing high quality smart ehealth IoT devices in Europe. SERENE-IoT project is labeled within the framework of PENTA, the EUREKA Cluster for Application and Technology Research in Europe on NanoElectronics. The project contributes to developing high quality connected care services and diagnostic tools based on advanced smart health-care IoT devices. The revealed vulnerabilities from hardware security evaluation of the Sec-Pump can detect the real potential risks in similar critical applications for the end-users and the service providers.

In brief, the main objectives of this thesis are summarized in the following:

- To implement an open-source, low-cost and efficient hardware evaluation platform to apply clock glitching FIA. This hardware platform will be generic and can be used for various embedded targets.

- To investigate and review the state of the art of the existing practical fault injection platforms that are used to attack various embedded systems

- To analyze the cost overheads, the advantages and the disadvantages of the proposed hardware evaluation platform in front of other existing platforms

- To define a practical evaluation process for the developers and non-security specialists at the design stage to identify the potential security vulnerabilities

- To evaluate the potential vulnerabilities at high level of the software and to narrow down the fault injection time intervals by using the results from the simulation-based experiments respectively

- To improve the coverage, efficiency, accuracy of injected faults and to simplify the analysis process for embedded applications

- To apply our evaluation framework which consists of a clock glitching FIA hardware platform and our evaluation methodology into a practical case study (Sec-Pump)

- To identify the security vulnerabilities of an IoT application (Sec-Pump as an example) by using our evaluation framework

### **1.3** Thesis Contributions

The main contributions of this thesis are summarized in the following:

#### • The Existing Fault Injectors are Reviewed

The first contribution of this work is to study the different non-invasive fault injection approaches and platforms. This helped to extract their important factors such as complexity, cost, and required usage expertise. The thesis focus has been on the clock, and voltage fault injection approaches due to their effectiveness and affordable equipment. Accordingly, this thesis first reviews the proposed clock and voltage glitch generators in the literature and categorizes them based on different essential parameters in the attack process.

This part has been published in [6].

#### • A Hardware Evaluation Platform for FIA is Designed

The reviewed state of the arts was challenging to adapt for general IoT designs and it lacked the proper configuration characteristics. The second contribution of this thesis is in Chapter 3, which introduces a practical evaluation platform to evaluate an MCU-based system running a software application against the Clock Glitching FIA. This platform is specifically focused on the clock glitching FIAs, and it is a low-cost and easy-to-use interface for nonsecurity specialists. Then, the utility of this platform is demonstrated by applying FIA to an encryption algorithm and analyzing its results.

This part has been published in [44].

#### Application-level Test Scenarios is Proposed

Another contribution of this thesis is to define high-level test scenarios to exploit and analyze the vulnerabilities of a target embedded software after injecting faults. This analysis is applicable for high-level patterns and standard C functions. After this analysis, a report will be generated, which can help the embedded developer to mitigate the vulnerabilities in the early developing stage of the application. The main focus of this thesis approach is on the analysis of the most prominent control flow and data flow integrity objectives.

This part has been published in [45].

#### • An Evaluation Framework for Software Developers is Provided

The fourth contribution is to provide a complete overview of the threat modeling for the critical assets of an embedded application against FIAs. The software developers should be guided correctly to identify the right critical assets of their application and then conduct an appropriate assessment against the potential attacks. Therefore, in addition to an evaluation platform, a methodized approach is defined to analyze the target code step by step.

This part has been published in [7,49].

#### • The Timing Characterization of Clock Glitching FIA is Improved

The next contribution is to introduce a mixed simulation-experimentation methodology to detect the security flaws against the clock glitching FIA. First, the simulation operates on the defined fault models as fault injection attacks into the RISC-V micro-architecture. This can help to improve the FIA timing characterization in the experimental attacks. Therefore, the experimentation attack could give the analyzer more detail and more precise results.

This part has been published in [50].

#### • Symbolic Assertion and Code Shredding to Obtain A Global Vulnerability Factor

The last contribution of this thesis is to use the symbolic assertions and obtain a global vulnerability factor for the embedded software evaluation against the clock glitching FIA. Accordingly, a partitioning approach is applied to divide an application into various code blocks with respect to the functionality and the main variables of each code block. Then, the detection patterns are inserted into the code to report the successful attack and obtain the vulnerability factor. This approach is an efficient criterion to evaluate all the corner case vulnerabilities of software blocks against FIA. The final goal of this thesis is to verify that by using such an approach, one could show the potential risks of the Sec-Pump blocks.

### **1.4** Organization of the Dissertation

The remaining part of the dissertation is organized as follows (Figure 1.6): Chapter 2 explains the basics of fault injection attacks and reviews the state-of-the-art of the existing fault injectors. Chapter 3 describes the details of a proposed evaluation platform against fault injection attacks. It will then show the experimental results and verify the usage of the platform. Chapter 4 presents the steps of a high-level evaluation approach for embedded software developers. To explain the introduced methodology, it has been applied in a case study (Sec-Pump). Chapter 5 studies the optimized evaluation methods to improve the assessment results. It is based on utilizing the simulation approach in order to improve the experimentation parameters. Finally, the conclusions and perspectives of this thesis are presented in Chapter 6 and 7.

## Chapter 2:

State of the Art

#### Chapter 3:

Hardware Security Evaluation Platform

### Chapter 4:

Hardware Security Assessment By Utilizing The Hardware Evaluation Platform

### Chapter 5 :

Optimizing the FIA Evaluation Process by Utilizing Simulation-based Analysis and Symbolic Assertion

#### Chapter 6 and 7:

**Conclusions and Perspectives**

Figure 1.6: The road map for the dissertation

# 2 STATE OF THE ART

#### Contents

| 2.1 | A Basic Setup for a FIA Platform                  | 15 |

|-----|---------------------------------------------------|----|

| 2.2 | Clock-Based FIAs                                  | 17 |

|     | 2.2.1 Concepts of Clock FIAs                      | 17 |

|     | 2.2.2 Clock Glitching Attack Examples             | 20 |

|     | 2.2.3 Clock Glitch Generator Characteristics      | 20 |

| 2.3 | Voltage-Based FIAs                                | 22 |

|     | 2.3.1 Concepts of Voltage FIAs                    | 22 |

|     | 2.3.2 Voltage Glitching Attack Examples           | 25 |

|     | 2.3.3 Voltage Glitch Generator Characteristics    | 26 |

| 2.4 | A Review of Fault Generators                      | 27 |

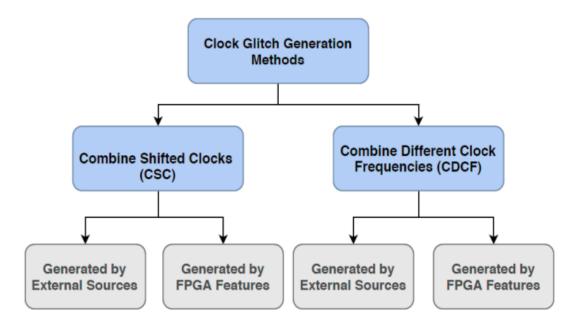

|     | 2.4.1 Clock Glitch Generators in the literature   | 27 |

|     | 2.4.2 Voltage Glitch Generators in the Literature | 35 |

| 2.5 | Conclusion                                        | 41 |

This chapter studies the fundamentals of FIAs and reviews the main fault generator parameters. These factors determine the applicability and efficiency of a fault injection platform. Then, the principles of clock and voltage generators are studied, and their important specifications are determined. Finally, it reviews the state-of-the-art clock and voltage fault generators and categorizes them based on their features.

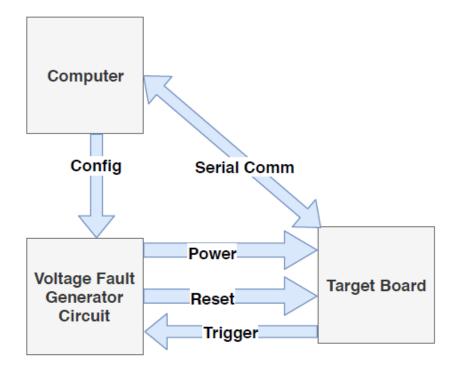

## 2.1 A BASIC SETUP FOR A FIA PLATFORM

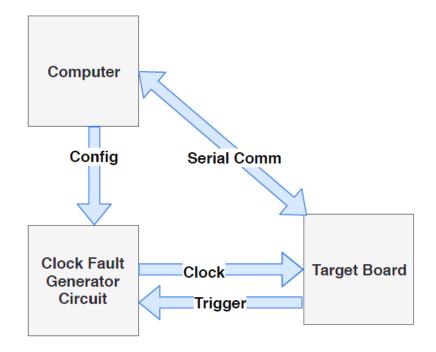

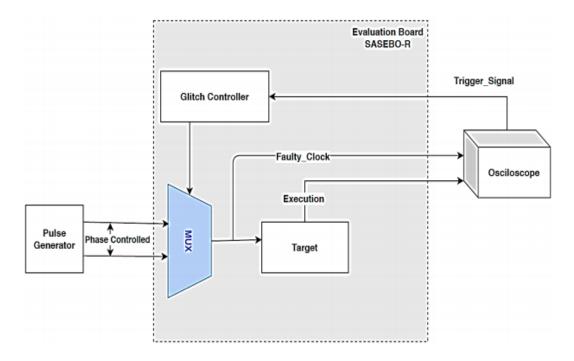

Figure 2.1 shows an experimental setup for a fault injection system. It includes a target board, a fault generator, and a controller computer. The fault generator is the crucial component of a fault injection system. In the following, the main characteristics of a fault generator, which affect the success rate of the attacks, are described.

Generally, in the hardware-controlled fault injection techniques, a separate external fault generator is used to induce faults in the running application. It is essential to produce well-controlled faults utilizing the generator in order to achieve the desired results. It is, therefore, a challenging

Figure 2.1: General Fault Injection Attack Setup

procedure to design a fault generator with a high level of accuracy and precision. Several factors determine the applicability and efficiency of a fault generator. Below, a list of features are identified, which are the main parameters for a hardware-based fault generator [38,51,52,53,54,55,56,57,58]:

- Accuracy in the generated faulty signal: The accuracy of the generated faulty signal can be defined as our control over the fault parameters. In fact, the more control one has over the generated faulty signals, the more achievement in successful attacks in terms of generating and exploiting the desired faults. Control over the time and location of injected faults can be achieved using the communication lines between the controller PC and the fault generator.

- Run-time fault configuration: In some evaluation platforms, the parameters of a faulty signal produced by the generator can be reconfigured during run-time. They are not limited to the design time and can be used to test a target system during the attack phase. This feature is available in some generators and is based on some kinds of FPGAs, allowing modification of some parameters during the run time [51].

- Reproducibility of the faulty signal: Reproducibility is the ability to obtain the same results in multiple repeats of the same test. Regarding this feature, the faulty signal should be reproducible and validated by a third party if the same hardware is used (for example, the same FPGA). This parameter becomes more important when the same evaluation platform is used multiple times to generate a faulty signal [38, 51, 52, 53, 56, 58].

- Randomness in faulty signal: Many of the faulty signal-generating methods presented, such as [59, 60, 61, 62, 63], are deterministic methods. To set up a fault generator and to apply an attack with high accuracy, all the output parameters must be prepared and calculated. However, as this requires complete and adequate information about the target, it is not applicable

Figure 2.2: Synchronous Representation of Digital ICs [55]

in all real-world attack scenarios. In addition, in order to achieve an efficient attack, a large number of possible combinations of the fault injection parameters need to be covered. This makes deterministic methods intractable within a limited time. To address this issue, a fuzzy-based fault generator has been proposed. It has been reported that this method has a high attack success rate [54].

These factors for the clock and voltage fault attacks include accuracy, development expenses, the complexity of the system setup, and user expertise.

In the following, the basic concepts and significant parameters in clock and voltage fault injection methods are reviewed.

# 2.2 CLOCK-BASED FIAS

Clock-based fault injection is a low-cost attack that can be applied by the attacker to devices supplied with an external clock such as smart cards. If the target uses an internal clock signal, this method is often not applicable. The fundamental concepts and related characteristics for this approach are provided in the following sub-sections.

## 2.2.1 CONCEPTS OF CLOCK FIAS

First of all, to explore the importance of proper timing in digital ICs, one has to understand the synchronous design concept [55]. This is the basis for simple to complex computing systems. Digital designs often consist of two main parts: 1) combinational logic for computational operations and 2) memories such as register banks to store the computation results after each clock cycle. Figure 2.2 shows the concepts of propagation delay and setup time as irrevocable delays for performing computational operations. They are important timing parameters and need to have valid stored values in the flip-flops.

The inequality in equation 2.1 should be satisfied in order to guarantee the correct behavior of the flip-flop.  $T_{clk}$  represents the clock period,  $T_{critical}$  represents the minimum time needed to

Figure 2.3: Violating Critical Path Delay by Insertion of Additional Positive Clock Edge

process the data through the combinational part, and  $T_{Setup}$  represents the setup time of flip-flops, specified as the minimum amount of time for which data input needs to be stable before the active edge of the clock:

$$T_{clk} > T_{Critical} + T_{setup} \tag{2.1}$$

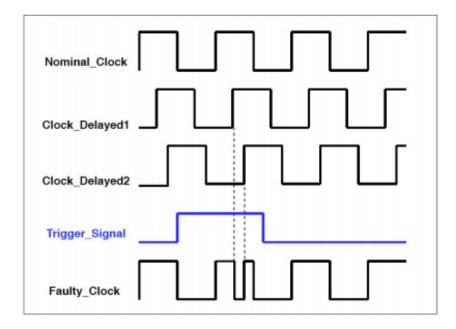

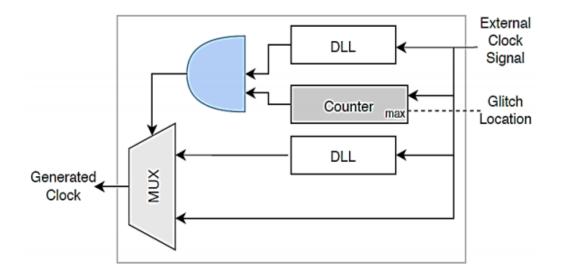

One way to perform fault injection attacks is to violate these timing constraints. Violation of the time constraints induces faults in the target.  $T_{critical}$  and  $T_{Setup}$  are two parameters that are dependent on the system logic design and the technology, therefore they cannot be manipulated to perform fault injection. Unlike the previous parameters,  $T_{clk}$  is a knob used for attackers to carry out their fault injections. Clock fault injection is applied by tampering with the clock signal temporarily or permanently. There are two different methods of clock fault injection: 1) Overclocking and 2) Clock glitching. Overclocking is a kind of timing violation attack in which one tries to apply a clock signal with a higher frequency than the nominal frequency for a specific time interval [55]. In fact, the overclocking method violates the timing constraint inequality (eq1) by decreasing the clock period. A clock glitch is regarded as an unwanted transition in the clock signal.

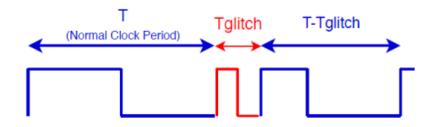

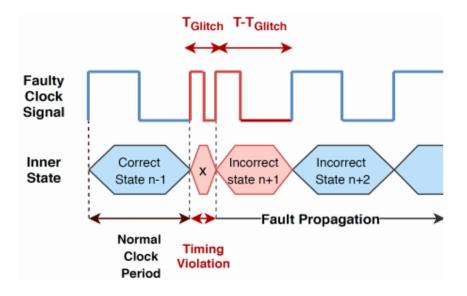

In the clock glitching method, the attacker generates glitches in the clock signal. The induced glitches produce extra edges in the clock signal, resulting in an erroneous output as the timing inequality has been violated. Figure 2.3 shows a typical clock signal in which a glitch is induced. In this figure, T represents the normal clock period, and  $T_{Glitch}$  is the width of the glitch signal. As it can be seen, an extra edge appears in the clock signal. Another important parameter is  $T_{min}$ , which is equal to the reciprocal of maximum frequency. In order to have erroneous behavior,  $T_{Glitch}$ " as a "post-glitch" phase. This abnormal semi-clock part could be considered as another approach for fault injection. In this case, if "T- $T_{Glitch}$ " is less than  $T_{min}$ , it leads to an erroneous behavior. Figure 2.4 shows how a clock glitch can inject faults in the system and how these faults can propagate through the next clock cycles [64].

Table 2.1 compares the accuracy of overclocking and clock glitch attacks. The first column, entitled spatial precision, refers to the level of accuracy with which the fault generator can inject a fault into a specific location. Temporal precision, the second column, is defined as the accuracy of the fault injection process in inducing a fault at a specific time. The third column reveals glitching parameters such as frequency, width, and amplitude. The last two columns show equipment costs

Figure 2.4: Representation of Clock Glitch and Fault Injection [64]

| Technique | Spatial   | Temporal   | Controlling     | Equipment | Required  |

|-----------|-----------|------------|-----------------|-----------|-----------|

| reeninque | precision | precision  | the intensity   | costs     | expertise |

| Over      | Low       | Not        | Clock frequency | Low       | Low       |

| Clocking  | (global)  | Applicable | Clock nequency  | LOW       | LOW       |

| Clock     | Low       | High       | Glitch          | Low       | Moderate  |

| Glitching | (global)  | (local)    | parameters      | LOW       | mouerate  |

Table 2.1: Clock Fault Injection Techniques and Characteristics

and the required level of expertise for fault injection, respectively. Since the clock is a global signal, sufficient control is needed to induce a fault in a specific location in the system. Consequently, fault induction in the clock signal would not have high spatial accuracy with either the overclocking or clock glitching techniques.

In the clock glitching method, high temporal precision can be achieved by synchronizing the target and the fault generator circuit. Temporal precision is meaningless in the overclocking technique as the clock frequency is considered a fault. Briefly, the clock glitching technique is more desirable than the overclocking technique as it provides more accuracy and flexibility to manipulate clock signal parameters. In fact, the overclocking technique is not applicable for injecting a fault into a specific instruction at a specific time. In such cases, clock glitching is the only technique for fault attacks. For accurate fault attack using the clock glitching technique, especially for complex processor architectures employing the instruction pipeline, the fault generator circuit must be highly accurate in terms of injection time and location. In addition, the injection process should be carried out as fast as possible to avoid synchronization violations [65].

In this thesis, the main focus is on the clock glitching attack approach. Figure 2.5 shows a

typical circuit employed by attackers to conduct a fault injection attack. A clock glitch generator generally consists of different hardware components such as FPGA boards, pulse generators, and micro-controllers to enable the implementation of various glitch generating methods. The desired configuration is provided by a controller PC connected to both target and generator sides. Synchronization is done by using the trigger signal between the target and the generator.

Figure 2.5: Experimental Setup of Clock Fault Attack

## 2.2.2 CLOCK GLITCHING ATTACK EXAMPLES

The clock glitching attack can significantly impact the critical parts of a running application, such as its encryption module and arithmetic or logical instructions. In several works, a clock glitching attack has targeted a specific round or operation of the AES algorithm to generate faulty cipher text [38, 44, 52]. These faulty outputs can be used to recover the encryption key. Other than AES, other cipher blocks, including DES, Camellia, CAST-128, SEED, and MISTY1, have been evaluated against the clock glitching in [58]. Five commercial and low-cost processors have been targeted by clock glitch injection in [52] to conduct a deep analysis of fault impacts.

## 2.2.3 CLOCK GLITCH GENERATOR CHARACTERISTICS

As discussed in previous sections, fault generators, in general, should have specific characteristics, namely accuracy, run-time configuration, reproducibility, and randomness. In this sub-section, the clock glitch generator characteristics are explained. Below is a list of the main features that are

identified, and then for each category, the related articles are compared.

- **Clock Glitch Accuracy:** This feature includes the parameters such as minimum glitch width, gliding shift steps, standard deviation, clock glitching placement, and clock glitch frequency control. These features depend on the characteristics of the clock generator and the method which is used to induce the glitches.

- Minimum glitch width: Most target systems contain protocols to protect their external clock input so that when an abnormal clock is observed and detected, it resets the system or produces an alert. Therefore, less glitch width results in a lower chance of detection. In addition, in many cases, a precise and short glitch is needed to target a specific instruction running on the processor or specific data being fetched. This makes it important to control the glitch width. The precision of the clock glitch width is on the time scale of picoseconds or a few nanoseconds. For example, in [58], a 2-channel pulse generator has been used to design an accurate 35ps glitch. [38,57] and [65] include glitches on the nanosecond scale.

- Gliding shift steps: this parameter refers to the minimum value by which a clock glitch generator adjusts the glitch width. These steps are on the nanosecond time scale. For example, in [52, 56], the gliding shift steps are reported as 1ns.

- **Standard deviation:** The standard deviation of the reported glitch width depends on the glitch generation algorithm and the limitations of the hardware used (e.g., FPGA).

- Clock glitching placement: It is important to induce a glitch into a specific position of the clock signal. For example, it is important to inject a glitch into a system at a certain round of encryption. [66] uses a counter to determine the location of the glitch injection.

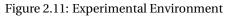

- Clock Glitch Run-Time Configuration: faulty clock parameters, such as phase delay and frequency, can be reconfigured at the run-time to help the attacker. For example, in [57], a digital clock manager (DCM) of an FPGA is used to configure the glitch. FPGA run-time adjustment can be used to change the phase-shifted values, but this method is limited to a certain range of values. [51] presents an approach for partial configuration using the FPGA configuration capabilities, including reconfiguring the DCM blocks at the run-time. The "bit-stream differential files" generated by FPGA tools are applied to substantiate the run-time configuration.

- Clock Glitch Reproducibility: this helps attackers to reproduce the faulty clock signal with the same characteristics as many times as they wish. It is important in some applications, which require the assessment of vulnerabilities and tracking of the clock glitch attack procedure. [58] includes a unique evaluation platform (SASEBO) for reproducible clock glitch generation.

• **Clock Glitch Randomness:** In most clock glitch generators, the glitch parameters such as frequency, width, precision, etc., are pre-determined, i.e., they are determined before run-time. This requires complete and adequate information about the target system, which would not be possible in all real-world attack scenarios. Furthermore, in order to have a highly efficient attack, one needs to cover a large number of possible combinations of the parameters mentioned, which would not be practical in a limited time. For this reason, in recent years, new techniques such as the fuzzy glitch generator [54] have been proposed for the generation of clock glitches. All of these techniques use ring oscillators instead of FPGA blocks and demonstrate the ability to achieve a highly successful attack rate. Details of the related works will be provided in the following section.

## 2.3 VOLTAGE-BASED FIAS

Voltage fault injection is another practical and low-cost attack that adversaries can use to conduct efficient attacks against targeted systems. They are used to attack embedded systems with one or multiple external power supply inputs. The fundamental concepts and related characteristics for this technique are provided in the following sub-sections.

## 2.3.1 CONCEPTS OF VOLTAGE FIAS

An important class of voltage glitch attack is manipulation of supply voltage [33, 56, 61, 62, 63, 67]. This is specifically applied in scenarios where the target system is fed from an external power supply [33]. Similar to clock fault attacks, a voltage fault attack is an approach that does not require extensive equipment or knowledge. Moreover, it can be used when access to the external clock input is not available on the target systems, i.e., those using their own internal clocks.

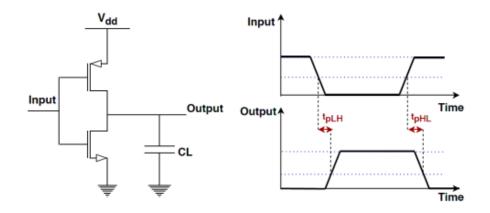

The non-equality in equation (2.1) points out the condition for correct circuit operation and correct value storage in memory. A standard approach to produce a timing constraint violation is to manipulate the clock period. The other approach is to increase the data propagation delay by tampering with the input voltage. In these approaches, equation (2.2) will not fulfill the timing condition for the correct circuit operation , which may result in erroneous data captured by memory cells and/or flip-flops. [68] discusses the relation between the input voltage and data propagation delay with a simple CMOS inverter as an example. Figure 2.6 shows that there are two propagation delays, named  $T_{pHL}$  and  $T_{pLH}$ , for the output variations from high to low and vice versa.

Equation 2.2 shows that these two delays depend on different factors, including the supply voltage. In this equation,  $V_{DD}$  is the power supply voltage,  $C_L$  is load capacitance,  $V_{th,p}$  is PMOS threshold voltage,  $u_p$  is holes mobility,  $C_{ox}$  is gate oxide capacitance, and  $(W_p/L_p)$  is the aspect ratio of the PMOS. By replacing the parameters related to the inverter's PMOS by NMOS parameters (e.g.  $u_n$ ,  $(W_n/L_n)$ ,  $V_{th,n}$ ),  $T_{pHL}$  can also be derived [68, 69]. Equation 2.2 demonstrates that  $T_{pHL}$

Figure 2.6: Inverter Circuit and T<sub>PHL</sub>, T<sub>PLH</sub> Parameters in Response Waveforms

and  $T_{pLH}$  have a direct relation with  $v_{DD}$ . In particular, reducing the power supply will increase  $T_{phl}$  and  $T_{plh}$  of the inverter. Therefore, manipulating the supply voltage (in long or short intervals) can be an efficient approach to inject a fault in order to violate the timing constraints [33,70].

$$T_{pHL} = \frac{C_L([\frac{2V_{thp}}{V_{DD} - |V_{thp}|}] + ln(3 - 4\frac{|V_{thp}|}{V_{DD}})}{u_P C_{ox} \frac{W_P}{L_x} (V_{DD} - |V_{thp}|)}$$

(2.2)

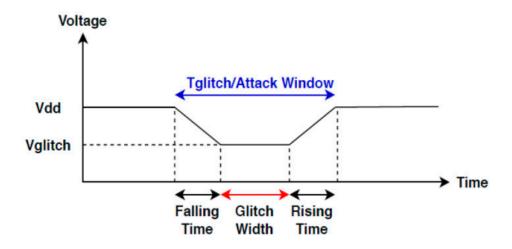

There are two main types of voltage attacks: 1) Underpowering and 2) Voltage glitching [70]. Underpowering is a type of voltage manipulation in which the target's supply voltage is applied permanently (or for a relatively long period) to a voltage source out of its nominal range (the standard voltages defined by the manufacturer). Voltage glitching is a sudden and momentary change in the supply voltage. It has been shown that under-powering is not sufficient to achieve a high success rate because it impacts multiple instructions that are executed [36].