# Modélisation et exploration d'architectures neuromorphiques pour les systèmes embarqués haute-performance

Edgar Lemaire

#### ▶ To cite this version:

Edgar Lemaire. Modélisation et exploration d'architectures neuromorphiques pour les systèmes embarqués haute-performance. Réseau de neurones [cs.NE]. Université Côte d'Azur, 2022. Français. NNT : 2022COAZ4009. tel-03665844v1

# HAL Id: tel-03665844 https://theses.hal.science/tel-03665844v1

Submitted on 12 May 2022 (v1), last revised 24 Apr 2023 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ÉCOLE DOCTORALE

SCIENCES ET

TECHNOLOGIES DE

L'INFORMATION ET DE

LA COMMUNICATION

THALES

# Modélisation et Conception d'Architectures Neuromorphiques pour les Systèmes Embarqués Haute-Performance

# **Edgar LEMAIRE**

Laboratoire d'Antennes, Électronique et Télécommunications (LEAT) & Thales Research & Technology (TRT-Fr)

Présentée en vue de l'obtention du grade de docteur en Electronique d'Université Côte d'Azur

**Dirigée par** : Benoît Miramond, LEAT **Co-Dirigée par** : Sébastien Bilavarn, LEAT **Co-Encadrée par** : Hadi Saoud, Thales

Soutenue le: 08 Mars 2022

#### Devant le jury, composé de :

Simon Thorpe, Dir. de Recherche, CerCO Gilles Sassatelli, Dir. de Recherche, LIRMM Olivier Bichler, Ingé. Chercheur, CEA-LIST Jean Martinet, Professeur, I3S Philippe Millet, Resp. pôle Innovation, Nexter Hadi Saoud, Ingé. Chercheur, Thales Benoît Miramond, Professeur, LEAT Sébastien Bilavarn, Maitre de Conf., LEAT

# Modélisation et Conception d'Architectures Neuromorphiques pour les Systèmes Embarqués Haute-Performance

Jury:

#### Rapporteurs

Simon Thorpe, Directeur de Recherche, Centre de Recherche Cerveau et Cognition (CerCO) - CNRS/Université Toulouse 3 Paul Sabatier

Gilles Sassatelli, Directeur de Recherche, Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier (LIRMM) – CNRS/Université Montpellier 2

#### **Examinateurs**

Jean Martinet, Professeur des Universités, Laboratoire d'Informatique, Signaux et Systèmes de Sophia antipolis (I3S) – CNRS/Université Côte d'Azur

Olivier Bichler, Ingénieur Chercheur, Laboratoire d'Intégration des Systèmes et Technologies (LIST) – CEA Tech

Philippe Millet, Directeur de l'Innovation, Nexter

Hadi Saoud, Ingénieur Chercheur, Thales Research & Technology (TRT), Thales

Benoît Miramond, Professeur des Universités, Laboratoire d'Eléctronique, Antenne et Télécommunications (LEAT) – CNRS/Université Côte d'Azur

Sébastien Bilavarn, Maître de Conférences, Laboratoire d'Eléctronique, Antenne et Télécommunications (LEAT) – CNRS/Université Côte d'Azur

# Résumé en Français

Les réseaux de neurones profonds ont permis des progrès sans précédent dans le domaine de l'apprentissage automatique. En imitant le calcul parallèle et distribué du cerveau, de tels algorithmes permettant en effet d'émuler n'importe quelle fonction, jusqu'aux plus complexes. Leurs applications vont de la vision par ordinateur (classification, segmentation, détection...), au traitement du language naturel en passant par la prédiction de séries temporelles. Dans tous ces domaines, les réseaux de neurones profonds n'ont cessé de repousser les limites de l'intelligence artificielle. D'autre part, nous assistons par ailleurs à l'émergence progressive de l'internet des objets (Internet of Things, IoT). Ces systèmes embarqués connectés ont un besoin grandissant en capacité de traitement, et les réseaux de neurones profonds semblent alors tout indiqués pour accomplir cette tâche. Qu'il s'agisse de navigation autonome dans des drones ou dans des voitures sans pilote, de reconnaissance faciale dans les téléphones portables ou plus généralement de traitement périphérique (Edge Computing) dans les réseaux de capteurs, les applications embarquées de l'apprentissage profond sont déjà nombreuses. Cependant, les algorithmes neuronaux sont complexes et particulièrement gourmands en ressources de calcul. En matière de consommation énergétique, ces derniers semblent en effet incompatibles avec la nature contrainte des systèmes d'IoT. Dans cette optique, l'approche de l'Electronique Neuromorphique consiste à s'inspirer du cerveau biologique pour en mimer l'efficacité énergétique. En effet, il s'agit du modèle de processeur neuronal le plus abouti à notre connaissance, affichant une consommation d'à peine 20 watts. À travers l'utilisation de modèles de neurones bio-inspirés proposés par les neurosciences computationnelles, l'approche Neuromorphique a pour objectif de réduire la consommation énergétique de l'intelligence artificielle embarquée. Cette approche repose sur des arguments prometteurs: la simplicité du calcul impulsionnel, l'aspect binaire des synapses et l'encodage "épars" (sparse). Cependant, la littérature scientifique spécialisée semble manquer de comparaison étendue de l'impact du domaine de codage sur l'efficacité énergétique des accélérateurs neuronaux. De ce fait, la contribution principale de cette thèse est une comparaison détaillée des domaines de codage impulsionnels et formels sur FPGA. Cette étude implique plusieurs cas d'usage et différents niveaux de parallèlisme. Ce volet de la thèse a été mené a bien au moyen du développement d'un estimateur de ressources et d'énergie pour les architectures neuronales sur FPGA. Cet outil permet d'accélérer l'exploration de l'espace des applications. D'autre part, nous proposons de quantifier les gains potentiels au moyen d'une métrique et d'un modèle de haut niveau: le ratio d'activité synaptique. Cette métrique permet d'évaluer rapidement les gains potentiels d'énergies offerts par le domaine impulsionnel pour une application donnée. Nous l'utilisons notamment pour trouver de nouvelles familles de réseaux impulsionnels prometteuses en termes énergétiques. Enfin, nous mettons à profit les enseignements de cette étude pour proposer l'accélération neuronale hybride, une architecture mélant les deux domaines d'encodage (impulsionnel et formel). L'architecture a été embarquée à bord du satellite OPS-SAT (lancé en Décembre 2019) et testée en vol. Ce faisant, il s'agit de la toute première architecture neuromorphique fonctionnelle dans l'éspace.

Mots Clefs - Réseaux de Neurones Artificiels, Réseaux de Neurones Impulsionnels, Eléctronique Numérique, Architecture Matérielle, Modélisation, Consommation énergétique, Systèmes Embarqués, Informatique en Périphérie, Eléctronique Neuromorphique, FPGA

# Abstract

Deep Neural Networks have recently pushed unprecedented progress in the field of Machine Learning. Those algorithms mimic the parallel and distributed computation paradigm of the biological brain to fit any desired functions, including the most complex ones. The range of applications for Deep Learning is very wide: from computer vision (classification, segmentation, detection...) to natural language processing and time-series prediction. Those domains were all greatly impacted by Deep Neural Networks, since they are continuously pushing back the limits of Artificial Intelligence. On the other hand, the emergence of the Internet of Things in recent years have opened a brand new range of applications for Deep Learning. Indeed, the processing abilities of those algorithms is particularly appealing for such autonomous systems like IoT. From navigation and obstacle detection in drones and self-driving cars, to face recognition in smartphones, or more generally for Edge Computing in networks of sensors, Deep Learning seems all indicated for the task. However, Deep Learning models are very complex and energy-intensive. In terms of energy consumption, they appear not to comply with the highly-constrained nature of embedded systems. To cope with this issue, the Neuromorphic Computing approach consists in taking inspiration from the biological brain. Our brain is indeed the most efficient neural processor anyone has ever heard of, with only 20W of average power consumption. By using bio-inspired models from Computational Neurosciences, the Neuromorphic approach thus aims in reproducing the energy efficiency of the brain. This choice is backed by several objective assessments, like the hardware-friendliness of the spiking synaptic operation, the sparse computation or the lightweight communication between neurons. However, the literature seems to lack broad and fair comparisons of the impact on neural coding on the energy consumption of hardware neural networks. Therefore, the first contribution of this work is a fair and extensive comparison between spiking and formal coding domains on FPGA. The study also takes low-level implementation into account, like parallelism. It was made possible by the development of an hardware-footprint estimator for hardware neural networks on FPGA, which drastically facilitates and accelerates the design and applications space exploration. Moreover, we propose an high-level metric and energy model to evaluate the energy consumption of neuromorphic accelerators. This model named Synaptic Activity Ratio (SAR) is based on the number of spikes per synapse and the ratio of energy consumption between spiking and formal synaptic operations. The model is indeed able to determine whether a given CNN model (tested on a given dataset) could bring energy savings on FPGA. This contribution also facilitates the exploration of applications relatively to neural coding domains. For instance, we also use this technique to find novel SNN representations which seem better adapted to hardware acceleration than the basic rate-coded conversion approach. Finally, we use the knowledge acquired from this study to introduce the novel concept of neural coding hybridization. We propose an hardware architecture which uses both formal domain for feature-extraction and spiking domain for classification. The architecture was embedded on-board OPS-SAT satellite (launched Dec. 2019) for in-flight test, being the world first neuromorphic architecture in space.

Keywords - Artificial Neural Networks, Spiking Neural Networks, Digital Electronics, Hardware Architecture, Modeling, Energy Consumption, Embedded Systems, Edge Computing, Neuromorphic Electronics, FPGA

# Acknowledgements

I would like to express my deepest gratitude to my supervisors: Benoît Miramond, Sébastien Bilavarn, Hadi Saoud and Philippe Millet for their unwavering help and support during the three years of my thesis. I would like to thank them for believing in me with this project although I had very little experience and knowledge on digital electronics; for teaching me so much professionally, technically and humanely; and for the support they brought me all along those three years.

I would also like to express my gratitude to Simon Thorpe, Gilles Sassatelli, Olivier Bichler and Jean Martinet for accepting to be part of my thesis jury. It is a great honor for me to defend my work in front of such prominent researchers.

I would also like to thank my colleagues of both LEAT and Thales RT for their support and the many friendship we built. In particular, I would like to sincerely thank Nassim Abderrahmane for all the work we have accomplished together, and all the help he offered me in the early stages of my thesis.

In addition, I would like to thank my parents Frédérique and Bruno Lemaire, my sister Félicie Lemaire, my grand-parents, uncles, aunts, cousins and friends for their support, encouragement and prodding. Each one of them had a role to play in the achievement of this work. I would also like to thank Manon Philip for her unwavering support and love, which helped me going forward during hard times.

This work was funded by Thales and ANRT (Agence Nationale de la Recherche Technologique), and hosted at both Thales Research Technology's LCHP (High Performance Computing Laboratory) and CNRS & Université Côte d'Azur LEAT (Electronics, Antennas and Telecommunication Laboratory).

# List of Publications

# Journal Papers

Abderrahmane, N., Lemaire, E., & Miramond, B. (2020). Design space exploration of hardware spiking neurons for embedded artificial intelligence. Neural Networks, 121, 366-386.

Lemaire, E., Miramond, B., Bilavarn, S., Saoud, H. & Abderrahmane, N., (2022). Synaptic Activity and Hardware Footprint of Spiking Neural Networks in Digital Neuromorphic Systems. ACM Transactions on Embedded Computing Systems (Accepted for publication)

## Conference Papers

Lemaire, E., Moretti, M., Daniel, L., Miramond, B., Millet, P., Feresin, F., & Bilavarn, S. (2020, October). An FPGA-based Hybrid Neural Network accelerator for embedded satellite image classification. In 2020 IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 1-5). IEEE.

## **Book Chapters**

Chapter 12: Space Use-Case, in the book:

Jahre, M., Göhringer, D., & Millet, P. (Eds.). (2021). Towards Ubiquitous Low-power Image Processing Platforms. Springer International Publishing.

### Workshop Papers

Férésin, F., Kervennic, E., Bobichon, Y., Lemaire, E., Abderrahmane, N., Bahl, G., ... & Benguigui, M. (2021). In space image processing using AI embedded on system on module: example of OPS-SAT cloud segmentation. In 2nd European Workshop on On-Board Data Processing.

#### **Patents**

FISO neuron model, submitted in September 2019, in proceeding.

# List of Figures

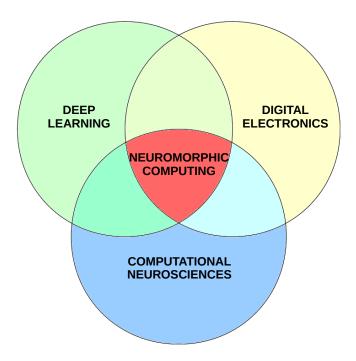

| 1.1  | Neuromorphic Computing is a trans-disciplinary approach between Deep Learning, Digital Electronics and Computational Neurosciences                                                                                                                       | ۷          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

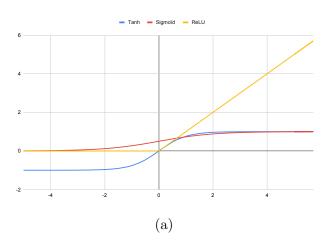

| 2.1  | Left: commonly used activation functions in formal neurons: hyperbolic tangeant (Tanh), sigmoïd and Rectified Linear Unit (ReLU). Right: Schema of FC layer, with 5 input and 2 output neurons                                                           | (          |

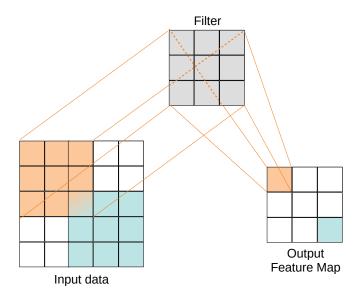

| 2.2  | Schema of a Convolutional layer, with a 5x5x1 input data, a single 3x3 filter and a stride of 1                                                                                                                                                          | 8          |

| 2.3  | Summary of LeNet-5 CNN. Conv is for Convolutional Layer, Pool is for Pooling layers and D is for FC layers. The visuals are obtained using N2D2 sotfware [1]                                                                                             | 8          |

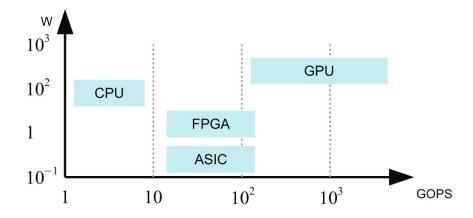

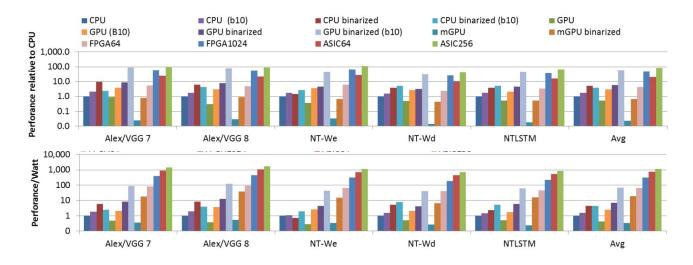

| 2.4  | Summary of comparisons between CPU, GPU, ASIC and FPGA for neural network acceleration in terms of power consumption and computing power [2]                                                                                                             | 1          |

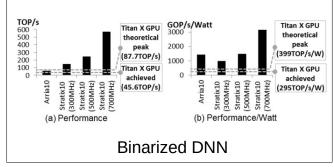

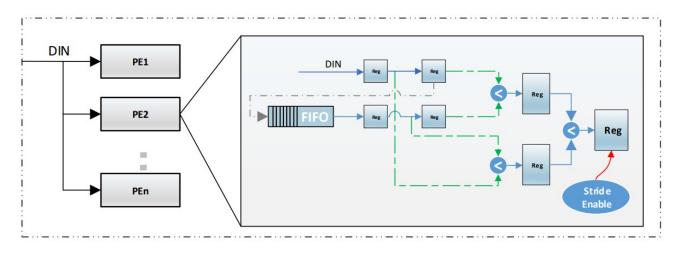

| 2.5  | Comparison of CPU, GPU, ASIC and FPGA for binary neural network acceleration in terms of speed and performance per Watt, on various neural network topologies [3].                                                                                       | 12         |

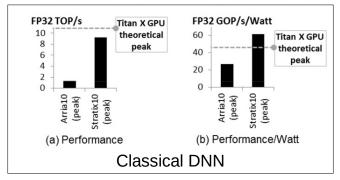

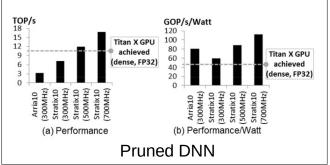

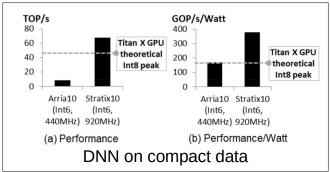

| 2.6  | Comparison of FPGA (Stratix 10) and GPU (Titan X) for Deep Neural Networks in terms of performance and performance per Watt, for various optimizations: prun-                                                                                            |            |

|      | ing, compact data and binarization. [4]                                                                                                                                                                                                                  | 13         |

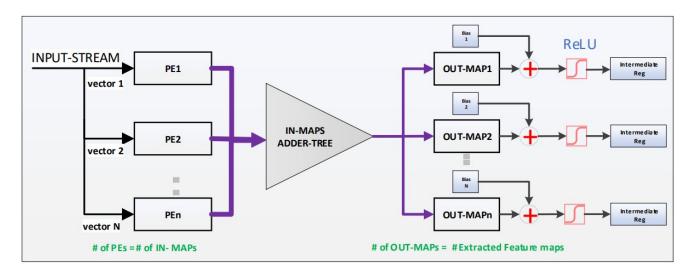

| 2.7  | Illustration of a VGT-generated convolution layer architecture [5]                                                                                                                                                                                       | 14         |

| 2.8  | Illustration of a Processing Element in VGT convolution layers [5]                                                                                                                                                                                       | 15         |

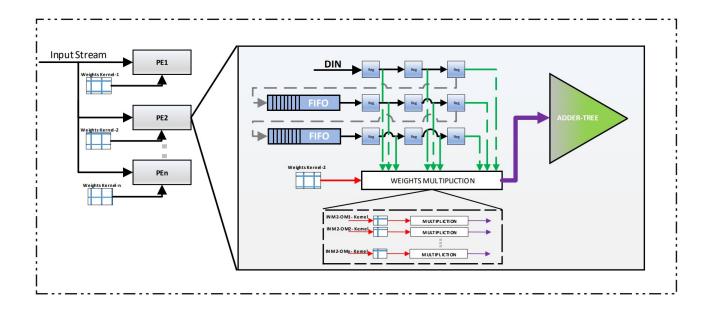

| 2.9  | Illustration of a VGT-generated max-pooling layer architecture [5]                                                                                                                                                                                       | 16         |

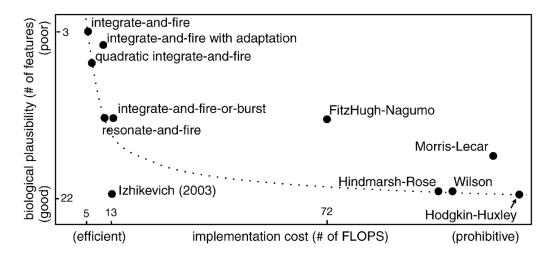

| 2.10 | Biological plausibility of Spiking Neuron models against implementation as stated in [6]                                                                                                                                                                 | 16         |

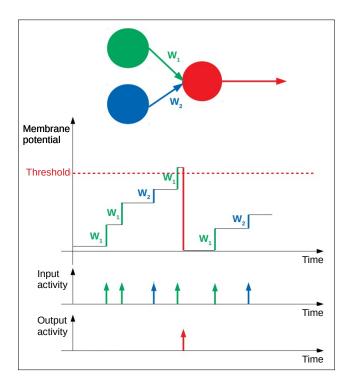

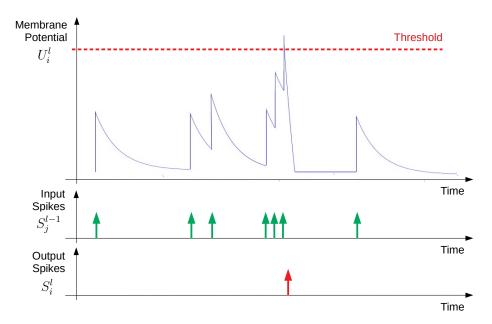

| 2.11 | Illustration of the Integrate & Fire neuron model. Top: network setup, bottom: membrane potential, input and output activity                                                                                                                             | 17         |

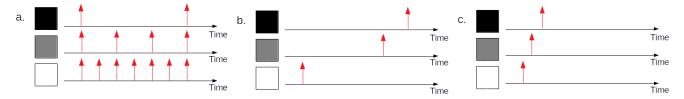

| 2.12 | Different spike coding methods: a. is rate coding, b. is latency coding, c. is order coding                                                                                                                                                              | 19         |

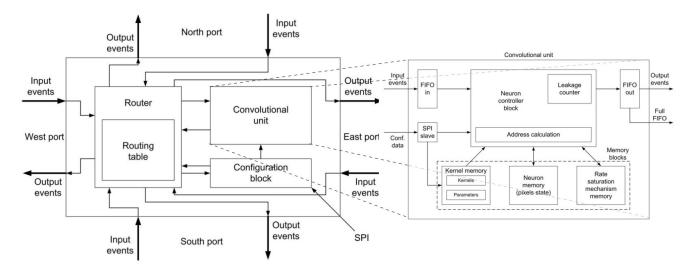

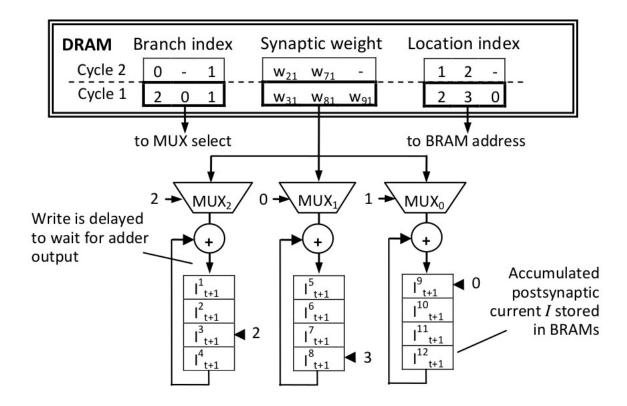

| 9 13 | Illustration of the Convolutional Processing Element found in [7].                                                                                                                                                                                       | 23         |

|      | Illustration of the weight distribution technique used in [7] to limit the memory access rate. module has 3 input synapse data per cycle. The neuron 1 connects to neurons 2, 3, 7, 8 and 9 in the network, and neuron 1 is fired in the last time step. | 20         |

|      | The figure shows the accumulation of three synaptic weights $(w_{3,1}, w_{8,1})$ and $w_{9,1}$ .                                                                                                                                                         | $2^{2}$    |

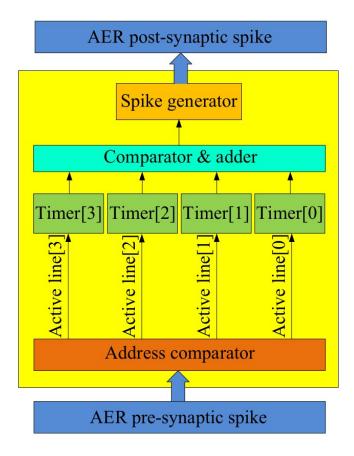

| 2 15 | Polychronous neuron circuit overview found in [8]                                                                                                                                                                                                        | 2!         |

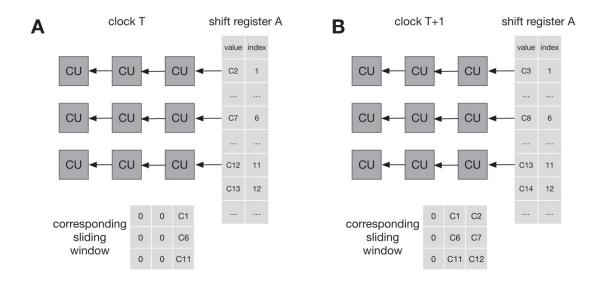

|      | Illustration of the pipelined parallel convolution implementation found in [9]. The                                                                                                                                                                      | <b>∠</b> ( |

|      | input data is first flattened in rows, and fed in a shift register. A systolic array of Convolution Units [10] then performs the operation in a pipelined fashion. A:                                                                                    |            |

|      | Situation at clock T, B: situation at clock T+1                                                                                                                                                                                                          | 26         |

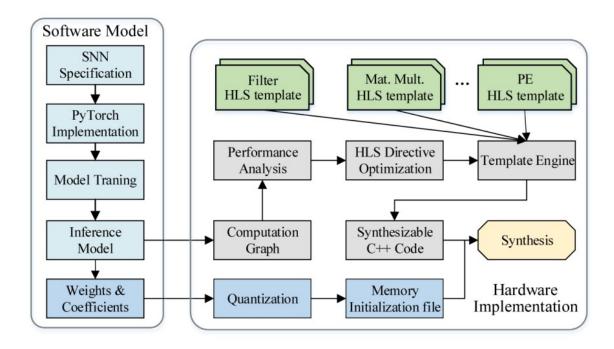

| 2.17 | Illustration of the training, compression, conversion and hardware deployment frame-                                                                                                                                                                     | ٠.         |

|      | work proposed in [11]                                                                                                                                                                                                                                    | 2          |

| 2.18 | Illustration of stabilized DVS data used for training and testing in [12]                                                                                                                                                                                | 28         |

LIST OF FIGURES vi

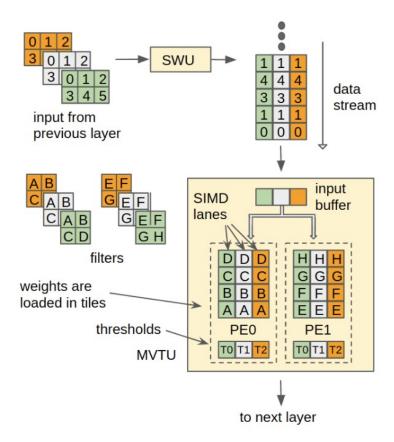

| 2.19       | Window Unit) flattens the input data and forwards it to the MVTU (Matrix Vector Threshold Unit). Each Processing Element (PE) inside the MVTU processes one output channel and has a number of SIMD (Single Instruction on Multiple Data) lanes that read from input channels and multiply the input by kernel weights in | 0.0      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.20       | parallel                                                                                                                                                                                                                                                                                                                  | 30       |

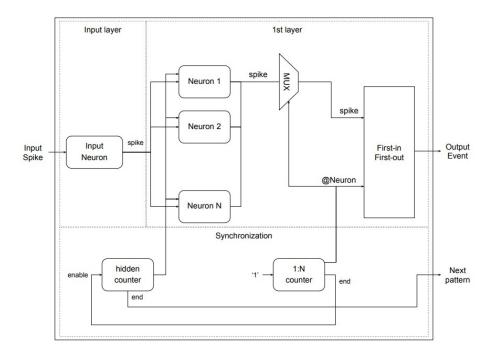

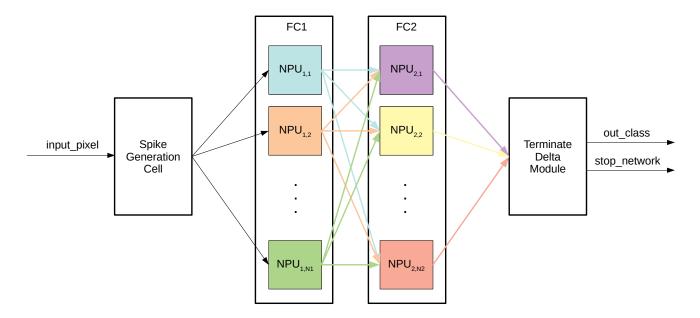

| 3.1        | High level representation of PADS architecture, for a 2-layers spiking MLP. FCi stands for the $i^{th}$ fully-connected layer with Ni neurons                                                                                                                                                                             | 36       |

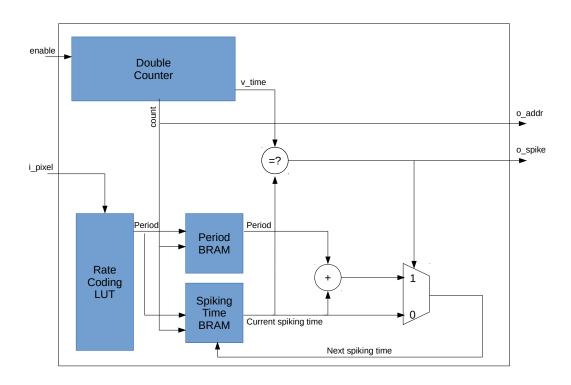

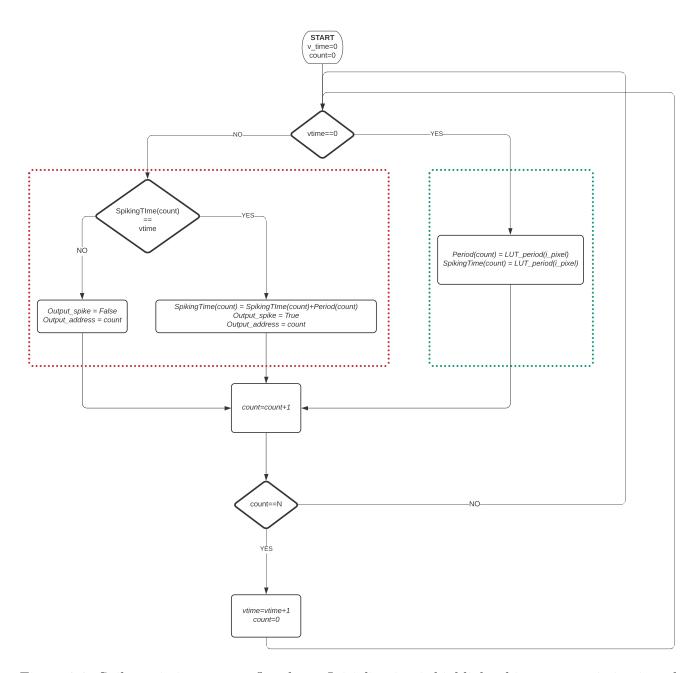

| 3.2<br>3.3 | Block Diagram of the Spike Generation Cell                                                                                                                                                                                                                                                                                | 37       |

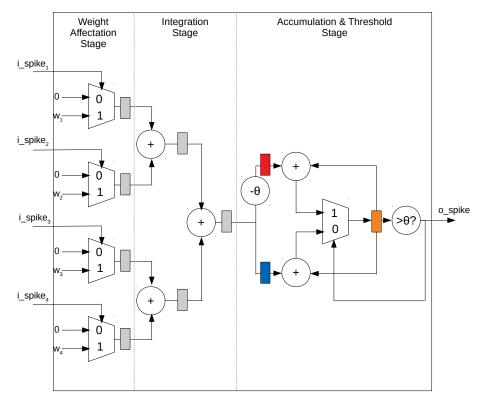

| 3.4        | Architecture of a generic NPU in PADS, represented with 4 input synapses. Register barriers are represented as rectangles                                                                                                                                                                                                 | 38<br>41 |

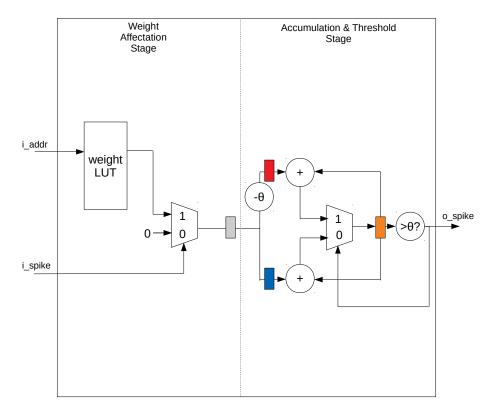

| 3.5        | Architecture of a PADS Input-NPU, optimized for the input FC layer                                                                                                                                                                                                                                                        | 42       |

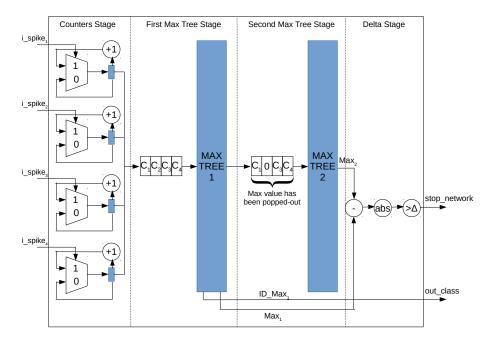

| 3.6        | Architecture of the PADS' Terminate Delta Module with 4 output neurons                                                                                                                                                                                                                                                    | 43       |

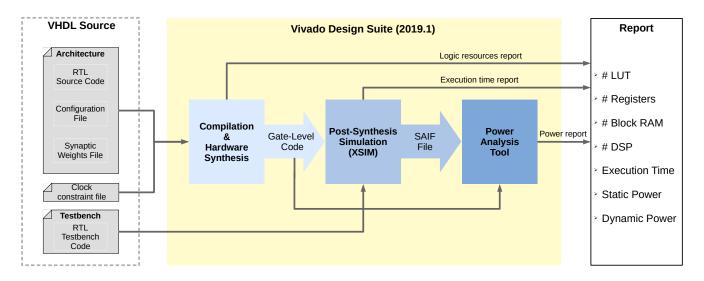

| 3.7        | Workflow for synthesis, simulation and reporting using Vivado Design Suite (2019.1). The source code (VHDL) is depicted on the left, and the resulting report on the                                                                                                                                                      |          |

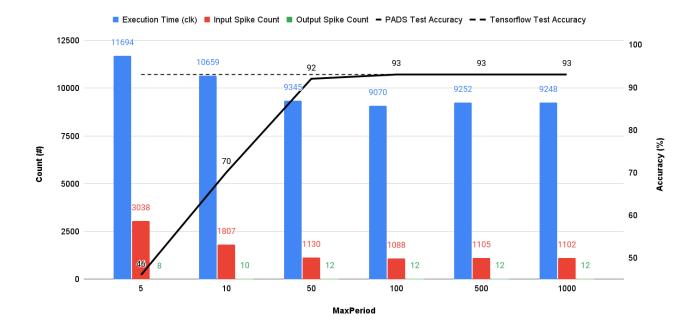

| 3.8        | right                                                                                                                                                                                                                                                                                                                     | 48       |

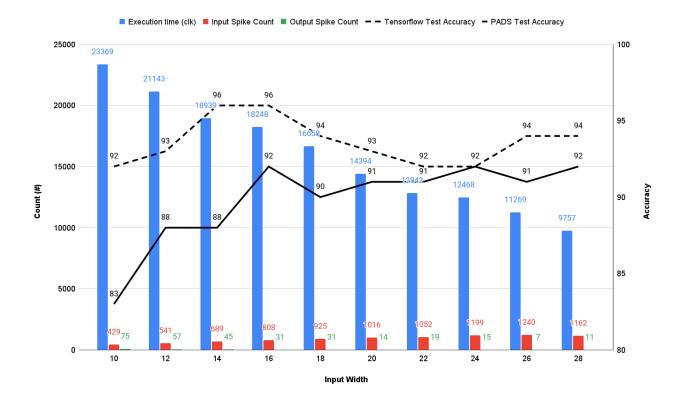

| 3.9        | Evolution of test accuracy, number of input & output spikes and execution time (in clock cycles) with respect to input size. All measurements are averaged on 100 samples. Single FC layer SNN on MNIST dataset with various input sizes                                                                                  | 49       |

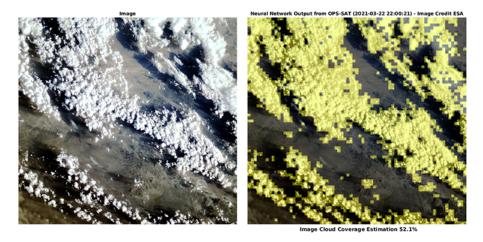

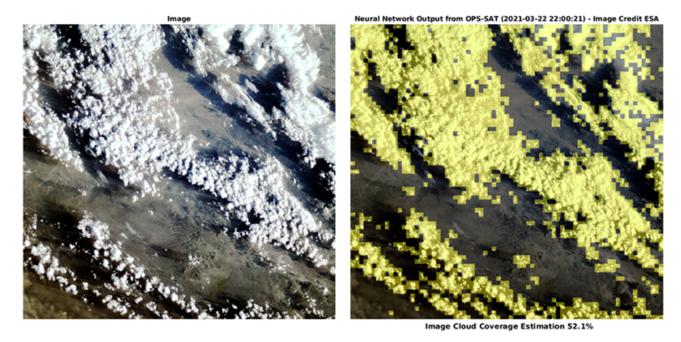

| 4.1        | Illustration of the CIAR cloud segmentation task. On the left, the original image taken by OPS-SAT. On the right, the resulting segmentation map, with cloudy patches in yellow. Source: [15]                                                                                                                             | 54       |

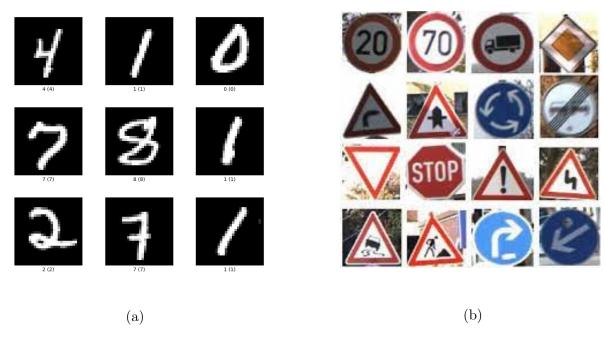

| 4.2        | a) Sample of MNIST dataset, b) Sample of GTSRB dataset                                                                                                                                                                                                                                                                    | 55       |

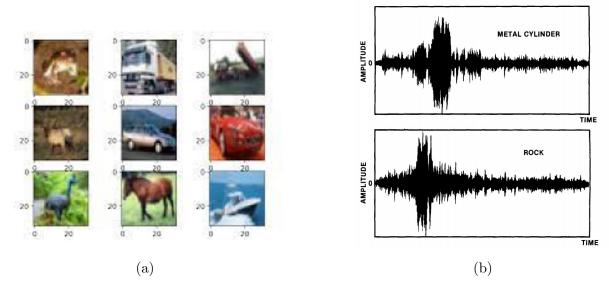

| 4.3        | a) Sample of CIFAR 10 dataset, b) Sonar echoes from Mines VS Rocks dataset [16]                                                                                                                                                                                                                                           | 56       |

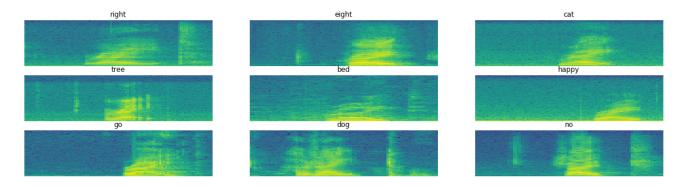

| 4.4        | Examples of spectrograms from Google Speech Commands dataset [17]. Spoken                                                                                                                                                                                                                                                 |          |

|            | Digits dataset use in this work is a subset of Google Speech Commands                                                                                                                                                                                                                                                     | 56       |

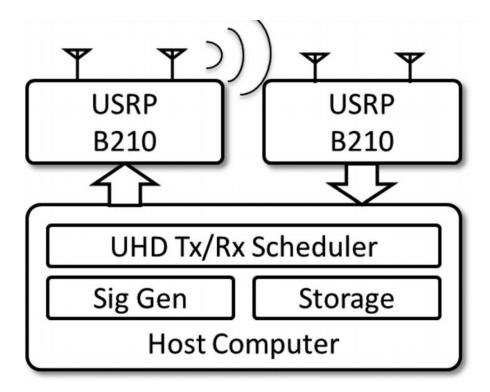

| 4.5        | Illustration of the over-the-air RadioML 2018 recording setup, found in [18]. A host computer generates the desired RF signal, which is emitted and received via two universal software radio peripherals (USPR)                                                                                                          | 57       |

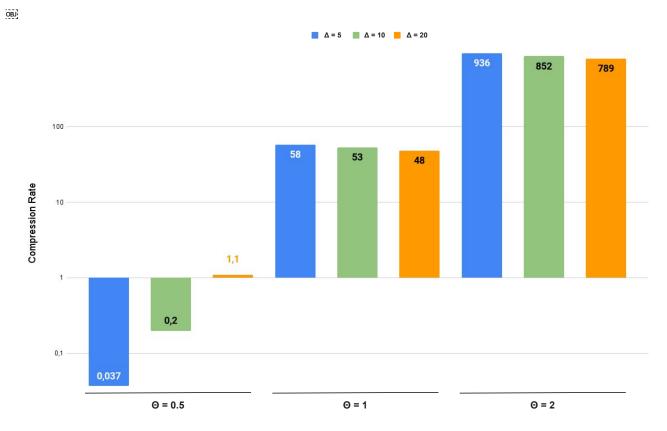

| 4.6        | universal software radio peripherals (USRP)                                                                                                                                                                                                                                                                               | 61       |

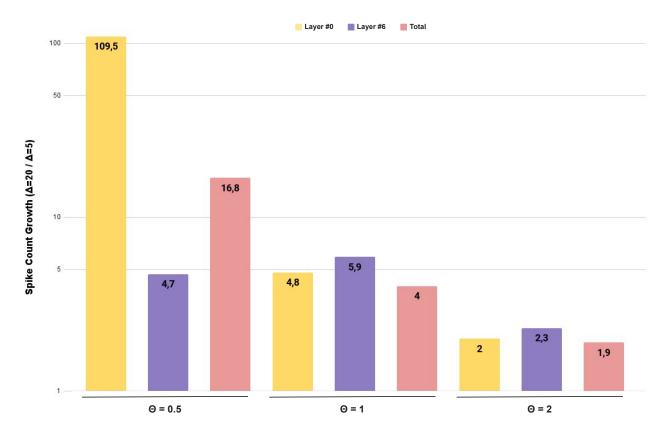

| 4.7        | Spike Count Evolution $\Delta = 5$ and $\Delta = 20$ in Layer #0, Layer #6 and in total, for                                                                                                                                                                                                                              | ΟI       |

| -          | various $\Theta_{\rm IF}$ on CIFAR-10 task. The vertical axis is logarithmic                                                                                                                                                                                                                                              | 62       |

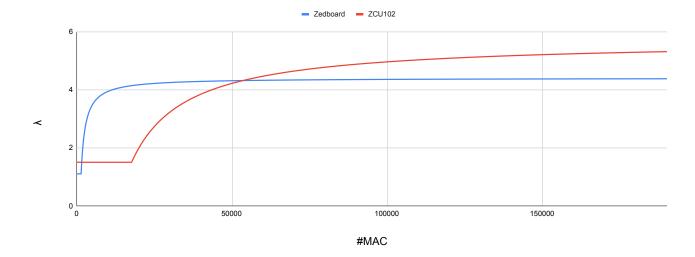

| 4.8        | Evolution of $\lambda$ against number of parallel MACs, for Xilinx Zedboard and ZCU102                                                                                                                                                                                                                                    |          |

|            | targets                                                                                                                                                                                                                                                                                                                   | 67       |

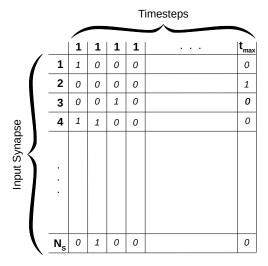

| 4.9        | Unified synaptic trace format                                                                                                                                                                                                                                                                                             | 68       |

LIST OF FIGURES vii

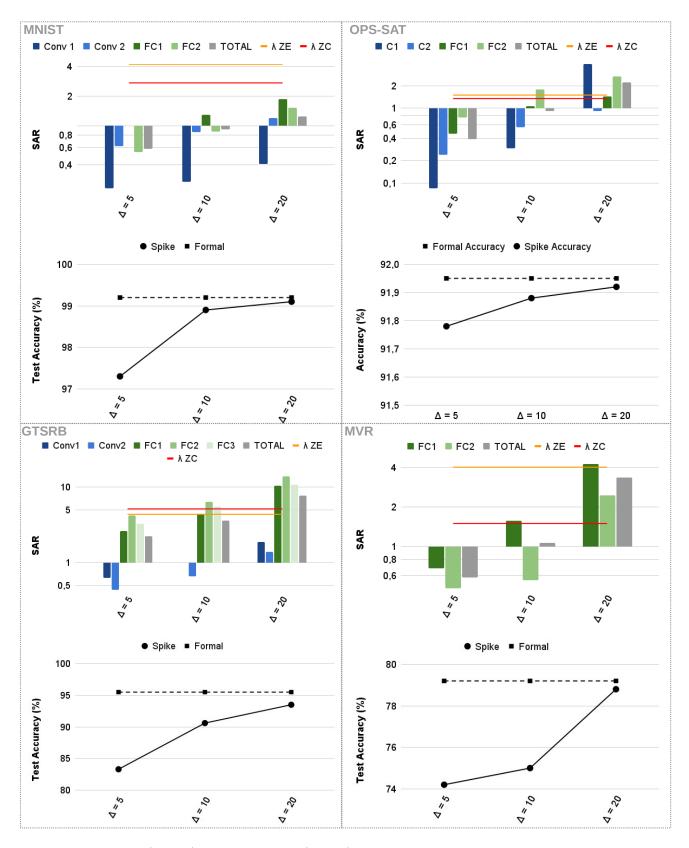

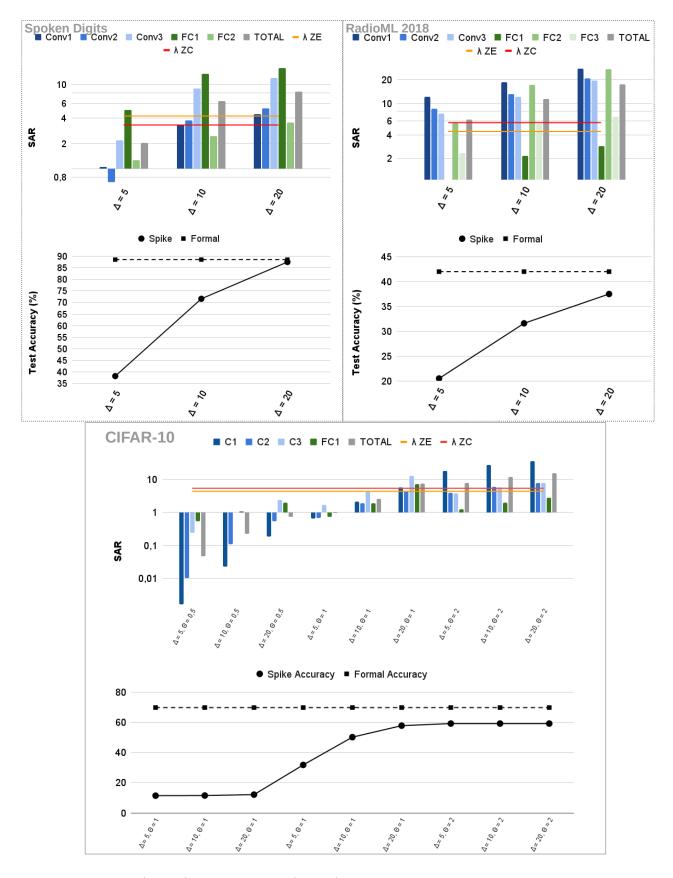

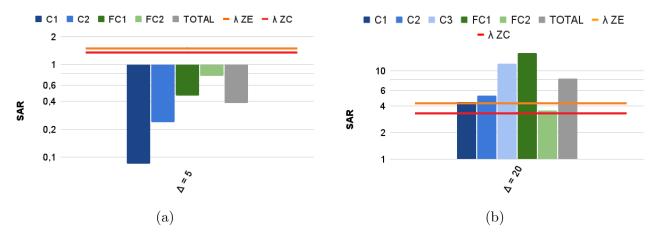

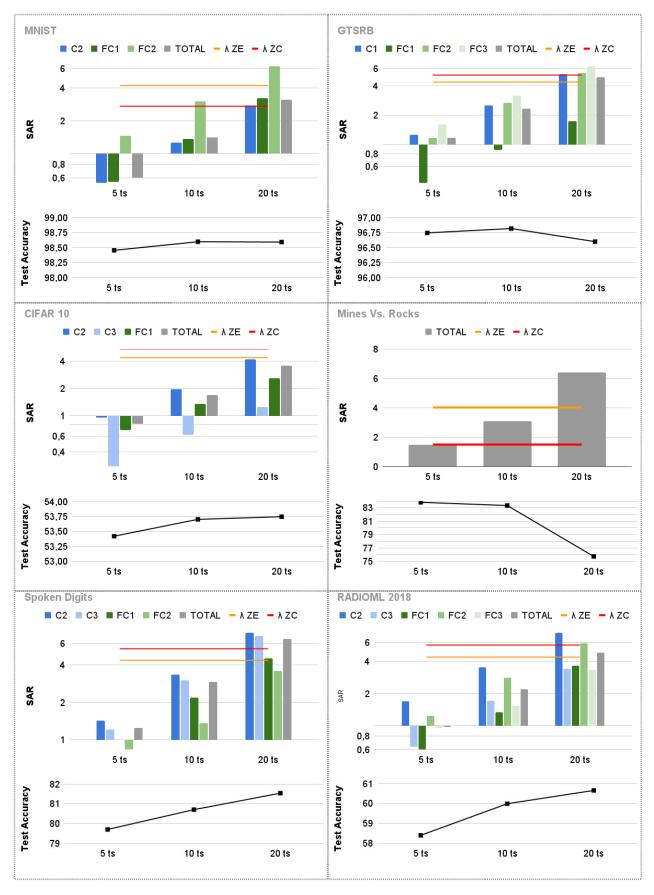

| 4.10 | Rocks datasets classification, for $\Delta = 5,10$ and 20. $\lambda_{\rm ZE}$ and $\lambda_{\rm ZC}$ are also represented. Spiking inference with N2D2                                                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.11 | SAR (above) and accuracy (below) on Spoken Digits, RadioML 2018 and CIFAR-10 datasets classification, for $\Delta = 5, 10$ and 20. $\lambda_{\rm ZE}$ and $\lambda_{\rm ZC}$ are also represented. Spiking inference with N2D2. Additionally, for CIFAR-10 $\theta_{\rm IF}$ varies between 0.5, 1 and 2 |

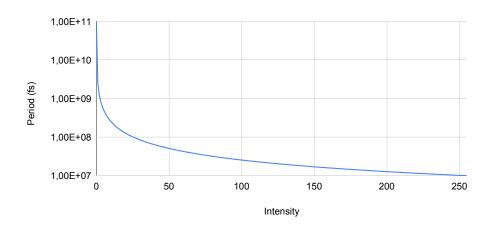

| 4.12 | Activity ratio on MNIST using a larger topology, obtained using N2D2. Spiking Accuracy = 98,73%; Formal Accuracy = 99,19%                                                                                                                                                                                |

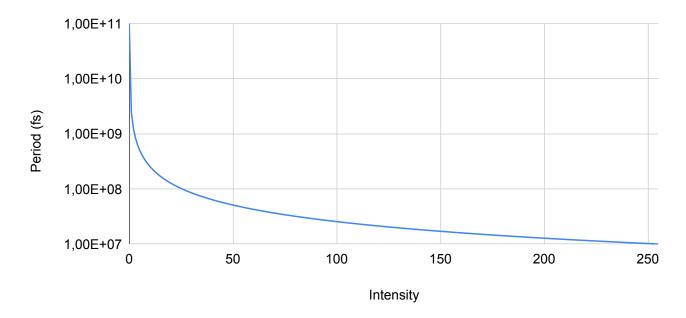

| 4.13 | Spike train period with respect to element intensity according to the rate-coding policy, with $PeriodMax = 1 \times 10^{11} fs$ and $PeriodMax = 1 \times 10^{7} fs$ (default N2D2 parameters used in our experiments)                                                                                  |

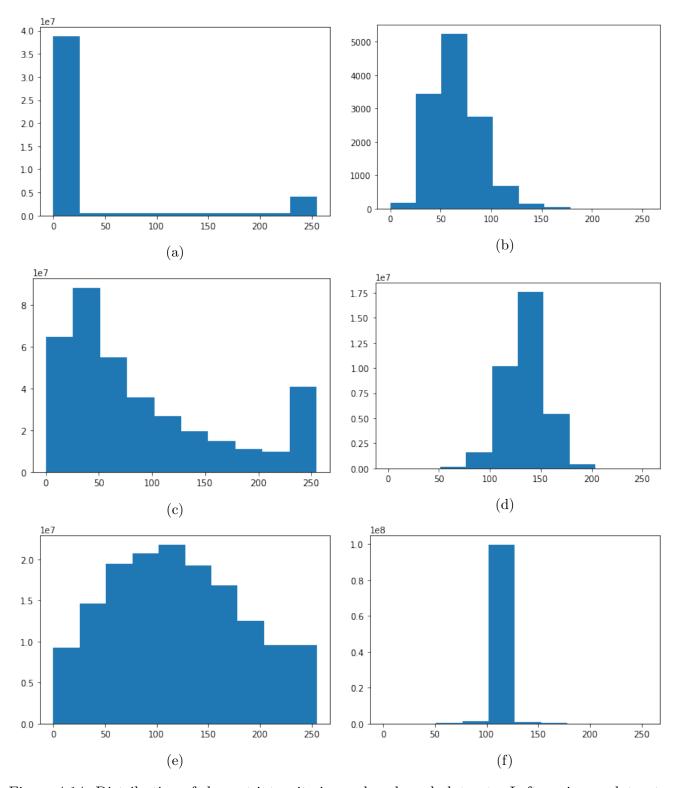

| 4.14 | Distribution of element intensity in our benchmark datasets. Left are image datasets, right are 1D datasets. a) MNIST, b) Mines VS Rocks, c) GTSRB, d) Spoken Digits, e) CIFAR-10, f) RadioML2018                                                                                                        |

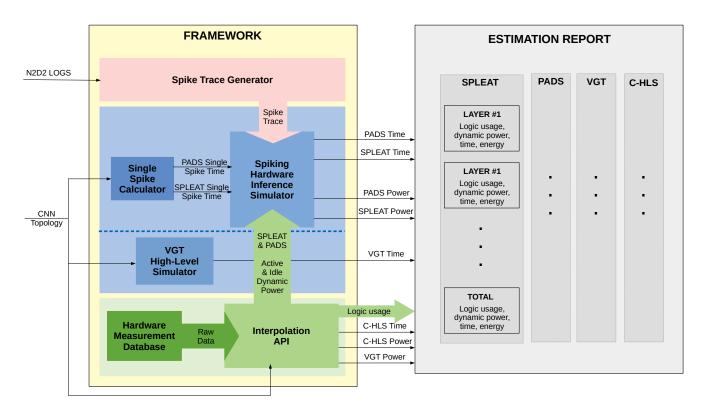

| 5.1  | Overview of the high-level estimation framework                                                                                                                                                                                                                                                          |

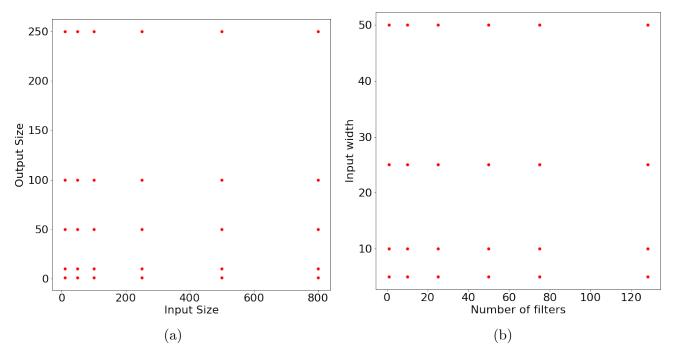

| 5.2  | Design space for a) FC layers (30 points), b) Conv & Pool layers (24 points each)                                                                                                                                                                                                                        |

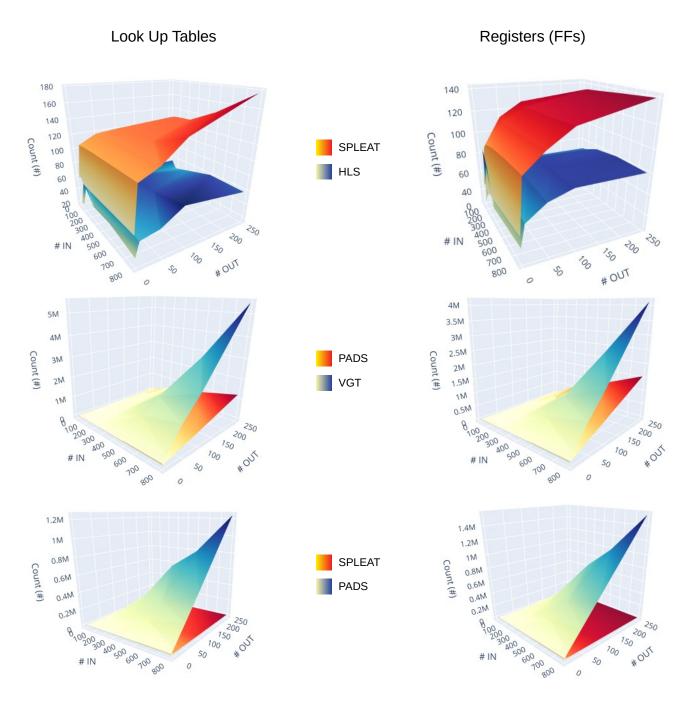

| 5.3  | 3D interpolations of LUTs (left) and FFs (right) for Fully-Connected layers. First row: SPLEAT (red) vs HLS (blue), second row: PADS (red) vs VGT (blue). Third                                                                                                                                          |

|      | row: SPLEAT (red) vs PADS (blue)                                                                                                                                                                                                                                                                         |

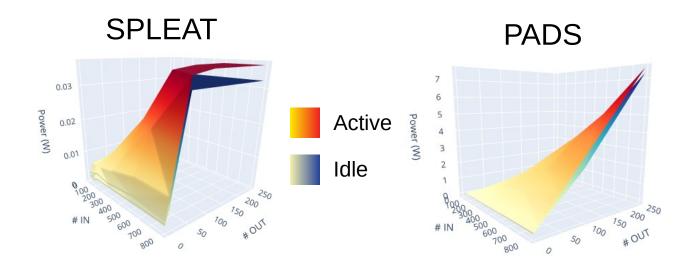

| 5.4  | 3D interpolations of active and idle power for Fully-Connected layers. Left: SPLEAT, right: PADS                                                                                                                                                                                                         |

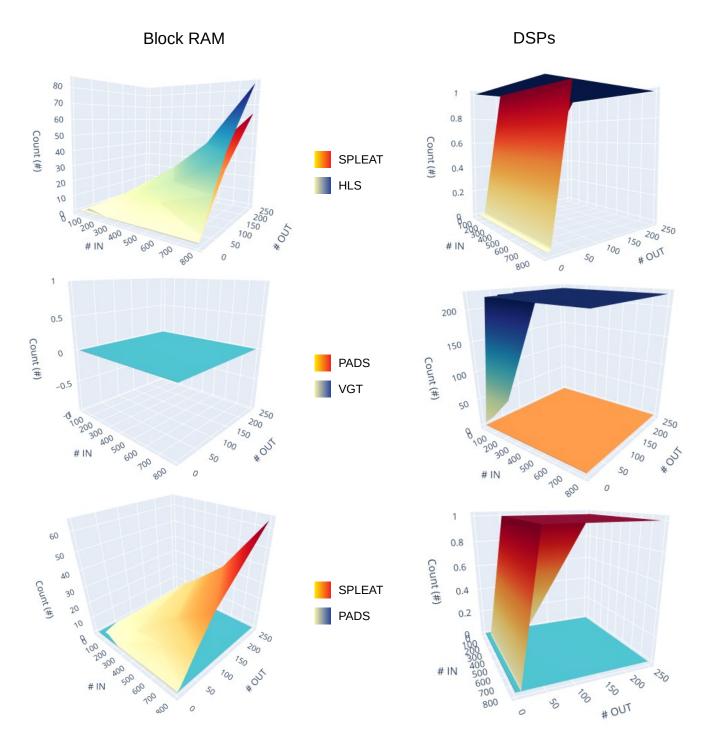

| 5.5  | 3D interpolations of Block RAM (left) and DSPs (right) for Fully-Connected layers. First row: SPLEAT (red) vs HLS (blue), second row: PADS (red) vs VGT (blue). Third row: SPLEAT (red) vs PADS (blue)                                                                                                   |

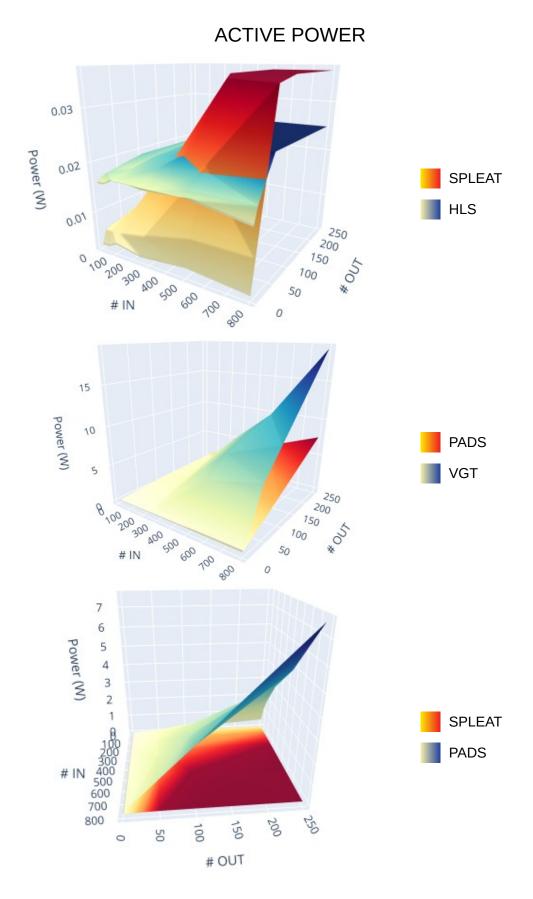

| 5.6  | 3D interpolations of Active Power for Fully-Connected layers. First row: SPLEAT (red) vs HLS (blue), second row: PADS (red) vs VGT (blue). Third row: SPLEAT (red) vs PADS (blue)                                                                                                                        |

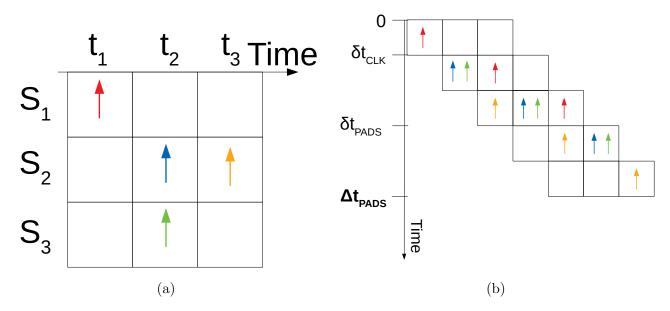

| 5.7  | a) Simple spike trace example with 4 input synapses and 4 time increments, b) Illustration of PADS parallel and pipelined process                                                                                                                                                                        |

| 5.8  | Illustration of SPLEAT sequential process                                                                                                                                                                                                                                                                |

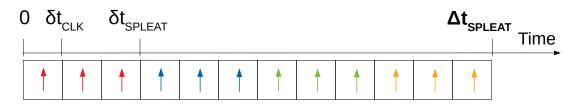

| 5.9  | a) FPGA power consumption model, b) Dynamic and Static power VS LUT occupation (%) on Zedboard                                                                                                                                                                                                           |

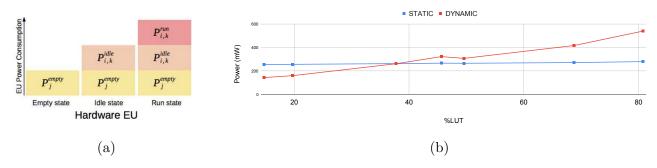

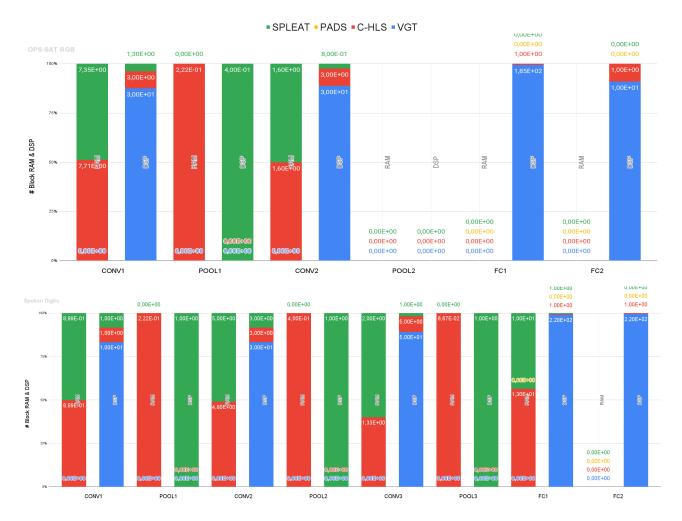

| 5 10 | Layer-wise LUT estimation in VGT, HLS, PADS and SPLEAT. Top: OPSSAT                                                                                                                                                                                                                                      |

| 0.10 | RGB, bottom: Spoken Digits                                                                                                                                                                                                                                                                               |

|      | Layer-wise RAM and DSP estimation in VGT, HLS, PADS and SPLEAT. Top: OPSSAT RGB, bottom: Spoken Digits                                                                                                                                                                                                   |

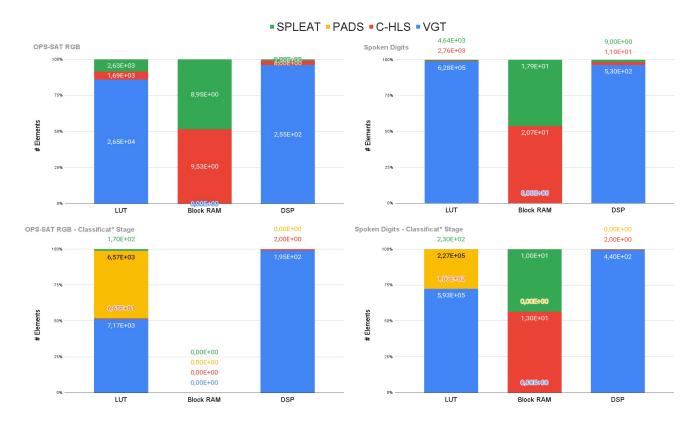

| 5.12 | Comparisons of resource usage in VGT, HLS, PADS and SPLEAT. Left: OPSSAT,                                                                                                                                                                                                                                |

|      | Right: Spoken Digits. Top: Full network, Bottom: Classification Stage                                                                                                                                                                                                                                    |

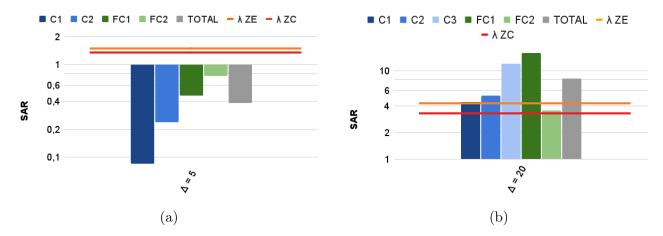

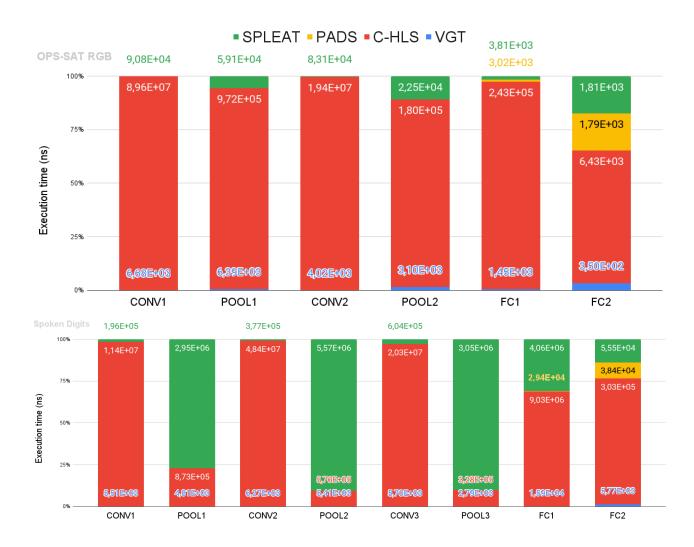

|      | Layer-wise and total SAR for a) OPS-SAT ( $\Delta = 4$ ) and b) Spoken Digits ( $\Delta = 20$ ). Layer-wise execution time (per image) estimation in VGT, HLS, PADS and SPLEAT.                                                                                                                          |

|      | Top: OPSSAT RGB, bottom: Spoken Digits                                                                                                                                                                                                                                                                   |

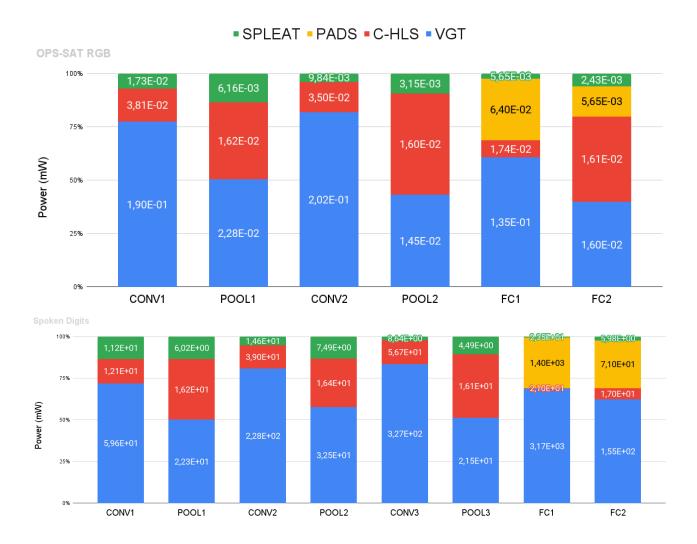

| 5.15 | Layer-wise Power estimation in VGT, HLS, PADS and SPLEAT. Top: OPSSAT                                                                                                                                                                                                                                    |

|      | RGB, bottom: Spoken Digits                                                                                                                                                                                                                                                                               |

LIST OF FIGURES viii

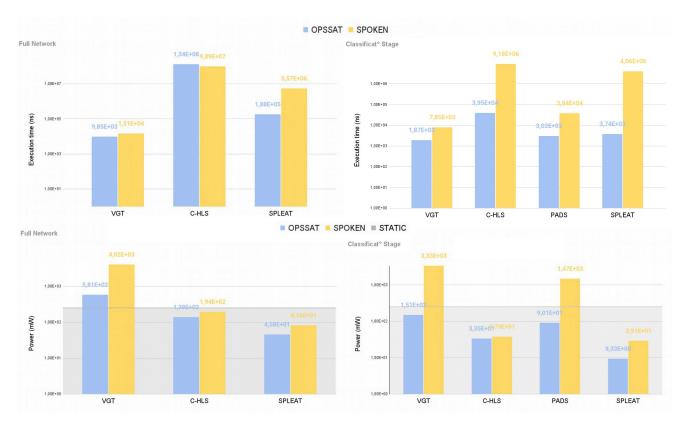

| 5.16       | and SPLEAT. Left: full network, Right: classification stage. Top: time, Bottom:                                                                                                                                                          |     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | power                                                                                                                                                                                                                                    | 100 |

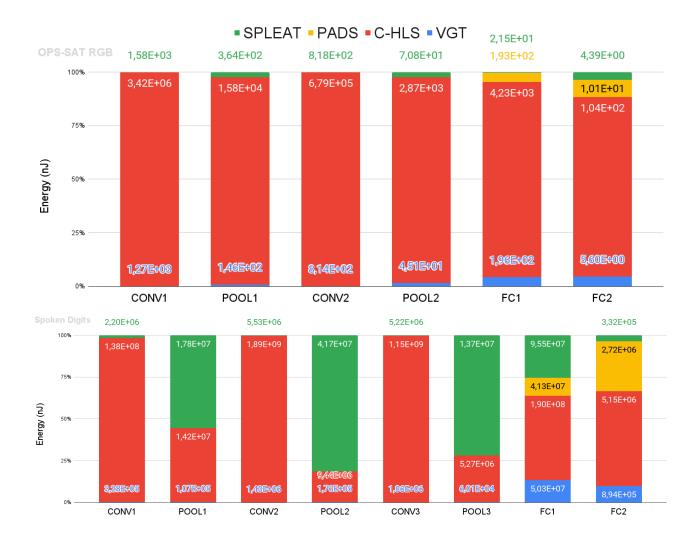

|            | Layer-wise energy estimation (per image) in VGT, HLS, PADS and SPLEAT. Top: OPSSAT RGB, bottom: Spoken Digits                                                                                                                            | 102 |

| 5.18       | Comparisons of energy consumption per image in VGT, HLS, PADS and SPLEAT.                                                                                                                                                                |     |

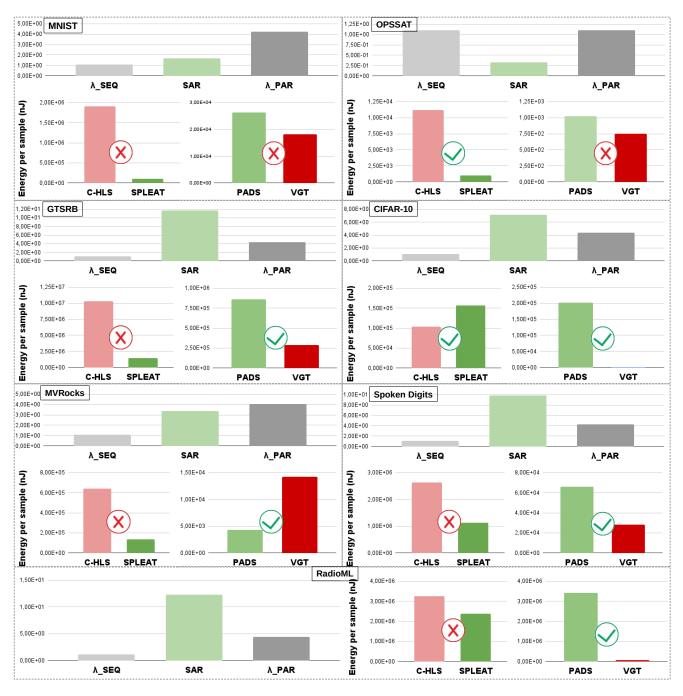

| 5.19       | mark: MNIST, OPSSAT, GTSRB, CIFAR-10, Mines VS Rocks, Spoken Digits and RadioML 2018. Validation is made separately for parallel and sequential architectures. Each subfigure is divided between SAR & $\lambda$ values (top) and energy | 103 |

| 5.20       |                                                                                                                                                                                                                                          | 105 |

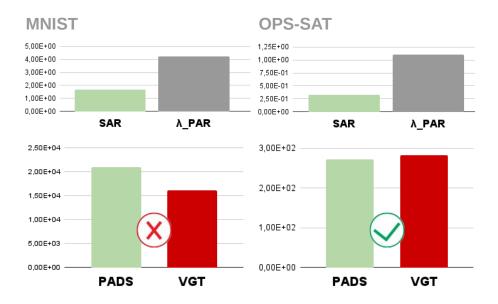

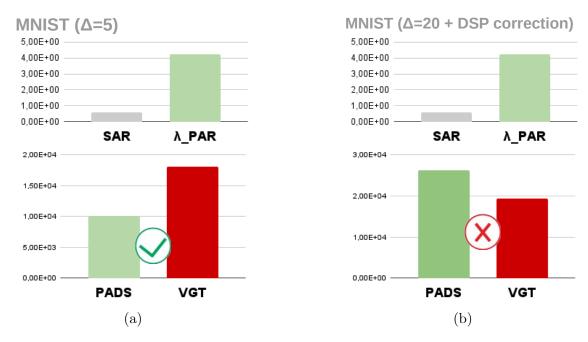

|            | 20) and OPSSAT( $\Delta = 4$ )                                                                                                                                                                                                           | 107 |

| 5.21       | SAR and energy estimations for MNIST with $\Delta = 5$ (left) and MNIST with $\Delta = 20$ after applying the DSP saturation correction (right)                                                                                          | 108 |

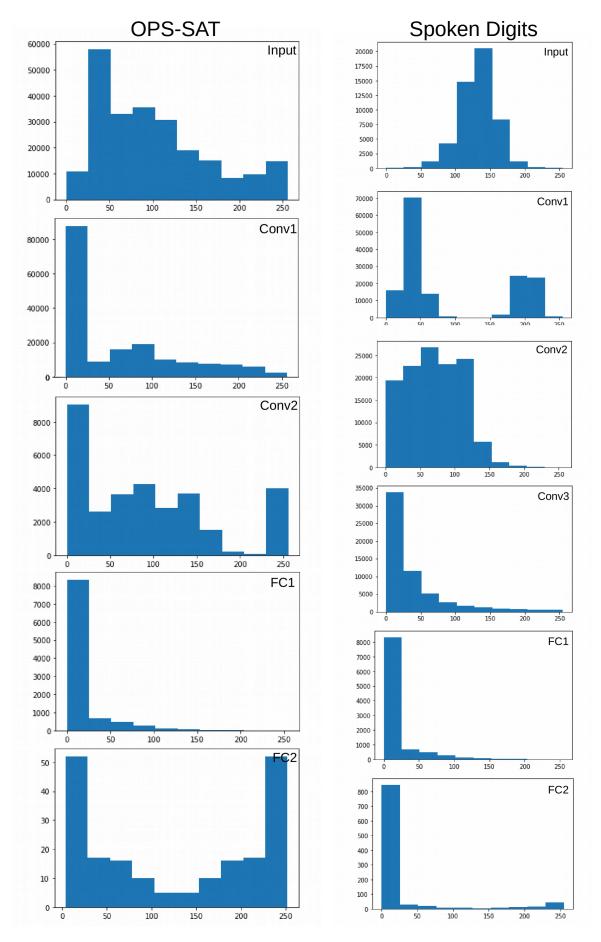

| 6.1<br>6.2 | Activity distribution in CNN layers for OPSSAT (left) and Spoken Digits (right) . Spike train period with respect to element intensity according to the rate-coding                                                                      | 114 |

|            | policy, with $PeriodMax = 1timestep$ and $PeriodMax = 100timesteps$                                                                                                                                                                      | 115 |

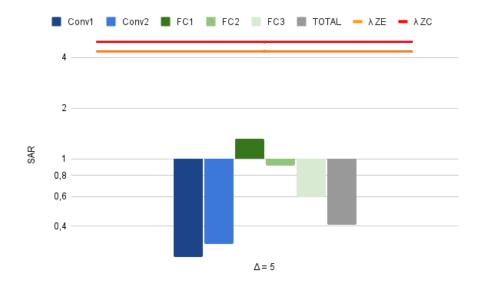

| 6.3        | Layer-wise and total SAR for a) OPS-SAT ( $\Delta = 4$ ) and b) Spoken Digits ( $\Delta = 20$ ).                                                                                                                                         | 118 |

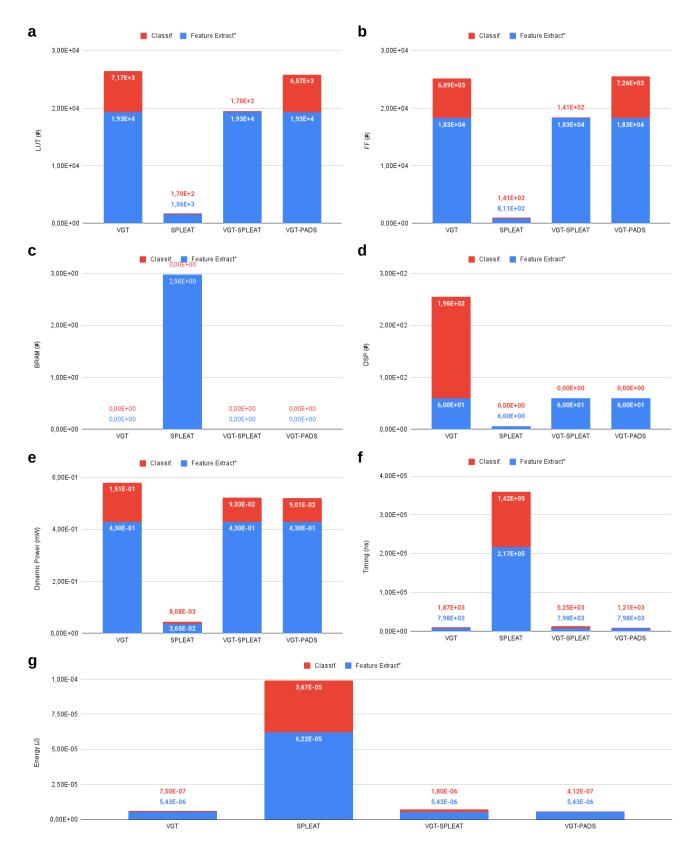

| 6.4        | Hardware footprint estimation of VGT, SPLEAT, Hybrid VGT-SPLEAT and Hy-                                                                                                                                                                  |     |

|            | brid VGT-PADS on OPS-SAT RGB dataset with $\Delta = 4$ , $MinPeriod = 1$ and $ManPeriod = 100$ , a) LUT b) Pariotage a) Plack PAM d) DSP a) Payon f)                                                                                     |     |

|            | MaxPeriod = 100. a) LUT, b) Registers, c) Block RAM, d) DSP, e) Power, f) Inference time and g) Energy                                                                                                                                   | 119 |

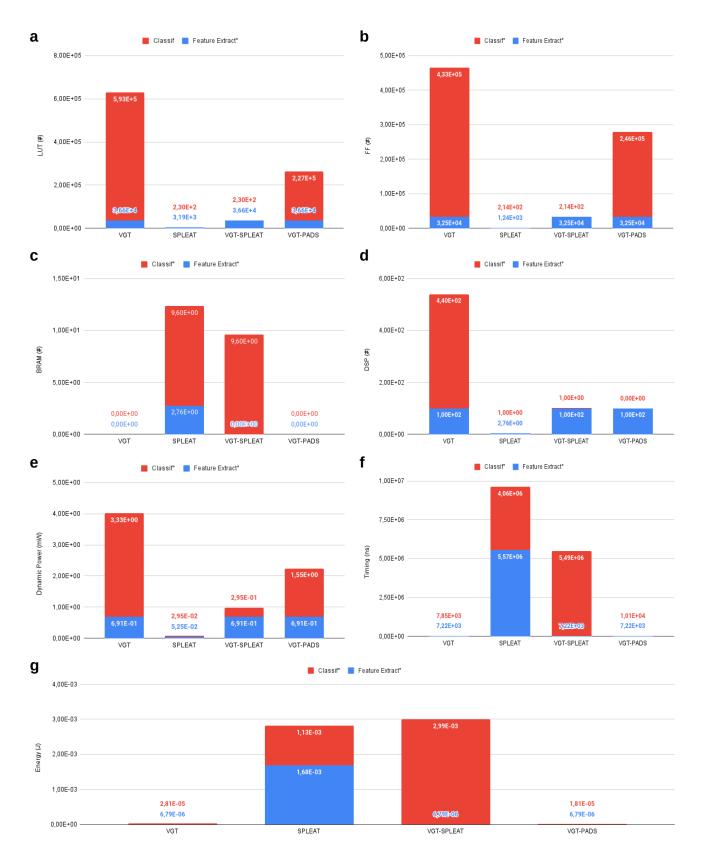

| 6.5        | Hardware footprint estimation of VGT, SPLEAT, Hybrid VGT-SPLEAT and Hy-                                                                                                                                                                  | 110 |

|            | brid VGT-PADS on Spoken Digits RGB dataset with $\Delta=4, MinPeriod=1$ and $MaxPeriod=100.$ a) LUT, b) Registers, c) Block RAM, d) DSP, e) Power, f)                                                                                    |     |

| 0.0        | Inference time and g) Energy.                                                                                                                                                                                                            | 121 |

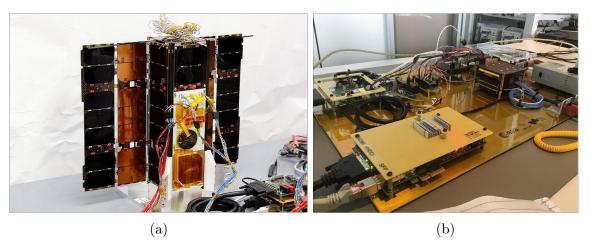

| 6.6        | a: OPS-SAT CubeSat being tested before launch. b: OPS-SAT FlatSat platform. Photo credits: TU Graz [19]                                                                                                                                  | 123 |

| 6.7        | Impression of OPS-SAT in low earth orbit [20]                                                                                                                                                                                            | 123 |

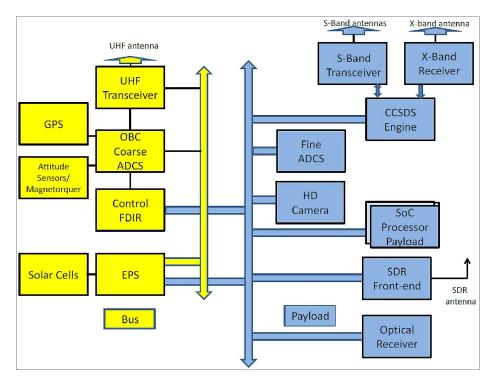

| 6.8        | Schematic of OPS-SAT architecture. The yellow part is for the "technical" bus,                                                                                                                                                           |     |

|            | and the blue part is for the payload. Source: [19]                                                                                                                                                                                       | 125 |

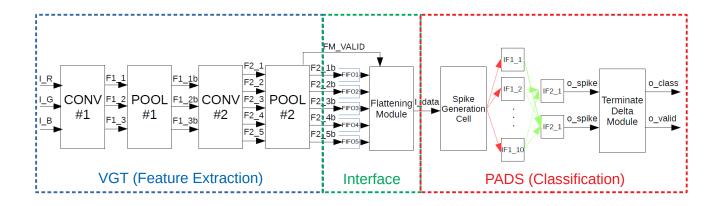

| 6.9        | Illustration of the CIAR Hybrid Neural Network Architecture                                                                                                                                                                              | 126 |

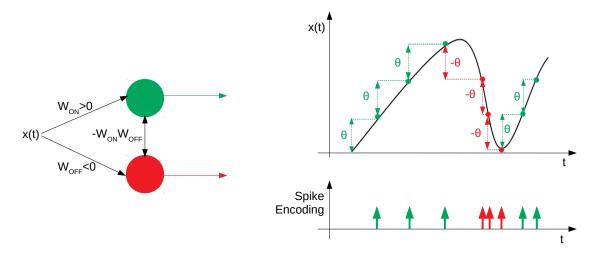

| 7.1        | Illustration of the Send-on-Delta spike encoding process used in $[21]$ , for $2$ IF neurons                                                                                                                                             |     |

|            | encoding a 1D temporal signal. Left: network setup. Right: input and output data.                                                                                                                                                        | 131 |

| 7.2        | Illustration of the Leaky Integrate & Fire neuron process. The membrane potential                                                                                                                                                        | 100 |

| 7.3        | is shown in blue, input spikes in green and output spikes in red                                                                                                                                                                         | 132 |

| 1.0        | work. Samples are presented for 5, 10 and 20 time-steps. The $\lambda$ value is depicted                                                                                                                                                 |     |

|            | in orange for the Zedboard and red for the ZCU102 (see Section 4.3.2). All mea-                                                                                                                                                          |     |

|            | surements are averaged on 10 runs                                                                                                                                                                                                        | 136 |

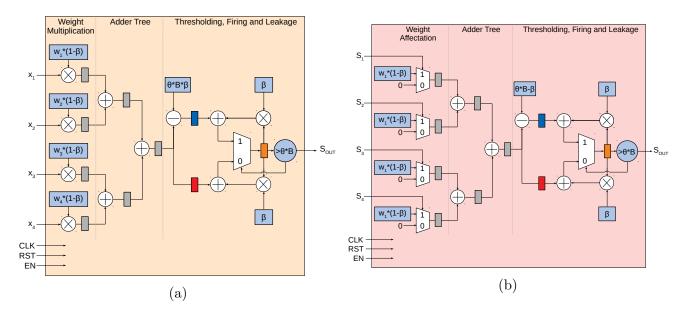

| 7.4        | Hardware architecture of: a) FISO neuron with 4 input pixels, b) LIF neuron with                                                                                                                                                         |     |

|            | 4 input synapses. Register barriers are shown in gray or colored rectangles. Data                                                                                                                                                        |     |

|            | stored in memory is depicted in light blue squares                                                                                                                                                                                       | 140 |

LIST OF FIGURES ix

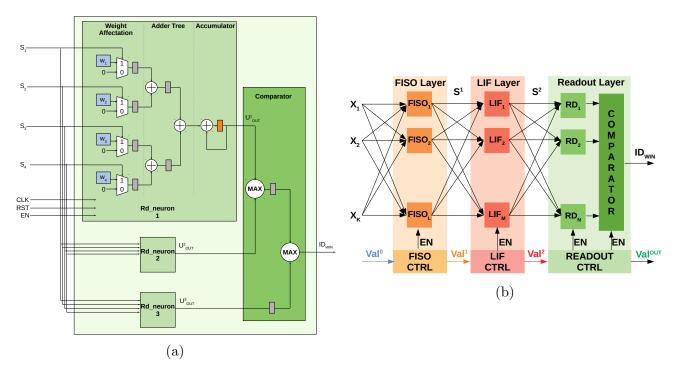

| 7.5 | a) Architecture of the Readout layer with 4 input synapses and 3 neurons. b)                                                                                                                  |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Overview of the full architecture of PADS V2                                                                                                                                                  | 141 |

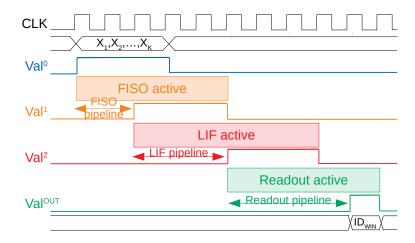

| 7.6 | Chronogram of the PADS-V2 pipelined process at network-level                                                                                                                                  | 142 |

| 1   | Illustration of the CIAR cloud segmentation task. On the left, the original image taken by OPS-SAT. On the right, the resulting segmentation map, with cloudy patches in yellow. Source: [15] | 160 |

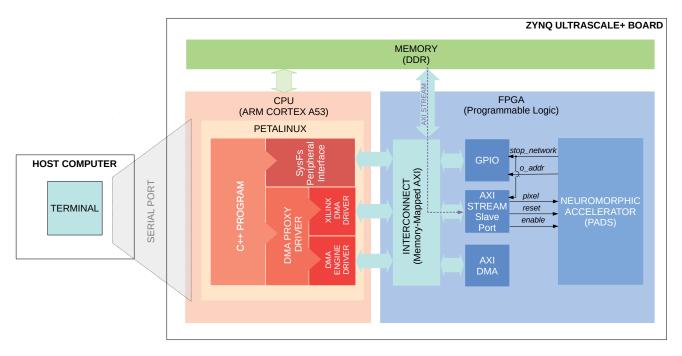

| 2   | Custom FPGA platform for neuromorphic accelerator deployment. The software                                                                                                                    |     |

|     | stack is in shades of red, and the hardware stack is in shades of blue                                                                                                                        | 162 |

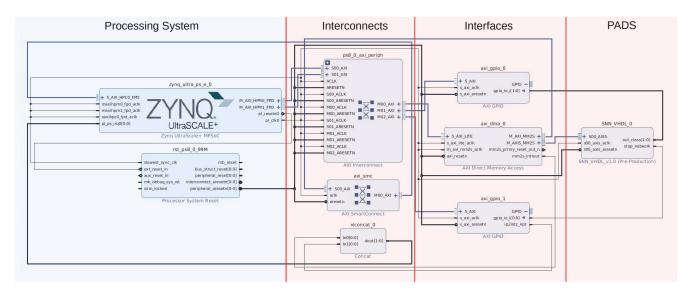

| 3   | Vivado block design of the FPGA part of the SNN deployment platform                                                                                                                           | 163 |

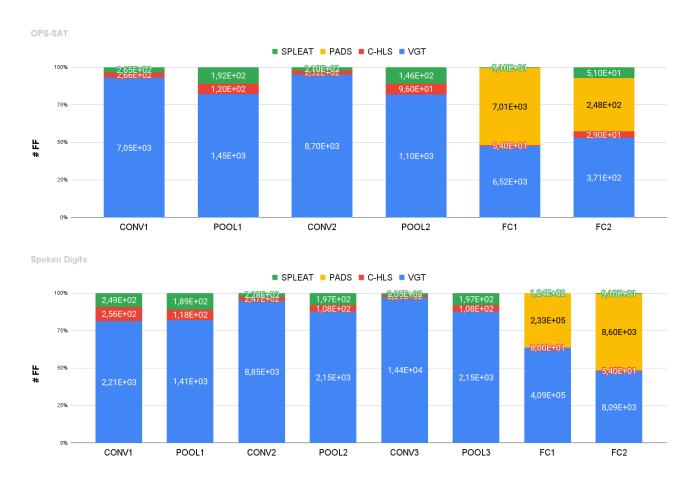

| 4   | Estimations on Flip-FLop usage for OPS-SAT and Spoken Digits associated CNNs                                                                                                                  | 164 |

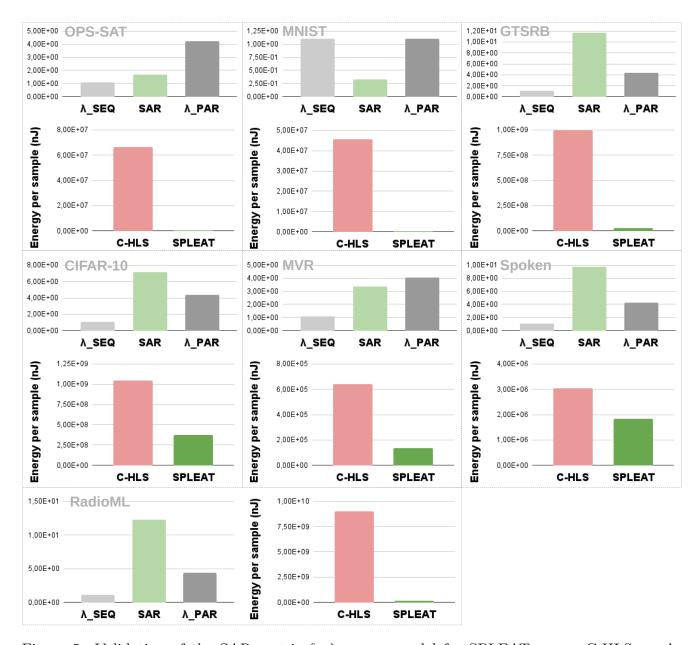

| 5   | Validation of the SAR metric & $\lambda$ energy model for SPLEAT versus C-HLS on the                                                                                                          |     |

|     | benchmark of datasets for full-networks. Top: SAR vs $\lambda_{SEQ}$ , Bottom: SPLEAT vs                                                                                                      |     |

|     | C-HLS energy consumption                                                                                                                                                                      | 165 |

# List of Tables

| 2.1               | Logic resources, execution time, power and energy of FPGA SNN accelerators found in the literature. Topology nomenclature: $KcWsX = Convolution$ layer with $K$ filters of size $W^2$ and a stride of $X$ , $KpWsX = Pooling$ layer with $K$ filters of size $W^2$ and a stride of $X$ . Fully-connected layers are referred to by their number of output neurons | 22             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.1<br>3.2        | TensorFlow Keras parameters used for training in all our experiments Hardware resources measures for PADS and VGT MLPs on OPS-SAT Grayscale Dataset: $28 \times 28$ - $100$ - $2$                                                                                                                                                                                 | 44<br>45       |

| 4.1<br>4.2<br>4.3 | Large CNN topology for Spoken Digits dataset. This CNN achieves 97.34% accuracy. List of CNN topologies for the classification benchmark                                                                                                                                                                                                                          | 58<br>59<br>60 |

| 4.6<br>4.7        | without DSPs                                                                                                                                                                                                                                                                                                                                                      | 66<br>69<br>72 |

| 5.1               | Dynamic power consumption in PADS with and without power gating, on the benchmark of datasets. VGT dynamic power usage is shown for comparison. Results are shown for the classification stage (FC layers) only. The results have been obtained through the estimation framework, for $\Delta=20$ (best accuracy)                                                 | 109            |

| 6.1<br>6.2        | CNN topologies for a) OPS-SAT and b) Spoken Digits datasets                                                                                                                                                                                                                                                                                                       | 115            |

| 6.3               |                                                                                                                                                                                                                                                                                                                                                                   | 117            |

| 0.0               |                                                                                                                                                                                                                                                                                                                                                                   | 126            |

| 7.1<br>7.2        | Comparison of accuracy and network-wise SAR with Conversion with Rate-coding and SGL with SoD. Bold letters show the best-case accuracy for reach method and                                                                                                                                                                                                      | 134            |

| 7.3<br>7.4        |                                                                                                                                                                                                                                                                                                                                                                   | 135<br>143     |

|                   |                                                                                                                                                                                                                                                                                                                                                                   | 143            |

LIST OF TABLES xi

| 1 | LUT, FF, Block RAM and DSP occupation measures for Convolution layers at          |     |

|---|-----------------------------------------------------------------------------------|-----|

|   | design-space measurement points. Measures obtained after hardware synthesis on    |     |

|   | Xilinx Vivado Design Suite, targeting Xilinx Zedboard                             | 166 |

| 2 | LUT, FF, Block RAM and DSP occupation measures for Pooling layers at design-      |     |

|   | space measurement points. Measures obtained after hardware synthesis on Xilinx    |     |

|   | Vivado Design Suite, targeting Xilinx Zedboard                                    | 166 |

| 3 | LUT, FF, Block RAM and DSP occupation results for Fully-Connected layers at       |     |

|   | design-space measurement points. Measures obtained after hardware synthesis on    |     |

|   | Xilinx Vivado Design Suite, targeting Xilinx Zedboard                             | 167 |

| 4 | Power measures for Fully-Connected layers at design-space measurement points.     |     |

|   | Measures obtained after hardware synthesis and simulation on Xilinx Vivado Design |     |

|   | Suite targeting Xilinx Zedboard                                                   | 167 |

| 5 | Power measures for Convolution layers at design-space measurement points. Mea-    |     |

|   | sures obtained after hardware synthesis and simulation on Xilinx Vivado Design    |     |

|   | Suite targeting Xilinx Zedboard                                                   | 168 |

| 6 | Power measures for Pooling layers at design-space measurement points. Measures    |     |

|   | obtained after hardware synthesis and simulation on Xilinx Vivado Design Suite    |     |

|   | targeting Xilinx Zedboard                                                         | 168 |

| 7 | Duration results for Fully-Connected layers at design-space measurement points.   |     |

|   | Measures obtained by calculation and validated using post-synthesis simulation    | 169 |

| 8 | Duration results for Convolution layers at design-space measurement points. Mea-  |     |

|   | sures obtained by calculation and validated using post-synthesis simulation       | 169 |

| 9 | Duration results for Pooling layers at design-space measurement points. Measures  |     |

|   | obtained by calculation and validated using post-synthesis simulation             | 170 |

# Contents

| 1        | Inti | roduction                                                   |

|----------|------|-------------------------------------------------------------|

|          | 1.1  | History of Deep Learning                                    |

|          | 1.2  | Energy Consumption and Embedded Systems                     |

|          | 1.3  | Bio-inspired neurons for Machine Learning                   |

|          | 1.4  | Problem statement and outline                               |

| <b>2</b> | Sta  | te of the Art & Contributions                               |

|          | 2.1  | Formal neurons                                              |

|          |      | 2.1.1 Feed-forward NN and CNNs                              |

|          |      | 2.1.2 Error gradient backpropagation algorithm              |

|          | 2.2  | FNN in hardware                                             |

|          |      | 2.2.1 Hardware neural networks on digital hardware          |

|          |      | 2.2.2 Example of FNN accelerators for FPGA                  |

|          | 2.3  | Spiking Neural Networks                                     |

|          |      | 2.3.1 Principle of Spiking Neural Networks                  |

|          |      | 2.3.2 Spike encoding                                        |

|          |      | 2.3.3 Training SNNs                                         |

|          |      | 2.3.4 Terminate Delta                                       |

|          | 2.4  | SNNs in hardware                                            |

|          |      | 2.4.1 Advantages of SNNs in Hardware                        |

|          |      | 2.4.2 Literature review                                     |

|          |      | 2.4.3 Confronting Spiking and Formal Neural Networks        |

|          | 2.5  | Conclusion                                                  |

|          | 2.6  | Contributions                                               |

|          |      | 2.6.1 Synaptic Activity                                     |

|          |      | 2.6.2 Quantitative comparison of formal and spiking domains |

|          |      | 2.6.3 Cartography of applications and neural coding domains |

|          |      | 2.6.4 How to benefit from spiking domain?                   |

| 3        | Spil | king Neural Networks parallel implementation: PADS 3-       |

|          | 3.1  | Hardware Architecture                                       |

|          |      | 3.1.1 Spike Generation Cell                                 |

|          |      | 3.1.2 Neural Processing Unit                                |

|          |      | 3.1.3 Terminate Delta Module                                |

|          | 3.2  | Hardware Synthesis Results                                  |

|          |      | 3.2.1 Methodology                                           |

|          |      | 3.2.2 Comparison with VGT                                   |

|          |      | 3.2.3 Spike Generation Overhead                             |

|          |      | 3.2.4 Conclusions on PADS hardware implementation           |

|          | 3.3  | Conclusion                                                  |

CONTENTS xiii

| 4 | Syn | aptic Activity Ratio & Energy Modeling               | <b>52</b>  |

|---|-----|------------------------------------------------------|------------|

|   | 4.1 | Representative Datasets                              | 53         |

|   |     | 4.1.1 Used topologies                                | 54         |

|   | 4.2 | Accuracy and synaptic activity measurements          | 55         |

|   |     | 4.2.1 Methods                                        | 56         |

|   |     | 4.2.2 Synaptic activity results                      | 58         |

|   |     | 4.2.3 Discussions on Synaptic Activity results       | 62         |

|   | 4.3 | Synaptic Activity ratio                              | 63         |

|   |     | 4.3.1 Energy Consumption Model                       | 63         |

|   |     | 4.3.2 The value of $\lambda$                         | 65         |

|   | 4.4 | Synaptic Activity Ratio measurements                 | 67         |

|   | 1.1 | 4.4.1 Synaptic Activity Ratio evaluation software    | 67         |

|   |     | 4.4.2 Network-wise SAR & theoretical cartography     | 69         |

|   |     | 4.4.3 Data type and rate-coding                      | 73         |

|   |     | 4.4.4 Layer-wise SAR & hybridization                 | 73         |

|   | 4.5 | Conclusion                                           | 74         |

|   | 4.0 | Conclusion                                           | 14         |

| 5 | Har | dware Footprint and High-Level Estimations           | 77         |

|   | 5.1 | Motivations                                          | 79         |

|   |     | 5.1.1 Speed-up cartography and exploration           | 79         |

|   |     | 5.1.2 Layer-wise approach                            | 79         |

|   |     | 5.1.3 Level of parallelism                           | 79         |

|   | 5.2 | Framework                                            | 80         |

|   |     | 5.2.1 Hardware measurements database                 | 80         |

|   |     | 5.2.2 Execution time                                 | 85         |

|   |     | 5.2.3 Spiking hardware inference simulator           | 90         |

|   | 5.3 | Ressource estimations                                | 92         |

|   | J.J | 5.3.1 Layer-wise estimation                          | 93         |

|   |     | 5.3.2 Network-wise estimation                        | 95         |

|   |     | 5.3.3 Conclusions                                    | 96         |

|   | 5.4 | Inference time and power estimations                 | 96         |

|   | 0.1 | 5.4.1 Layer-wise estimation                          | 96         |

|   |     | v                                                    | .00<br>001 |

|   |     |                                                      | 100        |

|   | 5 5 |                                                      | 101        |

|   | 5.5 | 0,                                                   | 101        |

|   |     | v                                                    |            |

|   |     |                                                      | 103        |

|   | - 0 | 0,                                                   | 104        |

|   | 5.6 |                                                      | 106        |

|   | 5.7 |                                                      | 107        |

|   | 5.8 |                                                      | 110        |

|   |     | 1                                                    | 10         |

|   |     | 1                                                    | 10         |

|   |     |                                                      | 11         |

|   |     | 5.8.4 Hybridization and other spike encoding methods | 11         |

CONTENTS xiv

| 6            | Net | ıral coding domain hybridization                     | 112          |

|--------------|-----|------------------------------------------------------|--------------|

|              | 6.1 | Motivations                                          | 113          |

|              |     | 6.1.1 SAR and footprint variability                  | 113          |

|              |     | 6.1.2 Distribution of activity                       | 115          |

|              |     | 6.1.3 Formal convolutions and spiking classification | 116          |

|              | 6.2 | Estimations on hybrid architectures                  | 116          |

|              |     | 6.2.1 Methodology                                    | 116          |

|              |     | 6.2.2 OPS-SAT                                        | 117          |

|              |     | 6.2.3 Spoken Digits                                  | 120          |

|              |     | 6.2.4 Discussions on hybrid estimations              | 122          |

|              | 6.3 | Hybrid hardware implementation                       | 123          |

|              |     | 6.3.1 Context                                        | 124          |

|              |     | 6.3.2 VGT-PADS Hybrid Architecture                   | 124          |

|              | 6.4 | Conclusion                                           | 127          |

|              |     | 6.4.1 Outlook                                        | 128          |

|              |     |                                                      |              |

| 7            |     | nancing PADS: FISO & LIF as Recurrent neurons        | 129          |

|              | 7.1 | Theoretical Background                               | 130          |

|              |     | 7.1.1 Send on Delta spike encoding                   | 130          |

|              |     | 7.1.2 LIF Neuron                                     | 131          |

|              |     | 7.1.3 LIF as recurrent neurons                       | 132          |

|              |     | 7.1.4 Surrogate Gradient Learning                    | 133          |

|              |     | 7.1.5 Output decoding: readout layer                 | 133          |

|              |     | 7.1.6 Application in the S2NET framework             | 133          |

|              |     | 7.1.7 Static input samples                           | 134          |

|              | 7.2 | Accuracy & SAR results                               | 134          |

|              | 7.3 | PADS V2                                              | 138          |

|              |     | 7.3.1 Architecture                                   | 138          |

|              |     | 7.3.2 Inference Time Results                         | 141          |

|              | 7.4 | Conclusions & Outlooks                               | 144          |

| 8            | Cor | nclusions and outlooks                               | 145          |

| O            | 8.1 | Conclusion                                           | 145          |

|              | 8.2 | Outlooks                                             | $143 \\ 147$ |

|              | 0.2 | 8.2.1 Short term and work-specific perspectives      | 147          |

|              |     | 8.2.2 Middle term outlooks and insights              |              |

|              |     | 8.2.2 Wilddie term Outlooks and hisights             | 140          |

| $\mathbf{A}$ | PPE | NDIX 1: CIAR project                                 | 159          |

| Α.           | DDE | NDIV 2. Custom SoC pletform                          | 161          |

| Α.           |     | NDIX 2: Custom SoC platform                          | 161          |

|              | .1  | Programmable Logic modules                           | 161          |

|              | .2  | CPU & Embedded Linux                                 | 162          |

| $\mathbf{A}$ | PPE | NDIX 3: Additional figures                           | 164          |

| $\mathbf{A}$ | PPE | NDIX 4: Measurements                                 | 166          |

| Δ            | PPE | NDIX 5: Raw Estimations                              | 171          |

# Chapter 1

# Introduction

In recent years, the field of artificial intelligence has been widely dominated by Deep Learning. This field of Machine Learning uses Artificial Neural Networks which model the biological neural networks in mathematical equations. This approach enables to emulate more and more complex cognitive functions in automated algorithms, such as image classification, object detection, natural language processing or decision making. Since it first appeared in the foreground of research in the 90's, all those domains have been revolutionized by Deep Learning. The complexity of the models growing further and further, the limits of Machine Learning are constantly pushed back, involving more and more application domains and industrial actors.

# 1.1 History of Deep Learning

Long before its modern supremacy, the premises of Deep Learning dates back to the very beginning of computer science. In the same school of thought of Alan Turing, researchers like McCulloch and Pitts worked to demonstrate that cognition could be modeled through mathematical functions. In 1943, they proposed the first artificial neuron model [22]. In this breakthrough publication, the authors demonstrated that a network of such formal neurons was able to emulate propositional logic functions. Later in 1957, Rosenblatt proposed the first application of formal neurons to automated classification: the perceptron [23]. The perceptron is made of a single layer of formal neurons. The major contribution of this pioneering publication is the learning algorithm. By iterating over a set of labeled training samples, the algorithm automatically adjusts the synaptic weights to minimize the output error. In doing so, the authors proposed the first supervised learning algorithm. However, the technique was limited to single layers of neurons, which were only able to solve binary classification problems. This limitation was leveraged in another major breakthrough when Werbos proposed the Multi-Layer Perceptron (MLP) and gradient BackPropagation (BP) algorithm in 1974 [24]. The MLP is considered by many as the first modern neural network model, and the BP algorithm is still a fundamental element of modern Machine Learning. The BP algorithm allows to train several successive perceptron layers at once, hence the name Multi-Layer Perceptron. The deeper meaning of this work is even more revolutionary: an MLP of arbitrary size and depth is theoretically able to solve any non-linear problem. However, the feasibility of this algorithm was limited by the available computing power in the early 70's.

Following Moore's law, the exponential growth of computing power made it possible in 1986, when Rumelhart proposed the first implementation of the BP algorithm in a feed-forward MLP [25]. This work opened the gates to what has since become modern Deep Learning by using deeper and deeper networks, the models were able to solve more and more complex tasks in various application fields. The most prominent of which was computer vision: extracting information from images for classification, segmentation or detection. In 1989, LeCun proposed the first Convolution Neural Network (CNN) [26] trained with the BP algorithm. The innovation of this model is to give a structure to the layers of neurons according to specificities of the application. For computer

vision, the convolution layers are designed to extract spatial patterns. LeCun later generalized the CNN model to various tasks in the fields of image classification, speech recognition and time-series prediction [27]. The convolution layers are still widely used in Deep Learning to this date, and are one of the key components of modern neural network architectures like VGG-16 [28]. In recent years, other Formal Neural Networks (FNN) models have emerged for various domains of application, like Transformer neural networks for Natural Language Processing [29]. In doing so, the models are getting deeper and deeper and more and more complex. For example, the recent GPT-3 transformer model proposed by the OpenAI team in 2020 [30] uses 175 billions of parameters, *i.e.* 175 billions of explicit synaptic connections.

### 1.2 Energy Consumption and Embedded Systems

Neural network models becoming more and more complex, they have higher and higher computational requirements for training and inference. For example, the GPT-3 transformer model with 175 billion parameters requires a bare minimum of 350GB of GPU memory for inference. That is equivalent to 8 Nvidia A6000 GPUs; the latest and most powerful deep-learning oriented High-Performance Computing (HPC) device. This represents a power consumption of 2400W. Therefore, the energetic scalability of Machine Learning starts to raise questions among the scientific and public communities. But this energetic issue is even more problematic in the field of embedded systems. Indeed, the recent emergence of the Internet of Things (IoT) opened a brand new field of applications for neural networks. From autonomous navigation in drones or self-driving cars, to advanced robotics and augmented reality, the need for such embedded artificial intelligence is just starting to rise. By definition, those systems are isolated from the power grid, and must run on battery or energy harvested from the environment (mostly solar panels). Quite straightforwardly, the energy budget of Deep Learning is not compliant with such constrained systems.

An approach chosen by many researchers in the field of neural network acceleration is to take inspiration from the most advanced and efficient neural processor anyone has ever heard of: the biological brain. The human brain is said to feature more than 10 000 billions synaptic connections per cm<sup>3</sup>. On the other hand, it consumes no more than 20W in average. Since the volume of human brain is roughly  $1450 \, \mathrm{cm}^3$ , that is an average of  $10^{-17} W$  per synapse. For comparison, the most advanced neural network model (GPT-3) running on the most advanced hardware available (Nvidia A6000) uses approximately  $10^{-8} W$  per synapse (175 billions synapses and 2400W for 8 A6000 GPUs). That is, if we omit the nature of the network itself (its topology and actual neuron dynamics) and if we consider that the number of synapses is a reliable metric to compare the brain and a deep learning model, the first is approximately one billion times more energy-efficient than the latter. It seems that we indeed have a lot to learn from biology regarding low-power neural processing.

## 1.3 Bio-inspired neurons for Machine Learning

In the field of Machine Learning, the main interest is to develop powerful models applied to solving real-world problems, like image segmentation for self-driving cars or natural language processing for virtual assistants. However, another field of research has long paid interest to artificial neural networks for other motivations. Neurosciences and Cognitive Sciences use them as a tool to simulate cognitive functions, providing a better understanding of the underlying mechanisms of the human mind. For this purpose, computational Neurosciences are interested in the biological plausibility of the neuron models. In doing so, many biological neuron models have been proposed, mimicking the event-based nature of the brain. In contrast with Machine Learning which uses static real-valued information encoding, the biological brain uses action potentials: brief electrical impulses better known by the name of spikes. In Spiking Neural Networks (SNNs), information is encoded temporally with spikes. The strong hypothesis at the basis of our approach is the following: spike encoding is one of the major sources of power efficiency in the biological brain, compared to formal Machine Learning models. This hypothesis is backed by several factual assessments. In the widely used Integrate & Fire spiking neuron model, multiplication-accumulation operations are replaced with accumulation. The latter uses fewer logic and power than the first [31], hence the expectations of a better hardware-efficiency. Moreover, the sparse encoding of information in SNNs enables a sparse computation. In other words, the design is only active upon processing input spikes and remains idle otherwise. This feature is known as "frame-free", in contrast with the frame-constrained nature of the formal approach. Additionally, spikes enable light-weight communication between neurons, further reducing the hardware footprint.

In the light of these assessments, a recent trend in the field of neural network acceleration is to use bio-inspired neurons in deep-learning network models. It consists in developing application specific hardware architectures to support the inference of deep SNN models. By using bio-inspired neuron and event-based computation, expectations are a major reduction of energy consumption. This is a particularly appealing promise for embedded systems. In all, SNNs are expected to leverage the energy consumption limitations of embedded artificial intelligence. The thesis lies precisely in this field of the research: Neuromorphic Computing. More precisely, this work deals with the hardware acceleration of Spiking Neural Networks on FPGA, and the associated energy savings.

### 1.4 Problem statement and outline

However, there is still a lack of clear, fair and extensive comparison between formal and spiking hardware neural networks in the literature. The hardware-efficiency promises remain unproven outside of very specific cases, and most importantly: to be quantified. In this thesis, we address the most widely used type of SNNs to our knowledge: rate-coded SNNs converted from formal models. The goal of this thesis is to evaluate the potential energy efficiency gains of this model over conventional Formal Neural Networks in the context of FPGA accelerators. More precisely, this thesis aims in providing a cartography of neural coding domains and applications. In other words, the goal is to determine which type of application would be better suited to spiking domain acceleration in terms of energy gains. Moreover, this study follows a hardware-software co-design approach: the model and the underlying hardware has to be designed according to one another. In doing so, our goal is also to find innovative ways to benefit from spiking neurons in hardware and vice versa. The contributions of this work relatively to the literature will be described further at the end of the State-of-the-Art section (Chapter 2).

This document begins with a detailed state-of-the-art (Chapter 2), including a theoretical background of formal and spiking neural network models and hardware acceleration. We also provide an overview of the existing architectures and few publications addressing the comparison of the two neural coding domains. In Chapter 3, we describe our prototype of hardware accelerators for fully-connected spiking layers: PADS. It is based on rate-coding, and is used as an experimental