## High-efficiency Si solar cell including tunnel junction for tandem photovoltaic cells

Xiao Li

#### ▶ To cite this version:

Xiao Li. High-efficiency Si solar cell including tunnel junction for tandem photovoltaic cells. Micro and nanotechnologies/Microelectronics. Université de Lyon, 2021. English. NNT: 2021LYSEI097. tel-03670810

## HAL Id: tel-03670810 https://theses.hal.science/tel-03670810

Submitted on 17 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2021LYSEI097

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de l'INSA de Lyon

## **Ecole Doctorale N° 160** Electronique, Electrotechnique et Automatique

## Spécialité/ discipline de doctorat :

Electronique, micro et nanoélectronique, optique et laser

Soutenue publiquement le 13/12/2021, par : Xiao LI

## **High-efficiency Si solar cell including** tunnel junction for tandem photovoltaic cells

#### Devant le jury composé de :

| M. PALAIS Olivier         | Professeur des universités     | IM2NP,<br>Aix-Marseille Université      | Rapporteur            |

|---------------------------|--------------------------------|-----------------------------------------|-----------------------|

| M. CUMINAL Yvan           | Maître de Conférences<br>(HDR) | IES,<br>Université Montpellier II       | Rapporteur            |

| Mme KAMINSKI-CACHOPO Anne | Professeur des universités     | IMEP-LAHC,<br>Université Grenoble Alpes | Examinatrice          |

| Mme MUNOZ Delfina         | Ingénieur de recherche         | LHET,<br>INES-CEA, Chambéry             | Examinatrice          |

| M. LEMITI Mustapha        | Professeur des universités     | INL, INSA Lyon                          | Directeur de thèse    |

| M. FAVE Alain             | Maître de Conférences          | INL, INSA Lyon                          | Co-encadrant de thèse |

## **Département FEDORA – INSA Lyon - Ecoles Doctorales**

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                         | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                                                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON  https://www.edchimie-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage secretariat@edchimie-lyon.fr                                                            | M. Stéphane DANIELE C2P2-CPE LYON-UMR 5265 Bâtiment F308, BP 2077 43 Boulevard du 11 novembre 1918 69616 Villeurbanne directeur@edchimie-lyon.fr                                                                                                                                           |

| E.E.A.    | ÉLECTRONIQUE, ÉLECTROTECHNIQUE, AUTOMATIQUE  https://edeea.universite-lyon.fr Sec.: Stéphanie CAUVIN Bâtiment Direction INSA Lyon Tél: 04.72.43.71.70 secretariat.edeea@insa-lyon.fr    | M. Philippe DELACHARTRE INSA LYON Laboratoire CREATIS Bâtiment Blaise Pascal, 7 avenue Jean Capelle 69621 Villeurbanne CEDEX Tél: 04.72.43.88.63 philippe.delachartre@insa-lyon.fr                                                                                                         |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME, MICROBIOLOGIE, MODÉLISATION  http://e2m2.universite-lyon.fr  Sec.: Sylvie ROBERJOT  Bât. Atrium, UCB Lyon 1  Tél: 04.72.44.83.62  secretariat.e2m2@univ-lyon1.fr | M. Philippe NORMAND Université Claude Bernard Lyon 1 UMR 5557 Lab. d'Ecologie Microbienne Bâtiment Mendel 43, boulevard du 11 Novembre 1918 69 622 Villeurbanne CEDEX philippe.normand@univ-lyon1.fr                                                                                       |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTÉ  http://ediss.universite-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 secretariat.ediss@univ-lyon1.fr                    | Mme Sylvie RICARD-BLUM Institut de Chimie et Biochimie Moléculaires et Supramoléculaires (ICBMS) - UMR 5246 CNRS - Université Lyon 1 Bâtiment Raulin - 2ème étage Nord 43 Boulevard du 11 novembre 1918 69622 Villeurbanne Cedex Tél: +33(0)4 72 44 82 32 sylvie.ricard-blum@univ-lyon1.fr |

| INFOMATHS | INFORMATIQUE ET MATHÉMATIQUES  http://edinfomaths.universite-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage Tél: 04.72.43.80.46 infomaths@univ-lyon1.fr                     | M. Hamamache KHEDDOUCI Université Claude Bernard Lyon 1 Bât. Nautibus 43, Boulevard du 11 novembre 1918 69 622 Villeurbanne Cedex France Tél: 04.72.44.83.69 hamamache.kheddouci@univ-lyon1.fr                                                                                             |

| Matériaux | MATÉRIAUX DE LYON  http://ed34.universite-lyon.fr Sec.: Yann DE ORDENANA Tél: 04.72.18.62.44 yann.de-ordenana@ec-lyon.fr                                                                | M. Stéphane BENAYOUN Ecole Centrale de Lyon Laboratoire LTDS 36 avenue Guy de Collongue 69134 Ecully CEDEX Tél: 04.72.18.64.37 stephane.benayoun@ec-lyon.fr                                                                                                                                |

| MEGA      | MÉCANIQUE, ÉNERGÉTIQUE, GÉNIE CIVIL, ACOUSTIQUE  http://edmega.universite-lyon.fr Sec.: Stéphanie CAUVIN Tél: 04.72.43.71.70 Bâtiment Direction INSA Lyon mega@insa-lyon.fr             | M. Jocelyn BONJOUR INSA Lyon Laboratoire CETHIL Bâtiment Sadi-Carnot 9, rue de la Physique 69621 Villeurbanne CEDEX jocelyn.bonjour@insa-lyon.fr                                                                                                                                           |

| ScSo      | ScSo* https://edsciencessociales.universite-lyon.fr Sec.: Mélina FAVETON INSA: J.Y. TOUSSAINT Tél: 04.78.69.77.79 melina.faveton@univ-lyon2.fr                                          | M. Christian MONTES Université Lumière Lyon 2 86 Rue Pasteur 69365 Lyon CEDEX 07 christian.montes@univ-lyon2.fr                                                                                                                                                                            |

\*ScSo : Histoire, Géographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

## **Acknowledgement**

This four-year journey as a PhD student was a special time of my life with enriching experiences. In the beginning, I didn't expect to do my PhD thesis abroad and to work with people who share different cultural backgrounds. But now I have spent four years in France, and it is the end of this unforgettable journey. When looking back on this period, I would like to express my gratitude to a lot of people. I could not have finished this thesis without their contribution.

First, I would like to express my sincere gratitude to my supervisors, Mustapha LEMITI and Alain FAVE. I appreciate that they have entrusted me with this thesis. Thanks to their knowledge and expertise, I have always learned something new from them and finally finished my thesis. I would also like to thank them for their kindness and help when I first arrived in France, which allowed me to adapt quickly to this new environment. I'm very grateful for their support, advice, and guidance during the last four years.

I would also like to express my gratitude to the jury members, Olivier PALAIS, Yvan CUMINAL, Anne KAMINSKI-CACHOPO, and Delfina MUNOZ for their constructive remarks and valuable suggestions to improve the quality of the manuscript.

What's more, I would like to acknowledge my collaborators in C2N (Centre de nanosciences et de nanotechnologies) and Marco VETTORI for their contribution to complete this work. I also want to thank the ANR (Agence Nationale de La Recherche) for the funding of this project and CSC (China Scholarship Council) for the scholarship.

Besides, I would like to express my appreciation to all the Photovoltaic team members and all the staff of the Nanolyon platform and INL administration.

I really appreciate the pleasant times spent with the PhD students in our lab, especially Nelly, Victor, Nicolas, Ali, Florian, Benoit, Jeremy, Alestair, and Huiru. They have helped me a lot in my work as well as my daily life. They are not only colleagues but also my cherished friends. Thanks to them, I have seen more possibilities in life and become more open-minded. I also want to thank all my other friends for relieving my stress and bringing joy to my life.

I would also like to thank my beloved Jean-Baptiste, who has always encouraged me when I was writing the manuscript and preparing my defense. He has helped me a lot to build my confidence.

Last but not least, I would like to thank my family for their love and support in my life. I

| am very grateful that they have always understood and respected my decisions at each period of my study. I feel very lucky to have them as my family. |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                       |  |  |  |

|                                                                                                                                                       |  |  |  |

|                                                                                                                                                       |  |  |  |

|                                                                                                                                                       |  |  |  |

|                                                                                                                                                       |  |  |  |

|                                                                                                                                                       |  |  |  |

|                                                                                                                                                       |  |  |  |

Abstract

2-terminal (2T) crystalline silicon (c-Si) based tandem solar cell is an approach to

overcome the Shockley-Queisser efficiency limit of single-junction solar cells. The objective of

this thesis is to fabricate a low-resistance c-Si tunnel junction and implement it as the

interconnection in 2T Si-based tandem solar cells. The proximity rapid thermal diffusion

technique is applied in this work to fabricate the Si tunnel junctions with a damage-free surface.

The fabrication and characterization of  $p^{++}/n^{++}$  tunnel junction on (111)-oriented Si wafer are

presented. Several parameters of the tunnel junction fabrication process are investigated. The

adjustment of the n<sup>++</sup> emitter by a two-step rapid thermal annealing has effectively facilitated

the fabrication of the p++/n++ tunnel junction. Si tunnel diodes have been fabricated to

characterize the electrical properties of tunnel junctions. The peak current density of the

tunnel diodes is within the range of 140-192 A/cm<sup>2</sup> with a peak to valley current ratio of 1.9-

3.2. Afterwards, the p<sup>++</sup>/n<sup>++</sup> tunnel junction was implemented in III-V nanowires/Si tandem

solar cells. Despite the defectuosity of the nanowires array, an increase of the open-circuit

voltage was observed in tandem solar cells in comparison with that of sole single-junction Si

solar cells. The fabricated tunnel junctions can be integrated with other top cell materials such

as perovskites and copper indium gallium selenide. The application of Si tunnel junctions

obtained by proximity rapid thermal diffusion will improve the development of competitive

high-efficiency c-Si based tandem solar cells.

**Keywords:** Si tunnel junction, proximity rapid thermal diffusion, tandem solar cell

iii

## Résumé

La cellule photovoltaïque tandem à base de silicium cristallin (c-Si) avec 2 terminaux (2T) est une solution permettant de dépasser la limite de Shockley-Queisser. L'objectif de ce travail de thèse est de réaliser une jonction tunnel en c-Si présentant une résistance faible afin de l'intégrer comme interconnexion des 2 sous-cellules constitutives de la tandem. La technique de diffusion thermique rapide par proximité est appliquée pour fabriquer les jonctions tunnel en silicium en minimisant les dommages causés à la surface du Silicium. La fabrication et la caractérisation de la jonction tunnel p++/n++ sur un substrat de silicium orienté (111) sont présentées. Plusieurs paramètres du processus de fabrication de la jonction tunnel sont étudiés. L'ajustement de l'émetteur n<sup>++</sup> par un recuit thermique rapide en deux étapes a effectivement facilité la réalisation de la jonction tunnel p<sup>++</sup>/n<sup>++</sup>. Des diodes tunnel en silicium ont été fabriquées pour caractériser les propriétés électriques des jonctions tunnel. Le pic de densité de courant des diodes tunnel se situe entre les valeurs 140 et 192 A/cm² avec un ratio de courant de pic à vallée de 1,9 à 3,2. Par la suite, cette jonction tunnel p<sup>++</sup>/n<sup>++</sup> a été intégrée dans des cellules photovoltaïques tandem nanofils III-V/Si. Malgré la défectuosité des réseaux de nanofils, une augmentation de la tension de circuit ouvert a été observée dans les cellules photovoltagues tandem par comparaison avec celle de la cellule solaire à simple jonction. Ce type de jonction tunnel peut également être intégré à d'autres types de cellules en dessus, par exemple les pérovskites ou le CIGS. L'application de jonctions tunnel en Si obtenues par la technique de diffusion thermique rapide à proximité pourrait faciliter le développement de cellules photovoltaïques tandem compétitives à haut rendement à base de c-Si.

**Mots-clés:** jonction tunnel en silicium, diffusion thermique rapide par proximité, cellule photovoltaïque tandem

## **Contents**

| Acknowledgement                                             | i                       |

|-------------------------------------------------------------|-------------------------|

| Abstract                                                    | ii                      |

| Résumé                                                      | iv                      |

| Contents                                                    | v                       |

| List of Abbreviations                                       | vii                     |

| Chapter 1 Introduction of photovoltaics and silicon-bas     | ed tandem solar cells 1 |

| 1.1 Photovoltaic cells                                      | 2                       |

| 1.1.1 Introduction of photovoltaic cells                    | 2                       |

| 1.1.1.1 Brief history of photovoltaic cells                 | 2                       |

| 1.1.1.2 State of the art of photovoltaic cells              | 2                       |

| 1.1.2 Physics of p-n junction solar cell                    | 3                       |

| 1.1.2.1 Solar radiation                                     | 3                       |

| 1.1.2.2 Carrier generation and recombination                | 5                       |

| 1.1.2.3 Working principle of p-n junction solar ce          | II6                     |

| 1.1.2.4 Characteristics of solar cell                       | 8                       |

| 1.1.2.5 Efficiency limit of single-junction solar ce        | l 12                    |

| 1.2 Si-based tandem solar cells                             | 14                      |

| 1.2.1 2T Si-based tandem solar cells                        | 16                      |

| 1.2.2 4T Si-based tandem solar cells                        | 18                      |

| 1.2.3 3T Si-based tandem solar cells                        | 19                      |

| 1.2.4 III-V nanowires/Si tandem solar cells                 | 20                      |

| 1.3 Tunnel junction                                         | 22                      |

| 1.3.1 Physics of tunnel junction                            | 23                      |

| 1.3.1.1 Quantum tunneling                                   | 23                      |

| 1.3.1.2 <i>I-V</i> characteristics of the tunnel junction . | 24                      |

| 1.4 Objective and outline of the thesis                     | 26                      |

| Chapter 2 Tools for fabrication and characterization of     | the tunnel junction28   |

| 2.1 Introduction                                            | 29                      |

| 2.2 Tunnel junction fabrication technique                   | 29                      |

| 2.2.1 Molecular beam epitaxy                                |                         |

| 2   | 2.2.2   | Che    | emical vapor deposition                                                                   | . 29 |

|-----|---------|--------|-------------------------------------------------------------------------------------------|------|

| 2   | 2.2.3   | Ion    | implantation                                                                              | . 31 |

| 2   | 2.2.4   | Rap    | oid thermal diffusion                                                                     | . 31 |

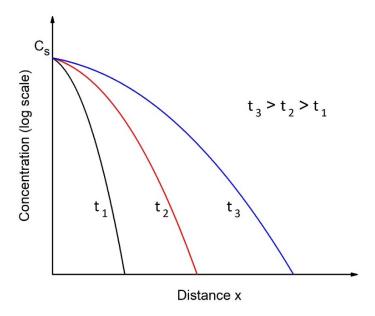

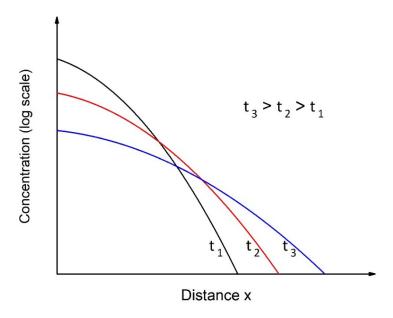

|     | 2.2.    | 4.1    | Diffusion theory                                                                          | . 32 |

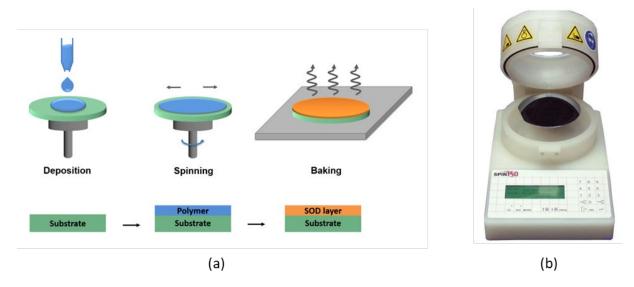

|     | 2.2.    | 4.2    | Spin-on doping                                                                            | . 37 |

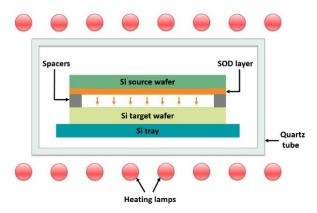

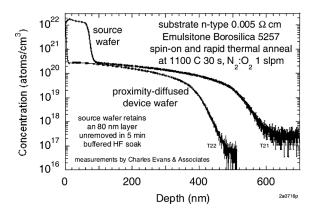

|     | 2.2.    | 4.3    | Proximity rapid thermal diffusion                                                         | . 38 |

| 2.3 | Char    | racte  | rization methods of the tunnel junction                                                   | . 40 |

| 2   | 2.3.1   | Dop    | oing profile characterization                                                             | . 40 |

|     | 2.3.    | 1.1    | Secondary ion mass spectrometry                                                           | . 40 |

|     | 2.3.    | 1.2    | Electrochemical capacitance-voltage profiler                                              | . 41 |

| 2   | 2.3.2   | I-V    | characterization                                                                          | . 44 |

| 2.4 | Cond    | clusio | on                                                                                        | . 45 |

| Cha | apter 3 | Fak    | prication and characterization of the Si p <sup>++</sup> /n <sup>++</sup> tunnel junction | 46   |

| 3.1 | Intro   | oduc   | tion                                                                                      | . 47 |

| 3.2 | Stud    | ly of  | parameters influencing tunnel junction fabrication process                                | . 47 |

| 3   | 3.2.1   | For    | mation of the n <sup>++</sup> emitter                                                     | . 47 |

| 3   | 3.2.2   | Adj    | ustment of n <sup>++</sup> emitter                                                        | . 51 |

|     | 3.2.    | 2.1    | RIE etching                                                                               | . 51 |

|     | 3.2.    | 2.2    | Two-step RTA in air and N <sub>2</sub>                                                    | . 55 |

| 3   | 3.2.3   | RTA    | temperature and time of B diffusion process                                               | . 59 |

| 3   | 3.2.4   | Cle    | aning process                                                                             | . 65 |

| 3   | 3.2.5   | Spi    | n-on speed to make B source wafer                                                         | . 69 |

| 3   | 3.2.6   | Opt    | timized fabrication process                                                               | . 70 |

| 3.3 | I-V c   | hara   | cterization of the tunnel junction                                                        | . 71 |

| 3   | 3.3.1   | Fab    | rication and characterization of tunnel diodes with vertical tunnel junction.             | . 71 |

|     | 3.3.    | 1.1    | Configuration and fabrication process                                                     | . 72 |

|     | 3.3.    | 1.2    | J-V characterization                                                                      | . 73 |

| 3   | 3.3.2   | Fab    | rication and characterization of Si tunnel diodes with lateral tunnel junction            | 75 ا |

|     | 3.3.    | 2.1    | Fabrication process                                                                       | . 75 |

|     | 3.3.    | 2.2    | J-V characterization                                                                      | . 78 |

| 3   | 3.3.3   | Opt    | timization of Al/Si contact                                                               | . 80 |

| 3.4 | Cond    | clusio | on                                                                                        | . 87 |

| Chap   | oter 4                       | Implementation of    | tunnel junction in solar cells 88               |

|--------|------------------------------|----------------------|-------------------------------------------------|

| 4.1    | Intro                        | luction              | 89                                              |

| 4.2    | Fabri                        | ation and characte   | rization of Si solar cells89                    |

| 4.2    | 2.1                          | Fabrication process  | of Si solar cells89                             |

| 4.2    | 2.2                          | Characterization of  | Si solar cells91                                |

|        | 4.2.2                        | .1 J-V and efficier  | cy characteristics91                            |

|        | 4.2.2                        | .2 External quant    | um efficiency92                                 |

| 4.2    | 2.3                          | Optimization of Si s | olar cell with tunnel junction on the surface93 |

| 4.3    | Fabri                        | cation and characte  | rization of NWs/Si tandem solar cell96          |

| 4.3    | 3.1                          | Introduction of NW   | s/Si TSC fabrication process96                  |

| 4.3    | 3.2                          | Development of NV    | Vs/Si tandem solar cell fabrication process99   |

|        | 4.3.2                        | .1 Encapsulation     | of NWs99                                        |

|        | 4.3.2                        | .2 Etching of poly   | mer106                                          |

|        | 4.3.2                        | .3 ITO contact de    | oosition111                                     |

|        | 4.3.2                        | .4 Realization of I  | NWs/Si tandem solar cell116                     |

| 4.3    | 3.3                          | J-V characterization | of NWs/Si tandem solar cell                     |

| 4.4    | Conc                         | usion                |                                                 |

| Cond   | lusion                       | and perspectives     | 122                                             |

| Conc   | lusion                       |                      |                                                 |

| Pers   | pective                      | s                    |                                                 |

| Bibli  | ograpl                       | у                    | 125                                             |

| Appe   | endix .                      |                      | 138                                             |

| Reac   | Reactive Ion Etching (RIE)13 |                      |                                                 |

| List o | of pub                       | ications             | 140                                             |

## **List of Abbreviations**

| Abbreviation | Description                               |

|--------------|-------------------------------------------|

| a-Si         | amorphous silicon                         |

| AM           | airmass                                   |

| BCB          | benzocyclobutene                          |

| CIGS         | copper indium gallium selenide            |

| CVD          | chemical vapor deposition                 |

| EQE          | external quantum efficiency               |

| HF           | hydrofluoric acid                         |

| HSQ          | hydrogen silsesquioxane                   |

| IBC          | interdigitated back contact               |

| IQE          | internal quantum efficiency               |

| ITO          | indium tin oxide                          |

| LPCVD        | low pressure chemical vapor deposition    |

| LYDOP        | Leaktight Yield Doping                    |

| MBE          | molecular beam epitaxy                    |

| MOCVD        | metal-organic chemical vapor deposition   |

| mono-Si      | monocrystalline silicon                   |

| NW           | nanowire                                  |

| PECVD        | plasma-enhanced chemical vapor deposition |

| PERC         | Passivated Emitter and Rear Cell          |

| poly-Si      | polycrystalline silicon                   |

| PRTD         | proximity rapid thermal diffusion         |

| RIE          | reactive ion etching                      |

| rpm          | revolutions per minute                    |

| RTA          | rapid thermal annealing                   |

| RTD          | rapid thermal diffusion                   |

| SA           | selective area                            |

| SHJ          | silicon heterojunction                    |

| SMU          | source measure unit                       |

|              |                                           |

#### List of Abbreviations

SQ limit Shockley-Queisser limit

TCA transparent conductive adhesives

TCO transparent conductive oxides

TLM transfer length method

VLS vapor-liquid-solid

μc-Si microcrystalline silicon

# Chapter 1 Introduction of photovoltaics and silicon-based tandem solar cells

| 1.1 | Photo | ovolt | taic cells                                        | 2    |

|-----|-------|-------|---------------------------------------------------|------|

| 1.3 | 1.1   | Intr  | oduction of photovoltaic cells                    | 2    |

|     | 1.1.1 | l.1   | Brief history of photovoltaic cells               | 2    |

|     | 1.1.1 | 1.2   | State of the art of photovoltaic cells            | 2    |

| 1.3 | 1.2   | Phy   | sics of p-n junction solar cell                   | 3    |

|     | 1.1.2 | 2.1   | Solar radiation                                   | 3    |

|     | 1.1.2 | 2.2   | Carrier generation and recombination              | 5    |

|     | 1.1.2 | 2.3   | Working principle of p-n junction solar cell      | 6    |

|     | 1.1.2 | 2.4   | Characteristics of solar cell                     | 8    |

|     | 1.1.2 | 2.5   | Efficiency limit of single-junction solar cell    | . 12 |

| 1.2 | Si-ba | sed t | tandem solar cells                                | . 14 |

| 1.2 | 2.1   | 2T S  | Si-based tandem solar cells                       | . 16 |

| 1.2 | 2.2   | 4T S  | Si-based tandem solar cells                       | . 18 |

| 1.2 | 2.3   | 3T S  | Si-based tandem solar cells                       | . 19 |

| 1.2 | 2.4   | III-V | nanowires/Si tandem solar cells                   | . 20 |

| 1.3 | Tunn  | el ju | nction                                            | . 22 |

| 1.3 | 3.1   | Phy   | sics of tunnel junction                           | . 23 |

|     | 1.3.1 | l.1   | Quantum tunneling                                 | . 23 |

|     | 1.3.1 | 1.2   | <i>I-V</i> characteristics of the tunnel junction | . 24 |

| 1.4 | Obje  | ctive | and outline of the thesis                         | . 26 |

|     |       |       |                                                   |      |

#### 1.1 Photovoltaic cells

#### 1.1.1 Introduction of photovoltaic cells

#### 1.1.1.1 Brief history of photovoltaic cells

The photovoltaic effect was first discovered by the French physicist Alexandre Edmond Becquerel in 1839 [1]. He placed two coated platinum electrodes in an electrolyte solution and found that voltage and current were generated once the electrodes were illuminated. In 1877, Englishmen William Adams and Richard Day demonstrated that it was possible to generate current in semiconductor selenium merely by light [2]. This led to the first thin-film selenium solar module fabricated by an American inventor Charles Edgar Fritts in 1883 [3].

The first p-n junction silicon solar cell with an efficiency of up to 6% was invented in 1954 [4]. In the following years, the efficiency was raised to 10%. Gallium arsenide (GaAs) and other alternative materials for solar cells were also presented apart from silicon. But the solar modules were only used for specific applications such as spacecraft because of the high cost until the early 1970s. Driven by the oil crisis in the 1970s, the public interest in solar cells for terrestrial application increased in that decade. Many companies started to develop photovoltaic modules and systems for terrestrial applications [5].

#### 1.1.1.2 State of the art of photovoltaic cells

Nowadays, plenty of solar cells have been invented. The most two common types are crystalline solar cells and thin-film solar cells.

Crystalline solar cells are the most widespread application in the photovoltaic field. They are wafer cells made from crystalline silicon or III-V semiconductors. Several technologies were developed for producing higher efficiency crystalline silicon solar cells, such as PERC (Passivated Emitter and Rear cell), IBC (interdigitated back contact) solar cell, and SHJ (silicon heterojunction) solar cell. Crystalline silicon is either monocrystalline silicon (mono-Si) or polycrystalline silicon (poly-Si). The reported efficiency record for a mono-Si solar cell is now 25%, obtained with a PERC solar cell [6]. The highest efficiency of the mc-Si solar cell is 24.4%, lower than mono-Si [7]. But the cost of mc-Si solar cells is normally less than that of the mono-Si solar cells. Thanks to the abundance of silicon element and mature fabrication technologies, Si-based solar cell has been commercialized and dominant in the photovoltaic field till now. III-

V semiconductor wafers can also be used to fabricate solar cells with high efficiency. They are mainly employed for space applications and concentrator photovoltaics due to the high cost of materials [5].

Thin-film solar cells are made from films that are much thinner than wafers, thus requiring a little amount of material, due to higher absorption coefficient, and processed at a lower temperature than c-Si. In contrast to wafer-based solar cells, thin-film solar cells need a carrier to give them mechanical stability. Glass, stainless steel, or polymer foils are usually used as carrier materials, indicating that it is possible to produce flexible thin-film solar cells. In addition to being used in the wafer cells, silicon and III-V semiconductor materials can also be deposited to make thin-film solar cells. Silicon is used in two forms, amorphous silicon (a-Si) and microcrystalline silicon (µc-Si). Chalcogenide solar cells are another kind of thin-film solar cell, with CIGS (copper indium gallium selenide) and CdTe (cadmium telluride) solar cells as typical. The efficiency of the CIGS solar cell can reach 23.35% at present [8]. Besides the inorganic solar cells, organic solar cells and hybrid organic-inorganic solar cells are also researched. Perovskite solar cells and dye-sensitized solar cells are two typical hybrid organicinorganic solar cells that attract a lot of attention. So far, the highest efficiency of perovskite solar cells is 22.6%, while that of dye-sensitized solar cells is 11.9% [9], [10]. Thin-film solar cells were expected to become much cheaper than wafer-based solar cells. However, due to the current price decline in silicon wafers, thin-film solar cells are not yet comparable to crystalline solar cells in commercial use.

In addition to the crystalline and thin-film solar cells, many advanced emerging technologies have appeared to fabricate high-efficiency solar cells that can overcome the efficiency limit for single-junction solar cells. These technologies include multijunction solar cells, concentrator photovoltaics, quantum dots solar cells, intermediate band solar cells, spectral up and down-conversion, multi-exciton generation, and hot carrier solar cells. Most of them are still in the fundamental research phase and it will take time to be implemented in PV modules. However, tandem cells, especially c-Si based tandem cells, are expected to be mass produced around 2023 [11].

#### 1.1.2 Physics of p-n junction solar cell

#### 1.1.2.1 Solar radiation

Solar radiation is the basis of photovoltaic cells. The sun is a gigantic nuclear fusion

reactor where hydrogen atoms are converted to helium atoms and generates tremendous energy. The temperature at the core of the sun is about 15 million degrees Celsius. The generated energy is released into space in the form of radiation. The total power of the radiation is about  $3.8 \times 10^{26}\,\mathrm{W}$ . Only a small fraction of the radiation,  $1.7 \times 10^{18}\,\mathrm{W}$ , reaches the earth [5]. The received power density or irradiance on the earth is calculated to be  $1357\,\mathrm{W/m^2}$ , named as the solar constant. It is the irradiance outside the earth's atmosphere. The carrier of radiant solar energy is the photon. Solar cells absorb photons of appropriate energy and convert them into electrical energy. Therefore, it is important to know the spectral distribution of solar radiation.

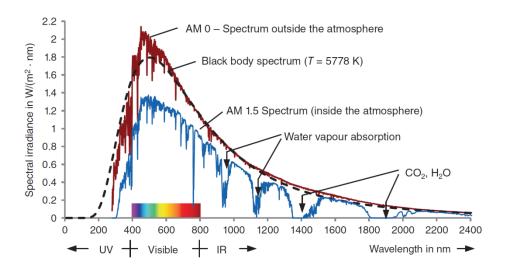

According to Planck's law of radiation, the surface temperature determines the spectrum of the radiation. The surface temperature of the sun is 5778 K and thus leads to the idealized black-body radiation spectrum shown in Figure 1.1. The solar spectrum measured outside the earth's atmosphere is approximate to the idealized line. AMO stands for the Air Mass 0, meaning that the sunlight has not passed through the atmosphere. The Air Mass coefficient is the ratio of the path length of sunlight when passing through the atmosphere to the shortest path length of the sunlight when the sun is at the zenith. It is given as:

$$AM = \frac{L}{L_0} = \frac{1}{\cos \theta} \tag{1.1}$$

with L is the actual path length of the sunlight,  $L_0$  is the shortest path length of the sunlight,  $\theta$  is the zenith angle.

Due to the reflection, absorption, and scattering, the solar irradiance is reduced after passing through the atmosphere. The real solar spectrum changes with the path length of the sunlight. The Air Mass coefficient characterizes the effect of path length on the reduction of solar irradiance. Therefore, the spectrum outside the atmosphere is designated by AMO. When the sun is at its zenith, the spectrum is called AM1. The standard spectrum for characterizing terrestrial solar cells is AM1.5 when the zenith angle is 48°.

Figure 1.1 Spectrum outside and inside the atmosphere [12].

#### 1.1.2.2 Carrier generation and recombination

When a semiconductor is illuminated, it absorbs the photons with energy equal to or greater than its bandgap. As a result, electrons from the valence band are excited to the conduction band and corresponding holes are produced in the valence band. This process is the generation of electron-hole pairs. In the doped semiconductors, the absorption of photons increases the number of both majority and minority carriers. The number of light-generated carriers is less than the number of existing majority carriers due to doping. Oppositely, the amount of the light-generated carriers is more than the existing minority carriers. Therefore, the light-generated carriers significantly impact the minority carriers.

Recombination is an unavoidable process in the semiconductor that is reverse to the generation. Electrons and holes are annihilated in this process. Generally, there are three types of recombination, radiative recombination, trap-assisted recombination, and Auger recombination.

Figure 1.2 Recombination mechanisms in semiconductors: (a) radiative recombination, (b) trapassisted recombination, and (c) Auger recombination.

Radiative recombination, also known as band-to-band recombination, is a spontaneous transition process in which an electron from the conduction band migrates to an unoccupied state in the valence band and releases a photon. It is the dominant recombination process in direct bandgap semiconductors.

Trap-assisted recombination is usually called Shockley-Read-Hall recombination or SRH recombination. It is a non-radiative process facilitated by impurities or lattice defects. These recombination centers introduce allowed energy levels called trap states within the forbidden gap. An electron can be trapped at this kind of state and consequently recombines with a hole that is attracted by the trapped electron. It is a non-radiative process and the excess energy is dissipated into the lattice in the form of heat. Trap-assisted recombination at the surface of a semiconductor is known as surface recombination. The dangling bonds caused by the discontinuation of the crystal lattice promote recombination. In solar cells, surface passivation can reduce the dangling bonds, thereby reducing the surface recombination.

Auger recombination is also a non-radiative recombination mechanism. It is a three particles process. The energy and momentum of the recombining electron and hole are transferred to a third carrier, rather than emitting the energy as heat or as a photon. Then the third carrier losses its excess energy in the form of heat. Auger recombination dominates in silicon and other indirect bandgap materials.

The generation and recombination of electron-hole pairs are crucial to the conversion efficiency of solar cells. Various technologies have been developed to enhance the carrier generation as well as weaken the carrier recombination to increase efficiency.

## 1.1.2.3 Working principle of p-n junction solar cell

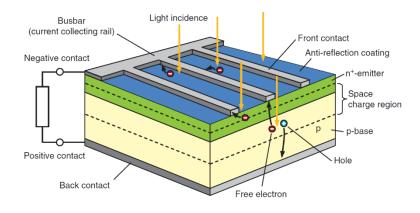

Figure 1.3 Configuration of a typical silicon solar cell [12].

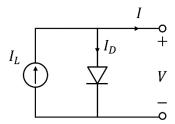

The configuration of a conventional p-n junction solar cell is shown in Figure 1.3. It basically consists of a p-n junction diode. When the solar cell is illuminated, penetrating photons with energy equal to or greater than the bandgap are absorbed and generate free electron-hole pairs. The generated electrons and holes in the depletion region are immediately separated by the built-in electric field [13]. Then electrons migrate to the n-side and holes migrate to the p-side, causing a current flowing from n-side to p-side in the depletion region. This current is called photocurrent  $I_L$ . As a result, the potential on the n-side decreases and the potential on the p-side increases. Thus, a potential difference appears, and this phenomenon is called the photovoltaic effect. An ideal solar cell can be modeled by a current source  $I_L$  in parallel with a passive diode [12]. If the solar cell is connected to the load, a current will flow through the load due to the existence of potential difference.

Figure 1.4 Equivalent circuit of an ideal solar cell.

Not all the light-generated electron-hole pairs contribute to the photocurrent. The photocurrent is determined by the migration of minority carriers in the depletion region. Most of the minority carriers generated in the electrical neutral region recombine before reaching the depletion region. Only a portion of them generated within the diffusion length can diffuse to the depletion before recombining and swept by the electric field to their respective majority carrier side of the junction. Generally, the diffusion length of electrons in the p-type semiconductor is higher than that of holes in the n-type with the same doping concentration. Hence, the electrons can be collected more effectively than holes outside the depletion region.

Besides, the amount of the photocurrent depends on the number of photons that are absorbed by the solar cell. The penetration depth of the photons in the solar cell should also be considered. Therefore, the p-n junction of the solar cell is normally asymmetrically doped, containing a thin highly doped n-type emitter on the illuminated side and a moderately p-type doped base on the rare side.

#### 1.1.2.4 Characteristics of solar cell

#### 1.1.2.4.1 I-V characteristics

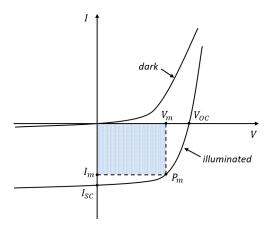

When the solar cell is connected to the external load, the relation curve between the current through the load and the voltage across the load is the current-voltage (*I-V*) characteristic of the solar cell (Figure 1.5).

Figure 1.5 Current-voltage characteristics curves of a solar cell in the dark and illumination conditions.

In the dark condition, there is no photocurrent generated and the solar cell behaves like a normal p-n junction diode. Its behavior follows the Shockley equation when a voltage U is applied,

$$I_{dark} = I_s \left[ \exp\left(\frac{qU}{nk_0T}\right) - 1 \right]. \tag{1.2}$$

Here  $I_s = Aq(\frac{D_n n_{p0}}{L_n} + \frac{D_p p_{n0}}{L_p})$ , represents the reverse saturation current. A is the solar cell area,  $D_n$  and  $D_p$  are diffusion coefficient of the electron, hole respectively,  $L_n$  and  $L_p$  are diffusion length of the electron, hole respectively,  $n_{p0}$  is the electron concentration in a p-type material at thermodynamic equilibrium,  $p_{n0}$  is the hole concentration in an n-type material at thermodynamic equilibrium, n is the ideality factor of the diode and it equals to 1 for ideal diodes.

When the solar cell is under illumination, the output voltage V causes a current  $I_D$  flow through the diode, which is given by

$$I_D = I_s \left[ \exp\left(\frac{qV}{k_0 T}\right) - 1 \right]. \tag{1.3}$$

The direction of  $I_D$  is opposite to the direction of  $I_L$ . Therefore, the output current is

$$I = I_L - I_D = I_L - I_s \left[ \exp\left(\frac{qV}{k_0 T}\right) - 1 \right].$$

(1.4)

#### (1) Short-circuit current $I_{sc}$

When the solar cell is short-circuited at its connections, the output current is the short-circuit current  $I_{sc}$ .  $I_D=0$  in this condition, thus

$$I_{sc} = I_L. (1.5)$$

It means that the short-circuit current  $I_{sc}$  is equal to the photocurrent  $I_L$  in an ideal solar cell. The short-circuit current strongly depends on the optical properties of the solar cell, such as the absorption and reflection of sunlight.

#### (2) Open-circuit voltage $V_{oc}$

According to the equation Eq. (1.4), the output voltage V is calculated as

$$V = \frac{k_0 T}{q} \ln \left( \frac{I_L - I}{I_S} + 1 \right). \tag{1.6}$$

The open-circuit voltage  $V_{oc}$  is the output voltage when the load is infinite. In this case, I=0, so that

$$V_{oc} = \frac{k_0 T}{q} \ln \left( \frac{I_L}{I_s} + 1 \right) = \frac{k_0 T}{q} \ln \left( \frac{I_{sc}}{I_s} + 1 \right). \tag{1.7}$$

$V_{oc}$  is the maximum output voltage of an ideal solar cell. It mainly depends on the reverse saturation current and photocurrent. Since the reverse saturation current is determined by the recombination,  $V_{oc}$  reflects the amount of recombination in the solar cell.

#### (3) Maximum output power $P_m$

The output power *P* of a solar cell is the product of output voltage and output current, varying with the load:

$$P = V \cdot I = VI_L - VI_s \left[ \exp\left(\frac{qV}{k_0 T}\right) - 1 \right]. \tag{1.8}$$

When the load changes, there is a point that makes the output power is maximum,

$$P_m = V_m \cdot I_m. \tag{1.9}$$

This point is called maximum power point. It is the optimal operating point of a solar cell. The corresponding  $V_m$  and  $I_m$  are respectively called maximum power point voltage and maximum

power point current.

#### (4) Fill factor FF

The fill factor FF is the ratio of the maximum output power to the product of  $V_{oc}$  and  $I_{sc}$  when the solar cell works under the optimal operating condition:

$$FF = \frac{P_m}{V_{oc} \cdot I_{sc}} = \frac{V_m \cdot I_m}{V_{oc} \cdot I_{sc}}.$$

(1.10)

It is an important parameter that reveals the quality of a solar cell. Typical values for efficient silicon solar cells are between 0.75 and 0.85 [12].

#### (5) Conversion efficiency $\eta$

The conversion efficiency  $\eta$  describes the proportion of the incident optical energy that can be converted into electrical energy. It is given by

$$\eta = \frac{P_m}{P_{in}} = \frac{FF \cdot V_{oc} \cdot I_{sc}}{P_{in}} \tag{1.11}$$

where  $P_{in}$  is the incident power. It is often used to compare the performance of one solar cell with another. Considering that it is relevant to the incident light, the measurement conditions should be carefully controlled.

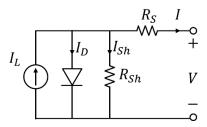

In reality, no solar cell is ideal so that the series resistance  $R_S$ , shunt resistance  $R_{Sh}$  and ideality factor n should also be considered. The equivalent circuit of a standard solar cell is shown in Figure 1.6.

Figure 1.6 Equivalent circuit of a standard solar cell.

The series resistance  $R_S$  consists of the resistance of the semiconductor material, contact resistance at the metal-semiconductor interface, and the resistance of the metal contacts. It leads to the reduction of the output voltage V. The current flows through the diode  $I_D$  is shown as:

$$I_D = I_s \left[ \exp\left(\frac{q(V + I \cdot R_S)}{k_0 T}\right) - 1 \right]. \tag{1.12}$$

The shunt resistance  $R_{Sh}$  is caused by the leak current. Generally, the leak current contains the leak current at the edge of the solar cell as well as the internal leak current caused by crystal defects and impurities in the p-n junction. Low  $R_{Sh}$  provides an alternative path for the photocurrent:

$$I_{Sh} = \frac{V + I \cdot R_S}{R_{Sh}}. ag{1.13}$$

The ideality factor n shows how much the properties of a diode resemble the ideal diode properties. For an ideal solar cell n=1, but for real solar cells, n varies from 1 to 2. Hence,

$$I_D = I_s \left[ \exp\left(\frac{q(V + I \cdot R_S)}{nk_0T}\right) - 1 \right]. \tag{1.14}$$

As a consequence, the current-voltage characteristics of the solar cell is modified as

$$I = I_L - I_S \left[ \exp\left(\frac{q(V + I \cdot R_S)}{nk_0 T}\right) - 1 \right] - \frac{V + I \cdot R_S}{R_{Sh}}.$$

(1.15)

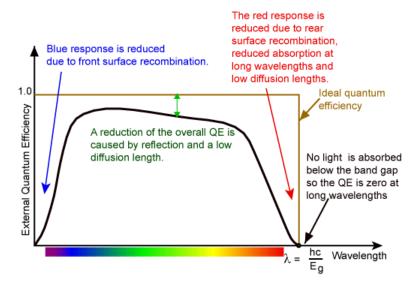

#### 1.1.2.4.2 Quantum efficiency

The Quantum efficiency of the solar cell indicates the amount of electron-hole pairs produced by incident photons with a certain wavelength. It reflects the contribution of photons with different energies to the short circuit current. There are two types of quantum efficiency: external quantum efficiency and internal quantum efficiency.

External quantum efficiency (EQE) is the ratio of the number of electron-hole pairs usable for the photocurrent to the number of incident photons with a certain wavelength.

$$EQE = \frac{I_{sc}(\lambda)}{q\phi(\lambda)},$$

(1.16)

where q is the elementary charge and  $\phi(\lambda)$  is the incident photon flow with wavelength  $\lambda$ .

Figure 1.7 External quantum efficiency of a silicon solar cell [14].

Internal quantum efficiency (IQE) is the ratio of the number of usable electron-hole pairs to the number of absorbed photons with a certain wavelength. In this case, the losses caused by reflection and transmission are considered. IQE is given by

$$IQE = \frac{EQE}{1 - reflection - transmission}.$$

(1.17)

## 1.1.2.5 Efficiency limit of single-junction solar cell

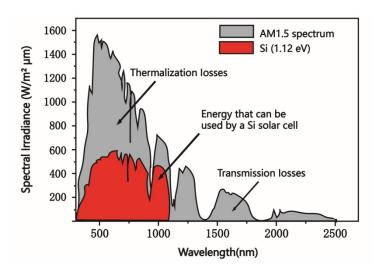

The conversion efficiency of single-junction solar cells can never reach 100% due to many factors. There are three principal loss processes in the single-junction solar cell: transmission losses, thermalization losses, and radiative recombination.

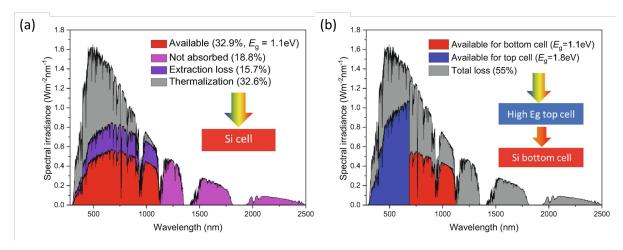

Transmission losses and thermalization losses are caused by the spectral mismatch between the energy distribution of photons in the solar spectrum and the bandgap of the semiconductor material. Photons with energy lower than the bandgap cannot be absorbed, thus no electron-hole pairs are generated by this portion of the solar spectrum. Photons with energy greater than the bandgap can generate electron-hole pairs and the excess energy is released to crystal lattice in the thermalization process. Figure 1.8 shows the losses due to spectral mismatch in an ideal Si solar cell. Thermalization losses and transmission losses can be avoided by emerging high-efficiency solar cells approaches, such as multijunction solar cells, intermediate solar cells, multi-exciton generation, and so on. Losses due to radiative recombination are fundamental and cannot be avoided.

Figure 1.8 Spectral losses in an ideal crystalline Si solar cell [15].

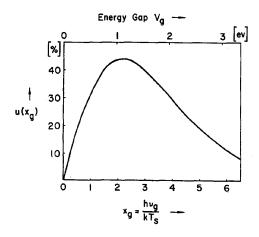

The ultimate theoretical efficiency limit of single-junction solar cells was calculated by Shockley and Queisser in 1961 [16]. They proposed a detailed balance limit based on several assumptions. First, all photons with energy greater than the bandgap are absorbed; each of them produces an electron-hole pair. Second, the mobility of carriers is infinite in the material, such that the separation of the quasi-Fermi levels throughout the entire device is equal. Third, there is no other loss mechanism in the solar cell except for the radiative recombination. Fourth, the sun and the solar cell are assumed to be blackbodies with a temperature of 6000 K and 300 K respectively. Besides, the solar cell is illuminated by non-concentrated sunlight. As a consequence, the dependence of the ultimate efficiency upon the bandgap of the semiconductor is demonstrated (as shown in Figure 1.9).

Figure 1.9 Dependence of the ultimate efficiency  $u(x_g)$  upon the bandgap  $V_g$  of the semiconductor [15].

The detailed balance limit is also known as the Shockley-Queisser limit or SQ limit. According to the SQ limit, the ultimate efficiency of single-junction Si ( $V_g$  = 1.12 eV) solar cell

is approximate 32%. However, the SQ limit is based on the assumption that only radiative recombination exists in the solar cell, which is not suitable for Si solar cells. Silicon is an indirect bandgap semiconductor where non-radiative Auger recombination is dominant. Taking this constraint into account, the theoretical efficiency limit of a single-junction Si solar cell is calculated as 29.4% [17].

#### 1.2 Si-based tandem solar cells

Up to now, the highest efficiency of the single-junction Si solar cell is 26.7%, approaching the SQ limit [18]. This result is obtained in an amorphous silicon/crystalline silicon heterojunction solar cell with interdigitated back contacts. The multijunction solar cell is a viable pathway to overcome the limit by stacking materials with different bandgaps together. The top cell and the bottom cell absorb different portions of the solar spectrum, thus reducing the thermalization losses, as shown in Figure 1.10 (b).

Figure 1.10 Losses and maximum available solar energy of (a) a silicon single-junction solar cell and (b) a Si-based tandem solar cell, illustrated in the AM1.5G solar spectrum [19].

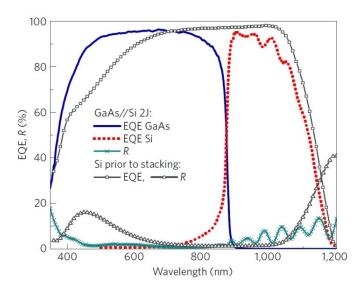

For instance, in the GaAs/Si tandem solar cell, GaAs mainly absorbs visible spectrum while Si mostly absorbs near-infrared spectrum. Consequently, the total EQE is increased, as shown in Figure 1.11. The dual-junction (2J) solar cell is the simplest multijunction structure. It is attractive due to the great efficiency gain and the lowest incremental fabrication cost over single-junction devices compared with other multijunction solar cells [21].

Figure 1.11 EQE and reflection curves of GaAs/Si dual-junction solar cell and the used Si heterojunction solar cell before stacking [20].

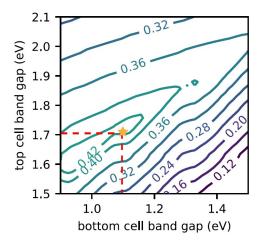

When designing high-performance tandem solar cells, the choice of bandgaps is crucial. The optimal bandgap combination of the 2J solar cell is around 1.62 eV and 0.91 eV, giving a limiting efficiency of 42.8% [22]. For 2J Si-based tandem solar cells, the maximum efficiency is around 42.4% with a 1.72 eV top cell. III-V compound semiconductor, perovskite, and chalcogenide are good candidates for top cells due to the wide range of bandgap energies.

Figure 1.12 Efficiency contours of 2J tandem solar cells against the bandgaps of top and bottom cells [22].

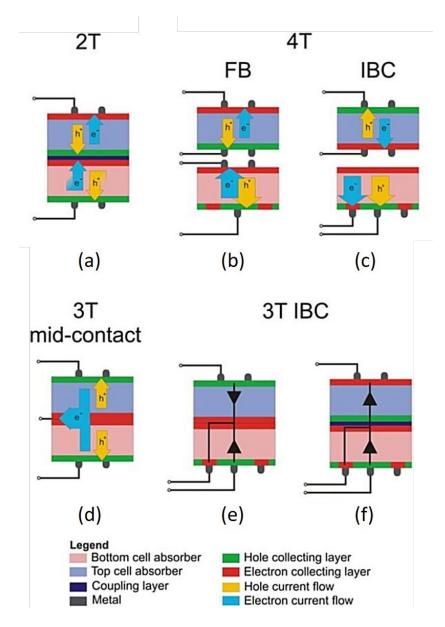

Generally, Si-based tandem solar cells are known as four-terminal (4T), two-terminal (2T), and three-terminal (3T) depending on the configuration, as shown in Figure 1.13. The details of these three kinds of Si-based tandem solar cells are described as follows.

Figure 1.13 Different internal interconnection schemes for 2J solar cells: (a) series-connected 2T tandem cell; Independently operating 4T tandem cells using (b) front-back (FB) contacted and (c) IBC bottom cells; 3T tandem cell with (d) mid-contact, (e) IBC bottom cell within a bipolar junction transistor, and (f) IBC bottom cell with a tunnel junction. Blue and yellow arrows indicate the current pathways of electrons and holes, while the thickness of the arrows qualitatively illustrates the respective current densities. Black equivalent circuit models in (e) and (f) highlight the arrangement of cell diodes [23].

#### 1.2.1 2T Si-based tandem solar cells

In 2T Si-based tandem solar cells, the two subcells are connected in series by an interconnection. A significant benefit of the 2T device is that it has only two terminals and can be operated as a standard single-junction solar cell, thus greatly simplifies its integration in PV modules and systems. In addition, there is no intermediate electrode as in 4T devices, thereby reducing the series resistance and parasitic absorption. Generally, 2T Si-based tandem solar

cells can be fabricated by direct growth or wafer bonding.

When directly growing tandem solar cells, an interconnection such as tunnel junctions or recombination layers are typically used to electrically connect the subcells [24]-[32]. Epitaxial growth of top cells on Si substrates is a straightforward approach that has been attractive for decades [33]-[41]. The benefit of direct epitaxial growth is that only one substrate and one epitaxial process are needed, thus reducing the manufacturing cost and complexity. When III-V materials are used as the top cell, the lattice mismatch between them and Si has always been a challenge. Therefore, the graded buffer layers grown by the metamorphic epitaxy have been widely used to transfer the lattice constants of silicon to that of III-V materials [36]-[41]. Monolithically epitaxial grown GaAs<sub>0.75</sub>P<sub>0.25</sub>/Si 2J solar cell with an efficiency of 23.4 ± 0.3% was demonstrated by Lepkowski, D. L. *et al.* [42]. The GaAs<sub>0.75</sub>P<sub>0.25</sub> top cell and Si bottom cell are connected by p<sup>++</sup>/n<sup>++</sup>-GaAs<sub>0.75</sub>P<sub>0.25</sub> tunnel junction and step-graded GaAs<sub>v</sub>P<sub>1-y</sub> buffer layer grown by metal-organic chemical vapor deposition (MOCVD). 25.0% efficient GaAs<sub>0.75</sub>P<sub>0.25</sub>/Si 2J solar cell grown by molecular beam epitaxy (MBE) was reported by Fan, S. *et al.* [41]. They improved the performance of the tandem cell by utilizing an AlGaAsP back surface field (BSF) layer and a backside textured Si bottom cell.

The recombination layers used in the monolithic tandem solar cells can be metal interconnects, transparent conductive adhesives (TCAs), or nanocrystalline silicon recombination junctions [27]-[32]. Monolithic perovskite/silicon tandem with a certified power conversion efficiency of 29.15% was reported by Al-Ashouri, A. *et al.*, exceeding the efficiency world record for a single-junction Si solar cell [43]. They used a self-assembled monolayer that provides both fast extraction and efficient passivation at the hole-selective interface as the interconnection. Soon after this, Oxford PV announced that they have fabricated a monolithic 2T perovskite/Si tandem solar cell with a certified efficiency of 29.52% [44].

When connecting subcells by wafer bonding, the lattice mismatch problem during the epitaxy growth process can be bypassed. For example, III-V top cells with good crystal quality can be grown on lattice-matched GaAs or Ge substrates and then transferred to Si bottom cell. The GaAs or Ge substrates are subsequently removed. Because the top cells are grown before bonding, there is no temperature limitation associated with the bottom cell. Al<sub>0.1</sub>Ga<sub>0.9</sub>As/Si 2J solar cell with an efficiency of 25.2% measured under a 600 nm-peaked halogen white light source of a one-sun intensity was reported [45]. Al<sub>0.1</sub>Ga<sub>0.9</sub>As top cell was grown on a GaAs

substrate by MBE and layer-transferred onto a Si bottom cell through the  $p^+$ -GaAs/ $n^+$ -Si direct fusion bonding at 300 °C and subsequent removal of the GaAs substrate. Another 2J III-V/Si solar cell fabricated by Surface-Activated direct wafer Bonding (SAB) was reported in 2019, with an efficiency of 21.1  $\pm$  1.5% at one-sun condition [46]. In their work, the III-V top cell is a heterojunction formed by an n-Ga<sub>0.5</sub>In<sub>0.5</sub>P emitter and a p-Al<sub>0.2</sub>Ga<sub>0.8</sub>As base.

One of the challenges for the wafer bonding method is the reuse of the high-cost epitaxial substrates for the top cells. Wafer bonding has to be combined with III-V substrate reuse strategies like epitaxial lift-off (ELO) or spalling to be cost-competitive [46], [47]. Besides, strict subcell surface treatments are required to achieve particle-free and mirror-polished surfaces with root-mean-square roughness values below 1 nm before bonding, increasing the processing complexity [48].

One of the shortcomings of 2T tandem solar cells is that the requirement of the current matching between the subcells limits the choices of materials in terms of bandgaps [22]. The fabrication process compatibility, such as fabrication temperature, should also be considered carefully.

#### 1.2.2 4T Si-based tandem solar cells

In 4T Si-based tandem solar cells, the subcells are fabricated separately and then joined together by mechanical stacking. An optically transparent insulating layer is indispensable between subcells. The two subcells in 4T tandem solar cells are only optically coupled but not electrically, hence no current matching requirement. The subcells can be independently optimized during the fabrication process. The fabrication flexibility eliminates the constraint for the orientation or polarity of subcells, thus allowing more choices for top cell materials. Besides, 4T tandem solar cell has lower sensitivity to spectral variations compared with 2T device according to the simulation result [49].

Up till now, the highest efficiency of III-V/Si 2J solar cell is 32.8%, achieved by mechanically stacking GaAs on SHJ bottom cell [20]. The GaAs top cell is grown by metalorganic vapour phase epitaxy (MOVPE) and attached to a glass slide which is stacked on the separately fabricated SHJ cell using a transparent adhesive. For 4T perovskite/Si tandem solar cells, maximum efficiency of 26.7% was achieved in 2018 [50]. The perovskite top cell is stacked on a high-performance PERC-Si cell.

Even though high efficiencies have been achieved in 4T tandem solar cells, there are

several disadvantages of this configuration. The additional contact (metal grids, or/and transparent conductive layer) at the backside of the top cell increases the optical and resistive losses. The insulating layer between two subcells and the additional contact also increases the material cost. Furthermore, the 4T designs are currently incompatible with monolithic growth. More electrodes and inverters are demanded in 4T devices, increasing its complexity and cost of integration in PV modules and systems [51].

#### 1.2.3 3T Si-based tandem solar cells

Compared with the conventional 2T and 4T tandem solar cells, 3T tandem solar cells combine the advantages of 2T and 4T solar cells designs. In 3T tandem solar cells, independently working subcells allow comparable design flexibility as in 4T tandem solar cells and thus result in higher cell efficiency and energy yield [23], [49]. At the same time, the monolithic design avoids the use of extra transparent interconnection layers, insulating layers, and intermediate electrodes. Compared with 2T tandem solar cells, the adding of the third contact in 3T tandem solar cells eliminates the requirement of current matching [52]. In general, there are two types of 3T tandem solar cells depending on the configuration of contacts, either with a front contact, a back contact, and a mid-contact (Figure 1.13 (d)), or with one front contact and two back contacts (Figure 1.13 (e) and (f)).

In mid-contact 3T tandem solar cells, the mid-contact collects the current from the physical contact between the two absorbers, thus avoiding the need for a tunnel junction between two subcells [53]. However, the fabrication of transparent and highly conductive middle electrodes remains a challenge and the lateral current collection between the two absorbers limits the area of the devices. Therefore, it is beneficial to move the mid-contact to the back side of the bottom cell.

The 3T tandem solar cells with one front contact and two back contacts are consist of a top cell with front contact and an IBC Si bottom cell. The first 3T Si-based tandem solar cell with IBC Si bottom cell was reported by Nagashima T. [54]. In their work, Al<sub>0.3</sub>Ga<sub>0.7</sub>As was used as the top cell and was stacked on Ge or Si bottom cell with two back contacts. This configuration avoids the need for transparent and highly conductive middle electrodes. Besides, there is no requirement for lateral current collection in this kind of tandem solar cells, thus allowing the fabrication of large-scale devices.

In 3T tandem solar cells, the maximum power point is determined for total power instead

of individually for each of the subcells [53]. The first experimental realization of 3T perovskite/Si tandem solar cell with an IBC SHJ bottom cell was reported to yield a combined stabilized conversion efficiency of 17.1% under maximum power point conditions [55]. The efficiency of an optimized 3T perovskite/Si tandem solar cell with a conventional SHJ bottom cell was calculated to be 32% [56]. 3T GaInP/Si tandem solar cell was reported to achieve an efficiency of 27.3  $\pm$  1.0% [57]. In their work, the GaInP top cell and the IBC Si bottom cell were bonded by a TCA consisting of silver-coated microspheres embedded in epoxy.

In spite of the many advantages of 3T Si-based tandem solar cells, their disadvantages cannot be ignored. Because the 3T device does not have an easily replicated unit that can be connected together in series, the interconnection design of 3T tandem cells is more complex than that of 2T and 4T tandem cells [53].

Overall, 2T, 4T, and 3T Si-based tandem solar cells have their own advantages and drawbacks. Even though the performance of the 4T device is better than that of the 2T device according to the efficiency in some cases, the 2T device is more promising for terrestrial applications due to the easier integration in modules and lower cost. So far, the 2T monolithically integrated device is the only configuration established for commercial application thanks to its simple interconnection scheme [51], [58]. This is the configuration we will use in this thesis which is part of the HETONAN (acronym for "High-efficiency tandem solar cells based on III-V nanowires on silicon") project.

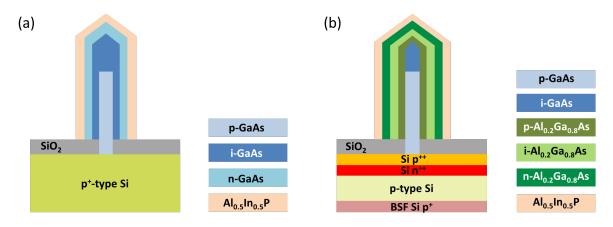

#### 1.2.4 III-V nanowires/Si tandem solar cells

As mentioned before, III-V compound semiconductor, perovskite, and chalcogenide are all good choices to be used as top cells in Si-based tandem solar cells. Among these candidates, III-V semiconductor solar cells are more attractive to us due to their remarkable efficiency and long-term reliability. The most efficient solar cell in the world is a III-V multijunction cell with an efficiency of 47.1% in a six-junction inverted metamorphic concentrator solar cell [59]. As a consequence, III-V solar cells play an irreplaceable role in space applications. After the development of several decades, the manufacturing technique of III-V solar cells has matured. However, the expensive material and processing limit the terrestrial applications of III-V solar cells. In order to reduce costs while maintaining high efficiency, III-V/Si tandem solar cell is a promising approach by replacing expensive Ge or GaAs substrates with cheaper Si substrates.

Considering the lower complexity of manufacturing and easier integration in photovoltaic

modules, 2T III-V/Si tandem solar cells have been studied [58]. Heteroepitaxy growth is a convenient approach to directly integrate III-V solar cells onto Si substrate [60], [61]. Nevertheless, the lattice mismatch between III-V materials and Si is a significant challenge for integration. To overcome this limit, III-V nanowires (NW)-based solar cells have been investigated by scientists since the mid-2000s [62]-[65].

Benefit from the small lateral dimension, lattice-mismatch-induced strain can be relaxed through the NW's sidewall, making it possible to direct epitaxy III-V NWs on Si [66]. What's more, NWs also reduce the reflection of light and increase the light-trapping of sunlight [64]. The theoretical limiting efficiency of two-junction GaAsP NWs/Si tandem solar cells is calculated to be 33.8% (1 sun, AM 1.5G) and 42.3% (500 suns, AM 1.5D) [67]. It indicates that III-V NWs/Si tandem solar cells are capable of competing with today's three- and four-junction solar cells. To date, there are only two reported experimental work on III-V NWs/Si tandem solar cells. The first realization of III-V NWs/Si tandem cells was reported by Yao, M. et al. in 2015 [62]. In their work, GaAs NWs top cell with an area of 1 mm<sup>2</sup> was grown by MOCVD on (111)-oriented Si bottom cell and the two subcells were connected by a low-resistance n<sup>+</sup>-GaAs/p<sup>+</sup>-Si heterojunction. An open-circuit voltage of 0.956 V and an efficiency of 11.4% were observed. The other fabricated III-V NWs/Si tandem solar cells was reported by Wood, B. A. et al. in 2017 [68]. GaAs<sub>0.75</sub>P<sub>0.25</sub> NWs array with an area of 100  $\mu$ m × 100  $\mu$ m was grown on Si solar cells by MBE. The two subcells were connected by p\*-GaAs<sub>0.75</sub>P<sub>0.25</sub>/n\*-Si heterojunction. Because the bandgap of GaAs<sub>0.75</sub>P<sub>0.25</sub> (1.7 eV) is higher than that of GaAs (1.42 eV), the opencircuit voltage of the tandem solar cell was increased to 1.16 V. Nevertheless, the efficiency of this GaAs<sub>0.75</sub>P<sub>0.25</sub> NWs/Si tandem cell was only 3.51%, lower than that of GaAs NWs/Si tandem cell.

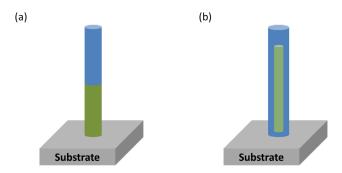

When using NWs as the top cell, there are two main configurations for the p-n junction, axial junction and radial junction, as shown in Figure 1.14. In axial junction, the direction of carrier extraction is parallel with the light absorption direction. Hence the height of the NWs with an axial junction is limited given the carrier diffusion length. While in the radial junction, the directions of light absorption and carrier extraction are decoupled into orthogonal spatial directions [69]. The NWs are allowed to keep long in the light incident direction to obtain optimal light absorption. At the same time, the small radius of NWs guarantees effective carrier collection as the carrier extraction direction is radial. Because the minority carrier diffusion length is generally longer than the NW radius, the NWs with radial junction are more

tolerant to the bulk defects which decrease minority carrier lifetimes [64]. NWs with radial junctions can achieve high efficiency with lower materials quality than in axial junction NWs.

Figure 1.14 Schematic of NW with (a) an axial junction and (b) a radial junction. Different colors represent different materials or the same material with different dopants.

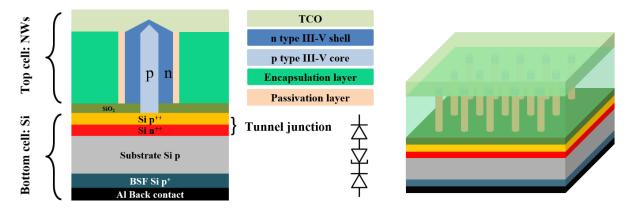

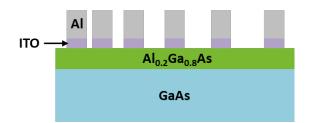

Therefore, a project named HETONAN funded by ANR (Agence Nationale de Recherche, ANR-15-CE05-0009-04) is carried out. The objective of this project is to fabricate high-efficiency III-V NWs/Si tandem solar cells. III-V NWs array with a radial junction is grown by molecular beam epitaxy (MBE) as the top cell and monocrystalline Si is used as the bottom cell (Figure 1.15). A low-resistance Si tunnel junction ( $p^{++}/n^{++}$ ) is implemented on the top of the bottom cell in order to electrically connect the two sub-cells. (111)-oriented Si substrate is required to guarantee the high vertical yields of III-V NWs epitaxy [70].

Figure 1.15 Schematic of targeted III-V NWs/Si tandem solar cell in HETONAN project.

## 1.3 Tunnel junction

As mentioned above, an interconnection is required to connect subcells in 2T monolithically integrated Si-based tandem solar cells. This interconnection should feature low electrical resistivity as well as high optical transmissivity. Normally, transparent conductive oxides (TCO) or interband tunnel junctions are adopted to satisfy these requirements. However,

the temperature tolerance of TCO makes them incompatible with a high-temperature top cell fabrication process. For example, degeneration of the electrical properties of indium tin oxide thin films has been observed when the annealing temperature reaches 500 °C [71], [72]. Besides, the parasitic absorption of TCO and its refractive index mismatch with silicon can lead to optical loss [73], [74]. Therefore, interband tunnel junction is used as the interconnection in this thesis. It is a reversed p-n junction that exists between the p-n junctions of the top cell and the bottom cell. Considering the requirement of current-match between subcells in 2T devices, tunnel junction allows effective current to flow with minimal voltage drop from one cell to the next based on the quantum tunneling phenomenon [75].

### 1.3.1 Physics of tunnel junction

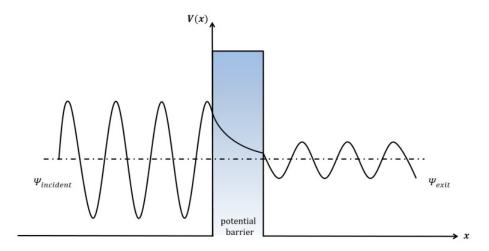

#### 1.3.1.1 Quantum tunneling

Quantum tunneling is a phenomenon in which quantum particles can penetrate or pass through a potential barrier whose maximum height is higher than the kinetic energy of the particles. It exclusively occurs on the quantum scale and there is no counterpart in classical mechanics. This phenomenon can be explained by the Heisenberg uncertainty principle that the position  $\Delta x$  and momentum  $\Delta p$  of an object can never be measured accurately at the same time, which is known as:

$$\Delta p \cdot \Delta x \ge \hbar/2[76]. \tag{1.18}$$

It means that electrons should be described by wave functions rather than particles when it comes to position. The wave function  $\Psi$  must satisfy the Schrödinger equation:

$$\frac{\mathrm{d}^2}{\mathrm{d}x^2}\Psi + \frac{2m}{\hbar^2}[E - V(x)]\Psi = 0 [77]. \tag{1.19}$$

The square of the wave function amplitude at a certain location represents the probability that an electron is observed at that location. When an electron collides with a potential barrier, the amplitude of the wave function decreases exponentially in the barrier. Once the wave function departs the barrier, its amplitude does not decay anymore. Therefore, the probability of the wave function passing through the barrier is nonzero. If the barrier is thin enough, the decrease of the amplitude will be minuscule and there is a great probability for the electron to be observed on the other side of the barrier. This phenomenon exists only from the perspective of quantum mechanics, so it is called quantum tunneling. It has important

applications in tunnel diodes, quantum computing, scanning tunneling microscope, and so on.

Figure 1.16 Schematic diagram of quantum tunneling.

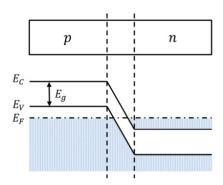

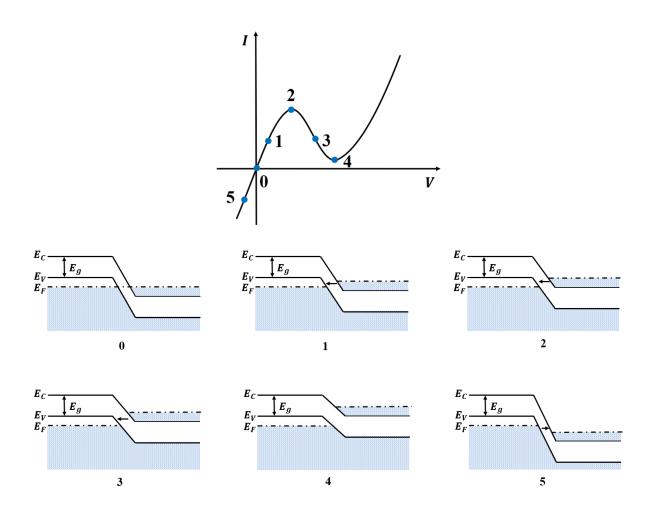

#### 1.3.1.2 I-V characteristics of the tunnel junction

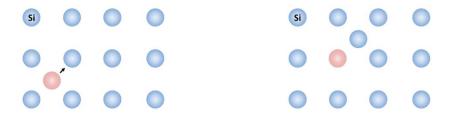

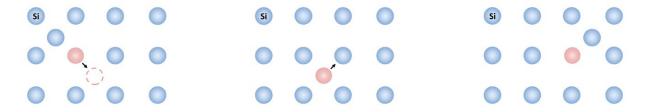

A tunnel junction can be formed by a heavily doped p-n junction in which both the p- and n-sides are degenerate. The first quantum electron device based on tunnel junction, known as tunnel diode, was invented by Esaki in 1957 [78]. A tunnel diode simply consists of a tunnel junction and two terminals. Fermi levels of tunnel junction on p-side and n-side are located within the allowed bands as shown in Figure 1.17. The bottom of the conduction band on the n-side is lower than the top of the valence band on the p-side. It means that there are identical energy states in the conduction band of the n-side and the valence band of the p-side. Because the tunnel junction is highly doped, the depletion region is narrow enough (5-10 nm) for electrons to tunnel through, resulting in the generation of tunneling current [13]. The current-voltage characteristic of the tunnel junction is shown in Figure 1.18. The forward current of a tunnel diode is composed of diffusion current and tunneling current. If a small forward voltage is applied, the diffusion current is very low and the tunneling current plays an important role.

Figure 1.17 Band structure of a tunnel junction.

When no voltage is applied, the tunnel diode is at the condition of thermal equilibrium and the Fermi level is continuous. There is no unoccupied state below the Fermi level and no occupied state above the Fermi level. Therefore, no electrons tunnel through the depletion region in this case, corresponding to point 0 in Figure 1.18.

When a small forward bias V is applied, the band on the n-side raises qV relative to the p-side. There are occupied states below the Fermi level on the n-side and unoccupied states above the Fermi level on the p-side with the same energy states. So, some electrons in the conduction band on the n-side move to the p-side by tunneling, forward current from p-side to the n-side generated, corresponding to point 1.

More and more electrons tunnel from n-side to p-side as the forward bias increases. As a result, the tunneling current keeps increasing until the Fermi level of the p-side is the same as the bottom of the conduction band of the n-side, which corresponds to point 2 in the *I-V* curve. At this point, the flux of tunneling electrons is maximum so that the tunneling current reaches its peak value.

If the forward bias is further increased, fewer electrons will tunnel through the barrier due to the decrease of available energy states on both sides. The tunneling current then decreases as the voltage increases, known as the negative differential resistance, as shown at point 3. This is a peculiarity of tunnel diodes.

When the forward bias is increased to  $V_{\nu}$ , the bottom of the conduction band on the n-side has the same energy level as the top of the valence band on the p-side. There are no more available quantum states on both sides and hence the tunneling current should decrease to zero. However, the valley current is much bigger than the forward diffusion current in practice. The excess current is attributed to the existence of impurities or defects in the bandgap [79]. When the forward bias is higher than  $V_{\nu}$ , the barrier height decreases and the current is gradually dominated by forward current [80].

When a reverse bias is applied, the band of the p-side raises relative to the n-side. The valence band electrons of the p-side tunnel into the conduction band of the n-side, resulting in reverse tunneling current. The reverse tunneling current increases with the increase of reverse bias, as shown at point 5.

25

Figure 1.18 Current-voltage characterization of the tunnel junction and corresponding band structures.

In this chapter, the working principle and the efficiency limit of single-junction solar cells have been reported. One approach to overcome this limit is to use multijunction solar cells. Therefore, three kinds of dual-junction Si-based tandem solar with different configurations (4T, 2T, and 3T) have been introduced. Among them, 2T Si-based tandem solar is more attractive to us due to its simple integration in modules and lower cost. The tunnel junction has been chosen as the interconnection in 2T Si-based tandem solar. The working principle and characterization of tunnel junctions have been presented.

# 1.4 Objective and outline of the thesis

The objective of this thesis is to fabricate Si tunnel junction and implement it as the interconnection in the tandem solar cells. As mentioned before, this thesis is part of the HETONAN (acronym for "High-efficiency tandem solar cells based on III-V nanowires on silicon",

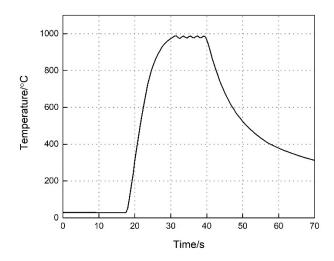

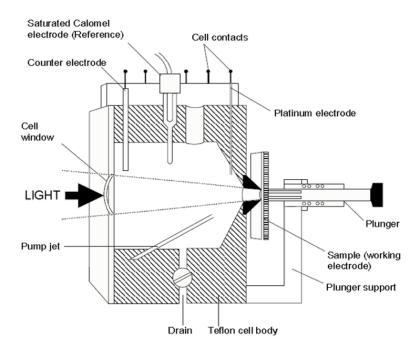

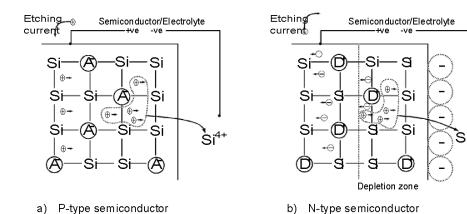

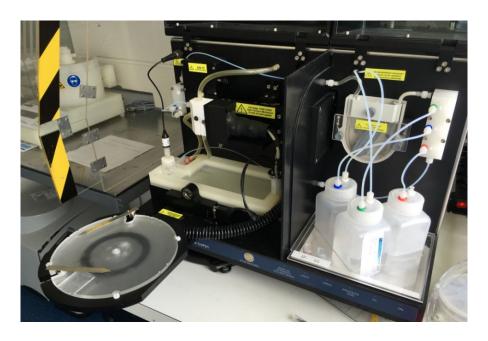

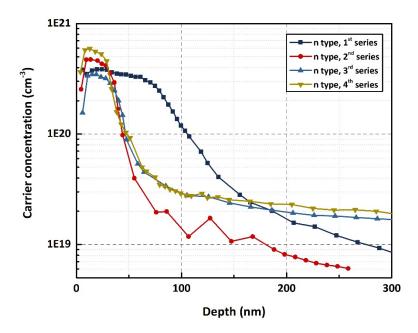

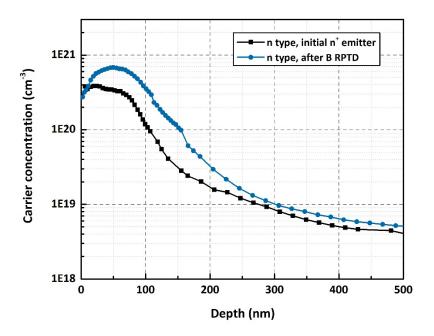

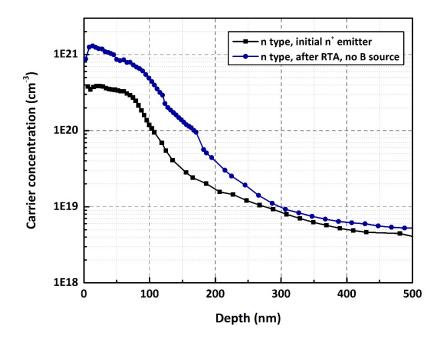

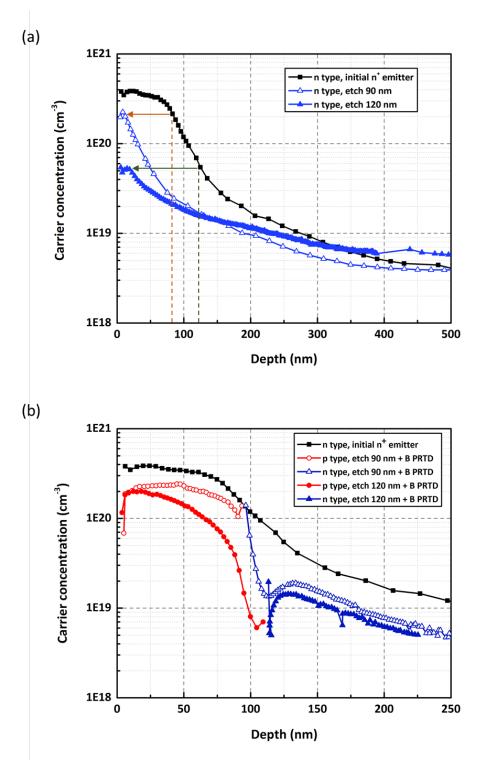

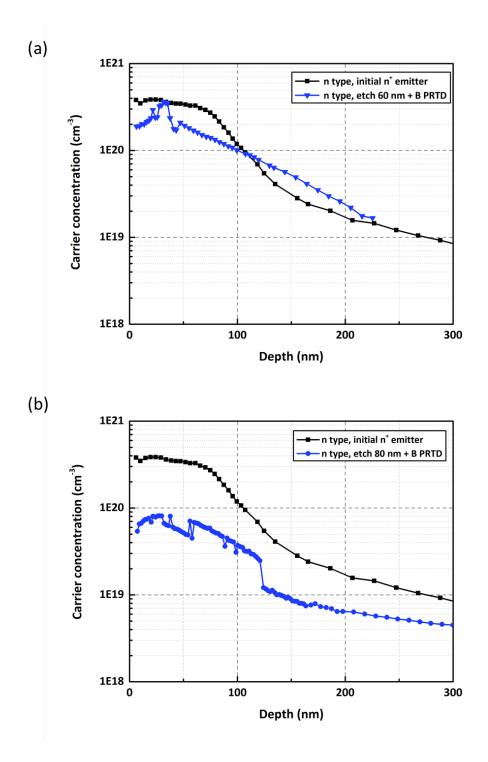

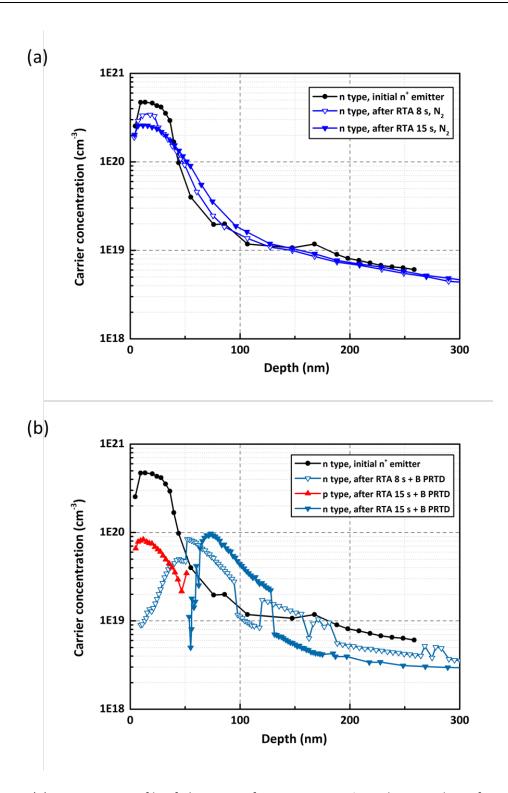

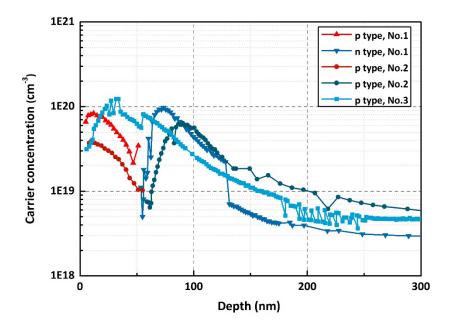

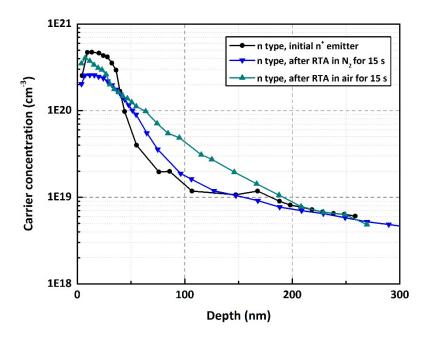

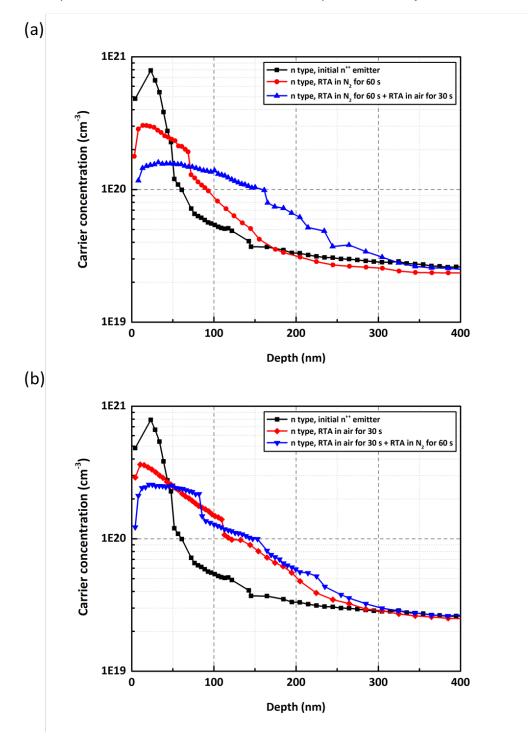

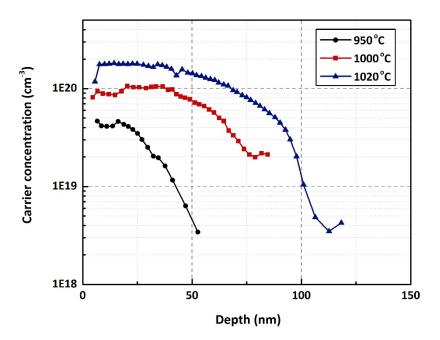

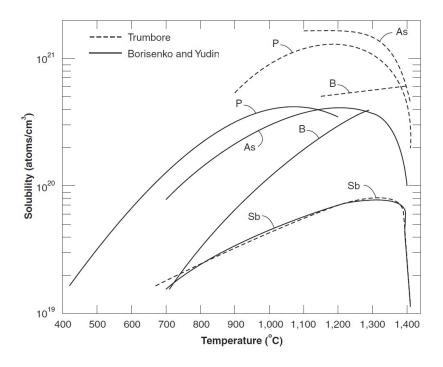

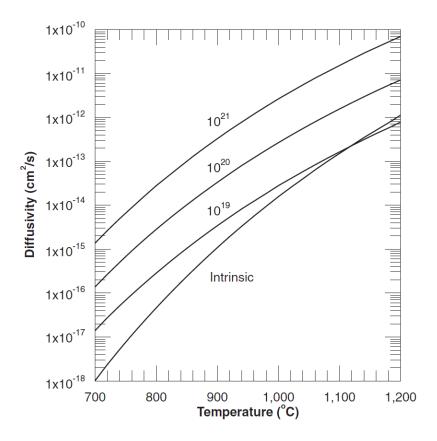

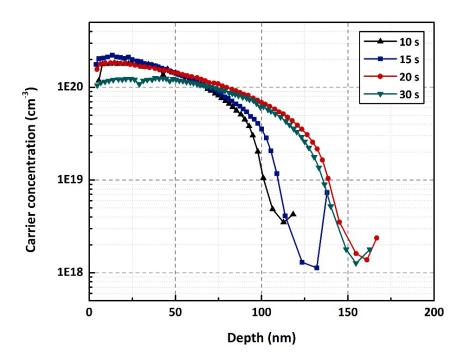

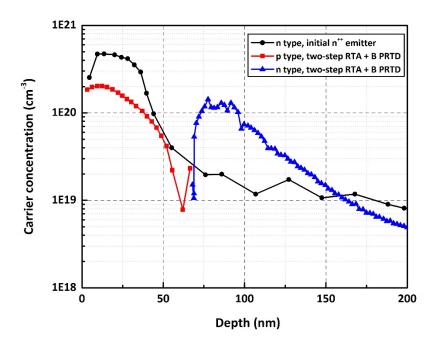

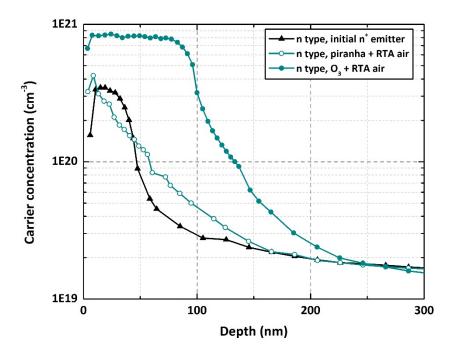

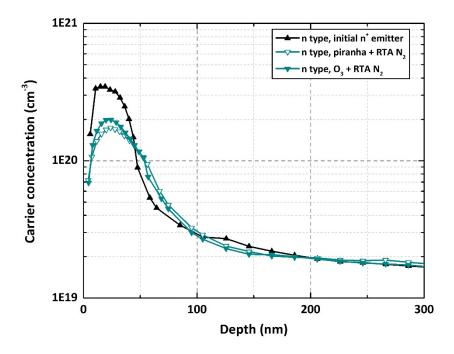

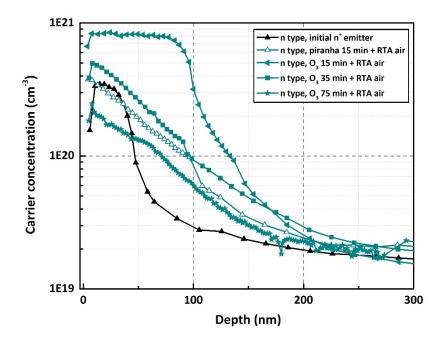

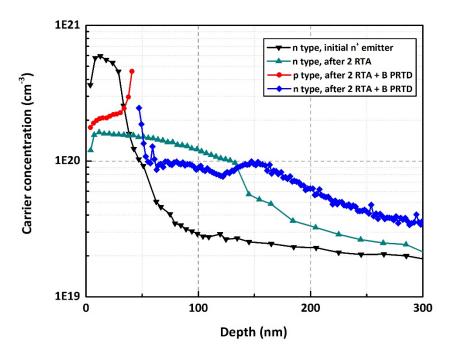

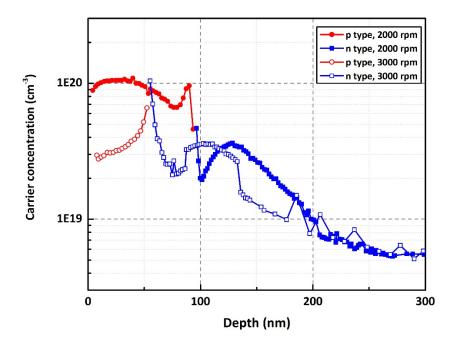

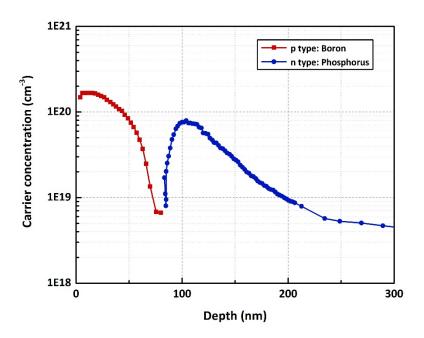

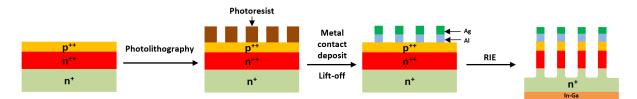

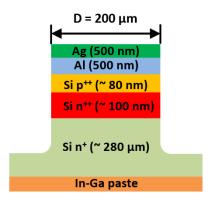

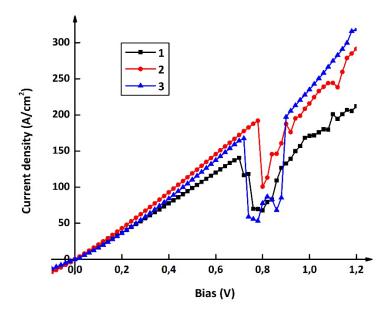

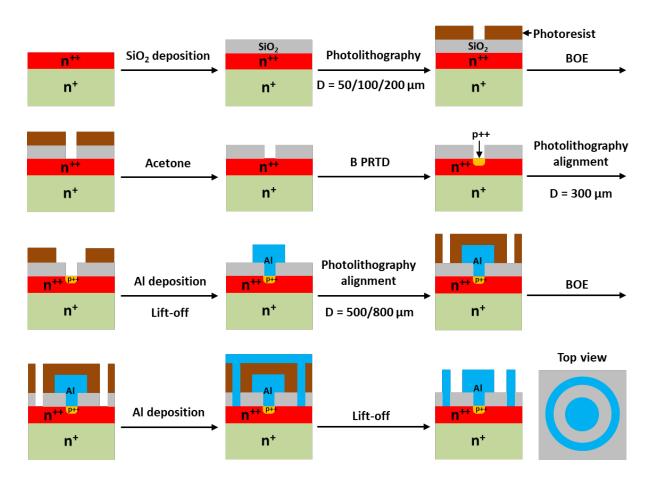

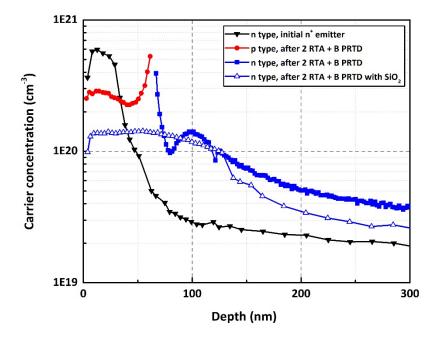

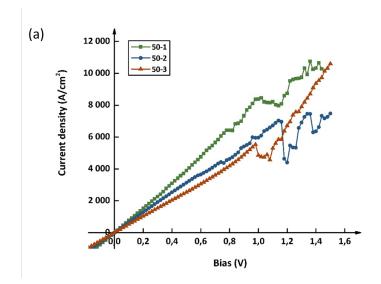

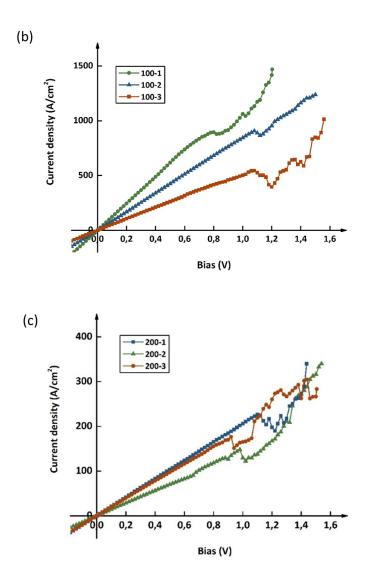

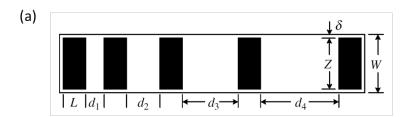

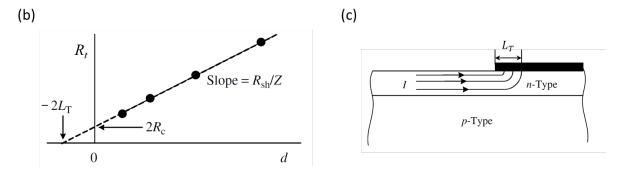

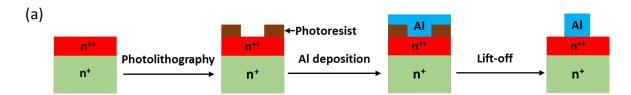

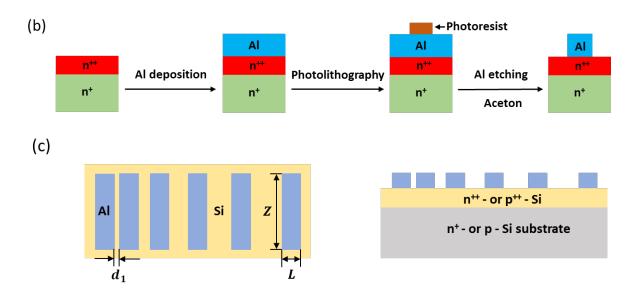

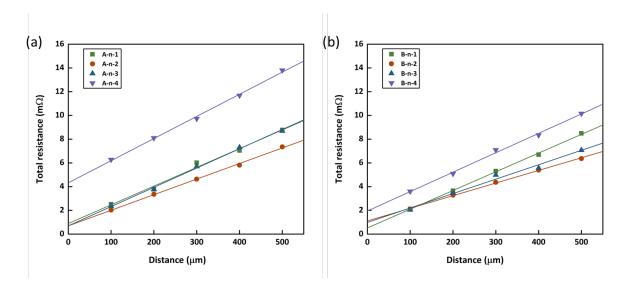

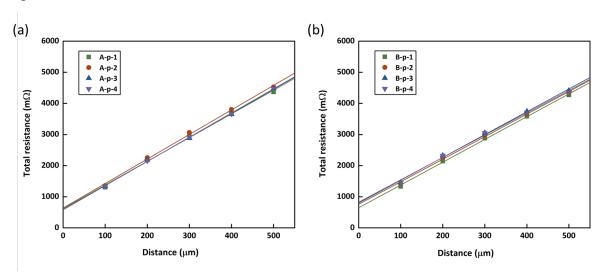

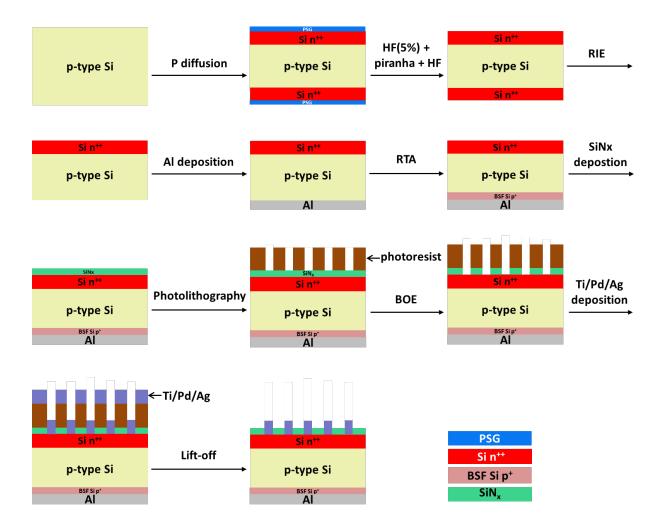

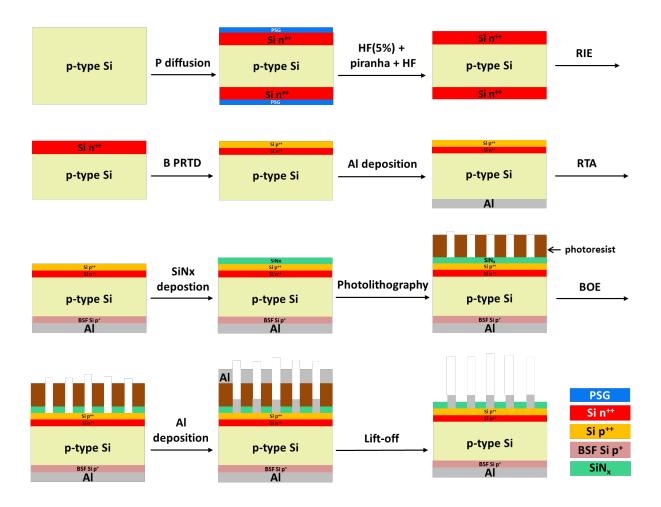

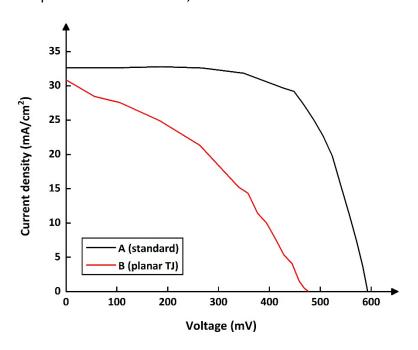

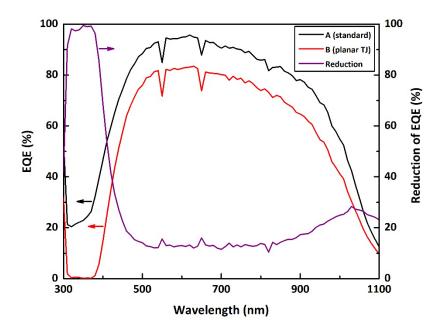

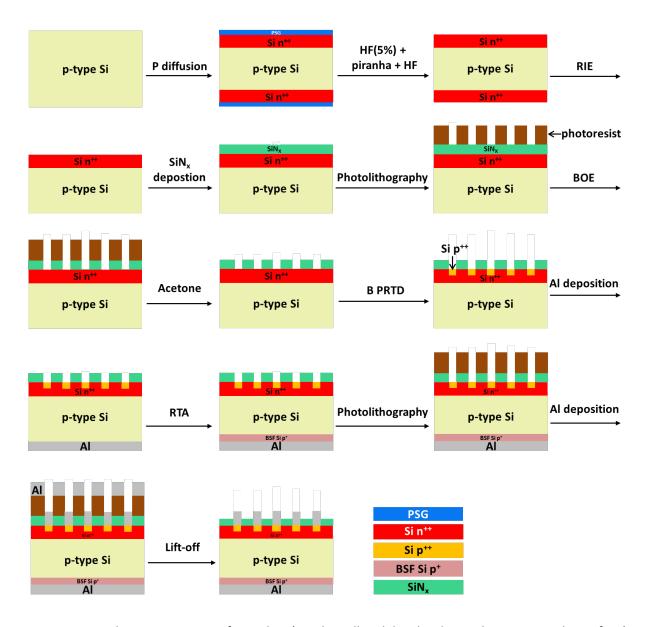

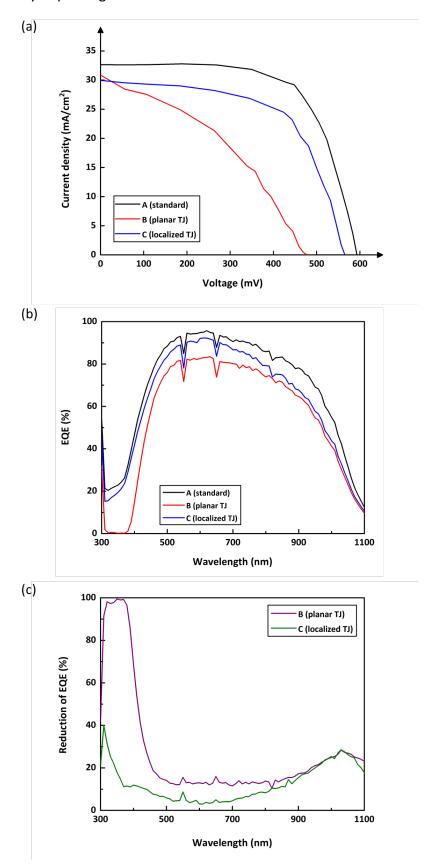

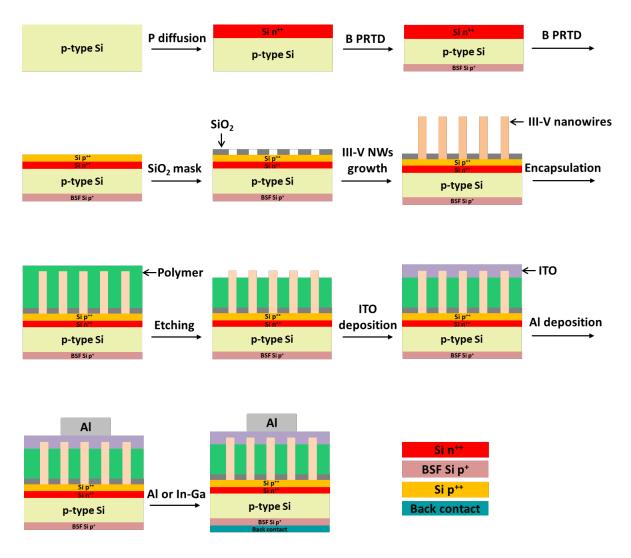

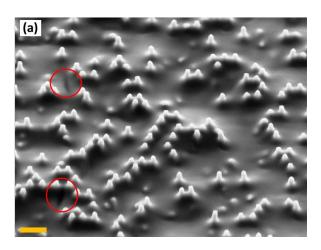

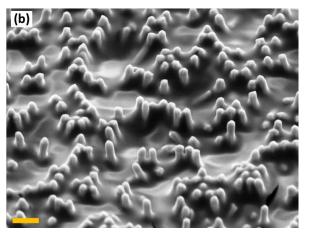

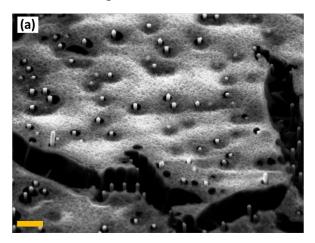

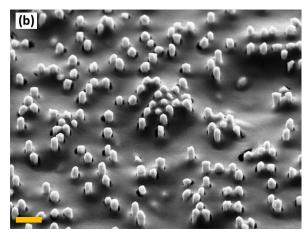

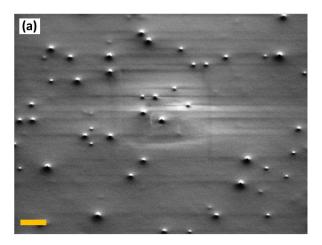

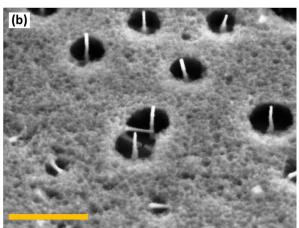

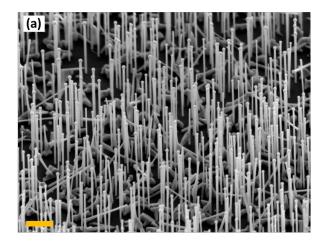

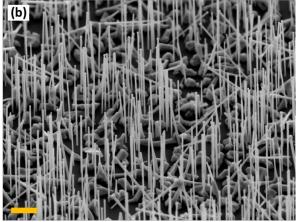

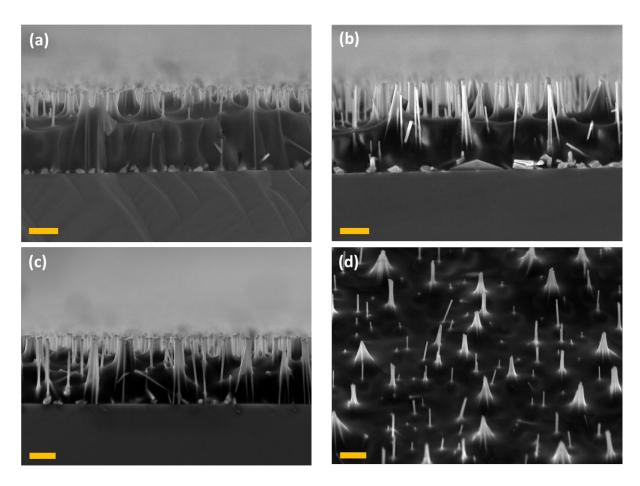

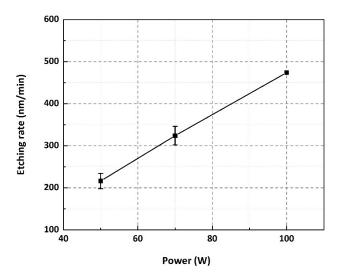

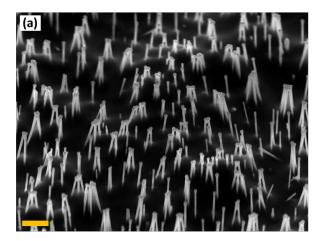

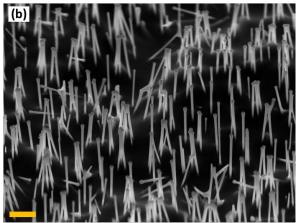

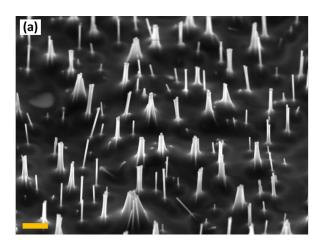

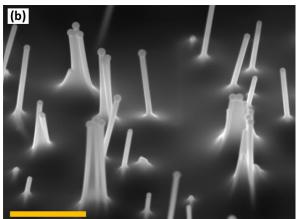

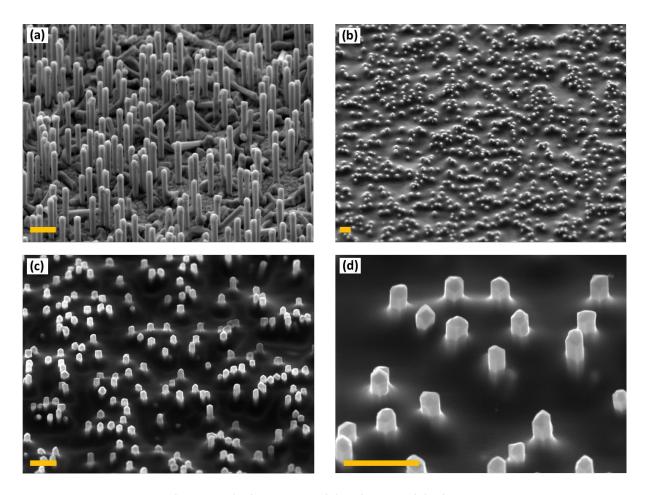

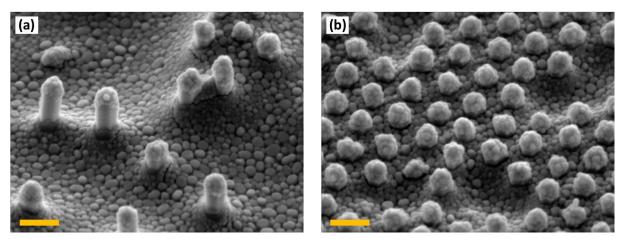

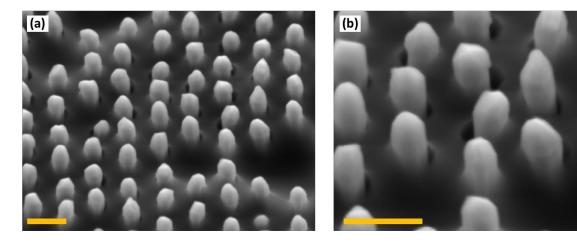

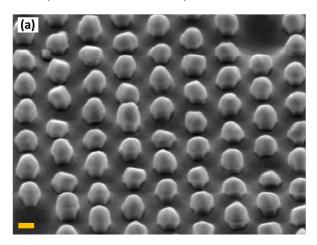

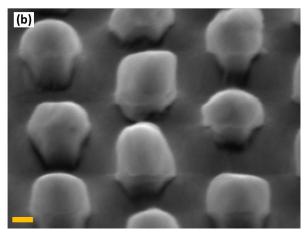

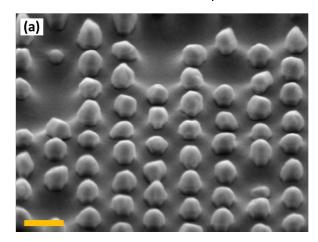

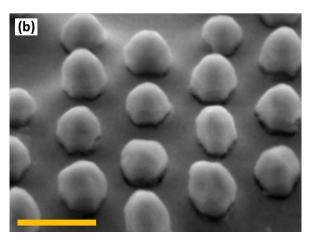

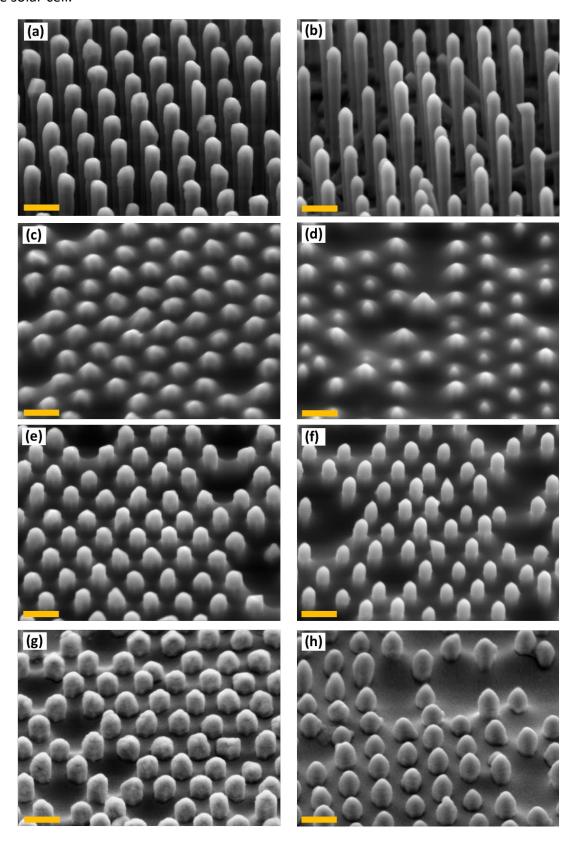

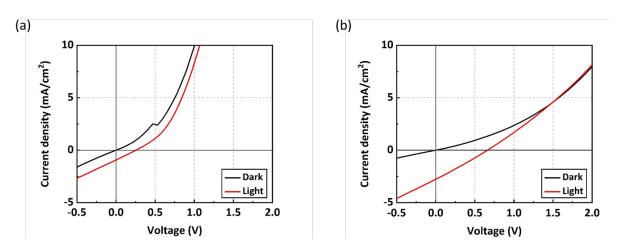

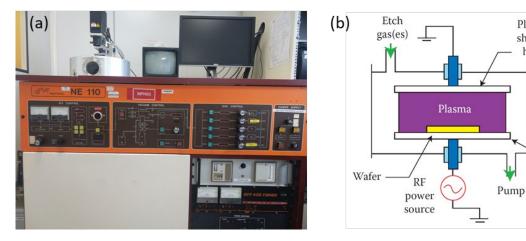

granted by ANR) project. The ultimate purpose of this project is to develop a high-efficiency tandem solar cell structure by combining a planar Si bottom cell with a III-V nanowires (NWs) top cell. The two subcells will be connected in series by a low-resistance Si tunnel junction elaborated in this thesis. The outline of this thesis is shown as follows.