## Fault Tolerance in Hardware Spiking Neural Networks Sarah Ali El Sayed

#### ▶ To cite this version:

Sarah Ali El Sayed. Fault Tolerance in Hardware Spiking Neural Networks. Micro and nanotechnologies/Microelectronics. Sorbonne Université, 2021. English. NNT: 2021SORUS310. tel-03681910v2

## HAL Id: tel-03681910 https://theses.hal.science/tel-03681910v2

Submitted on 30 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

## FAULT TOLERANCE IN HARDWARE SPIKING NEURAL NETWORKS

présentée par SARAH ALI ELSAYED

École Doctorale Informatique, Télécommunications et Électronique

réalisée au Laboratoire d'Informatique Paris 6

soutenue le 28 Octobre 2021

devant le jury composé de :

| M.   | Alberto BOSIO             | Prof., INL, Lyon                           | Rapporteur         |

|------|---------------------------|--------------------------------------------|--------------------|

| M.   | Ernesto SANCHEZ           | Assoc. Prof., Politecnico di Torino, Italy | Rapporteur         |

| M.   | Olivier SENTIEYS          | Prof., INRIA-IRISA, Rennes                 | Examinateur        |

| М.   | Ihsen ALOUANI             | MCF, IEMN, Lille                           | Examinateur        |

| Mme. | Ioana VATAJELU            | CR CNRS, TIMA, Grenoble                    | Examinatrice       |

| M.   | Luis CAMUÑAS MESA         | Research Assoc., IMSE-CNM, Spain           | Invité             |

| М.   | Haralampos STRATIGOPOULOS | DR CNRS, LIP6, Paris                       | Directeur de Thèse |

Sarah ALI ELSAYED: *Fault Tolerance in Hardware Spiking Neural Networks,* © Juillet 2021

To my father who always believed in me, my mother who did everything to make sure I succeed in life, and my sister who has been with me through it all...

### ABSTRACT

Artificial Intelligence (AI) and machine learning algorithms are taking up the lion's share of the technology market nowadays, and hardware AI accelerators are foreseen to play an increasing role in numerous applications, many of which are mission-critical and safety-critical. This requires assessing their reliability and developing cost-effective fault tolerance techniques; an issue that remains largely unexplored for neuromorphic chips and Spiking Neural Networks (SNNs).

A tacit assumption is often made that reliability and error-resiliency in Artificial Neural Networks (ANNs) are inherently achieved thanks to the high parallelism, structural redundancy, and the resemblance to biological neural networks. However, prior work in the literature unraveled the falsity of this assumption and exposed the vulnerability of ANNs to faults, proving that without adequate designs and proper protection measures, ANNs remain at risk of performance failure due to faults.

In this thesis, we tackle the subject of testing and fault tolerance in hardware SNNs. We start by addressing the issue of post-manufacturing test and behavior-oriented self-test of hardware neural networks and propose a self-testable version of an analog biologically plausible spiking neuron circuit at transistor-level. Then we move to defect-oriented testing, where transistor-level fault simulations on a large scale are usually prohibitive in time and cost. Therefore, we follow a bottom-up approach starting from transistor-level fault injection into a single analog Integrate-and-Fire (I&F) neuron and propose a behavioural-level fault model that is specific to SNNs, yet agnostic to the circuit design and architecture. We demonstrate the acceleration offered by this fault model by performing fault injection experiments that pinpoint the critical fault types and locations on two SNNs that we designed for two neuromorphic datasets, namely the N-MNIST and IBM's DVS-gesture datasets. By leveraging observations from these experiments, we propose a neuron fault tolerance strategy for SNNs, optimized for low area and power overhead.

Finally, we present a hardware-in-the-loop case-study which would be used as a platform for demonstrating fault-injection experiments and fault-tolerance capabilities.

## $\mathbf{R} \not \in \mathbf{S} \cup \mathbf{M} \not \in$

L'intelligence artificielle (IA) et les algorithmes d'apprentissage automatique sont au sommet du marché de la technologie de nos jours. Dans ce contexte, les accélérateurs matériels d'IA devraient jouer un rôle de plus en plus primordial pour de nombreuses applications, surtout ceux ayant une mission critique et un haut niveau de sécurité. Cela nécessite d'évaluer leur fiabilité et de développer des techniques peu coûteuses de tolérance aux fautes; un problème qui reste largement inexploré pour les puces neuromorphiques et les réseaux de neurones impulsionnels (Spiking Neural Networks, SNNs).

Il est souvent présumé que la fiabilité et la résilience aux erreurs dans les Réseaux de Neurones Artificiels (ANN) sont intrinsèquement obtenues grâce au parallélisme, à la redondance structurelle et à la ressemblance avec les réseaux de neurones biologiques. Cependant, des travaux antérieurs dans la littérature ont révélé le non-fondement de cette hypothèse et ont exposé la vulnérabilité des ANN aux fautes, prouvant que sans des conceptions adéquates et des mesures de protection appropriées, les ANNs restent à risque de manque de performance en raison des fautes.

Dans cette thèse, nous abordons le sujet de test et de la tolérance aux fautes pour les SNNs matériels. Nous abordons tout d'abord la question du test de post-fabrication des réseaux de neurones matériels et de leur autotest orienté sur le comportement. A l'issue de cette phase, nous proposons une version auto-testable d'un d'un neurone impulsionnel biologiquement plausible au niveau transistor. Ensuite, nous abordons le sujet de simulations de fautes à grande échelle au niveau des transistors qui est généralement contraignant en temps. Par conséquent, nous suivons une approche ascendante partant de l'injection de fautes au niveau transistor dans un seul neurone analogique du type Integrate-and-Fire (I&F) afin de proposer un modèle de fautes au niveau comportemental. Ce modèle est spécifique aux SNN et indépendant de la conception et l'architecture du circuit. Nous démontrons l'accélération offerte par ce modèle de fautes en effectuant des expériences d'injection de fautes. Ces expériences identifient les types et les emplacements de fautes critiques sur deux SNN que nous avons conçus pour la classification des basses de données N-MNIST et DVS-gesture d'IBM. En exploitant les observations de ces expériences, nous proposons une stratégie de tolérance aux fautes des neurones pour les SNNs qui a été optimisée afin de minimiser les surcoûts en surface et puissance du circuit.

Enfin, nous présentons une étude de cas "matériel dans la boucle" qui serait utilisée comme plateforme pour démontrer les expériences d'injection de fautes et les capacités de tolérance aux fautes.

## $P \, U \, B \, L \, I \, C \, A \, T \, I \, O \, N \, S$

As a result of this thesis the following publications have appeared:

- [1] S. A. El-Sayed, L. A. Camuñas-Mesa, B. Linares-Barranco, and H.-G. Stratigopoulos, "Self-testing analog spiking neuron circuit," in *International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design, Lausanne, Switzerland, 2019.*

- [2] S. A. El-Sayed, T. Spyrou, E. Afacan, L. A. Camuñas-Mesa, B. Linares-Barranco, and H.-G. Stratigopoulos, "Spiking neuron hardwarelevel fault modeling," in *IEEE International Symposium on On-Line Testing and Robust System Design*, Naples (virtual), Italy, 2020.

- [3] T. Spyrou, S. A. El-Sayed, E. Afacan, L. A. Camuñas-Mesa, B. Linares-Barranco, and H.-G. Stratigopoulos, "Neuron Fault Tolerance in Spiking Neural Networks," in 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble (virtual), France, 2021.

## A C K N O W L E D G M E N T S

"An honorable person won't tell people how great they are, people will experience their greatness just by being with them."

– Imam Al-Ghazali

Pursuing a PhD is a life-changing decision that should not be taken lightly. This is a lesson I have learned the hard way. As I look back over the last four years, I cannot help but feel thankful for the life-changing experience, grateful for all the people that have shared the journey with me, and relieved that I am finally done!

Perhaps the thing I am grateful for the most is meeting Haralampos Startigopoulos and having him as my supervisor. I will quote my colleague Julian here: there are only a few PhD students who like their supervisors, but in our case, it was much more than just a studentprofessor relationship. Besides being a very professional, attentive, and involved mentor to us all, you became a friend with whom we enjoy chatting and spending time and a supportive confidant who is always willing to solve whatever problems we face, administrative or personal, just to make sure that we are comfortable enough to focus on our work. Thank you, Haralampe<sup>1</sup>, for your patience, persistence, and support, and for showing me how a good academic should be. Thank you for constantly boosting my confidence and pushing me to do my best and for teaching me to always have the bigger picture in mind. I feel privileged to have had the chance to work with you and learn from you. I could not have asked for a better supervisor. And I will be waiting for you and your lovely family in Egypt someday.

A very special thank you is owed to **Alhassan Hadia**, the one who got me in contact with **Haralampos** in the first place and one of the main reasons I am here today. I owe a huge chunk of my success to him and his support over the years. And of course, **Hassan Abou Shady**, who was kind enough to recommend me and support my application to come to LIP6 and start my PhD journey.

An important factor in the advancement of this work is owed to **Luis Camuñas-Mesa** from the Instituto de Microelectrónica de Sevilla, Spain. I

<sup>1</sup> please note how I used the proper Greek way to address you!

am very grateful to him for giving us many of his team's IPs to experiment with and for always being available and patient enough to help us and answer all our questions.

People always say you do not make friends in the workplace, but that was definitely not true here at office 415. From the very first day, the overall atmosphere and the people were energetic and friendly. Our office was always full of conversations, jokes, food, coffee, and music. Over the years we have come to know each other pretty well and we exchanged cultures, food habits, and more desserts than I can count!

I would, however, have to start with the latest person to join the office. My one-day-apart twin (albeit a few years younger) and the breath of fresh air that my PhD so desperately needed; **Theofilos Spyrou**. An amazing friend with whom I enjoyed many conversations, debates, and lessons of life, language, and history. I am very thankful for your mix of enthusiasm and optimism without which I could not have made it through the past couple of years. I hope you know how much I appreciate everything you have done to help me, little brother. And now that I have come to realize that the Greek language and mythology are probably the origin of everything, Greece is my favorite country outside of my beloved home, Egypt.

It was not always pleasant to be the only girl in the office, but fortunately, I was blessed with some amazing friends who made it very easy for me with their comprehension and respect. **Julian**, who was very enthusiastic about me coming even before I arrived at the lab, and **Antonis**, whose first question to me when we met was *"how old are you?"*! And of course, **Gabriel**; the mature one. Thank you for sharing the journey with me from the very beginning. You guys are the best.

I am also deeply grateful for getting to know many other amazing colleagues at LIP6: **Ilias**, **Alan**, **Ning**, **Doaa**, and **Islam**. I am especially grateful to **Tamer Badran**, who was a huge help to me from day one in trying to figure out my way around the Préfecture and how exactly things work in France. I would like as well to thank **Engin Afacan** and **Spyros Raptis** for sharing the last year of my PhD journey and collaborating with me and **Theofilos** to try and get something meaningful and worthy out of this project.

As for life outside the lab, the was a story with many chapters. I have been so lucky to make many amazing friends who shaped my experience and eventually became like a second family to me.

The very first friend I made in France was **Joana Oliveira**, whom I met trying to learn how to say two sentences in French. I am so happy you took the initiative and asked me to do something that weekend in 2018.

We ended up seeing all of Paris together and spending so many days exploring Disneyland, "the happiest place on earth"! You made Paris a less lonely place for me, and for that I will be eternally grateful.

There is an Arabic proverb that goes: (a coincidence is sometimes better than a thousand appointments), which loses a lot of meaning in translation I'm afraid, but it is a perfect explanation of the wonderful day I met **Amel Raboudi**. Your decision to come and talk to me during that apéro three years ago literally changed my life. You are a wonderful and understanding friend and one of the kindest souls I will ever meet. I want to thank you even more for introducing me to **Sohaila** who became a little sister to me. Her and **Abdallah**'s home became my "little Egypt" here in Paris, full of food, movies, and all sorts of Egyptian traditions. Thank you guys for opening your homes to me and allowing me to share various aspects of your lives. And thank you for having my back and creating a sanctuary that I could run to whenever I needed to feel safe.

Nonetheless, the lion share of my gratitude belongs to the most important people in my life, my family. **Prof. Nagiba Shoker**, my mum who is a university professor herself, has been my biggest motivation for all I have accomplished in my life to this day. Thank you for supporting me and relentlessly pushing me to make something of myself. I am what I am today because of you. My sister **Wesam** who is my best friend, my partner in crime, and my biggest fan. The only one I can totally be myself with and feel absolutely safe. Thank you for putting up with me and for all that you have sacrificed for me. You are, and always have been, my backbone in this life and I cannot even begin to explain how much I appreciate your existence and support.

And last but not least, my new husband, **Tamer**. You have always been someone I could count on, even back when we were just friends from work. Thank you for your incredible patience and emotional support throughout this journey. And now, we can start our own story in peace.

Finally, I would like to thank my dad **Prof. Ali ElSayed** who, although no longer with us, continues to inspire me to follow in his footsteps. Thank you for being my role model. I hope you are proud of me...

Sarah

## C O N T E N T S

| 1                   | INT  | RODUC  | CTION                                                 | 1  |

|---------------------|------|--------|-------------------------------------------------------|----|

|                     | 1.1  | Prefac | ce                                                    | 1  |

|                     |      | 1.1.1  | AI Hardware Accelerators                              | 2  |

|                     |      | 1.1.2  | Neuromorphic Computing                                | 3  |

|                     |      | 1.1.3  | Is AI Hardware Fault-Tolerant?                        | 4  |

|                     | 1.2  | Motiv  | vation                                                | 5  |

|                     | 1.3  | Metho  | odology                                               | 6  |

|                     |      | 1.3.1  | Fault Injection                                       | 6  |

|                     |      | 1.3.2  | Fault Modeling                                        | 7  |

|                     |      | 1.3.3  | Fault Tolerance                                       | 7  |

|                     | 1.4  | Thesis | s Structure                                           | 8  |

| 2                   | SPI  | KING N | NEURAL NETWORKS & THEIR FAULT TOLERANCE:              |    |

| A LITERATURE REVIEW |      |        | 9                                                     |    |

|                     | 2.1  | Spikir | ng Neural Networks                                    | 9  |

|                     |      | 2.1.1  | The Spiking Neuron                                    | 10 |

|                     |      |        | 2.1.1.1 The Spike                                     | 10 |

|                     |      |        | 2.1.1.2 The Membrane Potential                        | 10 |

|                     |      |        | 2.1.1.3 Spike Generation                              | 11 |

|                     |      | 2.1.2  | Neural Coding Schemes                                 | 12 |

|                     | 2.2  | Spikir | ng Neural Networks in Hardware                        | 13 |

|                     |      | 2.2.1  | Neuron Models                                         | 13 |

|                     |      | 2.2.2  | Address Event Representation                          | 14 |

|                     | 2.3  |        | omorphic Technology Prospects and Challenges          | 15 |

|                     | 2.4  |        | of-the-Art in Testing and Fault Tolerance in Hardware |    |

|                     |      | Neura  | al Networks                                           | 18 |

|                     |      | 2.4.1  | Fault, Error, and Failure                             | 18 |

|                     |      | 2.4.2  | ·                                                     | 19 |

|                     |      | 2.4.3  | Fault Tolerance in the Literature                     | 23 |

| 3                   | A SI | ELF-TE | STING ANALOG SPIKING-NEURON CIRCUIT                   | 27 |

|                     | 3.1  |        | logical Perspective                                   | 27 |

|                     | 3.2  | The B  | Biologically-Inspired Neuron Circuit                  | 29 |

|                     |      | 3.2.1  | The Mathematical Model                                | 29 |

|                     |      | 3.2.2  | The Neuron Circuit                                    | 29 |

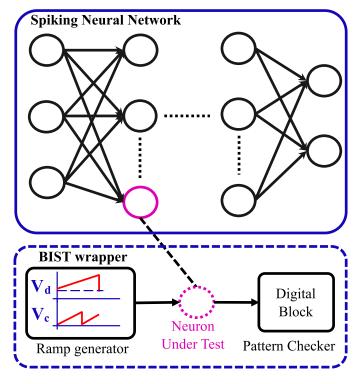

|                     | 3.3  | The B  | Built-In Self-Test                                    | 33 |

|                     |      | 3.3.1  | BIST Architecture                                     | 33 |

|                     |      | 3.3.2  | Expected BIST Response                                | 35 |

|                     |      | 3.3.3  | BIST Verification                                     | 35 |

|   | 3.4                           | Resul                          | ts and Di   | scussion                                   | 36       |  |

|---|-------------------------------|--------------------------------|-------------|--------------------------------------------|----------|--|

| 4 | HARDWARE-LEVEL FAULT MODELING |                                |             |                                            | 39       |  |

|   | 4.1                           | 4.1 Fault Simulation Framework |             |                                            |          |  |

|   | 4.2                           | The S                          | piking Ne   | euron                                      | 39<br>40 |  |

|   | -                             | 4.2.1                          |             | ral Model                                  | 40       |  |

|   |                               | 4.2.2                          | Transist    | or-Level Design                            | 41       |  |

|   | 4.3                           | Spikir                         |             | n Faulty Behaviors                         | 42       |  |

|   |                               | 4.3.1                          | 0           | phic Faults                                | 42       |  |

|   |                               | 4.3.2                          |             | tric Faults                                | 46       |  |

|   | 4.4                           | Behav                          |             | el Fault Model                             | 48       |  |

| 5 | FAU                           | LT INJ                         | ECTION      | AND RESILIENCY ANALYSIS IN SPIKING         |          |  |

|   | NEU                           | JRAL N                         | ETWORK      | S                                          | 49       |  |

|   | 5.1                           | Fault                          | Models .    |                                            | 49       |  |

|   |                               | 5.1.1                          | Neuron      | Fault Models                               | 50       |  |

|   |                               | 5.1.2                          | Synapse     | Prault Models                              | 51       |  |

|   | 5.2                           | Case S                         |             |                                            | 51       |  |

|   |                               | 5.2.1                          | The Spil    | ke Response Model                          | 52       |  |

|   |                               | 5.2.2                          | Case Stu    | udy (1): The N-MNIST SNN                   | 53       |  |

|   |                               |                                | 5.2.2.1     | The N-MNIST Dataset                        | 53       |  |

|   |                               |                                | 5.2.2.2     | The N-MNIST SNN Architecture               | 53       |  |

|   |                               | 5.2.3                          | Case Stu    | udy (2): The DVS-gesture SNN               | 55       |  |

|   |                               |                                | 5.2.3.1     | The DVS-gesture Dataset                    | 55       |  |

|   |                               |                                | 5.2.3.2     | The DVS-gesture SNN Architecture           | 56       |  |

|   | 5.3                           | Fault                          | Modeling    | g & Injection Methodology                  | 57       |  |

|   | 5.4                           | Fault                          | Injection   | Experiments & Results: (1) The N-MNIST     |          |  |

|   |                               | SNN                            |             |                                            | 59       |  |

|   |                               | 5.4.1                          | Neuron      | Faults                                     | 59       |  |

|   |                               |                                | 5.4.1.1     | Dead Neuron Faults                         | 59       |  |

|   |                               |                                | 5.4.1.2     | Saturated Neuron Faults                    | 61       |  |

|   |                               |                                | 5.4.1.3     | Parametric Faults                          | 61       |  |

|   |                               | 5.4.2                          | Synapse     | Faults                                     | 65       |  |

|   |                               |                                | 5.4.2.1     | Dead Synapse Faults                        | 66       |  |

|   |                               |                                | 5.4.2.2     | Saturated Synapse Faults                   | 67       |  |

|   | 5.5                           | Fault                          | Injection 1 | Experiments & Results: (2) The DVS-gesture |          |  |

|   |                               | SNN                            |             |                                            | 69       |  |

|   |                               | 5.5.1                          | Neuron      | Faults                                     | 69       |  |

|   |                               |                                | 5.5.1.1     | Dead Neuron Faults                         | 69       |  |

|   |                               |                                | 5.5.1.2     | Saturated Neuron Faults                    | 70       |  |

|   |                               |                                | 5.5.1.3     |                                            | 70       |  |

|   | 5.6                           |                                |             |                                            | 71       |  |

| 6 |                               |                                |             | LERANCE                                    | 73       |  |

|   | 6.1                           | Passiv                         | ve Fault T  | olerance Strategy                          | 73       |  |

|   |      | 6.1.1  | Training  | with Dropout                              | 74  |

|---|------|--------|-----------|-------------------------------------------|-----|

|   |      | 6.1.2  | SNN To    | lerance to Multiple Faults                | 78  |

|   | 6.2  | Active | Fault To  | lerance Strategy                          | 80  |

|   |      | 6.2.1  |           | ault Tolerance in the Output Layer        | 80  |

|   |      | 6.2.2  | Active F  | ault Tolerance in the Hidden Layers       | 80  |

|   |      |        | 6.2.2.1   | Offline Self-Test                         | 81  |

|   |      |        | 6.2.2.2   | Online Self-Test                          | 83  |

|   |      |        | 6.2.2.3   | Recovery Mechanisms                       | 84  |

| 7 | A SI | PIKING | NEURAI    | . NETWORK HARDWARE IMPLEMENTATION         | 87  |

|   | 7.1  | The C  | onvolutic | onal Node                                 | 87  |

|   |      | 7.1.1  | The Cor   | volutional Unit                           | 88  |

|   |      |        | 7.1.1.1   | Unit Parameters                           | 89  |

|   |      |        | 7.1.1.2   | The Convolution Operation                 | 91  |

|   |      |        | 7.1.1.3   | Global Leakage                            | 91  |

|   |      |        | 7.1.1.4   | Rate Saturation Mechanism                 | 91  |

|   |      |        | 7.1.1.5   | Output Event Generation & Traffic Control | 92  |

|   |      | 7.1.2  | The Rou   | ıter                                      | 93  |

|   |      | 7.1.3  | The Cor   | figuration Block                          | 94  |

|   | 7.2  | The E  | xperimen  | t                                         | 95  |

|   |      | 7.2.1  | The Pok   | er-Card Symbols Dataset                   | 95  |

|   |      | 7.2.2  | The Cor   | volutional SNN                            | 95  |

|   |      | 7.2.3  | The Exp   | erimental Setup & Results                 | 96  |

|   | 7.3  | Puttin | g the Ha  | rdware in the Loop                        | 97  |

| 8 | CON  | CLUSI  | ONS       |                                           | 101 |

|   | 8.1  | Thesis | Contribu  | ations                                    | 101 |

|   | 8.2  | Future | e Perspec | tives                                     | 103 |

|   |      |        |           |                                           |     |

BIBLIOGRAPHY

105

## LIST OF FIGURES

| Figure 2.1 | A spike                                                   | 11 |

|------------|-----------------------------------------------------------|----|

| Figure 2.2 | The dynamics of spike generation.                         | 11 |

| Figure 2.3 | Cause-Effect relationship between fault, error and        |    |

|            | failure                                                   | 19 |

| Figure 3.1 | Intrinsic Firing Patterns of Cortical Neurons             | 28 |

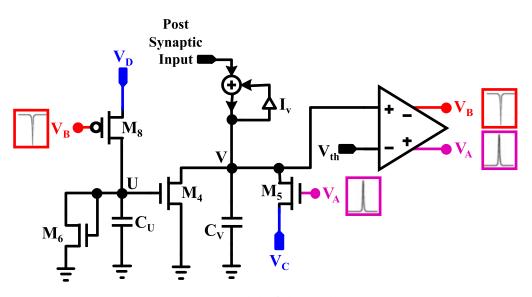

| Figure 3.2 | Transistor-Level Implementation of the Spiking            |    |

|            | Neuron Circuit                                            | 31 |

| Figure 3.3 | High-Level Model of the Spiking Neuron Circuit .          | 31 |

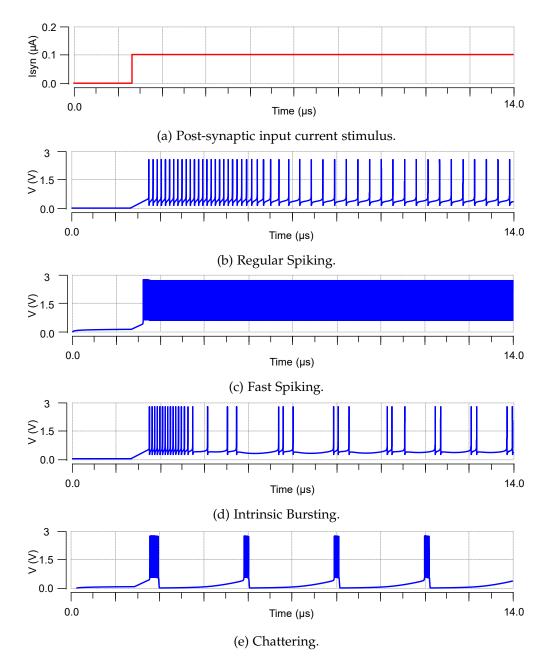

| Figure 3.4 | Output Spike Train Patterns of Neuron                     | 32 |

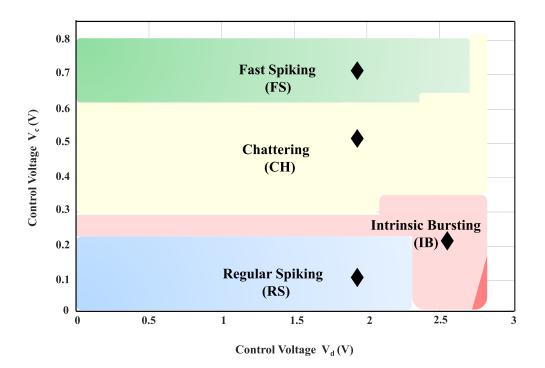

| Figure 3.5 | Approximate areas in the control voltages space           |    |

|            | $V_c$ - $V_d$ that produce the different firing patterns. |    |

|            | The diamond points correspond to the nominal              |    |

|            | control voltages combinations used to produce             |    |

|            | each firing pattern.                                      | 33 |

| Figure 3.6 | BIST Architecture                                         | 34 |

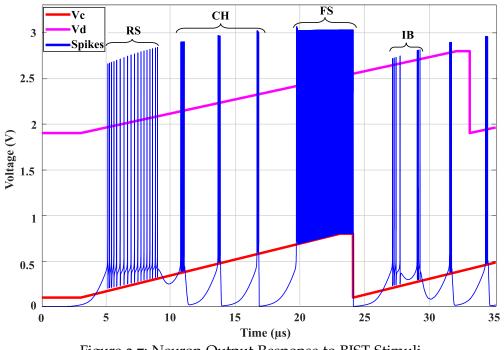

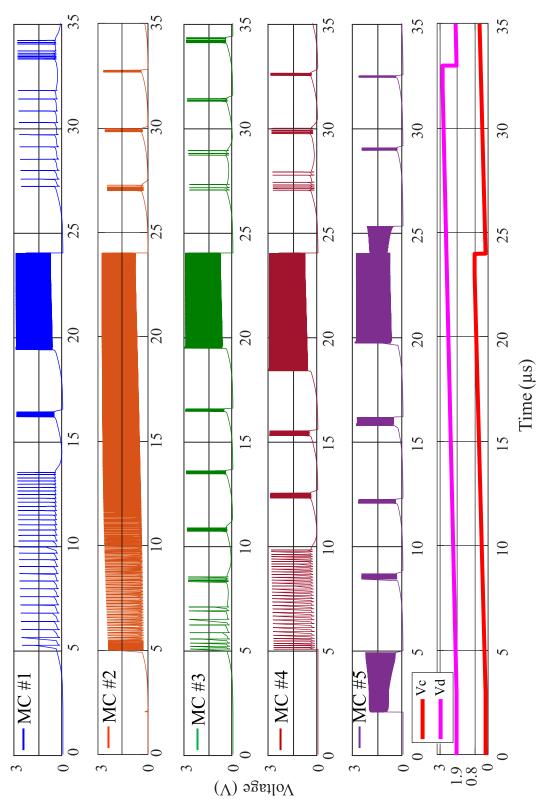

| Figure 3.7 | Neuron Output Response to BIST Stimuli                    | 35 |

| Figure 3.8 | Monte Carlo Analysis Showing the Neuron Output            |    |

|            | Response to BIST Stimuli for 5 Runs                       | 37 |

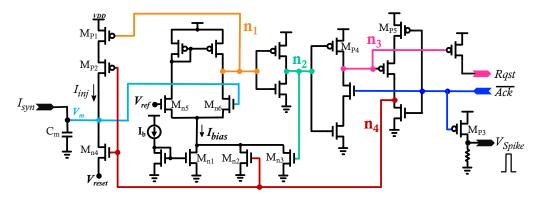

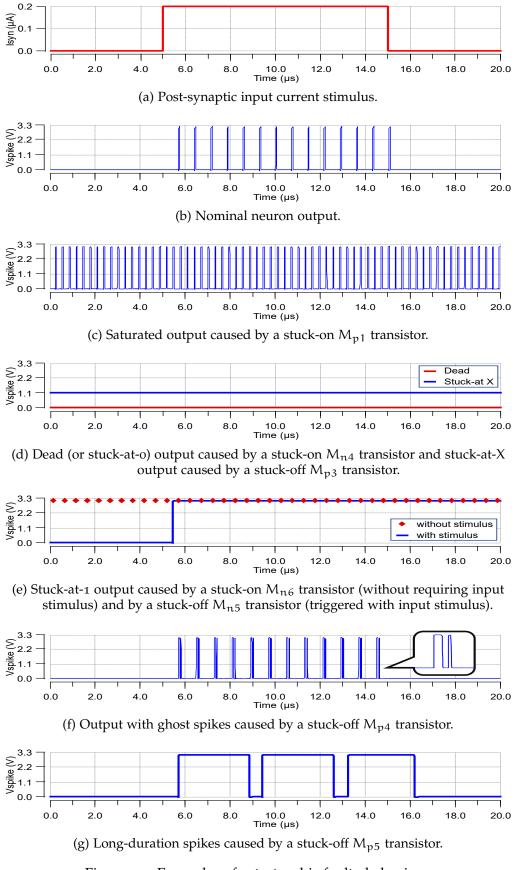

| Figure 4.1 | I&F Neuron                                                | 42 |

| Figure 4.2 | Examples of catastrophic faulty behaviors                 | 45 |

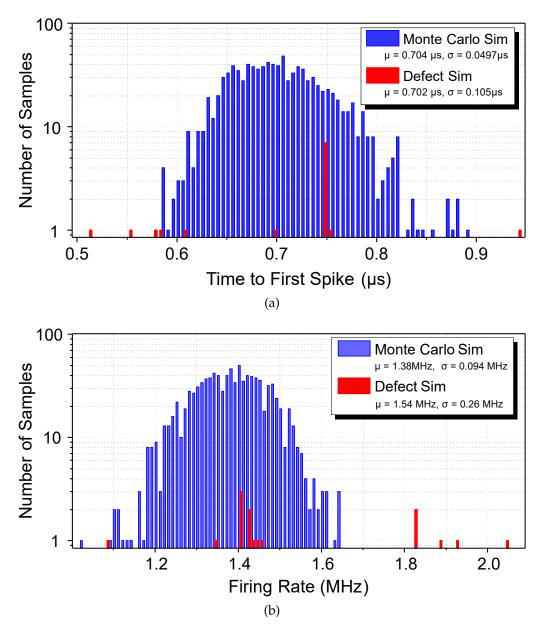

| Figure 4.3 | Histograms of timing variations.                          | 47 |

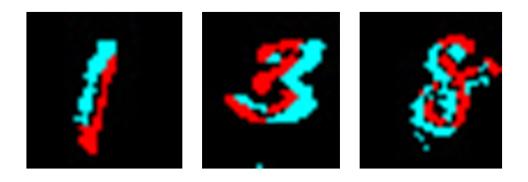

| Figure 5.1 | Samples of N-MNIST saccades snapshots in 2-D              |    |

|            | format. Black regions indicate no events, red indi-       |    |

|            | cates ON events, and blue indicates OFF events            | 53 |

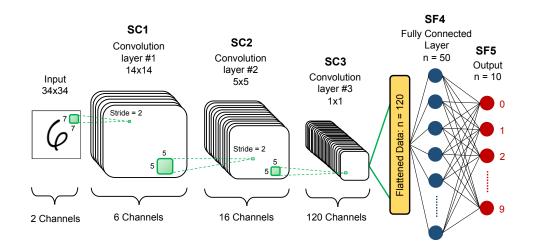

| Figure 5.2 | Architecture of the SNN for the N-MNIST dataset.          | 54 |

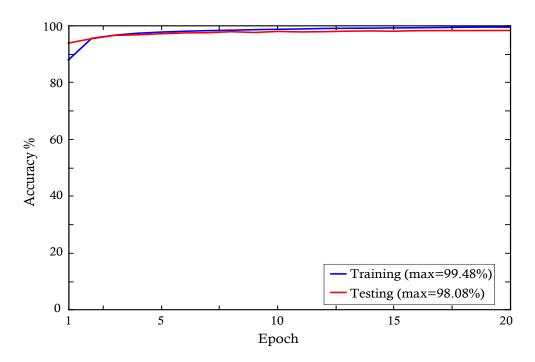

| Figure 5.3 | Learning Curve of the N-MNIST SNN                         | 54 |

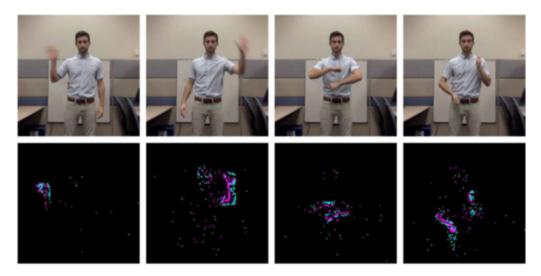

| Figure 5.4 | <b>TOP:</b> a video frame of an individual performing     |    |

|            | a few gestures from the dataset, from left to right:      |    |

|            | right-hand wave, left-hand wave, arm roll and air         |    |

|            | drums. <b>Bottom:</b> A 2-D representation of the same    |    |

|            | video frame above but in spiking form [64]                | 55 |

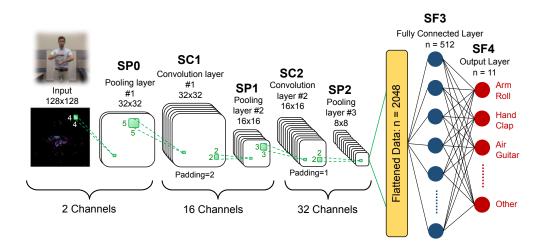

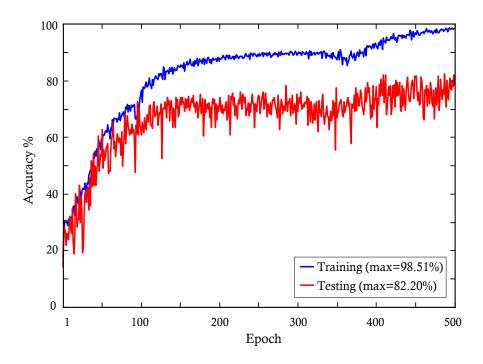

| Figure 5.5 | Architecture of the SNN for the DVS-gesture dataset.      | 56 |

| Figure 5.6 | Learning Curve of the DVS-gesture SNN                     | 56 |

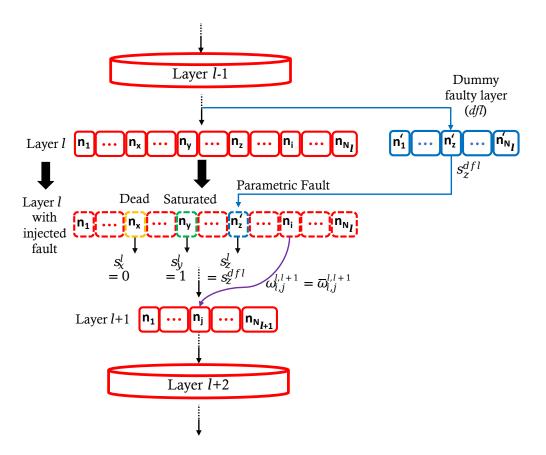

| Figure 5.7 | Fault injection methodology                               | 59 |

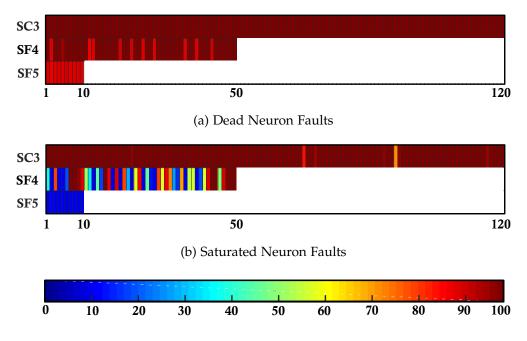

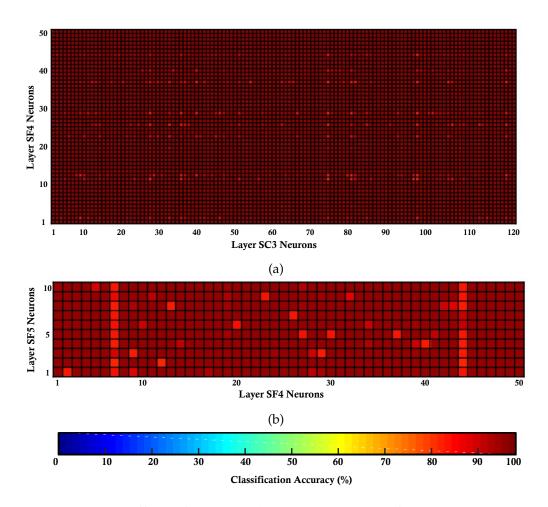

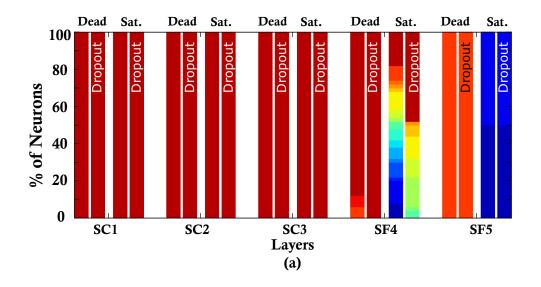

| Figure 5.8  | Effect of dead and saturated neuron faults on the N-MNIST SNN classification accuracy in the last 3 |    |

|-------------|-----------------------------------------------------------------------------------------------------|----|

|             | layers.                                                                                             | 60 |

| Figure 5.9  | Effect of dead and saturated neuron faults on the                                                   |    |

|             | N-MNIST SNN classification accuracy                                                                 | 61 |

| Figure 5.10 | Effect of integration faults on the last 3 layers of                                                |    |

|             | the N-MNIST SNN                                                                                     | 62 |

| Figure 5.11 | Effect of threshold perturbation faults on the last 3                                               |    |

|             | layers of the N-MNIST SNN                                                                           | 63 |

| Figure 5.12 | Effect of refractory period faults on the last 3 layers                                             |    |

|             | of the N-MNIST SNN.                                                                                 | 64 |

| Figure 5.13 | Synaptic weights values between SC3 and SF4                                                         | 65 |

| Figure 5.14 | Synaptic weights values between SF4 and SF5                                                         | 65 |

| Figure 5.15 | Effects of a dead synapse fault on synaptic con-                                                    |    |

| 0           | nections between (a) layers SC3-SF4 and (b) layers                                                  |    |

|             | SF4-SF5                                                                                             | 66 |

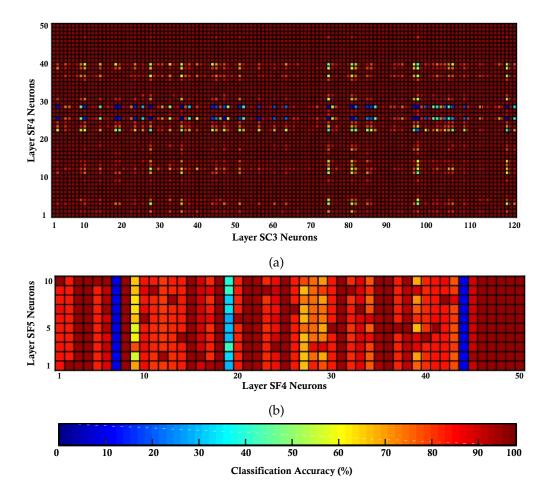

| Figure 5.16 | Effects of a negatively-saturated synapse fault on                                                  |    |

| -           | synaptic connections between (a) layers SC3-SF4                                                     |    |

|             | and (b) layers SF4-SF5                                                                              | 67 |

| Figure 5.17 | Effects of a positively-saturated synapse fault on                                                  |    |

| 0           | synaptic connections between (a) layers SC3-SF4                                                     |    |

|             | and (b) layers SF4-SF5                                                                              | 68 |

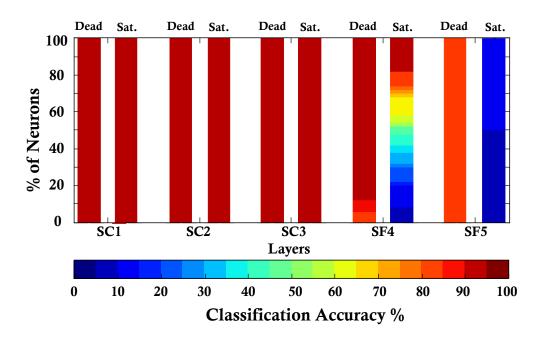

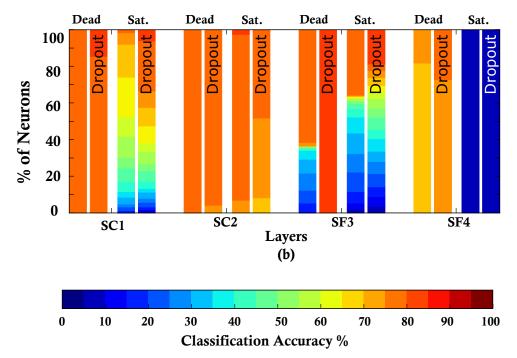

| Figure 5.18 | Effect of dead and saturated neuron faults on the                                                   |    |

|             | DVS-gesture SNN classification accuracy.                                                            | 69 |

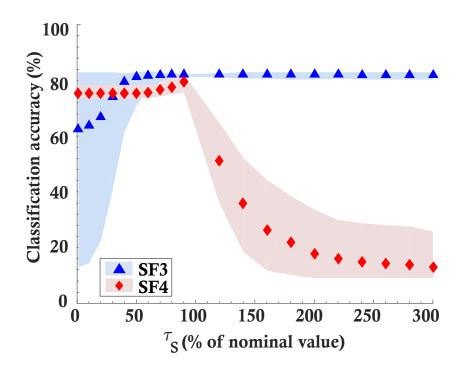

| Figure 5.19 | Effect of integration faults on the last 2 layers of                                                |    |

| 0           | the DVS-gesture SNN.                                                                                | 71 |

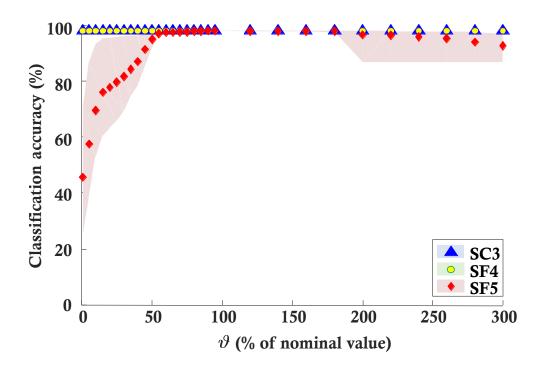

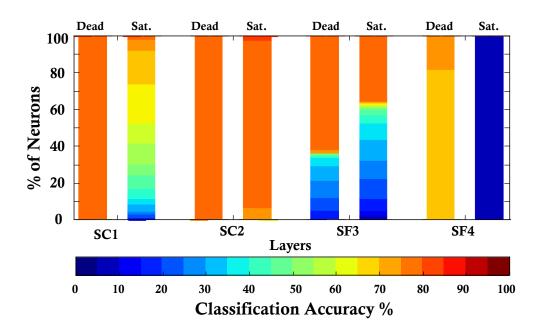

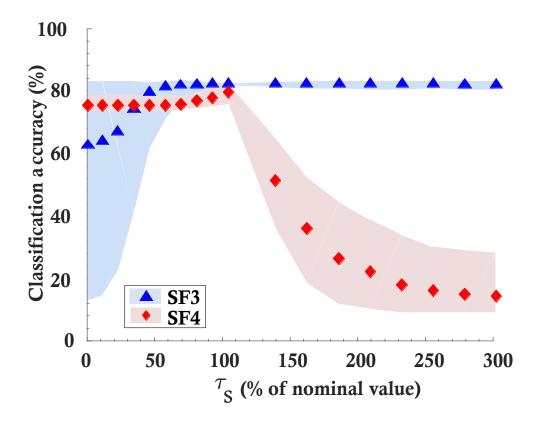

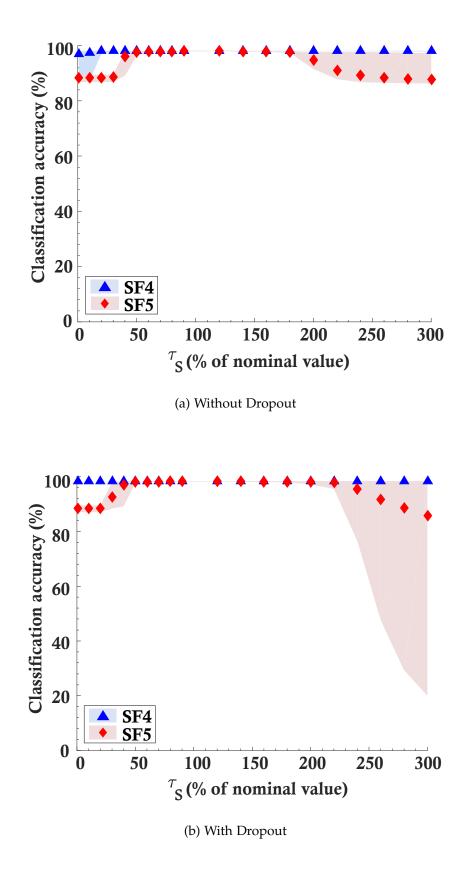

| Figure 6.1  | Effect of neuron faults on classification accuracy                                                  |    |

| C           | with and without dropout for: (a) N-MNIST SNN,                                                      |    |

|             | and (b) DVS-gesture SNN                                                                             | 75 |

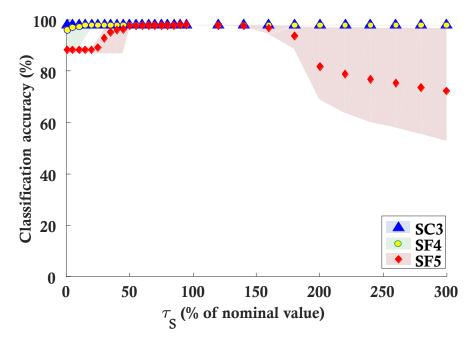

| Figure 6.2  | Effect of neuron timing variations for the N-MNIST                                                  |    |

| C           | SNN                                                                                                 | 76 |

| Figure 6.3  | Effect of neuron timing variations for the DVS-                                                     |    |

|             | gesture SNN                                                                                         | 77 |

| Figure 6.4  | Fault tolerance for multiple fault scenarios with                                                   |    |

|             | regular standard training vs. training with dropout.                                                | 79 |

| Figure 6.5  | TMR at the output layer.                                                                            | 80 |

| Figure 6.6  | Offline self-test scheme                                                                            | 82 |

| Figure 6.7  | Online self-test scheme                                                                             | 83 |

| Figure 6.8  | I&F neuron design showing the recovery operation                                                    |    |

|             | at neuron-level.                                                                                    | 85 |

| Figure 7.1  | The convolutional Node                                                                              | 88 |

| Figure 7.2  | The convolutional Unit                                                                              | 88 |

|             |                                                                                                     |    |

| Figure 7.3  | A conceptual figure showing the process of reading           |    |

|-------------|--------------------------------------------------------------|----|

|             | input events from the FIFO by the <i>controller block</i> .  | 90 |

| Figure 7.4  | The change in the state of the neuron with the               |    |

|             | incoming spikes. The red lines represent the ef-             |    |

|             | fect of the leakage mechanism, and T <sub>R</sub> represents |    |

|             | the refractory period that stops the neuron from             |    |

|             | spiking too soon                                             | 92 |

| Figure 7.5  | Block diagram of the destination-driven router               | 94 |

| Figure 7.6  | Generation of the poker card symbols dataset: (a)            |    |

|             | Picture taken with a frame-driven camera. (b) 2-D            |    |

|             | image obtained by collecting events in a 5ms win-            |    |

|             | dow [125]. The red square represents the 32x32               |    |

|             | window that shows the centered used for the sym-             |    |

|             | bols dataset.                                                | 95 |

| Figure 7.7  | Schematic block diagram of the convolutional SNN             |    |

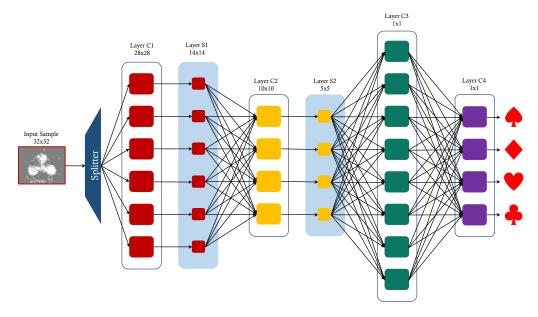

| 0           | used for this experiment.                                    | 96 |

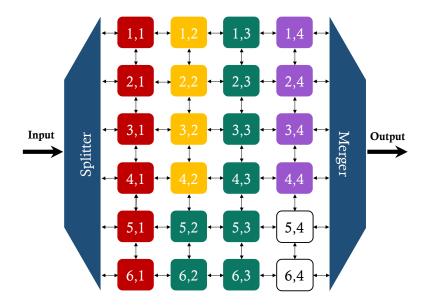

| Figure 7.8  | Schematic of the 2-D mesh implementation of the              |    |

| 0           | convolutional SNN on the FPGA. Each box rep-                 |    |

|             | resents a convolutional node in the network. The             |    |

|             | numbers indicate the address of the node in the              |    |

|             | mesh $(y,x)$ and the colors represent the different          |    |

|             | layers of the network.                                       | 97 |

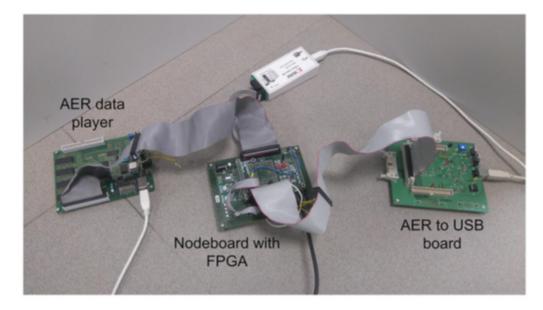

| Figure 7.9  | The experimental setup used for the convolutional            |    |

| 0           | SNN in [124]                                                 | 98 |

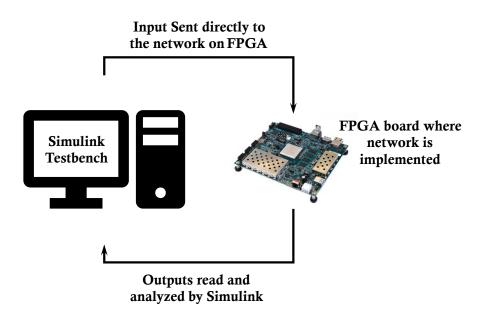

| Figure 7.10 | Hardware-in-the-Loop setup of the Xilinx FPGA                |    |

| <u> </u>    | board                                                        | 98 |

|             |                                                              | -  |

## LIST OF TABLES

| Table 4.1 | Catastrophic faulty behaviors resulting from defect |    |  |  |  |

|-----------|-----------------------------------------------------|----|--|--|--|

|           | simulation                                          | 43 |  |  |  |

## $A\,C\,R\,O\,N\,Y\,M\,S$

- ADC Analog-to-Digital Converter

- AER Address Event Representation

- AI Artificial Intelligence

- ANN Artificial Neural Network

- ASIC Application Specific Integrated Circuit

- ATE Automated Test Equipment

- BER Bit-Error Rate

- BIST Built-In Self-Test

- **CMOS** Complementary MOS

- CNN Convolutional Neural Network

- CPU Central Processing Unit

- DAC Digital-to-Analog Converter

- DNN Deep Neural Network

- DPR Dynamic Partial Reconfiguration

- DVS Dynamic Vision Sensor

- ECC Error Correction Code

- FIFO First-In-First-Out

- FIT Failure-in-Time

- FPGA Field Programmable Gate Array

- GPU Graphic Processing Unit

- HDL Hardware Description Language

- HIL Hardware-in-the-Loop

- I&F Integrate-and-Fire

- IC Integrated Circuit

- IoT Internet-of-Things

- MAC Multiply-and-Accumulate

- MC Monte Carlo

- NN Neural Network

NVM Non-Volatile Memory

**OpAmp** Operational Amplifier

- PDK Process Design Kit

- PLL Phase-Locked Loop

- QNN Quantized Neural Network

- **RRAM Resistive Random-Access Memory**

- RTL Register-Transfer Level

- SAR Successive-Approximation Register

- SAT satisfiability

- SEU Single Event Upset

SLAYER Spike LAYer Error Reassignment

- SNN Spiking Neural Network

- SPI Serial Peripheral Interface

- SRAM Static Random Access Memory

- SRM Spike-Response Model

- STDP Spike Timing-Dependent Plasticity

- STL Software Test Libraries

- TMR Triple Modular Redundancy

- TPU Tensor Processing Unit

- VHDL Very High-Speed Integrated Circuit Hardware Description Language

- VLSI Very Large Scale Integration

# INTRODUCTION

"If the brain were so simple we could understand it, we would be so simple that we couldn't."

- Emerson M. Pugh

#### 1.1 PREFACE

Understanding how the human brain works and building a machine that can match its computing power and efficiency has been a major force driving computer science research for decades. Nowadays, computers have reached remarkable performance levels in routine information processing such as basic math, and they even sometimes surpass human capacity in terms of computational speed and memory storage. However, the human brain still has an undeniable edge that is yet to be matched by a computer in non-routine tasks such as reasoning, awareness, problem solving, and learning from experience.

The first approach was a top-down strategy that looked at solving cognitive tasks algorithmically, i.e., mimicking the function but not the structure, and the von Neumann architecture quickly became the standard platform for this solution. The other approach took inspiration from biology for a bottom-up strategy and tried to imitate the structure of the biological brain in the hope of creating a machine that can think.

The earliest definitions of Artificial Intelligence (AI) were depicted in the mid-20<sup>th</sup> century when *Alan Turing* proposed the stored-program concept [1], [2]. He described an abstract machine that consists of an infinite memory strip and a scanner that moves through the memory, reads its contents, and modifies it according to a program of instructions also stored in memory, with the implication that if the machine operates on, it would modify and improve its own program. He went on to describe an "intelligent machine" as one that can learn from experience, and that the possibility of letting the machine alter its own instructions is the way to provide this mechanism.

The Turing Machine was perhaps the earliest design of a distributedprocessing system, and the inspiration from which Artificial Neural

#### 2 INTRODUCTION

Networks (ANNs) were eventually designed. However, his ideas could not be further exploited until the 1970s when Very Large Scale Integration (VLSI) technologies were developed. With the computing revolution that followed that era, ANNs began to regain attention.

#### 1.1.1 *AI Hardware Accelerators*

Today, AI has invaded our everyday lives affecting the way we work and spend our free time. Deep learning algorithms [3], and machine learning in general, are increasingly dominating the computer industry with applications that perform fundamental tasks like speech recognition, computer vision, and natural language processing, all the way to robotics, Internet-of-Things (IoT), autonomous self-driving vehicles, smart healthcare, etc. In all these applications, AI algorithms rely on hardware cores for performance acceleration in one form or another. AI hardware accelerators originally made use of existing technologies and traditional processors, such as general-purpose Central Processing Units (CPUs) and Graphic Processing Units (GPUs) [4], and to this day, the actual processing typically runs on giant servers in the cloud using CPU or GPU clusters. However, this hardware is too large to fit inside a portable device and it needs far more power than a device battery can provide.

Take IoT edge devices as an example; edge computing technology aims at pushing the execution of AI algorithms away from the cloud side and closer to the user side, i.e., the edge. Achieving this goal will contribute many advantages to the existing paradigm, e.g., provide availability of the application even in the absence of an internet connection, avoid latency, save network bandwidth which is overly occupied with the moving of data back and forth between the user and the cloud, and offer a much needed privacy since the data would be handled locally.

Compared to the human brain that has a neuron density of around 10,000/mm<sup>2</sup> and consumes approximately 10<sup>-11</sup> Joules per spike [5] -which means it runs on about 20 Watts-, CPUs are estimated to be about 10<sup>8</sup> less efficient in terms of size and energy consumption. In addition, several AI applications require a real-time response, as is the case with autonomous vehicles; an application running in constantly changing conditions with data coming from cameras, radars, accelerometers, sensors, etc. In the presence of this huge amounts of data, performing inference or on-line learning with a Neural Network (NN) running in software on a CPU is not an option. All these restrictions, along with other more technical challenges, such as the von Neumann bottleneck, also known as the memory-wall problem, and the approaching end of Moore's law [6], have made it crucial to find alternative architectures. Even with AI

accelerators like GPUs and Field Programmable Gate Arrays (FPGAs) [7] which perform far better than CPUs for AI related tasks, over one magnitude of cost-energy-performance improvements can be obtained with Application Specific Integrated Circuits (ASICs) [8], [9].

#### 1.1.2 Neuromorphic Computing

Neuromorphic computing, a term introduced by *Carver Mead* in the early 1990s [10], is the technology that uses special purpose VLSI silicon ANN implementations that resemble -or are inspired from-biology. Unlike the traditional von Neumann architecture that adopts a central processing system where a logic core performs computations on data fetched from memory, neuromorphic computing distributes the computational load and the memory among a multitude of elements.

Mainstream neural modeling nowadays is mostly digital and done at software-level, which is convenient since digital simulations offer precise and noise-free outputs. However, this paradigm ignores the fact that neural computing in the brain, which ANNs are essentially trying to emulate, is analog and noisy in nature. Biological NNs perform tremendous high-speed parallel computations in the presence of noise. They are highly adaptable and are even capable of exploiting noise in the environment to enhance computations [11], all the while consuming very little power and occupying a small space. In contrast, even the most powerful supercomputers cannot simulate neural connectivity in real time [12], [13].

Hence, it was only natural to look for something more suited to the objective in hand, and this was when neuromorphic technology started to appear in the spotlight. Silicon implementations provide a compromise between biological NNs and digital computers in terms of power and space, in addition to being far faster than biology [14]. While conventional ANNs fall under this description as well, the term "neuromorphic" usually refers to Spiking Neural Networks (SNNs).

Today, there exist many hardware neuromorphic chips either in digital, mixed analog-digital, or purely analog form. Some famous examples include: IBM's **TrueNorth** chip [15], Furber's **SpiNNaker** chip [16], MIT's **Eyeriss** [17], and Intel's **Loihi** chip [18]. These chips offer compact designs that incorporate large numbers of neurons and synapses with a very low power consumption and have been used to demonstrate various simple AI applications. However, their user base still consists mostly of universities and industrial research groups [19]. Before neuromorphic technology can move on to the actual industry field and take over the role dominated by mature conventional ANNs, many obstacles would have to be overcome.

For example, SNNs cannot be trained using standard learning techniques like the back propagation algorithm. They also need benchmark data sets in spiking form, which are not readily available yet. The specific advantages of SNNs, as well as the challenges they face, will be further discussed in Chapter 2.

#### 1.1.3 Is AI Hardware Fault-Tolerant?

A major preoccupation nowadays is the trustworthiness of AI systems. This includes privacy, avoidance of unfair bias, resilience to adversarial attacks, hardware dependability, etc. AI applications to test-related tasks have been extensively studied over the past decades [20], [21], including on-chip NNs as a Built-In Self-Test (BIST) engine for mapping low-cost measurements to chip-level pass/fail 1-bit decisions [22]. However, the "inverse" problem of testing and reliability of AI hardware has been customarily overlooked.

Biological NNs have remarkable error resilience and fault-tolerance capabilities. Not only can the brain tolerate a finite number of faults in the neurons and synapses, but it is also capable of regenerating or rewiring network elements to make up for larger damage. Modeled after the immensely parallel architecture and operation principles of biological NNs, both conventional ANNs and spike-based SNNs are assumed to be inherently as fault-tolerant as their biological counterparts. Moreover, both ANNs and SNNs usually contain more computational units than the minimum requirements of a certain cognitive task, a property known as over-provisioning [23], which allows for a certain degree of robustness [24].

However, arguing that this assumption is true based only on architecture resemblance to biology or over-provisioning is somewhat imprudent. In fact, many recent experiments have shown that AI hardware accelerators are limited by the constraints and imperfections of the VLSI technologies and are vulnerable to hardware-level faults resulting from manufacturing defects, process variations, aging, and Single Event Upsets (SEUs).

With the foreseen industrialization and high-volume production of hardware NNss in the coming years, special attention must be paid to the fault-tolerance aspect of AI hardware. Given that several targeted applications are safety-critical and mission-critical for which AI hardware accelerators must meet the functional safety standards regulated by every application domain, e.g., ISO 26262 for automotive and IEC 61508 for industrial systems, testing strategies specific to hardware NNs remains a topic that is largely unexplored [25].

But why does this need to be a special case? If a hardware NN is basically a VLSI circuit, either analog or digital, why can't standard testing and fault tolerance techniques apply directly and be enough? The answer to this question is the motivation behind the work carried out in this thesis.

#### 1.2 MOTIVATION

Typically, post-manufacturing testing in the VLSI industry aims at detecting manufacturing errors and is done per manufactured chip. In high-volume production, testing is performed on Automated Test Equipment (ATE) and needs to be completed in a few seconds. When it comes to safety- and mission-critical applications, testing would also need to be performed in the field concurrently with the operation or in idle times, in order to detect latent defects, aging, etc., calling for BIST capabilities to be added into the design to allow stand-alone evaluation of the health status of the chip without relying on external test instruments.

Testing strategies also vary depending on the type of the Integrated Circuit (IC), i.e., digital or analog. Testing of digital ICs is considered a mature field today [26], [27]. On the other hand, post-manufacturing testing for analog ICs still relies on measuring certain performance metrics of the circuit and comparing them to the nominal case [28], hence tests are still specific to the particular IC (e.g., Analog-to-Digital Converter (ADC), Digital-to-Analog Converter (DAC), Phase-Locked Loop (PLL), filter, Operational Amplifier (OpAmp), etc.), and specific to different architectures within each IC class (i.e., Successive-Approximation Register (SAR), pipeline,  $\Sigma\Delta$ , etc., architectures for the ADC class). BIST for analog ICs is not widespread since analog signal paths are sensitive and BIST circuitry tapping into them loads the IC and degrades the performance.

Like any other VLSI circuit, hardware NNs are prone to hardware faults that can happen any time during the chip's lifetime, and standard postmanufacturing testing strategies can technically be sufficient. State-ofthe-art deep ANNs comprise a multitude of layers of different types, i.e., convolution, pooling, fully connected, etc., tens of millions of synaptic weight parameters, and they perform a myriad of operations in a single forward pass. From a hardware perspective, this entails immensely dense designs, albeit with a certain degree of architectural modularity. Hence, intuitively, testing efficiency can be largely improved by exploiting the architectural particularities of hardware NNs and targeting only those fault scenarios that have a measurable effect on performance [29].

Most likely, post-manufacturing testing for digital NN implementations will not be any different than testing of regular digital ICs. However,

#### 6 INTRODUCTION

for purely analog NN implementations or implementations with analog sub-blocks, e.g., analog neurons, new post-manufacturing and BIST test strategies will need to be developed since, in the first place, it is not clear for specifications we should be testing. In addition, adapting testing strategies to each network type, architecture, or data type is an exhaustive task.

To this end, in the course of this thesis we investigated the possibility of global testing strategies and generic fault-tolerance techniques that can be applied to hardware SNNs, independent of the architecture, design, and data propagated through the network. The goal is to enable SNNs with fault tolerance capabilities against hardware-level faults. The followed methodology is discussed next.

#### 1.3 METHODOLOGY

To achieve our goal, we adopted a methodical approach of evaluating the robustness of a neural network against hardware-level faults, to which extent they affect the NN, and how they can be mitigated or bypassed. The approach comprises 3 main steps:

- 1. Simulation of faults injected at transistor level to understand how they affect the circuit.

- 2. Creating abstract fault models that can be used to test the network at system level.

- 3. Developing cost-effective fault tolerance mechanisms for SNNs.

At every step, the findings are evaluated and exploited to optimize the next.

#### 1.3.1 Fault Injection

The first step towards our goal is fault injection experiments. Fault injection is the intentional introduction of faults in a system to examine their effects [30]. While not really adequate for improving the system performance or debugging design errors, fault injection and simulation is a very effective way of testing the resilience and fault-tolerance capability of a system against known faults. In general, fault injection experiments can be helpful in evaluating the functional safety of a system with respect to the standard regulations of the respective domain.

Performing hardware-level fault injection experiments in hardware NNs, carried out at transistor-level or at system-level, can be a helpful tool so as to:

- ✤ Associate behavioral errors with hardware faults.

- Determine which faults are catastrophic and which are redundant.

- Build a compact fault model that can test the network regardless of its architecture, thereby reducing the post-manufacturing test costs.

- Identify critical layers and components within the network, so that appropriate strategies for hardening, self-test, error mitigation, error recovery, fault-tolerance, etc. can be followed.

- Understand the propagation of faults across layers. For example, it is shown that the normalization layers reduce the impact of faults by averaging fault values with adjacent correct values.

- Develop effective design-for-test techniques that exploit the hardware particularities.

#### 1.3.2 Fault Modeling

After performing fault-injection experiments at transistor-level, we exploit the results in order to build a fault model and a fault taxonomy that is specific to SNNs.

For the fault model to be efficient, it needs to be defined with certain characteristics. The fault model should be:

- Consistent with manufacturing defects that can affect the chip, i.e., with the transistor-level faults.

- Defined at the behavioral level to allow the acceleration of fault simulation for deep SNNs.

- Abstract, meaning that it can be used to test any SNN regardless of its architecture or implementation.

A fault model of this style allows the acceleration of large-scale fault injection experiments for deep SNNs. This way, the vulnerabilities of the network can be assessed, and measures can be taken to bypass or mitigate their effects.

#### 1.3.3 Fault Tolerance

The final step in this work is proposing some fault tolerance techniques in compliance with the results of the fault simulation experiments. But before we can do that, we need to illustrate what fault tolerance actually

#### 8 INTRODUCTION

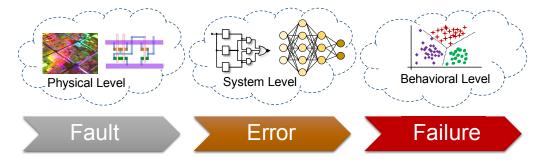

means, and how it differs from other terms often encountered in the literature.

A system is said to be *reliable* if it performs correctly with high probability in the presence of faults under previous stated conditions, meaning that statistics and probability theory are needed to estimate the reliability of a system. Reliability is a quality over time that is associated with failures that happen unexpectedly. Other popularly used terms are *robustness* and *error resilience*, which describe the tolerance of the system to noisy inputs and inexact computations.

*Fault tolerance*, on the other hand, is a property of the system that guarantees its proper operation in the event that one or more faults have manifested themselves in the system. This means that fault tolerance entails taking action to detect and bypass or counteract the effects of faults.

#### 1.4 THESIS STRUCTURE

In this thesis, we explore the inherent resiliency aspects of hardware SNNs to hardware-level faults and propose cost-effective fault-tolerance techniques applicable to any SNN.

In Chapter 2, we review the literature on SNNs and the work done to make them fault tolerant. Then, we kick off the experiments by designing a behavior-oriented BIST for a biologically inspired analog neuron in Chapter 3. Afterwards, we move on to a more practically adopted neuron model in Chapter 4, where we perform defect-oriented testing that maps transistor-level faults in analog neuron implementations into behavioral-level fault models. In Chapter 5, these fault models are used to assess the resiliency of a complete network, demonstrating the experiment on 2 separate SNNs. We leverage the results of these experiments in Chapter 6 to develop a neuron fault tolerance strategy for SNNs, and we show the fault-tolerant SNN architecture. In Chapter 7, we show a hardware convolutional SNN designed to run on FPGAs, and which we use as a platform to validate the ideas developed in this work. Finally, Chapter 8 concludes the work.

## 2 SPIKING NEURAL NETWORKS & THEIR FAULT TOLERANCE: A LITERATURE REVIEW

Despite all the impressive advances achieved by conventional ANNs, the human brain still excels in the most basic cognitive tasks. Originally a topic of interest in theoretical neurobiology and biophysics research, spiking neural networks were designed as an attempt to mimic the biological neural networks to enable the analysis of elementary processes of the brain. With the technological leap in AI and deep learning, neuromorphics and SNNs have come to the spotlight as a promising new paradigm that can possibly take deep learning to places it could not reach before.

In this chapter, we offer a basic literature review of the two pillar topics of this thesis: SNNs in hardware and previous efforts to make them fault tolerant.

#### 2.1 SPIKING NEURAL NETWORKS

A biological or an artificial neural network is made up of neurons connected in a sophisticated complex pattern through synapses. The neuron is the basic processing unit in a neural network, and according to the computational paradigm of their processing units, ANNs can be classified into three generations [31]. The first generation is based on the McCulloch-Pitts neurons, or the perceptrons. Built exclusively to give digital outputs, a multilayer perceptron is able to compute every boolean function with only one hidden layer. The second generation is based on neurons implementing an "activation function", such as the sigmoid function. Neural networks from the second generation can compute functions with analog inputs and outputs, which give them a more realistic essence than the first-generation networks if their output is thought of as representing the average firing frequency of a biological neuron. Nonetheless, functionality-wise, both generation models are very different from biological neural networks. Neurons in the brain communicate through discrete short electrical pulses called spikes. A typical neuron fires spikes at a frequency that is less than 100MHz, which means that a window of 20 - 30ms is needed only to compute the current firing rate [31]. However, experimental results have shown that a visual processing task can be completed in just 20 - 30ms, thus it was doubtful that biological neurons actually use the firing rate as a main coding scheme [32], [33]. Instead, it seemed that the timing of spikes plays an important role in neural coding [34].

These findings made way for a third generation of neural networks that uses spiking neurons as the basic element. Spiking neurons communicate -much like their biological counterparts- through spikes and code information in a spatio-temporal manner, making them more biologically realistic compared to the previous two models. In this section, we review the basic concepts of SNNs.

#### 2.1.1 The Spiking Neuron

The spiking neuron is the basic building block of neuromorphic systems and where most of the processing takes place. A spiking neuron is often described as an integrator with a threshold [35]. Instead of constantly firing, as in the case of first- and second-generation neurons, a spiking neuron accumulates inputs from preceding neurons, and if a certain number of spikes occur within a specific time frame, it generates a spike of its own.

#### 2.1.1.1 The Spike

The Spike, also known as the *action potential*, is the primary means of communication in between spiking neurons. It is a short electrical pulse of around 100mV amplitude and a 1 - 2ms duration, that represents an abrupt momentary change in the state of the neuron. Spikes are stereotypical events, shown in Fig. 2.1, that do not change form as they propagate from pre-synaptic to post-synaptic neurons. Consequently, the shape of the spike carries no information. Instead, the timing of each spike and the length of the inter-spike intervals are the key aspects of information coding in SNNs.

#### 2.1.1.2 The Membrane Potential

The membrane potential is the voltage that describes the state of the spiking neuron at any given time. In the quiescent state with no input spikes, the membrane potential of a typical biological neuron is strongly polarized at a resting voltage of about -65mV. Incoming spikes evoke

Figure 2.1: A spike

a positive or a negative change in the membrane potential, referred to as the *post-synaptic potential*. An excitatory input will reduce the negative polarization of the membrane potential, i.e., depolarize it, while an inhibitory input will hyperpolarize the membrane voltage even further.

#### 2.1.1.3 Spike Generation

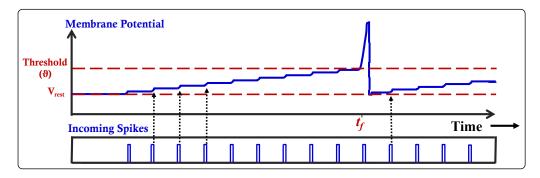

The mechanism of spike generation is conceptually illustrated in Fig. 2.2. When an input spike arrives, the membrane potential increases for a moment before it starts decaying again. This decay of the membrane voltage between incoming spikes is known as the *leakage*, which plays a significant role in the temporal correlation between spikes. Temporal correlation is a crucial concept which facilitates the possibility of exploiting the temporal information contained in real-world sensory data [31].

After the neuron spikes, the membrane potential returns to the resting value and stays there until the next input spike comes along. The neuron cannot fire again until a certain period has passed, which is known as the *absolute refractory period*. In response to an input stimulus, spiking neurons can emit a chain of action potentials, called a spike train, that can have regular or irregular intervals.

Figure 2.2: The dynamics of spike generation.

#### 2.1.2 Neural Coding Schemes

The concept of mean firing rate dates back to the 1920s [36], where Adrian *et al.* proved that the firing rate of certain neuron types in the muscles is related to the strength of the applied stimulus. For so long after that, the firing rate was thought to be the principle neural coding scheme. However, neuroscience experiments have demonstrated that for high-speed neural processing, the timing characteristics of individual spikes and spike trains cannot be ignored [32].

In SNNs, Coding schemes can be classified into [37]:

- 1. **Rate Coding Schemes**: converting the activity level of neurons into a firing rate, which does not benefit from sparse spikes inherent to biological systems [38]. The neuron firing rate can be calculated according to:

- The spike count: averaging over time.

- ✤ The spike density: averaging over several runs.

- The population activity: averaging over the activity of several neurons that act together.

- 2. **Spike Coding Schemes**: Coding strategies that are based on the timing of individual spikes. There are many timing aspects through which neurons in the brain communicate information, including:

- Time to first spike: in systems that require ultra-fast information processing, such as tactile and olfactory systems, the delay between the beginning of the input stimulus and the first output spike was shown to carry enough information [39], [40].

- Phase coding: where neurons can encode information in the phase of a spike with respect to some background oscillations.

- Rank order coding: information is coded in the order of output spikes in populations of neurons [41].

- Correlation and synchrony: a coding scheme based on the observation that neurons that encode pieces of the same information object fire synchronously.

Nonetheless, the distinction between rate coding and spike coding scheme is not very sharp, i.e., some of the codes that are viewed as timing codes can also be interpreted as variations of a rate code. For example, the time-to-first-spike coding scheme is related to the firing rate scheme since a neuron that spikes early would be expected to have a high firing rate, and vice versa.

#### 2.2 SPIKING NEURAL NETWORKS IN HARDWARE

#### 2.2.1 Neuron Models

There are numerous models of spiking neurons used in neuromorphic systems [42], most of which perform the accumulation and firing function, albeit with different mechanisms. In the simplest deterministic model, the neuron is assumed to fire whenever its membrane potential reaches a threshold ( $\vartheta$ ). The fired spike travels along the synapse that has an efficacy, or weight ( $\omega$ ).

Spiking neuron models can be grouped into broad categories based on their degree of complexity and their resemblance to biology in structure or function [43]. The question of which neuron model to use usually depends on the type of problem at hand [44]. These categories are:

#### Biologically-Plausible Models:

These models are built to explicitly model the behaviors observed in biological neurons and are mostly used for accurate simulations of biological neural systems. One of the most famous models of this category is the classical Hodgkin-Huxley model [45], which uses fourdimensional nonlinear differential equations to describe neural behavior. Other models like the Morris-Lecar model [46] try to simplify things by reducing the dimensions of the nonlinear equations. In any case, these models are often used to simulate a small number of neurons since they are usually very expensive to implement.

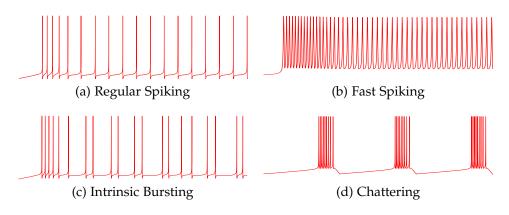

#### Biologically-Inspired Models:

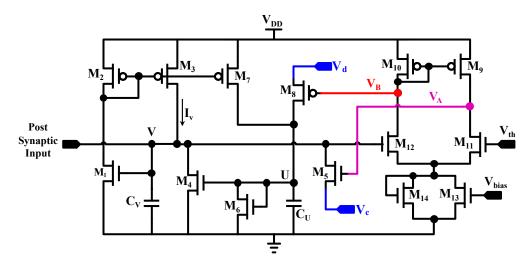

Biologically inspired models, on the other hand, try to replicate the neural behaviors without the obligation of emulating the physical activity of biological systems. Consequently, they are much simpler than the biologically plausible models in terms of computations and implementations and can therefore be more efficient in modeling large-scale systems. There are many models in this category that are very common in neuromorphic literature, including the FitzHugh–Nagumo model [47], [48] and the popular Izhikevich model [49], which can reproduce biologically accurate behavior with a set of two-dimensional ordinary differential equations.

#### Integrate-and-Fire Models:

Another category of spiking neuron models especially suited for minimizing computational complexity is the Integrate-and-Fire (I&F) models. These models can vary in complexity from the basic integration and firing function to something approaching the complexity level of the Izhikevich model. While not biologically realistic, I&F models are still complex enough to incorporate spiking dynamics. Beside the basic I&F model, there are also the leaky I&F model, the resonate-and-fire model [50], and the quadratic I&F model [51]. More complex implementations also exist, such the Adaptive Exponential Integrate and Fire model [52].

Another model that can technically fall under this category, although it performs the neural behavior in the form of response kernels rather than differential equations, is the Spike-Response Model (SRM) [34]. The SRM is a generalized form of the I&F model and will be discussed in more details in Chapter 5.

#### 2.2.2 Address Event Representation

In the attempt to build neural networks that resemble the human brain, the communication problem becomes evident. Compared to digital systems where each gate is connected to a relatively small number of outputs, a typical neuron can carry outputs to thousands of targets. This massive interconnection is easily built in biology using 3-D structures. However, it becomes a challenge when brought to 2-D silicon substrates [53]. On the other hand, a typical neuron fires at a rate ranging from 1 - 10 kHz, which means that a cluster of neurons can have a collective firing rate in the kHz to low MHz range; a rate that modern digital systems can effortlessly hold. Therefore, in neuromorphic systems, communication is usually carried out between clusters of neurons by time-multiplexing spikes on a single channel. In neuromorphic systems, this is done using the Address Event Representation (AER) protocol [54].

AER is a communication protocol that makes use of the fact that spikes carry no information other than the fact that neuron i fired at time  $t_f$ , and sends out only this information. Each neuron in a cluster is assigned a unique address and every generated spike is encoded into a sequence that indicates the identity (or address) of the neuron that fired that spike and the time at which it fired. This way, huge synaptic connections can be avoided, and the hardware resources can be efficiently allocated where they are needed.

There are multiple approaches to the implementation of AER eventbased systems that exploit the features of a hardware neural network [55]. The simplest form is a basic AER scheme where the whole network can share a single communication channel, and all events are processed through an external block that controls their traffic. Other schemes distribute this multiplexing among several points in the network. A more sophisticated scheme puts a router block within each cluster module that is responsible for directing traffic between modules. Using this scheme can be helpful in large-scale systems because it allows a 2-D mesh architecture where each module is only connected to its immediate neighbors. The router-based scheme will be further explained in the case study presented in Chapter 7.

#### 2.3 NEUROMORPHIC TECHNOLOGY PROSPECTS AND CHALLENGES

Judging by the rise in research activity over the past decade [43], neuromorphic computing is becoming mainstream with every passing day. This is mainly because of the many advantages that this technology promises, which could potentially take neuromorphic technology far beyond what has been accomplished by conventional ANNs. These advantages can be summed up into:

# 1. Power efficiency.

Much like biological neural networks, SNNs are built for eventdriven information processing. Information from the outside world is usually sparse, which means it can be processed in a way much more efficient than the frame-based approach of conventional ANNs. ANNs perform data sampling at predefined time steps that ignores the speed of incoming information. SNNs on the other hand process spikes as they come, meaning that the network is only working when there is something to be processed, otherwise, no computations are taking place. This event-driven operation is the basis of the huge power savings promised by neuromorphic computing and could make neuromorphic systems the go-to solution for applications such as IoT at the edge and autonomous vehicles. For example, IBM's TrueNorth Chip is a Complementary MOS (CMOS) ASIC made up of 5.4 billion transistors that make up 1 million neurons and 256 million synapses, all the while consuming only 73 mW.

# 2. Speed of computation.

Information in the brain is transmitted in the form of spikes propagating from layer to layer as soon as they are generated by a neuron. In contrast, conventional ANNs compute the output of neural layers sequentially, introducing significant delays while each layer waits for the output of the previous one to be computed. SNNs incorporate time into their model of operation together with the state of neurons and synaptic weights, thus information flows in the form of spike trains propagating between neurons asynchronously. When combined with event-based sensors, this leads to *pseudosimultaneous* information processing, where a first estimation of the output can be calculated at the output layer almost immediately after the introduction of the first input spikes [56].

# 3. Predisposition to bio-inspired unsupervised learning.

While supervised learning techniques have become the standard for ANNs, to this day, exact mechanisms of supervised learning in biology are still a mystery and presumably not the primary source of learning. The Hebbian process of learning proposed by Hebb in 1949 was the first attempt at explaining how learning occurs in the brain. The Hebbian plasticity principle, and the more comprehensive version known as Spike Timing-Dependent Plasticity (STDP) [58], [59], entail that the change in the weight of a synapse is proportional to the timing between pre- and post-synaptic spikes. Since SNNs are designed to use spike timing to code information, it is due to make full use of these unsupervised biologically inspired learning algorithms.

# 4. Inherent robustness to noise.

As discussed in Section 2.1.1.1, spikes have a standard shape that holds no information, making the presence of a spike the most important aspect. Moreover, every neuron generates its own set of spikes instead of just passing the same signal along, hence there is a kind of regeneration of signals at every neuron [60]. This gives SNNs an advantage similar to that observed in digital systems, that is their robustness to noise.

But with great promise comes great challenges. Despite all its promising prospects, neuromorphic technology still faces many obstacles that need to be addressed before it can be implemented in real world applications. The main obstacles that face neuromorphic technology today and stop it from realizing its full potential are discussed next.

# 1. Benchmark datasets in spiking form.

While it is counted as a drawback of SNNs that they cannot achieve high accuracy levels on typical benchmark datasets such as the MNIST handwritten digits dataset [61] or the CIFAR image dataset [62], the real issue is with the nature of these datasets. These datasets were created in a frame-based format which is fundamentally different from the way SNNs operate. The conversion of typical datasets into a spiking format is usually inefficient, since frame-based format holds a huge amount of redundant data that is simply not present in event-based formats. In the recent years, a new direction is being followed of directly collecting datasets in spiking format using Dynamic Vision Sensors (DVSs), such as the N-MNIST dataset (a neuromorphic version of the MNIST dataset) [63], the Dvs-Gesture dataset [64], along with other benchmark datasets that are optimized for visual recognition [65], [66].

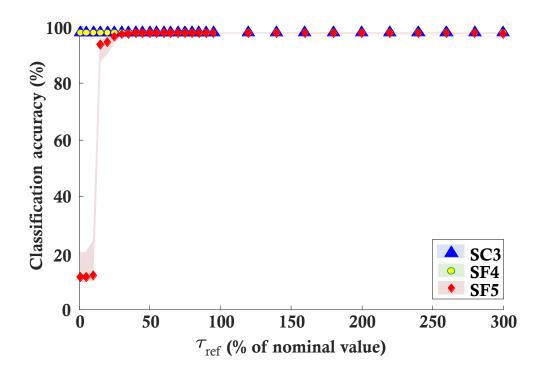

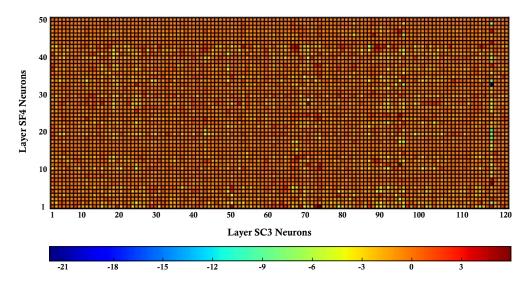

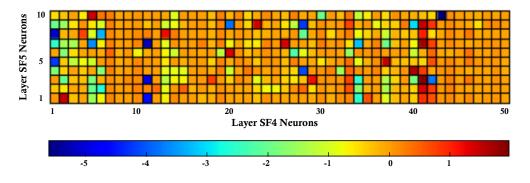

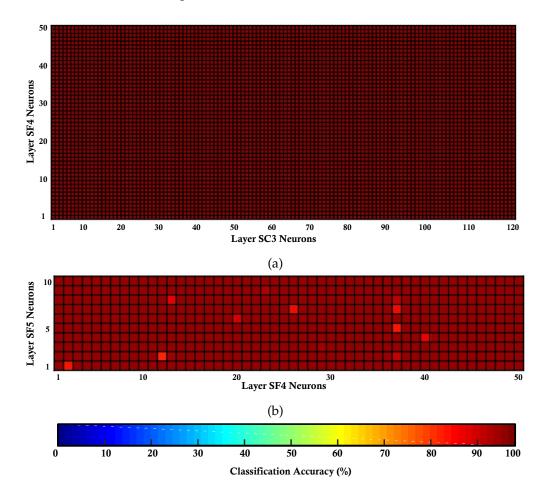

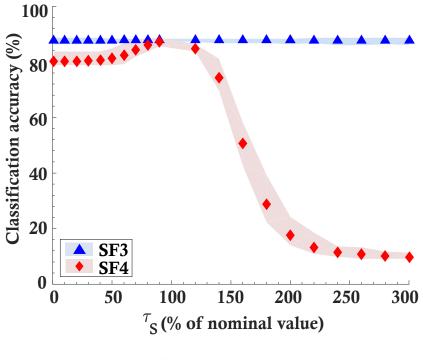

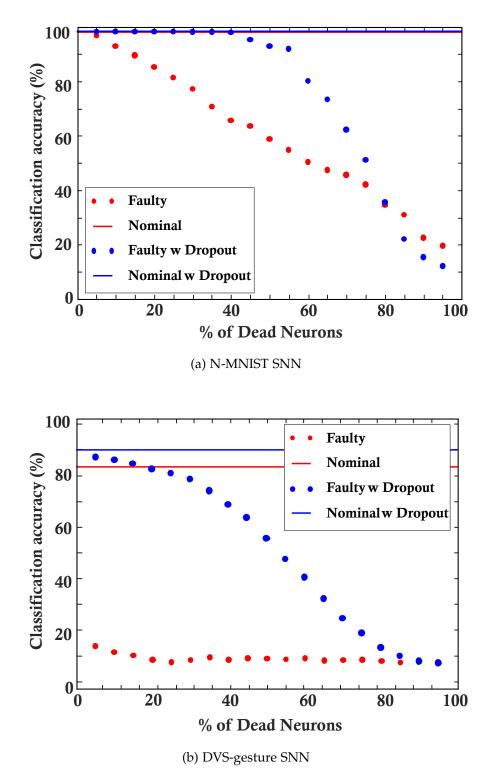

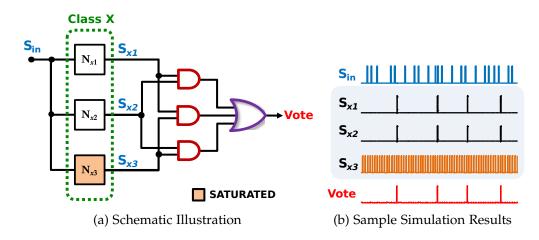

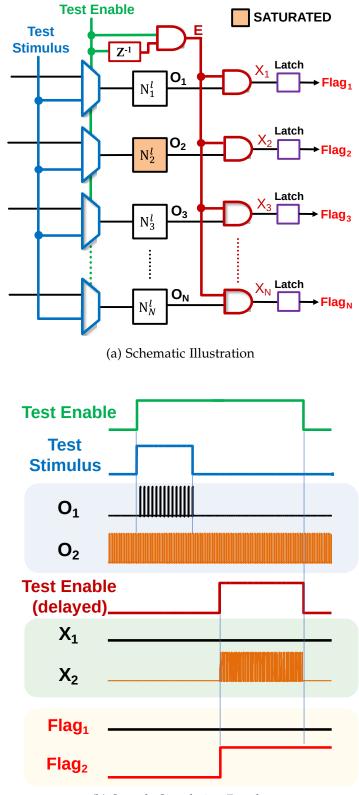

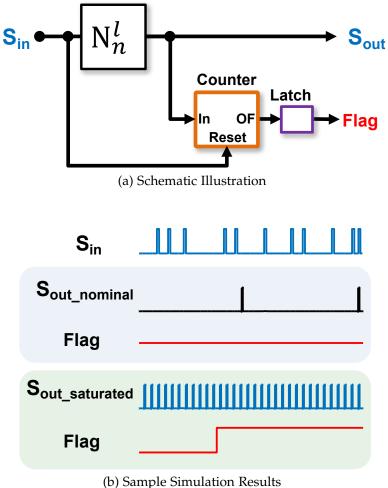

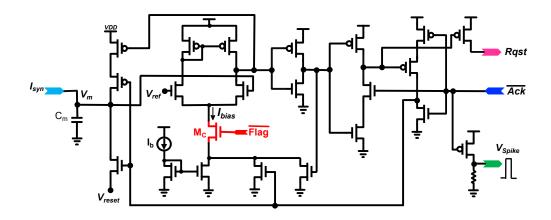

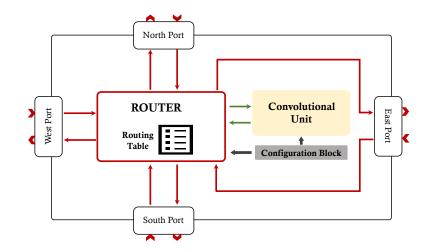

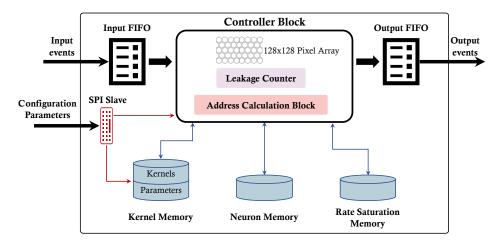

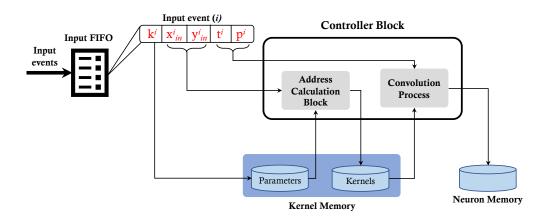

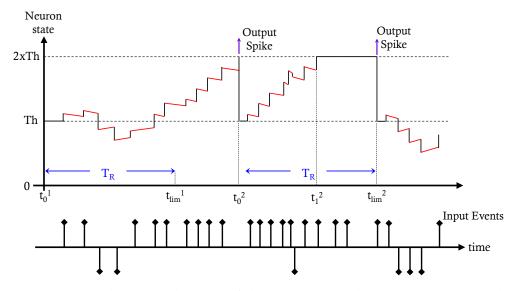

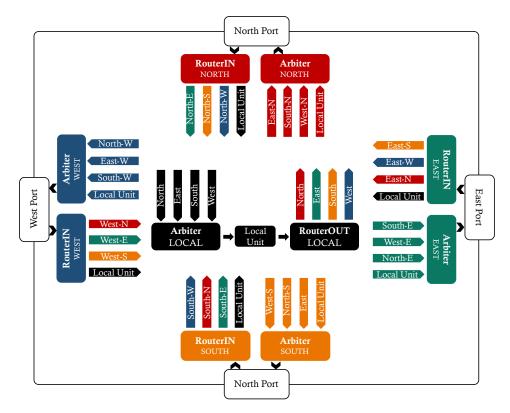

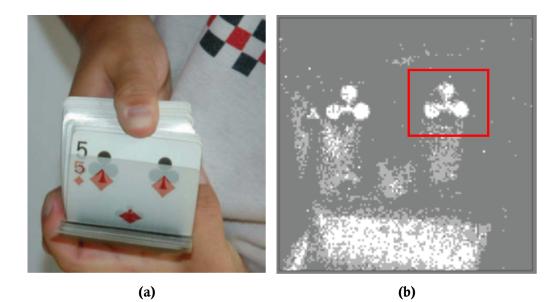

# 2. Efficient spike-based learning algorithms.