### Liveness analysis techniques and run-time environment for memory management of dataflow applications

Benjamin Dauphin

#### ▶ To cite this version:

Benjamin Dauphin. Liveness analysis techniques and run-time environment for memory management of dataflow applications. Embedded Systems. Institut Polytechnique de Paris, 2021. English. NNT: 2021IPPAT004. tel-03682675

#### HAL Id: tel-03682675 https://theses.hal.science/tel-03682675

Submitted on 31 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Liveness Analysis Techniques and Run-Time Environment for Memory Management of Dataflow Applications

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à Télécom Paris

École doctorale n°626 Institut Polytechnique de Paris (ED IP Paris) Spécialité de doctorat : Réseaux, Informations et Communications

Thèse présentée et soutenue à Sophia Antipolis, le 16 mars 2021, par

#### Benjamin Dauphin

#### Composition du Jury:

Laure Petrucci

Professeur des Universités, Université Paris 13 Présidente

Robert De Simone

Directeur de recherche, INRIA Sophia Antipolis Rapporteur

Jean-François Nezan

Professeur des Universités, INSA Rennes Rapporteur

Samuel Thibault

Maître de conférences, INRIA Bordeaux – Sud-Ouest Examinateur

Stéphane Mancini

Maître de conférences, Université Grenoble Alpes Examinateur

Andrea Enrici

Ingénieur de recherche, Nokia Bell Labs France Examinateur

Renaud Pacalet

Directeur d'étude, Télécom Paris Directeur de thèse

Ludovic Apvrille

Professeur, Télécom Paris Co-directeur de thèse

#### Remerciments

Je tiens à remercier toutes les personnes qui ont rendu ce travail possible.

En premier lieu mon directeur de thèse Renaud Pacalet, mon co-directeur Ludovic Apvrille, ainsi qu'Andrea Enrici et Rabéa Ameur-Boulifa. Vos conseils, nos échanges, votre intérêt et votre suivi de ce travail ont façonné ce qu'il est devenu aujourd'hui. Merci pour votre accompagnement.

Je souhaite également remercier les membres du jury. Les relecteurs, Robert de Simone et Jean-François Nezan pour le temps passé à la relecture de ce manuscrit et nos échanges ayant permis son amélioration. De même, je remercie Laure Petrucci, Samuel Thibault et Stéphane Mancini pour l'intérêt porté à mon travail et pour son évaluation.

J'adresse également un remerciement à toute l'équipe du LabSoC, notamment à Minh, Matteo, Emna, Maysam, Letitia, Le Van, Tullio. J'ai vraiment apprécié le temps passé ensemble, nos conversations à la pause déjeuner, et tout ce qui fait la vie de ce laboratoire de recherche.

Enfin, je remercie ma famille pour leur soutien et leurs encouragements toutes ces années, et sans qui je n'aurais jamais pu aller aussi loin.

#### Résumé substantiel

Cette thèse a été effectuée à Télécom Paris et a été financé par Nokia Bell Labs France. Les Bell Labs sont connus pour leurs recherches dans les domaines de l'informatique et de la télécommunication.

Dans cette thèse sont étudiées différentes techniques visant à la gestion des interblocages et de la saturation des capacités mémoires dans les systèmes embarqués.

Ce travail trouve sa motivation dans la complexification de l'architecture des systèmes informatiques au cours des dernières décennies, notamment avec la généralisation des architectures hétérogènes et Non-Uniform Memory Access (NUMA). Cette évolution se constate dans tous types de systèmes informatiques, de l'embarqué sur Multi-Processor System on a Chip (MPSoC) aux systèmes distribués pour le calcul haute performance (High-Performance Computing). Nous nous intéressons en particulier au problème de la saturation des capacités mémoires dans les systèmes embarqués utilisés pour le traitement numérique du signal (Digital Signal Processing). Nos contributions peuvent toutefois être utilisées pour d'autres types d'applications et de plateformes. Cette thèse apporte trois contributions.

La première contribution de la thèse, présentée dans le chapitre 3, consiste en une technique de prévention des interblocages se basant sur l'étude des cliques dans un type de graphes, les Memory Exclusion Graphs (MEG). Ces graphes représentent les buffers alloués en mémoire et leur possibilité d'allocation simultanée. La recherche de cliques comportant un ensemble de buffer dont l'allocation entrainerait une saturation de ressources mémoires permet de détecter des situations d'interblocages et de les prévenir en ajoutant des contraintes de précédence entre différentes tâches de la charge de travail. Ces contraintes de précédences sont ajoutées entre le consommateur d'un buffer de la clique et le producteur d'un autre buffer de cette même clique. L'ajout de la contrainte de précédence entraine une mise à jour du MEG et la recherche d'une nouvelle clique amenant à la saturation mémoire. Ce processus est répété jusqu'à qu'aucune clique correspondant à une saturation mémoire soit présent dans le MEG, garantissant l'impossibilité de saturation. Dans un objectif de minimisation de l'impact qu'entraine l'ajout d'une contrainte de précédence sur la durée d'exécution de la charge de travail, les tâches visées par cette

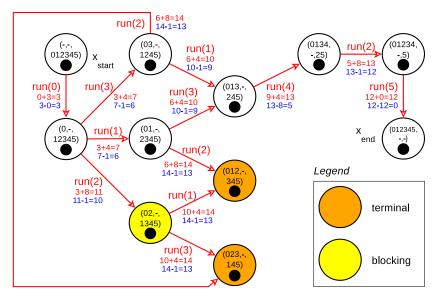

contrainte sont sélectionnées en fonction de leur date d'exécution limite.

Dans le chapitre 4 nous présentons la deuxième contribution, qui est une autre approche visant à résoudre les interblocages causés par la mauvaise gestion des ressources mémoires. Il s'agit d'une optimisation de l'analyse de vivacité convention-nellement utilisée pour l'étude de la saturation mémoire, permettant d'analyser des systèmes plus complexes en un temps réduit. Nous définissons un type d'automate appelé automate de contrôle, dont l'ensemble des états est un sous-ensemble de celui de l'automate conventionnel qui représente toutes les possibilités d'ordonnancement. Nous démontrons que l'analyse de ce sous-ensemble d'états est suffisante pour garantir l'absence d'interblocages, sans perte de précision par rapport à l'analyse conventionnelle. Cette réduction dans le nombre d'états à analyser permet de déployer l'analyse sur des systèmes plus complexes que ceux pour lesquelles l'approche conventionnelle est réalisable en un temps donné.

Ces deux contributions sont évaluées en les comparant à un outil issu de l'état de l'art dans le chapitre 5.

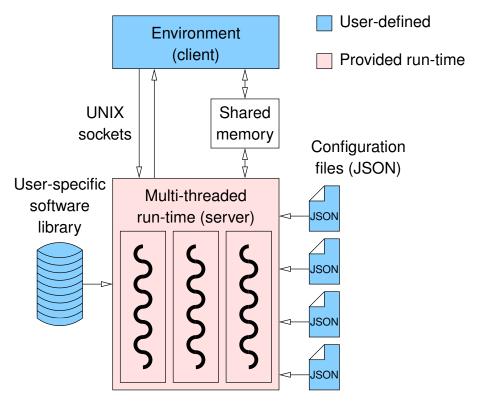

Le chapitre 6 détaille notre troisième contribution, correspondant à une mise en œuvre pratique de la deuxième contribution par le développement d'une technique d'évitement des interblocages utilisant les résultats de l'analyse de vivacité optimisée. Cette technique d'évitement a été intégrée à un environnement d'exécution expérimental, et peut également être intégrée à d'autres environnements d'exécutions issus de l'état de l'art. Nous présentons en détail l'architecture de notre environnement d'exécution, conçu pour fortement paralléliser l'exécution des fonctions de contrôle.

Pour conclure le chapitre 7 récapitule les différentes contributions, leurs limites et leurs possibilités d'améliorations. Nous proposons également plusieurs pistes de travaux futurs sur la base des contributions de la thèse.

# **Contents**

| C  | onten | ats                                             | 5  |

|----|-------|-------------------------------------------------|----|

| Li | st of | Figures                                         | 8  |

| Li | st of | Tables                                          | 10 |

| I  | Вас   | ckground                                        | 11 |

| 1  | Intro | oduction                                        | 13 |

|    | 1.1   | Modern Computing Platforms                      | 13 |

|    | 1.2   | Deadlocks                                       | 17 |

|    | 1.3   | Problem Statement                               | 18 |

|    | 1.4   | Thesis Contribution                             | 20 |

|    | 1.5   | Synopsis and Outline                            | 21 |

| 2  | Rela  | ated Work                                       | 23 |

|    | 2.1   | Introduction                                    | 23 |

|    | 2.2   | Models of Computation                           | 24 |

|    | 2.3   | Formalization of Scheduling Problems            | 34 |

|    | 2.4   | Liveness and Deadlocks                          | 38 |

|    | 2.5   | Run-Time Environments for Dataflow Applications | 45 |

|    | 2.6   | Conclusion                                      | 48 |

| II | Co    | ntributions                                                   | 51  |  |  |  |  |

|----|-------|---------------------------------------------------------------|-----|--|--|--|--|

| 3  | App   | Approximate Deadlock Prevention using Memory Exclusion Graphs |     |  |  |  |  |

|    | 3.1   | Introduction                                                  | 53  |  |  |  |  |

|    | 3.2   | Target Platform                                               | 54  |  |  |  |  |

|    | 3.3   | Applications and Workload                                     | 55  |  |  |  |  |

|    | 3.4   | Memory Shortage                                               | 59  |  |  |  |  |

|    | 3.5   | Conclusions and Limits                                        | 68  |  |  |  |  |

| 4  | Effic | cient Liveness Analysis                                       | 71  |  |  |  |  |

|    | 4.1   | Introduction                                                  | 71  |  |  |  |  |

|    | 4.2   | System models and design assumptions                          | 72  |  |  |  |  |

|    | 4.3   | Schedule Automaton                                            | 75  |  |  |  |  |

|    | 4.4   | Control Automaton                                             | 81  |  |  |  |  |

|    | 4.5   | Liveness Analysis of Automaton                                | 82  |  |  |  |  |

|    | 4.6   | Evaluation of Schedule and Control Automaton Analysis         | 85  |  |  |  |  |

|    | 4.7   | Mathematical Formalization                                    | 87  |  |  |  |  |

|    | 4.8   | Conclusion                                                    | 96  |  |  |  |  |

| 5  | Ехр   | erimental Evaluation                                          | 97  |  |  |  |  |

|    | 5.1   | Introduction                                                  | 97  |  |  |  |  |

|    | 5.2   | Implementation Details                                        | 98  |  |  |  |  |

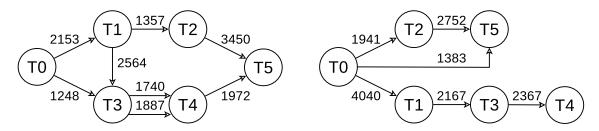

|    | 5.3   | Experimental Setup                                            | 99  |  |  |  |  |

|    | 5.4   | Minimal Supported Memory                                      | 100 |  |  |  |  |

|    | 5.5   | Permissiveness                                                | 101 |  |  |  |  |

|    | 5.6   | Computational Time                                            | 102 |  |  |  |  |

|    | 5.7   | Discussion                                                    | 104 |  |  |  |  |

| 6  | Run   | -Time Environment                                             | 107 |  |  |  |  |

|    | 6.1   | Introduction                                                  | 107 |  |  |  |  |

|    | 6.2   | Functionalities of a Run-Time Environment                     | 108 |  |  |  |  |

|    | 6.3   | Design Choices to Integrate the Deadlock Handling Policy      | 110 |  |  |  |  |

|    | 6.4   | Architecture of our Run-Time Environment                      | 112 |  |  |  |  |

|    | 6.5   | Conclusion                                                    | 129 |  |  |  |  |

| 7  | Conclusion |                              |     |  |

|----|------------|------------------------------|-----|--|

|    | 7.1        | Contributions of the Thesis  | 131 |  |

|    | 7.2        | Limitations and Improvements | 132 |  |

|    | 7.3        | Future Work and Perspective  | 133 |  |

|    |            |                              |     |  |

| Ш  | Bad        | ck matter                    | 137 |  |

| Ad | rony       | vms                          | 139 |  |

| Bi | bliog      | raphy                        | 143 |  |

# **List of Figures**

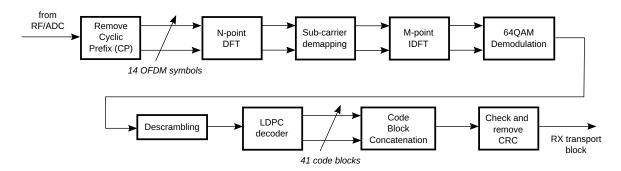

| 1.1 | 5G decoding chain (receiver side)                                                                                                   | 14 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

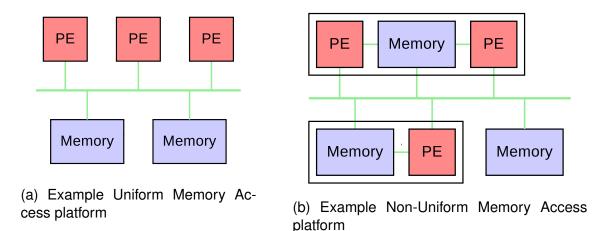

| 1.2 | Example memory architectures                                                                                                        | 16 |

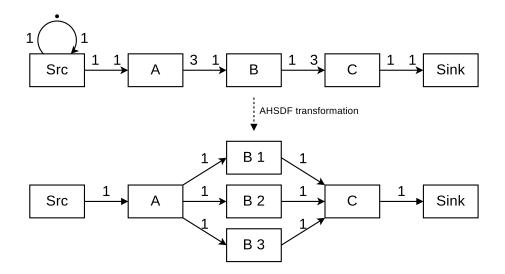

| 2.1 | Example of an application Synchronous Data Flow (SDF) graph and its corresponding Acyclic Homogeneous Synchronous Data Flow (AHSDF) |    |

|     | graph                                                                                                                               | 25 |

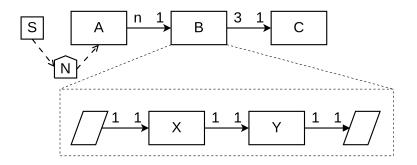

| 2.2 | Example of an application Parametrized & Interfaced Synchronous Data                                                                |    |

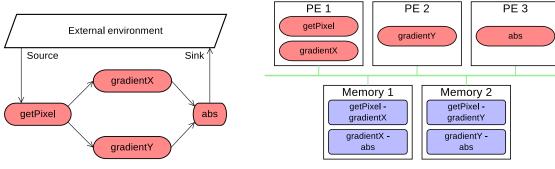

|     | Flow ( $\pi \text{SDF}$ ) graph. $S$ is a configuration actor, $B$ a hierarchical actor                                             | 28 |

| 2.3 | An example Petri net, before and after the firing of a transition                                                                   | 29 |

| 2.4 | Reachability graph of example Petri net from Figure 2.3                                                                             | 30 |

| 2.5 | Example Petri nets from different classes used to study sequential Re-                                                              |    |

|     | source Allocation System (RAS)                                                                                                      | 31 |

| 3.1 | Example logical architecture of a target platform                                                                                   | 54 |

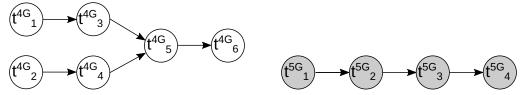

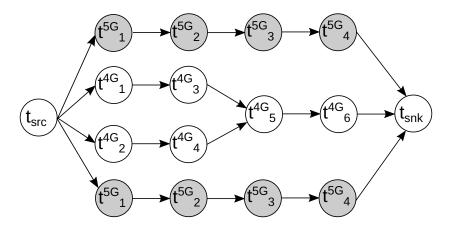

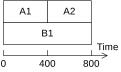

| 3.2 | Example applications' dependency graphs                                                                                             | 56 |

| 3.3 | Example workload composed of one iteration of the 4G application and                                                                |    |

|     | two concurrent iterations of the 5G application                                                                                     | 56 |

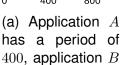

| 3.4 | Two example application extensions to a common period                                                                               | 57 |

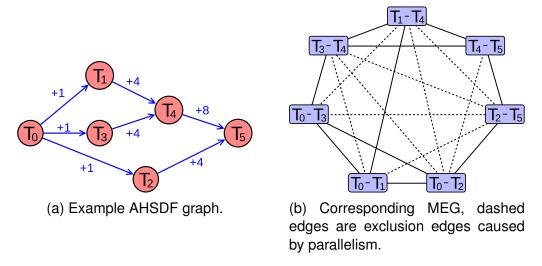

| 3.5 | Example AHSDF and its corresponding Memory Exclusion Graph (MEG).                                                                   | 61 |

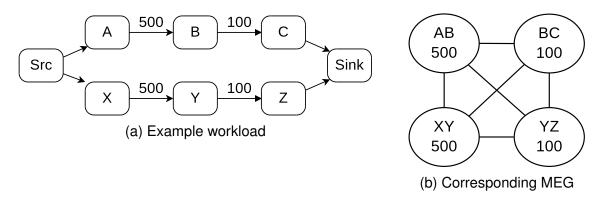

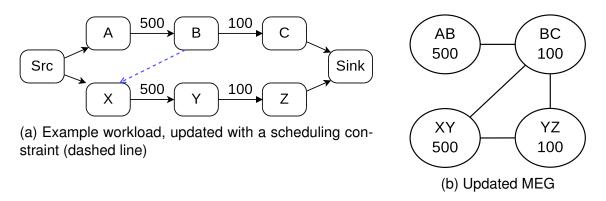

| 3.6 | Example applications, whose concurrent execution may cause a memory                                                                 |    |

|     | shortage                                                                                                                            | 64 |

| 3.7 | Updated applications, free of memory shortages                                                                                      | 65 |

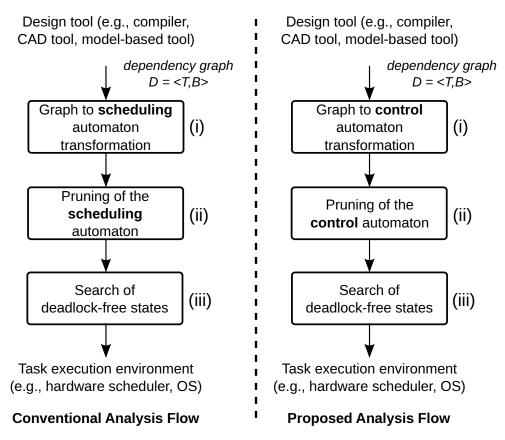

| 4.1 | The steps of liveness analysis                                                                                                      | 73 |

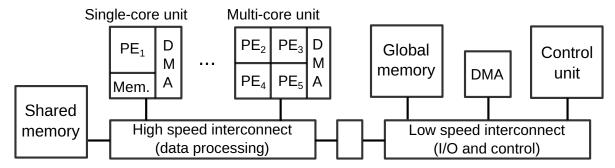

| 4.2 | Target architecture                                                                                                                 | 74 |

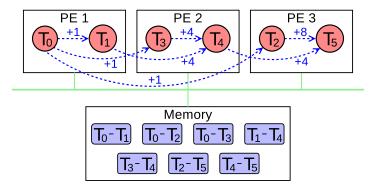

| 4.3 | Example AHSDF for a single-application, with mapping                                                                                | 75 |

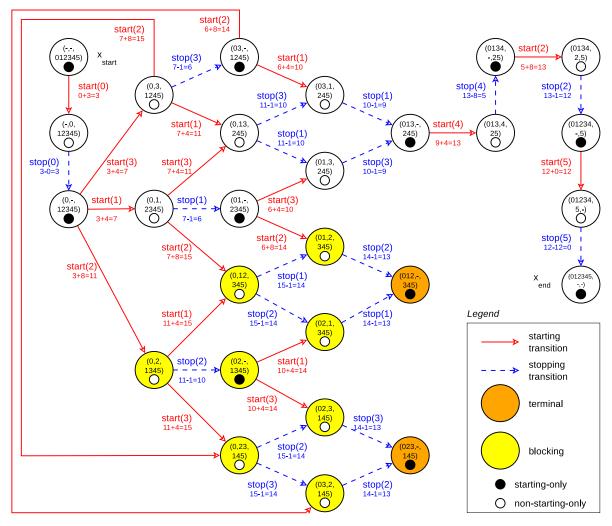

| 4.4 | Schedule automaton for example in Figure 4.3                          | 76  |

|-----|-----------------------------------------------------------------------|-----|

| 4.5 | Control automaton for Figure 4.3                                      | 81  |

| 5.1 | Two example applications used in our experiments. Numbers on edges    |     |

|     | represent buffer size                                                 | 99  |

| 6.1 | Example application and mapping                                       | 112 |

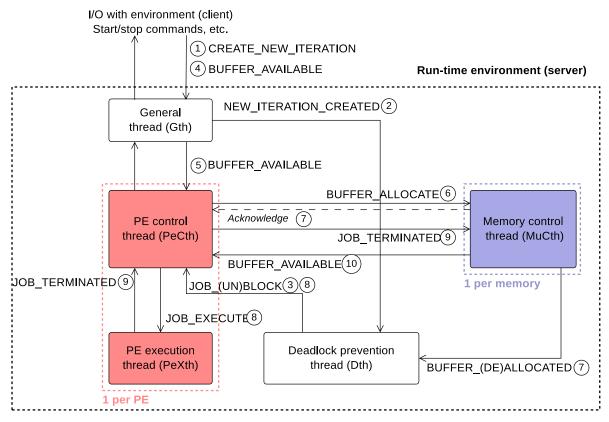

| 6.2 | Software architecture                                                 | 113 |

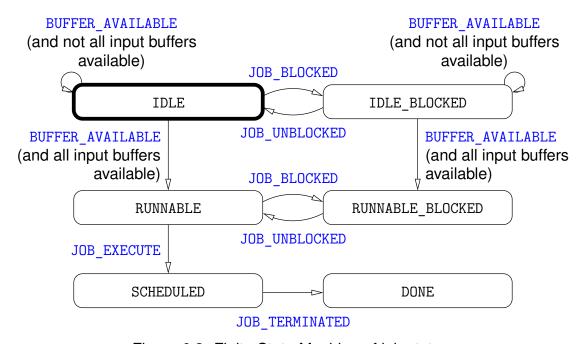

| 6.3 | Finite State Machine of job status                                    | 118 |

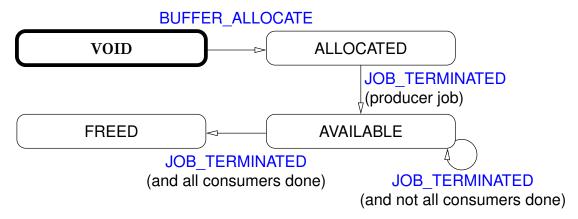

| 6.4 | Finite State Machine of buffer status                                 | 120 |

| 6.5 | Architecture of the server. Circled numbers correspond to the step in |     |

|     | which the event is sent in the example run                            | 121 |

# **List of Tables**

| 1.1 | Occurrence of deadlocks in our RAS                                                                                                            | 19       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | Comparison of a selection of deadlock handling tools and methodologies Run-time environments for task-based and dataflow-based applications . | 45<br>48 |

| 4.1 | Evaluation results for a test-bench of 3 workload types                                                                                       | 87       |

| 5.1 | Minimal supported memory size of the approximate approaches, in comparison to theoretical minimum of Contribution 2                           | 101      |

| 5.2 | Number of allowed schedules by approximate approaches, in comparison                                                                          |          |

|     | to the theoretical maximum of Contribution 2                                                                                                  | 102      |

| 5.3 | Computational time of the five approaches: three heuristics from memDAG,                                                                      |          |

|     | and our implementation of the first and second contributions                                                                                  | 103      |

# Part I Background

## Chapter 1

## Introduction

#### 1.1 Modern Computing Platforms

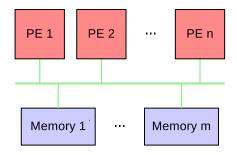

Today's heterogeneous multi-processor platforms embed tens of processing units such as general purpose Central Processing Units (CPUs), Digital Signal Processors (DSPs), Graphics Processing Units (GPUs) and dedicated hardware accelerators (e.g., Field Programmable Gate Arrays (FPGAs)). These platforms are used for real-time dataflow applications with high processing-power requirements in multiple domains: from the Digital Signal Processing (DSP) in wireless communication to image or video analysis in autonomous driving. These applications are subject to very large memory bandwidth and short memory latency constraints that often guide designers to adopt platforms with a Non-Uniform Memory Access (NUMA) architecture in which the memory resource is distributed over multiple, size-limited, physical memories. On one hand, these NUMA architectures offer designers the capability to meet memory bandwidth and latency constraints. On the other hand, memories are limited in size and computing nodes can usually access limited subsets of physical memories. This complicates the search for valid execution orders (schedules) for real-time dataflow applications as it introduces new sources for deadlocks.

This thesis is part of a collaboration between Télécom Paris and Nokia Bell Labs France. As such, the work of this thesis is focused on embedded systems for Digital Signal Processing. This thesis contributions could ideally be placed in the context of O-RAN software [3].

#### 1.1.1 Applications

Figure 1.1: 5G decoding chain (receiver side)

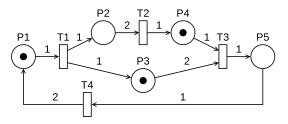

Dataflow applications are composed of a set of tasks representing different computations. The tasks are represented as the vertexes of a dependency graphs, in which edges represent precedence constraints and communication between tasks. For example, Figure 1.1 displays a 5G decoding chain in which the De-scrambling task will be executed after the 64 QAM Demodulation task, as the latter produces the input data used by the former.

Applications with multiple iterations can be analyzed as independent applications. It is also possible to analyze multiple iterations at the same time, which is interesting when some dependency constraints exist in (or can be added to) an application graph. For example if a task t in iteration n+1 should not be finished before t in iteration n, analyzing multiple iterations simultaneously reduces the complexity in comparison to treating the two iterations as independent.

#### 1.1.2 Evolution of the Architecture of Computing Systems

The steady increase in the complexity of applications and their performance requirement has led to significant evolution of the architecture of computing systems in the past decades. As they became more complex, modern computing systems also became harder to program.

#### From Homogeneity to Heterogeneity

The architecture of the first computing platforms, such as the ENIAC and the EDVAC had a single computational unit, allowing exclusively the execution of programs in a

fully sequential manner. The use of multiple computing units on a single platform quickly became an obvious way to increase computing performance, by allowing multiple computations to occur in parallel. This led to the rise of homogeneous architectures, architecture in which all computing units (or Processing Elements (PEs)) have the same capabilities, i.e., any task can run on any PE. Homogeneous architecture can potentially have PEs with different computing speed, such as having one PE being twice as fast as another. But homogeneous architecture have their limits, which have been challenged with the ever increasing demand for computing power. For example, it is not possible to increase the speed of general purpose CPUs indefinitely, physical constraints such as energy consumption and heat dissipation prevent to increase the frequency beyond a threshold. As such, the designers of computing systems have resorted to use more and more heterogeneous architectures over the years. For example heterogeneous embedded systems, called Multi-Processor Systems on a Chip (MPSoCs), feature processors of various types on a same chip. PEs of an MPSoC offer different capabilities, usually featuring some general purpose CPUs, as well as specialized PE (GPUs, hardware accelerators, etc.). This means that not all tasks can run on all PEs, but also that when a task is able to run on different types of PEs, their performance can vary drastically and in a nonlinear fashion. The Marvell OCTEON Fusion CNF95xx Family [2] is an example of heterogeneous platform designed for 4G and 5G base stations. For smartphones and tablets platform, we can cite the Samsung Exynos and Qualcomm Snapdragon ranges. The Xilinx Zyng UltraScale+ [72] family of System on a Chip (SoC) is an example heterogeneous platform designed for the domain of FPGA-based Digital Signal Processing.

#### **Memory Architecture**

The memory architecture of computing systems depends of the target platform, and can fall into different categories.

In a platform with Uniform Memory Access (UMA) each memory unit can be accessed by all PEs, and the access speed to units are identical for each PE. Figure 1.2a shows the memory system of a UMA platform with multiple memory units.

Figure 1.2b displays an example NUMA platform with multiple memory units. In NUMA architectures the access time between a PE and a memory unit depends

Figure 1.2: Example memory architectures

on the considered PE/unit pair. Some PEs can even have their memory accesses restricted to only one or a subset of the memory units. A typical example of this is a hardware accelerator PE tightly coupled with its working memory and that cannot access any other memory in the system. Another actor, for instance a Direct Memory Access (DMA) engine, is then used to move data in and out of the PE's working memory.

#### 1.1.3 Software Development for Modern MPSoCs

With the increasing complexity of the architecture of modern MPSoCs, their manufacturers started to provide development tools called Software Design Kits (SDKs). An SDK is a set of tools such as libraries, compilers, run-time environments, etc. aimed at easing the development for the platform. Example commercial SDKs includes those provided by Xilinx [71], Intel [5], or the Data Plane Development Kit (DPDK) [1] among many other. The quality of a platform's SDK is a crucial part of what will make the commercial success or failure of the platform, as it determines the ease of development onto the platform and therefore its adoption. Still, most SDKs for modern MPSoCs do not provide functionalities towards deadlock handling. As such, it is left to the software developers to ensure that the system stays in a safe state or can be recovered from an unsafe state. This lack of deadlock-handling tools in the official SDKs makes harder the task of developing for those platforms. One

of the aims of this thesis is to address this lack of deadlock handling strategy built into the SDKs, by providing design time and/or run-time tools providing deadlock handling to MPSoCs.

#### 1.2 Deadlocks

A deadlock is a situation in which a set of processes are each waiting from another process of the set to take an action in order to be able to continue their execution, such that no process is able to continue. These processes can represent algorithmic computations, but also the communication of data inside a platform for example. Deadlocks occur when the different processes occupy resources (be it memory buffers, communication nodes, etc.) in such a way that no process can get access to all the resources it needs to complete its tasks.

Many techniques have been developed over the years to address the issue of deadlocks. These techniques are usually categorized in three main types.

First, deadlock prevention techniques, which aim at ensuring at design-time that deadlock will not occur once the system is running. These techniques are focused on the respect of fixed constraints which can be analyzed statically. There advantage lies in the absence of run-time mechanism. Their main drawback is their high static cost to perform the analysis, or the over-conservativeness leading to reduced runtime flexibility. Deadlock prevention is used in systems which have limited resources such as embedded systems, due to their low run-time overhead, and in safety-critical domains such as avionics, medical devices, etc. where the occurrence of deadlock should be avoided at any cost.

Second, *deadlock detection and recovery* techniques are focused on letting the system run freely, with some sort of monitoring to check periodically if a deadlock occurred. When the monitor detects a deadlock, the system is rolled back to a safe state, by restoring the system to a previous state, or by dropping some computation results (which will have to be re-executed) for example. An important advantage of deadlock detection and recovery is the flexibility given at run-time to perform operations. The recovery mechanism is only used once needed, thus not constraining the execution. Deadlock detection and recovery has some run-time overhead due to the monitoring it requires. Furthermore, the recovery mechanism can be expensive

in itself, or require to execute again some expensive computations whose results have been lost in the process. As such, deadlock detection and recovery is used in systems with sufficient resource to handle the run-time overhead, and for which the occurrence of deadlock is rare enough for the cost of recovery to be acceptable. This is the case for example in some High-Performance Computing (HPC) systems for big data.

Third, *deadlock avoidance* techniques, which guide the execution of the system to ensure at run-time that no decision leading to a deadlock is taken. As for deadlock prevention, and contrary to deadlock detection and recovery, their goal is make sure no deadlocks occur. The difference lies in the fact that deadlock avoidance uses run-time control of the system execution. These techniques are commonly more flexible than deadlock prevention, but do incur some run-time overhead. There are suitable in situations where deadlock detection and recovery is too expensive, by the relative frequency of deadlocks if the system is given full run-time flexibility, or downright impossible by a lack of resources available to perform the recovery.

These three main categories of strategies to address the issue of deadlocks, as well as a selection of existing methods for each category, will be presented in details in next chapter.

#### 1.3 Problem Statement

The work of this thesis is focused on solving the issue of deadlock arising in computing systems and caused by memory shortages, by designing and implementing methods to tackle such deadlocks. This thesis does not address the issue of communication-induced deadlocks, nor aims at addressing deadlocks occurring in different kinds of systems such as distributed systems, High-Performance Computing (HPC), etc.

We target embedded systems such as MPSoCs, that we represent as a Resource Allocation System (RAS). In simple terms, a RAS aims at representing the use of a set of resources by processes, with each resource having a fixed capacity and each process requiring to be allocated a given amount of resources to be executed. RASs are presented in more details in next chapter. In the work of this thesis, we consider three kinds of resources: PEs, communication units, and memory units. Each mem-

ory port is considered as a separate communication resource, and memories are referred only in terms of their capacity (memory space). The capacity of PEs and communication units is 1, the capacity of memory units is their size.

Coffman et al. [19] determined four necessary and sufficient conditions for deadlocks to occur.

- Mutual exclusion: tasks require the exclusive use of a resource, every resource is either assigned to a single task or available.

- Hold-and-wait: a task is holding at least one resource while requesting additional resources.

- No preemption: a resource ownership cannot be suspended or canceled until the end of the task holding the resource.

- Circular wait: there is a set of tasks  $\{t_1, t_2, \dots, t_n\}$  such that  $t_1$  is waiting for a resource held by  $t_2$ ,  $t_2$  is waiting a resource held by  $t_3$ , and so on until  $t_n$  waiting for a resource held by  $t_1$ .

A summary of the occurrence of these conditions, in our RAS, is presented in Table 1.1.

| Condition        | Processing | Commu-<br>nication | Memory<br>(infinite) | Memory<br>(limited) |

|------------------|------------|--------------------|----------------------|---------------------|

| Mutual exclusion | true       | true               | false                | true                |

| Hold-and-wait    | false      | false              | true                 | true                |

| No preemption    | true       | true               | true                 | true                |

| Circular wait    | false      | true               | false                | true                |

| Deadlock risk    | no         | no                 | no                   | yes                 |

Table 1.1: Occurrence of deadlocks in our RAS

In our RAS, mutual exclusion does not occur in the case of (purely theoretical) infinite memory because new buffers can always be allocated in new memory space. The hold-and-wait situation can arise in memory units as some input buffers can be already allocated while others are yet to be. We supposed the absence of preemption for tasks on processing nodes, a very frequent situation in high-end data

processing systems with stringent time constraints (deadlines). There is also no preemption on memory as we decided that allocated buffers can only be freed once their consuming tasks have been executed (there is no mass storage in which to unload excess buffers). There cannot be circular waits for processing nodes as each task is executed on a single PE, and a task requests its processing node only once all the other resources it needs (e.g., in/out buffers) have already been allocated.

Based on the characteristics of our resource allocation problem and the hypothesis above, Table 1.1 allows us to conclude that deadlocks can only arise because of the shared use of memory units of limited capacity. In other words, memory shortages are the source of deadlocks in our target systems.

#### 1.4 Thesis Contribution

The objective of this thesis is to study memory induced deadlocks for dataflow applications running on embedded systems, and to develop and implement methods to avoid running into deadlocks at run-time. The contribution of this thesis is threefold:

- 1. An approximate deadlock prevention method for systems running applications with a common period (or which can easily be adapted to a common period). This method is based on the analysis of a graph called the Memory Exclusion Graph (MEG) representing the buffers allocated into a memory for the execution of tasks and the exchange of data from producing tasks to consuming tasks. This graph also tells us which buffers could possibly be allocated simultaneously, giving valuable information about the potential of memory shortages. Albeit of limited practical use, this method gave valuable insight to better understand the applications, platforms, and conditions leading to deadlocks.

- 2. A liveness analysis suitable for systems regardless of the timing constraints of applications, and its derived exact deadlock avoidance mechanism. This analysis and subsequent deadlock avoidance mechanism have been developed thanks to the insight given by the first contribution. They are also not held by the main drawbacks that limited the practical usability of the first approach.

- 3. The development of a control mechanism to prevent deadlock at run-time using the aforementioned exact deadlock avoidance mechanism. This control mech-

anism has been deployed in a prototype run-time environment which manages the execution of dataflow applications.

It should be noted that although developed in the context of embedded systems for Digital Signal Processing, the contributions could be applied for other types of applications (such as video processing or machine learning) and of target platforms having issues of memory (or other similar resource) shortage.

#### 1.5 Synopsis and Outline

Next chapter (Chapter 2) presents the state of the art in scheduling and deadlock prevention techniques. The following chapters present the contribution. In Chapter 3 the approximate deadlock prevention method is described. Chapter 4 presents the precise liveness analysis. Then Chapter 6 presents how the results from the precise liveness analysis can be used to prevent deadlock at run-time. In Chapter 5 experimental evaluations are conducted to compare the performance of the two deadlock handling mechanisms developed in this thesis with a state-of-the-art deadlock prevention tool. Finally Chapter 7 discusses the contributions and the future work.

## Chapter 2

## **Related Work**

#### 2.1 Introduction

In this thesis we look at the deployment of dataflow applications in embedded systems. This ranges from the modeling of the applications when designing the system, to their scheduling and execution onto the target platform, done by a run-time environment. When running such applications it is important to make sure the scheduling is safe, i.e., no memory overflows or shortages, deadlocks, etc. can occur. This raises the need to use liveness analysis and/or deadlock handling mechanism to ensure the safety, which can be critical for embedded systems used for avionics or medical applications, for example.

The goal of this thesis is to develop tools and algorithms that enable the safe deployment of dataflow applications onto heterogeneous and/or NUMA platforms. The remainder of this chapter is structured as follows. Section 2.2 presents different Models of Computation used to represent dataflow applications. Then Section 2.3 presents different ways to model scheduling problems and compute their schedules. Section 2.4 presents multiple strategies that have been developed to analyze the liveness of a system, and addresses the issue of deadlocks that arise when running concurrent computations. Section 2.5 presents various existing run-time environment managing the execution of dataflow applications. Finally, Section 2.6 concludes this chapter.

#### 2.2 Models of Computation

Over the years the complexity of dataflow applications has risen dramatically. To compensate for the continuous increase in the required computing power, platforms have become more parallel. This is shown by the advent of large-scale distributed systems, or of modern Multi-Processor Systems on a Chip (MPSoCs) having an increasing number of cores and hardware accelerators. This increase in the potential for parallelism and the complexity of platforms led to the development of higher level —more abstract—languages and Models of Computation (MoCs) for concurrent programming, to ease the otherwise complex programming. A Model of Computation (MoC) describes the set of rules that governs the execution of programs, by specifying the semantics of its component and how they may interact. The first dataflow MoC was presented by Dennis in 1974 [20]. More modern examples of such highlevel MoCs include Petri nets, and dataflow oriented MoCs such as the PRUNE MoC or the widely used SDF and its derivatives. Programming languages (such as C++, Java, etc.) differ from MoCs and are used to implement MoCs. A single programming language can be used to implement different MoCs, for example one could use Java to describe a Turing machine or an execution environment for Petri nets.

#### 2.2.1 Synchronous Data Flow

The Synchronous Data Flow (SDF) [48] is a MoC developed to describe signal processing applications, in order to expose their potential for concurrency, thus enabling an efficient use of parallel computing capabilities. SDF has fixed production and consumption rates when firing actors, and is highly analyzable statically. Formally, in an SDF graph  $G=(\mathcal{A},\mathcal{E})$ , the set of nodes  $\mathcal{A}$  (called actors) represents tasks interconnected by a set of edges  $\mathcal{E}$  that are First In, First Out (FIFO) buffers. In the SDF MoC, an actor starts execution (firing) when its incoming FIFOs contain enough tokens, it cannot be preempted and produces tokens onto its outgoing FIFOs. The number of tokens consumed/produced by each firing is a fixed scalar that is annotated to the graph's edges. As actors have no state in SDF graphs, if enough tokens are available, an actor can start several executions in parallel. For this reason, SDF graphs naturally express the parallelism of signal-processing applications and can be statically analyzed for several types of optimizations (e.g., memory allocation,

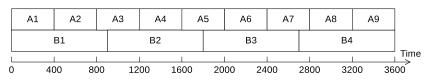

Figure 2.1: Example of an application SDF graph and its corresponding AHSDF graph.

scheduling). An example SDF graph can be seen at the top of Figure 2.1. In this graph, task Sre reads and writes to a first FIFO, the self-loop, and writes to a second FIFO. The self-loop allows for at most one concurrent execution of the Sre task, since it contains initially one token. Tokens that are present in the initial state of an SDF graph are called delay tokens. The second FIFO is the input of task A. After one execution of Sre, the self-loop has again one token, and the FIFO between Sre and A also has one token. An execution of task A will consume one token from the Sre to A FIFO, and output three tokens to the A to B FIFO (i.e., the edge from A to B).

#### A subclass of SDF: Acyclic Homogeneous SDF

SDF graphs can have two properties that are useful for their analysis, namely acyclicity and homogeneity. An SDF graph is called *acyclic* if it contains no cycle, i.e. there are no paths in the graph with the same starting and ending nodes. Acyclic graphs are commonly used to isolate a single iteration of the represented application. *Homogeneity* refers to SDF graphs in which the production and consumption rates are equal for each FIFO. Homogeneous SDF graphs fully expose the data parallelism and memory allocation options.

Any SDF graph can be transformed into an Acyclic Homogeneous Synchronous Data Flow (AHSDF), as described in [64]. In a AHSDF graph  $H = (\mathcal{T}, \mathcal{B})$ , tasks in  $\mathcal{T}$  are associated to identical production and consumption rates on FIFO buffers in  $\mathcal{B}$ . To do so, multiple instances of a same task are created when the production and consumption rates do not match in the original graph. Considering the original SDF graph  $G = (\mathcal{A}, \mathcal{E})$ . For any FIFO  $f \in \mathcal{E}$ , with  $p_f$  the production rate on f,  $c_f$ the consumption rate on f, and lcm(a,b) being the Least Common Multiple (LCM) of a and b. If  $p_f$  and  $c_f$  are not equal,  $lcm(p_f, c_f)/p_f$  instances of the producer are created and, conversely,  $lcm(p_f, c_f)/c_f$  instances of the consumer. For example, with a FIFO annotated with  $p_f = 200, c_f = 300$  in the original SDF graph, there will be lcm(200, 300)/200 = 3 instances of the producer and lcm(200, 300)/300 = 2 of the consumer in the AHSDF graph. The graph can be made acyclic by removing all FIFOs with delay tokens. The result of this transformation on the example SDF graph can be seen at bottom of Figure 2.1. This transformation is used to expose data parallelism and memory allocation options (Homogeneous SDF), as well as to isolate a single iteration of the algorithm captured by the original SDF graph (Acyclic Homogeneous Synchronous Data Flow).

#### 2.2.2 Cycle-Static Data Flow

The Cycle-Static Data Flow (CSDF) MoC is an extension of SDF first introduced by Bilsen et al. [12]. CSDF graphs are identical to SDF graphs in all aspects but the production/consumption rates on FIFOs. Indeed, in a CSDF graph the constant rate can be replaced by a finite sequence of values. For example, if a FIFO has a production sequence of (2,1), it means that the producing actor will add 2 tokens on its first firing, and 1 token on its second firing. Once the sequence end has been reached the sequence is repeated, so the third (and every odd-numbered) firing will again produce 2 tokens.

It has been demonstrated that CSDF is *not* more expressive than SDF, since any CSDF graph can be transformed into an equivalent SDF graph [60]. The main advantage of CSDF over SDF is that it allows to express complex applications with a smaller graph, and to statically analyze them as is the case with SDF. The counterpart is the higher computational cost of those analyzes.

#### 2.2.3 PRUNE MoC

The PRUNE MoC has been designed to describe the behavior of high-performance signal processing applications. In PRUNE applications are represented by a graph with nodes representing actors (computations), and edges FIFOs allowing the communication of input/output and control data. There exists three types of actors, namely static, dynamic, and configuration actors. There also exists three types of FIFOs, static FIFOs for which the production/consumption rate is constant, dynamic FIFOs that allow this rate to change, and control FIFOs, that manage the rate change of dynamic FIFOs Static actors are similar to SDF actors and always produce and consume the same amount of tokens on their input/output static FIFOs. Configuration actors have one or multiple output control ports connected to the input control port of dynamic actors. Dynamic actors have exactly one control port (linked to a control FIFO in input), are connected to at least one dynamic FIFO, and can be connected to static FIFOs as well. At each firing, they dynamically adjust the consumption or production rate of all their dynamic FIFOs, based on the value of the token in their input control FIFO. Similarly to homogeneous SDF graph, FIFOs have a symmetric rate, i.e., the production and consumption rates are equal. But the PRUNE MoC is more expressive than homogeneous SDF graphs, since it allows the dynamic reconfiguration of the FIFO rates. Both ends of a dynamic FIFO should be controlled by the same configuration actor, to ensure this symmetric rate. Since the stated goal of the PRUNE MoC is to allow the static decision on the liveness and memory-boundedness of the modeled applications, a set of design rules must be respected to ensure that these properties are decidable in a finite time, by constraining the control of dynamic actors.

Albeit more expressive than SDF, the contributions of this thesis are not using the PRUNE MoC, as the added expressiveness entails an higher complexity to design applications and analyze them.

#### **2.2.4** $\pi$ **SDF**

$\pi$ SDF is an extension of SDF that allows hierarchical actors and dynamic reconfiguration [23]. A hierarchical actor is an actor whose behavior is itself expressed using a MoC, here via a  $\pi$ SDF graph.  $\pi$ SDF hierarchical actors have been designed to

Figure 2.2: Example of an application  $\pi SDF$  graph. S is a configuration actor, B a hierarchical actor

ensure that their internal behavior does not influence the analyzability at the higher level. This is done using interfaces, which behave as circular buffers when more tokens are consumed than produced, and discard excessive tokens have been produced than are consumed. This interfaces behavior has been first defined in the Interface Based-Synchronous Data Flow MoC [62]. This behavior means that in Figure 2.2, the external behavior of actor B is not dependent of the internal behavior of actors X and Y, since they are interfaced (interfaces are represented as parallelograms in Figure 2.2). Here the interface connecting the lower level actor Y to the higher level B will act a circular buffer, since 1 token is produced when 3 are consumed. Hierarchical actors are convenient when designing applications, as they allow to compose and reuse application graphs. Similarly to PRUNE,  $\pi$ SDF has configuration actors that manage the dynamic reconfiguration. The configuration actors are fired once before every iteration of the full  $\pi SDF$  graph, and set parameters which will affect the production/consumption rates of some actors. For example in Figure 2.2, S is a configuration actor that set parameter N, which in turn determines the production rate of actor A.

Similarly to the PRUNE MoC,  $\pi$ SDF extends on SDF to allow dynamic reconfigurations. Again, the added expressiveness is not useful to express the behavior of our target applications.

- (a) Example Petri net, with initial marking  $M_0 = \{1, 0, 1, 1, 0\}.$

- (b) Example Petri net from Figure 2.3a after the firing of T1.

Figure 2.3: An example Petri net, before and after the firing of a transition.

#### 2.2.5 Petri Net

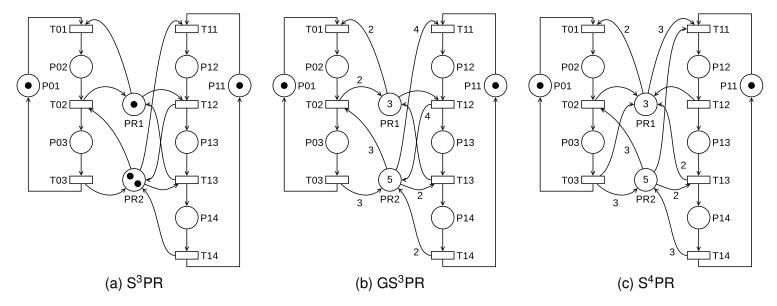

A Petri net is graph composed of two types of vertexes, called places and transitions, and directed arcs. A directed arc must connect a place to a transition or a transition to a place, but cannot connect two nodes of the same type. Figure 2.3a shows an example Petri net, in which circles P1 to P5 are the places, bars T1 to T4 the transitions, and arrows are the directed arcs. More formally, a Petri net is a directed bipartite graph  $N=(P,T,F,M_0)$ , in which the set of nodes  $P\cup T$  represents places and transitions, with  $P\cap T=\emptyset$ . Transitions T represent events that can occur, and places P represent conditions such as resource usage. The directed arcs F describe the preconditions and postconditions for each transition, i.e., which conditions must be satisfied before and after the transition for it to be enabled. Places are annotated with a positive integer representing the number of tokens present, which is called the *marking* of the Petri net.  $M_0$  corresponds to the initial marking of the Petri net's places, i.e. the initial state of the Petri net. In Figure 2.3a places P1, P3, and P4 have initially 1 token each. With this initial marking, transition T1 is the only enabled. After firing T1 we get the marking in Figure 2.3b.

The reachability graph of the example given in Figure 2.3 can be seen in Figure 2.4. Each vertex of the reachability graph corresponds to a possible state of the Petri net and is annotated with the corresponding marking. For example, in Figure 2.4 the uppermost state is annotated with 1,0,1,1,0, meaning that places P1, P3, and P4 each have one token while places P2 and P5 are empty, which corresponds to the marking displayed in Figure 2.3a. The marking of the Petri net in Figure 2.3b corresponds to the leftmost state (0,1,2,1,0) in the reachability graph

Figure 2.4: Reachability graph of example Petri net from Figure 2.3.

displayed in Figure 2.4. Each transition that is enabled for a given marking in the Petri net is represented by an edge coming from the state representing that marking in the reachability graph. For example, since T1 is the only transition enabled with the marking of Figure 2.3a, state 0,1,1,0,1 in Figure 2.4 has only one outgoing edge, which corresponds to the firing of T1.

Petri nets are commonly used because of their expressiveness and analyzability, making them suitable to model concurrent systems and check if they respect some properties guaranteeing a safe execution, such as liveness and boundedness.

**Pure nets** — A Petri net is said to be pure if it has no self-loop, i.e., there exists no place that is simultaneously an input and an output of a transition. Pure Petri nets are easier to analyze as they can be represented with an incidence matrix. A Petri net that is not pure cannot be represented by a single matrix. Instead two matrices are necessary, one to represent inbound arcs (going from a transition to a place), and another to represent outbound arcs (going from a place to a transition). The Petri net displayed in Figure 2.3a is pure.

**Boundedness** — A place in a Petri net is k-bounded if in all states reachable from the initial marking it never has more than k tokens. From the reachability graph in Figure 2.4, we can see that in the example Petri net P1 is 3-bounded, P2 is 2-bounded, and the remaining places are 1-bounded. As such the example Petri net given in Figure 2.3 is 3-bounded.

**Liveness** — Four levels of liveness have been defined for the transitions of a Petri net, each level being more restrictive than the last. A transition has liveness level:

- *L*<sub>1</sub>-live: if it can fire in at least one possible firing sequence;

- $L_2$ -live: if  $\forall k \in \mathbb{N}$  it can fire k times in at least one possible firing sequence. The

Figure 2.5: Example Petri nets from different classes used to study sequential RAS.

specific sequence can differ for each value of k;

- $L_3$ -live: if it can fire infinitely in at least one possible firing sequence, i.e., there is at least one infinite firing sequence such that the transition can always be fired an infinite number of times;

- $L_4$ -live: if it can fire in every possible state, it is always enabled.

A Petri net is called  $L_k$ -live if all its transitions are at least  $L_k$ -live. From the reachability graph in Figure 2.4, we can see that all transitions are  $L_3$ -live by making the infinite repetition of the sequence T1, T3, T4, T1, T2. As such, the example Petri net displayed in Figure 2.3 is itself  $L_3$ -live.

Petri nets are used as modeling tool for many systems such as to analyze business processes [10], parallel processing in computing systems, or the behavior of flexible manufacturing systems. Specialized, constrained, types of Petri nets have been developed to represent and analyze specific problems. Each type of constrained Petri net is called a Petri net class.

#### **Classes of Petri Nets**

Over the years many classes of Petri nets have been developed. Each class defines a set of constraints over the places and transitions of a Petri net. These constraints are used to guarantee that some mathematical properties always hold, which make analyzing Petri nets more efficient. A thorough survey of Petri net classes has been made by Liu and Barkaoui [53].

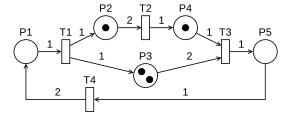

This thesis aims at addressing the issue of deadlocks for some sort of sequential RAS, i.e., a RAS in which resources are reusable. Figure 2.5 shows three classes of Petri nets based on the same principles: there is a set of resources represented as places, and a set of processes represented as a circuit made of places and transitions. Processes can be used to describe the execution of periodic dataflow applications, or the behavior of a flexible manufacturing system for example. For all the Petri nets displayed in Figure 2.5, places PR1 and PR2 are the resources. The loop made of P01, T01, P02, T02, P03, T03 represent a first process, and the loop made of P11, T11, P12, T12, P13, T13, P14, T14 represent a second process. The difference between the different classes lies in the edges they allow between the processes and the resource, i.e. in what resource usage they are able to represent.

Lets first present the Generalized Systems of Simple Sequential Processes with Resources (GS³PR) class [52], displayed in Figure 2.5b). A GS³PR Petri net is a pure net made of processes and resources such that each transition have at most one inbound edge connected to a resource, representing the allocation of some of the resource capacity to the process. Conversely, each transition can have at most one outbound edge connected to a resource, representing the deallocation of the resource capacity. Furthermore in a GS³PR, if a process place has an incoming transition allocating some resource, then any outgoing transition must free the same quantity of the same resource. This can be seen in Figure 2.5b) with the two arcs  $PR1 \rightarrow T01$  and  $T02 \rightarrow PR1$  both having a weight of 2. In other words a process cannot hold onto multiple resources simultaneously, and must free any allocated resource at its next execution step.

Systems of Simple Sequential Processes with Resources (S<sup>3</sup>PR) [28] (Figure 2.5a) is identical to GS<sup>3</sup>PR, excepted that there are no weight on edges. As such the S<sup>3</sup>PR class is said to be *ordinary*, and is more constrained but easier to analyze than GS<sup>3</sup>PR.

In Figure 2.5c is displayed a net of the S<sup>4</sup>PR (S<sup>4</sup>PR) class [68]. S<sup>4</sup>PR is more permissive than GS<sup>3</sup>PR, as it lifts the constrains on resource usage. This allows to represent process which can hold onto resources during their execution. In fact,

contrary to S<sup>3</sup>PR and GS<sup>3</sup>PR, it is possible to express the behavior of a set of AHSDF graphs using an S<sup>4</sup>PR net.

There exists a variety of other Petri net classes for sequential RAS beyond those presented here. For example the classes S\*PR (S\*PR) [29] or Processes Competing for Conservative Resources (PC<sup>2</sup>R) [54] are more permissive than S<sup>4</sup>PR. Since S<sup>4</sup>PR is permissive enough to express workloads of applications modeled as AHSDF graphs, we elected not to present them here.

A common approach to enforce liveness in Petri nets is the use of pure net supervisors. Pure net supervisors are sets of places, transitions, and arcs added to a Petri net that is not live in order to produce a new net that is live and pure. Zhong et al. [75] have pointed out that there does not always exist a maximally permissive liveness-enforcing pure net supervisor for a Petri net. This displays the importance of researching non pure net solutions to enforce liveness in a Petri net.

#### 2.2.6 Discussion

The high-level representation of dataflow MoCs enables application and system developers to describe parallelism in streaming applications, such as media processing, in a simple and intuitive way. The different varieties of MoCs existing in the literature each have their own characteristics. These include the execution semantics of the MoC, its expressiveness, analyzability, and restrictions, making them suitable for different kinds of applications and platforms.

In the work of this thesis, SDF is used as the MoC to model the applications to be executed on the target platform. It has been chosen for its high static analyzability associated with a suitable expressiveness for targeted applications, making it possible to minimize the amount of dynamic analysis required, and thus being suitable for embedded systems, where computing resources are limited and best used to compute the actual applications. MoCs that support the reconfiguration of applications, such as  $\pi$ SDF and the PRUNE MoC, have not been considered as the added expressiveness is not necessary to express our target applications. Millo et al. [57] present an interesting work, using the MARTE/CCSL formalism to express the allocation and real-time constraints falling upon SDF applications deployed on embedded systems. The idea of using different formalisms in conjunction to represent applications and

their constraints at different levels of abstraction has also been studied by Arras et al. [7].

#### 2.3 Formalization of Scheduling Problems

Scheduling is a common problem across many sectors. It refers to the need to allocate a limited amount of resources (e.g., materials and machines in a manufacturing plant, PEs in a computing system) in an efficient manner in order to complete a target work while optimizing some objectives (e.g., time, cost, energy consumption).

#### 2.3.1 Types of Scheduling Problems

To describe different kinds of scheduling problems, ranging from construction work, management of a manufacturing plant, to scheduling of applications and tasks in computing systems, a variety of scheduling problems and formalisms have been described. We will present hereafter two of the most common and significant scheduling problems addressed in the literature.

#### **Resource Constrained Project Scheduling Problem**

A common problem definition found in the literature is the Resource Constrained Project Scheduling Problem (RCPSP). Problems are defined by a set of activities (or tasks) which have various resource requirements and can be dependent on other activities completion. This problem description is aimed at logistical projects (such as transporting good or infrastructure building), but share common aspects with the scheduling of dataflow applications. Both share a common goal, which is the optimization of the execution of activities or tasks that have specified resource usage. There are different characteristics defining an RCPSP.

**Resources** — The resources studied in RCPSPs can be of different kind. Renewable resources are resources available in a maximal quantity at any time in the project, such as vehicles in a transportation problem. This is similar to memory resources in our case. Non-renewable resources are available in a limited quantity over the full course of the project: once consumed they are destroyed and cannot be reused at a later point in the project. Doubly constrained resources are non-

renewable resources that also have a maximal simultaneous use like renewable resources.

**Objective function** — RCPSPs can have different objective functions such as minimizing the cost of the project, its duration, etc.

**Activities** — Activities can have different characteristics depending on the specific problem. They can be preemptible or non-preemptible (such as in our work). They can by limited to a single mode, or have multiple modes with different duration, resource needs, etc. This can be similar to the execution of tasks in a heterogeneous system, where a task could have different execution time or memory usage depending on its execution node.

**Scheduling certainty** — Many papers studying RCPSPs assume that creating a basic scheduling table in advance for the whole project is feasible. In practice, variations in the time taken to complete activities, availability of resources, or other external factors can impact the schedule when the project is ongoing. Different kinds of scheduling have been proposed to address the uncertainty that can occur:

- Reactive scheduling. Each time an unexpected event occurs, a new schedule is created for the remaining part of the project.

- Stochastic scheduling. The duration of activities is assumed to follow some probabilistic rule, known in advance.

- Fuzzy scheduling are used when it is not possible to evaluate beforehand the probability distributions of the project's perturbations.

- Robust (or proactive) scheduling. Its goal is to create a schedule that is the most robust to events, i.e. to minimize the effect random events can have on the schedule's objectives.

- Sensitivity analysis aims at studying how variations in an RCPSP parameters impact, or not, the optimal solution and its cost.

An overview of many RCPSPs has been done by Habibi et al. [34]. In our case, reactive scheduling is not suitable as the cost of computing a complete schedule is high and events occur frequently. More generally, all these approaches aim to address uncertainty when trying to compute a full schedule that is either easily changed

when an unexpected event occurs, or replaceable. For our problem, computing a full schedule is not suitable since events such as an application start, end, or reconfiguration can occur frequently and significantly change the scope of the schedule.

#### **Resource Allocation Systems**

Another formalization commonly used is the Resource Allocation System (RAS). Generally speaking, a RAS is formalized by a set R of m different resource types:  $R = \{R_1, \ldots, R_m\}$ , and a set J composed of n process types  $J = \{J_1, \ldots, J_n\}$ . Every resource is characterized by its capacity  $C_i$ , a finite positive integer. A process type  $J_j$  is characterized by a sequence of request vectors of dimension m:  $\langle J_{jk}, k=1,\ldots,l(j)\rangle$  with l(j) the number of steps for process type  $J_j$ , and components  $J_{jk}[i], i=1\ldots,m$  indicating the amount of units of resource  $R_i$  required for the completion of step  $J_{jk}$ .

Multiple classes of RASs exist, each having different constraints on the valid resource requests. The most significant classes are the following ones, from the most restrictive to the most permissive:

- Single-unit RAS: Request vectors can have a single non-zero component of value one;

- **Single-type RAS:** Request vectors can have a single non-zero component that is a positive integer lesser or equal to the corresponding resource capacity;

- Conjunctive RAS: All components of request vectors can take any integer value from 0 to the corresponding resource capacity;

- **Disjunctive/Conjunctive RAS:** For every stage, the vector of dimension m is replaced by a set of vectors such that the step can be completed if any request in that set can be satisfied. Each of those vectors follows the constraints of the request vectors in conjunctive RAS.

The problem of scheduling applications on a multi-core platform can be represented by a conjunctive RAS, or by a disjunctive/conjunctive RAS if there exists multiple implementations of a task having different memory requirements. An example of the latter would be a heterogeneous system in which a task can be executed by

a generic CPU or by a hardware accelerator, and these alternative implementations have different memory footprints.

#### 2.3.2 Computation of Schedules for Multicore Systems

The scheduling of applications running on multi-core platforms is commonly divided in four successive steps, in order:

- 1. **Extraction:** The first step when scheduling for a multi-core system is to extract the potential parallelism contained within the set of applications to run. This parallelism can come from tasks having no dependency relation, but also from having multiple applications—or iterations of a same application—running concurrently. The extraction step for SDF graphs can be done via its transformation into an AHSDF graph (cf. Subsection 2.2.1).

- 2. Mapping: The mapping corresponds to assignment of tasks to PEs, and of buffers to memories. Task mapping is constrained by the computing capabilities of each PE in heterogeneous architectures, and is commonly done using heuristics with objectives such as minimizing the latency, following real-time constraints [16], maximizing the energy efficiency [41,46], etc. Buffer mapping in NUMA architectures is usually done to ensure the locality of data, i.e., assigning a buffer to a memory that can be quickly accessed from the PEs on which the tasks using that buffer have been mapped, such as in the work of Drebes et al. [26] for example.

- 3. **Ordering:** Once tasks have been mapped onto PEs an execution order is computing for each PE. The execution order must respect the dependencies between task, and can also be constrained via deadlines on tasks. It is common to compute the ordering simultaneously with the mapping, since the efficiency of a given mapping is affected by the task ordering.

- 4. **Timing:** Finally, timing corresponds to the assignment of a specific starting time for the execution of tasks. It depends on various factors such as data availability and system load. Except for the most critical systems, with hard deadlines that must be met in any circumstances, timing is usually done online by the run-time manager or the operating system.

Depending on whether these steps are done statically or online, four main scheduling strategies for multi-core systems can be described [47]:

- Fully static: All steps are computed offline, at design or compile time, leading

to a single schedule or a handful of schedules out of which one is selected at

run time depending on the configuration. It has the advantage of minimizing

the run time overhead, but at the cost of a reduced flexibility and a potentially

high computational complexity.

- **Self timed:** Only the timing step is computed dynamically. This gives more run time flexibility while keeping the overhead low. This approach is useful for systems where the execution time of tasks is variable.

- Static assignment: The extraction and mapping steps are done statically, while the ordering and timing are computed at run time depending on the dynamic conditions in the system.

- Fully dynamic: All steps are computed dynamically. This gives the highest flexibility to the system, but also the highest overhead at run-time, making it suitable only for systems where this overhead can be tolerated (typically with not strictly limited computing resources). An example fully dynamic scheduling for homogeneous multi-core systems can be seen in [11].

#### 2.4 Liveness and Deadlocks

#### 2.4.1 Liveness Analysis

A liveness analysis goal is to analyze a system to determine in which situations (or system states) does a given property hold (the system is *live*) or not. The analyzed property can represent for example resource usage (the system is live when there are no resource overflow), or are all buffer reads performed after a corresponding buffer write (the system is live when no incorrect read operation has occurred). The liveness analysis evaluates the given property on the reachable states of the system to determine which states are live or not.

Liveness analysis have many applications such as proving functional correctness, selecting a viable and efficient schedule for a system, or designing run-time monitoring mechanisms to ensure the safe execution of the analyzed system. For example, the results of some liveness analysis can be used to handle deadlocks, usually within deadlock prevention and deadlock avoidance strategies, which are presented in the next subsection.

An example of liveness analysis is the one developed in the PRUNE framework [15]. This analysis is based on the PRUNE MoC, presented in Subsection 2.2.3, which is designed to allow the static analysis of liveness and memory boundedness. As stated in Subsection 2.2.3, this static analysis is made possible via a set of design rules, that have been devised to ensure the consistent behavior of dynamic actors. The PRUNE liveness analysis takes as input a representation of the system composed of an application graph, a platform graph, and a mapping of tasks to PEs. The application graph is similar to one of the input of the first and second contributions of this thesis (presented in Chapter 3 and Chapter 4 respectively), excepted that PRUNE uses the more flexible PRUNE MoC, whereas contributions 1 and 2 use AHSDF graphs. Our contributions also require a mapping of tasks to PEs, but do not require a graph describing the platform. Instead the only necessary information is the size of memories (for contributions 1 and 2), and an estimation of tasks' execution time and communication delays (only for contribution 1). It should be noted that contribution 1 is *not* a liveness analysis but a deadlock handling strategy, which are described in next subsection.

#### 2.4.2 Deadlock Handling Strategies

The occurrence of deadlocks in multi-core systems is a common problem that is widely studied in the literature. Many mechanisms have been designed over the years to tackle the issue of deadlocks, with different strategies and types of deadlocks to remedy, depending on factors such as the requirements of applications, the system design, etc. In this thesis we focus on deadlocks caused by memory shortage, since they are the only kind possible in our target system (as explained in Chapter 1).

In this thesis deadlock handling strategies are classified in three different main

types, namely (i) prevention, (ii) detection and recovery, and (iii) avoidance. This classification is the most commonly used in the literature about deadlocks [19, 49, 65, 66]. These strategies have their own advantages and drawbacks, making them suitable for different kinds of scenarios.

#### **Deadlock Prevention**

A common approach to handle deadlock is to statically analyze the system and its possible configurations to make sure that under no circumstances a deadlock would occur. This is called deadlock prevention. The main drawback of this kind of strategy is its high computational cost and/or its restrictiveness.

Example deadlock prevention methods include:

• memDAG [56] is a tool developed by the research team behind StarPU [8]. It analyzes a graph derived from a task dependency Directed Acyclic Graph (DAG) to compute its maximal memory footprint. The maximal footprint is given by the topological cut with the highest footprint in the derived graph. If the maximal footprint of the Directed Acyclic Graph (DAG) is greater than the available memory on the system the DAG will run, memDAG computes artificial dependencies to prevent memory shortage from occurring. The memDAG tool proposes four different heuristics for the computation of artificial dependencies to respect the memory constraint. To avoid creating loops or meaningless dependencies, a dependency will always be added between two vertexes for which no paths previously existed. The RespectOrder heuristic has the advantage of never failing, but requires a valid schedule for the specified memory size to be computed beforehand. All the artificial dependencies it adds to the graph will respect the order of the provided schedule. The other three heuristics (MinLevel, MaxSize, MaxMinSize) have the drawback of sometimes failing to provide a valid solution even when one do exists. The purpose of MinLevel is to select artificial dependencies that minimize the critical path in the graph, in order to add the smallest overhead to the make-span of the application. MaxSize tries to minimize the weight of the next topological cut for each artificial dependency it adds. It adds a dependency by selecting the pair of vertexes which together contribute the most to the weight of the topological cut. MaxMinSize also tries to minimize the

weight of the next topological cut. It selects the pair of vertexes for which the minimum contribution among the two vertexes is the largest across all possible pairs. In other word, both vertexes contribute a lot to the weight of the topological cut. To better understand MaxSize and MaxMinSize let's take a simple example with four vertexes a,b,c,d respectively contributing 20,5,10,10 to the weight of the topological cut. We also assume that only two dependencies can be added:  $b \to a$  or  $c \to d$ , as the other dependencies would create a loop or add no constraint as a path already exists between the vertexes. MaxSize will choose  $b \to a$  since  $\max(20+5,10+10)=25$  (the sum of the contributions of a and b is the maximal, b0). MaxMinSize will choose b0 is 10, which is larger than the minimal contribution from b0 at 5).

- SynDEx [27] is a Computer-Aided Design (CAD) software for the development

of real-time applications in embedded systems. SynDEx relies on two input

graphs: the acyclic dependency graph of tasks, and the architecture graph

representing the targeted platform. Then, by statically analyzing those graphs,

it provides a static mapping and a static schedule guaranteed to be deadlockfree (i.e., deadlock prevention).

- PREESM [61] is a prototyping framework for dataflow applications. Its goal is to allow for the fast prototyping and deployment of applications to multi-core DSP systems, with stated goal to enable designers to perform Design Space Exploration (DSE). PREESM generates self-timed, deadlock-free code to run on the targeted system. The absence of deadlocks is ensured through the static analysis of the  $\pi$ SDF application model and the graph representing the target system to guarantee that the execution is memory-bounded and is not susceptible to a memory shortage.

- Stuijk et al., the authors of [67], developed a method for maximizing the throughput of multimedia applications running on MPSoCs, while minimizing buffers' sizes. In order to guarantee a maximal throughput the authors needed to produce deadlock-free schedules. They propose an exact approach which can be used for DSE, providing a Pareto front of memory requirement against max-

imal throughput. They also designed an approximate method with low overestimation of the buffers' sizes required to ensure deadlock freeness.

The first contribution of this thesis (presented in Chapter 3) is also a deadlock prevention method, computing artificial dependencies for dataflow applications running onto embedded systems. It differs from the methods presented above by its use of AHSDF graphs to describe applications. The most similar approach to our first contribution in its principle is memDAG [56] as it also computes artificial dependencies, but targets different types of systems. The approach of Stuijk et al. [67] and PREESM [61] have a similar target as contribution 1, as they also target dataflow applications running on embedded platforms, but uses different approaches to prevent deadlocks.

#### **Deadlock Detection and Recovery**

A totally different approach to handle deadlocks is the strategy of detection and recovery. The idea behind the approach is to monitor at run time the system in order to detect when a deadlock has occurred. If a deadlock is detected, the system is rolled back to previous *non-deadlocking* state, thus requiring the frequent save of checkpoints. It is efficient for systems where keeping checkpoints and dynamically monitoring the occurrence of deadlocks is (i) possible, and (ii) within a reasonable cost (in terms of time and memory overhead). This makes it suitable for systems where the occurrence of deadlocks is rare, since the restoration of the system to a previous checkpoint is an expensive operation, and with sufficient resources to spare in the monitoring process. This strategy is fully dynamic and useful for systems where static analysis for deadlock freeness would be too expensive in computation time, such as systems running highly reconfigurable applications.

The deadlock detection-based scheduling (DDS) [69] is an algorithm designed to detect deadlocks caused by the saturation of storage in HPC systems. The set of jobs to execute is represented through a weighted directed acyclic graph. Weights represent the estimated size of the input/output files to be written on the storage system. Once a deadlock has been detected, one or multiple jobs are selected to be rolled back and, as such, will have to restart their computation from scratch at a later point. This removal of jobs and their files frees storage capacity, thus enabling the

system to resume computations. Jobs are selected based on the quantity of storage space they currently use and are expected to require to complete their execution, as well as the expected computation time needed to restore their progress if removed.

Deadlock detection and recovery techniques are not suitable for the types of systems studied in this thesis. Indeed, the targeted embedded platforms have not enough resources both due to the limited computing power of such platforms, making the detection of deadlocks too computationally expensive, nor memory resources (with small Random-Access Memories (RAMs) and no mass storage such as hard disk drive) to save a system state for recovery.

#### **Deadlock Avoidance**