# Contribution to the design and control of the extended overlap-alternate arm converter

Pierre Vermeersch

#### ▶ To cite this version:

Pierre Vermeersch. Contribution to the design and control of the extended overlap-alternate arm converter. Other. Centrale Lille Institut, 2021. English. NNT: 2021CLIL0015. tel-03697250

# HAL Id: tel-03697250 https://theses.hal.science/tel-03697250v1

Submitted on 16 Jun 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### CENTRALE LILLE

#### THESE

Présentée en vue d'obtenir le grade de

## **DOCTEUR**

En

Spécialité : Génie Électrique

Par

## **VERMEERSCH Pierre**

#### DOCTORAT DELIVRE PAR CENTRALE LILLE

#### Titre de la thèse:

# Contribution to the Design and Control of the Extended Overlap-Alternate Arm Converter

Contribution au Dimensionnement et à la Commande de Convertisseur Extended Overlap Alternate Arm Converter (EO-AAC)

Soutenue le 21 Septembre 2021 devant le jury d'examen :

Président CARPITA Mauro, Professor, University of Applied Sciences of

Western Switzerland, Switzerland

Rapporteur BLAABJERG Frede, Professor, University of Aalborg, Denmark

**Examinateur** GREEN Tim C., Professor, Imperial College London, UK

**Examinateur** SAEEDIFARD Maryam, A. Professor, GeorgiaTech, USA

**Examinateur** FARR Ewan, Doctor, General Electric, UK

**Directeur de thèse** Xavier GUILLAUD, Professor, Centrale Lille

Invité MERLIN Michael M.C., Lecturer, University of Edinburgh, UK

**Invité** EGROT Philippe, Engineer, EDF R&D, France

**Encadrant** GRSUON François, A. Professor, Arts et Métiers Lille, France

Thèse préparée dans le Laboratoire L2EP

Ecole Doctorale SPI 072

# Table of Contents

| Table of Contents |                           |                                                                                         |    |  |

|-------------------|---------------------------|-----------------------------------------------------------------------------------------|----|--|

| R                 | ésum                      | é étendu                                                                                | 1  |  |

| In                | $\operatorname{trod}_{i}$ | uction to HVDC Systems                                                                  | 6  |  |

|                   | 1                         | Context and motivations                                                                 | 6  |  |

|                   | 2                         | Main Principles for the HVDC Systems                                                    | 7  |  |

|                   |                           | 2.1 Point-to-point schemes                                                              | 7  |  |

|                   |                           | 2.2 Multi-Terminal DC schemes                                                           | 7  |  |

|                   | 3                         | Power Electronics for HVDC system                                                       | S  |  |

|                   |                           | 3.1 Line Commutated Converter                                                           | S  |  |

|                   |                           | 3.2 Voltage-source topologies                                                           | 10 |  |

|                   |                           | 3.3 Modular hybrid topologies                                                           | 11 |  |

|                   | 4                         | Main Contributions and Layout of the Thesis                                             | 13 |  |

|                   | 5                         | List of publications derived from this work                                             | 13 |  |

|                   |                           |                                                                                         |    |  |

| 1                 |                           | e AC/DC Conversion for HVDC System                                                      | 15 |  |

|                   | 1.1                       | Introduction                                                                            | 15 |  |

|                   | 1.2                       | Full-wave controlled 2-Level VSC                                                        | 15 |  |

|                   | 1.3                       | Modulated voltage control                                                               | 20 |  |

|                   | 1.4                       | The Modular Multilevel Converter                                                        | 23 |  |

|                   | 1.5                       | Hybrid Topologies with Active Filtering Capability and Powers Decoupling .              | 29 |  |

|                   |                           | 1.5.1 Introduction                                                                      | 29 |  |

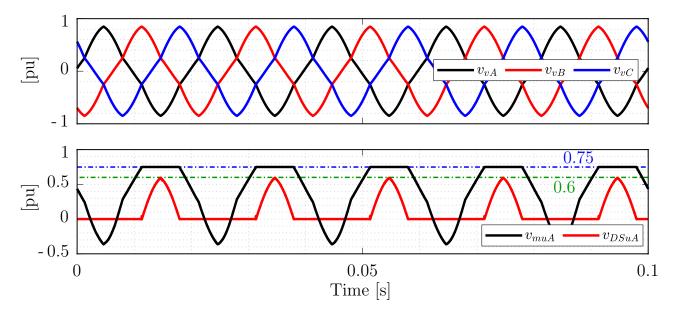

|                   |                           | 1.5.2 Modulation of $v_v$ and Active Filtering of AC currents                           | 29 |  |

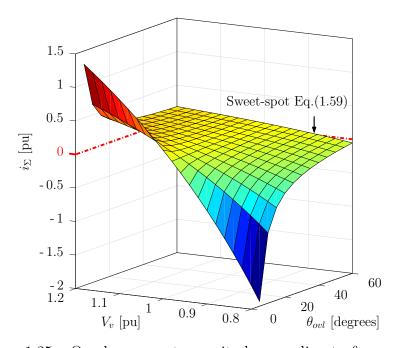

|                   |                           | 1.5.3 Introduction to the energy sweet-spot                                             | 34 |  |

|                   |                           | 1.5.4 The overlap operating mode                                                        | 36 |  |

|                   |                           | 1.5.5 Filtering of the DC current                                                       | 40 |  |

|                   | 1.6                       | Chapter Conclusion                                                                      | 46 |  |

| 2                 | Stea                      | ady-State Analysis                                                                      | 47 |  |

|                   | 2.1                       | Introduction                                                                            | 47 |  |

|                   | 2.2                       | Sizing of Stacks of SMs and DSs including ZSVI                                          | 48 |  |

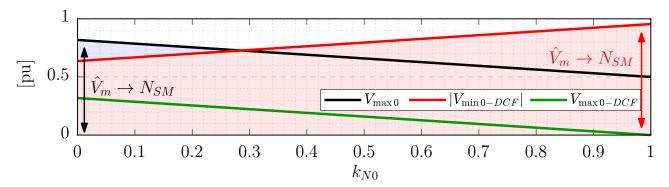

|                   |                           | 2.2.1 Modulated voltage peak value estimation according to $k_{N0}$                     | 48 |  |

|                   |                           | 2.2.2 DS voltage blocking capability according to $k_{N0}$                              | 51 |  |

|                   |                           | 2.2.3 DC-Fault Blocking Capability                                                      | 52 |  |

|                   |                           | 2.2.4 Selection of the sizing of the Stacks and DSs                                     | 53 |  |

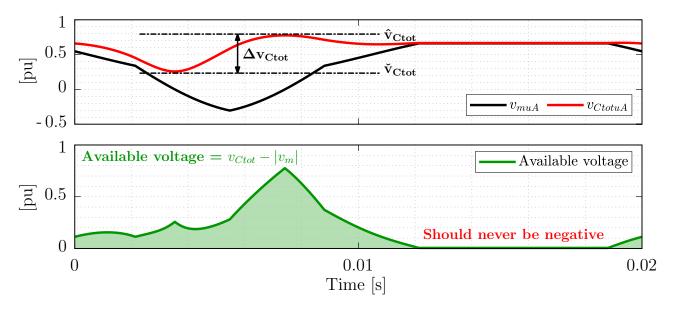

|                   | 2.3                       | Estimation of Internal Energy Storage: Comparison with MMC                              | 55 |  |

|                   |                           | 2.3.1 Basics of Stored Energy Requirement Estimation according to $\Delta v_{Ctot}$ [1] | 56 |  |

|                   |                           | 2.3.2 Assessment of stored energy requirement in MMC                                    | 57 |  |

| Bi | ibliog | graphy                                                                                                  | 156        |

|----|--------|---------------------------------------------------------------------------------------------------------|------------|

|    | 4.0    | Conordion                                                                                               | 102        |

|    | 4.5    | Conclusion                                                                                              | 152        |

|    |        | 4.4.1 DC-Fault                                                                                          | 144 $147$  |

|    | 4.4    | Operation during abnormal conditions                                                                    | 144<br>144 |

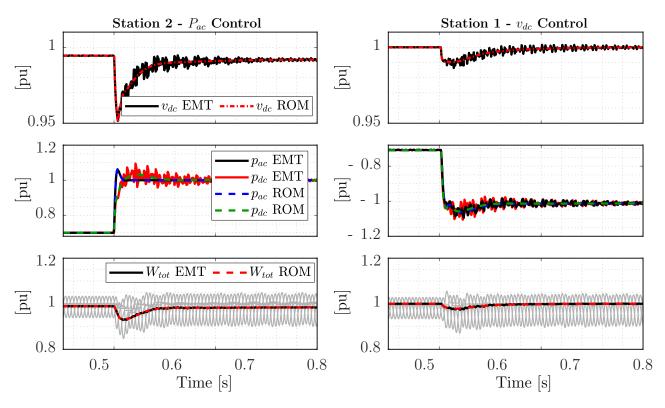

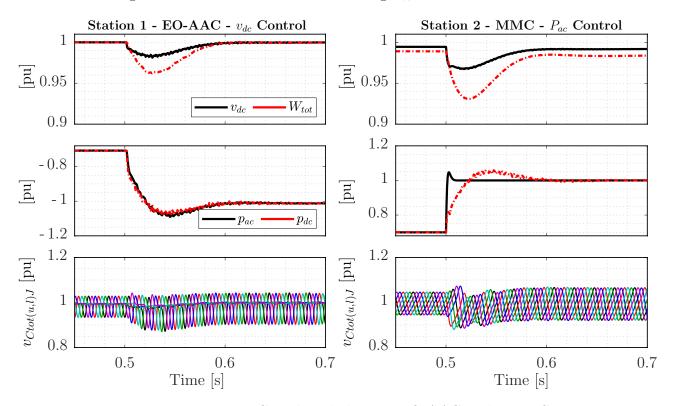

|    | 1 1    | 4.3.4 Detailed EMT Simulations                                                                          | 143        |

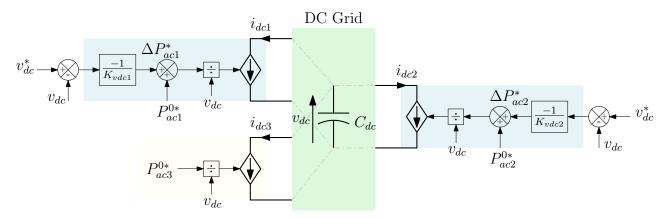

|    |        | 4.3.3 Operation under DC power derivative control                                                       | 141        |

|    |        | 4.3.2 Operation including converter's energy sharing                                                    | 139        |

|    |        | 4.3.1 DC voltage droop gain design                                                                      | 136        |

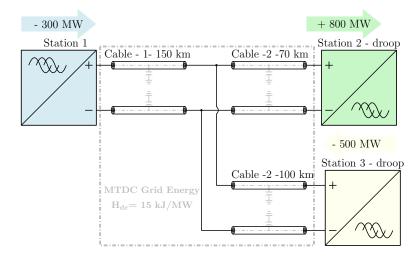

|    | 4.3    | Control of a Multi-Terminal DC Grid                                                                     | 136        |

|    | 4.0    | 4.2.3 Detailed HVDC link: Different application cases                                                   | 131        |

|    |        | 4.2.2 DC voltage dynamics improvement                                                                   | 127        |

|    |        | 4.2.1 Control of an EO-AAC connected to a variable DC voltage                                           | 125        |

|    | 4.2    | Control of an HVDC-Link                                                                                 | 124        |

|    | 4.1    | Introduction                                                                                            | 123        |

| 4  |        | plication to the HVDC and HVAC Grid Connection                                                          |            |

| 1  | Anr    | elieption to the HVDC and HVAC Crid Connection                                                          | 123        |

|    | 3.6    | Chapter Conclusion                                                                                      | 122        |

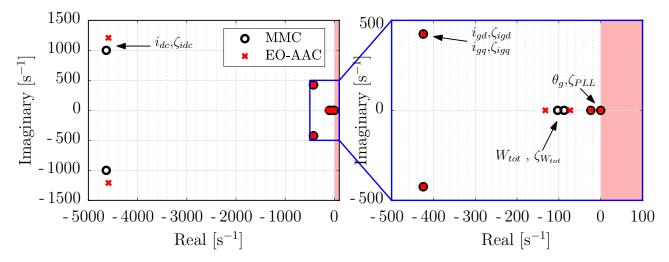

|    |        | 3.5.3 Common reduced order model for power system analysis                                              | 114        |

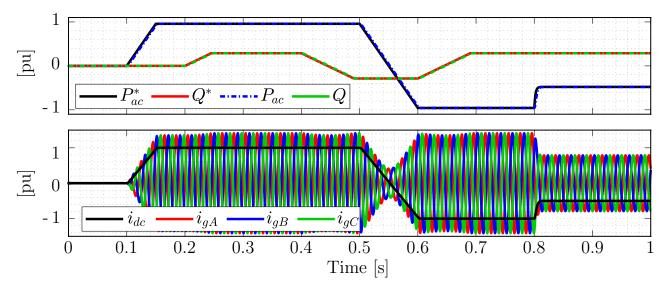

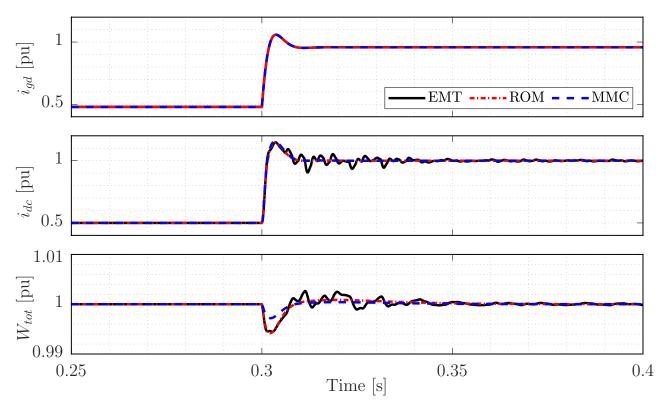

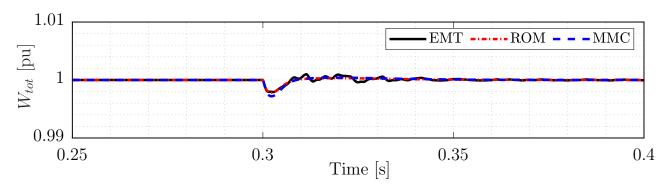

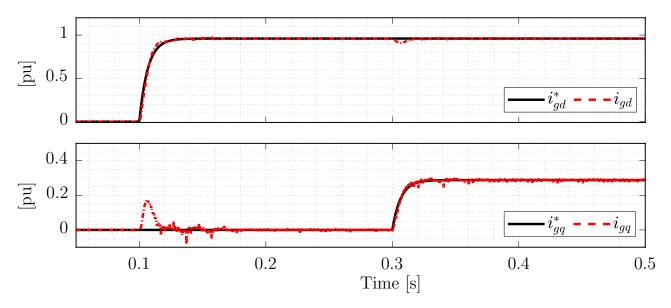

|    |        | 3.5.2 Response to active power reference changing                                                       | 113        |

|    |        | 3.5.1 Recall of MMC's Dynamics Modelling and Control                                                    | 111        |

|    | 3.5    | On Dynamic Equivalence between EO-AAC and MMC                                                           | 111        |

|    |        | 3.4.5 Vertical Balancing                                                                                | 106        |

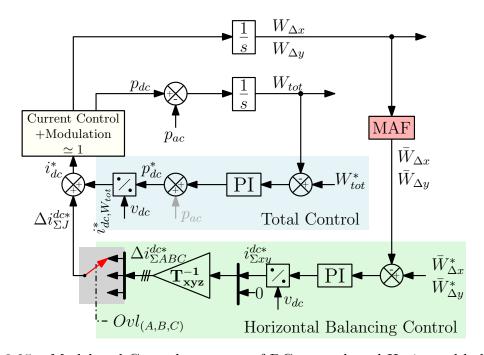

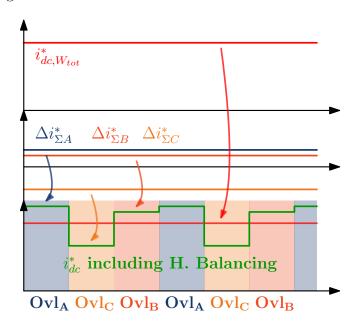

|    |        | 3.4.4 Horizontal Balancing                                                                              | 99         |

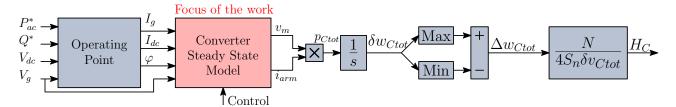

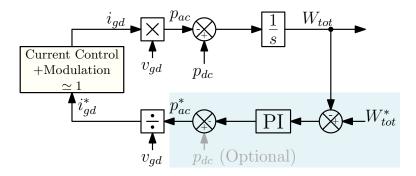

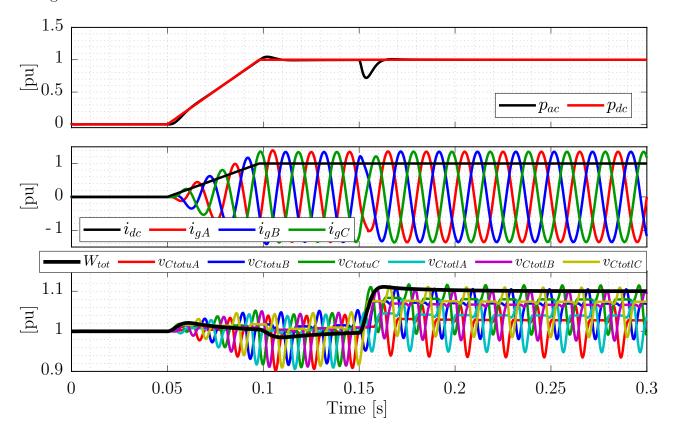

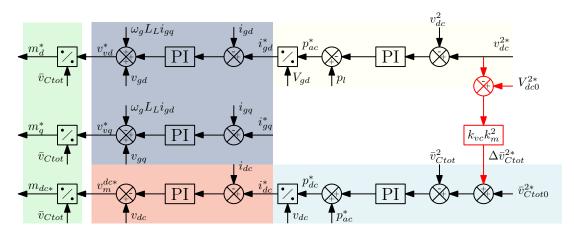

|    |        | 3.4.3 Total Energy Control                                                                              | 96         |

|    |        | 3.4.2 Basics of Energy Dynamic Models                                                                   | 95         |

|    |        | 3.4.1 AACs Energy Control Review                                                                        | 94         |

|    | 3.4    | Control of the Internal Stored Energy                                                                   | 92         |

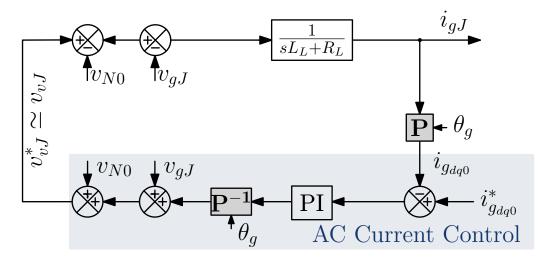

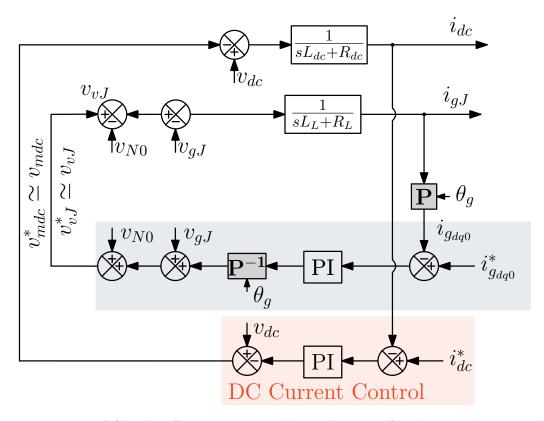

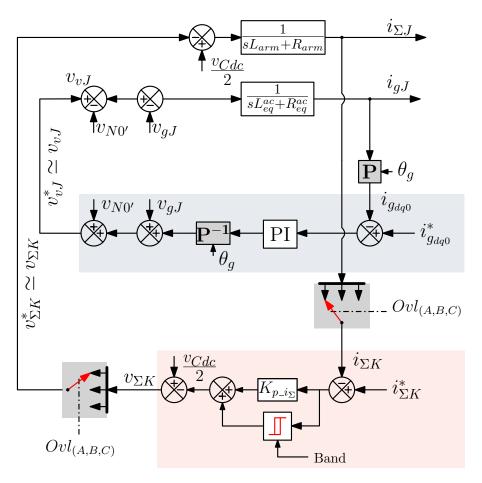

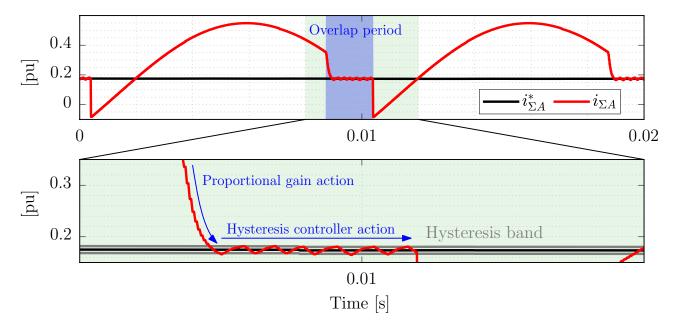

|    |        | 3.3.2 Current Control Structure                                                                         | 87         |

|    |        | 3.3.1 AC and DC side Dynamic Models                                                                     | 86         |

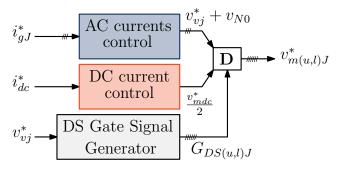

|    | 3.3    | Current Models and Control Structure Design                                                             | 86         |

|    |        | 3.2.2 Modulation Signals Generation                                                                     | 84         |

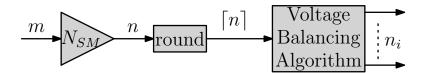

|    |        | 3.2.1 Insertion Index and SM Capacitor Voltage Balancing                                                | 80         |

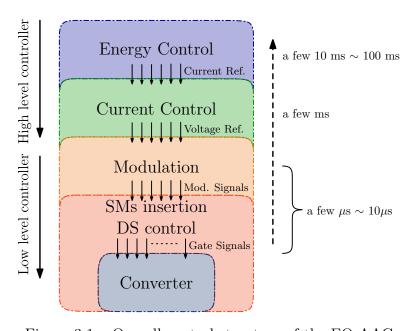

|    | 3.2    | Low-Level Controller                                                                                    | 80         |

|    | 3.1    | Introduction                                                                                            | 79         |

| 3  | Dyr    | namic Model and Control Structure Design of the EO-AAC                                                  | <b>7</b> 9 |

|    |        |                                                                                                         |            |

|    | 2.5    | Chapter Conclusion                                                                                      | 78         |

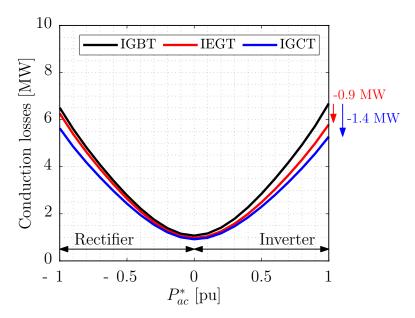

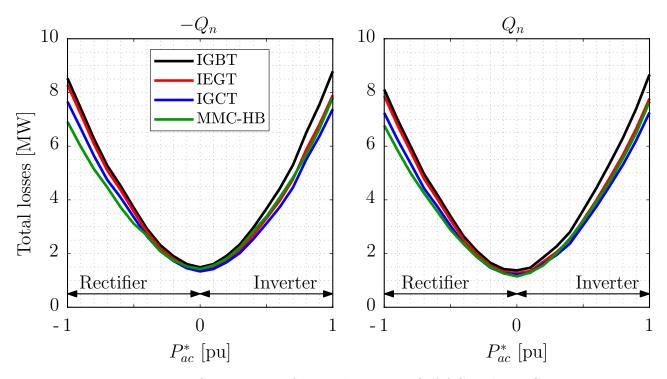

|    |        | 2.4.2 Losses Estimation Methodology                                                                     | 74         |

|    |        | 2.4.1 Description of Stacks Operation and Switching Lattern of Swis 2.4.2 Losses Estimation Methodology | 71         |

|    | 4.4    | 2.4.1 Description of Stacks Operation and Switching Pattern of SMs                                      | 69         |

|    | 2.4    | Losses Estimation In Modular Converters                                                                 | 69         |

|    |        | 2.3.4 Sub-Module Capacitance Selection                                                                  | 68         |

|    |        | 2.3.4 Sub-Module Capacitance Selection                                                                  | 67         |

|    |        | 2.3.3 Assessment of stored energy requirement in AAC                                                    | 60         |

| $\mathbf{A}$ | The | Short Overlap-Alternate Arm Converter           | 168 |

|--------------|-----|-------------------------------------------------|-----|

|              | A.1 | Modelling and Control of Currents in SO-AAC     | 169 |

|              |     | A.1.1 AC current dynamics modelling             | 169 |

|              |     | A.1.2 Overlap current dynamics modelling        | 169 |

|              |     | A.1.3 Control structure and validation          | 170 |

|              | A.2 | Zero Current Switching (ZCS) of the DSs         | 173 |

|              |     | A.2.1 Soft switching technique                  | 173 |

|              |     | A.2.2 Validation through EMT simulation         | 174 |

|              | A.3 | Energy Management in SO-AAC                     | 175 |

|              | A.4 | Conclusion on SO-AAC                            | 177 |

| В            | Pow | ver Derivations                                 | 178 |

|              | B.1 | MMC with sinusoidal modulation                  | 178 |

|              | B.2 | MMC with ZSVI                                   | 178 |

|              | B.3 | MMC with second order harmonic injection        | 179 |

|              | B.4 | Short-Overlap AAC                               | 180 |

|              | B.5 | Extended-Overlap AAC with sinusoidal modulation | 181 |

|              | B.6 | EO-AAC with ZSVI                                | 182 |

# Résumé étendu

#### Contexte de la thèse

L'utilisation massive des ressources d'énergie fossiles telles que le charbon, le pétrole ou le gaz naturel a grandement participer au réchauffement climatique dû à l'émissions de dioxyde de carbone (CO<sub>2</sub>). Dans l'objectif de ralentir l'augmentation de la température à la surface de la planète, une des actions possible consiste à repenser la manière dont l'électricité est produite. La production d'électricité était principalement basée sur l'utilisation de centrale à charbon, au gaz ou encore nucléaire. Afin d'améliorer l'impact carbone de la production d'électricité, il conviendrait de remplacer ces centrales à charbon ou au gaz par des sources d'énergie dites "renouvelables" telles que l'éolien et le solaire. Néanmoins, effectuer ce remplacement tout maintenant le niveau de résilience du réseau de transport actuel représente un réel défi.

En Europe, le potentiel de l'éolien offshore est très élevé, par exemple en mer du nord qui est en parti exploité par l'Allemagne, mais très souvent fortement éloigné des principaux points de consommation. Un rapatriement de cette énergie lointaine vers les consommateurs est donc nécessaire. Étendre le réseau de transport actuel en se basant sur des liaisons aérienne ou souterraine à courant alternatif (AC) est souvent in-envisageable pour deux raisons principales. La première concerne l'acceptation des personnes pour de nouvelles lignes aérienne principalement dû a une certaine méfiance vis-à-vis des ondes électromagnétiques générées par les conducteurs. La deuxième, technique, concerne la distance limite de transmission de l'énergie en alternatif au travers de câble sous-marins ou enterrés. Le couplage capacitif entre conducteurs enterrés augmente avec la longueur de la liaison et donc la consommation de puissance réactive de la liaison. Ainsi, la transport de l'énergie au travers de liaison sous-marine/souterraine à courant continu (DC) apparait comme une nécessité afin de permettre une intégration plus massive des sources renouvelables.

Contrairement à la transmission d'énergie par courant alternatif, dépendante de machines tournantes (ex: machine synchrone) et de transformateurs, l'utilisation de la technologie à courant continu nécessite une conversion statique de l'énergie au travers de convertisseurs d'électronique de puissance dédiés aux applications Haute Tension et Courant Continu (HVDC). Historiquement, le transport d'énergie au travers de liaison HVDC était réalisé au travers de convertisseurs à base de thyristors nommés LCC (Convertisseur Commuté par la Ligne), mais l'émergence des transistors de puissance IGBT (Transistor Bipolaire à Grille Isolée) dans les années 90 a permis d'envisager d'autres topologies telles que les convertisseurs à modulation de tension nommés VSC (Voltage Source Converter). Parmi les convertisseurs à modulation de tension, seules trois topologies ont étés implantées sur le réseau de transport. On retrouve notamment des structures classiques telles que les modulateurs 2-Niveaux et 3-Niveaux de type A-NPC (Active-Neutral Point Clamped), mais également des technologies de convertisseurs plus récente qualifiées de structures modulaires, notamment le Convertisseur Modulaire Multiniveaux (MMC). Les topologies traditionnelles de VSC nécessite une fréquence de modulation élevées afin de maintenir un taux de distorsion harmonique convenable dans les courant in-

jectés sur le réseau alternatif, cependant, il en résulte que les pertes d'énergie engendrées par la commutation des interrupteurs de puissance sont élevées (de l'ordre de 1 à 2%). De plus, la nécessité de monté en tension pour le réseau de transport HVDC impose une connexion en série de transistors impliquant une problématique de synchronisation des commutations et d'équilibrage des tensions aux bornes des interrupteurs. La classe des convertisseurs modulaires est basée sur l'utilisation de piles de Sous-Modules (SMs) permettant ainsi une approche multi-niveaux dans la modulation de tension. Cela permet de faciliter la monté en tension du convertisseur (et donc en puissance), de diminuer la fréquence de modulation pour un faible niveau d'harmonique rejetées et de fonctionner à rendement très élevée ( $\sim 99\%$ ).

### Les convertisseurs hybrides-modulaires

Depuis l'apparition du MMC et son utilisation comme convertisseur AC/DC pour les réseaux HVDC, l'intérêt pour les structures modulaires pour les applications haute tension/haute puissance n'a cessé de croitre. Cet intérêt à donné naissance à une nouvelle classe de convertisseurs d'électronique de puissance que l'on peut nommer: les convertisseurs hybrides modulaires.

Malgré certains avantages indéniables, le MMC, comme tout convertisseurs, a certains inconvénients tels que son incapacité a bloquer le courant de défaut lors d'un court-circuit côté DC (possible dans certains cas mais impact négatif sur le rendement) ou encore sont besoin stockage d'énergie interne élevé pour garantir un fonctionnement linéaire de la modulation de tension. La classe des convertisseurs hybrides-modulaires ambitionne de contourner certains inconvénients du MMC tout en gardant ces principaux avantages. L'un de ces convertisseurs pouvant potentiellement challenger le MMC, est le Convertisseur à Bras Alternés (AAC) dans un mode de fonctionnement dit à Empiètement Étendu (EO-AAC) qui représente le sujet de ces travaux de thèse.

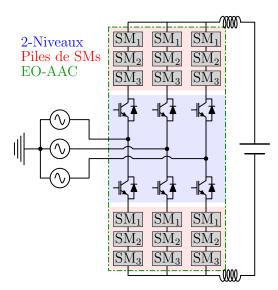

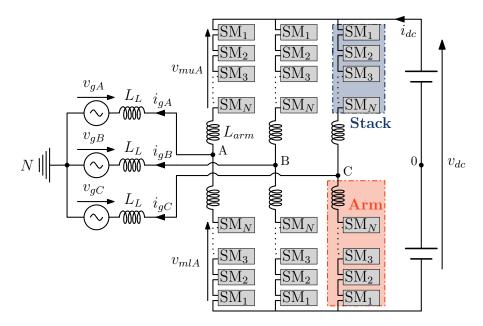

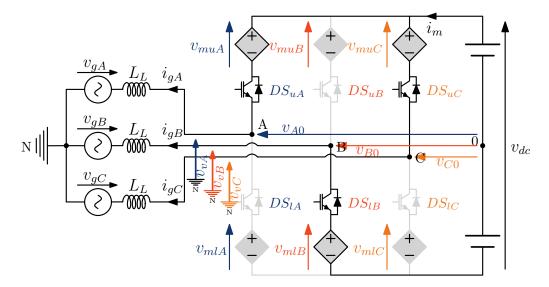

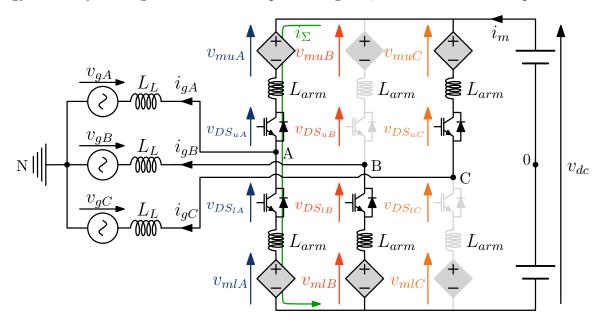

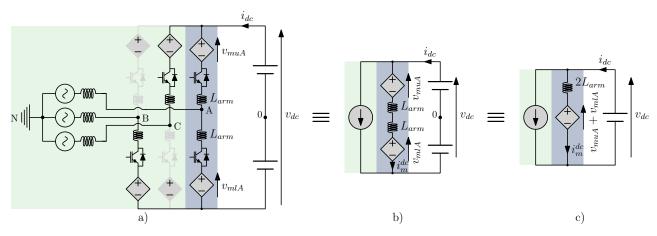

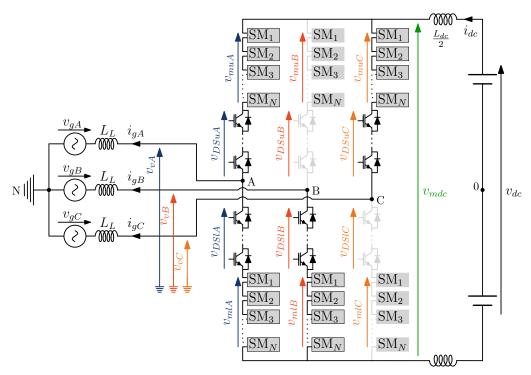

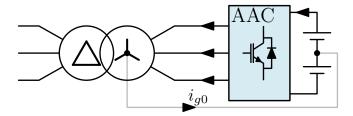

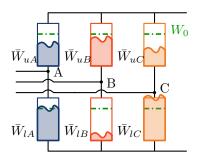

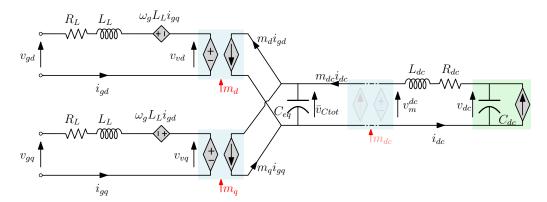

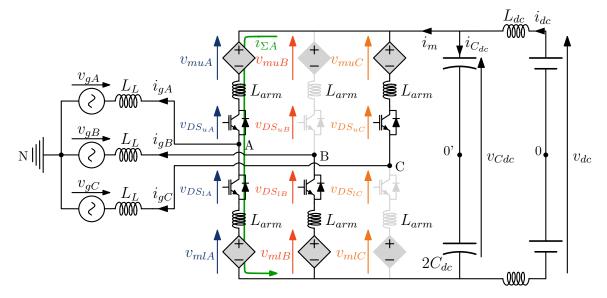

Figure 1 – Convertisseur à Bras Alternés - Mode de fonction à Empiètement Etendu (EO-AAC)

Comme le montre la Figure 1, le convertisseur EO-AAC est composé d'une structure 2-Niveaux haute tension (mise en avant dans le cadre bleu), qui implique la mise en série de transistors de puissance, et d'un pile de SMs dans chaque demi-bras (misent en avant dans le cadre rouge). Cet association de ces deux éléments (provenant des topologies 2-Niveaux et MMC) implique donc que la structure résultante, EO-AAC, est une structure hybride.

Les travaux existants sur cette structure montre qu'il est possible d'obtenir la capacité de blocage du courant de défaut lors de court-circuit côté DC avant un impact réduit sur le rendement du convertisseur ainsi qu'une empreinte au sol réduite comparé à un MMC de capacité en puissance équivalente.

Néanmoins, l'aspect de hybride de cette structure impose des contraintes en fonctionnement et sur la commande du convertisseur restant partiellement exploré. De plus, le fonctionnement et le comportement de ce convertisseur connecté au réseaux HVDC demeure très faiblement étudié malgré l'importance de ce sujet. Ainsi, l'objectif principale de ces travaux est de répondre à la question suivante : Le EO-AAC, peut-il réellement challenger le MMC pour les applications réseaux HVDC ? Pour y répondre, une étude rigoureuse comportant de l'analyse statique, dynamique et réseau a été menée.

#### Plan de la thèse

Le plan de la thèse s'articule autour de quatre chapitres.

- Chapitre 1: Une introduction à la modulation de tension pour les système de conversion AC/DC est donnée dans un premier temps pour ensuite présenter la structure EO-AAC. Ce chapitre revient notamment sur, comment générer un flux de puissance active au travers d'un convertisseur qu'il soit 2-Niveaux commandé en pleine-onde ou en Modulation à Largeur d'Impulsion (MLI) mais également multi-niveaux tel que le MMC. Ces caractéristiques fondamentales sont ensuite réutilisées afin d'introduire de manière systématique la structure EO-AAC. Grâce à cette introduction, la plupart des degrés de liberté exploitable par la commande sont mis en avant.

- Chapitre 2: Une étude de dimensionnement en régime permanent est réalisée dans ce chapitre. Celui-ci s'articule autour d'un modèle statique du convertisseur intégrant les degrés de liberté de la commande afin de les exploités pour obtenir un dimensionnement du convertisseur le plus avantageux possible. Ainsi, sur la base de ce modèle statique, on s'intéresse au nombre d'éléments actifs dans le convertisseurs, à l'estimation de stockage d'énergie interne requit pour fonctionner ainsi qu'à l'estimation des pertes dans la structure. La méthodologie appliqué dans ces travaux et les outils développés ayant pour but d'être générique et exploitable pour d'autres topologies modulaires.

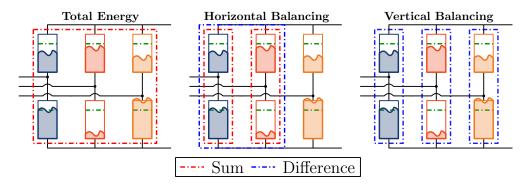

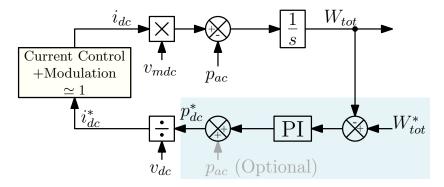

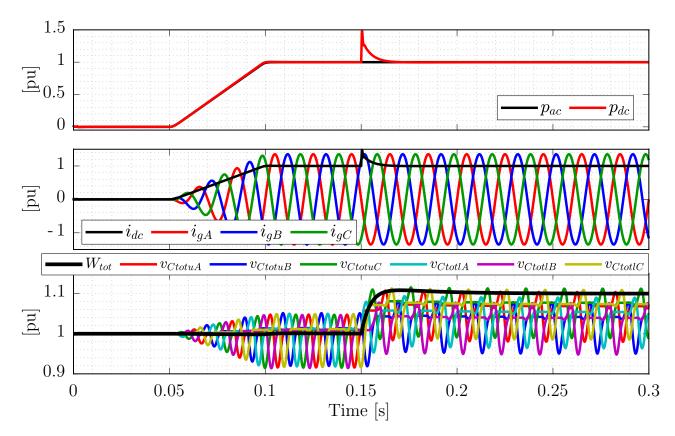

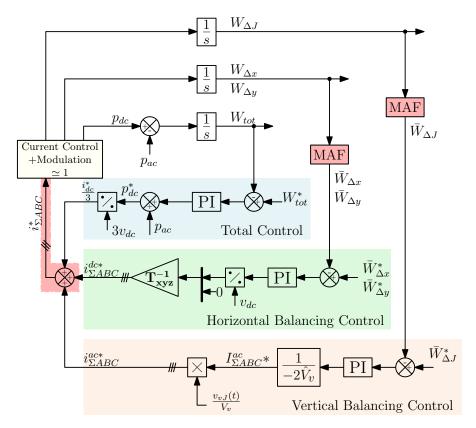

- Chapitre 3: Dans ce chapitre, la commande du convertisseurs est développée, depuis la commande dite de "bas niveaux" (proche du composant) jusqu'à la couche supérieur dite "haut niveaux" (boucle de régulation). Cette étude met l'accent sur la partie haut niveaux du contrôle, et notamment le contrôle de l'énergie stockée dans le convertisseurs. L'une des principales difficultés du EO-AAC quant à sa commande vient de l'aspect "discontinu" dans la régulation de l'énergie stockée dans chaque pile de SMs. Ainsi dans cette thèse, on introduit les notions de contrôle total et d'équilibrage horizontale et verticale dans la commande du EO-AAC permettant une distribution égale de l'énergie entre chaque pile de SMs en transitoire et en régime permanent. Finalement, il est démontré que grâce à la continuité du contrôle total il est possible d'obtenir un modèle d'ordre réduit et continu du EO-AAC en négligeant l'impact des boucles d'équilibrage horizontale et verticale. Ce modèle réduit permet, pour la première fois, d'envisager le EO-AAC dans étude de stabilité du réseau en petits signaux.

- Chapitre 4: L'intégration du convertisseur dans un environnement réseaux est détaillé dans ce chapitre. Il comporte deux principales point de discussions: la connexion au

réseau HVDC et les régimes de fonctionnement anormaux (exemple déséquilibre AC). La connexion au réseau HVDC est traité dans le cas d'une liaison point à point et étendue a un réseau multi-terminaux (MTDC). Grâce au développement du modèle réduit, il est montré que, comme le MMC, le EO-AAC peut participer au réglage de la tension DC en partageant sont énergie stockée avec le réseau HVDC. Cette participation à la stabilisation du bus DC est, aux valeurs de dimensionnement prés, strictement la même que le MMC malgré un fonctionnement interne des convertisseurs très différent. Cependant, cette différence de fonctionnement est mise en avant lorsque les conditions de fonctionnement ne sont plus idéales telles que lors d'un déséquilibre en tension sur le réseau. Dans ces conditions, la structure atteint ses limites mais également la commande bâti dans le Chapitre 3. Cela suppose donc de repenser une commande du EO-AAC ayant pour contraint le fonctionnement du convertisseur dans le cas du réseau alternatif déséquilibré.

#### Conclusions de la thèse

Les convertisseurs électroniques de puissance et les systèmes à courant continu sont les clés pour améliorer l'intégration des sources renouvelables à distance ainsi que le renforcement de certaines régions. Le convertisseur modulaire multi-niveaux s'est avéré être la topologie la plus appropriée pour atteindre ces objectifs. Cependant, les topologies émergentes combinant d'une part l'aspect modulaire du MMC et les fonctionnalités des convertisseurs AC/DC les plus simples comme l'Eo-AAC peuvent remettre en cause le MMC.

Cette thèse vise à étudier le fonctionnement, la conception et la commande des EO-AAC. Dans ce qui suit, les principales conclusions du chapitre sont résumées :

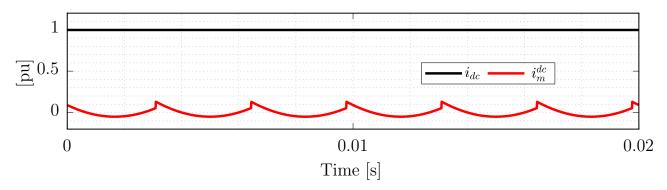

- 1. Une approche méthodologique expliquant l'origine de la topologie AAC et le principe de fonctionnement principal de l'EO-AAC ont été détaillés dans le Chapitre 1. L'idée principale derrière la topologie AAC est de faire fonctionner simultanément deux types de modulation: la commande pleine onde et la modulation de tension. Cependant, chaque méthode a ses propres spécificités. La modulation pleine onde nécessite que le convertisseur fonctionne comme une source de tension en fixant l'amplitude des tensions alternatives mais l'angle est un degré de liberté. Le contrôle de la tension modulée permet de fournir l'amplitude de la tension et son angle en degrés de liberté. Lorsqu'ils sont combinés, un convertisseur avec deux fois moins de SM qu'un MMC est obtenu. Néanmoins, son fonctionnement est limité à un certain indice de modulation fixé par la modulation pleine onde et le courant continu est toujours une quantité modulée fortement ondulée à six fois la fréquence de réseau. Le mode empiété est introduit pour permettre la mise en œuvre d'un schéma de contrôle d'énergie assurant l'équilibre de puissance dans le convertisseur et récemment étendu jusqu'à ce qu'une stratégie dédiée de filtrage actif du courant continu puisse être mise en œuvre. C'est dernière modification a donné lieu au EO-AAC.

- 2. L'EO-AAC a besoin de plus de SM par pile pour obtenir le filtrage actif du courant continu. Alors, la technique d'injection de tension homopolaire (ZSVI) a été réalisée pour diminuer le nombre de SM dans le convertisseur. Ainsi, le chapitre 2 a suivi l'impact du ZSVI sur le dimensionnement des composants de puissance, la capacité des SM et l'estimation des pertes. Ainsi, cette étude révèle que pour obtenir un blocage du défaut DC à haute tension alternative, il faut environ 25% moins de SM que le MMC. Le besoin en énergie est de l'ordre de 10-15 kJ/MVA. On estime que les pertes sont similaires à celles du HB-MMC fonctionnant à un faible indice de modulation (c'est-à-dire inférieur

- à 1). Cependant, avec une petite amélioration, le HB-MMC restera plus efficace que l'EO-AAC.

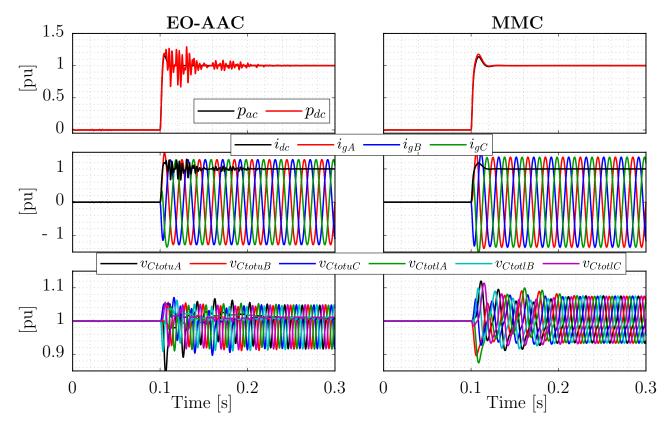

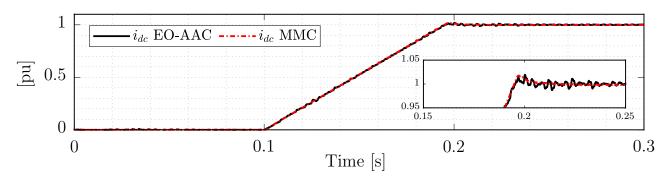

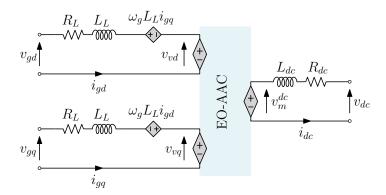

- 3. Dans le chapitre 3, une évaluation globale des contrôleurs a été détaillée. Du contrôleur de bas niveau, une exigence a été clairement mise en évidence. La nécessité d'une compensation appropriée de l'ondulation de tension du condensateur SM est très importante pour maintenir un filtrage actif efficace du courant continu. Dans une deuxième partie du chapitre, le contrôle haut niveau a été détaillé: le contrôle des courants alternatifs, du courant continu et de l'énergie stockée dans les piles de SMs. Une combinaison a été proposée réalisant un contrôle continu de l'énergie totale. Deux autres commandes, purement séquentielles, sont réalisées à des fins d'équilibrage horizontal et vertical. Ces comportements séquentiels impliquent une injection transitoire d'harmoniques sur le courant alternatif ou continu. Cependant, grâce à une dynamique continue, il est prouvé que l'EO-AAC exécute une dynamique similaire à celle du MMC, comme le soutient le modèle d'ordre réduit développé. Ainsi, la principale conclusion de ce chapitre est l'équivalence des deux convertisseurs du point de vue du réseau.

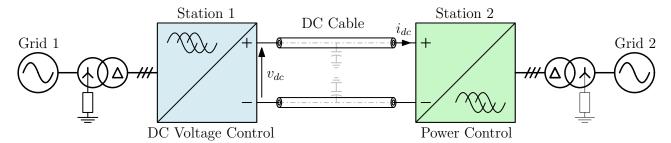

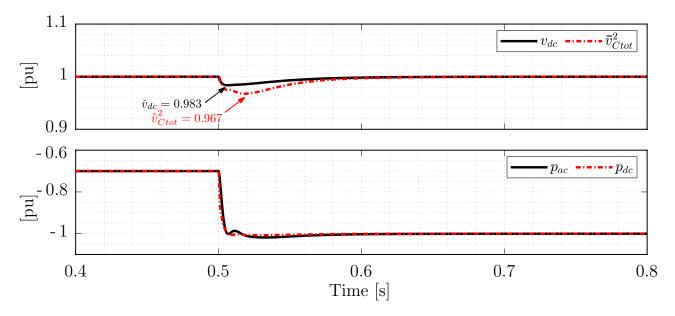

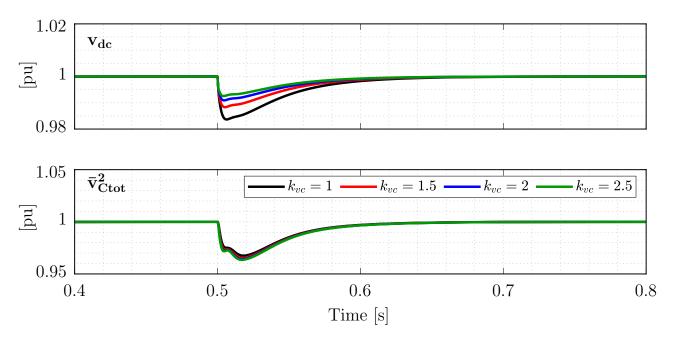

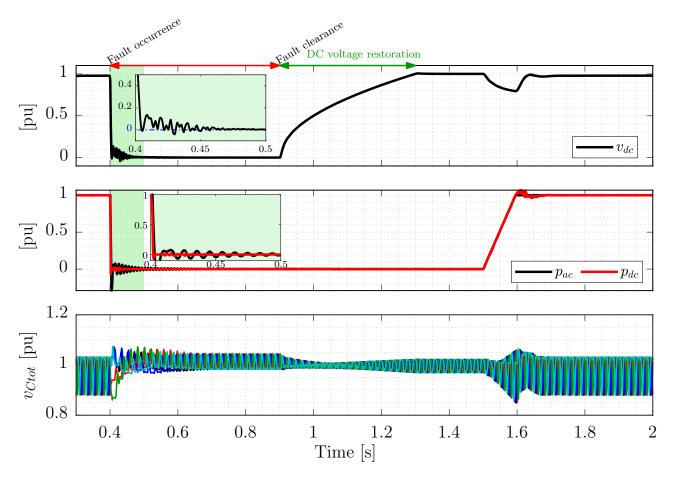

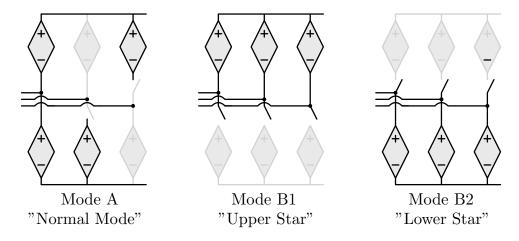

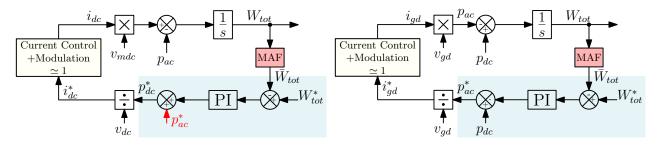

- 4. Pour étudier la dynamique du convertisseur lorsqu'il est connecté au réseau, le chapitre 4 fournit plusieurs cas de test basés sur le logiciel EMTP-RV. Ainsi, il est d'abord présenté un moyen d'obtenir un support de tension continue grâce à l'énergie interne du convertisseur initialement conçu pour le MMC. Cela a été possible grâce au contrôle continu de l'énergie totale basée sur la puissance continue. Ainsi, en rassemblant tous les contrôleurs conçus jusqu'à présent et les techniques de contrôle de la tension continue, des liaisons HVDC point à point ainsi que MTDC ont été simulées, montrant l'efficacité de l'EO-AAC. De plus, des tests d'interopérabilité de MMC ont été effectués, montrant les bonnes performances de l'ensemble du système, même en cas de MMC avec contrôle CCSC. Enfin, quelques ouvertures concernant la gestion de l'énergie en cas de défaut DC, système AC déséquilibré ont été présentées.

Aux travers des travaux menés au cours de cette thèse, il nous est possible de donner un avis général sur la topologie EO-AAC. Du point de vue de la conception et de l'encombrement, cette topologie est extrêmement intéressante car elle permet un fonctionnement similaire au MMC avec un nombre réduit de composants et de bras conducteurs. Cependant, ce dernier point est aussi ce qui semble être la principale limite de cette topologie comme souligné dans le Chapitre 4. Par exemple, dans le cas du contrôle de l'énergie par la puissance DC, plusieurs opérations sont assurées par un seul bras du convertisseur. (filtrage actif, contrôles total, horizontal et vertical). Ainsi, chaque fois qu'un déséquilibre potentiel se produit, ce manque de contrôlabilité et cette sensibilité élevée à l'indice de modulation peuvent être un problème.

Malgré une conclusion mitigée sur la topologie EO-AAC, il est à noter que l'étude de topologies aussi complexes (l'EO-AAC en est une parmi d'autres) nous a permis de prendre du recul sur la façon de contrôler certaines structures classiques comme le MMC. , STATCOM modulaire basé sur la méthodologie développée dans cette thèse.

# Introduction to HVDC Systems

# 1 Context and motivations

The massive use of fossil energy sources, oil, coal and natural gas has largely participated to the global warming due to carbon dioxide emissions [2, 3]. To slow down the increasing of the global temperature, one of the possible action is to rethink the way that electricity is produced. So far, electricity power plants were mainly based on coal, natural gas, nuclear reactors. Replacing the fossil fuels based power plants by renewable sources like solar or wind farms while maintaining the same level of resilience for the power system is a huge challenge.

In Europe, large amounts of renewable energy are available on remote locations, often off-shore or near the sea [4,5]. Expanding the current AC transmission system to bring these energy to the comsuption point is often not possible for two main reasons. Firstly, the acceptance of people for new lines is becoming more and more difficult to obtain. Then, the transmission of a large amount of power for a long distance are restricted for HVAC cables [6]. For these reasons, but also economical [7], High Voltage Direct Current transmission schemes (HVDC) are now becoming more and more relevant [8] to enhance the massive integration of renewable sources.

Unlike AC transmission system that relies on rotating electric fields through machine and transformer windings, the HVDC system is based on a static conversion of the energy for which dedicated power-electronics devices have developped. Up to 30 years ago, the most suitable technology in HVDC was the thyristor-based Line Commutated Converter (LCC) technology, but the Voltage Source Converter (VSC) technology is now well established in HVDC. There are different topologies of VSC, but only three of them have been adopted for real project: 2-level, 3-level Active-Neutral Point Clamped [9] (A-NPC) and Modular topologies [10–12]. Traditional topologies of VSC have a high switching frequency (1–2 kHz) for obtaining a low harmonic distortion, leading to higher switching losses as well as high voltage stresses. In high power applications, the conversion losses result in high cost for the grid operators [13]. For this reason, a new Modular VSC technology taking advantages of the principle of cascaded cells called Modular Multilevel Converters (MMC) introduced in [14]. The main advantage for this new class of converter is the possibility of working with lower switching frequencies (only several times the fundamental frequency), while simultaneously achieving better harmonic performance compared to traditional VSCs [15–17].

HVDC projects based on VSC-HVDC technologies highly increased these last twenty years. Thanks to Pr. Mike Barnes from the University of Manchester providing the monthly "VSC-HVDC NEWSLETTER", the information about the number of VSC-HVDC projects in operation, or not, is easily obtained for the community. Thus, as reported in this newsletter (dated to June 2021) some 47 projects are commissioned around the world while 55 are being commissioned within the 10-15 years.

# 2 Main Principles for the HVDC Systems

### 2.1 Point-to-point schemes

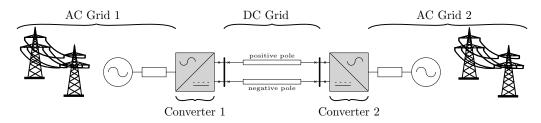

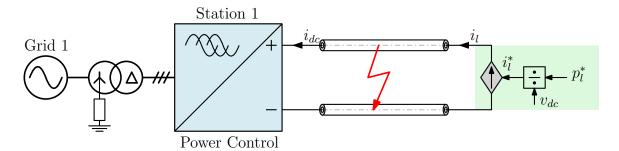

The most common configuration for HVDC projects is the so-called "point-to-point" scheme, which is depicted in Figure 2. In this configuration, there are two AC-DC converters interfaced through a DC conductor which may be a cable or an Over-Head Line (OHL). One of each converter in Figure 2 has a specific function. One converter is in charge of the power flow in the DC link, while the other fixes the DC voltage to a certain level as it will detailed in Chapter 4. The advantage of this configuration with respect to the classical AC lines is the ability to control the power flow in the system [18].

Figure 2 – Example of HVDC point-to-point scheme

Figure 2 depicts a symmetric monopole scheme which providing positive and negative poles and grounded middle point. Different types of scheme exist [19]: the asymmetric monopole using either earth or metallic grounded as a return, and the symmetric bipolar scheme requiring "twelve pulse" bridges (in both LCC or VSC technology) but more resilient in case of fault on one pole since the other one can be used to still convert energy.

Even if the list of HVDC link in the world is very extensive nowadays, the modern history of VSC-based HVDC link is remarked by three main disruptive events:

- 1. **2009**: ABB commissioned the first offshore HVDC system *BorWin1* which was the first one to use VSC for the converter stations [20,21].

- 2. **2011**: The first HVDC system using Modular Multilevel Converters; *Trans Bay Cable* commissioned by Siemens [22, 23].

- 3. **2015**: First HVDC link with MMCs for transmitting power in the GW range called *Inelfe*, which was commissioned by Siemens [24].

## 2.2 Multi-Terminal DC schemes

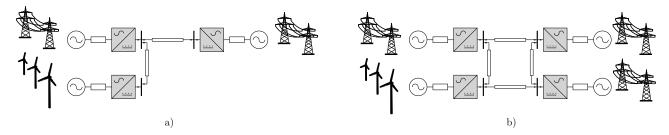

When more than two converter stations are connected to the same DC grid, the configuration is referred as a "Multi-Terminal DC" system (MTDC). As illustrated on Figure 3, a MTDC system can be radial (mostly in case of three terminals or long distance between converter stations) or meshed like the current AC transmission system.

These schemes, regardless of the system topology are expected to provide additional features compared to point-to-point HVDC links, such as:

- More flexibility in power dispatch [8]

- Optimized assets for offshore wind farm connection to shore and power transmission capability [25]

- Frequency support to onshore grids [26, 27]

Figure 3 – MTDC System: a) radial b) meshed

• More reliability (can operate or at least partially operate even if one element is out of service) [28]

To control the power flows in a DC system, meshed or radial, two layers of controllers are likely to be used [29]. The first control layer is managed by TSOs to dispatch suitable converter set-points in order to achieve a precise power flow control [30]. Also, in case of a contingency, it would automatically adapt set-points to find a new stable operating point [31]. Second, there are local controlers inside the HVDC stations such as DC voltage droop control used to the adjustments of set-points in real-time [32].

#### MTDC real projects

As for HVDC link, MTDC systems develoment has reached some milestones with the following project.

Even if the list of HVDC projects in the world is very extensive nowadays, the modern history of VSC-based HVDC systems is remarked by four main disruptive events:

- 1. **2013**: First three-terminal "multivendor" MTDC grid with MMCs commissioned by the State Grid Corporation of China (SGCC) [33].

- 2. **2020**: First four terminal MTDC system including MMC with  $\pm 500$  kV DC comissioned as the Zhangbei project by SGCC. [34,35].

- 3. **2020**: First Hybrid-MTDC system including LCC and MMC with  $\pm 800$  kV DC known as Wudongde HVDC project. It has been put in operation by China Southern Power Grid (CSG). [36].

Most of them are situated in China. The firsts were the well known Nan'ao and Zhoushan projects [37,38] in 2013 and 2014 respectively.

The latest MTDC systems have been commissioned with outstanding voltage and power ratings. The Zhangbei project [34,35] which connects four regions including the city of Beijing. The nominal DC grid voltage is  $\pm 500$  kV, stations ratings are 3000 MW and 1500 MW. The project also includes the use of DC breakers, which is a key point in the development of future DC systems. The second project, called Wudongde-UHVDC also highlights another important situation that may occur more often in the future: the interoperation between different kind of stations, also called hybrid MTDC systems. This project is very particular in respect of others since a 8000 MW LCC station is connected to two VSC stations (i.e. 5000 MW and 3000 MW). So far, the goal of 8000 MW is not reached.

Thus, these last two projects have presented the main concerns for future HVDC systems investigated these past years:

- the DC fault blocking capability through DC Circuit Breaker (DCCB) [39,40], or not

- the interconnections between different topologies (even different modulators i.e. current and voltage source)

#### DC circuit breaker

One of the key element to enable the expansion of MTDC schemes around the world is the protection in case of DC-Fault. Unlike the AC system which is highly inductive, a DC system has no natural current rising limitation like transformers, generators etc... In case of a DC-fault, the current rising is very high, requiring a very fast current interruption is mandatory [39]. Moreover, there is no zero crossing on DC side. To tackle this issue, specific DC Circuit Breakers (DCCB) have been developed as in the European project PROMOTioN [41].

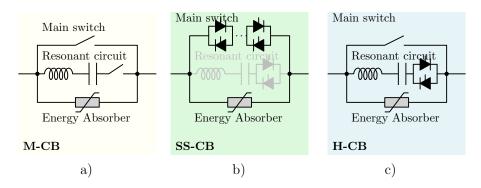

DCCBs are organised around three main categories. First, the Mechanical-CB which is leave a part in favour of newer topologies like the Solid State-CB (SS-CB) based on power-electronics devices like Gate Commutated Thyristors (GCTs) [40] or more recently, Hybrid-CB (H-CB). This last structure of CB features an ultra-fast mechanical switch and a solid-state part. The solid-state part participates to the current extinguish allowing to open the mechanical switch. These DCCBs are conceptualised below:

Figure 4 – Simplified illustration of DCCBs topologies: a) M-CB b) SS-CB c) H-CB

In each topology of DCCBs are found three characteristics elements: the main switch (mechanical or semi-conductor) an auxiliary switch that can activate a resonant circuit (some SS-CB are not containing a resonant circuit [39]) and an energy absorber [42–44]. Depending on the topology, the opening of the main switch and the fault isolation can be achieved in a few ms. For instance, the Zhangbei project tests report a fault isolation in less than 3 ms.

# 3 Power Electronics for HVDC system

As mentioned in a previous section, currently, three types of AC/DC stations may be found in operation on the grid: LCC, 2-level and 3-level topologies and the MMC.

#### 3.1 Line Commutated Converter

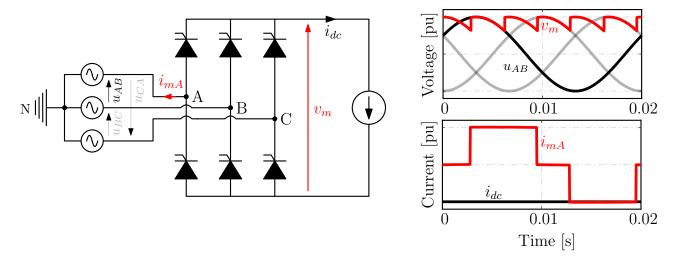

In the history of HVDC system, LCCs were the first conversion station to be used (with mercury-arc valves then replaced by thyristors). The LCC is a current-source converter; that means a modulation of the DC current to generate the AC ones. As a result, the DC voltage is modulated using the line-to-line voltages. This is depicted on Figure 5 where the modulated variables are labelled in red. The main principle of the LCC it to switch ON valves according to the firing angle reference  $\alpha$  in order to vary the average value of the DC voltage  $v_m$ . Hence, the power reversal is achieved by DC voltage polarity reversal. The OFF switching is not controllable in basic thyristors.

Figure 5 – Simplified illustration of a six-pulses LCC - Modulated quantities waveforms for  $\alpha=20$  degrees

Using LCC topologies as interface between AC and DC system present some advantages. Thyristors are very efficient regarding ON-state voltage drops [45–47] and can withstand high ratings in terms of continuous current and voltage blocking capability [48]. Therefore, HVDC stations using LCCs are likely to be generate a very level of losses. Hence, their power capability is huge, especially in case of bipolar link where twelve pulses bridges are used.

Despite these important features, LCCs also suffer from shortcomings. As the converter is not fully controllable active and reactive components in the AC side are coupled. Thus, the load angle of the AC currents is strongly linked to the value of  $\alpha$  [49]. In addition to this inherent reactive power generation, low order harmonics in modulated quantities are observed. Thus, on the AC side is needed a compensation of the reactive power and a passive filter. A second passive filter is needed on the DC side. It is also reported that the OFF switching may fail in some conditions often caused by AC voltage drops with high DC current or when connected to a weak grid. It results in a short-circuit of the DC side.

# 3.2 Voltage-source topologies

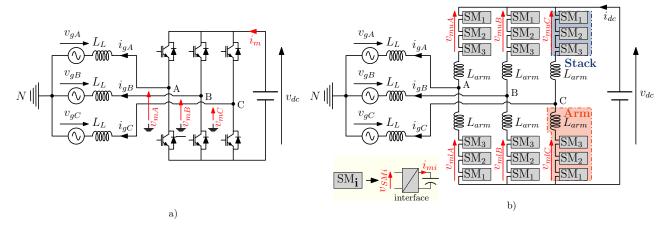

This section presents some basics about the 2-level and the MMC topologies as more detailed will be provided in Chapter 1. The 3-level A-NPC structure is not fundamentally different from the 2-level, so focusing on the this latter is sufficient. As in the LCC, the origin of the VSC comes from the kind of modulation that is performed. Most of the time, the modulation of a DC voltage is used, thus, 2-level converter and MMC are a part of the VSC class.

A 2-level VSC, depicted on Figure 6 a), is based on Insulated Gate Bipolar Transistors (IGBT) which are controllable at turn ON and OFF. As a result, the controllability can be improved compared to the LCC, as well as the harmonic distortion of currents if the modulation frequency is sufficiently high. On the other hand, IGBTs presents higher ON-state voltage drops and smaller ratings than thyristors increasing conduction loss. Moreover, the hard switching of transistors introduces high switching losses depending on the modulation frequency. In HVDC application, the switch assembly is made by several IGBTs connected in series as LCC valves [50], [51]. The switching needs for a perfect synchronism at the opening and closing to preserve the integrity of all switches. It becomes particularly challenging at high voltage and high frequency. Some solutions are reported in [52–56] which aims to use active or passive

approaches to synchronise gate signals and balance voltage across IGBTs.

Figure 6 – Simplified illustration of a) 2-level VSC and b) MMC including 3 SMs per stack

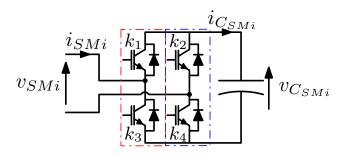

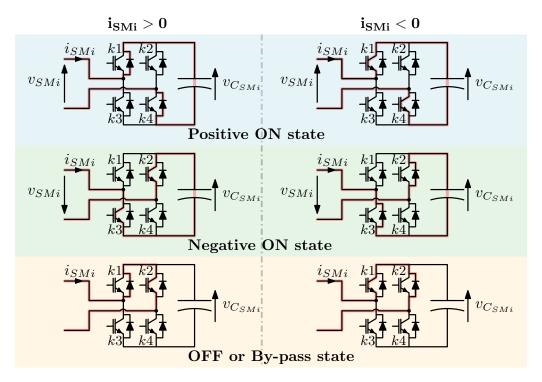

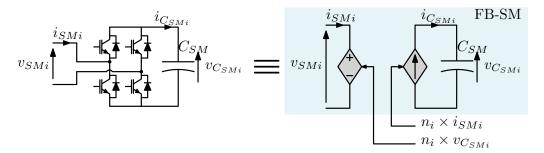

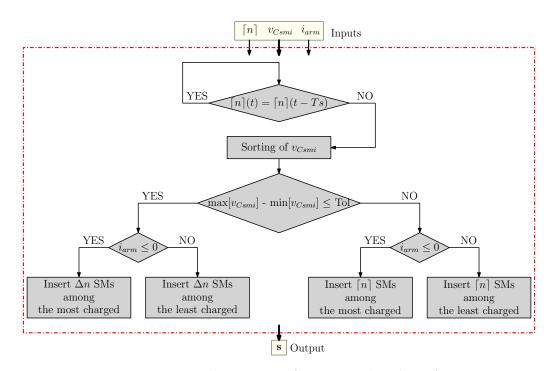

The MMC is fundamentally different from the 2 or 3-level topologies. This difference lies in the modulated quantities. Compare Figure 6 a) and b). A 2-level topology, modulates one of the AC and DC side quantity at the same time. With MMC, none of the grid side quantities are modulated. The modulation stage is internal and freed from the nature of the sources that are connected to the MMC terminals. This property comes from the elements constituting the arms. A MMC is composed of stack of SMs as presented on Figure 6 a). A SM, is composed of a floating capacitor interfaced through a small converter like the Half-Bridge (HB), the Full-Bridge (FB) or many others... By controlling this interface, the SM capacitor can be inserted or by-passed so that a multilevel modulated voltage waveform can be synthesized. In HVDC, several hundreds of SM are involved almost removing the needs for passive filtering.

The use of stacks of SMs also provide a significant advantages over classical topologies since it is no necessary to switch all the SMs at the same time and at high frequency. The insertion or the bypass of a SM is a punctual action, which, in average occurs a few times per fundamental period (i.e. the modulation frequency is less than 100-300 Hz) [57]. Thus, the overall switching losses decreased leading to a VSC-HVDC station with a very high efficiency challenging the LCCs for power ratings in the range of 1000-1500 MW (even 3000 MW according to newest projects).

Finally, one question may raise nowadays. More and more projects are based on MMC which has proven to be a powerful converter for many important points: modular hardware, energy efficiency, controllability, dynamics, system services etc... this is undeniable. So, can the MMC be challenged in the range where it is the best? Some solutions are worth being studied.

# 3.3 Modular hybrid topologies

First of all, let us provide a possible definition of Modular hybrid topologies which is important for the following of the section and Chapter 1.

<u>Def</u>: A modular hybrid topology uses the principle of stack of SMs. These stacks of SMs are combined to different topologies which are not limited to VSC. This combination of two modulators form an hybrid modulation scheme that must guarantee a proper functioning of the

resulting topology.

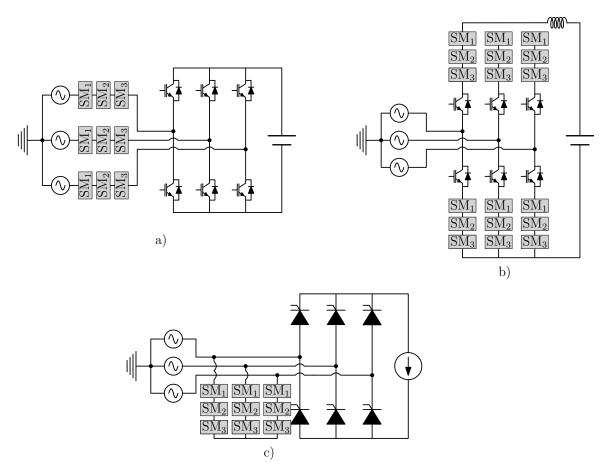

Over the years, many proposals for hybrid topologies suitable for HVDC (and even MVDC) have been published where the main of them and some others can be found in [58–72]. Until now, none of these solutions are proposed for commercial solution. A simplified illustration for some of them (the most "basic") is proposed in the following.

Figure 7 – Simplified illustration of a) Hybrid VSC with AC side stacks b) Hybrid VSC with DC side stacks and c) Hybrid LCC with single-star connected stacks

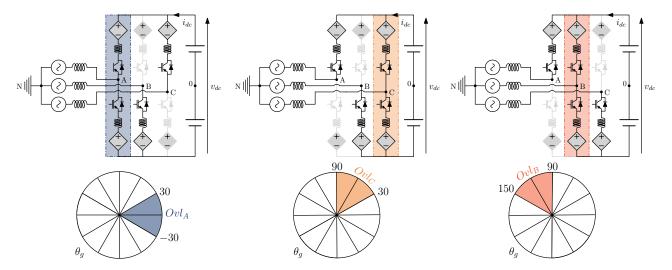

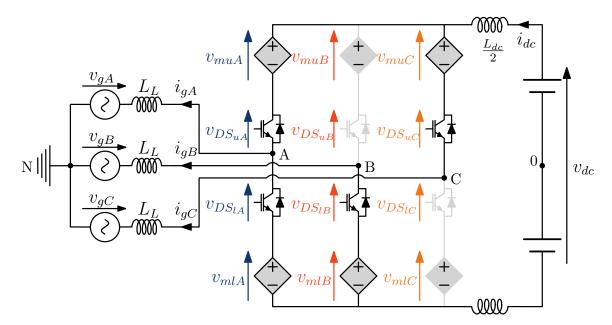

On Figure 7 are presented some of the simplest hybrid topologies based on both VSC and LCC technologies. Depending on the the initial converter, the stacks of SMs may act as an active filter of voltage or current. Thus, these kind of HVDC stations are expected to be more compact than a MMC with equivalent functionalities. Among these three topologies, b) is very similar to the MMC. It is called the Alternate Arm Converter (AAC) [64], more precisely, according to this figure this is an Extended Overlap-Alternate Arm Converter (EO-AAC) [71]. In this thesis, this last topology is studied.

# 4 Main Contributions and Layout of the Thesis

At the beginning of this research project (2017), the literature about AACs was limited to proof for the good working of the converter [64,72–74], some steady-state analyses [1,75]. The control of the converter was incomplete (or at least unpublished..) and finally the question of the dynamic behaviour when connected to the grid essentially focused on faulty conditions [19]. Based on this previous works, the following questions raise:

- 1. How to operate this hybrid topology and generate the appropriate hybrid modulation scheme?

- 2. How to improve the existing works on the converter steady-state analysis?

- 3. What is the appropriate approach to control internal dynamics?

- 4. Is the converter able to provide similar properties to MMC despite its hybrid operation?

This Thesis, which aims to answer the aforementioned questions, deals with the steady-state and dynamic modelling of the Extended Overlap Alternate Arm Converter. The idea is to adopt a step-by-step approach by establishing a solid basis for the analysis of this converter.

The main contributions and the layout of this work are listed below:

- 1. Chapter 1 presents a methodology explaining the origins of the AAC topology similarly to [58], but then, a rigorous approach highlights most of the degrees of freedom of the structure to be exploited by the control.

- 2. In Chapter 2, a detailed steady-state model considering each operating modes, the impact of the control, is proposed for the estimation power electronics devices sizing and passives as well. This steady-state model is extended to losses estimation.

- 3. Chapter 3 provides a comprehensive description of the dynamics modelling and control. A control structure allowing to manage every state-variables in the system is proposed and validated through strong events. A comparison between the MMC and EO-AAC dynamics is performed. Similarities and differences highlighted. From these similarities a reduced order model structure common to both topology is presented.

- 4. Chapter 4 is interested to the HVDC and HVAC grid connection. Thanks to the above simplified models, it is proven that DC voltage support using EO-AAC is possible using the exact same principle than MMC. This is extended to MTDC where the possible interoperation between EO-AAC and MMC is shown. The operations under abnormal conditions as the DC-Fault and the unbalanced AC system are presented highlighting limitations and providing leads for future works.

# 5 List of publications derived from this work

The publications resulting from this Thesis project and Master student supervision are listed below.

- Journal I: "Energy and Director Switches Commutation Controls for the Alternate Arm Converter". P. Vermeersch, F. Gruson, X. Guillaud, M.M.C. Merlin, P. Egrot. Mathematics and Computers in Simulation, 2018.

- Journal II: "A Novel DC Fault Ride Through Control Methodology for Hybrid Modular Multilevel Converters in HVDC Systems". E. Shahriari, F. Gruson, P. Vermeersch, P. Delarue, F. Colas, X. Guillaud IEEE Transactions on Power Delivery, 2020.

- Journal III: "Full Energy Management of EO-AAC: Toward a Dynamic Equivalence with MMC". P. Vermeersch, F. Gruson, M.M.C. Merlin, X. Guillaud, P. Egrot. IEEE Transactions on Power Delivery, 2021.

- Conference I: "Energy Control for the Alternate Arm Converter". F. Gruson, P. Vermeersch, X. Guillaud, P. Egrot. IEEE PES PowerTech, 2017.

- Conference II: "Director switches commutation control for the Alternate Arm Converter". P. Vermeersch, F. Gruson, X. Guillaud, M.M.C. Merlin, P. Egrot. Electrimacs, 2017.

- Conference III: "Control Design of MMC prototype based on OP 5600 Real Time Simulation and eMEGASIM". P. Vermeersch, M. Belhaouane, N. Stankovic, F. Colas, X. Guillaud. opal-rt's 10th International conference on real-time Simulation, 2018

- Conference IV: "On Stored Energy Requirement in the Alternate Arm Converter". P. Vermeersch, F. Gruson, M.M.C. Merlin, X. Guillaud, P. Egrot. IEEE PES Powertech 2019.

- Conference V: "A Stored Energy Control based Active DC Filter for the Alternate Arm Converter with an Extended Overlap Period". P. Vermeersch, F. Gruson, X. Guillaud, M.M.C. Merlin, P. Egrot. EPE ECCE EUROPE 2019.

- Conference VI: "Impact on the electrical characteristics, waveforms and losses of the zero-sequence injection on the Modular Multilevel Converter". F. Gruson, P. Vermeersch, P. Delarue, P. Le Moigne, F. Colas, H. Zhang, M. Belhaouane, X. Guillaud. EPE ECCE EUROPE 2020

- Conference VII: "EMT Simulation of an HVDC Link based on Extended Overlap-Alternate Arm Converter". P. Vermeersch, F. Gruson, P. Egrot, X. Guillaud, F. Colas. CIGRE 2022. UNDER REVIEW

# Chapter 1

# The AC/DC Conversion for HVDC System

## 1.1 Introduction

This chapter comes back to the basics of Voltage Source Converter (VSC) topologies and control. It is organised as it follows. The first part recall the square-wave modulation, called in this thesis full-wave control, highlighting the current and voltage waveforms and the way to achieve active power control. Then, in the second part, the principle of modulated voltage control is explained through the two main topologies: the 2-level VSC and the Modular Multilevel Converter (MMC). Finally, the third part of the chapter is composed of two main steps. First, the Alternate Arm Converter (AAC) topology is introduced as an hybrid solutions combining features of full-wave and modulated voltage controls. The different degrees of freedom of the control are explained in addition to the overlap operating mode mandatory for stable operation in both steady-state and transients situations. The second step fully exploit the potential of the overlap operating mode leading to the description of the Extended Overlap-AAC (EO-AAC) the main subject of the thesis.

Note: As a general rule for this chapter, every topologies studied are based on the assumption that the nominal active power is 1 GW and the DC bus voltage 640 kV. Moreover, every curves drawn in per-unit (pu) are obtained on the basis of the DC bus voltage.

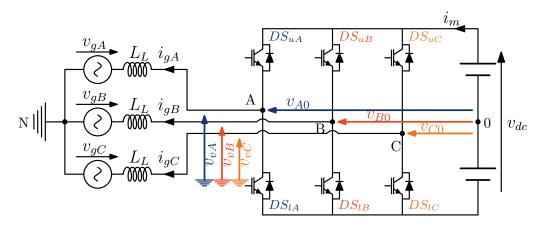

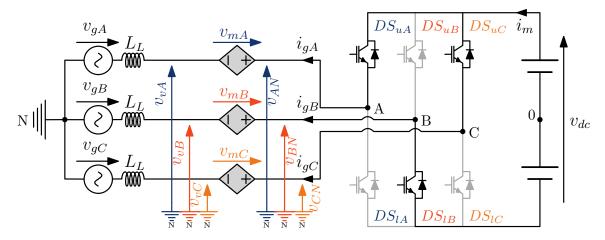

## 1.2 Full-wave controlled 2-Level VSC

The 2-Level VSC, illustrated on Figure 1.1. The AC side is composed of a three-phase voltage source in series with an inductance  $L_L$ . The DC side is connected to a constant voltage source. This configuration calls for a current bi-directionality for the DSs (i.e.  $DS_{(u,l)J}$ ). For high power application, since its inception, the IGBT has been the preferred solution thanks to suitable voltage and current ratings (up to 6.5 kV or above 1 kA).

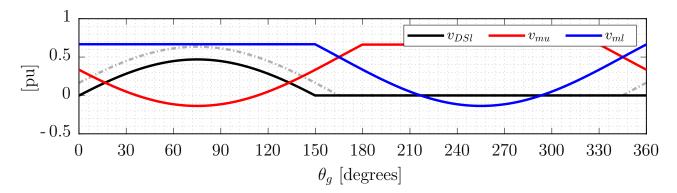

The DC voltage  $v_{dc}$  is modulated in order to generate a set of three-phase AC voltages called  $v_{A0}, v_{B0}$  and  $v_{C0}$ . Let us define  $G_{DSuA}$  and  $G_{DSlA}$  the gate signals of the upper and lower Director Switches (DS) of leg A so that

$$v_{A0} = (G_{DSuA} - G_{DSlA}) \frac{v_{dc}}{2} \tag{1.1}$$

If we define  $v_{vA}$ , the converter output AC voltage driving the AC currents such as

$$v_{vA} = v_{A0} - v_{N0} (1.2)$$

Figure 1.1 – 2-Level Voltage Source Converter

and assume the AC side to be balanced, the zero sequence voltage  $v_{N0}$  is derived as it follows

$$v_{N0} = \frac{1}{3}v_{A0} + \frac{1}{3}v_{B0} + \frac{1}{3}v_{C0} \tag{1.3}$$

leading to

$$v_{vA} = \frac{2}{3}v_{A0} - \frac{1}{3}v_{B0} - \frac{1}{3}v_{C0} \tag{1.4}$$

The three-phase grid voltages are defined as

$$v_{gJ} = V_g \sqrt{2} \sin(\omega_g t + \theta_J) = \hat{V}_g \sin(\theta_g + \theta_J)$$

(1.5)

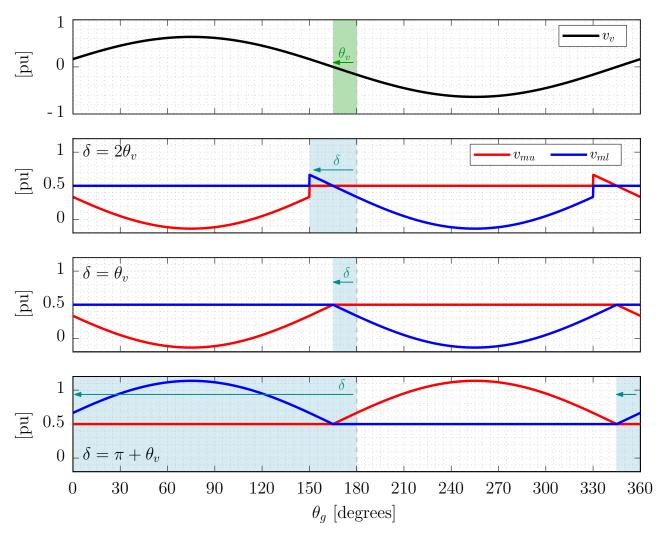

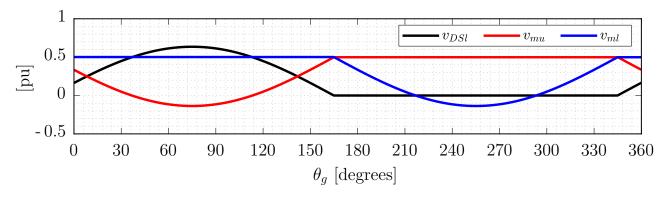

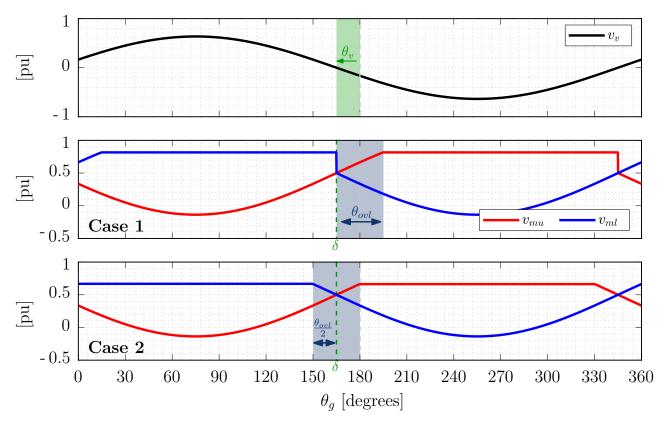

with  $\omega_g$  the grid frequency and  $\theta_J = [0; -\frac{2\pi}{3}; \frac{2\pi}{3}]$ . The principle of the full-wave modulation is to switch twice per period. These switching times are a degree of freedom. Therefore, let us introduce  $\delta$  such that the gate signals of each DS are determined using the following equations.

$$G_{DSuA} = 1 \text{ if } \theta_g \in [-\delta ; \pi - \delta]$$

$$G_{DSlA} = 1 \text{ if } \theta_g \in [\pi - \delta ; -\delta]$$

$$(1.6)$$

Applying (1.6) to get the desired switching pattern gives the following waveforms if we consider  $\delta$  equals to 15 degrees.

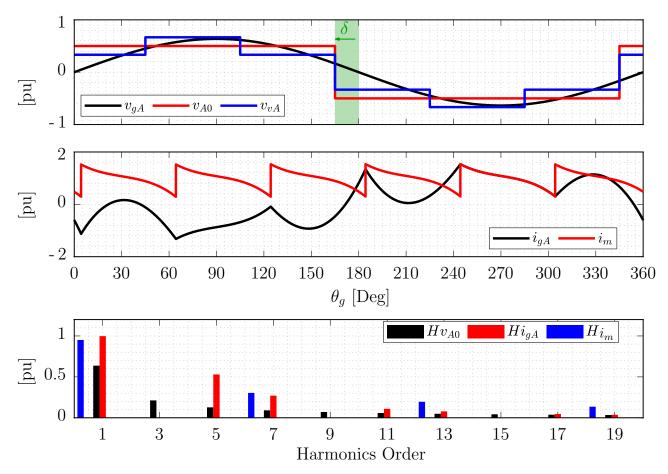

Figure 1.2 – Voltage and current waveforms of full-wave controlled 2-level Converter with  $\delta = -15^{\circ}$

As visible on Figure 1.2, most of the electrical quantities resulting from the full-wave modulation are composed of low order harmonics suggesting the need for bulky passive filters in both sides. The modulated voltages are the well-know 2-level voltages  $(v_{J0})$  between  $\pm \frac{v_{dc}}{2}$  while  $v_{vJ}$  is a 4-level voltage that can be equal  $\pm \frac{2v_{dc}}{3}$  and  $\pm \frac{v_{dc}}{3}$ .

After this brief recall about the full-wave control, let us introduce how to achieve the active power control with such a modulation scheme. Assuming a balanced operation, a single-phase representation is used in the following lines and the index of the phase is removed. Only the fundamental component of  $v_v$  is considered:

$$v_{v1} = V_{v1}\sqrt{2}\sin(\theta_{v1}) \tag{1.7}$$

where  $V_{v1}$  and  $\theta_{v1}$  are respectively the RMS value and the angle of the  $v_{v1}$ . It can demonstrated that

$$V_{v1} = \frac{1}{\sqrt{2}} \frac{4}{\pi} \frac{v_{dc}}{2} \tag{1.8}$$

showing that  $V_{v1}$  only depends on the value of the DC bus voltage and cannot be modified by the control. However, it is worth mentioning that full-wave control achieves the highest modulation index value possible for a conventional converter. This modulation index, noted m has for definition

$$m = \frac{2V_{v1}\sqrt{2}}{v_{dc}} = \frac{4}{\pi} \tag{1.9}$$

Then, if we focus on the fundamental, the following graphs can be obtained.

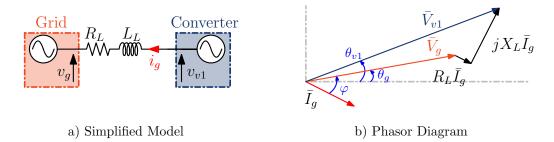

Figure 1.3 – Simplified representation and phasor diagram of two voltage sources interconnected by an inductance

Figure 1.3 a) presents a simplified model of the AC side where the grid voltage  $v_g$  and  $v_{v1}$  are interfaced through  $R_L$  and  $L_L$ . From this system, a phasor diagram can be drawn (Figure 1.3 b)). When neglecting the resistance, the well known expression of the active  $P_{ac}$  and reactive Q powers can be written:

$$P_{ac} = \frac{3V_g V_{v1} \sin(\theta_{v1} - \theta_g)}{X_L}$$

(1.10a)

$$Q = \frac{3V_g \left( V_{v1} \cos(\theta_{v1} - \theta_g) - V_g \right)}{X_L}$$

(1.10b)

Replacing  $V_{v1}$  by its value derived in (1.8), and  $\theta_{v1} - \theta_g$  by  $\delta$  gives the active and reactive power expressions of a full-wave controlled 2-level VSC

$$P_{ac} = \frac{\frac{6}{\pi\sqrt{2}}V_g v_{dc} \sin(\delta)}{X_I} \tag{1.11a}$$

$$Q = \frac{\frac{6}{\pi\sqrt{2}}V_g v_{dc}\cos(\delta) - 3V_g^2}{X_L}$$

(1.11b)

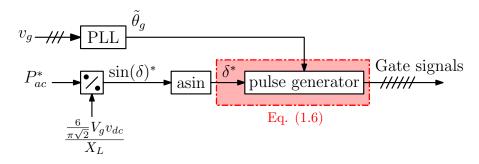

The equations of (1.11) show that  $\delta$  controls the active power and affects at the same time the reactive power. This later cannot be managed independently since a degree of freedom is missing. Finally, by reversing (1.11a), a basic control scheme can be derived in order to compute the value of  $\delta$  for a given active power set points as illustrated on Figure 1.4.

Figure 1.4 – Open-loop control scheme of full-wave controlled 2-Level VSC

where the reference for  $\delta$  is derived as it follows

$$\delta^* = \arcsin\left(\frac{P_{ac}^* X_L}{\frac{6}{\pi\sqrt{2}} V_g v_{dc}}\right) \tag{1.12}$$

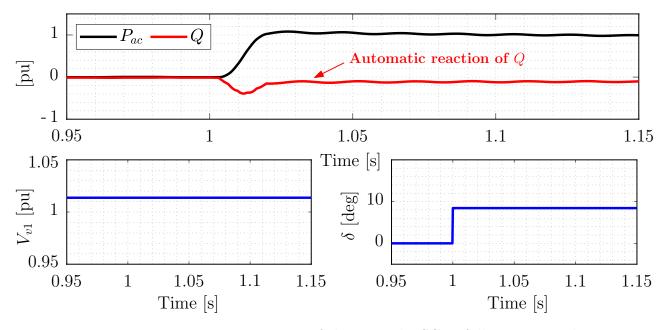

If this control scheme and DS synchronisation procedure are applied then the active power can be controlled as shown by on Figure 1.5. This simulation is achieved using the parameters of Table 1.1.

| Parameters                     | Value SI              | Value p.u  |

|--------------------------------|-----------------------|------------|

| Rated power $(S_n)$            | 1.04 GVA              | 1          |

| Nominal active power $(P_n)$   | 1 GW                  | 0.96       |

| Nominal reactive power $(Q_n)$ | 300 MVAR              | 0.29       |

| DC Voltage $(v_{dc})$          | 640 kV                | 1          |

| Grid Frequency $(f_g)$         | 50 Hz                 | 1          |

| RMS AC Voltage L-to-L $(U_g)$  | 500 kV                | $\sqrt{3}$ |

| RMS AC Voltage L-to-G $(V_g)$  | 288.67 kV             | 1          |

| Leakage inductance $(L_L)$     | 116.6 mH              | 0.15       |

| Leakage resistance $(R_L)$     | $60~\mathrm{m}\Omega$ | 0.005      |

Table 1.1 – Simulation parameters of the full-wave controlled 2-level converter

Figure 1.5 – Dynamic response of the 2-Level VSC in full-wave control

Figure 1.5 highlights power dynamics under an active power step of 1 GW at 1 second. Due to the high harmonic content in the AC current, the measurement of the powers is obtained through filters explaining this smooth transient. Note that  $V_g$  has been chosen in order to limit reactive power.

To conclude this section on full-wave controlled VSC, three main observations stand out. First, the active power is controlled by shifting the gate signals of all DSs by an angle named  $\delta$ . Second, the reactive power is not controlled, VAR compensators are therefore needed (using passive or active devices). The final point introduces the main drawback of such control schemes which are the low order harmonics in modulated quantities and AC currents. In both sides, bulky passive filters are required, or active filtering solutions.

# 1.3 Modulated voltage control

Technology improvements have led to a significant increase of power-electronics device switching frequency. Hence, the harmonic content of modulated quantities has been improved and a new degree of freedom introduced. Unlike the full-wave control, it is now possible to modulate the AC voltage amplitude. One of these solutions providing amplitude modulation is the well-known Pulse Width Modulation (PWM) scheme. Its main principle is to fix the switching frequency higher than the grid one (e.g. a few kHz). In a simplified way, its working principle is recalled as it follows.

First of all, let us introduce the three-phase modulation signals  $m_{vA}, m_{vB}$  and  $m_{vC}$  such as:

$$m_{vA} = m_{A0} - m_{N0}$$

$$m_{vB} = m_{B0} - m_{N0}$$

$$m_{vC} = m_{C0} - m_{N0}$$

(1.13)

according to (1.2). Neglecting the zero sequence component  $m_{N0}$  gives sinusoidal modulation functions

$$m_{vA} = m_{A0} = \hat{M}_{vA} \sin(\theta_g + \theta_{vA})$$

$$m_{vB} = m_{B0} = \hat{M}_{vB} \sin(\theta_g + \frac{2\pi}{3} + \theta_{vB})$$

$$m_{vC} = m_{C0} = \hat{M}_{vC} \sin(\theta_g + \frac{4\pi}{3} + \theta_{vC})$$

(1.14)

From this sinusoidal modulation signals, transistors gate signals are generated using, for instance, the triangular carrier based approach. Both signals are sent to a comparator, which, if the modulation signal is above the carrier command for the upper DS to be switched ON and vice-versa.

Let us move to a single-phase representation. When using the average converter model it can be written

$$\langle v_v \rangle_{T_{sw}} = \langle m_v \rangle_{T_{sw}} \frac{v_{dc}}{2} \tag{1.15}$$

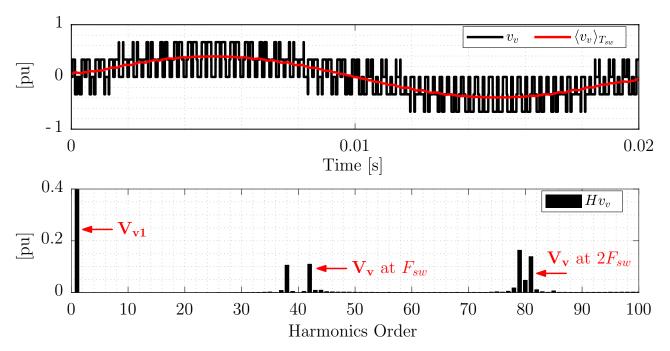

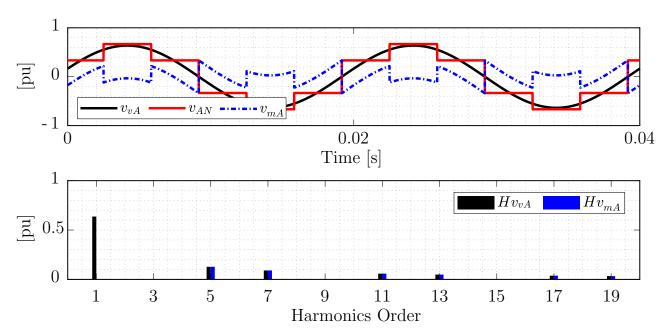

where  $T_{sw}$  is the switching period. It would results in the following waveform of Figure 1.6.

If the 2-Level converter uses a PWM scheme,  $v_v$  is composed of 5 levels 0,  $\pm \frac{2v_{dc}}{3}$  and  $\pm \frac{4v_{dc}}{3}$ . Compared to the full-wave modulation, the level 0 has been obtained. However, the main change regards the harmonic content and especially the gap between the fundamental and the first harmonics. Thus, if the average value of  $v_v$  over the switching period is calculated, the fundamental clearly appears in red.

Figure 1.6 – Illustration of a PWM 2-Level converter based on 2 kHz carrier and  $\hat{M}_v = 0.8$

To analyse the way to achieve power control, let us focus on the fundamental of  $v_v$ .

$$v_{v1} = m_v \frac{v_{dc}}{2} = \hat{M}_v \frac{v_{dc}}{2} \sin(\theta_g + \theta_v)$$

$$\tag{1.16}$$

where the peak value of the AC voltage is given by

$$\hat{V}_{v1} = \hat{M}_v \frac{v_{dc}}{2} \tag{1.17}$$

and  $\hat{M}_v$  is

$$\hat{M}_v \in \left[0; \frac{2}{\sqrt{3}}\right] \tag{1.18}$$

if the zero sequence component  $m_{N0}$  is used.

Now, as in the full-wave control, active and reactive power equations of (1.10) can be derived using the same phasor diagram but using (1.17).

$$P_{ac} = \frac{3M_v \frac{v_{dc}}{2} V_g \sin(\theta_{v1} - \theta_g)}{X_L}$$

(1.19a)

$$Q = \frac{3M_v \frac{v_{dc}}{2} V_g \cos(\theta_{v1} - \theta_g) - 3V_g^2}{X_L}$$

(1.19b)

These expressions are very similar to those of the full wave control but the difference lies in the independent reactive power control thanks to the management of the voltage magnitude.

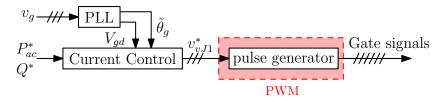

From these steady-state power equations, an open-loop control scheme could be designed following a similar procedure as for the full-wave control, but in practice a current loop is implemented as in Figure 1.7 to get a closed-loop control on AC currents.

Figure 1.7 – Simplified closed-loop control scheme of PWM 2-Level converter

This controllers can be, for instance, implemented in the Synchronous Rotating Frame (SRF) using dq0 coordinates. In such case, one axis current (e.g. d) is related to the active part while the second is for the reactive part depending on the chosen rotation matrix in the PLL.

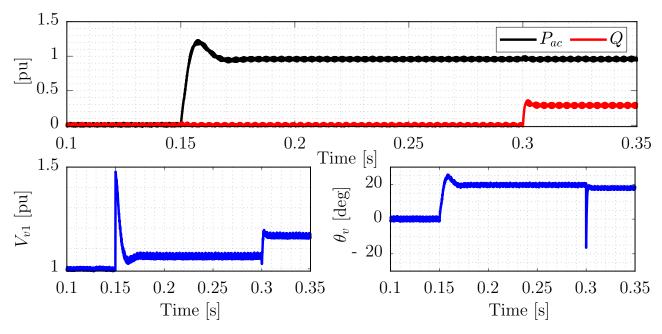

Finally, if we apply a closed-loop control on AC currents, then, the dynamic results of Figure 1.8 are obtained.

Figure 1.8 – Simulation results of PWM 2-Level converter including current controller

On the first graph of Figure 1.8 are depicted the active and reactive power responses to a step change on their references (respectively 1 GW and 300 MVAR). These curves highlight the effective decoupled control of both power components thanks to phase and amplitude modulation of  $v_v$ . The amplitude of  $V_{v1}$  and the value of  $\theta_v$  are presented on the two last graphs where it is clearly visible that  $\theta_v$  mostly governs the active power and  $V_{v1}$  the reactive power.

#### Conclusion on modulated voltage control using 2-Level topology

The principle of modulated voltage control and its application to 2-level converter has been recalled. Unlike the full-wave control, this technique allows simultaneous phase and amplitude modulation of the AC voltage fundamental featuring decoupled control of active and reactive powers. This capability is particularly useful for grid applications in order to get independent control of AC voltage and frequency. In addition to the AC powers decoupling, the modulation of  $v_{vJ1}$  through the increasing of the switching frequency, removes low order harmonics allowing to reduce passive filters size.

However, there are also some drawbacks in using this modulation scheme. The first one is the losses. Indeed, the increasing of the switching frequency has led to an increase of the switching losses.

## 1.4 The Modular Multilevel Converter

A second solution to get modulated voltage control and low order harmonics suppression from the modulated voltages is to consider the multi-level approach. So far, two topologies multilevel converter have been installed on the grid: the Active-Neutral Point Clamped (A-NPC) [9], and the MMC [14]. This section focuses on MMC which represents the most advanced and planned multilevel topology for future HVDC system. Its structure is illustrated as it follows.

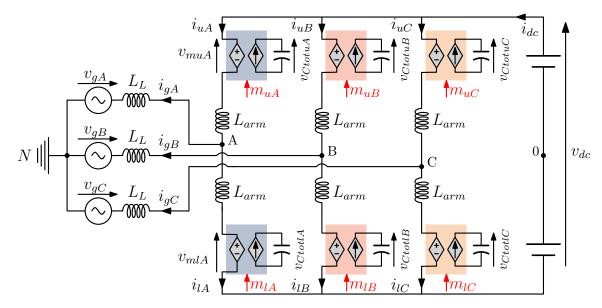

Figure 1.9 – Representation of the MMC

The operating principle of the MMC is very different from classical converter topologies since each MMC arm is never disconnected from the current path through a DS as in the 2-Level VSC. This is made possible by the use of a stack of Sub-Modules (SMs). A stack of SMs is made by a series connection of several elementary components which are small-scale power electronics devices interfacing a floating capacitor [76–79]. This continuous operating mode of the MMC arms involves that, from the DC side perspectives, four voltage sources are connected in parallel (three legs and the DC bus). To avoid uncontrolled power exchange between these sources (through circulating currents), arm inductors have been used. Therefore, each MMC arm is composed of a stack of SMs and an inductor.

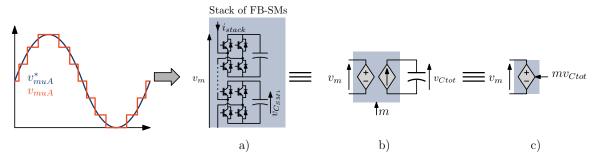

Through the gate signals of each SM, the capacitors can be inserted in, or by-passed from, the main current path in order to achieve a characteristic staircase illustrated on Figure 1.10

Thanks to these devices, the MMC has been presented to the community as a suitable solution for HVDC system involving a DC voltage at several hundreds of kV. To approximate the sinusoidal reference voltage, the MMC is equipped with many SMs per stack  $(N_{SM})$  to get a modulated voltage with  $N_{SM} + 1$  levels according to Figure 1.10. In the particular case of MMC-HVDC, hundreds of SMs are involved (e.g. 400).

Figure 1.10 – Illustration of MMC modulated voltage waveforms and a) stack of Full-Bridge SMs, b) Average Stack Model, c) Modulated voltage source

In this chapter, we are focusing on principles, then, a stack of SMs is reduced to its average model as in Figure 1.10 b). It results in the following simplified representation of the MMC of Figure 1.11.

Figure 1.11 – Simplified scheme of the MMC

Compared to conventional converters, the insertion of an internal energy storage devices in the converter arms totally decouple the AC and DC voltages in the sense that the DC bus voltage is no longer used for the modulation of  $v_{vJ}$ . Considering single-phase representation, modulated voltages are generated using the internal voltage called  $v_{Ctot}$  (see Figure 1.10) such as:

$$v_{mu} = m_u v_{Ctotu}$$

$$v_{ml} = m_l v_{Ctotl}$$

(1.20)

Each of these modulated voltages can used to control one of the MMC arm currents (i.e.  $i_u$  and  $i_l$ ). In order to decouple AC and DC quantities, a "sum" ( $\Sigma$ ) representation is often used so that  $\Sigma$  variables stand for the DC components in the arm quantities. Regarding the AC side, notations  $i_g$  and  $v_v$  are kept for the sake of consistency. Thus let us introduce:

$$v_v = \frac{-v_{mu} + v_{ml}}{2}$$

$$v_{\Sigma} = \frac{v_{mu} + v_{ml}}{2}$$

(1.21)

where  $v_{\Sigma}$  is the so-called differential voltage [80,81] or DC common mode voltage [82] around  $v_{dc}/2$ . It is also interesting to note that, unlike the 2-Level VSC the voltage  $v_v$  is fictitious. Indeed, applying the KVL leads to the following description of  $v_v$

$$v_v = v_g + \left(L_L + \frac{L_{arm}}{2}\right) \frac{di_g}{dt} + \left(R_L + \frac{R_{arm}}{2}\right) i_g \tag{1.22}$$

which highlights the implication of half of the arm inductors on the AC side dynamics and the fact that it cannot be measured in practice.

If a sufficient number of SMs is used, it is possible to assume the modulation function  $m_v = m_{v1}$  and by considering the zero sequence voltage to be zero, it can be demonstrated that

$$m_v = \hat{M}_v \sin(\theta_q + \theta_v) \tag{1.23}$$

$m_{\Sigma}$  the DC side modulation function is assumed to be constant.

$$m_{\Sigma} = M_{\Sigma} \tag{1.24}$$

Now considering the voltages  $v_{Ctotu}$  and  $v_{Ctotl}$  yields

$$v_v = \hat{M}_v \left( \frac{v_{Ctotu} + v_{Ctotl}}{2} \right) \sin \left( \theta_g + \theta_v \right)$$

$$v_{\Sigma} = M_{\Sigma} \left( \frac{v_{Ctotu} + v_{Ctotl}}{2} \right)$$

(1.25)

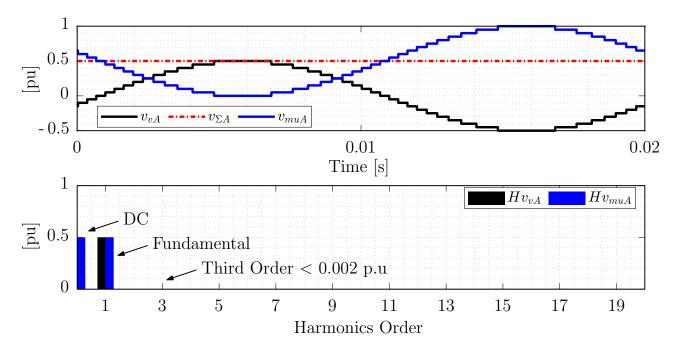

It results in the waveforms of Figure 1.12 assuming a MMC including 20 SMs per stack and constant capacitor voltages.

Figure 1.12 – Principle of modulation in MMC including 20 SMs per stack

Thanks to the multi-level approach, modulated voltages are almost sinusoidal and only composed of small voltage steps provided by the insertion or the by-pass of SMs. As a results,

$v_{vA}$  harmonic content is highly reduced involving AC current almost harmonics free. Obviously, the more the MMC has voltage levels, the less AC currents contains harmonics. Moreover, in steady-state each MMC leg generates a constant DC voltage making the DC current flowing through the converter terminals naturally smooth.

The dimensioning of the stacks of SMs is based on the steady-state analysis of modulated voltages peak value. To illustrate, let us consider an operating point at zero power. Thus,  $v_v = v_g$  and  $v_{\Sigma} = v_{dc}/2$ . The peak positive for  $v_{mu}$  is derived as it follows where the modulation index m is introduced

$\hat{V}_{mu} = \frac{V_{dc}}{2} + \hat{V}_g = \frac{V_{dc}}{2} (1+m) \tag{1.26}$

Thus, to achieve a modulation index close to 1, (1.26) shows that a MMC stack must be sized for the DC bus voltage. This constraint explains the large number of SMs per stack in HVDC-MMC operating at 640 kVdc. For this reason, most of the time in MMC including Half-Bridge SMs (HB-SMs) the nominal value for  $v_{Ctot}$  ( $V_{Ctot0}$ ) is set to

$$V_{Ctot0} = V_{dc} (1.27)$$

As in the PWM-VSC, it is possible to achieve both modulation of  $M_v$  and  $\theta_v$  but also of  $m_{\Sigma}$ . As above, let us describe power equations.

$$P_{ac} = \frac{3M_v \left(\frac{v_{Ctotu} + v_{Ctotl}}{2}\right) V_g \sin(\theta_v - \theta_g)}{X_L}$$

(1.28a)

$$Q = \frac{3M_v \left(\frac{v_{Ctotu} + v_{Ctotl}}{2}\right) V_g \cos(\theta_v - \theta_g) - 3V_g^2}{X_I}$$

(1.28b)

$$P_{dc} = 2m_{\Sigma} \left( \frac{v_{Ctotu} + v_{Ctotl}}{2} \right) i_{dc}$$

(1.28c)

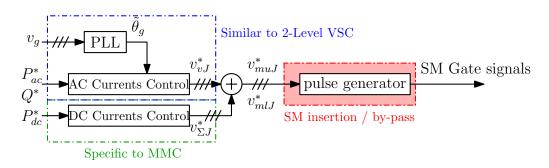

The modulation of  $v_{\Sigma}$  allows having a control of the DC power which is the main specificity of the MMC. From the above considerations, it is possible to derive closed-loop controllers that would lead to the following simplified control scheme of Figure 1.13.

Figure 1.13 – AC side Simplified control scheme of MMC

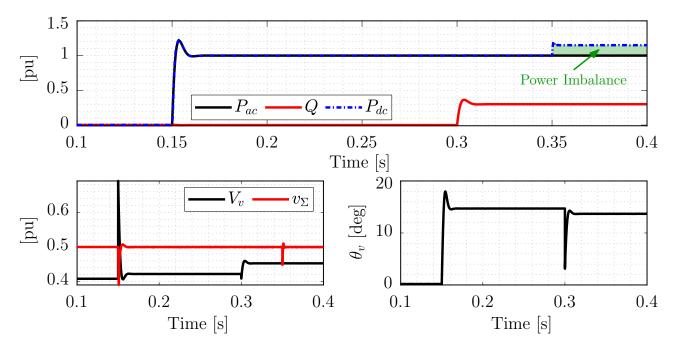

It is very similar to the 2-level converter control since the AC controllers are the same, however, the modulation of  $v_{\Sigma}$  introduces a new degree of freedom. Applying this control scheme in a time domain simulation gives the results of Figure 1.14 providing response of AC (active and reactive) and DC powers.

Figure 1.14 – Simulation results of 401 Levels MMC including AC and DC current controllers

As indicated in the Figure 1.14, the active and reactive powers on the AC side can be decoupled thanks to  $M_v$  and  $\theta_v$ . However, the most interesting point of this simulation result concerns the event at 0.35 second. Indeed, it is also true that  $m_{\Sigma}$  is decoupled from  $\theta_v$  meaning that  $P_{ac}$  is decoupled from  $P_{dc}$ . However, if these two control degrees of freedom are managed in a non-coordinated way, then a power imbalance can occur as highlighted in green. However, this difference of active power is supported by the MMC internal energy. So, to ensure the coordinated control of  $m_{\Sigma}$  and  $\theta_v$  an energy management is used.

#### MMC energy management

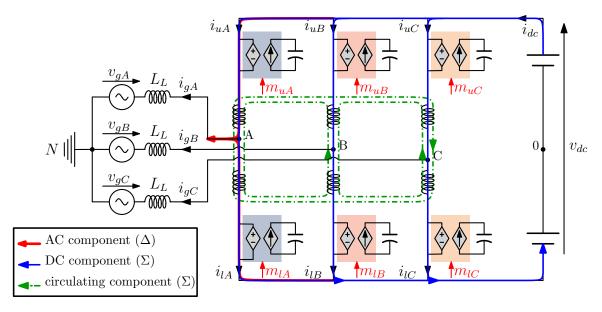

The introduction of a storage device inside the converter arms and its use for voltage modulation introduces an intermediate step in the energy conversion. Hence, the energy conversion becomes indirect and involves a decoupling between the AC and DC active powers (no straight relation between  $i_g$  and  $i_{dc}$  thanks to  $m_v$  and  $m_{\Sigma}$ ) and a possible deviation of the SM capacitor state of charge. To keep the capability of modulating  $v_{\Sigma}$  and  $V_v$  such a case must be avoided. To describe this important notion of MMC, the converter scheme depicted on Figure 1.15 is now including the different current components that may be found in a MMC arm.

In red line is depicted the AC component of the arm currents defined as

$$i_q = i_u - i_l \tag{1.29}$$

In blue and green lines are respectively presented the DC and the circulating components of the arm currents that belong to the  $\Sigma$  representation. The reason why these components have been separated lies in the fact that, circulating currents (i.e. internal MMC currents not reflected in the AC or DC side) are expected to be zero in steady-state, and hence, not participating in the active power flow<sup>1</sup> while the DC component is responsible for the power transfer and fairly assumed to be equals to  $i_{dc}/3$ . They can be represented through one single current  $i_{\Sigma}$  such as

<sup>&</sup>lt;sup>1</sup>Chapter 3 provide some details about MMC control and the role of circulating currents

Figure 1.15 – Simplified scheme of the MMC

$$i_{\Sigma} = \frac{i_u + i_l}{2} \tag{1.30}$$

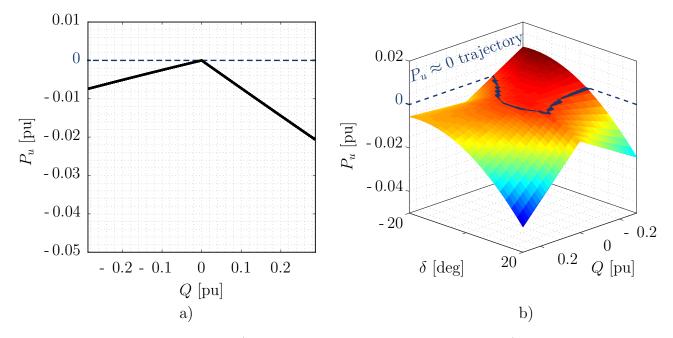

Through  $v_{\Sigma}$ ,  $v_v$ ,  $i_{\Sigma}$  and  $i_g$  the decoupling between the AC and DC active powers can be described. So let us focus on the upper stack. The power that is absorbed or furnished by the SM capacitors in instantaneous value  $(p_u)$  can be expressed as

$$p_u = v_{mu}i_u$$

$$= (v_{\Sigma} - v_v)\left(\frac{i_g}{2} + i_{\Sigma}\right)$$

(1.31)

where the active power part  $(P_u)$  can be isolated by deriving the average value of this power over the fundamental period.

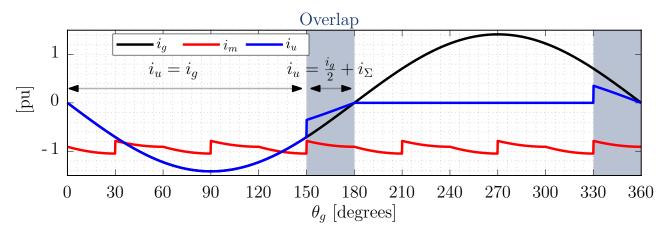

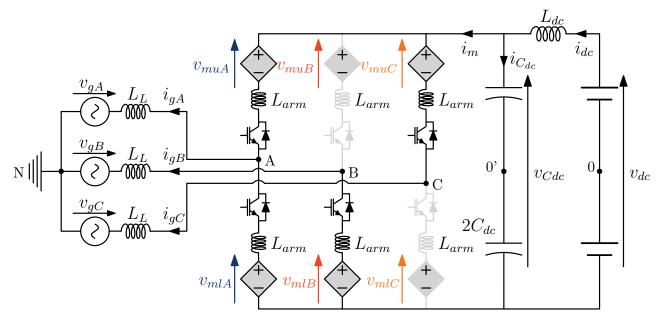

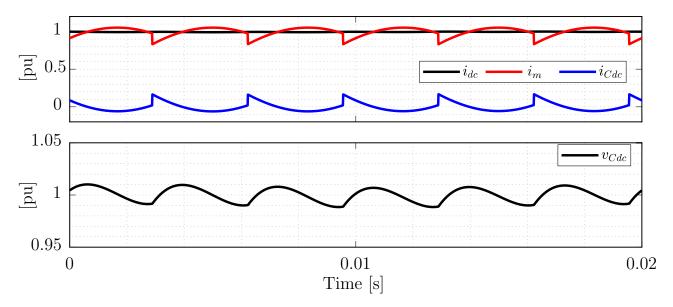

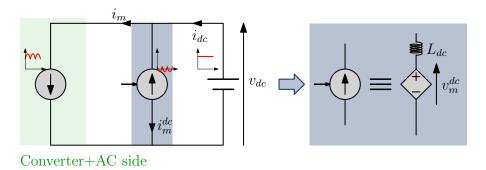

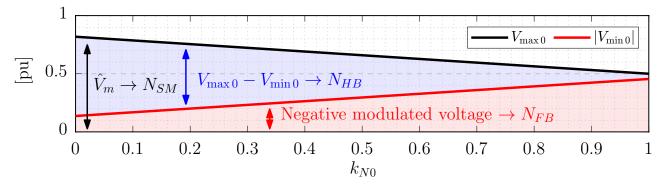

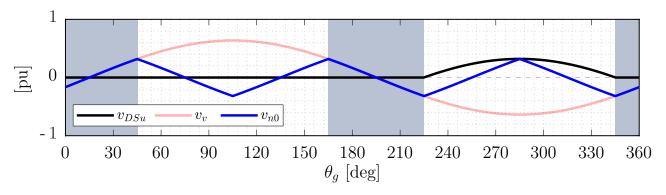

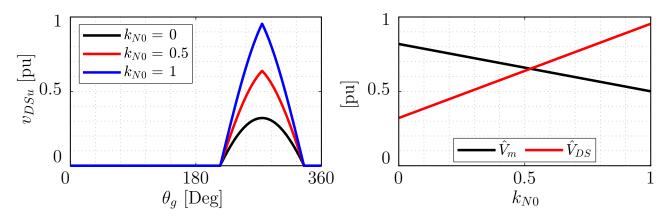

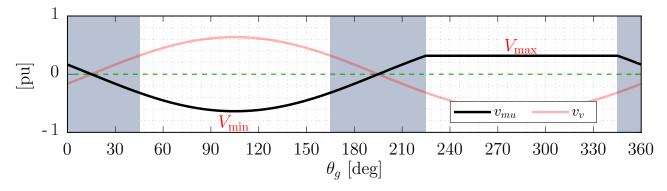

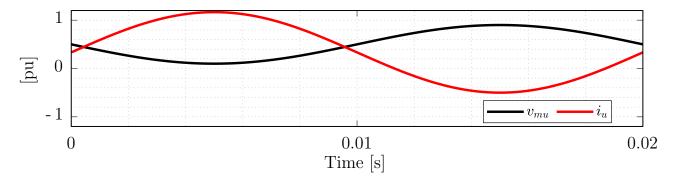

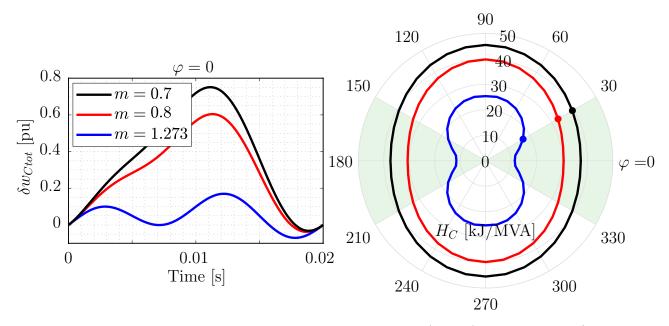

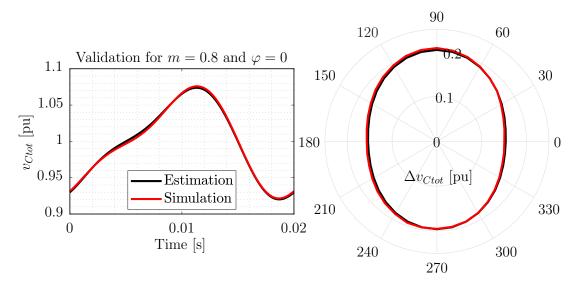

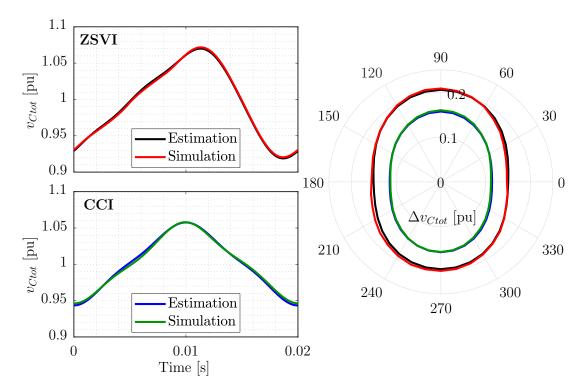

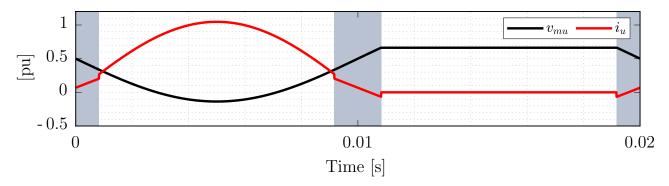

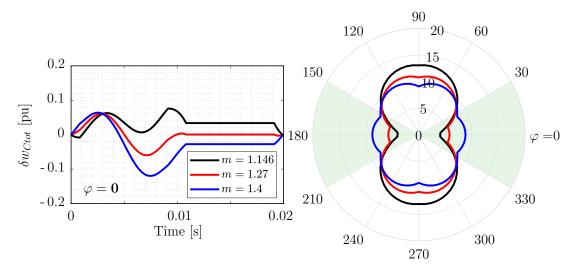

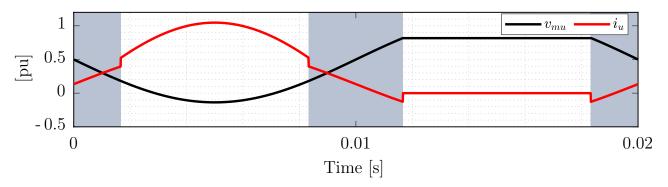

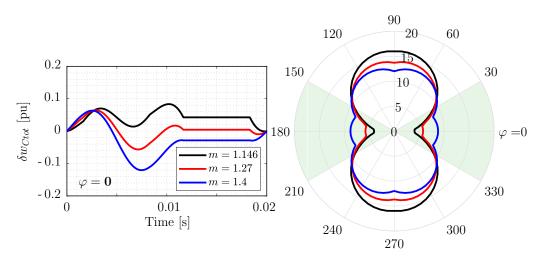

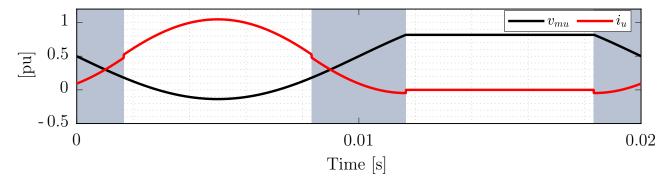

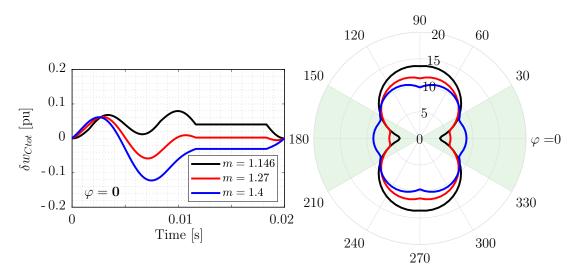

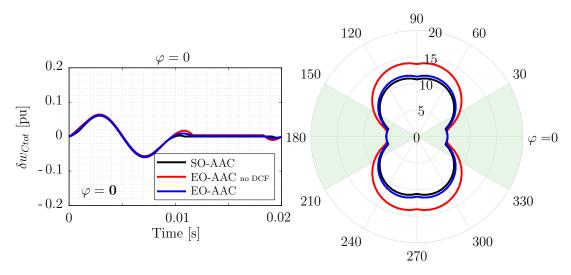

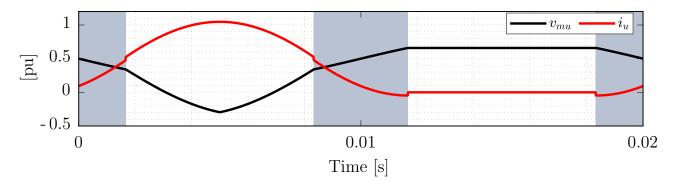

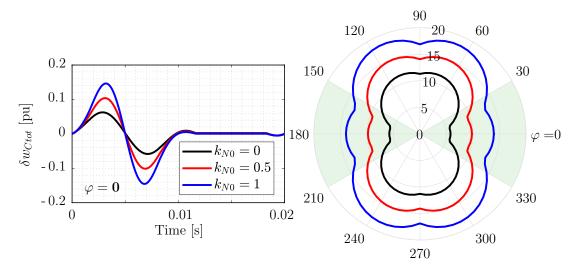

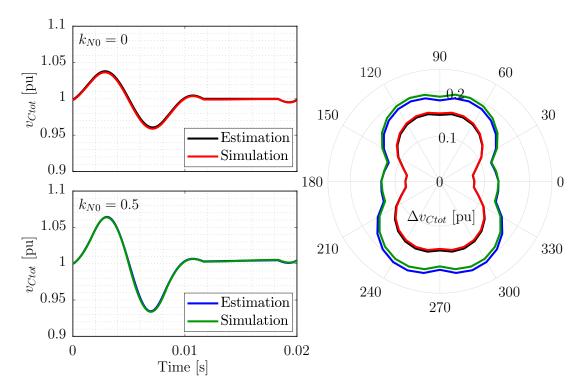

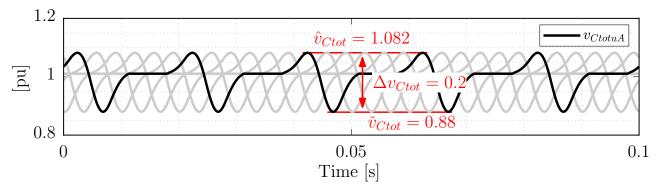

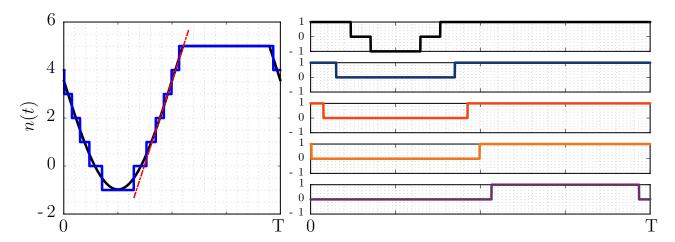

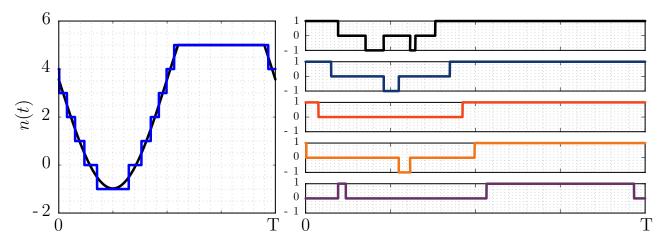

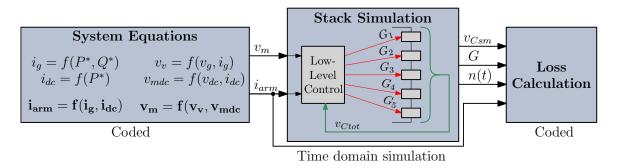

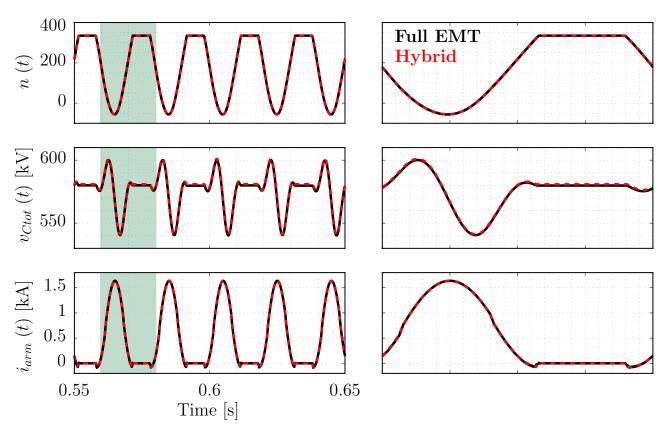

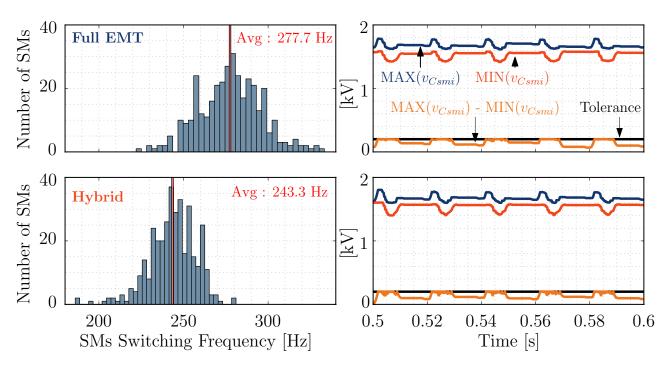

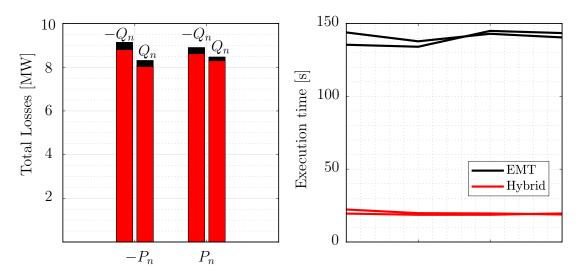

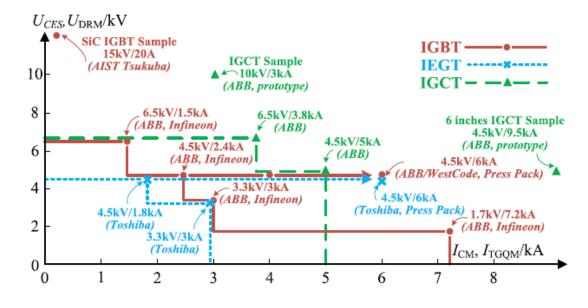

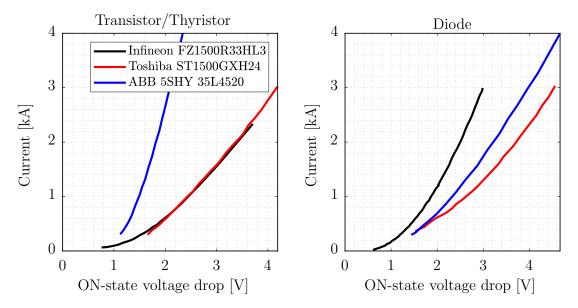

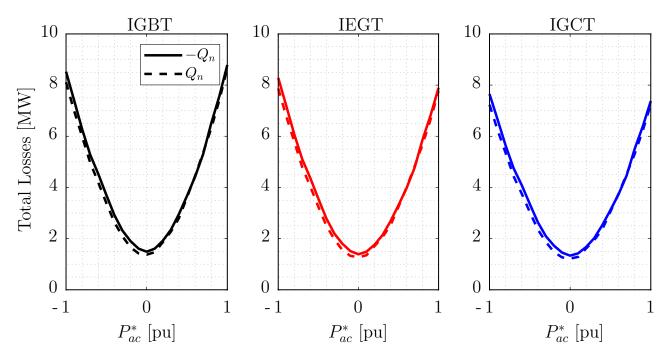

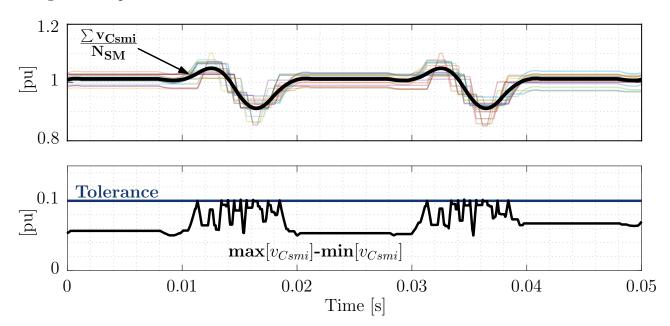

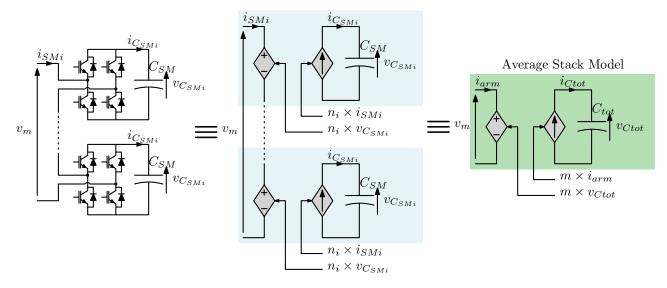

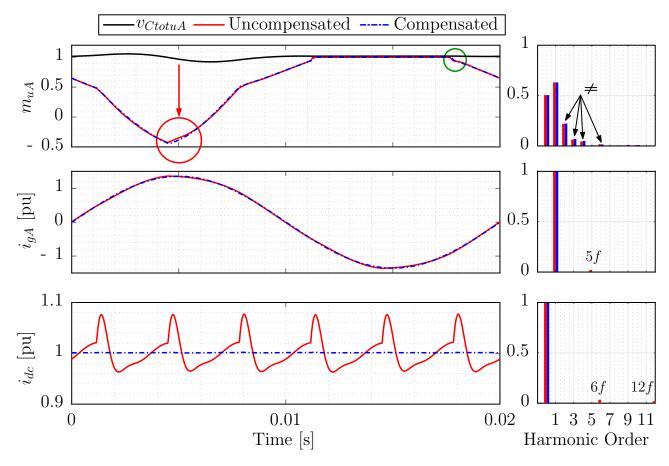

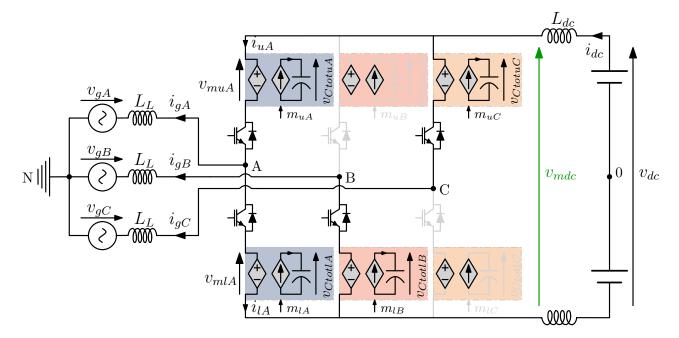

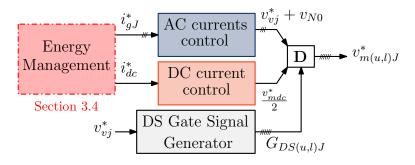

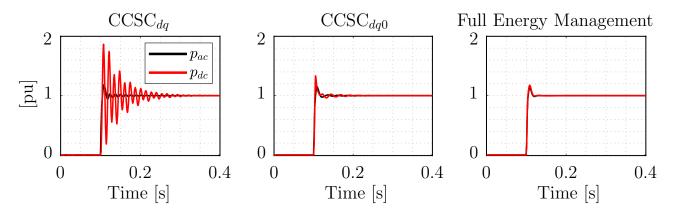

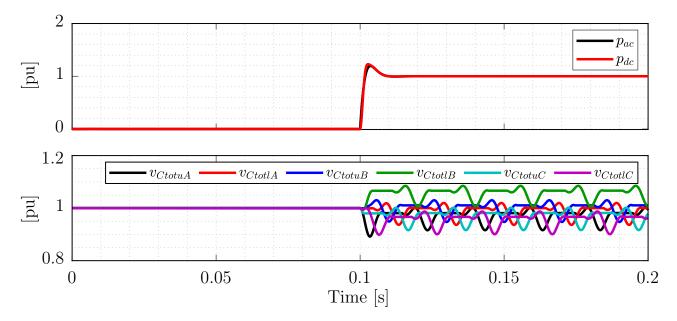

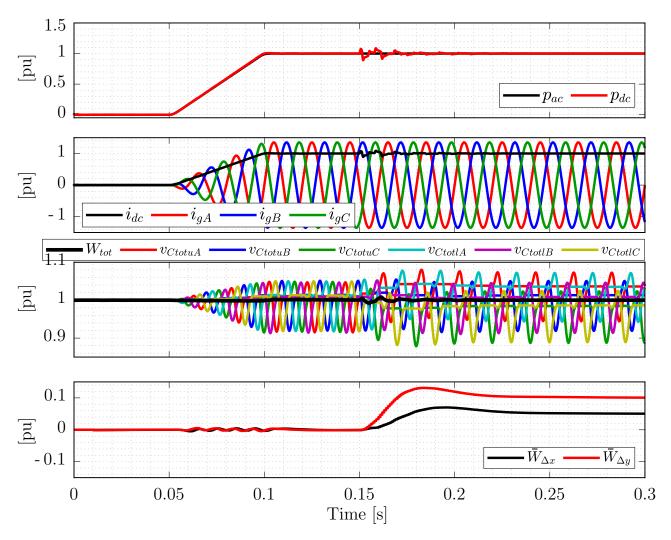

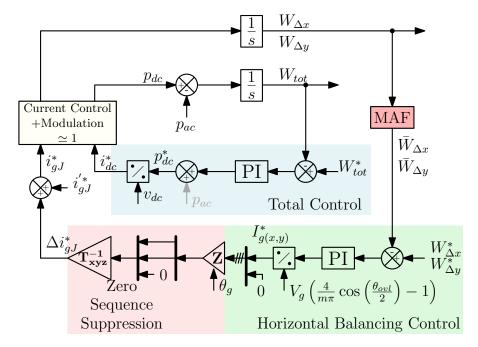

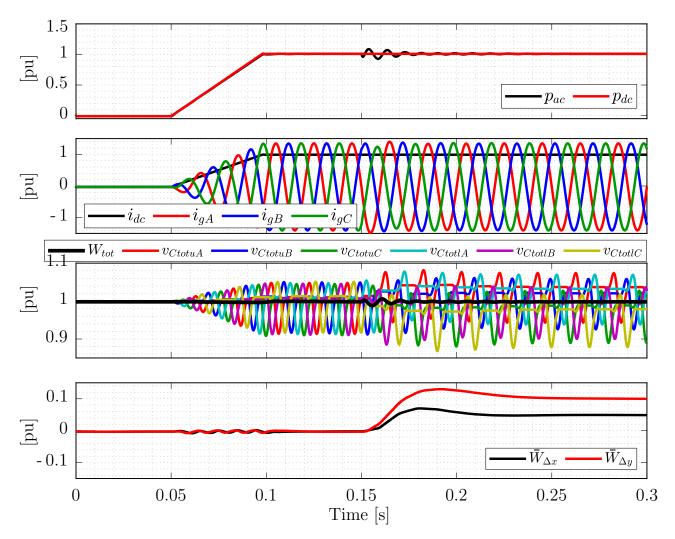

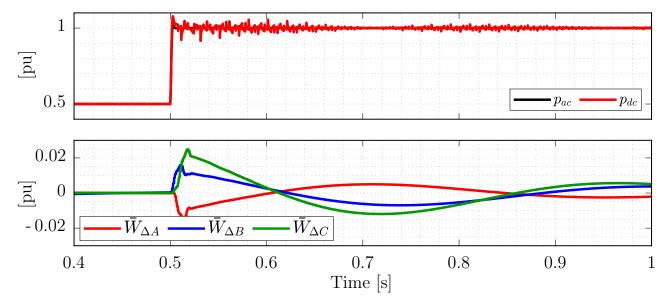

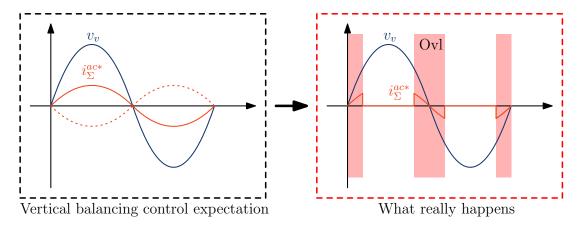

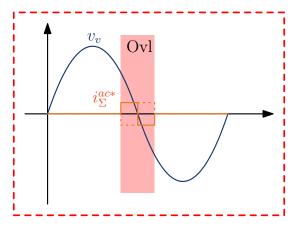

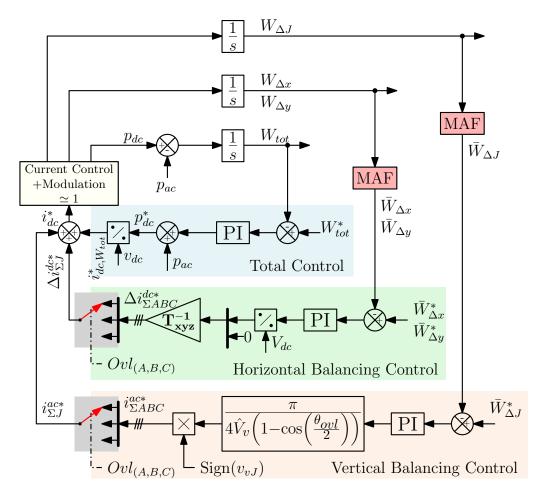

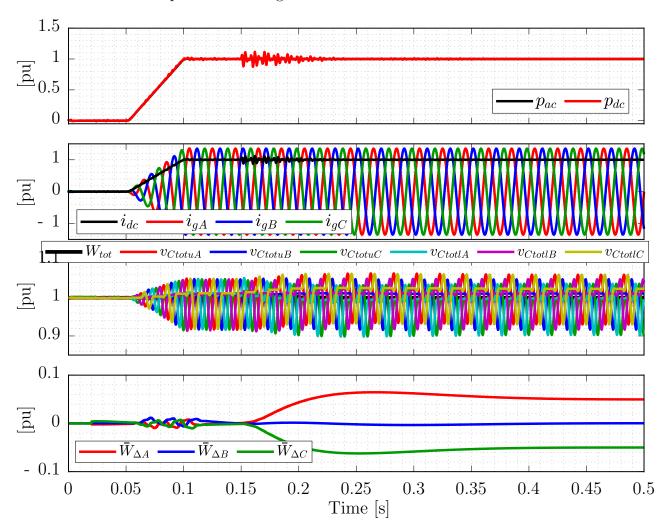

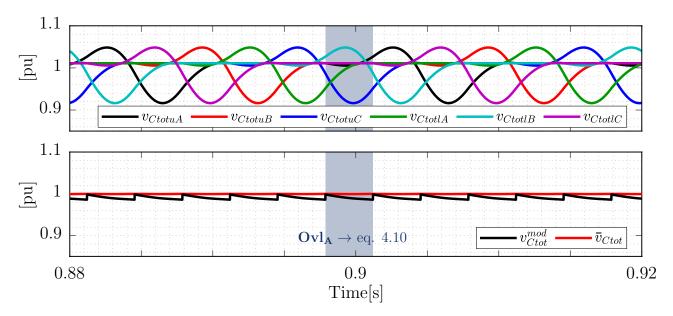

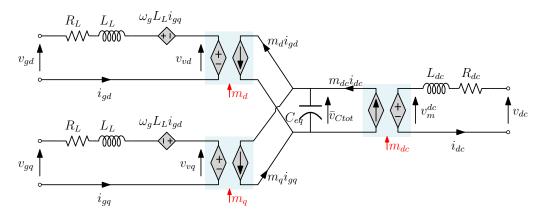

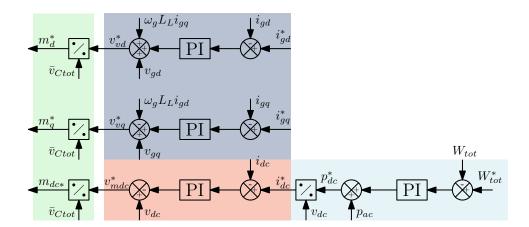

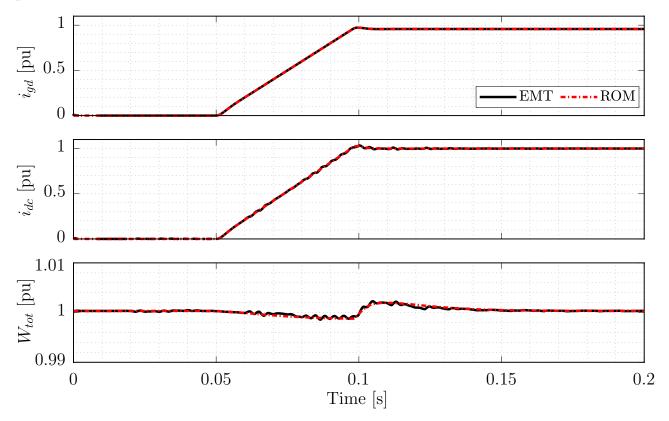

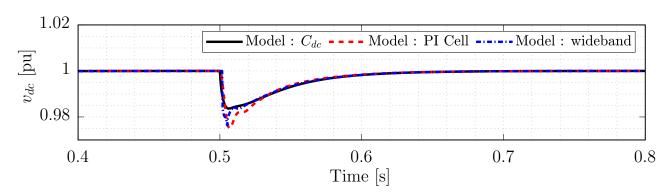

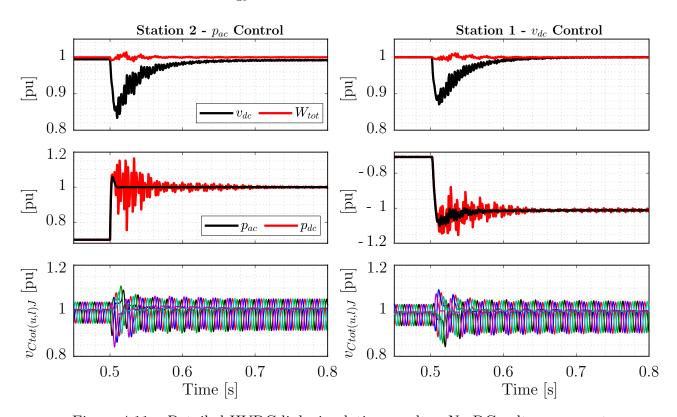

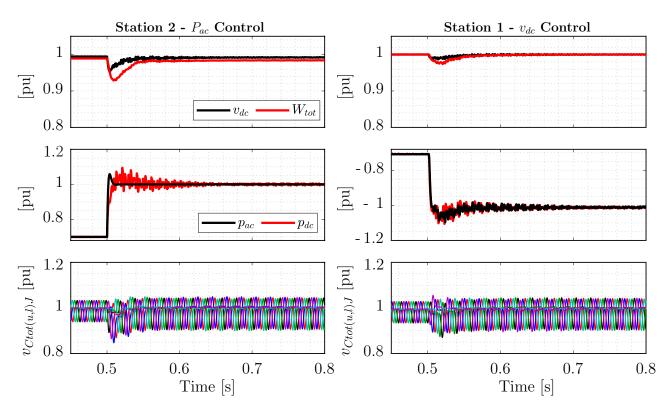

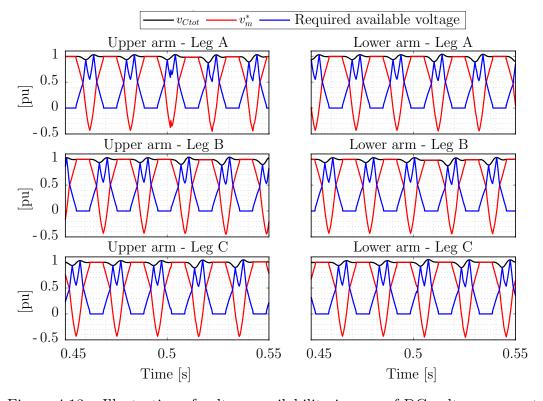

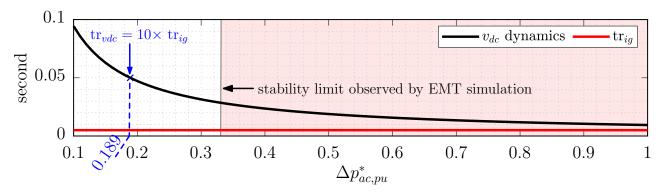

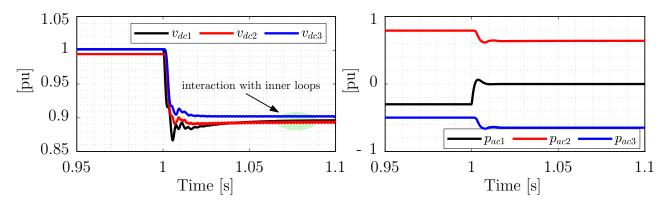

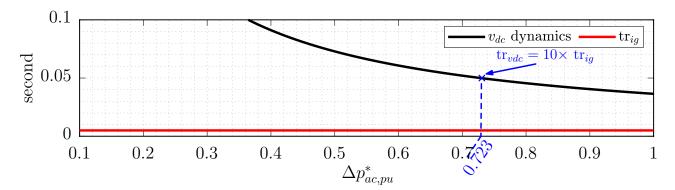

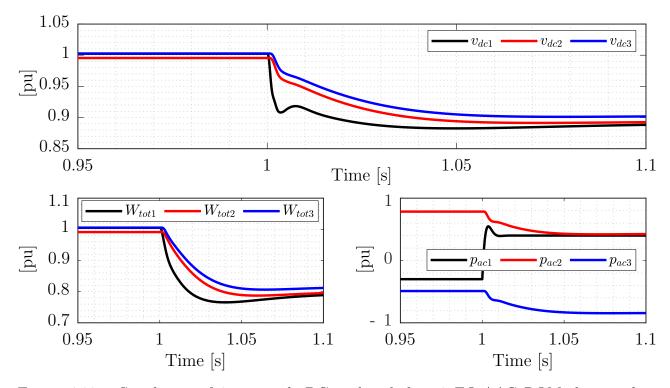

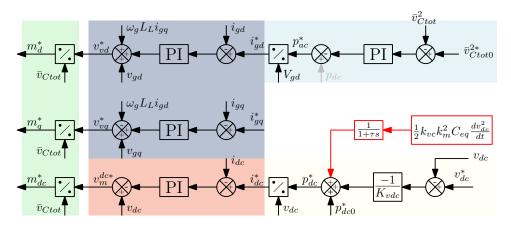

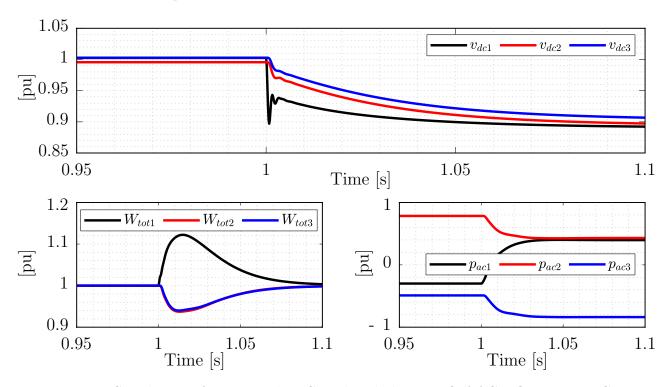

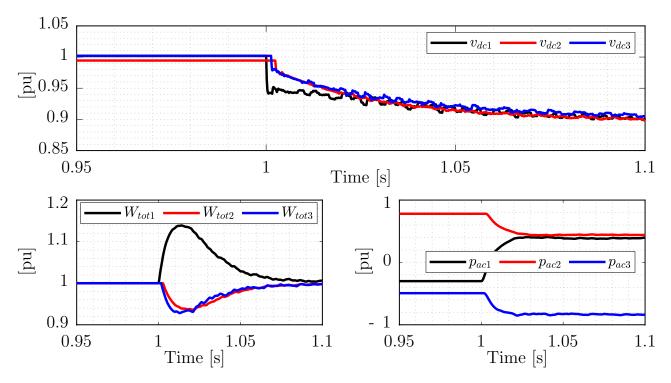

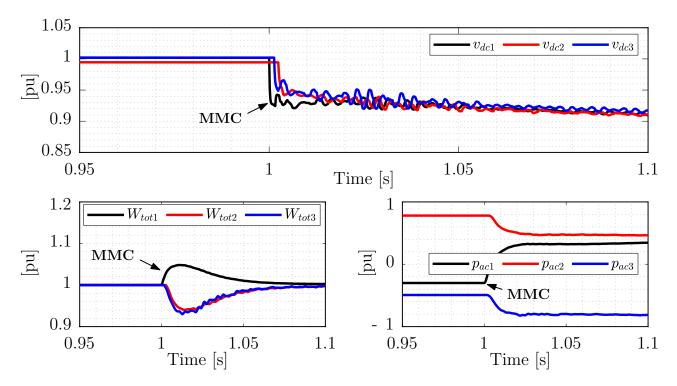

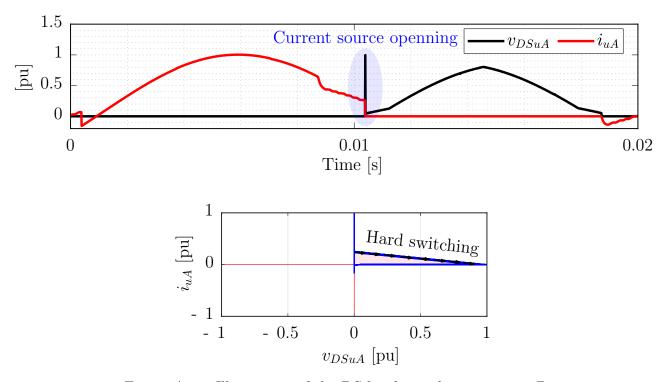

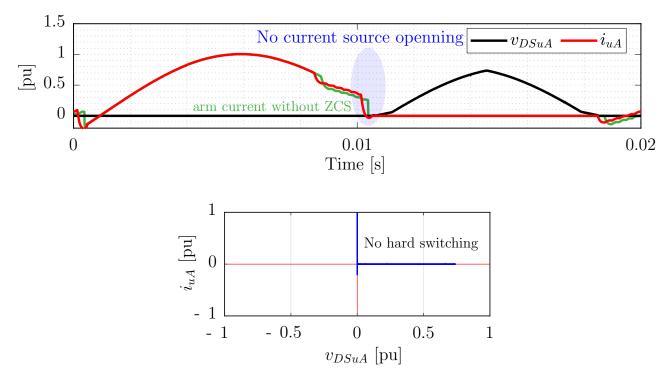

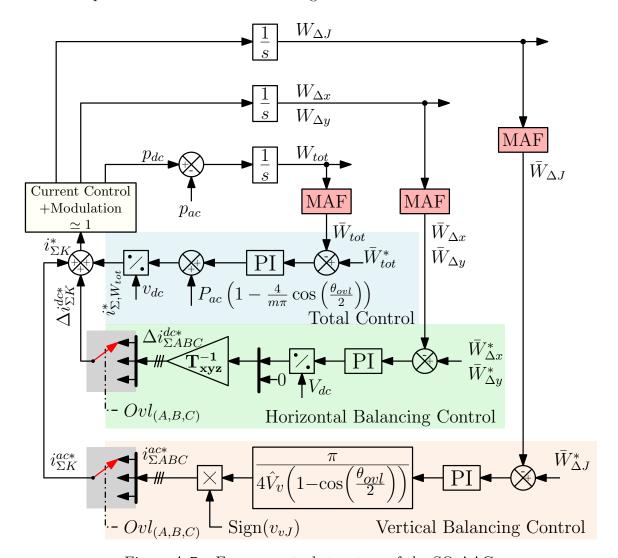

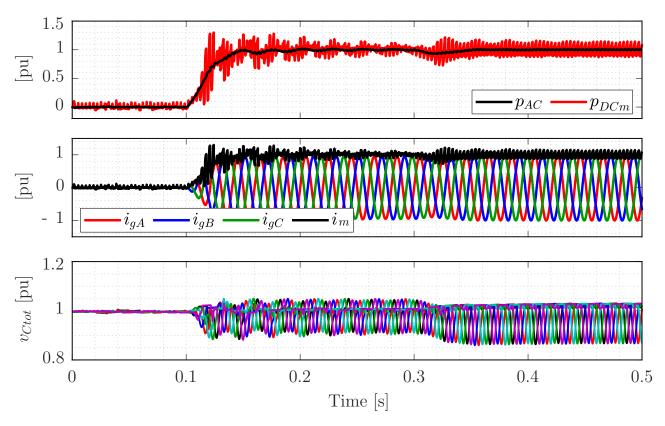

$$P_{u} = \frac{1}{2\pi} \int_{0}^{2\pi} \left( v_{\Sigma} - \hat{V}_{v} \sin(\theta_{g} + \theta_{v}) \right) \left( \frac{\hat{I}_{g}}{2} \sin(\theta_{g} + \varphi) + i_{\Sigma} \right) d\theta$$