# Integrated Programmable-Array accelerator to design heterogeneous ultra-low power manycore architectures Rohit Prasad

### ▶ To cite this version:

Rohit Prasad. Integrated Programmable-Array accelerator to design heterogeneous ultra-low power manycore architectures. Embedded Systems. Université de Bretagne Sud; Università degli studi (Bologne, Italie). Facoltà di Ingegneria, 2022. English. NNT: 2022LORIS624. tel-03701879

### HAL Id: tel-03701879 https://theses.hal.science/tel-03701879v1

Submitted on 22 Jun 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# DOCTORAT BRETAGNE LOIRE MATHSTIC

# THÈSE DE DOCTORAT DE

### L'UNIVERSITÉ DE BRETAGNE SUD

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : « ÉLECTRONIQUE »

# « Rohit PRASAD »

### « Integrated Programmable-Array accelerator to design heterogeneous ultra-low power manycore architectures »

Thèse présentée et soutenue à « Bologne, Italie », le « 20 janvier 2022 » Unité de recherche : « UFR » Thèse Nº : « 624 »

#### Rapporteurs avant soutenance :

Dr David NOVOChargé de Recherches, CNRS – LIRMMDr Paolo MELONIMaître de Conférences, Université de Cagliari, Italie

#### Composition du Jury :

| Président :        | Dr Paolo MELONI | Maître de Conférences, Université de Cagliari, Italie |

|--------------------|-----------------|-------------------------------------------------------|

| Examinateurs :     | Dr David NOVO   | Chargé de Recherches, CNRS – LIRMM                    |

|                    | Davide ROSSI    | Maître de Conférences, Université de Bologne, Italie  |

|                    | Kevin MARTIN    | Maître de Conférences, Université Bretagne Sud        |

| Dir. de thèse :    | Luca BENINI     | Professeur, Université de Bologne, Italie             |

| Co-dir. de thèse : | Philippe COUSSY | Professeur, Université Bretagne Sud                   |

Integrated Programmable-Array accelerator to design heterogeneous ultra-low power manycore architectures Rohit Prasad 2022

# Integrated Programmable-Array accelerator to design heterogeneous ultra-low power manycore architectures

Rohit Prasad

Thesis Directors Philippe Coussy & Luca Benini

Thesis Supervisors Kevin J. M. Martin & Davide Rossi

### 2022

Academic thesis, which with the approval of the Lab-STICC, UMR 6285, Université Bretagne-Sud (France) & Department of Electrical Energy and Information Engineering "Guglielmo Marconi", Università di Bologna (Italy) will be presented for public review in fulfilment of the requirements for a Doctor of Philisophy in Electronics Engineering.

Integrated Programmable-Array accelerator to design heterogeneous ultra-low power manycore architectures Rohit Prasad 2022

# Abstract

There is an ever-increasing demand for energy efficiency (EE) in rapidly evolving Internetof-Things end nodes. This pushes researchers and engineers to develop solutions that provide both Application-Specific Integrated Circuit-like EE and Field-Programmable Gate Array-like flexibility. One such solution is Coarse Grain Reconfigurable Array (CGRA). Over the past decades, CGRAs have evolved and are competing to become mainstream hardware accelerators, especially for accelerating Digital Signal Processing (DSP) applications. Due to the over-specialization of computing architectures, the focus is shifting towards fitting an extensive data representation range into fewer bits, e.g., a 32-bit space can represent a more extensive data range with floating-point (FP) representation than an integer representation. Computation using FP representation requires numerous encodings and leads to complex circuits for the FP operators, decreasing the EE of the entire system. This thesis presents the design of an EE ultra-low-power CGRA with native support for FP computation by leveraging an emerging paradigm of approximate computing called transprecision computing. We also present the contributions in the compilation toolchain and system-level integration of CGRA in a System-on-Chip, to envision the proposed CGRA as an EE hardware accelerator. Finally, an extensive set of experiments using real-world algorithms employed in near-sensor processing applications are performed, and results are compared with state-of-the-art (SoA) architectures. It is empirically shown that our proposed CGRA provides better results w.r.t. SoA architectures in terms of power, performance, and area.

# **List of Figures**

| 1.1  | Three design corners of six architectures, implemented with the same operating parameters.                                         | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Organization of chapters                                                                                                           | 6  |

| 2.1  | Architecture options for Digital Signal Processing applications                                                                    | 10 |

| 3.1  | Integrated programmable Array integrated system                                                                                    | 24 |

| 3.2  | EMF model elements                                                                                                                 | 26 |

| 3.3  | Application to CDFG                                                                                                                | 28 |

| 3.4  | Mapping of BB_4 (See Figure 3.3) onto 2x1 CGRA model and outline of                                                                |    |

|      | the generated assembly code                                                                                                        | 29 |

| 3.5  | smallFloat Unit                                                                                                                    | 30 |

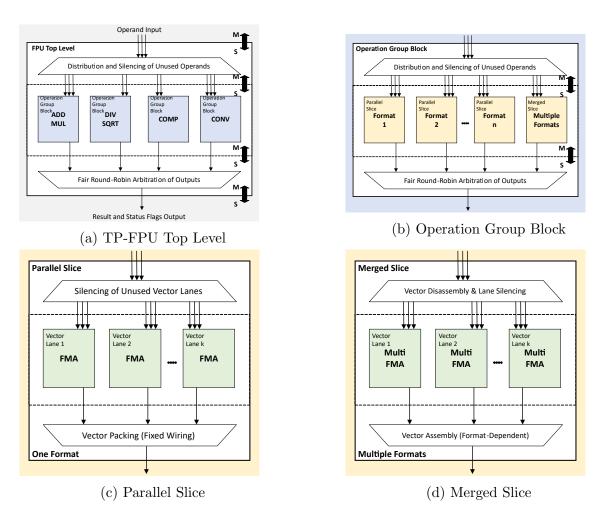

| 3.6  | TP-FPU [56] and its underlying hierarchical blocks. $M = Master port$ ;                                                            |    |

|      | $S = Slave port \dots \dots$ | 31 |

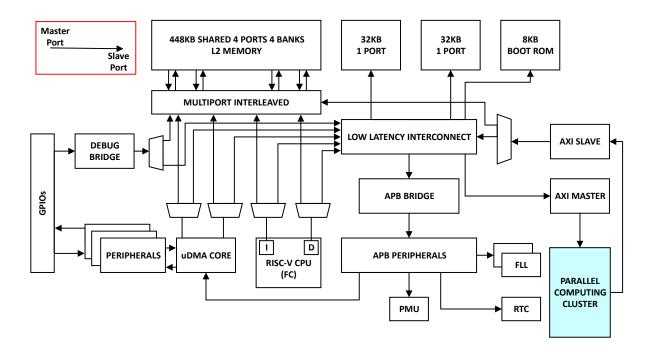

| 3.7  | PULP SoC block diagram detailing SoC domain                                                                                        | 33 |

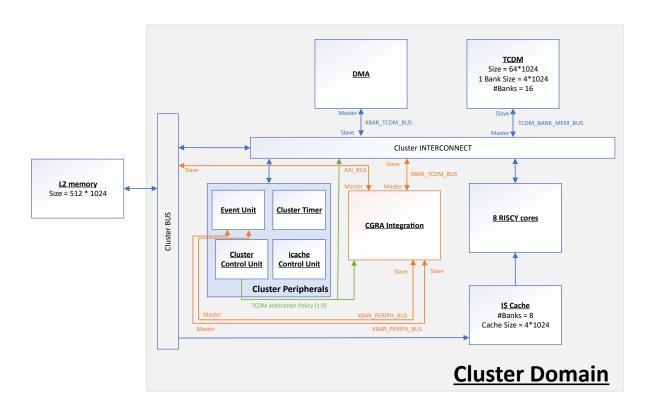

| 3.8  | PULP SoC block diagram detailing Cluster domain                                                                                    | 34 |

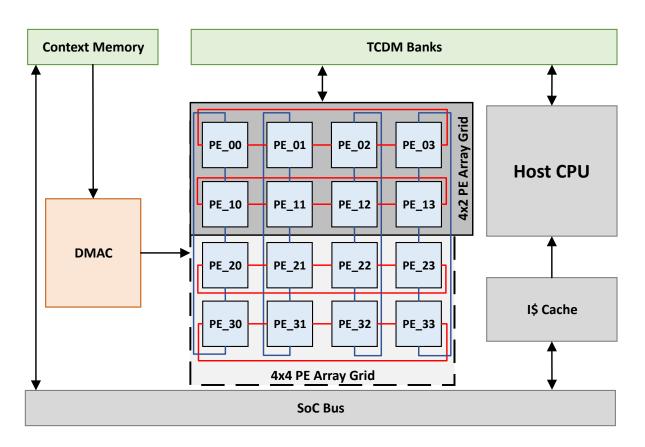

| 4.1  | CGRA Integrated System                                                                                                             | 40 |

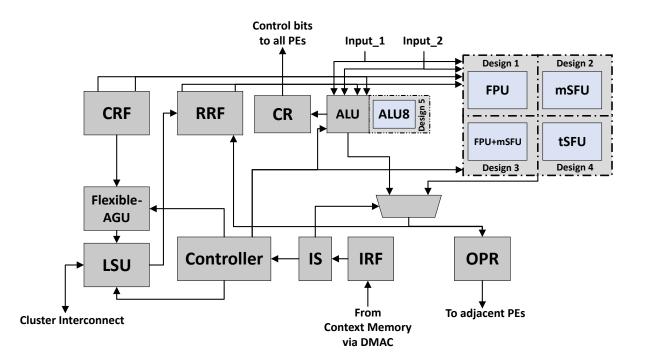

| 4.2  | Processing Element                                                                                                                 | 41 |

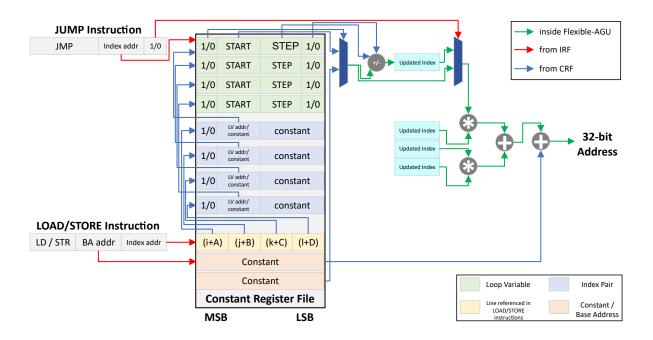

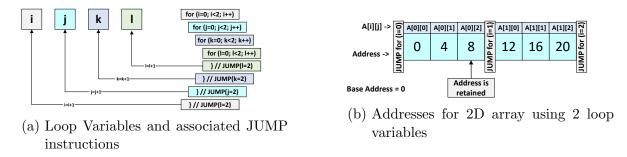

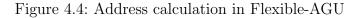

| 4.3  | Flexible-AGU                                                                                                                       | 42 |

| 4.4  | Address calculation in Flexible-AGU                                                                                                | 43 |

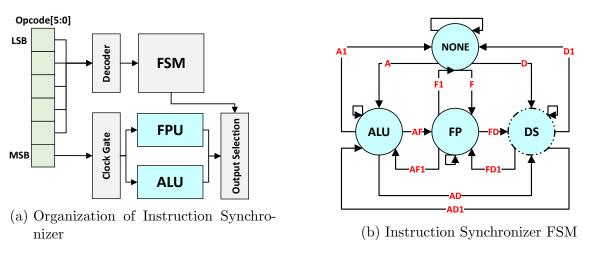

| 4.5  | Instruction Synchronizer                                                                                                           | 44 |

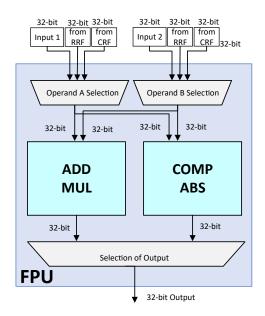

| 4.6  | FPU and its underlying hierarchical blocks                                                                                         | 45 |

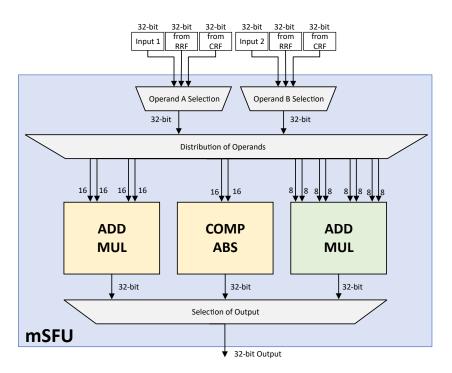

| 4.7  | mSFU and its underlying hierarchical blocks                                                                                        | 46 |

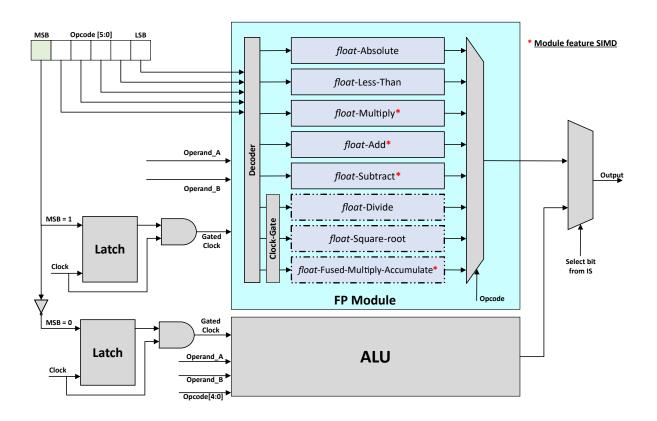

| 4.8  | Clock-Gating Scheme between FP module and ALU                                                                                      | 48 |

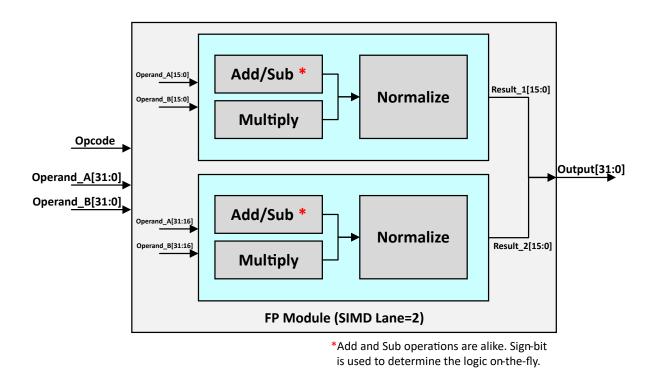

| 4.9  | SIMD execution in FP module                                                                                                        | 49 |

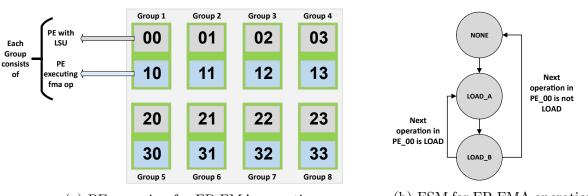

| 4.10 | Implementation of FP-FMA in CGRA                                                                                                   | 50 |

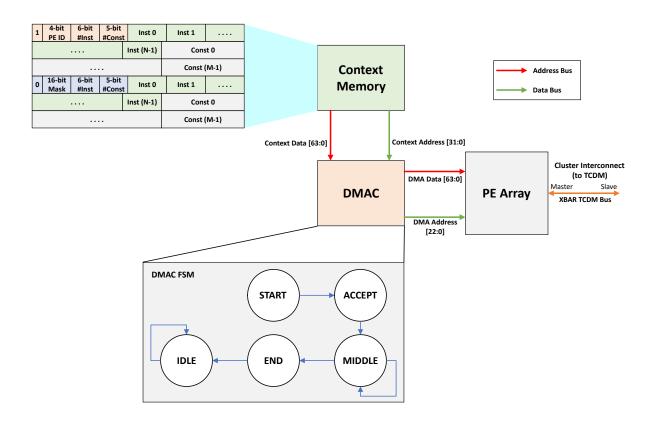

| 4.11 | Configuration Network for context loading                                                                                          | 54 |

|      | Segments of Context Memory                                                                                                         | 57 |

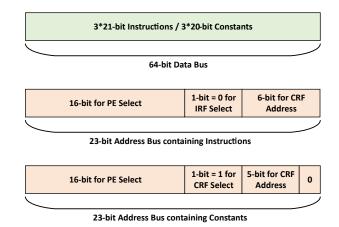

| 4.13 | Data and Address Bus in the configuration network                                                                                  | 57 |

| 5.1  | Compilation Flow                                                                                                                   | 63 |

| 5.2  | EMF model of CDFG                                                                                                                  | 65 |

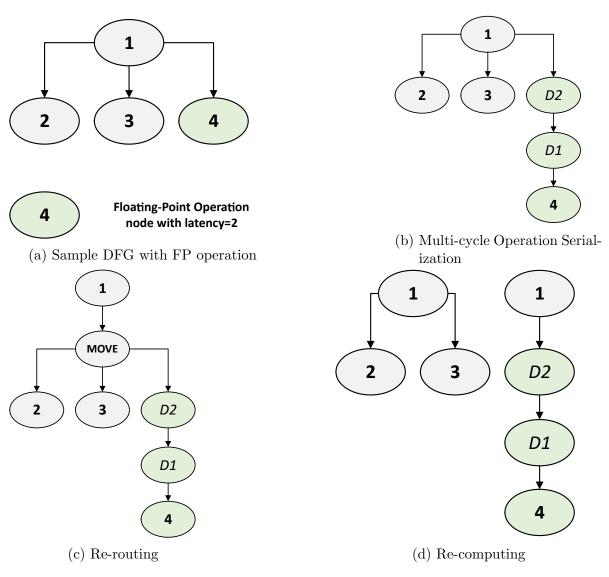

| 5.3  | Graph Transformation to add dummy nodes and Mapping of DFG nodes                                                                   |    |

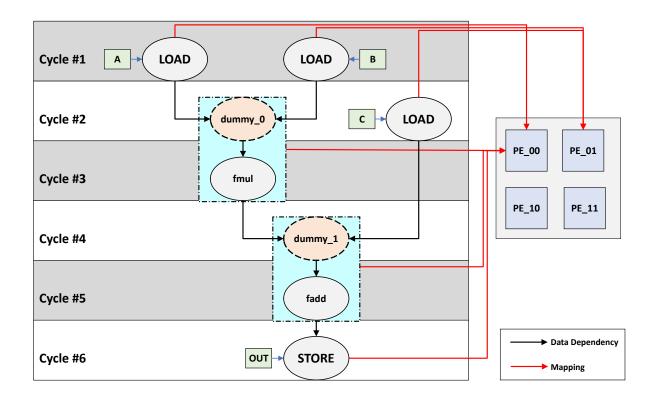

|      | onto PEs                                                                                                                           | 67 |

| 5.4  | Graph Transformation                                                                                                               | 69 |

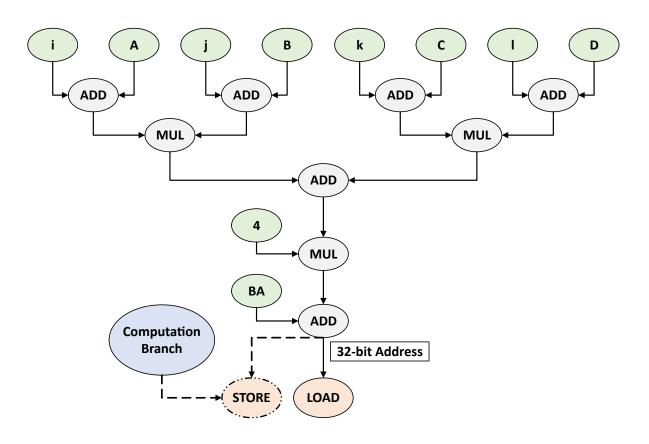

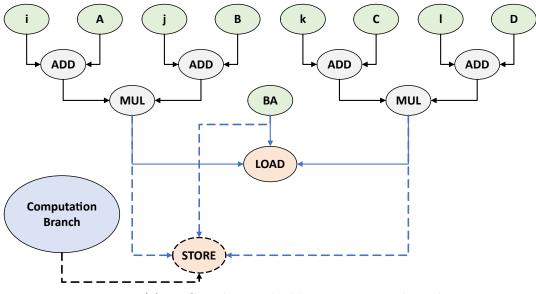

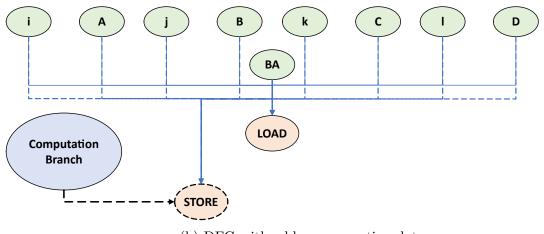

| 5.5  | DFG with address generation branches                                                                                               | 71 |

| 5.6  | Decoupling of address generation branches in DFG                                                                                   | 72 |

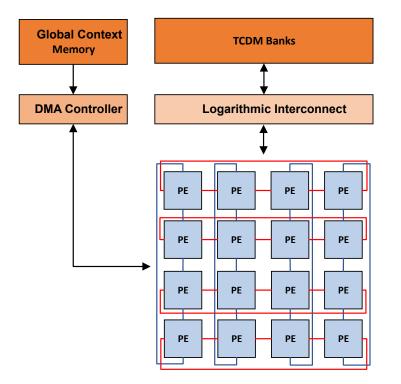

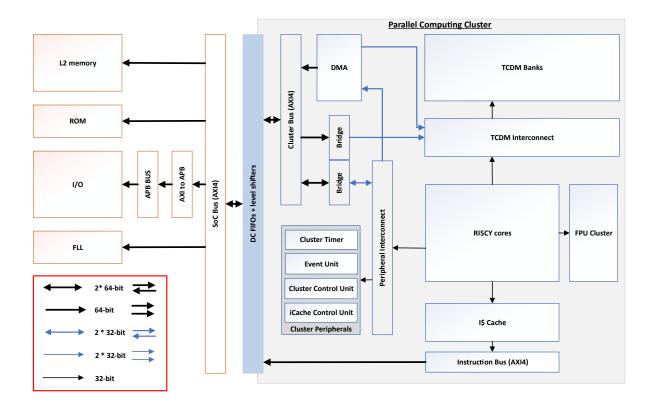

| 6.1 | Organization of CGRA and RI5CY in heterogeneous cluster                                 | 79  |

|-----|-----------------------------------------------------------------------------------------|-----|

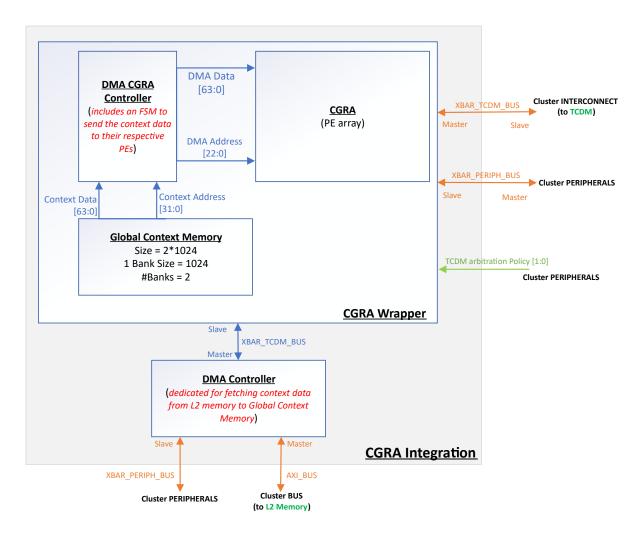

| 6.2 | CGRA integration                                                                        | 80  |

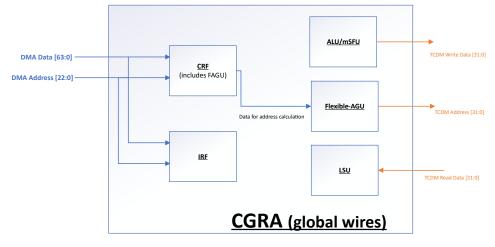

| 6.3 | CGRA global wires                                                                       | 81  |

| 6.4 | PULP SoC Memory Map                                                                     | 82  |

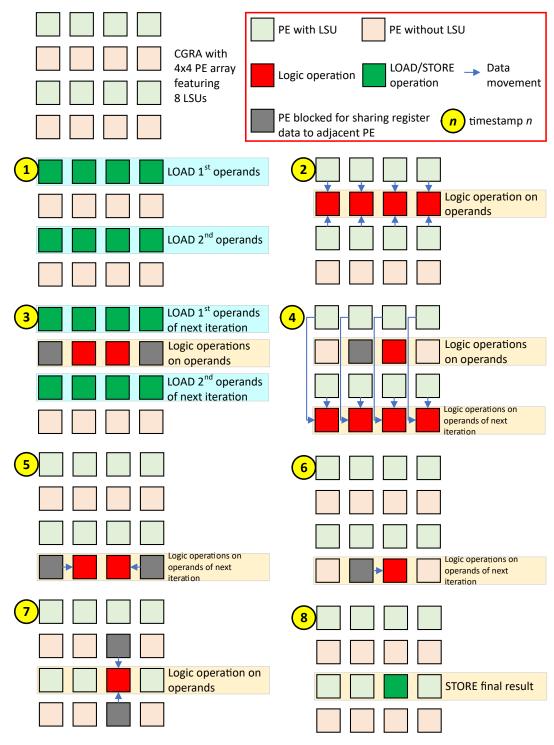

| 6.5 | Manual Mapping Approach 1                                                               | 85  |

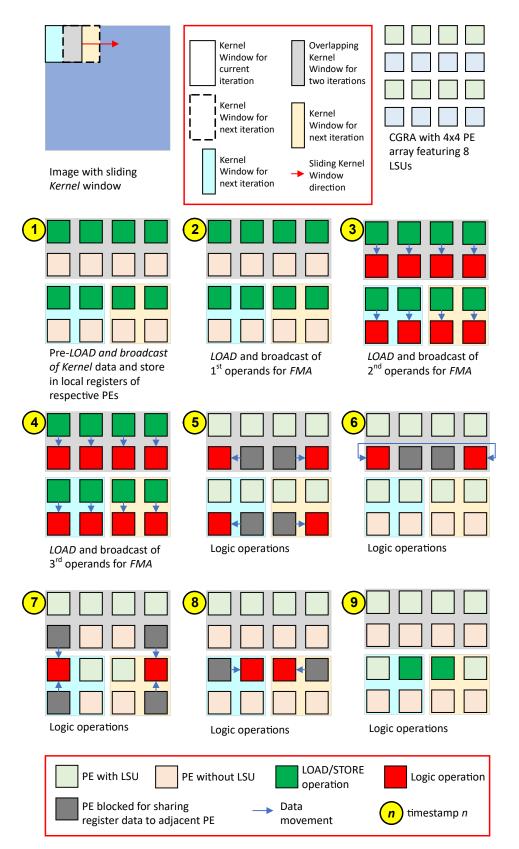

| 6.6 | Manual Mapping Approach 2 (used in $k$ -means)                                          | 86  |

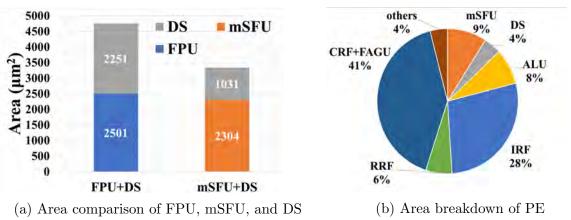

| 7.1 | Total cell area $(\mu m^2)$ breakdown and comparison                                    | 96  |

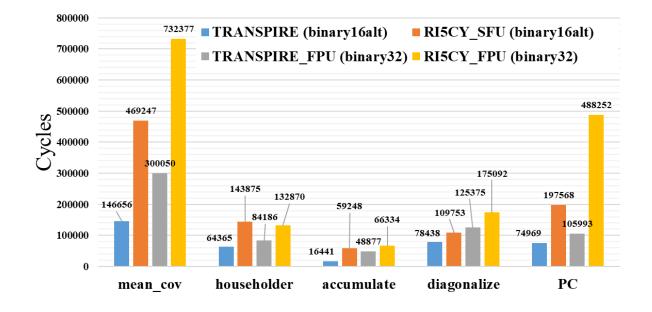

| 7.2 | Latency performance (cycles) of PCA kernels ( <i>binary16alt</i> and <i>binary32</i> )  | 98  |

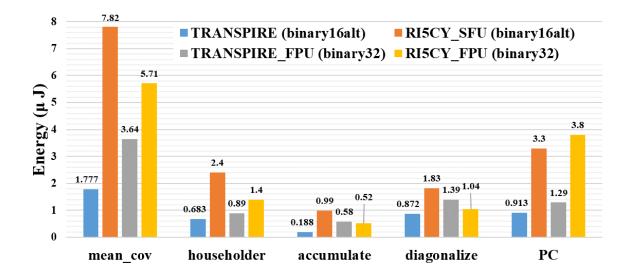

| 7.3 | Energy consumption $(\mu J)$ of PCA kernels ( <i>binary16alt</i> and <i>binary32</i> ). | 99  |

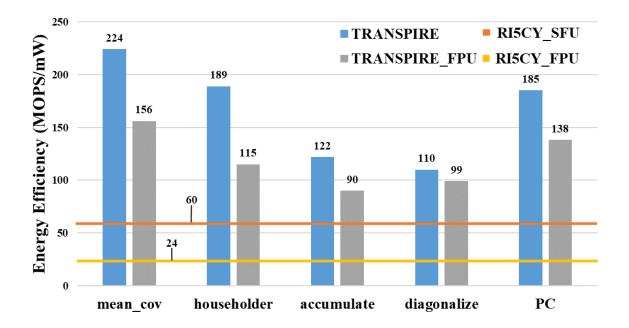

| 7.4 | Energy-Efficiency (MOPS/mW) comparison of 4 architectures                               | 100 |

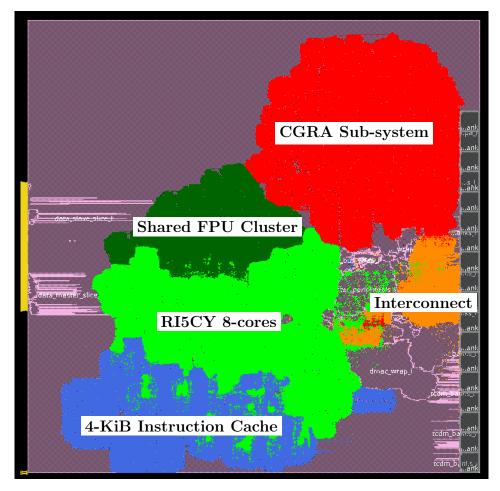

| 7.5 | Post-PnR view of heterogeneous cluster                                                  | 104 |

# **List of Tables**

| $2.1 \\ 2.2$      | Comparison of architectures                                                                        | 12<br>14 |

|-------------------|----------------------------------------------------------------------------------------------------|----------|

| 4.1<br>4.2<br>4.3 | Latency (cycles) of float operators                                                                | 45<br>50 |

|                   | masked, and remaining last 4-bit are used for decoding ALU8 operation.                             | 51       |

| 4.4               | Description of FSM states in DMAC                                                                  | 55       |

| 4.5               | 21-bit ISA Table                                                                                   | 56       |

| 4.6               | Structure of Context Memory segments                                                               | 56       |

| 4.7               | Summary of Opcodes ( $R = Result$ , $C = Condition bit$ ) Gray colored cells                       |          |

|                   | represent newly added opcodes                                                                      | 59       |

| 5.1               | Reserved keywords for FP datatype                                                                  | 66       |

| 6.1               | API for controlling CGRA                                                                           | 81       |

| 7.1               | Complexity of Kernels                                                                              | 94       |

| 7.2               | Accuracy Performance                                                                               | 95       |

| 7.3               | Total cell area $(\mu m^2)$ breakdown and comparison                                               | 96       |

| 7.4               | Average PE Utilization of kernels                                                                  | 97       |

| 7.5               | Latency Performance (cycles) of kernels ( <i>binary8</i> )                                         | 97       |

| 7.6               | Energy Consumption $(\mu J)$ of kernels $(binary8)$                                                | 98       |

| 7.7               | Kernel Complexity for CGRA                                                                         |          |

| 7.8               | Area comparison of CGRA sub-system and RI5CY sub-system                                            |          |

| 7.9               | Latency comparison of CGRA and 8-cores RI5CY                                                       | 105      |

| 7.10              | Latency comparison of CGRA and 8-cores RI5CY. Both architectures are executing with SIMD disabled. | 106      |

| 7.11              | Energy consumption comparison of CGRA sub-system and 8-cores RI5CY                                 | 105      |

| 7 1 9             | sub-system                                                                                         |          |

|                   | Energy consumption of heterogeneous cluster                                                        | 107      |

| 1.15              | and without CGRA                                                                                   | 108      |

| 7 14              | Correlation between PE Utilization and average Power consumption in                                | 100      |

| 1.11              |                                                                                                    | 109      |

| 7.15              | Dynamic PE Utilization of CGRA and dynamic core utilization of RI5CY                               |          |

| A.1               | Architectural features of RI5CY and CGRA (4x4 PE)                                                  |          |

| A.2               | Latency comparison of Dot-Product (in cycles)                                                      | 118      |

| A.3 | Energy consumption comparison of Dot-Product (in $\mu$ J). A single netlist |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | processed at 22 nm FD-SOI technology and running at 200 MHz is used         |     |

|     | for the energy calculation.                                                 | 118 |

# Nomenclature

| $\mu J$   | microJoule                                     |

|-----------|------------------------------------------------|

| $\mu m^2$ | microMeter Square                              |

| $\mu W$   | microWatt                                      |

| AGU       | Address Generation Unit                        |

| ALAP      | As Late As Possible                            |

| ALU       | Arithmetic Logic Unit                          |

| ALU8      | 8-bit integer based Arithmetic Logic Unit      |

| API       | Application Programming Interfaces             |

| ASAP      | As Soon As Possible                            |

| ASIC      | Application Specific Integrated Circuit        |

| ASIP      | Application-specific Instruction Set Processor |

| AXI       | Advanced eXtensible Interface                  |

| BA        | Base Address                                   |

| BB        | Basic Block                                    |

| CCA       | Canonical Correlation Analysis                 |

| CDFG      | Control Flow Data Graph                        |

| CFG       | Control Flow Graph                             |

| CGRA      | Coarse Grain Reconfigurable Array              |

| CONV      | Convolution                                    |

| CPU       | Central Processing Unit                        |

| CR        | Control Register                               |

| CRF       | Constant Register File                         |

| CT        | Computerized Tomography                        |

|           |                                                |

- DARPA Defense Advanced Research Projects Agency

- DFG Data Flow Graph

- DLP Data Level Parallelism

- DMAC Direct Memory Access Controller

- DRA Destination Register Address

- DS Divide-Square-root

- DSP Digital Signal Processing

- DWT Discrete Wavelet Transform

- ECG Electrocardiography

- *EEG* Electroencephalography

- *EMF* Eclipse Modeling Framework

- *ERI* Electronics Resurgence Initiative

- *FC* Fabric Controller

- FD SOI Fully Depleted Silicon On Insulator

- FFG Fast-Fast Global

- *FFT* Fast Fourier Transform

- FIR Finite Impulse Response

- *FLL* Frequency-Locked Loop

- FMA Fused-Multiply-Add

- FP Floating-Point

- FPGA Field-Programmable Gate Array

- FPU Floating-Point Unit

- GCC GNU Compiler Collection

- GCM Global Context Memory

- GNU GNU's Not Unix!

- GP CPU General Purpose-CPU

- GPIO General-Purpose Input/Output

- GPP General Purpose Processor

| HDL    | Hardware Description Language                     |

|--------|---------------------------------------------------|

| HDTV   | High-Definition Television                        |

| HLS    | High Level Synthesis                              |

| I2C    | Inter-Integrated Circuit                          |

| I2S    | Inter-Integrated-Circuit-Sound                    |

| I\$    | Instruction                                       |

| iCache | Instruction Cache                                 |

| IEEE   | Institute of Electrical and Electronics Engineers |

| IIR    | Infinite Impulse Response                         |

| ILP    | Instruction Level Parallelism                     |

| IoT    | Internet of Things                                |

| IP     | Intellectual Property                             |

| IRF    | Instruction Register File                         |

| IS     | Instruction Synchronizer                          |

| ISA    | Instruction Set Architecture                      |

| JTAG   | Joint Test Action Group                           |

| KiB    | Kilo Byte                                         |

| LN     | Logarithmic Number                                |

| LSB    | Least Significant Bit                             |

| LSU    | Load-Store Unit                                   |

| LV     | Loop Variable                                     |

| MAC    | Multiply and Accumulate                           |

| matMUL | Matrix Multiplication                             |

| MCU    | Microcontroller Unit                              |

| MHz    | Mega Hertz                                        |

| MIMD   | Multiple-Instruction stream-Multiple-Data stream  |

| MISD   | Multi-Instruction stream-Single-Data stream       |

| ML     | machine Learning                                  |

|        |                                                   |

| MOPS | Million Operations Per Second                  |

|------|------------------------------------------------|

| MRI  | Magnetic Resonance Imaging                     |

| MSB  | Most Significant Bit                           |

| mSFU | mini-SmallFloat Unit                           |

| NMOS | N-channel Metal–Oxide–Semiconductor            |

| NOP  | No Operation                                   |

| OPR  | Output Register                                |

| PCA  | Principal Component Analysis                   |

| PE   | Processing Element                             |

| PMOS | P-channel Metal–Oxide–Semiconductor            |

| PnR  | Place-and-Route                                |

| PPA  | Power, Performance,m and Area                  |

| PULP | Parallel Ultra-Low-Power                       |

| PWM  | Pulse Width Modulation                         |

| RF   | Register File                                  |

| RISC | Reduced Instruction Set Computer               |

| RRF  | Regular Register File                          |

| SCMD | Single Configuration Multiple Data             |

| SDH  | Software-Defined Hardware                      |

| SIMD | Single-Instruction stream-Multiple-Data stream |

| SISD | Single-Instruction stream-Single-Data stream   |

| SoA  | State-of-the-Art                               |

| SoC  | System-on-Chip                                 |

| SPI  | Serial Peripheral Interface                    |

| SRAM | Static Random Access memory                    |

| SSG  | Slow-Slow Global                               |

| SVM  | Support Vector Machine                         |

| TCDM | Tightly Coupled Data Memory                    |

|      |                                                |

| TLP      | Thread Level Parallelism                    |

|----------|---------------------------------------------|

| TP - FPU | Transprecision Floating-Point Unit          |

| tSFU     | tiny-SmallFloat Unit                        |

| TT       | Typical-Typical                             |

| UART     | Universal Asynchronous Receiver/Transmitter |

| ULP      | Ultra-Low-Power                             |

| UML      | Unified Modeling Language                   |

| UNIX     | UNiplexed Information and Computing System  |

| UNUM     | Unversal Number                             |

| UTBB     | Ultra-Thin Body and Buried oxide            |

| VLIW     | Very Long Instruction Word                  |

# Contents

| Lis | List of Figures |                                                                  |    |

|-----|-----------------|------------------------------------------------------------------|----|

| Lis | st of           | Tables                                                           | iv |

| 1   | Intr            | oduction                                                         | 1  |

| 2   | Rela            | ated Work                                                        | 9  |

|     | 2.1             | Taxonomy of Architectures                                        | 9  |

|     | 2.2             | FP support in low-power circuits                                 | 13 |

|     | 2.3             | Transprecision Computing                                         | 14 |

|     | 2.4             | CGRA Architecture                                                | 15 |

|     | 2.5             | CGRA with FP support                                             |    |

|     | 2.6             | Compiler support                                                 | 19 |

|     | 2.7             | Heterogeneous Computing Systems                                  |    |

|     | 2.8             | Summary and Concluding Remarks                                   | 22 |

| 3   | Bac             | kground                                                          | 23 |

|     | 3.1             | Integrated Programmable Array                                    | 23 |

|     | 3.2             | Flynn's taxonomy                                                 | 25 |

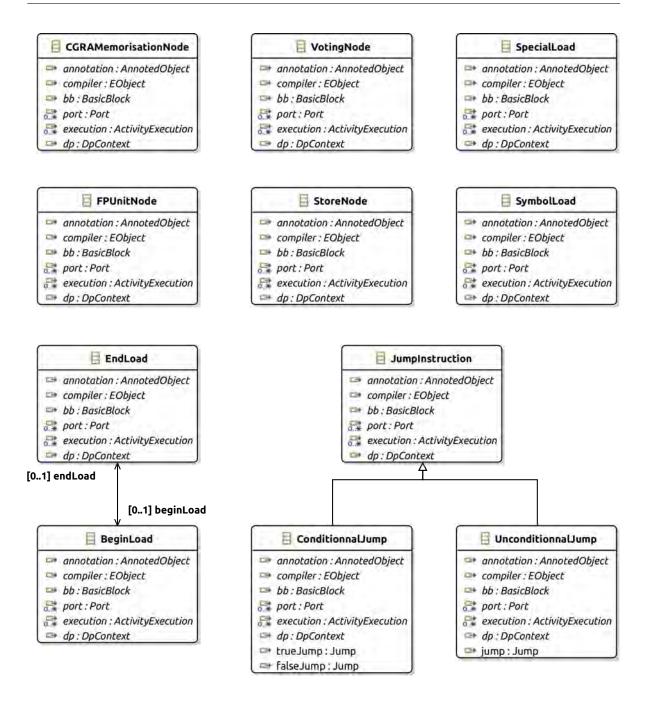

|     | 3.3             | Eclipse Modeling Framework                                       | 25 |

|     | 3.4             | CGRA Compiler                                                    | 27 |

|     | 3.5             | Transprecision Computing based Floating-Point Units              | 29 |

|     |                 | 3.5.1 smallFloat Unit (SFU)                                      |    |

|     |                 | 3.5.2 Transprecision FPU (TP-FPU)                                |    |

|     | 3.6             | PULP Architecture                                                |    |

|     | 3.7             | Summary and Concluding Remarks                                   | 36 |

| 4   | Ene             | rgy-Efficient Programmable Hardware Accelerator                  | 37 |

|     | 4.1             | CGRA Design Optimizations                                        | 38 |

|     |                 | 4.1.1 Design 1: IEEE 754-2008 Standard compliant $4x2$ PE Array  |    |

|     |                 | 4.1.2 Design 2: Transprecision FP compliant 4x2 PE Array         | 46 |

|     |                 | 4.1.3 Design 3: Mixed FP based 4x2 PE Array                      | 47 |

|     |                 | 4.1.4 Design 4: Transprecision FP compliant 4x4 PE Array         | 47 |

|     |                 | 4.1.5 Design 5: $4x2$ PE Array featuring 8-bit integer operators | 51 |

|     | 4.2             | Computation Model                                                | 54 |

|     | 4.3             | Summary and Concluding Remarks                                   | 60 |

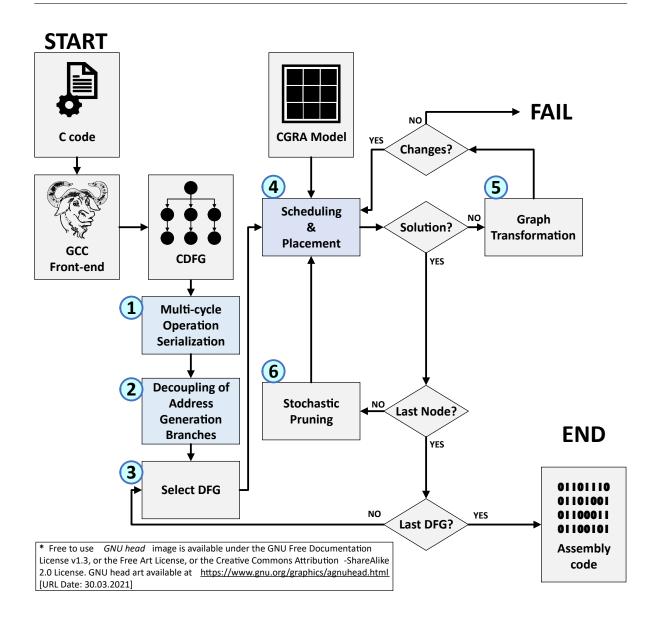

| 5  | 5.1 Compilation Flow |         |                                                             | <b>61</b><br>63 |

|----|----------------------|---------|-------------------------------------------------------------|-----------------|

|    |                      | 5.1.1   | DFG Mapping with multi-cycle operations                     | 66              |

|    | 5.0                  | 5.1.2   | 1 0 0                                                       | 69<br>70        |

|    | 5.2                  |         |                                                             | 72              |

|    | 5.3                  | Summ    | ary and Concluding Remarks                                  | 74              |

| 6  |                      | _       | eous Platform for Transprecision Computing                  | 77              |

|    | 6.1                  |         | ogeneous Platform                                           | 78              |

|    |                      | 6.1.1   | CGRA Integration                                            | 78              |

|    |                      | 6.1.2   | Software Infrastructure                                     | 80              |

|    |                      | 6.1.3   | PULP SoC Memory Map                                         | 81              |

|    |                      | 6.1.4   | Workload Synchronization between CGRA and RI5CY sub-systems |                 |

|    |                      | 6.1.5   | Manual Mapping approaches                                   | 85              |

|    | 6.2                  | Summ    | ary and Concluding Remarks                                  | 90              |

| 7  | Exp                  | erimen  | tal Framework and Performance Evaluation                    | 91              |

|    | 7.1                  | Analys  | ses of implementation of the proposed CGRA                  | 93              |

|    |                      | 7.1.1   | Evaluation Methodology                                      | 93              |

|    |                      | 7.1.2   | Quality of Results                                          | 94              |

|    |                      | 7.1.3   | Implementation Results                                      | 95              |

|    |                      | 7.1.4   | Latency Performance                                         | 97              |

|    |                      | 7.1.5   | Energy Consumption                                          | 99              |

|    |                      | 7.1.6   | Energy-Efficiency                                           | 100             |

|    | 7.2                  | Analys  | ses of implementation of the heterogeneous cluster          |                 |

|    |                      | 7.2.1   | Evaluation Methodology                                      | 101             |

|    |                      | 7.2.2   | Implementation Results                                      |                 |

|    |                      | 7.2.3   | Latency Performance                                         | 104             |

|    |                      | 7.2.4   | Energy Consumption                                          | 106             |

|    |                      | 7.2.5   | Utilization                                                 | 109             |

|    | 7.3                  | Summ    | ary and Concluding Results                                  | 110             |

| 8  | Con                  | clusion | & Future Work                                               | 111             |

| Α  | Eval                 | luation | of Architectures                                            | 117             |

|    |                      |         |                                                             |                 |

| Bi | Sibliography 119     |         |                                                             |                 |

# Chapter 1

# Introduction

Internet of Things (IoT) devices are rapidly evolving, and therefore, there is an everincreasing demand for ultra-low-power and energy-efficient computing architectures, i.e., IoT end nodes. Applying software-based optimizations to augment the performance of a system is not enough [1]. A good trade-off between architectural characteristics and computational capabilities must be considered to boost the performance of IoT end nodes [2]. Such resource-constraint ultra-low-power (ULP) architectures face challenges while executing algorithms involving near-sensor computing or embedded machine learning (ML). Multiple efforts to keep these architectures energy-efficient and flexible enough to cope with the evolving technologies are seen in recent research works [3, 4, 5, 6].

Coarse Grain Reconfigurable Array (CGRA) architectures hold the potential to fit the requirement of being energy-efficient and at the same time provide flexibility to support evolving algorithms involving near sensor computing or embedded ML. A CGRA consists of an array of Processing Elements (PE), which are relatively smaller and simpler than General Purpose Processors (GPP). These PEs are connected through a simple on-chip network to provide data movement within the array. Each PE is configurable to execute part of a kernel in parallel with other PEs in the array. To provide an efficient parallel execution, each PE features a small register file to temporarily keep data loaded from memory or immediate results, which can be shifted/moved to other PEs using the on-chip network, resulting in avoiding register spilling or memory traffic. CGRAs can provide silicon efficiency approaching that of an Application-Specific Integrated Circuit (ASIC) by exploiting spatial computation typical of dedicated hardware blocks while keeping the programmability of GPPs [7, 8]. Furthermore, CGRAs have always been competing for being adopted as high-performance accelerators [7, 8, 9, 10, 11].

Energy-efficient execution of fixed-point workloads is prevailing in the recent ULP architectures. However, emerging IoT end nodes demand support for operations on datatype with high dynamic data range, i.e., floating-point (FP) numbers [12]. An alternative is to port FP operations into low-cost fixed-point operations [13] but porting an FP application into its fixed-point equivalent is laborious and demands in-depth knowledge of the application domain. Besides, porting an FP application into a fixed-point is not always energy-efficient due to the execution of instructions required for organization and normalization of such operations to overlook the dynamic range of FP numbers, resulting in significant overheads [14].

An optimization technique to meet the computational demands of an application uses mixed, i.e., floating-fixed point representation. Such mixed representation is featured in State-of-the-Art (SoA) FP capable low-power architecture end-nodes like Cortex-M processors [15]. Again, this approach requires a tedious manual analysis of the applications for format selection between float and fixed for tuning the dynamic range and results in software overheads for such on-the-fly conversions. Furthermore, using such mixed representation results in degradation of the overall computational efficiency of Cortex-M processors, like, energy dissipated while managing the pipelines and register files in Cortex-M4 processor due to flushing or stalls [16].

A noticeable number of commercial architectures fail to turn off the FP units while fixedpoint operators are executing in the cores; this also further lowers the energy efficiency of such architectures [17].

Approximate computing is a technique where the computing system does not compute the precise result but computes an approximated result. In this technique, to boost the performance of a computing system, a trade-off to the quality of computation with the effort spent is realized, resulting in fewer circuits and less energy consumption. An emerging paradigm of approximate computing is *transprecision* computing [1] that aims to improve the energy efficiency of low-power systems by adopting multiple FP formats to satisfy the accuracy requirements of the target application without manual adjustments. *Transprecision* computing is an alternative for applications demanding operations with high dynamic data range (i.e., FP operations) in IoT end nodes. *Transprecision* computing provides both hardware and software-based control mechanisms to fine-tune the approximation of computations in an application. Integration of *transprecision* computing in ULP architectures holds the potential to achieve high energy efficiency while executing applications requiring high dynamic range FP operations [17].

This thesis explores the design of an energy-efficient ULP CGRA with native support for FP computation by leveraging *transprecision* computing. Different design optimizations and architectures are presented for developing the CGRA with support for multiple FP datatype, including SoA IEEE 754-2008 standard FP and new custom transprecision FP datatype. A design is incomplete without the aid of compilation tools, so the contributions in the compilation toolchain to add support for FP in CGRA are also presented. To envision the proposed CGRA as an energy-efficient hardware accelerator, system-level integration of CGRA in a System-on-Chip is performed to demonstrate the applicability of CGRA as an energy-efficient hardware accelerator by using real-world algorithms employed in near-sensor processing application fields (i.e., image, audio, bio-signals, and embedded Machine Learning). Finally, two sets of results are presented in this thesis. First, CGRA with a 4x2 PE array is compared with a single-core SoA processor resulting in CGRA achieving a maximum of  $10.06 \times$  better latency performance and consuming  $12.91 \times$  less energy, with an area overhead of  $1.25 \times$ only. Second, CGRA with a 4x4 PE array is compared with an 8-cores SOA processor sub-system resulting in the CGRA sub-system achieving a maximum of  $4.20 \times$  better latency performance and consuming  $7.80 \times$  less energy, while CGRA sub-system also being  $2.19 \times$  smaller than 8-cores SoA processor sub-system.

### Motivation

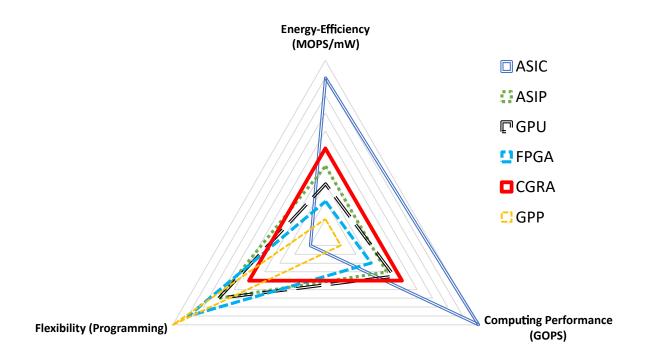

CGRAs are a raw coarse-grained implementation of the perception of reconfigurable computing proposed in the 1960s [18]. CGRA architectures were first introduced in the 1990s [19, 20] and have been developing extensively since the 2000s [21, 22, 23, 24]. CGRAs continuously attract both academia and industries, as CGRAs can provide near-ASIC energy efficiency and performance while maintaining software-like programmability with post-fabrication [11, 25, 26, 27, 28]. Figure 1.1 provides an overview of the positioning of hardware accelerator and processor architectures, i.e., Application-Specific Integrated Circuit (ASIC), Application-Specific Instruction Set Processor (ASIP), General Purpose Processor (GPP), Graphics Processing Unit (GPU), Field-Programmable Gate Array (FPGA), and Coarse Grain Reconfigurable Array (CGRA) with three design corners, where all architectures are implemented with the same operating parameters [7, 8, 11, 25, 29]. Breakdown of Figure 1.1 is as follows:

- ASICs are custom logic designs with fixed functions, making them the most energyefficient architectures with the highest computing performance. However, these architectures are comprised of custom and fixed functions with limited libraries and support. Hence, they are least flexible among all the architectures in Figure 1.1.

- ASIPs are designed for a specific application domain, and these architectures exhibit an instruction set designed to accelerate most executed and critical functions. These architectures provide a trade-off between energy efficiency, computing performance, and flexibility.

- GPPs are designed to provide maximum flexibility to support all applications. Hence, these architectures are least energy-efficient and have minimum computing performance among all architectures in comparison in Figure 1.1.

- GPUs exhibit a large parallel array of cores designed for rendering graphics. These architectures have relatively high energy consumption but somewhat similar computing performance and flexibility as that of ASIPs.

- FPGA consists of a large number of configurable logic blocks that are connected through programmable interconnects. Each configurable logic block is essentially an array of programmable gates. These architectures provide high flexibility. However, these architectures provide low energy efficiency and computing performance due to unavoidable overheads with such fine granularity.

- CGRAs are outset to provide a balance between these three design corners. These

Figure 1.1: Three design corners of six architectures, implemented with the same operating parameters.

hybrid architectures are essentially systolic arrays <sup>1</sup> that are expanded to be programmed using instructions, making them coarser than FPGAs in terms of flexibility. CGRAs exhibit simple architecture to provide moderately high energy efficiency and computing performance.

GPPs are the most flexible architectures, ASICs are the most energy-efficient and provide the highest computing performance. On the other hand, CGRAs provide a balance between these three design corners.

In academia, the researchers consider CGRAs as a firm competitor for mainstream computing architectures because CGRAs provide a good trade-off among efficiency, performance, and flexibility for a certain application domain [7, 8, 30, 31] and also because of extensive supports by organizations like the Defense Advanced Research Projects Agency (DARPA) [32]. The objective of DARPA ERI (Electronics Resurgence Initiative) is software-defined hardware (SDH), i.e., to enable hardware to provide near-ASIC performance ( $\approx 10 \times$ ) while maintaining the programmability for data-extensive kernels/algorithms. AHA Agile Hardware Project is an initiative to enable an agile hardware development flow. Under this project, especially for the rapid development of CGRAs, three domain-specific languages have been developed to generate individual components for CGRA. These are (1) PEak for processing tiles, (2) Lake for memory tiles, and (3) Canal for the interconnect [33].

<sup>&</sup>lt;sup>1</sup>Systolic array is a network of tightly coupled data processing elements. These processing elements perform the same logic operation with different data at the different timestamp.

In industry, Samsung presented their 8K high-definition television (HDTV) and Exynos SoC featuring a CGRA accelerator [10, 34]. The CGRA intellectual property (IP) cores are present in the satellite payload of Astrium, where the IP cores are developed by PACT Incorporated [24]. An Intel project to integrate CGRAs into its Xeon processor was initiated in 2016 [35]. Other companies also have related projects, plans, prototypes, or products like DRP [36] and DAPDNA [37].

Ever-increasing computational demand from applications attracts researchers/industries to implement FP-like computations (i.e., computing FP workload using integer-based operators or converting FP workloads into fixed-point workloads) in CGRAs [11, 38, 39, 40, 41, 42]. A recent trend to equip IoT platforms with FP unit is also seen in microcontroller units like M4 and M7 [43]; a factor leading to such trend is with technology node scaling below 40nm, the cost of FP operation is getting near 1pJ per operation [44, 45], so it has become affordable in terms of absolute power to use FP in IoT. This gave us an incentive to implement FP operators with variable dynamic range and variable precision in a CGRA targeting the ULP domain and applications involving near-sensor computing and embedded ML.

## Contribution

This thesis contributes to the following characteristics of practicing CGRAs as hardware accelerators in computing platforms.

- 1. Design of CGRA with support for FP computation: the main contribution of the thesis is the design of an energy-efficient ULP CGRA with support for FP computation. Multiple design optimizations and their architectures to add support for multiple FP datatype in CGRA are presented.

- 2. Efficient mapping of FP operations: the changes in the hardware must be propagated to the compilation flow, and integration of new features in the toolchain must produce efficient mappings of the FP operations. This thesis presents the techniques used and the challenges tackled during the change propagation from hardware to compilation flow.

- 3. Implementation of Flexible-AGU: to improve the performance of CGRA, address generation is decoupled from the compilation flow, and a hardware Flexible-Address Generation Unit is introduced in the PEs of the proposed CGRA. The Instruction Set Architecture (ISA) width of the CGRA is limited; encoding of data required to compute the address and decoding instructions in the hardware was a challenge and is also presented in this thesis.

- 4. System-level integration in an SoC: the point of presenting an energy-efficient ULP CGRA is to improve the overall performance of the computing platforms. This integration is necessary to envision the CGRA as a hardware accelerator

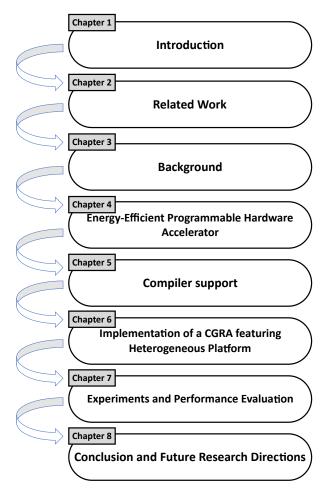

Figure 1.2: Organization of chapters

properly. The challenges in integrating the CGRA sub-system in an SoC to propose a heterogeneous platform are presented in this thesis.

5. Benchmark: this thesis empirically shows that the CGRA can improve the overall performance when integrated into a system. A wide range of real-world applications used in near sensor computing and embedded ML is used to benchmark the CGRA w.r.t. SoA architectures and all the experimental results obtained using gate-level simulation silicon-proven PULP platform [46].

## Organization

Figure 1.2 shows the outline of the thesis and follows the points described in the contribution section. In chapter 2 and chapter 3, the related work and the necessary background information associated with the contribution of this thesis are presented respectively. Chapter 4 discusses the architecture and design optimizations of the CGRA with support for multiple FP datatype. Then, chapter 5 discusses the compiler support to enable energy-efficient support for FP in CGRA. In chapter 6, a heterogeneous platform featuring the proposed CGRA sub-system is presented. Chapter 7 presents the evaluation methodology and performances of the proposed CGRA and the heterogeneous platform. Finally, in chapter 8, the thesis summarizes the given work and suggestions for possible future research directions.

### List of Publications

- R. Prasad, S. Das, K. J. M. Martin, G. Tagliavini, P. Coussy, L. Benini and D. Rossi, "TRANSPIRE: An energy-efficient TRANSprecision floating-point Programmable archItectuRE," 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2020, pp. 1067-1072, https://doi.org/10.23919/DATE48585.2020.9116408

- S. Das, R. Prasad, K. J. M. Martin and P. Coussy, "Energy Efficient Acceleration Of Floating Point Applications Onto CGRA," ICASSP 2020 - 2020 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Barcelona, Spain, 2020, pp. 1563-1567, https://doi.org/10.1109/ICASSP40776.2020.9054613

- 3. R. Prasad, S. Das, K. J. M. Martin, and P. Coussy, "Floating Point CGRA based Ultra-Low Power DSP Accelerator," Journal of Signal Processing Systems (2021). https://doi.org/10.1007/s11265-020-01630-2

- Journal to be submitted for publication. The title is as follows:

R. Prasad, G. Tagliavini, K. J. M. Martin, P. Coussy, L. Benini and D. Rossi, "Hopalong: A Heterogeneous Cluster for Transprecision Computing on IoT End Nodes".

# Chapter 2

# **Related Work**

#### Contents

| <b>2.1</b> | Taxonomy of Architectures        |

|------------|----------------------------------|

| 2.2        | FP support in low-power circuits |

| 2.3        | Transprecision Computing         |

| 2.4        | CGRA Architecture                |

| 2.5        | CGRA with FP support 18          |

| 2.6        | Compiler support                 |

| 2.7        | Heterogeneous Computing Systems  |

| 2.8        | Summary and Concluding Remarks   |

This chapter discusses the topics of (1) Taxonomy of architectures, (2) Floating-Point (FP) support in low-power circuits, (3) Transprecision computing, (4) CGRA architecture, (5) CGRAs supporting FP computations, (6) Compiler support for the development of CGRA, and (7) PULP SoC [46] based heterogeneous computing systems featuring different hardware accelerators. These topics serve as the related work for the thesis.

### 2.1 Taxonomy of Architectures

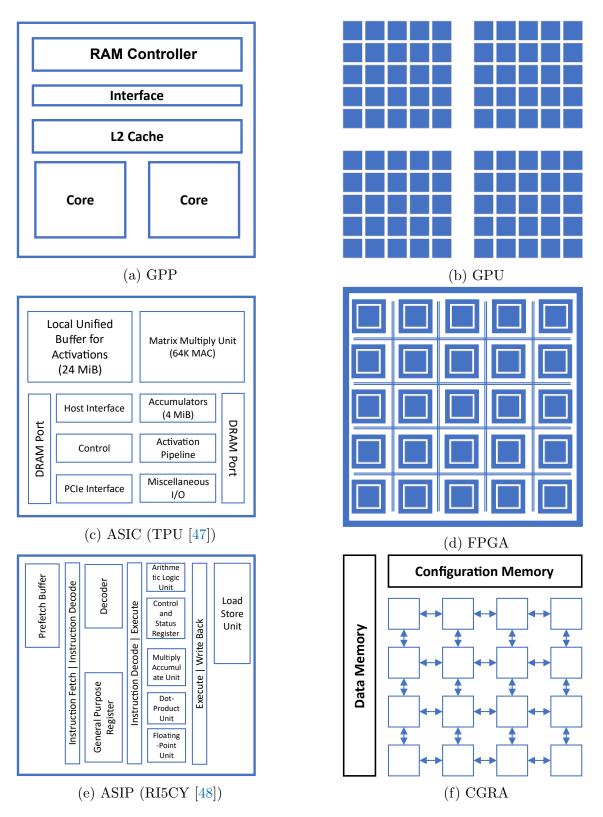

There are billions of IoT devices that execute digital signal processing (DSP) applications and the majority of them are battery operated. In this thesis, the proposed CGRA targets DSP applications and adopts multiple optimization techniques to boost the energy efficiency of the entire system. Figure 2.1 shows six architectural options that are interesting for digital signal processing applications. These architectures are described below.

Figure 2.1: Architecture options for Digital Signal Processing applications

### ASIC

Figure 2.1c shows the organization of an Application-Specific Integrated Circuit (e.g., Tensor Processing Unit or TPU [47]). Typically, ASICs are non-programmable and target only one application. ASICs were a preferred solution where the level of integration was limited, like Very Large-Scale Integration (VLSI) with the introduction of the first MOS Integrated Circuit by General Microelectronics in 1964 [49]. However, multiple solutions have been proposed over the past decades, and also, due to technological advancements, ASICs are not the only choice of architecture to be integrated into a system. Typically, ASICs are introduced for matured architectures with the highest level of optimizations. ASICs are able to reach the highest energy efficiency and computing performance for a target application.

### ASIP

Figure 2.1e shows the organization of an Application-Specific Instruction Set Processor (e.g., RI5CY [48]). An ASIP is designed for a specific application domain, and the instruction set architecture (ISA) of these architectures is designed to accelerate the frequently occurring functions or critical functions. The cost of hardware and the power consumption is relatively lower than other architectures in Figure 2.1 because ASIPs usually target predictable computing, so the design optimizations can be much higher while providing a substantial amount of flexibility for the target domain applications.

#### GPP

Figure 2.1a shows the organization of a General Purpose Processing unit with two cores. A GPP runs complex tasks and aims to facilitate maximum flexibility for all applications. Typically, GPPs are limited to perform certain concurrent tasks as these architectures consume a large amount of energy with little computing performance. The compiler and Operating System are designed to support all applications, which also requires a huge amount of engineering design time. Overall, building a GPP-based computer infrastructure from scratch is very expensive.

#### GPU

Figure 2.1b shows a typical Graphic Processor Unit. A GPU consists of many smaller specialized cores. These cores work together to deliver a massive performance by dividing the task and processing them in parallel. Initially, GPUs began as specific ASIC to accelerate specific 3D rendering tasks. Gradually, GPU cores evolved from fixed-function engines to become programmable and flexible cores. Nowadays, GPUs are also capable

| Type  | Power<br>Consumption | Strengths               | Constraints             |  |

|-------|----------------------|-------------------------|-------------------------|--|

| ASIC  | Ultra-Low            | Small silicon footprint | Fixed function          |  |

| ASIP  | Low to               | Targets                 | Complex instructions    |  |

| ASII  | Ultra-Low            | application domain      | and tasks               |  |

| GPP   | High                 | Flexible                | Few cores               |  |

| GPU   | High                 | Highly parallel cores   | Large silicon footprint |  |

| FPGA  | Medium               | Re-programmable         | Programming Complexity  |  |

| CGRA  | Low to               | Targets                 | Simple instructions     |  |

| UGIIA | Ultra-Low            | application domain      | and tasks               |  |

Table 2.1: Comparison of architectures

of handling a wide range of applications and compete against other general-purpose parallel processors.

### **FPGA**

Figure 2.1d shows a typical Field-Programmable Gate Array architecture. an FPGA consists of many logic blocks which can be programmed and reprogrammed to perform numerous functions at any point in time. These logic blocks are interconnected through a programmable interconnect network. Development on an FPGA is relatively cheaper due to nearly non-existent Non-Recurring Engineering (NRE) cost than other architectures in Figure 2.1. Such affordability makes FPGAs their preferred choice for designers to perform experiments or even realize any architecture design (mainly in the early development stages).

### CGRA

Figure 2.1f shows the organization of a typical Coarse Grain Reconfigurable Array architecture. A CGRA consists of an array of simple and small processing elements that are connected through an interconnect network. CGRA can efficiently exploit parallel computing due to the availability of an array of low-cost processing elements and also due to affordable data movement of the spatial-temporal data between the processing units. CGRAs were studied at first for accelerating the inner loop computation of the applications. Over time, CGRAs have evolved to become a competitive solution for high-performance accelerators.

Table 2.1 presents a comparison table of the six architectures. CGRA is the essence of this thesis, and all the topics presented in this thesis involves the development of CGRA architecture, its optimization techniques, and its associated toolchain.

### 2.2 FP support in low-power circuits

Using a data format with a fewer precision bits format to represent decimal FP numbers suffers substantially from the loss of accuracy. Applying such data formats with limited precision bits in real-world DSP applications, where intermediate results are frequently accumulated, can lead to undesirable loss of accuracy and devastating consequences like ARIANE 5: Flight 501 Failure (i.e., failure of the maiden flight of the Ariane 5 launcher on 4 June 1996) due to occurrence of errors while converting 64-bit FP number to 16-bit signed integer value [50].

FP operations are much more complex than integer operations, so it is familiar to trade-off between speed and accuracy while implementing FP computing modules. An example of combining two FP datatype modules (i.e., IEEE 754-2008 Decimal FP and IEEE 754-1985 Binary FP formats) is presented in [51, 52], where hardware resource sharing resulted in saving up to 58% of less area w.r.t. the combined areas of individual modules, with a negligible impact on the critical path delay for the combined module over the individual decimal modules. Representing a decimal digit in IEEE 754-2008 standard requires 4-bit, and this leads to a larger datapath, making it unsuitable for the FP units in the proposed ULP CGRA.

A good balance between delay, area, and accuracy for FP representation is provided by IEEE 754-2008 standard. However, FP computing with increased precision bits results in larger energy consumption, making those computing systems less attractive for ULP architectures. An alternative is to explore custom FP formats for enabling low-power circuits with FP operations. One such effort is presented in [53], where a Logarithmic Number System (LNS) based LNS Unit (LNU) efficiently performs FP operations by translating FP operations into simple integer operations. However, a fallacy to this implementation is that the LNUs take a larger area than their singleprecision FP counterparts. These LNUs become attractive when shared among several cores. They can be  $4.1 \times$  more energy-efficient than a similar area design using four private FPUs while executing standard nonlinear processing kernels.

An FP format similar to IEEE 754-2008 FP standard is Universal Numbers (UNUM). UNUM features an additional tag for self-description of the represented value (i.e., number of bits for exponent and precision), enabling them to represent variable-sized FP numbers [54]. The silicon implementation of an ASIC featuring UNUM-based ALU [55] showed 7% less memory footprint w.r.t. an IEEE 754-2008 single-precision FP unit. UNUM-based ALU also offered a more comprehensive range for half-precision FP formats with an increased datapath complexity, making the design choice less attractive for the proposed CGRA to avoid a complex interconnect network for PEs.

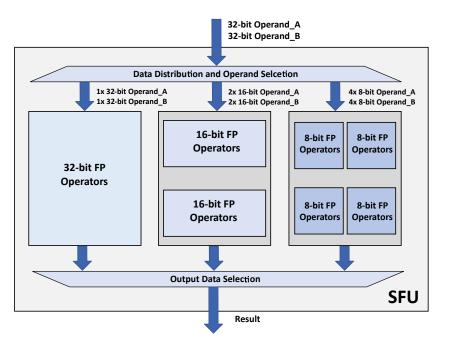

A new set of custom FP formats called smallFloat formats that can also be regarded as an alternative to IEEE 754-2008 FP standard (i.e., *float* and *float16*) are *binary16alt* and *binary8* [1]. These new FP formats exhibit the same dynamic range as that of IEEE counterparts with fewer precision bits. smallFloat formats are useful in applications that require low precision, like ML applications. The silicon implementation of a 32-bit

| Format       | #Bits | Exponent | Mantissa | Range                                  |

|--------------|-------|----------|----------|----------------------------------------|

| IEEE float   | 32    | 8        | 23       | $1.2 \ge 10^{-38}$ - $3.4 \ge 10^{38}$ |

| binary16alt  | 16    | 8        | 7        | $1.2 \ge 10^{-38}$ - $3.4 \ge 10^{38}$ |

| IEEE float16 | 16    | 5        | 11       | $5.9 \ge 10^{-8} - 6.5 \ge 10^4$       |

Table 2.2: FP formats used in IoT devices

RISC-V core based ASIP, including a multi-format FPU featuring both IEEE 754-2008 standard FP formats and smallFloat formats, showed the multi-format FPU could achieve a latency gain of  $1.67 \times$  w.r.t. an IEEE *float* based FPU without losing any precision in the results, and reducing the system energy by 37% [56]. These results make smallFloat formats very attractive for the proposed CGRA because the target domain applications of CGRA also require high dynamic range, low precision, and low power consumption.

### 2.3 Transprecision Computing

ML workloads executed by modern near-sensors applications demand both high dynamic data range and low-power consumption. IEEE 754-2008 standard provides double-precision (64-bit; IEEE *double*) and single-precision (32-bit; IEEE *float*) FP representations to realize the high dynamic data range demand, but such FP computations are too costly in terms of energy consumption for IoT end nodes leveraging ULP architectures. The half-precision FP representation introduced in IEEE 754-2008 standard (16-bit; IEEE *float16*) is a trade-off between dynamic range and energy cost, which is suitable for approximate computing. Over the years, significant advancements in approximate computing are seen. However, there is still a considerable demand for high dynamic data range and low-power consumption from IoT end nodes.

Typically, IEEE *float* and *float16* are used in IoT devices but these FP representations either high energy consumption (in IEEE *float*) or lack high dynamic data range (in IEEE *float16*). Recently, a new custom datatype has been introduced, called *binary16alt*, to cover the fallacies of these IEEE FP formats, i.e., provides a high dynamic range as of IEEE *float* and at the same time consumes similar energy as of IEEE *float16*. Table 2.2 shows these FP formats.

Range of SoA ML applications like Convolutional Neural Networks [57] and Temporal Neural Networks [58] relies on ML models which can tolerate lower precision computations without losing their accuracy [59] and IEEE *float16* and *binary16alt* FP datatype is well suited for such applications. Adopting such lower precision FP formats enables a system to achieve high performance and also be energy-efficient while executing such ML applications, but embracing such FP formats will require full software support and thorough analysis for tuning precision of FP variables to safely replace the high-cost FP formats with low-cost FP formats [60] in those applications.

Transprecision computing is an emerging paradigm of approximate computing which aims to fulfill those demands of providing high dynamic data range and be energyefficient [1]. In *transprecision* computing, the intermediate results preserve the dynamic range, and precision is tuned to fulfill the accuracy requirements of an application, allowing programmers to adapt to a new FP format with fewer bits. In [56], a siliconproven architecture has been introduced, which is an integral part of the *transprecision* computing framework by enabling programmers to fine-tune the workloads ranging from algorithms and software down to hardware and circuits.

### 2.4 CGRA Architecture

The applications used in IoT devices keep evolving due to increasing computational demands in IoT end nodes. Going for highly optimized and hardwired ASIC architectures could lead to a very aggressive time-to-market to deliver the next iteration of current designs. In this scenario, employing programmable hardware accelerators (i.e., CGRAs) as co-processors in such systems can ease the before-mentioned deadlines. CGRAs have proven to be effective in accelerating target applications by achieving silicon efficiency near an ASIC by exploiting spatial computation typical of dedicated hardware while keeping programmability typical of GPP [7].

Recent CGRAs have demonstrated effectiveness in executing fixed-point workloads because fixed-point units employ simpler architecture of integer arithmetic units [61]. However, there is an increasing demand for support for FP computation in emerging IoT end nodes [13]. Few CGRAs have been presented in the past to support FP computations. However, efficient and dedicated support for FP still lacks in those CGRAs [8, 11, 39, 40, 41, 42] which makes them less attractive for adoption in IoT end nodes or ULP architectures.

CGRA architectures have an ample design space as these architectures feature (1) tightly or loosely coupling to host processors, (2) types of on-chip interconnects and the interactions between producer-consumer resources, (3) reconfigurability/programmability of the array, (4) ways to control the executions in array, (5) support for different types of parallelism. Typical characteristics of a CGRA that motivate a ULP CGRA to execute FP computations efficiently are discussed below.

#### Reconfigurability

The salient feature of a CGRA is its ability to be reconfigured (i.e., flexibility). The three types of reconfiguration are:

1. Dynamic reconfiguration where CGRAs use small controllers to fetch new configuration every clock cycle from configuration buffers.

- 2. Static reconfiguration where configuration bits of CGRAs remain fixed for the whole execution of a loop.

- 3. Hybrid reconfiguration where CGRAs use a combination of both static and dynamic configurations.

Notably, in the case of dynamic reconfiguration, a full reconfiguration follows every execution cycle, and to better utilize such array, a simpler instruction fetching mechanism w.r.t. GPPs is employed for iterating through a loop body without any control flow like seen in ADRES [21], Silicon Hive [62], and MorphoSys [63]. Hybrid reconfigurable CGRAs like RaPiD [64] where static and dynamic reconfigurability is controlled by a small sequencer or PACT [65], where CGRA can self trigger events for partial reconfiguration and consumes a substantial amount of time. In contrast to these CGRAs, KressArray [66] features a fully static reconfiguration approach where CGRA is configured before a loop is executed. In such CGRAs, efficiently mapping of kernels onto hardware is prioritized, which is done at a higher level in the compiler.

While all before mentioned CGRAs avoid executing control statements mainly to minimize hardware complexity, our priority was to opt for dynamic reconfiguration of CGRA and execute a complete kernel by implementing low-cost control flow support in CGRA by combining efficient mapping of control statements in compiler and simple design choices in hardware.

### Scheduling and Issuing

Execution of operations and data transfers can be controlled in a CGRA either by dynamic, static, or hybrid reconfiguration. Such reconfiguration can be achieved in a compiler by scheduling the static code schedules like seen in VLIW processors [67] or the approach used in out-of-order processors can be used where processors issue instructions the availability required operands [68] or by combining static and dynamic reconfiguration and static and dynamic scheduling [21, 62, 63, 65, 66, 69, 70].

In the case of dynamic reconfiguration, the dynamic execution of control instructions consumes more power. In static scheduling, all possible paths, even the slower ones that might be taken infrequently during the execution, are scheduled and consumes more resources. It can be concluded that the design choices depend on the target application domain. In our case, we opted for a dynamic scheduling approach due to the simple architecture of the PEs. All architectural decisions are driven by the energy consumption of the modules implemented in PEs, including low power consuming controllers for fetching new instructions.

### **Parallel Processing**

With the availability of the number of cores of a CGRA, it is recognizable to implement support for different types of parallelism. In [65, 66], dynamic scheduling is implemented through a distributed event-based control mechanism, and thus implementing Thread Level Parallelism (TLP) is relatively simple and cheap. In this case, the execution of independent small loops (with a combined resource can fit) on the CGRA can be mapped on different parts of the distributed control resource. A different approach is to design an architecture with centralized control mechanism where parallel threads can run by implementing additional controllers or extending the central controller to support the execution of parallel threads concurrently. Such extensions can increase power consumption but might be suitable for certain code parts by saving datapath energy and energy consumed while fetching configuration data.

Alternatively, TLP can be converted into a combination of Instruction Level Parallelism (ILP) and Data Level Parallelism (DLP). At compile time, such a combined approach can exploit kernels with multiple threads by scheduling those threads together as one kernel and then selecting the appropriate combination of the scheduled kernel at run time [71].

In our CGRA, parallel processing is achieved by combining the implementation of additional controllers in hardware and exploitation of ILP and DLP in the kernels.

### Interconnect Network

The type of reconfiguration scheme plays an essential role in the selection of interconnecting networks. Interconnect networks are required in both phases of execution in CGRAs, i.e., (1) configuration phase, where a network is required to distribute the instructions to each core, and (2) compute phase, where a network is required to route the data flow. PEs of a CGRA can be interconnected in a wide range of connections (1) with direct connections (i.e., interconnect network), (2) with Register Files or other memories, and (3) with IO ports. In ULP architectures, energy efficiency is the main focus, and low power networks could be implemented to achieve the low-power consumption goal.

In the case of dynamic reconfiguration, if there is a centralized configuration network, then the network for configurations or instructions is accessed as frequently as the network for data flow by the cores of CGRA. In such a scenario, merging the two networks could be a convenient choice and the use of proper routing of data and instructions can avoid conflicts due to shared resources. If there is no centralized configuration memory, then it may result in high power consumption due to the implementation of separate networks for configurations and instructions.

In the case of static reconfiguration, a network dedicated for *configuration phase* is

used once per execution cycle, and a network dedicated for *compute phase* is used extensively, depending on the kernel. A low-cost interconnect network (like 2D mesh) should be implemented to obtain high energy efficiency in such a scenario.

#### **Register Files**

Compilers for CGRA schedule the operations and their respective data flow is routed over the connections between the PEs. These connections could be direct or latched, or connections that go through RF, depending on the type of operations are being scheduled. So, most compilers treat RFs as interconnects that can span over multiple cycles instead of temporary storage. Thus, RFs in between cores of a CGRA are included during design space exploration for interconnects. During such routing, (1) the number of interconnecting wires, (2) their topology, i.e., RF size, (3) their location, and (4) the number of ports contribute to determining the interconnectivity of cores of a CGRA.

#### Instruction Set Architecture

Implementing simple Instruction Set Architecture (ISA) could help minimize the cost of instruction fetching and decoding due to simple decoder design and also leads to the simple hardware design of the cores of CGRA, resulting in low-power consumption.

For example, a 32-bit ISA of RISC-V encodes a lot of information in each instruction. To execute an operation, the RISC-V core fetches 32-bit instruction and applies a complex decoder to decode the already fetched instruction. This gives a little room for optimization in the instruction fetch and instruction decode stage of the pipeline architecture of the RISC-V core. In the case of conditional instructions, most of the instruction space is non-utilized which also results in unavoidable power consumption due to fetching and decoding of 32-bit instruction where most of the instruction bits are zeros. While a simple ISA implementation with less number of bits (like 21-bit ISA of the proposed CGRA) can avoid such a complex decoder or fetching of instructions with large unused spaces (i.e., in case of conditional instructions), resulting in relatively low-power consumption than the RISC-V core featuring 32-bit ISA.

### 2.5 CGRA with FP support

CGRAs can efficiently exploit both Data Level Parallelism (DLP) and Instruction Level Parallelism (ILP) in a Digital Signal Processing (DSP) application because these architectures take advantage of the execution pattern characterized by repeated execution of a combination of operators like addition, subtraction, and multiplication. Mainly, DSP applications demand sharing or shifting of immediate data with the neighboring entities, which CGRAs can efficiently execute by featuring cheap MOVE operations due to simple cores and interconnect networks.

Real-world DSP applications are rapidly evolving and demand a more complex execution pattern than ever. These applications also demand FP operations to satisfy the wide dynamic range of the input/output data. In addition, recent CGRAs lack the flexibility to efficiently execute such demanding, complex execution patterns and support for FP operations. Microcontrollers like M4 and M7 [43] feature FP units and have been implemented below 40nm process node. Their cost of executing FP operation is near 1pJ [44, 45], demonstrating that cost-efficient implementation of FP operators in IoT devices is attainable.

Very few works have been demonstrated where a CGRA is featuring support for FP operations. These reconfigurable/programmable architectures are limited with low ILP and/or low DLP while adding support for FP operations. Imagine [38] is one of the early programmable architectures that featured FP unit hardware for single-precision FP operations, and the execution model of Imagine follows data streaming. RASP [39] is a DSP architecture featuring an array of coarse-grain computing elements with support for single-precision FP operations. RASP can efficiently execute sub-algorithms of filters applied in radar signal processing, namely, FFT, IIR, and matrix-multiplication, to help improve the overall computational efficiency of the radar system. Imagine and RASP lack the capability to execute an entire application, while the proposed CGRA can efficiently execute a whole application.

FloRA [40] and Wave CGRA [11] adopted a different approach of combining the integerbased operators to perform FP computations, resulting in a complex execution model, increased interconnect width, and degraded output quality. Another such architecture is Butter array [41], which combines integer-based addition, multiplication, and additional units for packing and rounding the output, resulting in extra area overhead and a lack of native FP support. An approach to converting FP workloads into fixed-point workloads before computing output is SDT-CGRA [42], which features a flexible interconnect network to support multiple computation models with reduced hardware complexity but the conversion of all FP inputs into fixed-point before the output is calculated brings a significant overhead and loss of accuracy. In conclusion, all of these architectures are too demanding in terms of power consumption to be considered for IoT end nodes or as ULP architecture.

### 2.6 Compiler support

Compiler plays a crucial role in determining the efficiency of a CGRA because a compiler inputs a human-readable application code to produce the target machine code (bit-stream). While compiling, a compiler faces challenges like (1) producing code according to the level of granularity of the target hardware system or (2) maintaining high utilization of the cores (with efficient exploitation of algorithmic parallelism) in

#### the CGRA array.

Typically, dataflow languages expose the potential parallelism of any application. Still, while generating required machine code for parallel General-Purpose-Processors (GPPs), the compiler considers the overall dataflow network of the application only (i.e., Data Flow Graph of the application). Due to such considerations by the compilers, potential parallelism extracted from the internals of the code is left out (i.e., a loop structure, pipelining of intra-agents, or task splitting and rescheduling). Allowing a CGRA compiler to exploit both ISA and micro-architecture of the CGRA enables the CGRA compiler to efficiently optimize the application to obtain maximum performances from the target CGRA.

A CGRA compiler could efficiently exploit architectural support of multilevel parallelism (i.e., data, instruction, memory, speculative, and thread) to obtain higher utilization of the cores in the CGRA array. Still, there are substantial trade-offs that must be taken into account. For instance, superscalar processors are more efficient by dispatching multiple instructions per clock cycle than scalar processors (Single Instruction Single Data processors). Hence superscalar processors can efficiently utilize ILP; multi-core processors are more efficient than superscalar ones due to the efficient utilization of Thread Level Parallelism (TLP); out-of-order processors exhibit better performance than inorder processors due to efficient utilization of speculative parallelism. In CGRAs, a good trade-off between area and power can lead to the implementation of efficient parallelism because when area and power overheads counterbalance the (latency) performance gain, the area efficiency and energy efficiency are degraded. Such degradation depends on both applications and architectures.

TRIPS [23] is a CGRA architecture that supports three modes of execution to support various parallelism (i.e., DLP, ILP, and TLP) [72]. Another example is Polymorphic Pipeline Array [73], which supports fine-grained parallelism by exploiting ILP and TLP with the help of software pipeline and coarse-grained pipeline parallelism. CGRAs presented in [74, 75, 76, 77] exploit a technique of software pipelining to explore coarse granularity of loop-level or kernel-level parallelism but pipelining of operations or instructions does not comply with the typical characteristics of CGRAs because CGRAs mainly rely on energy-efficient spatial computations instead of time-multiplexed instruction or operation pipelines. Such CGRAs are specifically proposed to counter out-oforder processors which dynamically exploit ILP in hardware. CGRAs like [23, 30, 78, 79, 80] use spatial computation model to implement ILP. In this technique, order of execution and data preparation is done by static scheduling of a DFG. This technique is also used to accommodate multiple DFGs on a single array. Domain-specific CGRA like [22, 31] implement DLP in Single Configuration Multiple Data (SCMD) manner to reduce area and power overheads due to fetching of same instructions for multiple-data, i.e., provides a programmable interface to minimize memory accesses and bypass redundant address generation. CGRAs with centralized control schemes are presented in [80, 81, 82, 21] where execution and reconfiguration of all cores of CGRA occur in lockstep, i.e., using a large configuration to reduce energy consumption and maximize resource utilization. However, integrating such CGRAs into a larger (hierarchical) CGRA could result in a CGRA with coarse-grained TLP.

On the other hand, in [83], a distributed control scheme has been implemented in a CGRA to execute multiple tasks simultaneously. Dataflow technique can be exploited to implement TLP in CGRAs like TRIPS [23] which uses static dataflow to enable spatial parallel execution of multiple DFGs, and CGRAs like SGMF [79] which exploits dynamic dataflow to execute multiple DFGs in an overlapping manner. TFlex [84] is a pipelined CGRA that implements speculative parallelism by introducing a predicate/branch predictor that uses all predicates in a block (i.e., code in both True and False paths of a condition statement) next block. In TFlex, if there is a misprediction, then the speculative block is flushed from the pipeline.

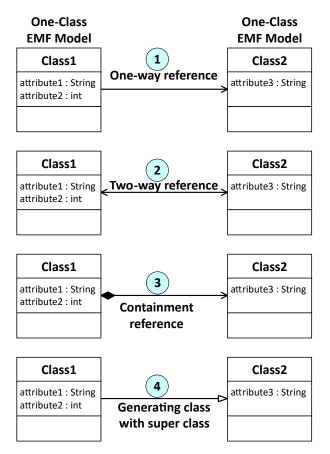

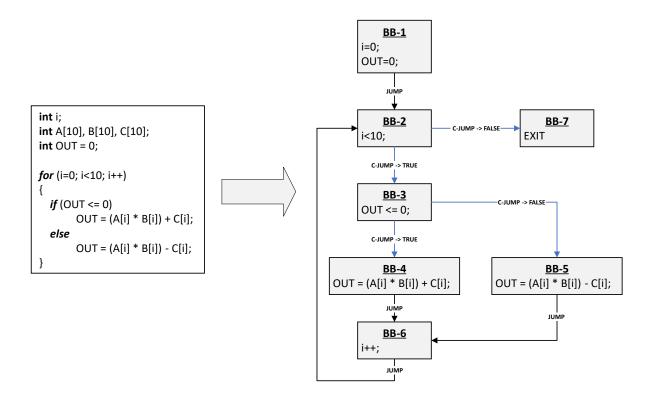

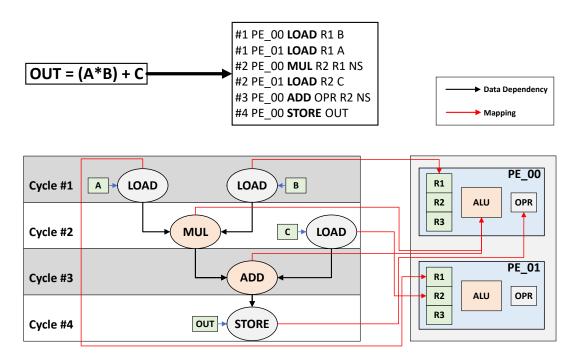

The compiler support used for the proposed CGRA plays a crucial part by providing quick and efficient mapping solutions for the target applications for the proposed CGRA. The mapping process is automated through a software tool implemented using an Eclipse-based modeling framework and code generation solution called Eclipse Modeling Framework (EMF) [85, 86]. The compiler shares a common framework with a High-Level Synthesis (HLS) tool called GAUT [87]. The contributions of this thesis to the existing compilation flow [88, 80, 89, 90] are (1) adding support for custom FP formats and multi-cycle operation support, and (2) decouple the data required for address generation from the mapping process and encode the data in the generated instructions that are to be decoded by a dedicated hardware module to calculate the corresponding address in the CGRA during execution.

## 2.7 Heterogeneous Computing Systems