## Notifying Memories for Dataflow Applications on Shared-Memory Parallel Computer

Alemeh Ghasemi

### ► To cite this version:

Alemeh Ghasemi. Notifying Memories for Dataflow Applications on Shared-Memory Parallel Computer. Hardware Architecture [cs.AR]. Université Bretagne-Sud, 2022. English. NNT: . tel-03704297v1

## HAL Id: tel-03704297 https://theses.hal.science/tel-03704297v1

Submitted on 24 Jun 2022 (v1), last revised 17 Jan 2023 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## DOCTORAT BRETAGNE LOIRE / MATHSTIC

# THÈSE DE DOCTORAT DE

## L'UNIVERSITÉ DE BRETAGNE SUD

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

#### Par

## « Alemeh GHASEMI »

# « Notifying Memories for Dataflow Applications on Shared-Memory Parallel Computer »

Thèse présentée et soutenue à « Lorient », le « 18 mai 2022 » Unité de recherche : Lab-STICC Thèse Nº : « 620 »

#### **Rapporteurs avant soutenance :**

Jocelyn Sérot Professeur - Université Clermont Auvergne Frédéric ROUSSEAU Professeur - Université Grenoble Alpes

#### **Composition du Jury :**

| Président :     | Jean-François Nezan  | Professeur - INSA Rennes                           |

|-----------------|----------------------|----------------------------------------------------|

| Examinateurs :  | Jocelyn Sérot        | Professeur - Université Clermont Auvergne          |

|                 | Frédéric Rousseau    | Professeur - Université Grenoble Alpes             |

|                 | Alix Munier Kordon   | Professeur - Sorbonne Université                   |

|                 | Midia Reshadi        | Research Fellow - Trinity College Dublin           |

| Dir. de thèse : | Jean-Philippe DIGUET | DR CNRS - IRL Crossing                             |

| Encadrant :     | Kevin Martin         | Maître de conférences - Université de Bretagne-Sud |

## ACKNOWLEDGEMENT

I would like to thank my supervisors, Dr. Kevin Martin and Dr. Jean-Philippe Diguet, for their patience, guidance, and support. I have significantly benefited from their knowledge and meticulous editing. I am incredibly grateful that they have conducted this thesis over the years.

I am also grateful for the help of the committee members, Professor Jean-François Nezan and Dr. Midia Reshadi. Their encouraging words and thoughtful, detailed feedback have been significant to me. Additionally, I greatly appreciate the reviewers of my thesis, who so generously took time out of their schedules to review my research and make this project possible.

Lastly, I thank my family for their endless support. They have always stood behind me, and this was no exception. I could not have done it without them.

## TABLE OF CONTENTS

| In                        | trod                | uction  |                                                            | 13 |

|---------------------------|---------------------|---------|------------------------------------------------------------|----|

|                           | Mot                 | ivation |                                                            | 21 |

|                           | Thesis organization |         | 25                                                         |    |

| 1                         | Syn                 | nmetri  | c Shared-memory Multiprocessor (SMP)                       | 29 |

|                           | 1.1                 | Symm    | etric Shared-memory Multiprocessor (SMP)                   | 29 |

|                           | 1.2                 | Synch   | ronization for SMP                                         | 30 |

|                           |                     | 1.2.1   | Synchronization Support in Software                        | 31 |

|                           |                     | 1.2.2   | Synchronization Support in the ISA                         | 36 |

|                           |                     | 1.2.3   | Synchronization Support in Hardware                        | 37 |

|                           |                     | 1.2.4   | Qualitative Comparison                                     | 40 |

|                           | 1.3                 | Cachir  | ng: terminology, mechanisms, and synchronisation           | 44 |

|                           |                     | 1.3.1   | Basic terminology                                          | 45 |

|                           |                     | 1.3.2   | Coherency                                                  | 47 |

|                           |                     | 1.3.3   | Synchronisation and caches                                 | 49 |

|                           | 1.4                 | Multi-  | core Simulators                                            | 50 |

|                           | 1.5                 | Summ    | ary and Concluding Comments                                | 56 |

| <b>2</b>                  | Dat                 | aflow 1 | Model of Computation                                       | 59 |

|                           | 2.1                 | Genera  | alities                                                    | 59 |

|                           | 2.2                 | Static  | Dataflow MoCs                                              | 61 |

| 2.3 Dynamic Dataflow MoCs |                     | 63      |                                                            |    |

|                           |                     | 2.3.1   | Generalities                                               | 63 |

|                           |                     | 2.3.2   | PiSDF: a Reconfigurable Dataflow Model                     | 63 |

|                           | 2.4                 | Datafl  | ow Prototyping Frameworks                                  | 64 |

|                           |                     | 2.4.1   | PREESM                                                     | 64 |

|                           |                     | 2.4.2   | SPiDER: Runtime Management Layer for Dataflow Applications | 66 |

|                           | 2.5                 | Cache   | Studies for Parallel Applications                          | 67 |

|                           | 2.6                 | Summ    | ary and Concluding Comments                                | 70 |

### TABLE OF CONTENTS

| 3 | Cac | he eva  | duation and dynamic memory management techniques                                                   | 71  |

|---|-----|---------|----------------------------------------------------------------------------------------------------|-----|

|   | 3.1 | Multi-  | -Core Model Used in Experiments                                                                    | 72  |

|   | 3.2 | The C   | Cache Impact on Dataflow Applications                                                              | 73  |

|   |     | 3.2.1   | Experimental Setup                                                                                 | 73  |

|   |     | 3.2.2   | Number of Cores – C                                                                                | 76  |

|   |     | 3.2.3   | L2 Sharing                                                                                         | 77  |

|   |     | 3.2.4   | L3 Sharing                                                                                         | 79  |

|   |     | 3.2.5   | Cache Size                                                                                         | 80  |

|   |     | 3.2.6   | Summary of Findings                                                                                | 82  |

|   |     | 3.2.7   | Final Remarks                                                                                      | 82  |

|   | 3.3 | Dynar   | mic Memory Management Techniques                                                                   | 83  |

|   |     | 3.3.1   | Motivation to Use CoW and NTM                                                                      | 83  |

|   |     | 3.3.2   | Copy-on-Write (CoW) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 85  |

|   |     | 3.3.3   | Non-Temporal Memory (NTM) Copying                                                                  | 87  |

|   |     | 3.3.4   | Results                                                                                            | 88  |

|   |     | 3.3.5   | Final Remarks                                                                                      | 94  |

|   | 3.4 | Concl   | usion                                                                                              | 95  |

| 4 | NM  | [4SMF   | P: Notifying Memories for Symmetric Shared-Memory Multi-                                           | -   |

|   |     | cessors |                                                                                                    | 97  |

|   | 4.1 | Overv   | riew of the Proposal                                                                               | 97  |

|   | 4.2 | Notify  | ving Memory for SMP (NM4SMP)                                                                       | 99  |

|   |     | 4.2.1   | NM4SMP Library                                                                                     | 99  |

|   |     | 4.2.2   | NM4SMP Middleware                                                                                  | 100 |

|   |     | 4.2.3   | NM4SMP Hardware                                                                                    | 102 |

|   |     | 4.2.4   | NM4SMP Workflow                                                                                    | 104 |

|   | 4.3 | Notify  | ving Memory Framework for PiSDF Dataflow Applications                                              | 107 |

|   |     | 4.3.1   | SPiDER's Runtime Management Layer                                                                  | 109 |

|   | 4.4 | Result  | ts                                                                                                 | 110 |

|   |     | 4.4.1   | Experimental Setup                                                                                 | 110 |

|   |     | 4.4.2   | SDF Applications Without RML                                                                       | 112 |

|   |     | 4.4.3   | Applications With RML                                                                              | 119 |

|   |     | 4.4.4   | NM4SMP Hardware Complexity                                                                         | 121 |

|   | 4.5 | Final   | Remarks                                                                                            | 123 |

| Conclusion and Perspectives | 127 |

|-----------------------------|-----|

| Bibliography                | 131 |

# LIST OF FIGURES

| 1   | Example of the architecture of a typical SMP $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                   | 14 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2   | Pyramid of memory hierarchy                                                                                                                       | 15 |

| 3   | Example of a simple application parallelized for N cores                                                                                          | 19 |

| 4   | Illustration of cache coherency overhead related to synchronization of com-                                                                       |    |

|     | $munication \ldots \ldots$ | 22 |

| 5   | Communication synchronization impact in a data<br>flow application                                                                                | 23 |

| 6   | Cache coherency overhead in the synthetic data<br>flow application                                                                                | 24 |

| 7   | Dataflow application mapped on SMP. (a) With software semaphore syn-                                                                              |    |

|     | chronization. (b) With NM4SMP synchronization                                                                                                     | 25 |

| 1.1 | Reference multi-core with symmetric processing (SMP) assumed in this work.                                                                        | 30 |

| 1.2 | simulator evaluation $\ldots \ldots \ldots$            | 56 |

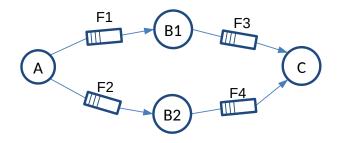

| 2.1 | Dataflow graph                                                                                                                                    | 60 |

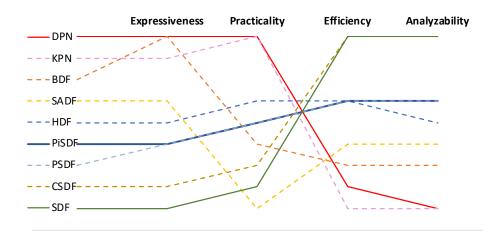

| 2.2 | Comparison of different dataflow MoCs [148]                                                                                                       | 61 |

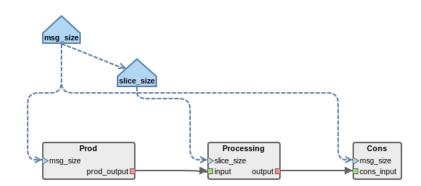

| 2.3 | SDF Dataflow graph of simple producer-consumer application                                                                                        | 63 |

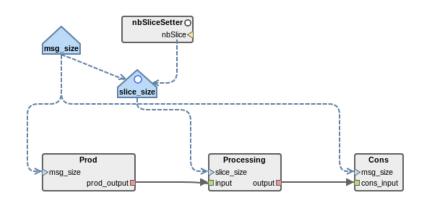

| 2.4 | PiSDF Dataflow graph of Synthetic producer-consumer application                                                                                   | 64 |

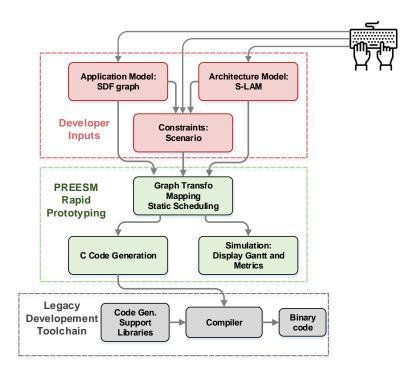

| 2.5 | Detailed overview of PREESM framework                                                                                                             | 65 |

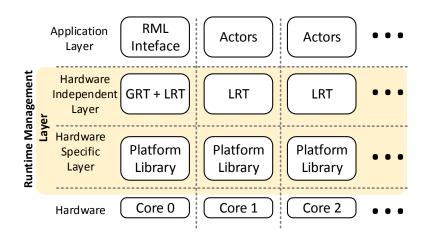

| 2.6 | SPiDER infrastructure as a Runtime Management Layer                                                                                               | 67 |

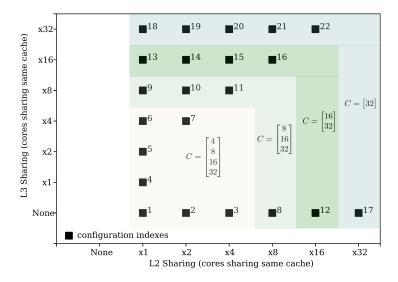

| 3.1 | Architecture overview of the baseline multi-core model                                                                                            | 72 |

| 3.2 | Overview of the reasoning behind the 22 cache configurations adopted in                                                                           |    |

|     | the experiments. $\mathbf{C}=$ number of cores simulated for each configuration                                                                   | 74 |

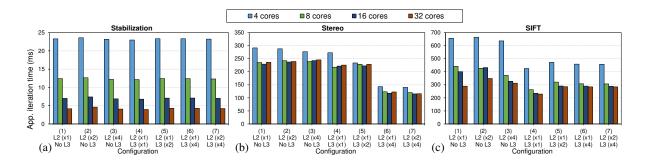

| 3.3 | Application iteration time over different number of cores for three applica-                                                                      |    |

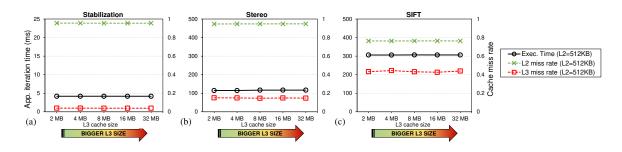

|     | tions: (a) Stabilization, (b) Stereo, (c) SIFT                                                                                                    | 77 |

| 3.4 | L2 sharing evaluation for three applications. (a) Stabilization, (b) Stereo,                                                                      |    |

|     | (c) SIFT                                                                                                                                          | 78 |

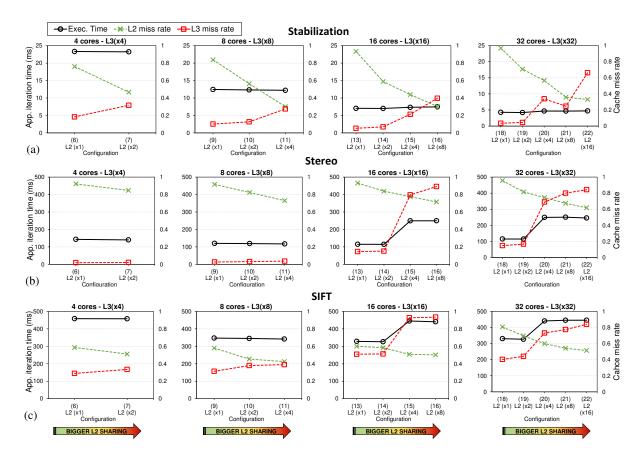

| 3.5 | L3 sharing evaluation for three applications. (a) Stabilization, (b) Stereo,                                                                      |    |

|     | (c) SIFT                                                                                                                                          | 80 |

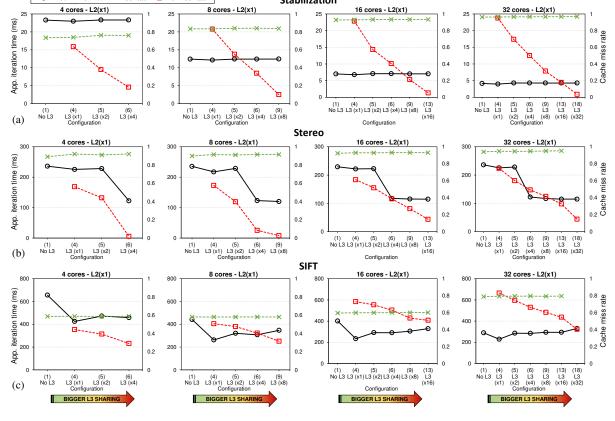

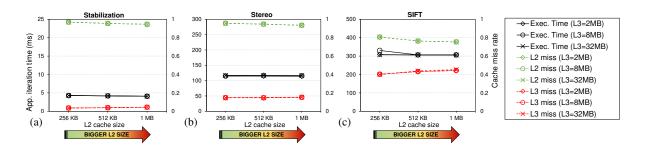

| 3.6   | L2 cache size comparison varying L2 size over multiples L3 sizes. (a) Sta-            |       |

|-------|---------------------------------------------------------------------------------------|-------|

|       | bilization, (b) Stereo, (c) SIFT                                                      | . 81  |

| 3.7   | L3 cache size comparison varying L3 size with an L2 private of 512KB. (a)             |       |

|       | Stabilization, (b) Stereo, (c) SIFT.                                                  | . 81  |

| 3.8   | Communication overview among actors of a dataflow-based fork-join ap-                 |       |

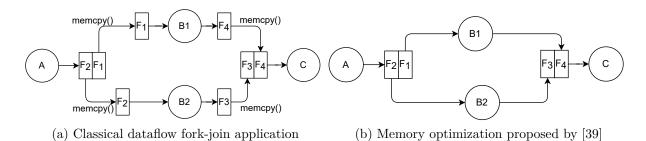

|       | plication.                                                                            | . 84  |

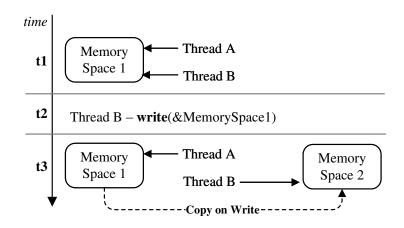

| 3.9   | Principle of the Copy-on-Write (CoW) mechanism.                                       | . 86  |

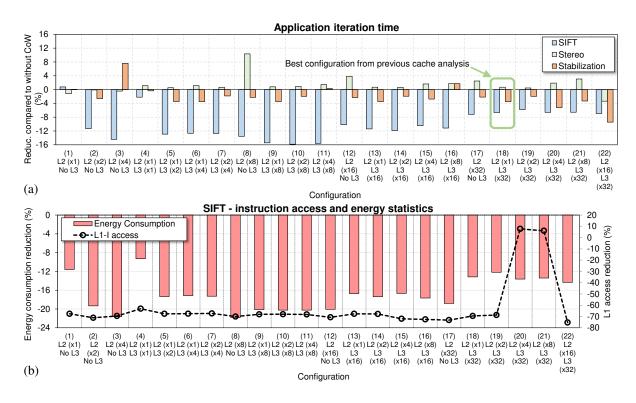

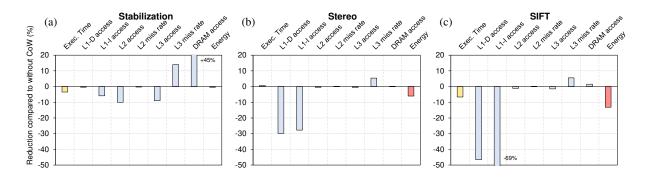

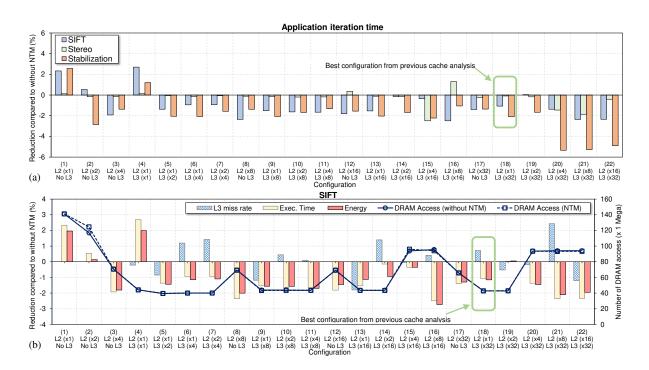

| 3.10  | Results using CoW. (a) Execution time evaluation. (b) Energy evaluation.              | 92    |

| 3.11  | Results for configuration 18 using CoW. (a) Stabilization. (b) Stereo. (c)            |       |

|       | SIFT                                                                                  | . 93  |

| 3.12  | Results using NTM. (a) Evaluation of execution time. (b) Detailed evalu-              |       |

|       | ation for SIFT application                                                            | . 94  |

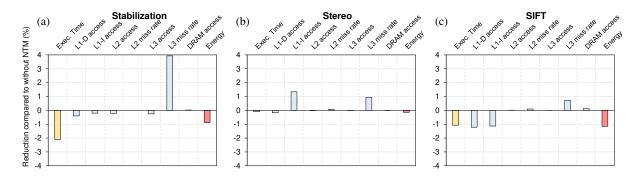

| 3.13  | Results for configuration 18 using NTM. (a) Stabilization. (b) Stereo. (c)            |       |

|       | SIFT                                                                                  | . 95  |

| 4 1   | (a) CDM (41) NM4CMD 1 and (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                     |       |

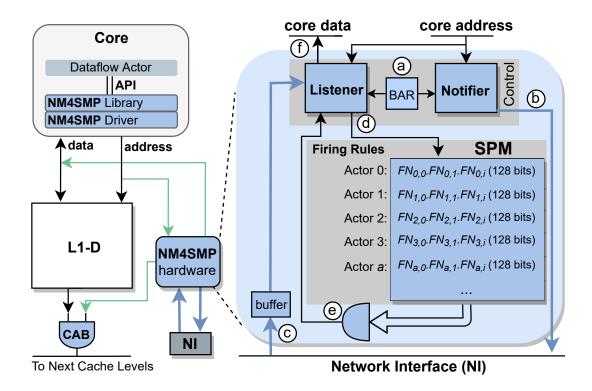

| 4.1   | (a) SPM with NM4SMP hardware module. (b) Overview of the proposed                     | 0.0   |

| 4.0   | NM4SMP mechanism.                                                                     | . 98  |

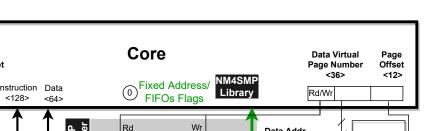

| 4.2   | Overview of NM4SMP software/hardware: new components are highlighted                  | 00    |

| 4.9   | in blue. <b>BAR</b> =Base Address Register. <b>SPM</b> =Scratchpad Memory             | . 99  |

| 4.3   | A more detailed view of the NM4SMP hardware. The coloring highlights                  | 101   |

| 4 4   | the components of the design                                                          | . 101 |

| 4.4   | (a) Array of mapping information. (b) Flow of updating SPM by capturing               | 109   |

| 4 5   | the Write and sending Notification.                                                   |       |

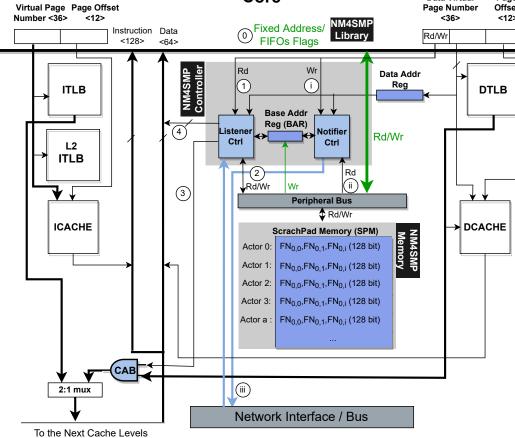

| 4.5   | NM4SMP Finite State Machines (FSM)                                                    | . 105 |

| 4.6   | Flowchart of the proposed framework to integrate NM4SMP co-design in                  | 107   |

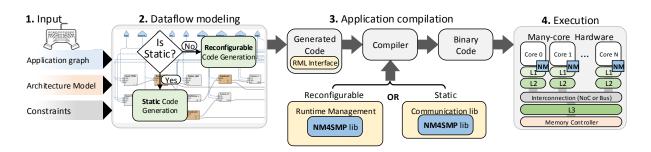

| 4 7   | the process of dataflow modeling, compilation, and execution.                         | . 107 |

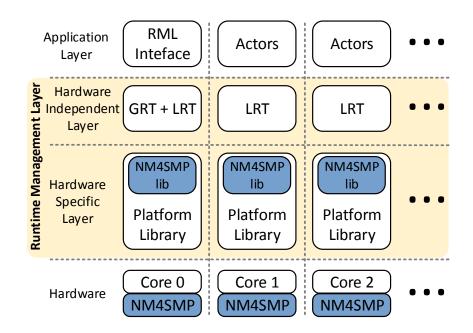

| 4.7   | SPiDER Runtime Management Layer (RML) structure. The blue rectan-                     | 100   |

| 4.0   | gles are new modules added in this work.                                              |       |

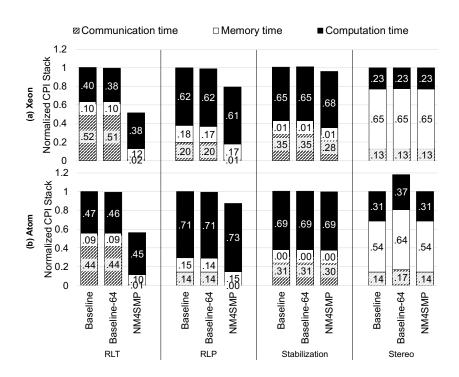

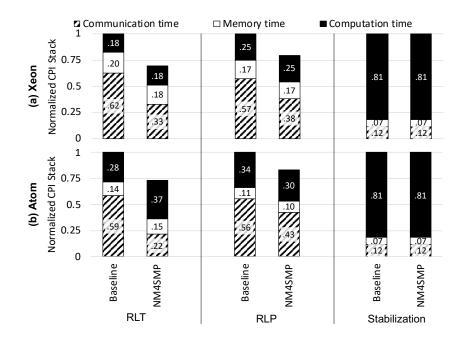

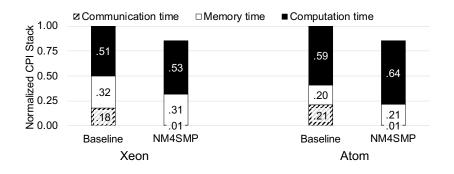

| 4.8   | Normalized CPI stack of static dataflow benchmarks for Xeon and Atom.                 | . 113 |

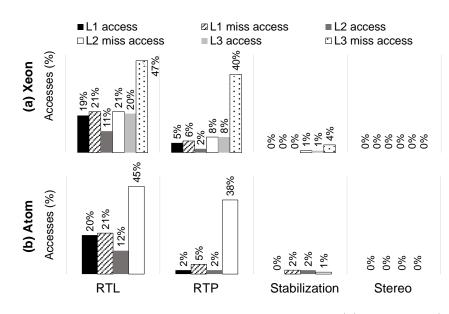

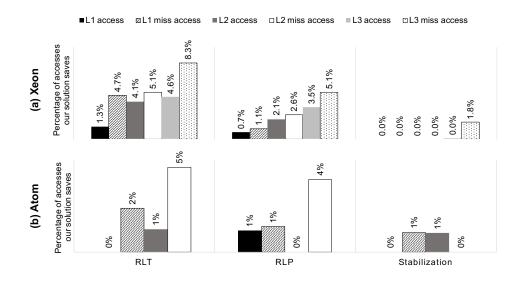

| 4.9   | Cache access reduction using NM4SMP for Xeon (a) and Atom (b) proces-                 | 110   |

| 4.10  | sors. $\dots$ | . 116 |

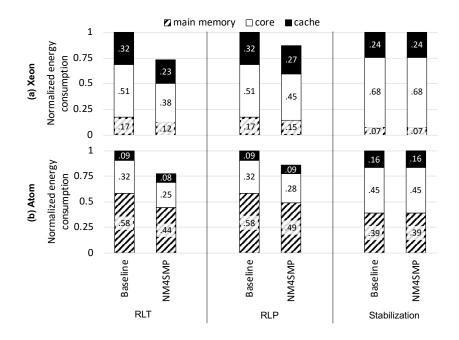

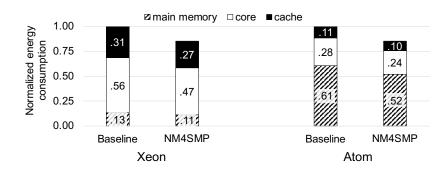

| 4.10  | Normalized energy consumption stack for Xeon (a) and for Atom (b) pro-                | 11 🖛  |

| 1 1 1 | cessors.                                                                              |       |

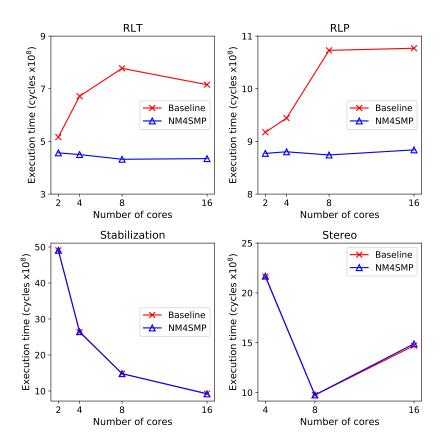

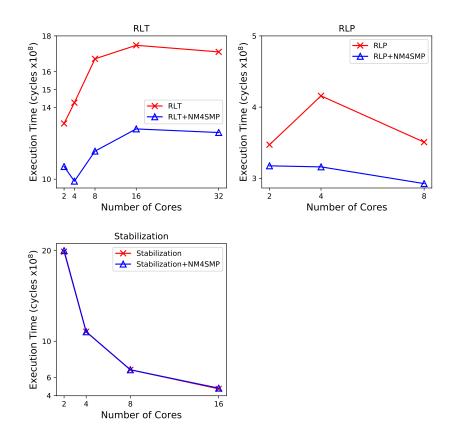

|       | Scalability of the static applications.                                               |       |

| 4.12  | CPI stack of the static application managed by RML                                    | . 120 |

| 4.13 | Cache access reduction for static application managed by Spider $\ldots$ $\ldots$ 1 | 121 |

|------|-------------------------------------------------------------------------------------|-----|

| 4.14 | Normalized Energy stack of the static application managed by RML 1                  | 122 |

| 4.15 | Scalability of the static application managed by RML                                | 123 |

| 4.16 | Normalized CPI stack of Sobel for Xeon and Atom                                     | 124 |

| 4.17 | Normalized energy stack of Sobel for Xeon and Atom                                  | 124 |

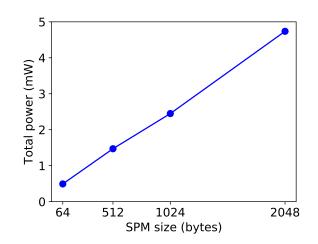

| 4.18 | Total power (static + dynamic) of NM4SMP module according to different              |     |

|      | Scratch Pad Memory (SPM) sizes                                                      | 125 |

# LIST OF TABLES

| 1.1 | Related works addressing data synchronization for parallel applications                     | 41  |

|-----|---------------------------------------------------------------------------------------------|-----|

| 1.2 | Overview of recent CPU simulators and their main characteristics $\ . \ . \ .$              | 52  |

| 2.1 | Related works studying the cache impact in parallel applications                            | 68  |

| 3.1 | Experimental setup: Hardware model settings                                                 | 74  |

| 3.2 | Experimental setup: Dataflow applications benchmark profile                                 | 75  |

| 3.3 | Core change for supporting the CoW mechanism, assuming: (1) $src_buffer$                    |     |

|     | is the source buffer, $(2) dst_buffer$ is the destination buffer, $(3) copy_length$         |     |

|     | is the copy length, (4) shm_open_fd is a file descriptor created with the                   |     |

|     | shm_open system call.                                                                       | 86  |

| 3.4 | Core change for supporting the NTM mechanism, assuming: (1) $src_buffer$                    |     |

|     | is the source buffer, dst_buffer is the destination buffer, copy_length is                  |     |

|     | the copy length.                                                                            | 87  |

| 3.5 | Memcpy profile addressed in CoW and NTM                                                     | 91  |

| 4.1 | Benchmark setup. RLT / RLP: Reinforcement Learning Training / Pre-                          |     |

|     | diction phases. $\mathbf{SDF}$ : Synchronous Dataflow. $\mathbf{PiSDF}$ : Parametererizable |     |

|     | Dataflow                                                                                    | 111 |

| 4.2 | Hardware simulation settings.                                                               | 112 |

| 4.3 | Performance and synchronization metrics.                                                    | 114 |

|     |                                                                                             |     |

## INTRODUCTION

The performances of uni-core processors have been constantly improving for decades owing to Instruction-Level Parallelism (ILP) and rising hardware clock frequencies. However, the performance of large single-core processors no longer scales since only a limited amount of parallelism can be achieved by employing conventional superscalar instruction techniques in a typical instruction stream [32, 85]. Moreover, elevating the clock speed on today's processors is limited by the power dissipation, which indicates the failure of Dennard scaling [25]. This power dissipation becomes prohibitive in all, but water-cooled systems [104]. Considering these problems and the large number of transistors available on today's microprocessor chip [99], a large and complex uni-core processor was too costly to design and debug, so this design trend was unsustainable. However, higher performance is still demanded, as manifested by predictions from the ITRS Roadmap 2011 [66], forecasting a need for 300x more performance by 2022. To avoid complex, unmanageable, and power-hungry designs while pushing for more performance, the chip designers have shifted to a new processor design paradigm: multi-core processors. Multi-core processors are highperformance computer systems built up by embedding several processing units as cores in the same processor, which communicate through an interconnection NoC (Network on Chip) or bus [44, 104].

The main advantage of multi-core systems is that they provide high-performance, adding more parallel resources (cores) rather than increasing clock frequency while maintaining the power characteristics [24]. Multi-core processors provide task-level rather than instruction-level parallelism. It means the application workload can be divided into parallel tasks that can run concurrently on the different cores while providing a faster execution of the application. As the complexity and variety of the applications have increased, the requirement for more performance and general-purpose programmability has grown. Hence, general-purpose multi-core processors have broadly been adopted in all industry segments, including digital signal processing and embedded systems, and are no longer restricted to the High Performance Computing (HPC) industry. Unfortunately, the performances of the applications do not scale automatically as newer processors 'architectures, pro-

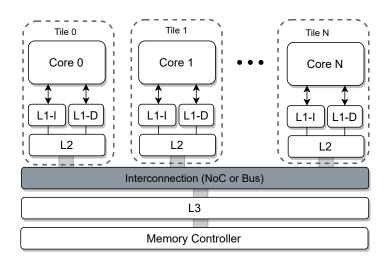

Figure 1 – Example of the architecture of a typical SMP. In this example, each core has a private L1 cache for instruction and a private L1 cache for data, a private L2 cache for both instructions and data. All the cores share the same L3 cache. The memory controller interfaces with the off-chip main memory.

gramming methods should evolve from a sequential to a parallel design approach. In a parallel program, the programmer, by dividing the application's code into tasks, expresses task-level parallelism (TLP), which can explicitly exploit the parallel hardware processing units of multi-core processors executing concurrently [105].

### Symmetric Shared-memory Multiprocessor (SMP)

Symmetric Shared-memory Multiprocessor (SMP) is an extensively used high-performance multi-core processor architecture as it helps the programmer to simplify the transformation from sequential to parallel programs, by preserving a single image of memory shared across the entire parallel cores. Using a global virtual address space minimizes the changes from a single processor machine to an SMP [131]. In this context, an application is composed of multiple threads that can run in parallel, TLP standing conveniently also for Thread-Level Parallelism.

A typical SMP includes several cores/processors all interconnected with a common shared main memory via an interconnection network (e.g., NoC or a bus). Figure 1 shows the architecture of a typical SMP. Due to technological limitations, the main memory and the cores are not in the same chip. Ideally, the two chips follow the same pace. Unfortunately, the disparity between the speed of processor cores and off-chip memory can be

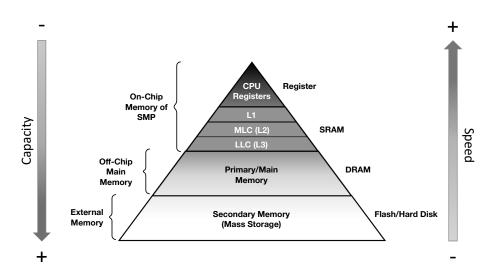

Figure 2 – Pyramid of memory hierarchy.

in the order of hundreds of cycles. The performances are limited by the memory latency. This is called the memory wall [94, 121, 145]. To circumvent this limitation, microprocessors, in general, and SMPs, in particular, use hardware-managed on-chip storage, called caches, to keep data within the chip to avoid such long accesses to the off-chip memory. The larger the cache, the lower the speed. Thus, typically, caches have been implemented in a hierarchical manner. Smaller and faster caches are close to the microprocessor while they are backed by two or three levels of larger caches. Frequently requested data is stored and accessed from a high-bandwidth and low latency cache which is usually a private local Level-1 (L1) cache of each processor core in the SMP. The lower levels of the caches (L2 and L3) are shared between the cores. Figure 1 shows an organisation where the L2 cache is private to each core, and the L3 cache is shared. The shared caches are slower both due to the size and the extra interconnection that is necessary to connect them to multiple cores, which also limits the bandwidth for sharing the data. This hierarchy of hardware-managed caches that are completely transparent to the developer is the key enabler of the illusion to access to a large and fast off-chip main memory.

The full memory hierarchy, from the registers of the processor to the hard-disk drive or the cloud, is usually represented in the form of a pyramid, with high speed but low capacity (and expensive) memory at the top, and low speed with high capacity (and cheap) memory at the bottom. Figure 2 presents the pyramid of memory hierarchy.

Caches exploit two forms of locality in the data accesses: temporal and spatial. Temporal locality means that when a memory location is accessed, it will be accessed in the near future again. Spatial locality refers to the property that when a location is accessed, the addresses in its vicinity will also be accessed in the near future. Exploiting these properties, the caches bring a block (e.g., 32 consecutive words) from memory and store it when a single location is accessed. Because of the temporal locality of the accesses, when the same location is accessed again, it is already present in the caches (called a hit), and the long latency access to the off-chip memory is not necessary. Since a block is fetched and stored, accesses to the neighboring locations will also be hit in the cache avoiding access to the main memory. By exploiting spatial and temporal locality, caches reduce the effective latency of loads and stores. But the threads running on the cores of the SMP also can change concurrently the values in the caches instead of waiting for the modification to get published to the main memory. This poses a challenge when the data is shared between the threads running on different cores. A thread that is reading a value from its local cache may not see the writes done to the same location by another thread that modified the value of the same address in its own local cache. To keep the values coherent across these threads, a cache coherence protocol is needed.

A cache-coherent parallel processor (e.g., an SMP) must provide the following guarantees. Changes to the shared data, even when cached, shall become visible to all the threads on all the cores within a bounded (and typically short period of) time. This guarantee is achieved through a cache coherence protocol that, in almost all modern machines, is implemented using an invalidation-based mechanism. Such protocols, which are typically implemented in the cache controllers, maintains the invariant that there is at most one writable copy of any given cache block in the system. When the writable copy exists in one of the caches, there are no other valid copies in the other caches. Cache coherency and its algorithms has and are still being studied extensively in the literature [129]. Most protocols inherit from the original four-state protocol devised by Goodman [53]: each cache block is either (1) invalid, (2) shared (read-only), (3) exclusive (written exactly once, and up-to-date in memory), or (4) modified (written more than once, and needs to update the memory). To maintain the aforementioned at-most-one-writable-copy invariant, the coherence protocol needs to invalidate (evict) any shared block in other cores' caches before updating it with a new value. When the caches are connected through a bus, invalidation is straightforward and is performed through a broadcast message. When the caches are connected through a network-on-chip or point-to-point connection, the coherence protocol typically maintains a form of directory that locates all other copies of a shared block. The invalidation principle causes the accesses to the data to miss in the cache due to the coherence protocol. Coherence protocol can cause loads and stores to miss in the cache since another core invalidates a previously cached block. Without code restructuring and a proper mapping of the threads on the cores, coherence misses are inevitable when some threads on a core writes and others on other cores read the same cache block in a small time window. To achieve high-performance execution for parallel programs, the threads need to exhibit thread locality in addition to temporal and spatial locality. Thread locality is referred to the property that modification to data in one thread is isolated from another thread at a given time. Thread locality reduces the aforementioned coherence cache misses that are due to shared data modifications and dependencies. Coherence can be managed by software or hardware mechanisms. In this thesis, we consider hardware-based coherence mechanisms.

Besides coherence and its considerations, caches need also to guarantee that accesses to some location will be visible in some form of consistent order to all the threads. Unlike coherence, the memory consistency model is exposed to the software and needs to be considered during execution. The memory consistency model is the degree to which accesses to the memory can or cannot be assumed to be published in a particular order. On a single-core machine, it is relatively straightforward to ensure that instructions, in general, and loads/stores, in particular, appear to complete in the program order. Ideally, it is desirable to ensure a similar consistent order on a parallel machine (e.g., an SMP) such that memory accesses, system-wide, would appear to constitute an interleaving of the completion order of the accesses on different cores. However, this sort of sequential consistency imposes significant performance overheads [77]. Therefore, the majority of the real-world systems implement a relatively more relaxed memory consistency model that can potentially exhibit inconsistency. That is to say, memory accesses by different threads, or to different locations by the same thread, may seem "out of order" from the perspective of threads that are running on the other cores. To this end, it is to the programmer or the compiler to ensure a specific order by means of synchronization. This is accomplished by using a set of special instructions that are more strongly ordered compared to other "ordinary" instructions as they force the core to temporally stop the execution and wait until the previous instructions are completed. These instructions are an essential part of synchronization algorithms on any non-sequentially consistent machine.

Execution on an SMP requires breaking up the code into multiple parallel threads that compute on shared data in the memory. Sharing data is how the threads communicate and satisfy their data dependencies. A producer thread writes to a shared location in

#### Introduction

the memory where the dependent consumer thread can read the necessary data from. Hence, the order of writes and reads is a crucial constraint for the correct computation of data of a multi-threaded programs on SMPs. A reader may access to the (old and wrong) value before the writer effectively commits the new value, this is called a race condition. As such, threads need to *synchronize* before accessing the shared data to avoid race conditions that lead to incorrect results. Such a data that needs to be protected is called a critical resource. Synchronization techniques usually require serializing the execution of parallel threads to impose the necessary order. From an abstract and fundamental point of view, only one thread is allowed to write or read to a critical resource. From the software's perspective, the region of the thread code that accesses the critical resource is called critical section. The memory accesses to these critical sections need to be synchronized to ensure the correct data exchange between dependent threads. At a high level, a thread is said to *lock* the critical section and exclusively enters it to finish its writes or reads before any other thread. At the hardware level [108], Atomic Memory Operation (AMO) is the ultimate operation for the software-based lock algorithms that enables the threads to mutually exclusively enter the critical section and consistently share data. Software semaphore is an example of software-based synchronization primitive to control access of multiple threads to the shared critical data. In semaphore synchronization technique, threads utilize two functions to modify the semaphore value wait() and signal(), but the functions allow only one thread to change the value at a specific time, i.e., two threads cannot simultaneously change the semaphore value. There are two types of semaphores; counting semaphores and binary semaphores.

The mutually exclusive execution inherently leads to the serialization of threads which in turn looses all the benefits of parallel execution. In addition, the necessity and prevalence of caches in the SMPs exacerbates the overheads since locking and synchronization highly involve the coherence protocol in the cache subsystem. Indeed, preserving consistency and coherency of the lock values is mandatory and requires cache coherency protocol messages [128, 141]. For instance, when a thread running on one of the cores in the SMP, is accessing the shared data, the cache coherency protocol needs to invalidate the data in the caches of the other cores. This is just an instance of the significant number of coherency messages that need to be exchanged between the caches to allow the threads to enter the critical section one by one. This coherency procedure (a.k.a., True sharing [136]) imposes performance overhead that could cost more than one hundred cycles [141]. As the number of cores/communication pairs increases on a chip, cache line ping-pong resulting

Figure 3 – Example of a simple application parallelized for N cores.

from true sharing can prevent proportional performance scaling, although the hardware provides more resources and processing cores.

## Dataflow Model of Computation (MoC)

The general availability of SMPs, ranging from HPC to embedded systems, gives the motivation to explore and enable their benefits for the Dataflow Model of Computation (MoC) [26, 71]. A Model of Computation (MoC) [122] is a high-level representation that enables expressing the specification of a complex application independently from the details of software and hardware implementation. Dataflow is a model of computation used across various domains, including Digital Signal Processing (DSP), video coding, multimedia, telecommunication, computer vision, machine learning, etc. In dataflow, applications are modeled by a graph composed of nodes representing the actors communicating through FIFOs modeled as edges. Each actor implements well-defined actions (functions), consuming input data, processing this data, and producing output data. Each edge is implemented by a FIFO connecting a producer actor output to a consumer actor input. Figure 3 represents an example of a dataflow graph of a producer-consumer application. In this application, *Producer* actor generates and writes data into output FIFOs, which are shared with the actors of  $Process_1$  to  $Process_N$ . Actors  $Process_1$  to  $Process_N$ , reading this data and after processing, write into the output, FIFO shared with the *consumer* actor.

The following features make the dataflow a good candidate to model parallel workloads [26]:

- 1. *Well-defined communicating interface*: each FIFO can have only one producer and one consumer.

- 2. Firing rules: a set of rules that define when the actor can execute (fire) an action.

In its simplest form, e.g. Synchronous Data Flow (SDF), the actor can start its execution only when all its inputs are available in its respective input FIFOs. The theoretical model considers unbounded FIFOs, which is not possible from a physical implementation point of view. Thus, another rule is that there is enough space in the output FIFOs. These firing rules are explicitly specified in the application. In the context of an SMP, having explicitly these firing rules offers the opportunity to improve the synchronisation of the threads and this is what we show in this thesis.

3. *Non-preemptive processing*: Once the processing part starts, the actor cannot be preempted. From a synchronous point of view, the outputs are instantly produced, whatever the execution time of the action.

From a dataflow specification, code is generated in a given programming language according to the hardware platform. In this thesis, we are interested in multi-threaded C language applications executed on an SMP.

Dataflow applications can potentially lend themselves to expose a fine granularity of parallelism. However, the same feature can directly contribute to increasing data communication and a higher degree of synchronization over shared data (FIFOs) and hence, stress the memory hierarchy when mapped on an SMP by imposing extra data traffic due to coherency. This behavior is specifically studied in this thesis and synchronization in multi-threaded execution of dataflow applications over SMPs is further discussed in the following chapters. Dataflow applications can leverage SMPs, which are prevalent platforms, for their faster execution. On the one hand, dataflow applications mainly rely on producer-consumer data exchange that is simpler than the general form of data sharing in other types of applications. On the other hand, the degree of sharing can be much finer in the dataflow model, leading to data access contention by requiring synchronization at a fine granularity. The Dataflow MoC can break the application to expose a high degree of Task Level Parallelism (TLP) and allow the application developer to exploit the parallel hardware resources more effectively in multi-core SMPs through well-defined producerconsumer communications. This finer granularity of TLP is a double-edged sword. While it enables using a significantly higher number of cores in the SMP, it also requires more synchronizations across many more parallel threads. That is, the synchronization curtails the scalability.

Although frameworks for dataflow applications have been proposed in recent years, they have not fully studied this challenge as the presence of the cache hierarchy in the target architecture is not considered. Thus the optimization methods they provide for memory management and communication are not well-tailored (well-adapted) to cache hierarchy. The effects of running dataflow application on SMP is not completely explored in the literature. Additionally the current state-of-the-art synchronization methods available on SMP machines, by design, are not suited to the dataflow MoC since they are not aware of the dataflow behavior. Studying these effects and proposing efficient synchronisation mechanisms dedicated to dataflow applications is the main motivation of the work described in this thesis.

### Motivation

This motivation is described in more details through the example of a simple dataflow application running on a baseline SMP. As discussed earlier, in a dataflow application, the actors communicate by exchanging the data tokens through FIFOs. Actors wait for the availability of data tokens on their inputs to start execution (checking firing rules). A dataflow framework, responsible for the generation of the code of the application, uses a communication interface to handle the communication between actors.

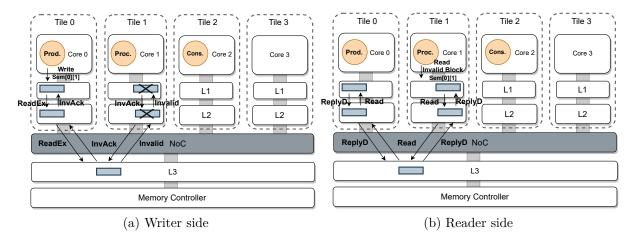

In a scenario where a dataflow application is running on an SMP, the FIFOs are placed in shared-memory as shared data among the actors, and a synchronization method like semaphore is used as the communication interface to synchronize the actors. When the actors are mapped on different cores, multiple threads access these FIFOs as critical resources. After processing the data and writing them into the FIFO, the producer actor "ups" the semaphore to inform the consumer that the data is ready. On the other side, the consumer actor is waiting for data to be ready then starts execution, so in order to check data availability (checking firing rules), it reads the semaphore state. This synchronization mechanism stresses the memory hierarchy and triggers the cache coherency protocol, resulting in performance overhead. An example helps to discuss this overhead better. Let's consider the example presented in Figure 3, with processing actors executing in parallel on SMP illustrated in Figure 4. Figure 4 illustrates the cache coherency overhead of synchronization of this synthetic application. We assume that the *Producer*, *Processing*, and Consumer actors are mapped on  $core_0$ ,  $core_1$  and  $core_2$  respectively. In order to synchronize between the actors, a semaphore is dedicated. For this scenario, we have a two-dimension array of semaphores in which each element of this array is dedicated to one synchronization between a source core and destination core of the data exchange (e.g., semaphore[sourceID][destinationID]). After  $core_0$  finishes execution of *Producer*, it sets

Figure 4 – Illustration of cache coherency overhead related to synchronization of communication

the value of the semaphore[0][1] (releasing the lock). As shown in the Figure 4 (a),  $core_0$  by writing into the related cache block of the semaphore[0][1] switches the state of this block to Modified which is done by sending the ReadEx request coherency message [128]. Following this message, the coherency directory residing in L3 sends the invalid request message to the caches containing this cache block as shared data; here the L1 and L2 caches of  $core_1$ . The caches respond to the invalid request message with an acknowledge message. When  $core_1$  wants to check the availability of the data produced by  $core_0$  in its input FIFO, it reads the lock, semaphore[0][1] value. Figure 4 (b) shows this procedure when  $core_1$  reads the cache block containing semaphore[0][1] value which is invalidated due to write procedure performed by  $core_0$  and, hence encounters a read miss. This read access results in sending read messages down to the coherency directory of L3, which triggers the procedure of updating the cache block with new data of  $core_0$  L1 (ReplyD message [128]). Recall that this coherency procedure could cost more than one hundred cycles [141].

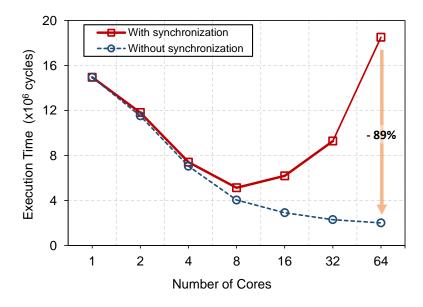

In our simple application, by breaking the *Processing* actor into multiple smaller actors with lighter workload executing concurrently, we achieve a finer-grained parallelism in the application as depicted in Figure 3. This representation of the application can exploit the parallel hardware resources in SMP in a more efficient way and can reach higher performance. The total execution time of the synthetic application with n number of *Processing* actors can be defined as follows:

Figure 5 – Communication synchronization impact in a dataflow application.

$$T_{total\ execution\ time} = T_{serial} + T_{parallel}(n) + T_{synchronization}(n) \tag{1}$$

Where:

$$T_{serial} = T_{Producer} + T_{Consumer}$$

$$T_{parallel}(n) = T_{sequential}/n$$

$$T_{synchronization}(n) = T_{Producer->Processing}(n) + T_{Processing->Consumer}(n)$$

The execution time of parallel part of application  $(T_{parallel}(n))$  has an inverse relation with the number of threads (n).

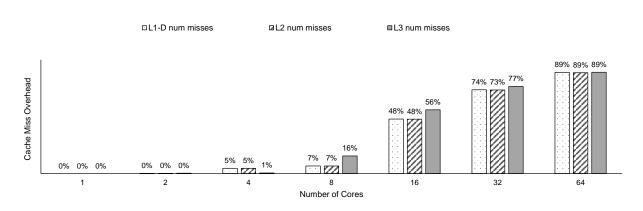

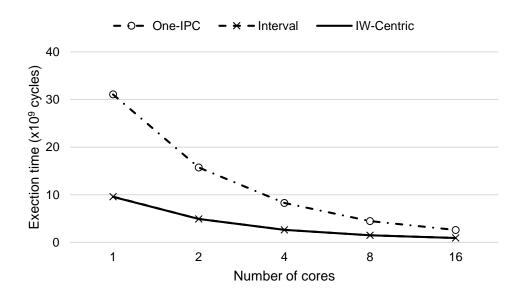

Meanwhile, synchronization time of the application has a direct relation with the number of threads. To study the speedup of our application, we run it on an SMP with a varying number of cores, from 1 to 64 cores. Figure 5 shows the result of execution time quantifying the synchronization overhead for our simple dataflow application of Figure 3. Each actor runs in a different core in a dedicated thread. The parallel actors (1 to N in case of Figure 3) are replicated, dividing the same amount of work according to the available number of cores. The figure has two plots, one considers the synchronization overhead, and the another has such overhead deducted from the application execution time. It is possible to observe that the synchronization penalties increase according to the number of cores, representing up to 89% of the application execution time in a scenario with 64 cores.

As explained above, semaphore synchronization causes cache coherency overhead which

#### Introduction

Figure 6 – Cache coherency overhead in the synthetic dataflow application.

decreases the performance. In other words, by increasing the number of cores, cache coherency protocol is more frequently triggered because more synchronization is required. Figure 6 shows the fraction of cache misses caused by semaphore mechanism using the same setup of Figure 5. As the number of cores increases, the overhead of cache misses caused by semaphore also increases.

In summary, the high level of parallelism in dataflow applications helps to efficiently exploit the parallel processors available in an SMP but, as highlighted by the example, the actors' communication imposes significant traffic to the cache hierarchy of SMP because of synchronization. This problem of dataflow applications in SMP systems, which is not properly studied in the literature, is the primary motivation behind our study in this thesis.

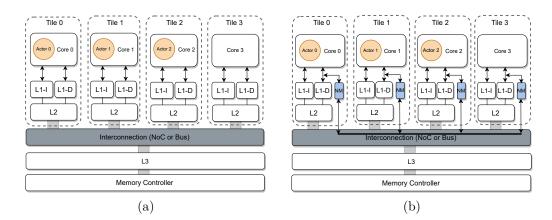

The main idea of our proposed technique for synchronization is illustrated in Figure 7. The scenario in Figure 7(a), is depicting a given dataflow application mapped on SMP where the actors are communicating via shared FIFOs based on a typical software synchronization mechanism such as the semaphore provided by the POSIX library. On the right-hand side, Figure 7(b) shows a dataflow-aware hardware logic implemented near the Level-1 (L1) cache which reduces the synchronization time and hence, leads to speed up the communication among the actors in the dataflow application. The proposed logic plays two dedicated roles, one on the producer side and another on consumer side, to handle the synchronization related to data communication in the FIFOs. On the producer side, after the data is written to the FIFO, the logic issues a message as notification to the core that holds the consumer actor. On the consumer side, the module collects all the messages from the producers as a firing rule to inform the waiting consumer actor as soon as its related firing rule is satisfied. The proposed module provides to the cores more than

Figure 7 – Dataflow application mapped on SMP. (a) With software semaphore synchronization. (b) With NM4SMP synchronization

a pure synchronization by also taking in charge the check of the firing rule. Employing this mechanism avoids the cache coherency traffic resulted from semaphore synchronization. This thesis focuses on developing the logic presented in Figure 7(b). The full stack of the implementation is presented in chapter 4, from software down to hardware level, implemented in a standard baseline SMP architecture. In this stack, a communication interface that uses the proposed synchronization solution is implemented at the software level that employs a driver of the OS level to connect to the hardware logic. In brief, this contribution helps in making the SMP dataflow-friendly.

### Thesis Organization

The two main contributions of this thesis are presented in two different chapters and are summarized as follows.

1. Cache evaluation and memory management techniques: This first contribution contains two parts. At first we perform a comprehensive study of the behavior of dataflow applications on SMP from a cache hierarchy point of view. This kind of in-depth study was missing in the literature. A generally accepted idea is that bigger and multi-level caches improve the performance of applications. This work evaluates such a hypothesis in a broad experiment campaign adopting different multi-core configurations related to the number of cores and cache parameters (size, sharing, controllers). The results show that bigger is not always better, and the foreseen future of more cores and bigger caches do not guarantee software-free better performance for dataflow applications. Secondly, the memory management optimization methods employed by the current frameworks do not generally exploit the cache hierarchy of the shared-memory multiprocessors efficiently for dataflow applications. For instance, PREESM framework uses exclusively memcpy() for *Broadcast* actors which results in the eviction of useful data in the cache. This is known as cache thrashing. In this thesis, we investigate the adoption of two existing memory management strategies for dataflow applications: Copy-on-Write (CoW) and Non-Temporal Memory (NTM). These techniques allow to bypass the cache hierarchy and reduce the cache thrashing. We show through experiments that in some cases, these techniques can optimize the data movement in the cache hierarchy and improve the performance.

2. Notifying Memory for SMP (NM4SMP) for dataflow communication: The communication interface relying on software semaphores used by existing dataflow frameworks has cache coherency overhead that penalizes the performance of the application running on an SMP. In this thesis we provide a novel communication interface using a near-memory processing implementation. Our *contributions* in this section are summarized as:

- A HW/SW co-design, including library, driver, and a near-memory hardware onchip device to synchronize dataflow actors, called NM4SMP (Notifying Memory for SMP).

- A methodology to integrate the NM4SMP co-design in the process of dataflow modeling, code generation and compilation of reconfigurable and static applications.

- A detailed power and performance evaluation of static and reconfigurable dataflow applications using NM4SMP for generic and low-power processors.

The rest of this document is organized as follows:

- Chapter 1 provides detailed background on multiprocessor architectures, memory hierarchy, synchronisation and the simulator used for our experiments.

- Chapter 2 presents Dataflow MoCs and rapid prototyping tools, with an emphasis on the existing tools used for our experiments: PREESM and the SPiDER runtime management layer.

- Chapter 3 presents the first contribution of this thesis: the behavior of dataflow applications on SMP and the use of existing dynamic memory management tech-

niques.

• Chapter 4 presents the second contribution of this thesis: Notifying Memory for Shared-memory Multiprocessor (NM4SMP) for dataflow applications. We propose NM4SMP for static dataflow applications as well as reconfigurable dataflow applications that are managed by a runtime management layer. We also present the evaluation and results of our approach.

Chapter 1

# SYMMETRIC SHARED-MEMORY MULTIPROCESSOR (SMP)

This chapter provides the background required to understand the main architectural and related synchronization concepts addressed in this thesis. It is divided in four sections. The first one discusses shared-memory processors (SMP) and delves into the various aspects of the architecture that impacts the correctness and performance of execution of applications. The second one focuses on the synchronisation mechanisms available to allow the safe sharing of data between concurrent threads. Then we come back on the main concepts related to the caches used to speed up access to potentially shared data. Finally, we explore the multicore simulators that are used to evaluate the proposed solutions in SMPs, and evaluate the simulator we utilized for our research in this thesis.

## 1.1 Symmetric Shared-memory Multiprocessor (SMP)

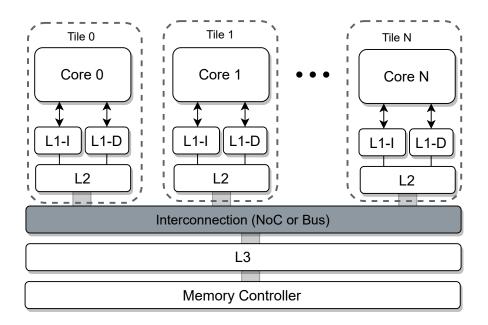

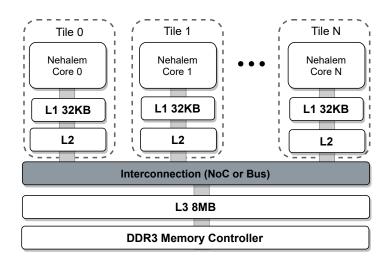

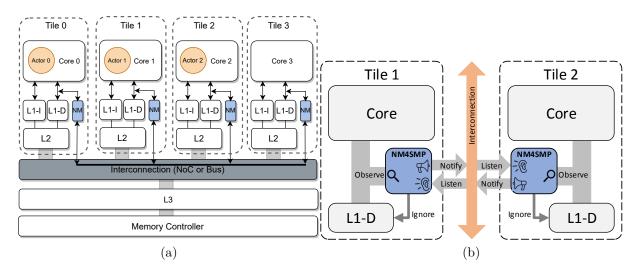

Symmetric Shared-memory Multiprocessor (SMP) is the highly dominant solution for current processor chips. SMP contains two or more processing elements (cores) sharing the same unique logical memory address space and is generally managed by one Operating System (OS) [116, 42]. An SMP architecture includes a single chip that comprises multiple cores which are connected to a physically shared main memory. Although a SMP might be designed without any cache, a commercial SMP is now built upon shared caching subsystem [116, 42]. This kind of architecture is the starting point of this thesis, and illustrated in Figure 1.1. It is composed of several tiles. The tiles are homogeneous, with the same hardware architecture. Figure 1.1 shows an example of a cache with three levels. Levels 1 and 2 are embedded inside the tile, working as private cache memories. The last-level cache (LLC), level 3, is shared by all the tiles and also interfaces with a memory controller. The memory controller interfaces with an off-chip main memory. The SMP assumes a shared memory that implements a cache-coherence protocol. Such a

Figure 1.1 – Reference multi-core with symmetric processing (SMP) assumed in this work.

cache organization is common in commercial products, it is for instance adopted in the SMP architectures used for our experiments in this thesis (Intel Xeon and Atom) [65]. Subsection 1.3 enters in details about cache mechanisms.

The tiles are interconnected by a bus or by a Network-on-Chip (NoC). A NoC is an on-chip communication infrastructure to interconnect tiles, decoupling the computation from communication. The NoC structure contains routers and wires. Routers have the function to implement the network control logic, defining the path for each exchanged packet between a source and target tile. Wires have the function to interconnect routers and to connect each router with its local tiles. While buses are typically used in multi-core with low core counts, NoCs are preferred in many-core architectures due to their benefits against the bus, as parallel communication among tiles and scalability [100, 19].

## 1.2 Synchronization for SMP

Our work focuses on providing specialized hardware mechanisms for synchronisation in dataflow applications. As such, it is related to previously proposed synchronization mechanisms that are surveyed in this section, which were (and still are) studied independently of the number of cores or the use of caches. The synchronisation issue is further exacerbated by the use of caches, and is specifically discussed in the next section. The advantage of shared-memory is that the application developer sees the memory as one, and all the cores can access all the memory locations. An important problem is to *synchronize* the shared memory accesses among different threads running in parallel. The synchronization means that threads must find an *agreement* with other threads to exclusively access to the shared data. The region of the thread program that accesses the shared data is called critical section. Critical sections are synchronized by ensuring a mutual exclusion access between the threads. The system used to protect the critical region is called a *lock*. Note that ultimately all software-based mutual exclusion lock algorithms are based on Atomic Memory Operations (AMO) at hardware level [108]. AMO means that the memory operation performed by the core is indivisible; therefore, no other entry can slip or suspend the operation involved in the AMO while the AMO was not finished.

According to the number of independent processes that compete for the same critical resource, and their frequency of access, it is possible to measure the *contention*. The contention occurs whenever one process or thread attempts to acquire a lock held by another process or thread. The finer-grained the available locks, the less likely one process/thread will request a lock held by the other. For example, locking a row rather than the entire table or locking a cell rather than the entire row will be less prone to contention.

In the next sections, we provide a comprehensive survey of studies on synchronization approaches at different abstraction levels. A lot of optimized synchronization solutions have been proposed by the researchers at software [95, 125, 36, 10, 54, 135], ISA [146, 139] and hardware level [80, 141, 46, 98, 132, 34, 47, 1, 3, 2, 81, 103, 84, 138, 149, 52, 69, 92].

### **1.2.1** Synchronization Support in Software

This section introduces the main concepts related to software synchronisation, using the example of the most adopted techniques available in the main stream OS, including Linux.

#### Spin-lock

Spin-lock is the most basic form to implement a lock. In summary, the threads perform a loop that constantly checks the value of a lock variable, shared among all cores. This checking is performed by AMO. A spin-lock is a lock which causes a thread trying to acquire it to simply wait in a loop ("spin") while repeatedly checking whether the lock

| Algorithm 1: Example of spin-lock used in RISC-V    |

|-----------------------------------------------------|

| 1 /* RISC_V spin_lock and unlock implementations */ |

| <pre>2 void spinlock(lock *lock_value){</pre>       |

| <b>3</b> bool locked;                               |

| 4 //Spin lock                                       |

| 5 do {                                              |

| $6$ locked = CAS(lock_value, 1, 0);                 |

| $7$ }while(!locked);                                |

| 8 }                                                 |

is available through Read-Modify-Write (RMW) operation [9]. Since the thread remains active but is not performing a useful task, the use of such a lock results in a busy waiting. Once acquired, spin-locks will usually be held until they are explicitly released.

Conventional designs employ either busy waiting or blocking for waiting. With busy waiting, waiting threads remain active, polling the lock until they manage to acquire it. With blocking, waiting threads release their hardware context to the OS. The OS is in charge of unblocking these "sleeping" threads when the owner releases that lock [10].

Algorithm 1 presents a function using CAS (Compare And Swap) instruction which is the basic implementation of atomic RMW lock operation, to acquire the lock in a RISC-V processor. When a thread calls this function it enters a while loop and in CAS, it compares the lock value with 1 if it is equal it means that the lock is successfully caught then swap it to 0 and returns True. If the lock value is equal to 0 it means that the lock is caught by another thread and CAS returns False so the thread should try again.

Test-and-Set (TAS), Test-and-Test-and-Set (TTAS), and ticket lock [95] (TICKET) are spinlock types in which threads spin the locks on a single memory location in busy waiting mode. Because of the simplicity of spinlocks, they are fast; however, it is a mechanism that will lead to higher degrees of contention when multiple threads are competing to acquire the lock. The main downside with spin lock is that it leads to three problems: (1) the atomic spin-lock operations such like **compare\_and\_swap** is by definition nonpreemptible, and waiting for the operation to perform degrades the performance as the number of competing processors increases; (2) In multi-threaded systems, a thread that is preempted during its critical section (meaning that it keeps the lock and no other thread can access to the shared resource) can delay every other threads that needs to acquire the lock [144]. This is typically known as the inversion of priorities. (3) It is noticeable that waiting processes stress the cache by spinning the lock which is energy consuming as they need cache consistency and messages in coherency protocol [129]. In proposed efficient lock techniques, an Operating System as Linux, put the waiting threads on sleep instead of staying in a busy waiting state and constantly spinning the lock.

#### **Mutexes and Semaphores**

**Mutexes:** Mutex or Mutual Exclusion Object provides access to a shared resource so that all the processes use the resource, but only one process is allowed to use the resource at a time. Mutex uses the lock-based technique to handle the critical section problem. The system will generate a mutex object with a unique name or ID whenever a process requests access. So, as the process wants to use that resource, it holds a lock on the object. After locking, the process uses the resource and lastly releases the mutex object. By locking the object, that shared resource is allocated to that particular process, and no other process can take the resource. Hence, in the critical section, no other processes are allowed to use the shared resource.

Semaphores: In semaphore synchronization technique, threads utilize two functions to modify the semaphore value wait() and signal(), but the functions allow only one thread to change the value at a specific time, i.e., two threads cannot simultaneously change the semaphore value. There are two types of semaphores; Counting semaphores and Binary semaphores.

In **Counting semaphores**, at first, the semaphore value is initialized with the number of resources available. Afterward, whenever a process demands some resource, the *wait()* function is called, and the semaphore value is decremented. The process then uses the resource, and after using the resource, it increments the semaphore value by calling *signal()* function. So, as semaphore value becomes 0, it means that all the shared resources are being used by the processes and there is no resource left to be used. Any other processes demand the resources, then they need to wait.

In **Binary semaphores**, the semaphore value can be 0 or 1 and it is initialized with 1. When one process wants to use some resources, it calls the wait() function and sets the semaphore value to 0. It uses the resource, and then by calling the signal() function and setting the semaphore value to 1, it releases the resource. When the semaphore value is 0, and a process wants to use the same resource, the process needs to wait for it to be released by the previous process.

Semaphores and Mutexes are both sleep-wait spin-lock, i.e., while a process or thread

can not take the lock (Mutex) or is waiting for the semaphore value to become positive, the operating system puts the thread on sleep.

The differences between mutex and semaphore are as follows: as Mutexes employ a locking mechanism for synchronization, the semaphore techniques employ a wait and signal mechanism. In synchronization using mutexes, multiple process can access one shared resource but only one process at a time. The semaphore technique also allows multiple processes to access the finite number of the resource until some resources become free. In mutex mechanism, the lock can be acquired and released by the same process. Conversely, the semaphore value can be changed by any process that needs some resource, but only one process can modify the value at a time.

#### Parallel Application Programming Libraries

Parallel application programming libraries are used to ensure a transparent and clear programming method to parallel application developers. They contains a set of Application Programming Interface (API) focused on allowing the developer to model the application following a parallel paradigm. The developer can call such API functions of programs in the code, allowing the OS to dynamically create new threads and to manage its execution among different cores.

POSIX Threads (Pthreads) libraries are standard-based thread APIs for C/C++, supported in Linux. It allows one to create a new parallel process flow. Pthread is the most efficient on multiprocessor systems where the process flow can be scheduled to be executed on another processor to gain parallelism to achieve performance. Threads require less overhead than "forking" or creating a new process because the system does not initialize a new virtual memory space and environment for the process. While most effective on a multiprocessor system, Pthreads benefits are also noticed on uniprocessor systems. Uniprocessors exploit latency in I/O and other system functions that may stop process execution, i.e., one thread may execute while another is waiting for I/O or some other system latency. All threads from the process share the same address space. A thread is created by defining a function and its arguments which will be processed in the thread. The main goal behind using the POSIX thread library in the program is to speed up its execution. Some parallel programming approaches like OpenMP rely on Pthread library.

#### Queue-based synchronization

Another group of synchronization techniques is based on queues. The queue-based techniques can mitigate the contention problem of the spinlock approach. These approaches substitute a single lock variable (or the boolean flag of a test and set lock) with a queue of waiting threads. Each thread knows its own place in line: it waits for its predecessor to finish before entering the critical section and signals its successor when it is done [125]. To reduce the contention problem, Mellor-Crummey and Scott [125] showed how to adapt queued spinlocks to the reader-writer case. Specifically, they presented reader-preference, writer-preference, and fair reader-writer locks based on the MCS lock.

MCS [125] and CLH [36] are queue-based spinlocks that create a queue of waiting threads where each thread is spinning on a unique location when busy waiting. Thus queue-based locks solve the problem of the single-memory-location bottleneck of simple spinlocks.

Some solutions combine multiple lock types to benefit from their advantages in specific situations. For instance, Antic et al. [10], introduce GLS, a middleware that dynamically switches among three locking algorithms (Ticket, MCS [125], Pthread mutex). It uses Ticket at low contention levels, MCS at high contention levels, and Pthread when it detects over-threading (i.e., more threads than cores).

A recent comprehensive analysis on software synchronization methods is presented by Guerraoui et al. [54]. Their research performs a thorough study considering throughput (traditionally the primary performance metric), energy efficiency, and tail latency of 28 state-of-the-art mutex lock algorithms, on 40 applications, on four different multicore machines. They have achieved significant findings including: i) rather than lock/unlock interface, applications stress the full locking API (e.g., trylocks, condition variables), (ii) application performance can be directly affected by the memory footprint of a lock, (iii) the interaction between locks and scheduling is a significant factor for performance (iv) no lock algorithm is systematically the best, (v) it is difficult to choose the best lock, and (vi) in the context of lock algorithms, energy efficiency has a direct relation with throughput.

To the best of our knowledge, the approach introduced by Szustack [135] is the only proposed software synchronization solution regarding dataflow applications for shared memory multicore architectures. This work introduces a strategy to speedup the thread synchronization for dataflow applications at the software level. The approach consists of synchronizing interdependent threads only by grouping them at the software level, instead of using global barriers. Interdependent threads have producer-consumer data dependencies. This approach is evaluated over two Stencil-based dataflow applications. Stencil is a class of numerical data processing solution which updates array elements according to some fixed patterns. In this algorithm, a single synchronization point called is used to synchronize a group of interdependent threads. This synchronization point uses a counter that contains the number of threads in the group and a global release flag. Once one of the threads in the group arrives to the synchronization point, the counter is decremented and the thread is suspended until the global flag is released. The flag is only released when all the threads have arrived and the counter has reached zero. A separate flag is used to release all the waiting threads. The synchronisation model proposed is limited to stencil style of programming and additionally it is still a centralized software-based mechanism that is prone to contention between the threads. It is not a viable solution for our problem, which needs a scalable solution. Our proposition, in contrast, considers pairs of producer-consumers and is not centralized.

#### 1.2.2 Synchronization Support in the ISA

Contrary to the software synchronization approaches in which typically a thread or a process is spinning on a lock value, some processors propose event-based mechanisms for synchronization in their Instruction-Set Architecture (ISA).

Among commercial ISAs, ARM instruction-set [146] includes several instructions for synchronization, Set Event (SEV), Wait For Event (WFE), Wait for Interrupt (WFI), and Yield. The SEV causes an event to signal to all cores within a multiprocessor system. The event is monitored by the WFE instruction through an Event Register. Intel ISAs offer the XCHG instruction to compare and set locks and the TEST for checking the status of the locks without changing its value.

In a different vein, the VAX instruction-set [139] supports hardware-accelerated queues. It has different instructions for communication on the hardware queue. The VAX instructions INSQHI, INSQTI, REMQHI, and REMQTI allow insertion or removal at the head or tail of a self-relative double-linked list. These instructions are interlocked and cannot be interrupted; this feature stops other processors from updating the queue at the same time. These complexities make it complicated to reach high performance, and programmers often prefer to implement their own software queues [80].

#### 1.2.3 Synchronization Support in Hardware

In this section, we overview the existing synchronization solutions in hardware. The studied hardware synchronization approaches can be categorized into different groups according to the techniques employed to accelerate the synchronization. The techniques include: (1) employing queue-based approach (2) accommodating the synchronization primitives in local memories or network interface to avoid shared memory accesses (3) by-passing the shared memory using a dedicated network for synchronization messages.

#### Queue-based Synchronization

In the first group, synchronization solutions primarily employ a queuing mechanism for synchronization approach [80, 141, 69]. Using queues are common in data communication and synchronization approaches of parallel programs. The **Q-based** approaches are efficient for the parallelism that are coarse-grained enough to amortize the enqueue and dequeue cost [80]. The hardware Q-based approaches are introduced to reduce the overhead of the software Q-based communications related to enqueue and dequeue operations.

As managing software queues in synchronization of fine-grain parallelism is expensive [80], several works introduced hardware synchronization approaches focus on hardware queues to decrease the overhead [80, 141, 69, 138]. However, they require ISA modification and custom interconnect. Additionally, they impose burdens on the operating system in terms of preserving the states of the queues across context switches.

The Hardware-Accelerated Queue (HAQu) [80] takes advantage of the benefits of hardware queuing while maintaining the benefits of software queues. Their proposed design provides three fundamental features: (1) it supplies a single instruction for *enqueuing/dequeuing* which decreases the overhead of fine-grained communications; (2) HAQu leverages on-chip interconnect and cache coherence protocol for transferring data from producer to consumer; (3) it solves the problem of context switch overhead of the OS. In HAQu, the queues states are entirely stored in the virtual address space of the application. With the help of these features, HAQu solution provides higher throughput and lower latency compared to optimized software implementations. Communication Acceleration Framework (CAF) [141], similar to HAQu, introduces a co-optimized software and hardware solution to accelerate the hardware queue operations. In CAF, they offload the communication responsibilities from processor and memory to a dedicated hardware device, Queue Management Device (QMD), attached to the Network on Chip to improve core communication. Contrary to HAQu, CAF does not impose memory access and coherency overhead. Moreover, it has less core modification than HAQu (only three new instructions added to ISA).

Swarm [69] is a scalable tiled multicore architecture designed for the applications presenting the *ordered irregular parallelism* in their execution pattern. Swarm architecture employs implicit communication, which is a commit protocol using hardware task queues. They use hardware queues for their proposed scheduler to synchronize the tasks. Applications with *ordered irregular parallelism* can be characterized by three main features [111, 59]. (i) Each task is an event (ii) which starts execution at specific time and modifies a specific component. (iii) Tasks dynamically create other tasks. This parallelism is abundant in many domains like simulation, graph analytics, and databases.

The Swarm execution model consists of distributed task queues, speculative out-oforder task execution, and ordered task commits, which helps Swarm's micro-architecture scale efficiently.

Vallejo et al. [138] introduce a Lock Control Unit (LCU) with a Local Reservation Table (LRT) that manages the hardware locks queues. LCU is attached to the core to accelerate reader-writer locking for core-to-core transfers. The authors assign the hardware locks to the lock requester by associating the thread ID of the lock requester to the lock. By doing so, the locks are decoupled from the cores and hence, provide efficient threads migration.

#### Accommodating Synchronization Primitives

Since memory access in synchronization operations is always a bottleneck, in order to accelerate synchronization, the researchers try to avoid shared memory access. The second group of hardware synchronization approaches are the solutions in which the synchronization resources are accommodated in local memory of Network Interface [46, 98, 47, 84, 2, 3, 81, 103].