# Reliable event-based techniques for ASK demodulation in NFC devices

Alexis Rodrigo Iga Jadue

#### ▶ To cite this version:

Alexis Rodrigo Iga Jadue. Reliable event-based techniques for ASK demodulation in NFC devices. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2022. English. NNT: 2022GRALT021. tel-03708633

### HAL Id: tel-03708633 https://theses.hal.science/tel-03708633v1

Submitted on 29 Jun 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité: NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministériel : 25 mai 2016

Présentée par

### **Alexis Rodrigo IGA JADUE**

Thèse dirigée par **Laurent FESQUET**, Maître de Conférence Grenoble INP / Phelma, Université Grenoble Alpes et co-encadrée par **Sylvain ENGELS**, STMicroelectronics

préparée au sein du Laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés

dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Techniques fiables basées sur événements pour la démodulation ASK des dispositifs NFC

# Reliable event-based techniques for ASK demodulation in NFC devices

Thèse soutenue publiquement le **24 février 2022**, devant le jury composé de :

#### **Monsieur Laurent FESQUET**

MAITRE DE CONFERENCE HDR, Université Grenoble Alpes, Directeur de thèse

#### **Monsieur Luc HEBRARD**

PROFESSEUR DES UNIVERSITES, Université de Strasbourg, Président **Monsieur Pascal NOUET**

PROFESSEUR DES UNIVERSITES, Université de Montpellier, Rapporteur

#### **Monsieur Gilles JACQUEMOD**

PROFESSEUR DES UNIVERSITES, Université Côte d'Azur, Rapporteur **Monsieur Emil NOVAKOV**

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes, Examinateur

### Remerciements

Cette belle aventure du doctorat en territoire français, a commencé bien avant que ce que l'on pourrait imaginer. C'était l'année 1982, et mon frère, âgé de 3 ans, refusait de rentrer faire son examen d'admission en maternelle dans une école anglaise dans notre quartier à Santiago du Chili. Ceci fût un événement clé de cette histoire, car quelques semaines plus tard, il acceptait sans soucis de faire cet examen dans l'école française du même quartier. C'était le début de ma connexion indissoluble avec la culture française, sa langue, ces habitudes et sa vaste communauté installée au Chili.

Toujours passionné par l'électronique, en 2009, je cherchais à faire un master en microélectronique en France, car je parlais déjà la langue, et ça me permettait d'avoir une expérience à l'étranger dans une culture plutôt familiale et habituelle. Parmi les trois options que j'avais entre Montpellier, Lyon et Grenoble, j'ai choisi cette dernière pour ces belles montagnes et sa grande réputation dans le domaine. Pendant la période du master MNE, j'ai eu la chance de rencontrer d'excellentes personnes parmi les enseignants, avec qui j'ai toujours maintenu le contact, et qui m'ont toujours donné leur support pour tous les projets que j'ai entrepris : Olivier Rossetto, Gilles Sicard et Gilbert Vincent. Aussi, pendant la période de stage en 2010, j'ai connu Rodrigo Possamai, qui faisait son doctorat, et avec qui nous avons partagé plusieurs moments ensemble, et avec qui j'ai aussi maintenu le contact.

Quelques années plus tard, en avril 2015, nous avons décidé de visiter l'Europe avec Giselle, ma chère femme, amie, collègue, mais surtout copine de multiples aventures. Quand elle a insisté de visiter Grenoble pour voir une fois de plus notre ville adoptive ainsi que quelques amis, j'ai décidé de contacter Gilles Sicard, Olivier Rossetto et Rodrigo Possamai pour déjeuner ensemble. Dans ce déjeuner, Possamai, qui était déjà devenu membre permanent de l'équipe CIS au laboratoire TIMA, m'a parlé du projet européen THINGS2DO que l'équipe venait d'obtenir. L'équipe avait besoin de quelques collaborateurs, donc il m'a invité à participer. Après quelques semaines de réflexion, nous avons finalement accepté son invitation. Merci beaucoup Rodrigo Possamai pour cette invitation et aussi pour m'avoir fait confiance. Ca a été le début d'une belle

histoire. Je tiens à remercie profondément mon ancien chef, Eduardo Carrasco, qui m'a donné tout son support quand je lui ai transmis que je partais en France, et m'a beaucoup aidé. Muchas gracias Eduardo por tu gran apoyo y ayuda para iniciar esta aventura.

Quelques mois plus tard je connaîtrais, par visioconférence, la personne clé de cette histoire, Laurent Fesquet, qui déjà se battait avec l'administration pour réussir à m'embaucher dans son équipe dans des conditions adéquates. Laurent, je te remercie profondément pour le support, la confiance et l'amitié que tu m'as accordé dans chaque situation, chaque projet, chaque conversation pendant cette aventure, et notamment pendant ces relectures très denses et fatigantes du manuscrit de thèse. Aussi, un grand merci Laurent d'avoir accepté un ingénieur déjà trop mûr (38 ans) parmi tes doctorants, ce n'est pas souvent que l'on voit une situation pareille. Je remercie fortement aussi à Sylvain Engels pour ta générosité, ton ouverture d'esprit par rapport à l'accueil et support des nouvelles idées, pour l'opportunité que tu m'as donné chez STMicroelectronics, pour les moments de partage, les multiples brainstormings et ta capacité de filtrage quand je te bombardais avec plusieurs nouvelles idées.

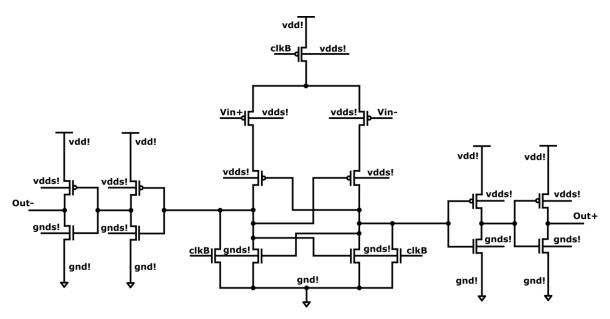

Merci beaucoup aussi à la communauté brésilienne de notre groupe, avec qui j'ai passé de moments inoubliables : les gros câlins matinales, conversations profondes, nos plus grosses fêtes Grenobloises, les cocktails, les cafés et surtout l'amitié d'Otto, l'humour sérieux de Raphael, les partages avec Leonel (merci particulier pour cette nuit blanche pendant le premier testchip), les heures infinies de travail avec Thiago avec son humour particulier, son amitié, ses danses et ces « franguiçies » sans fin. Aussi merci beaucoup aux membres de la deuxième vague, Matheus pour les conversations, les barbecues, et le partage de grille et Nucléos. Aussi merci à Ricardo pour son amitié, les partages au ski, les « easylovers » descendants les pistes, les « bobuns malucos » et les courses au bord de l'Isère. Merci aussi à Renato, pour les conversations, les soirées musicales, les bars, mais surtout ton spécial conseil d'utiliser les comparateurs « Strong-Arm », qu'avant notre conversation, je ne connaissais même pas.

Également, je remercie beaucoup Jean Simatic, pour sa grande amitié, les super brainstormings que nous avons partagés, les conversations, notre partage de connaissance sans fin, les soirées, la dent de Crolles, la lasagne de chocolat

« exquisita » et les shots. Merci à Karim pour les conversations, le partage et les soirées d'équipe chez lui avec cette belle vue depuis Saint-Martin-Le-Vinoux. Je remercie beaucoup aussi Amani, pour son amitié, les conversations profondes, les empanadas et les moments partagés. Je remercie beaucoup aussi Grégoire, pour tout le partage, les conversations techniques ainsi que personnelles, les grands brainstormings, son amitié, sa sympathie et la bonne ambiance de toujours. Aussi, je remercie Sophie pour le temps partagé ensemble, les conversations et la découverte du restaurant libanais avec Adrien. Je remercie Assia pour les conversations, le partage technique et l'ambiance agréable toujours.

Je remercie vivement mes collègues plus récents, Jérémy, Yoan, Mohamed, Olivier, Marco, Hasan, Diana, Xavier, Rosalie, Nils, Ankush, Dayana, Giovanni, Denis, Andrés, Ángel, pour tous les bons moments, les cafés, les restaurants, les bars, les conversations infinies, les brainstormings, les partages, les testchips, les barbecs et tous les types de différents échanges techniques comme personnelles.

Merci beaucoup à tous les membres du TIMA, Anne-Laure, Salvador, Raoul, Skandar, Stéphane, Manuel, Laurence, Youness, Aurore, Mamadou pour tout l'aide qu'il nous a donné, les conversations et son amitié, David, Daniel, Marc et les moments partagés à l'escalade, Ahmed et Fred pour votre support ces années, Florence, Sylvain Bourdel pour tout le support pendant mes CSI, mais notamment pour la confiance que tu m'as accordée.

Je remercie spécialement les membres techniques de nos plateformes de CAO au CIME, Mohamed, Robin, Abdelhamid et Alejandro, pour le magnifique support pendant toutes ces années, l'amitié, les très bons moments, les cafés, les partages de connaissances et bien sûr toutes les conversations. Je remercie beaucoup aussi les membres administratifs du CIME, Lorraine, Olivier, Ahmad, Déborah, pour tous les sourires, les blagues, les conversations et les moments toujours agréables.

Merci aussi à tous les membres du CMP, Christelle, Yann, Jean-François, Kholdoun, Aurélien, Romain, Isabelle, Patricia, François, Nicolas, Chantal, Lyubomir, pour votre support toutes ces années, les conversations et les échanges agréables et intéressants.

Je remercie aussi à tous les membres de l'équipe à STMicroelectronics, Marc, Franck, les Thiery, Alain, Guillaume, Venance, Andrei, Quentin et Sophie.

Sylvain et Laurent, je vous remercie particulièrement pour tous ces bons moments d'échange, de partages d'idées, d'amitié, de convivialité, les cafés, les conversations, l'énorme confiance que vous m'avez accordée (notamment dans ce moment de difficulté bien particulier), et bien sûr tout le support que vous m'avez donné depuis même avant de commencer ce défi.

Je remercie aussi mes chers amis qui m'ont toujours fait passer un excellent moment, pour ainsi maintenir les énergies et surmonter les moments difficiles, Ferenc, Rafael Della Giustina, Elodie, Migue, Margot, Mauricio, Francesco, Julio, Edith, Luana, Tatiana, Munique, Mathieu, Karen, Romain, Rudy, Pascal, et tous les coéquipiers des club de tennis de Saint Nazaire Les Eymes ainsi que du GUC.

Agradezco también a todos mis amigos cercanos que me apoyaron desde la adolescencia, confiados en que llegará un día en que exista la "Unidad Iga", jeje, quién sabe si algún día se pueda hacer realidad. También a los amigos de la Universidad que me apoyaron siempre en esta travesía, confiando en que lo conseguiría. También agradezco a mi familia cercana, que siempre me ha apoyado a cumplir mis sueños, a mi mamá, mi hermano, mi cuñada, mis queridos sobrinitos, Coni y Diego, y mi papá, por todo el amor que siempre me han entregado, aun estando lejos, siempre sentí su enorme apoyo y cariño. A mis abuelos, por habernos ayudado en nuestra educación y darnos un soporte y apoyo en todo momento. Agradezco también a mis tíos y mis primos que siempre me han entregado su gran cariño. Y a la querida familia Andonie-Estay que siempre me han apoyado y aconsejado.

Finalmente, agradezco especialmente a Giselle, mi compañera incondicional, quién ha sido un apoyo fundamental en todas las aventuras que nos hemos propuesto, en todos los momentos favorables como adversos, así como en las noches que pasé en vela intentando resolver alguno de los tantos enigmas que enfrenté durante el doctorado. Gracias infinitas amor por la concretización de esta gran aventura.

¡¡¡Gracias Totales!!!

# **Table of Contents**

| 1 Ir  | ntroduction                                                    | 1  |

|-------|----------------------------------------------------------------|----|

| 2 S   | tate of the Art                                                | 5  |

| 2.1   | Introduction                                                   | 5  |

| 2.2   | Event-based Analog-to-Digital Converter (EB-ADC)               | 6  |

| 2.2.1 | Non-Uniform Sampling and Level Crossing Sampling Scheme (LCSS) | 7  |

| 2.2.2 | Time-to-Digital Converter (TDC)                                | 11 |

| 2.3   | Asynchronous Circuits                                          | 16 |

| 2.3.1 | Synchronous circuits                                           | 16 |

| 2.3.2 | Synchronous method                                             | 16 |

| 2.3.3 | Asynchronous method                                            | 18 |

| 2.3.4 | Bundled-data encoding                                          | 20 |

| 2.3.5 | Four-phase handshake protocols                                 | 20 |

| 2.3.6 | Muller Gate                                                    | 23 |

| 2.3.7 | The advantages of micropipeline Asynchronous Circuits          | 25 |

| 2.4   | Conclusion                                                     | 27 |

| 3 N   | IFC Communications                                             | 29 |

| 3.1   | NFC demodulation                                               | 29 |

| 3.1.1 | NFC protocol                                                   | 29 |

| 3.1.2 | Analog demodulation                                            | 31 |

| 3.1.3 | Digital demodulation                                           | 32 |

| 3.2   | Objectives of the proposed solution                            | 35 |

| 3.3   | Conclusion                                                     | 36 |

| 4 A   | SK demodulator architecture and implementation                 | 39 |

| 4.1   | Introduction                                                   | 39 |

| 4.2   | Testbench: Simulation Scenario                                 | 41 |

| 4.2.1 | Matlab basic functions                                         | 41 |

| 4.2.2 | RF Input signal definition                                     | 41 |

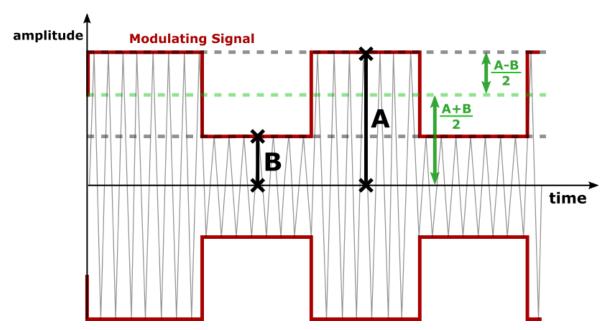

| 4.2.3 | Level-Crossing Sample Scheme Selection                         | 43 |

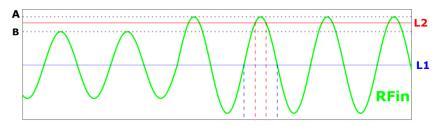

| 4.2.4 | First Proposed Solution                                        | 44 |

| 4.3   | Results obtained with the SystemVerilog testbench              | 51 |

| 4.3.1 | First proposal results                                | 51 |

|-------|-------------------------------------------------------|----|

| 4.4   | Conclusion                                            | 53 |

| 5 En  | hanced ASK demodulators                               | 55 |

| 5.1   | Second Proposal results                               | 55 |

| 5.1.1 | Introduction                                          | 55 |

| 5.1.2 | Second Proposed Solution                              | 56 |

| 5.1.3 | Ideal TDC Module                                      | 58 |

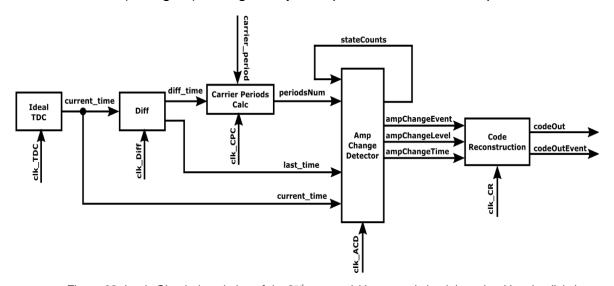

| 5.1.4 | Diff Module                                           | 58 |

| 5.1.5 | Carrier Periods Calc Module                           | 58 |

| 5.1.6 | Amp Change Detector (ACD)                             | 58 |

| 5.1.7 | Code Reconstruction Module                            | 59 |

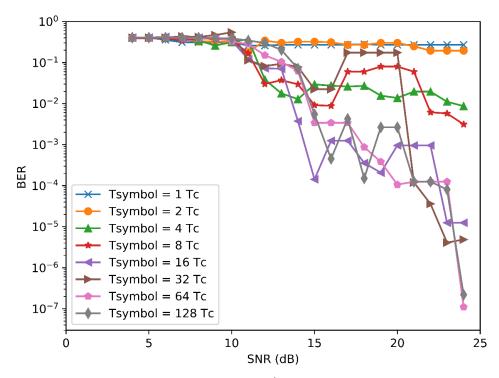

| 5.1.8 | Simulation Results                                    | 60 |

| 5.2   | Third Demodulation Solution                           | 61 |

| 5.2.1 | "Amp Change Detector" module's logic                  | 62 |

| 5.2.2 | TDC Implementation                                    | 63 |

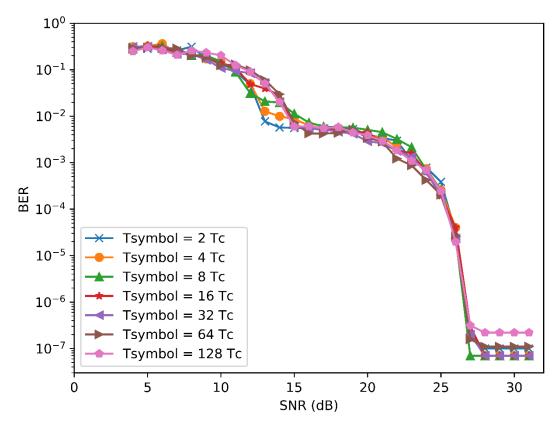

| 5.2.3 | RTL Simulation results                                | 68 |

| 5.3   | Comparison with the Solutions of the State-of-the-Art | 69 |

| 5.3.1 | Introduction                                          | 69 |

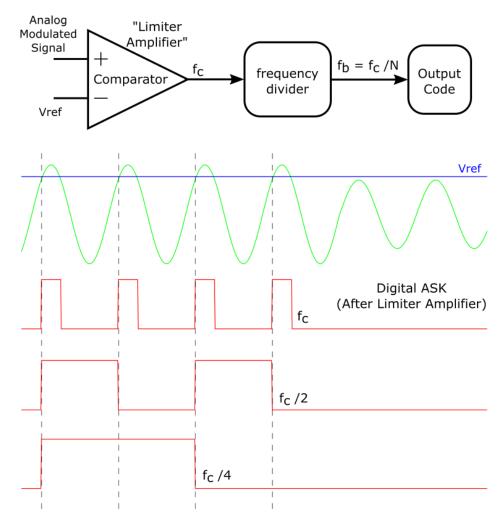

| 5.3.2 | Frequency Divider Technique                           | 70 |

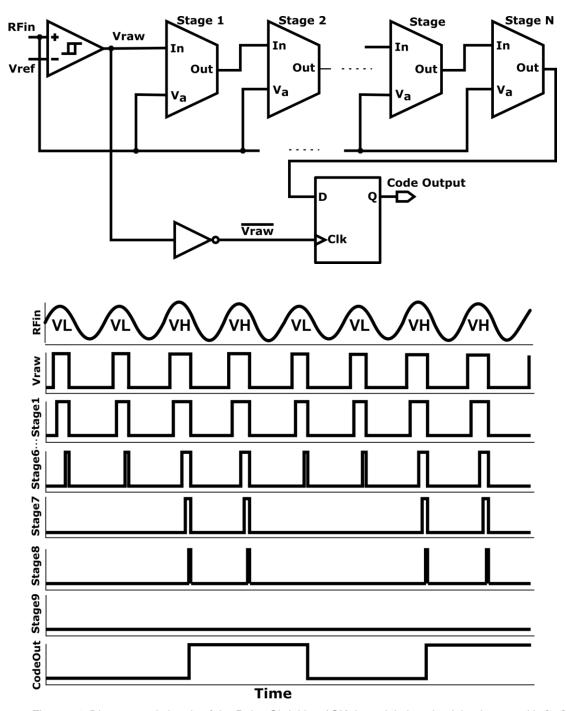

| 5.3.3 | Pulse Shrinking Method                                | 71 |

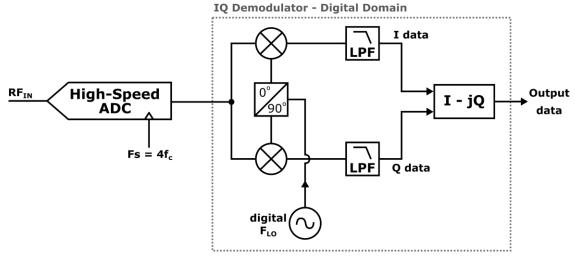

| 5.3.4 | Digital IQ Demodulation                               | 72 |

| 5.4   | Conclusion                                            | 74 |

| 6 Ph  | ysical Implementation: Testchip                       | 77 |

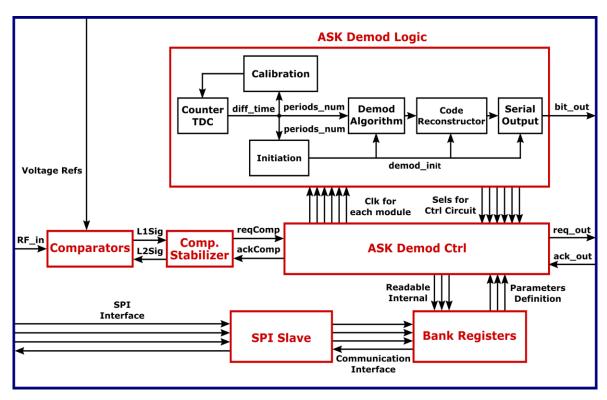

| 6.1   | Introduction                                          | 77 |

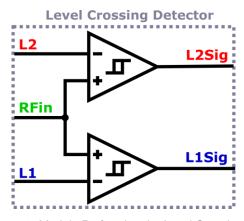

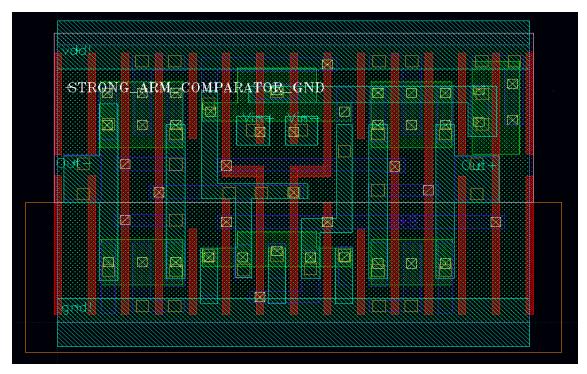

| 6.2   | Physical implementation of the comparators            | 78 |

| 6.3   | Comparison Stabilizer                                 | 82 |

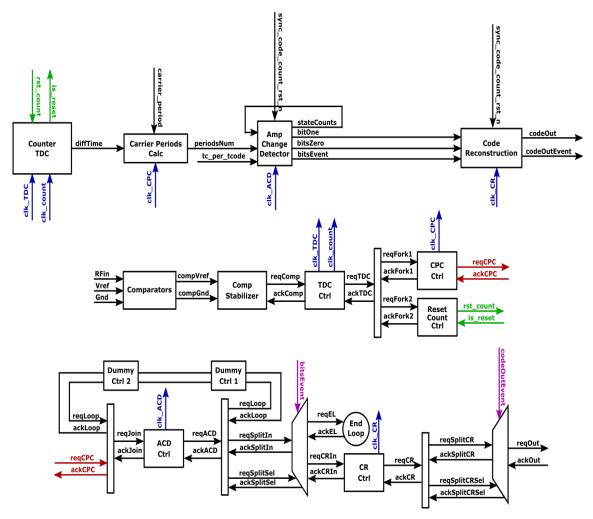

| 6.4   | ASK Demodulation Logic                                | 83 |

| 6.4.1 | Counter TDC                                           | 84 |

| 6.4.2 | Calibration                                           | 85 |

| 6.4.3 | Initiation                                            | 85 |

| 6.4.4 | Demodulation Algorithm                                | 86 |

| 6.4.5 | Code Reconstruction                                   | 86 |

| 6.4.6 | Serial Output                                         | 86 |

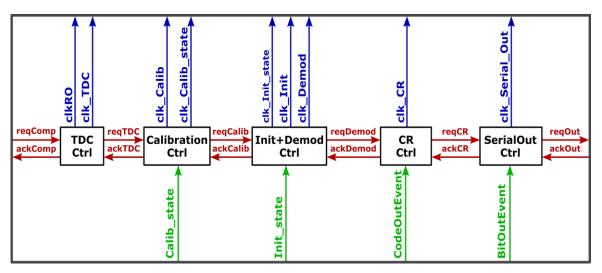

| 6.5   | ASK Demodulation Control                              | 87 |

|       |                                                       |    |

| 6.5.1  | Introduction                                      | 87  |

|--------|---------------------------------------------------|-----|

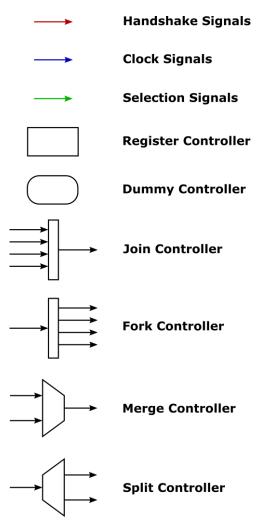

| 6.5.2  | Basic Elements of the Control Circuit             | 90  |

| 6.5.3  | TDC Control Circuit                               | 94  |

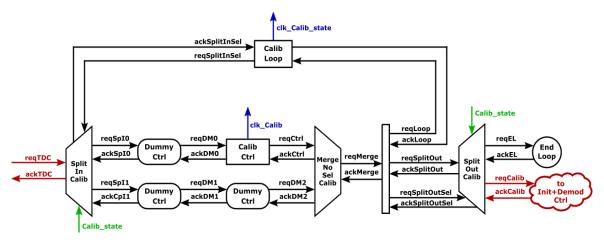

| 6.5.4  | Calibration Control Circuit                       | 96  |

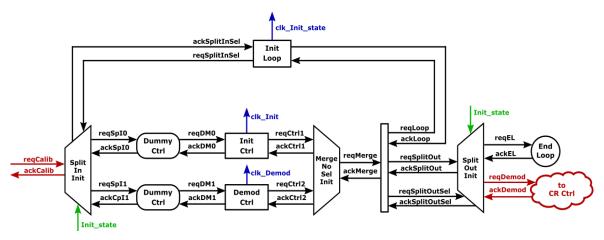

| 6.5.5  | Initiation and Demodulation Control Circuit       | 97  |

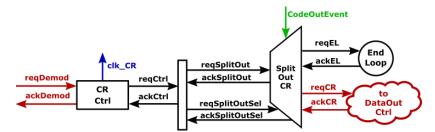

| 6.5.6  | Code Reconstruction Control Circuit               | 98  |

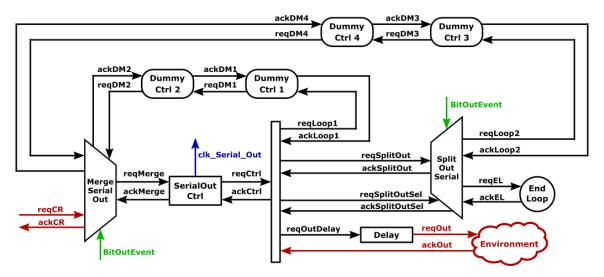

| 6.5.7  | Serial Output Control Circuit                     | 99  |

| 6.6    | SPI Slave and Bank of Registers                   | 99  |

| 6.7    | Results                                           | 100 |

| 6.7.1  | Synthetized area and power consumption estimation | 100 |

| 6.7.2  | Post-layout Performance Results                   | 101 |

| 6.8    | Conclusion                                        | 104 |

| 7 Co   | nclusions and Perspectives                        | 107 |

| 7.1    | Thesis contributions                              | 107 |

| 7.2    | Perspectives                                      | 109 |

| Refere | nces                                              | 111 |

# **List of Figures**

| Figure 1: Generic diagram of a digital demodulation system                  | 5        |

|-----------------------------------------------------------------------------|----------|

| Figure 2: Regular Sampling Scheme Example                                   | 7        |

| Figure 3: Irregular Sampling Scheme Example                                 | 8        |

| Figure 4: Conventional solution for EB-ADC, sometimes called "floating w    | /indow   |

| Level Crossing-ADC"                                                         | 10       |

| Figure 5: Basic analog TDC technique                                        | 12       |

| Figure 6: Enhanced analog TDC design                                        | 13       |

| Figure 7: Digital TDC design: Counter TDC                                   | 14       |

| Figure 8: Enhanced digital TDC design.                                      | 15       |

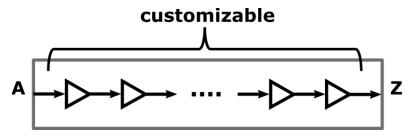

| Figure 9: Synchronous linear pipeline example.                              | 16       |

| Figure 10: Example of a standard Clock-Tree                                 | 17       |

| Figure 11: Asynchronous linear pipeline example                             | 18       |

| Figure 12: Classification of asynchronous circuits.                         | 19       |

| Figure 13: Bundled-data micropipeline linear example                        | 19       |

| Figure 14: Four-phase handshake protocol example                            | 21       |

| Figure 15: WCHB bundled-data micropipeline asynchronous register cor        | ntroller |

| implementation.                                                             | 22       |

| Figure 16: Symbol representation of the most common non-linear asynchr      | onous    |

| flow elements                                                               | 23       |

| Figure 17: Muller gate symbol and its truth table                           | 23       |

| Figure 18: Transistor level design of a weak-feedback muller gate           | 24       |

| Figure 19: Muller gate implementation using standard cells                  | 25       |

| Figure 20: Common structure of an analog ASK demodulation solution          | 31       |

| Figure 21: Example of an envelope detector (in red) and an average detector | ctor (in |

| blue)                                                                       | 31       |

| Figure 22: Digital IQ demodulator schematic                                 | 32       |

| Figure 23: Diagram and signal description of the frequency divider          | ASK      |

| demodulation circuit proposed in [2]                                        | 33       |

| Figure 24: Diagram and signals of the Pulse-Shrinking ASK demodulation      | circuit  |

| implemented in [24].                                                        | 35       |

| Figure 25: NFC wireless communication diagram                               | 39       |

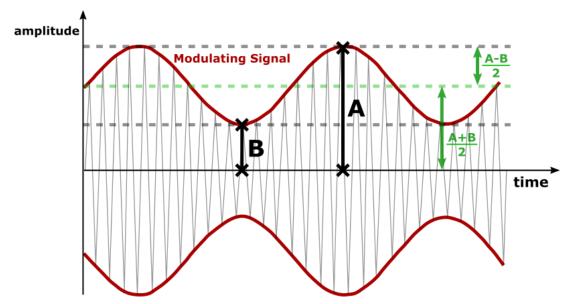

| Figure 26: Time domain representation of an AM signal4                                               |

|------------------------------------------------------------------------------------------------------|

| Figure 27: Time domain representation of an ASK modulation signal and NR2                            |

| coding42                                                                                             |

| Figure 28: Chosen Level-Crossing Sampling Scheme44                                                   |

| Figure 29: Schematic and signals of the circuit presented in the conference                          |

| EBCCSP 2019 [26]                                                                                     |

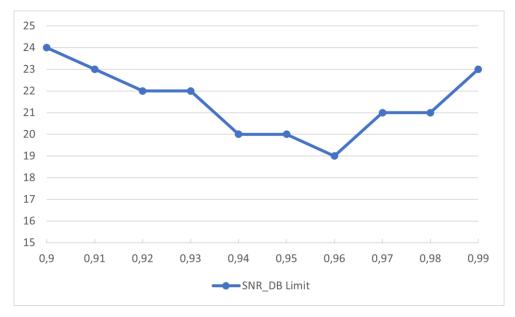

| Figure 30: Graphic showing the simulation result used for the L2 reference leve                      |

| selection                                                                                            |

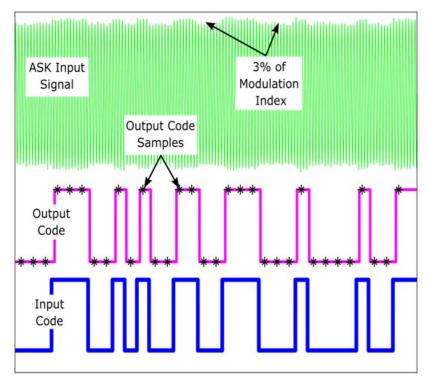

| Figure 31: Simulation Result of the first proposed EB-ASK demodulation technique                     |

| for SNR=28 dB, MI=3% and using a NRZ-L encoding                                                      |

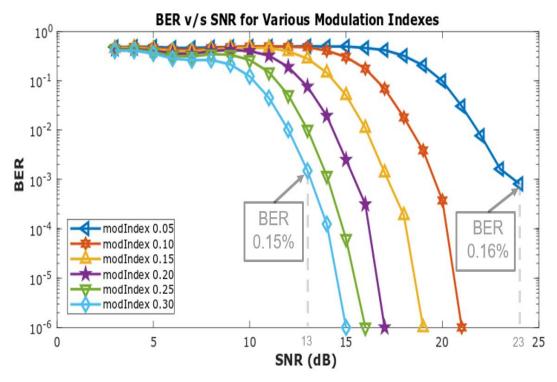

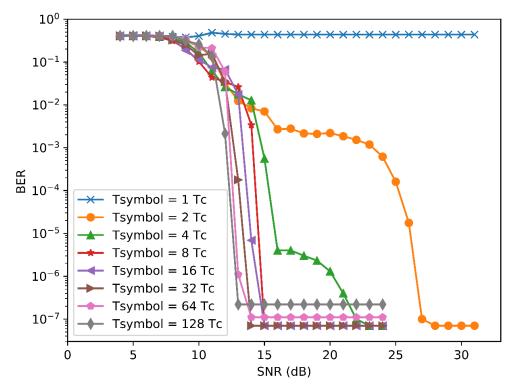

| Figure 32: BER v/s SNR simulation for various modulation indexes 48                                  |

| Figure 33: Results of the 1st proposed demodulation solution, for an MI of 10%                       |

| using the digital SystemVerilog testbench                                                            |

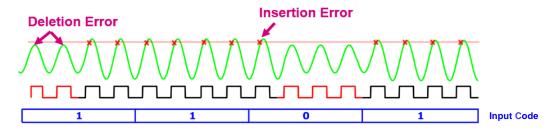

| Figure 34: Example of insertion and deletion errors                                                  |

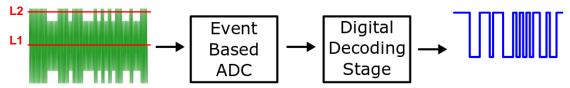

| Figure 35: High-level diagram of the demodulation system and the LCSS 55                             |

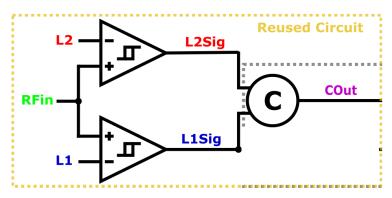

| Figure 36: Module Performing the Level Crossing Detection                                            |

| Figure 37: High-level description of the Continuous measurement TDC 56                               |

| Figure 38: Logic Circuit description of the 2 <sup>nd</sup> proposal (the control circuit is omitted |

| by simplicity)57                                                                                     |

| Figure 39: Example of the implemented algorithm in the « Amp Change Detector :                       |

| block                                                                                                |

| Figure 40: BER v/s SNR results of the 2 <sup>nd</sup> proposed solution, using a MI of 10%           |

| 60                                                                                                   |

| Figure 41: Diagram of the 3 <sup>rd</sup> proposed solution                                          |

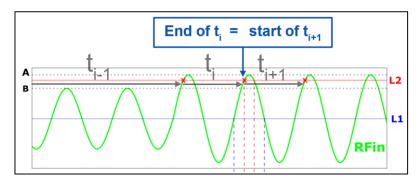

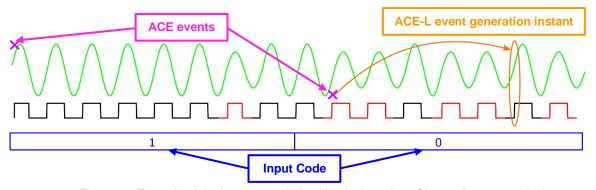

| Figure 42: Example of the demodulation technique sequence                                            |

| Figure 43: Diagram of the TDC reset circuit permitting to reset the TDC counte                       |

| safely                                                                                               |

| Figure 44: Timing diagram of the TDC reset circuit                                                   |

| Figure 45: Diagram of the counter TDC circuit, integrating the synchronization                       |

| block                                                                                                |

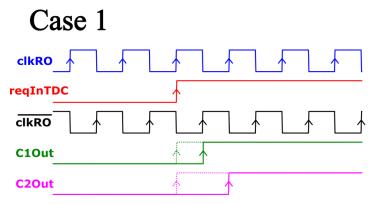

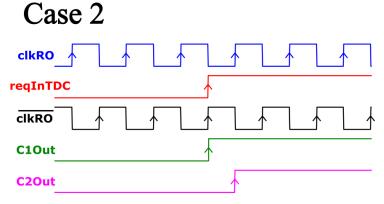

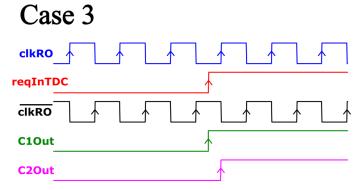

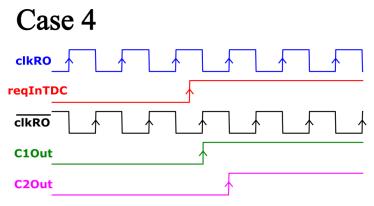

| Figure 46: Datagram indicating the input TDC request arriving in synchronization                     |

| with the rising edge of clkRO67                                                                      |

| Figure 47: Datagram indicating the input TDC request arriving in synchronization                     |

| with the falling edge of clkRO 67                                                                    |

| Figure 48: Datagram indicating the input TDC request arriving before the risi           | ng  |

|-----------------------------------------------------------------------------------------|-----|

| edge of clkRO                                                                           | 67  |

| Figure 49: Datagram indicating the input TDC request arriving after the rising ed       | ge  |

| of clkRO                                                                                | 68  |

| Figure 50: Results of the 3 <sup>rd</sup> proposed solution, using the same SystemVeril | log |

| testbench                                                                               | 69  |

| Figure 51: Results of the frequency divider demodulation technique, using t             | he  |

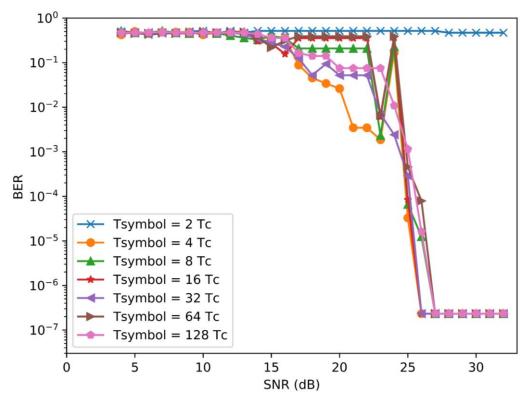

| same SystemVerilog testbench.                                                           | 71  |

| Figure 52: Results of the pulse shrinking demodulation solution, using the sar          | ne  |

| SystemVerilog testbench.                                                                | 72  |

| Figure 53: Schematic of the implemented pulse shrinking element                         | 72  |

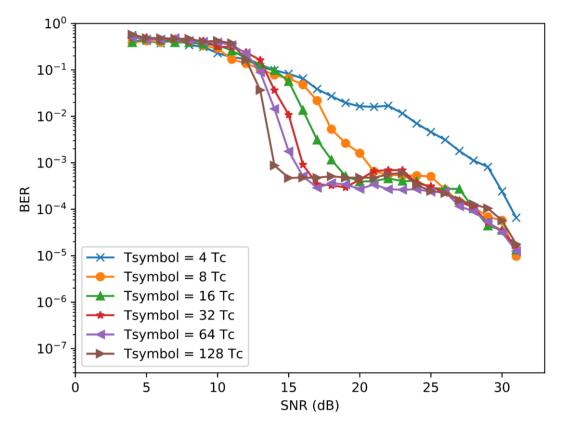

| Figure 54: Results of the digital IQ demodulation, using the same SystemVeril           | og  |

| testbench                                                                               | 73  |

| Figure 55: Diagram of the fabricated circuit, in the node FDSOI 28r                     | ٦m  |

| STMicroelectronics                                                                      | 78  |

| Figure 56: Module Performing the Level Crossing Detection                               | 79  |

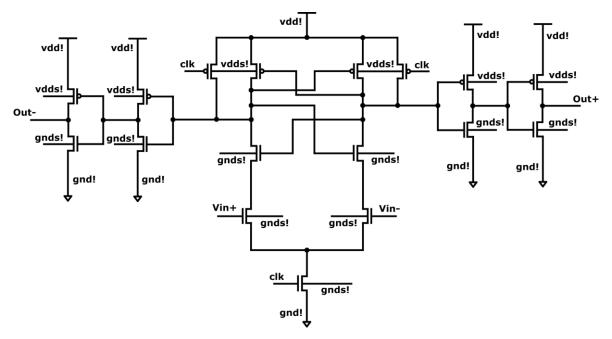

| Figure 57: Schematic of the Strong-Arm comparator adapted for signals near G            | nd  |

| (SAC-Gnd)                                                                               | 80  |

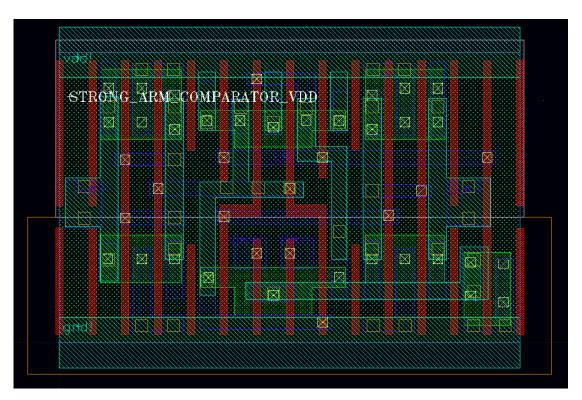

| Figure 58: Layout of the implemented SAC-Gnd                                            | 80  |

| Figure 59: Schematic of the Strong-Arm comparator adapted for signals near V            | dd  |

| (SAC-Vdd)                                                                               | 81  |

| Figure 60: Layout of the implemented SAC-Vdd                                            |     |

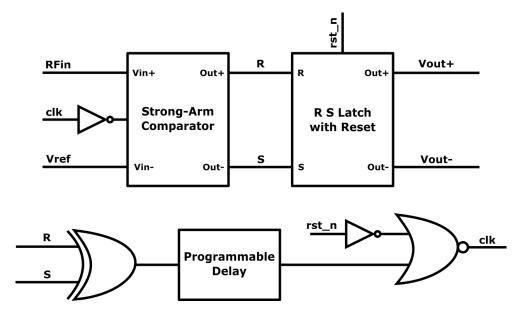

| Figure 61: Self-generation of the comparation clock for a SAC-Gnd - High-le             | vel |

| diagram                                                                                 |     |

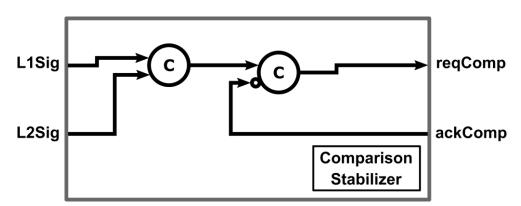

| Figure 62: Diagram of the comparison stabilizer module                                  | 83  |

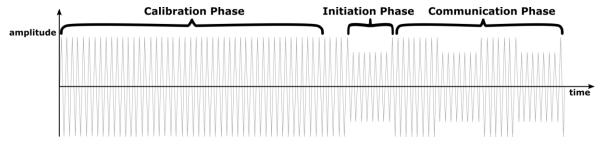

| Figure 63: Operation phases of the ASK demodulator.                                     | 84  |

| Figure 64: The TDC logic circuit implemented in the fabricated testchip                 |     |

| Figure 65: Example of the setup timing constraint verification                          | 87  |

| Figure 66: Example of the hold timing constraint verification                           |     |

| Figure 67: Diagram of the asynchronous control circuit, "ASK Demod Ctrl", of t          |     |

| fabricated testchip.                                                                    |     |

| Figure 68: Legend of the elements used in the controller's diagram description          |     |

|                                                                                         |     |

| Figure 69: Diagram of the implemented C-element.                                        |     |

| Figure 70: Diagram of the used "Register Controller" and its connection with a          |

|-----------------------------------------------------------------------------------------|

| onsecutive stage9 <sup>2</sup>                                                          |

| Figure 71: Diagram of the implemented "Delay Line"92                                    |

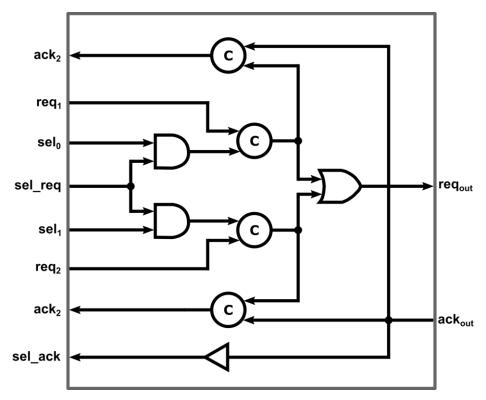

| Figure 72: Diagram of the implemented "Fork Controller"                                 |

| Figure 73: Diagram of the implemented "Join Controller"                                 |

| Figure 74: Diagram of the implemented "Split Controller"                                |

| Figure 75: Diagram of the implemented "Merge Controller"94                              |

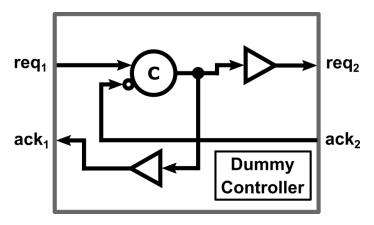

| Figure 76: Diagram of the implemented "Dummy Controller"94                              |

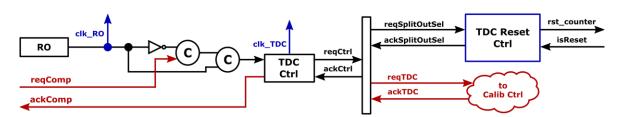

| Figure 77: Diagram of the implemented TDC Controller                                    |

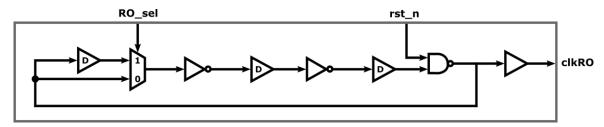

| Figure 78: Diagram of the implemented Ring Oscillator                                   |

| Figure 79: Diagram of the implemented Calibration controller97                          |

| Figure 80: Diagram of the implemented Initiation and Demodulation controller. 98        |

| Figure 81: Diagram of the implemented Code Reconstruction controller 98                 |

| Figure 82: Diagram of the implemented Serial Output controller                          |

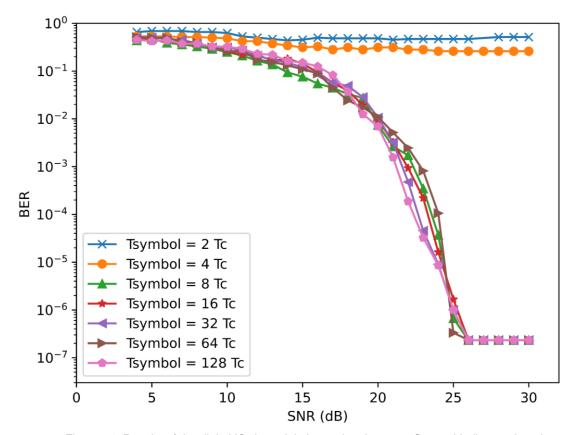

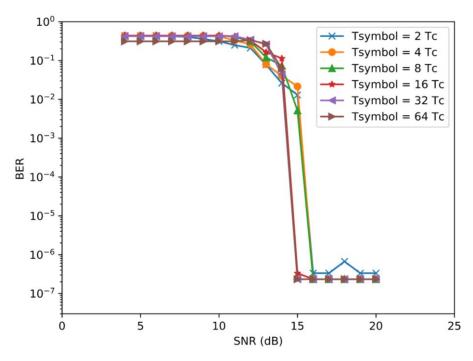

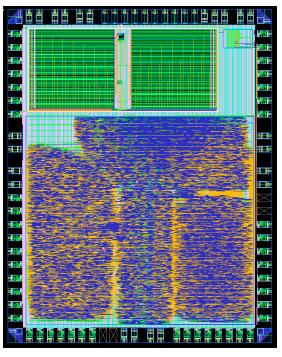

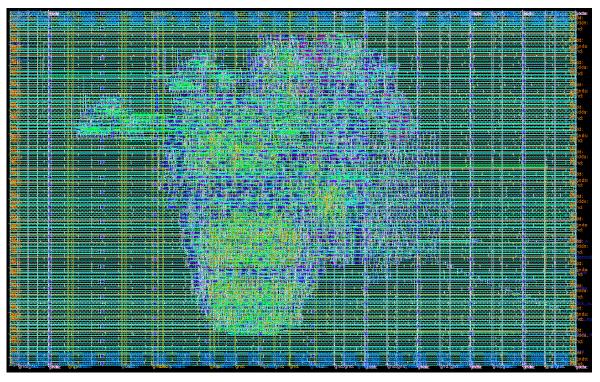

| Figure 83: Graph of the SNR v/s BER performance of the fabricated testchip. 102         |

| Figure 84: Layout TOP of the fabricated Testchip (1649 $\mu m$ x 2085 $\mu m$ )103      |

| Figure 85: Layout of the fabricated ASK demodulator IP (182.92 $\mu m$ x 114 $\mu m$ .) |

| 103                                                                                     |

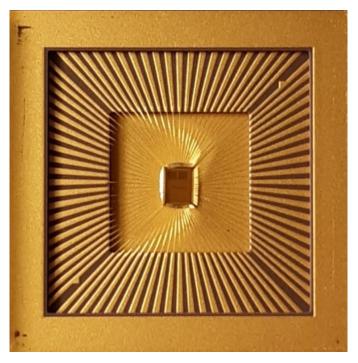

| Figure 86: Picture of the package of the fabricated Testchip104                         |

## **List of Tables**

| Table 1: Characteristics of regular v/s irregular sampled ADC      | 9   |

|--------------------------------------------------------------------|-----|

| Table 2: NFC tag types and their main characteristics              | 30  |

| Table 3: Synthetized area and power consumption results comparison | 100 |

# **List of Equations**

| Equation 2-1: Shannon theorem                                                          |

|----------------------------------------------------------------------------------------|

| Equation 2-2: Signal-to-noise ratio due to quantization error of regular sampled       |

| ADC7                                                                                   |

| Equation 2-3: Equations defining the Signal-to-noise ratio due to quantization of      |

| an irregular sampled ADC9                                                              |

| Equation 2-4: Beutler's condition for a correct reconstruction of the original signal. |

| 10                                                                                     |

| Equation 2-5: Calculation of the quantification step (or LSB) 10                       |

| Equation 2-6: Tracking Condition11                                                     |

| Equation 2-7: Logic equation representing a Muller gate                                |

| Equation 4-1: Calculation of the Modulation Index (MI) in an Amplitude Modulation.     |

| 42                                                                                     |

| Equation 4-2: Calculation of the Bit Error Rate (BER) in the ASK demodulator           |

| simulations53                                                                          |

## 1 Introduction

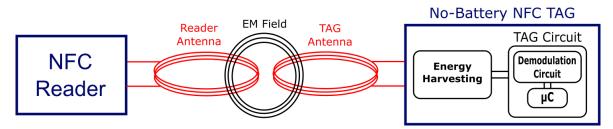

Nowadays, short-range wireless communication circuits are used in our daily life in several applications such as public transport validation, contactless payment cards, RFID product identification, access cards, and even in medical implants like pacemakers.

The most part of these short-range communication devices uses a very popular protocol called "Near-Field Communication" (NFC) that is widely fabricated and sold by important actors in the semiconductor industry like STMicroelectronics, NXP Semiconductors, Qualcomm Technologies, Broadcom, among others [1]. In that context, these competitors are constantly enhancing their products and innovating in the field in order to gain market shares. As announced in [2], the main characteristics for developing and improving these circuits are the reduction of the power consumption, the miniaturization, and the electromagnetic spectrum efficiency.

In the NFC ecosystem, the most popular product is the smartcard. Indeed, smartcards are usually battery-less systems, also called NFC passive devices. This means that its supply voltage is internally generated thanks to an internal harvester using the electromagnetic field emitted by the card reader. In these systems, the recovered energy is very limited. Therefore, the internal modules like the harvesting controller, the voltage limiter, the "Automatic Gain Control" (AGC), the demodulator and the digital processor should smartly be designed to avoid any power issue, mainly due to the power consumption peaks.

The NFC protocol integrates many standards, and all of them use the "Amplitude Shift Keying" (ASK) modulation with different "modulation indexes" (MI), bitrates and coding. As explained in [3] and [4], ASK demodulation is widely used on passive devices because of its simplicity and its low power consumption. As shown in [3] [4] [5], most of the passive ASK demodulation devices are designed using custom analog circuits simultaneously obtaining a controlled power consumption and quite good performances. However, these solutions do not benefit from the technology shrink, and hence the cost reduction. Indeed, when the transistor size is reduced, the passive electronic devices required for analog blocks (resistors, capacitors, inductors) will not

benefit from the technology node shrink, maintaining more or less a similar size, and so contributing to a higher fabrication cost.

On the other hand, the most popular digital *ASK* demodulation solutions implemented in literature [6] use a normal "*Analog-to-Digital Converter*" (*ADC*) with a high sampling rate, generating a large number of samples to process, and hence a high power consumption. For these reasons, these kinds of solutions are only implemented in battery-powered systems, like smartphones, smartwatches, tablets, *etc.*

For the industry, reducing costs and chip area are very challenging, and normally requires an important investment in person-hours and multidisciplinary teams. Nevertheless, advanced technology nodes are an opportunity to lower power consumption, reduce the costs, and enhance robustness and sensitivity of such systems. In battery-less communication systems, when using advanced technology nodes, the supply voltage reduction helps lowering the power consumption and relaxing the design constraints of the supply-voltage harvester. One of the benefits of digitalizing a system is the reusability of the design when the technology is shrunk. In that case, the testbench, the "Register Transfer Level" (RTL) simulation, the timing constraints statements and most of the automated design process are reused.

It is well known in literature that the digital asynchronous circuits are robust against supply voltage and process variations, due to their adaptation capabilities and relaxed timing constraints. These asynchronous solutions are responsive to events generated by the environment and remain idle between those events. Thus, they are very suitable for being connected to "Event-Based Analog-to-Digital Converters" (EB-ADC) using a "Level-Crossing Sample Scheme" (LCSS) [7] [8], because they produce events (samples) only when a level is crossed. When the appropriate levels are chosen, they capture a reduced number of samples compared to a Nyquist ADC based on a fixed sampling period.

After the evaluation of the characteristics exposed in the last paragraphs, the work presented in this manuscript is focused on the development of a novel digital *ASK* demodulation solution integrating the two following considerations:

• The use of an *EB-ADC* with a minimal number of levels generating a low number of samples, and including a *"Time-to-Digital Converter"* (*TDC*) to measure the time between two consecutive level crossing events.

• The implementation of a digital asynchronous *ASK* demodulator that takes the time measurement of each event as input and performs a demodulation algorithm for the modulation symbol recognition.

In other words, the main goal of this proposal is to present a digital *ASK* demodulation alternative that generates a minimal number of samples, uses the latest technology nodes, consequently operating at a reduced voltage, and as a result, reaching a better energy efficiency compared to their analog alternatives. Moreover, these solutions should also enable a cost reduction of these circuits thanks to the use of the most recent technology nodes. In Addition, the event-based asynchronous approach reduces the number of samples to be processed, limits the power consumption, spread in time the current peaks and therefore relax the energy harvesting constraints used in smartcards. Finally, a positive impact of this work is the opening of new perspectives to relax the constraints of the necessary analog modules used in the smartcards, or even completely remove them. Normally, these modules are an *AGC*, an adaptative impedance solution, a voltage-limiter, an energy-harvesting module, etc.

## 2 State of the Art

### 2.1 Introduction

In life, all the communications and interactions with the environment around us are analogical. Therefore, the implemented digital systems need a digital representation of the input analog signals before being processed and perform any calculation with it. In this case, an Analog-to-Digital Converter (ADC) is required. Moreover, if the digital system needs to interact and respond to its environment, a Digital-to-Analog Converter is also necessary (DAC).

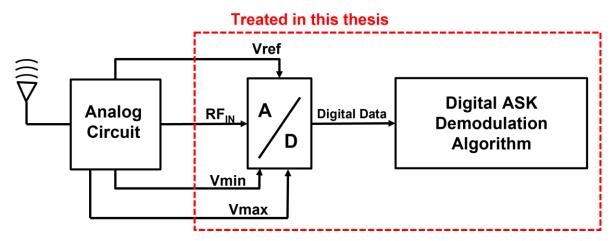

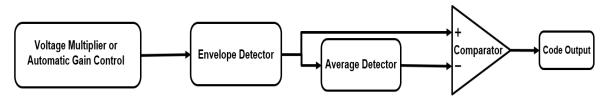

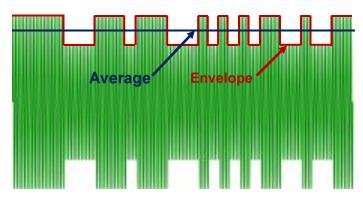

As explained in the introductory chapter, this thesis is focused on proposing a novel digital ASK demodulation solution. It is known that any ASK demodulation system in smartcards, needs some fundamental analog modules in order to recover energy, avoid overvoltage peaks, adapt the load connected to the antenna and adjust the amplitude of the "RF input" (RFin) signal for being used by the demodulation circuit. As shown in Figure 1, if a digital demodulation solution is employed, the analog module must provide the minimum and maximum amplitude levels of RFin, and the voltage references that will be used by the ADC module for a correct analog-to-digital conversion. Finally, the symbol recognition is done thanks to a digital demodulation algorithm.

Figure 1: Generic diagram of a digital demodulation system.

The Figure 1 presents a simplified diagram of a digital ASK demodulation system. This thesis is focused on offering a novel ADC solution, using an *EB-ADC* that produces a reduced number of samples, and proposing an adapted digital ASK demodulation solution for processing such samples. The asynchronous circuits are

known to be suited for event-based systems because they are designed to react to any incoming events and stay idle in between.

In this context, the main addressed subjects in this thesis are the development of an **event-based ADC** and a **digital asynchronous ASK demodulator circuit**. The analog circuit parts have not been considered in this thesis. Another team, expert in analog design, should develop this task later.

For the evaluation of the *EB-ADC*, which is composed by a level-crossing detector and a *TDC*, we first review the state of art of the "Level Crossing Sampling Schemes" (LCSS) and the basic theory of non-uniform sampling. Then, for the assessment of the TDC, we present some of the related state of art research made by the colleague of the CDSI team at TIMA Laboratory, Assia EI Hadbi, during her PhD. The study of the TDC alternatives permits us to find a simple and adapted solution for time stamping data produced by the *EB-ADC*. Then, the state of the art of asynchronous circuits is studied in order to find an event-driven digital technique for executing the demodulation algorithm. Moreover, the basic asynchronous elements have been studied, such as the C-elements (or muller gate) and the linear and non-linear asynchronous flow elements of a controller circuit. The latter allows us to understand how an asynchronous circuit is created. Finally, the ASK modulation and the NFC protocol are revised, showing its basic concepts and solutions, some definitions, and the state of the art of a few digital ASK demodulators.

# 2.2 Event-based Analog-to-Digital Converter (EB-ADC)

An ADC module is a system providing a digital representation of an analog signal, evaluated on each sample instant. An EB-ADC is a particular type of ADC that captures a sample when a reference voltage level is crossed. The analog signal is digitized on each level crossing, which produces a quantized value representing the time interval between two successive samples. In that particular case, the position and the number of reference voltages should be smartly chosen in order to obtain an appropriate representation of the signal, while generating a minimum number of samples. The next section reviews the theory of non-uniform sampling, the basis of the Level Crossing Sampling Scheme (LCSS) and finally gives some examples.

# 2.2.1 Non-Uniform Sampling and Level Crossing Sampling Scheme (LCSS)

#### 2.2.1.1 Uniform and non-uniform sampling ADC

As expressed before, when a digital system interacts with an analog environment, the use of an ADC is necessary. Normally, ADC are based on a regular sampling scheme, using a "Sample and Hold" (S/H) technique, as shown in Figure 2. In this case, to ensure that all the information of the bandwidth-limited (or band-limited) input signal has been captured by this sampling technique, the sampling rate should follow the Shannon theorem, as presented in Equation 2-1. It establishes that the sampling frequency ( $f_s$ ) should be more than twice the maximum frequency of the signal ( $f_{max}$ ).

$$fs \ge 2 \cdot f_{max}$$

Equation 2-1: Shannon theorem

Figure 2: Regular Sampling Scheme Example

If we consider an ideal clock that defines the sampling rate, and an ideal *S/H*, the system will be very precise for getting the time instants of each sample. However, it will incorporate a quantization error due to the noise added during the analog to digital

$$SNR_{dR} = 1.76 + 6.02 \cdot N$$

Equation 2-2: Signal-to-noise ratio due to quantization error of regular sampled ADC.

conversion. In this case, the signal-to-noise ratio (SNR), defined in Equation 2-2 [9], depends on the effective number of bits N of the converter.

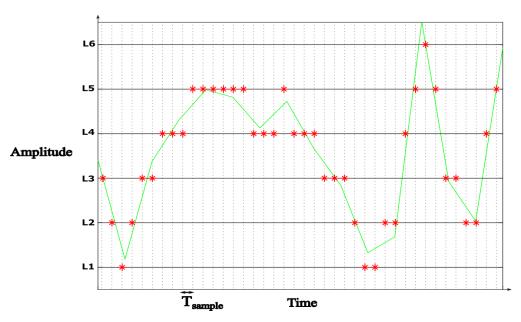

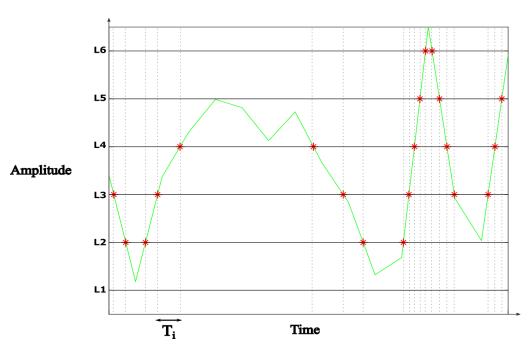

On the other hand, also non-uniform sampling scheme ADC exists. In that kind of ADC, the conversion is triggered at each level crossing, as depicted in Figure 3.

Thus, the system is very precise for obtaining the equivalent voltage level of each sample ( $L_i$ ). However, there will be a measurement error of the time elapsed between

Figure 3: Irregular Sampling Scheme Example

two consecutive samples ( $T_i$ ), which depends on the precision of the Time-to-Digital Converter (TDC). As stated in [10] - [11], if we define the precision of the TDC as  $T_c$ ,

each sample ( $S_i$ ) will be identified with the pair ( $L_i$ ,  $T_i$ ), where  $T_i$  has an associated error  $\Delta t$ , which belongs to the interval [ $0,T_c$ ].

Using the quantization noise power definition  $P(\Delta V)$ , we can estimate the signal-to-noise ratio (SNR<sub>dB</sub>) of the quantization process of a non-uniform sampling ADC, stated in the following equations:

$$\begin{split} P(\Delta V) &= P\left(\frac{dV_{in}}{dt}\right) \cdot P(\Delta t) & \text{(Quantization noise power)} \\ SNR_{dB} &= 10 \cdot \log\left(\frac{P(V_{in})}{P(\Delta V)}\right) & \text{(Generic SNR equation)} \\ P(\Delta t) &= \frac{T_C^2}{12} & \text{(Power of a random variable uniformly distributed across [0, Tc])} \\ SNR_{dB} &= 10 \cdot \log\left(\frac{12 \cdot P(V_{in})}{P\left(\frac{dV_{in}}{dt}\right)}\right) + 20 \cdot \log\left(\frac{1}{T_C}\right) & \text{(Quantization noise power)} \end{split}$$

Equation 2-3: Equations defining the Signal-to-noise ratio due to quantization of an irregular sampled ADC.

Equation 2-3 was originally proposed in [10] and then was corrected in [12]. Its first term can be defined by statistical properties of the input signal V<sub>in</sub>, and the second term is only dependent on the timing precision of the TDC (T<sub>C</sub>), and does not depend on the voltage quantization as in the uniform sampling case. Then, we can state that the SNR of an EB-ADC can be improved by *6.02 dB* when the TDC precision is improved to the double (i.e.: T<sub>C</sub> divided by 2).

The following table shows the main characteristics of a regular sampled ADC versus an irregular sampled ADC.

|                    | Uniform sampling | Non-uniform sampling |

|--------------------|------------------|----------------------|

| Conversion Trigger | clock            | level crossing       |

| Amplitude          | quantized        | exact value          |

| Time               | exact value      | quantized            |

| SNR dependency     | number of bits   | TDC precision        |

| Converter output   | amplitude        | amplitude and time   |

Table 1: Characteristics of regular v/s irregular sampled ADC.

#### 2.2.1.2 Beutler theorem

For non-uniform sampling ADC systems, another important aspect to consider is the condition for ensuring the correct reconstruction of the original signal. B. J. Beutler demonstrates in [13] that if the average sampling rate  $\overline{f_s}$  is greater than twice the signal maximum frequency  $f_{max}$  (signal bandwidth), the original signal can be reconstructed.

### 2.2.1.3 Conventional EB-ADC

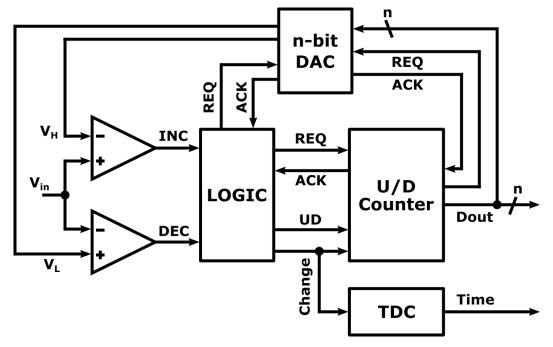

As shown in [14] - [10] - [12] and many other research works, the conventional solution for an "Event-Based ADC" (EB-ADC) or "Level-Crossing ADC" (LC-ADC) is the one presented in Figure 4, that is composed of two comparators, an n-bit digital-

Figure 4: Conventional solution for EB-ADC, sometimes called "floating window Level Crossing-ADC".

to-analog converter (DAC), an up/down counter, a TDC and a control logic. It is also called "floating window LC-ADC". This solution has been proven to correctly work in many articles. However, it can be high power consuming since the comparators consume permanently, and they support a full-scale input dynamic range. Additionally, the DAC contains either resistor chains or capacitor arrays, increasing its consumption for a smaller quantization level, and finally the TDC requires a higher power consumption when improving its precision.

In the floating window LC-ADC of Figure 4,  $V_H$  and  $V_L$  are two consecutive quantification levels obtained from the DAC, adapting its values for following the analog input signal  $V_{in}$ . For a proper operation,  $V_{in}$  must be permanently bounded by  $V_L$  and

$$q = \frac{V_{range}}{2^M - 1}$$

Equation 2-5: Calculation of the quantification step (or LSB).

$V_H$ . The gap between these values is called the comparison window and is always equal to one *LSB* (*less significant bit*), also denoted as q, the quantification step. If  $V_{range}$  is the amplitude range of a M-bit resolution LC-ADC, with  $2^M$  comparison levels uniformly distributed in  $V_{range}$ , then each comparison level corresponds to q. The following equation presents the calculation of q.

Then, if  $V_{in}$  is higher than  $V_H$ , INC=1, DEC=0, and UD=1, indicating the up/down counter to count up. In the opposite situation, if  $V_{in}$  is lower than  $V_L$ , INC=0, DEC=1, and UD=0, indicating the counter to count down. In both cases, the Change signal is generated, indicating the TDC to stop and store the current measurement, and reset the TDC to prepare it for the next measurement. At the same time, the counter output is connected to the n-bit DAC for generating the new values for  $V_L$  and  $V_H$ , producing a loop feedback for updating the system on each level crossing of  $V_{in}$ . The example showed in Figure 4 incorporates asynchronous handshake signals, REQ and ACK interconnecting the communication of LOGIC, U/D Counter and DAC modules, for indicating each other when each stage calculation has finished, when a new data is available and if each module is available or busy. This method avoids the usage of a clock signal and therefore an unnecessary activation of the system.

Another important aspect to consider when designing this kind of solutions, is the so-called "tracking condition". This condition ensures that the  $V_{in}$  signal will not cross any quantification level within any loop feedback delay, denoted  $\delta$ , and particularly the worst case, been  $\delta_{max}$ . The latter guarantees to capture every level crossing event. The Equation 2-6 presents the tracking condition calculation, considering the dynamic range  $V_{range}$ , the signal bandwidth  $f_{max}$  and the converter resolution M.

$$\max\left(\frac{\partial V}{\partial t}\right) \cdot \delta_{max} \leq \frac{V_{range}}{2^M - 1} = q$$

$$\max\left(\frac{\partial V}{\partial t}\right) = 2 \cdot \pi \cdot f_{max} \Rightarrow \delta_{max} \leq \frac{V_{range}}{2 \cdot \pi \cdot f_{max} \cdot (2^M - 1)}$$

Equation 2-6: Tracking Condition.

### 2.2.2 Time-to-Digital Converter (TDC)

A time-to-digital converter (TDC) is a device permitting to measure the time elapsed between a *start* and a *stop* signals. The TDC are used in many fields where

a precise measure of the time is required, as time-of-flight devices, particle physics systems, tracking and positioning techniques, among others. Its capability of providing a digital representation of the time enables its integration in large digital systems implemented in an ASIC CMOS chip or even being previously tested in a "Field-Programmable Gate Array" (FPGA) device.

As stated in the thesis work of our colleague, Dr. Assia El Hadbi [15], a first generation of TDC was mainly analog. The most basic analog technique was the controlled charge of a capacitance, for then using an ADC to measure the final voltage, and hence estimate a digital representation of the time elapsed between the charge activation (start) and deactivation (stop), as depicted in Figure 5.

Figure 5: Basic analog TDC technique.

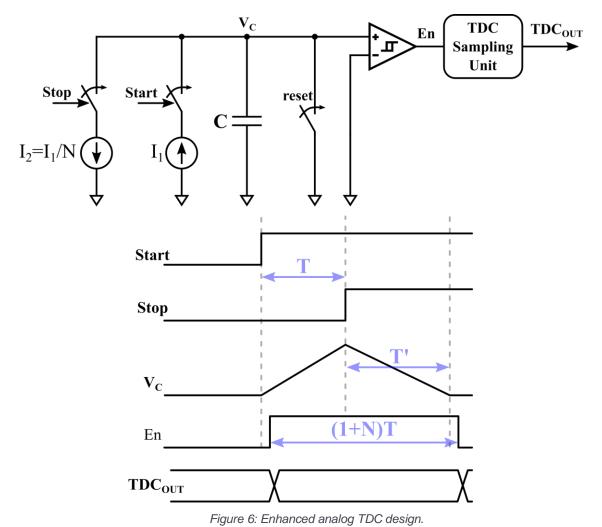

Figure 6 shows another analog solution that improves the latter, for avoiding using an ADC. It uses two current sources, one charging the capacitance, and the second one discharging it. Then, a zero-crossing element is used to detect the full discharge of the capacitance. Finally, a "TDC sampling unit", associated to a stable clock reference, registers the number of cycles during this process.

The analog TDC can reach a time resolution of tens or hundreds of picoseconds. However, they suffer from many issues. They are quite sensitive to temperature drift, not suitable for fast applications and they normally use an averaging procedure for calibration and for improving their time resolution. In addition, these TDC require a large area because of the use of capacitors, hence having more power consumption in comparison to a basic digital TDC solution, and also being less favorable for the technology shrink.

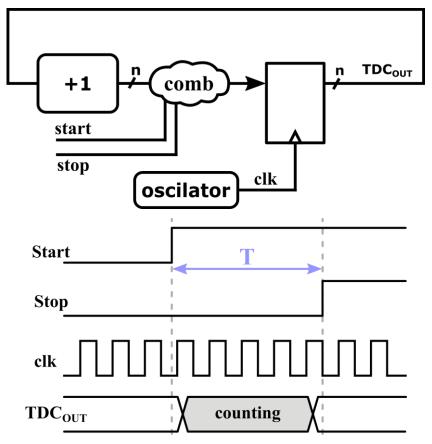

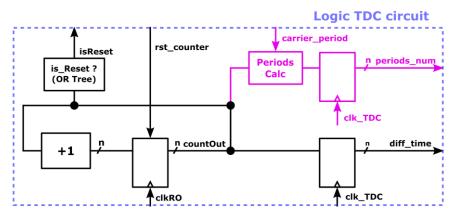

The second generation of TDC use full-digital techniques. The simplest TDC architecture corresponds to the use of a timer permitting to count the number of rising edge occurrences of a reference clock signal, between the activation of a start and a stop signal, see Figure 7. This solution is simple and compact, compared to the other solutions.

Figure 7: Digital TDC design: Counter TDC.

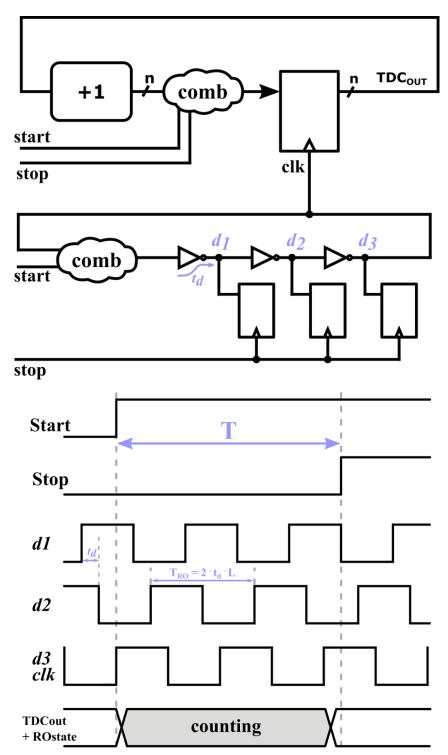

In order to improve the time measurement precision, another digital solution has been proposed, using an internal Ring-Oscillator (RO) as a clock reference to form a similar system to that proposed in Figure 7. Moreover, as depicted in Figure 8, it adds the registration of the final state of the looped signal after propagating through the inverter gates within the RO. If the delay of the inverter gates is known, the registered information is used to infer the number of inverters that has been crossed between the start and stop signals and, then, use the inverter gates delay for increasing the precision of this TDC. This solution is limited in precision by the delay of the gate used in the RO and changes when switching from one technology node to another one. In addition, this delay will evolve after fabrication due to the aging effect, and will also vary with the "Process, Voltage and Temperature" (PVT) conditions.

Figure 8: Enhanced digital TDC design.

### 2.3 Asynchronous Circuits

### 2.3.1 Synchronous circuits

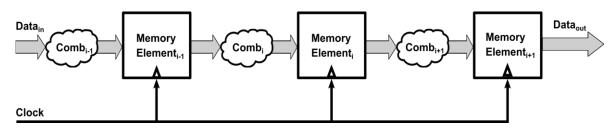

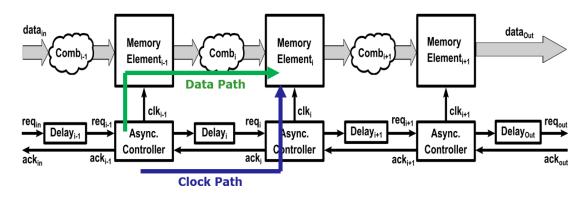

Digital electronic circuits are devices containing several logic gates executing operations and tasks. Normally, these circuits are composed by several pipeline stages, defining a structured sequence of data transmission. Each pipeline is composed by two main modules, a combinatorial stage and a register stage, as shown in Figure 9. In this figure, we present the synchronous circuit model in the simplest configuration case: the linear pipeline.

Figure 9: Synchronous linear pipeline example.

### 2.3.2 Synchronous method

Synchronous circuits are globally synchronized circuits, which use a global reference clock signal for activating all the register stages simultaneously. This clock defines the transmission instant, when the result of each pipeline stage is sent to the combinatorial inputs of the next stages. For the proper operation of this type of systems, all the combinational blocks of the circuit need to complete and stabilize its calculations within the clock period, in order to ensure that the resulting values saved in the registers are correct, and free of metastability or hazard. Due to the usage of a global clock, the clock period must be larger than the slowest combinational path between two registers on the whole circuit, which is called "the critical path".

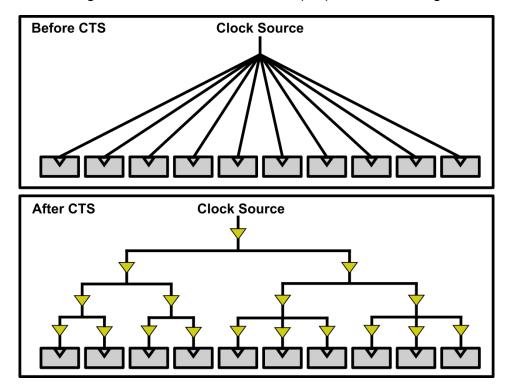

Then, for ensuring the right transmission and memorization of the data in the circuit, all of its registers must theoretically receive the clock signal at the exact same time. The latency or delay between the reference clock rising edge, and its arrival on the register clock input, is called "skew". For guaranteeing a minimal skew in all the registers of the circuits, the construction of a well-balanced clock-tree, called "Clock-

*Tree Synthesis" (CTS)* is necessary, which is composed by balanced buffers and inverters. The design of a standard "Clock Tree" (CT) is shown in Figure 10.

Figure 10: Example of a standard Clock-Tree.

The addition of the logical gates of the *CT* increases the area of the circuit and the complexity of the "Place and Route" (P&R) steps in the digital design flow. Moreover, as explained in [16] - [17], the clock propagation contributes between 20% to 45% of the total power consumption of a digital circuit. Additionally, the synchronous circuits require an oscillator (Phase Locked Loops or Delay Locked Loops) for the generation of the global reference clock. This oscillator normally requires the use of a large silicon area, negatively impacting the circuit cost. This constraint might be avoided if using a system that does not need it, like asynchronous circuits. Furthermore, the synchronization of the register activation of an entire circuit produces important electromagnetic noise emissions at the fundamental frequency of the clock, but also at its harmonics. These latter can cause huge interferences in wireless communications. Moreover, when evaluating the I-R drop and the power supply constraints of a circuit, this global register activation can also cause an important power supply reduction in the middle of the power lines, which might affect the correct operation of the digital circuit.

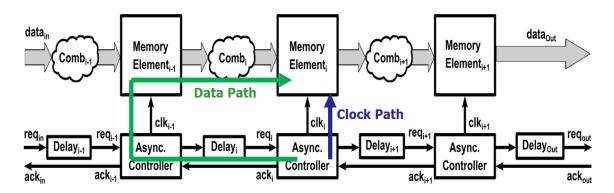

## 2.3.3 Asynchronous method

For mitigating the issues due to a global synchronization of the digital circuits, the researchers and designers have been working for decades on an alternative based on asynchronous circuits. The asynchronous logic has been introduced by the researchers during the 50's. In some articles, they analyzed the behavior of a circuit combining combinational circuits with the application of some delays between its outputs and its inputs, for establishing "secure" feedback loops [18].

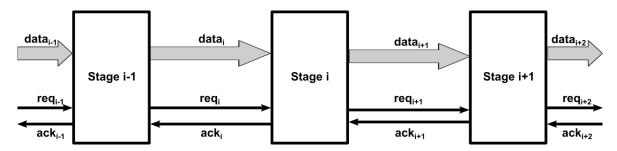

A sequential circuit is called "asynchronous", when a local handshake protocol is used to indicate when the calculation in a pipeline stage is finished, and when valid data at the input of its registers are ready to be transmitted to the inputs of the combinatorial part of the next pipeline stages. This protocol also indicates whether the next stages are available or not to receive new input data to process. If one or more of these stages are busy, the data transmission is stopped, blocking the following circuit stages subsequently.

Figure 11: Asynchronous linear pipeline example.

When analyzing the case of Figure 11, *stagei* receives a request, indicating that new valid data are available at the input of its registers. Next, if *stagei+1* is available, the *stagei* saves the data in its registers and it sends a request forward to *stagei+1* and an acknowledgment backward to *stagei-1*, indicating that the data has been processed. It is now ready for a new data transaction. This method activates a stage only if there is new data to process and stays idle otherwise. This technique allows only consuming dynamic power on the active parts of the circuit.

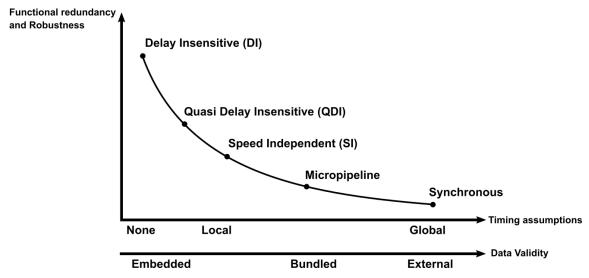

Varying on the signaling and data encoding convention, the asynchronous circuits are categorized in the following circuit classes [19]:

- Huffman circuit.

- Speed Independent circuit (SI).

- Quasi-Delay-Insensitive circuit (QDI).

- Delay Insensitive (DI).

- Micropipeline.

The Figure 12 represent the different types of asynchronous circuits in terms of their timing assumptions and their functional redundancy and robustness.

Figure 12: Classification of asynchronous circuits.

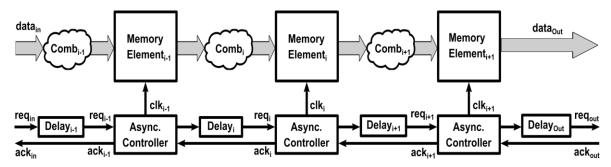

In asynchronous circuits the two most commonly used data encoding are bundled-data (micropipeline) and multi-rail encoding (embedded in data - *QDI*). Furthermore, the two most widely used handshake protocol are the two-phase protocol and the four-phase protocol.

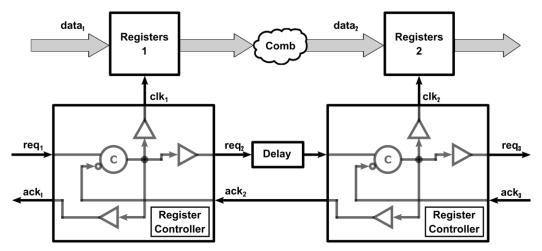

In this manuscript, only the four-phase, bundled-data micropipeline asynchronous circuits are used and hence reviewed. Therefore, only these concepts will be studied in the state of the art of this document. For these kinds of circuits, the data path remains similar to synchronous circuits, and only the globally distributed clock signal is replaced by a controller module that generates the clock signal at each pipeline stage as shown in Figure 13. The bundled-data micropipeline circuit used in this thesis is based on four-phase handshake protocol controllers.

Figure 13: Bundled-data micropipeline linear example.

#### 2.3.4 Bundled-data encoding

As explained before, asynchronous circuits use a local handshake protocol to indicate when a new data has arrived thanks to a request signal, and when the calculation has been done through an acknowledgment signal. For ensuring a correct synchronization between different pipeline stages in the circuit, request signals are associated to data in the system. In this manuscript, we used the bundled-data encoding for this purpose.

As shown in Figure 13, in bundled-data circuits, each pipeline is decomposed into a combinational module and a memorization module, normally composed by registers or latches. Additionally, each bit is binary encoded, and on each pipeline stage, the data validity is signaled by a dedicated request signal. Moreover, the asynchronous controllers are in charge of generating the local clock signals for indicating, to all the memory cells of the pipeline, the instant when capture and save the local data. Therefore, the request on each stage should arrive to the input of its associated asynchronous controller only when the data in the combinational part have been processed. For ensuring that the combinational computations have been treated, a delay module is inserted into the request line with a value larger than the worst combinational delay, commonly called "local critical path". Furthermore, the acknowledgement signal, normally indicating the end of the computation of the combinational part of the pipeline stage, is generated by the controller just after each switching of the clock signal.

#### 2.3.5 Four-phase handshake protocols

A protocol is the definition of a communication sequence permitting to send data from one point to another point of a circuit, network, bus, or any communication channel. In the case of asynchronous circuits, a handshake protocol set the basis for defining a synchronized approach to propagate data from one pipeline (or memorization stage) to the next one without any metastability or corruption of the data. Two essential characteristics differentiate the handshake protocols: the used data encoding and the data transfer sequence. In literature, several protocol implementations have been proposed [20]. These solutions are classified in two main categories, the two-phase protocols and the four-phase protocols. The first, also called "Non-Return-to-Zero" (NRZ) protocol, performs a complete data transfer in two steps.

On the other hand, the latter, also called "Return-To-Zero" (RTZ) protocol, needs four steps to achieve a complete data transfer, and is called RTZ because the request and acknowledgment signals must be cleared before a new data is allowed to be sent.

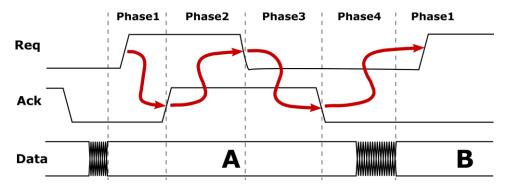

The Figure 14 describes an example of the cycles of a four-phase protocol.

Figure 14: Four-phase handshake protocol example.

- **Phase 1:** It begins when the sender enables a new data on its outputs and sets the request signal for indicating that a valid data A is available. Then the request *(reg)* signal takes some delay to arrive to the receiver interface.

- **Phase 2:** It starts when the receiver identifies the arrival of the rising edge of the *req* signal, processes the received data and sets the acknowledgment *(ack)* signal, for indicating to the sender that the data has been treated.

- **Phase 3:** It begins when the sender detects the rising edge of the *ack*, and then resets its *req* signal. This phase is called *Return To Zero (RTZ)*.

- **Phase 4:** It starts when the receiver identifies the falling edge of the *req*, then it resets the *ack* for indicating that it is now ready to receive a new data. This phase will stay active until the new data *B* is valid, and a new *req* is sent.

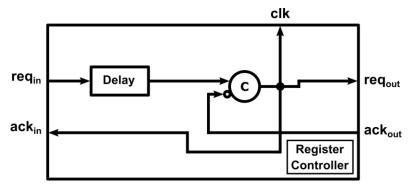

The simplest circuit implementation of a four-phase protocol is the frequently called "Weak-Conditioned Half-Buffers" (*WCHB*). In the case of a bundled-data micropipeline implementation of WCHB, the asynchronous register controller of Figure 13 is only composed by a Muller-gate (or also called C-element) and an inverter, as depicted in Figure 15.

Figure 15: WCHB bundled-data micropipeline asynchronous register controller implementation.

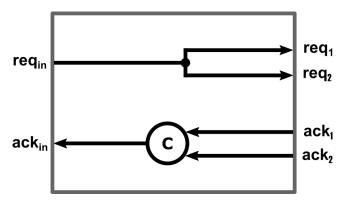

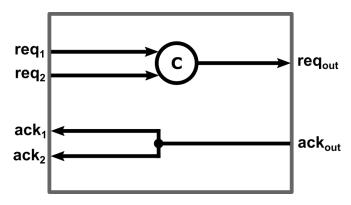

The controller of Figure 15 is called a *register controller* since it controls the activation instant of its associated memory block. From the asynchronous point of view, the register controllers are classified as "linear", because they allow the control of one data channel at its input, and one data channel at its output. They can be connected in series forming a linear structure, as depicted in Figure 13, for controlling the data transmission of a linear circuit, as for example a FIFO queue.

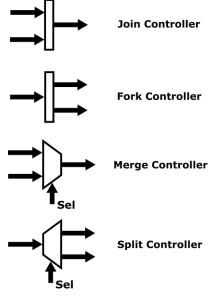

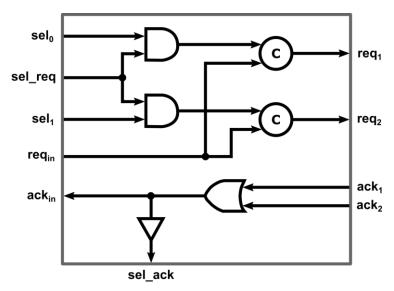

In a real circuit, many data channel interactions occur. In cases when various input signals enter one module, when one output is connected to several modules, or when conditional channel flow is required, non-linear structure controllers are needed to ensure a correct data transmission and avoid metastability issues. The list of these structures is presented below:

- Fork: is an unconditional asynchronous flow element with one input channel and several output channels. The event token is propagated from its input to all of its outputs.

- <u>Join:</u> is an unconditional asynchronous flow element with several input channels and one output channel. The event token is only propagated to the output after all the input tokens have arrived.

- Split: is a conditional asynchronous flow element with one input channel and various output channels. The event token in its input will only be propagated to one of its selected outputs, according to the selection value, only after the selection token has also arrived.

- Merge: is a conditional asynchronous flow element with multiple input channels and one output channel. After the selection token arrives, the input event token in the selected input channel, according to the selection value, will be transmitted to the output channel.

Figure 16: Symbol representation of the most common non-linear asynchronous flow elements.

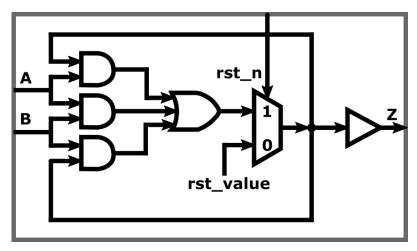

#### 2.3.6 Muller Gate

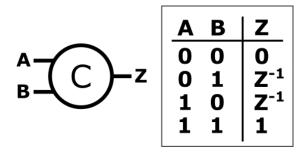

The muller gate, also called C-element, has been introduced by David Eugene Muller in 1963 [21]. The C-element is the basic element enabling the implementation of most of the known asynchronous control circuits. This gate switches its output to a value, only if all its inputs have the same value. Otherwise, if its inputs are different, the output is maintained to its previous state. This behavior facilitates the synchronization of its output with some of its inputs, which is the basic operation concept of the handshake protocol in asynchronous circuits.

When muller gates are implemented in a control protocol circuit, the previous behavior permits the validation of the arrival of several signals on its inputs before enabling the transmission of the output validation to the next stages.

The most basic implementation of Muller gate possesses two inputs and one output, as depicted in Figure 17.

Figure 17: Muller gate symbol and its truth table.

The logic equation representing the behavior of a basic two-input Muller gate is presented in the following equation:

$$Z = A \cdot Z^{-1} + B \cdot Z^{-1} + A \cdot B$$

Equation 2-7: Logic equation representing a Muller gate.

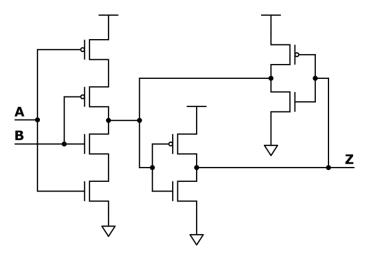

This behavior can be implemented using a transistor level design or with logic gates. The first option is more optimized in terms of size and speed. However, this gate is not usually distributed in commercial design kits (DK), so it must be manually created and characterized for every used technology node. The Figure 18 shows the most basic implementation of a C-element, called "weak-feedback", introduced by A.J. Martin in 1989 [22]. Other more complex implementations are presented in [23].

Figure 18: Transistor level design of a weak-feedback muller gate.

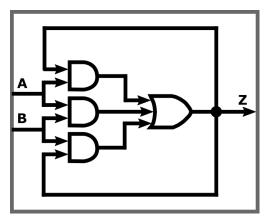

On the other hand, Figure 19 presents one of the possible implementations of a Muller gate using standard cells. Another typical implementation of the C-element is using a three-input Majority gate (MAJ3), with its output feedback connected to one of its inputs.

Figure 19: Muller gate implementation using standard cells.

A *set* or *reset* signals are normally necessary to initialize the state of the Muller gate.

# 2.3.7 The advantages of micropipeline Asynchronous Circuits

As depicted before, micropipeline asynchronous circuits are composed by several pipeline stages connected to each other in the same way as standard synchronous circuits. However, instead of using a global reference clock, asynchronous circuits implement, on each pipeline stage, a local clock ensuring a correct sampling of the data on its flip-flops (registers). The period of each local clock is locally determined by its combinational block delay. Moreover, the implicit behavior of asynchronous circuits could be assimilated to a fine-grained clock gating approach, because the memory elements are only clocked when necessary. The resulting benefits related to the use of asynchronous approach are described in the following chapters.

#### 2.3.7.1 High performance

The average processing delay for an asynchronous circuit varies on the distinct input combinations. Every input combination activates different paths of the systems, therefore varying the input-to-output delays. This occurs because the data propagation on each pipeline stage depends on the local pipeline critical-path, and not on the global critical-path as in synchronous circuits. Finally, it is stated that the circuit operating speed is the average of the local delays, and also, the average of the total delays

depending on the inputs of the system. Normally this results in a higher performance compared to the same synchronous solution.

#### 2.3.7.2 <u>Low power consumption</u>

In synchronous circuits, all the memory elements of the circuit are activated at the same time. For obtaining such a behavior, the synthesis of a Clock-Tree is necessary, as stated in chapter 2.3.2. The construction of that structure requires several synchronization elements, using a large circuit area, but also an important power consumption. On the other hand, when implementing an asynchronous approach, only local *CT* are necessary, reducing the number of synchronization elements, and thus considerably reducing the power consumption while ensuring a correct data transmission synchronization.

In low-power synchronous design, the use of clock-gating technique is very common. In asynchronous circuits, this behavior is already implicit, and is normally more energy efficient than the normal clock-gating method. Indeed, if no new data is arriving to the circuit inputs, it will stay in an idle or inactive state, consuming only static power.

In the context of reducing the power consumption, voltage scaling is a very effective technique that is commonly used in the industry. Reducing the power supply voltage decreases the dynamic power consumption, while lowering also the performance of the circuit. Implementing such a method in synchronous circuits requires an adjustment of the clock frequency for preventing timing violations and metastability. These constraints increase the design complexity, needing supplementary blocks for sensing the voltage changes and then applying the correct frequency adjustments. Conversely, in asynchronous designs this adaptation is naturally done. When the power supply voltage decreases, the propagation delays of the combinational parts increase. Therefore, in bundled-data systems, the delay associated to each pipeline stage will accordingly increase, while maintaining the correct timing constraints.

In some applications, the use of several clock domains is vital to reduce the power consumption. The direct synchronization of the different clocks used in this kind of design is not feasible. In that case, it is essential to use some elements to interface the communication between the different clock domains, augmenting the area usage and

the complexity of the specifications to take into account for avoiding errors in the design.

#### 2.3.7.3 Low electromagnetic emissions

As explained before, synchronous circuits use a global reference clock signal for activating all their memories (flip-flops, latches) at the same time, in order to control a correct data transmission in the circuit. When applying such solutions in wireless communications, a strong source of electromagnetic noise is the circuit itself, hindering the transmission. The synchronized register activation produces high current peaks matching the clock period. This effect results in an electromagnetic noise at the frequency of the clock and its harmonics, affecting the wireless communication performance.

In contrast, an asynchronous circuit activates its memory elements at different moments, depending on the local critical path delay of each pipeline stage. In that case, the current peaks are spread in time, resulting in lower electromagnetic noise emissions. In addition, in the PhD research work of our colleague *Sophie German* at STMicroelectronics and TIMA Laboratory [24], it has been proved that the electromagnetic emissions of a digital circuit can be controlled using the bundled-data asynchronous methodology. This approach allows fitting a frequency mask, which is used to avoid affecting the surrounding wireless communication.

### 2.4 Conclusion

In this chapter, we described and reviewed the state of the art of the two main blocks treated in this thesis, the EB-ADC and the ASK demodulator.

The EB-ADC is composed by a level-crossing detector and a TDC. It performs a non-uniform sampling, for which we have first reviewed its theoretical basis in order to find a minimum LCSS and, then, we have presented EB-ADC examples found in the literature. For the TDC, we reviewed several implementations found in the literature in order to evaluate which alternative could be best suited for our application.

Then, we checked the characteristics of synchronous and asynchronous circuits, highlighting their differences and checking why asynchronous circuits might be better adapted for the ASK demodulator application in NFC tags. Next, the bundle-data encoding was revised, showing the operation of the four-phase handshake protocol, which is the asynchronous approach we decide implementing for the proposed

solutions. For that methodology, the basic blocks used in the asynchronous control circuits have been presented, including two different possible solutions for the design of the C-element, which is a required gate for creating the different modules of the control circuit.

Finally, we reviewed the advantages associated to the micropipeline asynchronous circuits, highlighting the possibilities to reduce the power consumption when decreasing the number of activations of the circuit, implementing only local clock-trees, enhancing its voltage scaling capabilities and the elimination of the clock oscillator (PLL or DLL). Moreover, asynchronous circuits offer some possibilities to increase the performance of the circuit compared to its synchronous counterpart. Finally, we reviewed its advantages to reduce the electromagnetic emissions when controlling the delays of the pipeline stages. It is even possible to fit an electromagnetic spectral mask.

# **3 NFC Communications**

#### 3.1 NFC demodulation

#### 3.1.1 NFC protocol

The Near-field communication (NFC) is a short-range wireless communication protocol, widely used in our daily life in several applications, as public transport validation, contactless payment cards, access cards, and even in some medical devices like pacemaker prototypes. This technology is based on the existing radio-frequency identification (RFID) standards like ISO/IEC 14443, for type A and type B, and Felica for type F. The operation frequency of NFC is the unlicensed radio frequency ISM band of 13.56 MHz, which is part of ISO/IEC 18000-3 air interface standard. This protocol normally requires a separation of less than 10 cm between two NFC devices, defined as the initiator and the target, to communicate at bitrates going from 106 kbps up to 848 kbps, and beyond for some specific cases. The different NFC standards define the modulation schemes, coding, transfer speeds and frame structure of the RF protocol enabling the communication between NFC devices. Table 2 presents the different types of NFC tags and their characteristics.

Table 2: NFC tag types and their main characteristics.

|                               | Type NFC-A          | Type NFC-B          | Type NFC-F         |

|-------------------------------|---------------------|---------------------|--------------------|

| Supported                     | ISO 14443 A         | ISO 14443 B         | JIS X 6319-4       |

| Standard                      |                     |                     | (Felica)           |

| Carrier                       | 13.56 MHz ± 7 KHz   |                     |                    |

| Frequency                     |                     |                     |                    |

| Data Rate                     | 106/212/424/848     | 106/212/424/848     | 212/424/848 Kbps   |

|                               | Kbps                | Kbps                |                    |

| Modulation                    | ASK 100%            | ASK 10%             | ASK 10%            |

| (Reader to Tag)               |                     |                     |                    |

| Data Encoding                 | Modified Miller     | NRZ-L               | Manchester         |

| (Reader to Tag)               |                     |                     |                    |

| Modulation<br>(Tag to Reader) | Load Modulation     | Load Modulation     | Load Modulation    |

|                               | (ASK) with sub-     | (BPSK) with sub-    | (ASK) without sub- |

|                               | carrier (± 848 Khz) | carrier (± 848 Khz) | carrier            |

| Data Encoding                 | Manchester          | NRZ-L               | Manchester         |

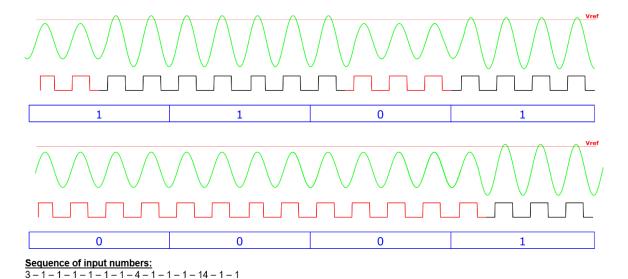

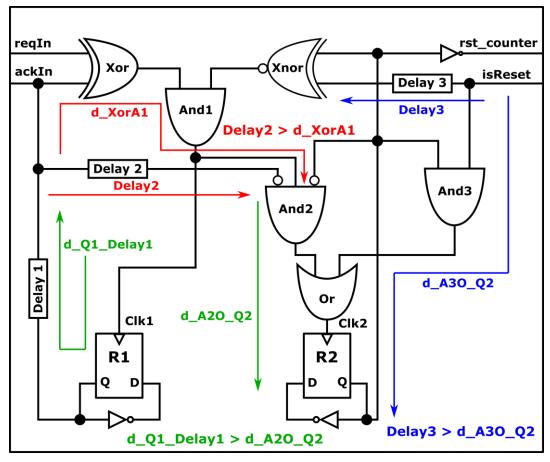

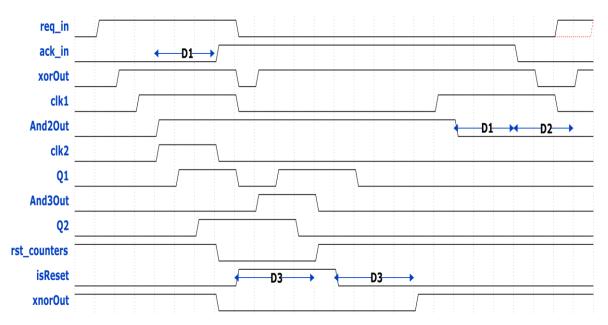

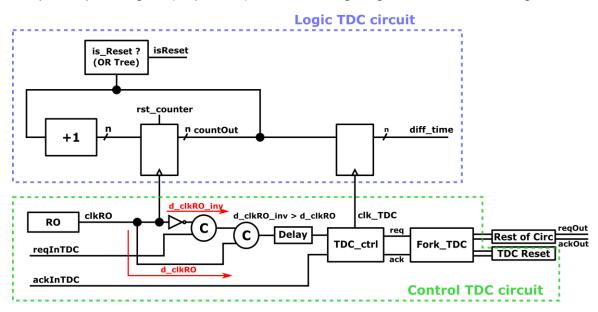

| (Tag to Reader)               |                     |                     |                    |