# Analysis, modelling and reduction of the simultaneous switching noise generated by the high data rate IOs of a STM32 microcontroller

Mélanie Moign

#### ▶ To cite this version:

Mélanie Moign. Analysis, modelling and reduction of the simultaneous switching noise generated by the high data rate IOs of a STM32 microcontroller. Electromagnetism. Université Côte d'Azur, 2022. English. NNT: 2022COAZ4027. tel-03710393

## HAL Id: tel-03710393 https://theses.hal.science/tel-03710393

Submitted on 30 Jun 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ÉCOLE DOCTORALE

SCIENCES

FONDAMENTALES

ET APPLIQUÉES

Analyse, modélisation et réduction du bruit de commutation simultanée généré par les interfaces d'Entrées/Sorties haute vitesse dans les microcontrôleurs STM32

## Mélanie MOIGN

Polytech'Lab - Université Côte d'Azur 7498

Présentée en vue de l'obtention du grade de docteur en Sciences

Pour l'Ingénieur

d'Université Côte d'Azur

**Dirigée par** : Gilles Jacquemod **Soutenue le** : 19 Avril 2022

Devant le jury, composé de :

Président du Jury et rapporteur :

Pascal Nouet, Professeur, Université de Montpellier

Rapporteur:

Luc Hebrard, Professeur, Université de Strasbourg

**Examinateurs:**

Laurent Fesquet, MCF-HDR, Université de Grenoble

Yves Leduc, Pr associé, UCA Nice

Jean-Pierre Leca, Ingénieur, STM Rousset Gilles Jacquemod, Professeur, UCA Nice

## Analysis, modelling, and reduction of the simultaneous switching noise generated by the high data rate IOs of a STM32 microcontroller

This thesis has been accomplished in the frame of a "Cifre convention" between the laboratory Polytech'lab and the company STMicroelectronics and is centered on the domain of electromagnetic compatibility (EMC). The rapid and constant evolution of microcontrollers (MCU) and the increase of their performance has led to an important degradation of their behavior regarding the EMC. For example, the Simultaneous Switching Noise (SSN) is a subject known since the 80s but that became a source of failure through the years because of, among other things, the increase of communication signals frequency. This thesis is focused on the study of this SSN effect in the constrained environment of the STM32. A modeling methodology of a complete system defined by the die, the package, and the Printed Circuit Board (PCB) has been validated thru a vast campaign of comparison between simulations and measurements. These simulations allow, on one hand, to investigate the root cause of a product failure and on the other hand, to observe the SSN effect to points that are physically unreachable in measurement.

This work allowed the definition of the main design rules to be applied to the chip, the package, and the PCB in order to improve the MCU robustness regarding the SSN effect. To conclude, this thesis presents a new development approach for designers with the use of a predictive model. This predictive model allows the anticipation of the future MCU behavior regarding EMC problematic and this, directly at the design stage. Considering the very fast evolution of the CMOS technology and therefore of the MCU, being able to anticipate these issues is a real advantage in the objective of being more competitive on the market with more robust and reliable products.

Keys words: Electromagnetic Compatibility (EMC), Input/Output interface (IO), Simultaneous Switching Noise (SSN), Autosusceptibility, Power distribution network (PDN), ICEM model, microcontroller modeling

# Analyse, modélisation et réduction du bruit de commutation simultanée généré par les interfaces d'Entrées/Sorties haute vitesse en technologie CMOS dans les microcontrôleurs STM32

Cette thèse réalisée dans le cadre d'une convention Cifre entre le laboratoire Polytech'Lab et la société STMicroelectronics, porte sur le domaine de la compatibilité électromagnétique (CEM). L'évolution continue et très rapide des microcontrôleurs (MCU) en vue de l'accroissement de leurs performances a malheureusement entrainé une dégradation importante de leur comportement vis-à-vis de la CEM. Par exemple, le bruit de commutation simultanée (BCS), connu depuis les années 80, est devenu une source de défaillance du MCU en raison notamment de l'augmentation des fréquences des signaux de communication. Cette thèse s'inscrit dans l'étude de ce phénomène au sein de l'environnement très contraint du microcontrôleur STM32. Une méthode de modélisation d'un système complet puce/boitier/circuit imprimé a été élaborée et validée par une importante campagne de comparaison entre mesures et simulations. Ces dernières permettent de pouvoir, d'étudier les principales défaillances d'un produit, et d'autre part observer l'effet du BCS à des endroits physiquement inatteignables en mesure.

Ce travail a permis de définir les principales règles de conception a appliquer sur la puce, le boitier et le circuit imprimé pour améliorer la robustesse du MCU au bruit BCS. Pour conclure, nous avons présenté une nouvelle approche de travail avec le développement d'un modèle prédictif permettant l'anticipation du comportement d'un futur MCU face aux problèmes de CEM, et cela, dès la phase de conception. Compte tenu de l'évolution très rapide de la technologie CMOS et des MCU, réussir à anticiper ces problèmes est un réel avantage pour pouvoir rester compétitif sur le marché avec des produits plus robustes et fiables.

Mots clés : Compatibilité électromagnétique, Auto-susceptibilité, Périphérique d'entrée/sortie, Bruit à commutation simultanée, Réseau de distribution d'alimentation, Model ICEM, modélisation

## Acknowledgments

This thesis work presented in this manuscript was carried out under a CIFRE agreement between the STMicroelectronics company and the laboratory Polytech'lab between 2017 and 2022. These years were incredibly enriching, both from a technical and a human point of view.

Firstly, I would like to express my gratitude to M. Gilles Jacquemod, director of the laboratory Polytech'lab for allowing me to carry out this thesis in his laboratory. I want to thank him for his perpetual support, his availability when I needed help -like for the redaction of this manuscript-. From the laboratory, I also thank M. Yves Leduc and M. Henri Braquet who helped me during this thesis.

I thank M. Jean-Pierre Leca, engineer evolving within the IO team of the MCD division of STMicroelectronics in Rousset, who supervised, helped and supported me during all this thesis. I also thanks M. Nicolas Froidevaux, manager of the IO team for having trusted me and allowing me to join his team.

I express all my gratitude to, M. Luc Hebrard and M. Pascal Nouet who kindly agreed to be the "rapporteurs" of my thesis. I also express my gratitude to M. Luc Fresquet and M. Yves Leduc who accepted to be members of my jury.

It was a real pleasure to work in contact with all the people of the IO team. I warmly thank you all for the discussions exchanged, all the advice you gave me which made me grow whether in a technical than a human point of view. Moreover, I would like to have my sincere thoughts towards all people I met during my thesis and who helped me to achieve this work.

Finally, I cannot end these acknowledgements without expressing all my gratitude to my family and friends who supported me from the beginning.

# **Contents**

| ACF  | KNOWLEDGMENTS                                                  | V                   |

|------|----------------------------------------------------------------|---------------------|

| CON  | NTENTS                                                         | VII                 |

| i ic | T OF FIGURES                                                   | VI                  |

|      |                                                                |                     |

| LIST | T OF TABLES                                                    | XIV                 |

| GEN  | NERAL INTRODUCTION                                             | 1                   |

| CH/  | APTER 1. BACKGROUND KNOWLEDGE TO UNDERSTA                      | ND THE SSN EFFECT 5 |

| 1.   | . Introduction                                                 | 5                   |

| 2.   |                                                                |                     |

|      | 2.1. MCU overview                                              |                     |

|      | 2.2. STMicroelectronics microcontroller family                 |                     |

|      | 2.2.1. Input/Output interfaces (IOs)                           |                     |

|      | 2.3. MCU Packages overview                                     |                     |

|      | 2.4. MCU evolution                                             | 11                  |

| 3.   | MOS Transistor                                                 |                     |

|      | 3.1. MOSFET history                                            |                     |

|      | 3.2. MOSFET Structure                                          | 14                  |

|      | 3.3. CMOS model and behavior                                   |                     |

|      | 3.4. Conclusion                                                |                     |

| 4.   | . UNDERSTANDING ELECTROMAGNETIC COMPATIBILITY                  |                     |

|      | 4.1. Introduction and EMC definition                           |                     |

|      | 4.2. The physics behind EMC                                    |                     |

|      | 4.3. Electromagnetic susceptibility and coupling path          | 21                  |

|      | 4.4. Electromagnetic interference (EMI)                        | 23                  |

|      | 4.5. Conclusion                                                | 24                  |

| 5.   | . From the CMOS inverter to the Simultaneous Switching Noise . |                     |

|      | 5.1. CMOS Inverter                                             | 25                  |

|      | 5.1.1. Inverter principle                                      | 25                  |

|      | 5.1.2. Voltage transfer characteristic                         | 26                  |

|      | 5.1.3. Dynamic properties of the inverter                      | 27                  |

|      | 5.2. Simultaneous Switching Noise (SSN) effect                 |                     |

|      | 5.3. Simultaneous Switching Noise (SSN) at the MCU level       |                     |

| 6.   | Conclusion                                                     | 36                  |

| CHA  | APTER 2. MODELING AND VALIDATION                               |                     |

| 1.   | Introduction                                                   | 37                  |

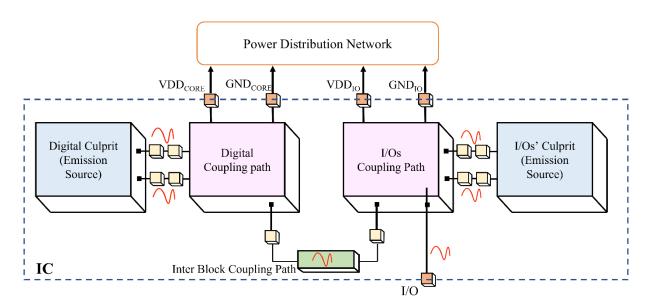

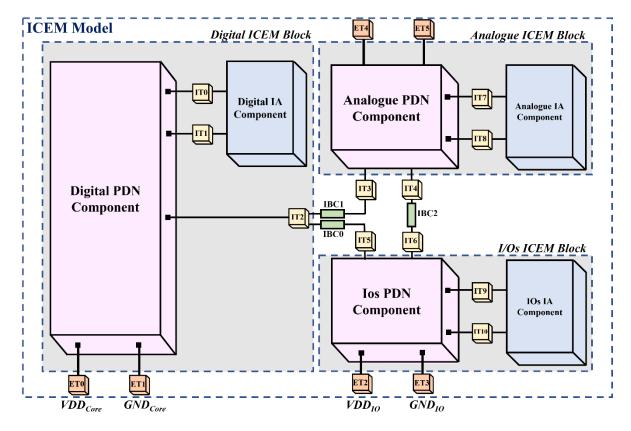

| 2   | 2. THE INTEGRATED CIRCUIT EMISSION MODEL (ICEM) STANDARD |    |

|-----|----------------------------------------------------------|----|

|     | 2.1. Standards provided by IEC organization              | 38 |

|     | 2.2. ICEM-CE standard                                    | 40 |

| 3   | 3. MODEL OF AN EXISTING MICROCONTROLLER                  | 41 |

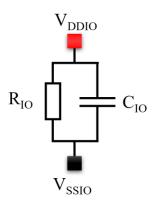

|     | 3.1. IO model                                            | 41 |

|     | 3.2. Die's power supplies line model                     |    |

|     | 3.3. Package's PDN                                       |    |

|     | 3.3.1. Hand calculation of PDN package                   |    |

|     | 3.3.2. PDN's extraction by software                      |    |

|     | 3.4. PCB model                                           | 53 |

|     | 3.4.1. Hand calculation of the PCB model                 |    |

|     | 3.4.2. PCB modeling by software                          | 55 |

|     | 3.5. Final model for simulation                          | 56 |

| 4   | 4. MODEL VALIDATION                                      | 58 |

|     | 4.1. Device under Test                                   | 59 |

|     | 4.2. Power observation for power integrity measurement   | 61 |

|     | 4.3. Signal observation through signal integrity         |    |

|     | 4.4. Model refinement in case of a non-validation        |    |

|     | 4.4.1. Load capacitor                                    |    |

|     | 4.4.2. Skin effect                                       |    |

|     | 4.4.3. Other paths for refinement                        | 66 |

| 5   | 5. Conclusion                                            | 66 |

| CII | IAPTER 3. SIMULATIONS AND RESULTS                        | (0 |

| СН  | IAPTER 3. SIMULATIONS AND RESULTS                        | 09 |

| 1   | I. Introduction                                          | 69 |

| 2   | 2. WORK ON A MANUFACTURED MCU                            | 69 |

|     | 2.1. 1st Device under test                               | 70 |

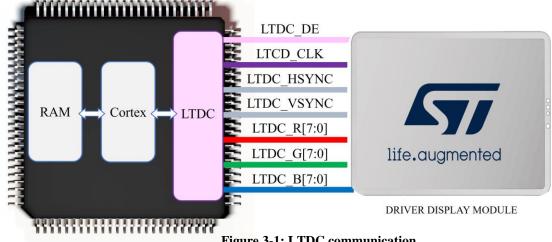

|     | 2.1.1. TFT-LCD communication                             |    |

|     | 2.1.2. DUT board                                         | 71 |

|     | 2.1.3. STM32 of the DUT                                  | 71 |

|     | 2.2. DUT modeling and validation                         | 73 |

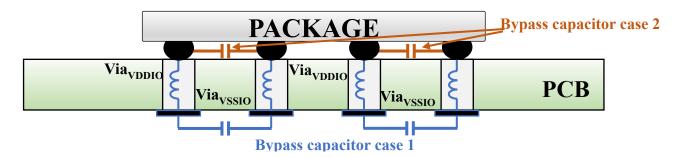

|     | 2.3. Bypass capacitor placement                          | 75 |

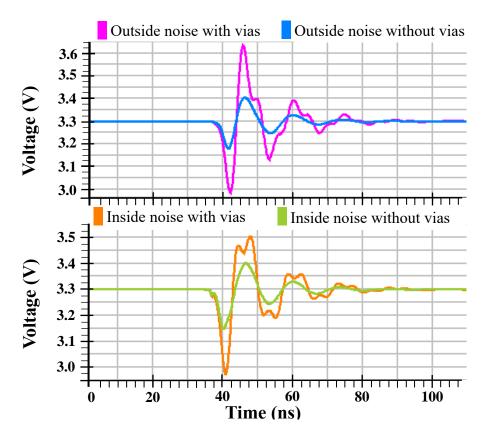

|     | 2.3.1. At PCB level with via influence                   | 75 |

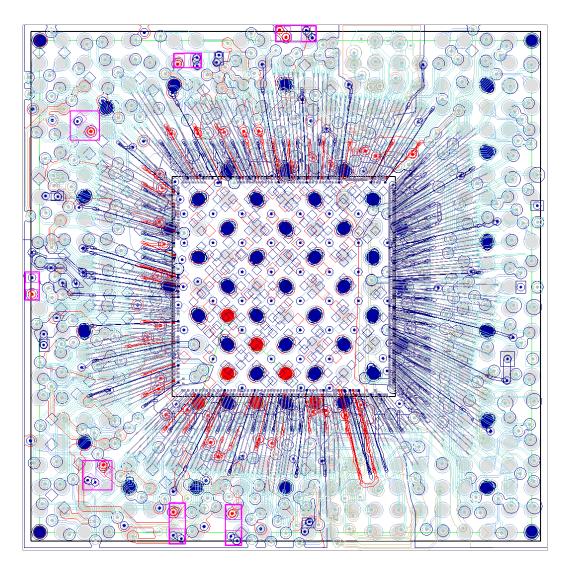

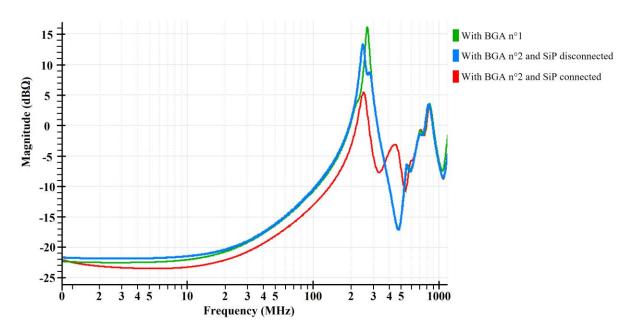

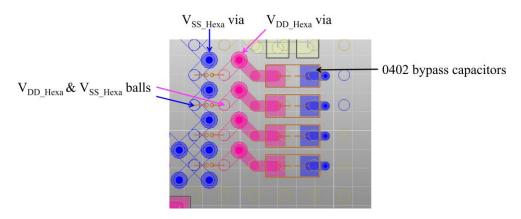

|     | 2.3.2. At package level with SiP                         | 77 |

|     | 2.4. Conclusion                                          | 81 |

| 3   | 3. Predictive model for future MCU                       | 82 |

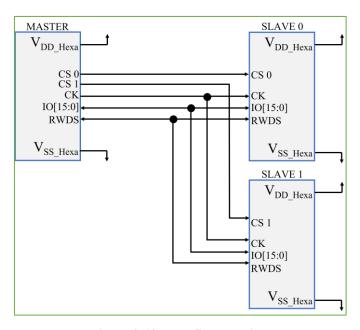

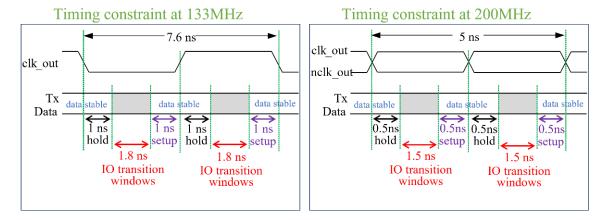

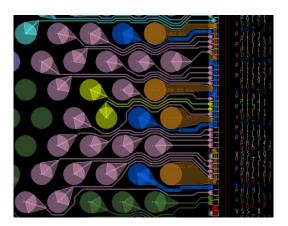

|     | 3.1. HexaSPI communication protocol                      | 82 |

|     | 3.2. Predictive model development                        | 84 |

|     | 3.2.1. Die predictive model                              | 84 |

|     | 3.2.2. Package predictive model                          | 85 |

|     | 3.2.3. Board predictive model                            |    |

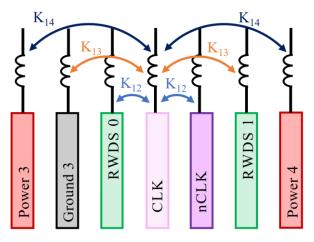

|     | 3.2.4. Issue with coupling factor                        | 86 |

| LIST OF PUBLICATIONS                                | 107 |

|-----------------------------------------------------|-----|

| BIBLIOGRAPHY                                        | 103 |

| GENERAL CONCLUSION AND PERSPECTIVES                 | 99  |

| 3.7. Conclusion                                     | 97  |

| 3.6. STM32 produced and predictive model refinement |     |

| 3.5. Study at die level                             |     |

| 3.4. Study at package level                         | 92  |

| 3.3. Study at board level                           | 89  |

| 3.2.5. Issue with Transmission line                 | 87  |

# List of figures

| FIGURE 1-1: SCHEMATIC DIAGRAM OF AN MCU                                                                            | 6  |

|--------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2: STM32 Family                                                                                           | 7  |

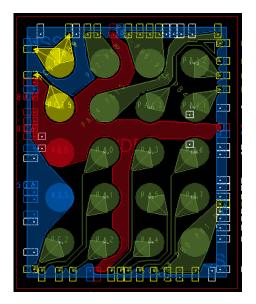

| FIGURE 1-3: EXAMPLE OF IO'S LAYOUT                                                                                 | 8  |

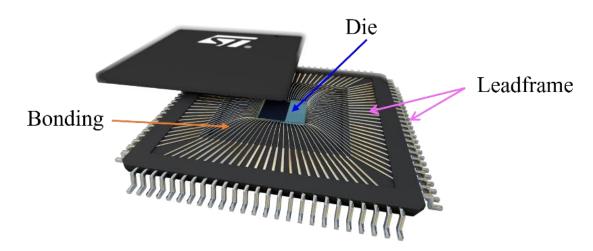

| FIGURE 1-4: QFP PACKAGE ILLUSTRATION                                                                               | 9  |

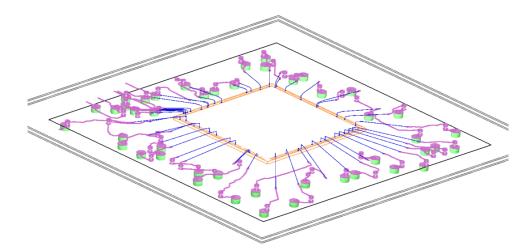

| Figure 1-5: BGA layout                                                                                             | 10 |

| FIGURE 1-6: ROUTING EXAMPLE FOR CSP PACKAGE                                                                        | 10 |

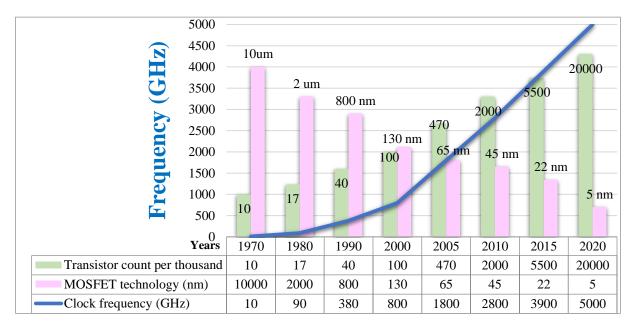

| FIGURE 1-7: 50 YEARS OF MICROPROCESSOR TRENDS                                                                      | 12 |

| FIGURE 1-8: SIMPLE STRUCTURE OF MOS TRANSISTOR                                                                     | 13 |

| FIGURE 1-9: FIRST SEMICONDUCTOR CREATED                                                                            | 14 |

| Figure 1-10: MOS structure                                                                                         | 15 |

| FIGURE 1-11: NMOS AND PMOS MODEL                                                                                   | 16 |

| FIGURE 1-12: MOS BEHAVIOR WITH, LEFT: $I_{DS}$ IN FUNCTION OF $V_{DS}$ AND RIGHT: $I_{DS}$ IN FUNCTION OF $V_{GS}$ | 17 |

| Figure 1-13: EMC issues gravity                                                                                    | 19 |

| FIGURE 1-14: RELATION BETWEEN VARIOUS EMC TERMS                                                                    | 20 |

| FIGURE 1-15: AUTO-SUSCEPTIBILITY OF AN INTEGRATED CIRCUIT                                                          | 22 |

| Figure 1-16: EMI classification overview                                                                           | 23 |

| FIGURE 1-17: EXTERNAL EMI USUAL SOURCES [3]                                                                        | 23 |

| FIGURE 1-18: WORKFLOW FOR EMC PROBLEM                                                                              | 24 |

| FIGURE 1-19: BASIC INVERTER SCHEMATIC                                                                              | 25 |

| FIGURE 1-20: I-V CURVE FOR PMOS AND NMOS                                                                           | 26 |

| FIGURE 1-21: I-V CURVE OF NMOS AND PMOS SUPERPOSITION                                                              | 26 |

| FIGURE 1-22: VOLTAGE TRANSFER CHARACTERISTICS OF AN INVERTER                                                       | 27 |

| Figure 1-24: Inverter transient behavior                                                                           | 28 |

| FIGURE 1-23: INVERTER SCHEMATIC WITH CLOAD                                                                         | 28 |

| FIGURE 1-25: CURRENT FLOW FOR THE CAPACITOR CHARGE AND DISCHARGE                                                   | 29 |

| FIGURE 1-26: IMPACT OF THE $C_{	ext{load}}$ ON RISING TIME AND CURRENT PEAK FOR A BASIC INVERTER                   | 30 |

| FIGURE 1-27: Inverter schematic with PDN's parasitic elements                                                      | 31 |

| FIGURE 1-28: SCHEMATIC REPRESENTATION OF A GENERAL PURPOSE INPUT/OUTPUT INTERFACE BLACK BOX                        | 31 |

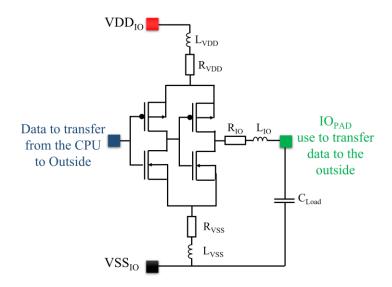

| FIGURE 1-29: IO'S OUTPUT BUFFER SCHEMATIC                                                                          | 32 |

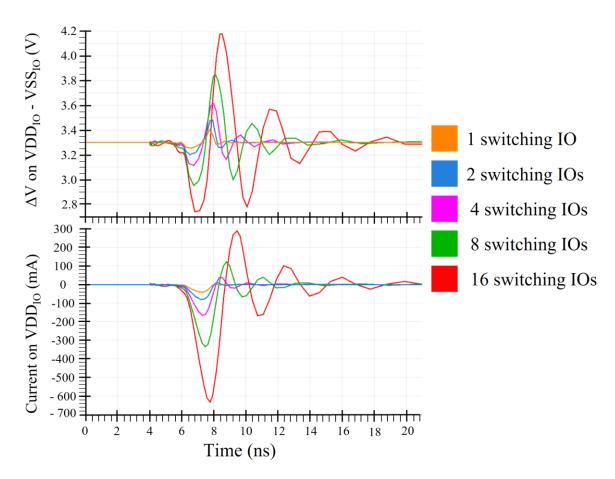

| FIGURE 1-30: SSN EFFECT ON VDD <sub>IO</sub> IN FUNCTION OF THE NUMBER OF SWITCHING IOS                            | 33 |

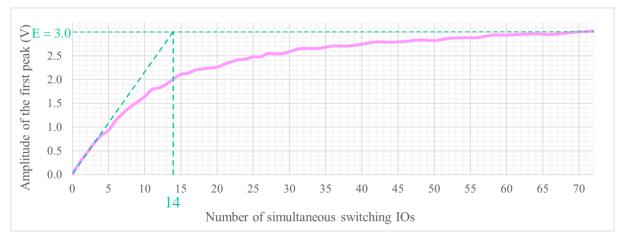

| FIGURE 1-31: SIMULATION EXTRACTION OF THE OVERSHOOT NOISE AMPLITUDE IN FUNCTION OF THE NUMBER OF SSO               | 34 |

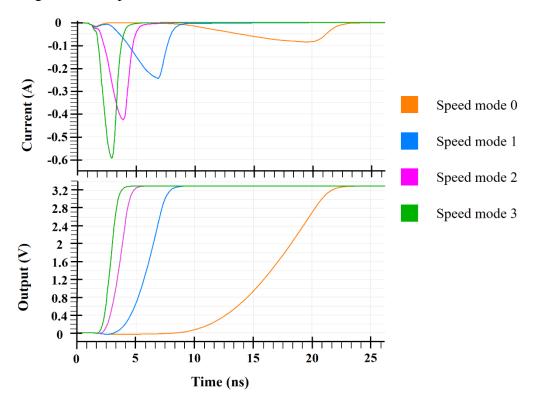

| FIGURE 1-32: EXAMPLE OF THE CURRENT PEAK DEPENDING ON THE IO SPEED MODE                                            | 35 |

| FIGURE 2-1: THE THREE TYPES OF EMISSIONS DEFINED BY THE STANDARD IEC 62014 [49]                                    | 39 |

| FIGURE 2-2: EXAMPLE OF CONDUCTED EMISSION DETAILED BY THE STANDARD IEC 62433-2                                     | 39 |

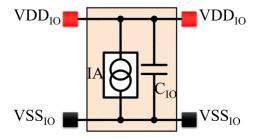

| FIGURE 2-3: ICEM-CE SCHEMATIC                                                                                      | 41 |

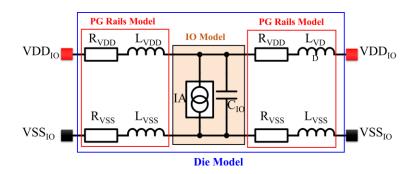

| Figure 2-4 : IO's schematic model                                                                                  | 42 |

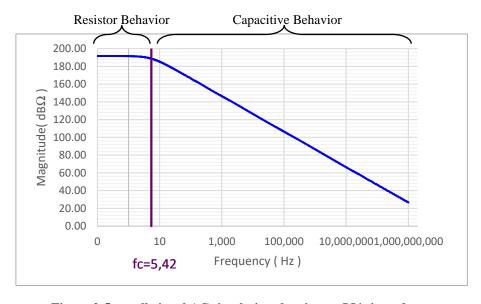

| FIGURE 2-5: SMALL-SIGNAL AC SIMULATION SHOWING AN IO'S IMPEDANCE                                                   | 42 |

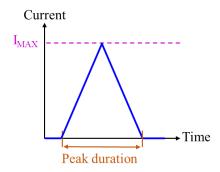

| FIGURE 2-6: CURRENT PEAK NOTATION                                                                                  | 44 |

| Figure 2-7: Final IO model                                                                                       | 44 |

|------------------------------------------------------------------------------------------------------------------|----|

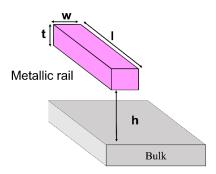

| Figure 2-8: Die metallic rails geometry                                                                          | 45 |

| FIGURE 2-9: DIE MODEL WITH ACTIVE/INACTIVE IO AND PDN                                                            | 46 |

| FIGURE 2-10: REPRESENTATION OF THE DIE MODEL                                                                     | 46 |

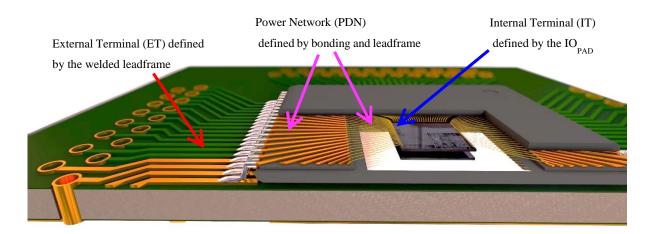

| FIGURE 2-11: SECTIONAL VIEW OF PACKAGE WELDED ON A BOARD                                                         | 47 |

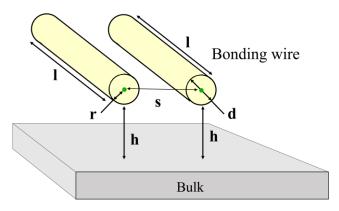

| FIGURE 2-12: SCHEMA OF BONDING WIRE AND ASSOCIATED PARAMETER                                                     | 48 |

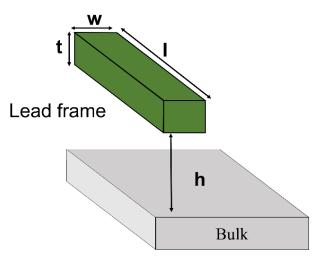

| FIGURE 2-13: LEAD FRAME AND BONDING GEOMETRY                                                                     | 49 |

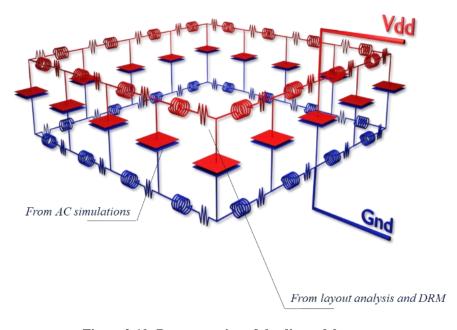

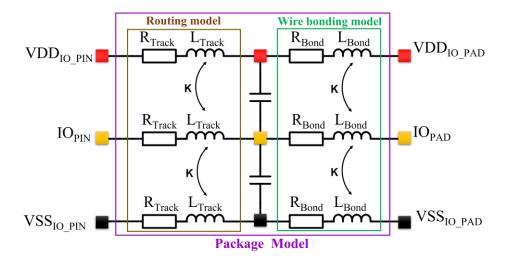

| FIGURE 2-14: MODEL OF THE PACKAGE OVERVIEW                                                                       | 51 |

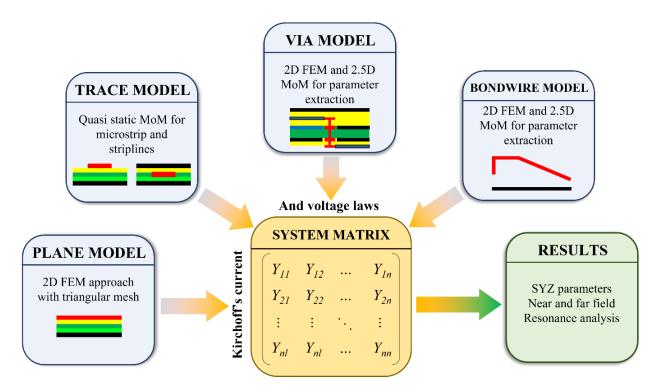

| Figure 2-15: SIwave solver workflow                                                                              | 52 |

| FIGURE 2-16: MODEL OF THE PACKAGE AND PARAMETERS EXTRACTION USING SIWAVE <sup>TM</sup>                           | 53 |

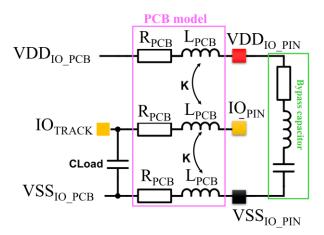

| FIGURE 2-17: MODEL OF PCB TO CREATE                                                                              | 53 |

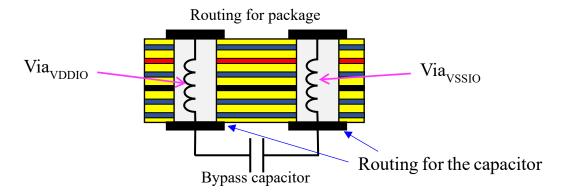

| FIGURE 2-18: MODEL OF TWO VIAS WITH A BYPASS CAPACITOR                                                           | 54 |

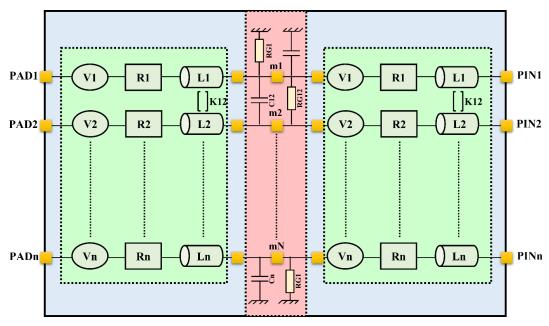

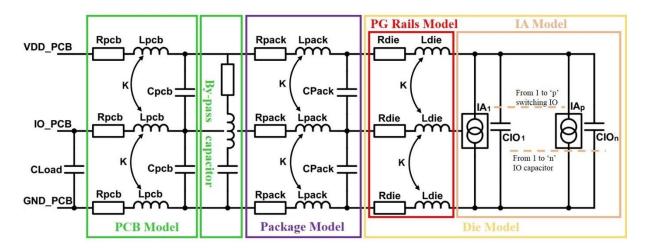

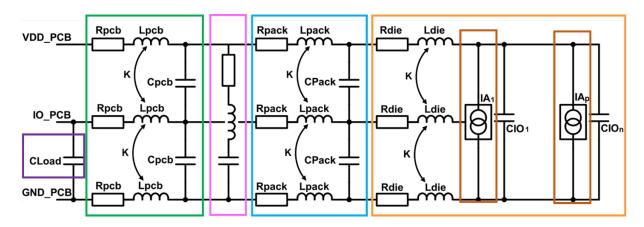

| FIGURE 2-19: ICEM-CE MODELING OF A COMPLETE SYSTEM                                                               | 56 |

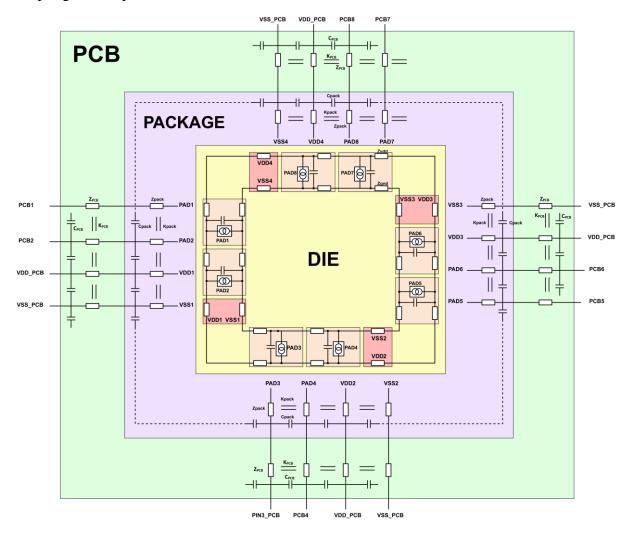

| FIGURE 2-20: REPRESENTATION OF A FINAL MODEL OBTAINED FOR SIMULATION                                             | 57 |

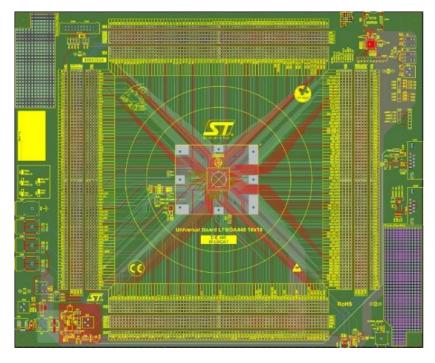

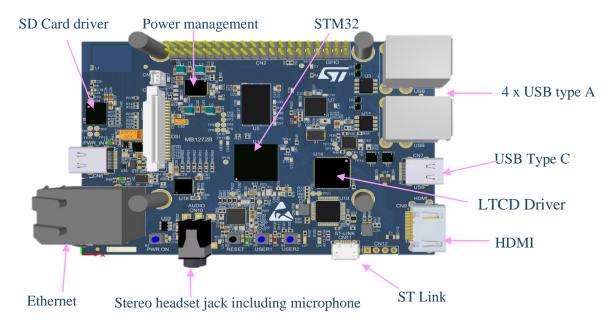

| FIGURE 2-21: PICTURE OF THE DISCOVERY BOARD DESIGNED BY STMICROELECTRONICS                                       | 60 |

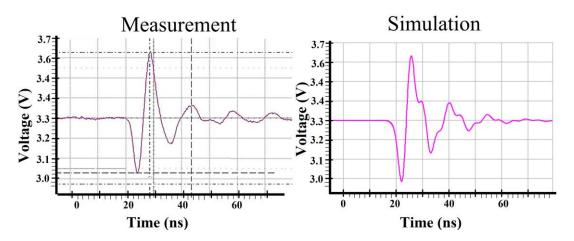

| FIGURE 2-22: COMPARISON MEASUREMENT VS SIMULATION FOR POWER OBSERVATION                                          | 61 |

| FIGURE 2-23: COMPARISON BETWEEN MEASUREMENT AND SIMULATION FOR SIGNAL OBSERVATION                                | 62 |

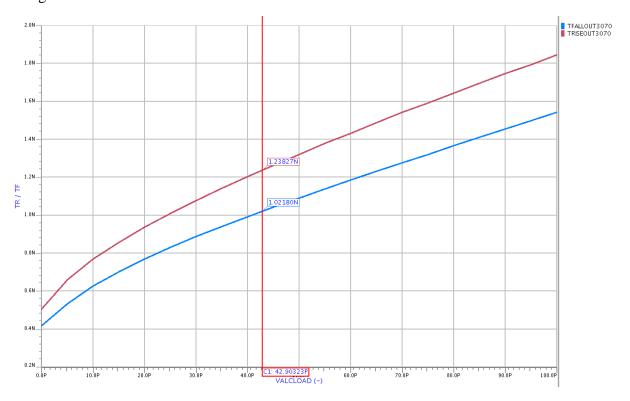

| FIGURE 2-24: ABACUS OF RISING/FALLING TIME IN FUNCTION OF LOAD CAPACITANCE                                       | 64 |

| FIGURE 2-25: ILLUSTRATION OF THE SKIN EFFECT                                                                     | 65 |

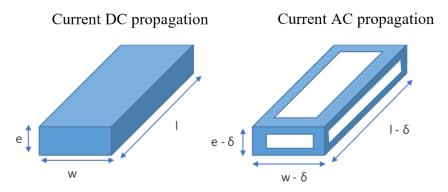

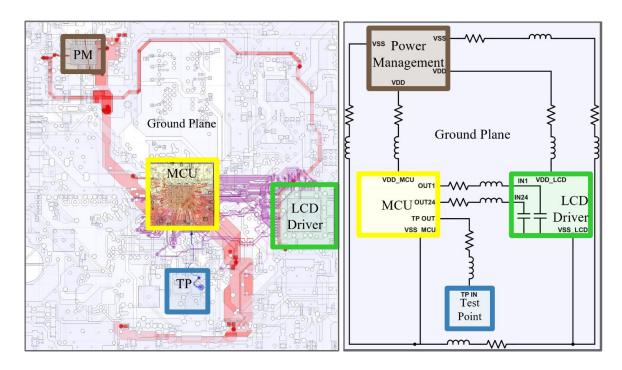

| FIGURE 3-1: LTDC COMMUNICATION                                                                                   | 69 |

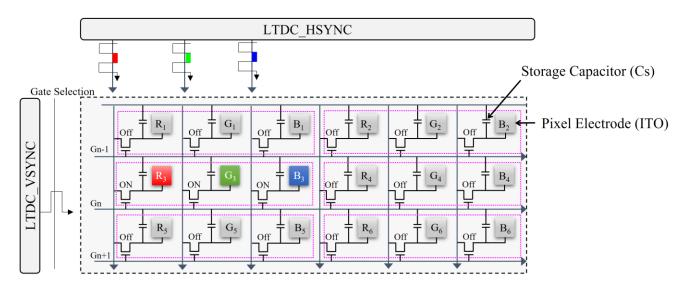

| FIGURE 3-2: CMOS MATRIX PRINCIPLE FOR LTDC DRIVER                                                                | 70 |

| FIGURE 3-3: DISCOVERY BOARD OVERVIEW                                                                             | 71 |

| FIGURE 3-4: 1 <sup>st</sup> DUT Padring schematic                                                                | 72 |

| FIGURE 3-5: OVERVIEW OF THE BOARD EXTRACTED                                                                      | 74 |

| FIGURE 3-6: REMINDER OF THE ICEM FOR THE 1 <sup>ST</sup> DUT MODEL                                               | 74 |

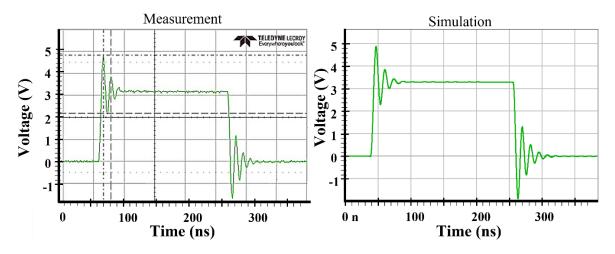

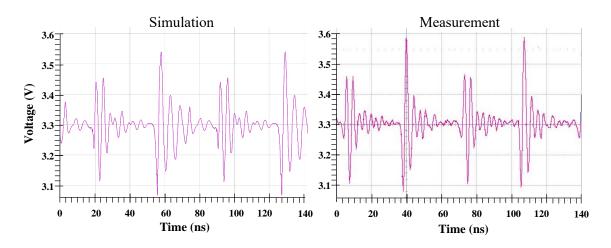

| FIGURE 3-7: SIMULATION VS MEASUREMENT COMPARISON FOR MODEL VALIDATION                                            | 75 |

| FIGURE 3-8: BYPASS CAPACITORS ILLUSTRATION FOR CASE 1 AND CASE 2                                                 | 76 |

| FIGURE 3-9: SIMULATIONS WITH AND WITHOUT VIAS                                                                    | 77 |

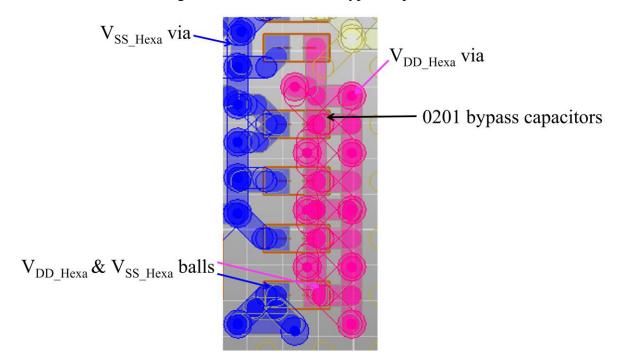

| FIGURE 3-10: LAYOUT OF THE BGA N°2 WITH SIP CAPACITORS                                                           | 78 |

| FIGURE 3-11: AC SIMULATIONS FOR PACKAGE COMPARISON                                                               | 79 |

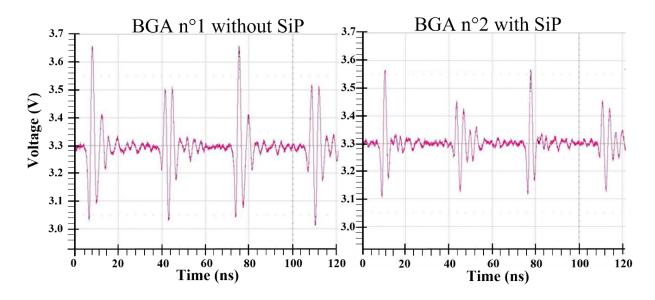

| FIGURE 3-12: Noise level ( $V_{DDIO} - V_{SSIO}$ ) measured with BGA without SiP (left) and BGA with SiP (right) |    |

| FIGURE 3-13: HEXASPI OVERVIEW                                                                                    | 82 |

| FIGURE 3-14: HEXASPI TIMING CONSTRAINT                                                                           | 83 |

| FIGURE 3-15: PADRING DISTRIBUTION FOR THE HEXASPI                                                                | 84 |

| FIGURE 3-16: COUPLING FACTOR ILLUSTRATION                                                                        | 85 |

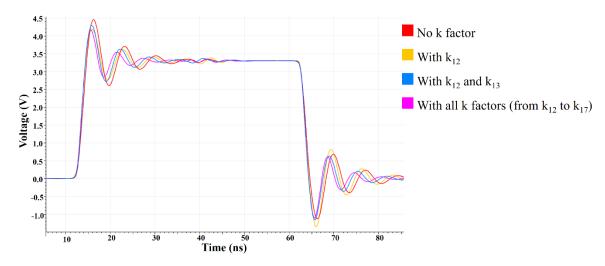

| FIGURE 3-17: COUPLING FACTOR EFFECT SIMULATED                                                                    | 87 |

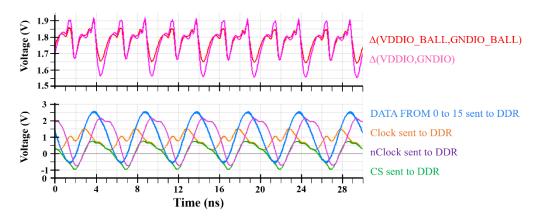

| FIGURE 3-18: ISSUE OBSERVED ON CLOCKS CROSSING WITHOUT TRANSMISSION LINE                                         | 88 |

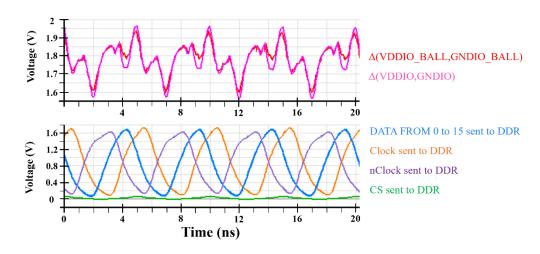

| FIGURE 3-19: SIMULATION WITH TRANSMISSION LINE TO COMPARE WITH FIGURE 3-18                                       | 88 |

| FIGURE 3-20: 1ST BOARD DESIGN FOR THE HEXASPI POWER AND GROUND                                                   | 89 |

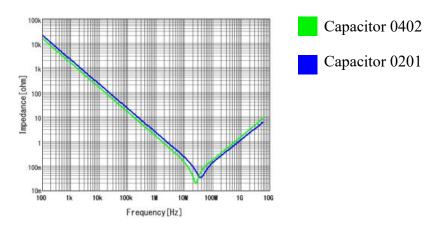

| FIGURE 3-21: CAPACITOR CUT-OFF COMPARISON BETWEEN 0402 AND 0201                                                  | 90 |

| FIGURE 3-22: FINAL PROPOSED BOARD DESIGN                                                         | 91 |

|--------------------------------------------------------------------------------------------------|----|

| FIGURE 3-23: CSP DESIGN WITH 1 LAYER.                                                            | 92 |

| FIGURE 3-24: CSP DESIGN WITH 2 LAYERS                                                            | 92 |

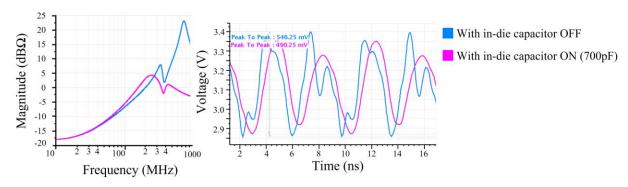

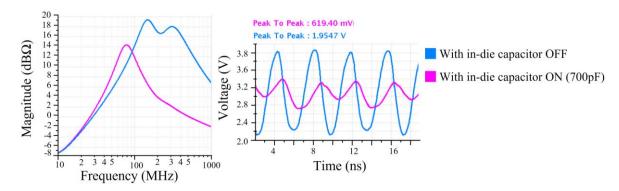

| FIGURE 3-25: SIMULATION IN FREQUENCY AND TIME DOMAIN, WITH IN-DIE CAPACITOR OFF AND ON           | 94 |

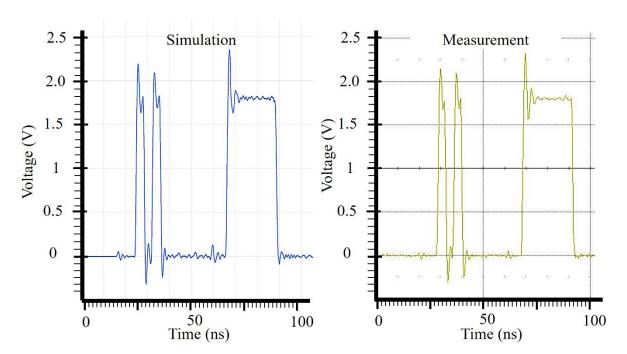

| FIGURE 3-26: OBSERVATIONS OF THE IN-DIE BYPASS CAPACITOR EFFECT IN THE FREQUENCY AND TIME DOMAIN | 95 |

| FIGURE 3-27: COMPARISON BETWEEN SIMULATION AND MEASUREMENT OF THE REFINED MODEL                  | 97 |

# List of tables

| TABLE 1-1: DIFFERENT PACKAGES OVERVIEW                                              | 11 |

|-------------------------------------------------------------------------------------|----|

| TABLE 1-2: MAXWELL'S EQUATIONS                                                      | 21 |

| TABLE 1-3: FAILURE LEVEL CLASSIFICATION FOR A SYSTEM DISTURBED BY AN EMI            | 21 |

| TABLE 1-4: VOLTAGE TRANSFER CHARACTERISTICS TABLE                                   | 27 |

| TABLE 1-5: PARASITIC VALUES EXAMPLE OF LEADRAME/ROUTING/WIREBOND FOR A PACKAGE [43] | 32 |

| TABLE 1-6: EXAMPLE OF IO SPEED MODE                                                 | 35 |

| TABLE 2-1: COMPARISON OF SIMULATIONS AND MEASUREMENTS VALUES FOR POWER OBSERVATION  | 61 |

| TABLE 2-2: COMPARISON OF SIMULATIONS AND MEASUREMENTS VALUES FOR SIGNAL OBSERVATION | 63 |

| TABLE 3-1: 1ST DUT IO SPECIFICATIONS                                                | 73 |

| TABLE 3-2: OVERVIEW OF THE 1 <sup>ST</sup> DUT MODEL VALUES                         | 74 |

| TABLE 3-3: SUMMARY OF BGA VS SIP COMPARISON IN MEASUREMENT AND SIMULATION           | 80 |

| TABLE 3-4: SUMMARY OF ALL STUDIED CASES ON THE 1 <sup>ST</sup> DUT                  |    |

| TABLE 3-5: HEXASPI SPECIFICATIONS                                                   | 83 |

| TABLE 3-6: PVT CASES USED FOR SIMULATION                                            | 89 |

| TABLE 3-7: SUMMARY OF SPECIFICATION OBSERVED IN SIMULATION FOR THE THREE PVT CASES  | 90 |

| TABLE 3-8: SUMMARY OF FINAL VALUES OBTAINED WITH THE BOARD RE-DESIGNED              | 91 |

| TABLE 3-9: SPECIFICATION COMPARISON OF THE TWO PACKAGES FOR SETUP 1                 | 93 |

| TABLE 3-10: SPECIFICATION COMPARISON OF THE TWO PACKAGES FOR SETUP 2                | 93 |

## **Acronyms List**

ADC ANALOG TO DIGITAL CONVERTER

BGA BALL GRID ARRAY

BJT BIPLOR JUNCTION TRANSISTOR

BSIM BERKELEY SHORT-CHANNEL IGFET MODEL

CMOS COMPLEMENTARY METAL OXIDE SEMICONDUCTOR

CPU CENTRAL PROCESS UNIT

CSP CHIP SCALE PACKAGE

DAC DIGITAL TO ANALOG CONVERTER

DDR DOUBLE DATA RATE

DIP DUAL IN LINE PACKAGE

DUT DEVICE UNDER TEST

EM ELECTROMAGNETIC

EMC ELECTROMAGNETIC COMPATIBILITY

EME ELECTROMAGNETIC EMISSION

EMI ELECTROMAGNETIC INTERFERENCE

EMMC EMBEDDED MULTI-MEDIA CONTROLLER

EMS ELECTROMAGNETIC SUSCEPTIBILITY

ESD ELECTROSTATIC DISCHARGE

ET EXTERNAL TERMINAL

FEM FINITE ELEMENTS METHOD

FET FIELD EFFECT TRANSISTOR

HSPI HEXASPI

IA INTERNAL ACTIVITY

IBC INTER-BLOCK COUPLING

IBIS INPUT/OUTPUT BUFFER INFORMATION SPECIFICATION

IC INTEGRATED CIRCUIT

ICEM INTEGRATED CIRCUIT EMISSION MODEL

ICEM-CE INTEGRATED CIRCUIT EMISSION MODEL - CONDUCTED EMISSION

IEC INTERNATIONAL ELECTROTECHNICAL COMMITTEE

IMIC INPUT/OUTPUT MODEL FOR INTEGRATED CIRCUIT

IO INPUT/OUTPUT INTERFACE

IP INTELLECTUAL PROPERTIES

IT INTERNAL TERMINAL

JEITA JAPAN ELECTRONICS AND INFORMATION TECHNOLOGY

INDUSTRIES ASSOCIATION

LCD LIQUID CRYSTAL DISPLAY

LECCS LINEAR EQUIVALENT CIRCUIT AND A CURRENT SOURCE MODEL

MCU MICROCONTROLLER

MOM METHOD OF MOMENTS

MOSFET METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR

MPU MICROPROCESSOR

NVM NON-VOLATILE MEMORY

P&G POWER AND GROUND

PCB PRINTED CIRCUIT BOARD

PDK PROCESS DESIGN KIT

PDN POWER DISTRIBUTION NETWORK

PI POWER INTEGRITY

PVT PROCESS, VOLTAGE, TEMPERATURE

QFP QUAD FLAT PACKAGE

RGB RED, GREEN, BLUE

SI SIGNAL INTEGRITY

SIP SYSTEM IN PACKAGE

SOC SYSTEM ON CHIP

SOP SMALL OUTLINE PACKAGE

SSN SIMULTANEOUS SWITCHING NOISE

TFT-LCD THIN FILM TRANSISTOR LIQUID CRYSTAL DISPLAY

TL TRANSMISSION LINE

VTC VOLTAGE TRANSFER CHARACTERISTIC

## **General Introduction**

Over the last few decades, the electronics industry has undergone a major evolution, particularly in the field of embedded systems. Designers have thus developed circuits with high integration density that allow multiple functionalities to coexist, while minimizing production costs. However, this increase of electrical performance has a negative repercussion on its reliability and in particular for its electromagnetic compatibility (EMC). EMC problems remain today one of the main causes of re-design of Integrated Circuits (ICs) [1]. Due to the lack of possibilities for internal measurement and reliable prediction, the IC design is frequently modified after the EMC qualification phases because their operation is not guaranteed in several conditions. In order to avoid additional production costs, designers have recently been trying to study and anticipate this problem.

Microcontrollers (MCUs) are considered as versatile IC used in many different applications of embedded system. Due to this strong presence of MCUs in everyday connected objects, the market has become ultra-competitive, resulting in a frantic race for performance. Thus, it becomes essential for a company to ensure MCU robustness and reliability especially in terms of EMC issues. It is in this framework that this research was carried out within the IO team (Input/Output interface) of the STMicroelectronics microcontroller division, one of the world leaders in the MCU market and in collaboration with Polytech'lab, a microelectronic laboratory attached to the University Côte d'Azur. EMC problems have already been studied in this team. The emission aspect (EMI) was studied by J.P Leca [2] who defended his thesis in 2012 and susceptibility aspect (EMS) against external aggressions was studied by Y. Bacher 2017 and L. Quazzo in 2022 [3].

This thesis is focused on another type of EMC problem, the susceptibility of the chip face to an internal aggression. Due to the complex evolution of MCU, they are more and more

subject to these new types of disturbances commonly named auto-susceptibility. It is a merging of the two previous subjects since the MCU degrades its performance because of an internal noise emission. One of this phenomena is the Simultaneous Switching Noise (SSN), which is a topic that becomes more problematic through the years because MCU evolution leads to a lowering of susceptibility thresholds and to an increase of the internal emission level.

In the literature, there is a large number of publications about these SSN problems with the first one dated from the mid-90s and are mainly interested in the mechanism of generation of this noise with some preliminary design solutions. Later on, researchers focused more on studying the impact of SSN on some functional blocks in order to propose some solutions to reduce these disturbances at chip or package level. However, although they are numerous and referential to establish state of the art, these works are not sufficient to solve this problem given the market competition where the MCU must be cheap, small and with the best performance possible, leading to several constraints for proposed solutions. In view of all of this, it has therefore become essential for all designers to control the EMC product by developing innovative methods to measure, analyze, understand, and predict the electromagnetic performance of the MCU. For that purpose, this manuscript developed the research carried out on the SSN problematic.

The first chapter details all necessary knowledge to properly understand this SSN effect. For that, a summary is given of the state of the art to explain the origin of SSN. Next, MCU produced by STMicroelectronics are introduced and all linked elements to properly understand the SSN with some explanations about package and EMC at die level.

The second chapter is dedicated to the development of a modeling method for a complete system defined by a chip with its package and a Printed Circuit Board (PCB). This modeling method is based on the ICEM standard. Then, we will explain a validation process developed through comparisons between measurements and simulations on a 1<sup>st</sup> DUT. This step is essential to ensure that the simulations reflect the physical MCU behavior in order to study the SSN.

The third chapter is divided into two parts. The first part presents a complete modeling of a manufactured MCU based on the methodologies developed in chapter 2. This product study allows observation of the in-die noise and understanding of which parameters are influencing the SSN. Thanks to this, we will provide first design rules for die/package/PCB in order to improve the product robustness against SSN effects. This study also allowed to fix a failure on the product detected during the qualification phase. The second part presents the development

of a predictive model used to anticipate the MCU behavior for a specific high-data rate communication. The implementation of modeling methods that allows the prediction of the susceptibility of an internal block is an effective approach to analyze the behavior of an IC with respect to a disturbance. Nevertheless, these methods require a real expertise because there is no modeling and/or simulation procedure integrated in Computer Aided Design tools to understand the effect induced by electromagnetic disturbances through the IC.

Finally, this manuscript will be concluded with a summary of the work carried out in this study and some perspectives are presented.

# Chapter 1. Background knowledge to understand the SSN effect

### 1. Introduction

Nowadays, Integrated Circuits (IC) play an important role in modern society, being used in most electronic appliances. Any electronic component created as one flat and small piece of semiconductor technology could be considered as an IC. This is the case for microcontrollers (MCU), microprocessors (MPU), several types of memories or sensors, etc. The development of IC is mainly based on the CMOS technology (Complementary Metal Oxide Semiconductor) and MOS transistors continue to follow Moore's Law: their size is divided by two every 18 months. This rapid and constant evolution of technology and MCU performance has led to an important degradation of MCU behavior in terms of Electromagnetic Compatibility (EMC) and it must be considered in order to stay competitive on the market. In this context, we propose to study an EMC problematic defined by the Simultaneous Switching Noise (SSN) generated by high-speed data rate Input/Output interfaces (IOs).

This chapter is dedicated to the definition of the thesis context with a first section that introduces 32-bits STM32 microcontroller defined as the device under test (DUT). Then, the second section details the semiconductor technology used for MCU development with a reminder of the MOS transistor origin and of its basic behavior in strong inversion. A third section briefly details Electromagnetic Compatibility (EMC) at MCU level. Finally, a fourth section details the SSN effect based on all knowledge acquired through this chapter.

## 2. Microcontroller (MCU)

#### 2.1. MCU overview

MCUs are used in a lot of embedded systems such as smartphones, smart watches, earphones but also in other domain such as automotive, medical, aeronautic, ... An MCU is

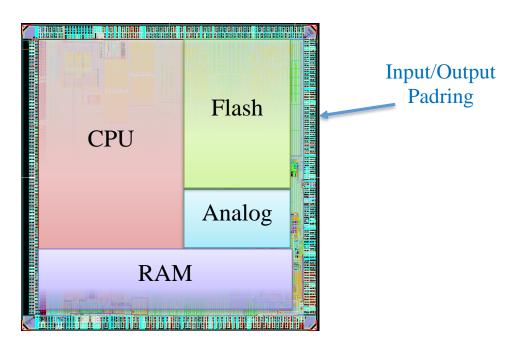

defined as a tiny System on Chip (SoC) composed of different blocks. Figure 1-1 schematizes this IC which incorporates:

- A Central Process Unit (CPU) or processor defined as the MCU core. The CPU could be seen as the "device brain".

- Several analog peripherals like ADC (Analog to Digital Converter) and DAC (Digital to Analog converter) which allows the communication between analog devices and the processor. Analog peripherals also include among other functionalities the power management of the MCU.

- Different types of memories as Flash, RAM or ROM used by the processor to store data and program instructions.

- Inputs/Outputs peripherals (IOs) that can be defined as an interface between the processor and the "outside world". Figure 1-1 depicts the IOs distribution all around the MCU, creating a ring of pads commonly named "Padring".

Figure 1-1: Schematic diagram of an MCU

In the next section the STM32 family, which are 32-bits microcontrollers manufactured by the STMicroelectronics company, is presented as the Device Under Test (DUT). In order to help the understanding of this thesis problematic, particular attention is given to the padring definition and to the MCU's package because they are important contributors to the SSN effect. Finally, the origin of SSN is explained thanks to the definition of the MOS transistor.

## 2.2. STMicroelectronics microcontroller family

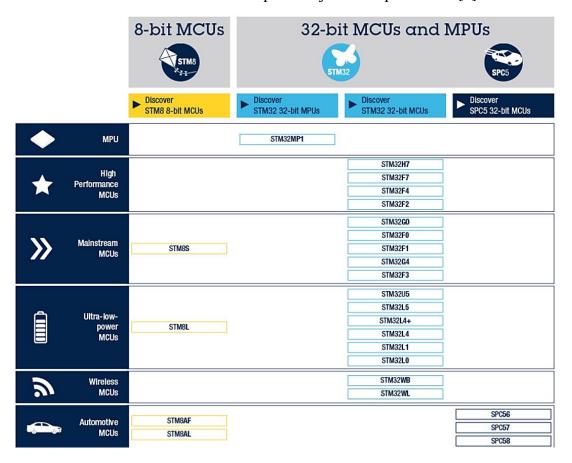

The STMicroelectronics company produces different MCUs and in particular the STM32. In order to satisfy all market needs, several types of MCU are produced. Each of them offers different functionalities regarding the size of the flash, the CPU frequency, the supply value for core and IOs, etc... Figure 1-2 depicts the "STMicroelectronics family" with all different manufactured products which are regrouped depending on their main functionalities and their purpose. A short definition of each of them is given bellow:

- A high-performance MCU includes a Non-Volatile Memory (NVM) in order to have a high performance for code execution and data processing.

- A mainstream MCU answers to the basic needs of the market where time and costs are essential.

- An ultra-low power MCU is a trade-off between cost, performance and power efficiency.

- A wireless MCU is able to run LoRaWAN protocol and, thanks to its functionalities will be favored by an RF designer.

- An automotive MCU will answer to many automotive applications and will also meet automotive constraints such as a temperature junction up to 165°C [4].

Figure 1-2: STM32 Family

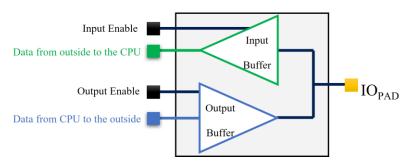

### 2.2.1. Input/Output interfaces (IOs)

IOs are used to make the link between the MCU's core and its external environment. In other words, each time a communication is settled between the MCU and an external component, this communication is done through IOs by using a dedicated communication protocol. For example, if the MCU needs to communicate with an SD Card reader, this will be done with the EMMC (Embedded Multi-Media Controller) communication protocol through IOs interface. Nowadays, to remain competitive on the market an MCU needs to handle many of these protocols like USB type C, the SDMMC, the xSPI – where x is the number of bits transferred from the DualSPI to HexaSPI-, the I2C/I3C, etc. Each of these protocols has its own particularities and specifications as the operating frequency, the number of switching IOs, etc. Moreover, they are also generally defined by standards to ensure homogeneity between all manufacturers. It would be too long to provide more details regarding these protocols because, there are many different possibilities for the power supplies values, the data rate frequency, etc. Nevertheless, we will define the HexaSPI, in the last chapter because it was used in the frame of research activities conducted for a future STM32.

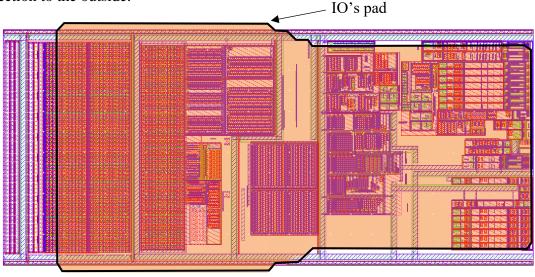

Regarding the IO design, one real structure is displayed in Figure 1-3. Such picture might not be easy to understand at first sight but it illustrates the complexity of current IOs. This complexity comes from all functionalities proposed by an IO like analog switches, different frequencies of work, Schmitt trigger to decrease noise perturbation, or the signal transmission for different power supplies value -for example, a 5V signal as input is transmitted to the core in a 1.2V signal-. This Figure 1-3 also shows the IO's pad used to establish the IO's connection to the outside.

Figure 1-3: Example of IO's layout

## 2.3. MCU Packages overview

An MCU is defined by the die embedded in a package. The package is used to protect the die from its external environment but also to preserve its electrical characteristics. Of course, the package is used to facilitate the connection between the die and the Printed Circuit Board (PCB). For example, the package will establish the connection from the IO's pad to a track of the PCB and also the connections for all power supplies. Through the years, the packages evolved from a basic protection enclosure to a key element of the MCU performance. The science of integrated circuit packaging progressed radically providing more IOs connections, a better power dissipation, more resistance to temperature and humidity and even a package that embedded SiP (System in Package) bypass capacitor to optimize noise decoupling. Nowadays, there are different types of packages used for MCUs, the physical characteristics of the three most used packages are detailed below:

• QFP (Quad Flat Package): From a physical point of view, it is composed of leadframes and bonding. The bonding is a gold or an aluminum wire that creates the connection from a die's pad to the leadframe. Then, the leadframe goes from the bonding to the outside of the package and will be soldered on the PCB. The size of this package is mainly constrained by the die's cavity in the center of the package. Figure 1-4 illustrates a QFP package with the die cavity area, bonding, and lead frame.

Figure 1-4: QFP package illustration

BGA (Ball grid array): This package is based on the same principle as QFP, the only difference is regarding external leadframes, replaced by balls for this package. Figure 1-5 shows an example of a BGA layout where only a few connections appear. IOs pads are represented in orange, then bonding in blue, leadframe in pink, and balls in green.

Figure 1-5: BGA layout

CSP (Chip Scale Package): This is one of the new packages, where optimization is the corner stone of its design. For this one, there is no bonding but only "fan-in" routing. The "fan-in" routing describes the development of the connection from the padring to the package center. Reversely, the "fan-out" will be the connection development from the padring to the outside in the principle of QFP or BGA. Thanks to this fan-in routing, the size of a CSP package is limited to the die size as illustrated in Figure 1-6. Then, its external connections are done via balls, in the same way as with the BGA.

Figure 1-6: Routing example for CSP package

For the purpose of illustrating the MCU packaging evolution, Table 1-1 summarizes the main packages used for MCU, their main connection characteristics and the maximum IOs connection allowed by each package [5].

| Packaging                         | Definition                                                                                          | Max allowed IOs |

|-----------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|

| THITITITIES .                     | Dual In line Package (DIP)  Through hole mounted package with wirebond                              | 40              |

| Similar                           | Small Outline Package (SOP) Surface Mounted package, with wirebond                                  | 100             |

| THE PROPERTY OF                   | Quad Flat Pack (QFP) Surface mounted package with wirebond                                          | 250             |

| 000000<br>00000<br>00000<br>00000 | Ball Grid Array (BGA)  Surface mounted package with wirebond and short routing and balls            | 100             |

|                                   | Chip Scale Package (CSP)  Surface mounted package without bonding and with custom routing and balls | >5000           |

Table 1-1: Different packages overview

We can see that there are two categories of packages concerning the way they are connected to the PCB as presented in Table 1-1. The first category is the "through hole" package. Connection to the PCB is achieved by pins that are inserted and soldered into holes, predrilled into the PCB. The second category is the "surface mounted" package which is the most widespread nowadays. In this case, the lead pins or leadframe are soldered directly on the top layer of the PCB thanks to its flat structure. The use of surface mounted package technology became dominant because of the gain of space on PCBs. Indeed, because there is no need to drill holes into the PCB, it is possible to optimize the space by soldering different packages on both sides of the board.

#### 2.4. MCU evolution

This section is dedicated to the MCU definition from several points of view: the general structure of the die, the specific block of the Input/Output Interface, the packages to embed a die and the STM32 family. To conclude this section, an overview of the MCU evolution through the years is provided. The MCU characteristics never stopped to evolve in terms of packages, dies and performance. The package, had to become as small and as cheap as possible, whilst at

the same time, increasing IOs connections and decreasing the supplies connections. In parallel, the die performance was increased as well as its operating frequency and its size, and its power supplies values were reduced. Moore's Law could be used to illustrate this MCU evolution: In 1965, Gordon Moore, using three points on the graph, extrapolated the trend predicting that the component number per IC would double every 18 months. When he outlined the IC future, he predicted it for the next 10 years. Finally, he presented a brilliant analysis of the IC future with the famous "Moore's Law" which already predicted the spread of electronics. Moreover, this rule even became a challenge in the semiconductor industry with a time slot reduction - the component number per IC would double every 18 months, the every 12 month, ect- [6]. To illustrate this IC evolution, a graph has been drawn in Figure 1-7, which illustrates 50 years of evolution for three specific points [7], [8], [9]. The first notable evolution is the size decrease of the CMOS technology with a transistor of 10 µm in 1970 and a transistor of 5 nm in 2022. The second main evolution is the number of transistors counted per thousand, illustrated in the same way with Moore's law. The third parameter is the CPU frequency evolution. Nowadays, we even speaking of the more than Moore law where the goal is a specific application instead of the new technology developments [10].

Figure 1-7: 50 years of Microprocessor trends

## 3. MOS Transistor

The MCU evolution is mostly due to the decrease in size of the MOS transistor. Indeed, the semiconductor technology is in constant evolution whether for its miniaturization or for its

manufacture and performance. Before going deeper into details of its creation, its structure definition and other specifications, a simplistic model of a MOS can be introduced in Figure 1-8.

Figure 1-8: Simple structure of MOS transistor

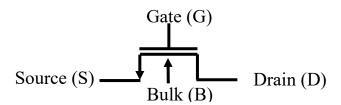

This structure reveals four terminals with the source (S), the drain (D), the bulk (B) and the gate (G) where source and drain could be interchangeable because of the device symmetry. From a basic point of view, the transistor operation can be considered as a switch. When the voltage at the gate ( $V_G$ ) is "high" and upper than the threshold voltage ( $V_T$ ), the transistor establishes a "connection" between the source and the drain. Otherwise, the transistor isolates the source and the drain from each other in the case of a "low"  $V_G$  [11]. This section introduces the MOS behavior to help the understanding of the IO switching and SSN origin for later.

### 3.1. MOSFET history

The explanation of transistor technology and semiconductor effect began in 1833 with Michael Faraday when he described the "extraordinary case" of the electrical conduction that increases with the temperature of silver sulfide crystals and defined as the first semiconductor effect [12]. In 1938, B. Davydov, N. Mott and W. Schottky defined the semiconductor effect by the setup of an asymmetric barrier to current flow created by the electrons' concentration on the surface of the semiconductor. This is considered as the first demonstration of the semiconductor effect [13].

In 1947, W. Shockley, J. Bardeen and W. Brattain presented their "magnificent Christmas present" which they named the "transistor" at a press conference. This first solid-state device was created with two gold contacts placed close to each other. They were held with a plastic wedge on a small slab of germanium with high purity [14]. Figure 1-9 is the picture of this first transistor known as the bipolar point-contact transistor [14]. In 1948, W. Shockley introduced the bipolar junction transistor (BJT) where both electron and electron holes could carrier charge. The BJT required 3 years of process development in order to be manufactured in quantity but became the first device used for the next three decades. In 1952, the first "transistorized consumer product" appeared on the market with the hearing aid from Sonotone. It was developed with one transistor which operated with two vacuum tubes and each transistor

cost \$229.50 USD. In 1956, the discovery of the transistor point-contact transistor was rewarded with the Nobel Prize for physics for "their research on semiconductors and their discovery of the transistor effect" [15]. Less than thirteen years later, J. Atalla and D. Kahng demonstrated the first field-effect transistor (FET) and developed the MOSFET.

Figure 1-9: First semiconductor created

From this first bipolar transistor (BJT) in 1947 to the CMOS design (complementary metal oxide Semiconductor) today, the evolution never stopped from all points of view: the manufacturing process and the tests procedure [16], [17], the materials of the transistor and its technology [18], [19] as well as theories, equations, and demonstrations for semiconductor effect [20], [21]. All of this leading to the electronics proliferation that we now take for granted in our everyday. Indeed, if the last few decades are analyzed, each generation could see the arrival of electronic devices in its daily life like home-computers, mobile phones, smart watches, virtual reality headsets, and so on. This change of common life and, more generally of the electronics world originated from the transistor discovery and evolution as it became the first technology used for the development of ICs.

#### 3.2. MOSFET Structure

The purpose of this subsection is a reminder of the physical transistor structure through a simplified n-type MOS (NMOS) shown in Figure 1-10. The connection with the transistor's terminals is made by metallic contacts. The NMOS transistor is manufactured on a p-type bulk also named substrate or well. The source and the gate are defined with two doped n regions. The gate is defined by a conductive piece of polysilicon or metal, isolated from the bulk with a silicon dioxide (SiO<sub>2</sub> or High-K dielectric). Another element to point out within this simplified structure, is the definition of L, the length of the gate which is the "source-drain path", and W its width. The principal action of the device occurs under the gate oxide in the substrate region with electron movement from the source to the drain depending on the V<sub>G</sub> voltage [22]. The

last and forth terminal is the bulk (B) used to set the bulk potential. The potential of the bulk has an important influence on the device characteristics even if generally, this bulk is directly connected to the minimum or the maximum potential of the circuit -for the NMOS, the bulk is connected to the minimum one-.

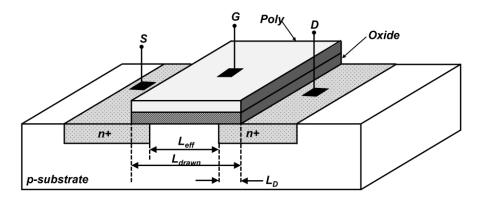

Figure 1-10: MOS structure

Finally, this CMOS technology embeds NMOS and PMOS transistors where PMOS is basically obtained by inverting all doping types including the bulk one [22], [23]. Hence, the two of them have an "opposite" behavior which permits a wide range of possibilities in CMOS design. The procedure required to manufacture this transistor and by consequence an IC is complex and involves different steps such as: Oxide growth, thermal diffusion, Ion implantation, definition of active area, photolithography, metallization, etc.[23]. Because this is not the main subject of this thesis this subsection didn't detail all of those steps. Nevertheless, should you like to know more, there are many books available on the market with all explanations [22], [23].

#### 3.3. CMOS model and behavior

For IC design, models are used to facilitate work and comprehension of a schematic. Maybe the best known example is the plan for a house construction where walls, stairs and so on are modeled with different geometrical forms. In electronic design, a model is used to represent a component or an object in a schematic. In CMOS technology there are different levels of complexity and accuracy for a model, going from the simplest one drawn by hand to a more complex one, as close as possible to the real structure, and used for computer simulations. For a transistor, standards are available to define the model that can be used for electronic simulations such as SPICE. One of these models is the BSIM (Berkeley Short-Channel IGFET Model) that provides a physical-based, accurate and predictive model of the transistor for SPICE [24], [25]. Another model to be mentioned is the EKV MOS model

developed by C. Enz, F. Krummenacher and E. Vittoz who named their model from their family name [26]. The EKV model is one of the most used by analog designers because it is an accurate and predictive model without discontinuity between operational regions [27]. Finally, symbols used for NMOS and PMOS are introduced in Figure 1-11 as well as useful voltages and currents [28].

Figure 1-11: NMOS and PMOS Model

For a first approach, the transistor behavior has been simplified by a controllable switch depending on the voltage applied to the gate. In reality, this is more complex and will be defined by several parameters listed below:

- Size of W and L, the channel width and length defining the "source-drain path size"

- Value of V<sub>DS</sub> and V<sub>GS</sub> respectively, the voltage between source/drain and source/gate for a polarization mode in weak, moderate, and strong inversion

- Value of V<sub>T</sub>: the threshold voltage defined by the transistor characteristics

- Technology characteristics as  $\mu_n$  or  $\mu_p$  and  $C_{ox}$ . Respectively the electron average mobility in the channel and the oxide capacitance. To note, the factor  $\mu_n * C_{ox}$  is defined as the device transconductance parameter.

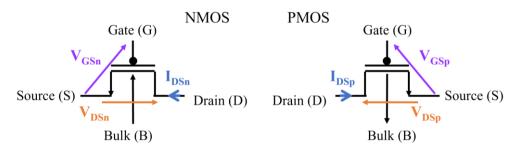

Then, the transistor's behavior could be characterized by the current  $I_{DS}$  because its equation is taking into account the characteristics listed above. From that, the transistor's behavior could be summarized with four different regions of operation [2], [23], [29]. Here we will only introduce the transistor behavior for a strong inversion because these explanations will be sufficient to study the IO behavior and in particular the SSN. A complete study of the transistor in weak, moderate and strong inversion can be found in the book of C. Enz [27].

The first region is the cut-off one also named subthreshold voltage. The transistor behavior is defined as "blocked", and the switch is open. In that case, there is no current flow which means the  $I_{DS}$  is equal to zero, only the leakage current can be measured. The transistor is in this region when  $V_{GS} < V_T$ .

The second region, named the linear, Ohmic or triode region, represents the region where the transistor operates like a resistor. The transistor operates in linear when  $V_{GS}>V_T$  and  $V_{DS}< V_{GS}-V_T$  with the  $I_{DS}$  calculation defined by the Equation 1-1. Moreover, when  $V_{DS}<< V_{GS}-V_T$  the associated resistance is defined by the Equation 1-2.

$$I_{DS} = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{1}{2} V_{DS}^2 \right]$$

Equation 1-1: I<sub>DS</sub> current in linear region and a strong inversion

$$R_{ON} = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}$$

Equation 1-2: Equivalent resistance of MOS in linear region

Third region is the saturation one and occurs with  $V_{GS}>V_T$  and  $V_{DS}>V_{GS}-V_T$ . A saturated transistor basically operates as a current source and is relatively independent of  $V_{DS}$ . Equation 1-3 provides the associated formula for the  $I_{DS}$  calculation.

$$I_{DS} = \frac{\mu_n C_{ox}}{2} * \frac{W}{L} * (V_{GS} - V_{TH})^2$$

Equation 1-3:  $I_{DS}$  current in saturation region and a strong inversion

The fourth and last region is the avalanche one. This region is reached when  $V_{DS}$  become superior to the maximum  $V_{DS}$  handled by the transistor and could lead to the transistor breakdown.

These four regions are summarized in Figure 1-12, where  $I_{DS}$  is defined in function of  $V_{GS}$  in the right figure and in function of  $V_{DS}$  in the left figure [29]. It is to be noted that, equations are defined here for the NMOS but can also be used for the PMOS with an opposite sign and  $\mu_p$  instead of  $\mu_n$ .

Figure 1-12: MOS Behavior with, Left: IDS in function of VDS and Right: IDS in function of VGS

#### 3.4. Conclusion

This section summarized the CMOS technology with the basic behavior of the MOS transistor in strong inversion. These details of MOS model and behavior are useful to understand the origin of SSN effect that will be introduced later in this chapter. The sections 1 and 2 were used to describe the general evolution of MCU performance thanks to the MOS technology. One example can be cited from Intel website to illustrate this evolution [30]: "The original transistor built by Bell Labs in 1947 was large enough that it was pieced together by hand. By contrast, more than 100 million 22 nm tri-gate transistors could fit onto the head of a pin [and this, less than 60 years later]"

Such performance evolution always implies some drawbacks. Indeed, when the MCU increases its operating frequency, decreases its size and its power supply values -as well as the amount of power supply pins for package- this creates new MCU constraints in terms of electromagnetic compatibility (EMC) like the problem of SSN. If these constraints are neglected, this could lead to an MCU failure, so they must be considered and anticipated in order to stay competitive on the market. Section 4 will go through the definition of EMC from a general point of view and regarding the SSN in particular. Then, section 5 will provide explanation about the SSN origin and its impact inside an MCU, based on the knowledge acquired with the MCU and the CMOS technology presentation.

## 4. Understanding electromagnetic compatibility

#### 4.1. Introduction and EMC definition

Because a microcontroller is a multi-application and versatile device, it has to be compatible with many environmental constraints. For example, an MCU must be able to work at high and also low temperature – generally, from -40°C to 125°C-, it must also resist to humidity, and it needs to have a certain level of electromagnetic compatibility (EMC). Nowadays, EMC is a phenomenon that concerns everyone. For example, passengers on airplanes need to turn off their mobile phones during landing and take-off. The EMC principle could be summarized as a system that must display its expected behavior when it is placed in a disturbed environment where interferences are generated by the system itself or by another electrical components in its environment [31]. A general definition for EMC can be cited from the International Electrotechnical Commission (IEC).

"The ability of a device, equipment or system to function satisfactorily in its electromagnetic environment without introducing intolerable electromagnetic disturbance to anything in that environment" [32].

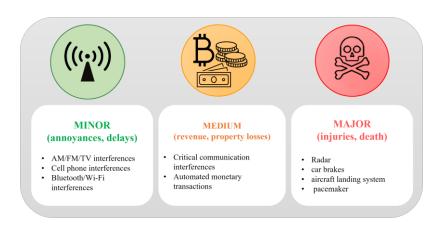

Two facts can be pointed out from this EMC definition. The first point is the principle of level and tolerance highlighted with "the ability to function satisfactorily" and the "intolerable electromagnetic interference". In other words, there are levels of susceptibility but also levels of electromagnetic emission accepted depending on the equipment usage. Nowadays, this is classified with standards that define limits for emitted and received interferences [3]. Figure 1-13 vulgarizes this classification with minor, medium or major issues. For example, if an interference disturbs the TV and impedes watching a movie this is a minor issue. Now, with the aircraft example, if an interference disturbs the aircraft systems, this could lead to injuries or deaths, which is definitely a major issue. So, in order to release an MCU or any electronics device on the market, the device must comply with requirements defined by the European directives to guarantee the EMC compliance and to obtain the CE marking.

Figure 1-13: EMC issues gravity

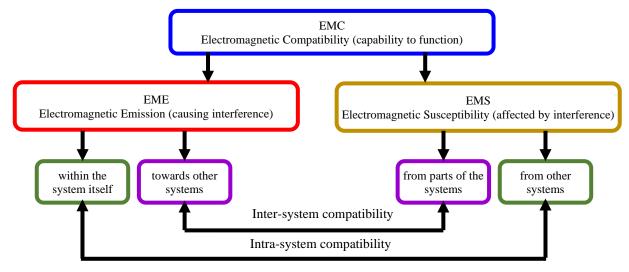

The second point to be noted is the difference between the susceptibility of a system to an electromagnetic interference and the generation of this interference by a system, dividing the EMC problematic in two parts. On one hand, the electromagnetic susceptibility (EMS) studies the immunity of the device in the presence of an interference. In that case, the electronic device is considered as the victim of its electronic environment. On the other hand, the electromagnetic interference (EMI) defines the device as an aggressor and studies its perturbation generation. Finally, the dissociation between intra-system and inter-system perturbation should be highlighted. In the case of inter-system, the electronic device is the victim of an external EMI generated in its electromagnetic environment as this is the case

with the example of aircraft and cellphone. In the case of intra-system, the victim is disturbed by an internal EMI, generated by the system itself leading to an auto-susceptibility problem. This is summarized with a diagram in Figure 1-14 [32].

Figure 1-14: Relation between various EMC terms

In this section, the EMC origin is explained with the Maxwell equations. Then, additional explanation regarding EMI and EMS are given as well as the propagation path between them. Finally, this section explains how the SSN is part of the EMC consideration into an MCU.

## 4.2. The physics behind EMC

The base of electromagnetic theory is given with Maxwell's equations which give the possibility to define the electromagnetic state of an environment in any point and at any instant. Even if electromagnetic principles were highlighted by many physicists such as Faraday, Ampere and Gauss, it was James C. Maxwell in 1860, who determined the equations that define the Electromagnetic Field (EM), composed of the electric field intensity vector  $\vec{E}$  (in V.m<sup>-1</sup>) and the magnetic flux density vector  $\vec{B}$  (in Wb.m<sup>-2</sup>) [33], [34]. Some approximations are generally made such as lumped-circuit model, initial and limit conditions -as long as the problem is electrically small- because being able to find a solution to those equations is not a simple process. Whatever equation's complexity as mentioned by C.R. Paul in his book [35]:

"Maxwell's equations form the cornerstones of electromagnetic phenomena [...]. We should always be cognizant of the fact that Maxwell's equations govern all electromagnetic phenomena and their [the equations] complexity does not change this fact".

Using Maxwell's theory, it is possible to define the EM field creation, to understand if this is a magnetic or electric field but also to determine how it is propagated [5] [35]. Table 1-2 gives a summary of Maxwell's equations with their integral forms as well as their differentials form -also named local or punctual-.

| Faraday Law                                       | $\nabla \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial \mathbf{t}}$         | $\oint_{\partial \Sigma} E \cdot dl = -\frac{d}{dt} \iint_{\Sigma} B \cdot dS$                                       |

|---------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Ampere's Law                                      | $\nabla B = \mu_0 \left( J + \epsilon_0 \frac{\partial E}{\partial t} \right)$ | $\oint_{\partial \Sigma} B.  dl  =  \mu_0 (\iint_{\Sigma}  J.  dS +  \epsilon_0 \frac{d}{dt} \iint_{\Sigma}  E.  dS$ |

| Gauss's Law                                       | $\nabla E = \frac{\rho}{\epsilon_0}$                                           | $ \iint_{\partial\Omega} E. dS = \frac{1}{\varepsilon_0} \iiint_{\Omega} \rho dV $                                   |

| Gauss's law for magnetism and charge conservation | $\nabla B = 0$                                                                 | $ \oint_{\partial\Omega} B. dS = 0 $                                                                                 |

Table 1-2: Maxwell's equations

#### 4.3. Electromagnetic susceptibility and coupling path

The electromagnetic susceptibility (EMS) is the ability of a device to operate without degradation of its performance in the presence of an EMI. Based on the standard IEC 62132, effects of electromagnetic perturbations on an IC are classified in four categories. This norm defines the device susceptibility level based on the observed EMI consequences [36]. This is summarized with Table 1-3:

| Level | Observations                                                                                                                                                              |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A     | Normal performance                                                                                                                                                        |  |  |  |

| В     | Temporary functionalities degradations or even a loss of functionalities. The nominal operation is recovered after the failure removal.                                   |  |  |  |

| С     | Temporary functionalities degradations or even a loss of functionalities. The nominal operation is recovered after the removal of the failure and a reset of the product. |  |  |  |

| D     | Permanent functionalities degradations dues to a system damage                                                                                                            |  |  |  |

Table 1-3: Failure level classification for a system disturbed by an EMI

Different parameters could influence the susceptibility of an IC. Besides the perturbation characteristics, there are also the design choices and the technology used as well as the IC usage [36]. More details about the STM32 susceptibility can be found in the thesis of Y. Bacher [3].

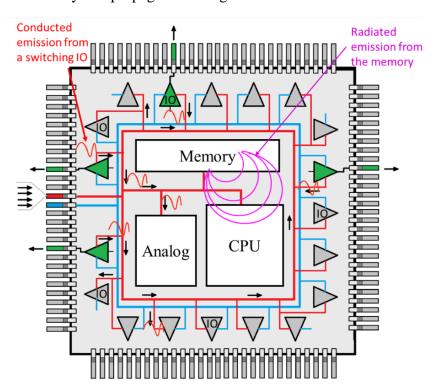

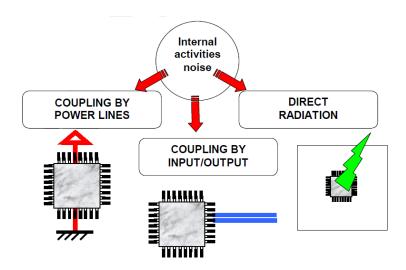

If a device is susceptible to interference, it means that there is a coupling path between the EMI and the EMS. By analogy to the Maxwell equations, the coupling path is defined as the electromagnetic interference propagation. Basically, a disturbance could be propagated through two different paths. Firstly, we will speak of conducted emission when a noise propagates through a physical connector. For example, when a light at home shortly lose intensity or blinks- because an electronic device required too much power. Then, we will speak of radiated emission when the noise is propagated through "the air" and disturb another device in its environment. This is the case for the example of the cellphone used in the airplane mentioned before. Inside the MCU, the same principle of intra-system radiated and conducted emission is found. An example of radiated emission could be cited in the internal memory perturbation studied by J.P. Leca thesis [2]. Then, the SSN effect is defined as a conducted emission where interference generated by an IO is propagated through power and ground supply lines. Figure 1-15 provides an example of intra-system propagation with conducted emissions through power and ground generated by the core or by switching IOs and radiated emission generated by the memory and propagated through air.

Figure 1-15: Auto-susceptibility of an Integrated Circuit

It is worth to be noted that an MCU is also susceptible to inter-system EMI propagated by conduction and radiation. The radiated emission could appear between two components close to each other and an interference could be propagated by conduction through any PCB physical connection.

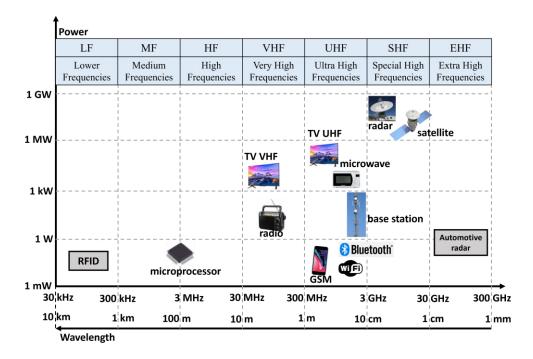

#### **4.4.** Electromagnetic interference (EMI)

From a general point of view, external EMI can be classified by its level of power and its frequency of work as illustrated in Figure 1-16 [36].

Figure 1-16: EMI classification overview

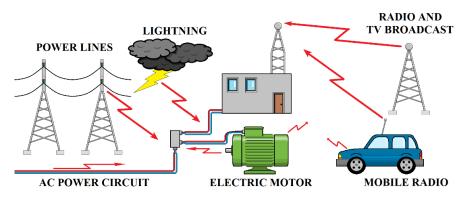

There are many different possible sources for an EMI and an overview of them is depicted in Figure 1-16. External EMI is the best known as it can be encountered by everyone in modern life as illustrated in Figure 1-17 [3]. It is mainly classified in two categories: natural or industrial. For natural noise, the source could be an atmospheric noise, a magnetic storm, a thunderstorm, etc. .... In contrary, any perturbation that emanate from a manmade object will be considered as an industrial EMI. This is the case with radio and wireless communications, motors, powerlines, Electrostatic discharge (ESD), but also from another integrated circuit close enough to the MCU on a PCB [3].

Figure 1-17: External EMI usual sources [3]

Secondly, an internal EMI is a type of noise sometimes neglected but which can significantly affect an electronic device [3]. Any perturbation that is generated by the device itself and disturbs its functionalities will be defined as an internal EMI. Internal EMI could have different origins such as a perturbation generated by the core, perturbation generated by the internal memory or simultaneous switching IOs with the SSN explained at the end of this chapter. An EMI could be critical for an STM32 as detailed J.P Leca in his thesis with the study of MCU auto-susceptibility from a radiated EMI generated by the internal memory [2].

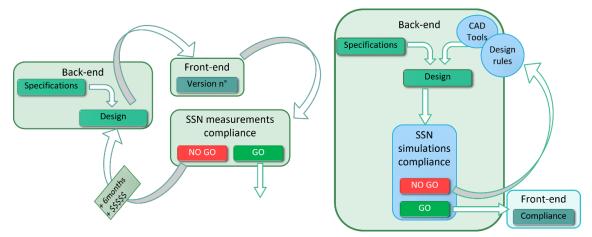

#### 4.5. Conclusion

This section introduced the EMC from a general point of view through the definition of EMI, EMS and coupling path. It allowed to properly understand how an MCU is susceptible to generate interference but also how this interference is propagated to the victim. It is important to note that EMC is a constant problematic for designers. It appears in 1895 with the creation of the radio where intentional or unintentional interferences could disturb a transmission. Unfortunately, it never stopped increasing and forced designers to have a new methodology of work in terms of EMC as illustrated in Figure 1-18. Typically, when designers understood that the product had an EMC failure this was at the validation stage, so after the MCU design and manufacture. When such problem appears at a late stage, finding a solution requires time and money for research, re-design and manufacture, but this also delays the product release on the market. So, designers changed their working methodology in terms of EMC and tried to anticipate the MCU compliance at the design stage to ensure the system good performance and remain competitive on the market. Finally, as it will be explained in the next section, the SSN effect is defined as a problem of MCU auto-susceptibility because an IO is at the same time, the aggressor and the victim. So, the SSN is part of the EMC compliance for STM32 and must be anticipated ensuring the STM32 robustness.

Figure 1-18: Workflow for EMC problem

# 5. From the CMOS inverter to the Simultaneous Switching Noise

In the bibliography, demonstration of SSN effect can be found in scientific papers from 1985 and even earlier [37]. In this section, we will explain the origin of this phenomenon, based on MOS transistor knowledge introduced in previous paragraphs. Then, the SSN effect at the MCU level will be defined, justifying in the same way the purpose of this thesis.

#### **5.1.** CMOS Inverter

#### **5.1.1.** Inverter principle

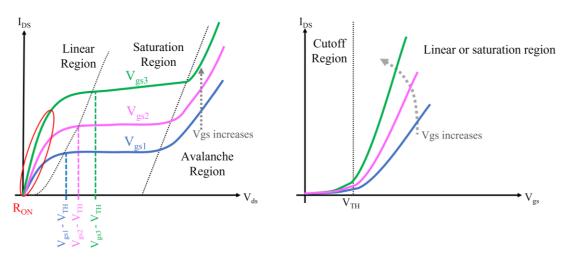

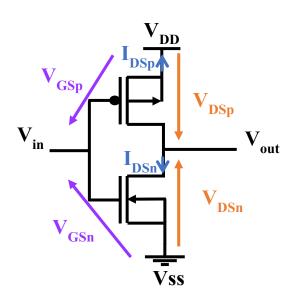

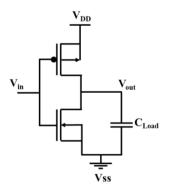

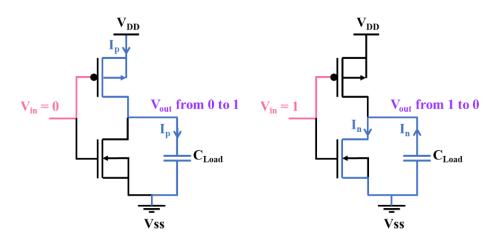

The CMOS inverter is one of the most basic circuits in analog and mixed design composed only of one PMOS and one NMOS transistors. Figure 1-19 schematizes this circuit including all notations for currents and voltages as  $V_{DS}$  the drain-source voltage and  $V_{GS}$  the gate-source voltage for transistors. The inverter behavior can be described as follows: when  $V_{in}$  is low and equal to  $V_{SS}$  the PMOS is in linear region and the NMOS in the cut-off region, leading to a logical '1' for the output. Reversely, when  $V_{in}$  is high and equal to  $V_{DD}$ , the PMOS is off and the NMOS is conducting which implies a logical '0' on the output [11].

Figure 1-19: Basic inverter schematic

#### 5.1.2. Voltage transfer characteristic

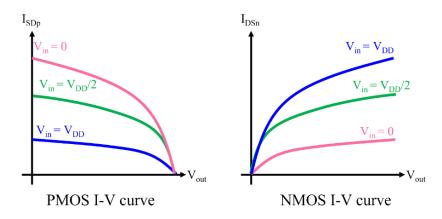

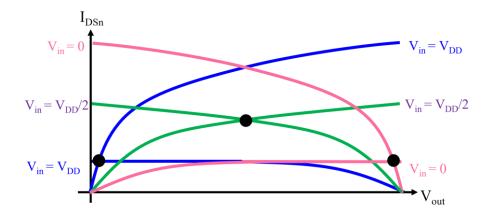

The voltage transfer characteristic (VTC) of a CMOS inverter is defined by the waveform of  $V_{OUT}$  in function of  $V_{IN}$ . This waveform is obtained by the superposition of the two I-V curves of each transistor. For a quick reminder, the I-V curve represents the  $I_{DS}$  current in function of the  $V_{DS}$  voltage for different values of  $V_{GS}$ . Figure 1-12 illustrated this for an NMOS transistor. Of course, for a PMOS transistor, this I-V curve will be on the "opposite" side which means it has to be "flipped over" compared to the NMOS curve. It is also necessary to express each of these I-V curve in function of  $V_{IN}$  and  $V_{OUT}$ . Figure 1-20 illustrates the typical I/V curves and for that, the following assumption needs to be made [38]:

- $I_{DSn} = -I_{DSp} = I_{SDp}$

- $V_{GSn} = V_{in}$  and  $V_{DSn} = V_{out}$

- $V_{GSp} = V_{IN}$   $V_{DD}$  and  $V_{DSp} = V_{OUT}$   $V_{DD}$

Figure 1-20: I-V curve for PMOS and NMOS

Finally, it is then possible to superpose the two curves, as depicted in Figure 1-21 [39].

Figure 1-21: I-V curve of NMOS and PMOS superposition

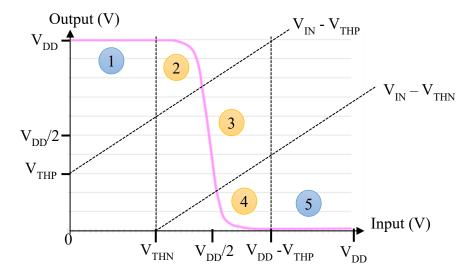

Once this waveform is obtained, we can extract the VTC waveform by identifying the value of  $V_{\rm IN}$  and  $V_{\rm OUT}$  at each crossing point -defined with a black dot in Figure 1-21-. Figure 1-22 illustrates the final VTC waveform obtained and Table 1-4 summarizes this waveform in terms of input and output values and transistor operation.

Figure 1-22: Voltage Transfer Characteristics of an Inverter

| Region | Input Voltage V <sub>IN</sub>                       | Output Voltage V <sub>OUT</sub> | NMOS Transistor | PMOS Transistor |

|--------|-----------------------------------------------------|---------------------------------|-----------------|-----------------|

| 1      | $V_{IN} \leq V_{THN}$                               | $V_{OUT} = V_{OH} = V_{DD}$     | Cut-off         | Linear          |

| 2      | $V_{THN} \leq V_{IN} \leq V_{OUT}$ - $V_{THP}$      | $V_{OUT} > V_{DD}/2$            | Saturation      | Linear          |

| 3      | $V_{IN} \approx V_{DD}/2$                           | $V_{OUT} \approx V_{DD}/2$      | Saturation      | Saturation      |

| 4      | $V_{OUT} + V_{THN} \le V_{IN} \le V_{DD} + V_{THP}$ | $V_{OUT} < V_{DD}/2$            | Linear          | Saturation      |

| 5      | $V_{IN} \ge V_{DD}$ - $V_{THP}$                     | $V_{OUT} = V_{OL} = 0$          | Linear          | Cut-off         |

Table 1-4: Voltage Transfer characteristics table

This demonstration has been done with the specific purpose of highlighting the three specific regions 2, 3 and 4. In these ones, PMOS and NMOS could be simultaneously in saturation mode or in saturation/linear mode. In other words, there are states where both of the transistors are conducting at the same time leading to a resistive current path between the power and the ground.

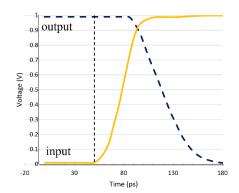

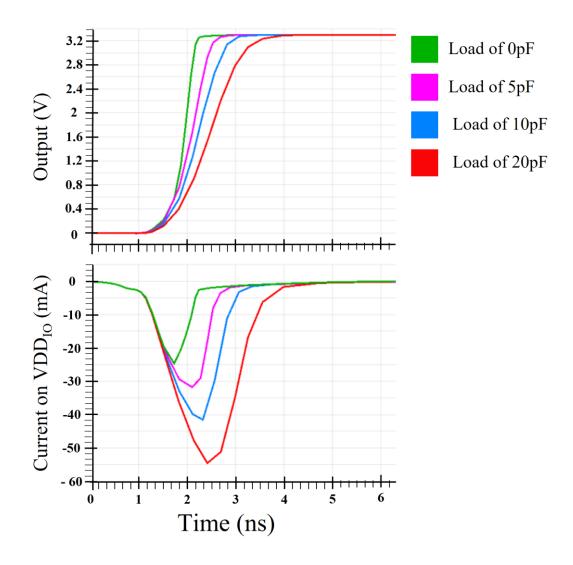

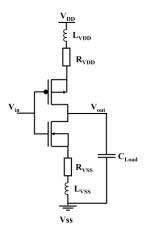

### **5.1.3.** Dynamic properties of the inverter

For this study, the schematic of the inverter has been redrawn in Figure 1-23 where a load capacitor was added to the output. Generally, the inverter is used to control an electronic block or to transmit information. Whatever is connected to its output, we can assimilate it to a