## Design of multi-FPGAs platform in the cloud for neural network applications

Wu Chen

#### ▶ To cite this version:

Wu Chen. Design of multi-FPGAs platform in the cloud for neural network applications. Micro and nanotechnologies/Microelectronics. Université de Lyon, 2021. English. NNT: 2021LYSES030 . tel-03720535

### HAL Id: tel-03720535 https://theses.hal.science/tel-03720535v1

Submitted on 12 Jul 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Nº d'ordre NNT : 2021LYSES030

#### THÈSE DE DOCTORAT DE L'UNIVERSITÉ DE LYON

opérée conjointement Université Jean Monenet

École Doctorale 488 Sciences Ingénierie Santé

#### Spécialité

Micro-électronique Soutenance publique le 29 Octobre 2021, par :

Chen WU

#### Design of multi-FPGAs platform in the cloud for neural network applications

#### Devant le jury composé de :

| M. Stéphane Mancini  | MCF-HDR | Grenoble INP- UGA         | Rapporteur            |

|----------------------|---------|---------------------------|-----------------------|

| M. Stefan Duffner    | MCF-HDR | Laboratoire LIRIS-INSA Ly | on Rapporteur         |

| M. Dominique Houzet  | PR      | Lab GIPSA-UGA             | Examinateur           |

| M.Jean-Paul Jamont   | PR      | LCIS-UGA                  | Examinateur           |

| Mme. Yang Fan        | PR      | ImVIA-Université de Bourg | ogne Examinateur      |

| M. Florent Carlier   | MCF- HC | CREN-Le Mans Université   | Invité                |

| Mme. Virginie Fresse | MCF-HDR | LaHC-UJM                  | Directrice de thèse   |

| M. Hubert Konik      | MCF     | LaHC-UJM                  | Co-directeur de thèse |

## **Contents**

| Снарті | er 1 Introduction                                            | 1        |

|--------|--------------------------------------------------------------|----------|

| 1.1    | GENERAL CONTEXT                                              | 2        |

| 1.2    | Objective                                                    | 3        |

| 1.3    | CONTRIBUTIONS                                                | 4        |

| 1.4    | ORGANIZATION OF MANUSCRIPT                                   | 5        |

| Снарті | er 2 CNNs on FPGA                                            | 7        |

| 2.1    | Convolutional Neural Network                                 | 8        |

|        | 2.1.1 Network layers                                         | 9        |

|        | 2.1.2 Inference and training                                 | . 1      |

| 2.2    | FIELD PROGRAMMABLE DEVICES                                   | <b>4</b> |

| 2.3    | DESIGN FLOW OF APPLICATION OF FPGA                           | 4        |

|        | 2.3.1 System specification                                   | 4        |

|        | 2.3.2 IP design                                              | . 5      |

|        | 2.3.3 IP integration                                         | . 5      |

|        | 2.3.4 Synthesis                                              | . 7      |

|        | 2.3.5 Placement & routing                                    | . 7      |

|        | 2.3.6 Programming FPGA                                       | . 8      |

| 2.4    | Challenges of CNNs on FPGAs                                  | . 8      |

| Снарті | ER 3 ACCELERATING CNNs FROM LOCAL TO VIRTUALIZED FPGA IN THE |          |

|        | CLOUD: A SURVEY OF TRENDS                                    | 21       |

| 3.1    | Introduction                                                 | 22       |

| 3.2    | Background                                                   | 26       |

|        | 3.2.1 FPGA cloud                                             | 26       |

|        | 3.2.2 FPGA virtualization                                    | 27       |

| 33     | CNN IMPLEMENTATION TECHNIQUES                                | 30       |

|       | 3.3.1 Hardware architecture design                                       | . 30 |

|-------|--------------------------------------------------------------------------|------|

|       | 3.3.2 Network compression                                                | . 31 |

|       | 3.3.3 Optimization strategy                                              | . 32 |

| 3.4   | Accelerating CNNs from local to virtualized FPGAs in the cloud $\dots$ . | . 33 |

|       | 3.4.1 CNNs on local FPGA                                                 | . 33 |

|       | 3.4.2 CNNs on local virtualized FPGA                                     | . 36 |

|       | 3.4.3 CNNs on virtualized FPGA in the cloud                              | . 38 |

|       | 3.4.4 CNN deployment in commercial cloud                                 | . 40 |

| 3.5   | Trends of CNN accelerators                                               | . 40 |

| 3.6   | Discussion                                                               | . 45 |

|       | 3.6.1 Unresolved challenges                                              | . 45 |

|       | 3.6.2 Industrial solution                                                | . 46 |

|       | 3.6.3 Roadblocks of FPGA Cloud                                           | . 47 |

| 3.7   | Conclusion                                                               | . 47 |

| Снарт | er 4 Accelerating CNNs on FPGA platform                                  | 49   |

|       | Principle of the platform                                                |      |

| 4.2   | Streaming                                                                | . 53 |

|       | 4.2.1 IP Design                                                          | . 53 |

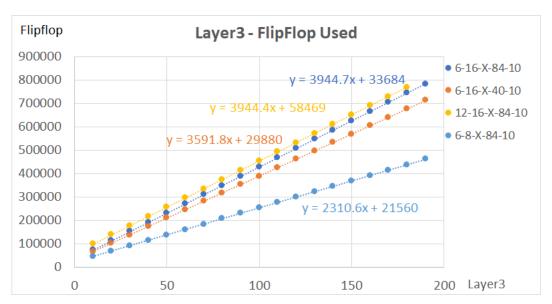

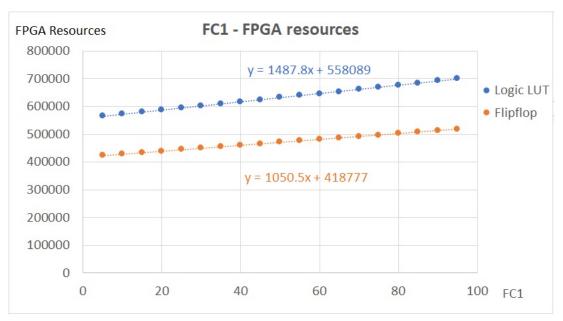

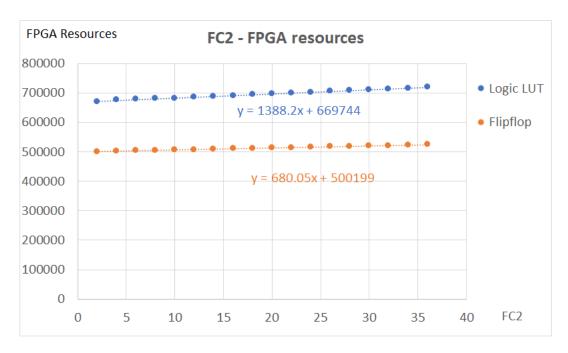

|       | 4.2.2 Mathematical model of resource utilization                         | . 59 |

|       | 4.2.3 Latency results                                                    | . 66 |

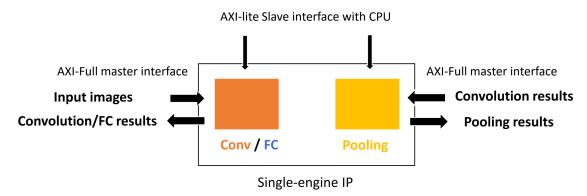

| 4.3   | Single Engine Computation                                                | . 68 |

|       | 4.3.1 IP design                                                          | . 68 |

|       | 4.3.2 Generic CNN parameters                                             | . 71 |

|       | 4.3.3 Optimization                                                       | . 71 |

| 4.4   | QUANTIZATION                                                             | . 73 |

|       | 4.4.1 Our quantization tool                                              | . 75 |

|       | 4.4.2 Experimental results                                               | . 79 |

| 4.5   | Conclusion                                                               | . 82 |

| CHART | er 5 Proposal of a FPGA-based Cloud platform                             | 83   |

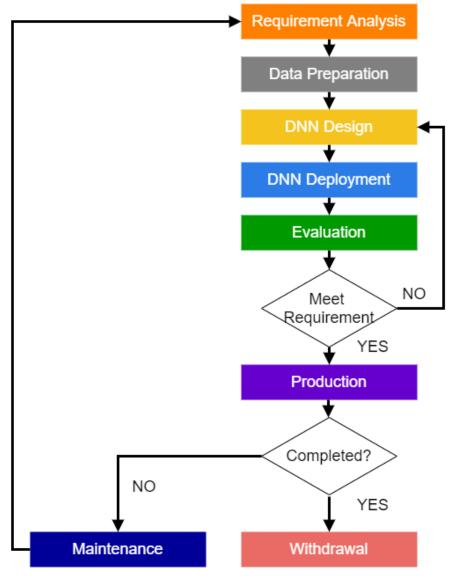

|       | OVERVIEW OF CNN-BASED APPLICATION LIFECYCLE                              |      |

| ٦.1   | 5.1.1 Requirement analysis                                               |      |

|       | 5.1.2 Data Preparation                                                   |      |

|       | 5.1.3 CNN design                                                         |      |

|       | JIIJ OININUOJEII                                                         | . 00 |

|         | 5.1.4 CNN deployment                                                   | 88  |

|---------|------------------------------------------------------------------------|-----|

|         | 5.1.5 Evaluation                                                       | 89  |

|         | 5.1.6 Production                                                       | 89  |

|         | 5.1.7 Maintenance                                                      | 90  |

|         | 5.1.8 Withdrawal                                                       | 91  |

| 5.2     | REVIEWING CNN DEPLOYMENT TOOLS IN FPGA CLOUDS                          | 91  |

|         | 5.2.1 Identified tools                                                 | 91  |

|         | 5.2.2 Analysis of the tools according to the CNN application lifecycle | 92  |

|         | 5.2.3 Challenges                                                       | 94  |

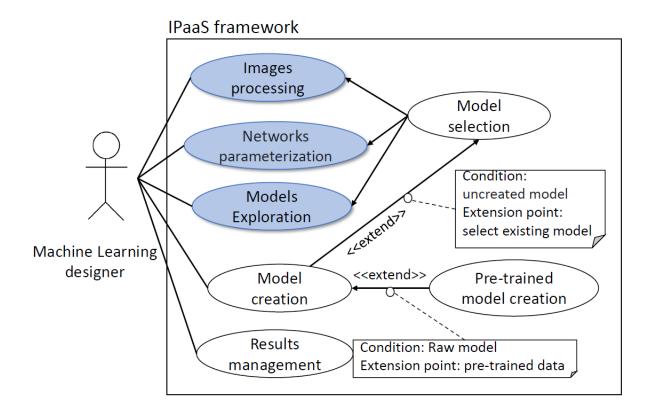

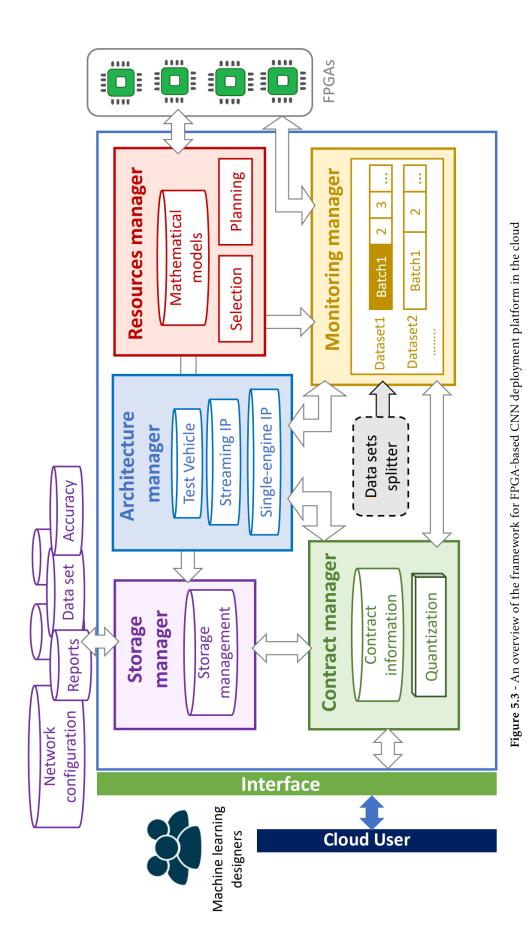

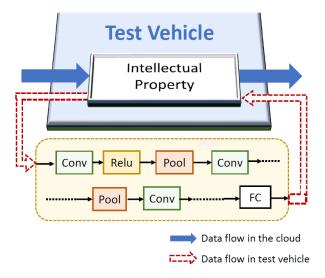

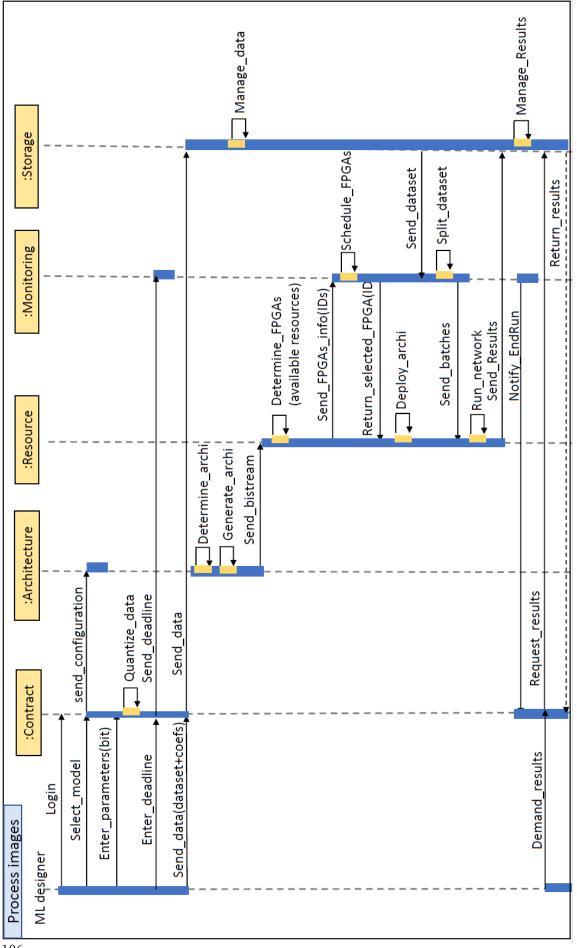

| 5.3     | A FRAMEWORK FOR FPGA-BASED CNN DEPLOYMENT PLATFORM                     | 97  |

|         | 5.3.1 Contract manager                                                 | 99  |

|         | 5.3.2 Architecture manager                                             | 99  |

|         | 5.3.3 Monitoring manager                                               | 100 |

|         | 5.3.4 Resource manager                                                 | 101 |

|         | 5.3.5 Storage manager                                                  | 102 |

| 5.4     | Study case                                                             | 103 |

| 5.5     | Conclusion                                                             | 107 |

| Снарт   | er 6 Conclusion and Perspectives                                       | 109 |

| 6.1     | CONCLUSION                                                             | 110 |

| 6.2     | Perspectives                                                           | 110 |

| LISTE D | DES CONTRIBUTIONS                                                      | 113 |

| LISTE D | DES CONTRIBUTIONS                                                      | 113 |

| List oi | FIGURES                                                                | 114 |

| List oi | F TABLES                                                               | 116 |

| Вівцю   | GRAPHY                                                                 | 117 |

#### Chapter 1

## Introduction

# Contents 1.1 General context 2 1.2 Objective 3 1.3 Contributions 4 1.4 Organization of manuscript 5

#### 1.1 GENERAL CONTEXT

This thesis is realized in the Hubert Curien Laboratory, supported by China Scholarship Council (Grant number, 201708070009).

In the field of deep learning, neural networks such as convolution neural networks (CNNs) and recurrent neural networks (RNNs) are widely used in computer vision, speech recognition, natural language processing, and other fields [25].

Since 2010, ImageNet ILSVRC Challenge[3] has been held annually to evaluate neural network algorithms for object detection and classification. Each participating group used a large-scale image data set to test the algorithm's performance in processing image classification, target positioning, target detection, and other applications. In 2012, the CNN algorithm achieved a historic breakthrough, where AlexNet[80] achieved a top-5 error of 15.3%, more than 10.8 % lower than that of others participating. CNN's take this breakthrough as an opportunity to promote the development of the current deep learning boom.

The rapid development of neural network algorithms has led to neural network architectures with more calculations and deeper structures. In addition, with the deepening of neural network, the execution of network on the CPU/GPU faces the problem of energy efficiency. Due to Moore's Law, the transistor scale of chips has reached its limit, resulting in slower growth in processor performance[118]. At the same time, because the CPU/GPU consumes too much energy (85W and 200W, respectively) [39], it is not feasible to increase the number of processors to improve execution capabilities. Therefore, the current problem is to reduce energy consumption while maintaining the high efficiency of network execution.

In this case, Field Programmable Gate Array (FPGA) has become another option for implementing neural network algorithms because of its lower energy consumption compared to CPU/GPU [4]. In addition, FPGA has the advantage of being reconfigurable and can be flexibly configured according to the characteristics of the neural network algorithm to meet diverse needs. Finally, FPGA supports multiple granular parallelisms, which means multi-core or many-core can be used to obtain coarse-grained parallelism for neural network acceleration. Therefore, it is possible to select the flexible data bit width of the arithmetic unit for neural network inference without wasting resources.

Meanwhile, cloud computing is considered a technology that can provide end-users

with high-speed, cost-effective, and scalable computing [104]. In the cloud computing scenario, users upload data to a cloud server and send task requests via the Internet. The cloud server processes the user data and returns the result. This calculation method improves the utilization of computing resources and reduces the maintenance cost of software and hardware resources for individual users.

Due to the advantages of cloud computing, many companies are working hard to deploy CPUs/GPUs in the cloud to improve computing power [66, 48, 13]. In 2002, Amazon introduced the Amazon Web Service [16], which allows individual users to access the computation resources in the cloud. In 2010, Microsoft launched the Azure [21] project to provide the facilities of the computing resources and services, which the users can dynamically use according to the application demands. However, deploying FPGAs in the cloud has less success than GPUs because the use of FPGAs in the cloud requires the user's hardware expertise and low-level cognition, which cannot be mastered in a short time. Therefore, only a few companies have put effort into deploying FPGAs in the cloud, such as Amazon AWS [1], HUAWEI cloud [2].

Porting FPGAs as the calculation resource in cloud computing benefits the following advantages: 1)calculation acceleration, the performance, and power benefits are achieved by designing custom calculations of data paths tailored to the application; 2) cloud security, allowing data to be stored and manipulated remotely in an encrypted form, effectively preventing the server from accessing the processed information; 3) lower energy consumption, using FPGAs as a calculation node and realize accelerators based on the FPGA in the cloud.

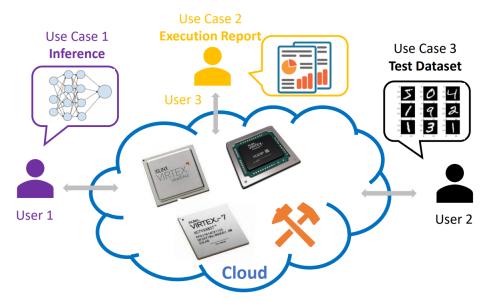

Therefore, this thesis aims to provide cloud users with an FPGA-based infrastructure to execute their CNN applications in various use cases (for example, CNN model exploration, network parameterization, etc.), not just perform CNN inference.

#### 1.2 OBJECTIVE

The objective of the thesis is to provide a cloud computing infrastructure in which there are several FPGAs of different families and types. These FPGAs communicate with each other and are made available to the machine learning engineer to execute CNNs.

This Cloud FPGA is dedicated to machine learning engineers when they wish to "execute" CNNs, that is to say, to perform training or inference on different CNN models

with image databases and without hardware expertise. The Cloud platform can generate different CNNs architectures and deploy these architectures in the appropriate FPGAs. Additionally, machine learning engineers can exploit these FPGAs by exploring the CNN model and available FPGAs in the cloud.

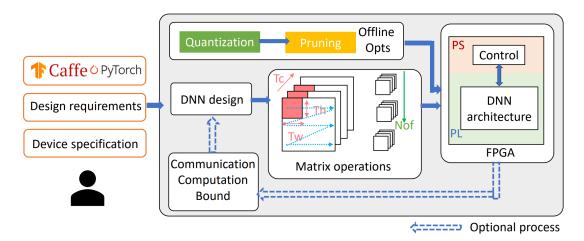

**Figure 1.1** - Cloud computing-type platform for CNNs inference on the FPGA.

#### 1.3 Contributions

The contribution of this thesis is to propose a cloud computing type platform for machine learning engineers to perform general CNN inference on FPGA. Furthermore, the proposed platform can analyze the user needs of different use cases, deploy the CNN hardware architecture on the appropriate FPGA, and implement optimization techniques when necessary.

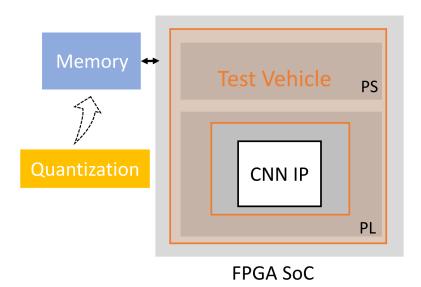

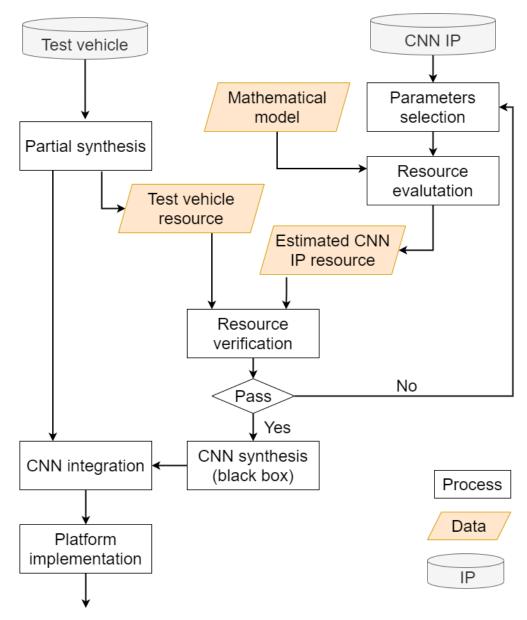

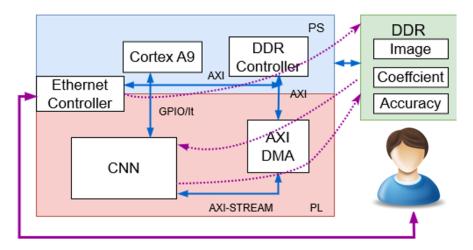

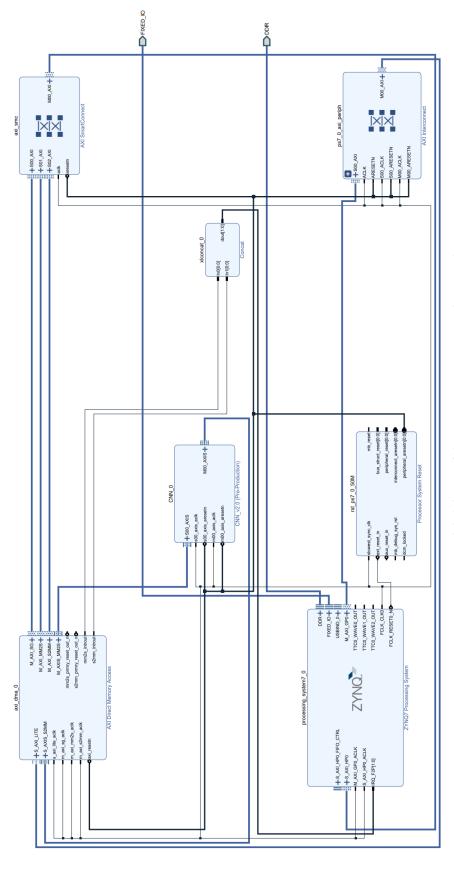

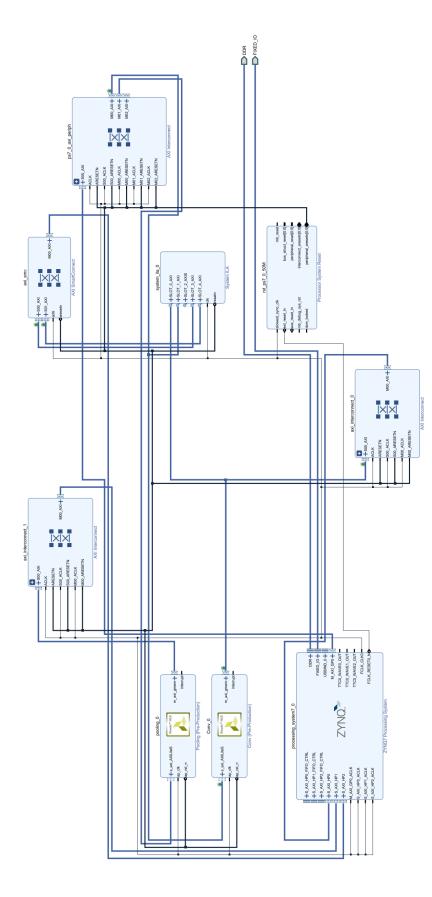

Two types of generic CNN IPs are defined and developed for generating CNN hardware architectures on the FPGA. These IPs are adapted to several CNNs algorithms by configuring the different CNN parameters. The CNN IPs are tested and integrated by the test vehicle on the FPGA SoC. A communication prototype between Programme logic (PL) and Process system (PS) of the FPGA is achieved in the design.

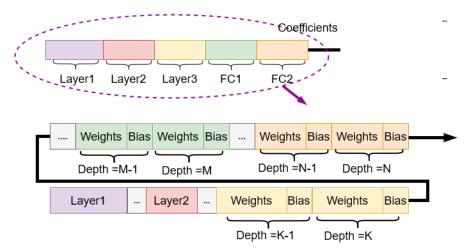

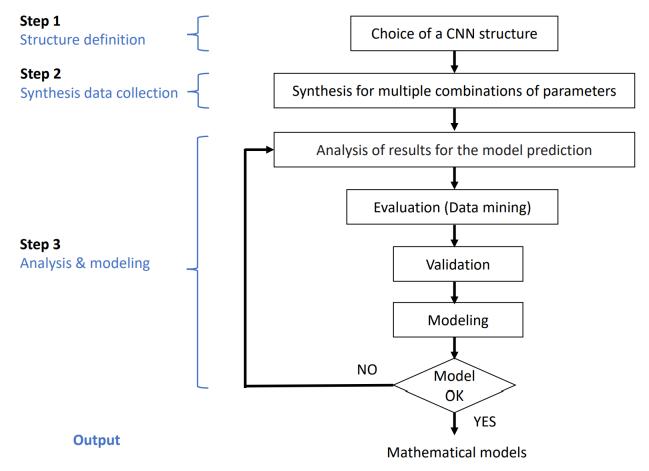

The platform involves several mathematical models, which estimate the resource usage of the two IPs developed. This estimation can help allocate FPGA resources well in the cloud. A quantization tool is developed to compress the network size on the FPGA. Then, a life cycle of the cloud platform is designed to show the process of executing CNN

inference. This life cycle includes different stages to clarify the execution process of multi-user CNN development.

#### 1.4 Organization of manuscript

This manuscript first starts by presenting the general context and objectives of the thesis.

Chapter 2 provides a comprehensive introduction to CNN and FPGA and implementation methods and related challenges.

Chapter 3 conducts in-depth research of the technologies and the evolution of CNN accelerators, from a single CNN in the local to multiple CNNs IN the cloud, enhancing the current understanding of the evolution of FPGA-based CNN accelerators.

Chapter 4 presents the realization of different CNN hardware architectures and the completion of quantification tools and optimization methods.

Chapter 5 proposes a novel platform with a lifecycle for multiple users to execute CNN on FPGA in the cloud.

Chapter 6 concludes this manuscript and presents the future directions of the work.

### Chapter 2

## CNNs on FPGA

| Contents |                                               |

|----------|-----------------------------------------------|

| 2.1      | Convolutional Neural Network                  |

|          | 2.1.1 Network layers                          |

|          | 2.1.2 Inference and training                  |

| 2.2      | FIELD PROGRAMMABLE DEVICES                    |

| 2.3      | DESIGN FLOW OF APPLICATION OF FPGA            |

|          | 2.3.1         System specification         14 |

|          | 2.3.2 IP design                               |

|          | 2.3.3 IP integration                          |

|          | 2.3.4 Synthesis                               |

|          | 2.3.5 Placement & routing                     |

|          | 2.3.6 Programming FPGA                        |

| 2.4      | CHALLENGES OF CNNs ON FPGAS                   |

This thesis proposes a cloud computing type platform for machine learning engineers to perform general CNN usages on FPGA. Therefore, the first step of this platform is to implement CNNs on the FPGA.

The development of CNNs, which involves hundreds of millions of learnable parameters, puts a higher demand on hardware performance. Therefore, how to implement high-performance CNNs on the FPGA-based device has been a new challenge. Besides, under the condition of ensuring performance, how to reduce the calculation and data workload is also an important aspect.

This chapter is organized as the following:

- Section 2.1 gives an introduction to CNN, including the explanation of CNN operation, as well as the training and inference phase in CNN;

- Section 2.2 presents the FPGA devices with the internal architecture and resources;

- Section 2.3 summaries the FPGA design flow, which comprises of several different steps or phases to finally execute an application;

- Section 2.4 lists several significant challenges for CNN's implementation on the FPGAs.

#### 2.1 Convolutional Neural Network

Convolutional Neural Network (CNN) is a famous neural network structure in the field of deep learning. Nowadays, many visual image applications apply the CNNs because multi-layer convolution has an impact on the feature extraction of three-dimensional images (RGB) [68, 130, 105].

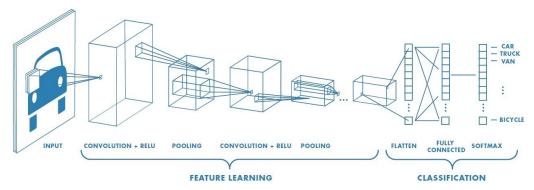

**Figure 2.1** - Structure of a convolution neural network[6].

In general, a standard convolutional neural network has four elements: convolution kernel, pool sampling, activation function, and full-connection. The convolution kernel is applied to extract higher-level abstraction of the input image, namely the feature map. Pooling sampling aims at reducing the feature map size. The activation function is to provide nonlinearity in the neural network classification. The fully connected layer is used as the classification output to predict the final results. Finally, the backpropagation algorithm is applied in a CNN to train the entire neural network. A structure of a convolution neural network is shown in the figure 2.1.

#### 2.1.1 Network layers

#### 2.1.1.1 Convolution (Conv)

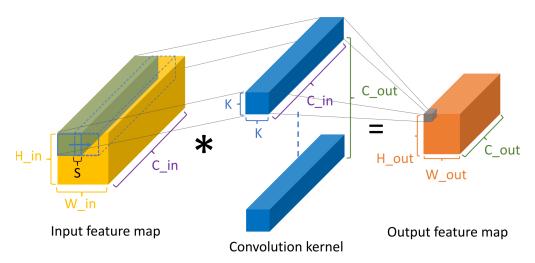

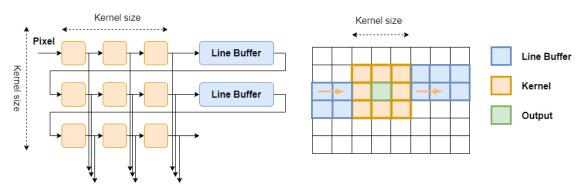

The convolution usually implements an operation similar to filtering. It applies a K x K size convolution kernel to the input feature map to perform vector point multiplication shown in the figure 2.2.

**Figure 2.2** - Example of the convolution operation.

The heavy computation of CNN is almost the convolution operation[109], we thus make a deep study to explain the process of the convolution clearly. Table 2.1.1.1 lists all necessary parameters in a convolution operation. The convolution input is an input feature map with W\_in x H\_in x C\_in and the kernel with K x K x C\_in x C\_out. The convolution output is the feature map with the dimension W\_out x H\_out x C\_in x C\_out. The convolution operation is essentially accumulable multiple and addition. After filling the input feature maps with the parameter P, the convolution operation firstly intercepts the feature map with K x K x C\_in dimension on the filled input feature map. This feature

map will be multiplied and accumulated with the three-dimensional convolution kernel of the same size to obtain a pixel of the output feature map. Secondly, the operation will traverse the input feature maps according to the stride S to obtain a two-dimension W\_out x H\_out result. Repeating these two steps in the C\_out channel, a final feature map with W\_out x H\_out x C\_out can be conducted. Finally, a bias is addded. The expression of the output **O** is 2.1:

$$O[n][x][y] = B[n] + \sum_{k=0}^{C_{in-1}} \sum_{i=0}^{W_{in-1}} \sum_{j=0}^{H_{in-1}} I[k][Sx+i][Sy+j] \times W[n][k][i][j]$$

$$0 \le n < C_{out}, 0 \le x < W_{out}, 0 \le y < H_{out}$$

$$(2.1)$$

| Parameter | Detail                                             |

|-----------|----------------------------------------------------|

| W/H_in    | Width and height of the input image                |

| W/H_out   | Width and height of the output image (feature map) |

| C_in      | Number of input channels                           |

| C_out     | Number of output channels                          |

| K         | Kernel size                                        |

| S         | Stride of the convolution                          |

| P         | Padding of the convolution                         |

|           |                                                    |

#### 2.1.1.2 Sampling (Pool)

Sampling is a process of downsampling, aiming to reduce image size and computation while keeping necessary information. Two types of sampling have been used in the CNN execution: maximum pooling and average pooling. During the sampling, the number of the channel remains unchanged. Taking max-pooling operation as an example, the feature map is usually divided into multiple large and small rectangular areas. Then, the maximum value in each sub-area is selected for output. For example, the expression of max-pooling 3x3 output **O** can be described as 2.2:

$$\begin{aligned} O[n][x][y] &= \max(I[k][Sx][Sy], I[k][Sx][Sy+1], I[k][Sx][Sy+2], I[k][Sx+1][Sy], \\ &I[k][Sx+1][Sy+1], I[k][Sx+1][Sy+2]I[k][Sx+2][Sy], \\ &I[k][Sx+2][Sy+1], I[k][Sx+2][Sy+2]), \\ &0 \leq n < C\_out, 0 \leq x < W\_out, 0 \leq y < H\_out \end{aligned} \tag{2.2}$$

#### 2.1.1.3 Activation

The activation function constructs a key part of CNN, which provides the nonlinear factor in the neural network to solve the linear indivisible problems in CNN. There are some common-used activation functions:

• Sigmoid: Sigmoid is a widely used funtion. The value range of output is [0,1], since it is often used as an output function, and the output value is expressed as a probability. The expression is:

$$f(u) = \frac{1}{1 + e^{-u}} \tag{2.3}$$

• ReLU: ReLU is the abbreviation of Rectified Linear Unit, and its characteristics are close to biological nerve, its expression is:

$$f(u) = max(0, u) \tag{2.4}$$

• tanh: Tanh is a traditional activation function, which is obtained by dividing the hyperbolic sine sinh and the hyperbolic cosine cosh. It can also be regarded as a variant of the Sigmoid function, with a value range of [-1,1] between. Its expression is:

$$f(u) = \tanh(u) \tag{2.5}$$

#### 2.1.1.4 Fully-connected (FC)

The fully connected are stacked behind the convolutional layer to finally extract the results. All the inputs from the previous layers are connected to every activation unit of the next layer. A fully connected layer applies a filter to the input feature map like a convolutional layer, while the kernel size is the same as the input feature map. Therefore, let  $W_{in} = K$ ,  $W_{out} = 1$ , and S = 1 in the equation 2.6, we can obtain the equation of the fully-connected:

$$O[n] = B[n] + \sum_{k=0}^{C_{-in-1}} \sum_{i=0}^{W_{-in-1}} \sum_{j=0}^{H_{-in-1}} I[k][i][j] \times W[n][k][i][j]$$

$$0 \le n < C \text{ out}$$

(2.6)

#### 2.1.2 Inference and training

CNN requires training and inference. First, a set of data is collected and labeled as a training data set to train CNN in the context of supervised training. Then, when

the training gradually converges with the expected results, we can use the data set for inference to obtain the accuracy.

#### **2.1.2.1** Training

Training is a process of learning to find weights in convolution and fully connected layers, which can minimize differences between output predictions and given ground-truth labels on a training dataset [159] through several epochs. To train a neural network, we should define some hyperparameters to control the training process, such as learning rate, mini-batch size, number of epochs, momentum.

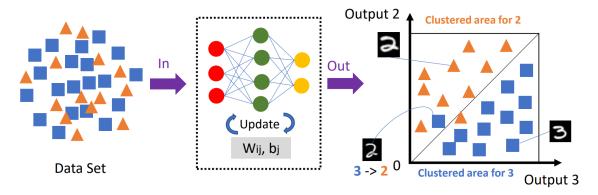

Figure 2.3 - Example of the training process

In training, most of the training of the neural network is based on the backpropagation algorithm. Then, the weight and bias are updated by a gradient descent optimization algorithm.

The backpropagation consists of the following steps:

- Forward the network model to get the activation of each layer including the output layer;

- Calculate the derivative of the activation function and residual of each layer;

- Calculate the partial derivatives of the cost function concerning the weights W and the biases b respectively;

- Update the W and b.

If the dataset of the network is m, then the cost function J(W,b) of an l-layer network can be expressed as:

$$J(W,b) = \left[\frac{1}{m} \sum_{i=1}^{m} J(W,b;x^{(i)},y^{(i)})\right] + \frac{\lambda}{2} \sum_{l=1}^{n_{l}-1} \sum_{j=1}^{S_{l}} \sum_{i=1}^{S_{l+1}} \left(W_{ji}^{(l)}\right)^{2}$$

$$= \left[\frac{1}{m} \sum_{i=1}^{m} \left(\frac{1}{2} \left\|h_{W,b}(x^{(i)}) - y^{(i)}\right\|^{2}\right)\right] + \frac{\lambda}{2} \sum_{l=1}^{n_{l}-1} \sum_{i=1}^{S_{l}} \sum_{i=1}^{S_{l+1}} \left(W_{ji}^{(l)}\right)^{2}$$

$$(2.7)$$

$s_l$  represents the number of activation of the l-th layer. Likewise,  $n_l$  represents the number of layers of the network model.

The gradient descent method can be used in training to continuously adjust the weight W and the bias b according to a particular learning rate  $\alpha$ , and obtain the optimal solution of W and b.

$$W_{ji}^{(l)} = W_{ji}^{(l)} - \alpha \frac{\partial}{\partial W_{ji}^{(l)}} J(W, b)$$

$$b_i^{(l)} = b_i^{(l)} - \alpha \frac{\partial}{\partial b_i^{(l)}} J(W, b)$$

(2.8)

The partial derivatives of the cost function for w and b can be expressed as:

$$\frac{\partial}{\partial W_{ji}^{(l)}} J(W, b) = \left[ \frac{1}{m} \sum_{i=1}^{m} \frac{\partial}{\partial W_{ji}^{(l)}} J(W, b; x^{(i)}, y^{(i)}) \right] + \lambda \left( W_{ji}^{(l)} \right)

\frac{\partial}{\partial b_{i}^{(l)}} J(W, b) = \frac{1}{m} \sum_{i=1}^{m} \frac{\partial}{\partial b_{i}^{(l)}} J(W, b; x^{(i)}, y^{(i)})$$

(2.9)

The residual  $\delta_i^{(l)}$  can be expressed as:

$$\delta_i^{(l)} = \sum_{i=1}^{S_{l+1}} \delta_j^{(l+1)} \cdot W_{ij}^{(l)} \cdot f'(z_i^{(l)})$$

(2.10)

Therefore, the derivation formula of the cost function expressed by the residual error concerning the parameters W and b can be described as:

$$\frac{\partial}{\partial W_{ji}^{(l)}} J(W, b) = \frac{\partial J(W, b)}{\partial z_i^{(l+1)}} \cdot \frac{\partial z_i^{(l+1)}}{\partial W_{ji}^{(l)}} = \delta_i^{(l+1)} \cdot a_j^{(l)}$$

$$\frac{\partial}{\partial b_i^{(l)}} J(W, b) = \frac{\partial J(W, b)}{\partial z_i^{(l+1)}} \cdot \frac{\partial z_i^{(l+1)}}{\partial b_i^{(l)}} = \delta_i^{(l+1)}$$

(2.11)

#### 2.1.2.2 Inference

The inference applies a pre-trained model from a training phase to infer the results of the dataset. When a dataset is sent to the pre-trained network, it outputs a prediction based on the predictive accuracy of the neural network. Differs from the training phase, inference will not update the weights and biases of layers according to the predicted result if the results have errors.

#### 2.2 FIELD PROGRAMMABLE DEVICES

Field Programmable Gate Array (FPGA) is a programmable logic array that can be reconfigured after production. The basic structure of FPGA includes programmable input and output units (IOBs), configurable logic blocks (CLBs), digital clock management modules, embedded block RAM, wiring resources, embedded dedicated hard cores, etc. Moreover, it consists of several Digital Signal Processor (DSP) which can process the special high-precision operation under maximum 500MHz[82]. FPGA logics are realized by loading programming data into the internal static storage unit. The value stored in the storage unit determines the function of the logic unit. It also determines the connection between the modules and I/O.

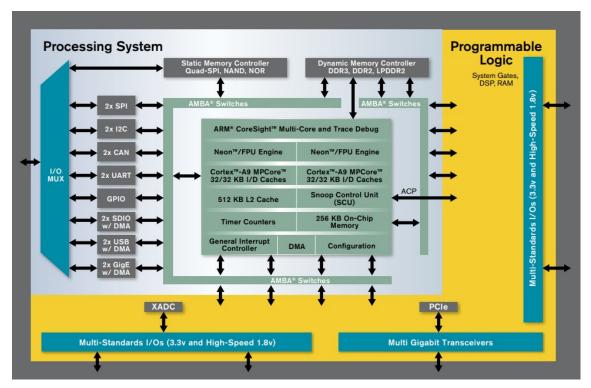

Later, a system-on-chip (SoC) FPGA with an integrated processor appeared, such as the Xilinx Zynq-7000 series [155]. The processing system (PS) side is usually dual-core, and the runtime control logic is executed on the Linux operating system or bare system. On the other hand, the programmable logic (PL) side has traditional FPGA resources such as DSP and LUT and can be configured for various applications. The communication between PS and PL is realized through different intellectual property (IP) and AMBA AXI.

#### 2.3 Design flow of application of FPGA

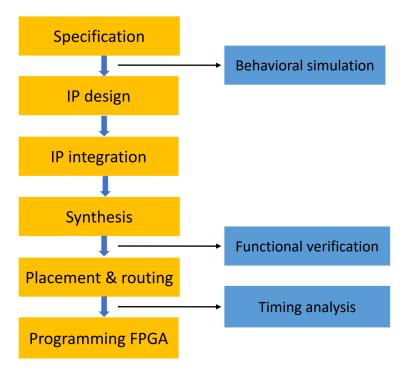

The FPGA design flow can be described as the following figure 2.5, from specifying the design with constraints to finally implementing the design on FPGA.

#### 2.3.1 System specification

"System specification" describes the specifications and constraints of the system, such as FPGA type, system function, required clock frequency, etc. In this step, the hardware designer determines the software and hardware parts for Intellectual Property (IP) design and the interconnection standards between the IP and the processor. At the same time, hardware designers can determine the necessary hardware resources to respond to previously defined constraints. You can also decide whether you need to design a verification process to ensure that the system is working correctly.

Figure 2.4 - Xilinx Zynq-7000 block diagram[155].

#### 2.3.2 IP design

"IP design" is to realize the functions of IP. Once the characteristics of IP have been identified in the step "System specification", the hardware designer can choose several methods to describe the design.

The traditional method uses hardware description language (HDL) such as VHDL and Verilog to generate register transfer level (RTL), which requires solid hardware acknowledges. The high-level synthesis (HLS) approach has come into being, allowing the bitstream or the RTL code from the software language, such as C++/C. This approach is more productive with less implementation time but at the cost of efficiency. For example, [107] proves that Key-value Store (KVS) implementation time in HSL has been reduced by 20% compared to HDL language flow.

It is also possible to use open source IPs or commercial IPs provided by the FPGA companies (e.g., Xilinx, Altera) or IP providers in this step.

#### 2.3.3 IP integration

"IP integration" is to interconnect all the IPs to achieve a complete system on the FPGA. It is possible to apply some data transfer protocols among the IPs. The most popular

Figure 2.5 - FPGA design flow.

standard is AMBA Advanced eXtensible Interface 4 (AXI4), which is supported by Xilinx [154] and Altera [15]. However, Altera also has its standard, Avalon [14]. In addition, it also exists several open-source standards, such as Wishbone [7]. These standards have several types of interconnections, which are summarised in the table 2.1. The type of the interconnection are following:

- Point-to-point type, usually used for the pipeline;

- Bus type, which allows one or more master devices to be connected to multiple masters to multiple slaves;

- Network on chip (NoC), which allows multiple IPs to be connected for parallel communication.

| Standard | Point to point | Bus                       | Others                    |

|----------|----------------|---------------------------|---------------------------|

| AMBA     | AXI streaming  | AXI MM, AXI lite, AHB,APB |                           |

| Avalon   | Avalon-ST      | Avalon-MM                 | Avalon conduit, Avalon-TC |

| Wishbone | Point to point | Shared bus, crossbar      |                           |

Table 2.1 - Standards and interconnections between IPs.

In our work, we use the standard AXI4 for the IP interacting with the processor of the FPGA. There exist three types of AXI4: AXI4-full, AXI4-lite, AXI4-stream.

The AXI4-full is a high-performance memory-mapped data and address interface that contributes to burst access to memory-mapped devices. The AXI4-lite is a subtype of AXI4, which has a more straightforward interface compared to AXI4-full. However, AXI-lite has not the burst access capability, which is suitable for a lightweight data transfer. The AXI4-Stream protocol is usually used for data-centric applications or the data flow paradigm, in which the address of data is not necessary for the design. Each AXI4-Stream acts as a single unidirectional channel for the handshake data stream [152]. Table 2.2 lists several features of the AXI standard.

Interface Features Data type Traditional memory mapped Data burst AXI4 address/data interface supported Traditional memory mapped Single data cycle AXI4-Lite address/data interface only AXI4-Stream Only data-interface Data-only burst

Table 2.2 - Difference between AXI4-full, AXI4-lite, AXI4-streaming.

#### 2.3.4 Synthesis

"Synthesis" is to convert the hardware architecture written in VHDL or Verilog into a netlist, which is a netlist representing electrical diagrams. This step can reveal some errors that were not detected during the functional simulation process, for example, timing closure issues that would lead to functional degradation in the system.

The synthesis can be carried out with the tools of the FPGA supplier or by third-party software. It is necessary to simulate the system after the synthesis. This simulation-based on the netlist is more precise than the functional simulation carried out before synthesis.

#### 2.3.5 Placement & routing

"Placement & routing" is to implement the architecture on a specific FPGA. During the implementation step, the netlist is attached to a particular FPGA. Next, the netlist components are placed on the internal structures of the FPGA, such as BRAMs, IOs, and registers. Then, these resources are routed while respecting the constraints of the FPGA. It is possible to add placement and timing constraints when performing this step. A timing analysis file is available and is generated. This file makes it possible to make a simulation integrating the propagation times. In addition, it makes it possible to analyze the causes of non-compliance with the design constraints.

#### 2.3.6 Programming FPGA

"Programing FPGA" is to download the bitstream generated in the design to the FPGA. Bitstream is a binary file that can configure FPGA. After obtaining the binary file, you can configure the FPGA again to change the design. You can also generate a binary file in the EEPROM so that the FPGA configuration information will not be lost after the power is turned off.

In this step, if the design has some bugs, you can use several debugging tools provided by FPGA manufacturers. For example, Xilinx offers an integrated logic analyzer (ILA), an oscilloscope that allows the observation of signals inside the FPGA. In addition, to debug the soft code of the CPU, Xilinx provides software called Xilinx SDK to verify the function of the CPU code. In addition, you can check the bus (AXI4) function to verify the data conversion between PS and PL. For example, Xilinx has AXI Verification IP (AXI-VIP), written in SystemVerilog, and uses Universal Verification Method (UVM) to implement software/hardware co-simulation.

#### 2.4 CHALLENGES OF CNNs on FPGAs

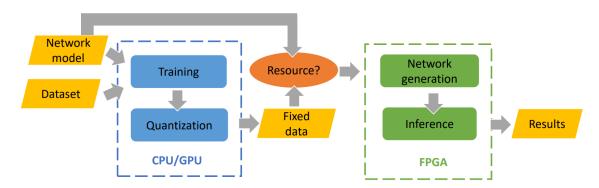

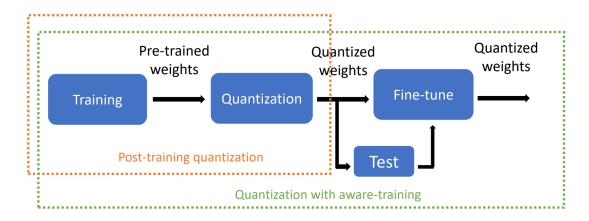

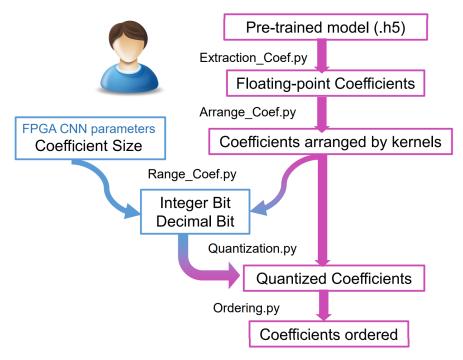

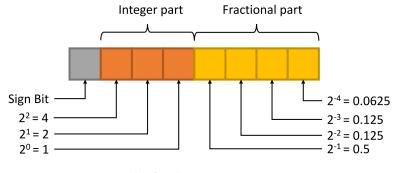

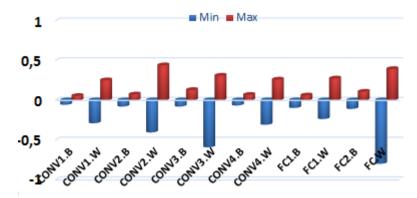

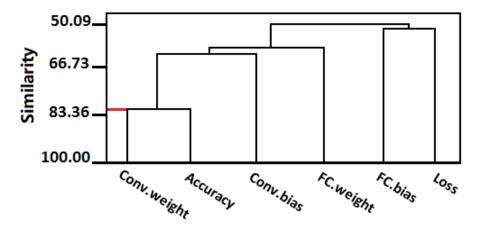

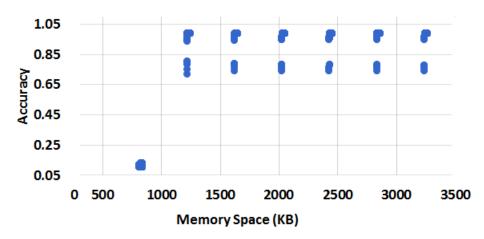

Figure 2.6 exhibits a general method of performing CNN training and inference phases. Under the condition of resources and bandwidth, the research on accelerating CNN inference on the FPGA has attracted more and more attention. Due to the complexity of the backpropagation algorithm and the need for high-precision data, the training phase is usually completed in a CPU- or GPU-based software platform. First, the network model with configurations is used on software and hardware platforms. Then, the training phase is based on the collected floating-pointed training dataset and test dataset. In several training iterations, the network will output the pre-training floating-pointed weights and biases. Finally, these floating-pointed data will be quantized into the fixed point format on the CPU- or GPU-based platform for the inference stage.

In the inference stage, as shown in figure 2.6, the FPGA platform has a network generation. Network generation completes several calculations in CNN or the entire CNN. The generator obtains the network configuration from the training phase, reads the input data from the outside, and generates approximate output for the CNN. In the process of execution, the network generation may be used multiple times.

The increasing scale and the innovating structures of CNN's bring challenges to realize

Figure 2.6 - General method for the CNN.

the CNN implementations on the FPGA. For the power consumption, the high-speed data flow inside the system, such as the data flow between the storage and the network computation block occupies a part of power consumption. For the throughput performance, the hardware resources and memory bandwidth are the key elements that limit the performance of the FPGA-based acceleration module factors. Based on the structures of the CNNs, how to improve performance and efficiency in the FPGA-based accelerators, reducing resource and power consumption, are needs to be further explored.

The challenges can be expanded as follows:

- Resource and bandwidth limitations: The most advanced neural networks usually have a large number of deep layers of computational operations, such as AlexNet (8 layers, 724M MAC) [81], GoogleNet (22 layers, 1.6G MAC)) [60] and ResNet (layer 152, 11.3G MAC)[60], which may cause insufficient resources for CNN deployment on the FPGA. Besides, in traditional CNNs, the convolution layer takes up a large percentage of computation and the data transmission (for example, AlexNet and VGG-16 accounts for 90% of the total computation [58]), which increase the off-chip bandwidth demand from weight transfer for large CNNs.

- Network generality: CNN structure has different convolutional layers and kernel sizes. General hardware modules that can adapt to other network structures should be designed to promote the deployment of CNN on FPGAs. Moreover, frameworks that automatically accomplish the CNN structure generation and implementation process are also desired.

#### Chapter 3

## Accelerating CNNs from local to virtualized FPGA in the Cloud: A survey of trends

| Contents |        |                                                           |    |

|----------|--------|-----------------------------------------------------------|----|

| 3.1      | Introi | DUCTION                                                   | 22 |

| 3.2      | Васко  | ROUND                                                     | 26 |

|          | 3.2.1  | FPGA cloud                                                | 26 |

|          | 3.2.2  | FPGA virtualization                                       | 27 |

| 3.3      | CNN II | MPLEMENTATION TECHNIQUES                                  | 30 |

|          | 3.3.1  | Hardware architecture design                              | 30 |

|          | 3.3.2  | Network compression                                       | 31 |

|          | 3.3.3  | Optimization strategy                                     | 32 |

| 3.4      | Accel  | erating CNNs from local to virtualized FPGAs in the cloud | 33 |

|          | 3.4.1  | CNNs on local FPGA                                        | 33 |

|          | 3.4.2  | CNNs on local virtualized FPGA                            | 36 |

|          | 3.4.3  | CNNs on virtualized FPGA in the cloud                     | 38 |

|          | 3.4.4  | CNN deployment in commercial cloud                        | 40 |

| 3.5      | Trend  | s of CNN accelerators                                     | 40 |

| 3.6      | Discus | SSION                                                     | 45 |

|          | 3.6.1  | Unresolved challenges                                     | 45 |

|          | 3.6.2  | Industrial solution                                       | 46 |

|          | 3.6.3  | Roadblocks of FPGA Cloud                                  | 47 |

| 3.7      | Conci  | LUSION                                                    | 47 |

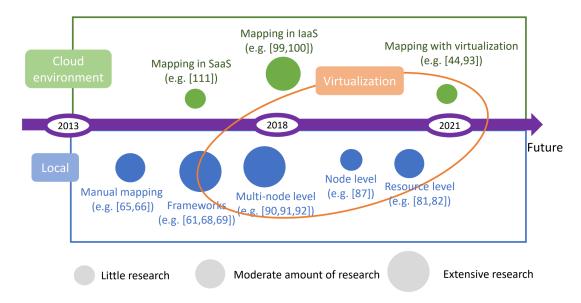

Field-programmable gate arrays (FPGAs) are widely used locally to speed up neural network algorithms (e.g., CNN) with high computational throughput and energy efficiency. Virtualizing FPGA and deploying FPGAs in the cloud are becoming increasingly attractive methods for network acceleration because they can enhance the computing ability to achieve on-demand acceleration across multiple users. In the past five years, researchers have extensively investigated various directions of FPGA-based CNN accelerators, such as algorithm optimization, architecture exploration, capacity improvement, resource sharing, and cloud construction. However, previous CNN accelerator surveys mainly focused on optimizing the CNN performance on a local FPGA, ignoring the trend of placing CNN accelerators in the cloud's FPGA.

In this chapter, we conducted an in-depth investigation of the technologies used in FPGA-based CNN accelerators, including but not limited to architectural design, optimization strategies, virtualization technologies, and cloud services. Additionally, we studied the evolution of CNN accelerators, e.g., from a single CNN to framework-generated CNNs, from physical to virtualized FPGAs, from local to the cloud, and from single-user to multi-tenant. We also identified significant obstacles for CNN acceleration in the cloud. This chapter enhances the current understanding of the evolution of FPGA-based CNN accelerators.

#### 3.1 Introduction

Neural networks have become a cutting-edge research topic owing to their excellent performance in image classification, detection, segmentation, and data prediction. Owing to the remarkable prediction capacity of datasets in a wide range of complex applications, researchers have proposed myriad networks, such as AlexNet [81], VGG16 [127], ResNet152 [61], Transformers [139], General Adversarial Networks (GANs) [47], and Variational Autoencoder (VAE) [78]. The success of CNNs has also attracted attention in the development of industrial platforms, such as Google Deepmind [106], Facebook AI [59], Amazon Alexa [89].

Traditionally, in academia and industry, graphics processing units (GPUs) are used to train CNNs, as they provide a high degree of parallelism to process these algorithms [130, 105]. However, the execution of CNNs on GPU-based platforms encounters energy/power and throughput bottlenecks. In 2016, a tensor processing unit (TPU) was announced by Google [74], which runs CNNs 15 to 30 times faster than contemporary GPUs using

similar technologies [73], and the energy efficiency is increased by a factor of 30–80. Despite its speedup and energy efficiency, the TPU has a high production cost, lacks reconfigurability, and cannot be adapted to the emergence of new network models with complex structures.

Field-programmable gate arrays (FPGAs) can achieve energy efficiency and high performance in the face of rapidly innovating CNN models and computational characteristics, as reported by Venieris et al [144]. FPGAs can achieve up to 20 tera multiply accumulates per second (TMACs), and the power consumption does not exceed 25 W, incurring a less than 10% overhead in the overall power consumption [4]. Moreover, FPGAs can provide a flexible hardware architecture with a fine granularity and massive pipeline level. Therefore, FPGAs have become an alternative method for accelerating CNNs.

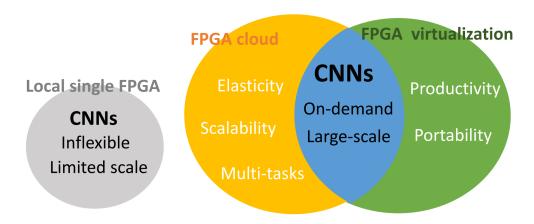

Early CNN accelerators (e.g., [183, 132, 117, 37]) are typically implemented on a single local FPGA fabric. As the number of learnable parameters and operations in CNNs increases, the resources of a single FPGA may be insufficient for the entire CNN deployment. The challenges of designing CNNs on a single local FPGA are described below.

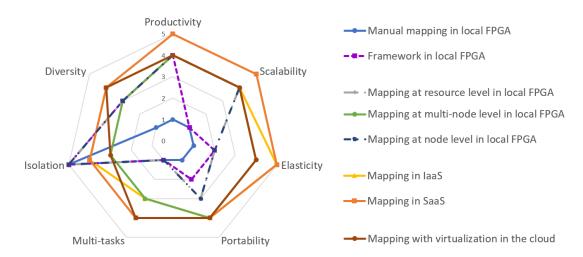

- Productivity: Owing to the complexity of CNN design, mapping a CNN onto an FPGA requires specific hardware expertise in hardware description language programming and performance optimization, which have long learning curves. According to the complexity of the CNN algorithm, deploying the CNN on the FPGA may be time-consuming and may increase the programming burden of designers. In recent years, productivity has improved owing to the emergence of compilation frameworks that automatically map CNNs onto the FPGA.

- Scalability: CNNs are computation- and data-intensive applications that require enormous computational resources. For example, VGG-16 has up to 39 billion operations and more than 500 million parameters for 224 × 224 image classification [83]. In deeper CNNs, the resource requirements may exceed the available resources in a single FPGA, limiting the scalability of the CNN architecture. Even if technologies and strategies are adopted to optimize the CNN architecture, when a large-scale CNN is deployed in a single local FPGA, the resource bottleneck can easily be reached.

- Elasticity: The solution of deploying CNN accelerators on local FPGAs lacks re-

Figure 3.1 - Characteristics of deploying FPGAs in the cloud and FPGA virtualization for CNN deployment.

source elasticity because it assumes that CNN resource allocation must be fixed throughout the deployment lifecycle. Because different CNN algorithms require different computing resources, memory bandwidths, and storage resources [175], these solutions cannot flexibly provide and deprovision resources at runtime and hence fail to match different workloads of the CNN.

- Portability: The deployment of most CNN accelerators directly depends on the characteristics of the FPGA platform and is therefore restricted to a specific FPGA vendor. Owing to the lack of an abstraction layer that isolates CNN accelerators from specific FPGA platforms, these accelerators may face portability issues of CNN structures. They cannot adapt quickly to the current changing CNN algorithms.

- Multi-tasks: Generally, the execution mode of a CNN on a local FPGA is limited to a single user executing a single CNN within a given time. It remains difficult for a single local FPGA to support multiple users by executing execute multiple CNNs in parallel and satisfy each user's time, cost, and quality of service (QoS) requirements. Some frameworks (for example, [33]) successfully solve the problem of multiple CNN scheduling but can only execute CNNs sequentially in the form of time slices in a single-task environment.

Deploying FPGAs in the cloud and/or virtualizing FPGAs can resolve the aforementioned challenges, as shown in Figure 3.1. The cloud paradigm enhances the computing capability of FPGAs with high throughput and low latency. It enables the sharing of single or multiple FPGA resources across multiple users, thereby efficiently scaling and accelerating on-demand CNNs. Virtualizing FPGAs abstracts low-level physical resources and

hides hardware design and compilation flow from the software designers' view, providing a high-level application-dependent architecture. Owing to FPGA virtualization, software designers can deploy CNN accelerators according to different requirements (e.g., throughput, execution time, and accuracy) without relying on a specific FPGA platform. The collaboration between FPGA virtualization and the FPGA cloud can satisfy the resource requirement, thereby taking advantage of the "unlimited" cloud capability to flexibly scale CNN accelerators.

While exploring techniques to accelerate CNNs on local physical FPGAs, researchers have also attempted to adopt FPGA virtualization and the FPGA cloud to facilitate the implementation of multiple CNNs at a large scale and achieve flexible deployment in a multi-user environment. Although the FPGA cloud and virtualization have brought breakthroughs to the deployment of CNNs, previous surveys (e.g., [101, 53, 22, 87, 23, 103, 36]) have mainly focused on CNN optimization and the design of local FPGAs (e.g., architecture design, simplification, optimization strategies). These surveys ignore the trend of CNN implementation on the timeline, that is, from local to virtual FPGA in the cloud. Moreover, no in-depth analysis or comparison of the challenges faced by the CNN accelerators at different stages of deployment was conducted. Relying on previous surveys, we aim to

- Provide an overview of the main techniques of FPGA-based CNN accelerators. These techniques were initially proposed to optimize the performance of CNN accelerators in a local FPGA, but they can also be applied to the FPGA cloud environment.

- Present the evolution of CNN accelerator deployment from local to virtualized FPGAs through an in-depth introduction of virtualization techniques and the FPGA cloud.

- Perform an in-depth analysis and comparison of the challenges faced by the CNN accelerators at each stage.

The chapter is organised as follows: Section 3.2 provides an FPGA cloud definition and a general overview of FPGA virtualization. Section 3.3 discusses the crucial approaches for accelerating CNNs on the FPGA, which is also applicable to the FPGA cloud. Section 3.4 describes the use of virtualization technology in local CNNs and cloud-based CNNs. Section 3.5 highlights the trends and evolution of the FPGA-based CNN and compares

the characteristics of these accelerators. Section 3.6 discusses the unresolved challenges of accelerating CNNs in the FPGA cloud and presents other directions for CNN acceleration. Section 3.7 gives the conclusion of the survey.

#### 3.2 BACKGROUND

This section presents an overview of the FPGA cloud and the available services in the cloud and introduces the FPGA virtualization technology from the viewpoints of the abstraction level and system architecture.

#### 3.2.1 FPGA cloud

Deploying FPGAs in the cloud involves leasing a bundle of specific software tools, platforms, or FPGA resources remotely in a cost-effective manner. Such an FPGA-enabled cloud maintains the advantages of FPGAs (e.g., low power consumption and programmability) and establishes scalability, elasticity, and multi-tenancy.

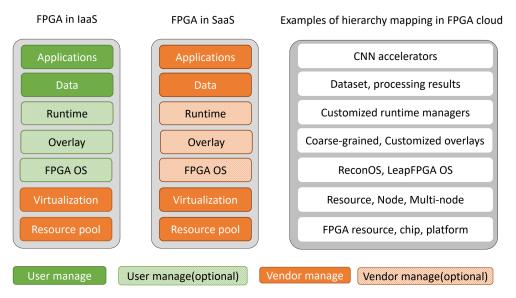

Provisioning FPGA resources is similar to provisioning traditional central processing unit (CPU)- and GPU-based clouds. Regarding the service categories in traditional cloud computing, FPGA cloud providers offer FPGAs as infrastructure as a service (IaaS) or software as a service (SaaS) [116]. Figure 3.2 presents an example of hierarchical mapping in the FPGA cloud. There is no standard definition or classification for FPGA clouds, and the hierarchical mapping may change over time.

#### 3.2.1.1 FPGA in IaaS

The FPGA in IaaS provides access to the FPGA computing resource pool and memory storage in the cloud. This paradigm divides the FPGA into multiple independent virtual instances and supports high-bandwidth communication to collaborate between each resource instance. Per-FPGA or multiple-FPGA granularity can be supported in the IaaS for application deployment. Cloud users must manually map their applications to resources if their applications are deployed across multiple FPGAs.

As a commercial example, the Amazon F1 instance offers a collection of eight FPGA devices with a high bandwidth. Enabling FPGA in IaaS has also attracted attention in the academic field. Byma et al. [26] abstracted FPGAs into virtual regions and managed resources across multiple FPGAs through OpenStack. Asiatici et al. [19] provided a

Figure 3.2 - IaaS and SaaS FPGA cloud. "Vendor manage (optional)" and "User manage (optional)" indicate that this hierarchy does not always exist in the FPGA cloud, and it is customised by each FPGA cloud vendor or user.

runtime management framework to map FPGA resources for different applications with limited overhead.

#### 3.2.1.2 FPGA in SaaS

The FPGA in SaaS offers acceleration services for cloud users to execute applications and process data. Technical processes have been hidden in the cloud background, and cloud users do not need to be responsible for the hardware design flow and FPGA resource management. For example, Microsoft released the Catapult project [108], which puts Altera Stratix vFPGA per CPU in the cloud to accelerate the Bing web search engine, with a 95% improvement throughout. Moreover, Microsoft released the BrainWare project, where FPGAs are used to accelerate state-of-the-art CNNs in major services such as Bing and Azure [30].

#### 3.2.2 FPGA virtualization

The objectives of FPGA virtualization are to 1) provide a virtual abstraction of resources and underly the low-level hardware design from users; 2) support FPGA sharing in the time and space domains to serve multiple tasks; and 3) facilitate the hardware design process and accelerate the program compilation [67, 138, 145, 128]. We review FPGA virtualization according to the abstraction level [137] and system architecture [111]. The definition of FPGA virtualization has changed over time in different scenarios.

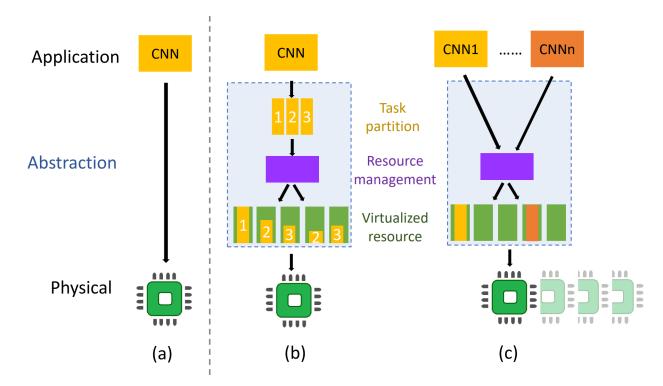

#### 3.2.2.1 Abstraction level

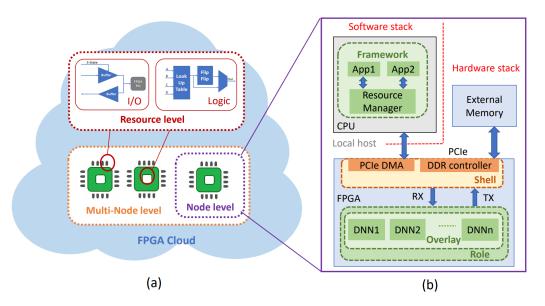

According to the scale of resource computing, FPGA virtualization can be divided into three abstraction levels: resource, node, and multi-node levels.

- Resource level: The resource level contains reconfigurable resources (e.g., logic) and non-reconfigurable resources (e.g., Input/Output blocks). Several uniform architectures, such as coarse-grained overlays, have been proposed to support the portability of this level between different types of FPGAs [79, 148].

- Node level: The node level considers a single FPGA as a node. Resource allocation and scheduling are concerned with a single FPGA at this level. Currently, time-division multiplexing (TDM) and space-division multiplexing (SDM) are the two principal methods for sharing a single FPGA resource [85, 168].

- Multi-node level: The multi-node level is designed to assign resources in multiple FPGAs to multiple applications or multiple users. However, mainstream compilation tools only support application deployments on a single FPGA [157]. Therefore, application mapping across FPGAs requires specific frameworks to solve hardware problems, such as intercommunication, resource partitioning, and traversing the physical boundary.

#### 3.2.2.2 System architecture

The system architecture refers to a structural view at the abstraction level. It usually covers the hardware, software stack, and overlay [129] but may be different at each level of abstraction. Here, we introduce the system architecture in a node-level abstract form, as shown in Figure 3.3, which can also be applied to other levels of abstraction.

- Hardware stack: The hardware stack can vary in the host interface, shell, and role.

- Host interfaces: 1) on-chip host inside the FPGA, which can be a soft core formed by programmable logic (PL) or a hard core in the processing system (PS) of a system-on-a-chip (SoC) FPGA; 2) local host, local CPU host, connected via high-bandwidth links (e.g., PCIe); 3) remote host placed remotely via the network.

- Shell: The shell is a static region, usually comprising a system memory controller (e.g., DRAM adapter), interface controller (e.g., DMA controller), and network

**Figure 3.3** - Overall architecture of the FPGA-based CNN accelerators in the IaaS cloud. (a) Different levels of abstraction in the FPGA virtualization technique. (b) Example of the system architecture in node-level virtualization.

interface controller (e.g., Ethernet core). For instance, the shell in [91] includes the user PCIe, management PCIe, card management system, and DDR access channel.

- Role: The role is a dynamic region in the FPGA, which can be regarded as a reserved region for deploying CNNs in our context. It runs independently of the shell and can be reconfigured every time for each application to satisfy user requirements.

- Software stack: The software stack runs on a host, provides users with an application programming interface, and enables the communication between the host and the FPGA. [111] introduces three types of software stacks: 1) Operating systems (e.g., LeapFPGA OS [38], Recon OS [11]), which are conceived to support multiple threads for runtime resource management. 2) The host application, which is written in OpenCL and C++, provides simultaneous access to a shared FPGA for multiple users. 3) Software frameworks (e.g., OpenStack), which can be used to share resources across multiple users and distribute several partial reconfigurations to one FPGA.

- Overlay: The overlay provides an intermediate layer between the hardware stack and the software stack to achieve program portability. It is considered a virtual reconfigurable architecture on top of a physical FPGA. Fine-grained granularity and coarse-grained granularity in overlays are used in various applications [28, 86].

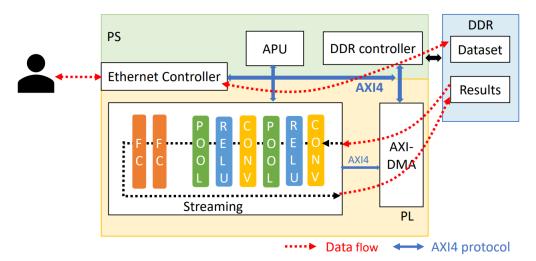

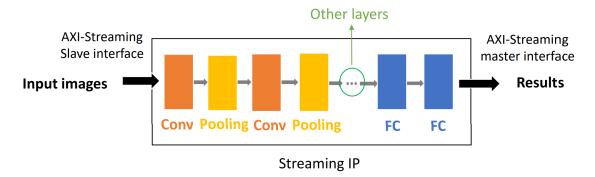

Figure 3.4 - Example of accelerating CNNs using the streaming architecture.

#### 3.3 CNN implementation techniques

To enhance the performance of CNNs on the FPGA locally and in the cloud, several techniques have been extensively studied. This section presents implementation techniques that have been recently investigated.

#### 3.3.1 Hardware architecture design

The widely used hardware architecture are streaming and single computation engine architectures.

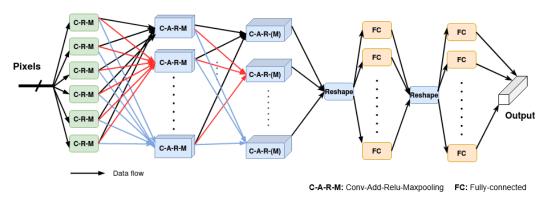

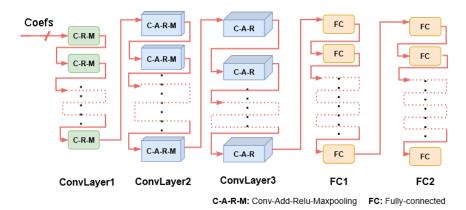

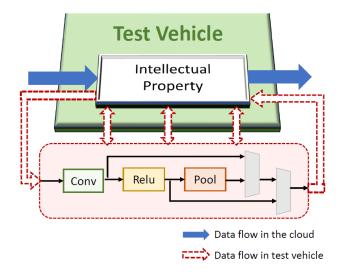

- Streaming architecture: The streaming architecture (Figure 3.4) implements an entire CNN on the side of the Programmable logic (PL) of the FPGA from the first convolutional layer to the final fully connected layer. On the PL side, it deploys a chain of sequential CNN intellectual property (IP) to process the dataset in the pipeline mode. The intermediate results (CNN feature maps) are stored on the chip on the PL side. This architecture enables an efficient data stream without frequent data exchange with external memory, significantly reducing the latency and obtaining throughput at a high frequency. A specific CNN model using a streaming architecture must be defined before generating the bitstream. Whenever the CNN model changes, architecture re-compilation and bitstream regeneration are inevitable. According to the selected CNN algorithm, the re-compilation of this architecture may be time- and resource-consuming.

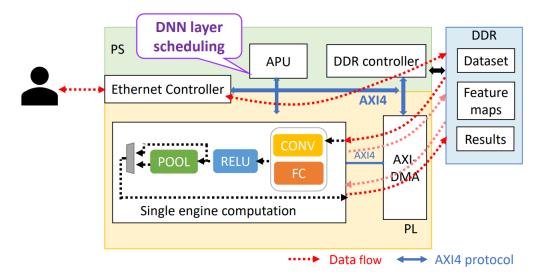

- Single Computation Engine: Single computation engine (Figure 3.5) implements a

Figure 3.5 - Example of accelerating CNNs using the single computation engine accelerator architecture.

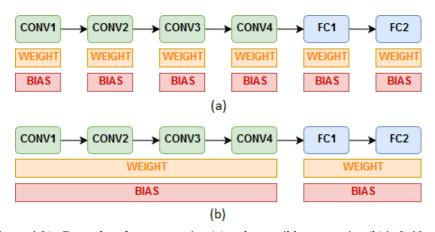

part or a layer of the CNN on the PL side. It is a universal fixed template, usually in the representation of a systolic array or multiple processing elements that can be configured as CNN layers of different scales [143, 110]. The execution of the entire CNN is achieved sequentially by configuring this template in the program on the PS side. The intermediate results (CNN feature maps) are stored off the chip. The architecture significantly reduces resource usage and introduces possibilities to scale accelerators. It has been widely used in accelerators to enrich CNN diversity. However, because the CNN blocks are executed sequentially on the FPGA, the execution time is extended significantly. Each time the CNN architectures changes, it is necessary to reload a complete bitstream to realize the novel CNN deployment on the FPGA.

Table 3.1 presents the major features of streaming and single computing engine architectures according to their performance (e.g., flexibility, reconfiguration, resource consumption).

#### 3.3.2 Network compression

The increasing amounts of learnable parameters and arithmetic operations of CNNs lead to a computational burden and additional resource consumption of hardware devices. Network compression makes CNNs more compact when the data width is limited, assisting in striking a balance between resource usage and accuracy. Thus far, quantization, pruning, and in-parallel pruning quantization have been successfully employed for

|                        | Streaming         | Single computation       |

|------------------------|-------------------|--------------------------|

| Network implementation | Entire network    | Function unit            |

| Structure              | Pipeline          | Recurrent                |

| Optimization mode      | Layer-independent | One-optimization-fit-all |

| Recompilation time     | Long              | Short                    |

| Dana Garantia          | Bitstream-level   | Processor control        |

| Reconfiguration        | reconfiguration   | configuration            |

| Flexibility            | Low               | High                     |

| Resource usage         | High              | Low                      |

| Speedup                | Fast              | Low                      |

|                        |                   |                          |

**Table 3.1** - Comparison of streaming and single computation architectures for CNN acceleration.

#### network compression.

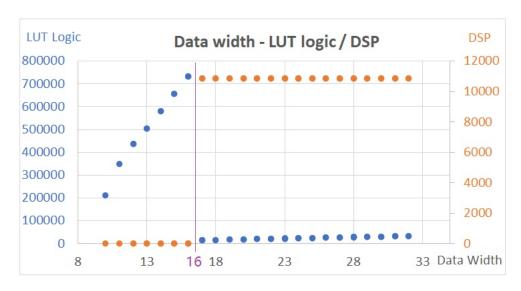

- Quantization: Network quantization converts floating-point data to fixed-point data with a selectable data width. Quantization includes uniform quantization with the same width for all network layers or dynamic quantization of each layer based on the layer characteristics. Researchers have widely adopted 16-bit fixed-point quantization (for example, [50, 150]), and 4- and 8-bit uniform quantization [56, 90] have already achieved good accuracy. Therefore, uniform quantization of a small width is promising owing to its ease of implementation on FPGA while maintaining accuracy.

- Pruning: Network pruning removes nonsignificant neurons to avoid overfitting. This is an efficient method, particularly in embedded systems, for reducing the network size and saving computing resources to fit the network to the memory size [102]. In [176], the authors compressed a trained CNN model and performed reverse pruning and peak pruning with fewer weights. Compared with the GPU, the compressed AlexNet on FPGA achieved 182.3× and 1.1× improvements in latency and throughput, respectively.

# 3.3.3 Optimization strategy

The scale of complex CNN structures introduces resource challenges. Moreover, the data (e.g., weights) stored in the external memory require enormous energy and latency. Because CNNs are composed of massive repeated loop operations, unrolling and tiling can be used to weaken off-chip communication and deal with parallel computation problems. A more detailed optimization was presented in [101].

• Loop unrolling: Unrolling executes a network or multiple layers in parallel—particularly

convolutional layers. The network can be fully expanded to achieve massively parallel processing or apply appropriate unrolling factors (iterations in the loop) across different layers for partial unrolling in the for-loop to optimize the datapath and maximise the throughput [52, 96]. Ma et al. [94] adopted four types of loop unrolling in kernel maps and feature maps to determine the parallelism scheme and maximise data reuse. In an experiment involving VGG-16 on an Arria 10 FPGA, a throughput of 645.25 GOPS was achieved.

• Loop tiling: Constrained by limited on-chip memories, the data to be processed are tiled into multiple tiles and stored in on-chip buffers. Selecting a suitable tiling size factor can determine the trade-off between resources and the required external memory bandwidth. For example, Yu et al. [93] designed an auto-compilation process based on RTL, which uses intra-block and inter-block strategies to divide the layer execution into multiple sequential tiles. The process designed in [146] supports both unrolling and tiling of input and output feature maps on binarised networks. A 2× area efficiency improvement was achieved compared with existing binarised networks.

#### 3.4 Accelerating CNNs from local to virtualized FPGAs in the cloud

The work of accelerating CNNs on FPGAs in our surveys covers local to the cloud and integrates the virtualization technique. The metrics used to evaluate these methods usually include throughput, power, and accuracy. Additionally, the adoption of virtualization techniques introduces additional characteristics such as portability and productivity, and in the cloud environment, QoS and isolation are regarded as new characteristics.

# 3.4.1 CNNs on local FPGA

Early studies (e.g., [84, 10, 35]) were dedicated to manually mapping a CNN model to a local FPGA with a streaming architecture. These studies take full advantage of CNNs parallelism and apply layer-independent optimization strategies to fit the entire network into the FPGA.

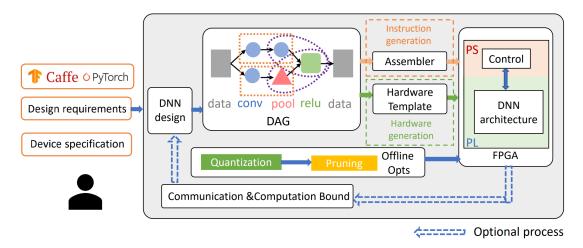

Benefiting from the well-defined structure of modern CNNs, which contain similar layers with repetitive operations, researchers have proposed frameworks with a single-engine computation structure [96, 174, 50, 123, 123, 158, 65], as shown in Figure 3.6. These frameworks take advantage of both software programmability and flexible hardware

Figure 3.6 - Generic frameworks for CNN accelerators.

Figure 3.7 - Generic compiler-inspired frameworks for CNN accelerators.

structures, making CNN implementation more diversified and achieving high performance with reduced resource consumption. More frameworks that automatically map single CNNs to local FPGAs were presented in [143]. Another new type of framework is a toolchain that includes a compiler [52, 156, 9]. The compiler is a CNN architecture-aware tool that can map a wide range of CNN applications to the instruction set architecture (ISA) and control signals [52]. Figure 3.7 presents an example of a compiler-inspired toolchain. Wang et al. [156] proposed a compiler that transforms a CNN deployment into a graph-level problem. The compiler first takes the software description as input and then transforms the description into directed acyclic graphs of computational operations. The networks generated by the compiler on Xilinx ZU9 reach throughputs of 2.82 TOPs/s (VGG), 1.38 TOPs/s (ResNet50), and 1.41 TOPs/s (GoogleNet).

More works are presented in Table 3.2.

Table 3.2 - Several examples of manual mapping and frameworks on the local FPGA.

|               | Works | Year   | Models         | Device                        | Data<br>format | Architecture                    | Strategy                                        | Perform<br>(GOPs)    |                    |       |

|---------------|-------|--------|----------------|-------------------------------|----------------|---------------------------------|-------------------------------------------------|----------------------|--------------------|-------|

| _             | [171] | 2015   | Costum<br>CNN  | Xilinx Virtex<br>vc707        | 32-bit<br>FP*  | Single<br>engine                | Unrolling                                       | 61.62                |                    |       |

|               | [54]  | 2015   | CIFAR10        | Xilinx<br>Kintex 325 T        | 16-bit         | Single<br>engine                | Quantization                                    | 260                  |                    |       |

| Man- –<br>ual | [110] | 2016   | VGG-16         | Xilinx Zynq<br>XC7Z045        | 16-bit         | Single<br>engine                | Unrolling,tilling                               | 137.3                |                    |       |

|               | [112] | 2016   | AlexNet        | Xilinx vc707                  | 32-bit<br>FP*  | Single<br>engine                | Unrolling,tilling                               | 75.16                |                    |       |

| _             | [84]  | 2016   | AlexNet        | xilinx vc709                  | 16-bit         | Streaming                       | Quantizaton,<br>ping-pong<br>buffer,batching    | 565.94               |                    |       |

|               | [179] | 2017   | LRCN           | Xilinx vc710                  | 16-bit         | Single<br>engine                | Pruning,<br>quantization,<br>unrolling, tilling | 75.5                 |                    |       |

|               |       |        | VGG16          | Xilinx                        |                |                                 |                                                 | 84.3                 |                    |       |

|               | [52]  | 2017   | YOLO           | Zynq                          | 8-bit          | Single engin                    | Per-layer quantization                          | 62.9                 |                    |       |

| _             |       |        | LeNet-5        | xc7z020                       |                |                                 |                                                 | 185.81               |                    |       |

|               |       | -      | MPCNN          | IPCNN Xilinx                  |                | _                               | 100.23                                          |                      |                    |       |

|               | [140] | 2016   | CNP            | Zynq                          | 32-bit FP*     | Streaming                       | Pipeline                                        | 150.91               |                    |       |

| _             |       | -      | CFF            | xc7z02                        |                |                                 | _                                               | 159.22               |                    |       |

|               |       |        | BNN-SFC        |                               |                |                                 |                                                 | 8265                 |                    |       |

|               | [136] | 2017   | BNN-LFC        | Xilinx                        | 1-bit          | Cturania                        | Pipeline, binarized                             | 908                  |                    |       |

|               |       | 2017_  |                | BNN-CNV ZC706 1-bit           | Streaming      | network –                       | 246                                             |                      |                    |       |

| -             |       | 2017 _ | VGG-19         | 19 Altera                     | 16-bit         |                                 |                                                 | 364.36               |                    |       |

|               | [50]  |        | LSTM-LM        |                               |                | Single engine Tilling, batching |                                                 | 315.85               |                    |       |

| Frame-        | [50]  |        | REsNet-<br>152 | SGSMD5                        | 16-DIT         | Single engine                   | Tilling, batching _                             | 226.47               |                    |       |

| work -        |       |        | 2017           |                               | AlexNet        |                                 |                                                 |                      |                    | 120.3 |

|               | [46]  | [46]   |                | GoogLeNet                     | Xilinx         | 16-bit                          | Single engine                                   | Quantization, loop — | 116                |       |

|               | [40]  | 2017   | ResNet-50      | Zynq<br>XC7Z045               | 10-011         | Single engine                   | e removal, <u> </u>                             | 122.3                |                    |       |

| _             | [174] | [174]  | [174]          | 2019                          | AlexNet        | Xilinx<br>UltraScale<br>KU060   | 1.6 h.;4                                        | Cin alo an ainl      | Manallina ninalina | 163   |

|               | [1/4] | 2018 - | VGG16          | Xilinx Virtex<br>vc709        | 16-bit         | Single engine                   | Unrolling, pipeline —                           | 354                  |                    |       |

|               |       |        | . 5310         | Xilinx<br>UltraScale<br>KU060 |                |                                 | _                                               | 266                  |                    |       |

| _             |       |        | AlexNet        | Altera                        |                |                                 |                                                 | 114.5                |                    |       |

|               | [96]  | 2018   | NiN            | Stratix V                     | 8-bit          | Single engine Unrolling         |                                                 | 117.3                |                    |       |

| _             |       |        | VGG            | GXA7                          |                |                                 |                                                 | 334                  |                    |       |

|               | [156] | 2019   | ResNet50       | Xilinx ZU2                    | 8-bit          | Streaming (                     | –<br>_Quantization, tilling                     | 228.7                |                    |       |

|               | [100] |        | GoogLeNet      |                               | 0 011          | · · · · · · · · · · · · · · · · | 231.5                                           |                      |                    |       |

<sup>\*</sup> FP = Floating point format.

**Figure 3.8** - (a)CNN deployment without virtualization. (b) Example of FPGA virtualization at the node level for deploying one CNN on a local FPGA. (c) Example of FPGA virtualization at the node level for deploying several CNNs in the cloud environment.

#### 3.4.2 CNNs on local virtualized FPGA

FPGA virtualization bridges the gap between the hardware stack and the software stack with the abstraction layer, enhancing the productivity and portability of CNN applications. Virtualization also enables resource sharing among multiple FPGAs with flexible resource management to support a wide range of CNNs. Figure 3.8 shows an example of virtualization at the node level.

At the resource level of virtualization, Tong et al. [44] propose a coarse-grained overlay-based framework for quantising and accelerating a CNN with any data width on an FPGA. The coarse-grained array comprises a reconfigurable NoC, a scheduler, and network computation components and is configured as CNN models according to instructions generated by the compiler of the framework. Such an overlay is independent of FPGA features and can be flexibly adapted to FPGAs provided by different vendors. To satisfy the metrics in virtualization, e.g., reducing the time and complexity of CNN reconfiguration, this framework reconfigures the coarse-grained array from the rightmost column to the leftmost column. The results indicate that the inference of AlexNet and VGG-16 on Xilinx UltraScale+ VCU118 takes only 0.13 and 2.63 ms, respectively.

|               | Coarse-grained overlay         | Fine-grained overlay             |

|---------------|--------------------------------|----------------------------------|

| Logic level   | RT level                       | Gate level                       |

| Data width    | Up to 32bit                    | 1 bit                            |

| Example logic | CNN function unit (e.g., Conv) | Control instruction (e.g., Load) |

| Goals         | Opitimise CNN datapath switch  | Enable CNN variability           |

| Advantage     | Area-efficiency                | Higher flexibility               |

Table 3.3 - Comparison of coarse- and fine-grained overlays on FPGAs for CNN acceleration