## Energy-Quality-Time Fault Tolerant Task Mapping on Multicore Architectures

Minyu Cui

## ► To cite this version:

Minyu Cui. Energy-Quality-Time Fault Tolerant Task Mapping on Multicore Architectures. Hardware Architecture [cs.AR]. École normale supérieure de Rennes, 2022. English. NNT: 2022ENSR0031. tel-03765873

## HAL Id: tel-03765873 https://theses.hal.science/tel-03765873v1

Submitted on 31 Aug2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

L'ÉCOLE NORMALE SUPERIEURE RENNES Comue Université Bretagne Loire

ÉCOLE DOCTORALE N°601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

## Par Minyu CUI

## Energy Quality Time Fault Tolerant Task Mapping on Multicore Architectures

Thèse présentée et soutenue à Rennes , le 24/06/2022 Unité de recherche : IRISA (UMR 6074), Institut de Recherche en Informatique et Systèmes Aléatoires

### Rapporteurs avant soutenance :

| Christophe JEGO    | Professeur des Universit | és, Bordeaux INP                                                     |

|--------------------|--------------------------|----------------------------------------------------------------------|

| Smail NIAR         | Professeur des Universit | és, Université Polytechnique Hauts-de-France                         |

| Composition d      | u Jury :                 |                                                                      |

| Examinateurs :     | Daniel CHILLET           | Professeur des Universités, Université Rennes1                       |

|                    | Christophe JEGO          | Professeur des Universités, Bordeaux INP                             |

|                    | Smail NIAR               | Professeur des Universités, Université Polytechnique Hauts-de-France |

|                    | Claire PAGETTI           | Ingénieur de recherche HDR, ONERA                                    |

| Dir. de thèse :    | Emmanuel CASSEAU         | Professeur des Universités, Université de Rennes 1                   |

| Co-enc. de thèse : | Angeliki KRITIKAKOU      | Maître de Conférences, Université de Rennes 1                        |

## ACKNOWLEDGEMENT

During my PhD studies, I have met many people who affected me personally and scientifically. Their presence was essential and meaningful to support me to come here, I dedicate all my thanks to them.

I would firstly like to thank my supervisors Prof. Emmanuel Casseau and Prof. Angeliki Kritikakou, for the guidance, encouragement and advice during the past few years. This dissertation could not have been completed without their consistent help. I would also like to mention a special thank to Prof. Lei Mo for his guidance and advice in the discussion of research works.

Secondly, I would like to thank the members of the TARAN team in Inria Rennes for the interesting scientific discussions in reading group and relaxing coffee breaks.

Finally, I would like to thank all the people who love me and whom I love, those who accompany me on my life journey and give me their love, support and kindness.

# TABLE OF CONTENTS

| $\mathbf{Li}$ | st of | acronyms                                                           | 7  |

|---------------|-------|--------------------------------------------------------------------|----|

| $\mathbf{Li}$ | st of | figures                                                            | 11 |

| $\mathbf{Li}$ | st of | tables                                                             | 13 |

| In            | trod  | uction                                                             | 27 |

| 1             | Bac   | kground                                                            | 31 |

|               | 1.1   | Multicore Architecture                                             | 31 |

|               | 1.2   | Task Model                                                         | 32 |

|               | 1.3   | DVFS Schemes                                                       | 34 |

|               | 1.4   | Power and Energy Consumption Model                                 | 35 |

|               | 1.5   | Fault Tolerance and Reliability Model                              | 36 |

|               |       | 1.5.1 Fault Origin                                                 | 36 |

|               |       | 1.5.2 Reliability Model                                            | 37 |

|               |       | 1.5.3 Main Fault Tolerance Techniques                              | 38 |

|               | 1.6   | Real-Time Task mapping in Multicore Systems                        | 39 |

| <b>2</b>      | Ene   | rgy-Reliability-Time Multi-criteria Task Mapping Mechanisms in SoA | 41 |

|               | 2.1   | Task Mapping Targeting Energy Minimization                         | 41 |

|               |       | 2.1.1 Task Mapping Without Reliability Guarantee                   | 42 |

|               |       | 2.1.2 Task Mapping With Reliability Guarantee                      | 44 |

|               | 2.2   | Task Mapping Targeting Reliability Maximization                    | 48 |

|               |       | 2.2.1 Task Mapping Without Fault Tolerance                         | 49 |

|               |       | 2.2.2 Task Mapping With Fault Tolerance                            | 49 |

|               | 2.3   | Task Mapping Targeting Schedule-Length Minimization                | 50 |

|               |       | 2.3.1 Task Mapping Without Fault Tolerance                         | 50 |

|               |       | 2.3.2 Task Mapping With Fault Tolerance                            | 51 |

|               | 2.4   | Limitations of SoA Task Mapping Approaches                         | 52 |

| 3             | Ene   | rgy Efficient Fault Tolerant Task Mapping with Optimal Solutions   | 55 |

|               | 3.1   | Motivation Example                                                 | 55 |

|    | 3.2    | Task Mapping Problem for Independent Tasks                         | 57  |

|----|--------|--------------------------------------------------------------------|-----|

|    |        | 3.2.1 System Model                                                 | 57  |

|    |        | 3.2.2 Problem Constraints                                          | 58  |

|    |        | 3.2.3 Objective Function and Problem Formulation                   | 60  |

|    |        | 3.2.4 Evaluation                                                   | 63  |

|    | 3.3    | Task Mapping Problem for dependent tasks                           | 78  |

|    |        | 3.3.1 System Model                                                 | 78  |

|    |        | 3.3.2 Problem Constraints                                          | 79  |

|    |        | 3.3.3 Objective Function and Problem Formulation                   | 80  |

|    |        | 3.3.4 Evaluation                                                   | 82  |

|    | 3.4    | Conclusion                                                         | 98  |

|    | _      |                                                                    |     |

| 4  |        | rgy-Efficient Fault Tolerant Task Mapping with Heuristic Solutions | 99  |

|    | 4.1    | Independent Tasks under Task Level DVFS                            | 99  |

|    |        | 4.1.1 Reliability-aware Fault-tolerant Task Mapping heuristic      | 99  |

|    |        |                                                                    | 103 |

|    | 4.2    | Independent Tasks under Processor Level DVFS                       |     |

|    |        | 4.2.1 Reliability-aware Fault-tolerant Task Mapping heuristic      |     |

|    |        | 4.2.2 Evaluation results                                           |     |

|    | 4.3    | Independent Tasks under System Level DVFS                          |     |

|    |        | 4.3.1 Reliability-aware Fault-tolerant Task Mapping heuristic      |     |

|    |        | 4.3.2 Evaluation results                                           |     |

|    | 4.4    | Dependent Tasks under Task Level DVFS                              |     |

|    |        | 4.4.1 Reliability-aware Fault-tolerant Task Mapping heuristic      |     |

|    |        | 4.4.2 Evaluation results                                           |     |

|    | 4.5    | Dependent Tasks under Processor Level DVFS                         | 143 |

|    |        | 4.5.1 Reliability-aware Fault-tolerant Task Mapping heuristic      | 143 |

|    |        | 4.5.2 Evaluation Results                                           | 144 |

|    | 4.6    | Dependent Tasks under System Level DVFS                            | 151 |

|    |        | 4.6.1 Reliability-aware Fault-tolerant Task Mapping heuristic      | 151 |

|    |        |                                                                    | 152 |

|    | 4.7    | Conclusion                                                         | 158 |

| 5  | Cor    | clusions and Perspectives                                          | 159 |

|    | 5.1    | Summary                                                            | 159 |

|    | 5.2    | Future work and perspectives                                       | 160 |

| Bi | ibliog | graphy                                                             | 161 |

## LIST OF ACRONYMS

| SoA                 | State of Art                                                    |

|---------------------|-----------------------------------------------------------------|

| DVFS                | Dynamic Voltage and Frequency Scaling                           |

| WCET                | Worst Case Execution Time                                       |

| WCEC                | Worst Case Execution Cycle                                      |

| $\operatorname{SL}$ | Schedule Length of DAG                                          |

| EST                 | Earliest Start Time                                             |

| m LFT               | Latest Finish Time                                              |

| $\operatorname{st}$ | Actual start time                                               |

| $\operatorname{ft}$ | Actual finish time of task                                      |

| $\mathbf{et}$       | Execution time                                                  |

| pred                | All immediate predecessors                                      |

| succ                | All immediate successors                                        |

| $\mathbf{SC}$       | Selected Configuration                                          |

| NC                  | New checked Configuration                                       |

| proc                | Task set that are allocated on processor                        |

| RAFTM               | Proposed Reliability-aware Fault-tolerant Task Mapping approach |

| RAM                 | Reliability-Aware Mapping approach in SoA                       |

| TDM                 | Duplication Mapping approach in SoA                             |

| O_RAFTM             | Proposed RAFTM approach with optimal solutions                  |

| $H_RAFTM$           | Proposed RAFTM approach with heuristic solutions                |

| O_RAM               | RAM approach with optimal solutions                             |

| H_RAM               | RAM approach with heuristic solutions                           |

| O_TDM               | TDM approach with optimal solutions                             |

| H_TDM               | TDM approach with heuristic solutions                           |

| $\mathbf{EC}$       | Energy consumption                                              |

| RI                  | Reliability improvement                                         |

| $\operatorname{CT}$ | Computation time                                                |

# LIST OF FIGURES

| 1    | Ordonnancement de tâches sur système multicœur.                                                                      | 22 |

|------|----------------------------------------------------------------------------------------------------------------------|----|

| 2    | Proposed task mapping approaches and related DVFS levels                                                             | 25 |

| 3    | General overview of the proposed reliability-aware fault-tolerant task mapping                                       |    |

|      | approach                                                                                                             | 25 |

| 1.1  | A DAG task graph with a global deadline $D$                                                                          | 32 |

| 1.2  | Time parameters for a periodic task                                                                                  | 33 |

| 1.3  | Cause to transient faults.                                                                                           | 37 |

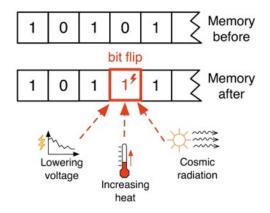

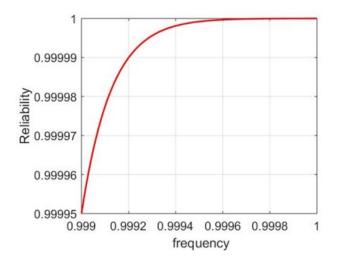

| 1.4  | Reliability as a function of frequency                                                                               | 38 |

| 1.5  | Task mapping on multicore architecture                                                                               | 40 |

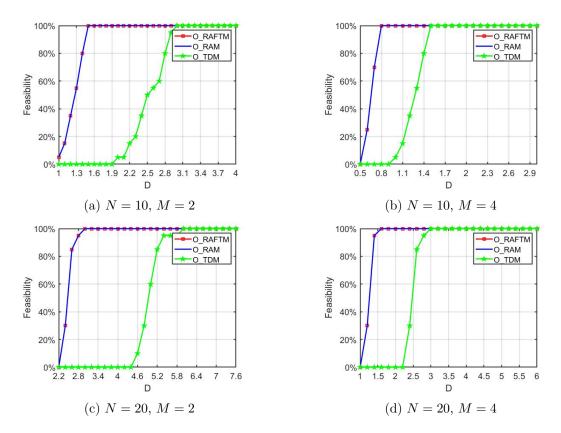

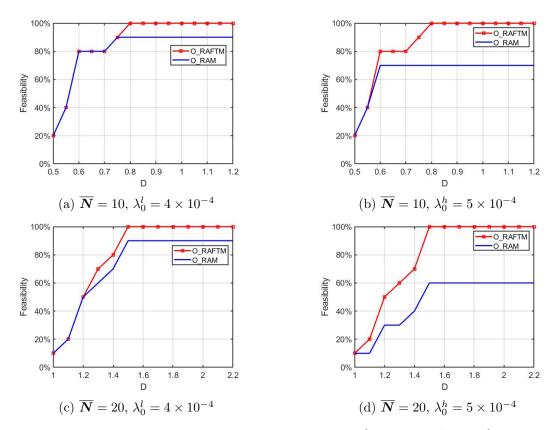

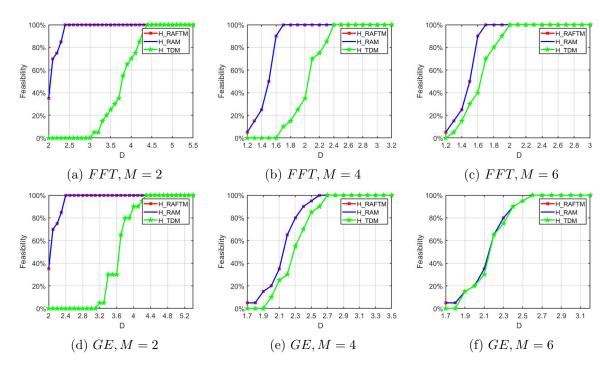

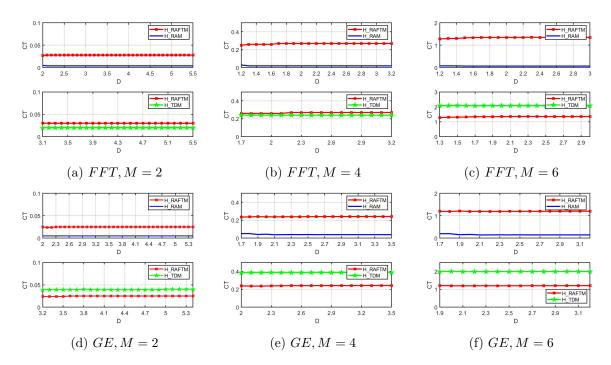

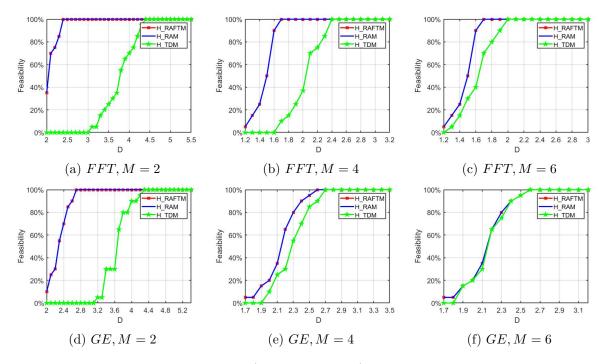

| 3.1  | Feasibility for independent tasks under all DVFS schemes                                                             | 66 |

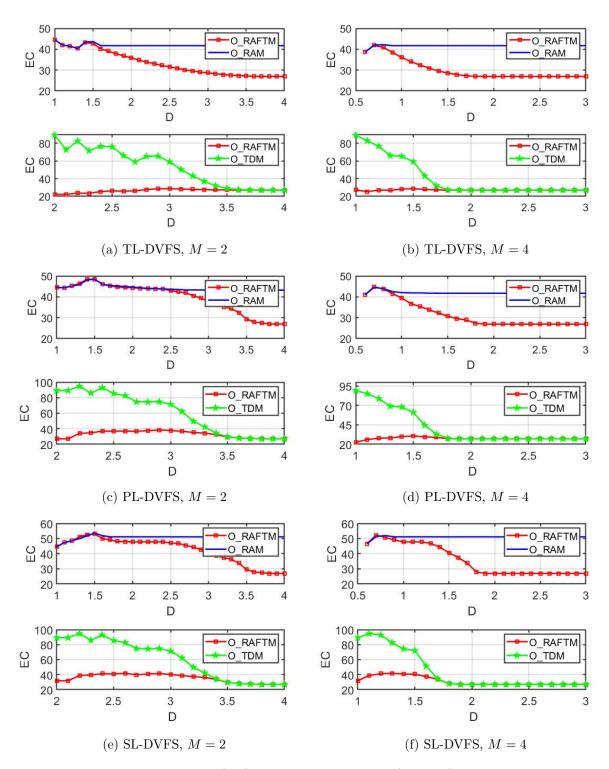

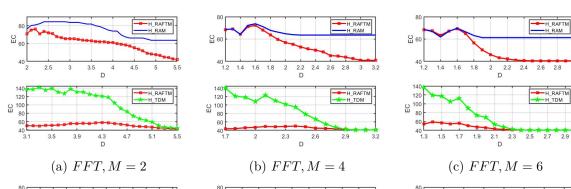

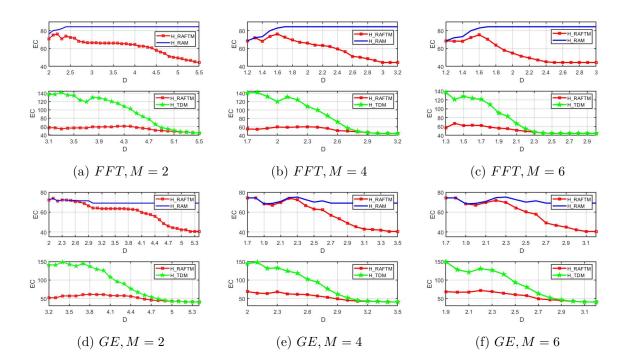

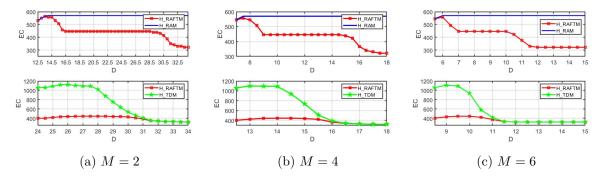

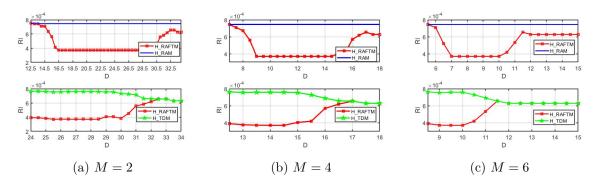

| 3.2  | Energy consumption (mJ) for independent tasks ( ${\cal N}=10)$ under all DVFS schemes.                               | 67 |

| 3.3  | Energy consumption (mJ) for independent tasks ( $N = 20$ ) under all DVFS schemes.                                   | 68 |

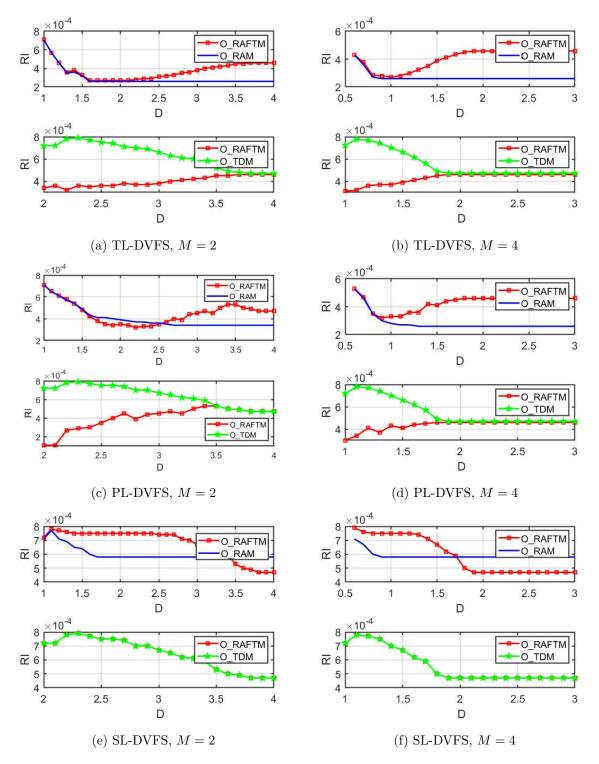

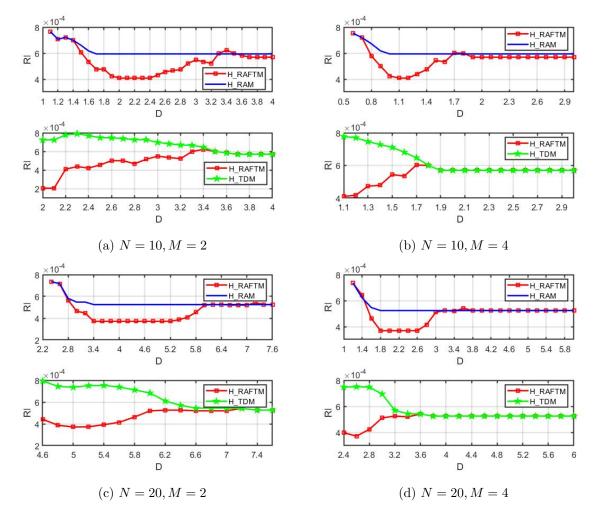

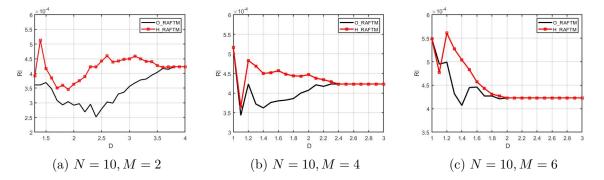

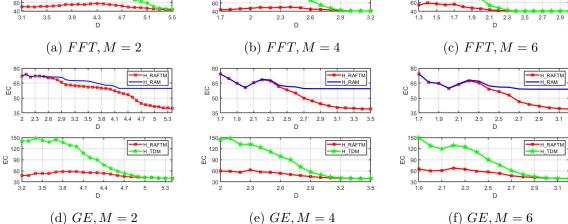

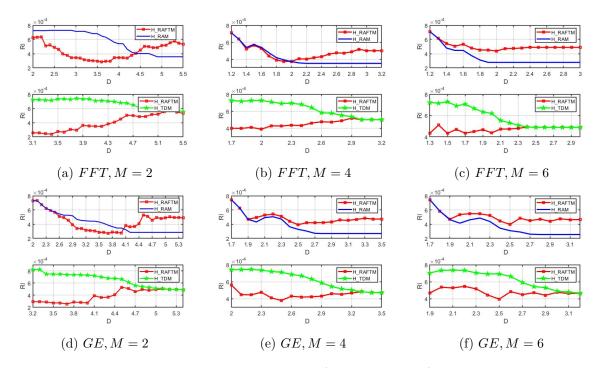

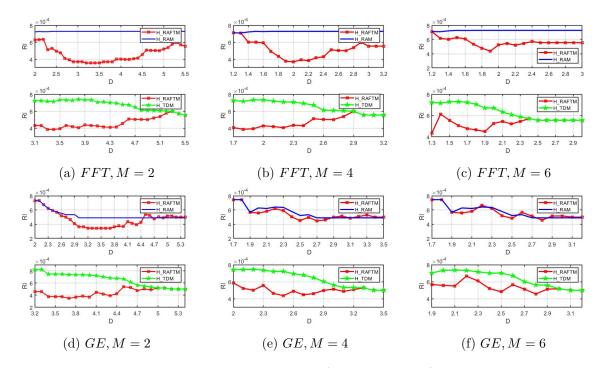

| 3.4  | Reliability improvement for independent tasks $(N = 10)$ under all DVFS schemes.                                     | 72 |

| 3.5  | Reliability improvement for independent tasks $(N = 20)$ under all DVFS schemes.                                     | 73 |

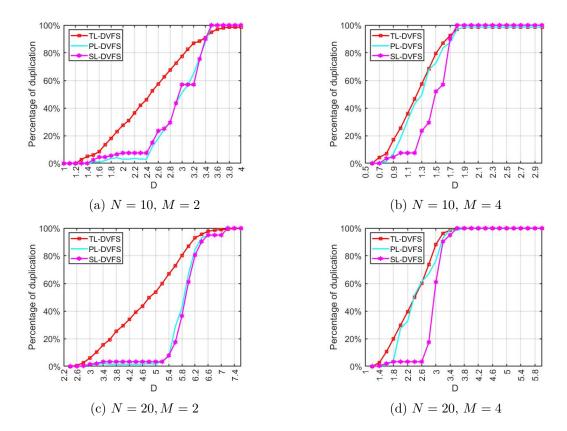

| 3.6  | O_RAFTM task duplication under all DVFS schemes                                                                      | 74 |

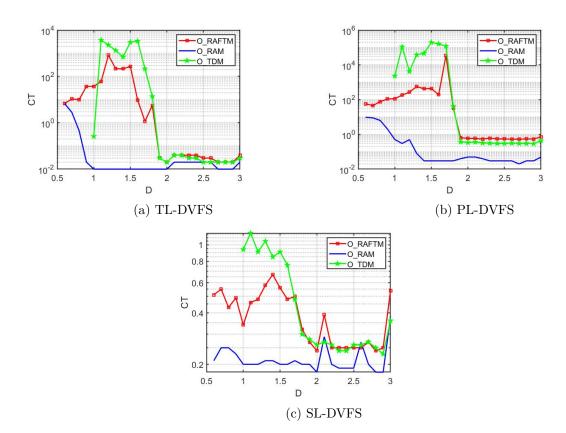

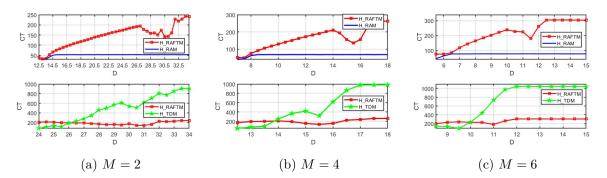

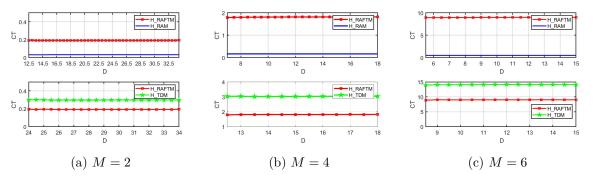

| 3.7  | Computation time on a logarithmic scale $(N = 10, M = 4)$ under all DVFS                                             |    |

|      | schemes                                                                                                              | 77 |

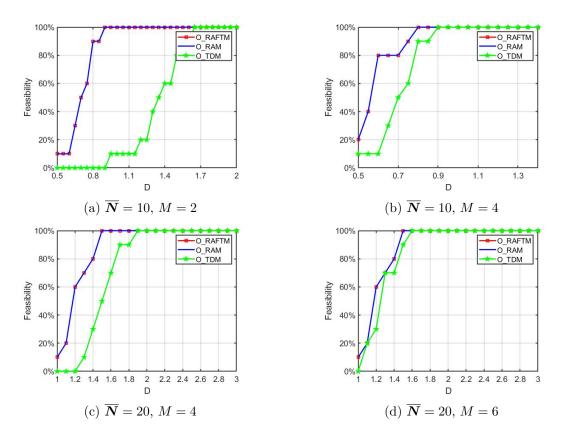

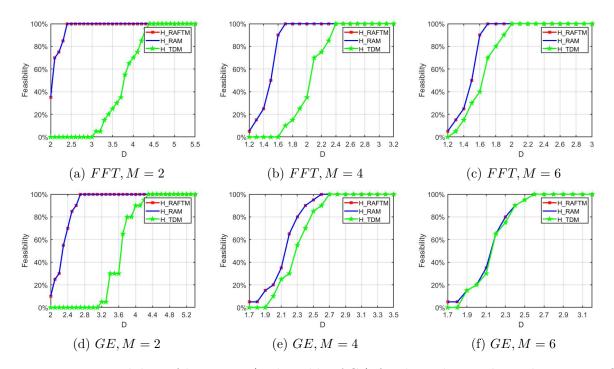

| 3.8  | Feasibility for dependent tasks under all DVFS schemes                                                               | 83 |

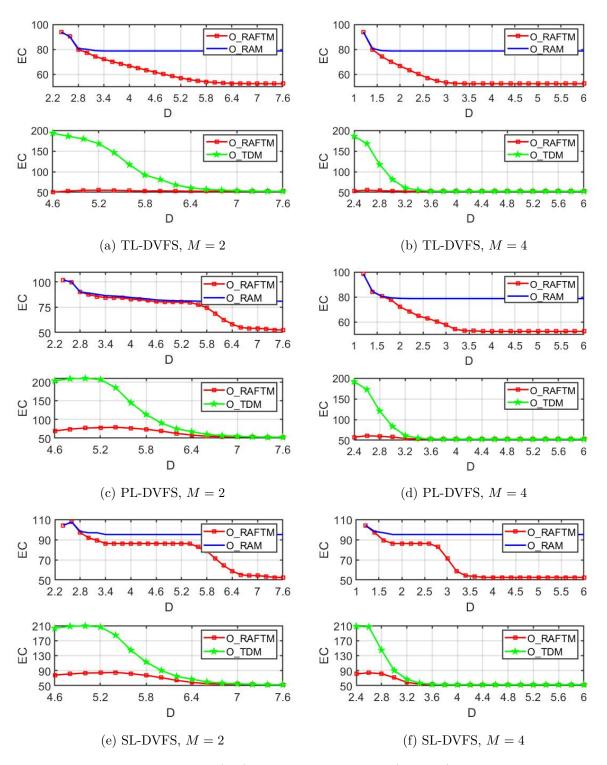

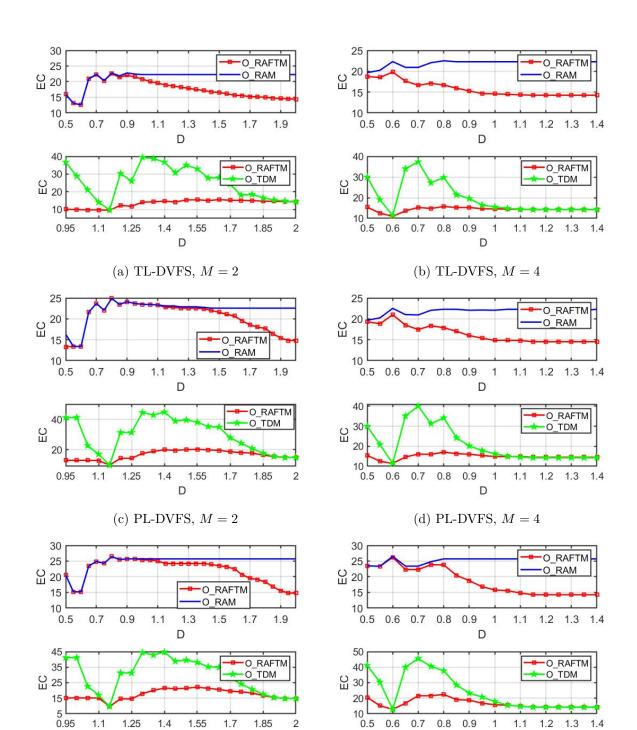

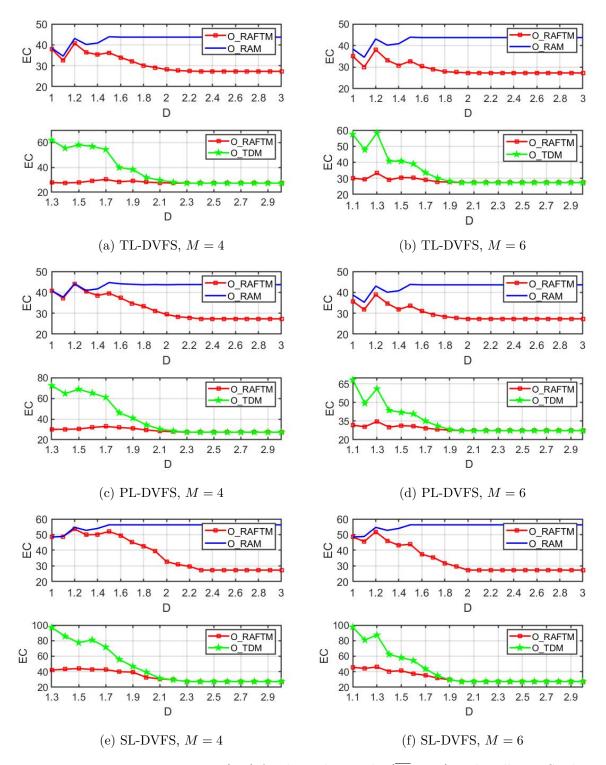

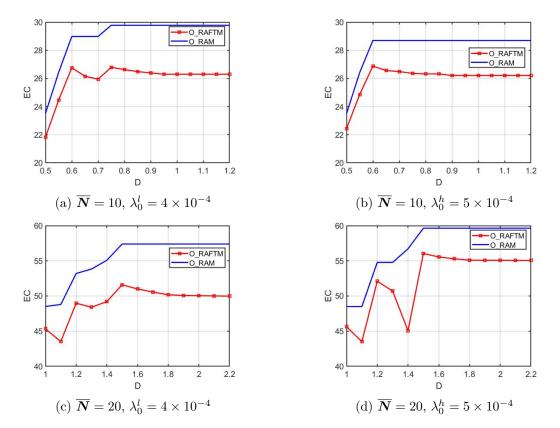

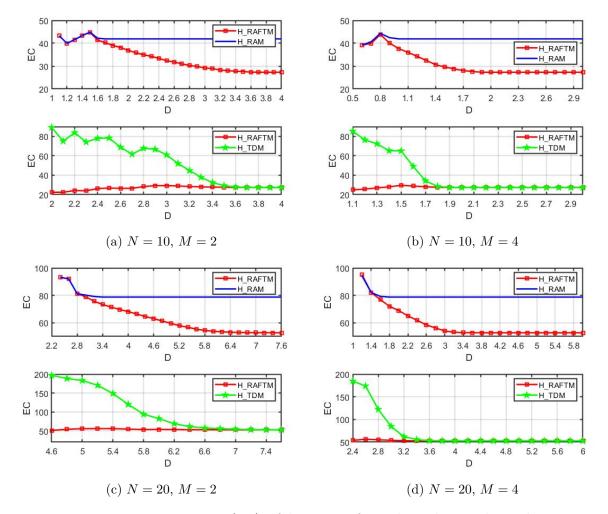

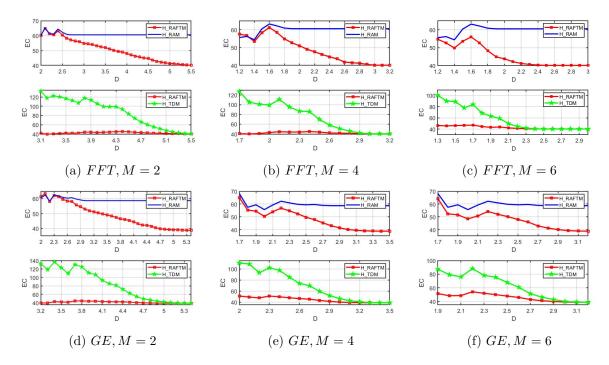

| 3.9  | Energy consumption (mJ) for dependent tasks ( $\overline{N} = 10$ ) under all DVFS schemes.                          | 86 |

| 3.10 | Energy consumption (mJ) for dependent tasks ( $\overline{N} = 20$ ) under all DVFS schemes.                          | 87 |

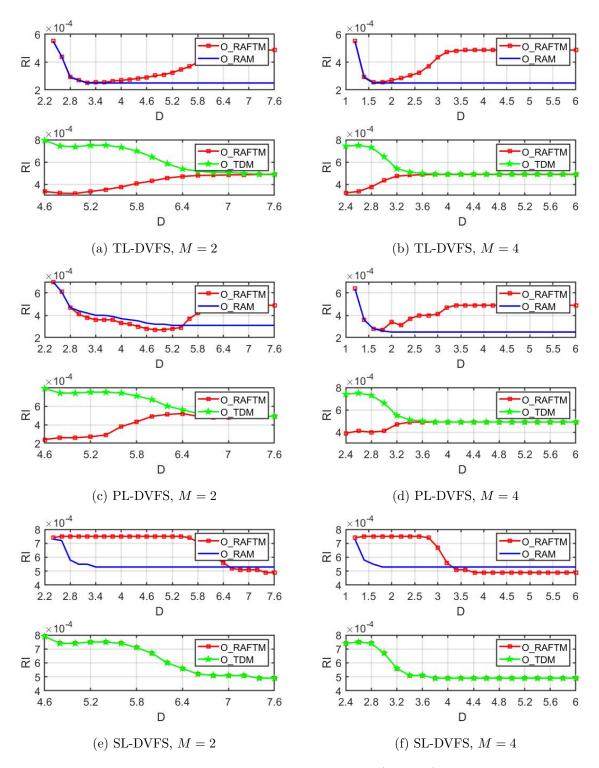

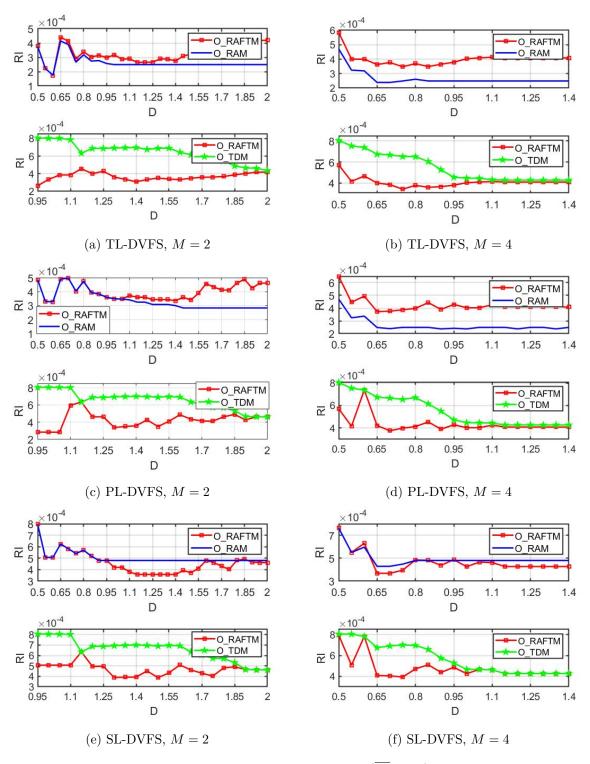

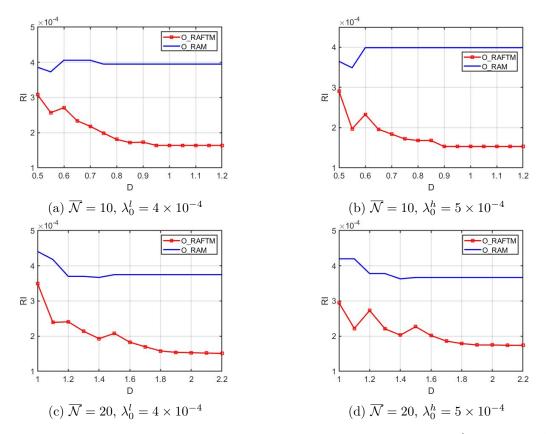

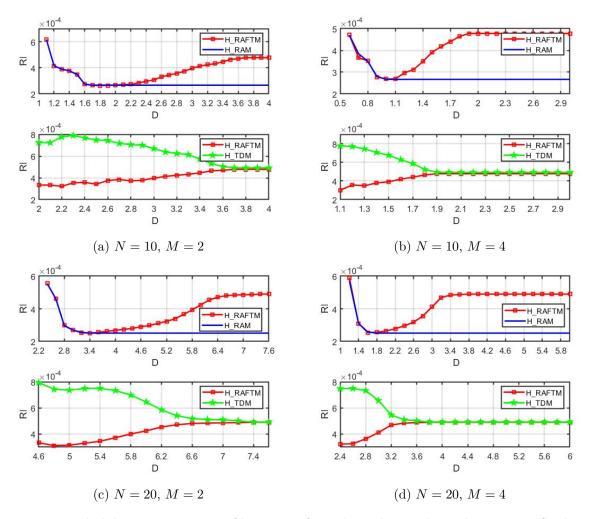

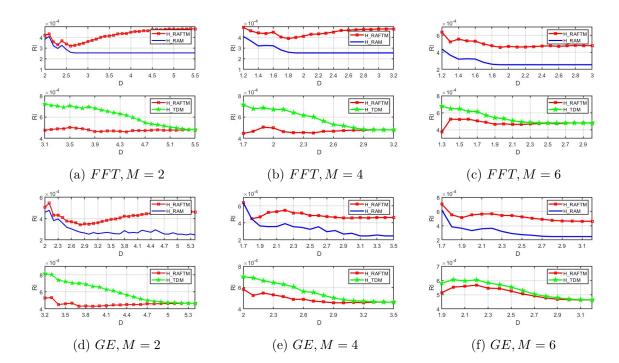

| 3.11 | Reliability improvement for dependent tasks ( $\overline{N} = 10$ ) under all DVFS schemes.                          | 89 |

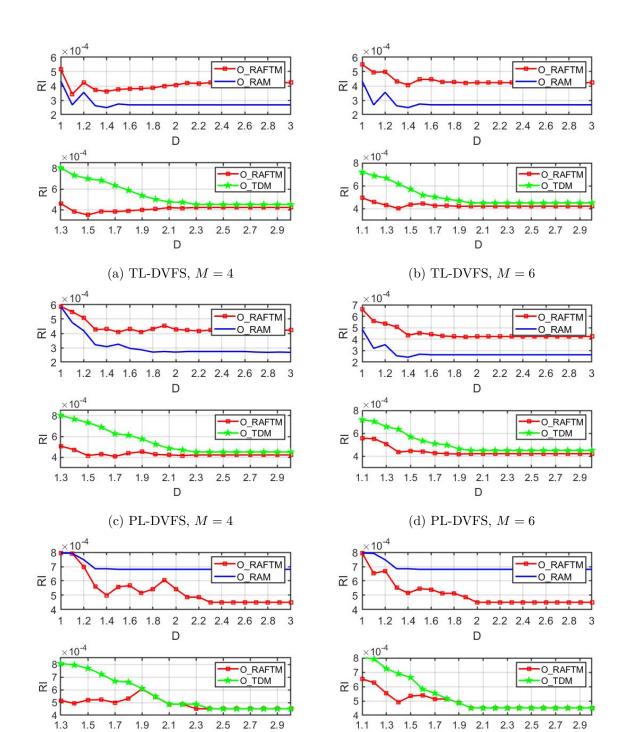

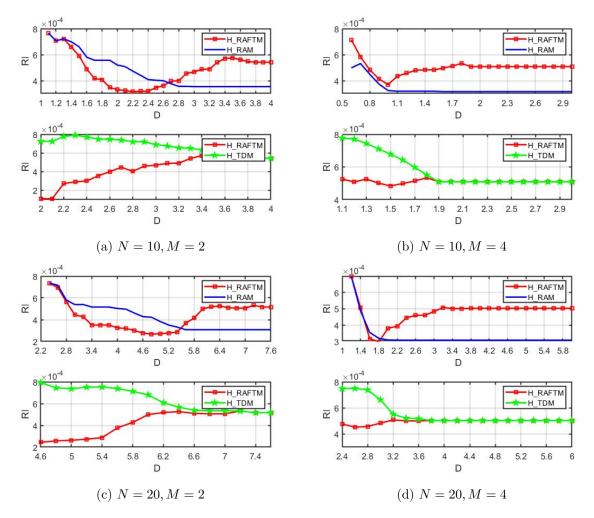

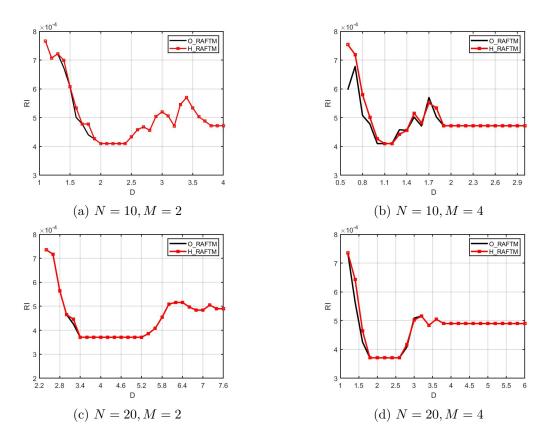

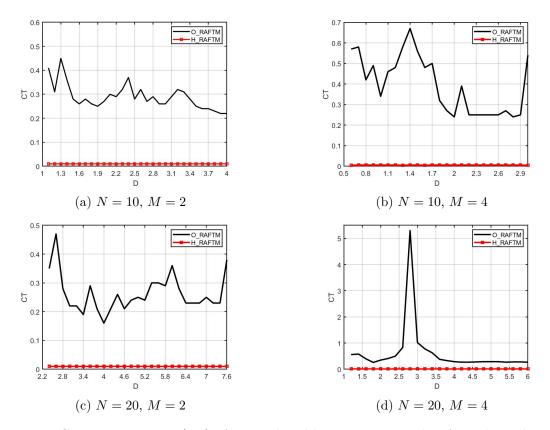

| 3.12 | Reliability improvement for dependent tasks ( $\overline{N} = 20$ ) under all DVFS schemes.                          | 90 |

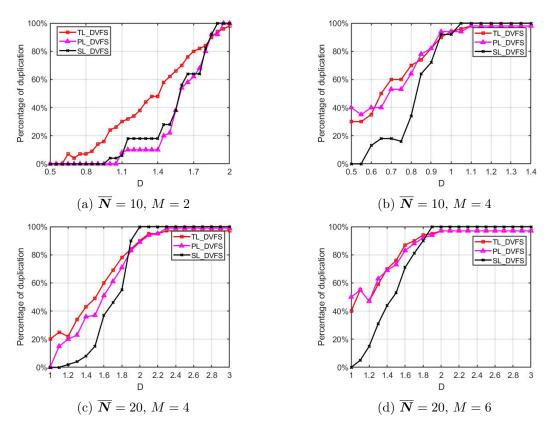

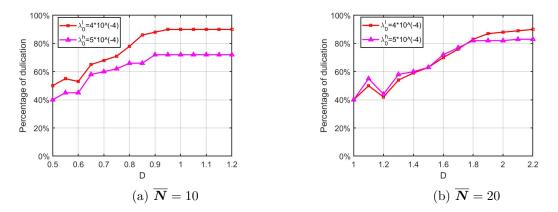

| 3.13 | O_RAFTM duplication percentage ( $\overline{N} = 10, M = 2$ and $M = 4$ , and $\overline{N} = 20$ ,                  |    |

|      | M = 4 and $M = 6$ ) for dependent tasks under all DVFS schemes                                                       | 91 |

| 3.14 | Feasibility for dependent tasks $(M = 4)$ with $\lambda_0^l = 4 \times 10^{-4}$ and $\lambda_0^h = 5 \times 10^{-4}$ |    |

|      | for TL-DVFS scheme.                                                                                                  | 94 |

| 3.15 | Energy consumption for dependent tasks $(M = 4)$ with $\lambda_0^l = 4 \times 10^{-4}$ and                           |    |

|      | $\lambda_0^h = 5 \times 10^{-4}$ for TL-DVFS scheme.                                                                 | 95 |

| 3.16 | Reliability improvement for dependent tasks $(M = 4)$ with $\lambda_0^l = 4 \times 10^{-4}$ and                      |    |

|      | $\lambda_0^h = 5 \times 10^{-4}$ for TL-DVFS scheme                                                                  | 96 |

| 3.17 | O_RAFTM task duplication percentage for dependent tasks (a) $\overline{N} = 10$ , and b)<br>$\overline{N} = 20, M = 4$ ) with $\lambda_0^l = 4 \times 10^{-4}$ and $\lambda_0^h = 5 \times 10^{-4}$ for TL-DVFS scheme. 97 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

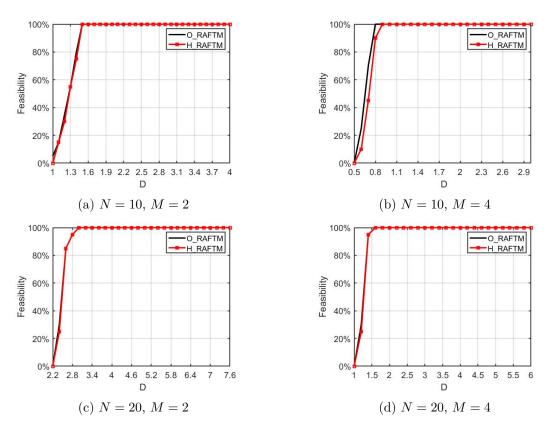

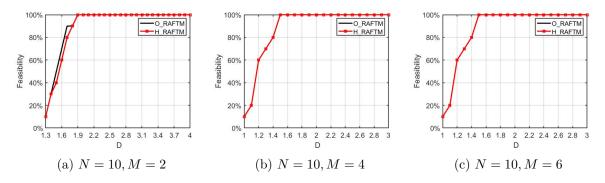

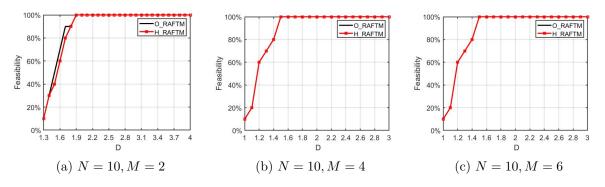

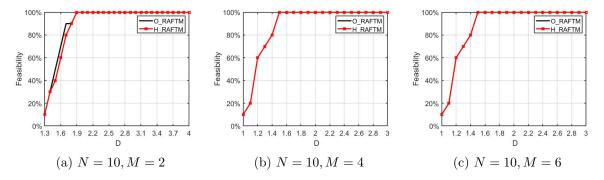

| 4.1  | Feasibility of optimal and heuristic approaches for independent tasks under TL-                                                                                                                                            |

|      | DVFS scheme                                                                                                                                                                                                                |

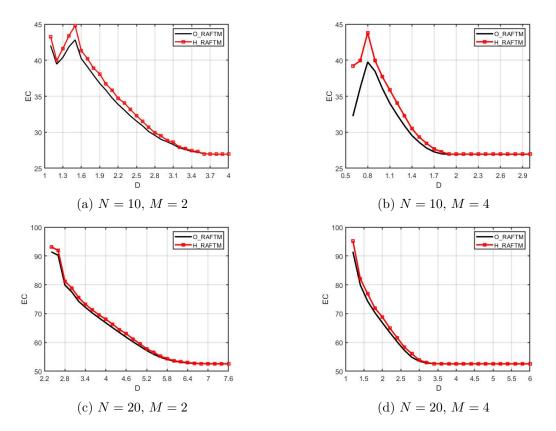

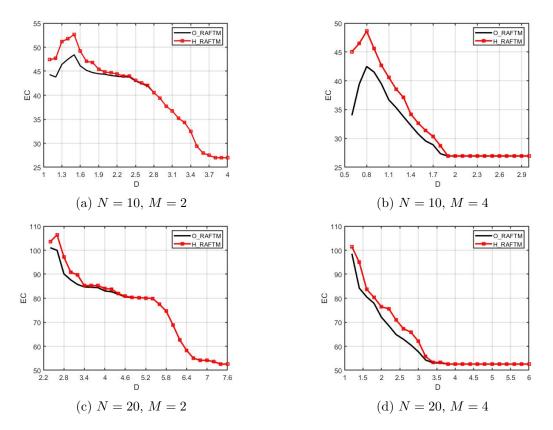

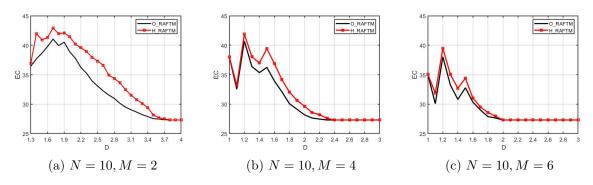

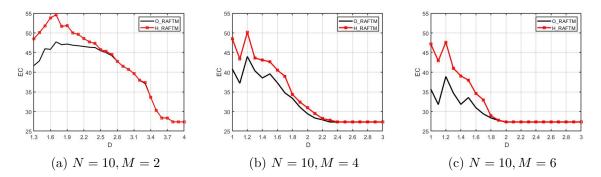

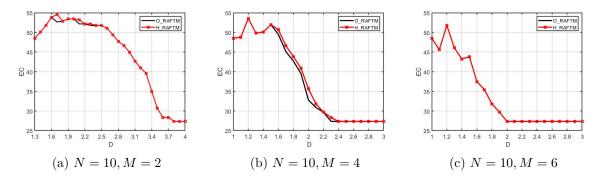

| 4.2  | Energy consumption (mJ) of optimal and heuristic approaches for independent tasks under TL-DVFS scheme                                                                                                                     |

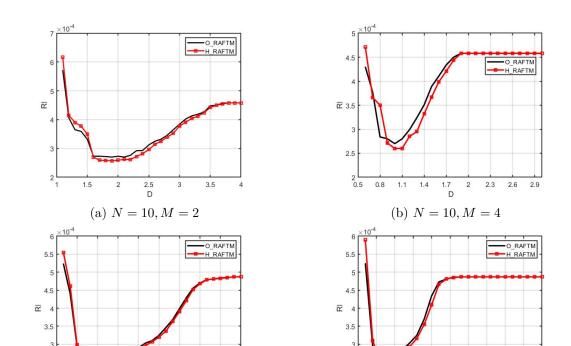

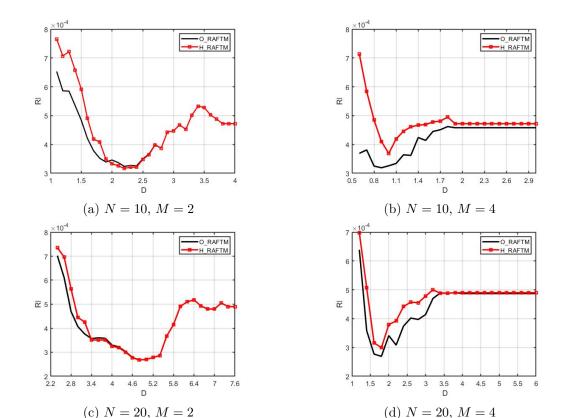

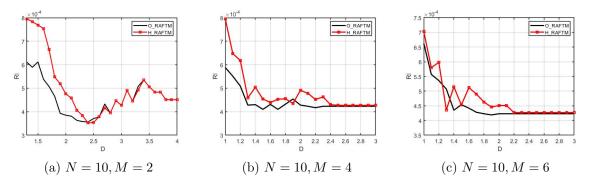

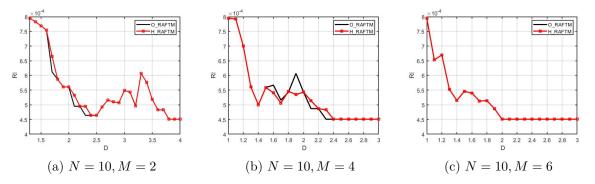

| 4.3  | Reliability improvement of optimal and heuristic approaches for independent tasks                                                                                                                                          |

|      | under TL-DVFS scheme                                                                                                                                                                                                       |

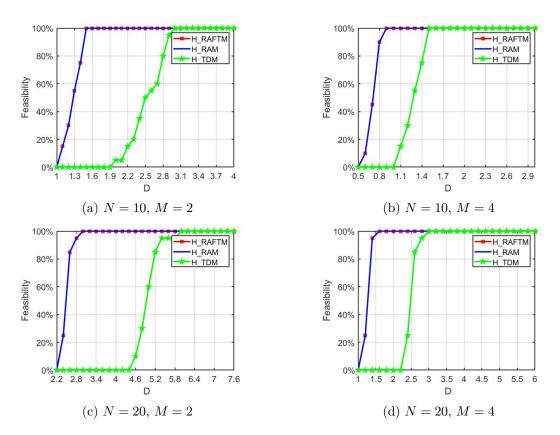

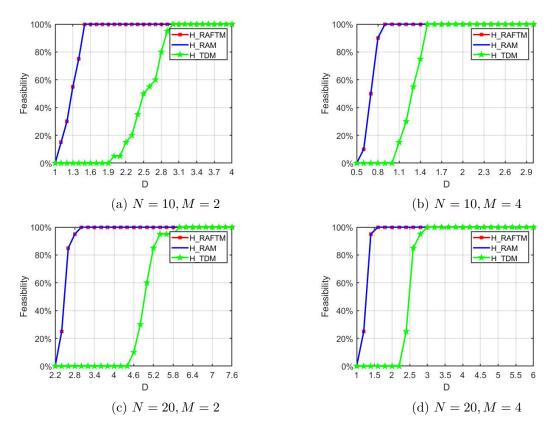

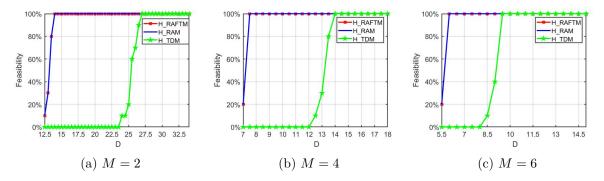

| 4.4  | Feasibility of heuristics for independent tasks under TL-DVFS scheme 108                                                                                                                                                   |

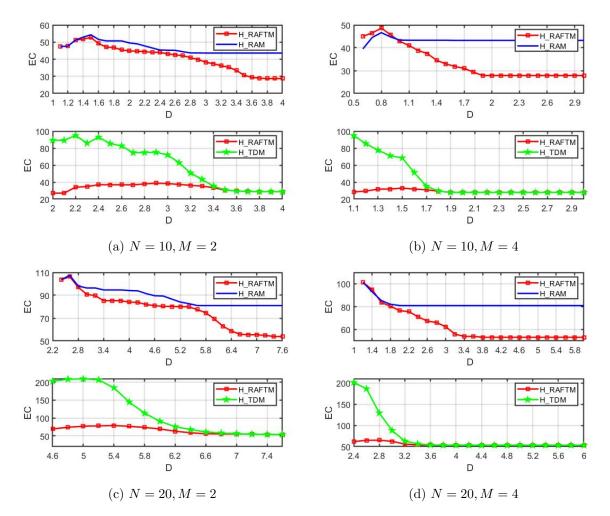

| 4.5  | Energy consumption (mJ) of heuristics for independent tasks under TL-DVFS                                                                                                                                                  |

|      | scheme                                                                                                                                                                                                                     |

| 4.6  | Reliability improvement of heuristics for independent tasks under TL-DVFS scheme. $110$                                                                                                                                    |

| 4.7  | Computation time (sec) of heuristics for independent tasks under TL-DVFS scheme. $111$                                                                                                                                     |

| 4.8  | Feasibility of optimal and heuristic approaches for independent tasks under PL-                                                                                                                                            |

|      | DVFS scheme                                                                                                                                                                                                                |

| 4.9  | Energy consumption (mJ) of optimal and heuristic approaches for independent                                                                                                                                                |

|      | tasks under PL-DVFS scheme. $\ldots$                                                                                                                                                                                       |

| 4.10 | Reliability improvement of optimal and heuristic approaches for independent tasks                                                                                                                                          |

|      | under PL-DVFS scheme                                                                                                                                                                                                       |

| 4.11 | Feasibility of heuristics for independent tasks under PL-DVFS                                                                                                                                                              |

| 4.12 | Energy consumption (mJ) of heuristics for independent tasks under PL-DVFS                                                                                                                                                  |

|      | scheme                                                                                                                                                                                                                     |

| 4.13 | Reliability improvement of heuristics for independent tasks under PL-DVFS scheme. $120$                                                                                                                                    |

| 4.14 | Computation time (sec) of heuristics for independent tasks under PL-DVFS scheme. $121$                                                                                                                                     |

| 4.15 | Feasibility of optimal and heuristic approaches for independent tasks under SL-                                                                                                                                            |

|      | DVFS scheme                                                                                                                                                                                                                |

| 4.16 | Energy consumption (mJ) of optimal and heuristic approaches for independent                                                                                                                                                |

|      | tasks under SL-DVFS scheme                                                                                                                                                                                                 |

| 4.17 | Reliability improvement of optimal and heuristic approaches for independent tasks                                                                                                                                          |

|      | under SL-DVFS scheme                                                                                                                                                                                                       |

| 4.18 | Computation time (sec) of optimal and heuristic approaches for independent tasks                                                                                                                                           |

|      | under SL-DVFS scheme                                                                                                                                                                                                       |

|      | Feasibility of heuristics for independent tasks under SL-DVFS scheme 127                                                                                                                                                   |

| 4.20 | Energy consumption (mJ) of heuristics for independent tasks under SL-DVFS                                                                                                                                                  |

|      | scheme                                                                                                                                                                                                                     |

|      | Reliability improvement of heuristics for independent tasks under SL-DVFS scheme.<br>129 $$                                                                                                                                |

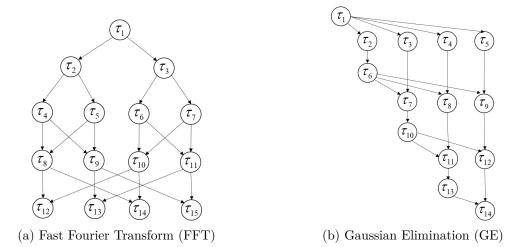

| 4.22 | DAG obtained from real code kernels                                                                                                                                                                                        |

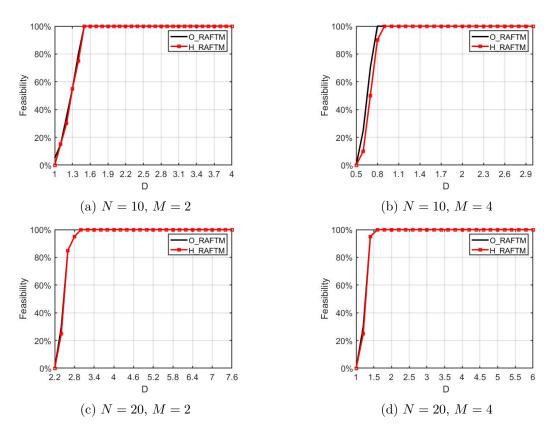

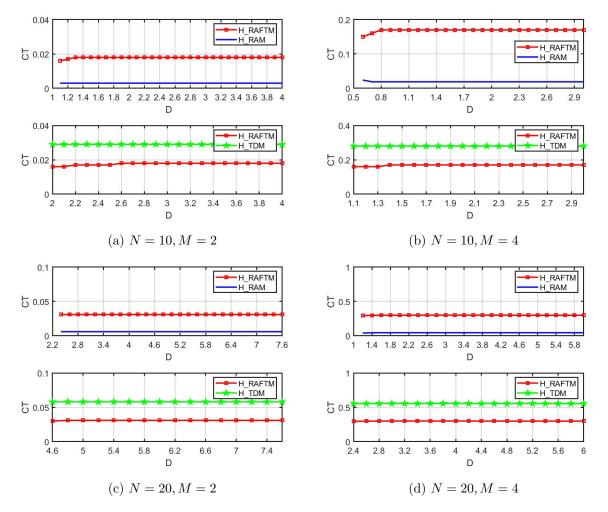

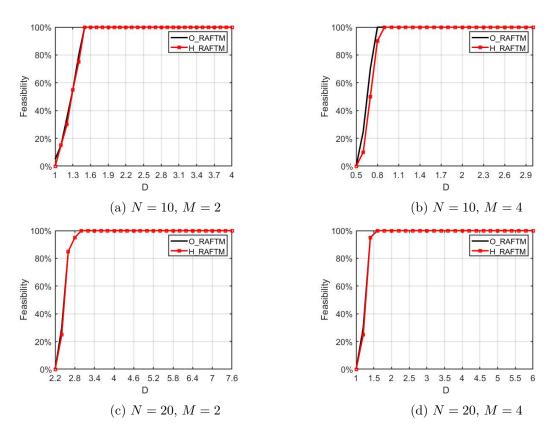

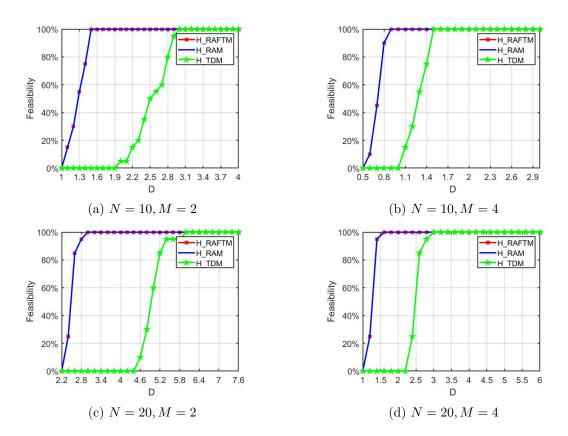

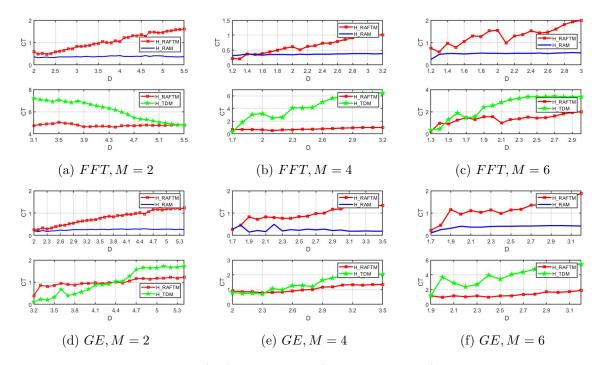

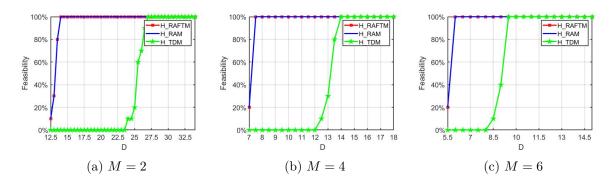

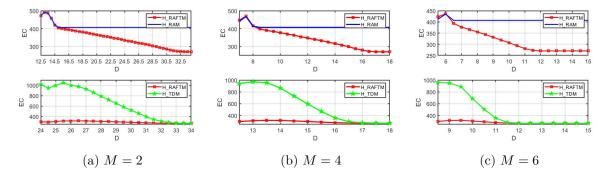

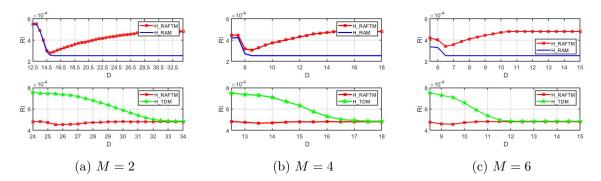

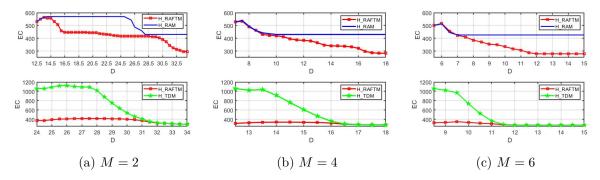

| 4.23 | Feasibility of optimal and heuristic approaches for dependent tasks under TL-<br>DVFS scheme                                 | 135   |

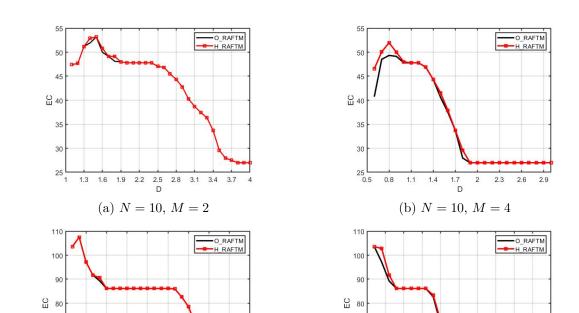

|------|------------------------------------------------------------------------------------------------------------------------------|-------|

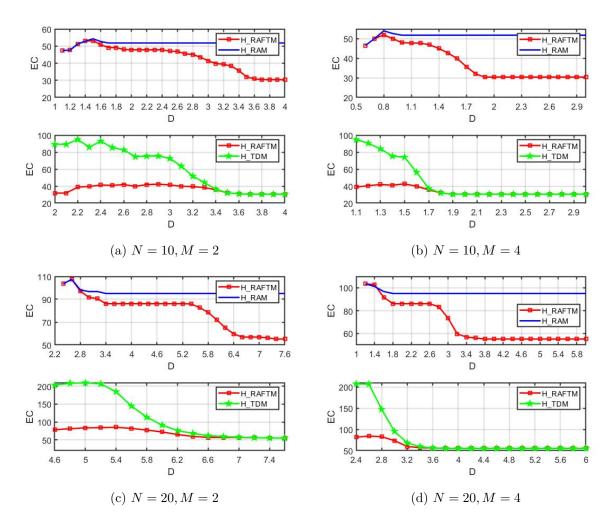

| 4.24 | Energy consumption (mJ) of optimal and heuristic approaches for dependent tasks under TL-DVFS scheme.                        | 136   |

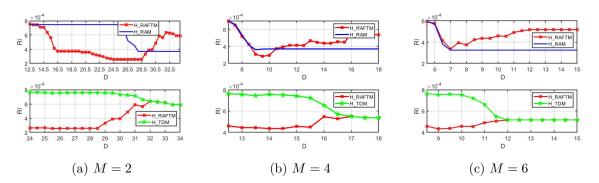

| 4.25 | Reliability improvement of optimal and heuristic approaches for dependent tasks                                              |       |

| 4.26 | under TL-DVFS scheme                                                                                                         | 136   |

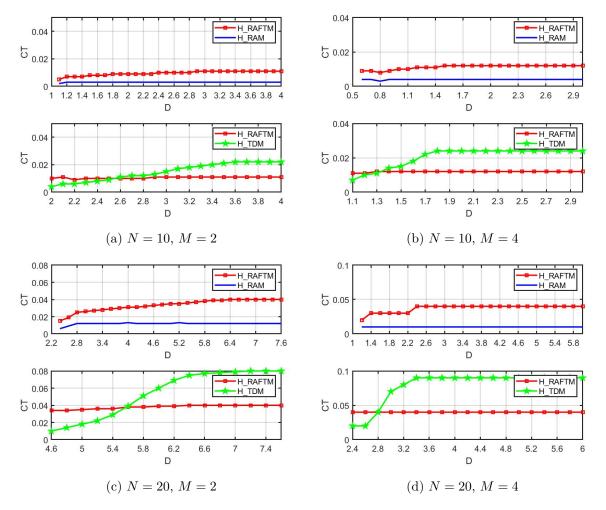

| 4.27 | scheme                                                                                                                       | 138   |

| 4.00 | under TL-DVFS scheme.                                                                                                        | 139   |

| 4.28 | Reliability improvement of heuristics (real-world DAGs) for dependent tasks under TL-DVFS scheme.                            | 140   |

| 4.29 | Computation time (sec) of heuristics (real-world DAGs) for dependent tasks under TL-DVFS scheme.                             | 140   |

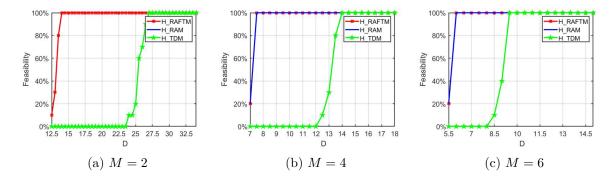

| 4.30 | Feasibility of heuristics (large randomly generated DAG, $N = 100$ ) for dependent                                           | 1 / 1 |

| 4.31 | tasks under TL-DVFS scheme                                                                                                   | 141   |

| 4 32 | 100) for dependent tasks under TL-DVFS scheme                                                                                | 141   |

| 1.02 | for dependent tasks under TL-DVFS scheme                                                                                     | 142   |

| 4.33 | Computation time (sec) of heuristics (large randomly generated DAG, $N = 100$ )<br>for dependent tasks under TL-DVFS scheme. | 142   |

| 4.34 | Feasibility of optimal and heuristic approaches for dependent tasks under PL-<br>DVFS scheme.                                | 145   |

| 4.35 | Energy consumption (mJ) of optimal and heuristic approaches for dependent                                                    |       |

| 4.36 | tasks under PL-DVFS scheme                                                                                                   | 145   |

|      | under PL-DVFS scheme                                                                                                         | 145   |

| 4.37 | Feasibility of heuristics (real-code DAGs) for dependent tasks under PL-DVFS scheme.                                         | 147   |

| 4.38 | Energy consumption (mJ) of heuristics (real-code DAGs) for dependent tasks under PL-DVFS scheme.                             | 1/18  |

| 4.39 | Reliability improvement of heuristics (real-code DAGs) for dependent tasks under                                             |       |

|      | PL-DVFS scheme.                                                                                                              | 148   |

| 4.40 | Computation time (sec)of heuristics (real-code DAGs) for dependent tasks under PL-DVFS scheme.                               | 149   |

| 4.41 | Feasibility of heuristics (large randomly generated DAG, $N = 100$ ) for dependent |     |

|------|------------------------------------------------------------------------------------|-----|

|      | tasks under PL-DVFS scheme.                                                        | 149 |

| 4.42 | Energy consumption (mJ) of heuristics (large randomly generated DAG, $N =$         |     |

|      | 100) for dependent tasks under PL-DVFS scheme                                      | 150 |

| 4.43 | Reliability improvement of heuristics (large randomly generated DAG, $N = 100$ )   |     |

|      | for dependent tasks under PL-DVFS scheme                                           | 150 |

| 4.44 | Computation time (sec) of heuristics (large randomly generated DAG, $N = 100$ )    |     |

|      | for dependent tasks under PL-DVFS scheme                                           | 150 |

| 4.45 | Feasibility of optimal and heuristic approaches for dependent tasks under SL-      |     |

|      | DVFS scheme.                                                                       | 153 |

| 4.46 | Energy consumption (mJ) of optimal and heuristic approaches for dependent          |     |

|      | tasks under SL-DVFS scheme                                                         | 154 |

| 4.47 | Reliability improvement of optimal and heuristic approaches for dependent tasks    |     |

|      | under SL-DVFS scheme                                                               | 154 |

| 4.48 | Feasibility of heuristics (real-code DAGs) for dependent tasks under SL-DVFS       |     |

|      | scheme                                                                             | 155 |

| 4.49 | Energy consumption (mJ) of heuristics (real-code DAGs) for dependent tasks         |     |

|      | under SL-DVFS scheme                                                               | 156 |

| 4.50 | Reliability improvement of heuristics (real-code DAGs) for dependent tasks under   |     |

|      | SL-DVFS scheme.                                                                    | 156 |

| 4.51 | Feasibility of heuristics (large randomly generated DAG, $N = 100$ ) for dependent |     |

|      | tasks under SL-DVFS scheme                                                         | 157 |

| 4.52 | Energy consumption (mJ) of heuristics (large randomly generated DAG, $N =$         |     |

|      | 100) for dependent tasks under SL-DVFS scheme.                                     | 157 |

| 4.53 | Reliability improvement of heuristics (large randomly generated DAG, $N = 100$ )   |     |

|      | for dependent tasks under SL-DVFS scheme.                                          | 158 |

| 5.1  | Proposed task mapping approaches and related DVFS levels                           | 159 |

| 5.2  | General overview of the proposed reliability-aware fault-tolerant task mapping     |     |

|      | approach                                                                           | 161 |

|      | * *                                                                                |     |

# LIST OF TABLES

| 2.1  | Representative State-of-the-Art targeting energy minimization                                                                    | 42  |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | Representative State-of-the-Art approaches targeting reliability maximization                                                    | 49  |

| 2.3  | $Representative\ State-of-the-Art\ approaches\ targeting\ schedule-length\ minimization.$                                        | 50  |

| 3.1  | Motivational Example. (*Optimal solutions are highlighted in bold). $\ldots$ .                                                   | 56  |

| 3.2  | Main Notations                                                                                                                   | 58  |

| 3.3  | Platform and benchmark characteristics                                                                                           | 64  |

| 3.4  | Min., avg. and max. energy consumption (mJ) of O_RAFTM under all DVFS $$                                                         |     |

|      | schemes                                                                                                                          | 70  |

| 3.5  | Min., avg. and max. energy saving gains (%) under all DVFS schemes. $\ldots$ .                                                   | 71  |

| 3.6  | Computation time (sec) for independent tasks $(N = 10, M = 2)$ under all DVFS                                                    |     |

|      | schemes                                                                                                                          | 75  |

| 3.7  | Computation time (sec) for independent tasks $(N = 10, M = 4)$ under all DVFS                                                    |     |

|      | schemes                                                                                                                          | 75  |

| 3.8  | Computation time (sec) for independent tasks $(N = 20, M = 2)$ under all DVFS                                                    |     |

|      | schemes                                                                                                                          | 76  |

| 3.9  | Computation time (sec) for independent tasks $(N = 20, M = 4)$ under all DVFS                                                    |     |

|      | schemes                                                                                                                          | 76  |

| 3.10 | Main notations for dependent tasks                                                                                               | 78  |

| 3.11 | Min, avg. and max energy gains (%) for dependent tasks under all DVFS schemes.                                                   | 85  |

| 3.12 | Computation time (sec) for dependent tasks ( $\overline{N} = 10, M = 4$ ) under all DVFS                                         |     |

|      | schemes                                                                                                                          | 92  |

| 3.13 | Computation time (sec) for dependent tasks ( $\overline{N} = 20, M = 4$ ) under all DVFS                                         |     |

|      | schemes                                                                                                                          | 92  |

| 3.14 | Computation time (sec) for dependent tasks ( $\overline{N} = 20, M = 6$ ) under all DVFS                                         |     |

|      | schemes                                                                                                                          | 93  |

| 3.15 | Computation time (sec) ( $\overline{N} = 10, M = 4$ ) with $\lambda_0^l = 4 \times 10^{-4}$ and $\lambda_0^h = 5 \times 10^{-4}$ |     |

|      | for TL-DVFS scheme.                                                                                                              | 97  |

| 3.16 | Computation time (sec) ( $\overline{N} = 20, M = 4$ ) with $\lambda_0^l = 4 \times 10^{-4}$ and $\lambda_0^h = 5 \times 10^{-4}$ |     |

|      | for TL-DVFS scheme.                                                                                                              | 97  |

| 4.1  | Main notations for independent tasks under TL-DVFS scheme.                                                                       | 100 |

| 4.2 | Computation time (sec) of optimal and heuristic approaches for independent tasks |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | under TL-DVFS scheme                                                             | 107 |

| 4.3 | Computation time (seconds) of optimal and heuristic approaches for independent   |     |

|     | tasks under PL-DVFS scheme.                                                      | 117 |

| 4.4 | Main notations for dependent tasks under TL-DVFS scheme                          | 130 |

| 4.5 | Computation time (sec) of optimal and heuristic approaches for dependent tasks   |     |

|     | under TL-DVFS scheme                                                             | 137 |

| 4.6 | Computation time (sec) of optimal and heuristic approaches for dependent tasks   |     |

|     | under PL-DVFS scheme                                                             | 146 |

| 4.7 | Computation time (sec) of optimal and heuristic approaches for dependent tasks   |     |

|     | (N = 10) under SL-DVFS scheme                                                    | 154 |

|     |                                                                                  |     |

## Contexte

Les systèmes critiques pour la sécurité consistent généralement en des systèmes où des garanties doivent être fournies sur la sécurité et la fiabilité des applications critiques, ce qui implique à la fois une tolérance élevée aux pannes et des contraintes temporelles strictes (temps réel) [1]. Par exemple, les systèmes avioniques sont constitués d'applications avec des niveaux élevés d'assurance de conception [2] et fonctionnant à des altitudes élevées exposées aux rayonnements. Les systèmes spatiaux consistent en des applications de contrôle de la navigation fonctionnant dans l'espace extra-atmosphérique avec des particules et un rayonnement électromagnétique à haute énergie. Les systèmes automobiles ont des applications comme par exemple un capteur dans une roue pour à la fois le contrôle de la stabilité et la régulation de l'accélération et sont soumis à des particules alpha, des pics de température élevés et de l'interférences électromagnétiques [3]. Ces stimuli naturels sont à l'origine de défauts qui impactent le fonctionnement du système [4]. De plus, au cours des trente dernières années, la taille du code des applications avioniques, spatiales et automobiles a considérablement augmenté [5]. Ces systèmes font face à une croissance exponentielle des exigences de performances, et les futures applications automobiles et aérospatiales nécessiteront des ressources de calcul encore plus performantes [1].

Pour faire face aux demandes croissantes de performances, le marché grand public s'est tourné vers les architectures multicœurs, en raison de la consommation d'énergie et des limites de dissipation thermique des processeurs monocœurs [1]. D'une manière générale, les multicœurs offrent des réductions de taille, de poids, de puissance consommée et ont des capacités de calcul élevées par rapport aux processeurs monocœur, et peuvent donc intégrer plusieurs applications sur la même plate-forme [6]. Cependant,deux principaux défis scientifiques sont soulevés par l'utilisation des multicœurs.

Le premier défi est la consommation d'énergie élevée qui est devenue l'un des plus grands obstacles au développement des systèmes informatiques hautes performances, en particulier pour les systèmes à budget énergétique limité, tels que les objets connectés alimentés par batterie ou à récupération d'énergie. Les smartphones utilisent des architectures multicœurs hétérogènes, telles que big.LITTLE [7], qui se compose de gros cœurs optimisés en termes de performances et de petits cœurs optimisés en énergie avec une seule architecture de jeu d'instructions (ISA) [8]. Les cartes embarquées pour les objets connectés, telles Raspberry Pi, Odroid, Edison, Jetson et Artik, disposent également de plusieurs cœurs [9, 10, 11]. Par conséquent, les plates-formes multicœurs ont été améliorées avec la possibilité de régler leur tension et leur fréquence (gestion dynamique de la tension et de la fréquence (DVFS) pendant l'exécution pour équilibrer les performances du système et les économies d'énergie.

Le deuxième défi est que le système multicœur lui-même est susceptible de subir des défauts en raison de la nature des systèmes électroniques. Conjugués à la réduction de la taille des transistors, les systèmes multicœurs deviennent de plus en plus sensibles aux conditions de fonctionnement et à l'impact environnemental [12]. Dans les systèmes électroniques, la variation de la tension de seuil dépend de la largeur du transistor, tandis que des trous ou de petites fissures dans les interconnexions entraînent des problèmes de source fermée ou ouverte. L'activité électrique et les points chauds sont inévitables et ils provoquent une électromigration, une instabilité de température de polarisation et une diaphonie, qui sont des sources de défauts. Pour améliorer la fiabilité du multicœur, soit des processeurs durcis aux radiations sont utilisés, soit le système est répliqué [13]. La première solution conduit à des systèmes avec des capacités de calcul limitées et nécessite une expertise de conception difficile à trouver. La seconde solution a un coût et une consommation d'énergie élevés. Pour réduire les coûts tout en assurant la fiabilité, la réplication des ressources et le surdimensionnement du système doivent être évités, dans la mesure du possible.

En tenant compte des deux défis présentés ci-dessus, afin d'exploiter pleinement les fonctionnalités des systèmes multicœurs tout en visant une exécution de l'application à la fois fiable, économe en énergie et satisfaisant la contrainte temps-réel, des méthodes sont nécessaires pour décider de l'exécution efficace des tâches. La manière dont les tâches sont exécutées sur une plateforme est déterminée par plusieurs facteurs. Le premier facteur est l'ordonnancement (à quel moment chaque tâche commence son exécution) et l'allocation (sur quel processeur chaque tâche est exécutée) des tâches. Le deuxième facteur est la décision de l'assignation de la tension et la fréquence du processeur lorsqu'il exécute une tâche spécifique, ce qui détermine le temps d'exécution de la tâche. Pour les applications critiques, les limites de pire temps d'exécution (Worst Case Execution Time (WCET)) sont utilisées car elles sont nécessaires pour garantir la fiabilité et le bon comportement fonctionnel.

### Modèles systèmes et ordonnancement temps-réel de tâches

L'objectif de cette thèse est de trouver un compromis multicritères d'un ordonnancement de tâches sur des architectures multicœurs, tolérant aux fautes, efficace en énergie et temps-réel. Dans un premier temps, nous définissons l'architecture et les modèles systèmes utilisés dans cette thèse :

#### Les architectures multicœurs

Pour répondre à l'augmentation rapide des besoins de calcul, à une faible consommation du

système, ainsi qu'assurer un parallélisme élevé dans l'exécutions des applications, les systèmes multicœurs sont des plates-formes prometteuses pour les systèmes embarqués temps réel. Sur le marché des circuits, de nombreux fabricants de puces, par exemple AMD et Intel, ont lancé des puces multicœurs avec un nombre croissant de cœurs, comme par exemple la série Intel Xeon. Une architecture multicœur se compose de deux ou plusieurs unités de traitement séparées (cœurs) sur un seul circuit intégré. Chaque cœur exécute les instructions du processeur en même temps, ce qui augmente la vitesse globale du calcul parallèle. Les architectures multicœurs peuvent être caractérisées comme des systèmes homogènes ou hétérogènes. Les systèmes multicœurs homogènes incluent des cœurs identiques comme certains systèmes sur puce multiprocesseurs (MP-SoC) couramment utilisés construits avec des cœurs ARM Cortex [14]. Les systèmes multicœurs hétérogènes combinent différents cœurs, comme par exemple l'architecture ARM big.LITTLE avec de « gros » processeurs avec des performances plus élevées mais gourmandes en énergie, comme l'A-15, et des « petits » processeurs avec des performances inférieures mais une meilleure efficacité énergétique, comme l'A-7 [15]. Dans cette thèse, pour faciliter l'approche (mais sans perte de généralité), nous nous concentrons sur des plateformes homogènes [16] comme par exemple le système Cortex-A53 quadricœur Arm.

#### Le modèle de tâches

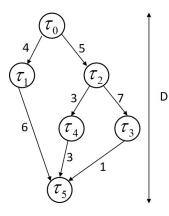

Comme introduit dans [17], une tâche fait référence à un ensemble d'activités cohérentes qui sont exécutées afin d'atteindre un but dans un domaine donné. Une application est généralement représentée par un ensemble de tâches. Selon les relations entre les tâches, deux catégories de modèles de tâches sont considérées dans cette thèse, à savoir les tâches indépendantes et les tâches dépendantes. Lorsque, dans certaines applications, des activités de calcul peuvent être exécutées dans un ordre arbitraire, celles-ci peuvent être considérées comme des tâches indépendantes. Sinon, les tâches sont *dépendantes* : elles doivent respecter les relations de précédence (ou de dépendance), c'est-à-dire qu'une tâche s'appuie sur des entrées fournies par d'autres tâches. De telles relations de dépendance entre tâches sont utilisées pour construire des graphes acycliques dirigés (directed acyclic graphs : DAG) pour décrire l'application [18]. Les DAG sont utilisés pour la représentation du calcul, de la communication et des dépendances des tâches applicatives. Un graphe DAG G consiste en une paire  $G = \{V, E\}$  où V est l'ensemble des sommets et E est l'ensemble des arêtes dirigées qui représentent la communication de données entre les tâches [19]. Un sommet cotrespond à une tâche et une arête représente une relation de dépendance. Pour deux tâches  $\tau_i$  et  $\tau_j$ , si  $(\tau_i, \tau_j) \in E$ , la tâche  $\tau_j$  dépend de la tâche  $\tau_i$  et ne peut commencer son exécution qu'une fois  $\tau_i$  ait terminé son exécution. Si une tâche  $\tau_j$  dépend de la tâche  $\tau_i$ (c'est-à-dire que la tâche  $\tau_i$  et la tâche  $\tau_j$  ont une relation de dépendance directe), alors la tâche  $\tau_i$  est appelée un *prédécesseur* de la tâche  $\tau_j$  et  $\tau_j$  est appelée un *successeur* de la tâche  $\tau_i$ . Si une tâche n'a pas de prédécesseur (successeur), elle est appelée tâche d'entrée (tâche de sortie).

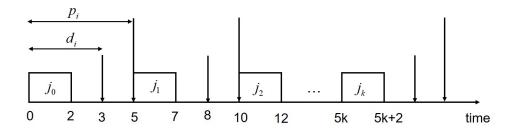

Pour fournir des garanties de synchronisation pour les systèmes temps réel durs, le WCET

doit être pris en compte lors de l'analyse et la conception du système. Le WCET d'une tâche est une estimation du temps d'exécution le plus long parmi tous les cas possibles. Le WCET d'une tâche dépend de la fréquence du processeur et des interférences dues à l'exécution parallèle de tâches sur le système multicœurs. Étant donné que la technique DVFS affecte le temps d'exécution, le WCET est donné en cycles d'exécution dans le pire des cas (Worst-Case Execution Cycle : WCEC), c'est-à-dire le nombre total de cycles CPU nécessaires dans le pire des cas, comme étudié dans [20, 21]. De plus, la date limite d'exécution est le temps avant lequel une tâche doit se terminer afin de satisfaire la contrainte temps réel du système. Dans cette thèse, nous considérons des applications de type trames, où l'exécution d'une application fonctionne de manière cyclique et où toutes les tâches de l'application doivent se terminer dans une période appelée trame [22, 23]. Les tâches sont libérées en début de trame et doivent avoir terminé leur exécution lors de la trame, ce qui détermine la date limite d'interment de l'application. Dans cette thèse, la période est considérée comme égale à la date limite globale à l'ensemble des tâches.

#### Les différents schémas de DVFS

Avec les systèmes multicœurs, la consommation d'énergie est devenue un facteur crucial, en particulier pour les systèmes avec un budget énergétique limité tels que les objets communicants alimentés par batterie ou à récupération d'énergie. En conséquence, des techniques de gestion adaptative ont été établies pour maximiser l'efficacité énergétique [24]. La gestion dynamique de la tension et de la fréquence (DVFS) est un mécanisme bien connu qui gère la consommation d'énergie dynamique en réduisant simultanément la tension et la fréquence d'alimentation du processeur, pendant l'exécution de la tâche [25, 24, 26]. La gestion de la fréquence et de la tension [27] peut être implémentée de plusieurs manières dans les plates-formes matérielles multicœurs. La première approche est la gestion globale de la fréquence et de la tension où un seul contrôleur est utilisé pour gérer la tension et la fréquence pour tous les cœurs simultanément. Par conséquent, tous les cœurs fonctionnent à la même fréquence. La deuxième approche est la gestion individuelle de la fréquence et de la tension où chaque cœur a son propre contrôleur et peut fonctionner à différents niveaux de tension et de fréquence, comme par exemple les processeurs Haswell-EP [28] et AMD Ryzen [29]. Compte tenu du coût matériel des contrôleurs, il existe des approches hybrides qui combinent une gestion globale et individuelle de la tension et de la fréquence, par exemple Ryzen 1700x [27]. Par conséquent, trois catégories de schémas DVFS peuvent exister en ce qui concerne l'attribution des tensions/fréquences aux tâches :

- DVFS au niveau tâche: L'attribution de fréquence est effectuée par tâche, c'est-à-dire que chaque tâche peut être exécutée à son propre niveau de fréquence. Les fréquences attribuées à chaque tâche sont indépendantes. Ce mécanisme DVFS est envisagé dans de nombreux travaux récents tels que [30, 31, 32, 33].

- DVFS au niveau processeur: L'attribution de fréquence est effectuée par processeur; toutes les tâches affectées à un même processeur sont exécutées avec la même fréquence.

Les fréquences attribuées aux processeurs sont indépendantes.

— DVFS au niveau système La même fréquence est affectée à tous les processeurs de la plate-forme, et la fréquence est modifiée en même temps pour tous les processeurs. Un tel schéma est appliqué par exemple dans [34, 35]

Modèle de consommation de puissance et d'énergie Dans une plate-forme multicœur compatible DVFS, la puissance consommée se compose généralement de deux parties : la puissance dynamique qui est causée par l'activité lors de l'exécution et la puissance statique due au courant de fuite [25]. La puissance statique est constante et indépendante de la tension et de la fréquence du système. Étant donné que dans cette thèse nous utilisons la gestion dynamique de la tension et de la fréquence pour gérer la consommation d'énergie, nous nous concentrons donc sur la réduction de la puissance dynamique, comme in [36] [37]. Nous adoptons un modèle de puissance largement utilisé, comme dans [25, 26, 33] :

$$P(f) = P_s + P_d = P_s + \hbar(P_{ind} + P_{dep}) \tag{1}$$

$P_s$  est la puissance statique qui est consommée pour maintenir le fonctionnement de base du circuit et qui peut être annulée lors de la mise hors tension du circuit. La puissance dynamique  $P_d$  comprend deux parties : 1) une composante de puissance consommée indépendante de la fréquence  $P_{ind}$  qui est causée par des modules périphériques comme la mémoire et des périphériques externes lorsque le système est en mode actif [26], qui peut être supprimé en mettant le système en mode veille, et 2) la puissance consommée dynamique du processeur et de tous les autres périphériques dépendant de la fréquence,  $P_{dep}$ .  $\hbar$  est un facteur qui décrit les modes du système, c'est-à-dire que lorsque  $\hbar = 1$ , le système est en mode actif et la puissance dynamique est effective, sinon lorsque  $\hbar = 0$ , le système est en veille mode et aucune puissance dynamique n'apparait.  $P_{dep}$  peut être exprimé comme  $P_{dep} = C_{eff} f^m$  où  $C_{eff}$  est la capacité de commutation effective et m est l'exposant de puissance dynamique, normalement non inférieur à 2.  $C_{eff}$ et m sont des constantes qui dépendent des caractéristiques du processeur/de la technologie. Dans cette thèse, nous nous concentrons principalement sur la puissance consommée dynamique dépendant de la fréquence, où la puissance consommée totale du système est dominée par la puissance consommée par les processeurs pour exécuter des tâches. Plusieurs schémas DVFS présentés ci-dessus sont utilisés pour ajuster la fréquence/tension afin de minimiser la puissance consommée totale du système.

Modèles de tolérance aux fautes et de fiabilité L'exécution correcte d'une application peut être menacée par plusieurs sources, telles que les rayonnements [38] et les interférences électromagnétiques. Une *faute* est un défaut physique ou une imperfection qui se produit dans un composant matériel ou logiciel [39]. Une faute peut entraîner un écart par rapport à l'exactitude ou à la précision du calcul, qui devient alors une *erreur*. Une *défaillance* est un écart par rapport à la valeur réelle et attendue. Un système est dit défaillant si le service qu'il fournit à l'utilisateur s'écarte de la conformité à la spécification pendant une période de temps donnée [40]. En général, les fautes sont les sources d'erreurs et les erreurs les sources de défaillance [39]. Les fautes matérielles peuvent généralement être classés en deux types : fautes permanentes et fautes transitoires en fonction de la durée de la faute. Pendant la durée de vie normale d'un système, les fautes transitoires se produisent plus fréquemment que les fautes permanentes, et sont donc considérées comme les principales menaces pour la bonne exécution des applications [32, 41]. En raison de la réduction de la taille des transistors, les systèmes sont devenus plus sensibles aux fautes transitoires [42]. Dans cette thèse, nous considérons les fautes transitoires. Une faute transitoire reste active pendant une courte période. Les causes des fautes transitoires sont principalement environnementales, telles que les particules (un impact de neutrons de rayons cosmiques ou de particules  $\alpha$ ), les décharges électrostatiques, les baisses de puissance électrique, la surchauffe ou les chocs mécaniques. Pour les systèmes compatibles DVFS, un niveau de tension/fréquence faible est plus susceptible de provoquer une faute transitoire. Le modèle de fautes transitoires suit une distribution de Poisson avec un taux de fautes moyen  $\lambda$  [36] où le taux de faute est le nombre de fautes attendu par unité de temps [39]. Pour les systèmes compatibles DVFS avec L paires de niveaux de tension/fréquence  $\{(v_1, f_1), ..., (v_L, f_L)\}$ , le taux de faute à la fréquence  $f_l$  suit une distribution exponentielle :

$$\lambda(f_l) = \lambda_0 \times 10^{d \frac{f_{max} - f_l}{f_{max} - f_{min}}} \tag{2}$$

où  $\lambda_0$  est le taux de faute moyen à la fréquence maximale, d (appelé facteur de sensibilité) est une constante, utilisée pour mesurer la sensibilité du taux de faute à la gestion dynamique de la tension/fréquence.  $f_{max}$  et  $f_{min}$  sont respectivement la fréquence maximale et minimale dans les L niveaux de tension/fréquence. La fiabilité de l'exécution d'une tâche est la probabilité d'exécuter la tâche sans faute. Lors de l'exécution d'une application, selon la loi de défaillance exponentielle [39], la fiabilité d'une exécution varie de façon exponentielle en fonction de son temps d'exécution comme

$$R(f_l) = e^{-\lambda(f_l) \times t} \tag{3}$$

où t est la durée d'exécution et qui est inversement proportionnelle à la fréquence. L'exécution d'une application est d'autant plus fiable que la fréquence augmente.

En pratique, il est impossible de construire un système parfait sans apparition de fautes, en particulier avec la diminution de la technologique [43]. Pour améliorer la fiabilité d'un système, plusieurs approches utilisent une fréquence élevée pour obtenir une grande fiabilité pour l'exécution de l'application. Mais avec l'augmentation de la complexité d'un système, la fiabilité du système diminue considérablement même en appliquant la fréquence la plus élevée pour exécuter des tâches. Par exemple, en supposant que la fiabilité d'une tâche est très élevée, par exemple 99,999% à fréquence maximale, lorsque le système comporte 10 tâches, la fiabilité du système après exécution de ces 10 tâches est de 99,99% ; lorsque le système a 20 tâches, cette valeur diminue à 99,98%, et lorsque le système a 100 tâches, la valeur est de 99,99%. Pour un système avec des exigences de fiabilité élevées, l'exigence de fiabilité ne peut pas être satisfaite en utilisant uniquement la haute fréquence. La *tolérance aux fautes* est la capacité d'un système à continuer à exécuter ses fonctions prévues en présence de fautes.

Il existe différentes approches pour implémenter la tolérance aux fautes. Dans cette thèse, nous considérons une technique de réplication active pour implémenter la tolérance aux fautes. La réplication de tâches [24, 32, 37, 44, 45, 46, 47] est une technique largement adoptée pour tolérer les fautes transitoires. Elle est basée sur la redondance spatiale : plusieurs copies d'une tâche sont exécutées sur différents cœurs. Il existe deux approches principales pour assurer la réplication. Avec la *réplication passive*, chaque tâche est répliquée plusieurs fois et ces répliques sont exécutées sur différents processeurs [24, 32, 37, 45]. Ce faisant, il est peu probable que toutes les répliques d'une tâche échouent à l'exécution. Un vote majoritaire est opérée à la fin de l'exécution afin de déterminer la valeur du résultat. Avec la *réplication passive* [46, 47], chaque tâche a une copie principale et une copie de sauvegarde. La copie de sauvegarde n'est activée que lorsque la copie principale échoue dans son exécution. Un dispositif de détection d'erreur permet de savoir à la fin de l'exécution si la copie s'est exécutée correctement ou non.

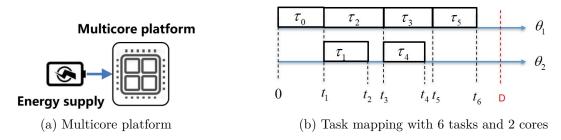

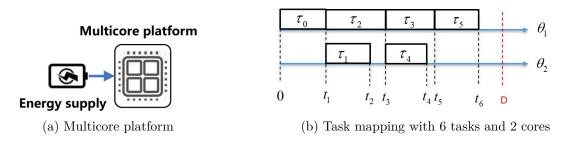

Ordonnancement temps-réel de tâches dans les systèmes multicœurs Dans un système multicœur, étant donné une application composée de plusieurs tâches, l'ordonnancement tempsréel de tâches s'attache à résoudre en fait deux problèmes : 1) l'allocation de tâches, qui décide de l'allocation tâche-cœur (sur que cœur est exécuté quelle tâche); 2) l'ordonnancement des  $t\hat{a}ches$  proprement dit, qui est l'affectation temporelle des tâches (quand une tâche commence à s'exécuter). Dans cette thèse, nous effectuons l'ordonnancement des tâches au moment de la compilation, c'est ce qu'on appelle un ordonnancement statique. Les systèmes temps réel, tels que la robotique, les applications automobiles et les systèmes de contrôle de vol, sont des systèmes informatiques qui doivent réagir dans des délais précis aux événements de l'environnement [22]. Comme nous nous concentrons sur les systèmes temps réel durs, l'exactitude de la sortie du système dépend non seulement du résultat fonctionnel du calcul, mais également du moment auquel les résultats sont produits [32]. La figure 1 illustre un ordonnancement de tâches sur une plate-forme multicœur. En supposant qu'il y a deux cœurs, les six tâches et que la date limite globale est D, l'allocation tâche-cœur est obtenue en affectant les tâches 0, 2, 3, 5 au cœur 1 et les tâches 1,4 au cœur 2. Les dates de début de chaque tâche sont  $\{0, t_1, t_3, t_5\}$ . La contrainte de temps est satisfaite dans cet ordonnancement car l'heure de fin d'exécution de la tâche la plus tardive ne dépasse pas D.

La plupart des cœurs modernes prennent en charge une large gamme de tensions et de

Figure 1: Ordonnancement de tâches sur système multicœur.

fréquences [22] gérée par DVFS. La gestion dynamique de la tension/fréquence a un impact important sur la consommation d'énergie, la fiabilité et la vitesse d'exécution. Malheureusement, les effets/conséquences sont généralement contradictoires. Par exemple, lorsqu'une fréquence plus basse est utilisée, le coût énergétique peut être diminué, mais cela a un impact négatif sur la fiabilité et entraîne également des temps d'exécution plus longs. Généralement avec la diminution de la consommation d'énergie, la qualité d'exécution de l'application se dégrade. Avec l'augmentation de la taille des applications, l'allocation et l'ordonnancement d'un ensemble de tâches à un groupe de cœurs sous plusieurs contraintes, telles que le coût énergétique, les performances temporelles, la fiabilité, sont devenues un défi majeur dans les architectures temps réel multicœurs modernes. Par conséquent, il est intéressant d'étudier des algorithmes d'ordonnancement de tâches appropriés qui permettent d'optimiser le compromis entre fiabilité, vitesse d'exécution et efficacité énergétique.

### Motivations et contributions

La fiabilité et la consommation d'énergie sont devenues deux préoccupations majeures dans les systèmes informatiques modernes. Bien que la tolérance aux fautes et la gestion de l'énergie aient été largement étudiées, la cogestion de la fiabilité du système et de l'efficacité énergétique n'a été abordée que récemment. Les approches existantes pour les plates-formes multicœurs considèrent généralement que l'allocation des tâches est donnée à l'avance ou qu'il est fixe, lors de l'exploration de la marge de temps disponible pour l'ordonnancement des tâches. Le couplage complexe entre les variables d'optimisation de l'ordonnancement des tâches et l'affectation de la tension et de la fréquence empêche les algorithmes d'atteindre la solution optimale. Par conséquent, des méthodes sous-optimales sont généralement proposées sur la base de 1) l'approximation/relaxation du problème et 2) l'utilisation d'heuristiques. Par rapport aux approches existantes, la thèse se concentre sur la conception de nouvelles méthodologies pour résoudre efficacement le problème de l'exécution de tâches sur des plates-formes multicœurs en abordant conjointement ces facteurs.

Dans cette thèse, nous nous intéressons à combiner le DVFS et des techniques de tolérance

aux fautes pour décider de l'exécution de l'application sur des architectures multicœurs et exploiter l'impact de trois schémas de DVFS représentatifs des schémas DVFS existant dans les plateformes multicœurs récentes. Tout d'abord, nous concevons des méthodologies pour l'ordonnancement des tâches sur des plates-formes multicœurs qui fournissent des solutions optimales pour les modèles de tâches indépendants et dépendants et pour les trois schémas de DVFS. Ensuite, pour faire face au temps de calcul élevé nécessaire pour obtenir des solutions optimales, nous proposons un ensemble d'heuristiques qui fournissent des solutions quasi optimales avec un temps de calcul réduit. Lors de l'analyse expérimentale, nous avons utilisé des graphes de tâches générés aléatoirement et des graphes de tâches d'applications réelles pour évaluer le comportement des approches proposées.

Pour mieux comprendre les contributions de cette thèse, nous posons les questions suivantes :

# 1. Que comprend l'ordonnancement des tâches dans les problèmes étudiés dans cette thèse ?

Nous avons étudié deux groupes de problèmes d'ordonnancement des tâches : le premier groupe concerne les tâches indépendantes. L'objectif des problèmes étudiés est de minimiser la consommation d'énergie sous des contraintes de temps réel et de fiabilité, en déterminant simultanément l'allocation des tâches, la duplication des tâches et l'affectation des fréquences. Le deuxième groupe concerne les tâches dépendantes ayant le même objectif sous des contraintes de temps réel, de fiabilité et de dépendance des tâches en déterminant simultanément l'allocation des tâches, l'ordonnancement des tâches (date de début d'exécution de chaque tâche), la duplication des tâches et l'affectation des fréquences.

## 2. Comment obtenir les solutions optimales pour les problèmes d'ordonnancement des tâches étudiés sachant qu'ils sont connus comme étant des problèmes NPdifficiles ?

En général, il est compliqué d'obtenir des solutions optimales pour les problèmes d'ordonnancement de tâches sur des plates-formes multicœurs car elles sont NP-difficiles. Les problèmes étudiés sont d'abord formulés sous forme de programmation non linéaire mixte en nombres entiers (MINLP), puis une méthode de remplacement de variables est utilisée pour transformer de manière équivalente les problèmes MINLP sous forme de problèmes en programmation linéaire mixte en nombres entiers (MILP) et qui peuvent être résolus avec des outils de type solveur, tels que Gurobi ou Cplex. Cette partie est présentée au Chapitre 3.

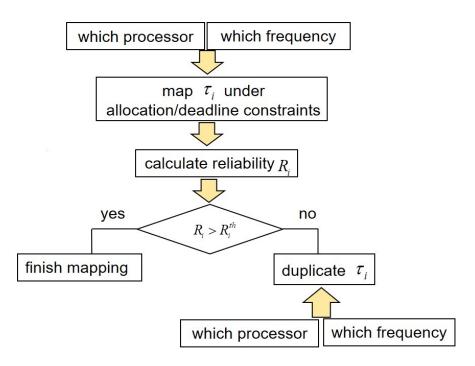

## 3. Quelles sont les idées centrales des approches heuristiques proposées pour les problèmes étudiés ?

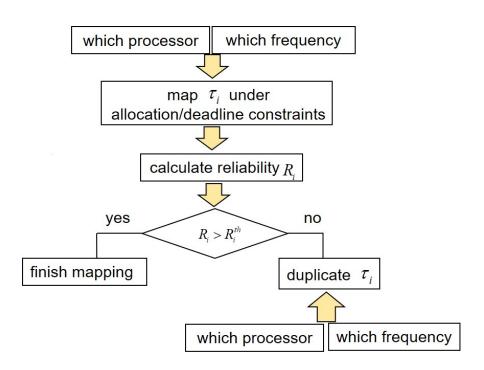

Afin de faire face à des temps de calcul longs pour obtenir les solutions optimales, un ensemble d'heuristiques est proposé. Le principe des heuristiques proposées consiste en deux phases : une phase d'élagage et une phase d'ordonnancement. La phase d'élagage ne maintient que les config-

#### LIST OF TABLES

urations de tâches qui satisfont les contraintes de fiabilité. Ensuite, la phase d'ordonnancement minimise l'énergie consommée sous contraintes de temps réel pour les tâches indépendantes et sous contraintes de temps réel et de précédence pour les tâches dépendantes. La phase d'élagage exclut les solutions inutiles dans l'espace des solutions et la phase d'ordonnancement utilise les solutions restantes pour rechercher les solutions quasi optimales aux les problèmes étudiés.

Dans cette thèse, nous avons considéré et évalué trois niveaux DVFS comme expliqué dans la section 3.2. Nous avons proposé une série de méthodologies d'ordonnancement des tâches qui peuvent être classées en deux groupes : 1) les algorithmes optimaux qui fournissent les solutions optimales, et 2) les algorithmes heuristiques qui fournissent des solutions quasi optimales, mais nécessitant beaucoup moins de calculs (voir figure 2). La figure 3 décrit l'idée générale de l'approche proposée RAFTM (Reliability-Aware Fault-Tolerant Task Mapping) basée sur la technique de duplication partielle pour répondre à la tolérance aux fautes. Dans l'approche proposée, nous fixons à deux le nombre maximal de répliques pour chaque tâche et sélectionnons une partie de l'ensemble de tâches pour effectuer la duplication.

Tout d'abord, les algorithmes optimaux pour les modèles de tâches indépendants et dépendants sous trois schémas de DVFS sont étudiés au chapitre 3, en utilisant une méthode de remplacement de variables pour transformer de manière équivalente les problèmes MINLP originaux dans les formes MILP, puisque les problèmes MILP peuvent être résolus à l'aide de solveurs d'optimisation. Cependant, le temps pour obtenir une solution avec de telles approches optimales devient rapidement trop important à moins que l'application ait très peu de tâches. Nous étendons donc l'approche proposée à des algorithmes heuristiques au Chapitre 4. En nous concentrant sur chaque schéma de DVFS, nous proposons les heuristiques correspondantes pour les modèles de tâches indépendantes et dépendantes. Enfin, nous menons un grand nombre d'expériences pour des graphes de tâches générés aléatoirement et pour des graphes de tâches d'applications réelles afin d'évaluer les approches proposées. Pour des solutions optimales, nous comparons nos approches avec deux autres approches de l'état d l'art. Les résultats expérimentaux montrent que les approches proposées permettent de gagner en énergie consommée et en capacité d'obtenir des solutions réalisables. Pour les approches basées sur des heuristiques, nous comparons d'abord les heuristiques proposées à des solutions optimales pour analyser l'écart de performance. De plus, des expériences sont réalisées pour évaluer les algorithmes heuristiques proposés par rapport à deux autres algorithmes heuristiques de l'état d l'art. Nos algorithmes heuristiques donnent des résultats très proches des algorithmes optimaux tout en ayant une complexité de calcul faible, et surpassent les heuristiques de l'état de l'art en matière d'énergie consommée et de capacité d'obtention de solutions réalisables.

| Optimal algorithms |                               |         | Heuristics algorithms |                   |

|--------------------|-------------------------------|---------|-----------------------|-------------------|

| TL-DVFS            | Independent tasks[Cui1][Cui3] |         |                       | Independent tasks |

| TL-DVF3            | Dependent tasks[Cui2]         | TL-DVFS | Dependent tasks[Cui4] |                   |

|                    |                               |         |                       |                   |

| PL-DVFS            | Independent tasks[Cui3]       | PL-DVFS | Independent tasks     |                   |

| 12-0410            | Dependent tasks[Cui2]         |         | PL-DVI 3              | Dependent tasks   |

|                    |                               |         |                       |                   |

| SL-DVFS            | Independent tasks[Cui3]       |         |                       | Independent tasks |

| 31-07-5            | Dependent tasks[Cui2]         | SL-DVFS |                       | Dependent tasks   |

|                    |                               |         |                       |                   |

Figure 2: Approches proposées d'ordonnancement des tâches pour différents niveaux de DVFS et différents modèles de tâches.

Figure 3: Présentation générale de l'approche proposée d'ordonnancement des tâches tolérant aux fautes et tenant compte de la fiabilité

## Organisation du document

Le mémoire de thèse est organisé de la manière suivante:

- Dans le chapitre 1, nous introduisons brièvement les concepts de base qui seront utilisés dans le reste du document. Dans un premier temps, nous présentons le modèle de plates-formes multicœurs. Ensuite, nous décrivons brièvement les deux modèles de tâches qui sont utilisés dans les problèmes étudiés. Comme l'objectif de la thèse est de minimiser la consommation d'énergie, nous introduisons le modèle de puissance/énergie et les trois schémas de DVFS utilisés. De plus, la thèse portant sur la fiabilité, nous présentons les principales sources de fautes et les modèles de fautes. Enfin, nous introduisons plusieurs techniques de tolérance aux fautes en nous concentrant sur les approches de réplication de tâches.

- Dans le chapitre 2, nous présentons les travaux de l'état de l'art liés à notre sujet. Trois catégories de problèmes d'ordonnancement des tâches sont introduites en fonction de l'objectif du problème étudié. La première catégorie vise à minimiser la consommation d'énergie. Plusieurs approches d'ordonnancement des tâches sans et avec tolérance aux fautes sont brièvement présentées. La deuxième catégorie vise la maximisation de la fiabilité. Ensuite, la troisième catégorie se concentre sur la minimisation de la durée d'exécution de l'application. Enfin, nous concluons avec les limites des approches d'ordonnancement des tâches de l'état de l'art.

- Dans le chapitre 3, nous présentons d'abord le problème étudié dans cette thèse pour les tâches indépendantes et dépendantes sous trois schémas de DVFS en tant que problèmes MINLP. Ensuite, nous décrivons comment transformer de manière équivalente les formulations MINLP en formulations MILP. Pour l'évaluation expérimentale, les solutions optimales sont obtenues à l'aide du solveur Gurobi. Les résultats montrent que les approches optimales proposées permettent d'obtenir une consommation d'énergie plus faible et trouvent des solutions lorsque d'autres approches de l'état de l'art ne parviennent pas à obtenir des solutions pour le problème traité.

- Dans le chapitre 4, nous considérons les mêmes problèmes étudiés qu'au chapitre 3 et nous proposons des heuristiques pour obtenir des solutions quasi-optimales avec une complexité de calcul raisonnable. Des résultats expérimentaux utilisant divers graphes de tâches générées aléatoirement ainsi que provenant d'applications réelles sont présentés pour évaluer les heuristiques proposées en comparaison des solutions optimales et d'heuristiques de l'état de l'art.

- Dans le chapitre conclusion, nous concluons notre travail de thèse par un résumé des travaux effectués et nous proposons des perspectives à ces travaux.

## INTRODUCTION

## Context

The safety-critical domain industries usually consist of systems where guarantees must be provided on safety and reliability for the critical applications, implying both high fault tolerance and hard real-time constraints [1]. For example, avionics systems consist of applications with high Design Assurance Levels (DAL) [2] operating in high altitudes exposed to radiation. Space systems consist of navigation control applications operating in outer space with extreme particle and high-energy electromagnetic radiation. Automotive systems have applications, among others, in the same wheel sensor for stability control and for the acceleration regulation while they suffer from alpha particles, high temperature peaks and electromagnetic interferences [3]. These natural and technical stimuli are the source of faults that impact the system functionality [4]. Furthermore, within last thirty years, the code size of avionics, space and automotive applications has significantly increased [5]. These systems face exponential growth in performance requirements, whereas future automotive and aerospace applications will require higher performance computing resources [1].

To deal with the increasing performance demands, the consumer market has shifted towards multicore architectures, due to power consumption and heat dissipation limits of single processors [1]. Generally speaking, multicores provide a Space, Weight and Power reductions (SWaP) and massive computing capabilities compared with single core processors, while they can integrate several applications on the same platform [6]. However, two main scientific challenges raised by the use of multicores.

The first challenge is high energy consumption which has become one of the biggest obstacles to develop green and high performance computing systems, especially for systems with limited energy budget, such as battery powered or energy-harvesting Internet of Things (IoT) devices. Smartphones use heterogeneous multicore architectures, such as big.LITTLE [7], which consists of performance-optimized big cores and energy-optimized little cores with a single Instruction Set Architecture (ISA) [8]. Embedded boards for Internet of Thing (IoT), such as Raspberry Pi, Odroid, Edison, Jetson, and Artik also provide multiple cores [9, 10, 11]. The use of multiple cores supports efficiently the IoT services, but the increase in the number of cores puts pressure on the energy resource of the device, since the power and energy consumptions are increased [48]. Hence, multicore platforms have been enhanced with the capability of scaling their voltage and frequency (Dynamic Voltage and Frequency Scaling - DVFS) during execution to balance system performance and energy savings.

The second challenge is that the multicore system itself is susceptible to faults due to the nature of electronic systems. Combined with the reduction of the transistor size and the technology, multicore systems are becoming more and more sensible to the operating conditions and to the environmental impact [12]. In electronic systems, the variation on the threshold voltage depends on the transistor width, whereas voids or small cracks in the wiring lead to close or open source problems. The current or voltage activity and hot spots are inevitable during the system operation, but they cause electromigration, Bias Temperature Instability (BTI) and crosstalk, which are sources of faults. To improve the multicore reliability, either radiation-hardened processors are used or the system is replicated [13]. The former solution develops systems with limited computation capabilities and it requires a difficult-to-find design expertise, which combines digital and analogue electronics with semiconductor physics. The latter solution has high cost and energy consumption. To reduce the cost while providing reliability, the resources replication and the system oversizing has to be avoided, whenever possible.

Taking the above two challenges into consideration, in order to fully exploit the features of multicore systems, while obtaining both reliable and energy efficient application execution meeting system specifications, methods are required to decide the efficient execution of the tasks on multicores with scalable operating features. The way that tasks are executed on a platform is decided by several factors. The first factor is the *task mapping*, which refers to both the task allocation (on which processor each task is executed) and the task scheduling (at which time each task starts its execution). The second factor is the decision of the *voltage and frequency assignment* of the processor when it runs a specific task, which determines the execution time of the task. For critical applications, Worst Case Execution Time (WCET) bounds are used since they are required for guarantees regarding reliability and correct functional behaviour.

### Motivation and Goals