## Cryptographic primitives adapted to connected car requirements

Etienne Tehrani

### ► To cite this version:

Etienne Tehrani. Cryptographic primitives adapted to connected car requirements. Cryptography and Security [cs.CR]. Institut Polytechnique de Paris, 2022. English. NNT: 2022IPPAT028. tel-03788940

## HAL Id: tel-03788940 https://theses.hal.science/tel-03788940

Submitted on 27 Sep 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Cryptographic Primitives Adapted to Connected Car Requirements

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à Télécom Paris

École doctorale n°626 École doctorale de l'Institut Polytechnique de Paris (EDIPP) Spécialité de doctorat: Information, Communications, Électronique

Thèse présentée et soutenue à Palaiseau, le 8 Juillet 2022, par

### **Etienne Tehrani**

Composition du Jury :

| Lilian Bossuet<br>Professur, Université Jean Monnet (Laboratoire Hubert Curien) | Président             |

|---------------------------------------------------------------------------------|-----------------------|

| Nele Mentens<br>Professeur Associée, Katholieke Universiteit Leuven (COSIC)     | Rapporteuse           |

| Guy Gogniat<br>Professeur, Université Bretagne Sud (STICC)                      | Rapporteur            |

| Lilian Bossuet<br>Professur, Université Jean Monnet (Laboratoire Hubert Curien) | Examinateur           |

| Karine Heydemann<br>Maîtresse de Conférence, Sorbonne Université (LIP6)         | Examinatrice          |

| Sylvain Guilley<br>Professeur, Télécome Paris (LTCI)                            | Examinateur           |

| Jean-Luc Danger<br>Directeur d'études, Télécom Paris (LTCI)                     | Directeur de thèse    |

| Tarik Graba<br>Maître de conférences, Télécom Paris (LTCI)                      | Co-directeur de thèse |

#### Abstract

Communications are one of the key functions in future vehicles. They are developing at high speed and require a high degree of security. Whether intra- or extra-vehicular, reliable communications are imperative in order to ensure rapid decision-making according to the environment. Nevertheless, it can be intercepted and even modified by potential attackers and therefore requires the use of protections. Cryptography is an obvious answer to secure communications, but the algorithms used today seem inadequate in terms of complexity and latency, especially to satisfy the physical and economic constraints of large-scale embedded systems. Although the automotive industry generally relies on standards, it is not uncommon for some players to prefer the use of ad hoc technologies that are more adapted to cost, performance and safety constraints. As long as the communication is internal, a standard is not necessary, but with inter-vehicle communications, the absence of a standard imposes a great versatility on the vehicle to ensure the compatibility of the communications, while respecting the constraints of complexity and latency. A second emerging problem specific to embedded systems is the protection against attacks, especially physical attacks due to the fact that the system can be accessed by the user. These attacks are formidable because they can bypass the mathematical protection of cryptographic algorithms. This is the case of the attacks by side-channels which exploit the leaks related to the activity of calculation by the means of consumption or electromagnetic radiation. It is therefore essential to take this aspect into account in the implementation of encryption algorithms to obtain a high level of security.

Within the context of the "Connected Cars and CyberSecurity (C3S)" Chair, the main objectives of the thesis are to study the feasibility of implementing a wide variety of symmetric lightweight encryption algorithms and their protection. More precisely, the goal is to implement several families of algorithms on a hardware that is surface constrained and that would have good performance in terms of physical security and latency. An optimal solution is to have an agile implementation, able to quickly execute different lightweight encryption algorithms, using few resources and guaranteeing protection against physical attacks. The implementation can be fully hardware-based or a dedicated processor implementation taking advantage of the presence of on-board Electronic Control Units. To ensure the best implementation compromise, this last architecture can start from a modification of the instruction set of a RISC processor to satisfy the agility property of light cryptography algorithms. This agility guarantees a great flexibility, a common protection base for the algorithms, for a cost comparable to that of a standard microcontroller.

We have studied many encryption algorithms and have proposed a first approach with a fully hardware architecture and a second approach with a dedicated processor in order to efficiently implement Lightweight Cryptography in a constrained embedded system. Our main contributions can be summarized as follows:

- Classification of Lightweight Encryption Algorithms by Block

- Configurable hardware implementation dedicated to the acceleration of the execution of Lightweight Block Ciphers of the SPN type

- RISC-V hardware extension dedicated to accelerating the execution of Lightweight Block Ciphers

- RISC-V hardware extension dedicated to the protection of Lightweight Block Ciphers against Auxiliary Channel Attacks

Each contribution is experimentally supported by tests to evaluate hardware cost, performance, latency and physical security against auxiliary channel attacks.

# Contents

| Со | ontents                                                                                                                                                                                                                                             | iii                                                   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Li | st of Figures                                                                                                                                                                                                                                       | v                                                     |

| Li | st of Tables                                                                                                                                                                                                                                        | vii                                                   |

| Ac | cronyms                                                                                                                                                                                                                                             | ix                                                    |

| Ré | ésumé en français                                                                                                                                                                                                                                   | xi                                                    |

| 1  | Introduction1.1Motivation1.2Contributions1.3Organisation                                                                                                                                                                                            | <b>1</b><br>1<br>2<br>2                               |

| 2  | <ul> <li>2.6 Side-Channel Attacks</li> <li>2.7 Introduction to Countermeasures</li> <li>2.8 RISC-V</li> </ul>                                                                                                                                       | <b>3</b><br>4<br>6<br>9<br>12<br>15<br>21<br>24<br>33 |

| 3  | <ul> <li>3.1 Implementation</li> <li>3.2 Configuration</li> <li>3.3 Instruction ordering</li> <li>3.4 K Module: The Key Addition</li> <li>3.5 S Module: The S-Box</li> <li>3.6 P Module: The P-Layer</li> <li>3.7 Implementation Results</li> </ul> | <b>35</b><br>36<br>37<br>37<br>38<br>38<br>43<br>45   |

## 4 Dedicated Processor Implementation of the RISC-V for LBC Agility 47

|    | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | Classification of Lightweight Block Ciphers                                                                                                                                                                                                                                   | 50<br>50<br>. 51<br>62<br>63<br>. 67 |

|----|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 5  | <b>Pro</b><br>5.1<br>5.2<br>5.3<br>5.4 | tected Processor Against Side-Channel Attacks         Proposed ISA Extension for Protection         Side-Channel Security Evaluation         Security Evaluation of Non-Protected Implementations         Security Evaluation of Protected Implementations         Conclusion | <b>73</b><br>73<br>80<br>. 84<br>89  |

| -  | 6.1<br>6.2<br>6.3<br>6.4               | nclusion         Results of an Agile Implementation         Results of an Agile Protection Against SCA         Perspectives         List of Scientific Productions                                                                                                            | 98<br>99<br>100                      |

| Bi | blio                                   | graphy                                                                                                                                                                                                                                                                        | 101                                  |

| Α  | Lig                                    | htweight Block Ciphers                                                                                                                                                                                                                                                        | 109                                  |

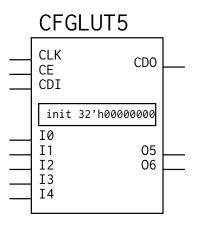

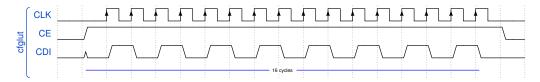

| В  |                                        | <b>figurable S-boxes implementation for Xilinx FPGAs</b><br>Xilinx Dynamically Reconfigurable Look-Up Table (LUT) primitives                                                                                                                                                  | <b>135</b><br>136                    |

# List of Figures

| 1          | Architecture Entièrement Matérielle pour les Algorithmes de Chiffre-                                       |

|------------|------------------------------------------------------------------------------------------------------------|

|            | ment de Type SPN                                                                                           |

| 2          | La Multiplication de Matrices Génériques                                                                   |

| 3          | L'Uniformisation des Tailles de Matrices                                                                   |

| 4          | L'Instruction de Permutation au Niveau Bit                                                                 |

| 5          | Sortie 64-bit Utilisant Deux Instructions RISC-V 32-bit                                                    |

| 6          | 256-bit de Configuration d'une Matrice $64 \times 64$ pour NMAT_D xxi                                      |

| 7          | The NMAT_D Instruction                                                                                     |

| 8          | The NMAT_D multiplication datapath                                                                         |

| 9          | VexRisc Platform                                                                                           |

| 10         | La NICV de PRESENT pour 32768 traces                                                                       |

| 11         | La Guessing Entropy de l'Exécution de PRESENT pour jusqu'à 30000                                           |

|            | Traces de Consommation Énergétique                                                                         |

| 12         | L'Etape de Confusion avec RSM                                                                              |

| 13         | Les Instructions RISC-V de Type R                                                                          |

| 14         | La Guessing Entropy de l'Exécution de PRESENT Protégé pour jusqu'à                                         |

|            | 1 million de Traces de Consommation Énergétique                                                            |

| 2.1        | Generic Feistel Round                                                                                      |

| 2.2        | Generic SPN Round                                                                                          |

| 2.3        | The $\alpha$ - reflective Property                                                                         |

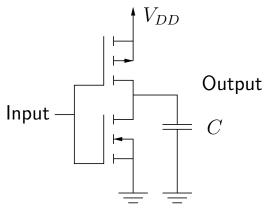

| 2.4        | A CMOS cell                                                                                                |

| 2.5        | The RSM Datapath on a Generic LBC                                                                          |

| 2.6        | The PULP Family (taken from the PULP website [63])                                                         |

| 2.7        | The Plug-in Insertion in the VexRiscv Pipeline                                                             |

|            |                                                                                                            |

| 3.1        | Fully Hardware Agile Architecture for SPN Ciphers    36                                                    |

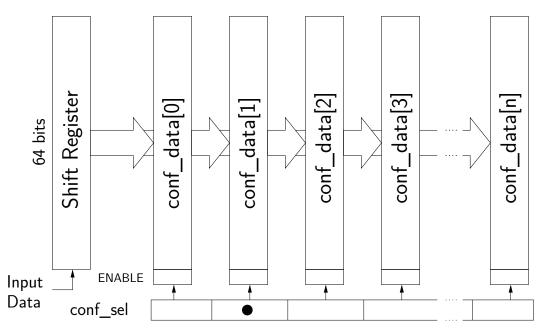

| 3.2        | The Configuration Scheme                                                                                   |

| 3.3        | The Agile Matrix Multiplication    38                                                                      |

| 3.4        | Turning the Useful Information of a $64 	imes 64$ Prince-type Matrix into a                                |

|            | $16 \times 16$ Matrix                                                                                      |

| 3.5        | Turning the Useful Information of a $4 \times 4$ Matrix into a $16 \times 16$ Matrix 40                    |

| 3.6        | The Agile Bit-Level Permutation Instruction                                                                |

|            | •                                                                                                          |

| 3.7<br>3.8 | Optimised $4 \times 4$ Crossbar-Like Module, The $4 \times 4$ Banyan Switch41Bit-level permutation layer42 |

|                                 | Nibble-level permutation layer                                                                               | 43<br>45          |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------|

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | 64-bit Output Using Two 32-bit RISC-V Instructions                                                           |                   |

| 4.7<br>4.8<br>4.9               | $\begin{array}{c} \mbox{tations} & \dots & $ |                   |

| 5.1<br>5.2<br>5.3<br>5.4        | The RSM Confusion Step                                                                                       | 75<br>76<br>82    |

| 5.5                             | 32768 Power Traces                                                                                           | . 84<br>85        |

| 5.6                             | Guessing Entropy of a Non-protected Execution of PRINCE, up to 32768<br>Power Traces                         | 86                |

| 5.7<br>5.8                      | Guessing Entropy of a Non-protected Execution of Midori, up to 32768<br>Power Traces                         | . 87              |

| 5.9                             | Power Traces                                                                                                 | 88                |

| 5.10                            | power traces                                                                                                 | 90<br>. 91        |

| 5.11                            | power traces                                                                                                 | . 91<br>92        |

| 5.12                            | Guessing Entropy of a Protected Execution of Midori, up to 2 million power traces                            | 93                |

| A.2                             | The Piccolo Round Permutation " $RP$ " Function                                                              | 113<br>113<br>128 |

# List of Tables

| 1      | 1 8                                                                                                                                       | xvi   |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2<br>3 | Les Différents Niveaux d'Agilité de l'Architecture                                                                                        | xvi   |

| 5      |                                                                                                                                           | vii   |

| 4      |                                                                                                                                           | viii  |

| 5      |                                                                                                                                           | xiii  |

| 6      | Nombre d'Instructions par Algorithme en fonction de l'ISA                                                                                 | xiv   |

| 7      | Coût Matériel de l'Implémentation Générique Protégée                                                                                      | xviii |

| 2.1    | Summary of properties of Lightweight Block Ciphers                                                                                        | 14    |

| 2.2    | Base Variants of the RISC-V ISA                                                                                                           | 24    |

| 2.3    | RISC-V Foundation Standardized Extension of the RISC-V ISA                                                                                | 25    |

| 2.4    | RISC-V ISA Variation Supported By the T-HEAD 9 Series Chips                                                                               | 28    |

| 2.5    | Synthesis Results of Different Cores at Different Working Frequencies .                                                                   | 31    |

| 3.1    | Module Ordering for LBCs                                                                                                                  | 37    |

| 3.2    | Cost of Architecture's Sub-Parts for the Level of Agility <b>C</b>                                                                        | 44    |

| 3.3    | Different Agility Levels of the Architecture                                                                                              | 44    |

| 3.4    |                                                                                                                                           | 4 -   |

|        | rithms it can implement                                                                                                                   | 45    |

| 4.1    | Classification of Lightweight Block Ciphers                                                                                               | 49    |

| 4.2    | Instructions Used by Each Algorithm                                                                                                       | 54    |

| 4.3    |                                                                                                                                           |       |

|        | Implementations                                                                                                                           | 58    |

| 4.4    | Comparison of the Number of Executed Instructions in One Round be-<br>tween the Non-Accelerated Ciphers and the Theoretically Accelerated |       |

|        | Cipher                                                                                                                                    | 63    |

| 4.5    | Resource Usage Overhead for the Additional Instructions                                                                                   | 68    |

| 4.6    | Resource Usage Overhead for Lightweight Block Ciphers                                                                                     | 68    |

| 4.7    | Instruction Count for Ciphers According to the ISA Used                                                                                   | 69    |

| 4.8    | Theoretical Instruction Count with Hand-Written Assembly Code                                                                             | 70    |

|        | Resource Usage Overhead for the Agile Protected Implementation $\ . \ .$                                                                  | 79    |

| 5.2    | Instruction Count for Execution of Ciphers using Base RISC-V ISA and                                                                      |       |

|        | ProtLBC-ISA                                                                                                                               | 80    |

| A.1 The S-Box Table of the Gamma Function of NOEKEON |

|------------------------------------------------------|

| A.2 The S-Box Table of the F Function of Piccolo     |

| A.3 The S-Box Table of LED                           |

| A.4 The S-Box Tables of GOST                         |

| A.5 The S-Box Table of Rectangle                     |

| A.6 The S-Box Table of PRESENT                       |

| A.7 The PRESENT Permutation Table                    |

| A.8 The S-Box Table of GIFT                          |

| A.9 The GIFT Permutation Table                       |

| A.10The S-Box Tables of PRINCE                       |

| A.11The S-Box and Permutation Tables of TWINE        |

| A.12The S-Box Table of SKINNY                        |

| A.13The S-Box Table of Midori                        |

| A.14The S-Box Table of MANTIS                        |

# Acronyms

| $\oplus$    | The XOR instruction                                                   |

|-------------|-----------------------------------------------------------------------|

|             | The addition instruction                                              |

| AES         | Advanced Encryption Standard                                          |

| AND         | The binary AND instruction                                            |

| CAN         | Control Area Network                                                  |

| CPA         | Correlation Power Analysis                                            |

| CSR         | Control Status Register                                               |

| DES         | Data Encryption Stadard                                               |

| DPA         | Differential Power Analysis                                           |

| FF          | Flip Flop                                                             |

| FPGA        | Field Programmable Gate Array                                         |

| GE          | Guessing Entropy                                                      |

| GEN         | Generalised Feistel Network                                           |

| HD          | Hamming Distance Model                                                |

| HW          | Hamming Weight Model                                                  |

| ISA         | Instruction Set Architecture                                          |

| LBC         | Lightweight Block Cipher                                              |

| LBC-ISA     | Lightweight Block Cipher Extension of the Istruction Set Architecture |

| LUT         | Look-Up Table                                                         |

| LWC         | Lightweight Cryptography                                              |

| NICV        | Normalized Inter-Class Variance for detection of side-channel leakage |

| ProtLBC-ISA | Protected Extension of the ISA for LBC                                |

| risc        | Reduced Instruction Set Computer                                      |

| RSM         | Rotating S-Box Masking                                                |

| RV          | Random Variable                                                       |

| SCA         | Side-Channel Analysis                                                 |

| SNR         | Signal to Noise Ratio                                                 |

| SPN         | Substitution Permutation Network                                      |

| XOR         | The binary exclusive OR instruction                                   |

## Résumé en français

#### Introduction

#### Contexte

Les communications font partie des fonctions clés dans les futurs véhicules. Elles se développent à grande vitesse et nécessitent une fort besoin de sécurité. Qu'elle soit intra- ou extra- véhiculaire, une communication fiable est impérative afin d'assurer la prise de décision rapide en fonction de l'environnement. Néanmoins, elle peut être interceptée et même modifiée par des attaquants potentiels et nécessite donc l'utilisation de protections. La Cryptographie est une réponse évidente pour sécuriser la communication, mais les algorithmes utilisés aujourd'hui semblent inadéquats en termes de complexité et de latence, surtout pour satisfaire les contraintes physico-économiques des systèmes embarqués utilisés à grande échelle. Bien que l'industrie automobile se base généralement sur des standards, il n'est pas rare que certains acteurs préfèrent l'utilisation de technologies ad hoc plus adaptées aux contraintes de coût, de performance et de sécurité. Tant que la communication est interne, un standard ne s'impose pas, mais avec les communications entre véhicules l'absence de standard impose au véhicule une grande versatilité pour assurer la compatibilité des communications, tout en respectant les contraintes de complexité et latence. Un second problème émergeant et propre aux systèmes embarqués est la protection contre les attaques, notamment les attaques physiques du fait que le système peut être accessible à l'utilisateur. Ces attaques sont redoutables car elles peuvent contourner la protection mathématique des algorithmes cryptographique. C'est le cas des attaques par canaux auxiliaires qui exploitent les fuites liées à l'activité du calcul par le biais de la consommation ou du rayonnement électromagnétique. Il est donc essentiel de prendre cet aspect en compte dans les implémentations des algorithmes de chiffrement pour obtenir un haut niveau de sécurité.

Dans le cadre de la chaire «Connected Cars and CyberSecurity (C3S)», les objectifs principaux de la thèse sont d'étudier la faisabilité d'implémentation d'une grande variété d'algorithmes de chiffrement symétrique ainsi que leur protection. Plus précisément la finalité est d'implémenter plusieurs familles d'algorithmes sur un matériel contraint en surface et qui aurait de bonnes performances en termes de sécurité physique et latence. Une solution optimale est d'avoir une implémentation générique, capable d'exécuter rapidement différents algorithmes de chiffrement légers, utilisant peu de ressources et garantissant une protection contre les attaques physiques. L'implémentation peut être totalement matérielle ou alors hybride matérielle / logicielle en tirant parti de la présence d'Unités de Contrôle Électroniques embarquée. Pour assurer le meilleur compromis d'implémentation, cette dernière architecture peut partir d'une modification du jeu d'instruction d'un processeur RISC pour satisfaire la propriété d'agilité des algorithmes de cryptographie légère. Cette généricité garantit une grande flexibilité, une base de protection commune aux algorithmes, pour un coût comparable à celui d'un micro-contrôleur standard.

#### Contributions

Nous avons étudié de nombreux algorithmes de chiffrement et avons proposé une première architecture matérielle, une seconde architecture hybride matérielle/logicielle afin d'implémenter de façon efficace la Cryptographie Légère dans un système embarqué contraint. Nos principales contributions se résument à:

- Classification des Algorithmes de Chiffrement Légers par Bloc

- Implémentation matérielle configurable dédiée à l'accélération de l'exécution des Algorithmes de Chiffrement Légers par Bloc de type SPN

- Extension matérielle du RISC-V dédiée à l'accélération de l'exécution des Algorithmes de Chiffrement Légers par Bloc

- Extension matérielle du RISC-V dédiée à la protection des Algorithmes de Chiffrement Légers par Bloc contre les Attaques par Canaux Auxiliaires

Chaque contribution est étayée expérimentalement par des tests pour évaluer le coût matériel, les performances, la latence et la sécurité physique face aux attaques par canaux auxiliaires.

#### Organisation

Le Chapitre 2 présente le contexte technique avec une base de connaissances prérequises pour appréhender le travail de recherche. Une attention particulière a été portée dans la description de chaque algorithme étudié lors de cette thèse. Même si une sous-partie des algorithmes a été conçue pour validation dans un circuit FPGA, tous ont contribué à trouver l'architecture la plus efficace.

Le Chaptire 3 décrit l'implémentation matérielle générique et configurable dédiée à l'accélération de l'exécution de certains Algorithmes Légers de Chiffrement par Bloc (LBC).

Le Chapitre 4 décrit l'implémentation hybride matérielle-logicielle, basée sur l'Architecture d'Ensemble d'Instructions (ISA) du RISC-V. Cette implémentation est en fait une extension de l'ISA du RISC-V avec des instructions matérielles dédiées à l'accélération de l'exécution des LBCs.

Le Chapitre 5 décrit l'implémentation de protections génériques contre les attaques par canaux auxiliaires rendant l'exécution des LBC résiliente aux attaques par observation de la consommation énergétique. Cette implémentation est également une extension de l'ISA du RISC-V par le biais d'instructions matérielles.

Enfin, le Chapitre 6 est une discussion générale des coûts et des gains de chaque contribution. Les perspectives à tirer de ces recherches y sont également abordées.

#### Implémentation Générique Entièrement Matérielle

Les Algorithmes Légers de Chiffrement par Bloc (LBC) suivent certains principes permettant d'assurer la sécurité mathématique et consistent en trois étapes (*Cf.* Sect. 2.4). Ces trois étapes ont permis d'identifier un moyen générique d'accélérer l'exécution des algorithmes LBC tout en réduisant significativement le surcoût de surface lié à l'implémentation de plusieurs algorithmes en parallèle. Nous avons donc réalisé une architecture unique et générique utilisant les mêmes instructions pour plusieurs algorithmes. Cette première réalisation est entièrement matérielle.

#### Architecture

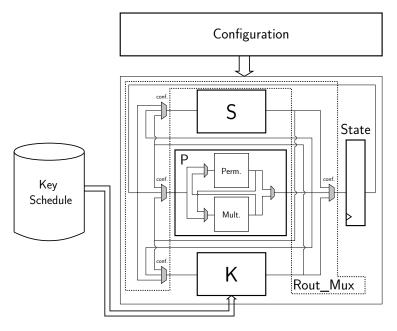

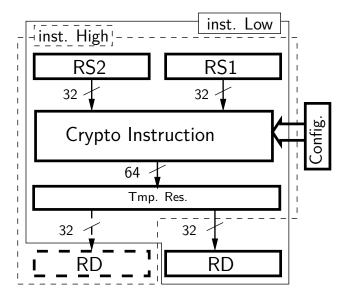

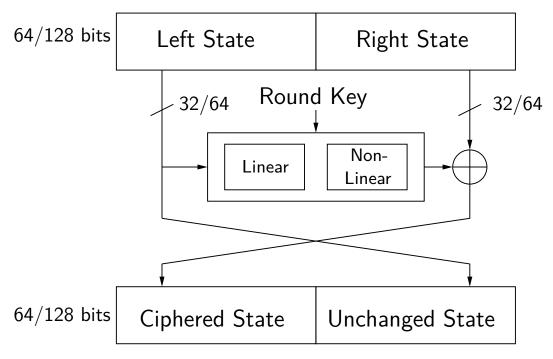

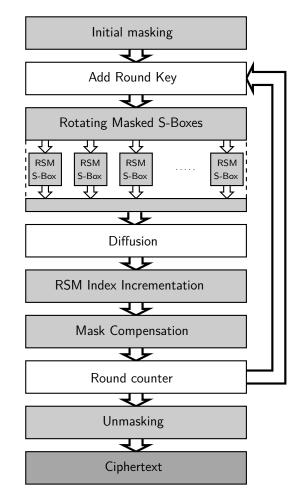

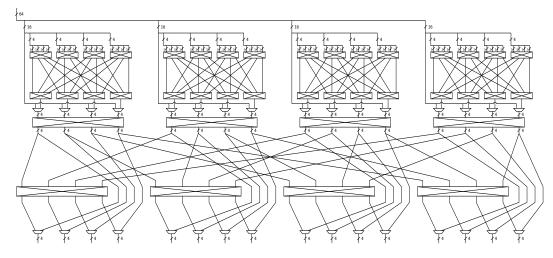

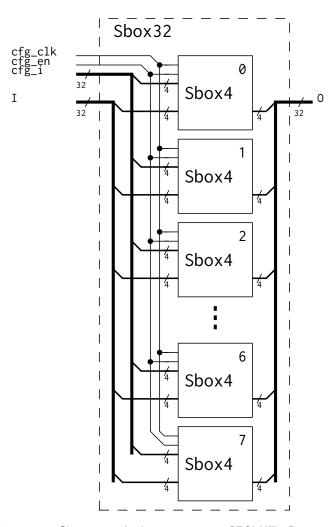

L'architecture de cette première implémentation est basée sur la structure des algorithmes SPN. Un module est dédié à chacune des trois étapes d'un chiffrement par bloc. Le module **S** correspond aux S-Boxs, ou l'étape de Confusion. Le module **P** correspond au P-Layer, ou l'étape de Diffusion. Le module **K** correspond à l'étape d'Ajout de la Clé. De plus, chaque module est configurable au niveau de l'ordre dans lequel les 3 étapes sont exécutées. Ceci se fait par le biais d'une série de multiplexeurs dont le module s'appelle Route\_Mux. Cette implémentation est représentée dans la Fig. 1

Figure 1: Architecture Entièrement Matérielle pour les Algorithmes de Chiffrement de Type SPN

Chacun des modules est présenté ensuite.

#### Le Module K: L'ajout de la clé

Le module **K** est composé d'un XOR 64-bit qui va XORer les 64-bit du bloc au 64bit de la clé de ronde. Cette clé de ronde est pré-calculée par le *Key Scheduling* et correspond à la clé de ronde de l'algorithme XORé avec les éventuelles constantes de ronde et adapté au format 64-bit. Le soucie majeur de ce module est le fait de garder en mémoire ces clés tout en accédant à une de ces clés par cycle. Cela peut être géré en utilisant une mémoire sécurisée ainsi qu'un *bypass* entre le module et la mémoire. Cette solution n'a pas été implémentée et reste théorique.

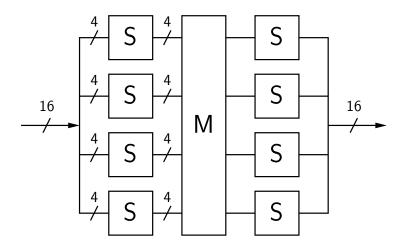

#### Le Module S: Les S-Boxs

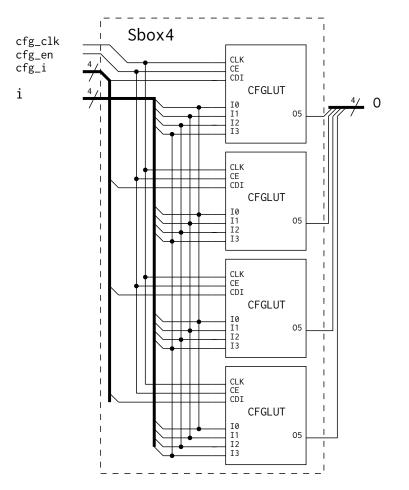

Ce module est composé de seize S-Box  $4 \times 4$  en parallèle et identiques, c'est-à-dire qui ont la même table de substitution. Une S-Box se comporte comme une LUT  $4 \times 4$  et c'est ainsi qu'elles sont réalisées. Ces S-Box, bien qu'identiques entre elles, peuvent être configurées entre chaque algorithme et au cours d'une exécution.

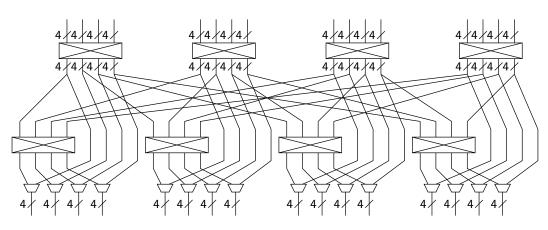

#### Le Module P: Le P-Layer

L'étape de Diffusion d'un algorithme SPN peut être divisée en deux sous-étapes: la première de ces sous-étapes est le *MixColumn*, qui correspond à une multiplication de matrices et la seconde est une permutation au niveau bit, qui correspond parfois à la fonction *ShiftRow*.

#### La Multiplication générique de Matrices

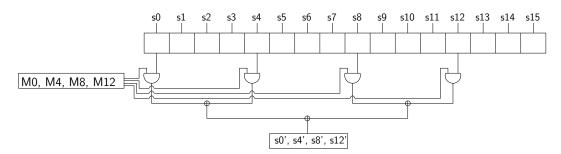

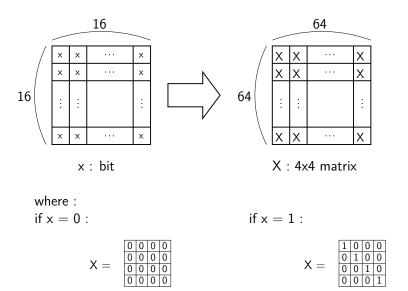

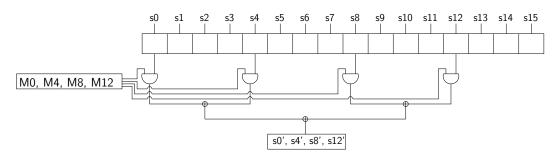

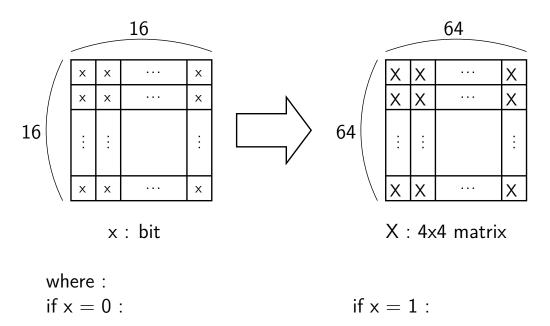

Figure 2: La Multiplication de Matrices Génériques

La multiplication de matrices de la Figure 2 va utiliser les quatre même bits de l'entrée (s0, s4, s8, s12) et quatre groupes de bits différents issus de la matrice (M0, M4, M8, M12).L'opération entre ces bits va permettre d'obtenir quatre bits en sortie (s0', s4', s8', s12') qui feront partie du résultat de la multiplication. Cette méthode permet de n'utiliser que 256 bits de la matrice au lieu des 2048 bits d'une matrice  $64 \times 64$ .

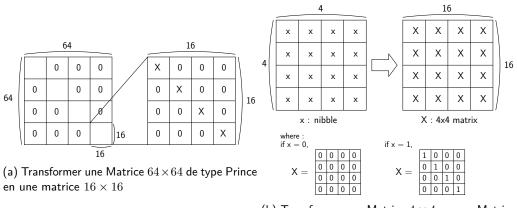

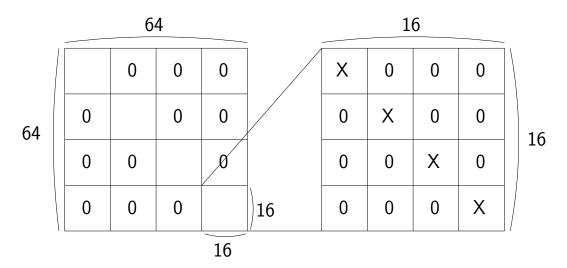

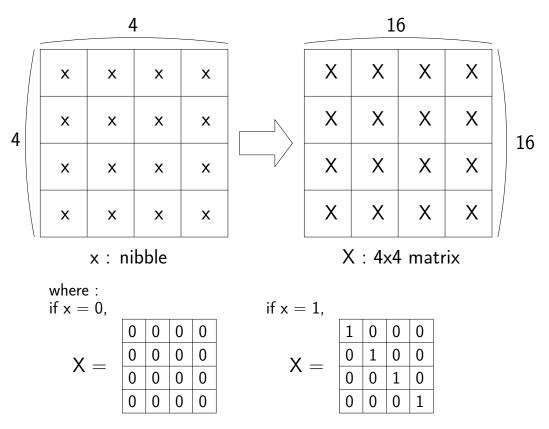

Cette réduction des paramètres est possible en ne considérant que des matrices de niveau nibble (4 bits) ou s'y rapportant. En effet, certains algorithmes utilisent des matrices  $64 \times 64$  ou  $4 \times 4$  dont l'information utile peut être transformée en une matrice  $16 \times 16$ , comme le montrent les Figures 3a et 3b.

(b) Transformer une Matrice  $4 \times 4$  en une Matrice  $16 \times 16$

Figure 3: L'Uniformisation des Tailles de Matrices

#### Permutation Niveau Bit Générique

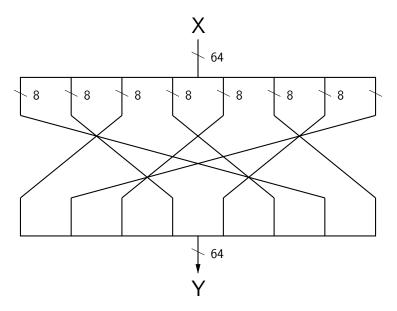

Parmi les différents algorithmes étudiés, certains utilisent le *MixColumn*, qui est équivalente au *ShiftRow* avec une rotation de certains nibbles. Pour les autres algorithmes, comme une simple rotation est insuffisante, il est nécessaire d'utiliser une permutation au niveau bit. Dans le cas d'une implémentation spécifique, ces permutations sont une réorganisation des connexions avec un coût nul pour un algorithme donné, mais assez complexe pour la rendre générique à plusieurs algorithmes. Comme il est très coûteux de concevoir une permutation générique  $64 \times 64$ , il a fallu se concentrer sur certains aspects de ces permutations qui permettent d'assurer la diffusion.

Figure 4: L'Instruction de Permutation au Niveau Bit

La solution choisie est représentée par la Fig. 4. Elle permet aussi bien d'exécuter *ShiftRow* que les permutations au niveau bit de PRESENT ou de GIFT en une seule instruction. Chaque module permettant la permutation de 4 bits ou de 4 nibbles sont implémentés comme des commutateurs Banyan (*Cf.* Sect. 3.6.2). Cela

permet à la fois d'accélérer l'exécution mais également de réduire significativement l'utilisation de la mémoire. En effet, on passe de 8 bits pour un crossbar à 5 bits en utilisant un commutateur Banyan, ce qui représente 200 bits de configuration au lieu de 320.

#### Résultats

Les coûts d'implémentation sont présentés dans la Table 1 qui donne le détail de chaque module. On observe que tous les modules qui demandent un haut

| Module        |                | Coût    |      | Pourcentage |

|---------------|----------------|---------|------|-------------|

|               |                | Surface | GE   | de Surface  |

|               | Route_Mux      | 695     | 678  |             |

|               | S-Box          | 348     | 339  |             |

| Configuration | Permutation    | 956     | 932  | 26.9        |

|               | Multiplication | 1390    | 1355 |             |

|               | Other          | 87      | 85   |             |

| Route_Mux     |                | 2791    | 2720 | 21.6        |

| S             |                | 1784    | 1739 | 13.8        |

|               | Permutation    | 2059    | 2007 | 01.7        |

| Р             | Multiplication | 744     | 725  | 21.7        |

| К             |                | 175     | 171  | 1.4         |

Table 1: Cout de modules de l'Architecture pour un niveau d'agilité C

niveau de configuration représentent une part importante du coût matériel. Notamment les parties Permutation et Route\_Mux qui ont un coût quasi-nul dans le cas d'implémentations classiques.

Table 2: Les Différents Niveaux d'Agilité de l'Architecture

| Algorithme       | Nive | aux d'Agi | lité |

|------------------|------|-----------|------|

| PRESENT<br>GIFT  | Α    | C         |      |

| SKINNY<br>Midori | В    | Ľ         | D    |

| PRINCE           |      |           |      |

| MANTIS           |      |           |      |

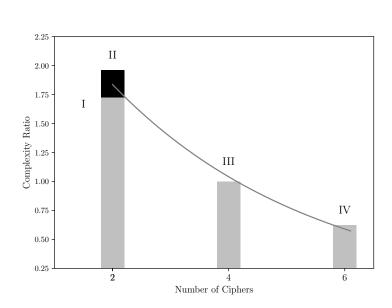

De plus, cette architecture peut être modifiée pour correspondre à différents niveaux d'agilité, présentés dans la Table 2. C'est-à-dire qu'en ajustant les modules il est possible d'adapter l'architecture pour accélérer l'exécution d'un nombre croissant d'algorithmes. En comparant ces résultats au coût d'implémentation de la somme de chacun des algorithmes indépendamment dans la Table 3 on observe qu'au-delà d'un certain niveau d'agilité, l'architecture générique permet des économies de ressources conséquentes. En effet, à partir de six implémentations d'algorithmes, la réduction des coûts matériels est de 62%.

| Niveau d'Agilité | Surface de<br>L'Architecture Générique<br>(en GE) | Somme du coût des<br>Implémentations<br>(Ratio de Complexité) |

|------------------|---------------------------------------------------|---------------------------------------------------------------|

| Α                | 8494                                              | 1.72                                                          |

| В                | 8245                                              | 1.96                                                          |

| С                | 9212                                              | 1                                                             |

| D                | 9631                                              | 0.625                                                         |

Table 3: Comparaison des Coûts entre les Niveaux d'Agilité et la Somme des Implémentations

Bien que ces résultats sont très bons, en termes d'agilité et complexité, une autre approche consiste à combiner les technologies matérielles et logicielles.

#### Implémentation Générique Hybride Matérielle-Logicielle

Dans les voitures modernes, la présence d'Unités de Contrôle Électroniques (ECU) à base de microcontrôleurs repose sur une exécution logicielle des algorithmes. Nous avons donc jugé pertinent de baser notre implémentation sur un jeu d'instructions logicielles ISA adapté, tout particulièrement l'ISA du RISC-V (*Cf.* Sect. 2.8). Ce jeu d'instructions (ISA) est libre et ouvert et a été conçu dans l'optique d'être étendu pour répondre au mieux à une diversité d'utilisations. Cette possibilité d'extension d'instructions permet l'ajout d'instructions matérielles spécifiques afin de réduire la latence d'exécution logicielle de divers algorithmes.

#### Classification des Algorithmes Légers de Chiffrement par Bloc

Afin de réduire les surcoûts liés à l'extension il est important de bien choisir les instructions qui seront implémentées. Pour ce faire, nous avons établi une classification, présentée en Fig. 4, de nombreux LBCs en fonctions des instructions requises à l'accélération de leur exécution.

| Catágoria | Algorithmo           | Confusion | Diffusio    | on     |

|-----------|----------------------|-----------|-------------|--------|

| Catégorie | Algorithme Confusion |           | Туре        | Niveau |

|           | Simon                | AND       | Rotation    | Bit    |

|           | Speck                | ADD       | Rotation    | Bit    |

|           | Simeck               | AND       | Rotation    | Bit    |

| •         | RC5                  | ADD       | Rotation    | Bit    |

|           | XTea                 | ADD       | Rotation    | Bit    |

| П         | GOST                 | S-Box     | Rotation    | Bit    |

|           | Rectangle            | S-Box     | Rotation    | Bit    |

| III a     | PRESENT              | S-Box     | Permutation | Bit    |

| iii a     | GIFT                 | S-Box     | Permutation | Bit    |

| III b     | PRINCE               | S-Box x2  | MatMult x3  | Bit    |

|           | TWINE                | S-Box     | MatMult     | Nibble |

|           | SKINNY               | S-Box     | MatMult     | Nibble |

| IV        | Midori               | S-Box     | MatMult     | Nibble |

|           | MANTIS               | S-Box     | MatMult x3  | Nibble |

Table 4: Classification des Algorithmes Légers de Chiffrement par Bloc

Cette classification divise les LBCs en quatre catégories, à chaque catégorie est associée un type d'instruction qui permet d'en accélérer l'exécution:

- Catégorie I: Les instructions utilisées sont déjà présentent dans l'ISA

- Catégorie II: Nécessite l'ajout d'une instruction S-Box

- Catégorie III: Nécessite l'ajout d'une instruction S-Box et d'une instruction de Permutation ou de Multiplication de Matrices, au niveau bit

- Catégorie IV: Nécessite l'ajout d'une instruction S-Box et d'une instruction de Multiplication de Matrices au niveau nibble

L'extension qui a été étudiée s'est concentrée sur l'ajout de ces catégories d'instructions.

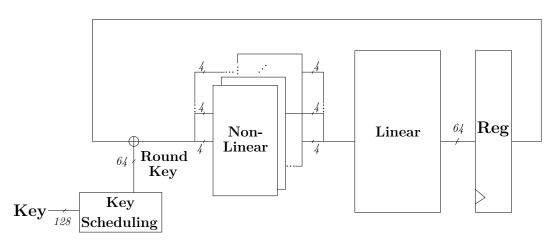

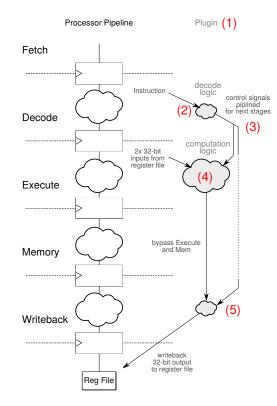

#### Le VexRisc Core

Il existe de nombreuses implémentations de l'ISA du RISC-V, et celle que nous avons choisie est le VexRisc Core 32-bit. En effet, il permet l'ajout de nouvelles instructions par l'utilisation de plug-ins qui n'impactent pas le cœur du RISC-V 32-bit.

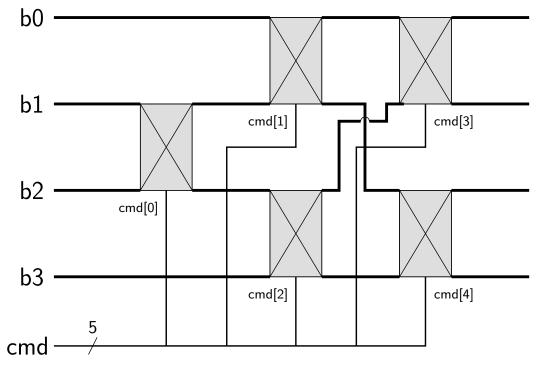

#### Proposition d'Extension d'ISA

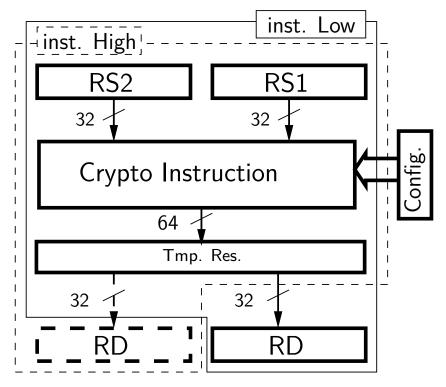

Une implémentation 32-bit pour manipuler des blocs de 64 bits ajoute tout de même une contrainte. En effet, la sortie des instructions est sur 32 bits, cela nécessite donc de dédoubler chaque instruction afin d'obtenir le résultat sur 64 bits, comme représenté en Fig. 5. Ainsi, lorsqu'une instruction sera évoquée, on parlera en fait d'un double instruction la première renvoyant la partie basse de la sortie, et la seconde renvoyant la partie haute de la sortie.

Figure 5: Sortie 64-bit Utilisant Deux Instructions RISC-V 32-bit

En nous basant sur la classification établie, nous avons décidé d'implémenter cinq instructions (ou groupes d'instructions) pour cette extension:

- L'instruction S-Box: **SBOX\_C**

- L'instruction permutation au niveau bit de PRESENT: PRESENT\_D

- L'instruction permutation au niveau bit de GIFT: GIFT\_D

- Les instructions de multiplication de matrices au niveau bit de PRINCE: PRINCE\_D

- L'instruction de multiplication de matrices au niveau nibble: NMAT\_D

Comme expliqué dans la partie précédente, les instructions génériques au niveau bit peuvent être très coûteuses, c'est pourquoi nous avons choisi de réaliser certaines instructions spécifiques à un algorithme. L'étape de Diffusion de PRINCE évolue au cours de l'exécution, c'est pourquoi plusieurs instructions sont nécessaires. Les instructions **SBOX\_C** et **NMAT\_D** sont quant à elles génériques et sont utilisées dans plusieurs algorithmes.

#### L'Instruction SBOX\_C

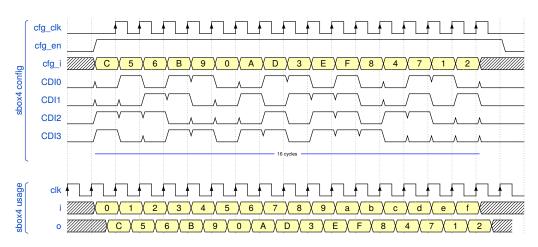

Cette instruction prends quatre bits en entrée et les transforme en quatre bits de sortie par le biais d'une table de substitution. Son comportement est donc le même que celui d'une LUT lorsque la table est configurable. Nous avons donc implémenté l'instruction **SBOX\_C** comme une LUT. La configuration de cette instruction a en principe lieu avant l'exécution mais certains algorithmes peuvent nécessiter une reconfiguration au cours de l'exécution.

#### Les Instructions PRESENT\_D et GIFT\_D

Ces deux instructions utilisées des permutations au niveau nibble. L'implémentation choisie n'est pas générique et dans les deux cas, l'implémentation se résume à une réorganisation des fils.

#### Le Groupe d'Instruction PRINCE\_D

L'algorithme de PRINCE utilise trois étapes de Diffusion différentes au cours de son exécution, c'est pourquoi nous avons implémenté trois instructions différentes. **PRINCE\_DF** qui est la Diffusion du début d'algorithme, **PRINCE\_DM** qui est la Diffusion du milieu d'algorithme et **PRINCE\_DL** qui est la Diffusion de fin d'algorithme.

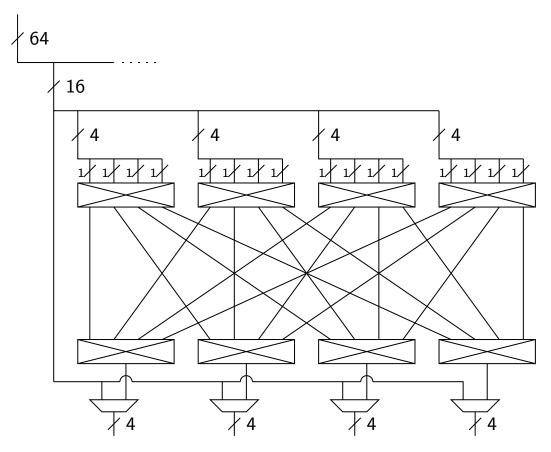

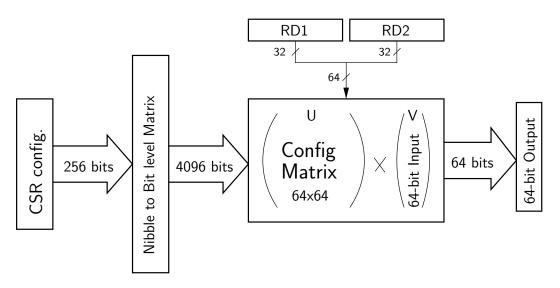

#### L'Instruction NMAT\_D

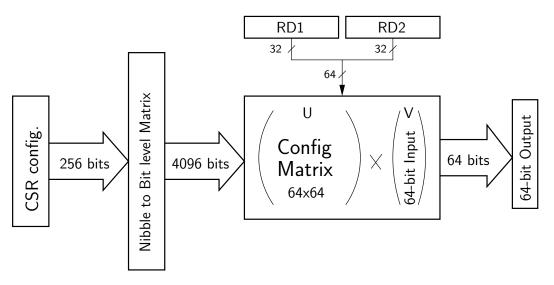

Cette instruction convient à tous les algorithmes qui utilisent une structure *ShiftRox MixColumn* au niveau nibble. Elle permet la multiplication par n'importe quelle matrice de nibble  $16 \times 16$  qui serait composée de 1 ou de 0 et nécessite 256 bits de paramètres. Bien que ces matrices  $16 \times 16$  contiennent toute l'information, il est nécessaire de les transformer en matrice  $64 \times 64$  pour les multiplier aux blocs 64-bit. La méthode est présentée dans la Figure 6

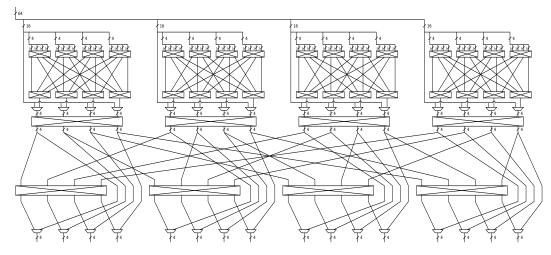

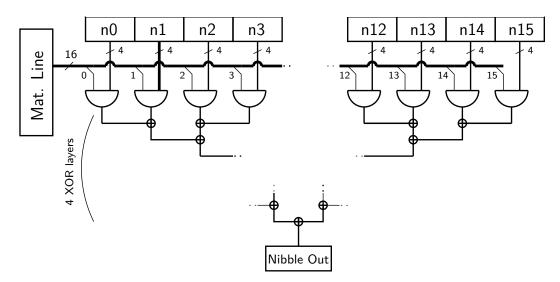

L'utilisation de cette instruction comprend donc plusieurs étapes, qui sont décrites dans Fig. 7. Les 256 bits de paramètre sont d'abord stockés dans huit registres CSR 32-bit. Les paramètres de chaque registre sont ensuite ANDés avec chaque nibble d'entrée, puis chaque résultat est XORé afin d'obtenir une sortie 64-bit.

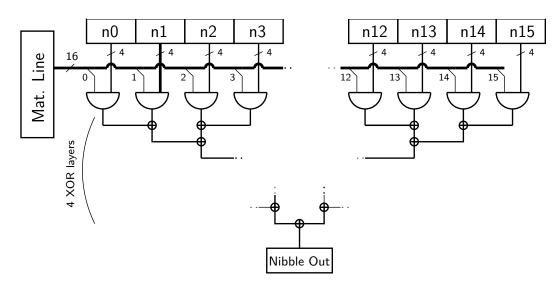

Le datapath de la multiplication en elle-même est montrée dans la Figure 8.

Une fois ces instructions choisies et implémentées, il a s'agit de les tester et de les valider.

Figure 6: 256-bit de Configuration d'une Matrice  $64 \times 64$  pour NMAT\_D

Figure 7: The NMAT\_D Instruction

#### Plateforme de Test et de Validation

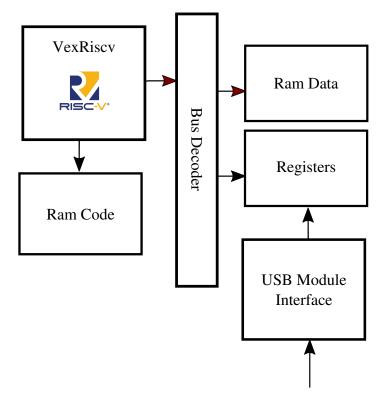

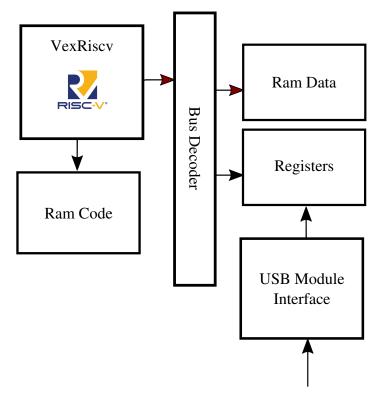

La plateforme que nous avons utilisée est basée sur l'implémentation VexRisc du RISC-V. Elle est représentée en Figure 9 et contient les éléments suivants:

- Un VexRisc Core

- Deux mémoires on-chip indépendantes de 32KB pour les programmes et les données

- Un module de communication permettant la connexion à un ordinateur hôte via une interface USB

Figure 8: The NMAT\_D multiplication datapath

- Un module de configuration qui inclut des registres d'adresse mémoire dédiés capable de lire et d'écrire depuis l'ordinateur hôte via le module USB

- Un module avec port GPIO (General Purpose Input Output) pour les interactions directes avec les utilisateurs

La carte cible est la Chipwhisperer CW305 [2]. Elle est basée sur un FPGA Artix-7, et a été conçue pour permettre les analyses de consommation par canaux auxiliaires.

Afin de tester la validité de chacune de nos instructions, chaque algorithme a été implémenté en C en utilisant la chaine de compilation GNU GCC pour RISC-V. A chaque fois, deux modes d'exécution ont été implémentés:

- Logiciel, qui utilise l'ISA RISC-V Standard

- Accélérée, qui utilise la version étendue LBC-ISA

Ce qui nous permet de tester à la validité des instructions mais également de comparer leurs performances.

#### Coûts et Gains de l'Implémentation

Nous avons d'abord comparé les coûts d'implémentation du RISC-V sans extension à ceux de divers configuration d'extension permettant d'accélérer l'exécution d'un ou plusieurs algorithmes.

Ces résultats, présentés dans le Tab. 5 montrent que les deux instructions les plus coûteuses que sont **SBOX\_C** et **NMAT\_S** font ensemble doubler le coût en LUT et moins de tripler le cout en mémoire. Le surcoût lié à l'utilisation d'instruction génériques n'est donc pas négligeable mais reste dans un ordre de grandeur semblable.

SKINNY

Figure 9: VexRisc Platform

|            |                              |      | -   | -    |       |

|------------|------------------------------|------|-----|------|-------|

| Algorithme | Instructions LBC-ISA         | LUTs | %   | FFs  | %     |

| None       |                              | 973  | -   | 765  | -     |

| PRESENT    | $SBOX_C + PRESENT_D$         | 1173 | +21 | 767  | +0.2  |

| GIFT       | $SBOX_C + GIFT_D$            | 1103 | +13 | 767  | +0.2  |

| PRINCE     | $SBOX_C + PRINCE_D$          | 1438 | +48 | 769  | +0.5  |

| PRINCE     | $2 \times SBOX_C + PRINCE_D$ | 1512 | +55 | 769  | +0.5  |

| Midori     | $SBOX_C + NMAT_D$            | 1778 | +82 | 1023 | +33.7 |

| TWINE      | $SBOX_C + NMAT_D$            | 1778 | +82 | 1023 | +33.7 |

Table 5: Coût en Surface de l'Extension du RISC-V par Algorithme

Nous nous sommes ensuite intéressés à l'accélération d'exécution engendrée par ces instructions, les résultats sont dans le Tableau 6 et sont donnés en nombre d'instructions.

1778

+82

1023

+33.7

$SBOX_C + NMAT_D$

La Table 6 montre qu'en termes d'accélération de l'exécution le facteur de gain est beaucoup plus important. En effet, il varie entre 8 et 100 ce qui représente entre 1 et 2 ordres de grandeur d'écart.

| Algorithm                      | Base ISA | LBC-ISA | Facteur de Gain |

|--------------------------------|----------|---------|-----------------|

| PRESENT                        | 12544    | 358     | 35              |

| GIFT                           | 10661    | 319     | 33              |

| PRINCE with reconfiguration    | 17357    | 2313    | 8               |

| PRINCE without reconfiguration | 17357    | 126     | 138             |

| Midori                         | 18944    | 232     | 81              |

| TWINE                          | 41279    | 622     | 66              |

| SKINNY                         | 40887    | 409     | 100             |

Table 6: Nombre d'Instructions par Algorithme en fonction de l'ISA

#### Implémentation Générique Protégée

Bien que les algorithmes de chiffrement soient mathématiquement protégés il n'en reste pas moins certaines failles qui menacent leur niveau de sécurité. Ces failles se trouvent notamment dans le matériel sur lequel sont exécutés ces algorithmes. En effet, dû à la nature des portes CMOS (*Cf.* Sect. 2.6.2) tout changement de valeur d'une porte engendre une consommation d'énergie qui peut être exploitée pour une attaque dite physique. Ce type d'attaque s'appelle les attaques par canaux auxiliaires SCA (*Cf.* Sect. 2.6), qui font partie des attaques physiques, et il est important de pouvoir s'en protéger. Cette dernière partie de thèse va consister à l'implémentation d'une autre extension du RISC-V permettant la protection contre les attaques par observation de consommation.

#### Méthode d'Évaluation de la Sécurité

Dans un premier temps, il s'agit d'identifier la présence de la menace en essayant d'attaquer l'exécution de chaque type d'algorithme afin d'extraire la clé secrète. Pour ce faire, nous allons utiliser différents outils permettant de repérer les fuites, d'attaquer ces fuites puis d'observer le résultat de ces attaques. Chacun de ces outils est basé sur l'utilisation de traces de consommation d'énergie. Ces traces sont utiles lorsqu'elles sont en grand nombre puisqu'elles permettent une étude statistique de la consommation énergétique significative en effaçant l'impact du bruit.

#### La Normalized Inter-Class Variance

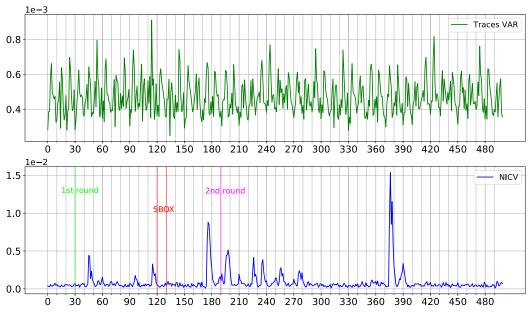

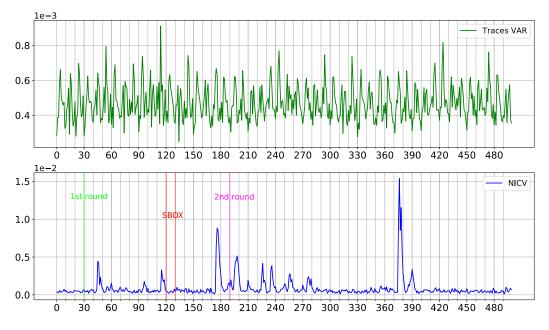

La NICV permet d'identifier chaque endroit de l'exécution où une fuite potentielle a lieu. Elle compare l'activité de l'intégralité du circuit à celle d'une valeur donnée en entrée. Cela permet d'observer des piques de corrélation comme sur la Figure 10.

Il est important de noter que ces piques indiquent les fuites potentielles mais que chaque pique n'est pas exploitable. Il faut ensuite mettre en adéquation ces graphiques aux simulations d'exécution des algorithmes.

Figure 10: La NICV de PRESENT pour 32768 traces

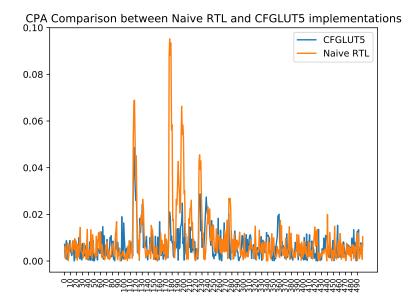

#### L'Analyse de Consommation Énergétique par Corrélation

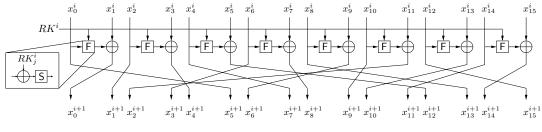

L'Analyse de Consommation Énergétique par Corrélation (CPA) est le concept de base de l'attaque utilisée, elle est expliquée en détails Section 5.2.3. Le principe est d'observer la consommation énergétique en sortie de S-Box qui est la seule instruction non-linéaire des algorithmes de chiffrement étudiés. C'est là qu'une corrélation discriminante peut apparaitre entre le *Poids de Hamming* et les traces d'exécution. Pour chaque valeur de nibble possible en sortie de S-Box, une hypothèse est faite et en comparant les résultats de cette hypothèse aux traces il est possible de déterminer la valeur cachée. Chaque hypothèse donne lieu à un coefficient, la valeur avec le plus haut coefficient est considéré comme la plus probable. Lorsque cette valeur la plus probable est la même que la valeur du nibble de la clé, on dit alors que ce nibble est *cassé* Lorsque suffisamment de nibble sont *cassés* alors on dit que la clé est *cassée* et l'algorithme de chiffrement n'est alors plus une protection.

#### La Guessing Entropy

La valeur la plus probable a son importance dans une analyse CPA mais il est également important d'observer la place de la valeur du nibble de la clé. En effet, la Guessing Entropy (GE) va donner la position dans le classement CPA de la vraie valeur du nibble de la clé en fonction du nombre de traces utilisées. La position utilisée est en réalité la moyenne des positions obtenue lors de huit attaques sur différents sous-groupes de traces. Cela permet d'observer l'évolution de l'efficacité d'une attaque au fur et à mesure que le nombre de traces augmente. C'est cette mesure que nous avons choisie pour représenter comment l'exécution des algorithmes se comporte face aux attaques.

#### Évaluation de la Sécurité des Implémentations non-protégées

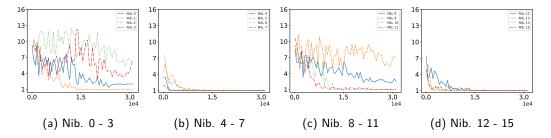

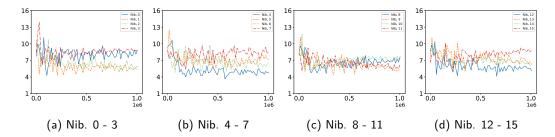

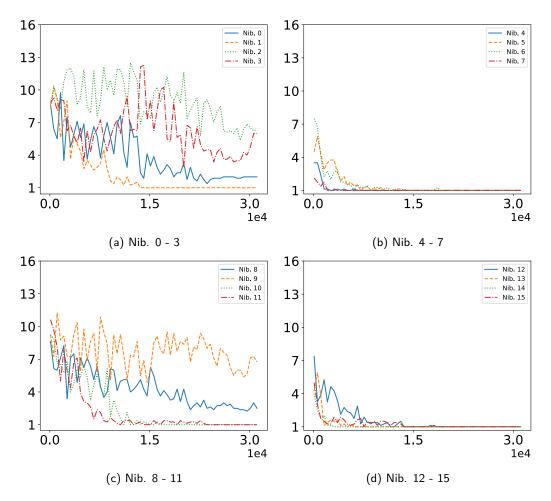

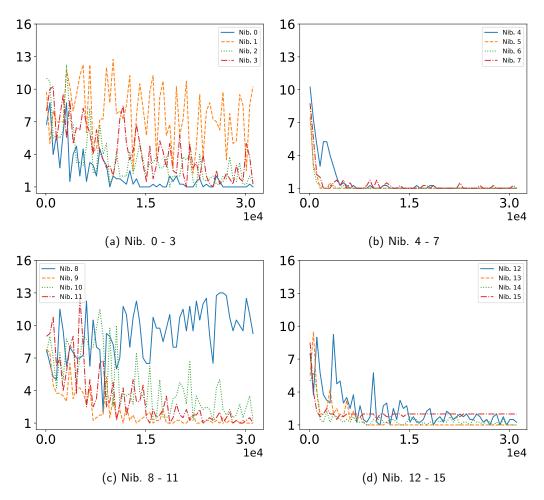

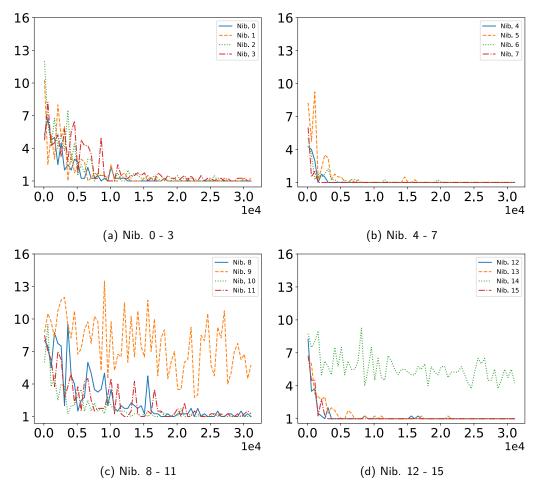

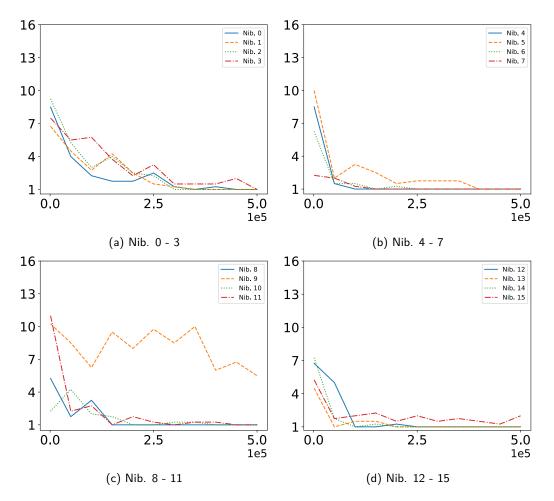

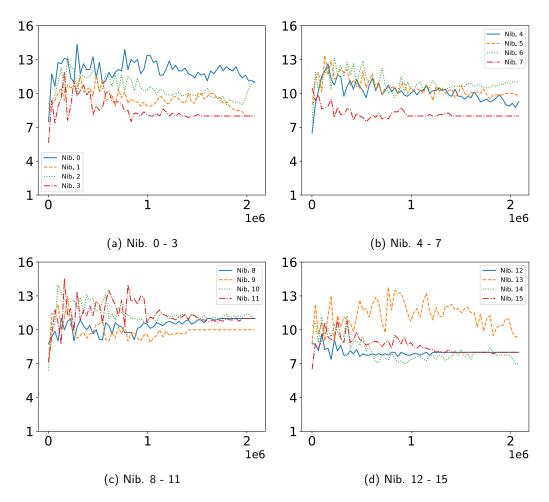

Pour différents types d'algorithmes, représentés par PRESENT, GIFT, PRINCE et Midori nous avons observé l'évolution de la GE pour des paquets de traces de taille croissante, allant de 100 à 32768. Les résultats pour PRESENT sont présentés dans la Figure. 11.

Figure 11: La Guessing Entropy de l'Exécution de PRESENT pour jusqu'à 30000 Traces de Consommation Énergétique

On observe que la majorité des nibbles a pu être *cassés* avant la barre des 15000 traces mais que certains semblent beaucoup moins sensibles à l'attaque. On note néanmoins que pour ces derniers nibbles la tendance est à la décroissance de la GE qui semble tendre vers 1.

Les résultats des autres algorithmes sont présentés dans la Section 5.3. Dans l'ensemble, l'attaque fonctionne de la même manière sur tous les algorithmes, une majorité des nibbles sont *cassés* avant 15000 traces et certains y sont moins sensibles. Nous n'avons pas d'explication à ce phénomène qui rend certains nibble plus difficiles à attaquer. Parmi les pistes évoquées il y a la possibilité que les S-Box ne s'exécutent pas toutes en parallèle ce qui créerait un décalage dans le flot d'exécution qui modifierait le moment de sortie des S-Box.

#### Proposition d'Extension d'ISA pour la Protection

Les résultats précédents mettent en évidence la nécessité de pouvoir se défendre contre les SCA. C'est pourquoi la suite de nos recherches se sont tournées vers l'implémentation de protections contre ces attaques. Pour ce faire nous avons maintenu la forme de cette implémentation comme une extension matérielle et logicielle de l'ISA du RISC-V.

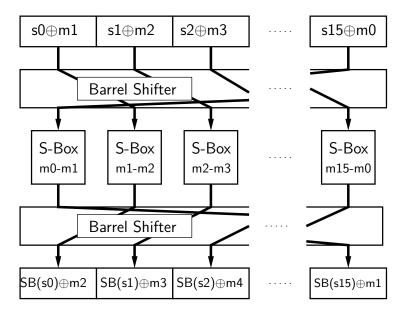

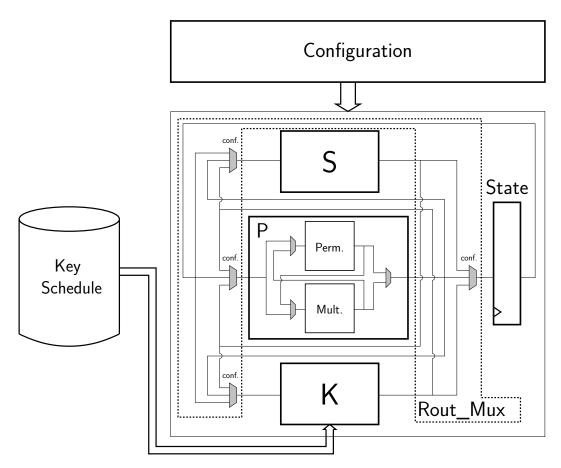

Parmi les divers contremesures existantes, celle qui a retenu notre attention est la protection par Masquage avec Rotation des S-Box (RSM), décrite dans la Section 2.7.2.2. Cette protection va masquer le texte d'entrée qui sera décalé d'un nibble après chaque S-Box. La particularité de cette protection est donc qu'elle s'applique directement aux S-Box et nécessite la modification des S-Box en fonction des nibble du masque. Ce qui est adapté à notre implémentation pour deux raisons:

Les algorithmes sur lesquels nous nous concentrons utilisent tous la S-Box, cette protection devrait donc s'appliquer à chacun d'en eux.  L'instruction S-Box de la LBC-ISA permet de configurer chaque S-Box indépendamment, et donc de le faire en fonction de chacun des nibbles du masque

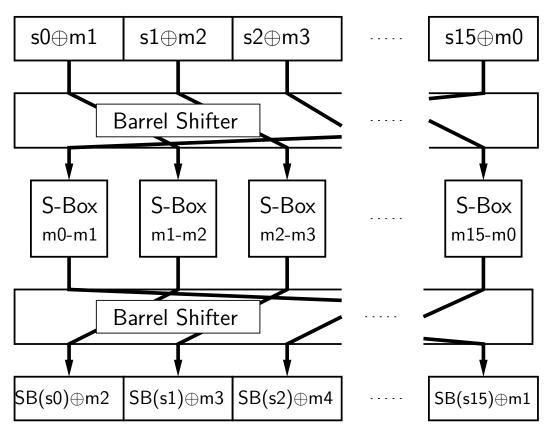

Le dernier point qu'il reste à traiter pour l'implémentation de RSM est la rotation. Pour ce faire, nous avons opté d'effectuer la rotation sur les entrées et sorties des S-Box, ce qui évite de revoir les reconfigurer en permanence. Nous avons donc implémentié un *Barrel Shifter* 64-bit au niveau nibble, qui permet d'effectuer n'importe quelle rotation au niveau nibble sur un mot de 64 bits. La Figure 12 montre comment ce *Barrel Shifter* permet d'assigner chaque nibble à la S-Box qui correspond à son nibble de masque. On peut voir que grâce aux S-Box

Figure 12: L'Etape de Confusion avec RSM

modifiées, les *Barrel Shifter* permettent d'assurer la rotation du masquage sans rotation du texte.

Nous avons implémenté deux instructions **NShift** et **InvNShift** qui forment l'extension protégée, nommée **ProtLBC-ISA**. Les instructions implémentées, sont de type R (*Cf.* Fig. 13) ce qui permet d'avoir deux entrées 64-bit mais ne laisse plus l'option de préciser la valeur du décalage (*shift amount*). Il est donc nécessaire de définir ce *shift amount* par le biais de registres CSR.

| 31 | 25     | 24 20 | 19 15 | 14 12  | 11 7 | 6 0    |

|----|--------|-------|-------|--------|------|--------|

|    | funct7 | rs2   | rs1   | funct3 | rd   | opcode |

Figure 13: Les Instructions RISC-V de Type R

L'utilisation d'un tel registre est de toute façon nécessaire puisque l'index de rotation initiale du masque est secret et doit donc être stocké dans un de ces registres. La valeur de l'index initial contenue dans ce registre est ensuite incrémentée après chaque étape de Confusion. De plus, comme le montre la Fig. 12, chaque utilisation de **NShift** implique l'utilisation de la rotation inverse, qui est exécuté par **InvNShift**. Ces deux instructions sont donc l'inverse l'une de l'autre, elles utilisent donc des paramètres légèrement différents, mais le matériel utilisé pour les implémenter est le même.

Le coût de cette implémentation est résumé dans le Tableau 7, la version complète du tableau est dans la Section 5.1.3.1

| Configuration                                        | Instruction<br>Supplémentaire                                                                                      | LUTs | %    | FFs  | %     |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| RISC-V ISA<br>de Base                                | -                                                                                                                  | 978  | -    | 775  | -     |

| RISC-V Etendu<br>LBC-ISA (PRESENT)                   | S-Box +<br>PRESENT_D                                                                                               | 1178 | +20  | 777  | +0.2  |

| RISC-V Etendu<br>LBC-ISA (ENTIERE)                   | S-Box + PRESENT_D +<br>GIFT_D + PRINCE_DF +<br>PRINCE_DM + PRINCE_DL +<br>MMULT_D                                  | 2135 | +118 | 1038 | +34   |

| RISC-V Protégé<br>Extension ProtLBC-ISA<br>(PRESENT) | S-Box + PRESENT_D +<br>Nibble-Level Barrel Shifter                                                                 | 1993 | +104 | 814  | +5.0  |

| RISC-V Protégé<br>Extension ProtLBC-ISA<br>(ENTIERE) | S-Box + PRESENT_D +<br>GIFT_D + PRINCE_DF +<br>PRINCE_DM + PRINCE_DL +<br>MMULT_D +<br>Nibble-Level Barrel Shifter | 2619 | +168 | 1070 | +38.1 |

| Table 7: Coût Ma | latériel de l'Implé | mentation Géné | rique Protégée |

|------------------|---------------------|----------------|----------------|

|------------------|---------------------|----------------|----------------|

#### Évaluation de la Sécurité de l'Implémentation Protégée

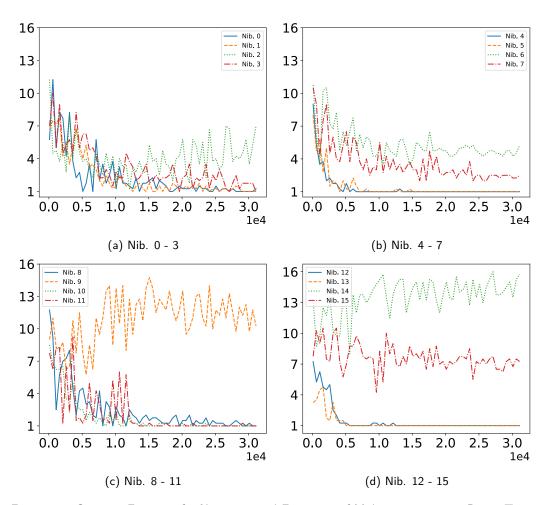

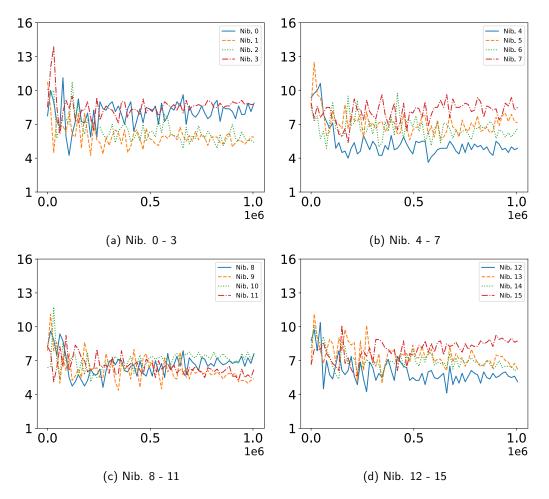

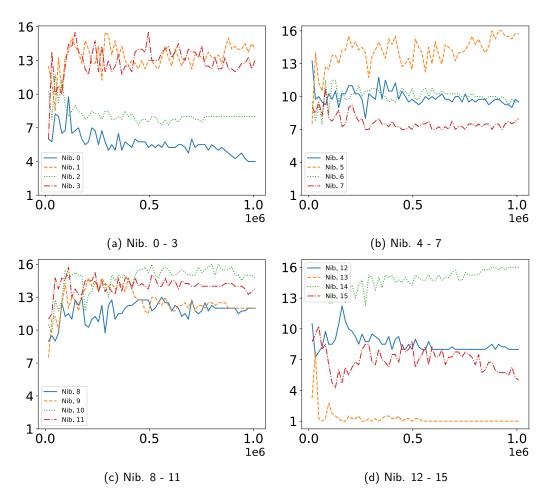

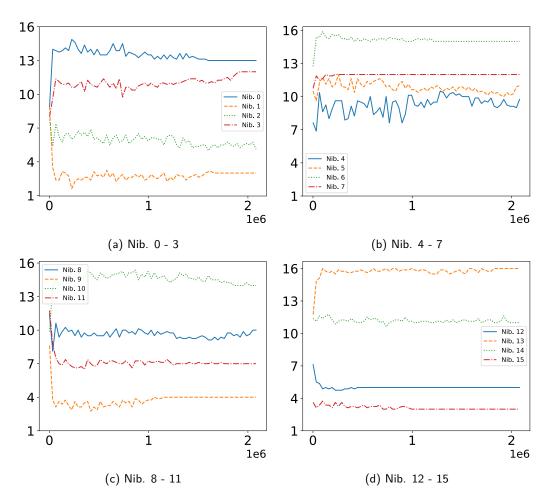

Nous avons utilisé la même méthode d'évaluation que pour les versions non protégée, excepté que nous avons augmenté le nombre de traces. Pour les algorithmes PRESENT et GIFT, nous avons capturé 1048576 de traces et pour les algorithmes PRINCE et Midori, nous avons capturé 2097152 de traces. La Figure 14 montre l'évolution de la GE pour l'attaque de PRESENT. Les résultats des autres algorithmes sont présentés Section 5.4.

Figure 14: La Guessing Entropy de l'Exécution de PRESENT Protégé pour jusqu'à 1 million de Traces de Consommation Énergétique

Ces courbes montrent que même pour des paquets de plus d'1 million de traces la GE ne converge pas vers 1, la tendance est plutôt à des valeurs entre 4 et 10. Cette absence de convergence vers 1 montre que le bon nibble de clé n'est jamais identifié par l'attaque comme étant le plus probable. Ainsi, l'efficacité de la protection a bien été montrée pour un nombre de traces supérieur à 1 million, soit environ 100 fois plus que pour les versions non protégées. Les résultats pour les autres algorithmes montrent des comportements similaires ce qui confirme également que la même protection va fonctionner sur d'autres algorithmes utilisant des S-Box.

#### Conclusion

Nous avons montré lors de cette étude qu'il était possible de grandement réduire la latence de nombreux algorithmes de chiffrement légers par blocs avec un nombre restreint d'instructions génériques dédiées. Pour ce faire, nous avons d'abord adopté une approche entièrement matérielle qui s'est avérée trop coûteuse et ne profitant pas assez des outils offert par le contexte.

Nous avons également montré qu'en choisissant avec attention ces instructions et en utilisant l'ISA du RISC-V, il était possible de réduire les coûts matériels. En effet, l'utilisation du logiciel a permis de réduire certaines contraintes liées à l'aspect générique. Il est donc bien possible d'adopter une approche générique à l'implémentation des LBC et d'obtenir un véritable gain de latence. Le coût matériel est quant à lui raisonnable et adaptable à l'agilité requise.

Pour ce qui est de l'implémentation des contre-mesures, nous avons pu montrer qu'une approche générique permettait d'assurer une très bonne protection. En effet, avec l'ajout matériel d'une seule instruction, nous sommes parvenus à montrer que la protection pouvait être augmentée d'un facteur de 100 en termes de nombre de traces. Cette protection a tout de même un coût en termes de latence puisque le nombre d'instructions augmente.

Lors de ces recherches nous nous sommes concentré sur l'objectif d'assurer une protection générique à des algorithmes dont l'exécution a été accélérée par des instructions elles aussi génériques. Ce que nous sommes parvenue à faire. Cependant nous avons laissé plusieurs questions en suspend et il aurait été intéressant de prendre le temps d'y répondre. Parmi elles, l'explication de la résistance de certains nibbles aux SCA pourrait donner lieu à des travaux intéressants.

### Chapter 1

## Introduction

#### 1.1 Motivation

Communication in modern car is developing at a very high pace and with it comes the need to secure these communications. Indeed, whether it is internally, or between vehicles, reliable communication is essential to allow modern car to take decisions and react to its surrounding autonomously. Nevertheless, communication signals can be intercepted and even modified by attackers and therefore require protection. Cryptography is the evident answer to secure communication, but existing cryptography is believed by some to be inadequate and the cost of implementing it in all the embedded systems too high. Although the car industry relies on standards, it also sometimes prefer to use *ad hoc* technologies more suited for its constraints in terms of cost, performance and security. As long as the communication is internal this does not represent an issue, but once the cars start communicating with each other, then lacking standard becomes a time sensitive problem.

A second issue with security of embedded communication is the protection against physical attacks. Indeed, these attacks can bypass the protection offered by sound cryptographic algorithms by exploiting the fact that these algorithms run on an accessible hardware device. Nowadays, protection against those physical attacks must be considered when designing the implementation of a cryptographic algorithm and such protections are far from being standardized.

In the context of The Connected Cars and CyberSecurity (C3S) Chaire [60], which financed this work, we wanted to see how multiple cryptographic algorithms could be handled by an embedded system. In other words, is it possible to keep a small hardware footprint while keeping good performances. What drove this work was therefore to find low-resource agile implementation for lightweight cryptographic algorithms while providing protection against physical attacks. The main constraints were therefore agility, low latency and low hardware cost. It is important to note that this only applies to the datapath and that *key scheduling* is not part of this work.

Although a fully hardware implementation is proposed, the context of embedded Electronic Control Units in modern cars, lead us to also study software implementations and to propose a dedicated processor. This allowed flexibility, which fully hardware implementations do not provide, while keeping hardware cost reasonable when compared to a standard microcontroller.

#### 1.2 Contributions

Throughout this work we have studied several cryptographic algorithms and proposed a hardware architecture and a dedicated processor to implement efficiently Lightweight Cryptography (LWC) in an embedded system. Our main contributions can be summarized as follows:

- Classification of Lightweight Encryption Algorithms by Block

- Configurable hardware implementation dedicated to the acceleration of the execution of Lightweight Block Ciphers of the SPN type

- RISC-V hardware extension dedicated to accelerating the execution of Lightweight Block Ciphers

- RISC-V hardware extension dedicated to the protection of Lightweight Block Ciphers against Auxiliary Channel Attacks

Each contribution is experimentally supported by tests to evaluate hardware cost, performance, latency and physical security against auxiliary channel attacks.

During our study, we also came across an interesting phenomenon of leakage linked to the internal pipeline execution order in a processor core and the instructions order in the executed software.

#### 1.3 Organisation

Chapter 2 give a thorough background regarding the state of the art of all the concepts studied during this work. As it will be explained later, all studied ciphers were not exploited to support our results, but they were nevertheless all considered for their potential use. All these ciphers are described in Appendix A.

Chapter 3 describes the configurable agile hardware implementation dedicated to the accelerated execution of the selected Lightweight Block Ciphers (LBC).

Chapter 4 describes the dedicated processor implementation, based on the RISC- V open Instruction Set Architecture (ISA). This implementation extends the RISC- V ISA with additional hardware instructions dedicated to the acceleration of LBCs execution

Chapter 5 describes an agile protection against side-channel attacks implemented to make the execution of LBCs resilient against power observation attacks. The implementation of this countermeasure expand also the RISC-V ISA with a dedicated set of instructions. The protection is evaluated experimentally for several LBCs by performing correlation attacks and comparing its resistance to the unprotected dedicated processor.

Finally, Chapter 6 is an overall discussion of the costs and benefits of each of the contributions, along with a look at the perspectives this work offers.

## Chapter 2

## State-of-the-Art

Understanding the state-of-the-art of cryptography is essential to understanding this work and this chapter will cover the basis of the principles and ideas used. It will first explain the basic cryptographic principle, before presenting those specific to ciphers and most specifically Lightweight Block Ciphers. Each of the ciphers considered for this research will be detailed in Appendix A. It will then explain the basic cryptanalysis principles which are used during an attack and more specifically a side-channel attack. Finally, it will present the RISC-V ISA and some of its implementations.

#### 2.1 Introduction to Cryptography

Whether it is at a very large scale with the Internet or at a very small scale with embedded technology, communication is at the heart of modern development in technology. Just as it becomes more and more essential to how our society work, it becomes more and more essential to protect it. These protections used are based on cryptography which is the science of protecting sensitive information. It is based on four principles [15]:

- Confidentiality: which makes sure that only the allowed party (or user) have access an understandable form of the message.

- Authenticity: which makes sure that users can identify themselves.

- **Integrity**: which makes sure that the transmitted message has not been tempered with (due to transmission or a third party).

- Non-Repudiation: which makes sure that no allowed party can deny being the sender or receiver of a message

A cryptographic algorithm or *cipher* will first *encrypt* a *plaintext* into a *cipher text*. This means that the original message or *plaintext*, which can be understood by anyone, is transformed or *encrypted* in an unintelligible form or *ciphertext*. Once the *ciphertext* has been obtained, it is then sent to the receiver. While the message is on its way to the receiver, it can be intercepted as the communication lines can hardly be entirely secured. Thanks to the encryption, the intercepted message isn't the hidden *plaintext*, but the unintelligible *ciphertext*, meaning that the actual information is still secure. The receiver then receives the message and uses the same *cipher* to transform back or *decrypt* the *ciphertext* back into the *plaintext*.

The security of this operation is based on the mathematical soundness of the ciphers. The encryption process uses a hidden key to transform the plaintext. This process will be further explained later. The size of the keys is important in gaging the security of an algorithm. These keys are usually at least 128-bit long, meaning that a *brute force* attack on the ciphertext would require testing out  $2^{128}$  possibilities, which would take more time to compute on the best supercomputer available than the age of the universe, by an unfathomable margin. There are other types of attacks, some of which will be covered later, but reliable attacks cannot only use the mathematical properties of the algorithms.

Although ciphers share these properties, there are many of them and each have their specificities.

## 2.2 Symmetric Cryptography

In symmetric cryptography, a single hidden key is shared between both users. Keeping this secret is the keystone of symmetric cryptography as if any of the users has his key disclosed, the entire security falls apart. The main issue with this type of cipher is therefore to ensure that both users get access to the secret key without having anyone else get a hold of that key. Symmetric cryptography can be divided in two main classes of algorithms which are *stream ciphers* and *block ciphers*.

## 2.2.1 Stream Ciphers

Stream ciphers [69] are based on bit sequence encryption using a pseudo random *key-stream*. This *key-stream* is generated with a *Linear Feedback Shift Register* (LFSR) using the secret key as a seed. There are two main types of stream ciphers:

- Synchronous Stream Ciphers: which use a *key-stream* independent of the plaintext or ciphertext. The *key-stream* is generally XORed with the plaintext. This method requires bit-level synchronization between the sender and the receiver.

- Self-Synchronizing Stream Ciphers: which uses a key-stream based of previous ciphertext or ciphertexts. This method is less demanding but is also more sensible to certain types of attacks, as any bit disruption in the plaintext results in the same bit being modified in the ciphertext.

This type of cipher is well adapted to certain types of communication where the package size is unknown and can vary such as mobile phone conversations. They are also efficient in terms of hardware and fit well embedded applications. Their main issue remains their levels of security which appears to be lower than that of block ciphers [48].

#### 2.2.2 Block Ciphers

As their name suggest, block ciphers do their encryption and decryption on *blocks*, which is a subdivision of a message in groups of a defined number of bit. The most common block sizes are 64-bits and 128-bits, although some more recent algorithms have opted to increase their block sizes ([13], [27], [52]). Block Ciphers apply a series of mathematical functions (linear and non-linear) which together form a *round*. The linear functions are two folds, first there is the *key addition*, second the *permutation*, which can also be combined with XORs to make matrix multiplication functions. The non-linear function is the *substitution*. These operations will be covered in more details later. This *round* is repeated a certain number of times, which depends on the algorithm itself and the security/latency equilibrium. The plaintext, the ciphertext and the intermediate values or collectively referred to as the *state*.

Block ciphers usually require a mode of operation in order to be used correctly, there are four of them [28]:

- Electronic Code Book (ECB) mode: Each plaintext is encrypted (and decrypted) separately. This may cause a security issue as the same plaintext is encrypted into the same ciphertext meaning that patterns may appear over large amount of data or when the same data block is used regularly.

- Cipher Block Chaining (CBC) mode: Each plaintext (resp. ciphertext) block is XORed with the previous ciphertext (resp. plaintext) block during encryption (resp. decryption). An initializing vector is used for the first plaintext (resp. ciphertext).

- Cipher Feedback (CFB) mode: Operates like the self-synchronizing stream ciphers (Cf. Sect. 2.2.1).

- Output Feedback (OFB) mode: Operates like the synchronous stream ciphers (*Cf.* Sect. 2.2.1).

## 2.2.3 Key Scheduling

The secret key is essential in providing security, and the level of security is based on the key size. Nonetheless, using the exact same key multiple times in a row in each round of a block ciphers can cause certain patterns to appear which could lead to specific attacks which strongly decrease the security level. The solution to this problem is to use *key scheduling*. Key scheduling consists in modifying the key using a specific algorithm in order to obtain a different key for each of the cipher's rounds called *round keys*. It is essential in ensuring the security and must itself be as mathematically reliable as the cipher itself to ensure it cannot be attacked [30].

Each algorithm has its own specific *key scheduling*, which may use both linear and non-linear functions. To lower complexity some ciphers re-use some parts of the cipher itself. *Key scheduling* is also useful in ensuring the entire 128 bits of key information is used to encrypt 64-bit size block ciphers.

# 2.3 Types of Block Ciphers

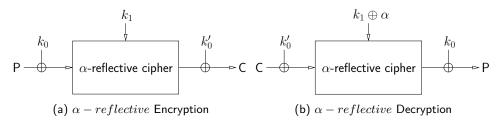

There are two main architectures for common block ciphers, Feistel Networks and Substitution and Permutation Networks (SPN). The algorithms that belong to these families have similar architectures with some differences in the sub-part functions and execution order. The most iconic examples are the Data Encryption Standard (DES) [75] and the Advanced Encryption Standard (AES) [29] that have respectively a Feistel and an SPN architecture. Another interesting subcategory of block ciphers, especially in the context of Lightweight Block Ciphers, is the  $\alpha$ -reflective architecture which can be illustrated with the PRINCE cipher [19].

## 2.3.1 Feistel and Generalized Feistel Network (GFN)