# Transient obfuscation for HLS security: application to cloud security, birthmarking and hardware Trojan defense

Hannah Badier

### ► To cite this version:

Hannah Badier. Transient obfuscation for HLS security : application to cloud security, birthmarking and hardware Trojan defense. Cryptography and Security [cs.CR]. ENSTA Bretagne - École nationale supérieure de techniques avancées Bretagne, 2021. English. NNT : 2021ENTA0012 . tel-03789700

## HAL Id: tel-03789700 https://theses.hal.science/tel-03789700

Submitted on 27 Sep 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

L'ECOLE NATIONALE SUPÉRIEURE DE TECHNIQUES AVANCÉES BRETAGNE

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

# Par Hannah BADIER

# **Transient Obfuscation for HLS Security**

Application to Cloud Security, Birthmarking and Hardware Trojan Defense

Thèse présentée et soutenue à ENSTA Bretagne, Brest, le 29/04/2021 Unité de recherche : Laboratoire Lab-STICC, UMR 6285

#### Rapporteurs avant soutenance :

Lilian BOSSUETProfesseur des Universités, Université Jean Monnet, Laboratoire Hubert Curien, Saint-EtienneRoselyne CHOTINMaître de Conférences, HDR, Sorbonne Université, LIP6 Paris

#### **Composition du Jury :**

| Président :                                                 | Régis LEVEUGLE                                                               | Professeur des Universités, Université Grenoble Alpes, TIMA                                                                                                                                                                            |

|-------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Examinateurs :                                              | Christian PILATO                                                             | Assistant Professor, Ecole Polytechnique de Milan, Italie                                                                                                                                                                              |

| Dir. de thèse :<br>Co-dir. de thèse :<br>Encadr. de thèse : | Bertrand LE GAL<br>Guy GOGNIAT<br>Philippe COUSSY<br>Jean-Christophe LE LANN | Maître de Conférences, ENSEIRB Matmeca, Laboratoire IMS, Talence<br>Professeur des Universités, UBS Lorient, Lab-STICC<br>Professeur des Universités, UBS Lorient, Lab-STICC<br>Enseignant-Chercheur, ENSTA Bretagne, Lab-STICC, Brest |

# Contents

| C  | onter             | $\mathbf{nts}$ |                                     | iii |  |

|----|-------------------|----------------|-------------------------------------|-----|--|

| Li | List of Figures v |                |                                     |     |  |

| Li | st of             | Table          | S                                   | vii |  |

| In | trod              | uction         |                                     | 1   |  |

| 1  | Bac               | kgrou          | nd and Related Work                 | 7   |  |

|    | 1.1               | Hardv          | vare Design Process                 | 7   |  |

|    |                   | 1.1.1          | IC Design Cycle                     | 7   |  |

|    |                   | 1.1.2          | HLS                                 | 12  |  |

|    |                   | 1.1.3          | Hardware IPs                        | 14  |  |

|    |                   | 1.1.4          | Hardware Design Threats             | 15  |  |

|    | 1.2               | Hardv          | vare IP Protection                  | 18  |  |

|    |                   | 1.2.1          | Foundry                             | 18  |  |

|    |                   | 1.2.2          | Layout Level and Gate-Level Netlist | 19  |  |

|    |                   | 1.2.3          | RTL                                 | 24  |  |

|    |                   | 1.2.4          | Behavioral                          | 26  |  |

|    |                   | 1.2.5          | Threats and Countermeasures         | 28  |  |

|    | 1.3               | Softwa         | are Obfuscation                     | 29  |  |

|    |                   | 1.3.1          | Definition and Principles           |     |  |

|    |                   | 1.3.2          | Threat Models and Use cases         |     |  |

|    |                   | 1.3.3          | Taxonomy and Common Transformations |     |  |

|    |                   | 1.3.4          | Commercial and Open-source Tools    |     |  |

|    |                   | 1.0.1          |                                     |     |  |

### CONTENTS

|   |     | 1.3.5  | Evaluation Metrics                                    | 36 |

|---|-----|--------|-------------------------------------------------------|----|

|   | 1.4 | Conclu | usion                                                 | 37 |

| 2 | Tra | nsient | Obfuscation against IP Theft during Cloud-based HLS   | 39 |

| - | 2.1 |        | t Model                                               | 40 |

|   |     | 2.1.1  | HLS-as-a-Service                                      | 40 |

|   |     | 2.1.2  | Threat Model                                          | 41 |

|   | 2.2 | Relate | ed Work and Background                                | 42 |

|   |     | 2.2.1  | Cloud Computing Challenge: Ensuring Data Security     | 42 |

|   |     | 2.2.2  | Algorithm Level Obfuscation                           | 43 |

|   | 2.3 | Propo  | sed Approach: Transient Obfuscation                   | 44 |

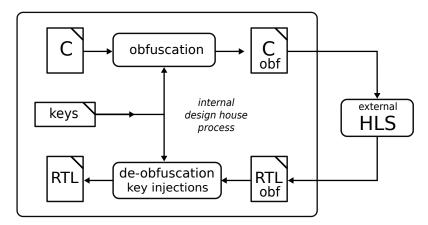

|   |     | 2.3.1  | Transient Obfuscation                                 | 44 |

|   |     | 2.3.2  | Complete Flow                                         | 46 |

|   | 2.4 | Propo  | sed Obfuscation Techniques                            | 48 |

|   |     | 2.4.1  | Bogus Code Insertion                                  | 48 |

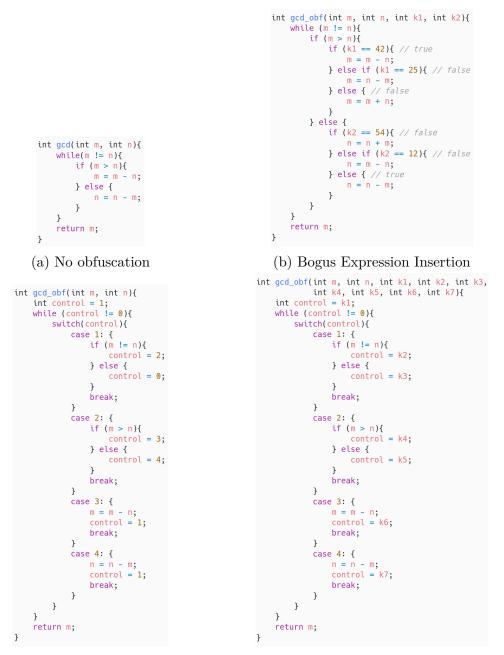

|   |     | 2.4.2  | Control Flow Flattening                               | 52 |

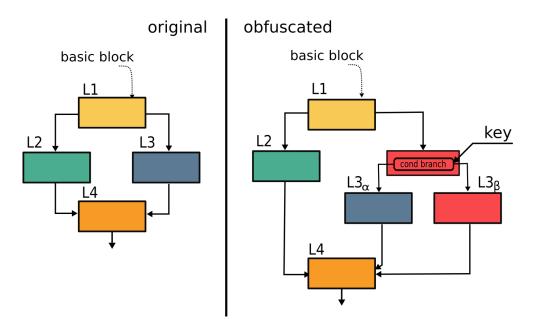

|   |     | 2.4.3  | Further Hiding of the Control Flow                    | 54 |

|   |     | 2.4.4  | Data Obfuscation by Literal Replacement               | 55 |

|   | 2.5 | De-ob  | fuscation: Making the Process Transient               | 56 |

|   |     | 2.5.1  | Pedagogical Example                                   | 57 |

|   |     | 2.5.2  | Naive Key Injection                                   | 58 |

|   |     | 2.5.3  | Targeted RTL Modification                             | 60 |

|   |     | 2.5.4  | Full RTL De-obfuscation                               | 61 |

|   | 2.6 | KaOT   | THIC: Key-based Obfuscating Tool for HLS In the Cloud | 62 |

|   |     | 2.6.1  | Obfuscation Flow                                      | 62 |

|   |     | 2.6.2  | Adding Randomness                                     | 63 |

|   |     | 2.6.3  | Obfuscation Parameters                                | 64 |

|   | 2.7 | Exper  | imental Setup and Results                             | 65 |

|   |     | 2.7.1  | Test Flow                                             | 65 |

|   |     | 2.7.2  | Overhead - Results and Analysis                       | 66 |

|   |     | 2.7.3  | Transience and Security: Discussion                   | 71 |

|   | 2.8 | Conch  | usion                                                 | 73 |

iv

| 3 | Tra | nsient | Obfuscation for BIP Birthmarking                                                                | 75  |

|---|-----|--------|-------------------------------------------------------------------------------------------------|-----|

|   | 3.1 | Threa  | t Model and Background                                                                          | 76  |

|   |     | 3.1.1  | Threat Model                                                                                    | 76  |

|   |     | 3.1.2  | Watermarking                                                                                    | 77  |

|   |     | 3.1.3  | Effects of Code Transformations on High-Level Synthesis                                         | 78  |

|   | 3.2 | Relate | ed Work                                                                                         | 79  |

|   |     | 3.2.1  | BIP Watermarking Techniques                                                                     | 79  |

|   |     | 3.2.2  | Software Watermarking Techniques                                                                | 79  |

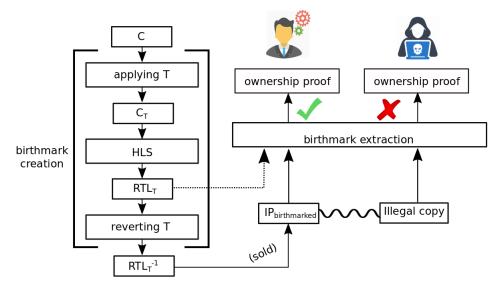

|   | 3.3 | Prope  | sed Approach                                                                                    | 80  |

|   |     | 3.3.1  | Complete Flow and Notations                                                                     | 80  |

|   |     | 3.3.2  | Watermark Insertion                                                                             | 82  |

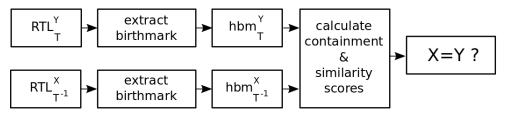

|   |     | 3.3.3  | Watermark Verification: Birthmarking Concepts                                                   | 83  |

|   | 3.4 | Metrie | cs for Watermark Verification                                                                   | 87  |

|   |     | 3.4.1  | Scheduling                                                                                      | 87  |

|   |     | 3.4.2  | Dataflow                                                                                        | 91  |

|   | 3.5 | Imple  | mentation and Experimental Setup                                                                | 96  |

|   |     | 3.5.1  | Experimental Setup and Dataset                                                                  | 96  |

|   |     | 3.5.2  | Scheduling                                                                                      | 97  |

|   |     | 3.5.3  | Dataflow                                                                                        | 97  |

|   |     | 3.5.4  | Crokus                                                                                          | 98  |

|   | 3.6 | Result | ts and Analysis                                                                                 | 99  |

|   |     | 3.6.1  | Scheduling                                                                                      | 99  |

|   |     | 3.6.2  | Dataflow                                                                                        | 105 |

|   |     | 3.6.3  | Benchmark Results                                                                               | 108 |

|   | 3.7 | Concl  | usion $\ldots$ | 110 |

| 4 | Tra | nsient | Obfuscation against Hardware Trojan Insertion                                                   | 111 |

| - | 4.1 |        | t Model and Definitions                                                                         |     |

|   |     | 4.1.1  | Hardware Trojans                                                                                |     |

|   |     | 4.1.2  | Threat Model                                                                                    |     |

|   |     | 4.1.3  | Examples of HTs in BIPs                                                                         |     |

|   | 4.2 |        | vare Trojan Countermeasures: Related Work                                                       |     |

|   | 1.4 | 4.2.1  | Detection and Run-time Monitoring                                                               |     |

|   |     | 1.4.1  |                                                                                                 | 110 |

### CONTENTS

|         | 4.2.2  | Design for Security                                                                             | 120 |

|---------|--------|-------------------------------------------------------------------------------------------------|-----|

| 4.3     | Propo  | sed Countermeasures for Hardware Trojan Insertion during                                        |     |

|         | HLS    |                                                                                                 | 121 |

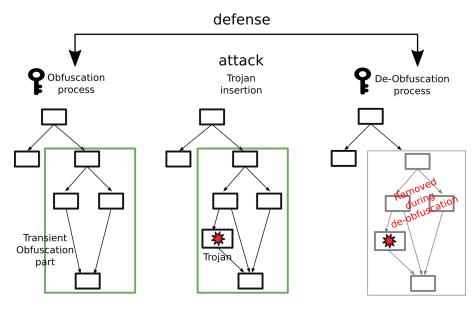

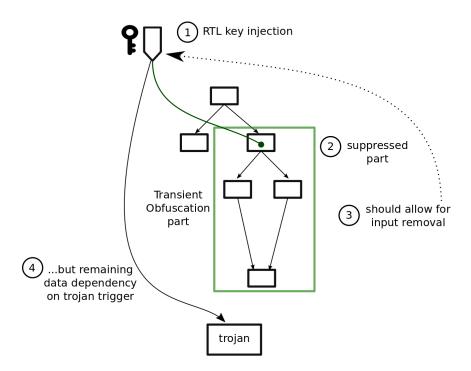

|         | 4.3.1  | Payload: Removal by De-obfuscation                                                              | 121 |

|         | 4.3.2  | Combinational Trigger: Detection during De-obfuscation                                          | 124 |

| 4.4     | Exper  | imental Setup and Preliminary Results                                                           | 127 |

|         | 4.4.1  | "Collatz" Hardware Trojan                                                                       | 127 |

|         | 4.4.2  | HT Removal                                                                                      | 129 |

|         | 4.4.3  | Discussion                                                                                      | 132 |

| 4.5     | Conclu | usion $\ldots$ | 133 |

| Conclu  | sion   |                                                                                                 | 135 |

| List of | publis | shed contributions                                                                              | 139 |

| Bibliog | graphy |                                                                                                 | 141 |

# List of Figures

| 1.1  | Gajski-Kuhn Y chart                                                            | 8    |

|------|--------------------------------------------------------------------------------|------|

| 1.2  | IC design flow.                                                                | 10   |

| 1.3  | HLS design flow.                                                               | 13   |

| 1.4  | HT attacks at different design stages. (from $[Bhu+14]$ )                      | 17   |

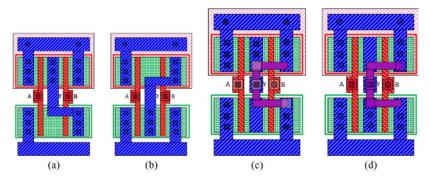

| 1.5  | Standard and camouflaged cell layouts for NAND [(a) and (c)] and               |      |

|      | NOR [(b) and (d)] gates. (from $[Raj+13]$ )                                    | 21   |

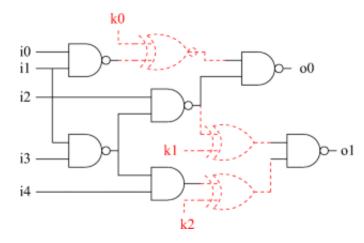

| 1.6  | Logic locking example on c17 benchmark. The correct key inputs                 |      |

|      | are k0=1, k1=0, k2=1. (from $[DF19]$ )                                         | 22   |

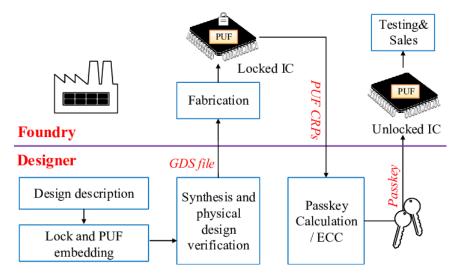

| 1.7  | Active hardware metering design flow. (from [CZZ17])                           | 23   |

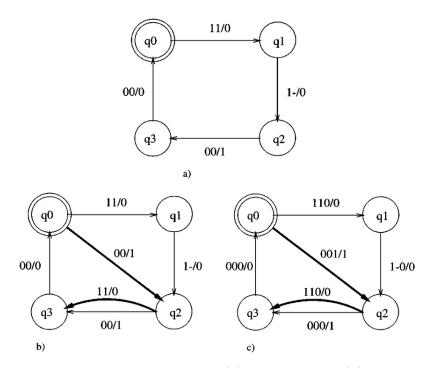

| 1.8  | FSM watermarking example: (a) original FSM, (b) adding transi-                 |      |

|      | tions, (c) augmenting input and adding transitions. (from $[TC00]$ )           |      |

|      |                                                                                | 24   |

| 1.9  | Modified FSM for key-based RTL obfuscation. (from $[CB10]$ )                   | 25   |

| 1.10 | Classification of obfuscating transformation mechanisms. (from $[{\rm Hos}+1]$ | [8]) |

|      |                                                                                | 33   |

| 2.1  | Vulnerable HLS in the cloud design flow.                                       | 42   |

| 2.2  | HLS in the cloud design flow secured by KaOTHIC, where the ex-                 |      |

|      | ternal HLS is considered untrusted.                                            | 47   |

| 2.3  | Behavioral and dataflow representation of a code with bogus code               |      |

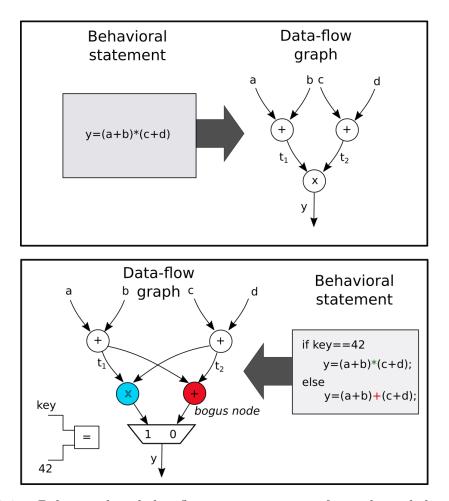

|      | insertion                                                                      | 49   |

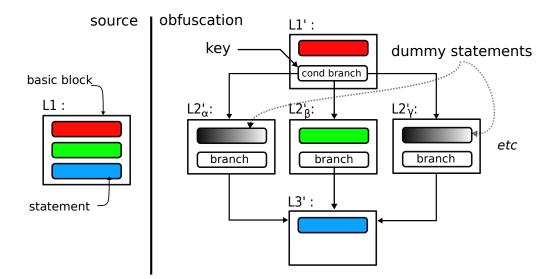

| 2.4  | Basic block example before and after obfuscation: insertion of two             |      |

|      | bogus expressions                                                              | 50   |

| 2.5  | Different obfuscation techniques applied by KaOTHIC to a function              |      |

|      | calculating the gcd of two numbers                                             | 51   |

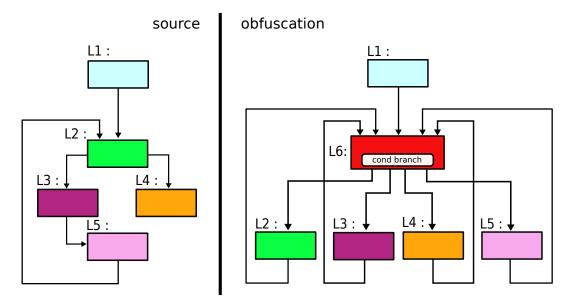

| 2.6  | Example CFG before and after obfuscation by adding bogus basic blocks.    | 52 |

|------|---------------------------------------------------------------------------|----|

| 2.7  | Example CFG before and after obfuscation by control flow flattening.      | 53 |

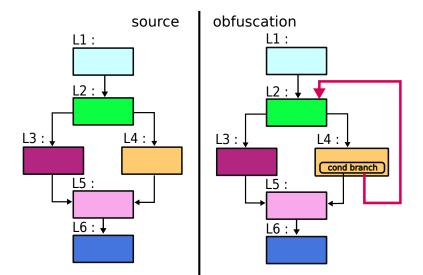

| 2.8  | Example CFG before and after obfuscation by adding bogus tran-<br>sitions | 55 |

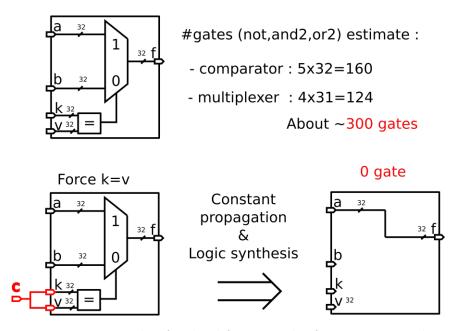

| 2.9  |                                                                           | 57 |

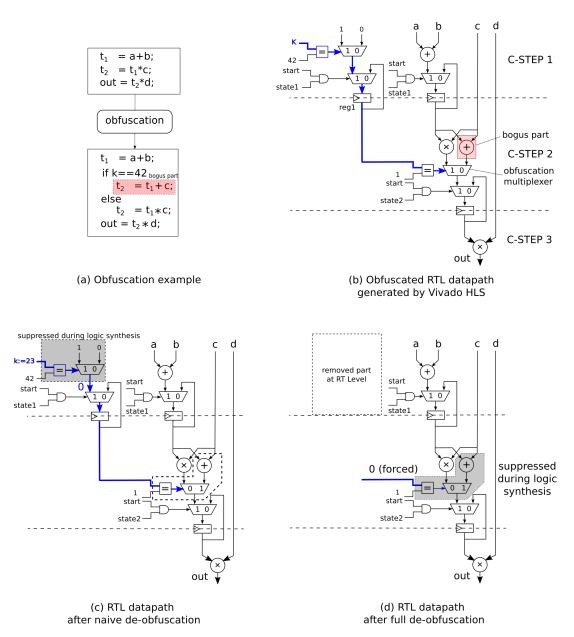

|      |                                                                           | 59 |

|      |                                                                           | 62 |

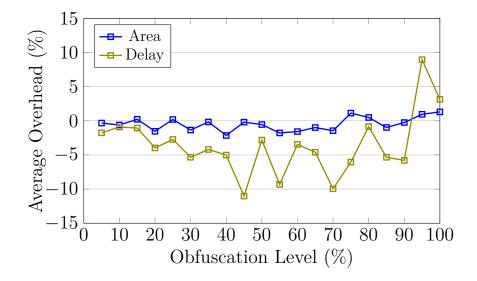

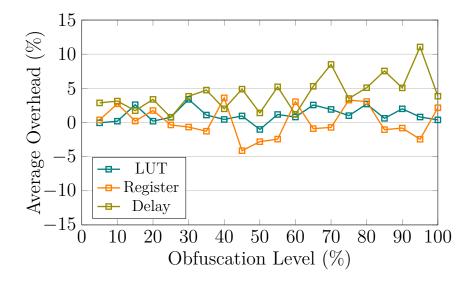

|      | Average design overhead per obfuscation level, for bogus expression       | 68 |

| 2.13 | Average design overhead per obfuscation level, for bogus expression       |    |

|      | insertion - FPGA                                                          | 68 |

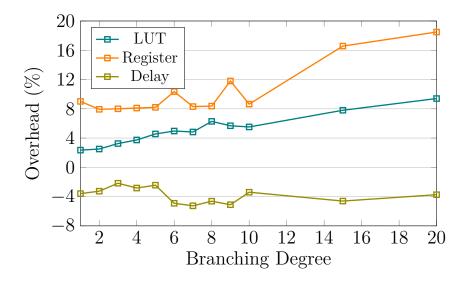

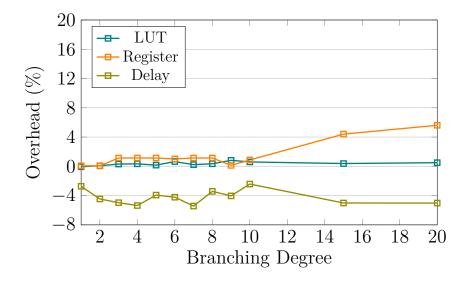

| 2.14 | Design overhead per branching degree, for bogus basic block inser-        |    |

|      |                                                                           | 69 |

| 2.15 | Design overhead per branching degree, for bogus basic block inser-        |    |

|      |                                                                           | 70 |

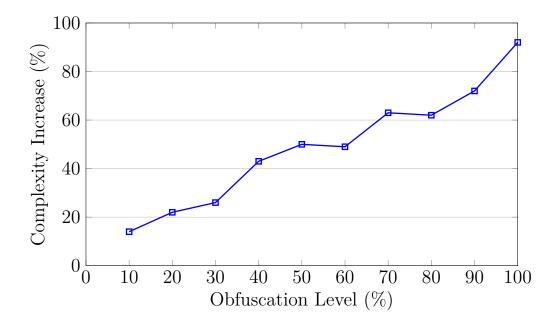

| 2.16 | Cyclomatic complexity increase of Needwun source code after ob-           |    |

|      | fuscation per obfuscation level                                           | 72 |

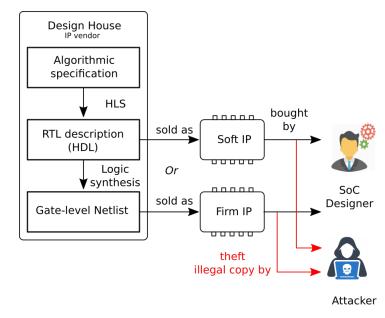

| 3.1  | Watermarking Threat Model.                                                | 76 |

| 3.2  | Watermarking Flow.                                                        | 81 |

| 3.3  | Birthmark Extraction Flow.                                                | 85 |

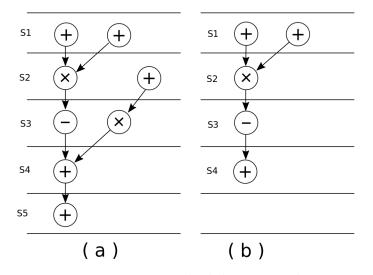

| 3.4  | Two scheduling examples.                                                  | 89 |

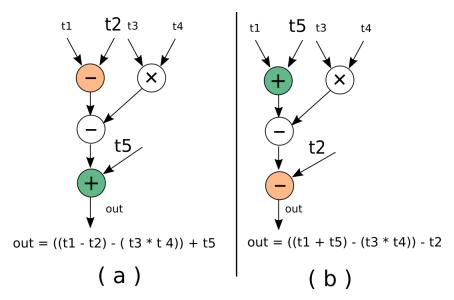

| 3.5  | Partial DFG of original and obfuscated code                               | 91 |

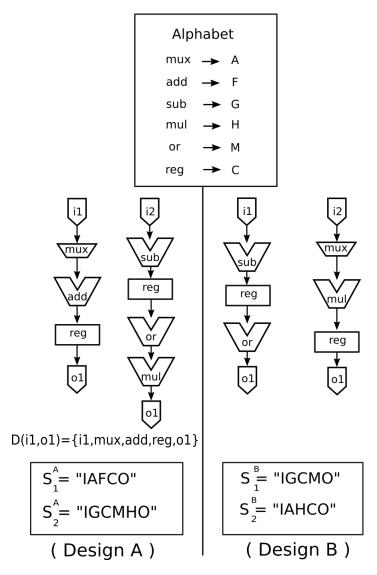

| 3.6  | Example of dataflow sequences for two designs.                            | 94 |

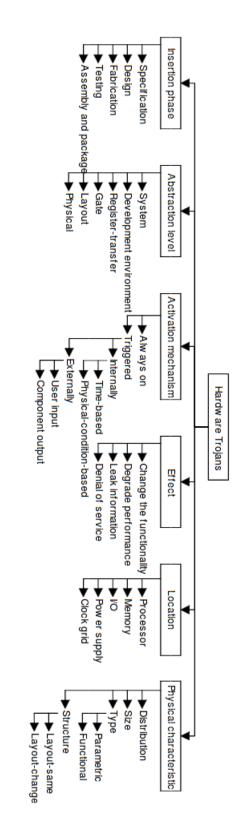

| 4.1  | HT Taxonomy - Trust-Hub.org                                               | 14 |

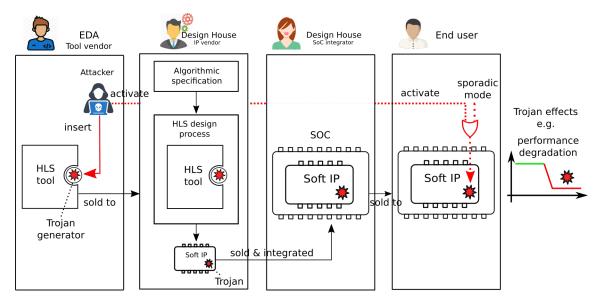

| 4.2  | HT insertion by HLS tool - threat model                                   | 15 |

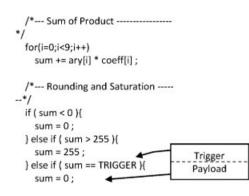

| 4.3  | Simple example of a HT inserted in a BIP. (from $[VS16]$ ) 1              | 17 |

| 4.4  | HT removal by de-obfuscation flow                                         | 22 |

| 4.5  | HT detection during de-obfuscation                                        | 25 |

| 4.6  | No Trojan, these lines are removed during de-obfuscation 1                | 26 |

| 4.7  | Key1 and Input1 are used as triggers for the Trojan                       | 26 |

### LIST OF FIGURES

| 4.8 | Code example of a Collatz HT inserted in a greatest common divisor                       |     |

|-----|------------------------------------------------------------------------------------------|-----|

|     | $calculation.  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 128 |

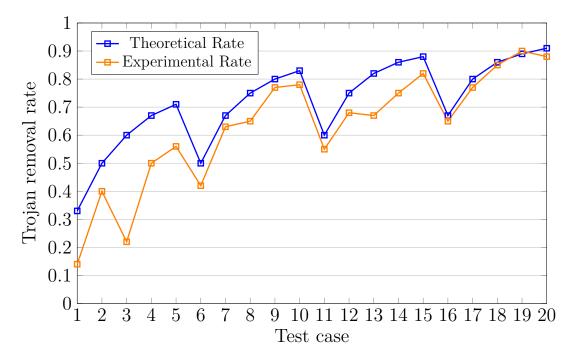

| 4.9 | Theoretical and experimental HT removal rate.                                            | 131 |

# List of Tables

| 1.1  | Common hardware threats and countermeasures                             |

|------|-------------------------------------------------------------------------|

| 2.1  | Average design overhead on ASIC                                         |

| 2.2  | Average design overhead on FPGA                                         |

| 3.1  | Similarity and containment of scheduling: experimental results 99       |

| 3.2  | Using scheduling containment as classifier: experimental results. $101$ |

| 3.3  | Using scheduling similarity as classifier: experimental results $102$   |

| 3.4  | Similarity and containment of scheduling: experimental results with     |

|      | obfuscation level $\geq 50\%$                                           |

| 3.5  | Using scheduling similarity and containment as classifier: ex-          |

|      | perimental results with obfuscation level $\geq$ 50% 103                |

| 3.6  | Similarity and containment of scheduling: experimental results with     |

|      | 5% bogus operators                                                      |

| 3.7  | Using scheduling similarity and containment as classifier: experi-      |

|      | mental results with 5% bogus operators                                  |

| 3.8  | Containment of dataflow: experimental results with obfuscation          |

|      | $level \ge 50\%106$                                                     |

| 3.9  | Similarity (Levenshtein) of dataflow: experimental results with         |

|      | obfuscation level $\geq 50\%$                                           |

| 3.10 |                                                                         |

|      | obfuscation level $\geq 50\%$                                           |

| 3.11 | Using dataflow containment and similarities as classifiers: experi-     |

|      | mental results                                                          |

| 3.12 | Similarity and containment of scheduling: experimental results with |

|------|---------------------------------------------------------------------|

|      | obfuscation level $\geq 50\%$ for <b>adpcm</b>                      |

| 3.13 | Similarity and containment of scheduling: experimental results with |

|      | obfuscation level $\geq 50\%$ for <b>AES</b>                        |

| 3.14 | Using scheduling similarity and containment as classifier: experi-  |

|      | mental results for <b>adpcm</b>                                     |

| 3.15 | Using scheduling similarity and containment as classifier: experi-  |

|      | mental results for <b>AES</b>                                       |

| 4 1  |                                                                     |

| 4.1  | HT Removal Rate: Experimental Results                               |

xii

# Introduction

### Context

In 1959, Jack Kilby at Texas Instruments and Robert Noyce of Fairchild Semiconductor Corporations both worked independently and received patents for the invention of the first integrated circuit (IC). Made of a large number of transistors and based on semiconductor material such as silicon, the IC quickly became the basis of almost all modern electronics. Today, this invention has changed not only the world of electronics, but every aspect of our society. Computers, mobile phones and other portable devices, gaming consoles, modern cars, and even household appliances all rely on ICs. Semiconductors are now present everywhere, at an incredible amount. No other device in history has been manufactured as often as the transistor<sup>1</sup>. The global IC market has reached \$360 billion in 2020<sup>2</sup>, and is expected to grow to \$468 billion by 2025. The main growth driver nowadays is the increasing use of connected devices and the widespread adoption of the internet of things (IoT) in everyday life. This continuous increase of sales can also be linked to the significant leaps that the industry continues to make in regards to ever higher performances and always smaller size.

However, this frantic market growth and continuing improvements have also lead to tighter time-to-market constraints, while ICs have steadily become more

<sup>&</sup>lt;sup>1</sup>13 Sextillion & Counting: The Long & Winding Road to the Most Frequently Manufactured Human Artifact in History. https://computerhistory.org/blog/13-sextillioncounting-the-long-winding-road-to-the-most-frequently-manufactured-humanartifact-in-history/

<sup>&</sup>lt;sup>2</sup>Integrated Circuits Global Market Report 2021. https://www. thebusinessresearchcompany.com/report/integrated-circuits-global-marketreport

complex, time-consuming and expensive to produce. These factors have lead to a globalization and a fragmentation of the whole IC supply chain, including both manufacturing and the design process.

Most semiconductor companies used to be integrated device manufacturers (IDM), meaning that they were responsible for both design and manufacturing. Nowadays, the cost of building new foundries to keep up with technological advances has become prohibitively expensive: market leader TSMC's newest foundry for 3nm technology, expected to start production in 2022, has been estimated to cost up to \$20 billion<sup>3</sup>. Today, it is no longer economically viable for most companies to build and maintain their own foundries. Only a few IDMs such as Texas Instruments and Intel remain. Most of the industry has evolved to a dual model, where design and manufacturing are completely separated: *fabless* companies, such as Nvidia or AMD, are responsible for design of new ICs, while *pure-play* foundries such as TSMC or UMC manufacture the devices for them. Moreover, test, assembly and packaging are increasingly getting outsourced as well, to so-called outsourced semiconductor assembly and test (OSAT) vendors.

This fragmentation of the supply chain is also directly affecting the design houses. To be able to keep up with increasingly tight time-to-market constraints, many rely on third party intellectual properties (IPs), reusable blocks of hardware designs sold by specialized vendors. In 2020, the worldwide semiconductor IP market is estimated at \$5.6 billion<sup>4</sup>. Design teams themselves are more and more spread out around the world, with the creation of one design potentially involving specialists located in different countries or even on different continents. Finally, the complexity of modern ICs has imposed the use of elaborate toolchains involving several distinct tools sold by different specialized electronic design automation (EDA) vendors.

This ongoing globalization has opened up many possibilities for industry advancement, but has also created several vulnerabilities to attacks. IP theft and illegal reuse, reverse-engineering, overproducing and counterfeiting are all known

<sup>&</sup>lt;sup>3</sup>TSMC Completes Its 3nm Multi-Billion Fab. https://www.tomshardware.com/news/ tsmc-3nm-fab-completed

<sup>&</sup>lt;sup>4</sup>Semiconductor Intellectual Property (IP) Market - Global Forecast to 2025. https://www.marketsandmarkets.com/Market-Reports/semiconductor-siliconintellectual-property-ip-market-651.html

#### CONTRIBUTIONS

challenges that the IC supply chain faces today. For example, it is estimated that counterfeit ICs represent up to 1% of semiconductor sales ([KP13]), leading to a loss of about \$100 billion of revenue for electronics companies ([PT06]). Malicious modifications of ICs during design or manufacturing in the form of hardware Trojans are also a growing concern. Several incidents that probably constitute hardware Trojan attacks have already been reported: the critical failure of Syria's air defense system during an Israeli air strike in 2017 is reported to have been intentionally triggered remotely through a so-called kill switch hidden in a microprocessor ([Ade08]).

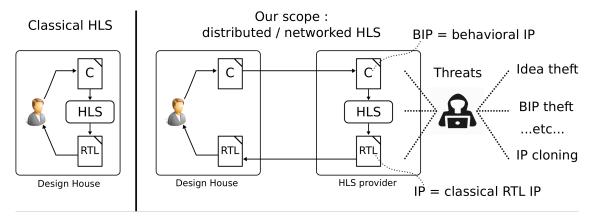

Research efforts in the past years have been concentrated on securing all steps of the IC design cycle, with special focus brought to manufacturing. However, not much attention has been brought so far to the security issues and protection possibilities linked with behavioral synthesis. High-level synthesis (HLS) is a technique that aims at converting untimed, behavioral level descriptions of circuits (e.g. in C/C++) to register transfer level (RTL) descriptions, written in hardware description languages such as VHDL or Verilog. While HLS has been a promising research subject since the 1980's, it has gained renewed attention in the last ten years and is now increasingly adopted by design houses as powerful leverage for increasing design productivity. However, using HLS also introduces new vulnerabilities and new attack vectors in the IC design cycle. While most works consider HLS to be a secure design step, done in-house with trusted tools, some recent publications have raised concerns about security risks at the behavioral level: [Pil+18a] [Bas+19] [VS17a]. It is thus imperative to address the potential threats introduced in the design cycle by HLS, as well as the risks that behavioral level IPs face.

### Contributions

This thesis studies different security issues related to behavioral level IPs and synthesis. It focuses on a novel obfuscation concept and its applications towards security during untrusted, in-house or external HLS, as well as towards securing behavioral IPs before, during and after HLS. The main contributions of this thesis are as follows:

- A novel concept for high-level, key-based hardware obfuscation: transient obfuscation, which involves an obfuscation and a de-obfuscation step to protect IPs at design time, specifically during HLS.

- Several practical techniques for transient obfuscation, created or adapted from existing software obfuscation techniques.

- A fully automated toolset, KaOTHIC, that implements the previous obfuscation techniques, as well as several tools for de-obfuscation.

- Three applications of transient obfuscation, with for each a detailed threat model, a characterization of the approach, a practical implementation and experimental validation:

- 1. A low overhead design flow for untrusted, cloud-based HLS, secured through transient obfuscation.

- 2. A method for exploiting transient obfuscation side effects as a birthmark to identify stolen behavioral IPs.

- 3. Two methods for using transient obfuscation against hardware Trojan insertion during HLS.

## Outline

**Chapter 1** begins by presenting the IC design cycle, with the different steps and actors involved. We give a more in-depth explanation of high-level synthesis, which is the main focus of this thesis. We then give an overview of different security threats, as well as a state-of-the-art of existing IP protection methods at different abstraction levels. Finally, since our focus in this work is on hardware protection at the behavioral source code level, we also give a presentation of software obfuscation principles and techniques.

In **Chapter 2**, we focus on the risk of IP theft during cloud-based HLS. We start by explaining why cloud-based HLS is a likely scenario and giving the security risks involved with this model. After a quick overview of relevant related work and background information on cloud security, we introduce our approach:

#### OUTLINE

*transient obfuscation*. We enumerate several obfuscation techniques and explain different methods for de-obfuscation. This chapter also presents a tool, KaOTHIC, implemented to apply transient obfuscation on C code, and finishes with a series of experiments to test our approach.

Chapters 3 and 4 extend the previous work by showing how transient obfuscation can also be used for other security purposes. In **Chapter 3**, we focus on the subject of stolen behavioral IP identification through watermarking, and in particular birthmarking. After presenting the threat model, as well as background and related work on watermarking, we propose a birthmark-based approach that uses the side-effects of transient obfuscation. We give a detailed presentation of this approach, before providing an experimental setup to validate our method. The end of the chapter presents the experimental results.

Chapter 4 in turn focuses on the subject of protection against hardware Trojans. We start by introducing the threat model, based on the risk of Trojan insertion by a malicious HLS tool, and by presenting related work on Trojan countermeasures. Then we explore two different methods for using transient obfuscation against Trojan insertion. An experiment to validate the first method is described and its results are presented. We also introduce a tool for hardware Trojan insertion in source code, used in the experimental setup.

# Chapter 1

# **Background and Related Work**

The hardware design process is more fragmented and complex than ever. The integrated circuit (IC) design cycle involves a multitude of design and validation steps at different abstraction levels, several actors working together, as well as complex toolchains and methodologies. In this chapter, we start by presenting background information about the IC design cycle, as well as the actors and concepts involved. We also give a short introduction into high-level synthesis, which is the step in the hardware design cycle we focus on in this work. The aforementioned complexity of the hardware design ecosystem has lead to the identification of several security threats. We present three of the main threats: reverse-engineering, piracy and hardware trojan insertion. To thwart these security issues, many methods have been developed. We give an overview of the protection techniques at different abstraction levels, while pointing out works that are relevant to the subject studied in this thesis, security during HLS. Finally, since our work aims at protecting high-level source code, we draw parallels with the software protection world by presenting software obfuscation principles and methods.

## 1.1 Hardware Design Process

#### 1.1.1 IC Design Cycle

Integrated Circuits (ICs), also called chips, are electronic devices based on semiconductors (silicon) and mainly made of transistors. Nowadays, with the advances of very-large-scale integration (VLSI), there are well over ten billion transistors on one chip, with the most recent progress in technology nodes as of 2020 being 3nm transistors. Several different types of ICs are fabricated. SoCs (system on chip) combine all or most components of a computer on a single chip. They contain a processor, memory units and advanced peripherals such as a GPU. ASICs (application specific integrated circuit) were initially ICs without a processor, designed for one specific application, for example in routers or switches. Nowadays most ASICs also have a SoC-type architecture, with one or several processors embedded on the chip. Their topology is decided in advance and not reconfigurable, but they can be parametrized to provide higher flexibility. They are usually manufactured in high volume, since their design cycle is time and resource consuming. In recent years, there has also been increasing interest for FPGAs (field programmable gate array). Contrary to ASICs, FPGAs are reconfigurable and programmable. They are for example used in digital signal processing (DSP) and for prototyping other ICs.

#### **Design Levels**

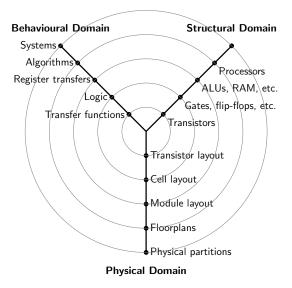

Figure 1.1 – Gajski-Kuhn Y chart.

IC design cycles are complex and can be separated into several steps at different

abstraction levels. These levels have been popularized by Gajski and Kuhn in 1983 in the so-called *Y diagram*, depicted on Figure 1.1. This chart shows three different domains used to describe hardware development: behavioral, structural and physical. Each axis on the diagram represents one domain in a top-down approach.

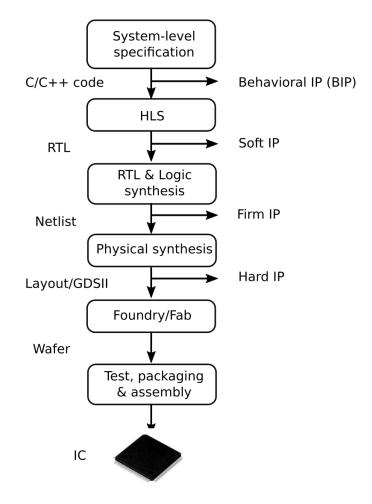

On Figure 1.2, the full design cycle with following abstraction levels is depicted:

- System level: during system specification, the functional requirements and external interfaces of the system (IC) are defined.

- Behavioral level: at this level, the function of the IC is described as an algorithm using high level languages such as C/C++ or SystemC. High-level synthesis (see Section 1.1.2) is used to convert this description into RTL.

- Register-Transfer Level (RTL): the complete IC design is captured using hardware description languages (HDLs) such as Verilog or VHDL. At this level, the circuit is modeled using sequential logic (registers) and combinational logic. The circuit is timed and its interfaces (input/output pins) and connectivity are defined. Logic synthesis is used to convert a RTL description into a gate-level netlist

- Gate-level netlist: at this level, the IC is implemented for a specific technology library in terms of interconnected logic gates, memory elements (flip-flops) and inverters. The netlist contains all the components of the circuit and their connectivity. A physical synthesis is then used to further specify the design.

- Layout level: during physical synthesis, several technology-specific steps such a floorplanning, partitioning, place-and-route are performed. These result in a low-level netlist, and finally in a graphical database system (GDSII) file, a binary file used to describe the full IC which can be sent to the foundry.

#### **IC Design Actors**

The ever-growing complexity and worldwide distribution of the IC supply chain means that there is a growing number of distinct actors involved in the design of

Figure 1.2 – IC design flow.

an IC. Each of these actors adds new vulnerabilities to the whole design flow.

- **Customer**: the customer orders an IC by giving the specifications, usually at system level, to a design house.

- **Design house**: the design house defines the IC's specifications and performs the different design steps up to the physical layout, including several testing and verification steps. During this process, reusable intellectual property (IP) blocks from external vendors can be bought and combined with inhouse components. The biggest design houses include Broadcom, Qualcomm, Nvidia and AMD.

- Third-party IP (3PIP) vendors: these vendors sell specialized IP blocks at different abstraction levels (see Section 1.1.3). The IPs are already optimized and are widely used nowadays: the global IP market is expected to reach \$8.81 billion by 2026<sup>1</sup>. By using 3PIPs, the design house can reduce design costs and reach better time to market thanks to faster design cycles.

- Foundry: Foundries are responsible for manufacturing wafers and dies. The cost of building a new fab has been steadily increasing, reaching over \$1 billion. The latest foundries for 3nm technology have been estimated to cost up to \$20 billion<sup>2</sup>. Due to this high entry cost, most design houses have moved to a *fabless* model, meaning that they outsource IC fabrication to specialized foundries instead of having an in-house foundry. Most of the foundries, e.g. TSMC, are located in China and Taiwan.

- Assembly: After fabrication, a separate actor is often responsible for packaging and testing of the IC, before shipping it to the design house or directly to market.

- EDA tool vendors: The growing complexity of IC design has led to the need for specialized tools such as high-level and logic synthesis tools or sim-

<sup>&</sup>lt;sup>1</sup>Global Semiconductor Intellectual Property (IP) Market Analysis 2020. https:// www.researchandmarkets.com/reports/5236592/global-semiconductor-intellectualproperty-ip

<sup>&</sup>lt;sup>2</sup>TSMC Completes Its 3nm Multi-Billion Fab. https://www.tomshardware.com/news/ tsmc-3nm-fab-completed

ulation tools. Electronic design automation (EDA) tool vendors sell their tools to design houses. The best known vendors include Synopsys, Cadence and MentorGraphics.

#### 1.1.2 HLS

To deal with the ever growing complexity of hardware systems and need for better design productivity, abstraction levels have been raised several times over the years, along with an increased automation of design methods and tools. Since the 1980s, low-level design at the gate and layout level has been replaced with the use of dedicated hardware description languages (HDL), mostly at register transfer level (RTL). The two most used HDLs are VHDL and Verilog. More recently, there has been a trend towards using new HDLs based on domain specific languages (DSLs) hosted by mainstream programming languages [Ker+19][LBK20]. At even higher abstraction level, high-level synthesis (HLS) has been a serious research subject since the 1990s, when the first commercial tools were made available [Kna96]. HLS tools transform an algorithmic level, usually untimed, description of an application into a fully timed hardware implementation at RTL. The resulting architecture, usually described using a HDL such as Verilog or VHDL, contains a controller, a data path, memory banks and communication interfaces [Cou+09].

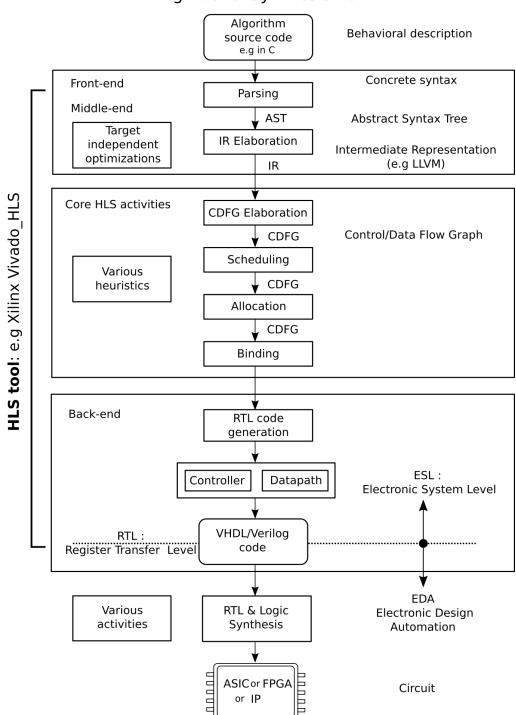

As shown on Figure 1.3, HLS tools perform the following tasks: parsing the source code, generating internal representations (IR, CDFG), allocation, scheduling, binding, and RTL generation. Allocation, scheduling and binding are usually performed in sequence, but the particular order can vary depending on the HLS tool [WC12]. These steps are detailed below.

#### Front- and Middle-end

The first HLS step starts with a algorithm's source code written in a high level language such as C, C++ or SystemC. A compiler front-end parses this code into an abstract syntax tree (AST), and then elaborates an intermediate representation (IR), which is chosen to ease development of most optimization passes. IRs such as LLVM or Gimple present themselves as assembly code independent from the final target. They provide an unlimited amount of registers and usually take a static

High-Level Synthesis flow

Figure 1.3 – HLS design flow.

single assignment (SSA) form, which explicitly describes dataflow relationships between variable definitions, assignments and uses. At this level, several optimization passes such as for example dead code removal or loop unrolling are performed. Finally a control and data flow graph (CDFG) is built to formally represent all data dependencies (in the form of basic blocks) and control dependencies (in the form of edges between the basic blocks).

#### Scheduling, Allocation and Binding

During the scheduling step, each operation is scheduled into one or several clock cycles. Several operations can be scheduled in parallel as long as there are no data dependencies between them. During allocation, the hardware resources necessary for the design are selected from an RTL component library. These resources include functional units and storage units. During binding, each operation is bound to one of these functional units, and each variable to one of the storage units. Resources can be shared by several operations or variables. Detailed presentations of these steps and the algorithms used for optimizing them can be found for instance in [Gaj+92].

#### Back-end

During the back-end step, the RTL architecture in form of a datapath and a controller is generated according to the design decisions taken during scheduling, allocation and binding. The datapath is made of functional units and registers and other storage elements, while the controller is a finite state machine (FSM) which controls the data flow. Finally, RTL code, usually written in a HDL such as Verilog is generated.

#### 1.1.3 Hardware IPs

Intellectual Property (IP) blocks, i.e. reusable components, are now widely integrated into hardware design cycles.

Different IP block types have been defined at different abstraction levels, as shown on Figure 1.2:

#### 1.1. HARDWARE DESIGN PROCESS

- Hard IPs: these IPs are mapped to a specific technology and are fully optimized in terms of performance. They are usually sold as low level circuit descriptions, for example in the form of fully placed and routed netlist, or full physical layouts.

- Firm IPs: these IPs are less specific than hard IPs, while still optimized for performance. They are sold as detailed floorplans combined with a netlist and usually synthesizable RTL. Contrary to hard IPs, firm IPs are not routed and are less technology dependent.

- Soft IPs: these IPs are defined at high level and usually sold in the form of synthesizable HDL (Hardware Description Language) code. They are more flexible and easier to modify and adapt than other IPs, but also offer less predictable performances in terms of timing, area, power consumption etc.

- Behavioral IPs (BIPs): BIPs have similar properties to soft IPs, but are sold as a description at behavioral level.

#### 1.1.4 Hardware Design Threats

The complexity and distributed character of hardware design cycles, with the involvement of several different actors, creates several different threats on design data and ICs.

#### **Reverse-Engineering**

Reverse-engineering an IC means trying to identify its functionality, design and structure. It can have several goals such extracting the transistor-level or gate-level netlist [VD01], identifying what technology is used, or understanding the functionality. Several tools and techniques have been developed to facilitate reverse-engineering. Reverse-engineering can be performed by several actors:

- IC user: the end user can de-package and delayer an IC, capture images of these layers and then using them to extract the netlist.

- Foundry: an attacker in the foundry can use the IC layout to reverse-engineer it.

• Higher level: during earlier design steps, for example during SoC integration, external IPs can also be reverse-engineered.

Design steps earlier in the flow are particularly vulnerable to reverse-engineering, for example BIPs and soft IPs, due to their better readability and high level of abstraction. Once reverse-engineering has been successfully performed, the IC or IP can easily be modified, copied and/or illegally resold. A design house or IP vendor can also use it for corporate espionage and to gain knowledge about a competitor's technology.

#### IC Piracy, Overbuilding and Counterfeiting

The high complexity and cost of fabrication has lead to a fabless model where design companies are no longer able to afford an in-house foundry: instead, they rely on external foundries. This model leads to several security risks during fabrication. IC descriptions can be stolen during fabrication and adjusted for another foundry [RKM08], which can use them to illegally produce ICs. The attacker can then claim ownership of the stolen ICs. At higher level, IP vendors can also be victims of illegal copying of their IPs, which can be resold on the market or copied and modified by their competitors.

Another possible threat is overbuilding or overproducing, where a foundry simply produces more chips and sells them on the black market without authorization from the design company.

On top of the previous risks, counterfeiting, where faulty or outdated ICs are sold as new, is also a threat. According to the authors in [Gui+14], more than 80% of all counterfeit ICs are recycled components that are sold as new after being remarked and repackaged. These counterfeit ICs represent up to 1% of all IC sales [KP13], causing an estimated loss of revenue of \$100 billion [PT06].

#### Hardware Trojan Insertion

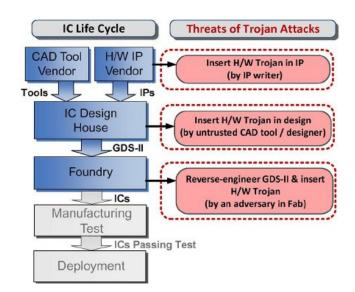

Figure 1.4 – HT attacks at different design stages. (from [Bhu+14])

Hardware Trojans are malicious modifications of a circuit, where the attacker surreptitiously inserts additional logic into the circuit. Hardware Trojans (HTs) can have several goals, such as leaking sensitive information, lowering the performance of the circuit, or creating unwanted behavior and causing errors. HTs can be inserted during manufacturing, but also at earlier design stages, by EDA tools or in 3PIPs, as illustrated on Figure 1.4. HTs are hard to detect during validation and testing, and can have significant impact on the circuit.

## 1.2 Hardware IP Protection

To prevent IP theft, counterfeit and other security issues, several different protection methods have been extensively studied. These methods can be classified according to the technique used: watermarking, obfuscation, locking, etc. They can also be divided into passive and active methods, where passive methods are used to detect if an illegal action such as copying of the circuit has occurred, while active methods are used to prevent such actions. In this section, we give an overview of different design protection methods classified by abstraction level. We focus mainly on active methods. A more in-depth review of some protection mechanisms, in particular at behavioral level, can be found in Section 2.2.2, Section 3.2.1 and Section 4.2.

#### 1.2.1 Foundry

To prevent IP theft and other attacks at the foundry level, split manufacturing has been proposed as a patent in [JM07]. With this technique, designs layouts are split into two parts: Front End Of Line (FEOL) layers and Back End Of Line (BEOL) layers, which are then fabricated in two different, independent foundries. The FEOL is made of the lower layers such as transistors, capacitors and resistors. These expensive layers need to be fabricated in a high-end foundry capable of fabricating the finest components. Most, if not all design houses, have to outsource this fabrication to an untrusted foundry. On the other hand, the BEOL layers (top metal layers, interconnects) can be manufactured in a lower end, but trusted foundry. Larger design houses can even use their own, in-house foundry. The BEOL can either be built directly on top of the previously fabricated FEOL, or both can be manufactured separately and then combined. By splitting designs in such a manner, the untrusted foundry does not have access to the full design, and specifically to the interconnect network.

However, research has demonstrated that it is possible for an attacker to recover the missing BEOL connections by reverse-engineering and analyzing the FEOL. This *proximity attack* [RSK13] relies on the following heuristic used in most floorplanning and replacement tools: FEOL features are usually connected close to one another, in order to reduce the wiring. With this attack, up to 96% of the BEOL interconnects can be recovered [RSK13]. Even more accurate results have been achieved by using deep learning techniques [Li+19a]. Split manufacturing thus needs to be combined with other defense mechanisms to ensure proper security.

#### **1.2.2** Layout Level and Gate-Level Netlist

#### **Physical Unclonable Functions**

Physical unclonable functions (PUFs) are entities that, when given a *challenge*, i.e. an input and conditions, produce a *response* as output. Each PUF has different physical characteristics, due to random variations during the manufacturing process. These characteristics are impossible to duplicate and lead to each PUF giving a unique and unpredictable response to a challenge. The PUFs thus each have a set of unique *challenge-response pairs* (CRP). Due to fhe variations introduced by manufacturing, it is impossible to obtain two PUFs with the same CRP. This means that a PUF can be used as a means to uniquely identify and authenticate an IC. This method is called *challenge-response authentication*.

PUFs were first introduced in 2002 in [Gas+02] and have been gaining more and more interest over the last 20 years. Several desirable properties have been defined for PUFs [CZZ17]:

- **Unclonability**: each PUF has a number of unique CRPs, which cannot be duplicated in another PUF.

- Unpredictability: the other CRPs of a PUF cannot be used to predict the response to a challenge.

- **Reliability**: the PUF should always produce the same response to a given challenge.

- Physical unbreakability: the PUF should be tamper-proof.

Several different types of PUFs have been proposed such as arbiter PUFs [Lim+05], ring-oscillator PUFs [SD07] or SRAM PUFs [HBF08]. Detailed surveys and state of the art studies can be found for example in [MV10] or [BS19].

In recent years, several vulnerabilities and weaknesses of PUFs have been studied. For instance, PUFs are vulnerable to side-channel attacks [DV13], as well as machine learning (ML) based attacks [Her+14], where an algorithm is trained with a subset of CRPs of a PUF to predict responses to unknown challenges.

#### Watermarking

Watermarking relies on applying slight modifications to a design by inserting a watermark, then later extracting and verifying this watermark as a means of claiming ownership of a stolen IP (for a more detailed definition, see Section 3.2.1). Watermarking can be applied at all abstraction levels, with the watermark propagating to later design stages.

With *constraint-based* watermarking [Kah+98], the design house's signature is converted into a set of constraints. These constraints are added to the original design's constraints. This reduces the solution space available for a given optimization problem. The resulting design after synthesis and optimizations is a unique solution that it is highly unlikely to obtain without the watermarking constraints. Constraints can be added for several different optimization problems, such as:

- Adding clauses to a satisfiability problem such as 3SAT [Kah+98].

- Adding unique timing constraints to the timing constraints of a path by breaking it into subpaths [Jai+03].

- Modifying the routing of a design, for example by modifying the number of bends used to route the nets of the design [Nar+01].

The main drawback of low-level, constraint-based watermarks is that they are hard to detect and verify after fabrication of the IC [ATA03].

#### Fingerprinting

Fingerprinting is a method used to trace stolen IPs [Cal+04]. Each instance of the IP core is assigned a unique identifier, contrary to watermarking where all instances of the IP share the same identifier. In case of a stolen IP, this identifier can then be used to find who stole the IP. In [Cal+04], fingerprinting is combined

#### 1.2. HARDWARE IP PROTECTION

with a previous constraint-based watermarking scheme. The IP buyer transmits a signature (public key) to the IP designer. This signature is converted into fingerprinting constraints and added to the design house's watermarking constraints. These constraints are taken into account during synthesis. The resulting design has both the designer's watermark and the buyer's fingerprint.

#### Camouflaging

The goal of camouflaging is to prevent reverse-engineering of an IC by hindering image-based extraction of the netlist. Several different techniques for camouflaging are possible:

Figure 1.5 – Standard and camouflaged cell layouts for NAND [(a) and (c)] and NOR [(b) and (d)] gates. (from [Raj+13])

- Using filler cells to fill any empty space in the IC [Cho+12].

- Adding dummy contacts [CBC07] to the layout: these dummy contacts fake a connection between two layers but have a gap in the middle to prevent forming a real electrical connection.

- Using logic gates that are all designed to look identical.

An example for logic cells with identical layouts is given on Figure 1.5 as depicted in [Raj+13]. The figure first depicts standard NAND (Figure 1.5(a)) and NOR (Figure 1.5(b)) gates. These cells have different layouts and are easy to differentiate during reverse-engineering. On the other hand, (Figure 1.5(c)) and (Figure 1.5(d)) show camouflaged layouts for NAND and NOR gates which look identical.

**Obfuscation and Logic Locking**

Figure 1.6 – Logic locking example on c17 benchmark. The correct key inputs are k0=1, k1=0, k2=1. (from [DF19])

Hardware obfuscation aims at hiding the functionality and implementation of designs. With logic locking, the circuit operates in a locked mode until the correct input key is applied and restores functionality. A simple example can be found on Figure 1.6. The terms "logic obfuscation", "logic locking" and "logic masking" are often used interchangeably, depending on the author. A formal definition and clearer distinction between these techniques can be found in [CBH16]. In the rest of this work, we will refer to logic locking for techniques applied at gate level, and obfuscation for higher level techniques.

In [RKM08], the authors propose a combinational logic locking method. Support for public-key cryptography, a public key and some circuitry to support a locking mechanism are added to the RTL description. This enriched RTL is then synthesized into a gate-level netlist. At this level, combinational locking is performed on the circuit by adding XOR and XNOR gates. A random key is generated and sent to the IP rights holder. After fabrication, a key exchange mechanism with the foundry leads to the right locking key being produced by the chip. Once this correct key appears, the circuit is unlocked and behaves as expected. With any other key, the circuit malfunctions. Because this technique is vulnerable to attacks such as oracle-based attacks ([Raj+12]) and SAT attacks ([SRM15]), several improvements have been proposed. A detailed overview of such techniques can be

found in [DF19]. Another systematic analysis of the back-and-forth between research on locking techniques and new attacks, as well as a critique of logic locking evaluation, is presented in [Tan+20].

Instead of combinational locking, other works such as [CB09] or [AKP07] propose sequential locking, by adding a Finite State Machine (FSM) to the circuit. At power-up, this FSM locks the design. The correct sequence of inputs is necessary to unlock it. In [CB09], the proposed method, on top of locking the circuit until authentication, also obfuscates it's design to provide protection against reverse-engineering.

# Hardware Metering

Figure 1.7 – Active hardware metering design flow. (from [CZZ17])

With hardware metering, the design house has access to the ICs after fabrication and can identify each IC individually. This method is used to track all manufactured ICs and can thus detect overproduced and cloned ICs. With active metering approaches, each IC is locked after fabrication and can only be unlocked by the design house. A unique key is used for each IC, contrary to logic locking where all produced ICs are locked with the same key. An example of such a flow is shown on Figure 1.7, as depicted in [CZZ17]: a lock and a PUF are embedded in the circuit before layout generation. After fabrication, a challenge given by the designer is applied to each IC and the response to this challenge is sent to the design house. Here, the PUF is used to uniquely identify each IC. With this response, the designer can authenticate each IC and send an activation key back to the foundry. The IC is only unlocked with the correct key.

#### 1.2.3 RTL

#### Watermarking

Figure 1.8 – FSM watermarking example: (a) original FSM, (b) adding transitions, (c) augmenting input and adding transitions. (from [TC00])

Watermarks can also be embedded at RTL, for example to protect soft IPs. One added challenge compared with lower level watermarking schemes is that the watermark must resist synthesis without being removed or modified by the tool. Some techniques rely on modifying the finite state machine (FSM) of a design. The approach introduced in [TC00], relies on adding bogus transitions on unused input/output pairs, as illustrated on Figure 1.8(b). On Figure 1.8(c), the previous method is extended by first augmenting the number of input bits and then adding bogus transitions. In [Oli01], the FSM is also used to hide a watermark. With this approach, the owner's signature is encrypted, hashed and divided into a sequence of input combinations to the design. Then the state transition graph (STG) is modified by adding extra states and transitions, so that when this sequence of inputs is followed, the design reaches a particular sequence of states, exhibiting a specific property. Ownership is proven by providing both the input sequence and the specific property defined by the owner.

Instead of modifying the FSM, in [Cas+07], the authors propose to form a watermark by spreading a signature throughout the design, in memory structures or existing combinational logic. To be able to extract the watermark at layout level, their method requires adding some dedicated circuitry to the existing design.

The test circuit of an IP can also be used for watermarking. In [FT03], a watermark generating circuit is added to the test circuit before logic synthesis. After fabrication, when the IP is run in test mode, the watermark generating circuit is activated and a watermark is sent out with the test pattern. This method has the advantage that the watermark extraction process is much simpler than for other techniques. However, it fails if the attacker simply removes the test circuit [ATA04].

A full survey of IP watermarking techniques can be found for example in [ATA04].

#### Obfuscation

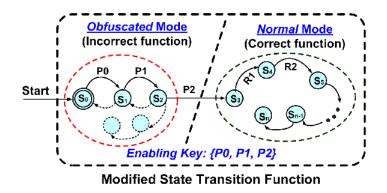

Figure 1.9 – Modified FSM for key-based RTL obfuscation. (from [CB10])

Similarly to logic locking at the gate level, key-based obfuscation can also be applied at RTL. In [CB10], the CDFG of an RTL IP is extracted. A "mode-control FSM" is then added to the IP, see Figure 1.9. This ensures that the circuit falls by default into an obfuscated mode, and only reaches normal mode if the correct input key sequence is applied ( $P0 \implies P1 \implies P2$  on Figure 1.9).

Other approaches focus on obfuscating the HDL source files to reduce their readability, by reusing classic software obfuscation techniques: [BY07], [Mey+11]. However, these techniques do not prevent illegal copying and reuse, provide little resistance against automatic software de-obfuscation tools, and are sometimes removed by logic synthesis tools.

#### 1.2.4 Behavioral

In this subsection, we quickly present an overview of a few approaches for IP protection at the behavioral level, before and during HLS. More detailed analyses of existing methods are given in Section 2.2.2, Section 3.2.1 and Section 4.2.

#### Watermarking

In [KHP05], the authors present a method to perform constraint-based watermarking during different steps of the HLS process. In particular, they detail how to insert a watermark during register allocation. However, they note that this method can also be used for other HLS tasks such as scheduling or partitioning. For register allocation, an interval graph is used to represent all the program variables as nodes, and their overlapping lifetimes as edges. A graph coloring algorithm is then used to solve the problem. The watermark is embedded by first encrypting and encoding the IP owner's signature. Then, edges are added to the interval graph according to this encoded signature. The additional edges result in additional constraints for the graph coloring problem. These specific constraints result in a design that is highly unlikely to obtain by coincidence, thus forming a watermark. [SBM16] proposes to improve the previous method by decreasing the watermark embedding cost and increase the resistance to attacks. By using particle swarm optimization (PSO) to explore watermarking solutions, the authors are able to find a low-cost optimal solution.

#### 1.2. HARDWARE IP PROTECTION

Several approaches for watermarking at the behavioral level targeting specifically digital signal processing (DSP) have been published, e.g. in [CD00] and [Ras+99]. In both cases, the watermark is embedded by performing minor changes in the requirements of filters. Verification is done by observing the slight modifications in the filter's response. These approaches are however highly sensitive [ATA04] to low-level design fluctuations as well as watermark removal attacks, since a minimal change in the filter's response can be enough to hide the watermark.

#### Obfuscation

Obfuscation can be applied at behavioral level, either on the algorithmic-level source code, or during HLS using a modified HLS tool. In [VS17a], the authors use traditional software obfuscation techniques applied on the source code before HLS. They then study the impact of this method on the HLS quality of results and propose two methodologies to find the optimal obfuscation. However, they only test basic layout obfuscation techniques, which make the code harder to read but do not affect functionality. Their techniques do not provide protection against IP theft and reuse, only reverse-engineering.

Similarly, in [SR17], the authors use compiler-based, high-level transformation to obfuscate IP cores. Their techniques are applied on the DFG and include redundant operation elimination, tree height reduction and logic transformation, where functions are replaced with other, logically equivalent functions. These techniques all change readability and hide the structure of the IP, but do not modify functionality.

In both [IK18] and [Pil+18b], the authors propose to modify an in-house HLS tool to apply obfuscation during HLS. This results in an obfuscated RTL description, which is protected both against IP theft at high level and against theft and reverse-engineering at foundry level. In [IK18], the obfuscation passes are applied on the CDFG during scheduling and datapath generation. In [Pil+18b], obfuscation is performed during all steps of the HLS flow, at front-end, mid-level and back-end. Both approaches offer *key-based* obfuscation, which, similar to logic locking at lower design levels, provides protection against illegal reuse.

|                                  | Reverse-<br>engineering | Hardware<br>Trojans | IP Piracy &<br>Overbuild-<br>ing | Counterfeiting |

|----------------------------------|-------------------------|---------------------|----------------------------------|----------------|

| Possible attackers               |                         |                     |                                  |                |

| Customer & End<br>User           | $\checkmark$            |                     |                                  |                |

| Design House &<br>SoC Integrator | $\checkmark$            | $\checkmark$        | $\checkmark$                     | $\checkmark$   |

| 3PIP Vendor                      |                         | $\checkmark$        |                                  |                |

| Foundry                          | $\checkmark$            | $\checkmark$        | $\checkmark$                     | $\checkmark$   |

| Test & Assembly                  | $\checkmark$            |                     |                                  | $\checkmark$   |

| EDA Tool                         |                         | $\checkmark$        | $\checkmark$                     |                |

| Countermeasures                  |                         |                     |                                  |                |

| Split Manufactur-<br>ing         | $\checkmark$            | $\checkmark$        |                                  |                |

| PUF                              |                         |                     |                                  | $\checkmark$   |

| Watermarking                     |                         |                     | $\checkmark$                     | $\checkmark$   |

| Fingerprinting                   |                         |                     | $\checkmark$                     | $\checkmark$   |

| Camouflaging                     | $\checkmark$            |                     | $\checkmark$                     |                |

| Hardware Meter-<br>ing           |                         |                     | $\checkmark$                     | $\checkmark$   |

| Obfuscation                      | $\checkmark$            | $\checkmark$        | $\checkmark$                     | $\checkmark$   |

#### **1.2.5** Threats and Countermeasures

Table 1.1 – Common hardware threats and countermeasures.

The previously presented hardware IP protection methods can be used at different abstraction levels and against different threats. Table 1.1 sums up the different threats and their countermeasures. It also indicates which actors can be involved in each attack.

In this work, we focus on threats introduced by the use of EDA tools, in particular HLS tools. In Chapter 2, we present an obfuscation-based solution against IP piracy during cloud-based HLS. In Chapter 4, we focus on the risk of hardware trojan insertion by a malicious HLS tool. Finally, in Chapter 3, we show how our methods can also be applied as a watermarking countermeasure against reverseengineering, IP piracy, overbuilding and counterfeiting at later design stages.

## 1.3 Software Obfuscation

Our focus in this work is on how to protect IPs against theft, counterfeiting and other threats at the *behavioral* level. Since behavioral IPs are usually provided in high level source code such as C/C++, protection methods can be strongly similar to those used for software protection. Software obfuscation specifically is of particular interest to our work. In this section, we thus give an overview of software obfuscation principles and techniques.

#### **1.3.1** Definition and Principles

Informally, obfuscating a program means rendering a program unintelligible while keeping it functionally and semantically equivalent with the original program. Obfuscation is based on the paradigm of *security through obscurity*. The idea was introduced in 1984 at the International Obfuscated C Code Contest, and first mentioned in literature by Collberg et al. in [CTL97] in 1997.

More formally, O is an obfuscator if O takes as input a program P and produces as output a program O(P) such as:

- O(P) has the same functionality as P

- O(P) is harder to understand than P

Program obfuscation is mainly used with the goal of protecting software intellectual property. It can be used to prevent reverse-engineering, but also to protect software watermarks or hide critical constants or predicates.

Most well known and used software obfuscation techniques rely on the predicate *security through obscurity*. The security of these techniques cannot be proven because they do not rely on a formal definition of obfuscation, since the notion of *harder to understand* has no clear formal foundation.

Practical program obfuscation is also called *code-based obfuscation*, opposed to model-based obfuscation [Xu+17]. Code-based obfuscation techniques focus on usability and are not provably secure. No metrics are known as of today to formally evaluate the security of these techniques. On the other hand, *modelbased obfuscation* techniques are based on a strong theoretical background and focus strongly on security. However, this comes with significant overhead and a lack of usability.

A formal description of what is called *virtual black box obfuscation* is given by Barak et al. in [Bar+12]. According to this definition, if a program is obfuscated, it should not be possible to gain more information from seeing the obfuscated code than from interacting with the unobfuscated code in a black box. In other words, other than observing inputs and outputs, there should be no information whatsoever to gain about the obfuscated program. With this definition, an obfuscator Ocan be formally defined by two conditions:

- The obfuscated program O(P) satisfies the previously mentioned virtual black box property.

- The obfuscated program O(P) has the same functionality as the unobfuscated program P.

In [Bar+12], the authors prove that black box obfuscation is impossible, in the sense that it is impossible to have one obfuscator that can obfuscate all programs of a certain class. However, they also give a new possible definition for obfuscation, *indistinguishability obfuscation*:

- The obfuscated program O(P) has the same functionality as the unobfuscated program P.

- Indistinguishability: given two functionally equivalent programs  $P_1$  and  $P_2$  of approximately the same size, the obfuscated programs  $O(P_1)$  and  $O(P_2)$  are computationally indistinguishable from one another.

While this definition is slightly weaker than full *black-box obfuscation*, research has revealed encouraging progress in this direction: a first candidate for building indistinguishable obfuscators was published in 2013 [Gar+13].

While there are some papers proposing implementations of indistinguishability obfuscators, they are as of now unusable in a real-life application [Xu+17]. A strong gap can thus be found between theoretical software obfuscation research and practical obfuscation implementations. Furthermore, it should be noted that

#### 1.3. SOFTWARE OBFUSCATION

these two subjects involve two different research communities: code-oriented obfuscation papers are usually published by the software security research community, while model-oriented obfuscation is more a focus in cryptography and theoretical computation research communities. To conclude, there are nowadays no obfuscation approaches that are both provably secure and usable. In the rest of this work, we will focus only on practical, code-oriented obfuscation.

#### 1.3.2 Threat Models and Use cases

There are two main users of obfuscation: software developers trying to protect the intellectual property of their programs from theft and misuse, and malicious actors trying to protect their malware from detection.

#### **Defensive Obfuscation**

Obfuscation is mainly used by software developers and companies to prevent socalled Man-At-The-End (MATE) attacks [Fal+11][Akh+15]: with this type of scenario, the attacker has physical access to the software and can inspect it, modify it and run it at will. This includes any software running on devices such as personal computers, smartphones etc., but also remote execution in potentially hostile environments such as cloud computing [HE12]. Several threats are involved with MATE attacks:

- Reverse-engineering:

- Extracting intellectual property such as proprietary algorithms and implementations.

- Finding critical information such as cryptographic keys, static integers [SL12].

- Discovering vulnerabilities in the program that can be exploited in future attacks, for example code injection where malicious code is injected into the program [BS05].

- Cloning:

- Making and distributing illegal copies.

- Circumventing Digital Rights Management (DRM) measures.

- Finding and breaking license checking mechanisms [KM14].

- Tampering [Got+01]: modifying the software in ways unintended by the developer.

#### **Black-hat Obfuscation**

Obfuscation is also used by malware authors as a protective measure [YY10] against defensive threats such as:

- Detection by automated defense mechanisms such as anti-virus scanners. Obfuscation can be used to hide key-words, code snippets or patterns known in malware databases.

- Reverse-engineering and analysis by security researchers: understanding how a malware works is often an essential step for preventing its execution and spread. It can also be used to identify the malware authors.

- Take-down of the malware: by searching for specific strings such as URLs, researchers can identify what server the malware communicates with and how it spreads.

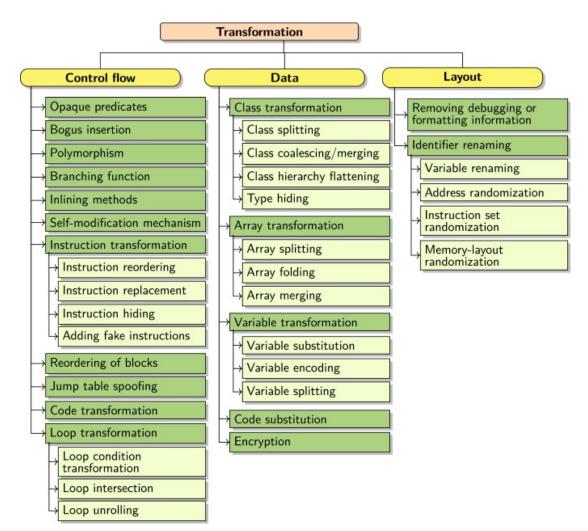

#### **1.3.3** Taxonomy and Common Transformations

Obfuscating transformations have long been classified by their target, in other words by what they are modifying. In [CTL97], the authors proposed a now widely used taxonomy where obfuscating transformations target either **layout**, **data** or **control flow** of the program. A detailed classification of common obfuscating transformations following this taxonomy can be found in Figure 1.10.

#### 1.3. SOFTWARE OBFUSCATION

Figure 1.10 – Classification of obfuscating transformation mechanisms. (from [Hos+18])

#### Layout Obfuscation

Layout obfuscation mainly aims at making the code harder to read for humans. It targets a program's structure and decreases readability by for example removing any formatting (line breaks, indentation, etc) from the source code, changing identifier names or deleting comments. Layout obfuscation is considered irreversible, since the original formatting cannot be recovered once removed. These techniques have no significant influence on the size of the obfuscated program or on the speed of execution. However, they are usually not resistant against automated tools such as disassemblers.

#### **Control Flow Obfuscation**

Control flow obfuscation aims at altering and/or hiding the control flow of a program. This can make the code harder to read and understand for a human, but can also prevent disassembly and reverse engineering with automated tools. Among the most common control flow transformations, following can be cited:

- Dead or redundant code insertion: bogus operands, statements, blocks, control flow transfers, classes, etc.

- Breaking computations up or merging them together

- Loop modifications: unrolling, extending termination condition

- Reordering instructions or computations

- Inlining functions

- Opaque predicates: predicates whose value is known at obfuscation time, but hard to evaluate for an attacker.

#### Data Obfuscation

Data obfuscation aims at hiding data and data structures. It usually [CTL97] affects the ordering, aggregation, storage or encoding of data. A few common data obfuscation techniques include:

- Splitting variables into two or several variables

- Aggregating several variables into one variable or array

- Restructuring arrays: merging, splitting, folding (increasing the number of dimensions of the array), flattening

- Reordering declarations, variables or arrays

- Modifying the encoding of variables

- Encrypting parts of the data

#### **1.3.4** Commercial and Open-source Tools

Several academic and/or open-source obfuscation tools at varying levels of maturity can be found online. Among the better known tools, the following should be cited: