## Investigation of aging and cracking mechanisms in advanced ceramic materials for microelectronics

Sarah Rubeck

#### ▶ To cite this version:

Sarah Rubeck. Investigation of aging and cracking mechanisms in advanced ceramic materials for microelectronics. Micro and nanotechnologies/Microelectronics. Université de Lyon, 2022. English. NNT: 2022LYSEI065. tel-03860220

## HAL Id: tel-03860220 https://theses.hal.science/tel-03860220

Submitted on 18 Nov 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Nº d'ordre NNT: 2022LYSEI065

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de l'INSA-Lyon

## **Ecole Doctorale** N° 34 **Ecole doctorale Matériaux de Lyon**

Spécialité/ discipline de doctorat : Matériaux

Soutenue le 08/07/2022, par : Sarah RUBECK

# Investigation of aging and cracking mechanisms in advanced ceramic materials for microelectronics

#### Devant le jury composé de :

Rafael ESTEVEZ Professeur - Université de Rapporteur

Grenoble

**Eric LE BOURHIS** Professeur - Université de Poitiers Rapporteur

**Thomas PARDOEN** Professeur - Université catholique Examinateur

de Louvain

Aurélie JANKOWIAK Docteure - ONERA Examinatrice

Solène DASSONNEVILLE Docteure – Aix-Marseille Université Examinatrice

**Jérôme CHEVALIER** Professeur - INSA Lyon Directeur de thèse

**Philippe STEYER** Professeur - INSA Lyon Co-directeur de thèse

**Sylvain MEILLE** Professeur - INSA Lyon Co-encadrant de thèse

**Sébastien GALLOIS-** Docteur - STMicroelectronics Invité

GARREIGNOT

## Département FEDORA – INSA Lyon - Ecoles Doctorales

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                                   | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                                                                                                          |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIMIE    | CHIMIE DE LYON  https://www.edchimie-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage secretariat@edchimie-lyon.fr                                                                      | M. Stéphane DANIELE C2P2-CPE LYON-UMR 5265 Bâtiment F308, BP 2077 43 Boulevard du 11 novembre 1918 69616 Villeurbanne directeur@edchimie-lyon.fr                                                                                                                                           |

| E.E.A.    | ÉLECTRONIQUE, ÉLECTROTECHNIQUE, AUTOMATIQUE  https://edeea.universite-lyon.fr Sec.: Stéphanie CAUVIN Bâtiment Direction INSA Lyon Tél: 04.72.43.71.70 secretariat.edeea@insa-lyon.fr              | M. Philippe DELACHARTRE INSA LYON Laboratoire CREATIS Bâtiment Blaise Pascal, 7 avenue Jean Capelle 69621 Villeurbanne CEDEX Tél: 04.72.43.88.63 philippe.delachartre@insa-lyon.fr                                                                                                         |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME, MICROBIOLOGIE, MODÉLISATION  http://e2m2.universite-lyon.fr  Sec.: Bénédicte LANZA Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 secretariat.e2m2@univ-lyon1.fr              | Mme Sandrine CHARLES Université Claude Bernard Lyon 1 UFR Biosciences Bâtiment Mendel 43, boulevard du 11 Novembre 1918 69622 Villeurbanne CEDEX sandrine.charles@univ-lyon1.fr                                                                                                            |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTÉ  http://ediss.universite-lyon.fr Sec.: Bénédicte LANZA Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 secretariat.ediss@univ-lyon1.fr                              | Mme Sylvie RICARD-BLUM Institut de Chimie et Biochimie Moléculaires et Supramoléculaires (ICBMS) - UMR 5246 CNRS - Université Lyon 1 Bâtiment Raulin - 2ème étage Nord 43 Boulevard du 11 novembre 1918 69622 Villeurbanne Cedex Tél: +33(0)4 72 44 82 32 sylvie.ricard-blum@univ-lyon1.fr |

| INFOMATHS | INFORMATIQUE ET MATHÉMATIQUES  http://edinfomaths.universite-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage Tél: 04.72.43.80.46 infomaths@univ-lyon1.fr                               | M. Hamamache KHEDDOUCI Université Claude Bernard Lyon 1 Bât. Nautibus 43, Boulevard du 11 novembre 1918 69 622 Villeurbanne Cedex France Tél: 04.72.44.83.69 hamamache.kheddouci@univ-lyon1.fr                                                                                             |

| Matériaux | MATÉRIAUX DE LYON  http://ed34.universite-lyon.fr Sec.: Yann DE ORDENANA Tél: 04.72.18.62.44 yann.de-ordenana@ec-lyon.fr                                                                          | M. Stéphane BENAYOUN Ecole Centrale de Lyon Laboratoire LTDS 36 avenue Guy de Collongue 69134 Ecully CEDEX Tél: 04.72.18.64.37 stephane.benayoun@ec-lyon.fr                                                                                                                                |

| MEGA      | MÉCANIQUE, ÉNERGÉTIQUE, GÉNIE CIVIL, ACOUSTIQUE http://edmega.universite-lyon.fr Sec.: Stéphanie CAUVIN Tél: 04.72.43.71.70 Bâtiment Direction INSA Lyon mega@insa-lyon.fr                        | M. Jocelyn BONJOUR INSA Lyon Laboratoire CETHIL Bâtiment Sadi-Carnot 9, rue de la Physique 69621 Villeurbanne CEDEX jocelyn.bonjour@insa-lyon.fr                                                                                                                                           |

| ScSo      | ScSo* https://edsciencessociales.universite-lyon.fr Sec.: Mélina FAVETON INSA: J.Y. TOUSSAINT Tél: 04.78.69.77.79 melina.faveton@univ-lyon2.fr Géographie Aménagement Urbanisme Archéologie Scien | M. Christian MONTES Université Lumière Lyon 2 86 Rue Pasteur 69365 Lyon CEDEX 07 christian.montes@univ-lyon2.fr                                                                                                                                                                            |

<sup>\*</sup>ScSo: Histoire, Géographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

## Contents

| R            | emer   | ciements                                                               | 6   |  |

|--------------|--------|------------------------------------------------------------------------|-----|--|

| $\mathbf{G}$ | enera  | al introduction                                                        | 8   |  |

| Ι            | Gen    | General considerations on reliability and on fracture of ceramics      |     |  |

|              | I.1    | Reliability in microelectronics                                        | 17  |  |

|              | I.2    | Fracture mechanics of ceramics                                         | 20  |  |

|              | I.3    | Conclusion                                                             | 31  |  |

| ΙΙ           | Mat    | terials and experimental methods                                       | 33  |  |

|              | II.1   | Investigated materials                                                 | 35  |  |

|              | II.2   | Characterization of mechanical properties                              | 37  |  |

|              | II.3   | Investigation of fracture mechanisms                                   | 54  |  |

|              | II.4   | Direct observation methods                                             | 61  |  |

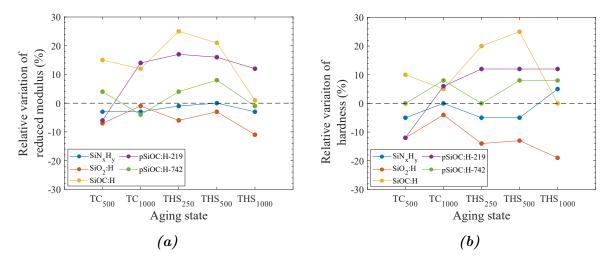

| II           | IInflu | uence of hydrothermal aging on mechanical properties of dielectric     |     |  |

|              | film   | ${f s}$                                                                | 63  |  |

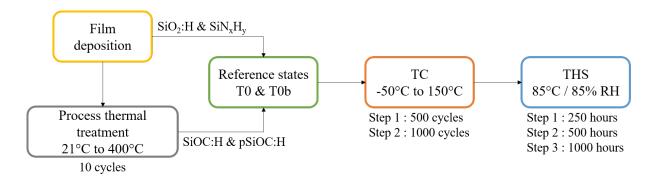

|              | III.1  | Experimental protocol                                                  | 65  |  |

|              | III.2  | Mechanical properties at $T_0$                                         | 66  |  |

|              | III.3  | Effect of process thermal treatment on SiOC:H properties               | 79  |  |

|              | III.4  | Effect of temperature cycling                                          | 85  |  |

|              | III.5  | Effect of temperature-humidity storage                                 | 91  |  |

|              | III.6  | Conclusion                                                             | 99  |  |

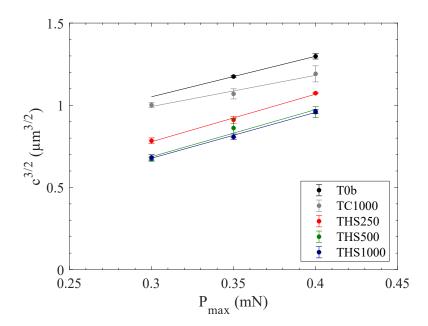

| Iλ           | Cha    | racterization of cracking mechanisms in porous SiOC:H                  | 101 |  |

|              | IV.1   | Fracture behavior of silicon wafer substrate by double-torsion testing | 103 |  |

|              | IV.2   | Fracture behavior of porous SiOC:H thin film by double-torsion         | 105 |  |

|              | IV.3   | Fracture behavior of porous SiOC:H thin film by four-point bending     | 106 |  |

| $\mathbf{V}$ | App   | olication to microelectronics 1                  | 43  |

|--------------|-------|--------------------------------------------------|-----|

|              | V.1   | Introduction                                     | 45  |

|              | V.2   | Effects of material aging on product reliability | .45 |

|              | V.3   | $Ultra-low\ k$ SiOC:H fracture behavior          | .52 |

|              | V.4   | Conclusion                                       | 155 |

| $G_{\ell}$   | oners | l conclusions 1                                  | 56  |

### Acronyms

**AEC** Automotive Electronic Council

**BEoL** Back End of Line

CMP Chemical-mechanical polishing

**CPI** Chip-Package Interactions

**CSM** Continuous Stiffness Measurement

CTE Coefficient of Thermal Expansion

**FEoL** Front End of Line

FIB Focused Ion Beam

**HAST** High Accelerated Steam Test

**HTOL** High Temperature Operating Life

**HTSL** High Temperature Storage Life

JEDEC Joint Electron Device Engineering Council

**MEoL** Middle End of Line

**OSG** Organo Silicate Glass

PECVD Plasma Enhanced Chemical Vapor Deposition

**PMD** Pre Metal Dielectric

**PSG** PhosphoSilicate Glass

RC Resistance-Capacitance

**SEM** Scanning Electron Microscopy

TC Temperature Cycling

**TEM** Transmission Electron Microscopy

**THS** Temperature-Humidity Storage

**USG** Undoped Silicate Glass

#### Remerciements

Les travaux présentés dans ce manuscrit sont le fruit d'une collaboration entre STMicroelectronics à Crolles et le laboratoire MATEIS à l'INSA de Lyon.

Tout d'abord, je tiens à adresser mes plus sincères remerciements à MM. Rafael Estevez et Eric Le Bourhis qui m'ont fait l'honneur d'être les rapporteurs de cette thèse, à M. Thomas Pardoen qui a présidé mon jury ainsi qu'à Mmes Aurélie Jankowiak et Solène Dassonneville qui ont examiné mon travail avec attention et participé à mon jury.

Pendant ces trois ans (et quelques...), j'ai eu la chance d'être encadrée par Jérôme Chevalier, Philippe Steyer, Sylvain Meille et Sébastien Gallois-Garreignot. Un grand merci pour votre disponibilité, votre partage, votre bienveillance et votre soutien qui ont largement contribué au bon déroulement de ma thèse. Il n'y a pas de résilience sans bon encadrement!

Je tiens à remercier également MM. Eric Sabouret et Emmanuel Vincent qui ont rendu cette thèse possible et qui m'ont fait confiance pendant ces trois ans. Mes remerciements vont également à M. Daniel Benoit pour l'opportunité d'après thèse.

Evidemment ce travail n'aurait pas été possible sans l'aide et le support technique de nombreuses personnes. Merci à Clément pour le thésarde-sitting d'un an (à quand ton premier thésard?) ; Vincent pour le domptage du nanoindenteur ; Alice pour ton super travail pendant tes six mois avec nous ; Thomas, Véronique et Sébastien pour avoir trouvé (presque) tous les indents introuvables ; Vivien pour la chouette collaboration et le chouette papier ; Philippe pour tous les dépôts ULK trop épais ; Paul pour les autres dépôts diel, les formations et ton aide pour le manuscrit et les slides ; Marco and Luca for the molding compound characterizations at Agrate ; Emanuele for all interesting discussions, advice and shared documents ; Lionel pour les caractérisations au LETI ; Aurélien pour les simulations et le chouette papier ; Victor pour les loooongues heures au MEB (hommage à l'échantillon du vendredi soir...) ; José, Christophe et Erwan pour la superbe micromachine ; Mathilde pour le soutien de rédaction entre co-doctorantes et Idir pour tes phrases cultes que seuls les balayeurs de miettes de silicium peuvent comprendre.

Je tiens aussi à remercier chaleureusement toutes les personnes que j'ai côtoyées pendant et après ces trois ans: la travée TCAD pour votre accueil de début de thèse (et les soirées match et chardon) ; l'équipe CPI pour votre accueil de milieu et fin de thèse et l'équipe diel pour l'accueil (presque) post thèse. Sans oublier les équipes SNMS et CERA, merci pour votre accueil chaleureux pendant mes périodes à Lyon. Bien sûr, un grand merci à tous les thésards de ST et MATEIS, ça fait plaisir de croiser des personnes dans le même état d'esprit et bon courage à ceux qui tiennent le bon bout !

Parce qu'une thèse ce n'est pas seulement de nombreuses heures de manip et d'écriture. Merci à l'équipe de grimpeurs de ST (et plus si affinités): Tarun pour ta patience pendant mes "attends, j'essaie un dernier truc pour voir" qui t'ont convaincu de l'utilité d'un assureur autobloquant (et merci pour bien d'autres choses!); Delphine et Manu pour les WE faranchins ou comment se reposer le cerveau dans du 7a+ A0 ou avec de la caipirinha, magnifique transition vers Cybelle que je remercie d'aimer le dévers presque autant que moi (à quand les runs dans le toit?); et bien sûr à tous les autres: Anne(s), Axelle, Emma, Gabrielle, Gabin, Marie, Paul, Surinda, Yelda (et Olivier), Yannick...Je vous dis à l'occaz au relais, à Villar-d'Arène ou à EV, toujours dans la bonne humeur même si les points sont à dache!

Merci également à vous le Lutin, Juliooos et le Phoque. 9 ans...Et dire que tout a commencé à mi-chemin entre la pelouse des humas (ou de la BU mais on s'en souvient plus) et des bâtiments A et B!

Et enfin, à tous mes proches: Nanjee, merci pour ta patience infinie et ta zen-attitude à toute épreuve. Il ne nous reste plus qu'à profiter des montagnes maintenant! Papa et maman, un docteur de plus à la maison, merci d'avoir rendu cela possible. Marie, Pauline, René et Raymonde, merci pour votre soutien tout au long de ces trois ans et bien avant. Valérie, Hervé et Ananta, merci pour vos encouragements et votre gentillesse.

Merci à tous!

PS: A toi, thésard qui est entrain de lire ces quelques lignes (parce qu'on commence tous par scruter les remerciements avant de se plonger dans le dur chapitre discussion...): bonne lecture!

#### General introduction

The increasing complexity of microelectronic devices illustrates the race to miniaturize the components and to optimize their performances, driving the microelectronic industry. Indeed, products have more and more functionalities thanks to always innovative processes and materials. In addition, the long-term reliability of electronic components has become a crucial commercial argument, especially for markets with a strong commitment to quality, such as automotive, medical or space.

Systematic product qualification is defined during its development to guaranty its reliability and ensures the minimum failure rate. In addition to the wide range of electrical failures, mechanical-induced failures are also sometimes observed. Indeed, with new integration schemes of package and extensive integration of new porous insulating materials with low mechanical properties, failure hazard increases dramatically.

At such scale (few hundreds of nanometers), the characterization of mechanical properties and the understanding of fracture mechanisms are a great challenge. Thin film effect, sample preparation, defect monitoring are just a few examples of the problems faced by the microelectronic industry in this field of research. This is even more complex when dealing with the mid and long-term reliability. In this context, this manuscript is set with the main objective of addressing these mechanical reliability issues focused on the chip. One can question if these issues come from a modification of the embedded materials due to aging effect and/or due to a time-dependent and/or cumulative process (fatigue mechanism, corrosion...).

These questions will guide our investigation throughout this manuscript. Before going deeper into the description of our objectives and strategy, a quick introduction to the very basic concepts of the microelectronics is given in the following part.

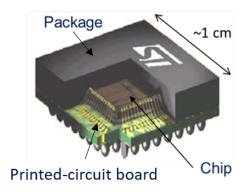

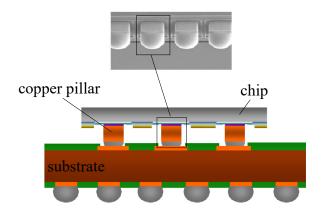

A packaged integrated circuit can be divided into two parts: the *Front End* and the *Back End*. The first is the active part, which is called the *chip* or the *die*. The latter is related to the package likely comprising the *molding compound* and the *printed-circuit board* (figure 1).

Chips are processed from wafers of semiconductor material, typically silicon, which presents electrical properties of either conductor or insulator material depending on the energy provided to the material. Nowadays, these single-crystal silicon wafers have usually a diameter of 200 or 300 mm. Then, the wafers are sawed into chips, assembled to the printed-circuit board and encapsulated to form a packaged integrated circuit.

Figure 1: Example of an integrated circuit in its package with partial opening of the molding compound revealing the chip, which is connected with gold wires to the printed-circuit board

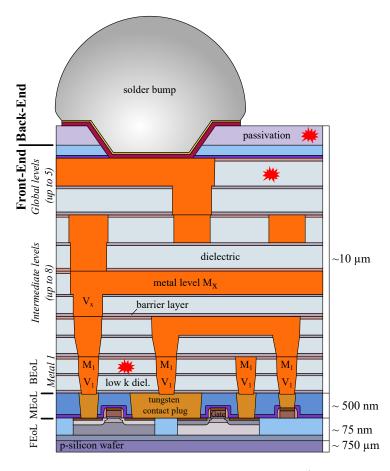

The Front End consists in a combination of three main parts:

- the Front End of Line (FEoL), housing the electrical active (transistors) or passive (resistors) components. A particular dimension of the transistor, the gate length, determines the technology node of the integrated circuit. Nowadays, commonly produced devices range from 130 nm downto 10 nm for the most advanced technologies.

- the *Middle End of Line* (MEoL), connecting the FEoL to the BEoL through tungsten contacts separated by the *pre-metal dielectric* (PMD)

- the Back End of Line (BEoL), where the active components are interconnected, through metal wires on several levels, according to the final function of the integrated circuit. The metal levels are referred as  $M_x$  for metal and  $V_x$  for via, where x stands for the interconnect layer number in ascending order from the FEoL to the BEoL. Depending on the device, this number may vary between 1 and 10.

A chip structure includes *insulating layers* (dielectric materials with a low dielectric constant to avoid parasitic RC<sup>1</sup> coupling between metal levels), *barriers* (such as silicon nitride and silicon carbo-nitride to prevent copper diffusion in the oxide layers), *metal levels* (copper is the material used for the most recent technologies because of its low electrical resistivity), two *passivation layers* (a PSG<sup>2</sup> layer to protect the BEoL structure from chemical contamination and a capping silicon nitride for preventing the BEoL structure from mechanical aggression) and *bonding sites* for the chip-package connections (aluminum contacts) (figure 2).

**Figure 2:** Schematic illustration of a chip cross-section (the red marks stand for the localization of the dielectric layers studied in this manuscript)<sup>3</sup>. Note that the figure is not scaled to better show the thinnest layers.

Material integration challenges in the BEoL The increase in traveling speed of a signal in a microelectronic circuit is proportional to the inverse of the circuit response time  $\tau$  also called the RC delay ( $\tau = RC$ ). Thus,  $\tau$  is the product of the resistance R, which slows the flow of electrons in the metallic interconnect line and the capacitance C, which slows the current through charging delays.

$<sup>{}^{1}</sup>RC = resistance/capacitance$

<sup>&</sup>lt;sup>2</sup>PSG stands for PhosphoSilicate Glass.

<sup>&</sup>lt;sup>3</sup>© Cepheiden / CC BY-SA 4.0 (via Wikimedia Commons), modified.

In order to improve the device performances, the need for new materials arises. On one hand, copper was introduced for the metal line manufacturing, in replacement of aluminum, to reduce the resistance. On the other hand, new insulating materials with low dielectric constant k were brought in to reduce the capacitance.

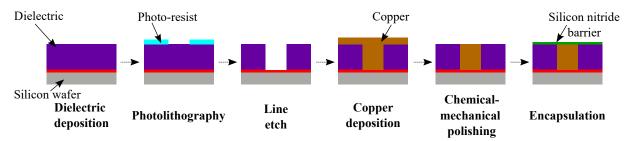

Metals From 2004, copper metal lines substitute aluminum to reduce the interconnection resistance. Indeed, its lower resistivity ( $\rho = 1.67~\mu\Omega.cm$  for the copper instead of  $\rho = 2.65~\mu\Omega.cm$  for the aluminum) and good resistance to electromigration make copper a good candidate for the interconnection processing. However, integrating copper requires a new fabrication process: the so-called double damascene process, illustrated in figure 3 in a very simplified way<sup>4</sup>: (1) dielectric deposition: the dielectric layer is deposited and will serve as a future insulator for the metal lines; (2) photolithography: the surface is coated with photo-resist and lithographically patterned; (3) line etch: the layer is etched to create the future metal lines; (4) copper deposition: the copper is now deposited and fills the previously etched lines; (5) CMP: a chemical-mechanical polishing is performed to flatten the surface for the next metal level processing; (6) encapsulation: a silicon nitride barrier is finally deposited.

Figure 3: Simplified schematic of the damascene architecture

Insulating materials In order to decrease the propagation time of information in the interconnections, low permittivity dielectrics were developed to replace the standard silicon oxide  $(SiO_2)$ . These low permittivity dielectric materials are commonly called the low k dielectrics and are deposited at the first metal levels (i.e. where the copper density is the highest). Among low permittivity films, we can cite hydrogen-doped silicon oxides, organic polymers, carbon-doped silicon oxides (low k SiOC:H) and porous and carbon-doped silicon oxides (ultra-low k SiOC:H).

These materials were developed for the improvement of their electrical properties (decreasing k value), usually at the expense of their mechanical properties. Indeed, these materials show mechanical properties (reduced modulus, hardness and fracture resistance) almost divided by 10 as compared to classical silicate glasses [10]. Thus, their integration to the BEoL and its integrity become critical.

<sup>&</sup>lt;sup>4</sup>Many other barrier layers are deposited, for example to limit the copper diffusion, to stop the CMP process and so one. They are not detailed here, only a simplified illustration of the double-damascene is given. See [17] for further details.

**Typical failure modes in the BEoL** During the different process steps, product qualification and service life, a device can experience a variety of mechanical and thermal stresses. The potential failures observed in a BEoL can be at the dielectric layers as well as at the metal lines: among others, *stress voiding* and *hillocks* for the metal interconnections, or *cracking* and *delamination* for the dielectric layers.

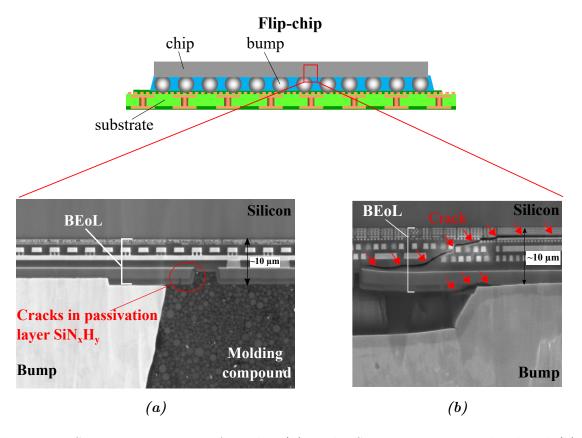

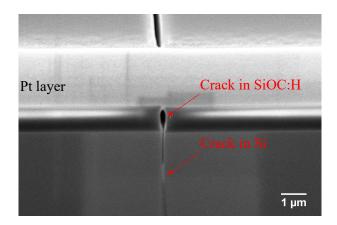

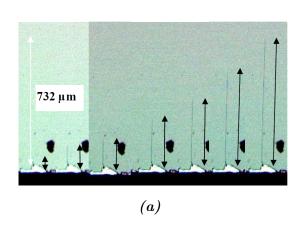

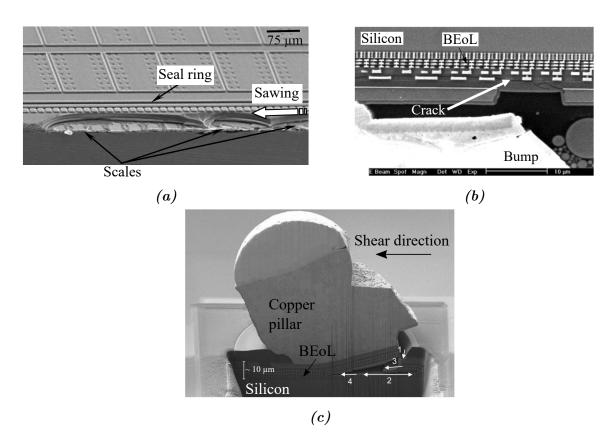

Cracking and delamination of the dielectric films become an increasingly important issue when integrating  $low\ k$  dielectric materials to the BEoL stack. Even if they are more critical due to their poor mechanical properties, the  $low\ k$  films are not the only ones subjected to cracking as cracks were observed also in other dielectric layers. Figure 4 illustrates a crack present (a) in the  $SiN_xH_y$  passivation layer near the bump side and one that propagates (b) throughout the BEoL stack.

**Figure 4:** SEM cross-sections of cracks: (a) at the  $SiN_xH_y$  passivation level and (b) in all the BEoL stack. Note that the FEoL component is not visible here due to the large scale.

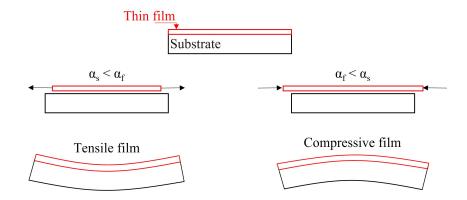

These failures can compromise the good functioning of the integrated circuit. Therefore, it is essential to identify their root-causes. The sources of stresses are diverse:

- at the chip level: the process flow, due to the different material deposition temperatures and their different Coefficients of Thermal Expansion (CTE), thermomechanical stresses arise in the structure. The material deposition parameters may also impact the intrinsic stresses. Both sources contribute to the residual stresses. - at the package level: depending on the package assembly option, mechanical loading may be applied to the BEoL. Package assembly induces also different deposition temperatures and materials, which lead to similar thermo-mechanical stresses.

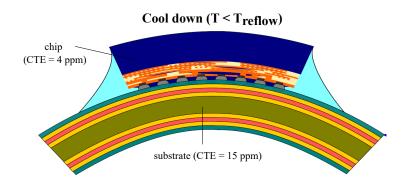

In this context, *Chip-Package Interactions* (CPI) are known for their criticality. They refer to the evidence of thermo-mechanical stresses within the chip, because of interactions with the package. Figure 5 illustrates how stresses can be transferred through bump connections towards the BEoL interconnections in case of a flip-chip assembly, embedded in many materials of different natures (metals versus ceramics), after thermal loading.

Figure 5: Schematic illustration of the chip-package interaction caused by CTE mismatch between the chip and the substrate for a flip-chip assembly (not scaled) [125]

Thesis motivations and strategy With the constant increasing integration density, new materials and architectures are continuously being developed to create innovative products. The mechanical reliability of these new components has become one of the key points to be mastered. Beyond the tests already in place, either on the assembly line or during product qualification, the question is raised of the mechanical behavior of the product throughout its operating life, and its related reliability.

In this work, a specific focus is done at the BEoL level<sup>5</sup> in order to reduce the failure hazard at these levels. Indeed, as introduced earlier, the porous  $low\ k$  dielectric materials, embedded in BEoL, are known to be critical. However, few is known about their mechanical behavior after aging and/or with regard to the environment. The main difficulties rely on the considered scales (typically  $< 0.5\ \mu m$ ) and their brittle behavior, causing many issues for implementing samples and  $in\ situ$  observations.

The approach adopted in this thesis is in line with the perspective of understanding the interactions between the environment (temperature and humidity) and the mechanical reliability of dielectric films. The strategy is twofold: first, evaluate the potential evolution

$<sup>^5</sup>$ This work is in collaboration with the Crolles site of STMicroelectronics, one of the world's leading industrial players in the field of microelectronics. This is a 200/300 mm Front-End manufacturing site, therefore, one where the main interests lie in the FEoL/BEoL layers.

of the mechanical properties of materials after environmental aging, second, investigate the contribution of the environment in the crack mechanisms. Such a dual approach should allow the investigation of potential root-causes of failures observed in the BEoL in long-term reliability.

Hence, the manuscript begins with **chapter I**, which shows how the microelectronic industry ensures their product reliability through accelerated aging tests and related standards. Then, the basics of fracture mechanics in brittle materials are reminded, and to study the influence of environment, the stress-corrosion cracking mechanism is introduced.

Chapter II introduces the panel of studied dielectric films. It covers the standard families of materials used in the most advanced technology nodes. Then, the chapter follows with the different characterization methods used in this thesis, and specifically developed for it.

In **chapter III**, we investigate the mechanical properties of the dielectric materials after temperature cycling and humid environment storage. The variations of the main mechanical parameters (reduced modulus, hardness and fracture resistance) are measured during the aging steps. Therefore, specific methods such as nanoindentation or wafer-curvature measurement are used to determine the local mechanical properties of the thin films and residual stress.

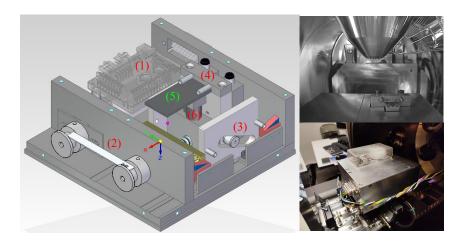

In **chapter IV**, the influence of the environment on the cracking mechanisms of the  $ultra-low\ k$  SiOC:H is more specifically studied. A dedicated characterization tool is thus designed. Specific sample preparation and experimental protocol are also developed to able an  $in\ situ$  small-scale cracking characterization. Besides, a finite element simulation is provided to bring added insights into the experimental results.

In the last **chapter V**, the experimental results found in the two previous experimental chapters are placed in an industrial context. They are discussed regarding our initial problematic on the product reliability in microelectronics. The amplitude of properties variation and crack mechanisms are compared to those encountered during standard qualification step. In that frame, finite element modeling is also used to feed the discussion.

Finally, the main achievements of this work are gathered, and we propose recommendations for future studies.

## CHAPTER I

# General considerations on reliability and on fracture of ceramics

Interconnections are structures comprising many different materials with complex geometries. Failures such as cohesive, interfacial or mixed (both cohesive and adhesive) cracks could happen during the assembly process as well as during the product service-life. To ensure product long-term reliability and validate product design, accelerated environmental aging tests are performed with varying conditions of temperature, humidity level and pressure. Any mechanical failure occurring during these tests needs to be analyzed, so to identify the origin of the failure and to propose solutions to prevent it.

The first part of this chapter is dedicated to the general description of a typical qualification flow. A particular attention is paid on two accelerated aging tests, which address the mechanical and environmental failure modes: the temperature cycling and the temperature-humidity storage.

Fracture mechanics is an excellent tool for describing and determining structure integrity. It will be used in this work to characterize the fracture properties of dielectric materials. The main notions of fracture mechanics in brittle bulk materials are first reminded. Then, the particularities linked to film-on-substrate systems are presented. Finally, as the environmental influence on the fracture properties of  $ultra-low\ k$  dielectric materials is one of the key problems of this PhD, stress-corrosion cracking is also introduced for ceramics.

## Contents

| I.1 | Relia | ability in microelectronics            | 17 |

|-----|-------|----------------------------------------|----|

|     | I.1.1 | Temperature cycling                    | 18 |

|     | I.1.2 | Temperature-Humidity Storage           | 19 |

| I.2 | Frac  | ture mechanics of ceramics             | 20 |

|     | I.2.1 | Linear elastic fracture mechanics      | 20 |

|     | I.2.2 | Crack nucleation                       | 22 |

|     | I.2.3 | Case of thin films                     | 24 |

|     | I.2.4 | Environment-assisted slow crack growth | 25 |

| I.3 | Con   | clusion                                | 31 |

## I.1 Reliability in microelectronics

The reliability determines the time period during which a product will maintain its initial function for which it was designed. To assess reliability, standardized accelerated tests are typically used to identify potential failure mechanisms in semiconductor devices and to estimate the rate of their occurrence.

The historical approach to investigate the relationship between a maximum failure rate during accelerated tests and a product failure rate during service is to choose an apparent thermal activation energy  $E_a$  for a given product. The activation energy is defined as the minimum amount of energy required to initiate a particular process. Its value indicates the relative tendency of a failure mechanism to be accelerated through thermal heating.

To ensure the device qualification, a set of aging tests, which are driven by standards, are performed depending on the product and its application [1]. In this manuscript, the automotive context is highlighted, where the reliability is the focus of much attention.

Today, the reliability assessment for key automotive products is mainly based on the following typical philosophy:

- 1. Determination of the failure mode (electrical, mechanical...)

- 2. Determination of the adequate acceleration model for the considered degradation process

- 3. Determination of the accelerated test duration according to the degree of robustness agreed with the involved customers (safety coefficient *versus* estimated end-of-life) to be in line with the service-life conditions of the products

Obviously, numerous tests are focused on electrical failure modes. These modes are out-of-scope of this PhD, which deals about mechanical reliability only, and thus are not described here.

The main tests with a mechanical scope are presented below:

- High Temperature Storage Life (HTSL) is a test used to determine how products wear can be accelerated by temperature (and current/voltage if High Temperature Operating Life (HTOL) test is performed). This test is performed at 125°C. Bond intermetallic material aging as well as die cracks are examples of addressed failure mechanisms with HTSL.

- Temperature Cycling (TC) is used to highlight the CTE mismatch between the materials, which compose the product. Indeed, TC is performed to estimate the ability of products to withstand thermally-induced mechanical stresses. The delta temperature depends on the final application. The automotive application targets for instance a temperature cycling from -55°C to 150°C. Metal shorts, passivation layer integrity, die cracks as well as solder bump detachment are some of addressed failure mechanisms susceptible to be initiated by TC.

- Temperature-Humidity Storage (THS) is performed to evaluate the moisture resistance of the products, especially of non-hermetic packages, in humid environment.

Metal corrosion and hermeticity loss are some of addressed failure mechanisms with THS.

- Highly Accelerated Steam Test (HAST) is a test, more severe than THS, which combines temperature, humidity and pressure effects. The targeted failure mechanisms are the same than THS, but involved under stronger moisture conditions.

Below are detailed more specifically two accelerated aging tests used in this PhD, the TC and THS, as they are known to be critical for the mechanical and environmental failure modes.

#### I.1.1 Temperature cycling

Temperature cycling is a common accelerated stress test used for microelectronic products to reproduce the temperature variations during their normal use. Self-heating of products during on/off cycles or cyclic environmental changes can cause these thermal variations. In both cases, these repeated temperature variations induce thermal cyclic loads, which can lead to product failure.

To evaluate test duration, the Coffin-Manson acceleration model is used as a standard to calculate the acceleration factor  $A_f$  (equation (I.1)) corresponding to the ratio of the product life at accelerated test and usual operating conditions.

$$A_f = \left(\frac{\Delta T_t}{\Delta T_u}\right)^m \tag{I.1}$$

where  $\Delta T_t$  and  $\Delta T_u$  are respectively the temperature change during aging and product life and m is the Coffin-Manson exponent, its value depends on the targeted failure mechanism.

Knowing the acceleration factor, the test duration is calculated with:

$$n_t = \frac{n_u}{A_f} \tag{I.2}$$

where  $n_t$  and  $n_u$  are respectively the temperature cycle number in aging test and in use environments.

Standards provide a framework for calculating the accelerated test specifications. The agreement then assumed that microelectronic devices experience an average thermal cycle temperature change of 76°C and about 54750 on/off cycles over 15 years of normal use. As perform reliability tests over such a long period would be not relevant, accelerated temperature cycling from -55°C to 150°C is done. To calculate the acceleration factor, m is set at 4 corresponding to cracks in hard metal alloys which is the supposed failure mechanism [1]. With this value and using equations (I.1) and (I.2), the total number of temperature cycles to perform in the accelerated test environment is 1034. This number

of cycles is used in most of qualification procedures at STMicroelectronics in agreement with the AEC standard [1].

In practice, the temperature amplitude is obtained with two thermal chambers: one set at -55°C and the other at 150°C. An automatic elevator mechanism transfers the specimens from one chamber to the other to perform a cycle every 15 minutes.

#### I.1.2 Temperature-Humidity Storage

Similarly, temperature-humidity storage is used to simulate how products are affected by humidity (*i.e.* corrosion, sealing of barrier...). Indeed, increasing humidity level can induce product or material failure occurring in shorter times as compared to dry environments. Humid testing is usually performed at elevated temperature to speed up aging, as the acceleration factor depends on both humidity level and temperature.

For temperature-humidity storage, the acceleration factor is calculated with the Hallberg-Peck equation:

$$A_f = \left(\frac{RH_t}{RH_u}\right)^p \frac{E_a}{k_B} \left(\frac{1}{T_u} - \frac{1}{T_t}\right) \tag{I.3}$$

where  $RH_{t,u}$  are the relative humidity levels,  $T_{t,u}$  the average temperatures,  $E_a$  the activation energy for the considered failure mechanism and  $k_B$  the Boltzmann's constant. The subscripts u and t are the same as for temperature cycling: u for use environment and t for test environment.

In operating conditions, over 15 years of use, the average relative humidity level is assumed to be 74% RH and the average temperature is 32°C [1]. In accelerated test environment, the humidity level is set at 85% RH and the temperature at 85°C. Moreover, the supposed failure mechanism is the bond pad corrosion. For such failure mechanism, p is equal to 3 and  $E_a$  to 0.8 eV given with equation (I.3) an exposure time of 960 hours [1]. Such duration is accepted in most of qualification procedures at STMicroelectronics in agreement with the JEDEC and AEC standards.

After being aged, the products are electrically tested to assess their good functioning. In addition to the qualification tests, systematic failure analysis is also provided to determine the failure root-causes. Imaging (e.g. SEM, TEM, X-Ray) and deprocessing (e.g. chemical, FIB, mechanical) methods are used to identify the crack characteristics. However, in order to understand and forecast these failures, a theoretical background is also needed. The field of fracture mechanics is introduced in the next paragraph.

#### I.2 Fracture mechanics of ceramics

Fracture toughness of thin film is a topic of great interest in microelectronics, where film-on-substrate systems are usually subjected to thermo-mechanical stresses. The crack nucleation and propagation is thus an important issue. This section aims to provide to the reader a global overview of the fracture mechanics, as in this manuscript, the cracking of thin films is discussed.

Ceramics are typically brittle over a wide range of temperatures [52, 56, 117]. Thus, around ambient temperature, they fracture after exceeding their elastic strength without (or with negligible) plastic deformation. Usually, their behavior is often considered as linear elastic until failure.

#### I.2.1 Linear elastic fracture mechanics

This section presents basics of the linear elastic fracture theory, commonly used to describe crack propagation in brittle bulk materials. This theory is valid for elastic materials with a limited damaged/plastic zone at crack tip as compared to crack length and sample dimensions.

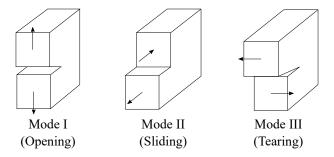

Three cracking modes exist and cover all the fracture cases observed (figure I.1). Mode I corresponds to the opening mode, *i.e.* the crack extension is perpendicular to the crack front. Mode II is the sliding mode corresponding to a crack extension in the crack front plan, in a perpendicular direction. Mode III is called the tearing mode and corresponds to a crack extension in the crack front plan and following the crack front direction.

Figure I.1: Crack extension modes according to the loading direction into mode I, mode II and mode III

Note that the fracture mechanics theory assumes the presence of a pre-defect into the structure studied. The crack nucleation process is beyond the scope of this theory. The analysis focuses then on the propagation of this defect.

#### I.2.1.1 Global approach: concept of energy release rate G

The Griffith theory is commonly used to describe pre-cracked brittle solids [47]. This approach is purely energetic and is a balance between two states: the initial state of a pre-cracked loaded structure and the same structure after the growth of this crack. The

principle is that if the strain energy released for the crack extension is greater or equal to the surface energy required to the creation of the new fractured surfaces, then the crack propagation occurs. The energy criterion is obtained from the energy balance between the two states:

$$\delta U_{pot} + \delta U_{kin} + G_c \delta_s = 0 \tag{I.4}$$

where  $\delta U_{pot}$  is the potential energy,  $\delta U_{kin}$  is the kinetic energy variation,  $G_c \delta_s$  is the energy required to initiate a crack of area  $\delta_s$ .  $G_c$  is the critical energy release rate of the material.

Thus, a crack extension occurs if:

$$G = \frac{-\delta U_{pot}}{\delta S} \ge G_c \tag{I.5}$$

The left term of equation (I.5) corresponds to the energy provided for the crack propagation, *i.e.* the energy release rate G. The right term is the energy needed to produce new surfaces during the crack propagation and corresponds to the critical energy release rate  $G_c$ .

Thus, if  $G < G_c$ , else the crack does not propagate without increasing the applied load. In the other side, if  $G \ge G_c$ , else the crack propagates in an unstable manner.

We note that  $G_c$  corresponds to a dissipation of energy per surface unit localized in the damaged zone around the crack tip. It is an intrinsic material property independent of the structure geometry.

#### I.2.1.2 Local approach: concept of stress intensity factor $K_I$

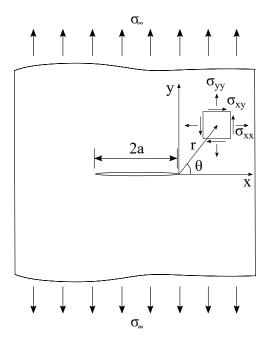

Irwin proposed the second commonly used approach to describe fracture in brittle material [63]. His work analyzed the stress field around the crack tip of a linear elastic material, considering a small crack in an infinite specimen (figure I.2).

The stress field ahead of the crack tip is described by the following function:

$$\sigma_{i,j}(r,\theta) = \frac{K_{\alpha}}{\sqrt{2\pi r}} f_{i,j}(\theta)$$

(I.6)

where  $\theta$  is the angle from the x-direction, r is the distance from the crack tip,  $K_{\alpha}$  is the stress intensity factor,  $\alpha$  is the opening mode and  $f_{i,j}$  are dimensionless functions of  $\theta$  (the subscripts i and j correspond to the space components x,y and z).

Equation (I.7) expresses the stress intensity factor at the crack tip:

$$K_{\alpha} = \sigma_{\infty} \sqrt{\pi a} \tag{I.7}$$

where  $\sigma_{\infty}$  is the applied stress.

The criterion for unstable crack propagation is the critical stress intensity factor  $K_c$  referred as the fracture toughness of a material.  $K_c$  depends on the opening mode (I, II or III), so labeled  $K_{Ic}$ ,  $K_{IIc}$  or  $K_{IIIc}$ . The stress intensity factor depends on the applied stress to the specimen and on the crack geometry.

Figure I.2: Crack specimen under mode I loading and stress fields in an arbitrary element ahead of a crack tip

The loading parameters G and K can be converted into each other with<sup>1</sup>:

$$G = \frac{K_I^2}{E} \tag{I.8}$$

#### I.2.1.3 Critical flaw size

With the case described in figure I.2 (*i.e.* finite crack into an infinite specimen loaded in mode I), a critical flaw size is defined combining equations (I.7) and (I.8):

$$a_c = \frac{EG_c}{\pi \sigma_\infty^2} = \frac{1}{\pi} \left(\frac{K_{Ic}}{\sigma_\infty}\right)^2 \tag{I.9}$$

where  $a_c$  is the critical flaw size, E the specimen Young's modulus,  $\sigma_{\infty}$  the applied stress.

This means that if a defect created in the material is smaller than  $a_c$ , there is no crack propagation for an applied stress  $\sigma_{\infty}$ . On the contrary, for defects longer than  $a_c$ , propagation is induced at  $\sigma_{\infty}$ .

#### I.2.2 Crack nucleation

As seen before, the theory of linear fracture mechanics considers only the crack propagation from a pre-existing defect. However, sometimes, structures don't have pre-cracks and the nucleation of a new crack in a material starts from geometric and/or material singularities.

<sup>&</sup>lt;sup>1</sup>In plane strain conditions,  $G = \frac{K_I^2(1-\nu^2)}{E}$

We saw previously two approaches to describe crack propagation from pre-existing defects. First, if the applied stress  $\sigma$  is larger than the critical value  $\sigma_c$ , then a crack propagates for a given crack size. On the other side, a crack propagates if the energy release rate G is greater than the critical value  $G_c$ .

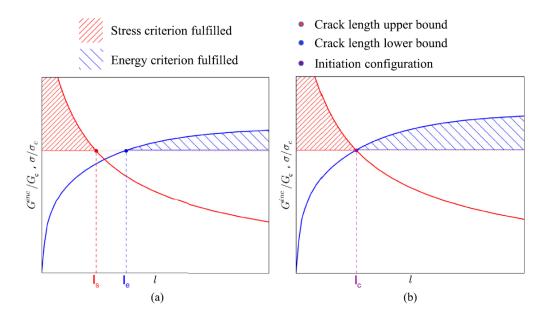

However, Leguillon showed that the two previous independent criteria are necessary but not sufficient conditions for the crack nucleation. He proposed a stress-energy coupled criterion [81], which states that both conditions (stress-based and energy-based) are necessary for crack nucleation. In other words, the stress level in the material has to be enough to initiate a crack and enough energy has to be accumulated to allow the crack opening.

Figure I.3 illustrates the coupled-criterion for crack initiation [28].

**Figure I.3:**  $\sigma/\sigma_c$  and  $G_{inc}/G_c$  ratios as a function of the crack length l (a) before the initiation loading and (b) at the initiation loading (from [28]).  $G_{inc}$  is the incremental energy release rate corresponding to the energy release rate G when l tends to 0.

First, for a decreasing stress, the distance l, on which the stress condition is valid, increases. Thus, the stress criterion determines an upper bond for all the admissible crack lengths at initiation  $l_s$ . Second, if the energy criterion is fulfilled for a crack length  $l_e$  at a given loading, then it is also fulfilled for all crack lengths greater than  $l_e$ . Thus the energy criterion determines a lower bond for all the admissible crack lengths. Figure I.3.b corresponds to the initiation loading where the lower and upper bonds coincide ( $l_s = l_e = l_c$ ).

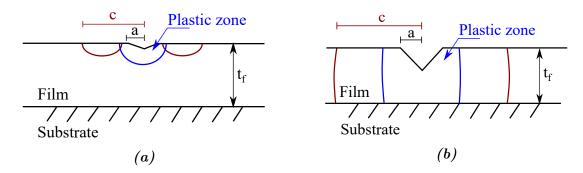

#### I.2.3 Case of thin films

Thin film deposition on substrates leads to residual stresses due to thermal property mismatch and material deposition parameters [27]. These residual stresses can cause the crack propagation through the film thickness or at the interface between the film and its substrate.

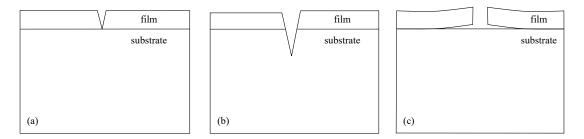

Fracture of thin films depends on the mechanical properties of the film, those of the substrate and those of the interface between the film and the substrate. Figure I.4 shows few examples of fracture cases that can occur in thin films.

**Figure I.4:** Different scenarios of cracks for thin films deposited on a substrate: (a) film channel cracking (b) film and substrate cracking (c) film channel cracking and interfacial cracking along the film/substrate interface

The released energy around a crack that propagates cohesively through a film deposited on a substrate is given by:

$$G = \frac{Z\sigma_{\infty}^2 h_f}{E_f} \tag{I.10}$$

where Z is a dimensionless factor depending on the elastic mismatch between the film and the substrate and on the crack geometry,  $\sigma_{\infty}$  is the applied stress,  $h_f$  the film thickness and  $E_f$  the film modulus.

The crack propagates if the released energy is greater than the critical energy release rate  $G_c$  of the film. Thus, rewriting equation (I.10), a critical film thickness exists under which the film cannot be cracked. This critical thickness is defined by:

$$h_{fc} = \frac{G_c E_f}{Z\sigma_{cc}^2} \tag{I.11}$$

For a given applied stress  $\sigma_{\infty}$ , a crack does not propagate if the film has a thickness of less than  $h_{fc}$ . In contrast, a crack propagation is possible in a film of thickness larger than  $h_{fc}$ .

#### Experimental methods

For thin films, the measurement of the film fracture toughness faces difficulties because of the small scale (thickness typically below one micron). Dedicated equipment, sample processing and surface roughness induce complex characterization at this scale. In addition, the films usually have different elastic, plastic and fracture properties as compared to their substrates. This increases the complexity of the fracture toughness determination of the film itself.

These difficulties lead to the development of many techniques owing their pro and cons to address the **interfacial fracture** (nanoindentation normal to the surface [139], nanoindentation on the cross-section [87], scratch techniques [76] and mechanical delamination tests [74]...) and **cohesive fracture** within the film (nanoindentation normal to the surface, cantilever beam deflection technique [92], freestanding film method [65, 100], micro-tensile fracture tests [68], and four-point bending [66]...) of a thin film. For the sake of clarity, all these different methods are not detailed here. However, some of them (nanoindentation, double-torsion and four-point bending), being used in this work, are described more precisely in the next chapter.

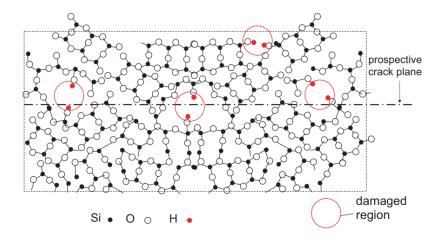

#### I.2.4 Environment-assisted slow crack growth

Dielectric thin films used in the interconnections are silicate-based ceramics. In this kind of materials, cracks can grow slowly at a stress intensity factor lower than the critical value  $K_{Ic}$ . This phenomenon is referred to as **slow crack growth**, as well as **stress-corrosion cracking**. It corresponds to the delayed fracture of a material from the application of stress due to the environment. It could be problematic, as components can fail long after they have been manufactured.

Stress-corrosion cracking corresponds to a combined effect of the stress field ahead of the crack and the environment surrounding the crack tip. This mechanism was observed in glasses since 1889 by Grenet [46]. Later, Orowan highlighted the role played by water on the crack propagation. His results showed that the critical fracture stress of glass can be three times lower in air than in vacuum. This suggests that corrosive molecules present in the environment are adsorbed at the crack tip, causing a decrease in surface energy of the glass, which becomes weaker [116] (figure I.5).

Figure I.5: Schematic illustration of interaction between environment corrosive molecules and material molecules at the crack tip

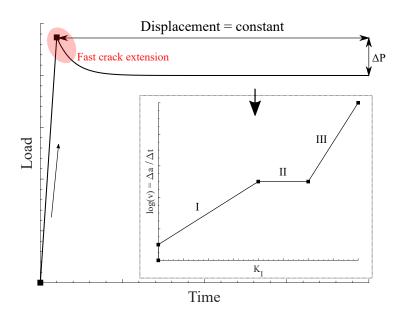

#### I.2.4.1 v- $K_I$ curve

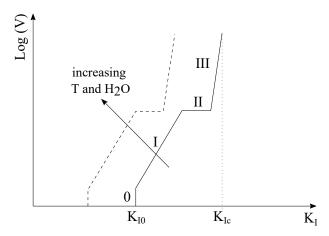

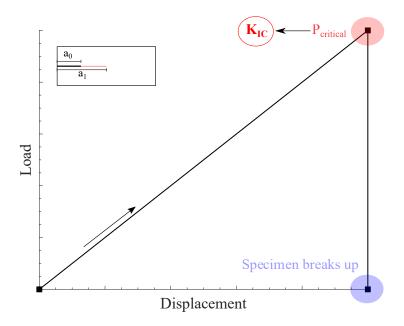

To characterize stress corrosion cracking in ceramics, the crack growth rate v (logarithm scale) is plotted as a function of stress intensity factor  $K_I$ . In figure I.6, a  $v - K_I$  curve is schematized for the cracking of a ceramic in a humid environment.

Figure 1.6: Schematic evolution of crack growth rate as a function of stress intensity factor

Four zones can be distinguished:

- In **region 0**, cracks do not propagate.  $K_{I0}$  corresponds to the cracking threshold. Wan *et al.* showed first the existence of the stress intensity threshold  $K_{I0}$  studying slow crack growth in mica crystal samples [140].

- In **region I**, the crack growth rate is limited by the reaction rate between corrosive molecules present in the environment and atomic bonds at the crack tip [106]. The crack growth rate v increases along with the stress intensity factor  $K_I$  following the analytic formula [52]:

$$v = A \left(\frac{K_I}{K_{cst}}\right)^n exp\left(\frac{-Q_{app}}{RT}\right)$$

(I.12)

where A is a constant,  $K_{cst}$  is a normalization constant, n is the sub-critical growth exponent and  $Q_{app}$  is the apparent activation energy of the sub-critical cracking kinetic.

- In **region II**, the crack growth rate is almost independent from the stress intensity factor  $K_I$  and is no longer limited by the reaction rate between the corrosive molecules and the material at the crack tip. The diffusion rate of the molecules to the crack tip drives the mechanism in region II [141].

- In **region III**, the crack growth rate becomes relatively independent from the environment. In contrast, the stress intensity factor drives the crack growth rate. In this region, the slope of the  $v K_I$  curve becomes steep, which is a sign of fast fracture. The crack propagation is linked to bond breaking, caused by the stress field at the crack tip with a limited influence of corrosion.

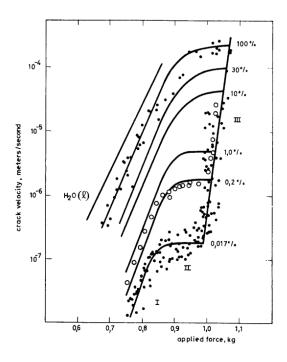

Characterization of  $K_{Ic}$ , usually obtained at high crack growth rate tests, is of importance. Figure I.6 suggests that the critical stress intensity factor can overestimate the actual crack resistance of the material, which may lead to a premature rupture of the ceramic component. In a practical case, the determination of  $K_{I0}$  is essential to set the lower limit of crack propagation. In addition, Wiederhorn showed that increasing the water content of the surrounding environment and the temperature decreases the threshold  $K_{I0}$ . The kinetic is also accelerated, meaning that for a similar stress intensity factor, the crack growth rate is increased (figure I.7) [141].

Figure I.7: Dependence of crack velocity on applied force for different humidity levels for bulk soda-lime glass specimens (from [141])

#### I.2.4.2 Slow crack growth in silicate glasses

Although slow crack growth in silicate glasses were observed for a long time [46], its characterization dates back to the 1960s [14]. Since then, slow crack growth in diverse ceramics have been widely studied [18, 78, 96, 112, 136, 142, 144].

The water content is not the only influential parameter, the temperature as well as other polar molecules can also modify the stress-corrosion cracking of ceramic materials [143]. In the following sections, only the influence of water will be discussed.

A physico-chemical interpretation of the slow crack growth in ceramics was proposed by Charles and Hillig [14]. They explained the phenomenon through a corrosion mechanism, which happens following three steps: (1) transport of the water molecule to the crack tip, (2) material dissolution and creation of the corrosion products, (3) transport of the corrosion products out of the crack tip. The crack propagation is controlled by the slower mechanism for the slower crack growth rates (*i.e.* material dissolution). However, this model did not take account the possibility of a crack propagation in the absence of water molecules (i.e. in vacuum, where a dissolution mechanism cannot happen).

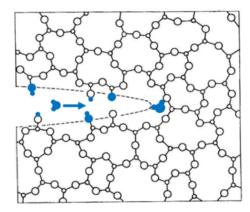

Later, Michalske and Freiman proposed a physico-chemical process to explain the slow crack growth in silicate glasses: the mechanism is attributed to ionic bond breaking [106]. In this case, the fracture is possible at a local critical stress reached in vacuum. In aqueous environments, the mechanical load needed to break these kind of bonds is decreased, as the mechanism is enhanced by the water molecules.

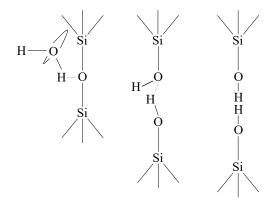

In more details, a Si-O-Si bond is dissociated to form two new silanol bonds (Si-O-H) according to the reaction:  $Si - O - Si + H_2O \rightarrow 2SiOH$  [29, 33]. Locally, the Si-O-Si bond is broken, enhanced by both the mechanical loading and the chemical reaction. The principle, which makes consensus among ceramists today, is schematized in figure I.8.

Figure 1.8: Schematic of the steps of the reaction between  $SiO_2$ -based ceramics and water happened at the crack tip

Later, Zhu *et al.* demonstrated experimentally how water molecules reduce the breaking energy of chemical bonds of silicate glass, which agrees with the model proposed by Michalske and Freiman [106, 149].

In the field of microelectronic, SiO<sub>2</sub>-based dielectric layers undergo stress-corrosion cracking, already studied by several authors.

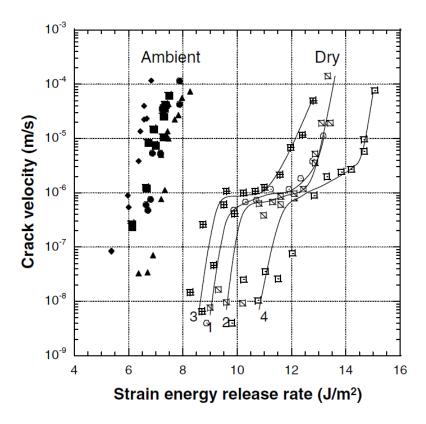

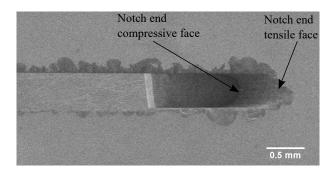

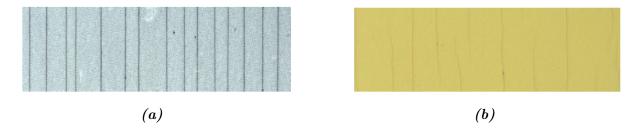

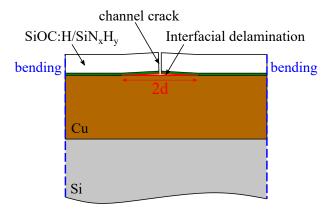

McElhaney and Ma (and previously Ma in [95]) demonstrated the advantages of a sample comprising a metallic interlayer to generate cohesive channel cracks in a thin brittle SiO<sub>2</sub> film without breaking the substrate [101]. The authors observed evidence of sub-critical crack growth in a 4 μm-thick PECVD silicate glass deposited on Si wafer with a metallic interlayer loaded in four-point bending configuration. Figure I.9 shows the crack velocity as a function of strain energy release rate for their SiO<sub>2</sub> samples tested under ambient and dry environments.

Figure I.9: Crack velocity as a function of strain energy release rate under ambient (25°C and 40 to 60% RH) and dry N2 environments. The 4  $\mu$ m-thick SiO<sub>2</sub> (Undoped Silicate Glass) films deposited onto 2  $\mu$ m of metal layer and a silicon substrate show increased crack resistance when tested in reduced humidity levels. The data from the dry environment also exhibit the characteristic S-shape of the three principal regions of moisture-assisted cracking (from [101]).

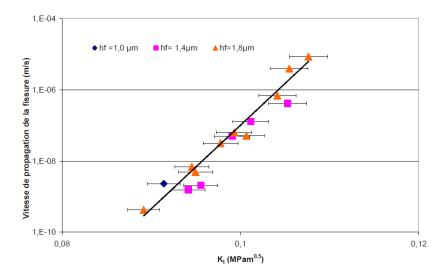

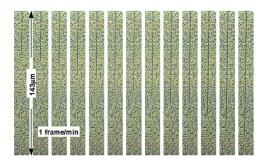

In her PhD manuscript, Brillet tried similar experiments (i.e. channel cracking tests) on  $SiO_2$  films of thicknesses ranging from 2 to 4 µm with a copper interlayer between the silicon substrate and the film. However, her experiments were unsuccessful as the silicon substrate fractured before any sign of crack propagation in the upper film. In contrast, Brillet showed that both more than 1 µm-thick PECVD and spin-on SiOC:H were subjected to sub-critical crack growth through four-point bending tests in ambient environment [10]. Figure I.10 presents the crack velocity measured in SiOC:H films with different thicknesses deposited on silicon substrates as a function of the stress intensity factor.

**Figure I.10:** Crack velocity as a function of stress intensity factor for SiOC:H/Si configurations tested in ambient environment(from [10]). If stands for film thickness.

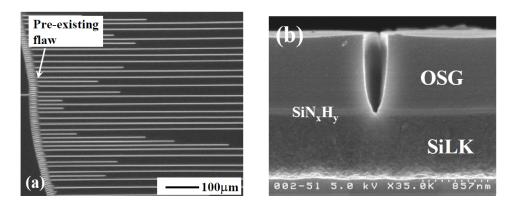

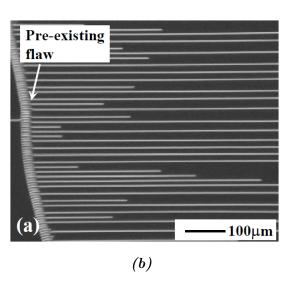

Concerning low k dielectrics, the possibility of generating arrays of stable channel cracks in OSG films of thickness of 2 µm deposited on silicon wafers was demonstrated [54] (see figure I.11), as well as of propagating an interfacial stable crack between an OSG layer and a SiN or SiCN barrier [23, 85, 90]. This demonstrates the sensitivity of this kind of materials and interfaces to sub-critical crack propagation.

Figure I.11: Channel cracks in OSG films (a) for a 2  $\mu$ m-thick OSG deposited on a silicon substrate and (b) for a 1  $\mu$ m-thick OSG deposited on a 60 nm-thick  $SiN_xH_y$  barrier and a 834 nm-thick low k SiOC:H film and then on a silicon substrate (from [54])

#### I.2.4.3 Slow crack growth in silicon nitrides

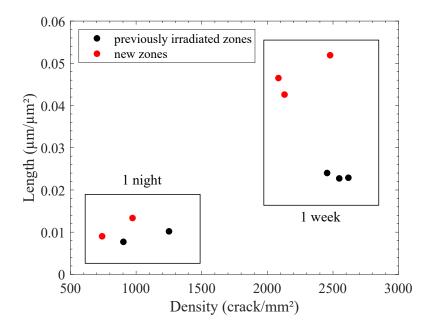

So far, there are few studies on environmentally-assisted cracking in  $SiN_xH_x$  films. In this field, Birringer et al. showed the influence of the environment on interfacial crack growth between  $SiN_xH_y$  films and copper [8]. More recently, Vellinga et al. observed faster crack propagation in  $SiN_x$  barriers deposited on polyethylene nephthalate substrates in higher relative humidity environments using resistance measurements and in situ optical microscopy [138]. They concluded that  $SiN_x$  barriers undergo crack growth enhanced by

the environment. In order to determine the sub-critical growth exponent n, Guan  $et\ al.$  performed dynamic and static bending tests on a  $\mathrm{SiN}_x$  layer deposited on polyethylene nephthalate substrate [48]. Their results suggested that  $\mathrm{SiN}_x$  thin film is sensitive to environmentally-assisted sub-critical crack growth in contrast to bulk  $\mathrm{Si}_3\mathrm{N}_4$ , which is essentially insensitive to this mechanism. However, these studies do not directly measure the crack growth rates as a function of driving force of channel cracks propagating in the  $\mathrm{SiN}_x$  layer. To discuss this problematic,  $\mathrm{Kim}\ et\ al.$  conducted an  $in\ situ$  optical microscopy channel crack experiment in PECVD  $\mathrm{SiN}_x$  layers deposited on PET substrates under different environmental conditions [71]. Their results showed that 250 nm-thick  $\mathrm{SiN}_x$  can be subjected to environmentally-assisted crack growth with a channel crack growth rate about 10 times higher in humid air than under a dry nitrogen atmosphere. Moreover, a higher channel crack density was observed in humid air, meaning that crack propagation and nucleation compete and are both accelerated by water presence in the surrounding environment.

PECVD deposited  $SiN_x$  films differ from the bulk  $Si_3N_4$  in their chemical structure and present oxygen (probably incorporated during the deposition process or by diffusion of oxygen and/or water vapor through the pores upon exposure to the atmosphere) and hydrogen mainly linked to Si and N atoms. Kim *et al.* explained the mechanism of sub-critical crack growth of  $SiN_x$  films similarly to what happen in glass samples [71]. In details, water molecules could enhance the rate of Si-N bond breaking, so the crack growth rate, at a crack tip. They proposed a stress-assisted hydrolysis reaction similar to the surface dissolution of  $Si_3N_4$ :  $Si_3N_4 + 6H_2O \rightarrow 3SiO_2 + 4NH_3$ . However, it is know that no crack growth in  $Si_3N_4$  can occur due to its covalent bonding features. If crack propagation is observed in PECVD silicon nitride materials, it seems to be more due to the presence of some hydrogen and oxygen molecules incorporated during the deposition process.

#### I.3 Conclusion

In this chapter, typical reliability tests used in the microelectronic industry were presented to provide a general understanding of the industrial requirements and solutions provided to reduce the long-term risk of product failure. These tests will be used in chapter III to study the influence of the environment (*i.e.* temperature and humidity level) on the dielectric materials integrity. A particular attention will be paid to films in production at STMicroelectronics. Indeed, these films are generally thinner than model samples, and a dedicated characterization is needed.

Then, basic introduction to fracture mechanics was provided to introduce notions used latter in chapter IV to analyze fracture testing results. A particular attention was paid to the stress-corrosion cracking mechanism already observed in dielectric materials, similar to the ones studied in this manuscript. However, most of the studies are performed on

thick model layers (*i.e.* thicknesses of more than one micron) deposited on substrates, while submicronic films are targeted in this PhD.

The next chapter will be dedicated to the presentation of the materials investigated in this work and the methods used in that frame.

## CHAPTER II

## Materials and experimental methods

Failures may occur in the BEoL stack due to chip-package interactions, and are particularly known for their criticality. This results in the appearance of cracks in the dielectric materials constituting the stack. Beyond the tests already performed either on the assembly line or during product qualification, questions remain open regarding the mechanical behavior of the product, its long-term reliability and the effects of the environment. Especially, porous materials with low dielectric constant  $(low\ k)$ , used on the most advanced technology nodes, are little described under this regime. Thus, in this manuscript, we propose to investigate more precisely four dielectric materials including two types of advanced  $low\ k$  and two others with a more classic nature. This would provide an overall picture of BEoL dielectric thin films used in microelectronic industry. The target is to evaluate the potential variations of mechanical properties due to environmental aging and the effect of the environment on the crack mechanisms.

This chapter first presents the studied dielectric materials. Then, experimental characterization methods involved in this PhD are described: nanoindentation for the determination of micro-mechanical parameters (reduced modulus, hardness, local fracture resistance) and wafer-curvature measurement for the evaluation of film residual stresses. Finally, complementary small-scale fracture tests are presented with different bending set-ups: double-torsion and four-point bending configurations.

## Contents

| II.1 Inve | stigated materials                                                      | <b>35</b> |

|-----------|-------------------------------------------------------------------------|-----------|

| II.1.1    | Silicon wafer substrate                                                 | 36        |

| II.1.2    | Silicon nitride                                                         | 36        |

| II.1.3    | Silicate glass                                                          | 36        |

| II.1.4    | Carbon-doped silicon oxide (low k)                                      | 37        |

| II.1.5    | Porous and carbon-doped silicon oxide (ultra-low k) $\ \ldots \ \ldots$ | 37        |

| II.2 Cha  | racterization of mechanical properties                                  | 37        |

| II.2.1    | Nanoindentation                                                         | 38        |

| II.2.2    | Wafer-curvature measurement                                             | 51        |

| II.3 Inve | stigation of fracture mechanisms                                        | <b>54</b> |

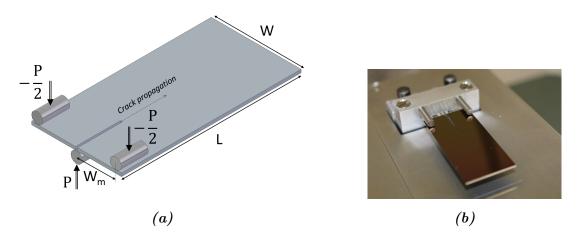

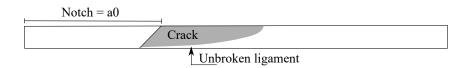

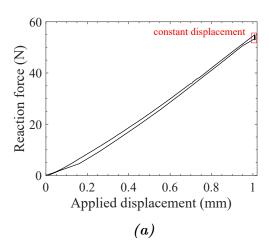

| II.3.1    | Four-point bending                                                      | 54        |

| II.3.2    | Double-torsion                                                          | 57        |

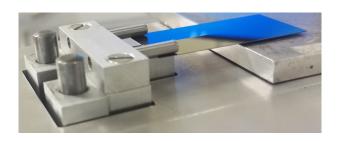

| II.3.3    | Bending micro-machine description                                       | 60        |

| II.4 Dire | ct observation methods                                                  | 61        |

| II.4.1    | Atomic force microscopy                                                 | 61        |

| II.4.2    | Scanning electron microscopy and focused ion beam                       | 62        |

## II.1 Investigated materials

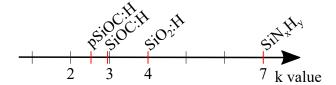

As already shown in the general introduction, most of the mechanical failures occur in the brittle dielectric materials rather than in metals. Interconnected metal lines are insulated from one to another through a matrix of dielectric materials. The embedded materials, characterized by their dielectric constant (figure II.1), depend on the technology node and can be divided in two categories: the dense and the porous materials. The former is the oldest one and is based on silicon oxide with various doping components. The latter, with a much lower dielectric constant, is used in the most advanced nodes. Hence, two porous dielectric materials, a typical silicate glass used as reference, and a passivation silicon nitride known as a stable material in environment, were selected. All of them are massively used in the microelectronic industry and will provide an overview of the behavior of this category of materials.

Figure II.1: Dielectric constant values for the studied dielectric materials. The dielectric constant refers to the relative permittivity of the material, which is the ratio of the capacitance of a capacitor using that material as a dielectric, compared with a similar capacitor that has vacuum as its dielectric.

In summary, four thin ceramic films, used as dielectric layers in the interconnect part of the chip, were studied:

- a silicon nitride

- a silicate glass

- a carbon-doped silicon oxide (referred to as low-k)

- a porous and carbon-doped silicon oxide (referred to as *ultra low-k*)

The silicon nitride is used as a passivation layer to protect the interconnections from any external aggression (environmental as well as mechanical). This layer is the last deposited at the very top of the BEoL stack. The silicon oxide is found at the global levels at the top of interconnections. The two last materials, found at the bottom of the stack (M1 to M5 - see figure 2), are the so-called *low-k* dielectrics, developed in the past decades to reduce the dielectric constant of the interconnection insulation.

All films correspond to industrial real layers deposited onto 300 mm diameter wafers under clean-room environmental conditions at STMicroelectronics Crolles site. They are deposited by Plasma-Enhanced Chemical Vapor (PECVD) deposition onto silicon substrates<sup>1</sup>. This technique consists in depositing a film on a substrate through surface

<sup>&</sup>lt;sup>1</sup>Thanks to the Process Development Dielectric team at STMicroelectronic Crolles site

chemical reaction, by creating the elements to be deposited in a gaseous form, then causing the nucleation of the film on the surface of a substrate. The gas phase includes the precursors carrying the chemical elements to be deposited, additives, and a carrier gas. In order to reduce the deposition temperature, the CVD technique is enhanced by plasma, which provides energy to the chemical reaction (PECVD). This technique is used to deposit dielectric films at a temperature of 400°C and below.

#### II.1.1 Silicon wafer substrate

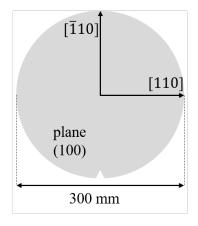

Substrates were (100) single-crystal silicon wafers with a diameter of 300 mm and a thickness of 775 µm (figure II.2). As silicon is anisotropic, its mechanical properties depend on the considered crystallographic plane. In this study, default mechanical properties of the substrate are taken from literature for single-crystal silicon considering the same crystallographic orientation [99].

Figure II.2: (100) silicon wafer

#### II.1.2 Silicon nitride

Amorphous silicon nitride ( $SiN_xH_y$ ) was deposited at a temperature of 380 °C from silane ( $SiH_4$ ), ammonia ( $NH_3$ ), and nitrogen ( $N_2$ ) precursors.  $SiN_xH_y$  contains about 36 at.% of silicon, 48 at.% of nitrogen and 16 at.% of hydrogen bonded both to the Si and N atoms [17]. Its dielectric constant, noted k, is about 7 (figure II.1).

# II.1.3 Silicate glass

Silicate glass (SiO<sub>2</sub>:H), known as the standard Undoped Silicate Glass (USG), was deposited from silane (SiH<sub>4</sub>) and nitrous oxide (N<sub>2</sub>O) precursors at 400 °C. SiO<sub>2</sub>:H contains a small amount of hydrogen (< 5 at.% [17]) forming Si-OH bonds. The SiO<sub>2</sub>:H has a dielectric constant about 4.

# II.1.4 Carbon-doped silicon oxide (low k)

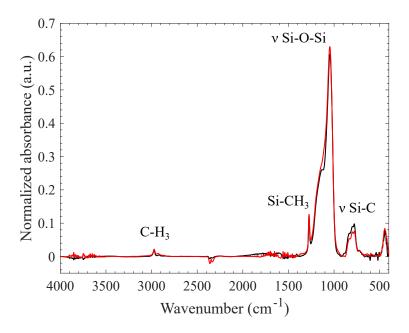

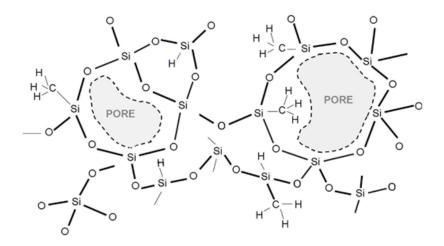

Carbon-doped silicon oxide (SiOC:H) was deposited from trimethylsilane (labeled 3MS,  $(CH_3)_3SiH$ ) and oxygen at 350 °C. SiOC:H has a dielectric constant about 3. This low value of k is obtained by incorporating methyl groups (replacing Si-O-Si bonds by Si-CH<sub>3</sub> bonds), which induces structural nanoporosity. SiOC:H has a porosity fraction about 6-8% and a density about 1.4 g/cm<sup>3</sup>.

# II.1.5 Porous and carbon-doped silicon oxide (ultra-low k)

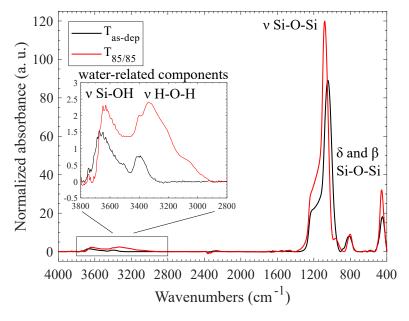

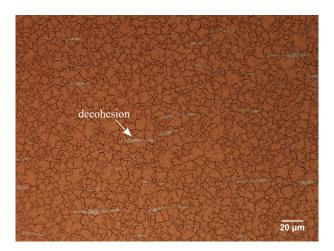

Porous and carbon-doped silicon oxide (pSiOC:H) was obtained from co-deposition at 300 °C of a silica-based matrix together with an organic polymer playing the role of sacrificial porogen. Precursors were methyldiethoxysilane ( $C_5H_{13}O_2Si$ , named mDEOS) and bicycloheptadiene ( $C_{14}H_{18}$ , named BCHD). After deposition, the film was irradiated by UV-assisted thermal curing at 380 °C to remove the porogen and create the pores. Its dielectric constant is less than 3. pSiOC:H has a density about 1.2 g/cm<sup>3</sup>.

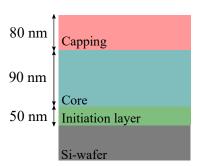

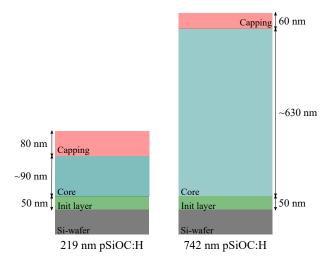

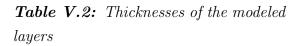

Three sub-layers form the p-SiOC:H: the initiation, the core, and the capping (figure II.3). The initiation layer is a silicate glass deposited on the silicon substrate. The core is then deposited and has an open porosity with a fraction of 17%. On top of it, there is the capping with a porosity fraction of 13%. The decrease in porosity is obtained by decreasing the proportion of porogen amount over the silica-based matrix. The pores have an average size of 0.6 nm. For a 220 nm thick p-SiOC:H, the initiation, core and capping layers have thicknesses respectively of 50, 90 and 80 nm.

Figure II.3: Schematic description of the 220 nm-thick ultra-low k porous and carbon-doped silicon oxide

# II.2 Characterization of mechanical properties

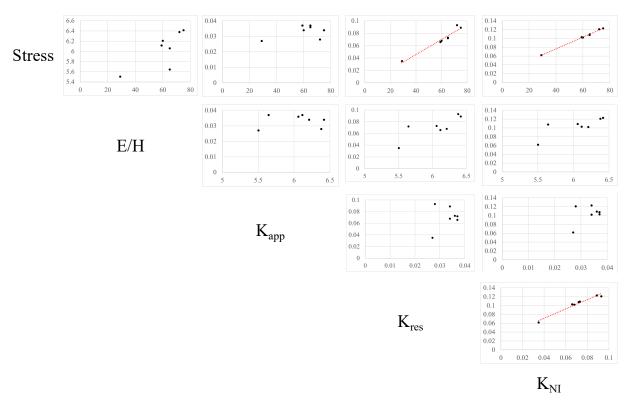

To evaluate the effect of environmental aging on dielectric materials, some mechanical key parameters need to be measured. Nanoindentation tests were performed to determine the reduced modulus, hardness and fracture resistance of the dielectric films at the local scale. In addition, the residual stresses of each film was also characterized thanks to the wafer-curvature measurement.

#### II.2.1 Nanoindentation

#### II.2.1.1 General presentation

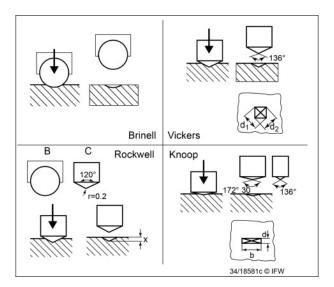

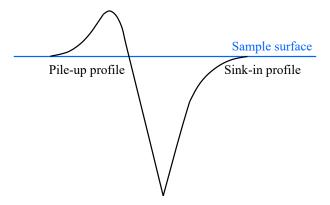

Nanoindentation is a widely used method for testing small-scaled materials. Indeed, this method is particularly suitable for evaluating local mechanical properties, which is especially attractive for thin films deposited on a substrate. Nanoindentation originates from the classical hardness test, whose the principle is to measure the print size left by a geometry-known tip after penetration. Several types of hardness are defined depending on the tip geometry (figure II.4)[97].

The difference between hardness test and nanoindentation is related to the penetration depth. The latter is limited to two hundreds of nanometers for the nanoindentation, whereas the micro and macro-indentation hardness tests go deeper into the tested material. Another difference relies on the resulting hardness computation. The area used for the hardness calculation corresponds to the print size measured on the contact surface for the standard hardness testing, while for instrumented nanoindentation, the area is the projected tip area calculated through calibration tests (detailed later).

Figure II.4: Classical hardness tests (from [97])

Modifying tip geometry and applied load, nanoindentation can give access to several mechanical properties: elastic modulus and hardness [113], toughness [80], as well as adhesion strength of films [72, 98, 119, 147].

#### II.2.1.2 Indenter geometry

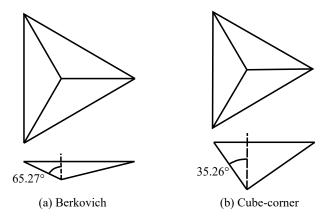

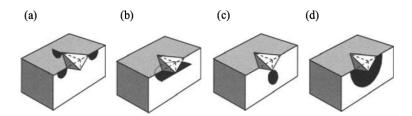

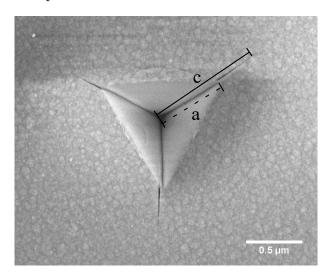

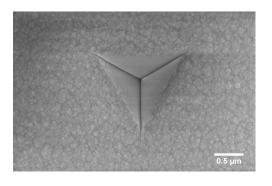

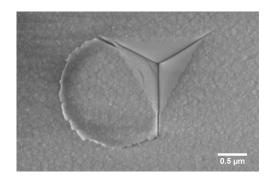

Several tip geometries can be used for nanoindentation testing. The choice of the geometry depends on the tested material and the targeted property. Two pyramidal indenters used to test our dielectric films are schematized in figure II.5: the Berkovich indenter for the measurement of reduced modulus and hardness on the one hand, and the cube-corner indenter to determine the fracture resistance on the other hand.

Figure II.5: Indenter tip geometries: (a) Berkovich and (b) cube-corner

Both are three-sided pyramids made of diamond, which elastic properties are taken into account through the reduced modulus. The two tips differ in their face angle: 65.27° for the Berkovich and 35.26° for the cube-corner (figure II.5).

The Berkovich is a common tip used to determine elastic modulus and hardness of materials [36], while the cube-corner is found to favor crack initiation at very small applied loads. Thus, this tip has gained popularity for the evaluation of an apparent fracture toughness in small volumes, for thin films in particular [62, 110]. Indeed, the sharp end of the cube-corner tip generates cracks more easily from the corners of indentation imprints; a higher strain is reached for an equivalent indentation depth. This approach is more detailed in §II.2.1.4.

#### II.2.1.3 Elastic modulus and hardness (Berkovich test)

#### Oliver-Pharr model

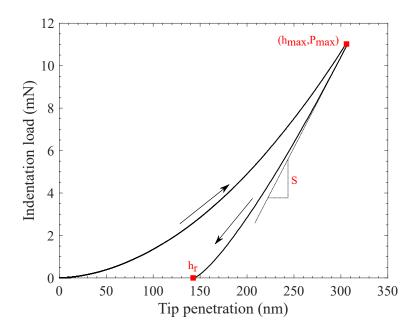

The calculation of reduced modulus and hardness parameters is based on a loading-unloading indentation cycle. During an instrumented indentation test, the applied load P and tip penetration h are recorded continuously (figure II.6).

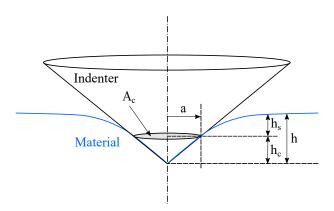

The most common analysis of indentation tests adopts the Oliver-Pharr's procedure [113, 114]. Its popularity comes from its simple implementation, the precise analysis of the load-displacement curve and the precise definition of the contact between the indenter and the material. We present the contact geometry in figure II.7 using a conical indenter as a reference case, as commonly done in instrumented indentation.

**Figure II.6:** Typical nanoindentation load-displacement curve: loading/unloading cycle.  $P_{max}$  is the maximal applied load,  $h_{max}$  is the maximal penetration reached by the indenter,  $h_r$  is the depth of the residual print after unloading and S is the contact stiffness at the beginning of the unloading.

**Figure II.7:** Schematic representation of the contact for a conical indenter as defined in [114]. h is the tip penetration,  $h_s$  is the vertical displacement of the surface,  $h_c$  is the true contact depth,  $A_c$  is the contact area calculated according to  $h_c$  and  $r_c$  is the contact radius.

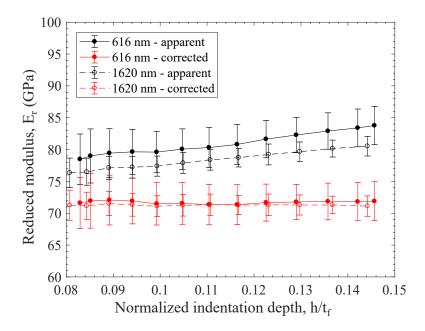

The true contact depth during indentation is calculated with:

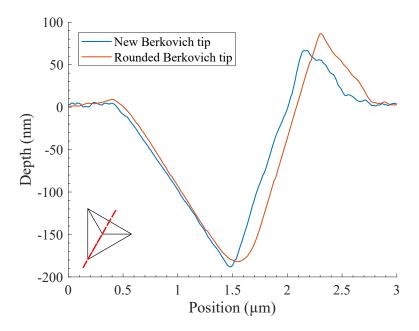

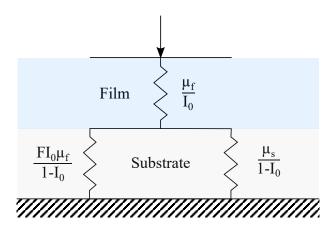

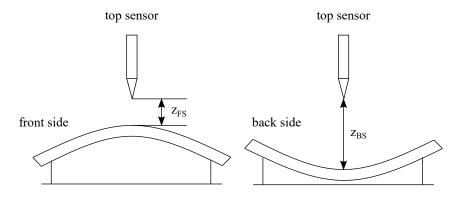

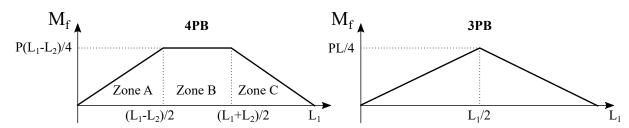

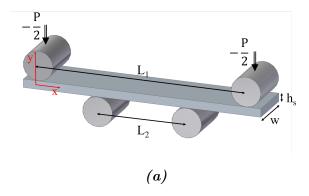

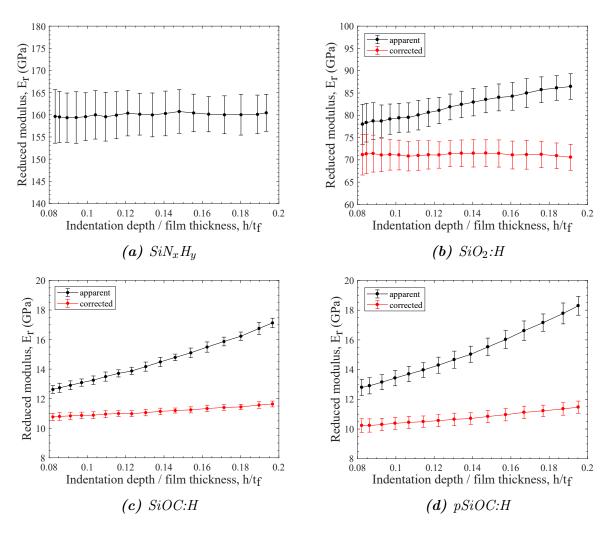

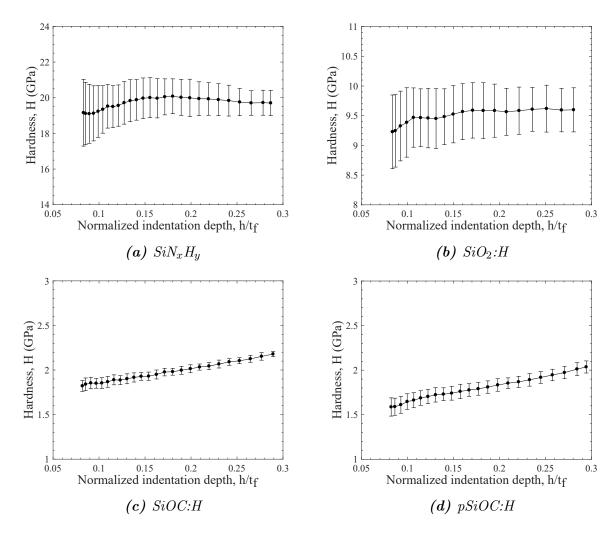

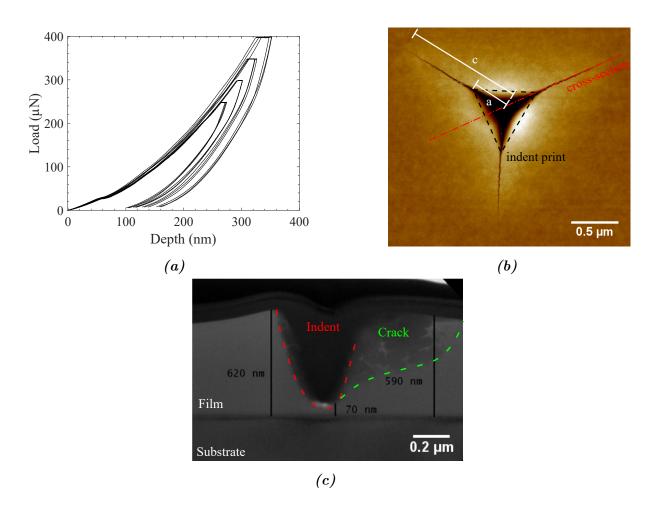

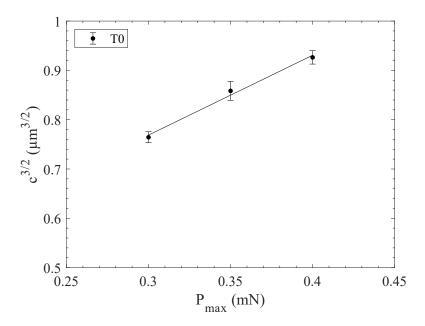

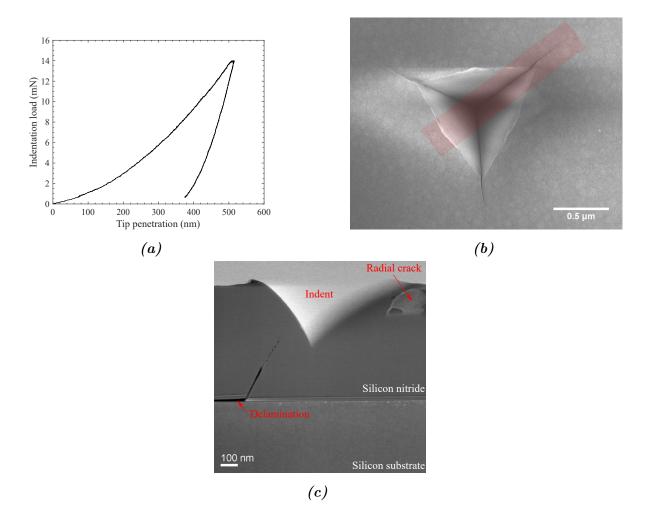

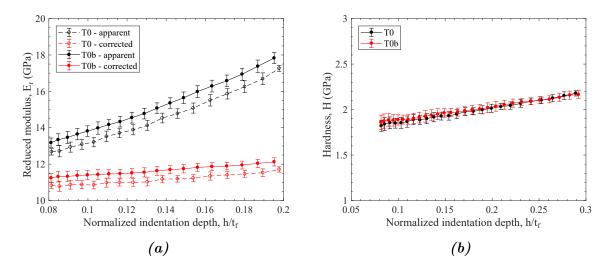

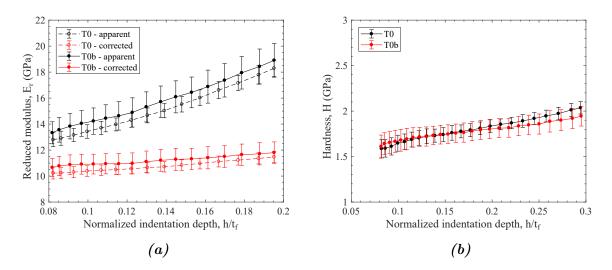

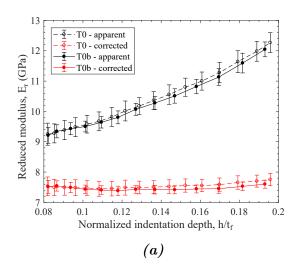

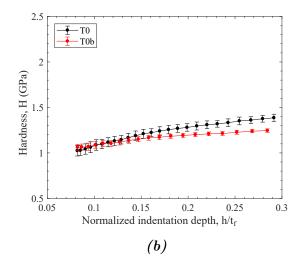

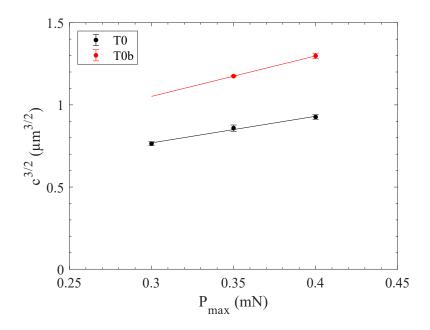

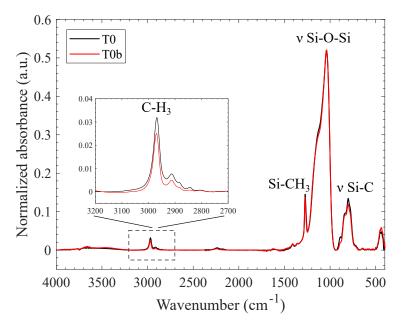

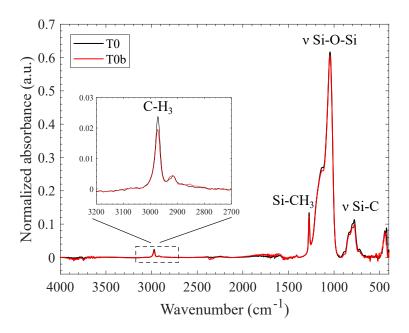

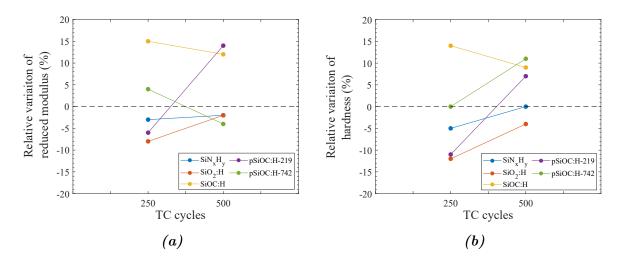

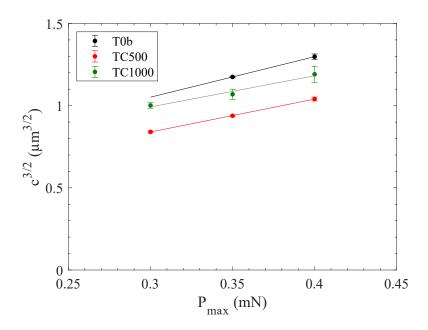

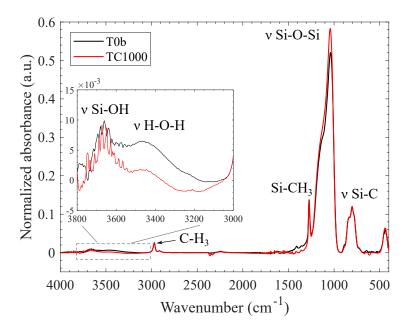

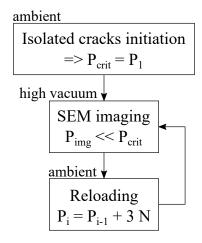

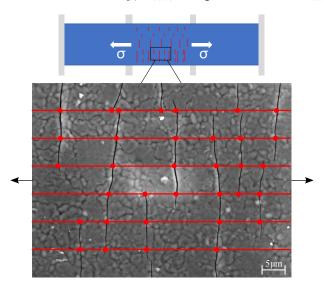

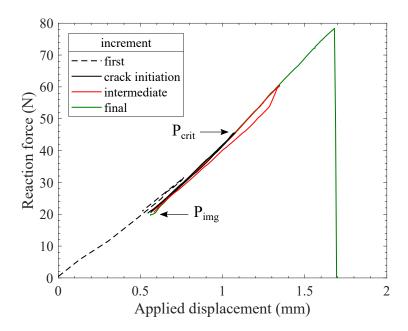

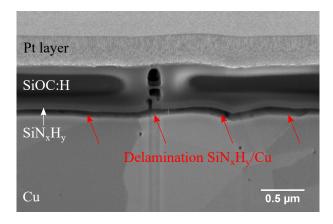

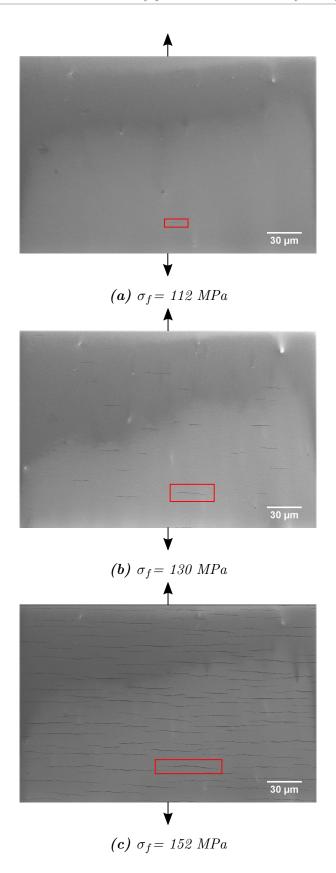

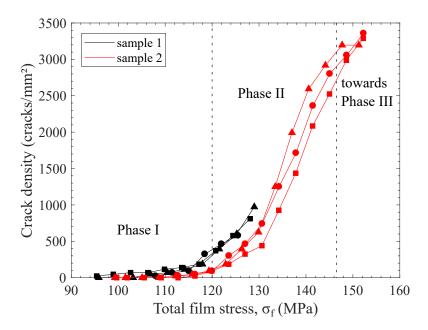

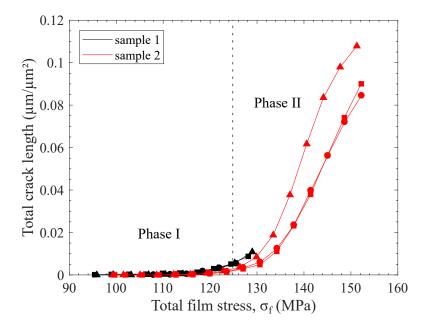

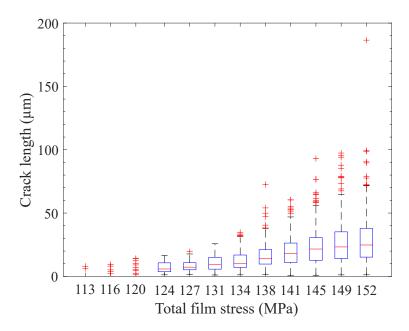

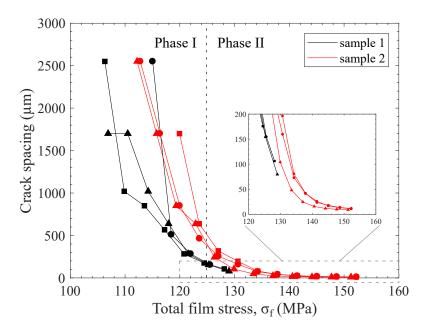

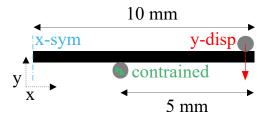

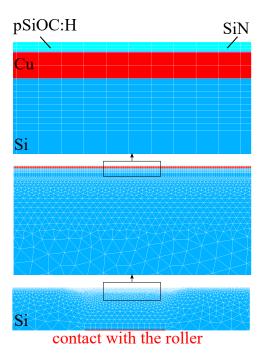

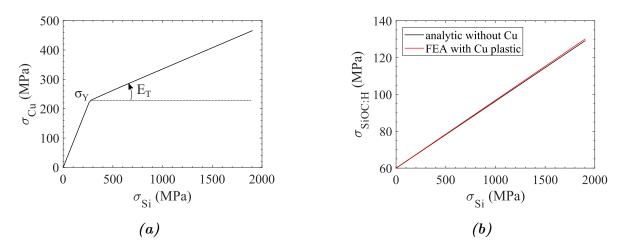

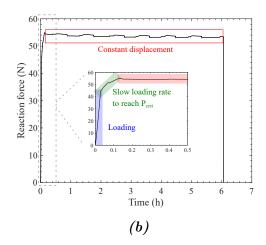

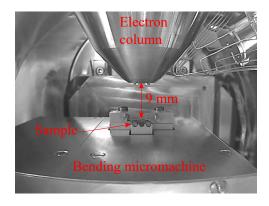

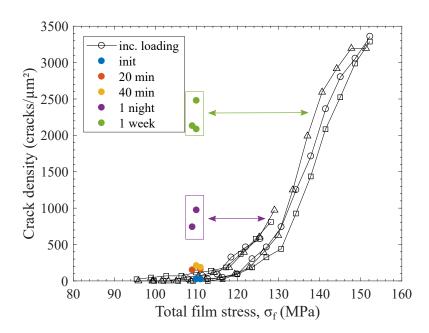

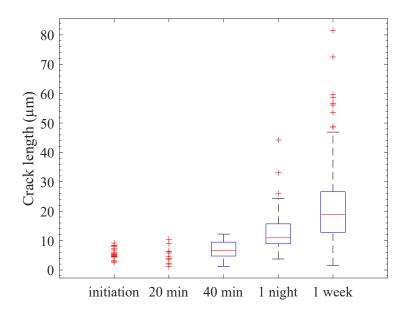

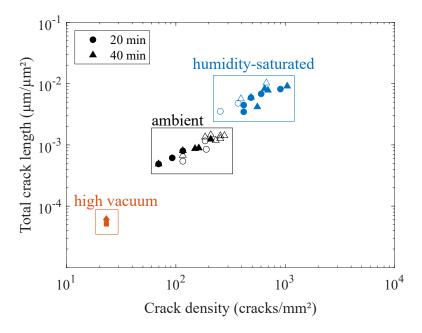

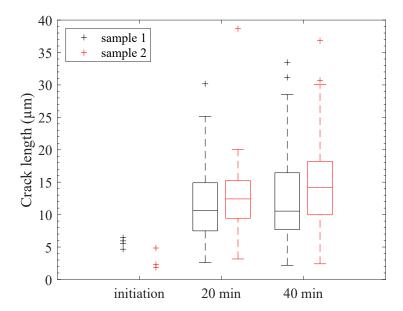

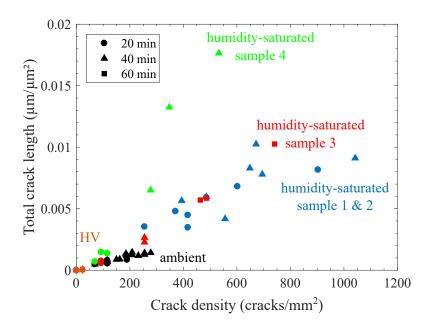

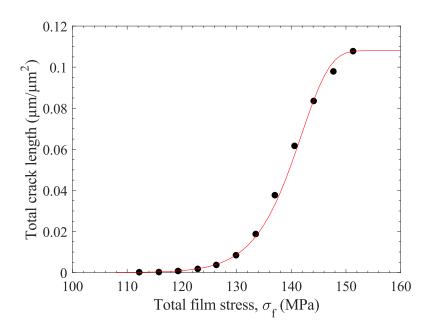

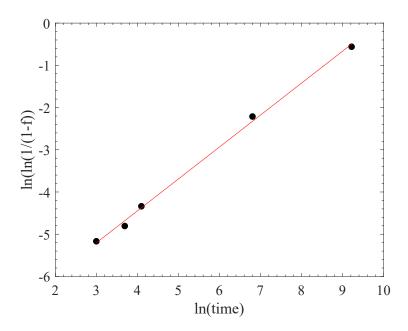

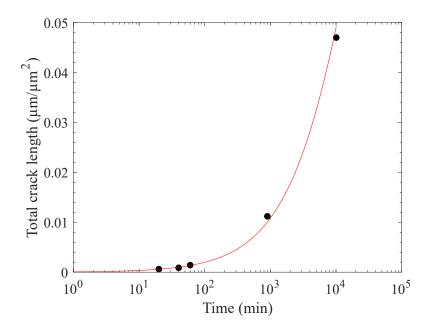

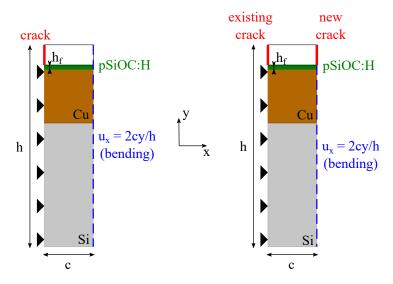

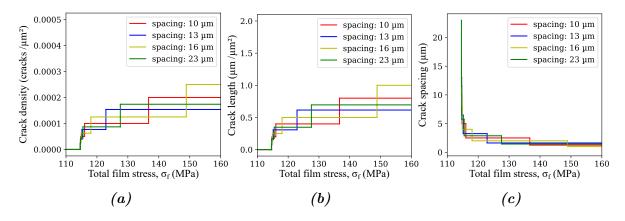

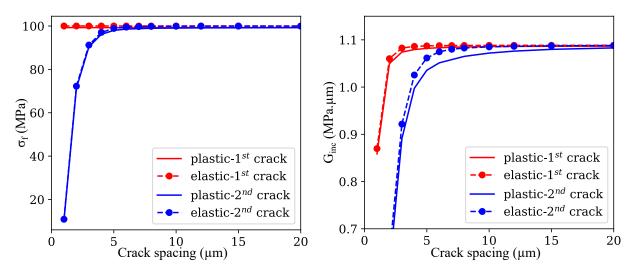

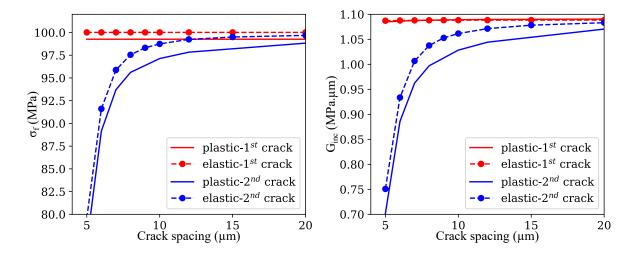

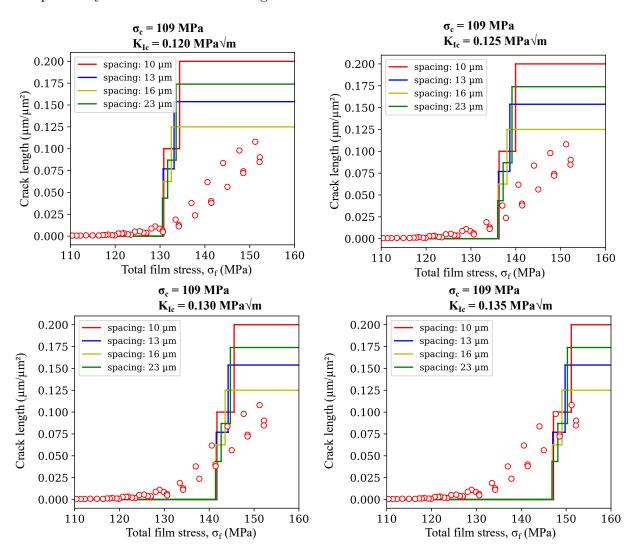

$$h_c = h - h_s \tag{II.1}$$