## Automated verification and synthesis of distributed systems: in particular applied to SDN-IoT platform

Abdul Majith Noordheen

#### ▶ To cite this version:

Abdul Majith Noordheen. Automated verification and synthesis of distributed systems: in particular applied to SDN-IoT platform. Networking and Internet Architecture [cs.NI]. Université Rennes 1, 2022. English. NNT: 2022REN1S035. tel-03882284

## HAL Id: tel-03882284 https://theses.hal.science/tel-03882284v1

Submitted on 2 Dec 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE

## L'UNIVERSITÉ DE RENNES 1

ÉCOLE DOCTORALE Nº 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: « l'informatique »

Par

## « Abdul Majith NOORDHEEN »

- « Automated Verification and Synthesis of Distributed Systems »

- « Applied to SDN and SDN-based IoT platform »

Thèse présentée et soutenue à Rennes, le 7 Juin 2022 Unité de recherche : « SUMO Team, Inria, Bretagne »

#### Composition du Jury :

Présidente : Sophie PINCHINAT Professeure, Université de Rennes

Rapporteurs : Thi-Mai-Trang NGUYEN Maitresse de conférence, HDR, LIP6, Sorbonne Université

Gwen SALAUN Professeur, CONVECS, LIG, Université de Grenoble

Examinateurs : Béatrice BÉRARD Professeure, LIP6, Sorbonne Université

Stefan Haar DR Inria, INRIA, LSV, ENS Paris-Saclay,

Dir. de thèse : Hervé MARCHAND Chargé de Recherche, HDR, INRIA, Rennes

Co-dir. de thèse : Dinh Thai BUI Nokia Bell Labs France

Co-dir. de thèse : Ocan SANKUR Chargé de Recherche, CNRS, Université de Rennes

## RÉSUMÉ

#### 1 - Introduction

Notre principale motivation pour ce travail est l'automatisation de la mise à jour cohérente et l'intégration incrémentale de nouvelles fonctionnalités pour des applications distribuées. Un système distribué est une collection d'entités communicantes qui sont en général complexes. Chaque entité est unique en termes de comportement, de type de matériel, de procédure intégrée et de contraintes locales. La collection de ces diverses entités doit satisfaire des exigences globales tout en respectant leurs contraintes locales. Concevoir, maintenir et mettre à jour des fonctionnalités supplémentaires dans l'application du système distribué sans erreur est un défi en lui-même. Dans le cadre de ce document, nous utilisons des schémas de vérification formelle pour vérifier que le système distribué satisfait aux exigences globales. Afin d'effectuer la vérification formelle d'un système distribué par rapport aux exigences globales, nous modélisons l'ensemble d'entités communicantes comme un système de transitions distribué. Nous utilisons la composition d'automates et de systèmes de transition symbolique communicants pour modéliser le système distribué donné. Les exigences globales du système distribué sont modélisés par l'intermédiaire de logique temporelle linéaire (LTL). Dans le but d'intégrer de nouvelles fonctionnalités dans l'application distribuée de manière incrémentale, nous utilisons des techniques de synthèse modulaire et compositionnelle. Nous modélisons les fonctionnalités correspondantes dans un modèle abstrait et ses exigences comme une spécification de sécurité. Basé sur le modèle distribué, en utilisant la technique de synthèse réactive, nous générons des contrôleurs de supervision pour ce nouveau modèle. Le contrôleur de supervision produit contrôle ce nouveau modèle, de sorte que celui-ci soit cohérent et satisfasse les spécifications globales. En général, la génération du contrôleur de synthèse pour les modèles distribués donnés est coûteuse en termes d'exigences de mémoire et de temps de calcul. Afin de générer le contrôleur en temps réel et d'ouvrir la possibilité d'intégrer de nouvelles fonctionnalités de manière incrémentale, nous utilisons des techniques de synthèse compositionnelle et modulaire.

Nous sommes particulièrement intéressés par l'application des techniques de vérification formelle et de synthèse vis-a vis du réseau *Software Design Design (SDN)* qui coordonne l'application de l'internet des objets (*IoT*). L'application *SDN-IoT* est un système distribué qui est bien adapté pour se fonder sur la synthèse et la vérification formelle. Les applications *IoT* ont un important impact dans divers domaines comme l'industrie, les appareils ménagers, la télésurveillance, etc. Les systèmes distribués permettent un mécanisme de contrôle économique et flexible permettant l'application de mise en réseau permettant de coordonner diverses applica-

tions *IoT* dans une plate-forme commune.

Pour montrer l'utilité de la synthèse de contrôle réactif et générer automatiquement les contrôleurs de supervision pour les différentes entités dans l'application *SDN-IoT*, nous prenons le comportement abstrait du véhicule pour tout ce qui est application et spécification *V2X*, et le modélisons dans l'outil de synthèse réactif *BZR*. Nous avons généré un contrôleur de supervision pour le modèle *V2X* ainsi que diverses spécifications de sécurité. En utilisant le même outil, nous avons généré le code *C* du contrôleur à partir du modèle et des spécifications correspondants. Cette façon de modéliser et de générer le code implémentable ouvre la voie à l'automatisation de l'intégration de nouvelles fonctionnalités à partir de comportements de fonctionnalités abstraites d'une manière cohérente.

## 2 - Vérification et contrôle de systèmes distribués

Les applications des systèmes distribués sont omniprésentes dans notre monde moderne. Prenons l'exemple des rovers martiens : depuis la terre, on peut commander un dispositif d'actionnement sur une autre planète et recueillir diverses données scientifiques. Ces boucles de commande et d'actions sont rendues possibles par la communication de divers dispositifs informatiques, capteurs et actionneurs. Un système distribué est un mot-clé vague et ambigu utilisé dans toute la littérature informatique. Lorsque nous mentionnons un système distribué (DS), nous voulons surtout dire ce qui suit :

#### **Systèmes Distribués**

Un système distribué est une coordination de plusieurs éléments informatiques autonomes qui apparaissent à ses utilisateurs comme un seul système cohérent. Chaque élément informatique autonome est capable de se comporter de manière indépendante et peut être un dispositif matériel ou un processus logiciel. Du point de vue de l'application, cette coordination de multiples éléments autonomes peut être considérée comme un système unique.

## 2.1 - Modèle de systèmes distribués

Dans un *DS* donné, deux entités quelconques communiquent via des files d'attente synchrones ou asynchrones. Ces files d'attente synchrones sont des canaux de réseaux locaux à haut débit qui transfèrent efficacement le message instantanément à l'autre, ce qui nécessite souvent un canal de connexion dédié entre la paire d'entités informatiques dans le *DS*. En revanche, les files d'attente asynchrones ne sont pas à haut débit et ces types de files d'attente sont le plus souvent du type *FIFO*, de sorte qu'une seule entité informatique centralisée peut répondre aux demandes

de nombreux utilisateurs en disposant d'un seul canal de file d'attente, ce qui constitue une solution rentable dans les services de réseaux typiques [ST16]. En théorie, les communications entre n'importe quelle paire d'entités dans le *DS* seront soit synchrones soit asynchrones.

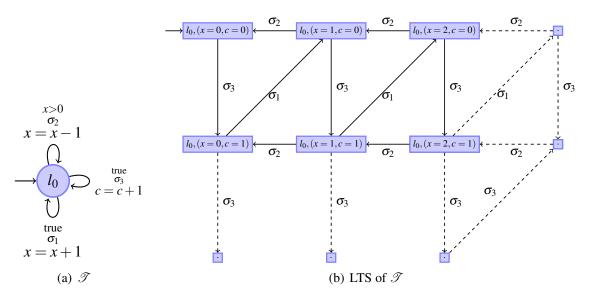

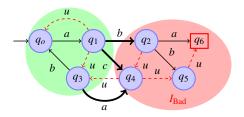

Dans ce document, nous considérons l'aspect synchrones et asynchrone. Nous utilisons la composition d'automates et de modèles de systèmes de transitions symboliques pour modéliser les divers composants. Pour les files d'attente asynchrones *FIFO*, nous avons défini le modèle de systèmes de transitions symboliques communicants avec des canaux *FIFO*. Nous considérons les systèmes composés de plusieurs systèmes qui communiquent de manière asynchrone au moyen de canaux FIFO supposés non limités et fiables (c'est-à-dire que nous ne sommes pas intéressés par le temps exact que prend un événement pour être transmis mais plutôt par le fait qu'il se produise) [Kal+14][PP91][MW08][LJJ06]. Le fait de choisir des canaux FIFO est motivé par le fait que nous nous intéressons aux systèmes distribués, dans lesquels les actions sont transmises d'un composant à un autre. Nous supposons que chaque composant est modélisé

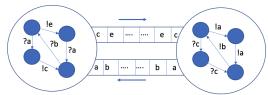

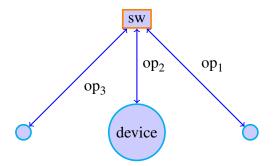

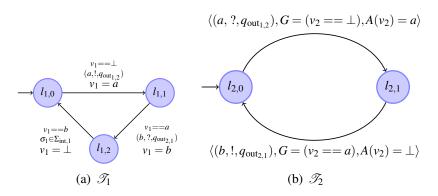

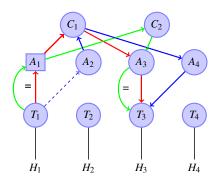

FIGURE 1 : Exemple de systèmes distribués communicant via des canaux FIFO par un système de transitions symbolique. Ainsi, chaque composant du système est un système de transition avec des variables, dont le domaine peut être infini, et est composé de transitions symboliques. Chaque transition possède une garde sur les variables du système et une fonction de mise à jour qui indique l'évolution des variables lorsque la transition est déclenchée. De plus, les transitions sont étiquetées avec des symboles pris dans un alphabet fini. Ce modèle permet la représentation compacte de systèmes infinis lorsque la modélisation du système distribué et les variables d'exigences prennent leurs valeurs dans un domaine infini.

## 2.2 - Vérification de systèmes distribués

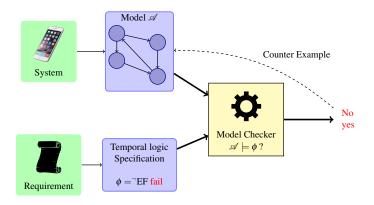

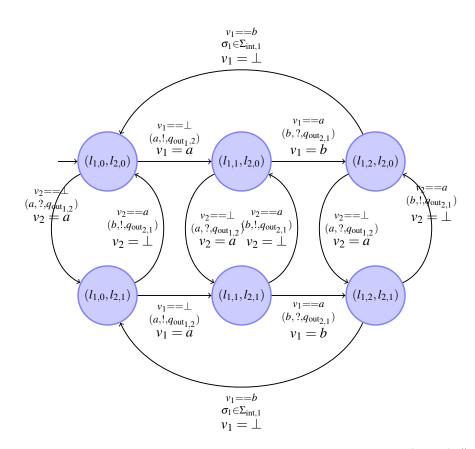

Dans le cadre général des systèmes distribués, pour analyser la correction du système vis-à-vis des exigences du système, on peut utiliser un schéma de vérification formelle, c'est-à-dire le principe du model checking pour les applications critiques de sécurité. Le principe de vérification de modèle peut être vu comme suit :

### Model-checking

Pour un ensemble donné de spécifications : si le système satisfait les spécifications, alors il produit le résultat disant que le système est correct par rapport aux spécifications données. Si ce n'est pas le cas, la vérification notifie l'utilisateur avec un *contre exemple* : une trace de la séquence d'actions effectuée dans le système qui viole la spécification.

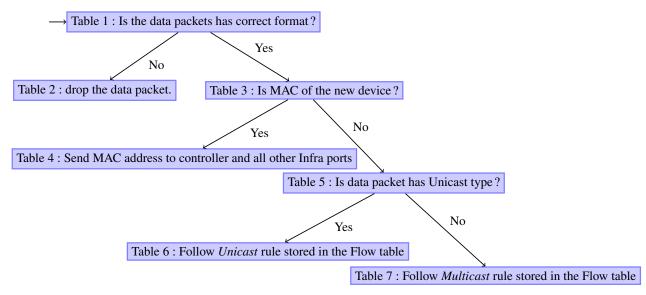

FIGURE 2 : Vérification formelle du système

L'expression des spécifications est importante dans le processus de model checking, pour exprimer les exigences du système. Il existe de nombreuses façons d'exprimer celles-ci; l'une d'entre elles est la logique temporelle linéaire (LTL) [Pnu77], un langage qui convient bien aux systèmes basés sur l'état (comme les automates).

Comme nous considérons les systèmes distribués, nous devons trouver un moyen de faire face à l'explosion de l'espace d'état due à la composition parallèle des différents composants des systèmes distribués. Le raisonnement compositionnel apparaît naturellement lors de la conception d'un système distribué, puisque le concepteur conçoit souvent des spécifications pour chaque composant du système sur lequel des exigences globales doivent être vérifiées. Le raisonnement compositionnel nous permet de vérifier les propriétés de chaque sous-système séparément, et de combiner ces règles pour déduire les propriétés du système global.

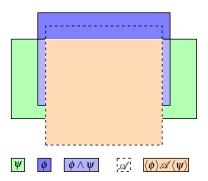

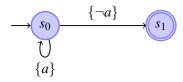

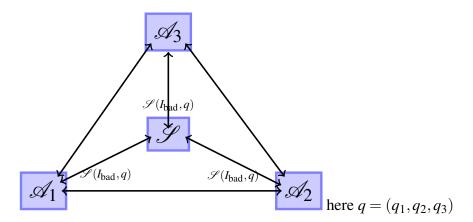

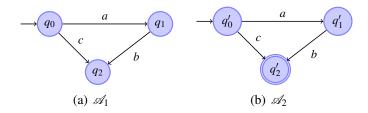

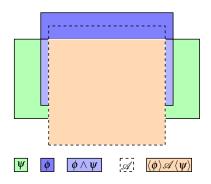

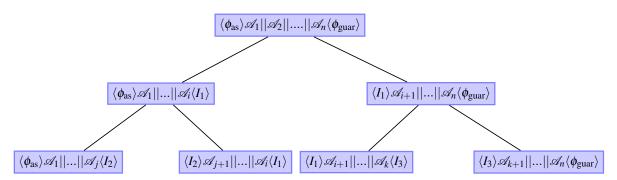

Étant donné un automate  $\mathscr{A}$  et des formules de sécurité LTL  $\phi$ ,  $\psi$ , nous désignons par  $\langle \phi \rangle \mathscr{A} \langle \psi \rangle$  un triple tel que  $\phi$  représente l'*hypothèse* que l'on peut faire sur l'environnement de  $\mathscr{A}$ , tandis que  $\psi$  représente la *garantie* que  $\mathscr{A}$  fournit sous l'hypothèse que l'environnement satisfait  $\phi$ .

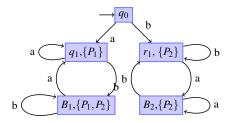

FIGURE 3 :  $\langle \phi_1 \rangle \mathscr{A} \langle \phi_2 \rangle$  illustration

En résumé et sans donner de conditions sur les différents composants et spécifications, ce que nous voulons prouver est le suivant :

$$\frac{\langle \phi_{as} \rangle \mathscr{A}_1 \langle \phi_I \rangle \qquad \langle \phi_I \rangle \mathscr{A}_2 \langle \phi_{guar} \rangle}{\langle \phi_{as} \rangle \mathscr{A}_1 \| \mathscr{A}_2 \langle \phi_{guar} \rangle} \tag{1}$$

l'équation (1) signifie que, si, sous l'hypothèse que  $\mathscr{A}_1 \models \phi_{as}$ ,  $\mathscr{A}_1 \models \phi_I$  et de même pour  $\mathscr{A}_2$  par rapport à  $\phi_I$ , où  $\phi_I$  est une spécification intermédiaire et  $\phi_{guar}$ , alors il entraîne que, si, sous l'hypothèse que le système composé  $\mathscr{A}_1 || \mathscr{A}_2 \models \phi_{as}$ , alors ce système vérifie  $\phi_{guar}$ .

Dans le document, nous avons considéré ce cadre de deux points de vue

- techniques de raisonnement compositionnel basées sur le langage

- techniques de raisonnement compositionnel basées sur des spécifications LTL

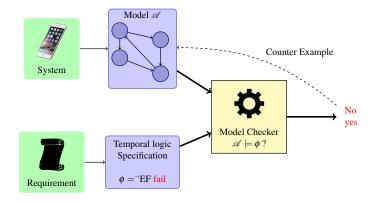

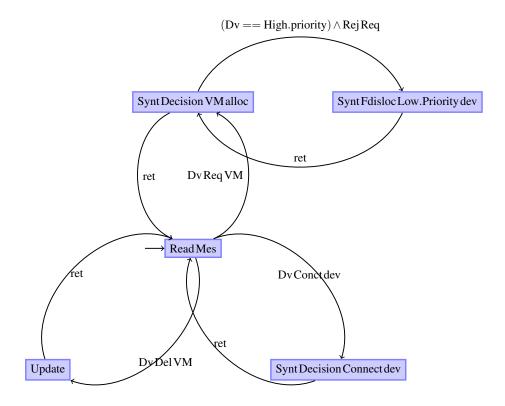

#### 2.3 - Contrôle de systèmes distribués

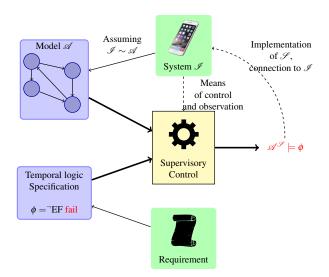

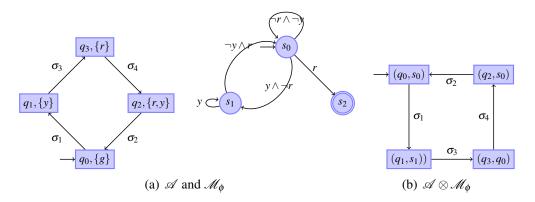

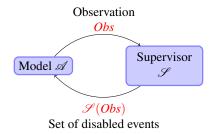

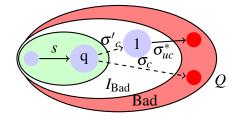

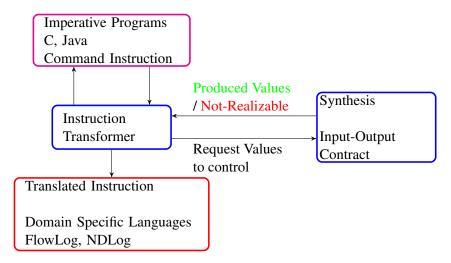

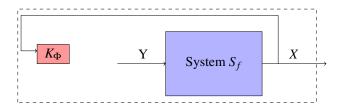

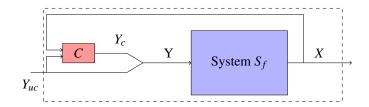

Dans le processus d'automatisation visant à faire fonctionner correctement le modèle de système en cas de violation de la spécification du système, on peut utiliser la technique de synthèse de contrôle réactif, qui repose sur le principe du contrôle des actions contrôlables du système de manière à ce que le comportement du système modélisé satisfasse la spécification du système en désactivant les actions spécifiques à certains instants spécifiques. Un schéma de synthèse abstrait est le suivant :

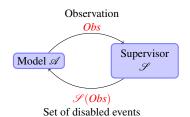

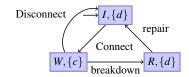

FIGURE 4 : Principe de la synthèse de contrôleur

FIGURE 5 : Contrôle par boucle fermée

#### Synthèse de Contrôleur

Cette théorie permet l'utilisation de méthodes constructives assurant, a priori, et au moyen du contrôle, les propriétés requises sur le comportement d'un système. Étant donné un modèle  $\mathscr A$  d'un système (qui est censé représenter correctement le comportement d'une implémentation) et une *spécification*  $\phi$  (c'est-à-dire des exigences), un contrôleur  $\mathscr S$  doit être dérivé par divers moyens de sorte que le comportement résultant du système en boucle fermée réponde aux exigences.

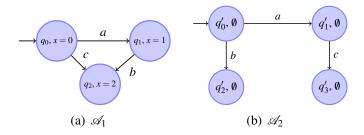

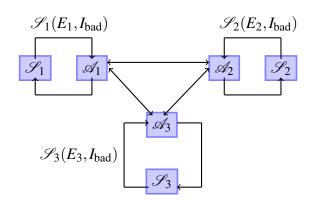

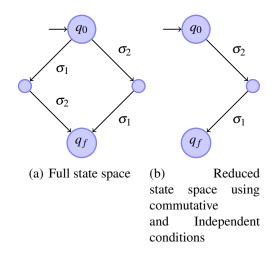

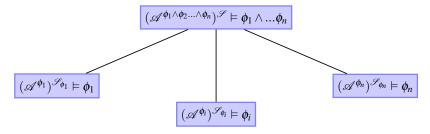

Dans ce document, nous avons d'abord étendu la théorie du contrôle de supervision pour des spécifications *LTL*, puis nous avons considéré le contrôle modulaire ainsi que le raisonnement compositionnel pour la théorie du contrôle décrite comme suit :

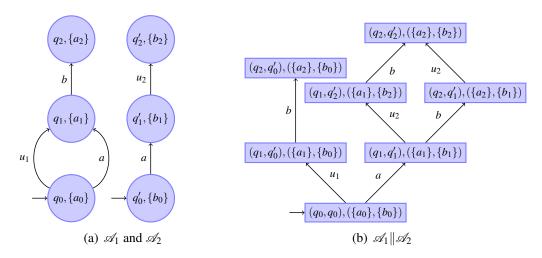

Étant donné deux automates  $\mathcal{A}_1$  et  $\mathcal{A}_2$  et deux spécifications de sécurité  $LTL \phi$  et  $\psi$ , alors

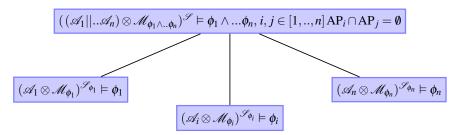

• Contrôle Modulaire

$$\frac{(\mathscr{A}_{1}^{\phi})^{\mathscr{S}_{\phi}} \models \phi \qquad (\mathscr{A}_{2}^{\Psi})^{\mathscr{S}_{\Psi}} \models \Psi}{((\mathscr{A}_{1}^{\phi})^{\mathscr{S}_{\phi}} || (\mathscr{A}_{2}^{\Psi})^{\mathscr{S}_{\Psi}}) \models \phi \wedge \Psi}$$

Raisonnement compositionnel

$$\frac{\langle \phi_1 \rangle (\,(\mathscr{A}_1)^{\mathscr{S}_{\phi_1 \Rightarrow \phi_2}}\,) \langle \phi_2 \rangle \qquad \langle \phi_2 \rangle (\,(\mathscr{A}_2)^{\mathscr{S}_{\phi_2 \Rightarrow \phi_3}}\,) \langle \phi_3 \rangle}{\langle \phi_1 \rangle (\,(\mathscr{A}_1)^{\mathscr{S}_{\phi_1 \Rightarrow \phi_2}}\,) \| (\,(\mathscr{A}_2)^{\mathscr{S}_{\phi_2 \Rightarrow \phi_3}}\,) \langle \phi_3 \rangle}$$

Les deux techniques de contrôle ci-dessus ouvrent la voie à l'intégration de nouvelles fonctionnalités distribuées de manière incrémentale et cohérente.

#### 3 - Software Defined Networks.

Dans ce manuscrit, nous nous intéressons particulièrement aux *software defined networks* contrôlant la coordination des applications de l'internet des objets. Nous avons appliqué le schéma de vérification et de synthèse formelles à cette plateforme *SDN-IoT*. Les méthodes de la vérification formelle et de la synthèse des systèmes distribués que nous fournissons ici ne soient pas limités à la plate-forme *SDN-IoT*, ils peuvent être appliqués à des systèmes distribués génériques.

SDN fournit une manière flexible de mettre en réseau les applications. Grâce à l'indépendance du contrôleur par rapport au réseau de traitement des données, l'entité de contrôle peut mettre en œuvre des algorithmes complexes propriétaires. Il fonctionne sur le principe de l'abstraction des applications, des services réseau. Elle contrôle les événements du réseau et planifie

les ressources du réseau à partir d'une vue abstraite et d'informations sur les réseaux de données à grande échelle et les utilisateurs du réseau. Une telle vue abstraite du principe de contrôle du réseau permet aux contrôleurs *SDN* de coordonner les divers utilisateurs et applications dans une plate-forme commune.

Un tel mécanisme de contrôle abstrait de *SDN* permet d'orchestrer diverses applications *IoT*. Les dispositifs *IoT* sont des systèmes intégrés qui sont intrinsèquement diversifiés et utilisés de manière intensive dans les applications industrielles, les appareils domestiques intelligents et les applications à distance à des fins diverses.

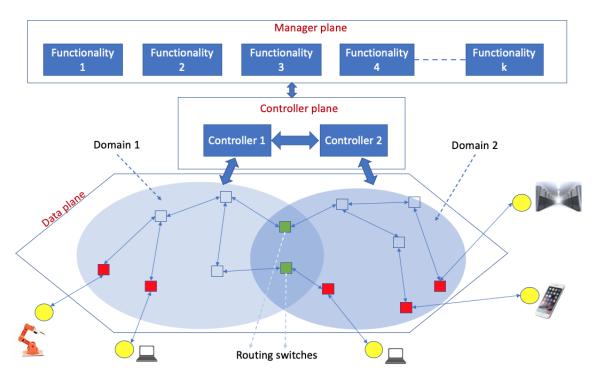

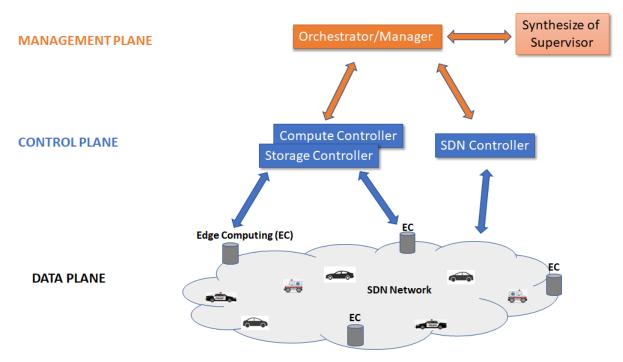

La figure 6 illustre l'architecture typique d'un SDN orchestrant les applications IoT. Le

FIGURE 6: Exemple d'une architecture SDN

data plane représente la couche contenant les *Open Flow Virtual* commutateurs, les clients agissant comme des sources et des terminaux. Les clients peuvent être un serveur, un ordinateur portable, un ordinateur personnel ou tout autre dispositif *IoT* (capteurs, actionneurs, etc.). Le gestionnaire d'applications réseau héberge un certain nombre de politiques réseau et *IoT* et communique avec le plan de contrôle *SDN* par le biais d'une interface de programmation d'applications ouverte, l'interface concernant l'état du réseau et ses exigences. Les contrôleurs, situés dans le data plane, dictent des règles d'acheminement aux éléments d'acheminement des données (commutateurs *Open Flow Virtual*) par le biais d'une *API*. Les fonctionnalités typiques de la couche du plan de gestion (ou couche du gestionnaire d'application) consistent à définir divers accès de contrôle du réseau, un planificateur de ressources, l'établissement de chemins de données sûrs et sécurisés entre diverses politiques de dispositifs authentifiés. Elle maintient également des informations de niveau abstrait sur les dispositifs *IoT* et leurs diverses exigences

d'application. En utilisant ces informations abstraites, il affine les politiques de réseau de niveau fin. En outre, en utilisant les politiques de réseau de niveau fin, il donne des instructions au plan de contrôle du SDN pour mettre en œuvre les politiques dans le plan de données et les utilisateurs du réseau.

Dans un tel contexte, nous utilisons des méthodes de vérification formelle pour assurer la sécurité d'un environnement SDN. En particulier, nous prenons le protocole spécifique SDN conçu par Nokia-Bell labs. L'une des principales difficultés était de comprendre ce protocole particulier et de le modéliser de manière formelle, afin de pouvoir vérifier l'exactitude du système par rapport aux spécifications de sécurité du système. Pour vérifier l'exactitude, nous avons choisi de modéliser le protocole dans l'outil de model checking SPIN. Lorsque les appareils connectés aux réseaux ont une position fixe, nous avons pu prouver que certaines propriétés fondamentales sont remplies par le protocole Nokia. Pour un cas dynamique (c'est-à-dire lorsque les appareils peuvent se déplacer d'une partie à l'autre ou quitter et revenir au réseau), nous avons constaté que le protocole viole l'objectif requis (exactement une propriété de confidentialité des données). Nous avons alors proposé avec l'aide de Nokia une solution pour éviter un tel scénario. Nous avons ajouté une telle solution dans notre modèle et testé le modèle final en vérifiant qu'il répondait bien à la spécification requise. Pendant la phase de vérification, nous avons également rencontré une explosion de l'espace d'état dans notre processus de vérification du modèle SDN. Pour éviter l'énorme espace d'état dans la vérification, nous avons utilisé le raisonnement par composition. Nous avons écrit un article sur la modélisation d'un tel protocole SDN et sa vérification automatisée, intitulé "Compositional model checking of an SDN platform", publié lors de la conférence Design of Reliable Communication Network, 2021 Milan, Italie.

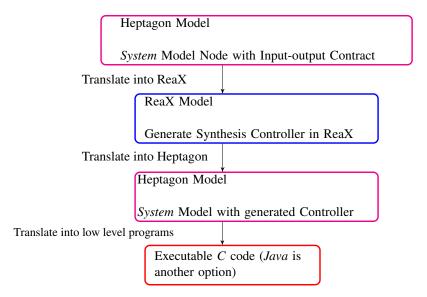

A partir de ce travail, nous sommes passés à la synthèse de commande réactive pour la génération automatisée de contrôleurs. L'étude des règles de raisonnement compositionnel dans notre dernier travail nous a aidé à proposer une "technique de synthèse compositionnelle" pour réduire le problème d'explosion de l'espace d'état dans la synthèse de contrôle discret. Nous avons décrit un cadre détaillé et une preuve de correction concernant la synthèse compositionnelle des systèmes distribués. Cette technique de synthèse compositionnelle ainsi que les techniques modulaires peuvent être utilisées pour trouver des superviseurs pour chaque entité locale d'un système distribué de manière efficace et en temps réel. Afin de montrer l'utilité de l'application de la synthèse, nous avons modélisé le comportement abstrait de V2X. En utilisant la synthèse de contrôle avec une approche compositionnelle et modulaire, nous avons généré le code implémentable de bas niveau de ces contrôleurs en utilisant un outil de contrôleur réactif synchronisé BZR comprenant l'outil Heptagon pour exprimer le modèle du système et ReaX pour automatiser la technique de synthèse afin de générer le contrôleur réactif.

## **TABLE OF CONTENTS**

| 1 | Intr | oductio                      | n                                                        | 15 |  |

|---|------|------------------------------|----------------------------------------------------------|----|--|

|   | 1.1  | Road I                       | Map To Thesis                                            | 16 |  |

|   | 1.2  | Distrib                      | outed Systems                                            | 17 |  |

|   | 1.3  | Challe                       | enges                                                    | 19 |  |

| 2 | Soft | ware-D                       | efined Networks and IoT Platforms                        | 21 |  |

|   | 2.1  | Introd                       | uction to SDN                                            | 23 |  |

|   | 2.2  | IoT De                       | evices and Related Applications                          | 26 |  |

|   | 2.3  | Orches                       | stration of <i>IoT</i> Platform using <i>SDN</i> Concept | 28 |  |

|   | 2.4  | Nokia                        | SDN-IoT Platform                                         | 30 |  |

|   |      | 2.4.1                        | General Problem and Assumptions                          | 31 |  |

|   |      | 2.4.2                        | Cluster of <i>IoT</i> Devices or Virtual Space           | 32 |  |

|   |      | 2.4.3                        | Decentralized Nokia-SDN Network                          | 33 |  |

|   |      | 2.4.4                        | Communication Procedures                                 | 34 |  |

|   | 2.5  | Chapte                       | er Conclusion                                            | 38 |  |

| 3 | Mod  | leling tl                    | he Distributed System and Requirements                   | 39 |  |

|   | 3.1  | Model                        | ling Notations                                           | 39 |  |

|   |      | 3.1.1                        | Languages                                                | 39 |  |

|   |      | 3.1.2                        | Automaton                                                | 40 |  |

|   | 3.2  | 2 Symbolic Transition System |                                                          |    |  |

|   | 3.3  | Forma                        | l Verification of Distributed system                     | 52 |  |

|   |      | 3.3.1                        | Expressing the System Requirements as Specifications     | 52 |  |

|   |      | 3.3.2                        | Verification of Monolithic System                        | 55 |  |

|   |      | 3.3.3                        | Formal Verification of Distributed System                | 57 |  |

|   | 3.4  | Contro                       | ol Synthesis of Distributed system                       | 58 |  |

|   |      | 3.4.1                        | Control Synthesis of Finite State System                 | 60 |  |

|   |      | 3.4.2                        | Control Synthesis of LTL Safety Specifications           | 63 |  |

|   |      | 3.4.3                        | Synthesis of Finite State Distributed System             | 65 |  |

|   |      | 3.4.4                        | Extending the Synthesis concept to the Infinite System   | 71 |  |

|   | 3.5  | Chante                       | er Conclusion                                            | 73 |  |

| 4 | Stat                                                      | e Space                                            | Reduction Techniques                                                    | 75  |  |

|---|-----------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------|-----|--|

|   | 4.1                                                       | State S                                            | Space Explosion Problem in Formal Verification and Synthesis            | 75  |  |

|   | 4.2                                                       | Partial Order Reduction for Model Checking Process |                                                                         |     |  |

|   | 4.3                                                       | Avoidi                                             | ing State Space Explosion Problem by Compositional Reasoning            | 78  |  |

|   |                                                           | 4.3.1                                              | Introduction to Compositional Reasoning                                 | 81  |  |

|   |                                                           | 4.3.2                                              | Compositional Reasoning from a language-based point view                | 82  |  |

|   |                                                           | 4.3.3                                              | Compositional Reasoning for LTL Specification                           | 84  |  |

|   | 4.4                                                       | Extend                                             | ding Compositional Reasoning to Control Synthesis of LTL Specifications | 87  |  |

|   | 4.5                                                       | Chapte                                             | er Conclusion                                                           | 92  |  |

| 5 | Fori                                                      | mal Ver                                            | rification Scheme for Nokia SDN-IoT Platform                            | 95  |  |

|   | 5.1 Existing Modelisation and Verification of SDN systems |                                                    | ng Modelisation and Verification of SDN systems                         | 95  |  |

|   |                                                           | 5.1.1                                              | VERIFLOW                                                                | 96  |  |

|   |                                                           | 5.1.2                                              | KUAI                                                                    | 98  |  |

|   |                                                           | 5.1.3                                              | VERICON                                                                 | 100 |  |

|   | 5.2                                                       | Model                                              | checking Tool                                                           | 101 |  |

|   |                                                           | 5.2.1                                              | Promela Language                                                        | 101 |  |

|   |                                                           | 5.2.2                                              | SPIN                                                                    | 104 |  |

|   | 5.3                                                       | Nokia-                                             | -SDN platform                                                           | 106 |  |

|   |                                                           | 5.3.1                                              | Architecture Building Blocks                                            | 106 |  |

|   |                                                           | 5.3.2                                              | The User's Intent                                                       | 107 |  |

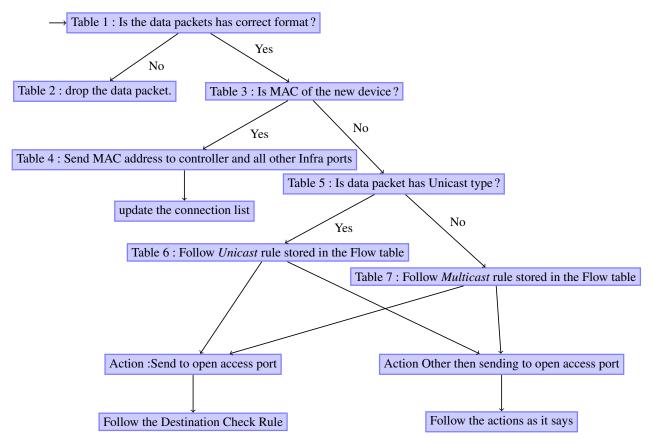

|   |                                                           | 5.3.3                                              | Device Discovery via MAC Learning                                       | 107 |  |

|   |                                                           | 5.3.4                                              | Packet Forwarding                                                       | 108 |  |

|   | 5.4                                                       | Model                                              | lisation of SDN                                                         | 109 |  |

|   | 5.5                                                       | Genera                                             | ated Automata Models                                                    | 111 |  |

|   |                                                           | 5.5.1                                              | Automaton for Devices                                                   | 111 |  |

|   |                                                           | 5.5.2                                              | Automaton for Switches                                                  | 112 |  |

|   |                                                           | 5.5.3                                              | Automaton for Controllers                                               | 114 |  |

|   |                                                           | 5.5.4                                              | Automaton for Managers                                                  | 115 |  |

|   |                                                           | 5.5.5                                              | SDN specification                                                       | 116 |  |

|   |                                                           | 5.5.6                                              | Experimental Results                                                    | 118 |  |

|   | 5.6                                                       | Chapte                                             | er Conclusion                                                           | 123 |  |

| 6 | Disc                                                      | rete Co                                            | ontrol Synthesis for an SDN-IoT platform                                | 125 |  |

|   | 6.1                                                       | Existir                                            | ng Synthesis of Network Services                                        | 126 |  |

|   |                                                           | 6.1.1                                              | Synthesis of Consistence updates                                        | 126 |  |

|   |                                                           | 6.1.2                                              | Guided Network Synthesis                                                | 128 |  |

|   |                                                           | 6.1.3                                              | SMT based Synthesis of SDN                                              | 134 |  |

|   | 6.2                                                       | Synthe                                             | esis Tool                                                               | 134 |  |

| Bibliog    | raphy                                                                      |                                                                | 161 |

|------------|----------------------------------------------------------------------------|----------------------------------------------------------------|-----|

| Conclusion |                                                                            |                                                                | 157 |

| 6.5        | Chapte                                                                     | er Conclusion                                                  | 154 |

|            | 6.4.3                                                                      | Properties that has to be fulfilled by Devices                 | 153 |

|            | 6.4.2                                                                      | Properties that have to be fulfilled by the Manager            | 150 |

|            | 6.4.1                                                                      | Global Properties to be fulfilled by the <i>SDN</i> platform   | 149 |

| 6.4        | Compositional Control Synthesis Framework for the Layered SDN Architecture |                                                                |     |

|            | 6.3.2                                                                      | Abstract Specifications and Model                              | 144 |

|            | 6.3.1                                                                      | An Application Scenario : Edge Computing V2X communications    | 141 |

| 6.3        | Contro                                                                     | ol Synthesis of a typical SDN Application - A Modular Approach | 141 |

## INTRODUCTION

This document is a result of collaborative work between Nokia Bell Labs, Paris-Saclay IoT-Control network team and Inria, Rennes Sumo team within the *ADR Sapiens* project. The main theme of this project is the automation of an Software-Defined Network (*SDN*) based architecture which serves as support for an Internet of Things (*IoT*) platform. This automation could be applied to the creation of the user interfaces to specific user's application in the platform or to the integration of new functionalities into the platform in real-time. In a more generic view, we aim to create high level models for various and useful functionalities, providing the tools and methods to convert the model into low-level machine code and ensuring the consistent integration of functionalities to the existing platform. This document is about the exploration of theoretical and implementable possibilities of the above themes. In particular, we are using automated model checking to verify that the system is working correctly with respect to the various functionalities requirements (process of verification) and providing the working methodology for introducing high level functionalities model and integrating the same to the existing real time platform by means of synthesis controller.

**Readers Digestion:** In this introduction chapter, we will introduce various terminologies related to SDN, model-checking and synthesis without much explanation, definitions or references. We choose to do this way so that it does not complicate the readers and gets involved into the specific details. It will also help to understand the overall contents with little details but the main theme of this thesis. We do this with the consideration of many papers published in the literature of distributed systems, SDN, IoT, model checking and control synthesis. These fields are wide and also have many subtle variations in the definitions, design, procedures and so on. We strongly believe that if one thinks of the interesting subject in a more abstract way will help to bring the core of the problem. The advantage of thinking about the core problem in an abstract way is it allows us to choose the well aligned modeling framework and propose the solution in a simplistic yet the best implementable procedures or designs. This introduction chapter will slowly introduce various concepts of model checking, synthesis, distributed system concepts in this chapter and the following chapters. Please continue to read this chapter with common sense rather than expecting formal definitions for each notion or notation. We will progressively introduce each notion formally and give comprehensive comments with examples in the following chapters.

**Brief introduction about the working teams :** Sumo team is a research team that mainly works

on theoretical studies in the fields of Model-Checking, Synthesis of Discrete Event System, Game Theory, Fault Tolerant and Diagnosis, Markov process/chain etc. Nokia, Paris-Saclay IoT Control network team works on 5G network, *IoT* system, *SDN* etc and concentrate on design, testing and implementation.

## 1.1 Road Map To Thesis

In this ADR project, we were interested in the automated procedure of *Verification* and *Synthesis* of *Distributed Systems*, and we focused on the Software defined networks (*SDN*) application to the Internet of things (*IoT*) platform. *Software Defined Networks* is an example of such a Distributed system. The modeling and technique we used in this document is not particular for *SDN* or *IoT*, it can be used for any generic distributed systems. In the path of our work, we also tackled the *state space explosion*, which appears to be a severe problem in the verification and synthesis process. We provide our contribution from the theoretical side to avoid this *state space explosion* problem. In order to overcome this *state space explosion*, we revisited the composition technique (assume-guarantee technique) and generalized little but enough to use for postponing the state space explosion in the process of *SDN* verification and control synthesis. Based on our knowledge, *State space explosion problem* can't be avoided completely, can only be postponed.

In chapter 2, we will go through the overall working nature of *SDN* system, *IoT* platform and we will also mention short notes about Nokia, Nozay *SDN-IoT* platform design.

In chapter 3, we will give a generic modeling scheme for the distributed system to do verification and discrete control synthesis. Most of them are from literature but some of them are further improved by the author and advisors. Main improvements are in the direction of synthesis of safety *LTL* specifications (temporal properties about the system) for the automaton model of monolithic and distributed systems.

In chapter 4, we will state the important problem of verification and synthesis related to 'State Space Explosion' and we go through some of the techniques from the literature and authors contribution in this aspect to reduce the state space to limit the state space explosion effects on the experimentation of model checking and discrete control synthesis procedure. In the same chapter, we developed compositional control synthesis of *LTL* safety specifications.

In chapter 5, we model the specific Nokia-SDN platform as an automaton and express the system requirements as *LTL* specifications and do the verification experiments using the model checking tool *SPIN*.

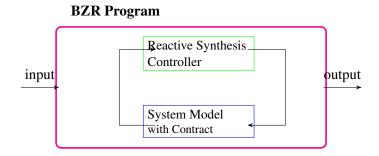

In chapter 6, in the direction of producing the discrete controller for the expressed model and specification of the *SDN-IoT* platform as a demonstration, we state some of the specific functionalities of *SDN-IoT* platform and model them in high level language called *Heptagon* (a reactive modeling of distributed system) and produce the control synthesis using *BZR-ReaX* and translate them into classical high level languages like *C* and *Java* and provide the possibility of

integrating the produced control model with real time systems.

## 1.2 Distributed Systems

A Distributed system [ST16] is a vague and ambiguous keyword used throughout the computer science literature. When we mention distributed system (*DS*), we mostly mean the following :

#### **Distributed systems**

A distributed system is a coordination of multiple autonomous computing elements that appear to its users as a single coherent system. Each autonomous computing element is able to behave independently and can be either hardware devices or software processes. From the application side, these coordination of multiple autonomous elements can be viewed as a single system.

FIGURE 1.1 : A Typical Distributed System (DS) : Image downloaded from https://www.icar.cnr.it/en/sistemi-distribuiti-e-internet-delle-cose/

There are two main characteristics that can be referred to from the above definition.

1 It is a collection of computing elements able to behave independently of each other.

2 It is believed as a single system by the users (being people or applications).

Autonomous computing entities of the distributed system might be either a super computer, a personal computer or smaller computing devices or even a software process. This of course includes server farms, supercomputers, sensor networks, organizational Intranet, and the Internet, but also our laptop in which many components have some independence. In principle, they are acting independently from each other and their aims were to achieve common or separate (individual) goals. *DS* (and also distributed computing) captures a wide variety of situations which includes computers or processes and also serves as a model for numerous phenomena in the natural sciences. Clearly, this is a vast and heterogeneous field. Meanwhile, they are programmed to communicate with each other by exchanging messages to realize specific applications. How to establish this communication channel i.e collaborations between computing processors is at the heart of developing the distributed systems.

In a given DS any two entities communicate via synchronous or asynchronous queues. These synchronous queues are high speed Local-area networks channels which effectively transfer the message instantly to one another which often needs the dedicated connection channel between the pair of computing entities in DS. Where-us the asynchronous queues are not high speed and these queue types are mostly First In First Out (FIFO), so that a single centralized computing entity can serve many user's requests by having a single queue channel which is a cost effective solution in typical network services [ST16]. In theory, communications between any pair of entities in DS will fall into either synchronous or asynchronous. In an asynchronous setting, DS reads messages by some polling mechanism or FIFO manner; it is specific about the architecture and protocol. In synchronous setting, reading and sending a message action based on either shared variables (common memory block access) between the processors or by means of a dedicated synchronous channel (RDV channel). This communication can be assumed reliable (meaning the message sent by some processor never fails to reach the receiver). In case of asynchronous FIFO communication, one can assume the queue length is bounded (in the real system this is the case, but in the theoretical model one typically assumes unbounded queue length). However, When dealing with DS, one can not assume the existence of a global clock in all the entities in the considered distributed system. This leads to the fundamental problem of synchronization and coordination of common actions and progress in the computation process within a distributed system. The information one computing entity expects from another computing entity may be delayed in an unbounded way, so there is no way to guarantee that such a computing entity is simply slow, completely broken, or maliciously refusing to cooperate at this point. Even when all messages from other computing entities eventually arrive, message arrival order may be arbitrary. Note that asynchronous is a real headache: it can arise from computational differences between the computing entities, properties of the underlying communication channel between them or other reasons, and hence must be dealt with care. This issue is so central that even this sub-field of asynchronous distributed systems is large [Lyn96; AW04; Wig17].

When a distributed system is designed with a set of coordinated computing elements that have to meet certain requirements, the goals of a DS we mention here after as either network wide-invariant or specifications in the rest of the document. In fact, it is the designer's responsibility to design the communications interface between each computing element as well as the behavior of each computing element of the DS to meet the required specifications. It is important to ensure the correct behavior of the designed DS to meet required specifications. Since in our Nokia-Inria (ADR) project, we are interested in automating techniques, we are using Verification and Synthesis mechanisms to check and correct the designed DS for the given specifications.

There are some well known reasons in the literature as mentioned in the survey [ST16], why the design of *DS* fails to meet the required specifications, even-though it is designed by experienced designers. To name some of them: assuming that the network communication between the different entities is reliable and secure with respect to a given architecture, i.e the connection of network among the entities is stable with zero latency together with an unbounded bandwidth, then there is only one controller for each autonomous computing entity, and its computing speed are same of the given *DS* components.

## 1.3 Challenges

In the automated verification and control synthesis of DS systems, there are a couple of challenges which depend on the kind of distributed system one is considering, since distributed systems itself is a vast and highly diverse field. One of the main problems of verification and control synthesis of a given distributed system is State Space Explosion, a problem that arises when one tries to trace all possible execution paths of given DS. In our case, a DS contains too many components, and/or the communications between the components of DS are asynchronous i.e communicating via FIFO queues which makes the formal analysis very difficult to complete the process. There are some techniques to avoid this brute force analysis to name few: partial order technique [BK08], assume guarantee technique [HQR98; Sta85], abstraction [Cla+18] of the system in case of verification process. For the synthesis purpose, one can use modular nature of property and the system, a well known technique to reduce state space explosion in the literature [WR88]. We will provide more details of these techniques in the following chapters. Our main contribution to alleviate the state space explosion in this document is the *compositional reasoning* for verification and control synthesis for DS. This compositional reasoning technique is inspired from the rely-guarantee technique introduced by [Sta85]. Apart from this theoretical result, the main works towards the automation apart from the mathematical framework (or definition) involves in this thesis as follows:

1 Properly understanding the design *SDN-IoT* of Nokia, Nozay team, so that it can be formally modeled to proceed with model checking and control synthesis schemes.

- 2 Identifying the set of requirements and expressing them as a specification so that we can test the model with respect to the specification.

- 3 Providing the use case in the direction of proposing the high level model description and producing the control synthesis for the proposed model design automatically and converting them into classical high level language so that one can integrate the produced high level codes with real working *SDN* system.

Digestion of Proposed Automated Procedure: First and foremost import things to stress that what we are doing is automated verification and synthesis, and every automatic scheme where there is a hidden automated procedure. The usefulness of an automatic scheme purely depends on robustness and adaptability of the written automated procedure. If one wants to maintain a distributed system that works without errors, then it will hugely depends on one's knowledge and envision capability about the kind of environment the proposed system or design will going to work and the expected applications from the design and unsafe states can possibly occurs in the proposed design so that one can express and quantify the required properties and check the proposed design with the expressed properties in the model checking process i.e Verification of proposed system model with respect to various expected properties. In case of synthesis, one should check the limitation of control synthesis techniques and the kind of properties control synthesis solution can support to the DS system and making the DS system to work without reaching an error state (unsafe situation) and also in non-blocking way (i.e have to work and provide useful application rather than just avoiding the error states).

# SOFTWARE-DEFINED NETWORKS AND IOT PLATFORMS

Data networks are made up of many routers, data forwarding switches, firewalls and so on. Such communication networks are complex and dynamic in nature i.e the multiple events (like mobility of users, requirement changes, traffic in the routing path) that can occur simultaneously throughout the network. The main objective of the network operators is to control the communication network and respond to a wide range of network events such as intrusions, loss of traffic in the data path and so on. The difficulties in operating the networks lies in its scale (number of users, number of network nodes). In traditional *IP* networks (both wired and wireless), the network controller and the network fabric are tightly coupled within a network node. Such a network node architecture is quite effective in terms of network performance but the outcome is a complex and *relatively static* overall architecture [Kre+15].

Such a tightly bundled control and data plane collocated within the network node often makes it difficult to operate (e.g. upgrade) the network and generate high operational cost as one has to perform the same operation on all nodes associated with the control plane. Adding a new application to such a static architecture is not to be a cost effective one, since it often requires the reconfiguration of the control plane on all the network nodes spread across the network topology. The operational cost of maintaining a network infrastructure is significant to the expenditure capabilities of network service providers, which does not provide more space for innovation.

Thus, it is preferable to have stable network fabrics and data plane, but a dynamic programmable control plane with an abstraction level to serve various applications. In such a case, an architecture that makes most sense could consist in network controllers that program the network fabrics based on network manager instructions e.g. automated system to implement the network dynamic policies. Within this architecture, the network manager plays the role of the abstraction level which interfaces with various applications and which translates high-level policies received from the latter into low-level network policies. This is part of the *Software-Defined Network* (abbreviated as *SDN*) framework.

Within such a framework, one can centralize the control software (e.g. within a data center) for ease of upgrade/update and make the network node a white box. As a result, a simple white box network node can be bought from any vendor (i.e. off the shelf) with simple data

plane functionalities that leads to a reduction in network node complexity and thus network operational cost. The programmability and the flexibility of the network relies on the control plane software which communicates with network nodes in a much standardized way via open application program interfaces (*API*).

Additionally, the advent of *IoT* technology and its applications impose important new constraints on the communication network. Indeed, the latter network also has to handle the scale related to a huge number of *IoT* devices. Roughly we have more than 15 billion *IoT* devices (like various sensors signaling, GPS system of cars, smart phones and their application, RFID, Google glass, smart home, and so on) connected to the *internet* and this number is expected to grow exponentially with more and more interactions between devices due to smart applications brought by the *IoT* technologies and platforms.

For both fixed and wireless communication networks, which have to effectively support the 'Internet of Things' (*IoT* will be introduced later in this chapter), they are expected to support a wide range of applications coming from autonomous communication among sensors and actuators as well as the interactions between users (humans) and machines, like smart cities, intelligent mobility, industry automation just to name a few. It is clear that modern networks have to face human-type and machine-type interactions. Heterogeneous characteristics of the applications (sensors, actuators, control entities) together with a large range of qualities of service are part of the set of requirements. There should be enough flexibility in the network to deal with such heterogeneous applications. In contrast with hardware-based deployments of previous generations, the design of new communication networks took the advantage of *softwarization* and *virtualization*.

*Softwarization* is a paradigm which runs, defines and dynamically updates the functionalities via software rather than via pre-programmed hardware. It guarantees a high degree of flexibility and reconfigurability by solely updating software code rather than adding or removing the existing hardware from the service. This leads to a cost effective solution.

Virtualization is a concept of creating abstract entities for the hardware platforms, operating systems, storage devices and data network resources that exploit the low cost virtual machines instead of dedicated hardware for various intended network applications. Virtualization offers different applications and services that share a pool of configurable resources in a cloud environment. A cloud environment provides the processing, storage, and networks resources to the users. The network users can deploy their applications in this cloud environment and use the underlying cloud infrastructure and services. It is noted that virtualization is an enabler for softwarization.

From the network point of view, *Software-Defined Network* is considered as a main realization of *softwarization* concept [LKR14]. Another key concept in recent network architecture is the *Network Function or NF* [LKR14],[Kre+15]. The latter is defined as "a functional block within a network infrastructure with well-defined interfaces and well-defined behavior". The

NF can be physical (i.e. implemented by hardware) or virtual (i.e. software-based). The latter could be placed and migrated across physical network infrastructure according to the needs of network operator and traffic management, providing room for making the independence of network functions from hardware i.e. a Virtual Network Function (VNF) can be decoupled from hardware and placed in different hardware locations to maintain the services without interruption. This is called the Network Function Virtualization (NFV) paradigm. Together with the NFV framework, the SDN framework allows to partition the operator network infrastructure into isolated logical networks of varying sizes and structures with each of them dedicated to a different type of services. This allows for multiple usages and tenants sharing the same operator network infrastructure lead to network cost optimization.

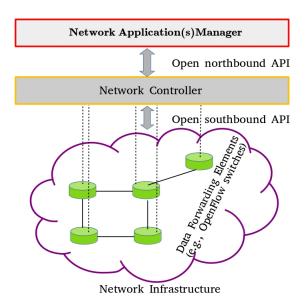

#### 2.1 Introduction to SDN

Software-Defined Network [Kre+15] is an emerging network architecture that decouples network control function from network forwarding functions, enabling the network control to become directly programmable. In such a case, the underlying network infrastructure has to be abstracted for applications and network services.

SDN and NFV are complementary in the softwarization of the network. While the former decouples the network control functions from the network forwarding functions, the latter aims essentially at decoupling any network function from the hardware on which it runs. Both facilitate the network design and help the infrastructure to be virtualized and abstracted with different software building blocks. SDN uses NFV infrastructure (e.g. virtual machines) to run the network control functions so that the latter can easily be deployed on different network infrastructures. The aforementioned list of virtualization functions are intensively deployed on an NFV infrastructure as SDN network controller functions to set the data forwarding rules on the network nodes (both physical and virtual switches or routers).

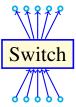

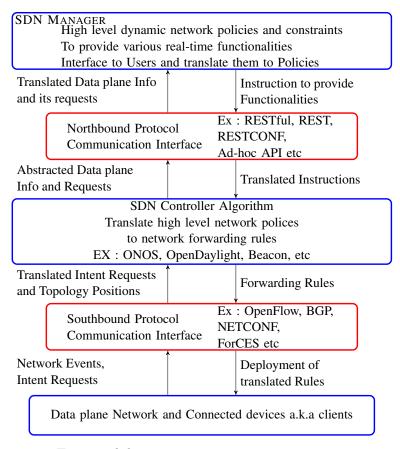

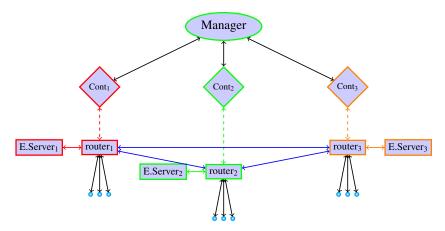

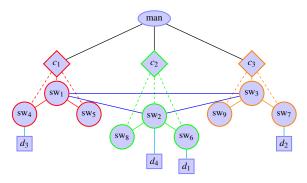

*SDN* architecture consists generally of three building blocks : network managers (or management plane), network controllers (or control plane) and data forwarding elements (or data plane) as depicted in Figure 2.1.

**Data Plane : Network Elements [Kre+15]** A data plane or data forwarding plane contains a set of network elements that receives data packets on its (communication) ports and performs few simple network operations on them. For example, the network device may forward a received packet, drop it, alter the packet header (source, destination information about junk of data piece), and so on (refer the figures 2.1, 2.2). The network elements are, for example, routers which operate generally at the *Internet Protocol* i.e *IP* layer. Additional examples include network elements that may operate at a layer above *IP* such as firewalls, load balancers, and video transcoders or below *IP* such as Layer 2 switches and optical or microwave network elements.

FIGURE 2.1 : SDN infrastructure with layered connections

Network elements can be implemented in hardware or software and can be either physical or virtual.

FIGURE 2.2 : Simple Network Switch

|                   | Packet_header,In port  | Action                  |

|-------------------|------------------------|-------------------------|

| rule <sub>1</sub> | 10***, pt <sub>1</sub> | pt <sub>3</sub> forward |

| rule <sub>2</sub> | 111**, pt <sub>3</sub> | drop                    |

| rule <sub>3</sub> | 101**, pt <sub>2</sub> | modify.packet.header    |

|                   | •                      |                         |

|                   | •                      |                         |

| rule <sub>k</sub> | 01***, pt <sub>4</sub> | ask controller          |

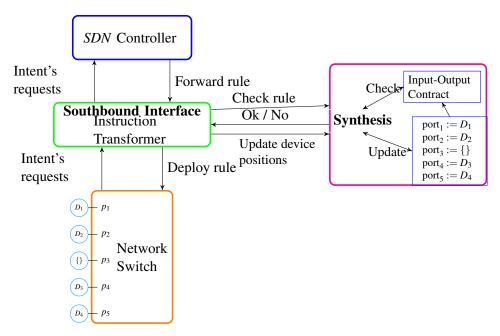

TABLE 2.1 : Forward table of switch S

Control Plane [Kre+15] The control plane is a logical decision implementer of *SDN* network manager instruction to the data plane. The control plane, usually a set of control entities, is responsible for the configuration of forwarding elements in the data plane by communicating via the (Control-plane) South bound Interface (*SI*) protocol[Kre+15]. The control plane is responsible for instructing data plane elements about how to handle network (data) packets. A control plane entity, called as *SDN controller*, translates a new request from the application into a sequence of instructions that will implement new forwarding rules on network devices via Southbound interfaces [Kre+15] (an *API*'s refer the figure 2.3). Communication between control-plane entities (i.e between *SDN controllers*), referred as "east-west" interface, is usually implemented through gateway protocols such as Border Gateway Protocol (*BGP*) or protocols such as Path Computation Element (*PCE*) [Kre+15] and so on. These corresponding protocol messages are usually exchanged in-band and subsequently redirected by the forwarding plane

to the control plane for further processing. Control plane functionalities usually include: topology discovery (i.e data plane and various network users/clients), data packet route selection, path fail-over mechanisms in case of dynamic change of physical network or change in traffic. Control plane southbound interface SI is usually defined with following characteristics: time-critical interface that requires low latency with higher bandwidth in order to perform many operations in a short-time period, oriented towards wire efficiency (efficient machine readable and function activation code) and device representation instead of human readability. Examples include fast- and high-frequency of flow table updates, and robustness for packet handling and events. Control plane SI can be implemented using a protocol, an API, or even inter-process communication. If the control plane and the network device are not collocated, then this interface is certainly a protocol. Examples of control plane SI are the ForCES and the OpenFlow protocols. Control-plane service examples include a virtual private LAN (local area network) service, service tunnels, topology services, etc. The control plane also has a North Bound Interface NI via which it communicates the system state, the quality of network services and high level information about the data plane to the management plane.

The *SDN* controller algorithms are designed to catch up and implement various instructions from the *SDN* manager. Some of the main activities of an *SDN* controller are listed below:

- 1 Shortest Path Forwarding rule: to set the communication path between various users in the data plane by constantly monitoring the traffic scenario and the data plane network switches availability,

- 2 Security Mechanisms: set the routing data packet rule such that it avoids from reaching the data to malicious users.

- 3 Monitoring the data plane topology and users positions in the data plane,

- 4 Process the data plane events, intent requests and inform the same to manager,

- 5 and so on.

Management Plane [Kre+15] The management plane is a logical decision maker and decides the functionalities of *SDN* usage which aims to introduce constraints to the network functions and ensures that the network as a whole runs optimally by communicating with the network controllers using a Management-Plane Northbound Interface. Management-plane functionalities are typically initiated, based on an overall network view, and traditionally have been human-centric. However, artificial intelligence algorithms are lately replacing several human interventions. Management plane functionalities include fault monitoring, configurations of the data plane users and services availability in addition. Its functionalities may also include entities such as orchestrators, Virtual Network Function Managers and so on.

The typical management plane roles are listed below, but it may vary depending on the applications

- 1 Classify user-defined policies,

- 2 translate the above policies to network policies,

- 3 provide to the users various network virtualization functions which could change dynamically according to the requirements or based on requests from these users,

- 4 and many more depending on the applications.

Communications between and within SDN layers [Kre+15] In the set up of well separated layers as in SDN architecture, there should be a clear communication protocol defined between each pair of layers and one defined between entities within each layer. For each of these protocol frameworks, data and information models should be specified. In the literature there are various protocols that are defined to build the communication links between and within SDN layers - i.e. northbound, southbound, east-and-westbound interface protocols are available. For Northbound API's (i.e. communication between the control plane and the management plane) we have adhoc API's, RESTful API's, etc. For Southbound API's (i.e. communication between the control plane and the data plane) we have OpenFlow, ForCES and OVSDB, just to name a few. The East-and-Westbound (essentially between controllers when we have distributed controllers compared to centralized controllers) communication API's totally depends on the kind of controllers, the details of the data abstraction used in those controllers for communication. Just to name a few examples of SDN controllers: Onix, Beacon, Floodlight, OpenDaylight, ONOS and etc. The fig. 2.3 explains the overall working nature of various SDN entities and interfaces.

That's the end of *SDN* introductory notes, now we move on to the introduction about *IoT* devices and its applications.

## 2.2 *IoT* Devices and Related Applications

Thing in the Internet of things or IoT devices that can communicate via a communication network. IoT is the set of physical objects like sensors, actuators, vending machine, automatic teller machine (ATM), etc (mentioned as things) can be primarily characterized as embedded system (smart electronic devices) that are used for the purpose of connecting and exchanging data with other (IoT) devices and systems via Internet (or local network services) or mobile networks. IoT has evolved a lot thanks to the help of the evolution of Internet (including wireless technologies) like LAN, sub-net, Ad-hoc network and mobile networks.

FIGURE 2.3: SDN Entities and its Working Nature

Traditional *IoT* devices are embedded systems, wireless sensors, control systems, automation systems (home, building, car, ship, airplane, industrial automation, and so on), and others, all contribute to enable the 'Internet of things'. *IoT* technologies are sets of products pertaining to the concept of *smart devices*, including devices and appliances (such as lighting fixtures, thermostats, home security systems and cameras, and other home appliances) of a common platform, and can be controlled via devices associated with that platform, such as smartphones and smart speakers. The concept of first smart devices emerged from Carnegie Mellon university where computer science network geeks played around the coca-cola vending machine to monitor from a remote server the current availability of coke canes and its temperature by accessing sensors installed on the machine. These traditional embedded systems devices used to be high energy consuming entities due to direct point-to-point connections (i.e. long range wireless communication). With the ubiquity of the internet nowadays, one can go for low-energy consuming and short-range wireless communication devices. This is one of the benefits of modern network to *IoT* applications.

As by the European Telecommunications Standards Institute (*ETSI*) the *IoT* applications are projected for smart devices, smart cities, smart grids, the connected car, eHealth, home automation and energy management, public safety and remote industrial process control. Apart from the wide applications of *IoT*, it is important to emphasize the fact that *IoT* devices are

highly heterogeneous and not a unique type of electronic devices. They vary depending on the type of hardware they are using (Micro-controller, micro-processes), computing power, energy consumption, action-behavior response with respect to environment (in case of actuators), the data handling devices and so on. In such heterogeneous types of *IoT* devices, it is important to coordinate them to make an application secure and safe. In the sense that actuating a wrong actuator or providing open access to sensitive data handling devices can cause severe damage either physically or economically, also brings privacy related issues. These are the challenges faced (or has to) by the *IoT* applications developer for coordinating such heterogeneous devices using global controlled software in a common platform.

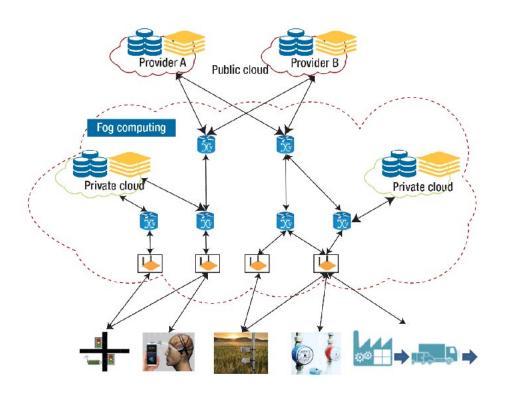

## 2.3 Orchestration of *IoT* Platform using *SDN* Concept

In the modern 'communication network' era, the communication network is highly connected. It provides global network control framework for discovering, deploying various IoT devices, applications and its interactions with humans. In such a scenario it needs smart control, actuation and automation to manage the global network control mechanism. The main challenges of global network control mechanisms is the realization of *IoT* applications which involve the interoperability among various *IoT* entities. The fact of applying *SDN* (layered network) concept to coordination (orchestration) of *IoT* devices is not new, for example the paper [Sar+14] gave brief summary about realization of *IoT* application using *SDN* framework. The reason for using such layered network architecture is mainly for quick response to the dynamic network instances using data abstraction from bottom to top layer of SDN network. SDN inter-operable architecture for IoT, is assumed to overcome most of the obstacles in the process of large scale expansion of IoT. It specifically addresses heterogeneity of IoT devices, and enables seamless addition of new devices across applications. Large number (approx. a billion) of IoT devices are going to be connected with *Internet* within a few years, which will generate enormous amounts of data and exchanges of those data among IoT devices and various applications. Using a global centralized (or co-ordinated) SDN controller paves the way to minimize the delay and load balancing in *IoT* applications network.

In a complex highly connected network operation, knowing the fine details of the network and connected devices is very difficult especially as a network user. Maybe an expert level or an experienced network user can manage the network integration but as a layman it's not as trivial. As a result, most end-users do not share their connected devices and do not benefit from *IoT* services which could result from rich associations. To benefit from some popular services, most end-users purchase connected devices for their application without being aware of all the services they could benefit from, provided their *IoT* services are associated with devices belonging to other smart environments. This situation is explained by considering human skills required to face complexity in terms of [Sar+14]:

- Awareness of *IoT* services and ability to select suitable connected objects.

- Ability to deploy and configure all functions to make expected services work. This particularly involves the configuration of the network layer to support *IoT* services involving different physical functions spanning multiple smart environments.

The scope of SDN to coordinate IoT devices can be illustrated with the following three key concepts,

- 1 Discovery and positioning the *IoT* resources:

SDN working nature naturally provides the functionalities of discovering various *IoT* devices and its current position in the given application network. It keeps track of the real time position of various *IoT* devices and its operation conditions and modes.

- 2 Allocation of *IoT* resources in an *IoT* services:

Based on the tracking of *IoT* positions, operational modes and requirements, it provides the external resources to those devices like allocating the virtual hardware to support the computation required by the *IoT* devices.

- 3 Dynamic grouping of *IoT* devices:

This is one major advantage of providing dynamic grouping of various *IoT* devices in the required applications, which make use of the resources efficiently to serve various functionalities in real time.

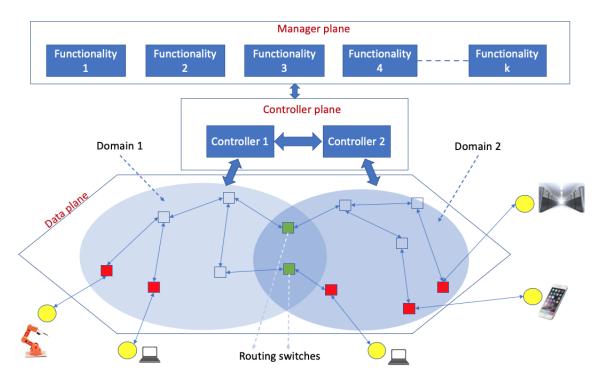

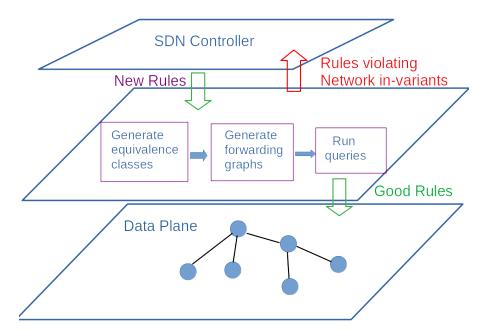

**EXAMPLE 2.1** Typical SDN architecture to orchestrate the IoT applications is depicted in figure 2.4. The data plane represents the layer holding the Open Flow Virtual switches, the clients acting as traffic sources and sinks. The clients can be a server, laptop, personal computer or any IoT devices (sensors, actuators etc.). The network applications manager hosts the number of IoT policies and communicates with the SDN control plane through open northbound Application Programming Interface. Interface regarding the status of the network and its particular requirements. The controllers, situated in the control plane, dictate forwarding rules to the data forwarding devices through open southbound API.

The typical functionalities in the manager plane layer (or application layer) will be network control access, resource scheduler, establishing safe and secure data path between various authenticated devices. Maintaining abstract level information about IoT devices involved in various applications. Further this abstract information can be about the performance of those devices or status about its working nature, etc.

The next section explains a particular *SDN-IoT* platform developed by Nokia, France 5G network team.

FIGURE 2.4: Example of SDN architecture orchestrating the IoT applications

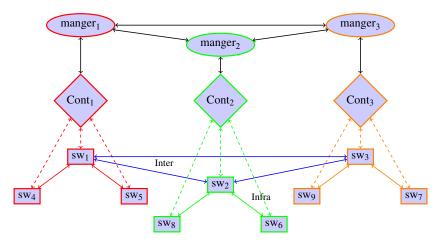

#### 2.4 Nokia SDN-IoT Platform

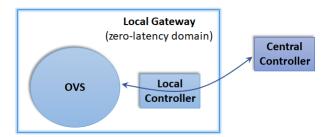

Here, we will describe the general principle behind the Nokia *SDN* architecture. We will give a very narrow and general intention of *SDN-IoT* platform constructed by the Nokia Bell Labs team. For our modelization, verification and synthesis scheme, we only focus on a specific part of Nokia *SDN-IoT* platform; more details will be given in the respective forthcoming chapters.

Before going into the further details of Nokia *SDN* design, we will recall here three characteristics of distributed systems that are universally desirable that we call *CAP* theorem.

- 1 *Consistency* (information should be consistent throughout the network), in the sense that system should responds *identically* no matter which node (i.e in our case decentralized *SDN* controllers and manager) receives the request from the data plane.

- 2 *Availability* (response to the requests) means that system (in our case *SDN* controller and manager) should responds to a query (in our case intend requests although the response may not be consistent or correct)

- 3 *Partition Tolerance* in case of communication failure of any one of the node (either switch, controller or manager) system should continue to function. Although this specific partition tolerance is not considered or analyzed in detail in the forthcoming chapters. Nonetheless, it is an important criteria to consider in the distributed environments.

In the distributed community [GL02], it was identified only any two of above three characteristics can be full-filled at any given time but not all three. It was first conjectured by Eric Brewer

later proved by Gilbert and Lynch. It is also important to note that the CAP theorem not only applies to asynchronous but also synchronous distributed systems.

Network switches, *SDN* controllers and managers all are computational entities. In case of a switch - slave computation entity which receives and forward the data packets, and receives and sends the intent request to update the forward rule table. Controller receives and processes the data plane requests and follows the instruction from the manager plane to satisfy various specifications. Whereas the manager observes the abstract information about the data plane and its requests also for the needs of application, it dynamically changes the network policies. *CAP* theorem naturally applies to the working nature of *SDN*.

In the context of the CAP theorem, if one considers partition tolerance of paramount importance, traditional control-plane operations are usually local and fast (available, and it goes to inconsistent state for a shorted period of time once in a while), while management-plane operations are usually centralized (consistent) and may be slow (can't available all the time so naturally slow in response to the requests). In this theoretical limitations, when we build such complex distributed system, it is important to analyze the *safety-critical* specifications (this is one of the reason *ADR sapiens* (who is funding my Phd thesis) project choose to do model checking of Nokia *SDN-IoT* platform) (properties or requirements) with respect to *CAP*'s *availability*, *consistency* and *partition tolerance*.

## 2.4.1 General Problem and Assumptions

Smart devices are simply connected logical objects interconnected with other logical objects via the service links provided by the network operators through network routers or switches. The connected entities are objects that can produce, receive, forward or process data. These connected objects can be a physical object, an application, a piece of software, etc. Such a collection of smart devices communicating with each via an established network are referred as IoT application. In the presence of a large number of heterogeneous smart devices to make an IoT application works for various requirements either Industrial automation or smart home appliance or some other applications which involves controlling the blend of virtual and physical systems together. Manually, managing such a complex system because of the sheer number and heterogeneous device types involved in the applications. In such a complex enterprise application, SDN-IoT platform facilitates heterogeneous behavior of IoT devices with a unified way of data communication protocol. They can advantageously be used in smart and complex applications scenarios to group similar devices while enforcing safe and secure IoT applications. Apart from the heterogeneous nature of *IoT* devices, the proposed *SDN* solution should be able to handle the sheer number of *IoT* devices involved in the application. That is *SDN* solution should be well scaled to handle latency problem, quick action responses to the *IoT* applications. In order to scale down the problem of controlling the bigger network and variety and too many

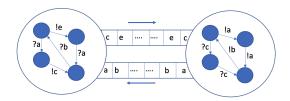

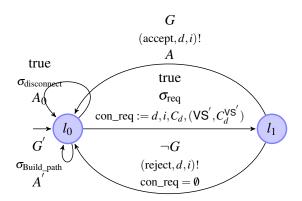

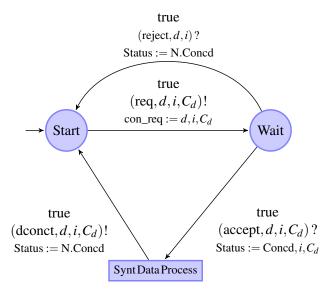

numbers of *IoT* devices involved in the application, two major concepts were introduced to control. These concepts are *Virtual Places* and *Virtual Spaces*.