# Design and implementation of high efficiency power amplifiers for 5G Applications

Joe Bachi

#### ▶ To cite this version:

Joe Bachi. Design and implementation of high efficiency power amplifiers for 5G Applications. Micro and nanotechnologies/Microelectronics. Institut Polytechnique de Paris, 2022. English. NNT: 2022IPPAT039. tel-03911284

### HAL Id: tel-03911284 https://theses.hal.science/tel-03911284

Submitted on 22 Dec 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Design and Implementation of **High Efficiency Power Amplifiers** for 5G Applications

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à Télécom Paris

École doctorale n°626 École Doctorale de l'Institut Polytechnique de Paris (ED IPP) Spécialité de doctorat : Electronique et Optoélectronique

Thèse présentée et soutenue à Palaiseau, le 28/11/2022, par

Joe BACHI

#### Composition du Jury:

Sylvain BOURDEL

Professeur, Grenoble INP Président

Nathalie DELTIMPLE

Professeure, Bordeaux INP Rapporteur

Alain PEDEN

Professeur, IMT Atlantique Rapporteur

Jean-Christophe COUSIN

Maître de Conférences. Télécom Paris Examinateur

Patricia DESGREYS

Professeure, Télécom Paris Directrice de thèse

Alexandre GIRY

Docteur, CEA-LETI Co-Encadrant

Ayssar SERHAN

Docteur, CEA-LETI Invité

Dang-Kièn Germain PHAM

Maître de Conférences, Télécom Paris Invité

### Acknowledgments

fter four years of hard work, I am happy to have produced this manuscript. This however would not have been possible without the support, guidance, and assistance that were provided to me by a lot of different people both in professional and personal circles. It really does take a village!

First and foremost, I would like to thank my advisors starting with my thesis director Pr. Patricia Desgreys whose comments and insight proved invaluable to producing a scientific document of this scale. I am also grateful to my advisor Dr. Alexandre Giry for always encouraging me to aim higher and believing in my potential. A special thanks to Dr. Germain Pham whose methodical and rigorous scientific approach was only surpassed by his caring and aimable nature. Finally, words fail to do justice to the recognition deserved by Dr. Ayssar Serhan who never skipped an opportunity to provide his full support and commitment to this project.

I would also like to thank Pr. Sylvain Bourdel, Pr. Nathalie Deltimple, Pr. Alain Peden, and Dr. Jean-Christophe Cousin for accepting to be part of the jury and taking the time to review my work.

Thank you to the members of the LAIR laboratory at CEA-Leti for making me feel welcomed during my three-year stay, with a special mention to Dr. Dominique Morche who was always available to help out the PhD students. I am especially grateful to the members of the PA/FEM team Dr. Pascal Reynier and M. Damien Parat for their continuous support and assistance.

During this PhD, I was able to meet other aspiring PhD students, interns, and researchers, who became some of my closest friends. Etienne, Mathilde, Abdess, Saad, Jorge, Ghita, Naci, Aicha, Lucien, Nouheila, Léa, and Mohammed, thank you all for your friendship, support, and all the fun activities, coffee, and drinks, I wish you all good luck on your respective journeys.

None of this would have been possible without the love, support, and sage advice of parents, Emile and Najah, and my amazing sisters Jessy and Christelle. I am blessed to have had you all by my side.

Last but certainly not least, I would like to thank my best friend, fiancé, and future wife, Julia for being my constant support system and helping me get through the low phases.

# **Table of Contents**

| Ackn   | owledg                          | ments                                                                                                                                            | i              |

|--------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Table  | e of Cor                        | ntents                                                                                                                                           | ii             |

| List o | of Figur                        | res                                                                                                                                              | v              |

| List o | of Table                        | es                                                                                                                                               | xii            |

| Gloss  | sary of A                       | Abbreviations                                                                                                                                    | xiii           |

| Chap   | ter 1.                          | Introduction                                                                                                                                     | 1              |

| 1      | Evo                             | lution of Mobile Communication Standards                                                                                                         | 3              |

| 2      | 5G S                            | System Specifications                                                                                                                            | 4              |

| 3      | RF I                            | Front-End Architectures                                                                                                                          | 6              |

| 4      | Thes                            | sis Objectives                                                                                                                                   | 8              |

| Chap   | ter 2.                          | Power Amplifier Basics                                                                                                                           |                |

| 1      | RF I                            | Power Amplifiers                                                                                                                                 |                |

|        | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Output Power Efficiency Gain Linearity Bandwidth                                                                                                 | 13<br>14<br>14 |

| 2      | PA (                            | Operation                                                                                                                                        | 18             |

|        | 2.1<br>2.2<br>2.3               | Linear Class PAs  Class-E PA  Back-Off Operation                                                                                                 | 24             |

| 3      | Load                            | d Modulated PA Architectures                                                                                                                     | 30             |

|        | 3.1<br>3.2                      | Outphasing PA Architecture                                                                                                                       |                |

| 4      | Con                             | clusion                                                                                                                                          | 39             |

| Chap   | ter 3.                          | Load Modulated Power Amplifier Combiner Design                                                                                                   | 41             |

| 1      | Outp                            | phasing PA Combiners                                                                                                                             | 43             |

|        | 1.1<br>1.2<br>1.3<br>1.4        | Reactive Compensation  Delay-Line Compensation  Driving Mode  Outphasing Combiner Analysis  1.4.1 Unified Outphasing Combiner Design Methodology | 47<br>48<br>49 |

| 2      | Doh                             | erty PA Combiners                                                                                                                                | 57             |

|        | 2.1                             | DPA Combiner Analysis                                                                                                                            |                |

| 3      | Con                             | clucion                                                                                                                                          | 66             |

| Chap | ter 4.   | SOI-CMOS Class-E Doherty PA                 | 67  |

|------|----------|---------------------------------------------|-----|

| 1    | Doh      | erty PA Design                              | 69  |

|      | 1.1      | Power Stage Design                          | 70  |

|      |          | 1.1.1 Impedance Matching                    |     |

|      |          | 1.1.2 PA Stability                          | 74  |

|      | 1.2      | Driver Stage Design                         |     |

|      | 1.3      | Inter-Stage Matching Network Design         |     |

|      | 1.4      | Two-Stage DPA Line-Up and Simulation        |     |

| 2    | Integ    | gration Technology                          | 83  |

|      | 2.1      | SOI-CMOS Technology                         | 83  |

|      |          | 2.1.1 Inductors                             |     |

|      |          | 2.1.2 Capacitors                            |     |

|      |          | 2.1.3 Power Device                          |     |

|      | 2.2      | Package Substrate Technology                |     |

|      | 2.3      | PCB Technology                              |     |

| 3    | Circ     | uit Implementation and Measurement          |     |

|      | 3.1      | Layout                                      |     |

|      | 3.2      | Validation                                  |     |

|      | 3.3      | CW and LTE Performance                      |     |

| 4    | Con      | clusion                                     |     |

| Chap | ter 5.   | Towards an Outphasing PA Transmitter System | 101 |

| 1    | Outp     | phasing PA Design                           | 103 |

|      | 1.1      | Class-B OPA                                 | 103 |

|      |          | 1.1.1 Outphasing Angle Boundary Condition   | 104 |

|      | 1.2      | Class-E OPA                                 | 106 |

|      |          | 1.2.1 Offset Transmission Lines             |     |

|      |          | 1.2.2 Load-Pull Contours Rotation           | 108 |

| 2    | DPE      | O System Level Analysis                     | 112 |

|      | 2.1      | Look-Up Table Approach                      | 112 |

|      | 2.2      | Modelling-Based Approaches                  | 114 |

|      |          | 2.2.1 In-SCS DPD Architecture               | 115 |

| 3    | PA I     | Modelling                                   | 117 |

| 4    | Con      | clusion                                     | 119 |

| Conc | lusion d | & Future Work                               | 121 |

|      |          | cations                                     |     |

|      | ences    |                                             | 124 |

| List of | Append    | ices                                                     | 131 |

|---------|-----------|----------------------------------------------------------|-----|

| Appen   | dix A.    | Active Device Modelling                                  | 132 |

| Appen   | dix B.    | Two-Port Networks                                        | 134 |

| B.1.    | Transm    | nission Lines                                            | 135 |

|         | B.1.1.    | Quarter-Wave Transmission Line                           | 135 |

|         | B.1.2.    | Half-Wave Transmission Line                              |     |

|         | B.1.3.    | Cascading Transmission Lines                             | 136 |

|         | B.1.4.    | Lumped Element Equivalent Model                          | 137 |

|         | B.1.5.    | Differential to Single-Ended Transformation              | 137 |

| B.2.    | Dual N    | etworks                                                  | 138 |

|         | B.2.1.    | Note on the direction of active sources in dual networks | 139 |

| Appen   | dix C.    | Complex Load OPA Combiner Design                         | 140 |

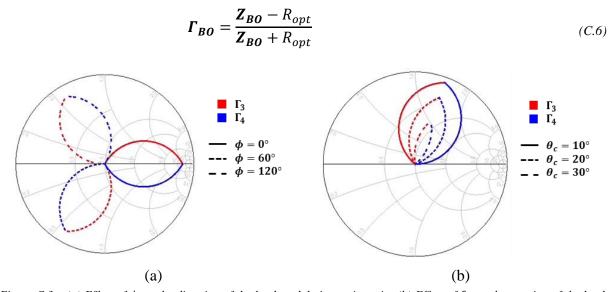

| C.1.    | OTL-B     | ased OEPA Design                                         | 140 |

| C.2.    | Genera    | lized Solution                                           | 144 |

| Résum   | é de la T | 'hèse                                                    | 147 |

# **List of Figures**

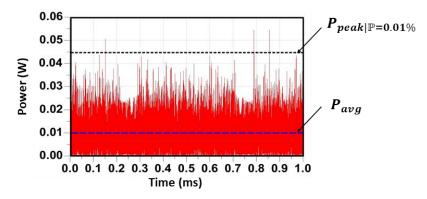

| Figure 1.1 – Power envelope snippet in the time domain showing the peak and average power levels5                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

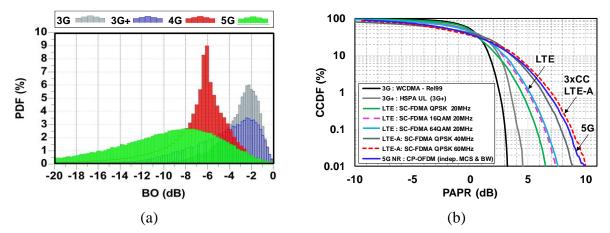

| Figure 1.2 – (a) Simulated PDF of different mobile communication standards. (b) CCDF of different carrier waveforms plotted against PAPR [9].                                                                                                                |

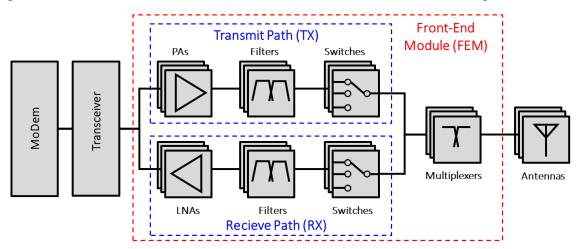

| Figure 1.3 – Simplified RF FEM block diagram6                                                                                                                                                                                                                |

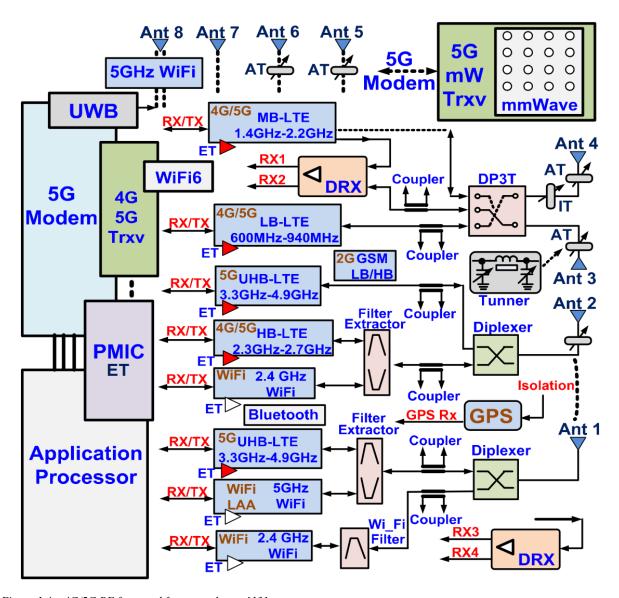

| Figure 1.4 – 4G/5G RF front-end for smartphones [13]                                                                                                                                                                                                         |

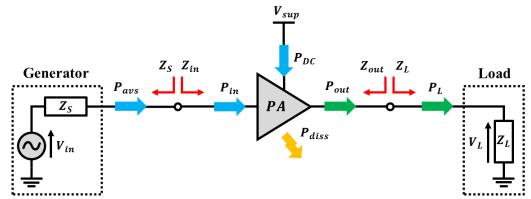

| Figure 2.1 – Generic power amplifier schematic with power and impedance representation 13                                                                                                                                                                    |

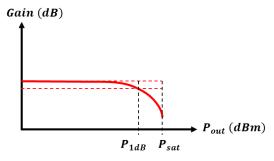

| Figure 2.2 – Gain compression showing the 1dB power level and the saturation power 14                                                                                                                                                                        |

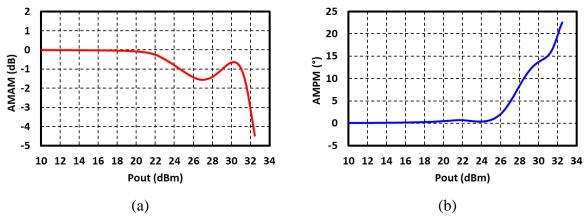

| Figure 2.3 – Example of a simulated PA's (a) AMAM and (b) AMPM response with respect to output power                                                                                                                                                         |

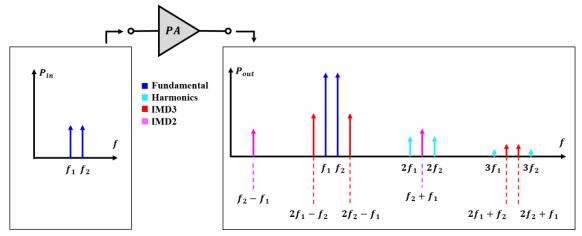

| Figure 2.4 – Two-tone PA test showing power spectrum of the input signal and output signal with the fundamental, harmonics, third order (IMD3) and second order (IMD2) intermodulation components                                                            |

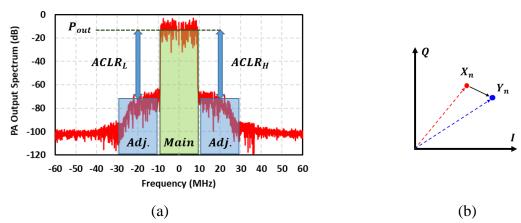

| Figure 2.5 – (a) PA output spectrum showing Main channel and high, low adjacent channels, (b) IQ plot showing original and emitted symbols with error vector16                                                                                               |

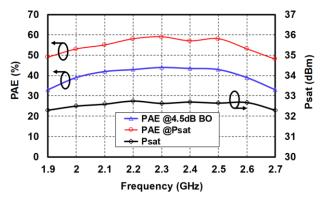

| Figure 2.6 – Measured PAE and Psat over frequency [14].                                                                                                                                                                                                      |

| Figure 2.7 – Generic power amplifier schematic                                                                                                                                                                                                               |

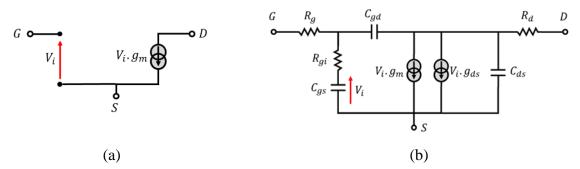

| Figure 2.8 – (a) DC sweep transistor schematic. (b) Normalized Id-Vg characteristic representing drain current vs gate voltage. (c) Normalized Id-Vd characteristic representing drain current vs drain voltage for different gate voltages with knee region |

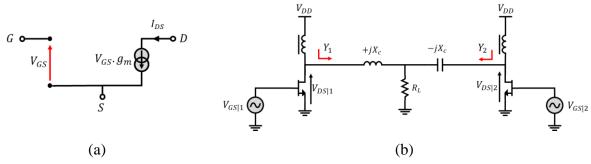

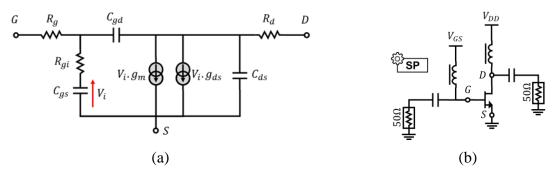

| Figure 2.9 – (a) Ideal large-signal transistor model (b) Large-signal transistor model with linear parasitic elements                                                                                                                                        |

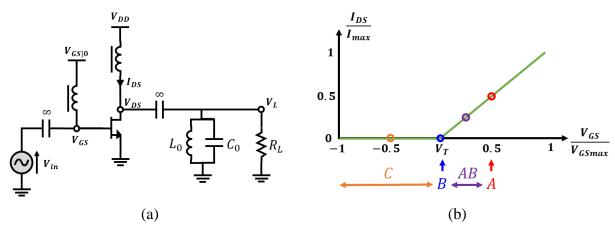

| Figure 2.10 – (a) Linear-class PA schematic. (b) Transistor characteristic with the bias voltage point for different classes                                                                                                                                 |

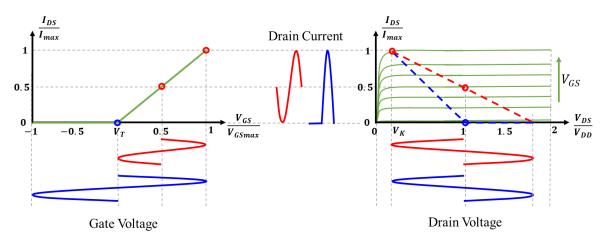

| Figure $2.11 - \text{Examples of Class-A (red)}$ and Class-B (blue). $VT = 0$ for simplicity20                                                                                                                                                               |

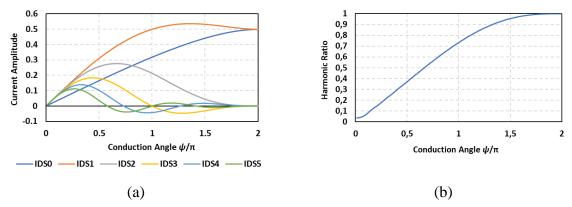

| Figure 2.12 – Drain current (a) harmonics amplitude and (b) harmonic ratio for different conduction angle values                                                                                                                                             |

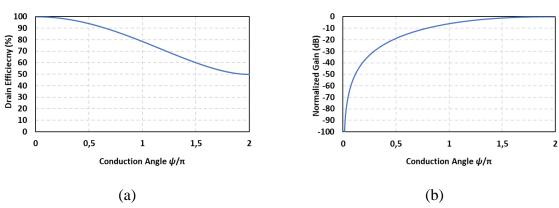

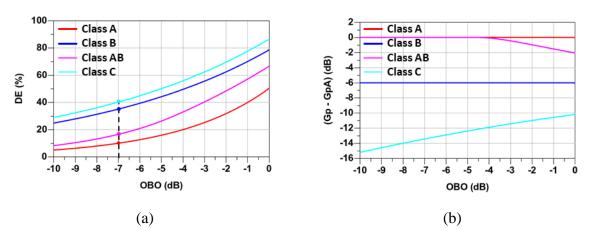

| Figure 2.13 – (a)PA drain efficiency and (b) power gain for different conduction angles 23                                                                                                                                                                   |

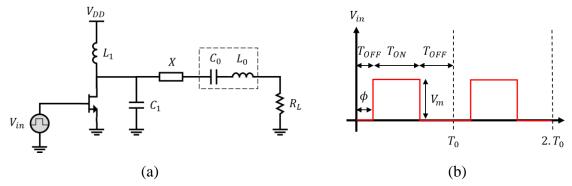

| Figure 2.14 – (a) Ideal class-E PA with shunt capacitance. (b) Square-wave input voltage V <sub>in</sub> .                                                                                                                                                   |

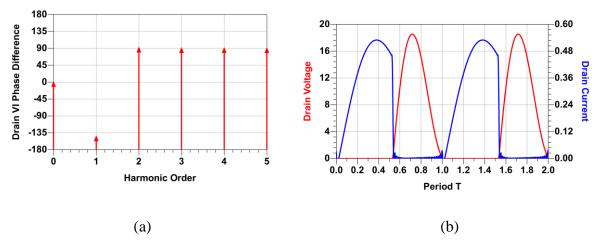

| Figure 2.15 – (a) Drain Voltage-Current phase difference at different harmonics (b) Drain voltage and current time domain waveforms                                                                                                                          |

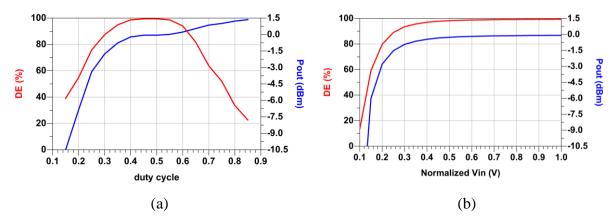

| Figure 2.16 – (a) Class-E PA drain efficiency and output power as a function of duty cycle (b) Single-tone sinewave driven Class-E PA drain efficiency and output power as a function of input voltage amplitude.                                            |

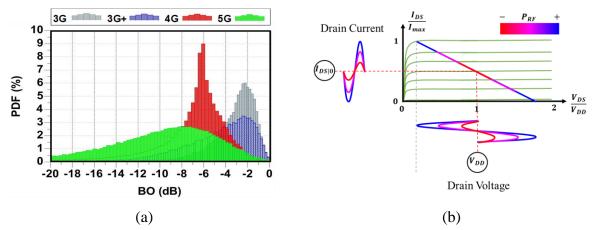

| Figure 2.17 – (a)Probability distribution functions of different communication standards versus back-off power level. (b)Class-A PA load-line for different RF power levels showing drain voltage and current waveforms.                                     |

| Figure 2.18 – (a) PA drain efficiency and (b) power gain versus normalized output power for class-A, class-AB, and class-B PA simulations                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

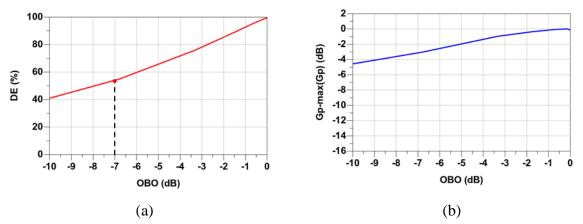

| Figure 2.19 – Class-E PA simulation results showing (a) drain efficiency and (b) normalized power gain versus normalized output power.                                                                                                                                                                          |

| Figure 2.20 – Supply modulation on a class-A PA.                                                                                                                                                                                                                                                                |

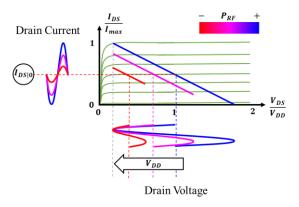

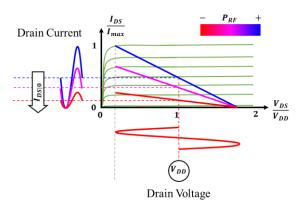

| Figure 2.21 – Load modulation on class-A PA loadlines and drain I-V curves                                                                                                                                                                                                                                      |

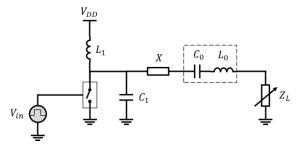

| Figure 2.22 – Class-E PA with varying load ZL for load-pull simulation                                                                                                                                                                                                                                          |

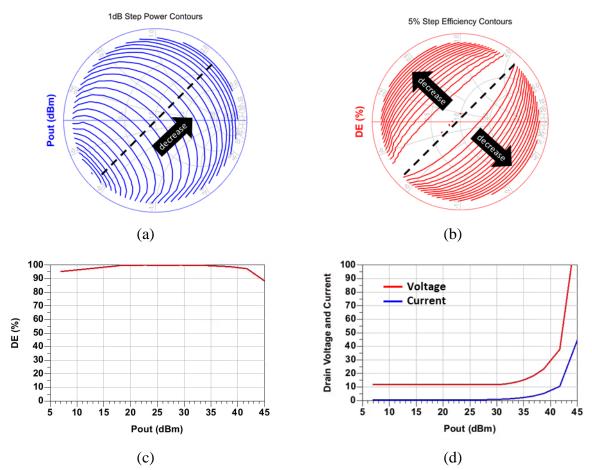

| Figure 2.23 – Smith Charts normalized to R with optimal performance load line in black showing: (a) Output power contours (b) Drain efficiency contours. For impedance values located on the optimal performance load line: (c) Drain efficiency versus output power, (d) Drain voltage and current amplitudes. |

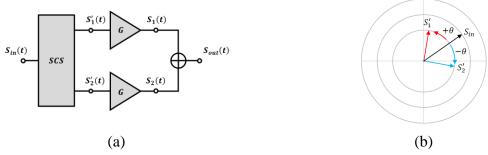

| Figure 2.24 – (a) Outphasing PA block diagram, (b) Complex-plane, input signal decomposition                                                                                                                                                                                                                    |

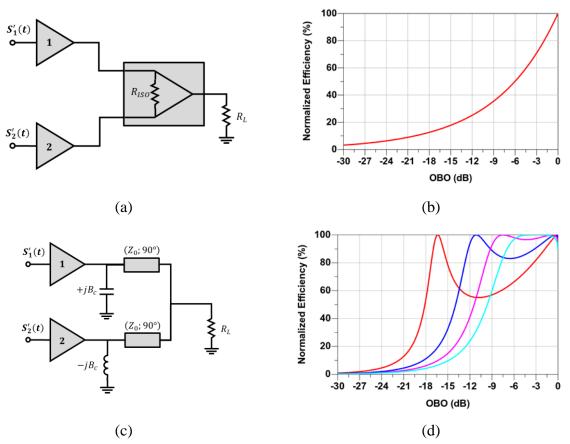

| Figure 2.25 – (a) Isolating Wilkinson combiner based OPA and (b) its associated efficiency profile with respect to back-off output power level. (c) Classic Chireix non-isolating combiner based OPA with (d) possible efficiency profiles that can be achieved depending on the combiner design values.        |

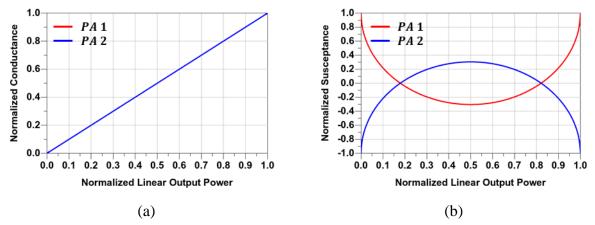

| Figure 2.26 – OPA Chireix combiner simulation showing normalized PA load (a) conductance and (b) susceptance versus output power                                                                                                                                                                                |

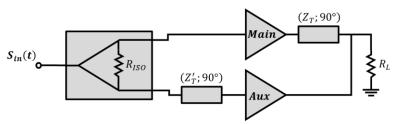

| Figure 2.27 – Classic DPA power stage and output combiner schematic                                                                                                                                                                                                                                             |

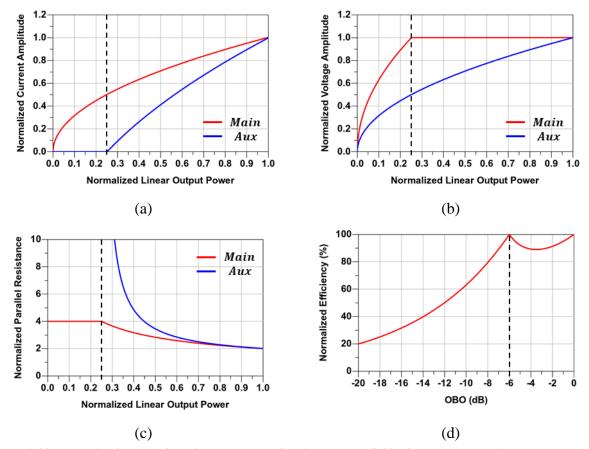

| Figure 2.28 – Normalized Main and Auxiliary (a) current (b) voltage (c) parallel load resistance versus linear output power. (d) Normalized DPA efficiency versus normalized output back-of in dB. The dashed line marks the BO critical operation point separating low power and Doherty regions               |

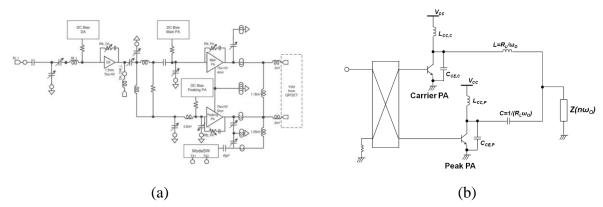

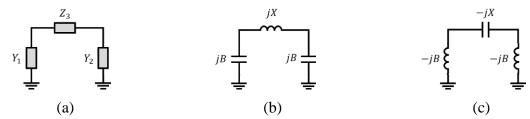

| Figure 2.29 – Examples of published DPA designs using (a) LCL combiner [43] and (b) LC combiner [42]                                                                                                                                                                                                            |

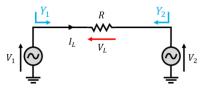

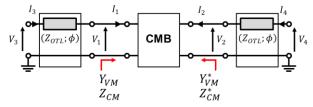

| Figure 3.1 – Differential Outphasing voltage combiner                                                                                                                                                                                                                                                           |

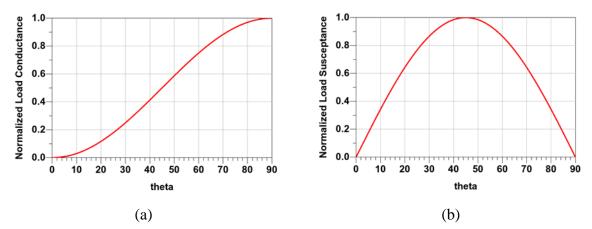

| Figure 3.2 – (a) Normalized load conductance, (b) Normalized load susceptance 44                                                                                                                                                                                                                                |

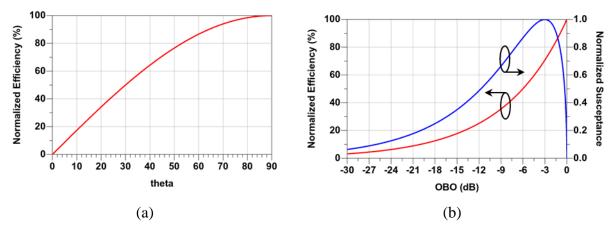

| Figure 3.3 – (a) Normalized efficiency, (b) OPA efficiency and load susceptance with respect to normalized output power (OBO)                                                                                                                                                                                   |

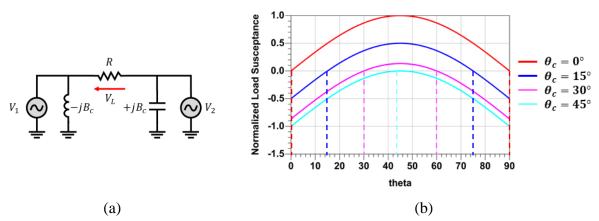

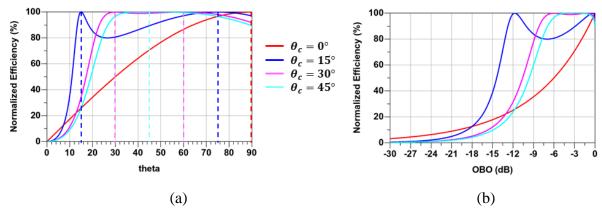

| Figure 3.4 – (a) Differential voltage combiner with reactive compensation, (b) Load susceptance versus Outphasing angle for different compensation angle values                                                                                                                                                 |

| Figure 3.5 – (a) Efficiency with respect to Outphasing angle, (b) Efficiency with respect to output power back-off (OBO)                                                                                                                                                                                        |

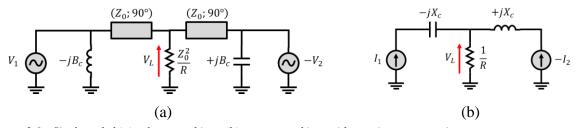

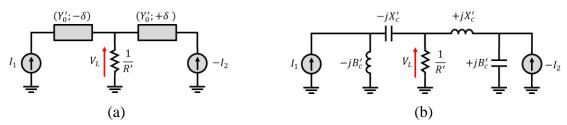

| Figure 3.6 – Single-ended (a) voltage combiner, (b) current combiner with reactive compensation                                                                                                                                                                                                                 |

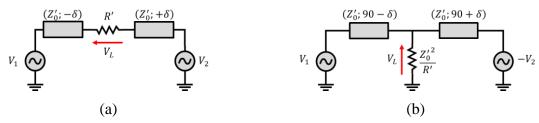

| Figure 3.7 – (a) Differential voltage combiner, (b) Single-ended voltage combiner with delay-line compensation                                                                                                                                                                                                  |

| Figure 3.8 – (a) Single-ended (a) current combiner with delay-line compensation, (b) current combiner with simplified lumped equivalent of delay-line compensation                                                                                                                                              |

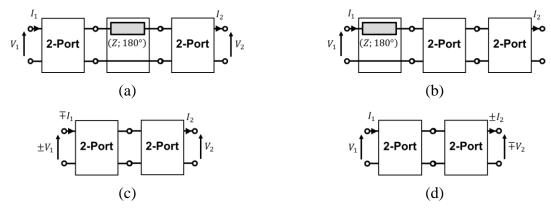

| Figure 3.9 – (a) Voltage combiner and (b) Current combiner with reactive compensation, (c) Voltage combiner and (d) Current combiner with delay-line compensation. Without negative signs at sources                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

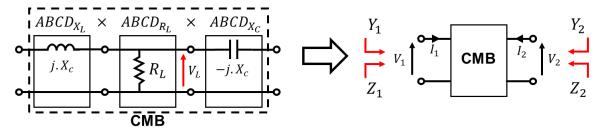

| Figure 3.10 – Cascaded two-port representation of the RCC combiner and its equivalent simplified form to be used for analysis.                                                                                                                           |

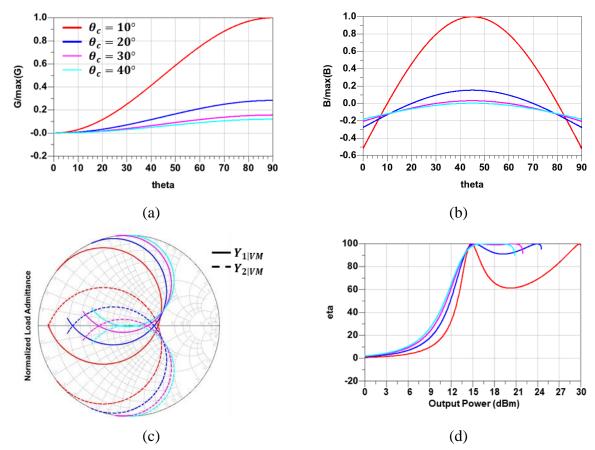

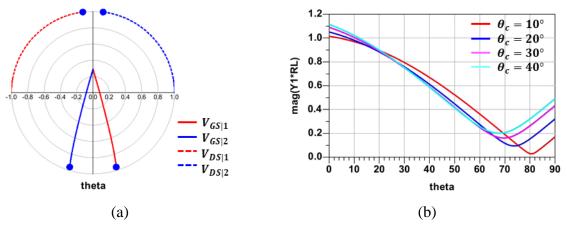

| Figure 3.11 – (a) Normalized Conductance and (b) Susceptance. (c) Normalized load admittance trajectories. (d) Efficiency with respect to output power for different values of $\theta c$                                                                |

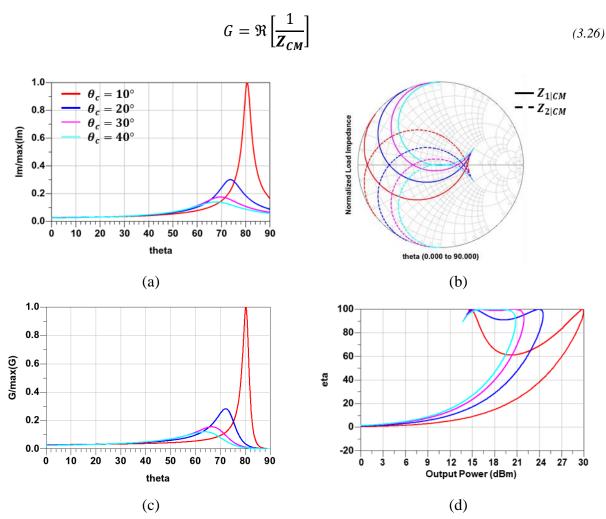

| Figure 3.12 – (a) Input current amplitude evolution with respect to $\theta$ for different values of $\theta c$ , (b) Normalized input impedances, (c) Normalized load conductance, (d) Efficiency with respect to output power                          |

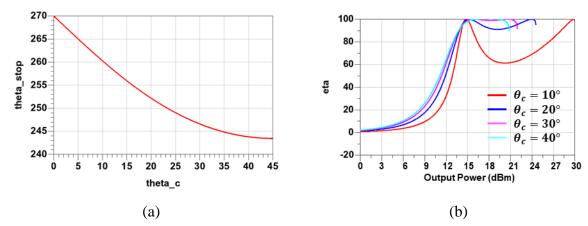

| Figure 3.13 – (a) Maximum Outphasing angle $\theta$ stop with respect to compensation angle variation. (b) Efficiency with respect to output power.                                                                                                      |

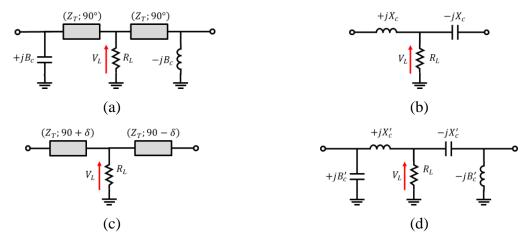

| Figure 3.14 – (a) Reactive compensation voltage combiner (RCV) (b) Reactive compensation current combiner (RCC) (c) Delay-line compensation voltage combiner (DCV) (d) Delay-line compensation current combiner (DCC)                                    |

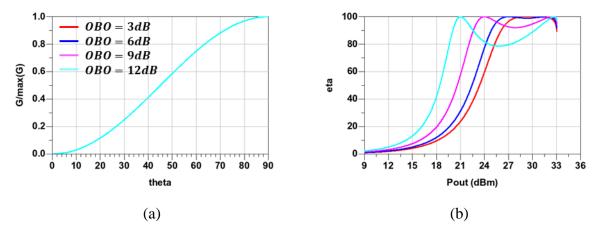

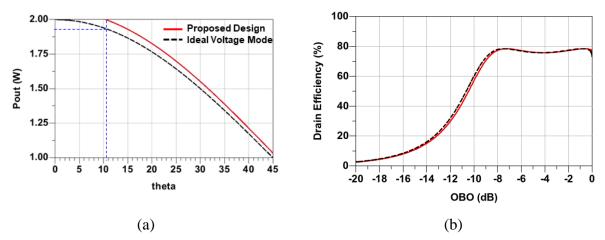

| Figure 3.15 – (a) Normalized load conductance and (b) Efficiency with respect to output power for different targeted OBO in voltage-mode operation                                                                                                       |

| Figure 3.16 – (a) Normalized current amplitude and (b) load conductance for different values of OBO in current-mode operation                                                                                                                            |

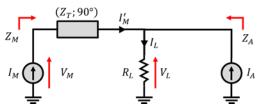

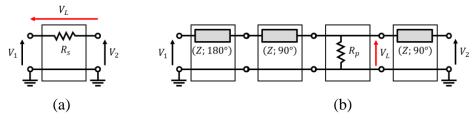

| Figure 3.17 – Simplified current-mode representation of the DPA architecture57                                                                                                                                                                           |

| Figure 3.18 – (a) Lossy two-port representation of the black-box method, (b) Lossless three-port representation of the black-box method                                                                                                                  |

| Figure 3.19 – Cascaded two-port network representation of the reactive compensation current combiner for DPA operation                                                                                                                                   |

| Figure 3.20 – Cascaded two-port network representation of the reactive compensation current combiner for DPA operation                                                                                                                                   |

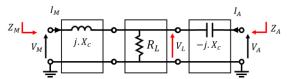

| Figure $3.21$ – Maximum theoretical back-off value $\zeta max$ with respect to $\phi$ 63                                                                                                                                                                 |

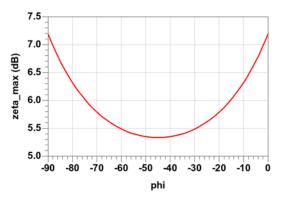

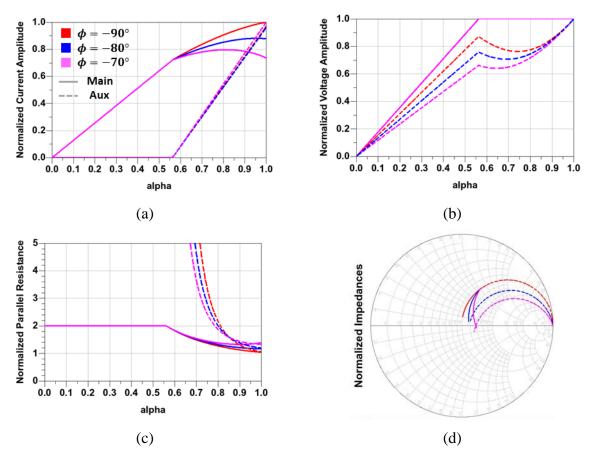

| Figure 3.22 – Main and auxiliary normalized (a) current amplitude, (b) voltage amplitude, (c) parallel load resistance, and (d) impedance for different values of $\phi$ at $\zeta = 5dB$ 64                                                             |

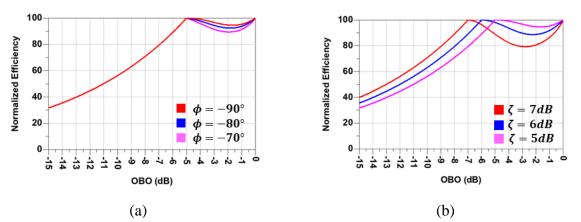

| Figure 3.23 – DPA combiner efficiency versus normalized output power for (a) different values of $\phi$ at $\zeta = 5dB$ and (b) different levels of $\zeta$ at $\phi = -90^{\circ}$                                                                     |

| Figure 4.1 – Two-stage DPA block diagram69                                                                                                                                                                                                               |

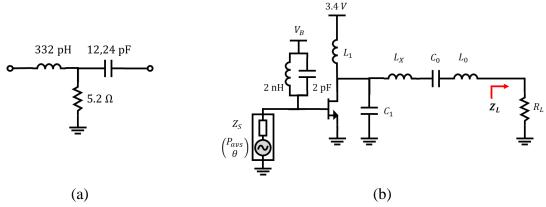

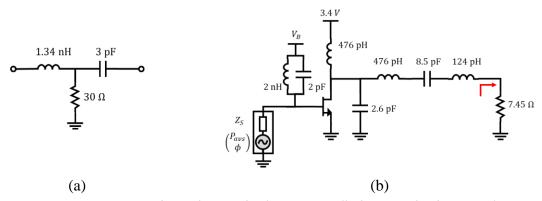

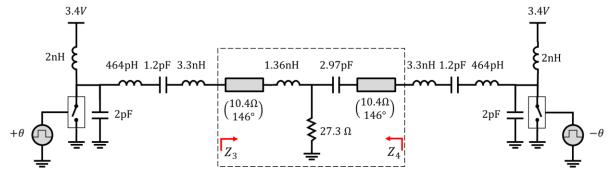

| Figure 4.2 – (a) Reactive compensation current combiner, (b) Class-E power cell schematic                                                                                                                                                                |

| Figure 4.3 – Schematic of the class-E DPA power stage with combiner71                                                                                                                                                                                    |

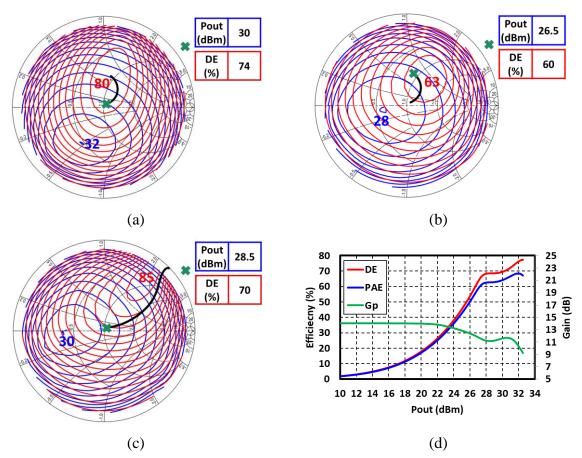

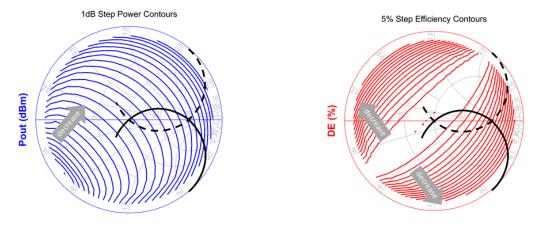

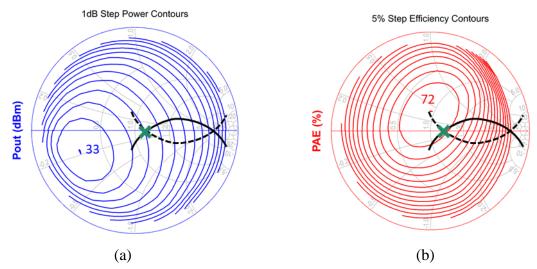

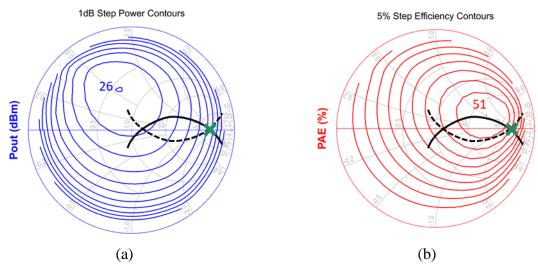

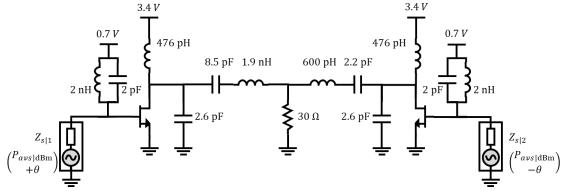

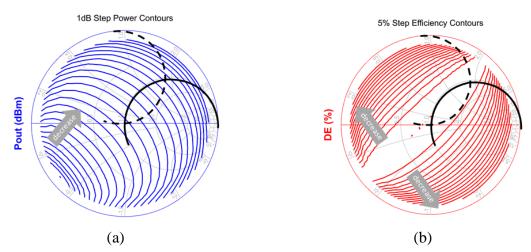

| Figure 4.4 – 1dB step power contours and 5% step efficiency contours with load modulation trajectory seen at (a) main branch at peak, (b) main branch at back-off, (c) auxiliary branch at peak. (d) DPA stage efficiency and gain versus output power71 |

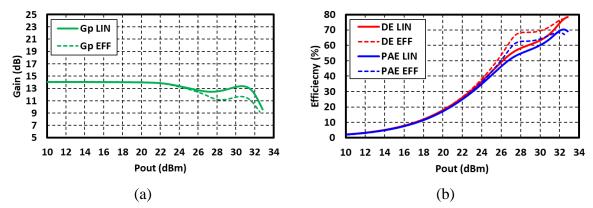

| Figure 4.5 – Comparison of DPA (a) gain and (b) efficiency versus output power in the case of linear and efficient operation modes.                                                                                                                      |

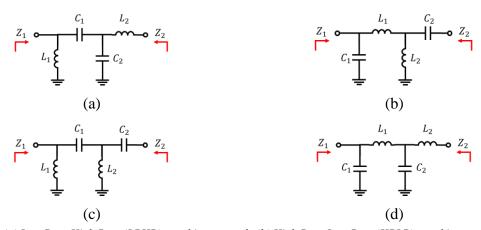

| Figure 4.6 – (a) Low Pass-High Pass (LPHP) matching network, (b) High Pass-Low Pass (HPLP) matching network, (c) Low Pass-Low Pass (LPLP) matching network, (d) High Pass-High Pass (HPHP) matching network          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.7 – (a) PAE and (b) Power gain performance versus output power for different IMN architectures                                                                                                              |

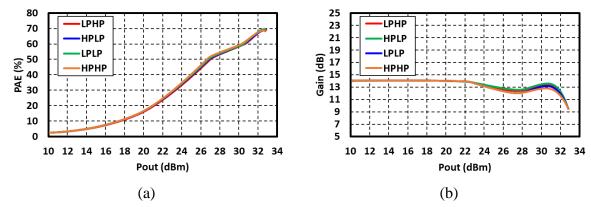

| Figure 4.8 – (a) Dual-input DPA reflection coefficients, (b) Input and output impedance extraction                                                                                                                   |

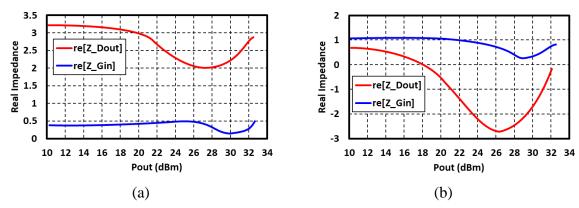

| Figure 4.9 – Real part of the input and output impedances of (a) Main and (b) Auxiliary branch PAs                                                                                                                   |

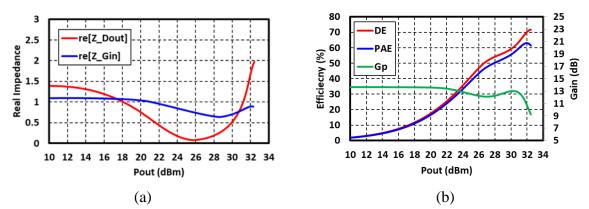

| Figure $4.10 - (a)$ Real part of the input and output impedances of the auxiliary branch PA after tuning. (b) Simulated DPA efficiency and gain versus output power achieved after tuning 75                         |

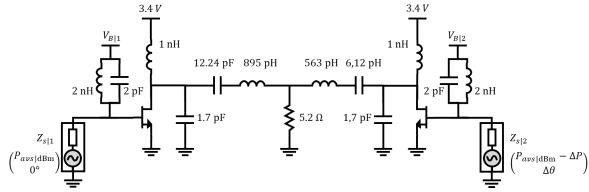

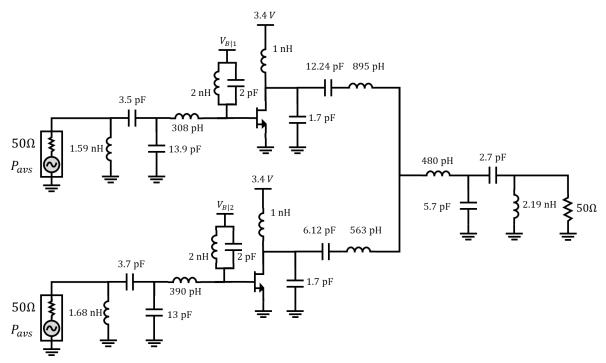

| Figure 4.11 – Single-stage dual-input DPA schematic with input and output matching networks                                                                                                                          |

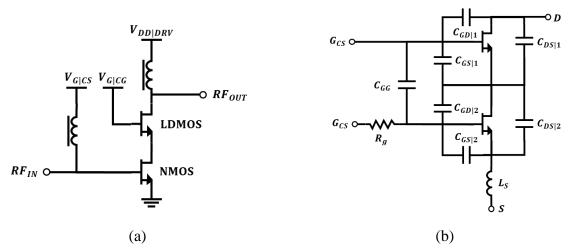

| Figure 4.12 – (a) Cascode topology schematic and (b) Driver stage equivalent model 76                                                                                                                                |

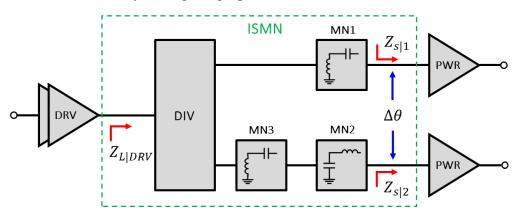

| Figure 4.13 – ISMN sub-circuit components                                                                                                                                                                            |

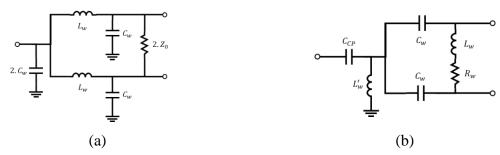

| Figure 4.14 – (a) Conventional lumped-element Wilkinson divider, (b) Modified Wilkinson lumped-element divider                                                                                                       |

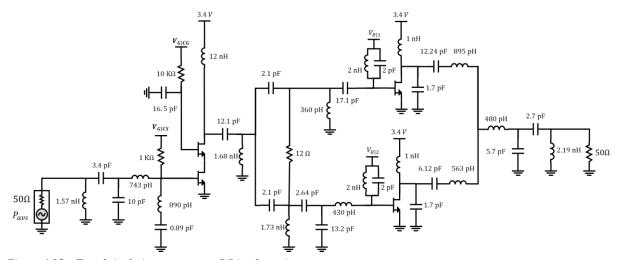

| Figure 4.15 – Tuned single-input two-stage DPA schematic                                                                                                                                                             |

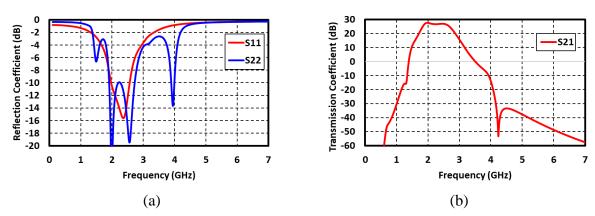

| Figure 4.16 – (a) Reflection coefficients, (b) Transmission coefficient                                                                                                                                              |

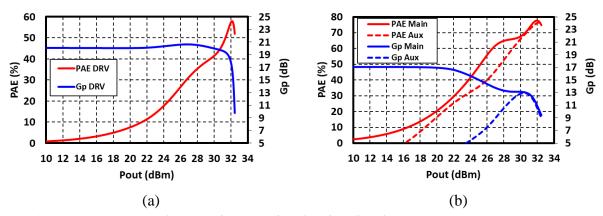

| Figure 4.17 – (a) Driver stage performance, (b) Main and auxiliary branch performance 79                                                                                                                             |

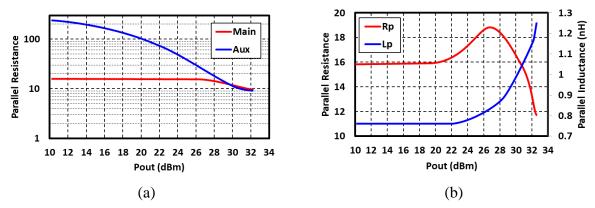

| Figure 4.18 – (a) Real power stage load modulation, (b) driver stage load modulation 80                                                                                                                              |

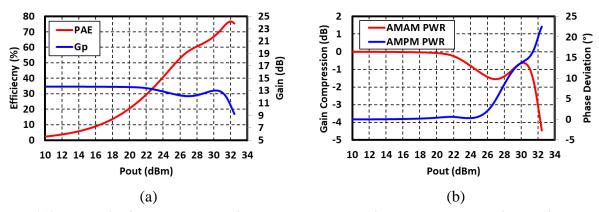

| Figure 4.19 – (a) Simulated power stage PAE and gain versus output power. (b) power stage AMAM and AMPM distortions                                                                                                  |

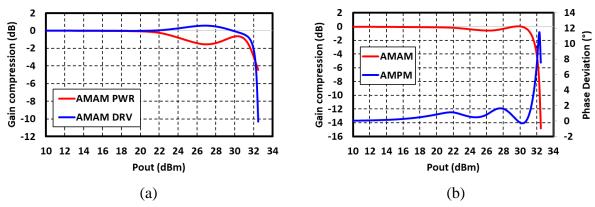

| Figure 4.20 – (a) Power and driver stage AMAM distortion, (b) Two-stage DPA AMAM and AMPM distortion.                                                                                                                |

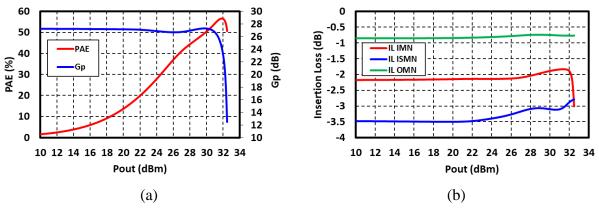

| Figure 4.21 – (a) Two-stage DPA line-up performance, (b) Insertion loss of the matching stages                                                                                                                       |

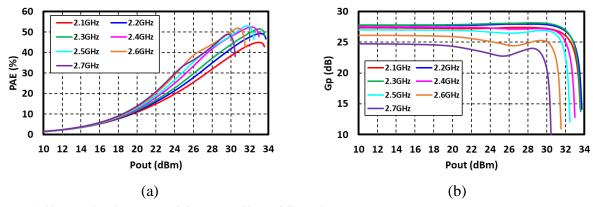

| Figure 4.22 – Simulated (a) PAE and (b) gain profiles at different frequencies                                                                                                                                       |

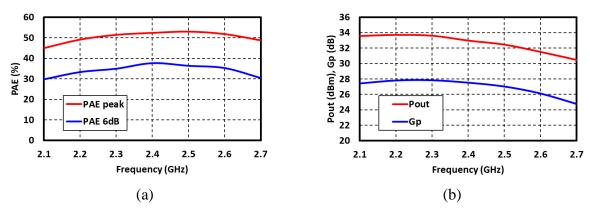

| Figure 4.23 – Simulated (a) Peak and 6dB Back-Off PAE and (b) Output power and gain with respect to operating frequency.                                                                                             |

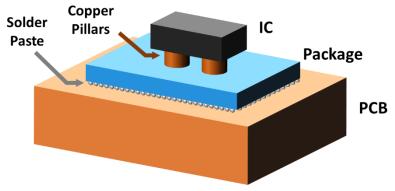

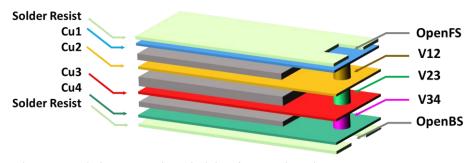

| Figure 4.24 – Assembly technology stack-up.                                                                                                                                                                          |

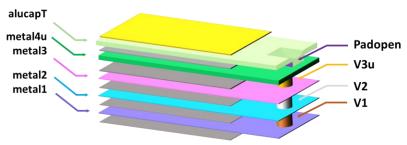

| Figure 4.25 – RF-SOI technology M4TCTA stack showing metals on the left and vias on the right.                                                                                                                       |

| Figure 4.26 – Custom inductor with (a) High quality factor, (b) High compacity                                                                                                                                       |

| Figure 4.27 – Custom inductor with (a) High quality factor, (b) High inductance in a compact size.                                                                                                                   |

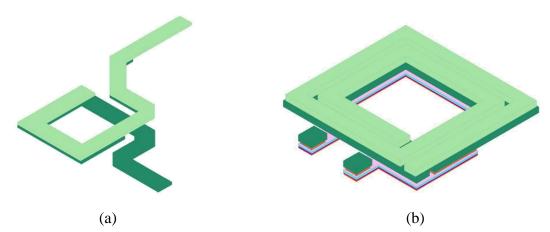

| Figure 4.28 – EM simulation results of the series auxiliary inductor <i>Ls</i>   <i>Aux</i> and the LC tank bias inductor <i>LBias</i> showing (a) inductance value and (b) quality factor with respect to frequency |

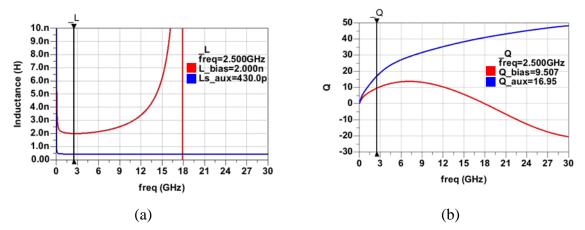

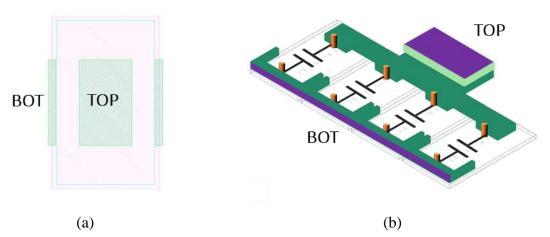

| Figure 4.29 – 3D representation of (a) 3 metal layers MOM capacitor. (b) MIM capacitor 85                                                                                                                            |

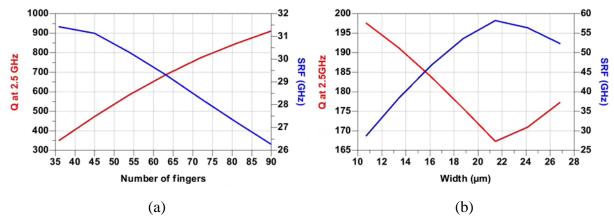

| Figure 4.30 – Quality factor at 2.5GHz and self-resonance frequency simulated for 1pF using DK (a) MOM capacitor model, (b) MIM capacitor model                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.31 – (a) 2D layout view of the elementary MIM capacitor cell with top and bottom pins on the metal4u layer, (b) 3D view of the access structure with the external top and bottom pins marked in purple, and the internal connection pins to the unitary capacitor cells marked in orange. |

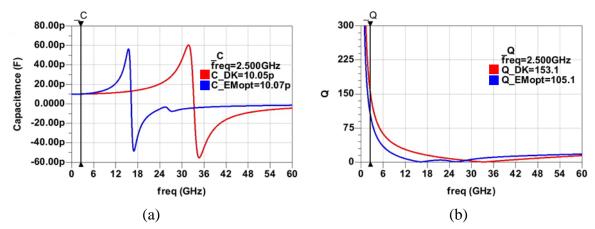

| Figure 4.32 – (a) Capacitance and (b) Q-factor of the equivalent capacitor using 4 parallel capacitors with the DK model only (red) and EM model of the access+capacitor DK model (blue)                                                                                                           |

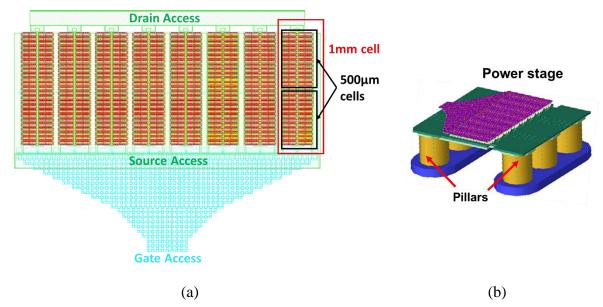

| Figure 4.33 – (a)2D layout view of the 8mm LDMOS PA cell, (b) 3D layout of the power stage with copper pillars                                                                                                                                                                                     |

| Figure $4.34 - \mu PCB$ laminate stack showing metals on the left and vias on the right                                                                                                                                                                                                            |

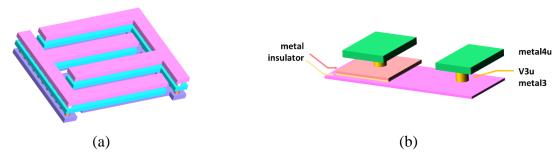

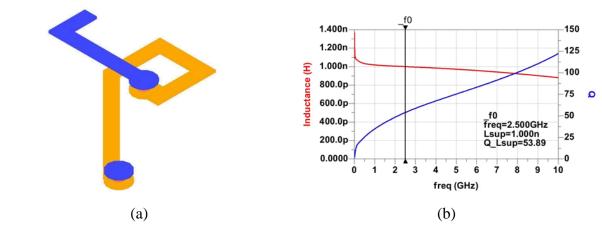

| Figure 4.35 – (a) 3D view of the supply inductor layout, (b) Inductance and Q-factor of the EM model.                                                                                                                                                                                              |

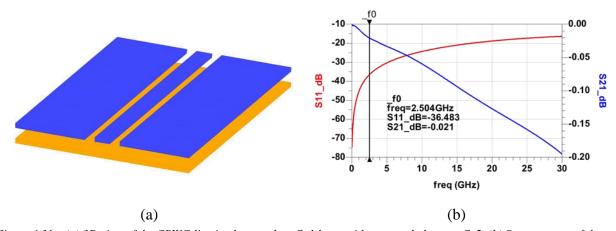

| Figure 4.36 – (a) 3D view of the CPWG line implemented on Cu1 layer with a ground plane on Cu2, (b) S-parameters of the EM model.                                                                                                                                                                  |

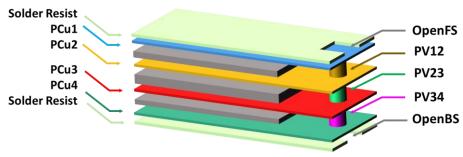

| Figure 4.37 – PCB technology stack showing metals on the left and vias on the right90                                                                                                                                                                                                              |

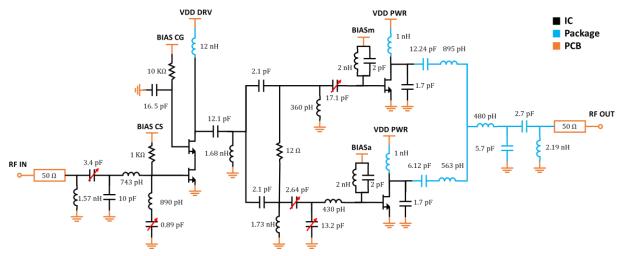

| Figure 4.38 – Tuned single-input two-stage DPA schematic                                                                                                                                                                                                                                           |

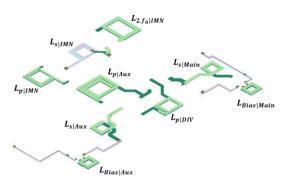

| Figure 4.39 – RFpro 3D view of the integrated IC inductors                                                                                                                                                                                                                                         |

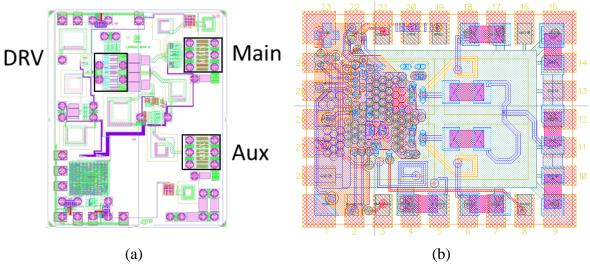

| Figure 4.40 – (a) 2D layout view of the IC chip with black boxes outlining the main, auxiliary, and driver cells. (b) 2D layout view of the μPCB package92                                                                                                                                         |

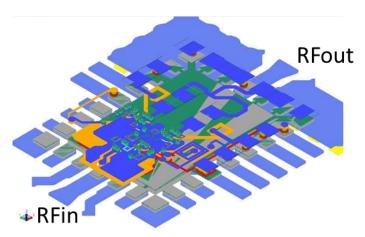

| Figure 4.41 – 3D RFpro view of the full-stack for EM simulation92                                                                                                                                                                                                                                  |

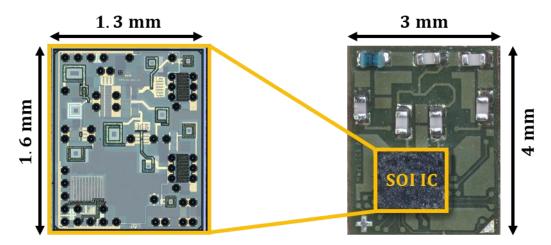

| Figure 4.42 – IC die and laminate package photograph93                                                                                                                                                                                                                                             |

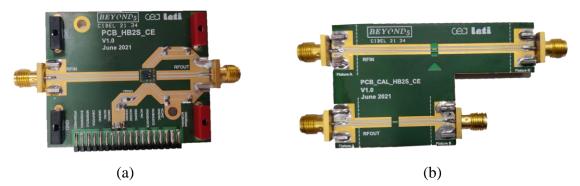

| Figure 4.43 – (a) Fabricated PCB with mounted IC and package (b) PCB access lines test structure                                                                                                                                                                                                   |

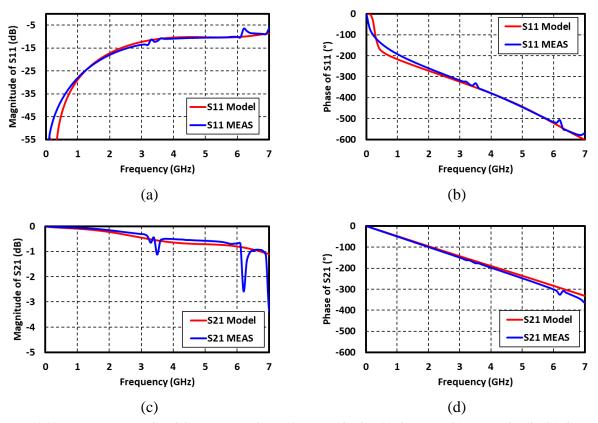

| Figure 4.44 – Measurement and model comparison of (a) S11 magnitude, (b) S11 phase, (c) S21 magnitude, (d) S21 phase                                                                                                                                                                               |

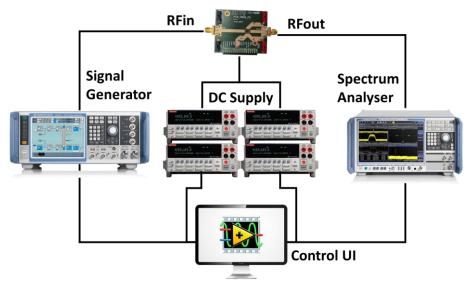

| Figure 4.45 – PA measurement setup                                                                                                                                                                                                                                                                 |

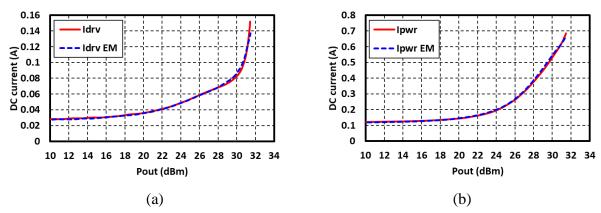

| Figure 4.46 – (a) Driver and (b)Power stage DC drain current comparison between measurements and EM model                                                                                                                                                                                          |

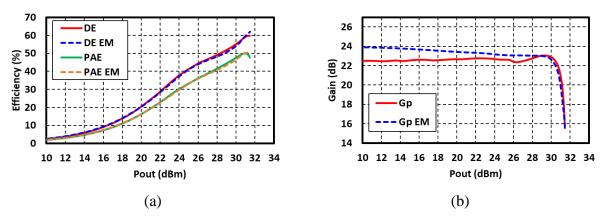

| Figure 4.47 – (a) PAE, DE and (b) power gain comparison between measurements and simulation                                                                                                                                                                                                        |

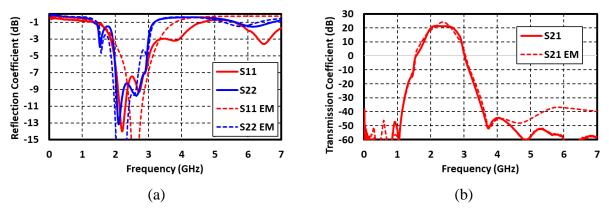

| Figure 4.48 – (a) Reflection and (b) transmission coefficient comparison between measurements and simulation96                                                                                                                                                                                     |

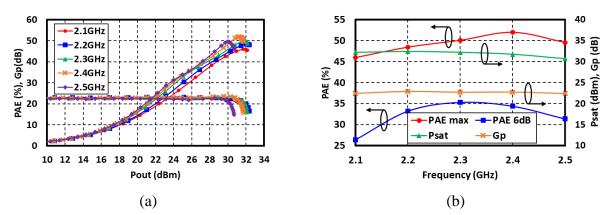

| Figure 4.49 – (a) PAE and gain profiles at different operating frequencies. (b) Extracted power, efficiency and gain at different operating frequencies in CW mode96                                                                                                                               |

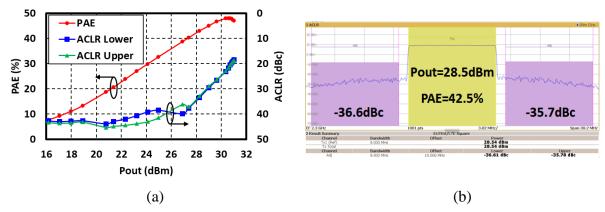

| Figure 4.50 – (a) PAE and E-UTRA ACLR versus <i>Pout</i> measured at 2.3GHz using 10MHz LTE QPSK 50RB uplink signal with memoryless DPD and (b) Output Spectrum97                                                                                                                                  |

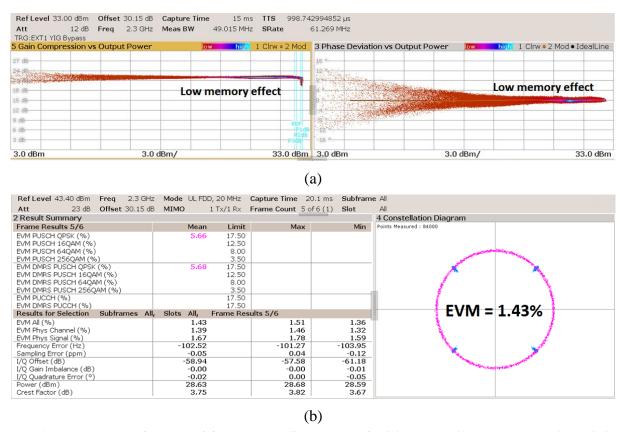

| Figure 4.51 – (a) AMAM and AMPM and (b) output constellation measured at 2.3GHz using 10MHz LTE QPSK 50RB uplink signal                                                                                                                                                                            |

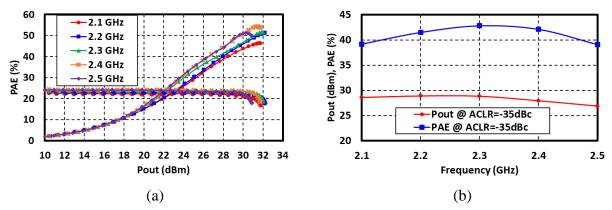

| Figure 4.52 – (a) Measured PAE and <i>Gp</i> versus <i>Pout</i> and (b) PAE and <i>Pout</i> extracted for ACLR=-35dBc at different frequencies using 10MHz LTE QPSK 50RB uplink signal 98         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

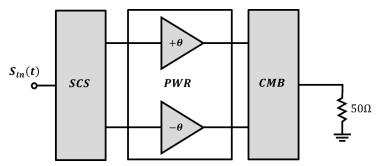

| Figure 5.1 – Generic OPA block schematic showing its three main components 103                                                                                                                    |

| Figure 5.2 – (a) Ideal transistor model (b) Simplified OBPA with reactive compensation voltage combiner                                                                                           |

| Figure $5.3$ – (a) Complex plane representation of normalized drain and gate voltages (b) Normalized admittance magnitude for different compensation angle values                                 |

| Figure $5.4 - (a)$ Output power and (b) efficiency evolution for ideal voltage-mode (dashed black) and the proposed OBPA design (red)                                                             |

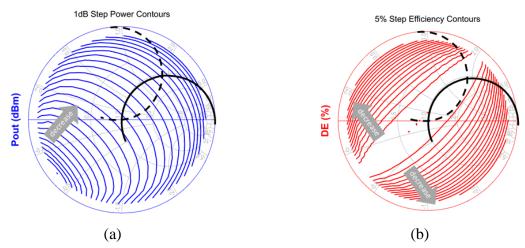

| Figure 5.5 – Ideal switch-based q=1 class-E PA load-pull contours showing (a) output power and (b) efficiency contours with classic Outphasing load modulation schemes overlaid in black          |

| Figure 5.6 – Two-port representation of the Outphasing combiner with offset transmission lines.                                                                                                   |

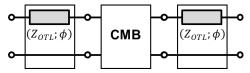

| Figure 5.7 – Ideal switch-based q=1 class-E PA load-pull contours showing (a) output power and (b) efficiency contours with rotated OTL Outphasing load modulation schemes overlaid in black      |

| Figure 5.8 – Ideal switch-based q=1.3 class-E PA load-pull contours showing (a) output power and (b) efficiency contours with classic Outphasing load modulation schemes overlaid in black        |

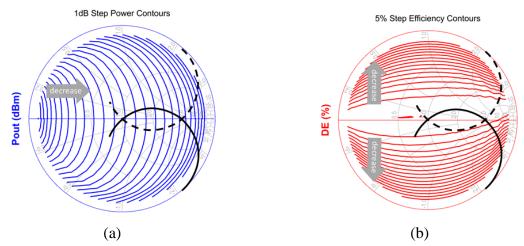

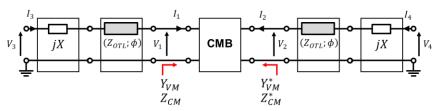

| Figure 5.9 – (a) Reactive compensation combiner schematic, (b) Class-E power cell schematic with red arrow marking complex load modulation plane                                                  |

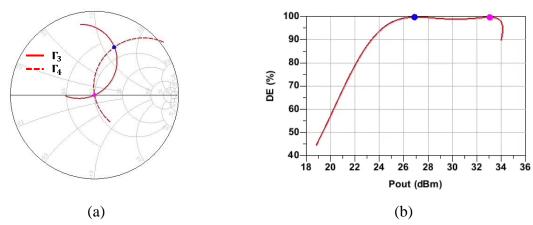

| Figure 5.10 – Load-pull contours at $Pavs dBm = 23.5dBm$ (a) Power contours, (b) PAE contours                                                                                                     |

| Figure 5.11 – Load-pull contours at $Pavs dBm = 13dBm$ (a) Power contours, (b) PAE contours                                                                                                       |

| Figure 5.12 – Dual input OEPA schematic                                                                                                                                                           |

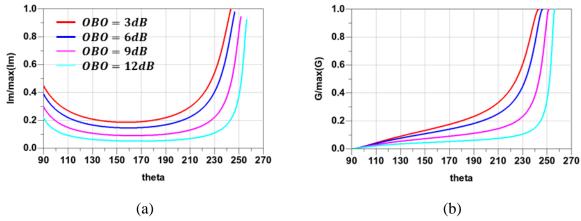

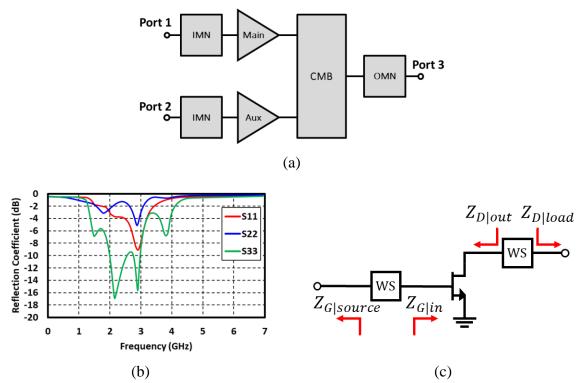

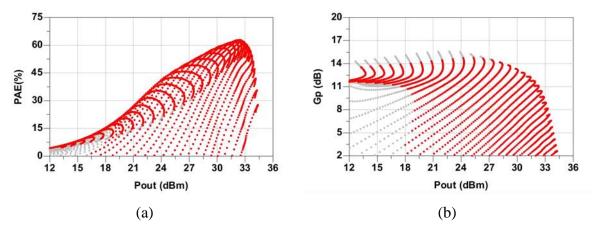

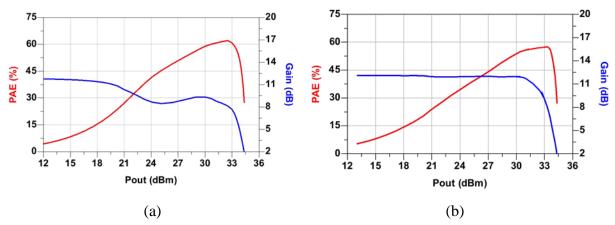

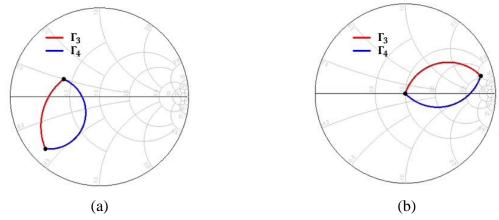

| Figure 5.13 – Possible (a) PAE and (b) power gain performance versus output power for different values of $\theta$ in OPA operation for $q = 1.3$ . Potentially unstable points are shown in grey |

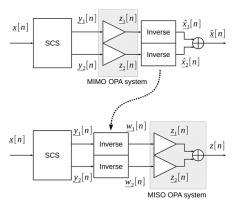

| Figure 5.14 – Conventional (signal) diagram of an OPA                                                                                                                                             |

| Figure $5.15$ – PAE and gain profiles versus output power extracted from the OEPA simulation using (a) maximum PAE criterion, and (b) constant gain value $Gp = 12dB$ criterion 113               |

| Figure 5.16 – Signal representation of LUT approach for dual input OPA 113                                                                                                                        |

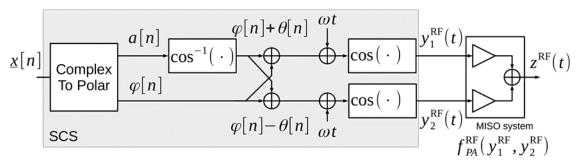

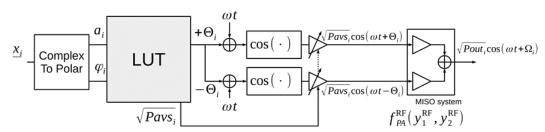

| Figure 5.17 – LUT-based DPD integrated in OTX system                                                                                                                                              |

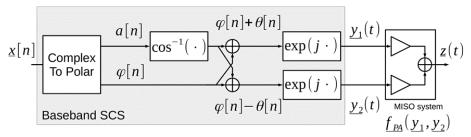

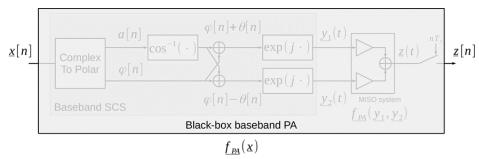

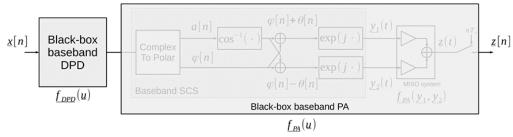

| Figure 5.18 – Equivalent baseband signal diagram of the conventional OPA 114                                                                                                                      |

| Figure 5.19 – SISO basedband OPA model representation                                                                                                                                             |

| Figure 5.20 – SISO basedband DPD model representation                                                                                                                                             |

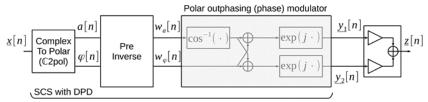

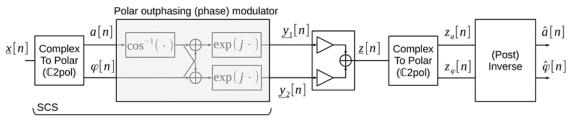

| Figure $5.21 - OTX$ diagram showing how the post-inverse can be used as a pre-inverse $116$                                                                                                       |

| Figure 5.22 – Pre-inverse configuration of the In-SCS DPD architecture                                                                                                                            |

| Figure 5.23 – Associated post-inverse configuration of the proposed In-SCS DPD architecture.                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

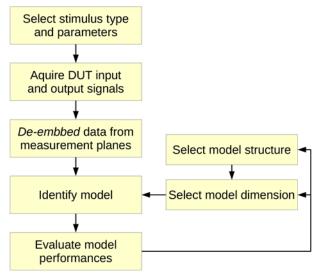

| Figure 5.24 – PA behavioural modelling flow chart                                                                                                                                                             |

| Figure A.1 – Two-port network representation                                                                                                                                                                  |

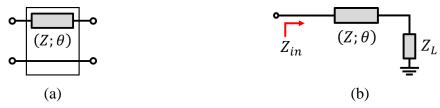

| Figure B.1 – Two-port network representation                                                                                                                                                                  |

| Figure B.2 – (a)Transmission Line representation as a two-port network, (b) Transmission line terminated in a load $ZL$                                                                                       |

| Figure B.3 – Transmission Line representation as a two-port network                                                                                                                                           |

| Figure B.4 – (a) Differential power combining topology, (b) Equivalent common-mode power combiner                                                                                                             |

| Figure B.5 – (a) Differential power combining topology, (b) Equivalent single-ended power combiner                                                                                                            |

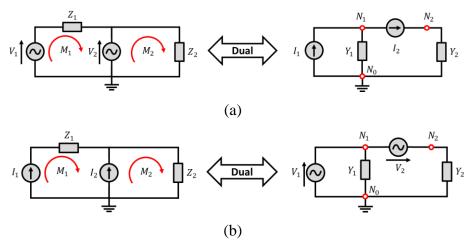

| Figure B.6 – Examples of dual circuits with (a) Voltage sources and (b) Current sources 139                                                                                                                   |

| Figure C.1 – Generic Outphasing load modulation combiner with offset transmission lines 140                                                                                                                   |

| Figure C.2 – Ideal switch-based q=1 class-E PA load-pull contours showing (a) output power and (b) efficiency contours with rotated OTL Outphasing load modulation schemes overlaid in black.                 |

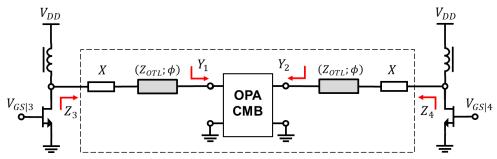

| Figure C.3 – (a) Effect of $\phi$ on the direction of the load modulation trajectories (b) Effect of $\theta c$ on the opening of the load modulation trajectories and the distance between the intersections |

| Figure C.4 – Ideal OTL-based OEPA schematic                                                                                                                                                                   |

| Figure C.5 – (a) OEPA load modulation trajectories (b) Efficiency versus output power of the OEPA                                                                                                             |

| Figure C.6 – Output power evolution for ideal voltage-mode (dashed black) and the proposed OBPA design (red)                                                                                                  |

| Figure C.7 – Simplified schematic of the generalized combiner design circuit                                                                                                                                  |

| Figure C.8 – (a) Complex load modulation trajectories referenced at $50\Omega$ (b) Complex load modulation trajectories referenced at $\mathbf{Z}\boldsymbol{\alpha}$ *                                       |

# **List of Tables**

| Table 1.1 – Classification of the different 5G NR frequency bands and their application. | _   |

|------------------------------------------------------------------------------------------|-----|

| Table 2.1 - K-set design equations for 0.6≤q≤1.65                                        | 25  |

| Table 2.2 – State of the art sub-6 GHz Outphasing PAs                                    | 34  |

| Table 2.3 – State of the art sub-6 GHz Doherty PAs                                       | 37  |

| Table 3.1 – Combiner design expressions.                                                 | 55  |

| Table 4.1 – DPA target performance                                                       | 69  |

| Table 4.2 – Linear DPA drive profile                                                     | 72  |

| Table 4.3 – Modified DPA drive profile                                                   | 75  |

| Table 4.4 – MOM and MIM specs comparison.                                                | 85  |

| Table 4.5 – Comparison with the state-of-the-art LTE Doherty PAs                         | 98  |

| Table B.1 – Common component ABCD matrices                                               | 134 |

| Table B.2 – Dual networks of elementary components                                       | 138 |

| Table C.1 – Combiner Component Design Values for OTL-based combiners                     | 142 |

## **Glossary of Abbreviations**

1G First Generation Mobile Communication Standard

**2D** Two dimensional

**2G** Second Generation Mobile Communication Standard

**3D** Three dimensional

**3G** Third Generation Mobile Communication Standard

4G Fourth Generation Mobile Communication Standard

**5G** Fifth Generation Mobile Communication Standard

**5G NR** 5G New Radio

**5G NSA** 5G Non-Standalone

**5G SA** 5G Standalone

ACLR Adjacent Channel Leakage Ratio

**ACPR** Adjacent Channel Power Ratio

**ADS** Agilient Design System

**AMAM** Amplitude Modulation to Amplitude Modulation

**AMPM** Amplitude Modulation to Phase Modulation

**BEOL** Back End of Line

**BO** Back-Off

**BPSK** Binary Phase-Shift Keying

**BS** Base Station

**CCDF** Complementary Cumulative Distribution Function

**CDMA** Code Division Multiple Access

**CG** Common Gate

**CMB** Combiner Stage

**CMOS** Complementary MOS

**CPWG** Coplanar Waveguide

**CS** Common Source

Cu Copper

**CuP** Copper Pillars

**CW** Continuous Wave

**DC** Direct Current

**DCC** Delay-Line Compensation Current (combiner)

**DCV** Delay-Line Compensation Voltage (combiner)

**DDR** Dynamic Deviation Reduction

**DE** Drain Efficiency

**DK** Design Kit

**DL** Downlink

**DPA** Doherty Power Amplifier

**DPD** Digital Predistortion

**DRV** Driver Stage

**EER** Envelope Elimination and Restoration

**EM** Electromagnetic

**eMBB** Enhanced Mobile Broadband

**ET** Envelope Tracking

E-UTRA Evolved Universal Terrestrial Radio Access

**EVM** Error Vector Magnitude

**FDMA** Frequency Division Multiple Access

FEM Front End Module

GaAs Gallium Arsenide

**GMP** Generalized Memory Polynomial

**GSM** Global System for Mobile Communications

**GPS** Global Positioning System

**HCD** Hybrid Chireix-Doherty

**HR** Harmonic Ratio

IC Integrated Circuit

ILA Indirect Learning Architecture

IMD Intermodulation product

IMN Input Matching Network

**IoT** Internet of Things

**ISMN** Inter-Stage Matching Network

**LDMOS** Laterally-Diffused MOS

**LINC** Linear Amplification using Non Linear Components

**LNA** Low Noise Amplifier

LTE Long Term Evolution

LTE-Advanced

**LUT** Look-Up Table

MIM Metal-Insulator-Metal

MIMO Multiple Input Multiple Output

MISO Multiple Input Single Output

**mMIMO** Massive MIMO

**mMTC** Massive Machine Type Communication

**mmW** Millimetre-Wave

MOM Metal-Oxyde-Metal

MOS Metal Oxide Semiconductor

MP Memory Polynomial

NMOS N-type MOS

**OBPA** Class-B OPA

**OBO** Output Back-Off

**OEPA** Class-E OPA

**OFDMA** Orthogonal Frequency Division Multiple Access

OMN Output Matching Network

**OPA** Outphasing Power Amplifier

**OTL** Offset Transmission Line

OTX Outphasing Transmitter System

**PA** Power Amplifier

**PAE** Power Added Efficiency

**PAPR** Peak to Average Power Ratio

**PCB** Printed Circuit Board

**PDF** Probability Density Function

**POM** Polar Outphasing Modulator

**PWR** Power Stage

**QAM** Quadrature Amplitude Modulation

**QPSK** Quadrature Phase-Shift Keying

**RCC** Reactive Compensation Current (combiner)

**RCV** Reactive Compensation Voltage (combiner)

#### Glossary of Abbreviations

**RF** Radio Frequency

**RX** Receiver

SCS Signal Component Seperator

SiGe Silicon Germanium

SISO Single Input Single Output

**SMA** Subminiature version A

**SMD** Surface Mounted Device

**SOI** Silicon on Insulator

**SP** Scatter Parameters

**SRF** Self-Resonance Frequency

**TDMA** Time Division Multiple Access

TX Transmitter

**UMTS** Universal Mobile Telecommunications System

UE User Equipment

UL Uplink

**uRLLC** Ultra-Reliable and Low Latency Communication

VNA Vector Network Analyzer

VGA Variable Gain Amplifier

**VoIP** Voice over Internet Protocol

WiFi Wireless Fidelity

WiMAX Worldwide Interoperability Microwave Access

# **Chapter 1. Introduction**

| 1 | Evolution of Mobile Communication Standards | 3 |

|---|---------------------------------------------|---|

| 2 | 5G System Specifications                    | 4 |

| 3 | RF Front-End Architectures                  | 6 |

| 4 | Thesis Objectives                           | 8 |

ellular communications have become an integral part of everyday life. Since the rise of smartphones in 2007, demand for higher data-rates and increased network capacity has exponentially grown which has fuelled the research and development of new communication standards. As of 2018, the groundwork has been laid out for the next step in mobile communication, the 5G standard. However, each new technology brings new challenges. This first chapter outlines the context of 5G development and the requirements it imposes from a circuit design point of view. These criteria are used to define the current needs and subsequently the objectives of the following thesis.

#### 1 Evolution of Mobile Communication Standards

Cellular communications have come a long way since the deployment of the first-generation standards (1G) in 1984. Back then, wireless communication was achieved through analog frequency modulation known as Frequency Division Multiple Access (FDMA). Each user would be allocated a frequency band of 30KHz on a carrier frequency around 500MHz. Moreover, the different existing standards were incompatible [1].

The rise of the number of users quickly led to a saturation of the radio-frequency (RF) spectrum which served as the motivation for creating the second generation of communication standards (2G). This effort was initially led by the Conference of European Post and Telecommunication Administrations (CEPT) which founded the coordinating group Groupe Spécial Mobile (GSM) to oversee European cellular radio development. However, as time went on, GSM's aspirations became much more far-reaching and its acronym now stood for Global System for Mobile Communications. This new standard was the world's first digital cellular system, opening up the possibilities for improvement upon the 1G system. Thanks to its use of digital signals, which can be clearly defined in time, Time Division Multiple Access (TDMA) was made possible. As a result, several channels can be multiplexed onto a single carrier with a bandwidth of 200KHz with the two main frequency bands being 900MHz and 1800MHz [2].

The advent of the 2000s saw the arrival of the third generation (3G) of communication standards which focused on providing internet services such as video streaming and email exchange. This was done through the Universal Mobile Telecommunications System (UMTS) based on Code Division Multiple Access (CDMA) which further improved spectral efficiency. While UMTS was not the standard to bring internet connectivity (that distinction goes to the EDGE standard which can be considered as an evolution of the 2G GSM standard; a 2.5G), it did greatly improve data-rates from 384Kbit/s to 1.92Mbit/s. Furthermore, additional bands were allocated for 3G use in the 900-2600MHz range with channel bandwidths of 3.84MHz [3].

The introduction and rise in popularity of smartphones in the 2010s fuelled the demand for increased data-rates which could accommodate Voice-over Internet Protocol (VoIP) applications such as video-calls and live streaming. The International Telecommunications Union (ITU) therefore set the technical specifications of the next mobile standard evolution, the fourth generation (4G), one of which were data-rates of 100Mbit/s and 1Gbit/s for moving and stationary users respectively as well as channel bandwidths between 5 and 20MHz. Two main standards are considered 4G-compliant: The first is the Worldwide Interoperability for Microwave Access (WiMAX), and the second more popular one is the Long-Term Evolution Advanced (LTE-A). It should be noted that while the precursor to LTE-A, the LTE was commercialized as a 4G service, it did not in fact fulfil the data-rate requirement and as a result cannot be considered a 4G standard. Both WiMAX and LTE-A were based on Orthogonal Frequency Division Multiple Access (OFDMA) air interface which improves on the FDMA by using multiple narrowband sub-carriers which are mutually orthogonal, thereby preventing interference between them [4], [5].

Finally, the fifth generation (5G) evolution of mobile standards has three main objectives: The first is enhanced Mobile Broadband (eMBB) which serves as an extension to 4G services, allowing for higher data-rates (up to 10Gbit/s) and better coverage in urban settings through the use of massive Multiple Input Multiple Output (mMIMO) protocols. The second objective is ultra-Reliable and Low Latency Communication (uRLLC) which allows for the evolution of

certain services such as autonomous self-driving cars and remote surgery where high speed communication is essential. The last objective is massive Machine Type Communication (mMTC) which will provide connectivity between smart objects and sensors; namely the Internet of Things (IoT) [6], [7].

As this work primarily deals with 5G applications, the next section will focus on 5G system specifications.

### 2 5G System Specifications

The 5G New Radio (5G NR) standard was first introduced in 2018 with the publication of Release 15 by the Third Generation Partnership Project (3GPP). The launch of this new standard would be done in two phases: Phase 1 refers to the deployment of the 5G Non-Standalone (5G NSA) mode which relies on existing LTE infrastructure and is mainly concerned with eMBB applications. As a result, this deployment mode, which began in 2020 uses much of the same frequency bands as LTE referred to as Frequency Range 1 (FR1) which are spread between 450MHz and 6GHz.

Phase 2 will see the deployment of the 5G Standalone (5G SA) mode which cater to eMBB as well as uRLLC and mMTC applications. This second mode will require an update of current cellular infrastructure and extend into millimetre-wave (mmW) frequencies between 24GHz and 52GHz also referred to as FR2 [8].

The different 5G NR frequency bands can therefore be grouped in four main categories as shown in Table 1.1 below.

| 5G Band Group    | Carrier Frequencies | Current standards | Best suited 5G application |

|------------------|---------------------|-------------------|----------------------------|

| Low Bands        | <1GHz               | 2G/3G/4G/IoT      | mMTC, eMBB                 |

| Middle Bands     | 1 – 2.7GHz          | 2G/3G/4G          | eMBB                       |

| High Bands       | 3 – 6GHz            | LTE-A             | eMBB, uRLLC                |

| Ultra-High Bands | 24.25 – 52GHz       | -                 | eMBB, localised uRLLC      |

Table 1.1 – Classification of the different 5G NR frequency bands and their main target application.

The 5G air interface is based on OFDMA variants such as CP-OFDMA and DFT-s-OFDM. This allows the system to allocate time and frequency slots dynamically depending on the needs of each user. To this end, 5G can operate at different channel bandwidth depending on the frequency band in use. Low, middle, and high bands can have a channel bandwidth between 3.84MHz and 100MHz, while the very high bands can go up to 400MHz. Moreover, different modulation schemes can be used to code binary digital data onto the carrier frequency signals; these include phase modulation schemes such as QPSK and  $\pi/2$ -BPSK as well as amplitude and phase modulation schemes such as 16, 64, and 256-QAM.

The flexibility provided by the new 5G NR standard comes at the cost of signal complexity. One of the ways of assessing this complexity is by examining the signal's Peak to Average Power Ratio (PAPR) which can be calculated using the equation from (1.1).

$$PAPR = 10.\log_{10}\left(\frac{P_{peak} \mid \mathbb{P}=0.01\%}{P_{ava}}\right)$$

(1.1)

The PAPR is commonly expressed in decibels (dB) and represents the ratio of the peak power, defined as the power level with a probability of 0.01%, and the average signal power. These two power levels are shown in Figure 1.1.

Figure 1.1 – Power envelope snippet in the time domain showing the peak and average power levels.

A more thorough approach for calculating the PAPR is possible when looking at the signals from a statistical perspective.

Figure 1.2—(a) Simulated PDF of different mobile communication standards. (b) CCDF of different carrier waveforms plotted against PAPR [9].

Figure 1.2(a) shows the Probability Density Function (PDF) of different signals with respect to the power back-off level (BO). In other words, it gives the probability of a waveform to have a power value that is x dB lower than the peak power of the signal. As can be seen, the BO level with the highest concentration decreases with every new standard, meaning that the signal will have a lower mean power but require a larger dynamic range in order to reach its peak. The PDF function can be used in order to calculate the Complementary Cumulative Distribution Function (CCDF) as shown in (1.2).

$$CCDF(PAPR) = 1 - \int_{P_{min}}^{PAPR+P_{avg}} PDF(x) dx$$

(1.2)

In this form, it is possible to determine the probability of the signal achieving a given PAPR level. The PAPR of the signal is defined as the value for which the CCDF is 0.01%. Figure 1.2(b) plots the CCDF functions of different waveforms and shows once again that the PAPR increases when going from 4G to 5G signals.

#### 3 RF Front-End Architectures

In a typical cellular communication scenario between two mobile terminals, each referred to as User Equipment (UE), are connected via one or more intermediaries known as the Base Stations (BS). Ever since the introduction of 2G, the connection between UE and BS has been dictated by two sub-protocols of the communication standard in use.

The first protocol, Uplink (UL), refers to a communication form the UE to the BS. In 5G NR, this protocol typically uses Cyclic Prefix OFDM (CP-OFDM) and Discrete Fourier Transform spread OFDM (DFT-s-OFDM) air interfaces as well as Single-Carrier FDMA (SC-FDMA) [10]–[12]. The maximum power transmitted by a UE is typically capped at 23dBm.

In the case of BS to UE communication, i.e. Downlink (DL), the CP-OFDMA is used. Depending on the application (rural/urban) different types of coverage cells are used with maximum power levels up to 50dBm.

In both BS and UE terminals, commination is achieved through the RF transceiver which allows for the wireless transmission and reception of modulated signals. Figure 1.3 shows the basic structure of the RF Front-End Module (FEM). In a UL scenario, the MoDem, short for Modulator/Demodulator, encodes binary data into a baseband signal which is then upconverted to RF and fed into the transmitter (TX) chain of the Front-End Module. There, the signal is amplified by the Power Amplifier (PA) before being sent through a filter in order to remove unwanted out-of-band emissions before finally being sent to the antenna. When in DL, the signal is captured by the antenna and filtered before being amplified by the Low Noise Amplifier (LNA) in the receiver (RX) and then downconverted before decoding in the MoDem.

Figure 1.3 – Simplified RF FEM block diagram.

Depending on the operating frequency of the transmitted or received signal, different filters are selected by the switches. Meanwhile the multiplexers act as filters between the different antennas and TX/RX branches.

Over the years, the FEM architecture has become more and more complex in an effort to accommodate different frequency bands and communication standards so as to offer seamless and backwards compatible operation to worldwide users. Today, smartphone FEMs are expected to address 2G, 3G, 4G and 5G standards as well as other standards such as Bluetooth, WiFi, and GPS. An example of a modern FEM architecture taken from [13] is provided in Figure 1.4.

Figure~1.4-4G/5G~RF~front-end~for~smartphones~[13].

Within the different FEM components, the PA can be singled out as the most critical. That is because a PA's power consumption represents more than half of the total FEM consumption. As a result, the efficiency of the PA is directly linked to battery consumption and thermal dissipation in a smartphone. Moreover, the performance of the PA can greatly affect the quality of communication as transmitted signals can become distorted when amplified thus making them unreadable at reception.

### 4 Thesis Objectives

PA efficiency plays a crucial role since improving it would lead to an increase in battery life and decrease in heat dissipation. Component integration is another vital characteristic. That is because today's phone must be compliant with many different standards and frequency bands, which leads to an increase in the number of required components within the FEM. Integration therefore becomes essential in keeping mobile form factors from becoming too cumbersome. Finally, PAPR is increasing with every new standard, meaning that the next generation of PAs must be able to operate efficiently at high back-off level.

The different components of the FEM are typically implemented using different technologies. While switches are typically made using RF-SOI, most LNA and PA blocs are built using SiGe and GaAs respectively. However, recent years have seen an increase in the use of RF-SOI for LNA and PA implementation. RF-SOI has the potential to address high output power levels (in the range of 30 to 36dBm), while providing high efficiency operation. This technology is therefore chosen for the implementation of the proposed PA architecture thereby opening the door to full FEM integration in the future.

This work will focus on finding an innovative design of high efficiency power amplifiers for 5G applications using combiner analysis and then validate it through circuit implementation and measurement. However, given the wide scope of such a topic, the study will focus on two load modulation PA architectures: Doherty and Outphasing. The PAs are to be used in mobile applications and as a result will be implemented using a 130nm RF-SOI process with a supply voltage of 3.4V. The target operation band is the 5G Mid Band, with a primary focus on bands n40 and n41 of the 5G NR FR1. As a result, the PAs must be designed to operate between 2.3GHz and 2.7GHz. Finally, the PA must be capable of delivering a peak output power of 33dBm and operate at an average efficiency higher than 40% at -35dBc of E-UTRA ACLR.

This PhD work is the result of a joint collaboration between the LAIR and LTCI laboratories of CEA-Leti and Télécom Paris respectively. The following manuscript is organized into five chapters as outlined below:

Chapter 1 presented the context and motivations of the thesis work by recounting evolution of modern mobile communication standards. The new challenges of the 5G standard were explored and their impact on the mobile RF front-end architecture were assessed.

Chapter 2 introduces the basics of PA operation and performance metrics. Classic operation modes are explored before moving on to high efficiency architectures such as load modulation which includes Doherty and Outphasing.

Chapter 3 focuses on load modulated power combiner design. Outphasing combiners are examined first and a new unified analysis and design methodology is presented. Next, an analysis method for Doherty combiners is proposed. The novel analysis provides a way to determine the maximum back-off power level at which Doherty operation can be achieved. Moreover, it gives the current evolution profiles required at the combiner inputs for ideal Doherty operation.

Chapter 4 focuses on the design and implementation of a two-stage Doherty PA. The designed PA is simulated and optimized using load-pull analysis. The different packaging technologies are then showcased before moving on to circuit implementation. Finally, realized DPA circuit

is measured and shown to be capable of similar performance to the current state-of-the-art PAs, thus validating the combiner analysis and design method from the previous chapter.

Chapter 5 explores the Outphasing PA architecture and proposes a design for a class-E OPA. The dual input OEPA is then analysed from a system perspective in an effort to integrate the digital predistortion bloc (DPD) directly into the OPA. A model-based DPD architecture is then formalized. Efforts were also made to create a PA behavioural model to be used in the DPD architecture.

# **Chapter 2. Power Amplifier Basics**

| 1 RF Power Amplifiers |      |                              | 13 |

|-----------------------|------|------------------------------|----|

|                       | 1.1  | Output Power                 | 13 |

|                       | 1.2  | Efficiency                   |    |

|                       | 1.3  | Gain                         | 14 |

|                       | 1.4  | Linearity                    |    |

|                       | 1.5  | Bandwidth                    |    |

| 2                     | PA ( | Operation                    | 18 |

|                       | 2.1  | Linear Class PAs             | 20 |

|                       | 2.2  | Class-E PA                   |    |

|                       | 2.3  | Back-Off Operation           | 27 |

| 3                     | Load | d Modulated PA Architectures | 30 |

|                       | 3.1  | Outphasing PA Architecture   | 32 |

|                       | 3.2  | Doherty PA Architecture      |    |

| 4                     | Cone | clusion                      |    |

|                       |      |                              |    |

ower amplifiers (PA) have the most impact on the mobile front-end module (FEM) since they dissipate the most power and as a result are responsible for most of the heating issues. In order to better understand the challenges and compromises required for PA design, this chapter introduces the main evaluation criteria used to benchmark and compare PA performance.

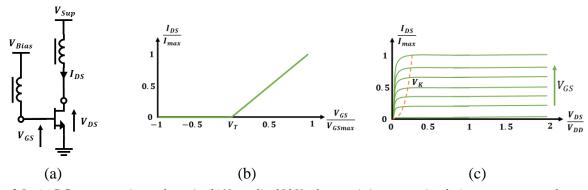

The basics of PA operation are then explained starting with transistor characterization and sizing. Next, traditional linear classes are analysed, followed by the switch-mode class-E.

Finally, load modulation architectures are introduced as a solution to enhance the PA efficiency at back-off power levels. Outphasing and Doherty PA architectures are briefly discussed and shown to be good candidates for LTE and 5G applications.

### 1 RF Power Amplifiers

When it comes to RF power amplifiers (PA), there are five main performance indicators:

- Output power

- Efficiency

- Gain

- Linearity

- Bandwidth

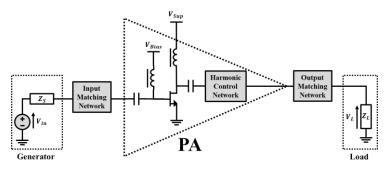

The schematic in Figure 2.1 shows a generic, simplified power amplifier circuit.

Figure 2.1 – Generic power amplifier schematic with power and impedance representation.

The power provided by the generator is referred to as the available source power  $P_{avs}$ . Maximum power transfer refers to the case where all of the available power is delivered to the PA, i.e.  $P_{in} = P_{avs}$ . This occurs when the impedances  $\mathbf{Z}_{s}$  and  $\mathbf{Z}_{in}$  are conjugately matched  $(\mathbf{Z}_{s} = \mathbf{Z}_{in}^{*})$ . DC power  $(P_{DC})$  is pulled from the supply voltage source  $(V_{sup})$  and converted into RF output power  $(P_{out})$ . A portion of the pulled DC power, is lost through heat dissipation within the PA  $(P_{diss})$ .

### 1.1 Output Power

Maximum power transfer from the PA output to the load is achieved when  $Z_L = Z_{out}^*$  leading to  $P_{out} = P_L$ . The load power  $P_L$  can be calculated through:

$$P_L = \frac{1}{2} \cdot |\mathbf{V}_L|^2 \cdot \Re\left[\frac{1}{\mathbf{Z}_L}\right] \tag{2.1}$$

Using the power conservation principle, the output power can be expressed as:

$$P_{out} = P_{in} + P_{DC} - P_{diss} (2.2)$$

#### 1.2 Efficiency

The efficiency of PA can be assessed using different metrics. The first is the drain efficiency defined as the DC-to-RF conversion ratio between the output power and the DC power. It can be calculated using (2.3).

$$DE = \eta = \frac{P_{out}}{P_{DC}} \tag{2.3}$$

The second efficiency indicator is the power added efficiency (PAE), expressed in (2.4) below.

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{2.4}$$

#### 1.3 Gain

PA gain can be calculated in two different ways. The power gain  $G_p$  is the ratio between the output and input powers as shown in (2.5).