# High-level synthesis (HLS) on FPGA for inverse problems: application to tomography and radioastronomy

Daouda Diakité

#### ▶ To cite this version:

Daouda Diakité. High-level synthesis (HLS) on FPGA for inverse problems: application to tomography and radioastronomy. Hardware Architecture [cs.AR]. Université Paris-Saclay, 2022. English. NNT: 2022UPASG080. tel-03924606

### HAL Id: tel-03924606 https://theses.hal.science/tel-03924606v1

Submitted on 5 Jan 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### High-Level Synthesis (HLS) on FPGA for Inverse Problems: application to tomography and radioastronomy

Synthèse de haut niveau sur FPGA pour problèmes inverses: application à la tomographie et à la radioastronomie

Thèse de doctorat de l'Université Paris-Saclay

École doctorale n° 580. SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION (STIC) Spécialité de doctorat: Sciences du traitement du signal et des images Graduate School: Informatique et sciences du numérique. Référent: Faculté des sciences d'Orsay

Thèse préparée dans l'unité de recherche Laboratoire des signaux et systèmes (Université Paris-Saclay, CNRS, CentraleSupélec), sous la direction de Nicolas GAC, Maître de conférences

Thèse soutenue à Paris-Saclay, le 15 Décembre 2022, par

#### Daouda DIAKITE

#### **Composition du jury:**

Membres du jury avec voix délibérative

Frédéric CHAMPAGNAT

Maître de recherche 2, ONERA

**Emmanuel CASSEAU**

Professeur, Université de Rennes 1

Florent DE DINECHIN

Professeur, INSA Lyon Mickaël DARDAILLON

Maître de conférences, INSA Rennes

Virginie FRESSE

Maîtresse de conférences, Université Jean Monnet

Président

Rapporteur & Examinateur

Rapporteur & Examinateur

Examinateur

Examinatrice

#### **ÉCOLE DOCTORALE**

Sciences et technologies de l'information et de la communication (STIC)

**Titre:** Synthèse de haut niveau sur FPGA pour problèmes inverses: application à la tomographie et à la radioastronomie

Mots clés: Adéquation Algorithme Architecture, FPGA, Synthèse de Haut Niveau, Problème Inverse, Radioastronomie, Tomographie.

Résumé: Le besoin croissant de puissance de calcul imposé par la complexité des algorithmes de traitement et la taille des problèmes nécessite l'utilisation d'accélérateurs matériels pour répondre aux contraintes de temps et d'énergie. Les architectures FPGA sont connues pour être parmi les plateformes les plus économes en énergie, notamment pour les systèmes embarqués à travers les langages de description matérielle. L'apparition des nouveaux outils de synthèse de haut niveau a été un facteur majeur dans la prise en compte des FPGAs pour les applications complexes, comme c'est le cas avec les processeurs manycores. Les outils de synthèse de haut niveau génèrent une conception de description matérielle à partir de langages de haut niveau tels que C, C++ ou OpenCL. Les derniers FPGAs sont équipés de plusieurs unités de calcul à virgule flottante capables de répondre aux exigences de précision d'un large éventail d'applications. Cependant, l'exploitation du plein potentiel de ces ar-

chitectures a toujours été une préoccupation majeure. Cette thèse vise à explorer les méthodologies d'accélération des algorithmes de problèmes inverses mal posés sur les architectures FPGA grâce à de nouveaux outils de synthèse de haut niveau appliqués à la reconstruction tomographique et à la radioastronomie. En effet, de nombreux algorithmes pour ces applications sont limités par la mémoire. Une architecture sur-mesure dérivée d'une méthodologie d'adéquation algorithme-architecture a été proposée pour surmonter le goulot d'étranglement de la mémoire. Nous avons appliqué cette méthodologie à l'opérateur de rétroprojection 3D dans le contexte de la reconstruction itérative. L'architecture du rétroprojecteur 3D tire parti d'une stratégie d'accès à la mémoire pour atteindre un débit de calcul élevé. Ensuite, nous prenons en compte la parallélisation de l'algorithme d'optimisation complet sur FPGA. Nous discutons également de la place des FPGAs en radioastronomie, notamment pour le système d'imagerie du pipeline SKA.

**Title:** High-Level Synthesis (HLS) on FPGA for Inverse Problems: application to Tomography and Radioastronomy

**Keywords:** Algorithm Architecture Co-design, FPGA, High-Level Synthesis (HLS), Inverse Problem, Radioastronomy, Tomography.

Abstract: The increasing need for computing power imposed by the complexity of processing algorithms and the size of problems requires using hardware accelerators to meet time and energy constraints. FPGA architectures are known to be among the most power-efficient platforms, especially for embedded systems using hardware description languages. The appearance of the new high-level synthesis tools has been a major factor in the consideration of FPGAs for complex applications, as is the case with the many-core processors. The highlevel synthesis tools generate a hardware description design from high-level languages such as C, C++, or OpenCL. The recent FPGAs are equipped with several floating-point computing units capable of meeting the precision requirements of a wide range of applications. However, exploiting the full potential of these architectures has always been a major concern. This thesis aims to explore methodologies for accelerating inverse problem algorithms on FPGA architectures through new high-level synthesis tools applied to tomographic reconstruction and radioastronomy. Indeed, many algorithms for these applications are memory-bound. A custom architecture derived from an algorithm-architecture codesign methodology has been proposed to overcome the memory bottleneck. We applied this methodology to the 3D back-projection operator in the context of iterative reconstruction. The 3D backprojector architecture takes advantage of a custom memory access strategy to reach a full computational throughput. Then we consider the parallelization of the complete optimization algorithm on FPGA. We also discuss the position of FPGAs in radio astronomy, particularly for the SKA pipeline imaging system.

### Acknowledgments

I would like to thank God for allowing me to go through this project with courage and commitment.

This thesis would not have been possible without several key people.

I am deeply grateful to my supervisor Nicolas Gac for his constant encouragement, support, and unfailing guidance throughout this project. I was honored to learn from his knowledge of computer architecture, parallel computing, and inverse problem algorithms. I also thank Nicolas Gac for his research interest, enthusiasm, patience, and feedback. His expertise and valuable suggestions were of significant importance in the completion of this thesis. I have been fortunate to have Nicolas Gac as my thesis supervisor.

I would like to thank the reviewers of this thesis, Emmanuel Casseau and Florent de Dinechin, for agreeing to review this manuscript and for their time, effort, and valuable comments. I also like to thank the examiners of the doctoral committee, Frédéric Champagnat, Mickaël Dardaillon, and Virginie Fresse, for evaluating my work and the insightful discussion on my research topic.

I would like to thank Thomas Rodet for having accepted to be my thesis supervisor at the beginning before Nicolas Gac got his HDR. I also thank him for his valuable insights and for being part of the doctoral committee.

I would like to thank Daniel Charlet for giving me access to one of their FPGA boards at the IJCLab and his interest in promoting hardware acceleration through high-level synthesis tools. I also thank Intel Corporation for granting me access to their DevCloud to use Stratix 10 PAC with the oneAPI framework.

I sincerely thank my dear colleagues and friends Nicolas, Marine, Ralph, Mickaël, Pierre, Agathe, Stefano, Dan, Sunrise, Eduardo, Jean-Batiste, and Josee, for the warm environment and dynamics within the team that we have maintained despite the pandemic. I am grateful for the coffee, lunch breaks, and interesting discussions. Furthermore, I thank François Orieux, Charles Soussen, Patrice Brault, and the GPI team.

To Dah, Ousmane (N'diaye), Ousmane (Dao), Bocar, and Ibrahim (thanks for the re-reading), I want to thank you for all your support and encouragement throughout these years of the thesis. Last but not least, I would like to express my profound gratitude to all my family, especially my parents, siblings, and uncles, for their patience and constant support. The successful completion of this thesis would certainly not have been possible without them.

# Contents

| Contents |       |         |                                 |     |  |  |

|----------|-------|---------|---------------------------------|-----|--|--|

| Li       | st of | Figur   | es                              | vi  |  |  |

| Li       | st of | Table   | ${f s}$                         | vii |  |  |

| In       | trod  | uction  |                                 | 1   |  |  |

| 1        | Hig   | h-Leve  | el Synthesis for FPGAs          | 5   |  |  |

|          | 1.1   | Comp    | outer architectures             | 6   |  |  |

|          |       | 1.1.1   | General-purpose processors      | 7   |  |  |

|          |       | 1.1.2   | Specific-purpose co-processors  | 7   |  |  |

|          |       | 1.1.3   | Specific circuits               | 8   |  |  |

|          | 1.2   | High-   | Level Synthesis                 | 11  |  |  |

|          |       | 1.2.1   | HLS history                     | 12  |  |  |

|          |       | 1.2.2   | High-Level Synthesis Tools      | 13  |  |  |

|          | 1.3   | Intel 1 | HLS Tools                       | 15  |  |  |

|          |       | 1.3.1   | Intel HLS Compiler              | 15  |  |  |

|          |       | 1.3.2   | Intel FPGA SDK for OpenCL       | 15  |  |  |

|          |       | 1.3.3   | Intel oneAPI                    | 18  |  |  |

|          | 1.4   | Open    | CL Optimizations                | 19  |  |  |

|          |       | 1.4.1   | Compiler-aided Optimizations    | 19  |  |  |

|          |       | 1.4.2   | NDR kernels                     | 20  |  |  |

|          |       | 1.4.3   | Single Work-Item (SWI) kernels  | 21  |  |  |

|          |       | 1.4.4   | Loop optimizations              | 21  |  |  |

|          | 1.5   | Concl   | usion                           | 27  |  |  |

| 2        | SK    | A, an I | HPC use-case for FPGA-based HLS | 29  |  |  |

|          | 2.1   | Squar   | e Kilometre Array (SKA) imaging | 30  |  |  |

|          |       | 2.1.1   | Iterative algorithms            | 30  |  |  |

|          |       | 2.1.2   | SKA imaging                     | 31  |  |  |

|          | 2.2   | Decon   | nvolution                       | 33  |  |  |

ii Contents

|   |     | 2.2.1  | Least square deconvolution                  | 33 |

|---|-----|--------|---------------------------------------------|----|

|   |     | 2.2.2  | CLEAN deconvolution                         | 35 |

|   |     | 2.2.3  | FPGA-based CLEAN using OpenCL               | 36 |

|   | 2.3 | Conclu | usion                                       | 40 |

| 3 | X-r | ay Cor | nputed Tomography Acceleration              | 41 |

|   | 3.1 |        | graphy reconstruction algorithms            | 42 |

|   |     | 3.1.1  | Image reconstruction                        | 42 |

|   |     | 3.1.2  | Projection/back-projection pairs            | 43 |

|   | 3.2 | Accele | eration of CT algorithms                    | 50 |

|   |     | 3.2.1  | Acceleration on parallel architectures      | 51 |

|   |     | 3.2.2  | Acceleration on specific circuits           | 52 |

|   | 3.3 | FPGA   | a implementations with OpenCL HLS           | 54 |

|   |     | 3.3.1  | Siddon                                      | 54 |

|   |     | 3.3.2  | Joseph                                      | 56 |

|   |     | 3.3.3  | Back-projection                             | 57 |

|   | 3.4 | Perfor | mance evaluation                            | 58 |

|   |     | 3.4.1  | Experiment setup                            | 58 |

|   |     | 3.4.2  | Results                                     | 60 |

|   | 3.5 | Concl  | usion                                       | 63 |

| 4 | Rea | ching  | FPGA Computational Peak Performance         | 65 |

| • | 4.1 |        | ne model                                    | 66 |

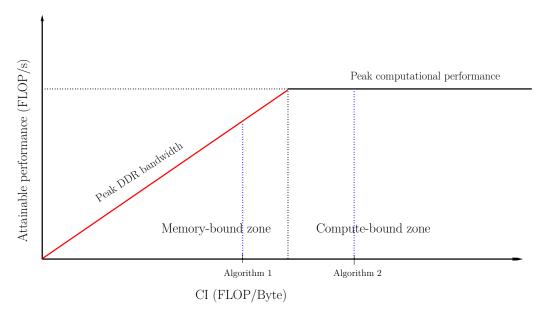

|   | 1.1 | 4.1.1  | Basic roofline model                        | 66 |

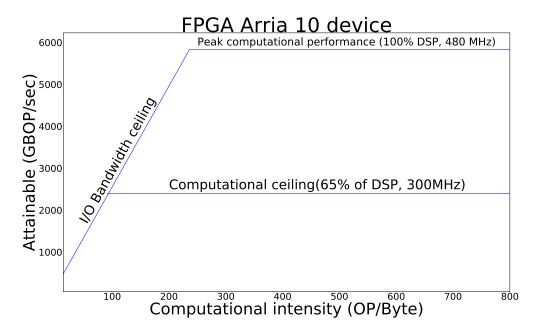

|   |     | 4.1.2  | Roofline model for FPGAs                    | 67 |

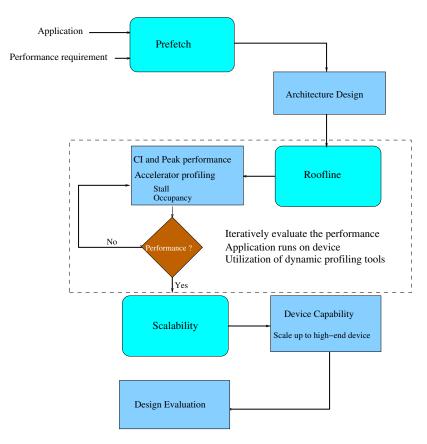

|   | 4.2 | Adopt  | sed Methodology                             | 69 |

|   |     | 4.2.1  | Prefetch                                    | 70 |

|   |     | 4.2.2  | Roofline                                    | 70 |

|   |     | 4.2.3  | Scalability                                 | 71 |

|   | 4.3 |        | aced optimizations                          | 73 |

|   |     | 4.3.1  | Reduce access to local memory               | 73 |

|   |     | 4.3.2  | Shift register                              | 74 |

|   |     | 4.3.3  | Conditional branches balancing              | 75 |

|   |     | 4.3.4  | Initiation Interval and operating frequency | 75 |

|   |     | 4.3.5  | Arithmetic operations overhead              | 76 |

|   | 4.4 | Prefet | ch benefits illustrated for 2D Convolution  | 76 |

|   |     | 4.4.1  | 2D Convolution                              | 76 |

|   |     | 4.4.2  | OpenCL-based convolution on FPGA            | 77 |

|   |     | 4.4.3  | Performance evaluation                      | 79 |

|   | 4.5 | Concl  |                                             | 81 |

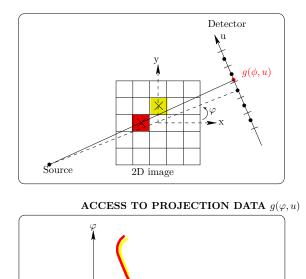

| 5  | BP-    | -Prefet  | tch Architecture for CT Reconstruction       | 83    |

|----|--------|----------|----------------------------------------------|-------|

|    | 5.1    | BP-P     | refetch design                               | . 84  |

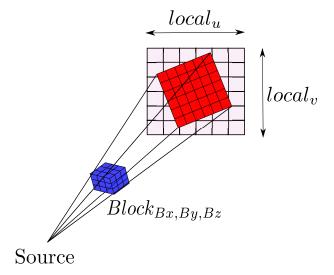

|    |        | 5.1.1    | Back-projection algorithm                    | . 84  |

|    |        | 5.1.2    | Memory access strategy                       | . 85  |

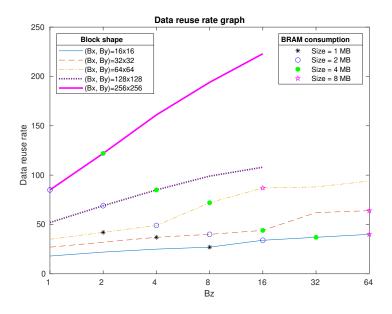

|    |        | 5.1.3    | Reconstruction by voxel blocks               | . 86  |

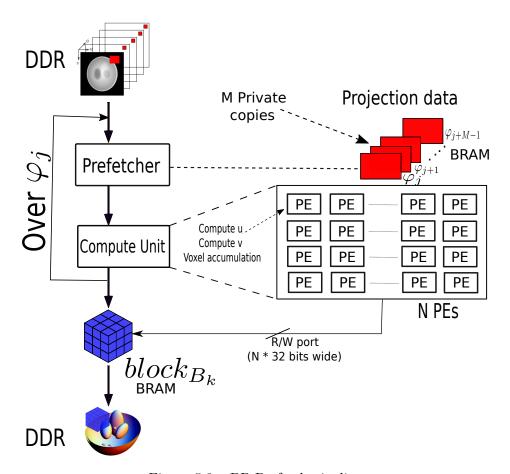

|    |        | 5.1.4    | BP-Prefetch architecture                     | . 87  |

|    | 5.2    | Archit   | $\operatorname{tecture\ tuning}$             | 90    |

|    |        | 5.2.1    | Offline Analysis                             | 90    |

|    |        | 5.2.2    | Design on Arria 10                           | . 92  |

|    |        | 5.2.3    | Replication potential on Stratix 10          | . 93  |

|    | 5.3    | Result   | $\operatorname{ts}$                          | 94    |

|    |        | 5.3.1    | Design evaluation                            | . 95  |

|    |        | 5.3.2    | Image Accuracy                               | . 99  |

|    | 5.4    | Comp     | arison and discussion                        | 101   |

|    |        | 5.4.1    | Implementation on general-purpose processors | . 101 |

|    |        | 5.4.2    | Performance comparison                       | 102   |

|    |        | 5.4.3    | Resource and power analysis                  | 104   |

|    | 5.5    | Tomo     | graphy oneAPI                                | 105   |

|    |        | 5.5.1    | Design                                       | 105   |

|    |        | 5.5.2    | Performance analysis and comparison          | 106   |

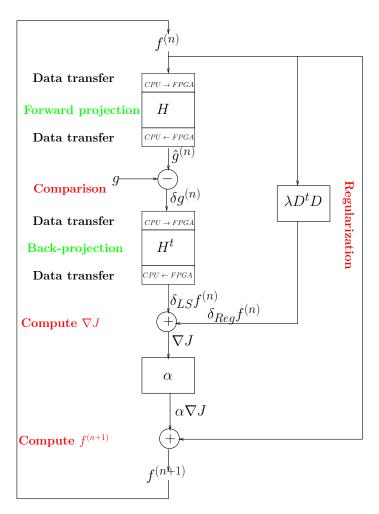

|    | 5.6    | Iterati  | ive reconstruction algorithm                 | 107   |

|    |        | 5.6.1    | TomoGPI                                      | 108   |

|    |        | 5.6.2    | CPU-FPGA strategy                            | . 108 |

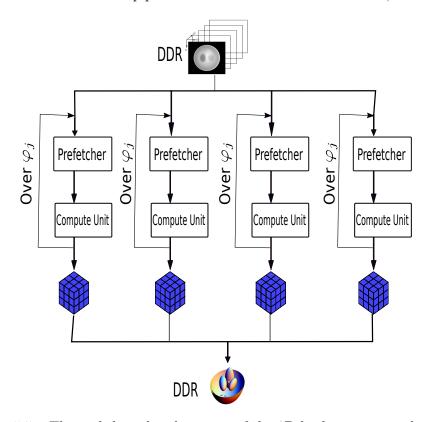

|    |        | 5.6.3    | Full FPGA strategy                           | 110   |

|    | 5.7    | Concl    | ${f usion}$                                  | . 111 |

| 6  | Cor    | ıclusio  | n and Perspectives                           | 113   |

|    | 6.1    | Concl    | usion                                        | 113   |

|    | 6.2    | Perspe   | ectives                                      | 114   |

| Sc | cienti | ific cor | ntributions                                  | 117   |

| R  | ésum   | ié en F  | Prançais                                     | 119   |

| Bi | ibliog | graphy   | •                                            | 123   |

# List of Figures

| 1.1 | FPGA architecture                                                     | 9  |

|-----|-----------------------------------------------------------------------|----|

| 1.2 | Stratix 10 Hyperflex core architecture from [Intel Corporation 2021c] | 11 |

| 1.3 | FPGA Design flow with HDL languages                                   | 11 |

| 1.4 | Design efficiency from [Pelcat 2016]                                  | 12 |

| 1.5 | OpenCL Memory Model                                                   | 17 |

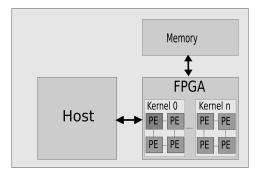

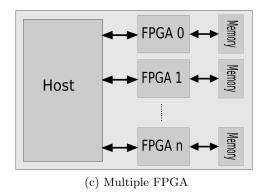

| 1.6 | Intel FPGA SDK for OpenCL platform                                    | 18 |

| 1.7 | Loop pipelining                                                       | 22 |

| 1.8 | Loop Unrolling                                                        | 23 |

| 1.9 | Loop interleaving                                                     | 26 |

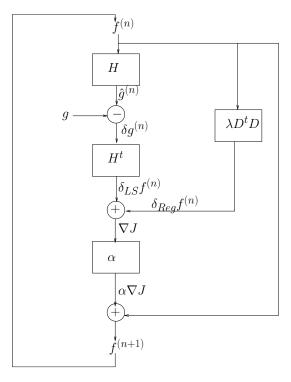

| 2.1 | Block diagram of iterative image reconstruction                       | 31 |

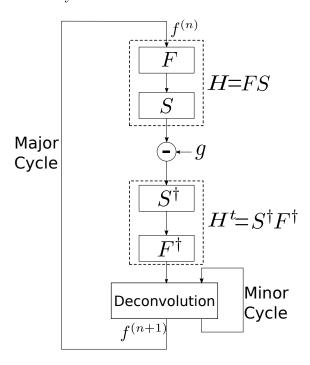

| 2.2 | Bloc diagram of radio astronomical imaging                            | 32 |

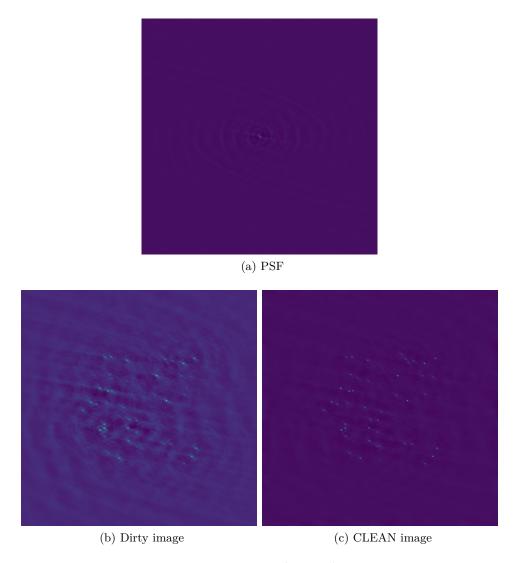

| 2.3 | Image deconvolution                                                   | 34 |

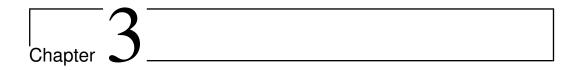

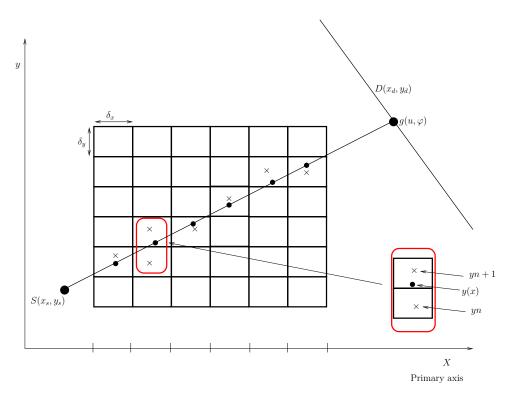

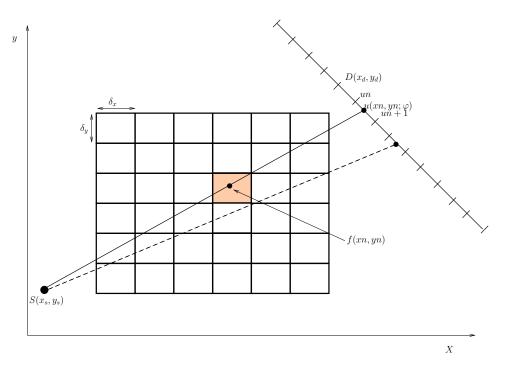

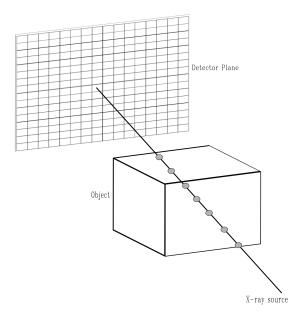

| 3.1 | X-RAY CT Projection                                                   | 43 |

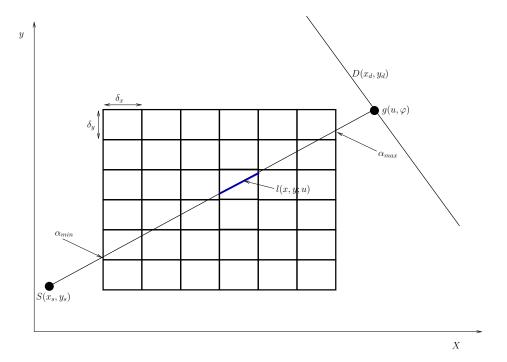

| 3.2 | 2D representation of Siddon ray-tracing method                        | 45 |

| 3.3 | 2D representation of Joseph ray-tracing method                        | 48 |

| 3.4 | Voxel-driven back-projector                                           | 50 |

| 3.5 | 3D projection memory access pattern                                   | 55 |

| 3.6 | 3D back-projector memory access pattern for reconstruction a single   |    |

|     | voxel                                                                 | 58 |

| 4.1 | Basic roofline representation with two applications: memory-bound     |    |

|     | and compute-bound examples                                            | 67 |

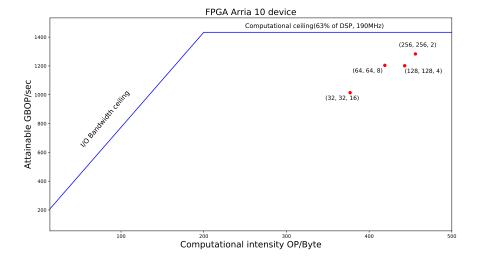

| 4.2 | Roofline representation on Intel Arria 10. The higher roof represents |    |

|     | the FPGA capacity and the second roof is the ceiling for a design     |    |

|     | using 65% of DSP running at 300 MHz                                   | 68 |

| 4.3 | Adopted methodology of acceleration on FPGA devices using HLS         |    |

|     | tools                                                                 | 69 |

| 4.4 | Design scalability on FPGA                                            | 72 |

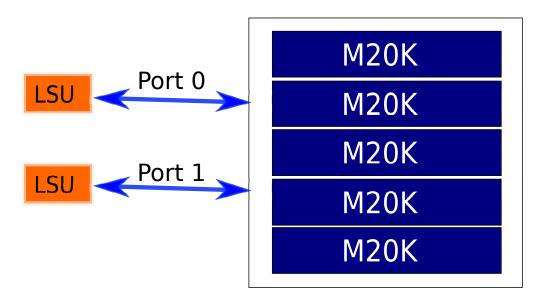

| 4.5 | The internal structure of Intel FPGA local memory                     | 74 |

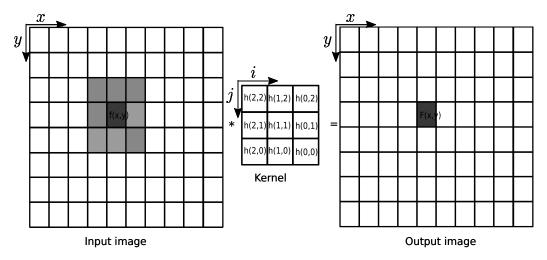

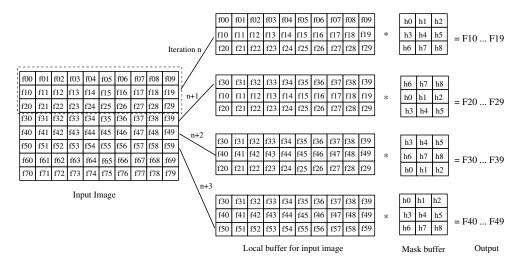

| 4.6  | 2D Convolution with a $3\times3$ mask. The '*' is the convolution operator. | 77  |

|------|-----------------------------------------------------------------------------|-----|

| 4.7  | Memory access strategy with circular shift applied to the mask. The         |     |

|      | '*' is the convolution operator                                             | 79  |

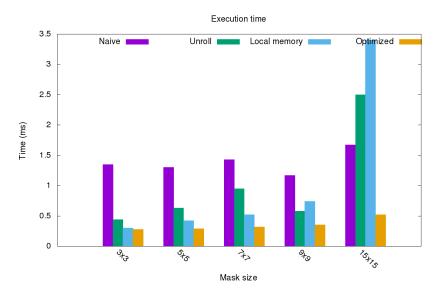

| 4.8  | OpenCL execution time of 2D convolution on Intel Stratix 10 FPGA            | 79  |

| 5.2  | Voxel block (in blue) and its projection (in red)                           | 86  |

| 5.3  | BP-Prefetch pipeline                                                        | 89  |

| 5.4  | Data reuse rate with 3 different shapes with $B_z$ variation                | 91  |

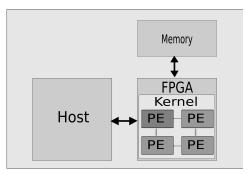

| 5.5  | The multikernel architecture of the 3D back-projection algorithm            | 94  |

| 5.6  | Roofline of BP-Prefetch with different $B_z$ on Arria 10                    | 96  |

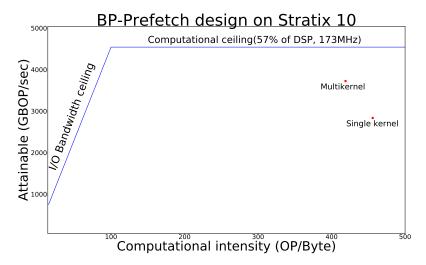

| 5.7  | Roofline of BP-Prefetch on Stratix 10                                       | 98  |

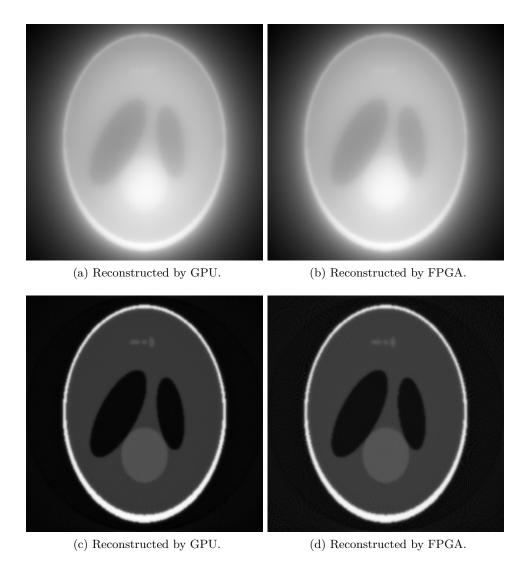

| 5.8  | Shepp-Logan phantom reconstructed image slice 128. Fig. 5.8a-5.8b:          |     |

|      | The reconstructed image using single back-projection. Fig. 5.8c-5.8d:       |     |

|      | The reconstructed image after the full MBIR algorithm                       | 99  |

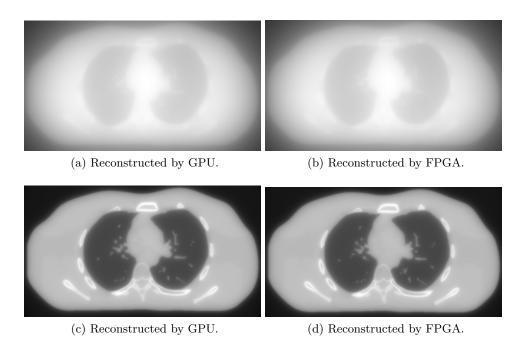

| 5.9  | XCAT phantoms reconstructed image slice 128. Fig. 5.9a-5.9b: The            |     |

|      | reconstructed image using single back-projection. Fig. 5.9c-5.9d:           |     |

|      | The reconstructed image after the full MBIR algorithm                       | 100 |

| 5.10 | Block diagram of iterative image reconstruction using CPU and FPGA.         |     |

|      | Data transfers (black), blocks run on CPU (red) and FPGA (green)            |     |

|      | are highlighted                                                             | 109 |

# List of Tables

| 1.1 | An overview of HLS tools                                            | 13  |

|-----|---------------------------------------------------------------------|-----|

| 2.1 | The CLEAN algorithm parameters                                      | 39  |

| 2.2 | Performances of the Högbom CLEAN deconvolution on Intel Stratix     |     |

|     | 10 device                                                           | 39  |

| 3.1 | Platforms used in the experiment                                    | 59  |

| 3.2 | Performances of forward and back-projection operators on Arria 10 . | 60  |

| 3.3 | Performance comparison with other works                             | 62  |

| 4.1 | Memory access latencies on Intel Arria 10                           | 73  |

| 5.1 | Static analysis of CI for different blocks                          | 92  |

| 5.2 | Block size variation effect on the performance on Arria 10          | 95  |

| 5.3 | Single kernel versus multikernel on Stratix 10                      | 97  |

| 5.4 | Image quality evaluation between GPU and FPGA reconstructed         |     |

|     | images on different datasets                                        | 100 |

| 5.5 | Performance comparison of our work and other works                  | 102 |

| 5.6 | FPGA resources consumption                                          | 104 |

| 5.7 | Design energy efficiency                                            | 105 |

| 5.8 | Comparison between one API and OpenCL on Arria 10                   | 107 |

# Acronyms

| $\mathbf{ALM}$   | Adaptive Logic Module9                    |

|------------------|-------------------------------------------|

| $\mathbf{AOC}$   | Altera Offline Compiler                   |

| ASICs            | Application Specific Integrated Circuits9 |

| BSP              | Board Support Package                     |

| BRAM             | Block RAM                                 |

| BSP              | Board Support Package                     |

| $\mathbf{CI}$    | Computational Intensity                   |

| $\mathbf{CT}$    | Computed Tomography                       |

| $\mathbf{CPU}$   | Central Processing Unit                   |

| $\mathbf{CUDA}$  | Common Unified Device Architecure         |

| $\mathbf{CLB}$   | Configurable Logic Blocks                 |

| $\mathbf{CC}$    | Correlation Coefficient                   |

| $\mathbf{CP}$    | Computational Performance                 |

| $\mathbf{DSL}$   | Domain-Specific Language                  |

| $\mathbf{DSP}$   | Digital Signal Processing                 |

| DD               | Distance-Driven                           |

| $\mathbf{FPGAs}$ | Field Programmable Gate Arrays            |

| FOD              | Focus-Object Distance                     |

| $\mathbf{FDD}$   | Focus-Detector Distance                   |

| $\mathbf{FBP}$   | Filtered Back-Projection                  |

| GPGPU            | J General Purpose GPU                     |

| $\mathbf{GPUs}$  | Graphical Processing Units                |

| GUPS             | Giga Updates Per Second                   |

| GBOPS            | Giga Bytes Operations Per Second          |

List of Tables

| $\mathbf{GPL}$  | General Purpose Language                    |

|-----------------|---------------------------------------------|

| HDL             | ${\bf Hardware\ Description\ Languages$     |

| HLS             | High-Level Synthesis                        |

| $\mathbf{HLL}$  | High-Level programming Language             |

| HPC             | High-Performance Computing                  |

| HBM2            | High-Bandwidth Memory 2                     |

| II              | Initiation Interval                         |

| IR              | Intermediate Representation                 |

| JIT             | Just-In-Time                                |

| $\mathbf{LLVM}$ | Low-Level Virtual Machine                   |

| LSU             | Load Store Units87                          |

| $\mathbf{LUT}$  | Look-up Tables                              |

| MBIR            | Model-Based Iterative Reconstruction        |

| MPPA            | Massively Parallel Processor Array          |

| NDR             | NDRange                                     |

| NRMSI           | E Normalized Root Mean Squared Error        |

| OpenCl          | L Open Computing Language                   |

| $\mathbf{PE}$   | Processing Element                          |

| $\mathbf{PET}$  | Positron Emission Tomography53              |

| PSF             | Point Spread Function                       |

| $\mathbf{QoR}$  | Quality of Results11                        |

| RTL             | Register Transfer Level                     |

| SWI             | Single Work-Item                            |

| SDP             | Science Data Processor                      |

| $\mathbf{SKA}$  | Square Kilometre Array                      |

| $\mathbf{SNR}$  | Signal to Noise Ratio                       |

| $\mathbf{SM}$   | Streaming Multiprocessors                   |

| $\mathbf{SDK}$  | Software Development Kit14                  |

| $\mathbf{SF}$   | Separable Footprint                         |

| SFTR            | Separable Footprint Trapezoidal-Rectangular |

| SFTT            | Separable Footprint Trapezoidal-Trapezoidal |

| $\mathbf{TET}$  | Transmission Electron Tomography53          |

| $\mathbf{UQI}$  | Universal Quality Index                     |

### Introduction

The increasing need for computing power imposed by the complexity of processing algorithms and the size of these problems requires the use of hardware accelerators to meet time and energy constraints. However, as a consequence of the decline of Moore's Law, it is impossible to reduce the processing size of transistors at a certain limit. Currently hardware accelerators such as GPUs or FPGAs are being use to increase performance. For example, since the appearance of CUDA language, GPUs have been the preferred architecture over the past decade for HPC applications because of their massively parallel computing pattern. At the same time, FPGAs have recently experienced multiple technological advances and can be considered an alternative for computationally-intensive applications. These advances concern both emergence of more mature high-level synthesis tools, and the technology and number of recent DSPs present in FPGAs capable of performing floating point operations as required in HPC applications.

FPGAs have been used for several decades and have proven themselves in the field of embedded systems, particularly for their energy efficiency and meeting realtime constraints of the applications. When FPGAs are considered for intensive computing, these same advantages should be preserved while meeting the computing needs of these applications. In the context of this thesis, the considered HPC applications are computed tomography and radioastronomy. Indeed, for a long time FPGA technology has been only reserved for hardware designers using hardware description languages. This level of abstraction requires a strong knowledge of FPGA architectures and their programming tools. Also, FPGA development is very time-consuming using these languages compared to general-purpose processor programming models. The necessity to reduce the development time and alleviate the complexity of FPGA programming has motivated the emergence of high-level synthesis tools. The main vendors of FPGAs have contributed considerably by proposing more mature tools that allow the use of FPGAs through high-level languages. Thanks to high-level synthesis tools, the development time of FPGAs has been considerably reduced and made accessible to a wide audience of developers and complex applications.

2 List of Tables

#### Motivation

Reducing the processing time for large-scale problems is a topic of interest in highperformance computing and image processing domains. In computed tomography, it is essential to reduce the radiation dose for the patient during the acquisition without affecting the image quality. Iterative reconstruction methods are used to reconstruct the image from this low-dose tomography. According to the literature, iterative reconstruction algorithms take several minutes to several hours. For instance, the computation time of the Expectation Maximization (EM) algorithm for 500 projections of  $736 \times 64$  pixels of projection data in the CPU is 1.52 hours [Chen 2012a]. An important axis to accelerate these computations relies on the exploration and the use of hardware accelerators. GPUs have been the preferred architecture for the past decade due to their massively parallel computing pattern. Our objective is to emphasize the position of FPGAs for compute-intensive applications since the emergence of high-level synthesis tools. FPGA architectures can be an alternative to the GPU thanks to their cycle accuracy and power efficiency. However, systematic use of software languages on FPGAs does not guarantee good performance. A specific focus is then required to perform FPGA-specific optimizations in order to assist the high-level compiler in synthesizing an efficient pipeline. User expertise is essential to exploit FPGAs' full potential and make them competitive with GPUs for HPC acceleration. Indeed, despite recent advances in FPGA technology, this architecture is still behind GPU architecture in a wide range of applications, mainly because of the substantial computing power of GPUs as well as their high global memory bandwidth.

Radioastronomical imaging algorithms could also benefit from the high energy-efficiency of FPGA devices through HLS tools. The supercomputer for the Square Kilometre Array (SKA) radio telescope should use hardware accelerators to meet the different constraints of this project. SKA is the largest radio telescope in the world, using streaming data to generate multidimensional images of the sky at 7.2 Terabit/s without any storage capabilities. The Science Data Processor (SDP) generates the sky images in the SKA pipeline, and this SDP is highly energy-constrained. Currently, GPUs are the candidate with the most potential to meet the computing needs of SDP. However, these many-core GPUs are very power-hungry in order to meet the energy consumption budget. Another alternative must be explored and since the emergence of the new high-level synthesis tools, FPGAs have proven to be a power-efficient platform. Thus, FPGAs could be a more practical alternative for the SKA SDP system.

#### Thesis Outline

This thesis aims to explore methodologies for accelerating inverse problem algorithms on FPGAs through new high-level synthesis tools with an application to the field of tomographic reconstruction and radioastronomy. The main contribution of

List of Tables 3

this dissertation is the design of a custom architecture of the 3D back-projection algorithm. This architecture takes advantage of a specific methodology based on offline memory access analysis to alleviate the memory bottleneck.

The manuscript is organized as follows:

- Chapter 1 introduces computer architectures and the acceleration requirement for compute-intensive applications. The position of FPGAs is discussed as an accelerator and the evolution of HLS tools for their programming. Then, particular attention is paid to Intel's HLS tools used in this study.

- Chapter 2 presents the imaging system of the SKA pipeline and the iterative algorithms used to reconstruct the sky image. The chapter uses the deconvolution use-case to illustrate the design of the algorithm on FPGA using OpenCL HLS tool.

- Chapter 3 highlights the tomography reconstruction problem as an inverse problem. We present the operators used in iterative reconstruction algorithms and the related work about their acceleration on CPU, GPU, FPGA. The first hardware acceleration results of the projector and back-projector operators are also discussed in this chapter.

- Chapter 4 presents our adopted methodology for algorithm-architecture codesign in order to accelerate computationally-intensive applications to overcome the memory bottleneck. We also present several advanced FPGA-aware optimizations using high-level tools to fully harness the device. Then, the adopted methodology is applied to a simple use-case of 2D convolution in order to illustrate the prefetching impact on the design performance using OpenCL HLS.

- Chapter 5 proposes a custom architecture of the 3D back-projection operator used in iterative image reconstruction. The memory access strategy that increased the algorithm's data reuse rate is presented. The roofline model is used to profile and guide the optimization steps of the design, and the scalability strategy to higher-end FPGA is discussed. This chapter also compares the OpenCL and oneAPI tools for the back-projection use case. Furthermore, this Chapter discusses the different strategies for porting this iterative algorithm to the FPGA board. The gradient descent algorithm is considered in the context of CT reconstruction.

## High-Level Synthesis for FPGAs

| Contents                   |                                |           |

|----------------------------|--------------------------------|-----------|

| 1.1 Computer architectures |                                | 6         |

| 1.1.1                      | General-purpose processors     | 7         |

| 1.1.2                      | Specific-purpose co-processors | 7         |

| 1.1.3                      | Specific circuits              | 8         |

| 1.2 High-Level Synthesis   |                                | 11        |

| 1.2.1                      | HLS history                    | 12        |

| 1.2.2                      | High-Level Synthesis Tools     | 13        |

| 1.3 Intel HLS Tools        |                                | <b>15</b> |

| 1.3.1                      | Intel HLS Compiler             | 15        |

| 1.3.2                      | Intel FPGA SDK for OpenCL      | 15        |

| 1.3.3                      | Intel oneAPI                   | 18        |

| 1.4 OpenCL Optimizations   |                                | 19        |

| 1.4.1                      | Compiler-aided Optimizations   | 19        |

| 1.4.2                      | NDR kernels                    | 20        |

| 1.4.3                      | Single Work-Item (SWI) kernels | 21        |

| 1.4.4                      | Loop optimizations             | 21        |

| 1.5 Conclusion             |                                | <b>27</b> |

Processor architectures have undergone enormous advances over time to meet large-scale applications' increasing demands for computing power. These advances in internal processor architectures have improved the raw performance of these machines over many years by adding more transistors while decreasing process sizes, as predicted by *Moore's Law*. However, Moore's Law is reaching its end with increasing technological complexity. Thus, increasing processor performance by increasing chip density was no longer a viable solution. Other strategies have been employed

to fill the gap created by stagnant performance. These strategies included increasing the operating frequencies and expressing parallelism (ILP, pipelining, ...) of general-purpose processors. However, improving internal architectures with out-of-order execution or deeper pipelines has become counterproductive. In addition, increasing the clock frequency has come up against issues with power dissipation in the circuits. The multiplication of computing cores within a single processor has been adopted to address the concern of energy dissipation caused by increased frequency. Multi-core and manycore processors, e.g., GPUs, were thus developed. In addition, other types of architectures continued to evolve in parallel, such as FPGAs and ASICs, both used for custom application-based design. The most significant difference between the two is that ASICs are not reprogrammable, and their development cost is higher than FPGAs. The increasing maturity of high-level synthesis tools for FPGAs and ASICs and the evolution of their internal architectures with more computational resources make them potential hardware accelerators for large-scale applications.

However, the multiplication of computational units in general-purpose processors and specific circuits has added a layer of complexity to these circuits' programming to exploit better the computational potential offered by these architectures. The programming paradigm is not the same for these distinctive processors. Some will excel better in applications with more control than computation, while others do better with the expression of parallelism on extensive data. For example, FPGAs are well known for their efficiency in executing control- or data-flow applications in a well-elaborated pipeline. Thus, the choice of architecture should depend on the underlying application in order to perform an algorithm-architecture co-design approach to leverage better the full computational capacity offered by the device.

This chapter will present an overview of the most commonly used computing accelerators, from general-purpose processors to specific circuits, before focusing on FPGAs, which are at the heart of this thesis work. We will then present the high-level synthesis tools on FPGAs by presenting their evolution and the different tools developed since the emergence of this technology. The FPGA devices used in our work come from Intel corporation. Therefore, we will discuss the Intel-specific tools and detail those used during our experiments. The OpenCL tool will be presented in detail, starting with its programming model and ending with the various basic optimizations offered by this tool to take advantage of the FPGAs.

### 1.1 Computer architectures

The requirement of sustainable computing power relies on the constant growth of high-performance application complexity. The development of hardware architecture has been evolving to address compute-intensive problems from single-core processors to parallel processors. The well-known Moore's Law [Moore 1965] and Dennard scaling [Dennard 1974] have driven the advances in computer technology regarding performance and energy efficiency.

#### 1.1.1 General-purpose processors

#### 1.1.1.1 CPU

Central Processing Unit (CPU) is the reference architecture in computer systems. The first generation of CPUs was presented with sequential architecture and executed software as a set of instructions. This architecture is well established for its versatility and ease of use through software programming languages. Therefore, to push the limit of Moore's Law, the operating frequency was increased, and multiple enhancements were provided to the architecture, such as pipelining, out-of-order execution, speculative execution, etc. Multi-core microprocessors have emerged to improve performance and overcome the limits of architectural improvement to CPUs. The multi-core processors use two or more compute cores to execute a set of instructions. These multi-core processors delivered better performance than single-core ones thanks to the exploitation of all the compute cores via parallel programming languages. The versatility of CPUs lies in the management of control in their architecture, which leaves less room for calculations. This makes CPUs dominant in multitasking but hard for them to excel in compute-intensive applications.

#### 1.1.2 Specific-purpose co-processors

Hardware accelerators are used as co-processors in order to meet the need for computing power. These accelerators offer high computing power compared to traditional CPUs for a large number of applications. We will briefly look at these hardware accelerators in this section.

#### 1.1.2.1 GPU

Used for 3D rendering since the 1990s, Graphical Processing Units (GPUs) architectures have been democratized as General Purpose GPU (GPGPU) and are now adopted as the most privileged architecture for compute-intensive applications in various domains. Their massively parallel computing model using thousands of cores explains this preference [Xu 2007]. Indeed, GPUs are considered as *many-core* processors and can perform thousands of computations simultaneously. The compute cores of GPUs are grouped into Streaming Multiprocessors (SM) with a reduced instruction set compared to CPU, and each core in the same SM executes the same program in parallel.

In 2006, Nvidia introduced its Common Unified Device Architecture (CUDA) API to leverage their GPU architectures as hardware accelerators through a software language based on C. GPUs are based on massive parallelism of elementary tasks called *threads*, where each thread represents a set of instruction sequences. Threads execute the same instructions for the same CUDA kernel. GPU programming model organizes threads into warps consisting of a group of 32 threads. Threads in the same warp have the same context of execution. A group of warps constitutes a block, and multiple blocks form a grid. Each block is mapped to a GPU SM during

execution.

CUDA is a proprietary framework only supported on Nvidia's GPUs. OpenCL, initiated by Apple and maintained by KHRONOS GROUP since 2008, has been released in order to provide a programming framework supported by all vendors' devices [Khronos 2009]. OpenCL enables cross-vendor portability for heterogeneous platforms and devices. The programming paradigm of OpenCL and CUDA are relatively similar. However, OpenCL is supposed to support devices other than GPU, such as CPU, DSP, or FPGA.

#### 1.1.2.2 MPPA manycore processor

The Massively Parallel Processor Array (MPPA), launched by Kalray in 2012, is an embedded manycore architecture for high performance and low power purposes. The processor consists of 16 compute clusters communicating through a Network on Chip (NoC). Each cluster comprises 16 VLIW application cores sharing the same local memory. The compute core in MPPA has a fully pipelined 32-bit VLIW processor that performs up to five instructions per cycle. The MPPA processor is connected to a host CPU using high-speed interfaces such as PCIe. Multiple programming models based on standard C/C++ are available to program the heterogeneous MPPA processor, such as OpenCL, OpenMP, POSIX, etc.

#### 1.1.2.3 Digital Signal Processor

Digital Signal Processors are specialized circuits designed to perform specific computations in digital signal processing such as Discrete Fourier Transform (DFT), Fast Fourier Transform (FFT), filtering, correlation, convolution, etc. Like traditional microprocessors, a DSP device contains several units to perform arithmetic or logical operations and on-chip memories object. DSP devices also contain multipliers and Multiply and ACcumulate (MAC) units which are required for most signal processing applications. In addition, they are also equipped with several address generators to handle separate memory spaces. While general-purpose processors are based on Von Neumann architecture, DSPs use Harvard architecture so that they can fetch data and program instructions at the same time.

#### 1.1.3 Specific circuits

Other types of hardware accelerators based on specific circuits are also used to speed up applications. These accelerators are renowned for their energy efficiency and computing performance, particularly in embedded systems and real-time systems. However, the development of these circuits is not accessible to the general public, as is the case with general-purpose and specific-purpose processors.

#### 1.1.3.1 ASIC

Application Specific Integrated Circuits (ASICs) are an integrated circuit designed for a particular application. The ASIC technology offers the best trade-off between performance and power efficiency. ASICs are not reprogrammable, and their design cycle is time-consuming. Thus, their manufacturing process is costly, making them viable only from large volumes of production.

#### 1.1.3.2 FPGA

Field Programmable Gate Arrays (FPGAs) have been developed since the mid-1980s. In contrast to general-purpose fixed architectures (CPUs and GPUs), FPGAs are reconfigurable circuits that offer designers the ability to build a custom architecture driven by the underlying application. The strength of FPGAs lies in the flexibility they offer to build an efficient pipeline architecture. This flexibility positions FPGAs as a mid-range architecture between general-purpose processors and ASICs. In addition, the energy and cyclic efficiency of FPGAs make them excellent candidates for embedded system applications with real-time constraints and a limited power budget.

#### FPGA architecture:

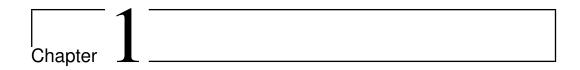

Figure 1.1 – FPGA architecture

The internal architecture of FPGAs is presented in Fig. 1.1. FPGAs are composed of several Adaptive Logic Module (ALM) (or Configurable Logic Blocks

(CLB) in Xilinx terminology), routing switch matrix, and different I/O blocks. An ALM is made of:

- Several Look-up Tables (LUT) with four to six inputs.

- Several registers

- Multiple adders and multiplexers

The interconnection of ALMs and configurable memory cells (e.g., SRAM) can perform several arithmetical and logic operations. The switch matrix is used to interconnect the selected logic block to implement a given application. The I/O blocks are for communication between the FPGA chip and the external components.

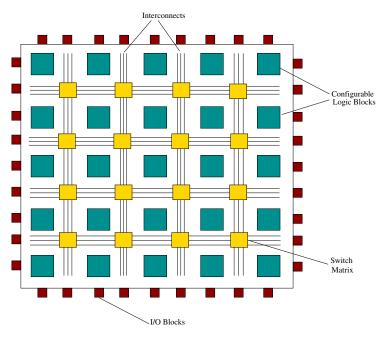

In addition to more logic elements, modern Intel FPGAs provides several hard-IPs primitives such as dedicated memory blocks, e.g., Block RAM (BRAM), Digital Signal Processing (DSP) units, etc. These floating-point units provide high design flexibility and are optimized to support high-performance DSP applications in IEEE 754 compliant floating-point single precision. One such example is the Intel Stratix 10 architecture presented in Fig. 1.2. This FPGA device is a 14 nm technology with millions of logic cells and more than five thousand DSP based on Hyperflex core architecture [Intel Corporation 2021a]. The Hyperflex device contains registers everywhere throughout the FPGA core to enable aggressive optimizations, retiming, or pipelining. However, hyperflex architecture comes with several problems. Firstly, routing on these devices is tedious and extremely slow, which is accentuated when using HLS tools. Secondly, a fairly deep pipeline through multiple registers is required to achieve correct frequencies.

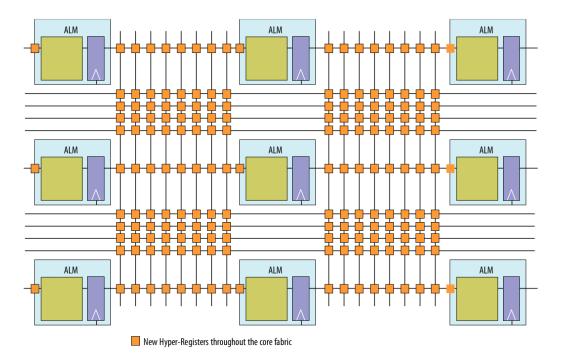

#### FPGA Synthesis:

Basically, an FPGA application is described using Hardware Description Languages (HDL) such as VHDL or Verilog. The use of these languages allows the designer to control the generated pipeline but requires strong knowledge of the FPGA architecture and the synthesis tools. The design flow includes different steps before the bitstream generation for the target FPGA, as illustrated in Fig. 1.3. The first step is to specify the Register Transfer Level (RTL) specifications of the design using HDLs. This step contains several behavioral simulations for the correctness of the application. The RTL description is then translated into a *netlist* made of registers and logic cells. The netlist is mapped into FPGA primitives and placed on the FPGA fabric. The placement step is iterative to find the best combination that minimizes the propagation delay and maximizes the operating frequency. The final step before bitstream generation consists to route the placed netlist which ensures that all resources are connected accordingly to meet all the timing constraints. The place-and-route steps are the most time-consuming ones and are likely to fail when there are unmet constraints.

This traditional design flow is time-consuming and only accessible by strongskilled hardware designers. In order to reduce the development time of FPGAs

Figure 1.2 – Stratix 10 Hyperflex core architecture from [Intel Corporation 2021c]

and make them accessible to a wide audience of programmers, High-Level Synthesis (HLS) tools have been developed for decades and have only recently reached maturity.

Figure 1.3 – FPGA Design flow with HDL languages

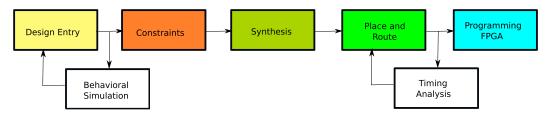

### 1.2 High-Level Synthesis

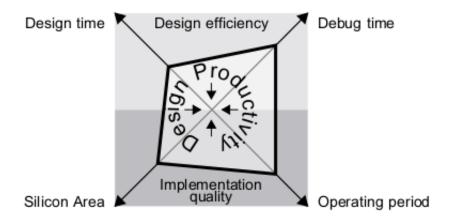

HLS is a discipline that attempts to provide more productivity to designers by offering synthesis tools at a high abstraction level than the traditional HDLs. The principle is to automatically generate a hardware circuit from the behavioral descriptions of a given application. A high-level design is entitled to meet several criteria to be effective. The design efficiency, the quality of implementation and the Quality of Results (QoR) in terms of area, performance, and accuracy, should be as good as those obtained with HDL tools. HLS tools provides high design productivity than HDL languages. As illustrated in figure 1.4, the polygon should

be as small as possible to provide both good design efficiency and implementation quality [Pelcat 2016]. Several HLS tools have been developed over four decades, driven by substantial research results and industrial works.

Figure 1.4 – Design efficiency from [Pelcat 2016]

#### 1.2.1 HLS history

The early research in HLS has taken place since the 1970s [Barbacci 1973]. Academic research has led to many advances and tools development, as it can be found in [Gupta 2008, Coussy 2008]. An overview of HLS evolution has been presented in [Martin 2009], and they provided a categorization of the evolution of HLS in three generations preceded by a prehistoric period. A global view of different HLS tools was detailed in [Nane 2015, Numan 2020], including academic and commercial ones. As explained by the authors, the first and second generations (till the early 2000s) of HLS have failed, mainly because the expectations placed on them were too ambitious. Among those expectations, we can find the choice of the right input languages, the guarantee of good QoR, high productivity, etc. The developed tools hardly addressed software developers for these generations and became a commercial failure.

Nevertheless, the third generation of HLS tools succeeds on many levels compared to the previous ones. Many major vendors proposed several tools with a strong focus on the domain of application, the input languages, the target users, the synthesis process, etc. The design entry of an HLS tool could be a Domain-Specific Language (DSL) or a General Purpose Language (GPL). The QoR has seen a significant increase for this generation allowed by the exploitation of most compiler-based optimizations, as is the case for general-purpose languages.

Availability Tool Design entry Target architecture Year Owner Bluespec Compiler BSV ASIC, FPGA BlueSpec 2007 ASIC, FPGA C/C++, SystemC 2004 Catapult-C Calypto CHC Compiler C/C++, SystemC FPGA 2008 Altium FPGA CoDeveloper Impulse-C 2003 Impulse Accelerated Commercial tools (License required) C-to-Silicon C/C++, SystemC ASIC, FPGA Cadence 2008 CyberWorkBench C, SystemC ASIC, FPGA 2011 NEC Cynthesizer SystemC ASIC, FPGA 2004 FORTE ASIC, FPGA DK Design Suite Handel-C 2009 Mentor Graphics HDL Coder Matlab, Simulink ASIC, FPGA 2012 MathWorks C/NAC ASIC, FPGA HerculeS 2012Ajax Compiler Intel HLS Compiler C/C++FPGA 2017 Intel Intel oneAPI DPC++ FPGA 2019 Intel Intel SDK for OpenCL FPGA 2013 Intel OpenCL LabView FPGA FPGA 2003 National Instruments MaxCompiler MaxJ, OpenSPL FPGA Maxeler Tech. 2010 Merlin Compiler Falcon Comp Sol. C/C++ FPGA 2017 SDAccel C/C++, OpenCL FPGA 2014 Xilinx SPIRAL ASIC, FPGA SPL 2008 U. Carnegie Mellon ASIC, FPGA Synphony C C/C++ 2010 Synopsys ASIC, FPGA C++, SystemC Stratus HLS 2015 Cadence Vivado HLS C/C++, SystemC FPGA Xilinx 2013 ASIC, FPGA Politec. Milano Bambu 2012 DEFACTO FPGA 1999 U. South California DWARV C subset FPGA 2012 TU. Delft CHiMPS FPGA 2008 . Washington CtoVerilog С ASIC, FPGA 2008 U. Haifa Academic tools (Open-source) C subset Garp **FPGA** 2000 U. Berkeley GAUT ASIC, FPGA 2010 U. Bretagne-Sud С FPGA 2011 U. Korea gcc2verilog HIPAcc С FPGA 2014 U. Erlangen-Nürnberg Kiwi С# **FPGA** 2008 U. Cambridge LegUp FPGA U. Toronto 2011 MATCH MATLAB FPGA 2000 U. Northwest FPGA Sarnoff Corp. Napa-C C subset 1998 FPGA PARO PAULA U. Erlangen-Nürnberg 2008 PipeRench Compiler DIL PipeRench 2000 U.Carnegie M. ROCCCC FPGA 2010 U. California SA-C SA-C FPGA 2003 U. Colorado Sea Cucumber FPGA 2002 U. Brigham Y. Java SPARK  $\overline{\mathbf{C}}$ ASIC, FPGA 2003 U. Cal. Irvine  $\overline{\mathbf{C}}$ Trident FPGA 2007Los Alamos NL

Table 1.1 – An overview of HLS tools

#### 1.2.2 High-Level Synthesis Tools

The emergence of the new high-level synthesis tools for FPGA has been a significant factor in their consideration in complex applications. We present in Table 1.1 a non-exhaustive list of HLS tools, updated with the new tools developed, including academic and commercial ones. Several research works [Koch 2016, Nane 2015, Numan 2020] have provided a complete description of each tool in this table.

Among these tools, the *CHiMPS* compiler is an academic HLS framework, developed for hybrid CPU-FPGA platform for High-Performance Computing (HPC)

applications [Putnam 2008]. The tool takes an input described in C language to generate a synthesizable VHDL for FPGAs. GAUT is also an academic tool from Université de Bretagne-Sud designed for DSP applications. The GAUT compiler generates the VHDL description from an input C language and also handles the communication and memory management. The ROCCC compiler [Villarreal 2010], an open-source HLS framework, is developed at the University of California for compute-intensive applications. Another academic tool is LeqUp [Canis 2011] based on Low-Level Virtual Machine (LLVM) compiler. From an input C language, LeqUp can generate the desired custom accelerators as well as the general purpose processor. It is worth mentioning other academic frameworks depending on the domain of application or target architecture, such as Kiwi [Singh 2008], DWARV [Nane 2012], BAMBU [Pilato 2013], etc. In addition to open-source frameworks, several commercial HLS tools have emerged. Cataputt-C [Calvpto 2004] was developed by Mentor Graphics<sup>1</sup> to generate HDL descriptions to target ASICs and FPGAs from a High-Level programming Language (HLL). C-to-Silicon, developed by Candence, is a commercial HLS tool aimed for ASICs and FPGAs. This tool generates Verilog code by using a HLL for the target devices mentioned above.

There was a massive surge of interest when major vendors started offering more mature tools for different audiences. Vivado HLS, formerly AutoPilot, developed initially by AutoESL, was proposed by Xilinx in 2011. Vivado HLS allows to synthesize a custom design from an input C, C++ or SystemC to target Xilinx FPGAs. The output of Vivado HLS compiler will be Verilog or VHDL IP cores ready to be programmed into the FPGA. Xilinx also proposed their OpenCL-based HLS tool SDAccel for software programmers. OpenCL Software Development Kit (SDK) enables FPGA programming for software developers through HLLs such as C, C++, or OpenCL without a strong knowledge of FPGA architectures. The Xilinx SDAccel was motivated by the Altera OpenCL released one year early. Indeed, the Intel FPGA (formerly Altera) SDK for OpenCL was developed by Altera in 2013<sup>2</sup>. Both Intel OpenCL SDK and Xilinx SDAccel are LLVM-based compilers that produce RTL level design from HLLs and then perform the full synthesis. In 2017, Intel released a new HLS tool called Intel HLS Compiler which is an IPdriven synthesis tool for Intel FPGAs addressed to hardware designers like Vivado HLS. This tool allows traditional HDL designers to describe their applications using C or C++ languages allowing them to gain productivity while having the control to tune the design. The high-level design is converted to a LLVM Intermediate Representation (IR), which will be subject to multiple aggressive optimizations by expressing parallelism, pipelining, etc.

However, exploiting the full potential of these architectures using high-level tools has always been a significant concern. Therefore, an algorithm-architecture co-design approach is necessary in order to use these parallel architectures better. For FPGAs with custom architecture, HLS tools provide the guidelines required

<sup>&</sup>lt;sup>1</sup>Before its acquisition by Calvpto Design Systems

<sup>&</sup>lt;sup>2</sup>Intel acquired Altera in 2015

to implement applications efficiently and thus produce an efficient pipeline. The efficiency of these pipelines has not yet reached that obtained through HDL descriptions, but their development time is drastically reduced.

Nevertheless, a strong knowledge of the architecture of the FPGAs and the functioning of these compilers are essential to help the compiler efficiently synthesize the design and ensure good performance. Besides, an algorithm analysis is critical to choose the architecture that best matches the application. In this work, we only focus on HLS tools from Intel corporation to accelerate our applications.

#### 1.3 Intel HLS Tools

Intel has proposed several tools depending on the target audience to open up the field of FPGA development to software developers and allow hardware designers to gain productivity. Among these HLS tools, we have Intel HLS Compiler, Intel FPGA SDK for OpenCL, and Intel oneAPI, which all use a HLL to synthesize a design on Intel FPGAs.

#### 1.3.1 Intel HLS Compiler

The Intel HLS Compiler is an HLS tool that produces an RTL level design optimized for Intel FPGAs from an input of C/C++ languages. The tool aims to quicken the design for traditional FPGA designers and allow them to integrate their accelerator into a larger system. The tool is IP-driven which means that it synthesizes a C/C++ function into an RTL design as an IP that can be used along with HDL designed IPs in a more complex system. Intel HLS Compiler design flow includes an emulation step to verify the component functionality and allow a quick hardware verification of the accelerator by generating a testbench in the cosimulation step. In summary, the design flow of an Intel HLS Compiler application consists of multiple iterations of functional correctness and architectural verification followed by the placement and routing of the generated IP and then the integration into the FPGA system. The HLS design can benefit from several basic compiler optimizations. The designer may explore these optimizations to better harness the FPGA through multiple pragmas and attributes.

#### 1.3.2 Intel FPGA SDK for OpenCL

Open Computing Language (OpenCL) is an open royalty-free standard parallel programming API for heterogeneous processing platform (CPU, GPU, FPGA) [Khronos 2009]. The purpose is to give software developers the ability to exploit the parallelism potential of modern processors with code portability. In 2013, Altera presented their OpenCL SDK to allow software developers to target their FPGAs using HLLs.

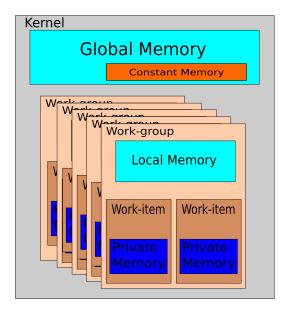

#### 1.3.2.1 Programming model

OpenCL allows cross-vendor and cross-platform portability, which was a reaction to CUDA. Therefore, the programming model OpenCL is similar to CUDA based on massive threads parallelism. Each thread is called a *work-item* in OpenCL terminology, and multiple work-items are organized to form a *work-group*. Work-items within the same work-group are synchronized using *barriers* to ensure memory consistency. The local memory allows work-items within the same work-group to share data. Data stored into global memory is visible by all work-items within the work-groups.

Based on the C99 standard, OpenCL supports both data- and task-parallel programming models known as Single Work-Item (SWI) and NDRange (NDR) kernels [Khronos 2009] in OpenCL terminology. The former, called SWI kernel, models the design as a deep pipeline to exploit the parallelism at the finest granularity. This execution model uses only one work-item within a single work-group to execute the program through the pipeline. The challenge is to feed the pipeline with incoming data efficiently. A new piece of result is produced, as long as the pipeline stages are full, in a regular interval called **Initiation Interval (II)**. The latter, NDR kernel, exploits thread-level data parallelism to achieve better throughput. The NDR model on FPGA is different from the GPU-like model. Indeed, to exploit the multiple compute cores available on GPU devices, multiple work-items are created to run simultaneously on these cores. However, the compiler generates, for an NDR design on FPGAs, a single pipeline as a compute unit, and all the work-item passes through it to complete the execution. The attempt, in this case, is to launch a new thread at regular II cycles. One can infer SIMD unit or compute unit replication to achieve thread-level parallelism.

The programming model of OpenCL is based on the host and devices paradigm. The application is composed of two programs: a host part and the kernel compiled separately using Just-In-Time (JIT). The JIT compilation is not supported due to the long-time placement and routing step for bitstream generation for FPGAs. Therefore the OpenCL kernel is compiled offline using a vendor-specific compiler followed by the full synthesis flow. The host program is run on the host device and the kernel by the accelerator device. The OpenCL API handles the communications between the host and the device.

An overview of the OpenCL memory model is presented in Fig. 1.5. OpenCL has four memory models regardless of the underlying device. The first one is the **global memory** which is a large-sized long latency off-chip memory visible to all work-items. Then, a small part of global memory is configured as read-only memory with a high cache hit rate called the **constant memory**. This read-only memory acts like cache memory, and data stored in it should fit in the constant memory once. A cache miss in constant memory is extremely expensive. The third memory is **local memory** with low access latency and small in size compared to the external memory. The local memory is used to prefetch data and is visible to all work-items within a work-group. The last one is **private memory** only visible

by one work-item. After OpenCL kernel synthesis, the global memory space resides in the external off-chip memory of the board (DDR or HBM memory), while the local memory space is mapped to the on-chip memory of the FPGA (made of M20K BRAM). Private memory can be implemented using on-chip BRAMs or registers.

Figure 1.5 – OpenCL Memory Model

The major FPGA manufacturers have proposed their OpenCL SDK to program their FPGAs. This work only deals with Intel FPGA SDK for OpenCL. This Intel OpenCL SDK provides all necessary components to run an application on Intel FPGA devices, including Altera Offline Compiler (AOC) to compile the kernel, host libraries (for host applications), and all utilities related to the Board Support Package (BSP).

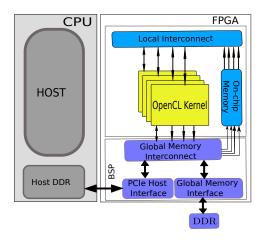

#### 1.3.2.2 Board Support Package

The generated bitstream programs the FPGA after compiling the compute kernel using a vendor-specific compiler. A BSP is used to interface the FPGA with the external devices to run the OpenCL kernel. Therefore, the BSP provides all necessary interfaces between the FPGA and external components (memory, host, etc.). The BSP, as shown in Fig. 1.6, provided by the board manufacturers, allows programmers to run the kernel executable on the target FPGA. It packages features such as IP Cores, DDR controllers, PCIe controllers, and DMA drivers to establish communication between the host and the FPGA device. Many manufacturers of boards based on Intel FPGAs provide boards with their specific BSP to quickly design and run applications using Intel FPGA SDK for OpenCL. The main concern is that the vendor updates of BSPs do not necessarily follow OpenCL compiler updates. This prevents the programmer from taking advantage of some of the new compiler features. However, Intel ensures a minimum of two years of backward compatibility

between BSP and the compiler. In addition, designers can implement their custom BSP and, in particular, add additional functions to their application. OpenCL SDK also provides, besides OpenCL directives, many FPGA-specific optimizations to fully harness the device's potential.

Figure 1.6 – Intel FPGA SDK for OpenCL platform

#### 1.3.3 Intel oneAPI

OneAPI [Intel Corporation 2021b] is Intel's new unified and standardized toolkit that allows targeting multiple platforms using a single-source C++ programming language. Intel oneAPI is based on the DPC++ (Data Parallel C++) language, which is an extension of standard C++ incorporating the SYCL standard [Keryell 2020]. DPC++ is a modern C++ extended HLL based on the OpenCL programming model, and the purpose is to target different architectures (such as CPU, GPU, FPGA, etc.) at a higher level abstraction than OpenCL. The main advantage of the oneAPI framework is that it alleviates programming complexity and allows code reuse across different platforms while ensuring performance. The DPC++ compiler builds the oneAPI project for the target architecture. The JIT compilation can be used when targeting CPU or GPU devices, as is the case for OpenCL. However, JIT compilation is not supported on FPGAs as explained in Section 1.3.2.1. Unlike OpenCL, oneAPI supports single-source compilation for the host and the device application. A BSP, to ensure the interface and communications between the FPGA chip and external hard-IP, is required to run oneAPI application on FPGAs.

Intel plans to replace OpenCL with oneAPI in the next few years. In this case, this tool must be able to offer the same level of performance as the OpenCL tool or offer better performance for FPGAs to make it into the HPC world. This manuscript will also focus on the oneAPI framework to accelerate our compute-intensive algorithms and compare the two languages for the same types of applications.

OneAPI is a superset of OpenCL in terms of kernel programming directives. The problems and optimization solutions are based on the same concepts. However, the names of the attributes and pragmas are usually different. In the rest of this document, the optimizations presented are universal to both tools, but we will present them using OpenCL terminology.

#### 1.4 OpenCL Optimizations

This section deals with OpenCL kernel optimization techniques to leverage the FPGA architecture. In fact, the use of the tools allows reducing the development time on FPGA considerably without however any guarantee of performance. The HLS compilers implement different optimizations based on their particular IR, such as pipelining or expressing data-level parallelism. However, they suffer from a lack of support for many other unexploited FPGA-specific optimizations for arithmetic operations [Uguen 2019] for instance. In order to exploit their full potential, it is essential to apply some advanced optimizations in addition to the basic compiler optimizations. The OpenCL tool has been evaluated for many HPC applications such as the Rodinia benchmark [Zohouri 2019] or computed tomography [Martelli 2019]. In this section, we will present the optimizations applicable to an FPGA compute kernel to have an efficient pipeline.

#### 1.4.1 Compiler-aided Optimizations

The use of FPGAs through HLS tools such as OpenCL requires careful attention to optimizations for efficient pipeline generation. Compilers for general-purpose processors can apply some advanced optimizations without much developer intervention. This is not the case for the new HLS compilers for FPGAs. To take advantage of the FPGA architecture, the designer must assist the HLS compiler by providing FPGA-specific optimizations such as concurrent execution, pipelining, data representation, etc. Several basic optimizations are presented in programming guides [Intel Corporation 2019a, Intel Corporation 2019b]. We will look here at some optimizations relevant to FPGA design.

#### 1.4.1.1 Floating-point optimizations

Intel's new FPGAs are equipped with DSPs to perform floating-point operations. However, the cost of these floating-point operations can be reduced for applications with a tolerance for arithmetic precision by relaxing or balancing these floating-point calculations.

The order of arithmetic floating-point operations can be relaxed using the *-fp-relaxed* option in the *aoc* command. The relaxing is done by implementing balanced tree hardware as described in [Langhammer 2008]. The *-fpc* option directs the compiler to remove intermediary floating-point rounding operations and conversions whenever possible and to carry additional bits to maintain precision. The rounding is performed only at the end of the chain of floating-point operations. Using these

floating-point optimizations may introduce numerical variations in the computation results.

#### 1.4.1.2 Global memory interleaving

The offline compiler, by default, interleaves global memory (1024 bytes interleaved) across the external memory banks to efficiently share the bandwidth between all the memory objects. This configuration leads to poor memory bandwidth utilization for compute-intensive algorithms due to the problem size and the non-contiguous memory access pattern. Therefore, using interleaved memory may result in high stall performance. In order to avoid this automatic memory interleaving, the offline compiler may be invoked with -no-interleaving flag in the aoc command. This makes it possible to perform read and write operations in different memory banks for high throughput. In the case where the board support package includes different memory types (DDR, QDR, HBM), the memory which has to be prevented from the interleaving must be specified in the aoc command (-no-interleaving=DDR, for instance). In our case, we notice that non-interleaved global memory access can reduce the worst-case stall percentage by half.

#### 1.4.2 NDR kernels

Several optimizations must be applied to an NDR kernel to achieve high throughput. This programming kernel must avoid multiple barriers when using local memory and reduce stalls due to data dependencies.

Listing 1.1 - NDR kernel

```

1 __kernel void NDR_kernel(//kernel arguments

2           ){

3           // get index of the work item

4           int index = get_global_id(0);

5           // Some computations

6 }

```

#### 1.4.2.1 Specifying work-group size

Intel provides an attribute to set work-group size in order to minimize the BRAM consumption. If not specified, the default work-group size is set at 256, leading to a potential waste of BRAM resources. This optimization can save valuable resources on the FPGA that could be used to increase the overall design performance. Specifying work-group does not impact the performance in all cases. However, when the kernel contains barriers and if a value is not determined, the compiler sets the work-group size to one at runtime even though the default value was set to 256 at compile time. This behavior can significantly degrade the design performance. The impact of work-group size on the performance has been evaluated in [Shata 2019]. They presented cases for their benchmark where the performance can be improved by setting a specific or a maximum value.

#### 1.4.2.2 Parallelism

To achieve data parallelism for NDR kernels, SIMD inference or compute unit replication can be used through adequate attributes. The <code>num\_simd\_work\_items</code> attribute is also used to allow kernel vectorization in a SIMD fashion. This enables work-item-level parallelism and allows more computation per work-item without modifying the kernel's body. The use of the SIMD attribute requires to specify the work-group size. The <code>num\_compute\_units</code> attribute is used to generate multiple compute units to increase the kernel throughput. Each work-group will be mapped to a compute unit. Therefore, all the work-items in a work-group may share the same resources. Both attributes increase throughput by increasing the number of FPGA resources. However, the SIMD attribute only replicates the data path of the pipeline while the compute unit attribute implements each instance as a single sufficient pipeline leading to more resource usage. Hence, the SIMD attribute is more area efficient than the other. Nevertheless, in practice, combining these two attributes will potentially give a good trade-off between resource consumption and throughput.

#### 1.4.3 Single Work-Item (SWI) kernels

FPGAs have proven a strong ability to express fine-grained parallelism through pipelining. Therefore, it is encouraged by the major vendors of FPGAs to choose a SWI kernel instead of NDR kernel to better leverage the full potential of their architecture. A given function is designed as a deep pipeline with multiple stages. A key point in pipeline parallelism is to avoid memory stalls due to data or memory dependencies. A stall will hold a computation when the required data is not available, making some stages of the pipeline idle at some clock cycles. Also, the II optimization is another key for this kind of kernel. It should be noted that the ideal value of II is 1, which means that the design produces a new result at every clock cycle once the pipeline is filled. For a SWI kernel, particular attention is given to loops for optimization purposes since loops are vastly present in compute-intensive applications.

Listing 1.2 – SWI kernel

```

1 __kernel void SWI_kernel(//kernel arguments

2          ){

3     for(int index = 0; index<N; index++){

4          // Some computations

5     }

6 }</pre>

```

#### 1.4.4 Loop optimizations

In compute-intensive applications, we have a nest of nested loops to perform processing on large data. For simplicity of illustration, the following optimizations are

often applied to a single loop but are equally applicable to nested loops. One of these loop optimizations consists of merging the nested loops into one.

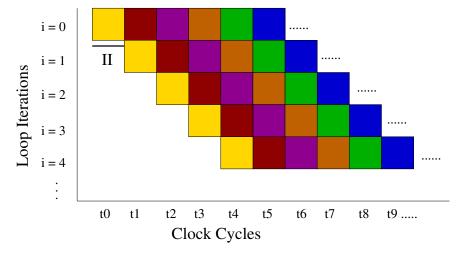

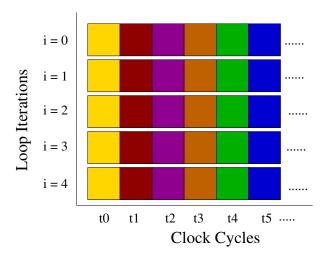

# 1.4.4.1 Loop pipelining

Loop pipelining consists of subdividing a loop's body into several micro-operations (called pipeline stages) that can be executed concurrently, as shown in Fig. 1.7. The aim is to overlap the loop iterations so that one iteration can start before the completion of its predecessor. A new iteration has to start as soon as possible to reduce the overall clock cycles of the loop. The number of clock cycles between two consecutive iterations is the II value of the pipeline. The same concept is present in general-purpose processors, allowing one to use the available resources on the device at its full potential. This is even more interesting on FPGAs as the synthesis tools synthesize custom designs based on the user's input description. Instead of using a fixed architecture, as is the case with general-purpose processors, HLS tools can generate a custom pipeline for each loop of a program according to the operations performed on FPGA. Loop pipelining uses FPGA hardware efficiently and avoids resource under-utilization. Therefore, loop pipelining improves the area usage and the design performance simultaneously. The AOC compiler attempts to pipeline,

Figure 1.7 – Loop pipelining

by default, all the loops in the kernel for SWI with an II value of one (the optimal value). Loop-carried dependencies must be avoided to achieve the optimal II value. When the dependency is not avoidable, the designer should manage to handle it in one clock cycle by inferring shift register, for instance, or any other relevant optimizations. One important limitation of loop pipelining on FPGAs is the necessity to know the loop trip count at compile time to generate an efficient pipeline. When the loop trip count cannot be determined at compile-time, the compiler will not be able to analyze the loop and evaluate the loop exit condition, which will lead to the generation of a loop pipeline with high II value. Consequently, some recent