# Design of millimeter-wave receivers for embedded automotive radars

Hugo Vallée

#### ▶ To cite this version:

Hugo Vallée. Design of millimeter-wave receivers for embedded automotive radars. Electronics. Université de Bordeaux, 2020. English. NNT: 2020BORD0230. tel-03935606

# HAL Id: tel-03935606 https://theses.hal.science/tel-03935606

Submitted on 12 Jan 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Ecole doctorale n°209

#### Sciences physiques et de l'ingénieur

Thèse pour obtenir le grade de Docteur de l'Université de Bordeaux

Présentée par Hugo Vallée

Dirigée par le *Professeur Thierry Taris*, Bordeaux INP

Préparée au sein du

Laboratoire d'Intégration du Matériau au Système Bordeaux, France

NXP Semiconducteurs, Toulouse, France

Ecole Doctorale  $n^2209$ Spécialité : Electronique

# Conception de récepteurs millimétriques pour des applications radars automobiles embarqués

# $Design \ of \ millimeter-Wave \ Receivers \ for \ Embedded$ $Automotive \ Radars$

Thèse soutenue publiquement le 11 décembre 2020,

Après avis de :

M. Sylvain BOURDEL Professeur Grenoble INP Rapporteur M. Domenico ZITO Professeur Aarhus University Rapporteur

Devant la commission d'examen formée de :

| M. Jean-Baptiste BEGUERET | Professeur | Université de Bordeaux | Président           |

|---------------------------|------------|------------------------|---------------------|

| M. Xavier HOURS           | Ingénieur  | NXP Semiconductors     | Examinateur         |

| M. Christophe LANDEZ      | Ingénieur  | NXP Semiconductors     | Examinateur         |

| M. Gilles MONTORIOL       | Docteur    | NXP Semiconductors     | Invité co-encadrant |

| M. Thierry TARIS          | Professeur | Bordeaux INP           | Directeur de thèse  |

# Résumé

# Conception de récepteurs aux fréquences millimétriques pour des applications radars automobiles embarqués

Depuis plusieurs années, l'industrie automobile multiplient les systèmes d'aide à la conduite dans l'objectif d'améliorer l'autonomie des véhicules. Pour cela, chaque véhicule intègre un panel de capteurs de plus en plus étoffé. Le radar 80GHz embarqué présente alors des avantages multiples : immunité aux conditions extérieures, mesure simultanée de la distance et la vitesse... Ainsi, l'industrie du semiconducteur se trouve face à deux défis : réduire le coût des puces et améliorer leurs performances. Cela passe par l'utilisation de technologie CMOS avancées et, par l'amélioration des principaux facteurs de mérite du radar comme la puissance de sortie de son transmetteur, le bruit de phase de son oscillateur local et le facteur de bruit de son récepteur. L'objectif de cette thèse est de proposer des architectures et topologies susceptibles d'améliorer significativement les performances d'une récepteur radar.

Dans ce cadre, le récepteur radar est soumis à deux contraintes qui peuvent être contradictoires. Placé derrière le pare-chocs, le module radar est affecté par la réflexion du signal transmis. Face au risque d'apparition de non linéarités, donc de fausses cibles, de fortes contraintes sont exigées en termes de point de compression. De l'autre côté, pour réduire le facteur de bruit globale du récepteur, il y a besoin de maximiser le gain et minimiser le facteur de bruit de sa partie millimétrique. Pour répondre à cela, cette thèse propose plusieurs pistes.

Le premier axe est centré sur les techniques de conception de circuits millimétriques. D'un côté, il s'agit de réduire la consommation des circuits au travers d'étages complémentaires et l'opération en moyenne inversion. De l'autre côté, il s'agit d'implémenter des techniques d'annulation de bruit. Ces techniques permettent simultanément de travailler sur de larges bandes passantes et d'améliorer les performances en bruit. Cela a amené au développement d'une topologie dite « complémentaire à couplage transversale capacitif ».

Le second axe de ce travail se concentre sur les techniques de mélange. Les mélanges actifs présentent un bon compromis entre gain, linéarité et facteur de bruit mais également un bruit en 1/f élevé, malgré l'implémentation de techniques pour le réduire. Ces topologies peuvent adresser des applications de RADAR courte portée mais pas longue portée. Les mélangeurs passifs présentent de meilleures performances en bruit mais sont plus contraignants en termes de linéarités. Pour cela, cette thèse propose d'implémenter un mélangeur en courant à 80GHz pour améliorer simultanément les performances en bruit et linéarité, capable d'adresser des applications RADAR longue portée.

Mots clés: radar, amplificateur à faible bruit, mélangeurs, millimétrique, radiofréquence,

# Abstract

#### Design of millimeter-Wave Receivers for Embedded Automotive Radars

Since few years, automotive industry implements more and more advanced driven assistance systems to improve safety and autonomy of vehicles. To achieve high autonomy level, each vehicle may include more and more sensors. The embedded 80GHz radar presents many advantages for car manufacturers: great immunity to outdoor conditions, real-time measurement of distance and velocity... To face such requirements, semiconductor industry has to simultaneously reduce cost and improve radar performances. It requires first to use advanced CMOS technologies (40nm, 28nm and smaller nodes). However, the main figures of merit should be improved such as the output power of the transmitter, the phase noise of the local oscillator and the noise figure of the receiver. The objective of this thesis is to propose new architectures and topologies able to improve the radar receiver performances.

In an automotive context, the radar receiver face two main issues. Mounted behind the bumper, the radar module is impacted by the reflection of the transmitted signal. It may cause non linearities in the demodulation chain thus creating false targets. For this reason, the level of linearity is high, especially regarding the compression point and the limited front end (FE) gain. The improvement of the RADAR sensitivity requires both to maximize the FE gain and to minimize the noise figure (NF) of the receiver front-end. To face such contradictory specifications about the FE gain, this thesis works on more advanced design techniques and topologies.

In this thesis, a specific focus is proposed on two design techniques. First, the circuits are designed to improve their efficiency  $(g_m/I_D)$  by operating in the moderate inversion region which contributes to reduce the power consumption. Secondly, the common-gate based noise cancelling technique is explored at 80GHz. This topology achieves simultaneously a wideband behavior and a low noise figure. It leads to develop a topology called "complementary capacitor cross-coupled" which achieves high RF performance at a reduced power consumption with respect to the operating frequency.

Besides this thesis studies various mixing approach to determine the best suited for radar applications. First, considering its interesting performance trade-off in BICMOS technology implementations, active mixers are explored. Whereas the level of 1/f can allow for short range operations, it is too large for long range RADAR. To address this issue, passive mixers are then studied. They achieve better noise performances but severely impact the linearity performances. To overcome this drawback, an 80GHz current mode mixer featuring noise and linearity improvement is developed.

Keywords: radar, low noise amplifier, mixer, millimeter-Wave, radiofrequency

# Acknowledgment

This work would not have been possible without the support of many people. I would first like to thank my research advisor, Pr. Thierry Taris, for his strong support, availability and constant help during these three years. I would like to thank my industrial co-advisor, Dr. Gilles Montoriol for his ability to share his wide experience. I express all my gratitude to Mr. Xavier Hours and Mr. Christophe Landez for giving me the opportunity to work in their design teams and study this interesting field of automotive radar.

I am thankful for the professional and personal support I received from many of my colleagues of NXP Toulouse design & validation teams which provides me a great technical support: Thierry, Cristian, Jean-Paul, Fabien, Jean, Birama, Stéphane, Jean-Stéphane, Pierre, Sébastien, Léo and Salime; and from NXP Eindhoven design team, especially: Kostas, Anton and Marteen. I would also like to thank all my colleagues at the IMS Laboratory, especially Magali de Matos, all the professors and associate professors of IMS Design teams - and all my PhD colleagues.

I also thank the thesis committee members for accepting to participate as a jury and evaluate my research activities. First, I would like to thank Pr. Jean-Baptiste Begueret from Université de Bordeaux who acts as president of the jury. Second, I would express all my gratitude to Pr. Sylvain Bourdel from Université Grenoble Alpes and Pr. Domenico Zito from Aarhus University for reviewing my manuscript and providing interesting comments. Furthermore, I also thank the thesis examiner Christophe Landez and Xavier Hours from NXP Semiconductors.

Finally, let me express all my gratitude to my parents, Ludovic and all my friends who have given me a constant support, encouragements and help during these three years.

This work would not have been possible without them.

# Contents

| Chapter 1. 77GHz Embedded Automotive Radar      |

|-------------------------------------------------|

| I. Radars in automated vehicles                 |

| 1. Introduction to automated vehicles           |

| a. Automated vehicles trends                    |

| b. Sensors in automated vehicles                |

| c. Sensor data fusion                           |

| 2. Automotive radar overview                    |

| a. Radar system                                 |

| b. Expectations of automotive radar             |

| c. Spectral occupation                          |

| d. Automotive Radar Standards                   |

| 3. Radar applications in automated vehicles     |

| a. Short Range Radar (SRR)                      |

| b. Medium Range Radar (MRR)20                   |

| c. Long Range Radar (LRR)20                     |

| II. FMCW Modulation Basics                      |

| 1. Distance measurement                         |

| 2. Velocity measurement                         |

| 3. Conclusion                                   |

| III. 77 GHz FMCW Radar IC                       |

| 1. Noise in automotive radar [17]27             |

| a. Maximum range regarding the demodulator NF28 |

| b. Noise distribution on RF demodulator chain   |

| c. Noise figure de-sensitization                |

| c. Conclusion on noise specifications           |

| 1. Linearity in Automotive Radar [20]           |

| a. In-band linearity (ICP1)                     |

| b. Intermodulation (IIP3)                                | 33 |

|----------------------------------------------------------|----|

| c. Bumper impact on linearity (ICP1)                     | 34 |

| 2. Conclusion                                            | 35 |

| IV. Considerations on receiver RFFE for automotive radar | 36 |

| 1. RF CMOS opportunities                                 | 36 |

| 2. mmW Front-End architecture                            | 38 |

| a. RFFE Basics                                           | 38 |

| b. RF signal processing                                  | 39 |

| 3. Conclusion                                            | 40 |

| V. Thesis outline                                        | 40 |

| Chapter 2. 77-GHz Noise-cancelling active downconverter  | 43 |

| I. Noise cancelling principle                            | 43 |

| 1. Why noise cancelling is interesting?                  | 44 |

| a. Limitation of noise matched structures                | 44 |

| b. Noise cancellation principle                          | 45 |

| 2. Common-gate based noise cancelling                    | 46 |

| a. Impedance matching                                    | 47 |

| b. Gain balance                                          | 47 |

| c. Noise cancellation                                    | 48 |

| d. Distortion cancellation                               | 49 |

| e. Conclusion                                            | 50 |

| II. RF Noise Cancelling Blixer                           | 50 |

| 1. Noise cancelling applied to mixer                     | 51 |

| a. Noise cancellation in a mixer                         | 52 |

| b. Attractive properties of Blixer                       | 53 |

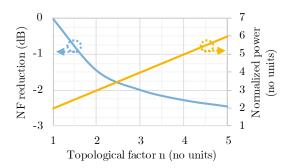

| 2. Noise figure improvement                              | 53 |

| 3. Low power improvement                                 | 54 |

| a. Auxiliary path improvement                            | 55 |

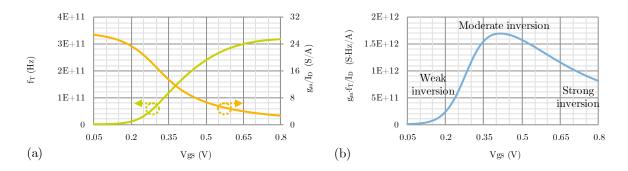

| b. Design in moderate inversion                          | 55 |

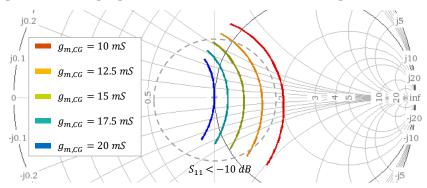

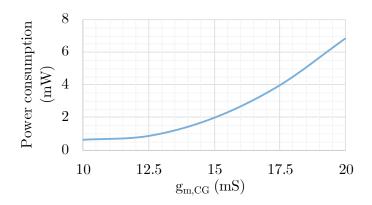

| c. Impedance matching                                    | 56 |

| 4.           | Performances of implemented RF-Blixer               | 57 |

|--------------|-----------------------------------------------------|----|

| 5.           | Conclusion                                          | 30 |

| III.         | 77GHz Noise Cancelling Mixer                        | 30 |

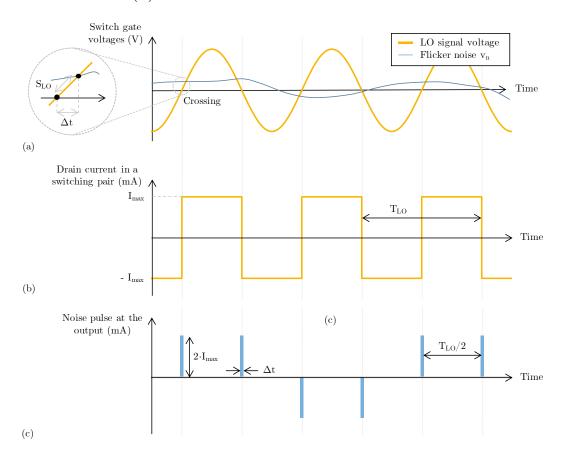

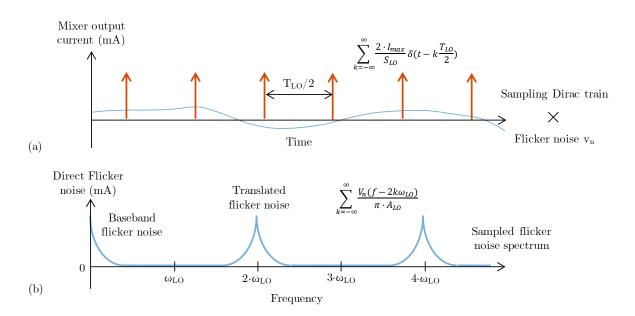

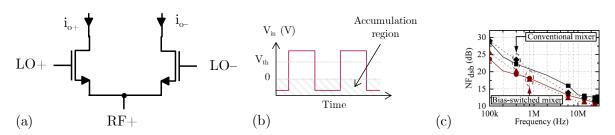

| 1.           | Flicker noise in CMOS active mixers                 | 31 |

| a.           | Flicker noise in CMOS switching pair                | 31 |

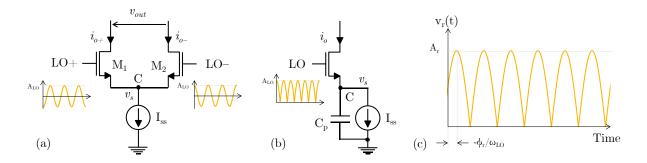

| b            | Flicker noise reduction techniques                  | 36 |

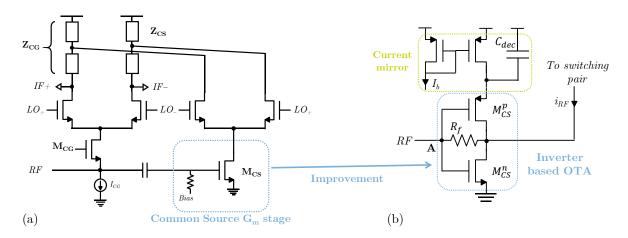

| c.           | Proposed flicker noise reduction                    | 38 |

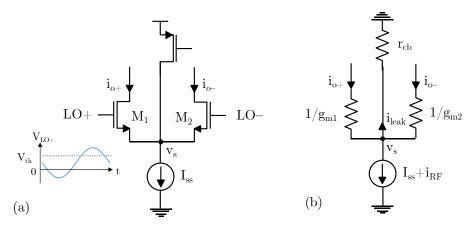

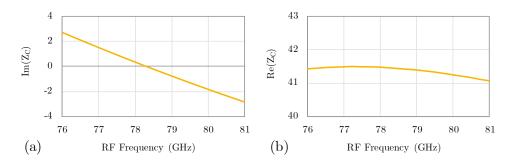

| 2.           | mmW noise cancelling mixer model                    | 70 |

| a.           | Impedance matching                                  | 70 |

| b            | . Conversion gain                                   | 72 |

| c.           | Noise                                               | 73 |

| 3.           | Measurement and simulations.                        | 74 |

| 4.           | Conclusion on 77GHz mixer                           | 78 |

| IV.          | Conclusion on noise cancelling mixer                | 30 |

| Chapter      | 3. 77-GHz low noise amplifier                       | 33 |

| I.           | Introduction to conventional RF architecture        | 33 |

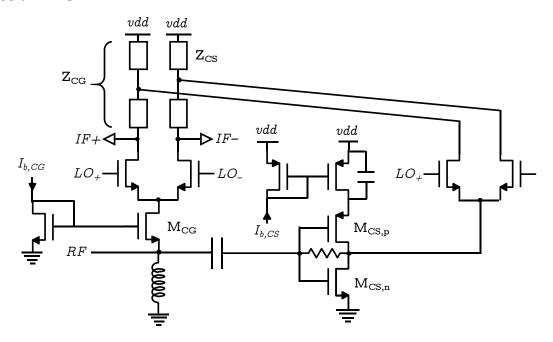

| 1.           | LNA specification: Noise Figure                     | 34 |

| 2.           | LNA specification: Linearity                        | 35 |

| 3.           | Conclusion on LNA Specifications                    | 35 |

| II.          | Single-balanced noise-cancelling LNA                | 36 |

| 1.           | Noise-cancelling LNA modelling                      | 37 |

| $\mathbf{a}$ | ) Input Matching                                    | 38 |

| b            | ) Conversion gain                                   | 39 |

| c)           | Noise figure                                        | 39 |

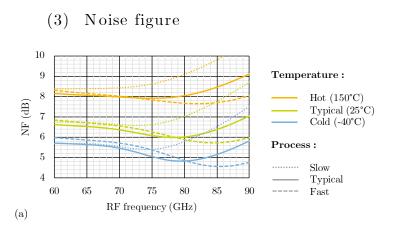

| 2.           | Post-layout simulations                             | 39 |

| 3.           | Single Balanced LNA and down converter performances | 92 |

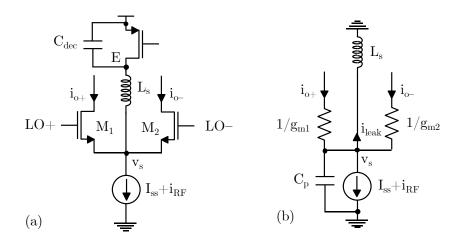

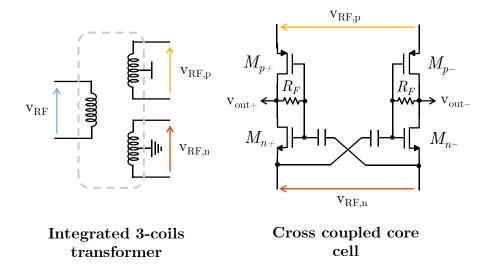

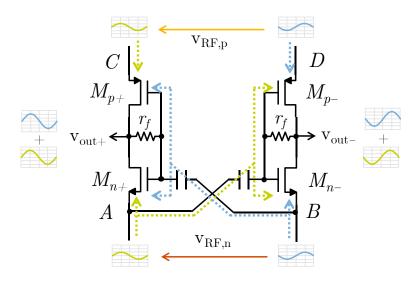

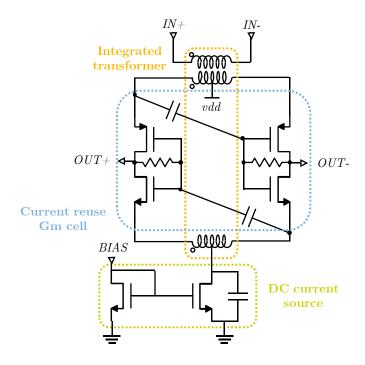

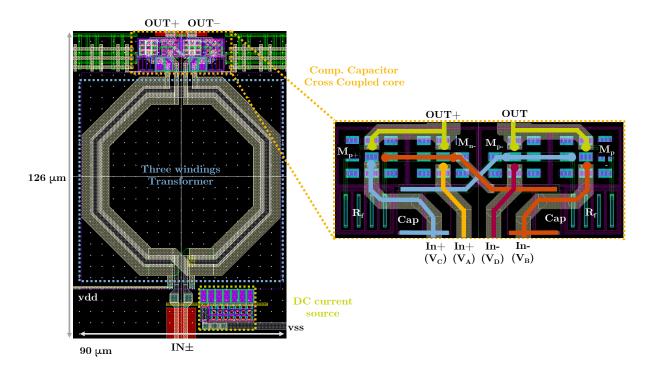

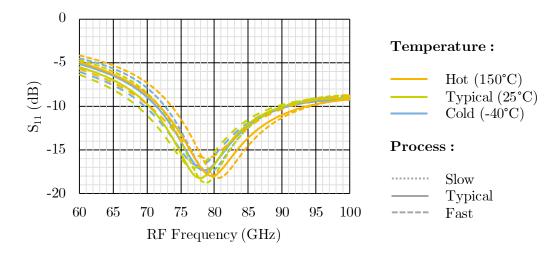

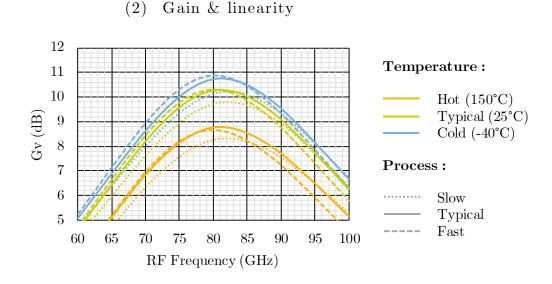

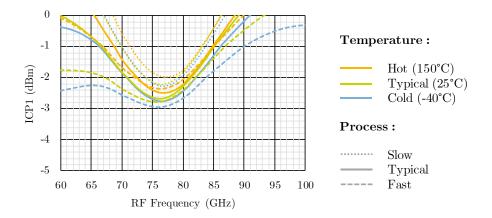

| III.         | Complementary capacitor-cross-coupled amplifier     | 93 |

| 1.           | Introduction to differential noise-cancelling       | 93 |

| a.           | Fully differential noise-cancelling LNA             | 93 |

| b            | . Capacitor-cross-coupled LNA                       | 94 |

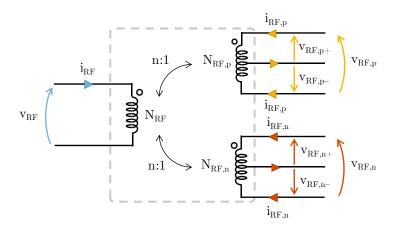

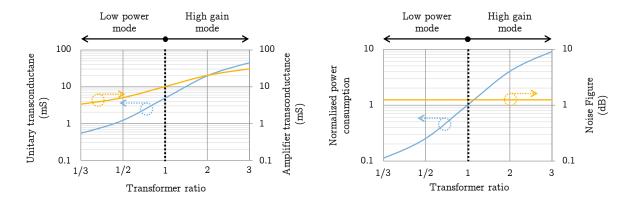

| 2. Principle of C4 LNA                          | 96  |

|-------------------------------------------------|-----|

| a. Modelling of the three-coil transformer      | 97  |

| b. Modelling of C4 LNA                          | 98  |

| c. Noise analysis of C4 LNA                     | 100 |

| d. C4 amplifier design trade-off                | 102 |

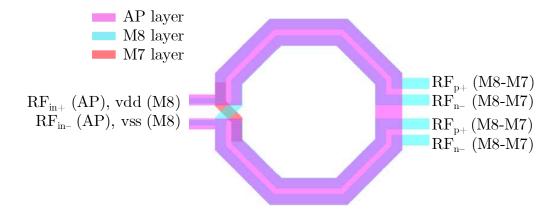

| 3. Implemented mmWave C4 LNA                    | 103 |

| 4. C4 LNA Conclusion                            | 106 |

| IV. Conclusion                                  | 108 |

| Chapter 4. 77-GHz Downconverter                 | 110 |

| I. Introduction to CMOS passive mixer modelling | 110 |

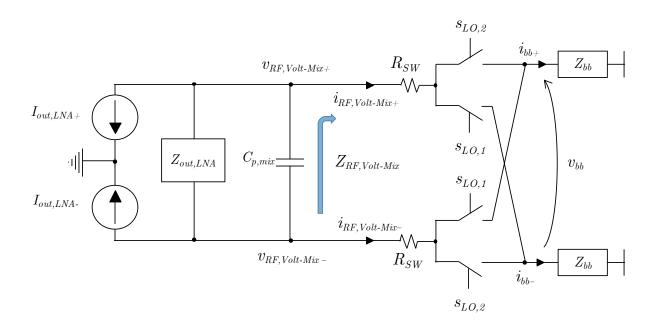

| II. Voltage mode downconverter                  | 113 |

| 1. Demodulation chain                           | 113 |

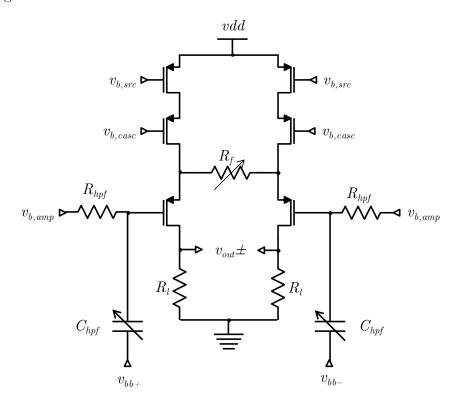

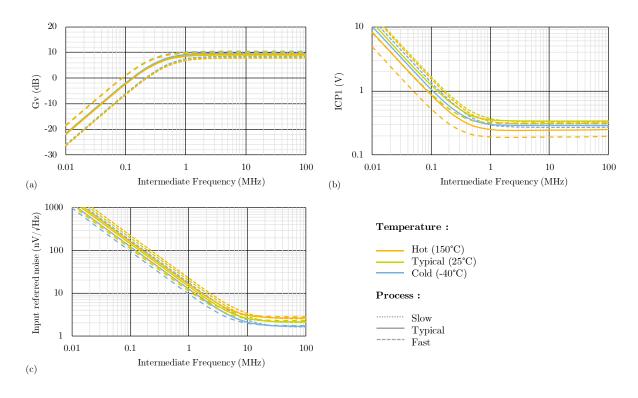

| a. Baseband analog signal processing            | 113 |

| b. Millimeter-Wave Voltage-mode Front-End       | 116 |

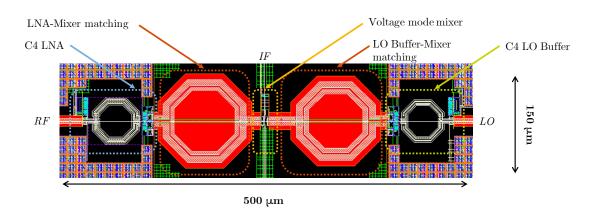

| 2. Post layout simulations                      | 117 |

| 3. Conclusion                                   | 120 |

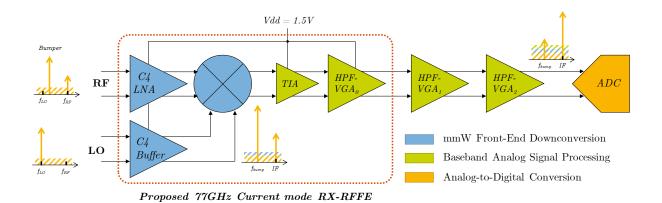

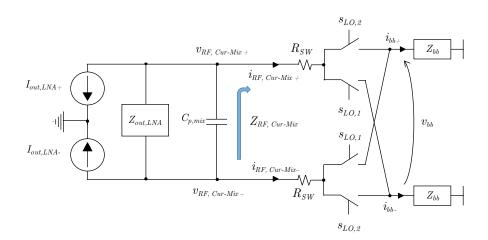

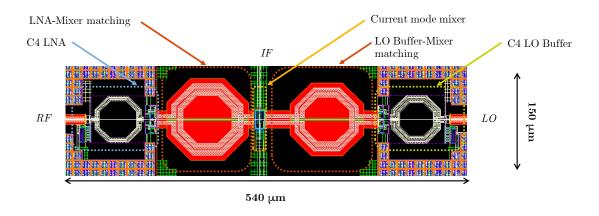

| III. Current mode downconverter                 | 122 |

| 1. Demodulation chain                           | 122 |

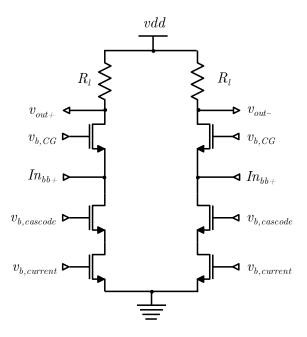

| a. Baseband analog signal processing            | 123 |

| b. Millimeter-Wave Current mode front-end       | 125 |

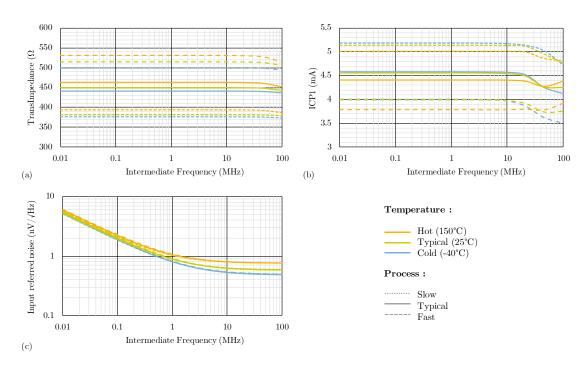

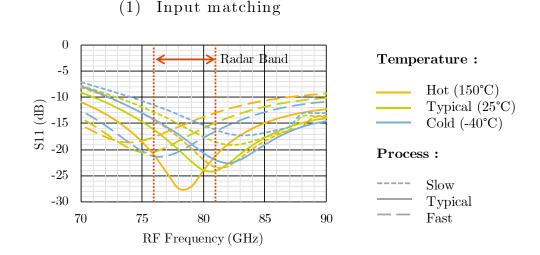

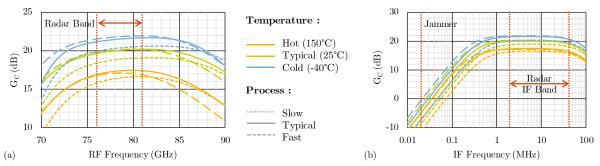

| 2. Post-layout simulations                      | 126 |

| 3. Conclusion                                   | 128 |

| IV. Conclusion                                  | 130 |

| Chapter 5. Conclusion                           | 133 |

| Bibliography                                    | 140 |

# Chapter 1. <u>77GHz Embedded</u> <u>Automotive Radar</u>

Since few decades, automotive industry moves to safer and autonomous cars. In this way, car manufacturers integrate more and more advanced driver assistance systems to monitor car vicinity. In this chapter, some generalities of radar markets are first proposed, specific focus is then proposed on modern modulations for automotive radar. The third section details the constraints and specifications of a 77GHz radar receiver. Finally, some specific points are opened in the last section.

# I. Radars in automated vehicles

Since few years, Automotive industry is hugely working on safer and more autonomous vehicles. The main trend of vehicle automation is presented in section 1 while the constraints on automotive radar are detailed in section 2. Finally, a quick description of the different automotive radars is proposed in section 3.

# 1. Introduction to automated vehicles

This section proposes a brief overview of automated vehicle and draws the context where automotive radars take place. First, a top-level outline of automation levels is first proposed. To reach vehicles to the highest level, different sensors are proposed with their own advantages and drawbacks as presented in section b. Finally, section c details the different architectures of sensor data fusion.

#### a. Automated vehicles trends

The next decades will present many challenges for automotive industries. First, safety is a major concern as 1 million people died each year in road crash due to human error [1]. Besides, traffic congestion becomes an issue for many cities and will cost more than 4 billion dollars to the western economies between 2013 and 2030 [2]. According European Commission, transportation represents 25% of all European  $CO_2$  emissions [3] while environmental issues lead to change our mobility and reduced greenhouse gas emissions. To face those challenges, Automated Vehicles (AV) are a promising solution [4]. A more efficient driving should reduce both the risk of accident and the traffic congestion. Besides, safer vehicles allow car

manufacturers to reduce the physical protections and, finally, their weight which is highly correlated to CO<sub>2</sub> emissions. Finally, AV open up to new mobility paradigms.

Figure 1 - Levels of Driving Automation defined by SAE J3016

The Society of Automotive Engineers proposes a classification of automation levels for vehicles from 0 to 5 [5]. A quick description is proposed:

- Level 0 No automation: Human driver performs all the *dynamic driving tasks*, safety features only provide warning or momentary assistance such as *Automatic Emergency Breaking*, *Blind Spot* or *Lane Departure* warning,

- Level 1 Driver assistance: Human still drive and monitor the environment but features proposes assistance for basic driving nodes like *cruise control* or *lane centering*,

- Level 2 Partial automation: The car can drive in some driving modes, but human driver must constantly monitor the environment and be ready to take control,

- Level 3 Conditional automation: Automated system can drive under limited conditions (ex. *Traffic jam chauffer*) but human must drive when feature requests,

- Level 4 High automation: The automated driving system performs all driving task in many driving circumstances,

- Level 5 Full automation: Automation system can drive anywhere in all condition using only its own systems.

#### b. Sensors in automated vehicles

To reach to SAE level 5, autonomous cars manufacturers require a continuous and ubiquitous monitoring of the car environment. To address this purpose different technologies are proposed. The most popular, reported in Table 1, are: lidar, radar and secure vehicle-to-environment communication (V2X). Since these technologies provide a unique and different benefit, they are not concurrent but complementary [6].

| Technology          | Lidar                | Radar           | $\operatorname{Camera}$ | Secure V2X      |

|---------------------|----------------------|-----------------|-------------------------|-----------------|

| Range               | Up to 200m           | Up to 300m      | ±                       | +               |

| Distance Estimation | Time of Flight       | Time of Flight  | Indirect                | Indirect        |

| Velocity Estimation | Indirect             | Direct          | Indirect                | Indirect        |

| Angular Separation  | < 0.25°              | ≈ 3°            | Megapixels              | Indirect        |

| Outdoor conditions  | Limited for weather, | Through all     | Very limited            | Through all     |

|                     | Good for night       | weathers, night | very minited            | weathers, night |

| Colour pattern      | Intensity only       | No              | Yes                     | No              |

|                     | Simultaneous         | Reliable in all | Object                  | Safe connection |

| Best for            | Localization and     | weather, speed  | classification,         | to X (Traffic   |

|                     | Mapping              | measurement     | sign reading            | Lights, cars)   |

Table 1 - Comparison of the proposed sensors for automated driving

Lidar technology uses a pulsed laser to illuminate the target and to measure the reflected pulses to evaluate the distance. Achieving high accuracy, Lidar is used to make a digital map of the car environment. Nevertheless, lidar is not yet industrialized with concurrent technologies: solid-state lidar, MEMS mirrors, optical phase arrays... and remains expensive, up to more than ten thousand euros.

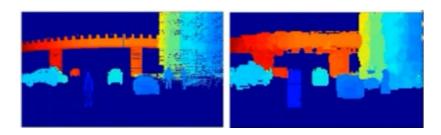

Radar systems use the reflection of Electro-Magnetic (EM) waves on objects to determine its distance, velocity and angle. Thanks to its great immunity to outdoors conditions (luminosity, rain...) and its high detection range, radar is a key element for detecting objects. To replace Lidar solutions for 3D cloud mapping, Imaging Radars (IR) are a promising solution. Implementing a Multiple-Input Multiple-Output architecture, IR provide an angular resolution lower than 1°. Even it's not as performant as lidar as illustrated in Figure 2, IR has a very competitive cost.

Figure 2 - Cloud map of car environment with Lidar and high-resolution radar [14]

The automotive CMOS image camera is a crucial sensor for automated driving. Thanks to its high megapixel resolution and the colour information, cameras are extremely superior for object recognition and classification, lane tracking, signalization analysis... Very different from consumer electronics, CMOS automotive image sensors have specific needs such as a high dynamic range, an improved sensitivity, a lower resolution, a faster response time.

In addition to other sensors, V2X can also help to automated driving by connecting the car to nearby infrastructure (traffic lights...), vehicles or pedestrians. With the exchange of data on vehicle position, traffic signal, accidents or congestions, autonomous cars can anticipate the situation and make relevant choice.

#### c. Sensor data fusion

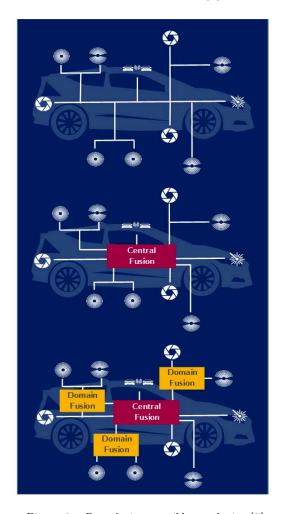

As presented in section b, each sensor technology has pro and cons. Hence a fully autonomous car requires combining the data of various sensors to improve the perception of the environment, and to improve the relevance of decision. Since few years, various systems of sensor data fusion are proposed [7].

Figure 3 – Data fusion possible topologies [7]

On *Distributed Fusion*, data fusion and decision process are done locally at sensor module level with all the data of the other sensors. This option has several disadvantages: high complexity of sensors, expensive data processing for each sensor, low level of interoperability.

On Centralized Fusion, all raw data of naive sensor are processed in a central server which also made the decision. This solution has many advantages: cheaper and simplified sensors, very accurate fusion... On the other hand, centralized fusion requires a high interoperability, a very efficient central unit and an extended bandwidth for raw data.

An intermediate solution can be found in *Hybrid Fusion* which allows both smart sensing with local data processing and central fusion. It allows for partitioning of resource effort between sensor and the central server. It reduces the cost of data distribution and maintain a good fusion accuracy.

The two last fusion models are in competition. Historic car manufacturers like Volkswagen or Renault-Nissan choose the hybrid fusion scenario which offers a good trade-off between flexibility, adaptability, complexity and cost. On the other hand, new "Californian" car manufacturers like Tesla or Weymo work on centralized fusion exploiting to its high accuracy. This situation brings to the development of adaptable sensors featuring high sensoring performances and data processing resources.

# 2. Automotive radar overview

As discussed in the previous section, automotive radar is one of the critical sensors for automotive safety and automation. This section exposes the main expectations of automotive radar, its characteristics and the different user cases.

#### a. Radar system

Radar systems were developed in the early '40 for military aeronautics and then become popular for civilian applications. As explained in 1.b, the radar is based on the emission of an electromagnetic signal with a specific signature. When the signal illuminates an obstacle, it's reflected to a receiver module which detects and computes the signal. The radar receiver can determine the time of flight and the signature modification to measure the distance to the target, its speed and even its position relative to the sensor.

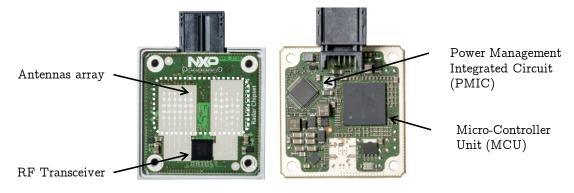

Figure 4 - Example of Radar board with a Transceiver (a), Antennas (b), PMIC (c) and MCU (d)

A complete radar module is presented in Figure 4. As isolation between transmission and emission is a critical point, a bistatic architecture is chosen with two antennas arrays as we can see on the Figure 4.b. The RF transceiver is integrated in a single chip (Figure 4.a), a detailed description of this chip is proposed in III. The two other components of a radar module are the Power Management Integrated Circuit (*PMIC*) and the Microcontroller Unit (*MCU*), respectively Figure 4.c and Figure 4.d. The second one assures the digital signal processing and is integrated in the RF Transceiver chip for the new radar generations.

#### b. Expectations of automotive radar

To maintain a high level of sensing, car manufacturers define several specifications linked to the maximum range, the resolution range, the velocity and the angular measurement. The measurement accuracy is obviously important for the determination of the target distance and velocity. Besides, the ability to recognize target signature, throughout its radar cross section, is critical for classification. If two targets are closed, the object separation is a critical parameter to distinguish one target from another. Besides the ability to echo detection is critical

in the case where target echo is masked by unexpected large signals such as interferers, large echoes, jamming...

Additionally to RF performances, the radar is supposed to be used over several decades of years in very different conditions such as desert, mountain roads... Hence the robustness and the reliability are also important metrics in the development of radar modules.

#### c. Spectral occupation

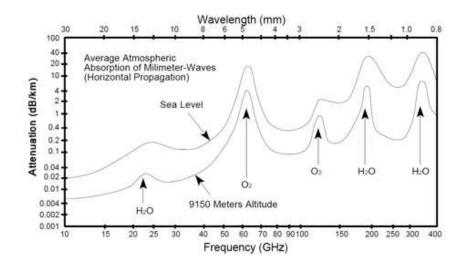

In radar applications, frequency is a key parameter since it contributes to the performance, field of use and form factor. The increase of the operating frequency, and bandwidth as well, improves the skills. For this reason, industry has pushed up to operate automotive radar in millimeter Waves frequency band. In this domain, H<sub>2</sub>O and O<sub>2</sub> absorption has a strong impact on atmospheric attenuation, as illustrated in Figure 5. Since the attenuation is critical for the application, radar band are positioned in low absorption frequency band such as 24GHz and 76 to 81GHz.

Figure 5 - Atmospheric attenuation in mm-Waves domain [8]

#### d. Automotive Radar Standards

In European Union, the European Telecommunications Standards Institute oversees the standardization of telecommunication industry. The ETSI defines the European Standards noted EN in link with International Telecommunication Union and national administrative authorities. These standards are only related to spectral occupation and level of emissions/receptions of RF signals. For automotive radar, the different European standards are proposed in Table 2 and based on measurement techniques which are defined in ETSI EN 303 396 [9]. All metrics are related to transmitted/received RF signals of the overall radar module, including antennas. This metrics are given for in-band signals, signals closed to RF band called "out of band" and for spurious in remote-band.

Spurious

in-band

out-of-band

remote-band

Emissions (dBm EIRP)

Signals handling at 10m

(dBm EIRP)

| Standards          | Band        | EN 302     | EN 301 | EN 302                |

|--------------------|-------------|------------|--------|-----------------------|

|                    | Bana        | 858        | 091    | 264                   |

| Frequency (GHz)    | /           | 24.05-24.5 | 76-77  | 77-81                 |

| Mean Power (dBm)   | in-band     | /          | 50     | $-3~\mathrm{dBm/MHz}$ |

| Peak Power (dBm)   | in-band     | 20         | 55     | 55                    |

| Unwanted emissions | out-of-band | 10         | 0      | -30                   |

| (dBm EIRP)         | Spurious    | -30        | -30    | -30                   |

-47

0

10

10

-47

10

20

20

-47

10

20

20

Table 2 – ETSI Automotive Radar standards from [10], [11] and [12]

#### Radar applications in automated vehicles 3.

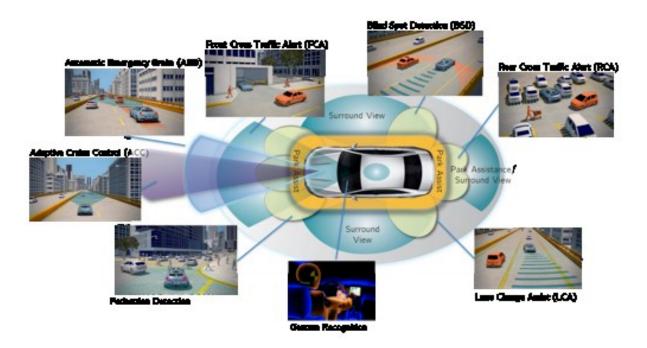

Figure 6 – Radar applications in automated vehicle

The flexibility and the reliability of radar technology are attractive for a large scope of detection scenarios as illustrated in Figure 6. In practice, three kinds of radar modules are exploited in the automotive industry: Long Range Radar (LRR), Medium Range Radar (MRR) and Short-Range Radar (SRR). Their specifications are reported in Table 3 and further discussed in the next sub-sections.

Table 3 - Typical LRR, MRR and SRR specifications [13]

| Radar type                                       | LRR                | MRR                | SRR                |

|--------------------------------------------------|--------------------|--------------------|--------------------|

| R Range (m)                                      | 10 to 250m         | 1 to 100m          | 0.15  to  30  m    |

| $\Delta R$ Range resolution (m)                  | $0.5 \mathrm{m}$   | $0.5 \mathrm{m}$   | 0.1m               |

| $\delta R$ Range accuracy (m)                    | 0.1m               | 0.1m               | $0.02 { m m}$      |

| $\Delta v$ Velocity resolution (m/s)             | $0.6\mathrm{m/s}$  | $0.6\mathrm{m/s}$  | $0.6\mathrm{m/s}$  |

| $\delta v$ Velocity accuracy (m/s)               | $0.1 \mathrm{m/s}$ | $0.1 \mathrm{m/s}$ | $0.1 \mathrm{m/s}$ |

| $\phi_{max}$ 3dB beamwidth in azimuth (°)        | 15°                | 40°                | 80°                |

| $\delta \phi$ Azimuth angular resolution (°)     | 0.1°               | $0.5^{\circ}$      | 1°                 |

| $\vartheta_{max}$ 3dB beamwidth in elevation (°) | 5°                 | 5°                 | 10°                |

### a. <u>Short Range Radar (SRR)</u>

Shorts range radars are designed to monitor the car vicinity and detect targets within 80 meters. Thanks to the use of numerous SRR, it's possible to create a 360° safety cocoon around the car with several applications such as surround view, pedestrian detection, park assist or side impact detection. To address these various applications, SRR has a high azimuth aperture angle, up to 90°, and need a high spatial resolution to detect simultaneously several targets. However, as autonomous cars are supposed to used more than ten radar modules, the power consumption and the price of SSR modules are critical.

# b. Medium Range Radar (MRR)

Many applications such as blind spot detection, rear or forward cross traffic alert or autonomous emergency braking needs medium range radar with a higher detection range up to 160-m but a lower angular aperture. MRR performances represents a trade-off between SRR and LRR ones.

# c. <u>Long Range Radar (LRR)</u>

Long range radars need to detect long distant targets up to 300 meters. The applications such as lane change assist, adaptive cruise control need a very narrow field of view with a small horizontal angle, around  $5^{\circ}$ , with strong constraints on object separation or angular resolution. For instance, a  $0.1^{\circ}$  accuracy is needed for spatial resolution. Due to these constraints, radar transmitter is supposed to generate a signal with a high effective isotropic radiated power (EIRP) whereas the receiver is expected to achieve a high sensitivity. This metric denotes the ratio between signal power and noise power and it's a key parameter to define RF performances of a radar system.

# II. FMCW Modulation Basics

The radar industry develops many modulations: pulsed radar, continuous wave, FSK modulation... Frequency Modulated Continuous Wave (FMCW) modulation is still dominant in ADAS. This technique is based on "chirps", a continuous signal whose frequency varies linearly with time, which gives to FMCW some advantages:

- Easy generation of the transmitted signal,

- Simultaneous measurement of target distance and velocity with a good resolution,

- Simple baseband for signal processing at few MHz,

- Low peak power constraint compared to pulsed radar.

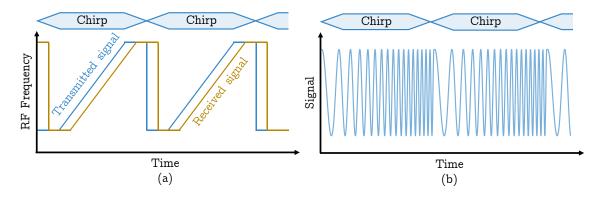

Figure 7 - FMCW modulation among time in frequency domain (a) and signal for transmitted signal (b)

Widely used for automotive radar, the saw tooth pattern modulation is illustrated in Figure 7.a. When the chirp transmitted signal illuminates an object, it creates a reflected attenuated signal at radar receiver input with some propagation delay. An illustration of signal variation in time domain is also proposed in Figure 7.b. This section details the measurement techniques for the estimation of the distance and the velocity of a target in an FMCW radar system. The main trends in FMCW signal characteristics for modern ADAS applications and their impact on Receiver characteristics are further discussed.

# 1. Distance measurement

Figure 8 – FMCW modulation for Automotive Radar regarding the (a) RF Frequency and (b) the frequency difference f<sub>beat</sub>

For all radars, the time of flight of the signal measures the target distance and, with FMCW modulation, is easy to relate to signal characteristics. Illustrated in Figure 8, the distance between the target and the radar module is equivalent to the measurement of frequency difference between emission and reception.

Equation 1 - Range (R) measurement for Linear FMCW radar

$$R = \frac{C}{2} \Delta t \iff R = \frac{C}{2} \frac{T_{chirp}}{BW_{chirp}} f_{beat}$$

The Table 4 details the link between distance measurement performances key indicators and the signal characteristics. In modern ADAS applications, radars are expected to measure distant target with a high resolution and a good accuracy. For instance, a modern radar must be able to identity pedestrians over a long range and possibly close to a larger vehicle.

| Performance parameter | Equation                                                           | Conditions                                                                                              |

|-----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Maximum range         | $R_{max} = \frac{C}{2}  \frac{T_{chirp}}{BW_{chirp}} f_{beat,max}$ | Depending on maximal $f_{beat,max}$ measurement                                                         |

| Range resolution      | $\Delta R = \frac{c}{2  BW_{chirp}}$                               | As $\Delta f = \frac{2  \Delta R  BW_{chirp}}{c  T_{chirp}}$ and $\Delta f \approx \frac{1}{T_{chirp}}$ |

| Range accuracy        | $\delta R = \frac{c}{3.6  BW_{chirp} \sqrt{2  SNR}}$               | Fraction of range resolution depending of SNR                                                           |

Table 4 - Target distance measurement performances (SNR: Signal-Noise-Ratio)

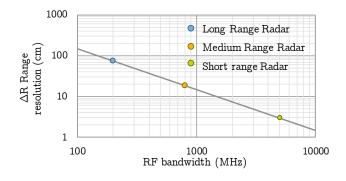

Two major trends exist to improve the performance of the measured distance. First, RF chirp bandwidth is increased to improve range resolution and accuracy. For instance, a 1GHz bandwidth achieve a resolution of 15cm, a 4GHz bandwidth improves it to 4cm. Modern fast chirp modulation leads to reduce chirp time thus increases the maximum measurable frequency difference ( $f_{beat}$ ). In consequence, RF wideband receivers with higher baseband Intermediate Frequency (IF) are needed.

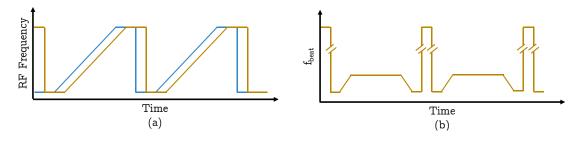

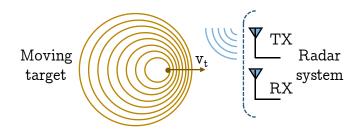

# 2. Velocity measurement

Figure 9 - Example of Doppler effect

When the receiver and the target, which is considered as a wave source, are in motion, the Doppler effect corresponds to an alteration of the received signal frequency. When the target approaches (or recedes) from the radar, each successive emitted wave travels further (or farther) before impacts the car and be reflected to radar receiver as presented in Figure 9. Due to this effect, the wave distance decreases (or increases) and is interpreted as an increase (or a decrease) of the measured frequency. One of the key advantages of automotive radar is the measurement of target velocity thanks to the Doppler effect. This section details the velocity measurement techniques in FMCW Radar and especially the recent change due to recent evolution to fast chirp modulation.

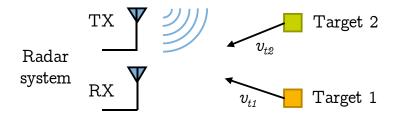

Figure 10 - Two targets situation

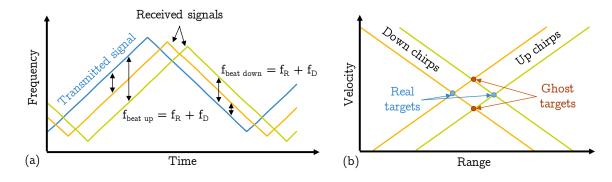

In slow chirp measurement with a chirp duration of 1ms, the velocity measurement is performed with a triangular signal. The frequency difference between emission and reception is shifted by the Doppler frequency f<sub>D</sub>. However, in a situation with multiple targets illustrated by the Figure 10, slow chirp FMCW has a problem of ambiguity as shown Figure 11. For the resolution, four crossing points of range and velocity are measured. It induces the presence of two ghost targets. In consequences, slow chirp FMCW modulation is no longer preferred for modern ADAS radars.

Figure 11 – Slow chirp FMCW modulation in a case with multiples targets for (a) transmitted and received signals and (b) velocity and range system resolution

Due to this ambiguity, modern ADAS applications prefer fast chirp FMCW modulation where the emission is done with a frame of N chirps with small duration of few microseconds. This measurement method enables an accurate estimation of distance and velocity without ambiguity as presented in Figure 12.

Figure 12 – FMCW processing flow of received signal with the (a) RF signal; downconverted to (b) baseband signal; and its (c) interpretation by a 1st FFT to determine the range; and (c) a velocity estimation thanks to a second Doppler FFT

In fast chirp modulation, the Doppler frequency is neglectable in front of the distance measurement frequency. Therefore, the range calculation is made with a first Fast Fourier Transform (FTT) on the downconverted signal to calculate  $f_{beat}$ . The phase of the received signal embeds the Doppler frequency information. Thanks to a second FFT, it's possible to calculate the target velocity with the phase difference between two chirps.

Equation 2 - Measurement of velocity with a fast chirp modulation

$$s(t) = f(f_{beat}t + \Delta\phi_r)$$

with  $\Delta\phi_r = \frac{4\pi v T_{chirp}}{\lambda}$

To avoid any ambiguity between equidistant objects with different velocities, the fast FMCW uses a frame of N chirps. Each chirp has a different phase embedding the phase information of each target. A second FFT, called Doppler-FFT, is made on this N-system and separate the contributions of each objects. It allows the measurement of their velocity without ambiguity as expressed in Equation 3.

Equation 3 - Velocity measurement at Doppler FFT output

$$v_i = \frac{\lambda \, f_{v\,i}}{2 \, T_{chirp}}$$

The Table 5 presents the performance assumptions on velocity measurement for modern ADAS. As fast targets should be detected, the chirp time should be small enough. In the same time, an important frame time, corresponding to numerous chirps, is done to maintain a good velocity resolution and a better accuracy.

| Table 5 - | Velocity | measurement | performances |

|-----------|----------|-------------|--------------|

|-----------|----------|-------------|--------------|

| Performance         | Equation                                                   | Conditions                                                   |

|---------------------|------------------------------------------------------------|--------------------------------------------------------------|

| Maximum velocity    | $v_{max} = \frac{\lambda}{4  T_{chirp}}$                   | Unambiguous measurement for $ \Delta \phi  < \pi$            |

| Velocity resolution | $\Delta v = \frac{\lambda}{2  T_{chirp}  N}$               | Unambiguous measurement for $\Delta \omega > \frac{2\pi}{N}$ |

| Velocity accuracy   | $\delta v = \frac{\lambda}{3.6  T_{chirp}  N  \sqrt{SNR}}$ | Fraction of velocity resolution depending in SNR             |

# 3. <u>Conclusion</u>

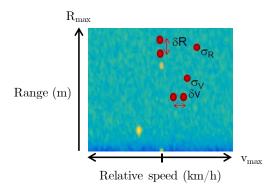

Figure 13 – 2-D image of car vicinity in a situation with multiple targets and the ley parameters of radar performance expecting the angular ones [14]

In conclusion, modern ADAS applications are now moving to fast chirp FMCW modulation which allows non-ambiguous measurement of distance and velocity of different targets in the same environment. This resolution is performed by an important digital processing and can propose a 2D image of the car environment as shown in Figure 13. To maintain a high unambiguous velocity measurement, a chirp duration between 20 and 50µs is mandatory. Increasing the range resolution is also critical for vehicle automation as discussed in section 2.b. This trend leads to increase the RF bandwidth as illustrated in Figure 14.

Figure 14 - Improving the range resolution regarding the RF bandwidth;

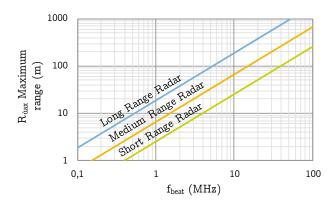

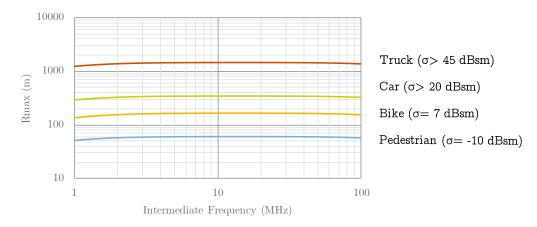

Considering the characteristics of the various radars exposed in the Table 3, the Figure 15 proposes the maximum archivable range regarding the  $f_{beat}$  frequency. In the range of ten microseconds, and for distant target,  $f_{beat}$  increase up to 40MHz. These trends make more challenging the analog signal processing in baseband sections and lead to faster RF bandwidth.

Figure 15 - Maximum range regarding the beat frequency

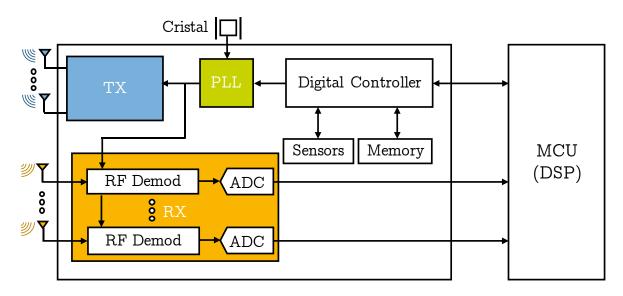

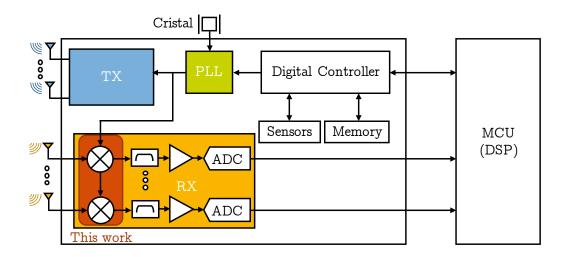

# III. 77 GHz FMCW Radar IC

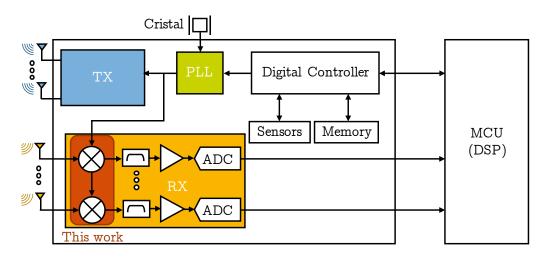

A high-level description or radar module is first presented in this section. The RF metrics are then discussed with respect to the radar performances. A radar module is presented in Figure 16. It includes some digital or analog parts such as digital controller, memory, sensors, power management; but also, the RF Front-End (RFFE) with the Phase-Locked Loop generating the Local Oscillator (LO), the transmitter (TX) and the Receiver (RX). This one is composed with a RF Demodulator (DEMOD) and an analog-to-digital converter (ADC).

Figure 16 - Architecture of automotive radar module [17]

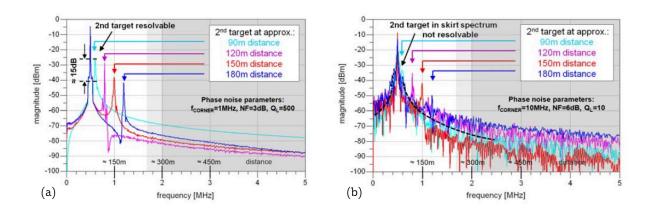

The transmitted signal is generated by a Phase-Locked Loop which features chirp linearity and phase noise which directly impacts the object separation [15]- [16]. As illustrated in Figure 17, considering 15dB SNR, the object separation cannot be resolved if the phase noise is too high (Figure 17.(b)). Indeed, the maximum range of detection is determined by the radiated power as illustrated in Equation 5. As consequences, the TX is expected to yield a high output power  $P_{TX}$ , +12dBm at least, which is challenging regarding the operating frequency, the technology capabilities and reliability issues.

Figure 17 – Simulation of the influence of phase noise on target signal quality when a distant target approaching to a 75m object considering a LO with: (a) a low phase noise; (b) a high phase noise [15]

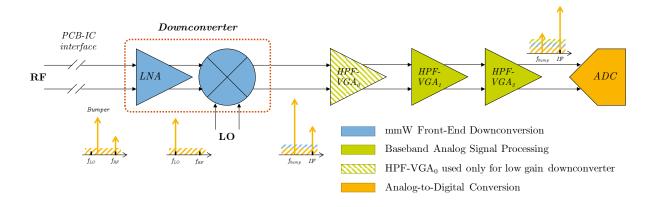

The third critical block for the RF Transceiver is the RX section featuring the RF Demodulator which downconverts the RF signal and formats the baseband signal for the ADC. The Analog-to-Digital Converter (ADC) transforms the analog signal into digital data which are further processed by the Micro Processor Unit. A detailed description of the RF Demodulator is proposed in the section 1.b. In this chain, the RF downconverter is critical, and this section focus on its main specifications: gain, noise and linearity. In the following sections, the terms downconverter and RX-RFFE will be used as equivalent.

# 1. Noise in automotive radar [17]

As shown in Figure 5, atmospheric losses are negligible at 77GHz and the losses are mainly due to natural dispersion of the EM wave. The purpose here is to determine the maximum range due to the signal treatment. Three phenomena are then considered: the propagation of radar signal considering radar module characteristics, the noise distribution overall the demodulation chain, the de-sensitization of the receiver due to cross-talk between transmission and reception.

#### a. Maximum range regarding the demodulator NF

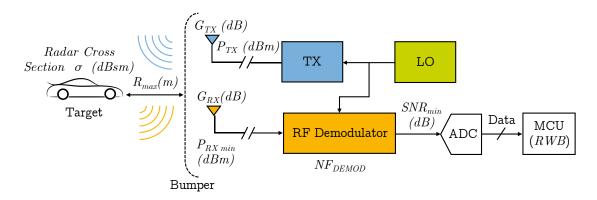

Figure 18 - Schematic of radar signal attenuation in use case

An illustration of the radar emission/reception is proposed in Figure 18. As expressed in section 3, the Radar standards define the transmitted power noted  $P_{TX}$ , including the TX output power, the number of transmitters, the PCB losses, and the transmission antenna gain  $G_{TX}$ . The antenna gains are calculated thanks to antenna characteristics (Table 3) and gain formula from [18]. On the other hand, the receiver needs a minimum input power called sensitivity noted  $P_{RX,min}$ , to properly process the signal. The Equation 4 links the maximum achievable range to these parameters.

Equation 4 - Radar maximum achievable range

$$R_{max}(m) = \left(\frac{P_{TX}G_{TX}G_{RX}\lambda^2\sigma}{(4\pi)^3P_{RX,min}}\right)^{0.25}$$

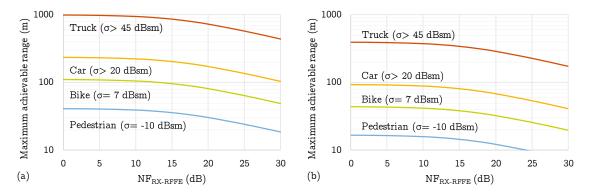

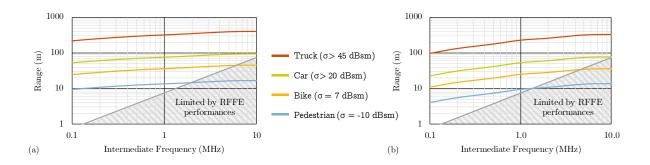

The Radar Cross Section  $\sigma$ , expressed in m<sup>2</sup> or dBsm [dB(m<sup>2</sup>)], represents the target signature and depends on the target size, its physical properties and its shape. In Table 6, some common targets radar cross sections are proposed:

Table 6 - Common radar cross section for specific targets [19]

| Target Type | $\sigma  (\mathrm{dBsm})$                                                |

|-------------|--------------------------------------------------------------------------|

| Pedestrian  | -10                                                                      |

| Bike        | 7                                                                        |

| Car         | $\text{Maximum } \{10 \text{ log } (\text{Range } (\text{m})) + 5; 20\}$ |

| Truck       | $\text{Maximum } \{20 \text{ log } (\text{Range } (\text{m})) + 5; 45\}$ |

The MCU performs an FFT of the data with a resolution (RBW) as illustrated in Figure 18. To execute this signal processing, a minimum Signal-on-Noise Ratio  $(SNR_{min})$  is required at ADC input. The SNR<sub>min</sub> is linked to  $P_{RX,min}$  by the Equation 5 which defines the receiver

sensitivity from noise floor at -174dBm accounting the noise contribution of the RF demodulator represented by its noise figure NF<sub>DEMOD</sub>.

$Equation \ 5 - Sensitivity \ definition \ for \ a \ receiver$

$$P_{RX,min}(dBm) = -174dBm + NF_{DEMOD}(dB) + 10\log(RBW) + SNR_{min}(dB)$$

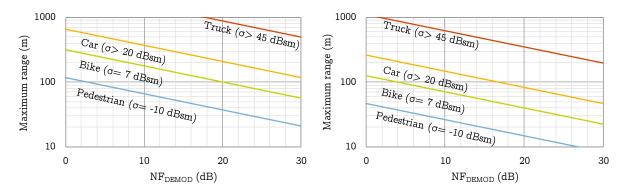

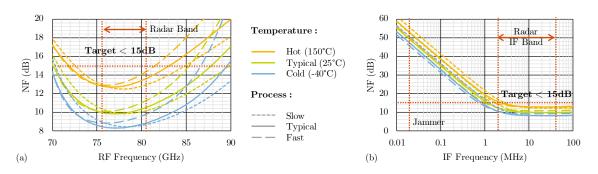

Considering these two equations, a top-level specification on the maximum range define the maximal NF of the RF demodulator as proposed in Figure 19. In short range use case, a 20 dB NF<sub>DEMOD</sub> is expected to target at 80m. In long range use case, the maximal measurable distance should be higher than 200 meters, such feature leads a NF<sub>DEMOD</sub> at 17dB. These noise specifications may appear as relaxed, but it should consider the noise distribution overall the all demodulator chain and the NF de-sensitization. These two elements are discussed is the following sections.

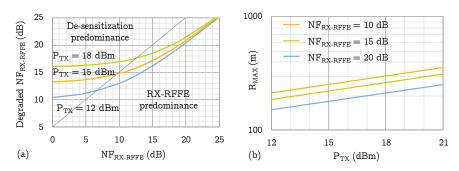

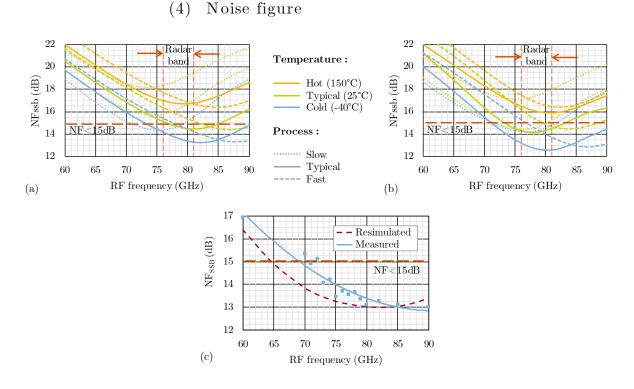

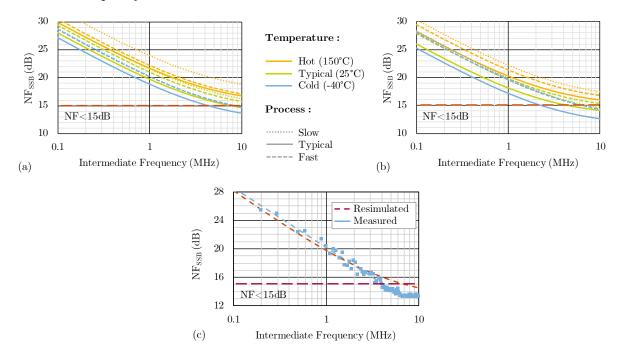

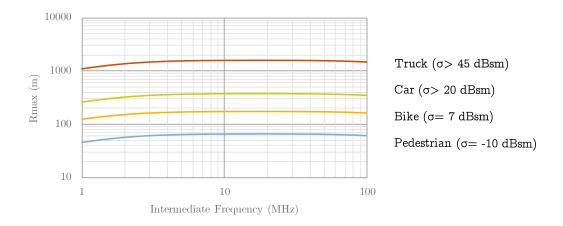

Figure 19 – Maximum achievable range of various targets regarding the RF demodulator NF for (a) long range radar and (b) short range radar

#### b. Noise distribution on RF demodulator chain

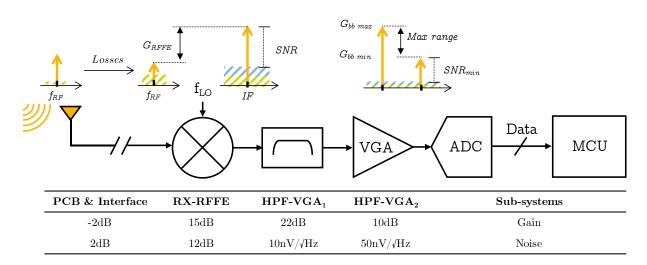

Figure 20 - Signal processing and noise distribution throughout the RF demodulator

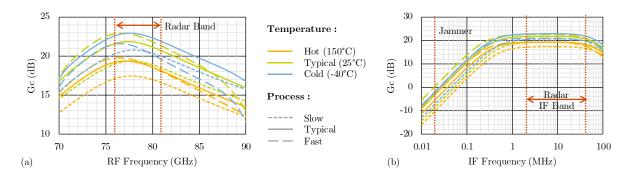

The Figure 20 proposes an illustration of the overall architecture of the RF demodulator. The interconnection of the antennas to the IC, the PCB routing and the interface directly impacts the noise performance due to losses which are estimated to 2dB. The RX-RFFE downconverts the RF signal to baseband domain from 1 to 40MHz. Analog filtering eliminates out-of-band jammers, and the Variable Gain Amplifier (VGA) improves the dynamic range of the signal at ADC input. The Figure 20 also presents an evaluation of the noise contribution and gain of the different blocks. Based on the Friis formula for a cascaded chain of blocks, from Equation 6, the noise factor  $F_{DEMOD}$  can be derived.

Equation 6 - Friis formula for the RF demodulator considering noiseless filter

$$F_{DEMOD} = F_{RX-RFFE+PCB} + \frac{\left(e_{n,VGA1}\right)^{2}}{k_{B}T Z_{S} \left(G_{PCB} + G_{RX-RFFE}\right)} + \frac{\left(e_{n,VGA2}\right)^{2}}{k_{B}T Z_{S} \left(G_{PCB} + G_{RX-RFFE} + G_{VGA1}\right)}$$

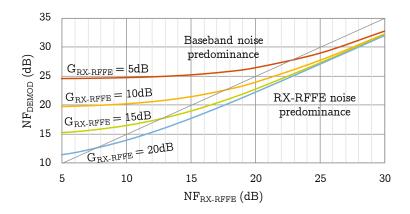

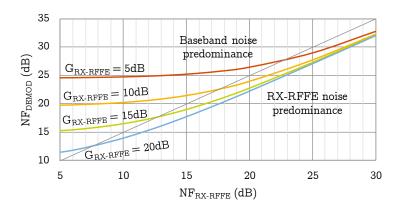

The Figure 21 presents the noise performance of RF demodulator regarding the gain and noise figure of the RX-RFFE, considering the baseband characteristics exposed in the Figure 20. Conventional downconverters have a noise figure from 10 to 16dB in the worst case. Considering this typical value, the impact of RX-RFFE gain is critical. According to Figure 21, G<sub>RX-RFFE</sub>, should exceed 10dB to significantly moderate the noise contribution of baseband circuit to NF<sub>DEMOD</sub>. In the following analysis, a gain of 12.5dB will be considered.

$Figure\ 21-RF\ Demodulator\ noise\ performance\ regarding\ RX-RFFE\ characteristics$

#### c. Noise figure de-sensitization

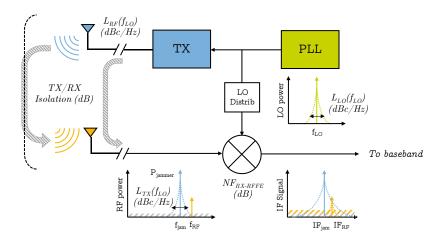

Considering the reflecting effect of a bumper and the coupling through the PCB, the isolation between TX and RX is estimated at 35dB. The lack of isolation creates a jammer  $P_{jammer}$  at RX input defined by the Equation 7.

Equation 7 - Jammer due to lack of isolation

$$P_{iammer}(dBm) = P_{out}(dBm) - Isolation (dB)$$

Figure 22 - NF de-sensitization phenomenon due to uncorrelated phase noise and isolation

Due to the different paths between the LO distribution to RX and TX, uncorrelated phase noise appears between both paths. This phase noise is evaluated to -144dBc/Hz. Hence, the downconverter jammer presents an important noise skirt modeled by a noise source  $e_{degrad}$  defined in Equation 8.

Equation 8 - Noise degradation due to de-sensitization

$$e_{dearad}^{2}(mW/Hz) = P_{iammer}(mW) \cdot (10^{L_{TX}(dBc/Hz)} + 10^{L_{LO}(dBc/Hz)})$$

This additional noise source can significantly degrade the noise figure of the downconverter as illustrated in Figure 23.(a). This expansion of noise figure is particularly important for low noise RX-RFFE but reduced as the NF increases. Considering a 12dB noise figure, this degradation is limited to 2dB for a +12dB output power, which is equivalent to one TX enable, but it rises to almost 5dB if four TX are on ( $P_{TX} = +18dBm$ ). This noise desensitization phenomena must be considered evaluating the overall performance of the radar in receiver mode. Nevertheless, as shown in Figure 23(b), the increase of the transmitted power  $P_{TX}$  remains a possible solution to improve the radar range.

Figure 23 – Effect of de-sensitization on (a) Noise figures for various transmitted powers; (b) Maximum achievable range regarding the transmitted power for various NF<sub>RX-RFFE</sub>

#### c. Conclusion on noise specifications

The proposed analysis allows to define a specification of the maximum detection range with an associate NF for the RF demodulator. The overall noise budget must account for distributed contributions such as PCB losses, IC interface, the RF Front End and the baseband circuits. The RFFE de-sensitization due to the lack of isolation between TX and RX and the uncorrelated phase noise in the LO distribution must be also considered. Accounting for these noise phenomena, we determine the maximum achievable range regarding the RX-RFFE noise figure for the short- and long-range use cases as illustrated in Figure 24.

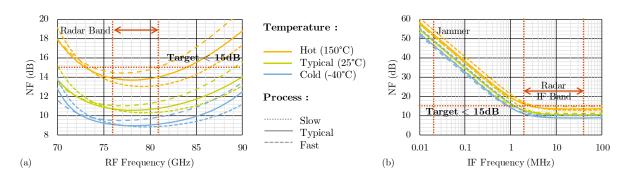

Figure 24 - Maximum range regarding the RFFE noise figure for various targets for (a) long range applications; (b) short range applications

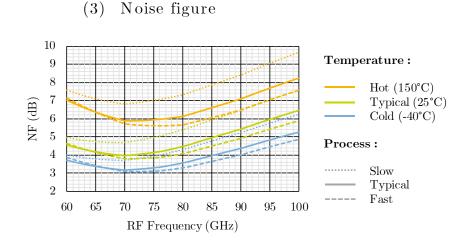

The downconverter noise figure is a key indicator of the radar performance. To address long range or even imaging radars use cases, the RX RF Front-End may achieve a 12dB noise figure at 150°C in the worst case. For short range use cases, the noise specification is relaxed to 15dB.

# 1. <u>Linearity in Automotive Radar [20]</u>

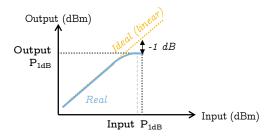

For an ideal Front-End, the output signal is a linear image of the input signal. Unfortunately, the downconverter introduces some distortions which corrupt the original signal. These non-linearities are further discussed in this section.

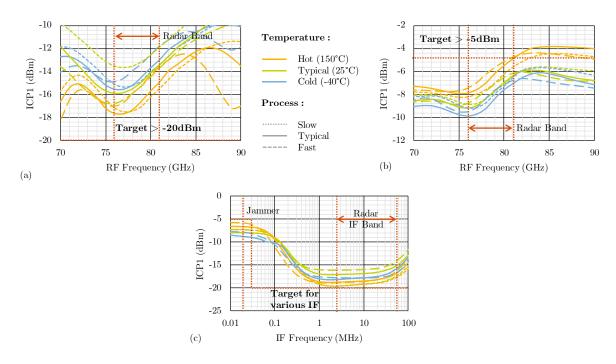

# a. In-band linearity (ICP1)

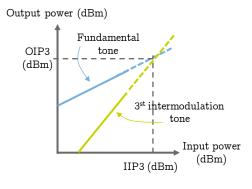

Figure~25-1dB~compression~point~definition

Equation 9 - In band compression point specification

$$inband P_{1dB}(dBm) = OP_{max} - G_{RX} \approx -20 dBm$$

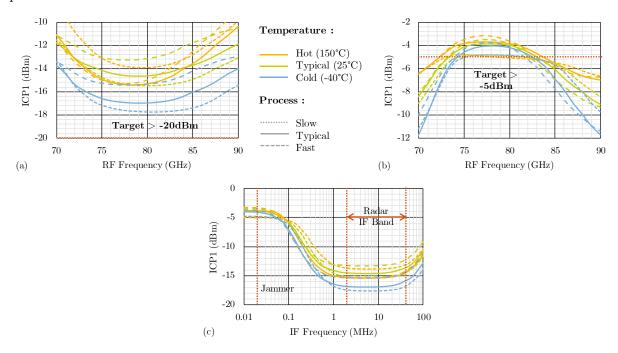

Any RX-RFFE behaves linearly up to a level of input power which drives then the system in saturation as illustrated in Figure 25. Entering the non-linear mode, the received signal is corrupted and the information cannot be retrieved. The linear region is defined by the -1dB compression point (*CP1*) which can be referred at the input (ICP1) or at the output. In automotive radar, the in-band compression point, due to target reflection, is defined by the Equation 9 considering the total gain of the Receiver chain. In our case, we consider it around -20dBm in the worst case.

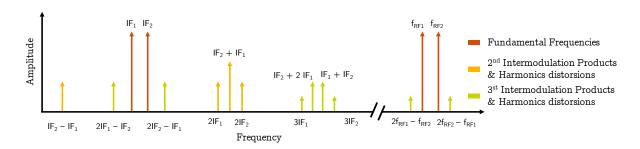

#### b. Intermodulation (IIP3)

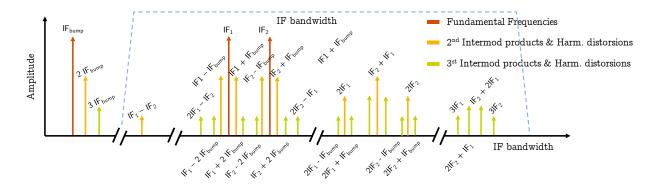

Figure 26 - Intermodulations & distorsions products in real downconverter

Most of the time, several targets are present in the radar scope. It leads to several inband signal with different frequencies at RX input, i.e. at fundamental frequencies  $f_{RF1}$  and  $f_{RF2}$ . A linear receiver is supposed to process and to transfer signal at these two harmonics only. A real receiver will be affected by a mixing effect. It leads to create in-band intermodulation products as illustrated in Figure 26, i.e.  $2^{nd}$  and  $3^{st}$  intermodulation productions (IP2 & IIP3) and  $2^{nd}$  and  $3^{st}$  harmonic distortions. Most of them are filtered out by the system but the third order intermodulation,  $2f_1$ - $f_2$  and  $2f_2$ - $f_1$ , are located in the radar bandwidth. These harmonics can be interpreted as spurs and leads to identify ghost targets.

Figure 27 - IIP3 definition

The third order intercept point (IP3) is a figure-of-merit which evaluate this intermodulation. The IP3 is a hypothetical point at which the power of the third order harmonic rise to the fundamental harmonic power. This parameter can be referred at the input (IIP3) or at the output. The in-band IIP3 specification is expressed in Equation 10 considering the RX chain gain and is estimated at -26dBm.

Equation 10 - In band IIP3 specification

Inband IIP3

$$(dBm) = 16 - G_{RX} \approx -26 dBm$$

#### c. Bumper impact on linearity (ICP1)

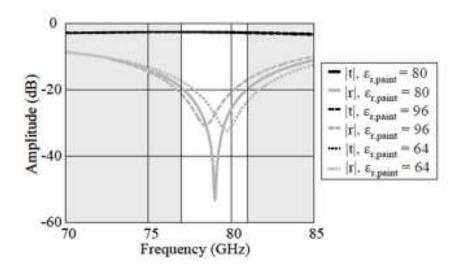

According equations Equation 9 and Equation 10, the intrinsic specifications for inband linearity of a radar RX are not tough. However, these two equations don't consider the environment of radar in the car. As radars antennas are mounted behind bumpers, the transmitted signal may be reflected by the bumper to the radar receiver. Intensive researches investigate the development of invisible bumpers, so far the reflection is limited to -20dB over the entire 76-81GHz band as shown in Figure 28.

$Figure\ 28-Transmission\ and\ reflection\ through\ a\ bumper\ with\ metallic\ paint\ [21]$

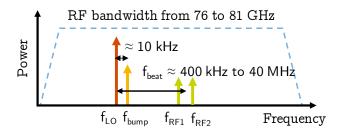

Due to the bumper proximity, a high power reflected signal is presented at the receiver input with a very small frequency shifting, evaluated at 10kHz around the transmitted frequency. Unfortunately, this signal can't be filtered out as illustrated in Figure 29. The bumper blocker is further downconverted and processed in baseband.

Figure 29 - Spectrum at Front-End input

The presence of the in-band blocker, located at f<sub>bump</sub> as illustrated in Figure 29, is an important issue for downconverter linearity. First, the LNA should not be placed in saturation mode. Besides, if one or two tones are present at the input, important intermodulation products will be created as illustrated in Figure 30. These spurs can be considered as targets by the MCU. The ghost targets are obviously a major issue in automated vehicles. To handle this major issue, the 1dB compression point specification is revised to -5dBm.

Figure 30 - IF spectrum with intermodulations due to bumper

# 2. <u>Conclusion</u>

Radar IC is a complex system with some specific constraints related to the application and its environment. At commercial stage, four key specifications are critical regarding the competitor in semiconductor industry: the form factor (price, size and consumption), the transmitted output power, the PLL phase noise and the Noise Figure of the RX chain. More specifically the development of the downconversion part of a radar module would address some challenges to be competitive. One is related to the linearity due to the close location of the bumpers. Beside the sensitivity of the radar requires not only a low NF but also a large conversion gain. These two characteristics would be improved with a reduced impact on the overall power consumption. The Table 7 sums up some of the important specifications of a radar RX-RFFE.

Table 7 - Specifications of receiver RF front-dnd

| Specifications          | Min | Тур | Max |

|-------------------------|-----|-----|-----|

| RF bandwidth (GHz)      | 76  |     | 81  |

| IF bandwidth (MHz)      | 1   | /   | 40  |

| Noise figure (dB)       |     |     |     |

| For LRR                 |     |     | 15  |

| For SRR                 |     |     | 17  |

| ICP1 (dBm)              | -5  |     |     |

| Passband ICP1 (dBm)     | -20 |     |     |

| IIP3 (dBm)              |     | -26 |     |

| LO-to-RF Isolation (dB) |     |     | -35 |

| Objectives              | Min | Тур | Max |

| Conversion Gain (dB)    |     | 10  |     |

| Power consumption (mW)  |     | 20  |     |

# IV. Considerations on receiver RFFE for automotive radar

As discussed in previous section, the RX specifications are challenging and as consequences, the receiver is a critical block for automotive radar. This section focusses on the selection of the technology for the next generation radar, which will have an impact on RX-RFFE possible architecture.

# 1. RF CMOS opportunities

Automotive radars were originally designed in III-V GaAs technologies. As shown in Table 8, they presented good performances in terms of gain, cut-off frequency or temperature behavior which are critical for 77GHz radar applications. Nevertheless, III-V technologies are expensive and do not offer a large scale of integration for digital processing. For these reasons, III-V technologies were reserved for luxurious car with an implementation based on discrete components, whereas semiconductor industry is moving to Silicon technologies for mass market products.

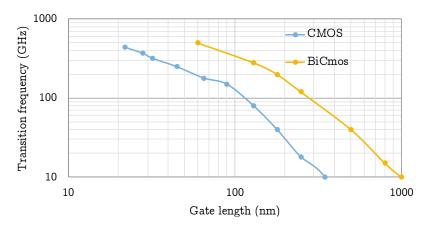

The two historic market leaders (NXP and Infineon) have selected BiCMOS technology on Silicium-Germanium substrate for their products thanks to their good trade-off between integration level and RF performances. As shown in Figure 31, BiCMOS technologies can achieve high transition frequencies with good performances. Nevertheless, modern ADAS do

not only require good RF performances but also a high level of integration and a low-cost production. On one hand, as discussed in 1.c, digital functions are included in radar chip and semiconductor manufacturers are considering the integration of the MCU and radar transceiver. On the other hand, as expressed in 3, radar modules are about to be massively deployed in modern cars, so the price of radar IC become critical.

| ·                    |           |                       |                       |  |

|----------------------|-----------|-----------------------|-----------------------|--|

| Technology           | CMOS      | BiCMOS<br>(SiGe)      | III-V<br>(GaAs)       |  |

| Transition frequency | Medium    | $\operatorname{High}$ | Very High             |  |

| Breakdown voltage    | Low       | ${f Medium}$          | $\operatorname{High}$ |  |

| Power gain           | Medium    | $\operatorname{High}$ | Very High             |  |

| Temperature behavior | Poor      | Good                  | $\operatorname{Good}$ |  |

| Integration level    | Very High | Medium                | Very Low              |  |

| Cost                 | Low       | Medium                | High                  |  |

Table 8 - Comparison of integrated technologies

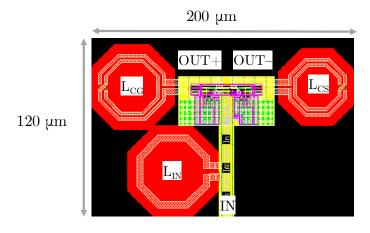

These trends push the semiconductor industry is moving to consider CMOS technologies for the implement of the next generations of radar modules. As illustrated in Figure 31, recent advanced RF CMOS technologies are now compatible with 77GHz radar constraints, especially regarding the transition frequency which exceeds 300GHz for technology nodes below 50 nm. The circuits proposed in this manuscript are developed in a 28nm CMOS process. The technology back end is illustrated in Figure 32. The three tick upper metal layers (AP, M8, M7) are used for RF routing. The six thin lower metal layers (M1 to M6) are basically used for digital blocks.

Figure 31 – Transition frequencies of CMOS & BiCMOS technologies

Figure 32 - 28nm CMOS technology back-end

# 2. mmW Front-End architecture

# a. RFFE Basics

Figure 33 - Radar mmW Front End in 180 BiCMOS technology [17]

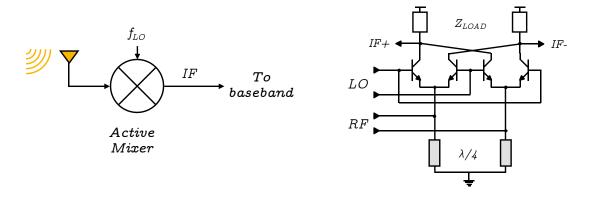

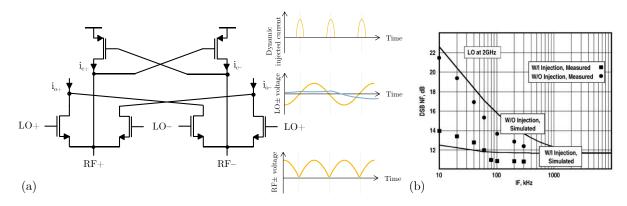

The core of the downconverter is the mixer. Active topologies, based on Gilbert cell, presented in Figure 33, are usually exploited in BiCMOS receiver architecture. This topology exhibits a good trade-off between conversion gain (typ. 17dB) and the compression point (-5dBm) with moderate Noise Figure (typ. 13dB). In terms of integration the input matching performed with quarter wave line require a significant silicon area.

Figure~34-Radar~mmW~typical~architecture

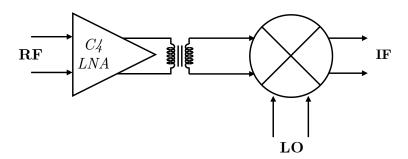

Many CMOS Receivers do not use active mixer due to flicker noise contribution. In such a case, the receiver features a Low Noise Amplifier (LNA), a passive mixer and, eventually, a low noise baseband amplifier. The large voltage gain of the LNA is supposed to hide the noise of the following stage as expressed in Friis formula (Equation 11).

Equation 11 - Friis formula on noise

$$F_{RX} = F_{LNA} + \frac{F_{mixer} - 1}{G_{LNA}} + \frac{F_{baseband} - 1}{G_{LNA}G_{mixer}} + \dots + \frac{F_n - 1}{G_1 \dots G_n}$$

Nevertheless, a high gain LNA compromises the linearity of the system. This issue is illustrated in Equation 12. To reduce the degradation of the receiver linearity (IP3) due to cascaded stages, the linearity of the second stage  $IP_{3 \text{ mixer}}$  would be  $G_{LNA}$  time larger than  $IP3_{LNA}$ , the  $IP3_{baseband}$  would be ( $G_{LNA} \cdot G_{mixer}$ ) time larger than  $IP3_{LNA}$  and so on. Any increase in  $G_{LNA}$  requires the same improvement in the IP3 of the following stages. To keep the IP3 of a radar receiver at a high level, the voltage gain of the LNA is reduced which degrades the noise figure according Equation 11. Hence the design of the LNA is led by a tradeoff between linearity and NF performance.

Equation 12 - Cascaded IIP3 formula

$$\frac{1}{IIP3_{RX}} = \frac{1}{IIP3_1} + \frac{G_1}{IIP3_2} + \frac{G_1G_2}{IIP3_3} + \dots + \frac{G_1 \dots G_{n-1}}{IIP3_n}$$

Frequency down-converters based on active and passive mixers are further investigated in this work.

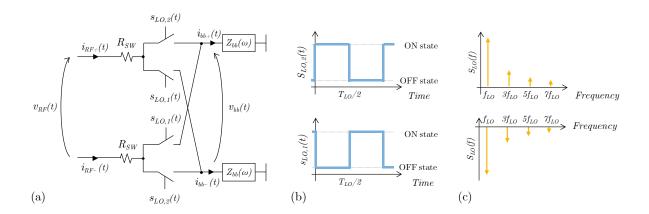

#### b. <u>RF signal processing</u>

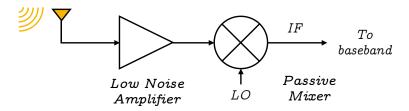

Figure 35 - IQ downconverter

A large majority of recent radars use a frequency down conversion based on in-phase signal processing as illustrated in Figure 34. This strategy is mainly motivated by a lower complexity and a reduced cost due to an implementation for baseband analog [14]. As discussed in section 1, the evolution of radar module specifications requires an overall improvement of RF performances. To address this challenge, a better RF signal processing is required. To leverage such challenge a complex (or I-Q) mixer is investigated in radar receivers. This kind of architecture presents in Figure 35, is based on a parallel processing, in-phase and inquadrature, in the down conversion operation to cancel out the image contribution  $f_{\rm IM}$  of the RF signal  $f_{\rm RF}$ . I-Q downconversion improves in theory the Noise Figure by 3dB. Indeed, a real receiver downconverts the noise at image frequency, the image band foldback is cancelled with a I-Q configuration. In practice, the benefit is limited due to signal loss in the I-Q imbalance due to the implementation. Inherent to the image cancellation the I-Q signal processing also mitigates the intermodulation occurring in RFFE and improve "bumper rejection" and interference tolerance. This feature can be exploited for better safety monitoring. Besides, it mitigates the noise degradation due to TX/RX crosstalk.

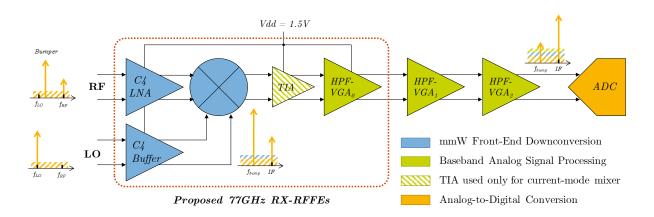

# 3. Conclusion

The overall trend to integrate all the digital blocks with the RF transceiver leads to select highly integrated CMOS technologies for the next generation of radar. New receiver architectures are investigated to address the challenging specifications inherent to radar modules. Various RX implementations (passive or active, voltage and current mixing) will be discussed throughout this manuscript using noise cancelling approach for simultaneously wideband behavior and noise performances.

# V. Thesis outline

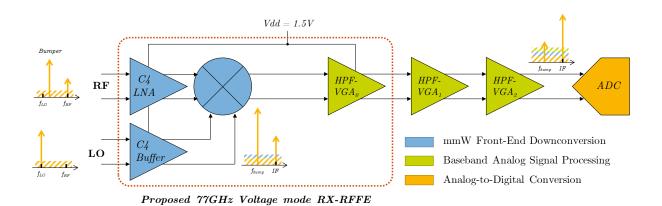

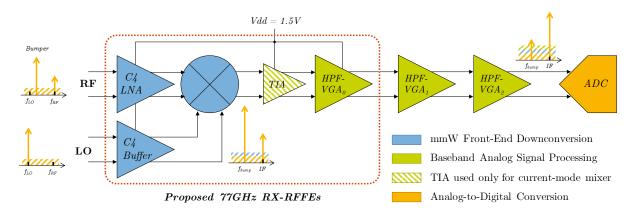

Due to the development of automotive full automation, new generations of 77GHz radar require both a high level of digital integration and a low-cost development which leads to the selection of advanced 28nm RF CMOS technology. Bearing in mind the general specifications of power consumption, form factor or PVT robustness, the radar module presented at Figure 36 has four critical specifications: PLL phase noise, PLL linearity, TX output power and the RX noise figure. This work focusses on the design of downconverters which are critical for noise specifications.

Figure 36 - The RX-RFFE in the radar module

Various downconverter architectures can be proposed to address the stringent radar specifications. Considering these various architectures, circuits techniques such as noise cancelling can be proposed to strengthen robustness to PVT variations and maintain good noise performances.

| Specifications            | Min. | Typ. | Max. |

|---------------------------|------|------|------|

| RF bandwidth (GHz)        | 76   |      | 81   |

| IF bandwidth (MHz)        | 1    | /    | 40   |

| Noise figure (dB) for LRR |      |      | 15   |

| ICP1 (dBm)                | -5   |      |      |

| Passband ICP1 (dBm)       | -20  |      |      |

| IIP3 (dBm)                |      | -26  |      |

| LO-to-RF Isolation (dB)   |      |      | -35  |

| Objectives                | Min. | Typ. | Max. |

| Conversion Gain (dB)      |      | 10   |      |

| Power consumption (mW)    |      | 20   |      |

Table 9 - Specifications of receiver RF front-end

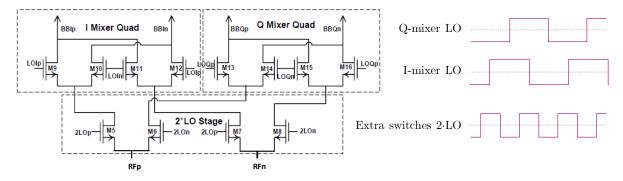

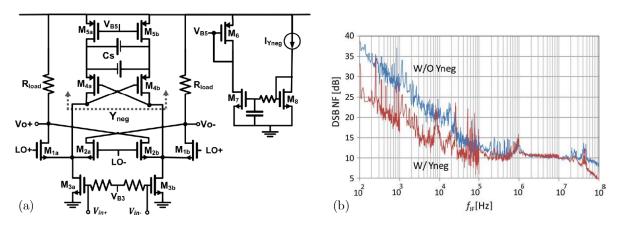

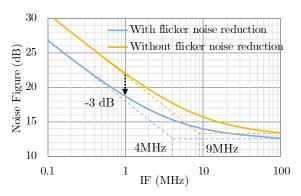

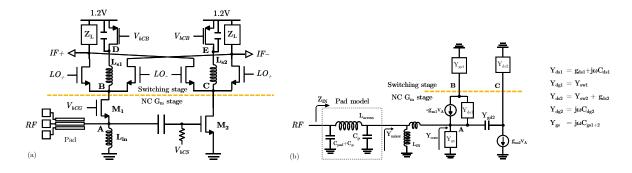

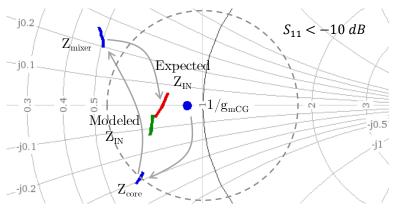

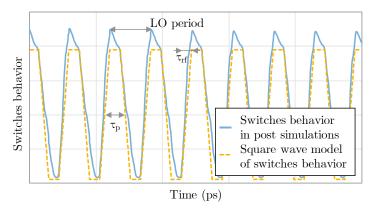

The Chapter 2 presents active mixers in 28nm CMOS based on noise cancelling architecture. Due to large 1/f noise in advanced RF CMOS, specific flicker noise reduction techniques are implemented in millimeter-Wave domain. Two active mixers were designed: a proof of concept for RF band and an application-oriented downconverter at 77GHz.

The Chapter 3 introduces various Low Noise Amplifiers which use noise cancelling approach with a differential architecture and leads to the development of a complementary capacitor cross coupled amplifier. Several implementations are proposed: the first on is a proof

of concept for RF multistandard applications and the others are application-oriented LNAs at 77GHz.

The Chapter 4 describes two Receivers using the proposed complementary capacitor cross coupled LNA. This chapter presents two downconversion architectures with either voltage mode mixer either a current mode mixer to compare their respective performances regarding the specifications.

The Chapter 5 draws the conclusions of this thesis and introduces the future works in Radar Automotive RX field.

The proposed research is realized in partnership with Bordeaux IMS Lab and NXP Semiconductors focusing on the design of downconverter adapted to the constraints of 77GHz Embedded Automotive Radar.

# Chapter 2. <u>77-GHz Noise-cancelling</u> active downconverter

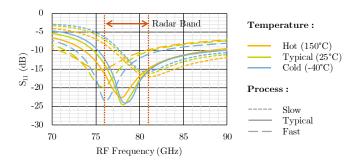

Previously, in Chapter I, the system analysis brings up challenging specifications on RX front-end such as low noise and high linearity. Therefore, conventional architectures featuring Gilbert active mixer or common-source LNA combined with passive mixers are no longer sufficient to address the specifications presented in Table 9, especially in advanced RF CMOS technologies. Hence advanced circuit techniques are required to address these requirements.

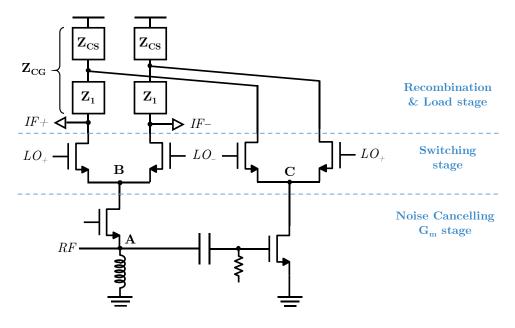

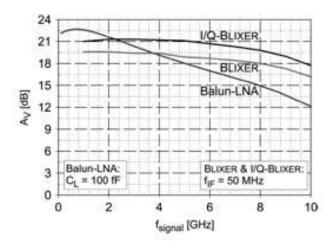

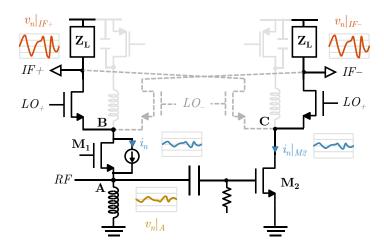

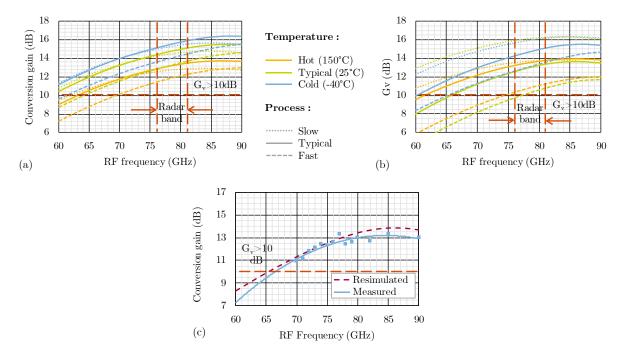

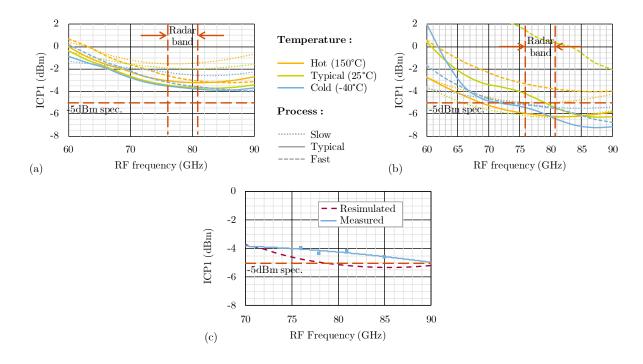

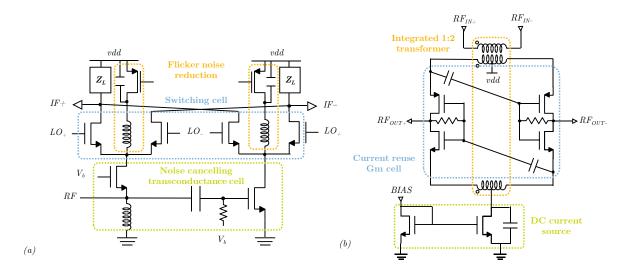

This chapter proposes to study the application of noise cancelling downconversion to 77-GHz Radars. Active mixers are considered due to their good trade-off between gain, noise figure and linearity. Furthermore, downconverter based on noise cancelling architecture achieve wideband operation and overall high performances.

The first section proposes an introduction to noise cancelling topologies and their implementation. An RF demonstrator applying noise cancelling and low power techniques for IoT applications is proposed and measured in section II. To address automotive radar specifications, a noise cancelling mixer is proposed in section III with specific solutions to overcome CMOS flicker noise limitations. The measurement results are also reported. Finally, the section IV draws the conclusion about the downconverter regarding the state-of-art and the applications.

# I. Noise cancelling principle

In order to address 5GHz band, a wideband design can enhance the robustness to PVT corners and the performance flatness over frequency. For multi-band and multi-standards communications receivers, a noise cancelling architecture is an emerging solution to perform both wide bandwidth and high RF requirements. This work proposes to export this topology to millimeter-wave domain, first the principle of noise cancellation is introduced.

In this section, the limitation of conventional noise matching approach is first outlined and then the overall principle of noise cancellation is explained. Furthermore, the conditions to build a common-gate based noise cancelling circuits are detailed and the advantages of this architecture are discussed.

# 1. Why noise cancelling is interesting?

#### a. Limitation of noise matched structures

According Chapter I.3, noise performance is a key metric for RF RX front-ends. For an RF device, the noise factor is expressed in Equation 13 considering the Lange invariant (N), the noise optimal impedance  $(Z_{opt}=R_{opt}+jX_{opt})$  and the minimal noise factor  $(NF_{min})$ . To lower the noise factor (F) to the minimum noise factor  $(F_{min})$ , the noise impedance of the device  $(Z_{opt})$  must be equal to the source noise impedance  $(Z_{S})$

Equation 13 - Noise factor regarding the noise parameters [22]

$$F = F_{min} + \frac{N}{R_s R_{opt}} |Z_{opt} - Z_s|^2$$

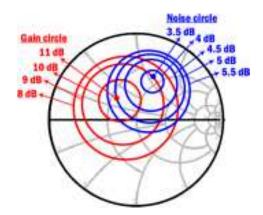

Nevertheless, this impedance  $Z_{opt}$  can be slightly different from the impedance which allows for a maximum of power transfer -i.e. power matching- as illustrated in Figure 37. This divergence between power and noise matching can lead to a poor trade-off and important variations over wideband operations or under PVT conditions.

Figure 37 - Example of 94-GHz BiCMOS LNA noise and gain circle in Smith chart [23]

To achieve those matching requirements, two approaches are used with resonant or non-resonant matching. The former solution is based on a combination of passive elements resonating out the input impedance of the circuit to achieve a high level of noise (or power) matching at a given frequency. If it offers better RF performances, this topology is unfortunately narrowband and sensitive to PVT variations. The second approach avoids the use of resonant inductive elements and prefers wideband networks such as resistors, shunt feedback or common-gate structures. These topologies are intrinsically wideband, and some specific configurations can be controlled by biasing, allowing for some PVT compensations, at the cost of moderate gain and noise performances.

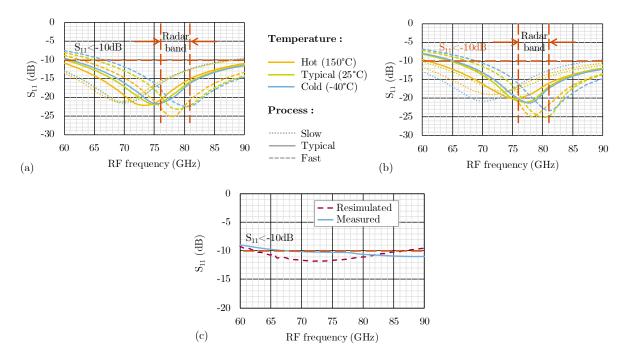

As detailed in Chapter I.3.1, automotive radar receivers have stringent specifications regarding the noise figure, directly linked to the achievable range, the bandwidth which must cover 76 to 81GHz to target short-range applications, and the robustness to PVT variations, up to a temperature of 150°C. To fulfill these conditions, a noise canceling topology can be interesting.

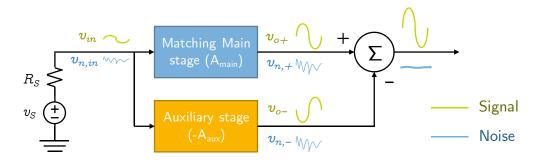

#### b. Noise cancellation principle

Figure 38 - Noise cancelling principle

The principle of noise cancelling architecture can be illustrated by the block diagram proposed in Figure 38 [24]. The main stage  $(A_{main})$  achieves the impedance matching and determines the gain performance. Its noise is modeled by a noise source at its input  $(v_{n,in})$ . This stage is usually a wideband circuit with a poor noise performance. On the other hand, the auxiliary stage  $(-A_{aux})$  assures the voltage sensing and performs the noise cancellation of the main stage. A combination is necessary to perform the effective cancellation of the noise. The key of noise cancelling principle is to identify the two circuit nodes where the signal is in-phase (respectively in-opposition) but noise is opposite (respectively in phase).

Considering only the main path of the block diagram in Figure 38, the input and output nodes have anti-phase noise voltages  $(v_{n,in})$  and respectively  $v_{n,+}$  and in-phase signal voltage  $(v_{s,in})$  and respectively  $v_{o+}$ . The auxiliary stage uses a voltage sensing to pick up the signal and the noise voltage. By designing an auxiliary stage with a similar transfer function -i.e.  $|A_{main}| = |A_{aux}|$  with opposite phase-, it's then possible to have at its output an opposite-phase signal and an in-phase noise with respect to the main path. By combining the output nodes of each path, signals are constructive throughout the adder whereas noise contributions are destructive and will be removed at the output. Inherent to the noise cancellation operation, the input signal experiences an increase of the voltage dynamic by a factor 2. This feature contributes to theoretically improve the voltage gain by +6 dBv.

The aforementioned noise cancelation process only concerns the white noise sources located in the main stage. Hence the noise of the auxiliary path holds, as well as non-white noise sources of the main stage, and the noise figure of a noise canceling circuit is not null.

However, the technique of noise canceling significantly relaxes the trade-off between input matching, noise and gain performances.

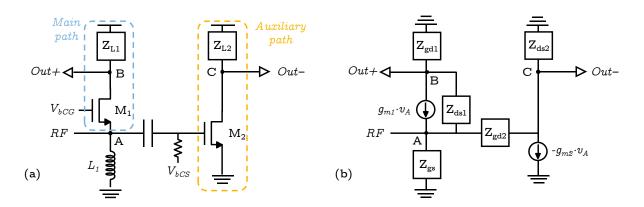

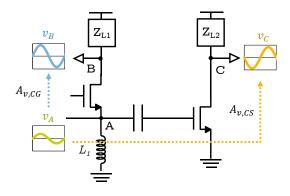

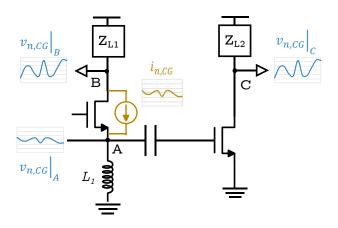

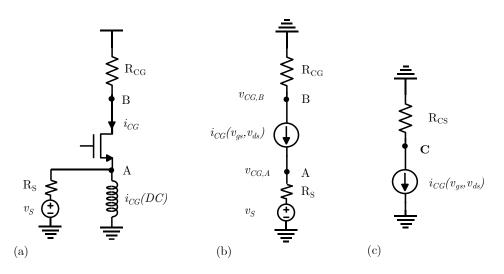

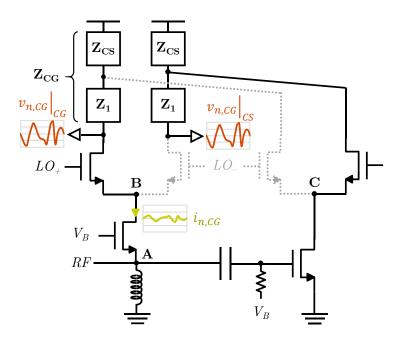

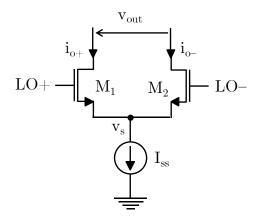

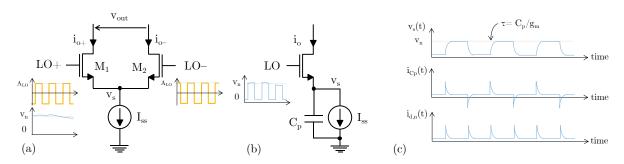

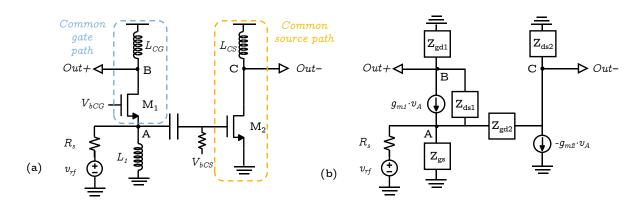

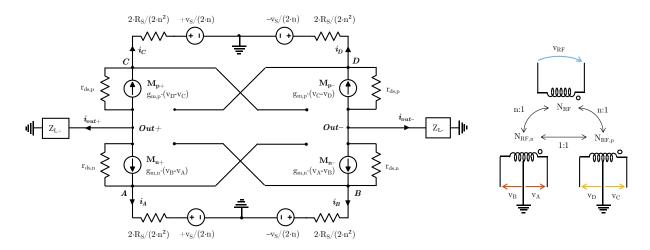

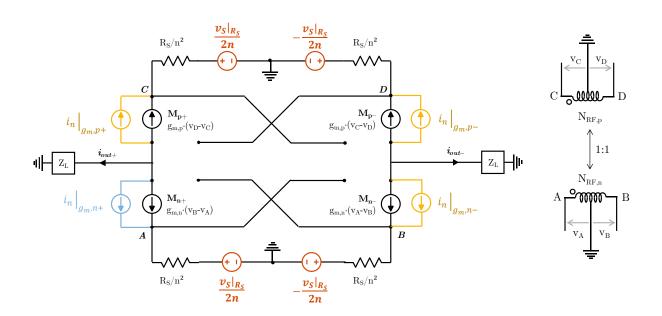

# 2. Common-gate based noise cancelling

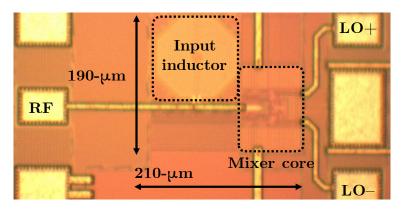

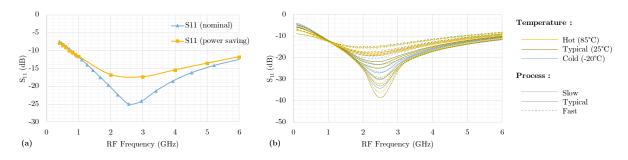

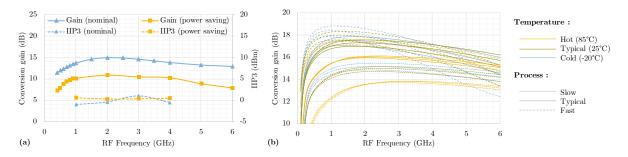

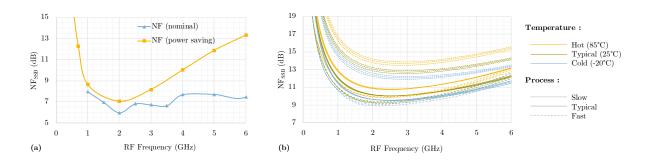

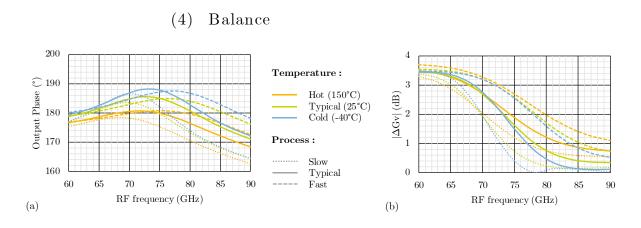

Figure 39 - Common-gate based noise cancelling LNA in (a) schematic; and (b) small signal model