# Design Tools for Millimeter Wave Ultra Wideband Distributed Amplifiers

Mohamad El Chaar

# ▶ To cite this version:

Mohamad El Chaar. Design Tools for Millimeter Wave Ultra Wideband Distributed Amplifiers. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2022. English. NNT: 2022GRALT067. tel-03936695

# HAL Id: tel-03936695 https://theses.hal.science/tel-03936695v1

Submitted on 12 Jan 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS) Spécialité : Nano électronique et Nano technologies

Unité de recherche : Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés

# Outils de conception pour l'amplification distribuée ultra large bande aux fréquences millimétriques

# Design Tools for Millimeter Wave Ultra Wideband Distributed Amplifiers

Présentée par :

### **Mohamad EL CHAAR**

# Direction de thèse :

Florence PODEVIN Directrice de thèse

Enseignante-Chercheure, Université Grenoble Alpes

Sylvain BOURDEL Co-directeur de thèse

Enseignant-chercheur Grenoble INP, Université Grenoble Alpes

Manuel José BARRAGAN ASIAN Co-directeur de thèse

Chargé de Recherche, CNRS

#### Rapporteurs:

#### **FRANK ELLINGER**

PROFESSEUR DES UNIVERSITES, Technische Universität Dresden, Faculty of Electrical and Computer Engineering

#### **Thierry PARRA**

PROFESSEUR DES UNIVERSITES, Université de Toulouse III Paul Sabatier

# Thèse soutenue publiquement le 29 septembre 2022, devant le jury composé de :

Florence PODEVIN Directrice de thèse

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

Sylvain BOURDEL Co-directeur de thèse

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

Philippe BENECH Président

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

FRANK ELLINGER Rapporteur

PROFESSEUR DES UNIVERSITES, Technische Universität Dresden,

Faculty of Electrical and Computer Engineering

Thierry PARRA Rapporteur

PROFESSEUR DES UNIVERSITES, Université de Toulouse III Paul

Sabatier

Jean-Yves DUPUY Examinateur

DOCTEUR EN SCIENCES, THALES DMS FRANCE SAS

Philippe CATHELIN

INGENIEUR, STMicroelectronics

Antonio A. L. DE SOUZA

PROFESSEUR ASSOCIE, Federal University of Paraíba

Pour les amis, la famille et la France... Santé! For Friends, Family and France... Cheers! "Vacation?... What is this?... Never heard of it..."

A PhD candidate in mm-wave IC design

# **Abstract**

Over the last few years, both data center and network traffic increased by several folds (more than six-fold, as stated by CISCO Systems, Inc.) and are still experiencing an ongoing growth. This demand for higher capacity while meeting with higher end-to-end quality service projects a continuous need for improvements in spectral efficiency enhancement techniques; however, a given spectrum band has its limit of volume it can support before reaching saturation levels. This pushes research efforts towards finding other solutions and a promising one is by exploiting the uncrowded millimeter-wave (mm-wave) spectrum through arranging more bandwidth. Signal amplification is one of the most basic and prevalent circuit function in modern RF- and microwave- systems. On the topic of wideband operation, distributed amplifier (DA) has proved to be a suitable and promising candidate with its ultra-wideband (UWB) performance. Meanwhile, the design of integrated circuit (IC) in mm-wave spectrum is becoming a challenging process due to the unavoidable parasitic that affect circuit performance and complicate design process. The reliability of the conventional design techniques through deriving mathematical equations, a simple and direct design process commonly used at low frequencies, starts to diminish. Another proposed design technique is by combining advanced-scripting languages with a proper physical model; this will lead to a smart and efficient technique of designing mmwave IC DAs through a process referred as computer-automated design (CAutoD) process. In this thesis, in particular, we propose for DAs an original ABCD-parameter based chain matrix model, a well-known formalism originating from the passive RF-circuit domain, in addition to a CAutoD methodology built upon it. Following this design technique is considered complete to a much greater extent, since the model gives flexibility in controlling a wider range of correlated design parameters. It is also considered reliable, a crucial criterion for mm-wave design, since the model does not apply simplification or neglect parasitic effects. It is simple, since the designer does not have to deal with the tiny effects (parasitic) that affect DA behavior and, finally, it is considered versatile, since it does not impose restrictions on the design component topologies the designer might be interested to use. Our end-goal is to offer the mm-wave designer a different and interesting technique in which the outcome of the suggested CAutoD process is a set of 3D graphical design exploration (DSE) plots. Designers then can explore different feasible solutions and choose the best design that meet their multiple performance objectives. Its benefit here is demonstrated by exploring the design space of DAs with BWs  $\geq$  80 GHz where STMicroelectronics (ST) 55-nm CMOS technology process is used, reporting 216 feasible DA options to explore from. Two global optimum DAs amplifying frequencies up to 100 GHz were then implemented as circuit prototypes: a single stage DA with 6.01 GHz/mW of measured gain-bandwidth product over DC consumption (GBP/P<sub>DC</sub>) and a 17.5 THz GBP cascaded DA with 71.96 GHz/mW of GBP/P<sub>DC</sub>, being the highest figure of merits, to the authors' knowledge.

# **Contents**

| Abs           | stract  |                                                                     | V   |

|---------------|---------|---------------------------------------------------------------------|-----|

| Cor           | itents  |                                                                     | vii |

| Cha           | pter 1  | General Introduction                                                | 1   |

| 1.1           | Ana     | log Signal Amplification                                            | 2   |

| 1.2           | Mo      | ve Towards Low-Cost Production: CMOS Technology as a Solution       | 2   |

| 1.3           | Mo      | ve Towards High-Frequency Band: Millimeter-Wave Band as a Solution  | 3   |

| 1.4           | Mo      | ve Towards High-Frequency Band: Issues Encountered                  | 3   |

| 1.5           | Mo      | ve Towards High-Frequency Band: CAutoD Technique as a Solution      | 4   |

| 1.6           | The     | sis Objectives                                                      | 4   |

| 1.7           | Org     | anization of the Report                                             | 5   |

|               | _       | Introduction to Wideband Amplifiers – Distributed Amplifier for n   |     |

| <b>Wa</b> 2.1 |         | essure Trends for Millimeter-Wave Applications                      |     |

| 2.1           |         | plifier Circuit Topologies with Wide Bandwidth Characteristic       |     |

| 2.2           | 2.2.1   | Small-to-Large Bandwidth Amplifiers Topologies                      |     |

|               | 2.2.1   | Table-of-Comparison for Performances Analysis                       |     |

| 2.3           |         | at is a Distributed Amplifier?                                      |     |

| 2.3           | 2.3.1   | Walk Through History                                                |     |

|               | 2.3.1   | Structure and Basic Principle of Operation                          |     |

|               | 2.3.2   | Performance Demonstration through Different Technologies and Topolo |     |

|               | 2.3.3   | Teriormanice Demonstration through Different Teemhologies and Topok | _   |

|               | 2.3.4   | State-of-the-Art Table on Distributed Amplifiers                    | 32  |

| 2.4           | Cor     | relusion                                                            | 35  |

| Cha           | apter 3 | Proposition of a Novel Model to Design DAs: the Four-Port Chain     |     |

|               | -       | lodel                                                               | 37  |

| 3.1           | Intr    | oduction                                                            | 37  |

| 3.2           | Exi     | sting Distributed Amplifier Design Techniques                       | 39  |

|               | 3.2.1   | Artificial-Line Based Model [40]                                    | 39  |

|               | 3.2.2   | Stage-Scaling Based Model [51]                                      | 40  |

|               | 3.2.3   | Distributed-Line Based Model [52]                                   | 41  |

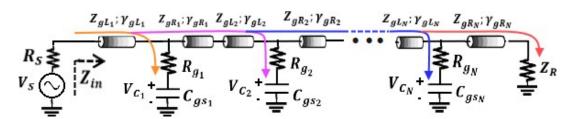

|               | 3.2.4   | Artificial Neural Network Based Model                               | 45  |

|               | 3 2 5   | Widespread Design Technique: Through CAD Software                   | 46  |

| 3.3 | Des                | ign Limitations when Operating in mm-Wave Band                                       | 47   |  |

|-----|--------------------|--------------------------------------------------------------------------------------|------|--|

| 3.4 | Pro                | Proposed Solution: Chain Matrix (ABCD) Based Design Model [73]                       |      |  |

| 3.5 | Cor                | nclusion                                                                             | 53   |  |

|     | apter 4<br>npensa  | Model Application – Computer Automated Design for Loss-<br>ted Distributed Amplifier | 56   |  |

| 4.1 | -                  | s-Compensated Distributed Amplifier                                                  |      |  |

|     | 4.1.1              | Overview of Publication                                                              | 57   |  |

|     | 4.1.2              | Loss-Compensation Technique: Graphical Analysis                                      | 58   |  |

|     | 4.1.3              | Loss-Compensation Technique: Analytical Analysis                                     | 61   |  |

|     | 4.1.4<br>Comp      | Implementing Loss-Compensated Cascode Gm-Cell in a Numerical uting Environment       | 63   |  |

| 4.2 | Los                | s-Compensated Distributed Amplifier CAutoD Process                                   | 65   |  |

|     | 4.2.1              | Distributed Amplifier Bandwidth Extension and Flattening Concept                     | 65   |  |

|     | 4.2.2              | Algorithmic Design Methodology                                                       | 67   |  |

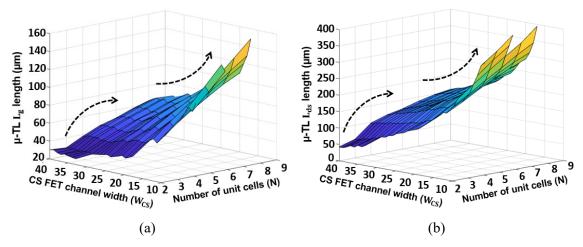

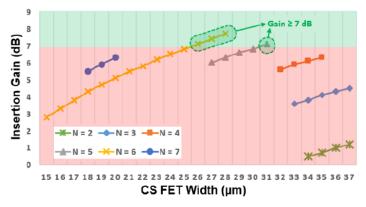

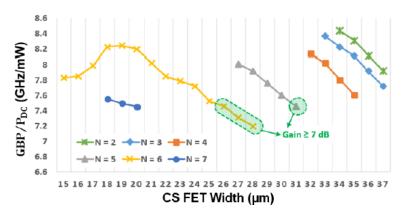

| 4.3 | 3D                 | Design Space Exploration Plots: Parameters and Variables                             | 71   |  |

|     | 4.3.1              | DA Design Parameters: Gain, Bandwidth and P <sub>DC</sub>                            | 71   |  |

|     | 4.3.2              | DA Design Parameters: Synthesizing a Unit-cell                                       | 73   |  |

| 4.4 | Cor                | nclusion                                                                             | 75   |  |

| Cha | pter 5             | 100-GHz Single Stage CMOS Distributed Amplifier                                      | 77   |  |

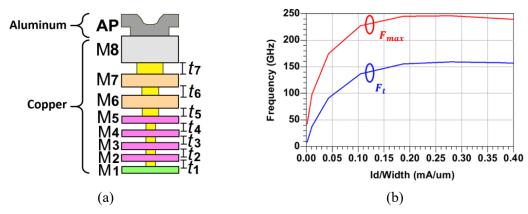

| 5.1 | STI                | Microelectronics 55-nm Node Process Technology                                       | 78   |  |

| 5.2 | 100                | -GHz Single-Stage CMOS DA: Circuit Design                                            | 78   |  |

| 5.3 | 100                | -GHz Single-Stage CMOS DA: Circuit Implementation                                    | 81   |  |

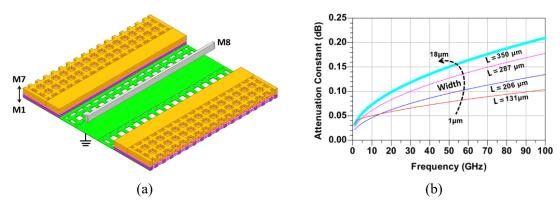

|     | 5.3.1              | Microstrip Transmission Line                                                         | 81   |  |

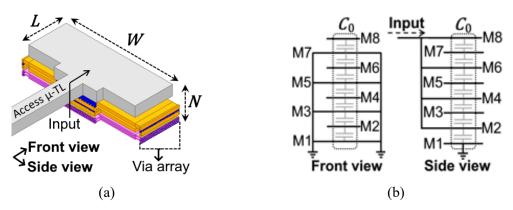

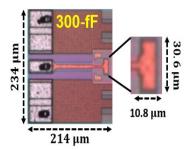

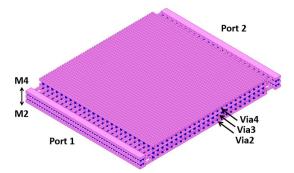

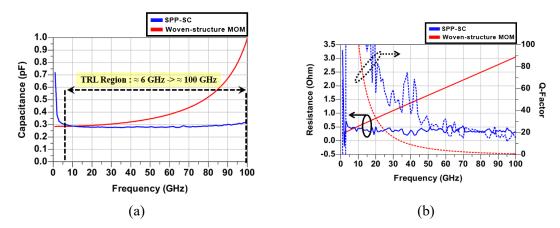

|     | 5.3.2              | High Quality and SRF Stacked Parallel Plate Shunt Capacitor [61]                     | 82   |  |

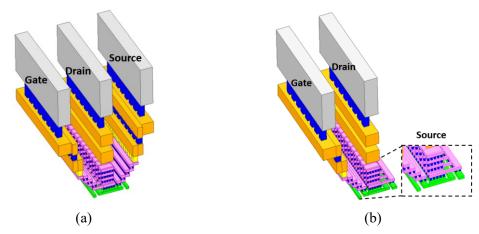

|     | 5.3.3              | MOS Transistor Interconnection                                                       | 89   |  |

|     | 5.3.4              | Standalone Unit-Cell Layout and Microphotograph                                      | 90   |  |

|     | 5.3.5              | 100-GHz Single-Stage DA: Layout and Microphotograph                                  | 91   |  |

| 5.4 | 100                | -GHz Single-Stage CMOS DA: Experimental Results                                      | 93   |  |

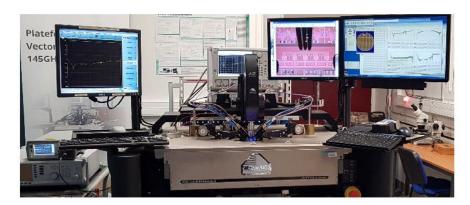

|     | 5.4.1              | Vector Network Analyzer Description                                                  | 93   |  |

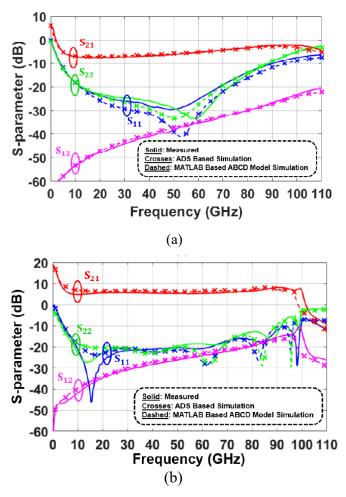

|     | 5.4.2              | S-parameters Analysis: Unit-Cell and DA Model Validation                             | 94   |  |

|     | 5.4.3              | Implemented DA Performance Analysis                                                  | 95   |  |

| 5.5 | Cor                | nparison with State-of-the-Art CMOS-Based DAs Performances                           | 98   |  |

| 5.6 | Cor                | nclusion                                                                             | 99   |  |

|     | npter 6<br>plifier | THz Gain-Bandwidth Product 100-GHz Cascaded CMOS Distribution                        | ıted |  |

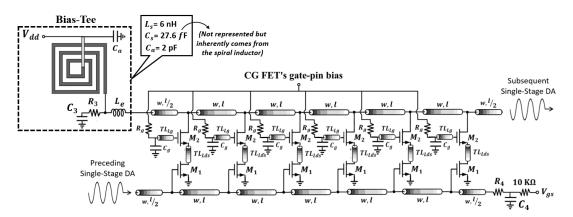

| 6.1 | тц,                | z GBP Cascaded CMOS DA: Circuit Design                                               | 101  |  |

| 6.2 | TH      | z GBP Cascaded CMOS DA: Circuit Implementation           | 103 |

|-----|---------|----------------------------------------------------------|-----|

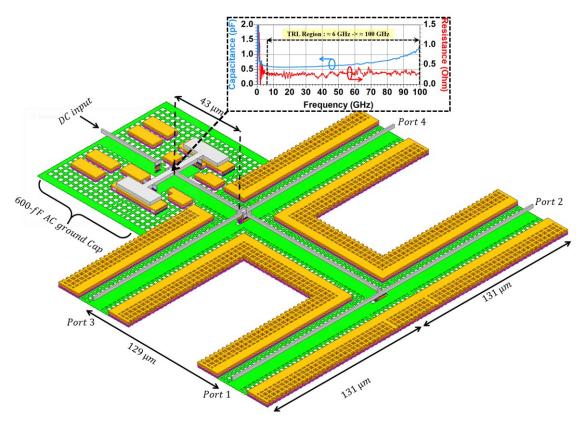

|     | 6.2.1   | Integrated Wideband Millimeter-Wave Bias-Tee [68]        | 103 |

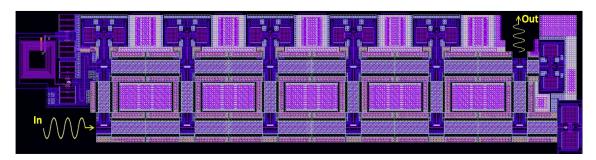

|     | 6.2.2   | 100-GHz Single-Stage DA: Layout and Microphotograph      | 109 |

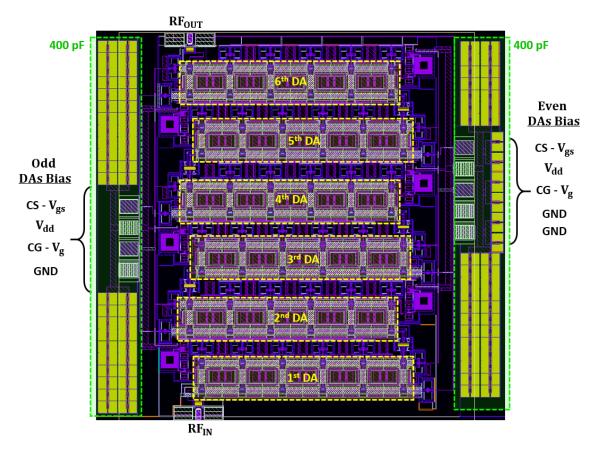

|     | 6.2.3   | Six-Stage Cascaded 100-GHz DA Layout and Microphotograph | 111 |

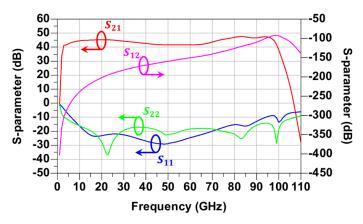

| 6.3 | TH      | z GBP Cascaded CMOS DA: Simulation Results               | 112 |

|     | 6.3.1   | S-parameter Analysis                                     | 112 |

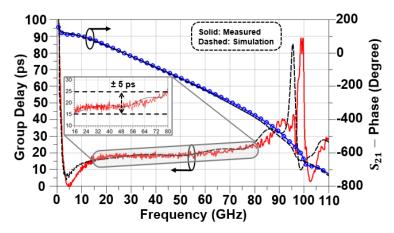

|     | 6.3.2   | Group Delay Performance Analysis                         | 113 |

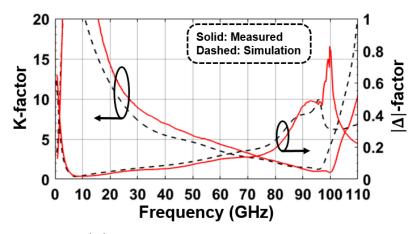

|     | 6.3.3   | Stability Performance Analysis                           | 113 |

| 6.4 | Con     | nparison with State-of-the-Art DAs Performances          | 114 |

| 6.5 | Cor     | nclusion                                                 | 116 |

| Cha | pter 7  | General Conclusion                                       | 118 |

| Pub | licatio | ns                                                       | 120 |

| Bib | liograp | ohy                                                      | 121 |

# Chapter 1

# **General Introduction**

The aim of this first chapter is to overview the reader on the subject of this thesis work that is wideband amplification in the millimeter-wave (mm-wave) frequency band (30 GHz-300 GHz). This high frequency band attracts strong interest for its uncrowded characteristic and opportunity to produce high date rate systems such that significant efforts are being dedicated to overcome the challenges faced when designing high-end mm-wave circuits. In particular, integrated circuit (IC) amplifier is a popular topic of study between the research community that is undergoing continuous improvement to break the limits on high frequency of operation, especially when the wideband criterion is targeted from a few GHz to hundred GHz and above. The need for such criterion has lead researcher towards distributed amplification as a promising candidate that offers such great capability and hence a critical circuit to adequately design. This topic also gains widespread interest especially when using complementary metal-oxide-semiconductor (CMOS) technology process for its attractive low-cost, high-volume production features and its ability of high frequency operation with continued device scaling. Nevertheless, a crucial challenge encountered is the lack of appropriate and accurate design techniques at such band where the simple analytical-based approaches, traditionally applied at low frequency spectrum, begin to fail and therefore advocate for a revaluation of design techniques.

The following sections outlines our context starting from a general overview on analog signal amplification and ending by stating our needs for an automated circuit design approach when dealing with mm-wave operating frequencies. Distributed amplification, which is the heart of this work, will be considered in Chapter 2, devoted specifically to introducing wideband amplifiers.

# 1.1 Analog Signal Amplification

Signal amplification is one of the most basic and prevalent circuit functions in modern RF and microwave systems. Amplifier block is found as a first component of any receiver front-end circuitry, on which overall receiver performance depends, as well as the last component of any transmitter front-end circuitry, on which a reliable transmission depends. In addition, an amplifier can be considered for implementation as an intermediate block in a complete system to compensate for any signal degradation encountered through intrastages circuitry.

Those applications share one common goal and it is magnifying a weak signal for further RF-treatment or digital signal processing. From the literature, it is clear that the amplifier design subject and application in fully integrated systems dates back to the early 21th century. Demonstrative implementation inside receivers and transmitters front-ends, and even transceivers have been reported using Si CMOS [1]-[3], SiGe BiCMOS [4]-[7] and various III-V technologies such as GaAs and InP [8]-[10], to mention but a few. Those show its widespread interest between RF- and microwave- research community for performance exploration and improvement. While the demos of those systems can be considered old dated, but their added contribution to the community and value stays the same till this day. Their concept can be re-used in recent years for their originality and enhanced by benefiting from the advancement of semiconductor technologies towards smaller nodes for the purpose of operating at higher frequencies [11]-[13].

# 1.2 Move Towards Low-Cost Production: CMOS Technology as a Solution

To meet today needs of the consumer marketplace and the radio chipset to be practical for very large-scale production, the cost, size, and power consumption of any circuit solution has to be significantly below what is being achieved today using compound semiconductor technology. Traditionally, analog radio front-end ICs, especially the ones operating at high frequencies, have been designed using III-V compound technologies which have superior performance compared to SiGe BiCMOS and Si CMOS technologies due to their higher electron mobility [14], [15].

Still, a CMOS implementation promises higher levels of integration and reduced cost. ICs implemented using CMOS technology directly benefit from the higher speed limit of the scaled technology [16] and with continued device scaling, enable circuit blocks to operate at ever-increasing frequencies.

Typical telecommunication applications require not only transceiver and sensing hardware, but also digital circuity to process the acquired data. Silicon CMOS technologies are good candidates for the integration of such systems. These technologies are being considered particularly attractive for their potential of integration with intermediate frequency (IF) and baseband digital signal processing (DSP) functions, together with high performance analog frontends, enabling true systems-on-chip (SoC).

# 1.3 Move Towards High-Frequency Band: Millimeter-Wave Band as a Solution

Over the last few years, both data center and network traffic increased by several folds, and are still experiencing an ongoing growth at an unsustainable rate [17]. This increasing demand for higher capacity while meeting with the demand for high end-to-end quality service projects a continuous need for improvements in spectral efficiency enhancement techniques, particularly if the medium has to be shared with many users and interchanged data.

However, a given spectrum band has a limit for the volume of data it can support. Improving its throughput using bandwidth portioning and spectral aggregation techniques has already been exhausted, leading to their evolvement arguably providing insignificant enhancements to the recent spectrum bands since the latter have already reached their saturation level due to being over-packed. This pushes us to search for other solutions and one promising alternative is by arranging more bandwidth. The availability of uncrowded spectrum in the millimeter band to exploit from makes it possible to accommodate future significant increase in network traffic and producing multi-gigabit per second data accesses. This motivated research attempts to overcome the limitation on high frequency of operation through advancement in semiconductor technology process, such as technology scaling, for instance, and in the continuous proposal of innovative analog circuits. For what concerns the latter, it necessitates the development of advanced circuit topologies and suitable design techniques capable of meeting with the marketplace requirements. Therefore, mm-wave ICs is gaining a growing interest and receiving focus from recent activities by the research and development (R&D) department of both private and public sectors.

# 1.4 Move Towards High-Frequency Band: Issues Encountered

Operating at millimeter-wave spectrum, however, is seeing continuous efforts in system design to satisfy the demand for high-speed applications.

Generally speaking, synthesizing analog ICs in the high frequency spectrum subjects one to performance degradation cause by reduced quality of passive components and increase in parasitic that impact the highest operating frequency one could reach. Technological-wise speaking, and in this particular case, the attractive low-cost CMOS processes experience high sheet resistance, strict metal density rules and lossy silicon substrate that makes it challenging to achieve high-end mm-wave CMOS circuits.

In terms of design process, designing at mm-wave renders the conventional analytical-equation based design techniques difficult to be applied. The simplicity offered by them starts to diminish since more behavior-dominant parasitic elements comes into role and become difficult to neglect. Since simplicity is desirable in any design process, approximation is adopted, inaccuracy in design parameter sizing increases and hence dependency on electronic computer-aided design (CAD) softwares grows, such as Keysight Advanced Design System (ADS) or Cadence Virtuoso software. Since the demand of wireless and wireline communication is at high pace, the optimum design of any IC component becomes major part.

# 1.5 Move Towards High-Frequency Band: CAutoD Technique as a Solution

To meet the ever-growing demand of quality and competitiveness, iterative physical prototyping is now often replaced by automated prototyping. The introduction of artificial intelligence (AI) algorithms into the design process realizes an intelligent and automatic design, and consequently considerable time and effort could be saved. Meanwhile, designers will not have the concern that whether a specific topology can meet the design specification or whether another parameters set exists that corresponds to better performance.

However, before any code scripting can be performed or any proposal of algorithms and design methodologies can be possible, developing a suitable physical model that can properly simulate a given circuit behavior is considered an essential first step to this process. This model is required to be complete and accurate, besides offering the designer the possibility to have control over all design variables. Having control over all analog-circuit components equates to having the option to propose several design methodologies meeting multiple design objectives such as maximized output, highest speed, and cost-effectiveness, and identifying multiple figures of merit. It also equates to obtaining a design solution considered more of a global optimum solution than a local optimum solution. In addition, an important metric when proposing a design model is simplicity. When speaking of mm-wave IC design, especially, the less the designer has to deal with the plethora of tiny parasitic effects, the easier and time-efficient his design task is considered.

Combining both circuit design-model and the widespread of advance scripting languages will lead to a smart and efficient way of designing mm-wave ICs, which is commonly referred to CAutoD process. Such process will give the designer the ability to virtually explore a complete circuit before it is implemented for production.

# 1.6 Thesis Objectives

After demonstrating the big-picture of this thesis work, one can conclude that the theme of this manuscript will be about IC amplifier design, implemented using low-cost CMOS technology, with amplification bandwidth extending into the mm-wave frequency range. In addition, it emphasizes on the need for a simple design process based on computer automation, from proposing a versatile and complete physical model, and appropriate methodology to achieve a desired performance criterion by the analog designer. Combining both is required to provide optimum sizing-values for the circuit design parameters.

Among wide bandwidth amplifiers, our focus will be laid specifically on distributed amplifiers with the following report organization.

# 1.7 Organization of the Report

The remaining of this manuscript is organized as follows.

In Chapter 2, a specific introduction on wide bandwidth amplifiers is provided. Here, insights on the future trend towards operating at millimeter-wave are first discussed followed by a more particular discussion on distributed amplifier device as a promising solution to overcome the upper limit on frequency.

In Chapter 3, an overview of existing design techniques for distributed amplifiers and their limitations for mm-wave usage are described. An original matrix-based design model, based on four-port chain *ABCD*-parameter, is then proposed as a reliable and accurate model for this specific active circuit design to reach full CAutoD process.

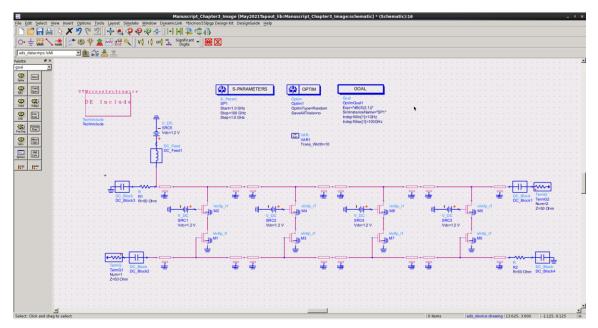

In Chapter 4, a loss-compensated distributed amplifier, a topology for mitigating the high losses issue of mm-wave frequencies, is described. Based on its concept and using the proposed model of Chapter 3, an algorithmic design methodology is presented that maximizes bandwidth for a given passband flatness. Its outcome is a set of 3D design space exploration (DSE) plots that enables to explore a wide range of possible distributed amplifier solutions.

In Chapter 5, from the resulting DSE plots of Chapter 4, a global optimum 100-GHz bandwidth CMOS-based distributed amplifier is chosen and implemented for on-wafer characterization.

In Chapter 6, a THz gain-bandwidth cascaded CMOS-based distributed amplifier, with the same upper operating frequency of 100 GHz, is presented.

In the previous three chapters, the 55-nm CMOS process provided by STMicroelectronics (ST) was adopted for both illustration, and design exploration and implementations.

Finally, Chapter 7 provides a summary and general conclusion for the work presented in this manuscript.

# Chapter 2

# Introduction to Wideband Amplifiers – Distributed Amplifier for mm-Wave Access

In this chapter, a particular discussion is devoted on amplifiers capable of extending their operating frequency deep in the mm-wave band and proving distributed amplification as a unique solution with ultra-wide bandwidth performance from a few gigahertz until hundredth of gigahertz.

This chapter is structured as follows. Section 2.1 explains the motivation behind recent trend followed by analog designers towards realizing ICs in mm-wave band. It also sheds light on broadband amplification as an indispensable component of high demand in the near future. Section 2.2 examines several amplifier circuit topologies proposed in the literature to overcome the limitation on bandwidth, and demonstrates distributed amplification as a promising candidate for ultra-wide bandwidth. Section 2.3 focuses on the history, principle of operation, and technology versatility of distributed amplifiers. Here, a state-of-the-art table in different technology processes is provided for performance tradeoff comparison. Finally, Section 2.4 concludes this chapter and sets the tasks that will be covered in the following chapters.

# 2.1 Future Trends for Millimeter-Wave Applications

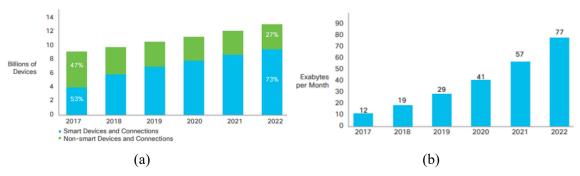

The RF spectrum is a finite resource to be shared by all network devices in the world. As years progress, the number of connected devices and data traffic is increasing at a significant rate, as illustrated in Figure 2.1. Those statistical graphics are provided by Cisco corporation [17] and demonstrate, via Figure 2.1(a), that by the year 2022 the overall amount of connected devices will reach 12.3 billion units, a 43% growth from 8.6 billion devices in 2017. In addition, via Figure 2.1(b), the overall mobile data traffic is expected to

grow to 77 exabytes (10<sup>9</sup> gigabytes) per month by 2022, a seven-fold increase over 2017. Both statistics point to a no nearby deceleration in the amount of circulating information, on the contrary, they indicate a continuous surge in telecommunication in the upcoming years.

Figure 2.1: Global (a) growth of connected devices and (b) mobile data traffic in exabyte (10<sup>9</sup> gigabytes) per month, from 2017 to 2022. [17]

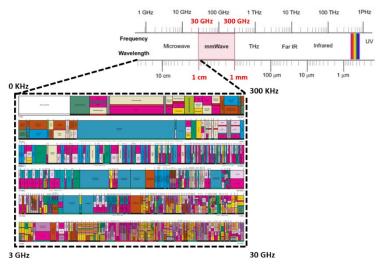

Usually, the frequency spectrum is divided into several differently sized small-portions in order to accommodate the multi RF-applications. A demonstrative example of such radio spectrum partitioning, adopted by the United States [18], is illustrated in Figure 2.2. Oversharing of the spectrum, however, can lead to unintentional interference. This can happen between signals through overlapping of a given carrier sideband with upper and/or lower sidebands of adjacent carriers, and interference that occurs when frequencies shift slightly. In either case, they make it difficult or near impossible for receivers to pick out the correct signal. This unintentional interference mostly occurs because generating and treating an RF-signal is an imperfect process. Figure 2.2 can also serve as a visual proof for demonstrating the congestion we reached in recent frequency spectrum due to oversharing. Indeed, the common range spanning from few KHz to 30 GHz is over-populated and it is becoming progressively difficult to open room for future devices and applications, and a bottleneck for the support of the many attractive but bandwidth-demanding services of the coming multimedia society.

Figure 2.2: Radio spectrum demonstrating frequency allocations adopted by the United States. [18]

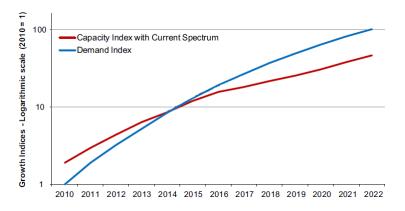

One common way used to alleviate this issue is by increasing the spectral efficiency, unit of measurement defined by (bits/sec)/Hz. This can be achieved through signal multiplexing techniques; for instance, through orthogonal frequency-division multiplexing (OFDM). Such ways, however, are starting to reach saturation levels in recent years [19], as shown in Figure 2.3, where capacity growth is slowing down and unable to keep up with the continuous increase in services demand. Due to occurring congestion in the frequency spectrum below 30 GHz, we reached a period in time where trying to push few bits of extra information in just a single Hertz of frequency component is becoming significantly challenging. Figure 2.3 also gives an early intuition that recent years advancement in radio resources management techniques is slowing down in demonstrating a notable improvement compared to the previous years; therefore, advocating the need to look for other solutions for the years to come.

Figure 2.3: Comparing data capacity growth to demand growth. [19]

By referring back to Figure 2.2, one could perceive another promising solution and it is exploring the mm-wave band, i.e., beyond 30 GHz, to arrange more bandwidth. As formalized in the Shannon-Hartley theorem, enlarging bandwidths does indeed comply with obtaining higher channel capacity. In theory, there is an unlimited amount of unexploited bandwidth available in the 300 GHz frequency spectrum. It has motivated many research contributions on mm-wave electronics for wireless communication in general and broadband implementation in particular. Indeed, the sufficient broadband spectrum that exists there has sparked interest in a variety of potential applications, such short-range high data-rate wireless personal area networks (WPANs), wireless local area networks (WLANs) with extraordinary capacity, and wireless uncompressed digital-video transmission. This also allows for a variety of applications including gigabit/s point-topoint links, wireless docking for portable devices, and vehicular radar. Millimeter-wave systems find also place in the field of bio-medical devices. Today, imaging devices are largely confined to health-centers and large hospitals. The dynamics of patient-health provider interaction will radically change if these diagnostic tools are available by patient's side rather than at long distances. Examples include large-array low-power ultrasonic imagers and lab-on-chip devices for rapid detection of pathogens or sequencing of DNA [20]-[22]. Diagnostic medical imaging is another application that can greatly benefit from large capacity offered by such spectrum. Even in wireline communication, wireline backbones, such as fiber optic communication systems, with data rates of over 100 Gb/s per channel will be required in the near future and for those ultra-broadband systems with

a minimum required bandwidth of 50 GHz are key components in such systems [23]. Therefore, the 30 GHz-300 GHz spectrum spanning about 55 GHz of contiguous bandwidth is identified as the most suitable candidate to accommodate the ever increase of circulating data deduced. It is also appearing as a promising solution for the support of all kinds of bandwidth-demanding services and applications that run at fiber speeds and beyond.

In fact, significant efforts in the development of ICs with frequencies extending into the mm-wave spectrum is already being observed. In parallel, silicon technology is being considered as an attractive design tool for the cost-reduction and miniaturization offered by it. Those efforts can be noticed from the available state-of-the-art research work [24]-[29], [30]-[36], to give example of few, which highlights the trend being adopted in pushing the limit of high frequency operation and in enlarging bandwidth performance. Through those available researches, diverse circuit techniques are being proposed besides their corresponding design theory and while offering the design tools and methodologies necessary to replicate such performance characteristics.

In this thesis, efforts were concentrated on broadband mm-wave amplification, in particular on a minimum of 50 GHz bandwidth to support future 100 Gb/s capacity and higher. This is elaborated more in the next section (Section 2.2) where several amplifier topologies, each with its own bandwidth limit, are listed and briefly described, where the most promising one is a distributed structure.

# 2.2 Amplifier Circuit Topologies with Wide Bandwidth Characteristic

As telecommunication technology proceeds, expectations from an amplifier increase with it. Today's telecommunication systems require wideband, efficient and high gain amplifiers. Depending on the application, requirements on an amplifier change. Obtaining high-gain and wideband systems has been one of the main areas of focus in wireless and wireline technologies. In RF and microwave amplifiers, transistors are employed as the main component; however, physical constraints of transistors put an upper limit to the gain and bandwidth of a practical amplifier. This fact is observed as gain-bandwidth product (GBP) which stays constant for an amplifier design. For these reasons, special consideration must be given to the problem of designing wide bandwidth amplifiers. Researchers have come up with some topologies to overcome the limitation on bandwidth. Some of those common approaches are listed below; note in each case that an improvement in BW is achieved at the expense of complexity, i.e., more correlated design variables to take into consideration, an added challenge when searching for optimum performance.

#### 2.2.1 Small-to-Large Bandwidth Amplifiers Topologies

The topic of integrated amplifiers is not considered as a newborn research topic. For that, the literature demonstrates plenty of circuit prototypes implemented in several process nodes and each with different performance improvement objectives. In this section, concentration is put solely on the ones with bandwidth improvement as objective. Those topologies are listed starting by the one that offers the smallest bandwidth and ending by the topology that offers the largest one. For each case, a single optimum design example is

given. A short description for each design is given accompanied by frequency behavior examination through S-parameter analysis.

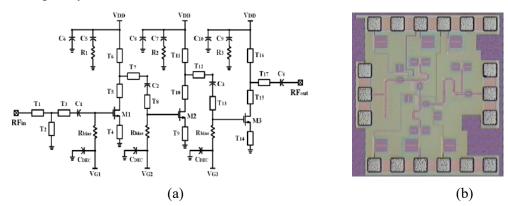

# 2.2.1.1 Single-Transistor Amplifier Topology [24]

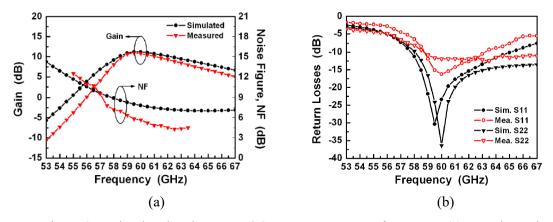

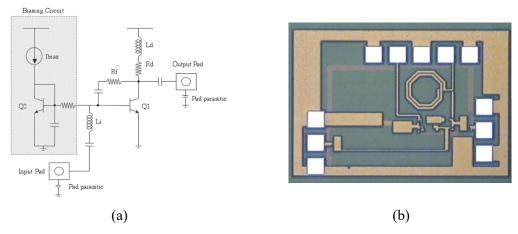

We begin this listing by what could be arguably considered as the simplest topology one could synthesize and it involves using a single transistor as Gm-cell. It is considered of importance to demonstrate what one could obtain as frequency behavior when using just a simple transistor biased in the active region in order to support the efforts towards more complex topologies. It will also serve as a performance benchmark for the topologies coming after. [24] demonstrates such amplifier through a prototype implemented in 90-nm CMOS technology. Figure 2.4(a) and Figure 2.4(b) illustrate the circuit schematic and microphotograph, respectively. This amplifier is synthesized as a three-stage amplifier connected in series in order to increase its gain in the given bandwidth: a sign of weak amplification provided by just a single transistor. From Figure 2.5(a), the fabricated amplifier exhibits 10.8 dB of gain with 5 GHz of 3-dB bandwidth around 60 GHz, i.e., 8.3% of fractional bandwidth (FBW). The total power consumption is only 5.5 mW from a 1-V power supply. From Figure 2.5(b), both input and output return losses,  $S_{11}$  and  $S_{22}$ , respectively, exhibit narrowband behavior with values better than -15 dB at 60-GHz center of frequency.

Figure 2.4: Single-transistor amplifier topology. (a) Schematic circuit diagram. (b) Microphotograph. [24]

Figure 2.5: Simulated and measured *S*-parameters versus frequency. (a) Insertion gain. (b) Input and output return losses. [24]

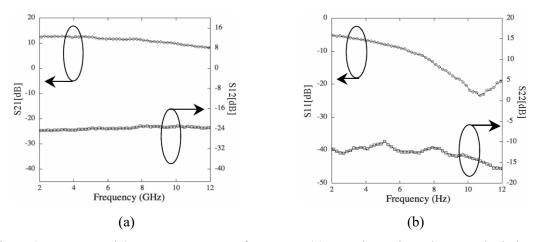

### 2.2.1.2 Resistive-Feedback Amplifier Topology [25]

The first suggested topology for obtaining wide bandwidth amplification is through resistive-feedback configuration [25]. Figure 2.6(a) illustrates the schematic view of this topology. The resistive shunt-feedback provides wideband input matching. Its bandwidth is dominated by the RC time constant at the input/output node. Figure 2.6(b) shows the implemented microphotograph using 0.18-µm SiGe BiCMOS process. The measured S-parameters are plotted in Figure 2.7. From Figure 2.7(a), a gain of 13 dB with 3-dB bandwidth of 10 GHz is obtained, i.e., more than 100% of FBW. While FBW here does seem interesting at first; however, one should note that as we increase in frequency, the inherent parasitic of the transistor start to affect the shunt matching provided by the resistive feedback. This makes it challenging to maintain wideband matching at mm-wave spectrum and support the efforts for more complex topologies. The fabricated amplifier consumes 4 mA from a 2.4-V power supply. From Figure 2.7(b), the input and output return losses are below -5 dB and -10 dB, respectively, within the declared passband. Through this topology, bandwidth enlargement is possible compared to the single-transistor amplifier topology [24] discussed at the beginning of this section.

Figure 2.6: Resistive-feedback amplifier topology. (a) Schematic circuit diagram. (b) Microphotograph.[25]

Figure 2.7: Measured S-parameters versus frequency. (a) Insertion gain and reverse isolation. (b) Input and output return losses. [25]

# 2.2.1.3 Cascode Amplifier Topology [26]

Since design interest is focused on the mm-wave frequency region, parasitic capacitance becomes difficult to neglect. The most unfavorable capacitance that causes gain and bandwidth degradation a single transistor experiences is the input-to-output overlap parasitic, leading to a parasitic Miller capacitance. Arguably, the most widely used technique to mitigate it is by using a conventional cascode topology, where two transistors configuration is used at its simplest form. [26] demonstrates such cascode cell designed at 60 GHz and implemented with a 90-nm CMOS process. Its circuit topology and microphotograph are shown in Figure 2.8(a) and Figure 2.8(b), respectively. Its frequency response through S-parameters characterization is demonstrated in Figure 2.9. The amplifier exhibits 14 dB gain with a 3-dB bandwidth of 23 GHz around 60 GHz at 32-mW of total power consumption, i.e. 38.3% of FBW. The input and output return losses are below -8 dB within the declared passband region. Through this topology, a near five-fold fractional bandwidth enlargement is possible compared to the single-transistor amplifier topology [24] discussed at the beginning of this section.

Figure 2.8: Cascode amplifier topology. (a) Schematic circuit diagram. (b) Microphotograph. [26]

Figure 2.9: Simulated and measured S-parameters versus frequency. [26]

### 2.2.1.4 Balanced Amplifier Topology [27]

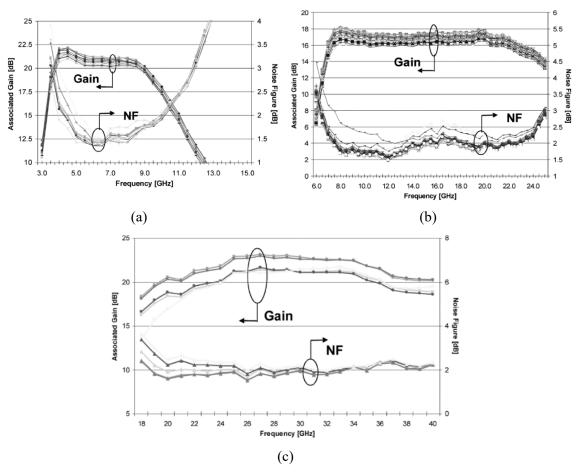

A common issue between microwave transistors is that they typically are not well matched to  $50 \Omega$  (a common standard reference-impedance). In the case of previous amplifiers topologies, matching networks where used. While matching network provides good input and output matching over the desired frequency bandwidth; however, it gives maximum gain only over a relatively narrow bandwidth. The balanced amplifier circuit solves this problem by using two 90-degree couplers to cancel input and output reflections from two identical amplifiers. [27] demonstrates such topology through a family of balanced amplifiers developed to cover an operating range of 4-40 GHz and implemented in a 0.1-µm pseudomorphic InGaAs/AlGaAs/GaAs HEMT production process. Schematic circuit diagram of only one design is presented here in Figure 2.10(a) with its respective microphotograph in Figure 2.10(b). The first 90° hybrid coupler divides the input signal into two equal-amplitude components, with a 90° phase difference, which drive the two amplifiers. The second coupler recombines the amplifier outputs. Because of the phasing properties of the hybrid coupler, reflections from the amplifier inputs cancel at the input to the hybrid, resulting in an improved impedance match; a similar effect occurs at the output of the balanced amplifier. [27] targeted three designs with different frequency bands including 4-9 GHz, 9-20 GHz, and 20-40 GHz, as illustrated in Figure 2.11. The two first designs demonstrate the excellent qualities of balanced amplifiers in terms of matching characteristics, while proving higher FBW than previously discussed designs, 77% and 76% for the 4-9 GH and 9-20 GHz cases, respectively, with a maximum of -15 dB of return loss for the 4-9 GHz and -17 dB for the 9-20 GHz. The 20-40 GHz also proves an extended bandwidth but return loss is not provided; nonetheless, its FBW extends up to 66.7%. Through the two first topologies, a nine-fold fractional bandwidth enlargement is possible compared to the single-transistor amplifier topology [24] discussed at the beginning of this section. The third topology shows an eight-fold improvement.

Figure 2.10: Balanced amplifier topology. (a) Schematic circuit diagram. (b) Microphotograph. [27]

Figure 2.11: Measured insertion gain responses of (a) 4-9 GHz, (b) 9-20 GHz and (c) 20-40 GHz balance-topology amplifier. [27]

#### 2.2.1.5 Transformer-Coupled Amplifier Topology [28]

Similar to the balanced amplifier concept, the transformer-coupled topology aims at providing a wide bandwidth input- and output- matched impedances. Instead of using a 90degree coupler, the following topology proposes the usage of transformers for input and output matching. Through them, they can simultaneously perform impedance transformation and differential-to-single-ended conversion. [28] demonstrates such circuit realized in a 0.13-µm SiGe BiCMOS process at 60 GHz with two coupled loop inductors as transformers. Circuit schematic is shown in Figure 2.12(a) with its microphotograph shown in Figure 2.12(b). Performance characterization of the amplifier against frequency is illustrated in Figure 2.13. A 3-dB bandwidth of 56 GHz, from 34 to 90 GHz, i.e. 90% of FBW, is obtained with gain of 12.25 dB while consuming a total  $P_{DC}$  of 270 mW. Matching is poorer than 6 dB in the lower band from 34 to 50 GHz. By reducing requirements to a reasonable matching better than 6 dB, the passband reduces within 50 to 90 GHz, i.e. still 57% of FBW that is almost seven-fold the one of the reference single transistor. Nonetheless, by relaxing the constraints on matching characteristic and on the basis of solely the stated amplification-passband 3-dB bandwidth (56 GHz), through this topology almost eleven-fold bandwidth enlargement is possible compared to the single-transistor amplifier topology [24] discussed at the beginning of this section.

Figure 2.12: Transformer-coupled amplifier topology. (a) Schematic circuit diagram. (b) Microphotograph. [28]

Figure 2.13: Measured S-parameters versus frequency. [28]

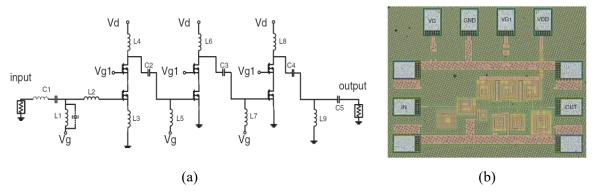

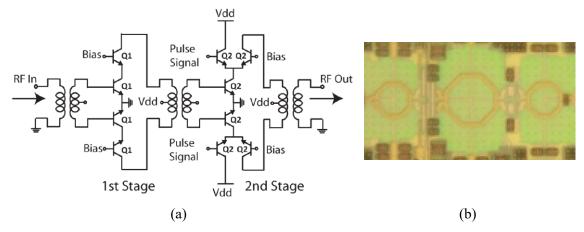

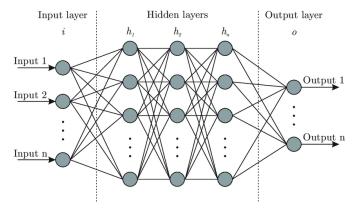

#### 2.2.1.6 Distributed Amplifier Topology [29]

We end this listing by mentioning the topology that offers the widest bandwidth. Ultrawide bandwidth characteristic is possible with distributed amplifier topology. As a short overview, with more in-depth details on its principle of operation provided in Section 2.3, the DA achieves its large bandwidth trough connecting pair of inductive-type segments at both the input and output ports of Gm-cell. Since the Gm-cell experiences input and output parasitic capacitance at high frequencies, the latter combined with inductive-type segments create what is called artificial transmission line (TL). Those artificial lines provide wide bandwidth matching which makes broadband amplification possible. Meanwhile the high gain of the DA results from the cumulative gains of those small Gm-cells. As a demonstrative example, [29] illustrated the performance capability of a 100-GHz DA, centered around 50 GHz from 4 to 104 GHz, i.e. 200% of FBW, implemented in a 45-nm CMOS SOI process. The meaning of center operating frequency loses somewhat sense with this architecture that can be seen as an accumulation of small sections of Gm-cells, each one showing an extended cut-off frequency due to inductive-type segments. In spite of that, its cut-off frequency can be adjusted through its design parameters, such as transistor size,

and thus justifying the possibility to mention here the 50 GHz center frequency. Figure 2.14(a) and Figure 2.14(b) represent both its schematic diagram and fabricated circuit, respectively. From Figure 2.15, the amplifier attains 16 dB of gain while being powered from a 5-V supply. Through this topology, a twenty-two-fold bandwidth enlargement is possible compared to the single-transistor amplifier topology [24] discussed at the beginning of this section.

Figure 2.14: Distributed amplifier topology. (a) Schematic circuit diagram. (b) Microphotograph. [29]

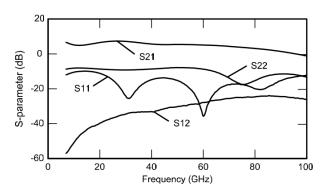

Figure 2.15: Measured S-parameter versus frequency. [29]

# 2.2.2 Table-of-Comparison for Performances Analysis

The six amplifier topologies that were presented in subsection 2.2.1 are summarized in Table 2.1. The purpose of this table is to review their performance tradeoffs and highlight, as a matter of course, why, in the context of RF spectrum enlargement towards mm-waves, the suitable topology is distributed amplification that will be the subject of further study in this manuscript. Since overcoming the upper limit on the gain and bandwidth of a practical amplifier is the motivation behind the proposal of such designs, the accent is put here on Gain-Bandwidth product (GBP) criterion. Special consideration on minimum bandwidth of 50 GHz is taken into account as it is important for future 100 Gb/s and beyond applications, as discussed previously in Section 2.1.

TABLE 2.1: PERFORMANCE COMPARISON BETWEEN WIDE BANDWIDTH AMPLIFIER TOPOLOGIES.

| Ref. | Amplifier<br>Topology           | Gain<br>(dB) | Bandwidth<br>(GHz) | P <sub>DC</sub> (mW) | Chip Area (mm²) | GBP<br>(GHz) |

|------|---------------------------------|--------------|--------------------|----------------------|-----------------|--------------|

| [24] | Single Transistor<br>(Cascaded) | 10.8         | 5                  | 5.5                  | 0.39            | 17           |

| [25] | Resistive-feedback              | 13           | 10                 | 9.6                  | 0.88            | 45           |

| [26] | Cascode                         | 14           | 23                 | 32                   | 0.22            | 115          |

|      | Balanced                        | 20           | 5                  | 187.5                | 12.16           | 50           |

| [27] |                                 | 17           | 11                 | 187.5                | 12.16           | 78           |

|      |                                 | 22           | 20                 | 187.5                | 8.6             | 252          |

| [28] | Transformer-<br>Coupled         | 12.25        | 56                 | 270                  | 0.15            | 229          |

| [29] | Distributed                     | 16           | 100                | N/A                  | 0.73            | 640          |

The first three topologies: single-transistor [24], resistive-feedback [25] and cascode [26] amplifiers are the one which present relatively simple design process compared to the remaining topologies, since they involve few components to deal with. They even show attractive low  $P_{DC}$  suited for low power consumption applications. However, they do not meet the required minimum bandwidth of 50 GHz and provide the lowest GBP merit, and hence were disregarded. Balanced amplifier topology [27] could demonstrate possible potentials in reaching this bandwidth requirement when pushed towards higher frequencies and it also shows flexibility in its GBP where one can obtain different BWs using the same topology. However, its design necessitates the implementation of two Gm-cells devices, as illustrated in Figure 2.10(a), hence twice the DC power, but with an overall delivered gain equal to that of a single Gm-cell device.

Both transformer-coupled amplifier [28] and distributed amplifier [29] topologies fulfill the minimum bandwidth requirement. However, as explained in Section 2.1 and illustrated by Figure 2.1, the number of connected devices and data traffic, in other words, data network, is constantly increasing and with no sign of stopping in the future. At one moment in the future, even larger bandwidths will be of need. Hence, a good research practice would be to anticipate the future and be prepared for the system demand. For that reason, distributed amplifier is chosen as topic of further discussion since it is the only topology that presents potential ultra-wide bandwidth performance reaching deep into the millimeterwave spectrum. It also coincides with continuous advancement in technology nodes where smaller nodes are reaching higher frequency limits. It is worth also adding from a practical point of view, that the transformer-coupled amplifier presents inability to start amplifying from very low frequencies, if needed, compared to distributed amplifier. A requirement for fiber optic communications. This lack of ability to amplify starting from DC-level is because in the former topology, the input signal is being fed through a transformer to the input of the transistor, as shown in Figure 2.12(a), compared to being feed through a transmission line segment as in the case of a DA, as shown in Figure 2.14(a).

As a conclusion and on those bases, the remaining of this chapter is dedicated into describing the DA circuit topology and analyzing its basic principle of operation and performances.

# 2.3 What is a Distributed Amplifier?

In Section 2.1, a serious issue of congestion in the lower side of the radio spectrum due to over-sharing was identified. It highlighted the efforts taken by analog designers in moving towards the unexplored millimeter band as a promising solution to respond to the consumer marketplace for high-speed applications and possibility, by expanding the allocation bandwidth, to accommodate further increase in data traffic. Several proposed amplifier topologies for enlarging bandwidth were discussed in Section 2.2 and demonstrated the trend adopted in continuously trying to push the upper frequency limit. Since DA presented the potentials of achieving the largest bandwidth, suitable for today and future needs, this section is dedicated to elaborate more on the subject. For a systematic presentation, it is divided into four subsections. It starts by presenting the history and interest of DA design since 1936. Then, it introduces its structure and principle of operation. The intention here is to give the reader a first step towards understanding how a DA usually functions and what controls its behavior. Several DAs implemented in different IC technology processes are also provided that demonstrate its widespread popularity between research community for performance exploration. Finally, a state-of-the-art table summarizing all IC DAs in different technology processes is presented and discussed.

# 2.3.1 Walk Through History

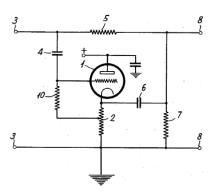

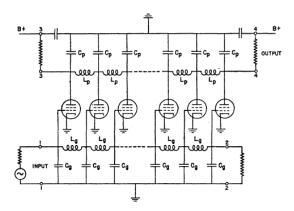

The potential of distributed amplification for obtaining gains over wide frequency bands has long been recognized. Historically, distributed amplifier is an ancient concept appearing in the 20th century. It was first explored by British inventor William S. Percival with vacuum tubes to compensate for the parasitic capacitance of electrodes. He later was the first to deposit a single patent on this topic in 1936 [37], shown in Figure 2.16, but without any exhaustive explanation or any trace of further discussion of this idea in the literature.

Figure 2.16: Thermionic valve circuit - William S. Percival's 1936 patent. [37]

The work became renown with the publication of [38] in 1948, where both Ginzton, Hewlett, Jasberg and Noe, based on the concept disclosed by William Percival, discovered that by appropriate distribution of vacuum tubes along artificial transmission lines, it is possible to obtain amplification over much greater bandwidths than would be possible with ordinary circuits. Their objective at that time was to find a practical solution for extremely broadband "video" amplifiers which have flat frequency response from low audio frequencies to frequencies as high as several hundred Megahertz. Due to technology

limitation at their generation, practical limitations of electron tubes prevented them to reach frequencies up to 1000 MHz. Nevertheless, [38] was considered the first published research work to present the principle in wide-band amplifier design and hence the term "distributed amplifier" was born. Figure. 2.17 illustrates the general principle of distributed amplification using vacuum tubes as amplification elements presented by [38], which later was adopted and still being adopted in recent research work.

Figure 2.17: First schematic diagram of distributed amplifier using vacuum tubes from 1948. [38]

Implementation using solid-state devices followed with early demonstration presented by [39] in 1969, where an attempt was made in implementing a distributed amplifier with 2 GHz bandwidth using MESFET technology.

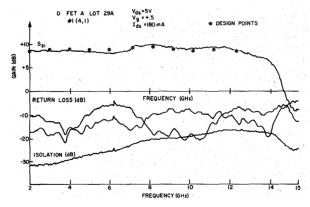

In 1982, [40] was published introducing a new concept of treating the DA as a continuous-structure model. It provided the required analytical approach to represent a DA gain behavior with respect to frequency and the design tools necessary to size one. In [40], the design concept was enhanced and made suitable for implementing amplifiers with several gigahertz of bandwidth. They demonstrated their idea through a practical example where they realized a DA that covers 1-13 GHz using 1-µm GaAs FET technology.

Even in the early 21<sup>st</sup> century, this concept is still being widely adopted between authors, such as [30]-[36], while synthesizing DAs at multi-gigahertz frequencies.

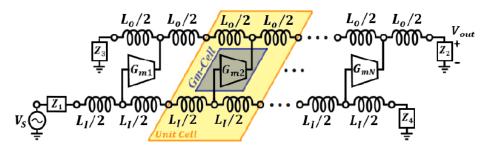

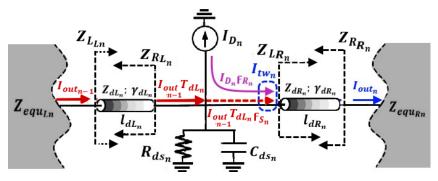

### 2.3.2 Structure and Basic Principle of Operation

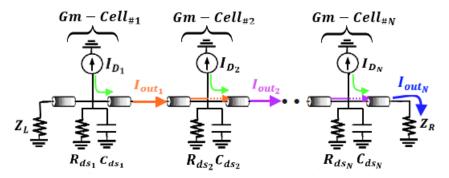

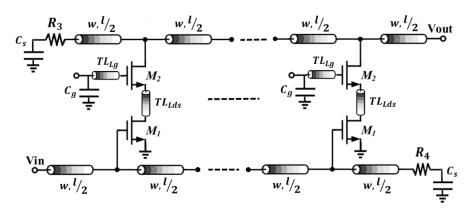

Figure 2.18 illustrates the configuration of a conventional distributed amplifier. The core of a DA design consists of what is commonly referred to as a unit cell. A unit cell is composed of a Gm-cell connected to a set of four inductive-type segments, depicted here as having an inductance value of  $L_I/2$  and  $L_O/2$ , on both its respective input and output sides. A set of N unit cells are connected together until a desired overall level of amplification is reached within a given passband. Since every Gm-cell is loading each inductive side by its own inherent output and input complex impedances, the overall upper and lower sides of DA are referred to, in this manuscript, as output- and input- loaded lines, respectively.

Figure 2.18: Conventional distributed amplifier made of *N* unit cells.

An RF signal  $(V_S)$  applied at the input end of the loaded input line travels towards the right side, where it is absorbed by the terminating load impedance  $Z_4$  at the opposite end. As it travels down, each Gm-cell samples a portion of the signal at different phase and amplitude, and then transfer it to the output line through its own transconductance. Due to the non-ideality of those Gm-cells, a small portion of both signals is wasted through dissipation caused by the cells resistive loads distributed along the input and output lines.

If the phase delay of the signal at the output-loaded line is identical to the phase delay of the input-loaded line, then the signals on the former line add constructively. The addition will be in phase only for the forward-traveling signal. There is also a backward traveling wave component on the output line, but the individual contributions to this wave will not be in phase, and therefore they at least partially cancel. Any signal which travels backward and is not completely cancelled by the out-of-phase additions, will be absorbed by the termination output impedance, represented by  $Z_3$  in Figure 2.18.

The basic principle behind distributed amplification is the absorption of the bandwidth limiting parasitic capacitances of Gm-cell into artificial transmission lines, which allows high bandwidths. In this approach, the added inductive-type segments combined with the parasitic capacitances are forming artificial TLs on each sides of the DA. The artificial lines will result in high cut-off frequencies, which will determine the new gain-bandwidth behavior of the desired amplifier. For a more in-depth explanation of this statement, the next discussion is dedicated to presenting the mathematical aspect behind the DA concept.

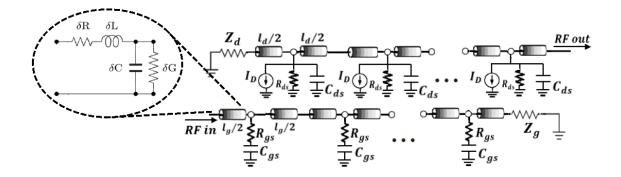

However, beforehand, for a clearer and more realistic analysis, the following modifications are carried out. First, the DA is split into two halves, as shown in Figure 2.19. The lower side represents the input loaded line and the upper side represents the output-loaded line. Second, since by the end of this manuscript a FET-based DA will be implemented as a circuit prototype for on-wafer characterization, it is considered suitable to adopt here, in the theoretical part, a FET-based Gm-cell and represent its behavior by its AC-equivalent lumped model. A unilateral assumption is used for its electrical model for the purpose of simplifying the derivation for a better interpretation of the concept. Finally, since in practice the ideal lumped inductors,  $L_I/2$  and  $L_O/2$ , are typically implemented each as physical microstrip, they are replaced here by microstrip transmission ( $\mu$ -TL) segments of length  $l_g/2$  and  $l_d/2$ , respectively.

Figure 2.19: Simplified equivalent-circuit representation of a FET-based distributed amplifier.

Referring to Figure. 2.19, both  $R_{gs}$ ,  $C_{gs}$ ,  $R_{ds}$ ,  $C_{ds}$  and  $I_D$  are the small-signal intrinsic elements of the FET transistor, and  $\delta R$ ,  $\delta L$ ,  $\delta C$  and  $\delta G$  are the per-unit-length series resistance ( $\Omega/m$ ), series inductance (H/m), shunt capacitance (H/m) and shunt conductance (H/m) of the lumped-element equivalent circuit of the  $\mu$ -TL segment.

The combination of the distributed FET parasitic with the segments creates the artificial transmission lines. The input (gate) and output (drain) loaded-lines are represented by their effective series inductance-per-unit-length  $\delta L_g$  and  $\delta L_d$ , respectively, of their own segments. Their effective shunt capacitance-per-unit-length is a result of a merge between the parasitic capacitances from the FETs and segments, i.e.,  $(\delta C_g + C_{gs}/l_g)$  and  $(\delta C_d + C_{ds}/l_d)$ , respectively. What remains as resistive lumped elements act as per-unit-length series and shunt losses for those equivalent transmission lines.

The previous assumption of equivalent lines is only valid when the spacing between the FETs, i.e.,  $l_g$  and  $l_d$ , is very small compared to the wavelength of operation (2.1).

$$l_g\big|_{max}$$

and  $l_d\big|_{max} << \lambda_{guided} = \frac{c}{\sqrt{\varepsilon_{eff}} \cdot f_{operation}}$  (2.1)

If this condition is satisfied, both lower and upper lines can be approximated each as continuous structure, referred to as artificial gate and drain lines, since FETs are used. Their characteristic impedances and propagation constants are deduced to be (2.2), (2.3) and (2.4), (2.5), respectively, [56].

$$Zc_g \approx \sqrt{\frac{\delta L_g}{\delta C_g + \frac{C_{gs}}{l_g}}}$$

(2.2)

$$Zc_d \approx \sqrt{\frac{\delta L_d}{\delta C_d + \frac{C_{ds}}{l_d}}}$$

(2.3)

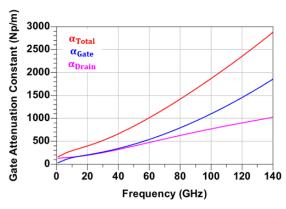

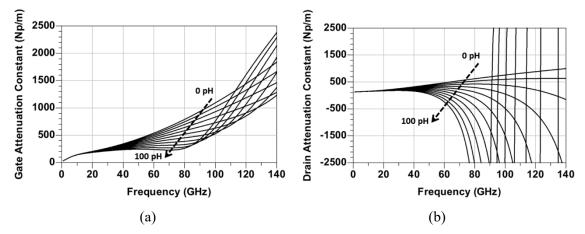

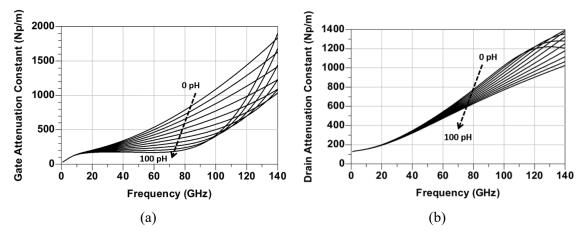

$$\gamma_{g} = \alpha_{g} + j\beta_{g} \approx \left(\frac{\delta R_{g}}{2} \sqrt{\frac{\delta C_{g}}{\delta L_{g}}} + \frac{\omega^{2} R_{gs} C_{gs}^{2} Z c_{g}}{2l_{g}}\right) + j\omega \sqrt{\delta L_{g} \left(\delta C_{g} + \frac{C_{gs}}{l_{g}}\right)}$$

(2.4)

$$\gamma_{d} = \alpha_{d} + j\beta_{d}$$

$$\approx \left(\frac{\delta R_{d}}{2} \sqrt{\frac{\delta C_{d}}{\delta L_{d}}} + \frac{Zc_{d}}{2R_{ds}l_{d}}\right)$$

$$+ j\omega \sqrt{\delta C_{d} \left(\delta C_{d} + \frac{C_{ds}}{l_{d}}\right)}$$

(2.5)

By preserving what was declared as initial condition in (2.1) for short length segments between Gm-cells, the gain expression for an *N*-cell DA circuit can be derived as follows.

For an incident source voltage,  $V_S$ , the voltage on the gate-to-source capacitance of the n<sup>th</sup> FET,  $V_{c_n}$ , can be written as (2.6) for a phase reference from the first transistor.

$$V_{C_n} = V_S e^{-(n-1)\gamma_g l_g} \left( \frac{1}{1 + j\omega R_{gs} C_{gs}} \right)$$

(2.6)

The factor in parentheses in (2.6) accounts for the voltage division between  $R_{gs}$  and  $C_{gs}$ . For small node FET parameters,  $(\omega R_{gs}C_{gs}) << 1$ ; therefore, this factor can be approximated as unity over the passband of the amplifier.

The output current on the drain line can be found by recognizing that each voltage-controlled current-source contributes to waves of the form  $(-1/2)I_{D_n}e^{\pm\gamma_dx}$  in each direction when perfect matching is assumed from both sides of each node. Since the transconductance of a given Gm-cell is given, by definition, as  $I_{D_n} = g_{m_n}V_{C_n}$ , the total output current at the  $N^{\text{th}}$  terminal of the drain line is found to be (2.7), [56].

$$I_{o} = -\frac{1}{2} \sum_{n=1}^{N} I_{dn} e^{-(N-n)\gamma_{d}l_{d}}$$

$$= -\frac{1}{2} g_{m} V_{S} e^{-N\gamma_{d}l_{d}} e^{+\gamma_{g}l_{g}} \sum_{n=1}^{N} e^{-n(\gamma_{g}l_{g} - \gamma_{d}l_{d})}$$

(2.7)

Using the geometric series summation formula given by (2.8), allows (2.7) to be simplified as (2.9).

$$\sum_{n=1}^{N} x^n = \frac{x^{N+1} - x}{x - 1} \tag{2.8}$$

$$I_{o} = -\frac{g_{m}V_{S}}{2} \frac{e^{\gamma_{d}l_{d}} \left(e^{-N\gamma_{g}l_{g}} - e^{-N\gamma_{d}l_{d}}\right)}{e^{-(\gamma_{g}l_{g} - \gamma_{d}l_{d})} - 1}$$

$$= -\frac{g_{m}V_{S}}{2} \frac{e^{-N\gamma_{g}l_{g}} - e^{-N\gamma_{d}l_{d}}}{e^{-\gamma_{g}l_{g}} - e^{-\gamma_{d}l_{d}}}$$

(2.9)

For a matched input and output ports, i.e.,  $Zc_g = Z_{in} = Z_4$  and  $Zc_d = Z_{out} = Z_3$ , the amplifier gain can be calculated as (2.10), [56].

$$Gain = \frac{P_{out}}{P_{in}} = \frac{\frac{1}{2} |I_o|^2 Z c_d}{\frac{1}{2} |V_S|^2 / Z c_g}$$

$$= \frac{g_m^2 Z c_g Z c_d}{4} \left| \frac{e^{-N\gamma_g l_g} - e^{-N\gamma_d l_d}}{e^{-\gamma_g l_g} - e^{-\gamma_d l_d}} \right|^2$$

(2.10)

As mentioned previously, if the phase velocity of the signal at the drain line is identical to the one of the gate line, then the output signals on the drain line add constructively. The addition will be in-phase only for the forward traveling signal. Referring to equation (2.7), the terms in the summation will add only when  $\beta_g l_g = \beta_d l_d$ , i.e., the phase delays on the gate and drain lines are synchronized.

Applying the synchronization condition of  $\beta_g l_g = \beta_d l_d$  allows equation (2.10) to be further simplified to (2.11), [56].

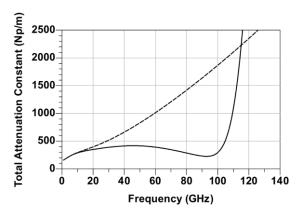

$$Gain = \frac{g_m^2 Z c_g Z c_d}{4} \frac{\left(e^{-N\alpha_g l_g} - e^{-N\alpha_d l_d}\right)^2}{\left(e^{-\alpha_g l_g} - e^{-\alpha_d l_d}\right)^2}$$

(2.11)

For an ideal case where the DA losses are neglected, the gain equation (2.11) can be reduced to (2.12)

$$Gain = \frac{g_m^2 Z c_g Z c_d N^2}{4} \tag{2.12}$$

Several interesting aspects of the distributed amplifier can be deduced from the gain expression of (2.11) and (2.12), as follows. From Equation (2.11), for a lossless distributed amplifier, the gain increase as  $N^2$ . When loss is present, Equation (2.11) specify that gain approaches zero as N tends to infinity. This behavior is explained by the fact that the input voltage on the input-loaded line decays exponentially. The same applies for the output-loaded line. Thus, the FET at the end of the amplifier receive no input signal.

Those imply that, for a given set of transistor parameters, there will be an optimum value of N that maximizes the gain of the amplifier. This can be found by differentiating (2.11) with respect to N and setting the result to zero to obtain (2.13).

$$N_{opt} = \frac{ln(\alpha_g l_g / \alpha_d l_d)}{\alpha_g l_g - \alpha_d l_d}$$

(2.13)

This result (2.13) depends on the frequency, the Gm-cell parameters and the line lengths through the attenuation constants given in (2.4) and (2.5).

## 2.3.3 Performance Demonstration through Different Technologies and Topologies

Distributed amplification topic received popularity between amplifier-research community as being a promising candidate for breaking restrictions on upper frequency limit. Owing to that, a noticeable amount of research work was made public demonstrating the versatility of DA in different IC technology processes from Si, SiGe and compound III-V technologies, such as InP and InGaAs. The common objective between those works, as was also stated by the authors, was presenting the possible performances from gain, bandwidth and  $P_{DC}$  one is capable of reaching through each technology. In this section, a handful of design examples that illustrates optimum performance in each technology is provided. Those designs are sorted out on the basis of their GBP achievements before their electrical performance are finally summarized in a state-of-the-art table for tradeoffs comparison in subsection 2.3.4. Only single stage DAs are duly presented herein for state-of-the-art relevance, excluding any cascaded DA configurations where achievable gains are inherently higher. Nonetheless, the later are introduced in Table 2.2 and their interest is justified with the discussion that follows it.

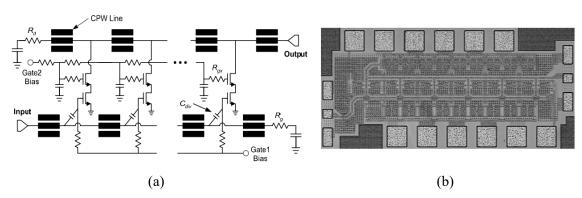

#### 2.3.3.1 A 4-91 GHz Bandwidth Distributed Amplifier in 90-nm Si CMOS [30]

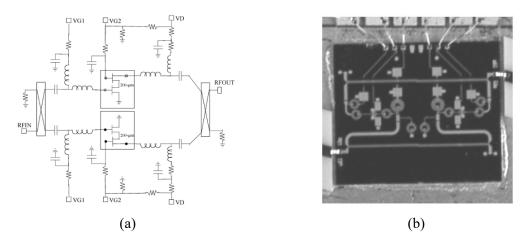

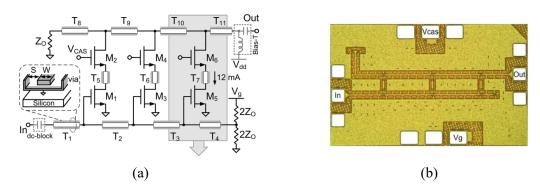

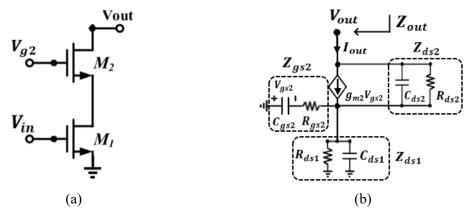

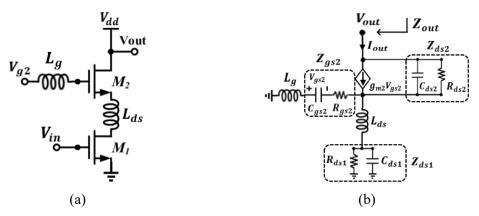

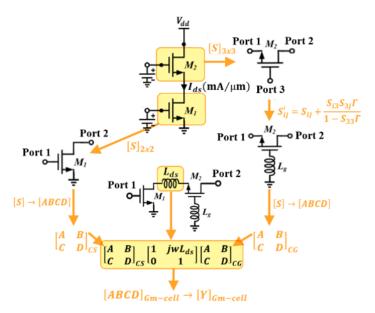

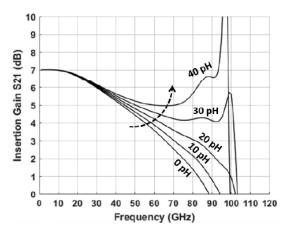

This article presents the design of a CMOS-based DA implemented in silicon 90-nm process node. This technology is benchmarked at  $f_t = 160$  GHz and  $f_{max} = 142$  GHz. The DA is synthesized with six unit-cells. Figure 2.20(a) illustrates its circuit diagram and Figure 2.20(b) its microphotograph for on-wafer characterization. The fabricated circuit occupies a chip area of  $0.6 \times 1.2$  mm<sup>2</sup> including pads. The conventional cascode topology with a two-transistor configuration was adopted for the Gm-cell and coplanar waveguide (CPW) was used for realizing inductive-type segments instead of conventional microstrip lines. Authors explain that with their back-end technology, they could guarantee lower losses at high frequency using CPW topology.

Figure 2.20: Six unit-cells 90-nm Si CMOS-based distributed amplifier. (a) Schematic diagram. (b) Microphotograph. [30]

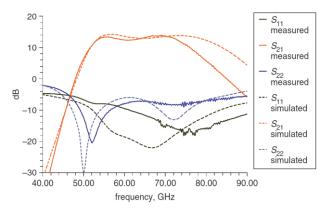

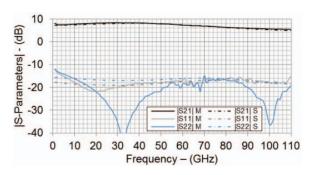

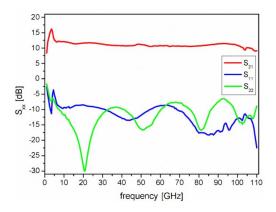

Referring to Figure 2.21, the measured S-parameters performance against frequency is shown. Their six-unit cell DA achieves a peak gain of 7.4 dB with a 3-dB bandwidth of 80 GHz. This results in a GBP of 190 GHz. The amplifier consumes 120 mW from a 2.4-V power supply. The measured output and input return losses across the 3-dB bandwidth reaches a maximum of -10 dB. The reverse isolation is better than -20 dB for the whole passband region.

Figure 2.21: Measured S-parameters of the 90-nm Si CMOS-based distributed amplifier. [30]

#### 2.3.3.2 A 92-GHz Bandwidth Distributed Amplifier in 45-nm SOI CMOS [31]

This article presents the design of a CMOS-based DA implemented in silicon-on-insulator (SOI) 45-nm process node. This technology is benchmarked at  $f_t = 350$  GHz and  $f_{max} = 300$  GHz. The DA is synthesized with three unit cells. Figure 2.22(a) shows the schematic diagram of the device and Figure 2.22(b) shows its microphotograph for on-wafer characterization. The fabricated circuit occupies a chip area of  $0.5 \times 0.8$  mm<sup>2</sup> including pads. The Gm-cell adopted is based on a cascode topology with a two-transistor configuration and the inductive-type segments are conventional microstrip lines.

Figure 2.22: Three unit-cells 45-nm SOI-based distributed amplifier. (a) Schematic diagram. (b) Microphotograph. [31]

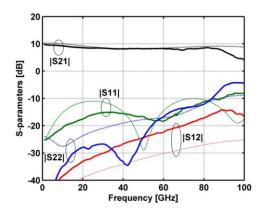

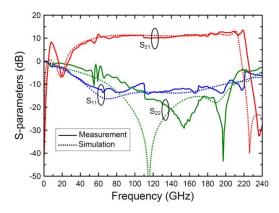

Referring to Figure 2.23, the measured S-parameters against frequency are plotted along with the simulated results. The amplifier achieves a 3-dB bandwidth of 92 GHz and a gain of 9 dB with a gain-ripple of  $\pm 1.5$  dB inside the passband region. This offers an overall gain-bandwidth of 259 GHz. The amplifier consumes 73.5 mW from a 1.2 V supply. The measured input return loss across the entire 3-dB bandwidth is better than -10 dB, but remains better than -15 dB below 70 GHz. The measured output return losses across the 3-

dB bandwidth is less than -6 dB but remains better than -10 dB below 84 GHz. The reverse isolation is -15 dB at 88 GHz and better than -20 dB below 70 GHz.

Figure 2.23: Measured (solid lines) and simulated (dotted lines) *S*-parameters of the 90-nm Si CMOS-based distributed amplifier. [31]

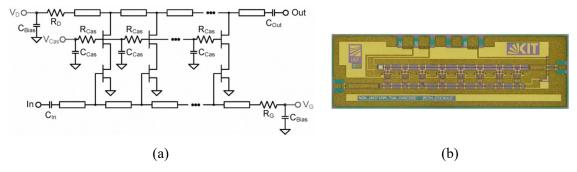

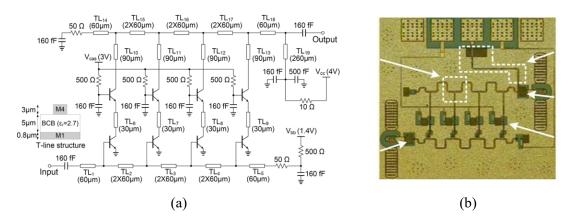

#### 2.3.3.3 A 110-GHz Bandwidth Distributed Amplifier in 22-nm FD-SOI CMOS [32]

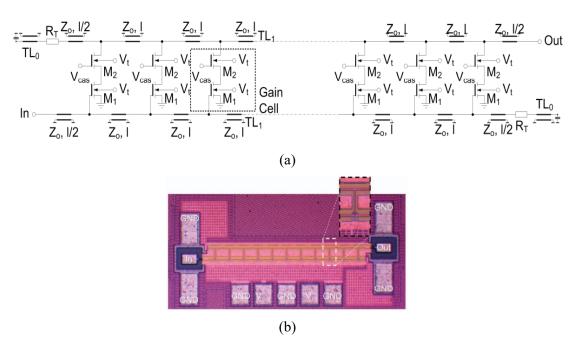

This article presents the design of a CMOS-based DA implemented in fully-depleted silicon-on-insulator (FD-SOI) 22-nm process node. This technology is benchmarked at  $f_{max} = 396$  GHz (authors did not provide value for  $f_t$ ). The DA is synthesized using eleven unit cells. Figure 2.24(a) shows the schematic diagram of the device and Figure 2.24(b) shows its microphotograph for on-wafer characterization. The chip occupies an area of  $0.38 \times 1$  mm<sup>2</sup> including the pads. The Gm-cell adopted is based on a cascode topology with a two-transistor configuration and the inductive-type segments are conventional microstrip lines.

Figure 2.24: Eleven unit-cells 22-nm FD-SOI-based distributed amplifier. (a) Schematic diagram. (b) Microphotograph. [32]

Referring to Figure 2.25, the measured S-parameters against frequency are plotted along with the simulated results. The amplifier achieves a 3-dB bandwidth of 110 GHz and a gain of 8.5 dB. This offers an overall gain-bandwidth of 292 GHz. The amplifier consumes 80 mW from a 2-V supply. The magnitude of the input and output return losses are both better than -15 dB for the whole amplifier bandwidth.

Figure 2.25: Simulated and measured *S*-parameters of 22-nm FD-SOI-based distributed amplifier. [32]

## 2.3.3.4 A 112-GHz, 157-GHz, and 180-GHz Bandwidth Distributed Amplifier in 100-nm InP HEMT [33]

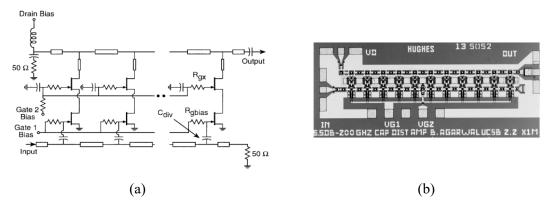

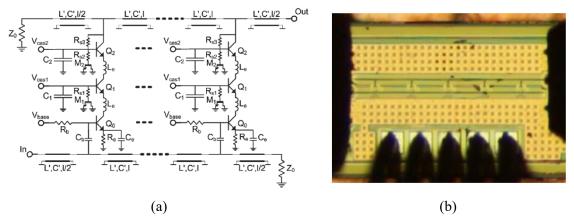

This article presents the design of a high-electron-mobility transistor (HEMT)-based DA implemented in 100-nm gate length InGaAs/InAlAs technology. This technology is benchmarked at  $f_t = 160$  GHz and  $f_{max} = 300$  GHz. It demonstrates the capability of such technology by synthesizing three DAs with different bandwidths: A 1-112 GHz, 1-157 GHz, and a third amplifier with 5-dB gain and a 180-GHz high-frequency cutoff. Figure 2.26(a) shows the schematic circuit diagram of the DA. The cascode topology with a two-transistor configuration and conventional  $\mu$ -TL line for the inductive segments were adopted as unit-cell Gm-cell. Figure 2.26(b) shows the microphotograph of the fabricated chip of 1-157 GHz DA. It consists of eleven unit cells and the die size is about 1 × 2.2 mm² including pads.

Figure 2.26: Eleven unit-cells 100-nm InP-based distributed amplifier. (a) Schematic diagram. (b) Microphotograph of the 1-157-GHz version. [33]

Referring to Figure 2.27, measured insertion gain  $(S_{21})$  for all three DAs against frequency are plotted. From Figure 2.27(a), the 1-112 GHz and 1-157 GHz DAs provide

7 dB and 5 dB of gain, respectively. The third DA, with 180 GHz cutoff frequency provides 5 dB of gain as shown in Figure 2.27(b). Those offer an overall gain-bandwidth of 248 GHz, 277 GHz and 320 GHz, respectively. The authors did not provide data for power consumptions.

Figure 2.27: Measured insertion gain of (a) 1-112 GHz and 1-157 GHz, and (b) 180 GHz 100-nm InP-based distributed amplifiers.[33]

#### 2.3.3.5 A 105-GHz Bandwidth Distributed Amplifier in 50-nm InGaAs mHEMT [34]

This article presents the design of a metamorphic HEMT-based DA implemented in 50-nm InGaAs technology. This technology is benchmarked at  $f_t = 380$  GHz and  $f_{max} = 500$  GHz. The DA fabricated consists of eight unit cells. Figure 2.28(a) illustrates the schematic circuit diagram. The Gm-cell adopted was based on cascode topology with a two-transistor configuration and conventional  $\mu$ -TL line was used for the inductive-type segments. Figure 2.28(b) illustrates the microphotograph of the implemented DA. The die size is  $0.75 \times 2.25$  mm<sup>2</sup>.

Figure 2.28: Eight unit-cells 50-nm InGaAs-based distributed amplifier. (a) Schematic diagram. (b) Microphotograph. [34]

Referring to Figure 2.29, the measured S-parameters against frequency are plotted. The DA covers a 3-dB bandwidth of 110 GHz with 11 dB of gain while consuming a total of 450 mW from a 6-V supply voltage. This leads to a GBP of 373 GHz. The passband region experiences a gain-ripple of around  $\pm 1$  dB from 5 GHz to 110 GHz. The gain peak, in the frequency range from 2 GHz to 5 GHz, is caused by the inductive feed of the DC bias voltages used for on-wafer measurements. The input return loss is below -10 dB from 10

GHz up to 110 GHz with a maximum of -5 dB for frequencies below 10 GHz. The output return loss is below - 7.5 dB from 5 GHz up to 100 GHz.

Figure 2.29: Measured S-parameters of 50-nm InGaAs-based distributed amplifier. [34]

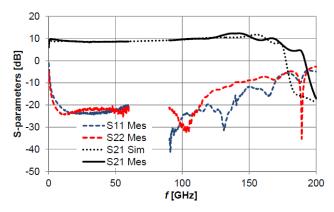

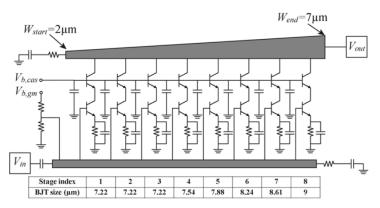

#### 2.3.3.6 A 170 GHz Bandwidth Distributed Amplifier in 130-nm SiGe HBT [35]

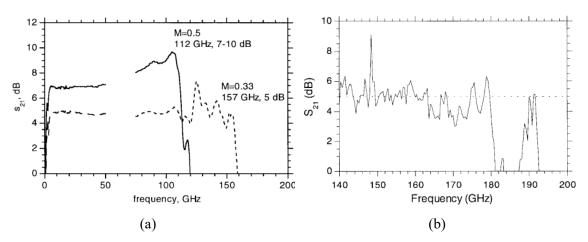

This article presents the design of a HBT-based DA implemented in 130-nm SiGe-BiCMOS technology. This technology is benchmarked at  $f_t = 300$  GHz and  $f_{max} = 500$  GHz. The DA fabricated consists of five unit cells and the Gm-cell adopted is based on cascode topology with a three-transistor configuration to increase voltage swing and hence output power. Slow-wave  $\mu$ -TL line topology was used for the inductive-type segments to reduce lines length. The cascode is designed to compensate the transmission-line-losses at high frequencies in order to extend the bandwidth as well as the GBP. Figure 2.30(a) and Figure 2.30(b) illustrate the schematic circuit diagram and the microphotograph of the implemented DA. The chip occupies an area of  $0.85 \times 0.45$  mm<sup>2</sup> including pads.

Figure 2.30: Five unit-cells 130-nm SiGe-based distributed amplifier. (a) Schematic diagram. (b) Microphotograph. [35]

Referring to Figure 2.31, the simulated and measured S-parameters against frequency are plotted. The amplifier provides a gain of 10 dB up to a 3-dB bandwidth of 170 GHz. It consumes a total of 108 mW FoM a 3.6-V supply. This leads to a GBP of 537 GHz. The passband region experiences a gain-ripple of  $\pm 2$  dB. The input return loss is below -20 dB

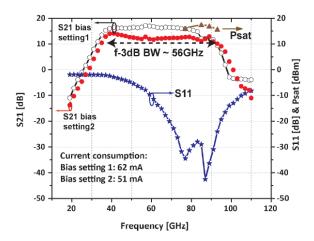

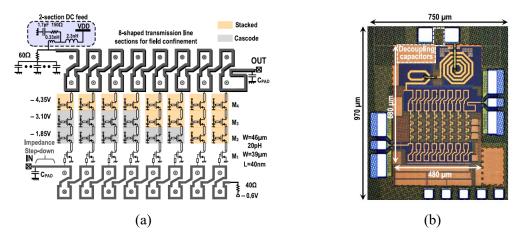

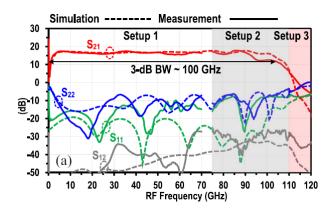

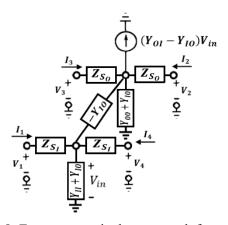

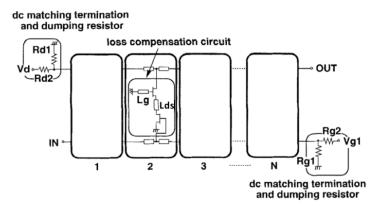

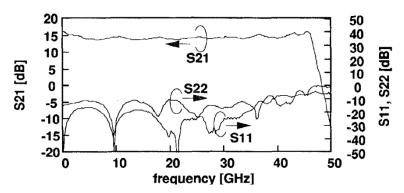

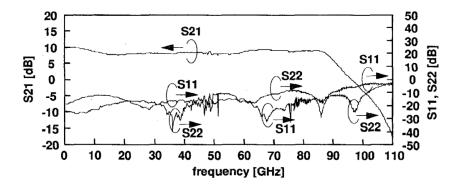

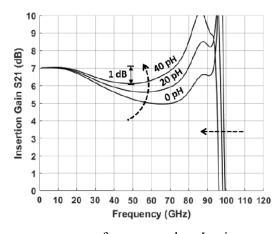

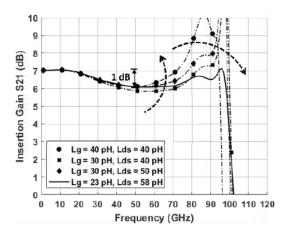

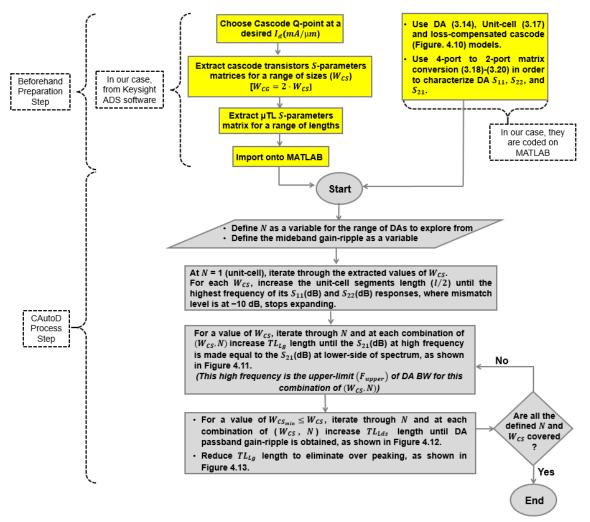

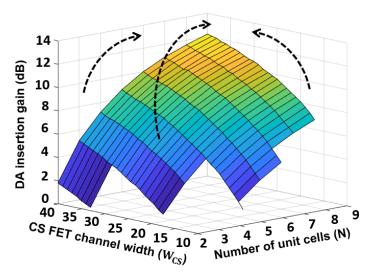

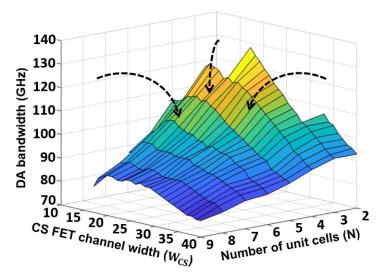

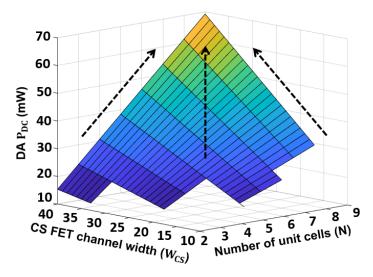

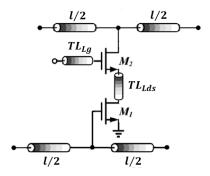

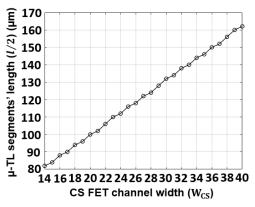

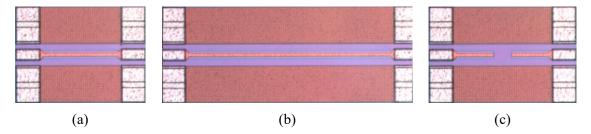

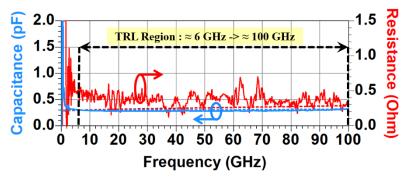

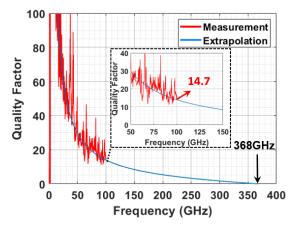

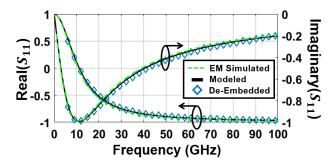

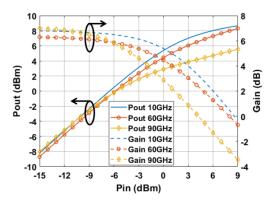

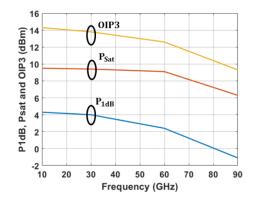

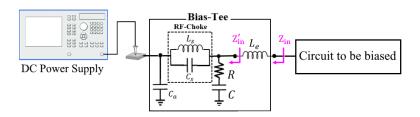

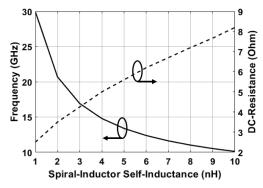

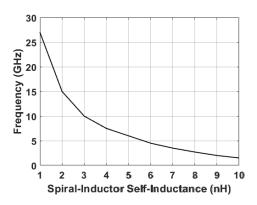

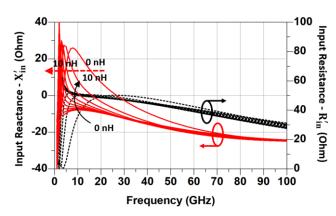

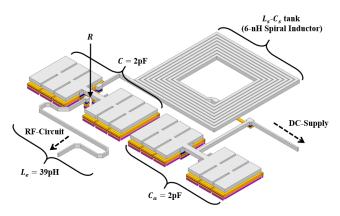

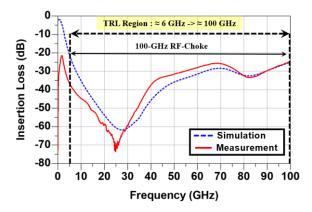

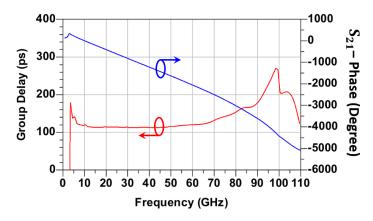

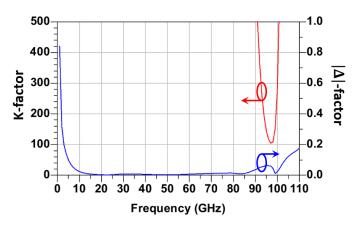

up to 100 GHz and then it increases with frequency reaching a maximum of -5 dB at 170 GHz. The output return loss is below -20 dB up to a higher frequency of around 140 GHz and then it starts to increase reaching a maximum of -5 dB at 170 GHz.