### Integrated circuits for energy harvesting from piezoelectric transducers

Liana Wassouf

#### ▶ To cite this version:

Liana Wassouf. Integrated circuits for energy harvesting from piezoelectric transducers. Micro and nanotechnologies/Microelectronics. Université de Strasbourg, 2022. English. NNT: 2022STRAD010. tel-03937733

#### HAL Id: tel-03937733 https://theses.hal.science/tel-03937733v1

Submitted on 13 Jan2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE STRASBOURG

# ÉCOLE DOCTORALE MSII (ED n°269)

LABORATOIRE ICUBE (UMR 7357)

# THÈSE

présentée par :

### Liana WASSOUF

soutenue le : 14 décembre 2022

pour obtenir le grade de : Docteur de l'université de Strasbourg

Discipline/ Spécialité : Micro et Nanoélectronique

### Circuits intégrés pour la récupération d'énergie à partir de transducteurs piézoélectriques

| THÈSE dirigée par :<br>M. FRICK Vincent | Maître de conférences HDR, Laboratoire ICube, Université de Strasbourg, CNRS |

|-----------------------------------------|------------------------------------------------------------------------------|

| RAPPORTEURS :                           | Chargée de recherche, Laboratoire LIP6, Sorbonne Université,                 |

| Mme. LOUERAT Marie-Minerve              | CNRS                                                                         |

| Mme. DESGREYS Patricia                  | Professeure, Laboratoire LTCI, Télécom Paris Tech                            |

| AUTRES MEMBRES DU JURY :                | Professeur, Laboratoire ICube, Université de Strasbourg, CNRS                |

| M. HEBRARD Luc                          | Maître de conférences, Laboratoire GREEN, Université de Lorraine             |

| M. JAMSHIDPOUR Ehsan                    | (co-encadrant)                                                               |

To my familly, Bassem, Hadi and Zeina. To my mother Mariana, and father Mahmoud in his peaceful place.

## Contents

| Lis | t of                                                 | Figures                              | 1                                                |

|-----|------------------------------------------------------|--------------------------------------|--------------------------------------------------|

| Lis | t of                                                 | Tables                               | 5                                                |

| Ré  | sumé                                                 | Long en Français                     | 7                                                |

| Ab  | ostrac                                               | t                                    | 11                                               |

| 1.  | 1.1.<br>1.2.<br>1.3.                                 | Context and objectives of the thesis | <b>13</b><br>13<br>17<br>24<br>25                |

| 2.  | <ol> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> </ol> | Introduction                         | 27<br>28<br>32<br>33<br>33<br>33<br>39<br>43     |

| 3.  | <b>Full</b><br>3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.  | Introduction                         | <b>47</b> 47 48 49 49 51 57 57 50 60 61 62 64 67 |

|     | 3.6.                                                                  | Transistor-level simulation results                                     | 68  |  |  |

|-----|-----------------------------------------------------------------------|-------------------------------------------------------------------------|-----|--|--|

|     | 3.7.                                                                  | Measurement results and discussion $\ldots$                             | 72  |  |  |

|     | 3.8.                                                                  | Conclusion                                                              | 76  |  |  |

| 4   | . Enhanced SSHC-based Full Active Rectifier with Reduced Set of Flip- |                                                                         |     |  |  |

| т.  | ping Capacitors (FAR-FC) 79                                           |                                                                         |     |  |  |

|     |                                                                       | Introduction                                                            | 79  |  |  |

|     | 4.2.                                                                  | Capacitor-based SSH interface circuit                                   | 79  |  |  |

|     | 4.3.                                                                  | FAR-FC interface circuit topology and operation principle               | 82  |  |  |

|     | 4.4.                                                                  | FAR-FC performance analysis                                             | 84  |  |  |

|     | 4.5.                                                                  | Circuit implementations of FAR-FC interface                             | 86  |  |  |

|     |                                                                       | 4.5.1. Damping/Building capacitors array $(D/B)$                        | 86  |  |  |

|     |                                                                       | 4.5.2. Active AC/DC rectifier and voltage regulator (VR) blocks $\dots$ | 87  |  |  |

|     | 4.0                                                                   | 4.5.3. Control (CTRL) and switch drivers (SD) blocks                    | 88  |  |  |

|     | 4.6.                                                                  | Transistor-level simulation results                                     | 94  |  |  |

|     | 4.7.                                                                  | Measurement results and discussion                                      |     |  |  |

|     | 4.8.                                                                  | Conclusion                                                              | 104 |  |  |

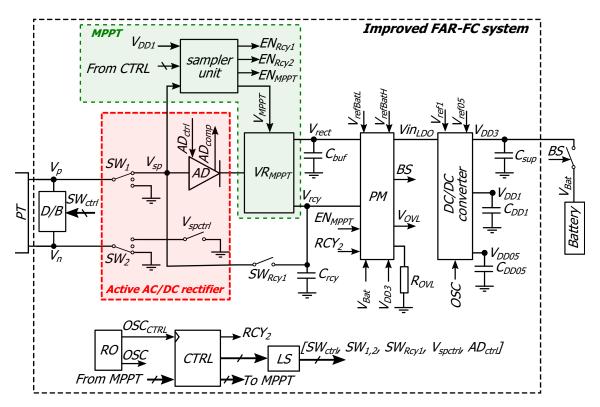

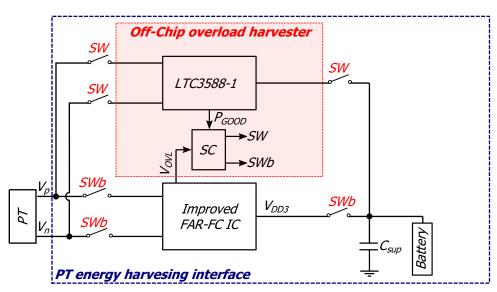

| 5.  | Impi                                                                  | roved Dynamic FAR-FC Interface Circuit                                  | 105 |  |  |

|     | 5.1.                                                                  | Introduction                                                            |     |  |  |

|     | 5.2.                                                                  |                                                                         | 105 |  |  |

|     |                                                                       | 5.2.1. Damping/Building capacitors array (D/B) and active AC/DC         | 107 |  |  |

|     |                                                                       | rectifier                                                               |     |  |  |

|     |                                                                       | 5.2.2. Maximum output power tracking circuit (MITT)                     |     |  |  |

|     |                                                                       | 5.2.4. DC/DC converter and level-up shifter block (LS)                  |     |  |  |

|     |                                                                       | 5.2.5. Control block (CTRL)                                             |     |  |  |

|     | 5.3.                                                                  | Simulation results and discussion                                       |     |  |  |

|     | 5.4.                                                                  | Operating under high PT mechanical excitation levels issue              |     |  |  |

|     | 5.5.                                                                  | Conclusion                                                              |     |  |  |

| 6   | Con                                                                   | clusion and perspectives                                                | 125 |  |  |

| 0.  | 6.1.                                                                  | Conclusion of the work                                                  |     |  |  |

|     | 6.2.                                                                  | Future work and open problems                                           |     |  |  |

| Ac  | know                                                                  | ledgments                                                               | 129 |  |  |

| Δ   | Pror                                                                  | oosed Full Active Rectifier (FAR)                                       | 131 |  |  |

| д.  | •                                                                     | First order FAR circuit during power extraction phase when the out-     | TOT |  |  |

|     | 4 1.1 1.                                                              | put voltage is lower than the regulated voltage                         | 131 |  |  |

|     |                                                                       |                                                                         |     |  |  |

| Bil | bliogr                                                                | raphy                                                                   | 133 |  |  |

# **List of Figures**

| 1.         | Système typique pour la récupération d'énergie piézoélectrique         | 8  |

|------------|------------------------------------------------------------------------|----|

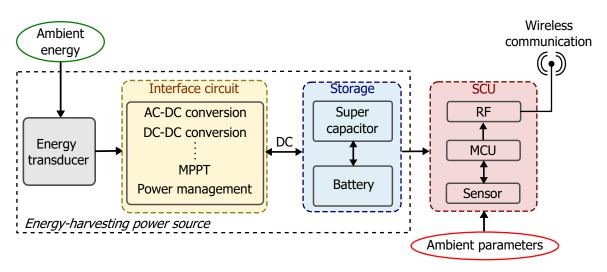

| 1.1.       | Typical block diagram of a wireless sensor node powered from ambient   |    |

|            | energy source                                                          | 14 |

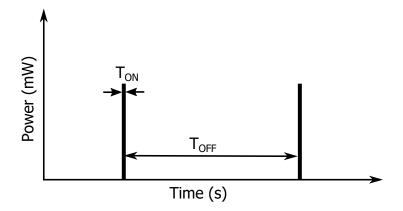

| 1.2.       | Wireless sensor operation.                                             | 15 |

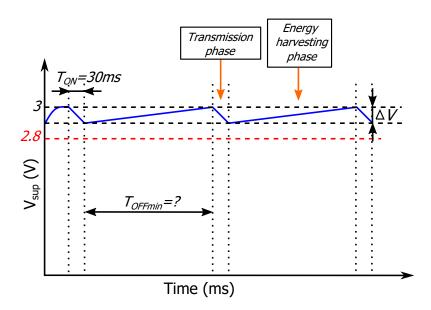

| 1.3.       | Storage elements voltage evolution during on-state and off-state wire- |    |

| <b>.</b> . | less sensor operation modes.                                           | 16 |

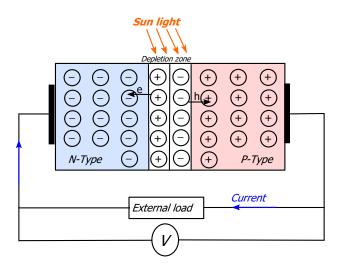

| 1.4.       | Principle operation of a PV cell.                                      | 17 |

| 1.5.       | The main types of the PV cell [1]                                      | 18 |

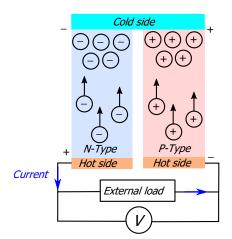

| 1.6.       | The seebeck effect of a thermocouple.                                  | 18 |

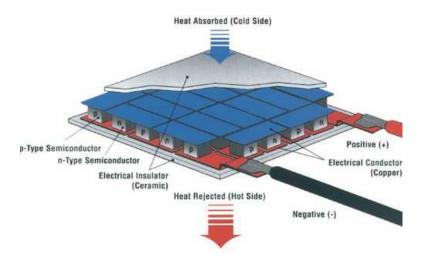

| 1.7.       | Thermoelectric generator structure [2]                                 | 19 |

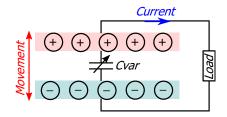

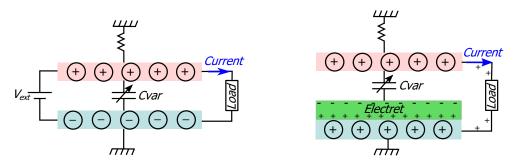

| 1.8.       | Electrostatic energy conversion principle.                             | 20 |

| 1.9.       | Electrostatic harvester types: electret-free (left) and electret-based | 20 |

| 1 10       | (right)                                                                | 20 |

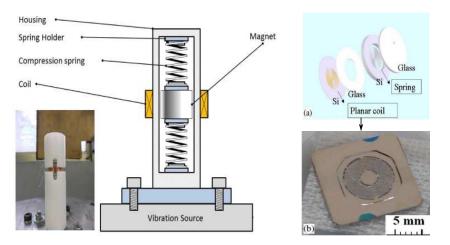

| 1.10.      | Electromagnetic harvesters: macro harvester (left) [3], and micro har- | 01 |

| 1 1 1      | vester with planner coil (right) [4].                                  | 21 |

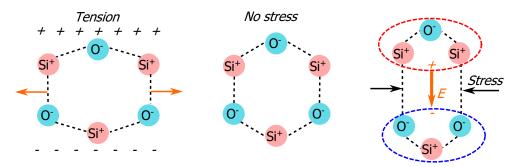

| 1.11.      | Piezoelectric effect in quartz crystal.                                | 22 |

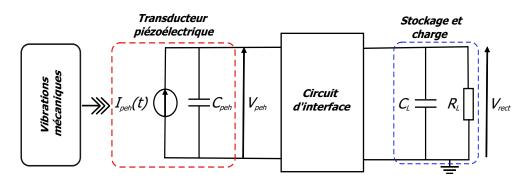

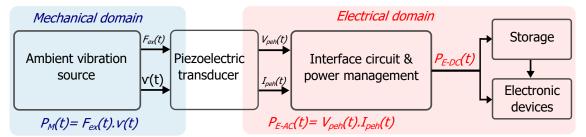

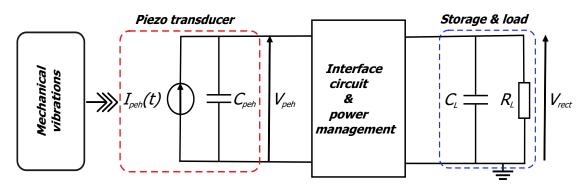

| 2.1.       | Piezoelectric harvesting system (PHS)                                  | 27 |

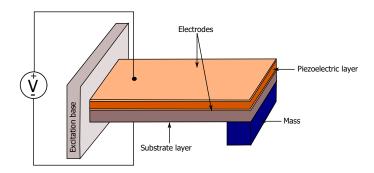

| 2.2.       | A cantilevered piezoelectric transducer structure                      | 28 |

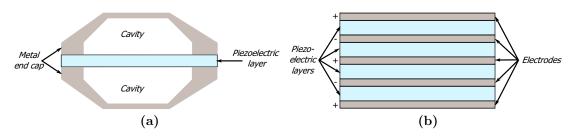

| 2.3.       | (a) Cymbal transducer structure, (b) Stacked transducer structure [5]. | 29 |

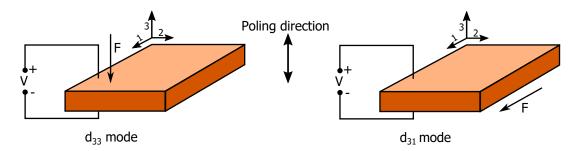

| 2.4.       | PT operation modes                                                     | 30 |

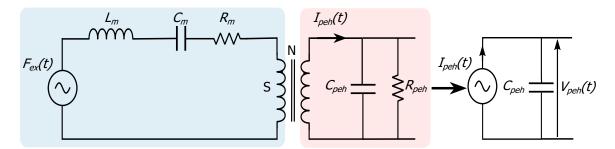

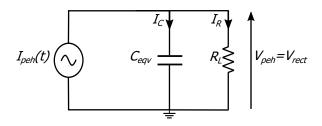

| 2.5.       | Equivalent circuit of piezoelectric transducer PT                      | 30 |

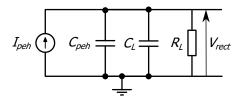

| 2.6.       | Equivalent circuit of piezoelectric harvesting system (PHS)            | 31 |

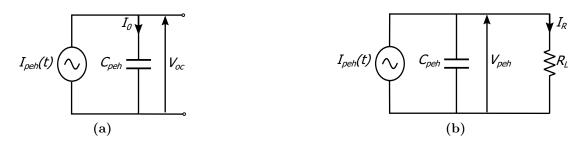

| 2.7.       | (a) PT in an open circuit configuration, (b) PT with a load resistor   | 32 |

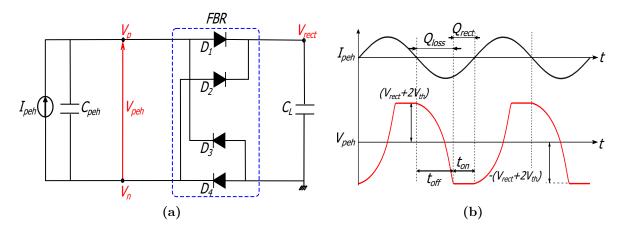

| 2.8.       | (a) Full bridge rectifier (FBR) typology, (b) Associated waveforms.    | 34 |

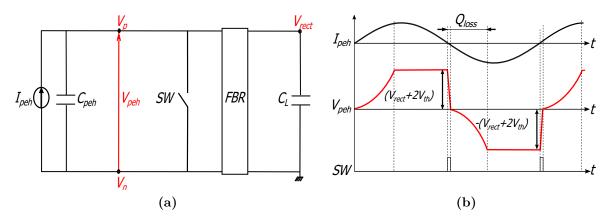

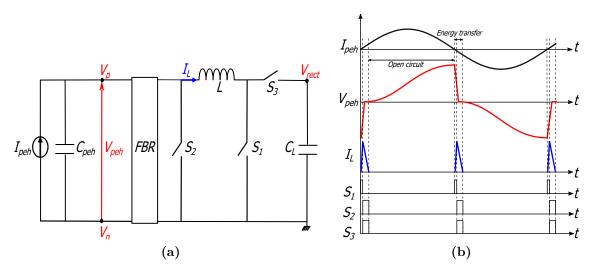

| 2.9.       | (a) Switch-Only interface circuit, (b) Associated waveforms            | 36 |

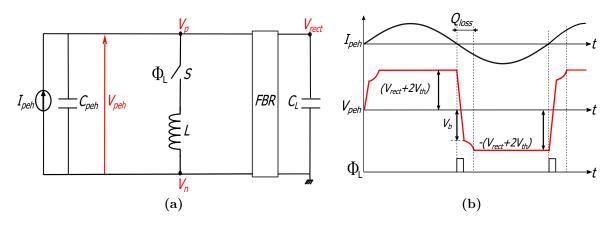

|            | (a) SECE interface circuit, (b) Associated waveforms.                  | 38 |

| 2.11.      | (a) P-SSHI interface circuit, (b) Current, voltage and control signal  |    |

|            | waveforms.                                                             | 40 |

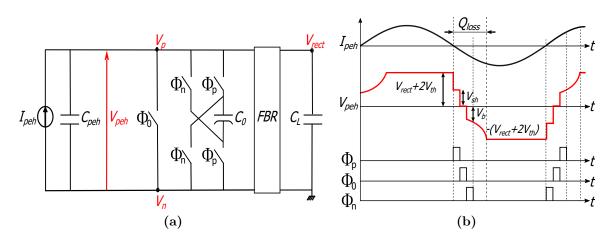

| 2.12.      | (a) One-capacitor SSHC interface circuit, (b) Current, voltage and     | 10 |

|            | control signals waveforms.                                             | 42 |

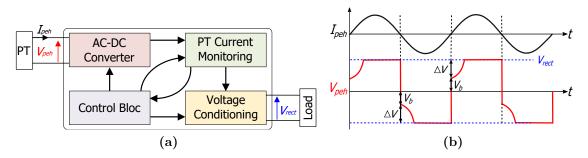

| 3.1.       | (a) Typical active interface architecture, (b) Example of associated   |    |

|            | signals.                                                               | 48 |

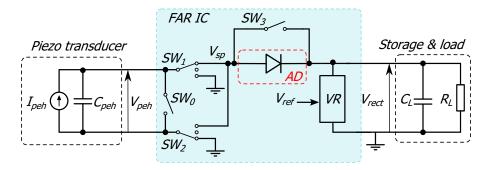

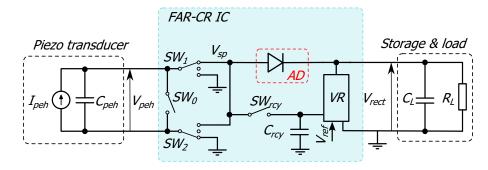

| 3.2.       | Basic full active rectifier (FAR) interface circuit.                   | 50 |

|            |                                                                        |    |

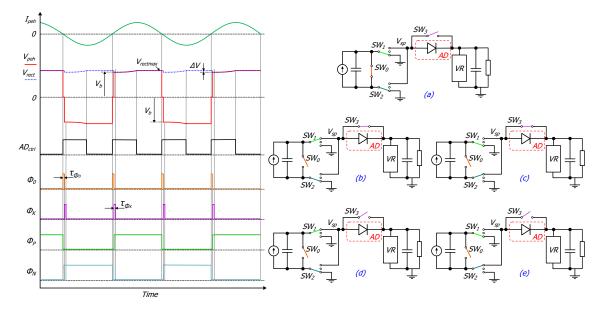

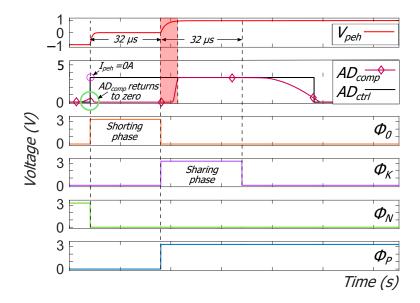

| 3.3.  | (left) FAR waveforms and control signals, (right) circuit configura-                                                                |    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|----|

|       | tions : (a) shorting phase, (b) sharing phase with $I_{peh} > 0$ , (c) sharing                                                      |    |

|       | phase with $I_{peh} < 0$ , (d) power extraction phase with $I_{peh} > 0$ , (e)                                                      | 50 |

|       | power extraction phase with $I_{peh} < 0. \ldots \ldots \ldots \ldots \ldots$                                                       | 50 |

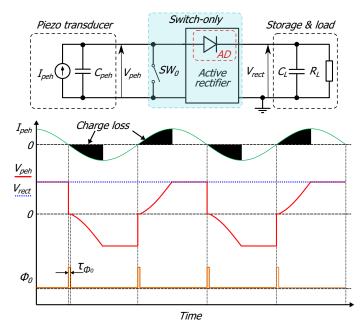

| 3.4.  | Switch-Only interface circuit and associated waveforms and switch                                                                   |    |

|       | control signal.                                                                                                                     | 52 |

| 3.5.  | Electrical model of PHS during power extraction phase                                                                               | 53 |

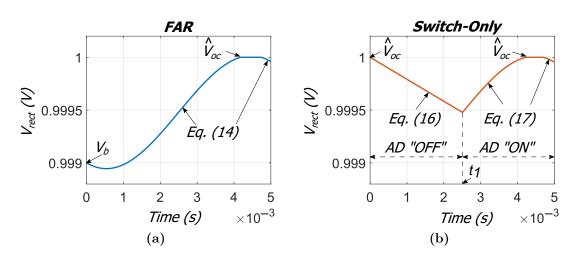

| 3.6.  | Simulated evolution of $V_{rect}(t)$ on half a period if $I_{peh}$ , (a) FAR, (b)                                                   |    |

|       | Switch-Only. The parameters are: $C_{peh} = 100nF$ , $C_L = 100\mu F$ ,                                                             |    |

|       | $R_L = 48k\Omega, f_{ex} = 100Hz, I_{peh} = 62.8\mu A.$                                                                             | 54 |

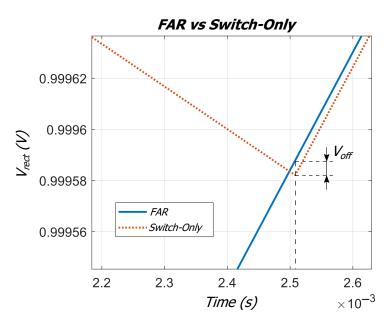

| 3.7.  | Detail plot around $t = t_1$ of Figure 3.6 (a) and Figure 3.6 (b) super-                                                            |    |

|       | imposed                                                                                                                             | 55 |

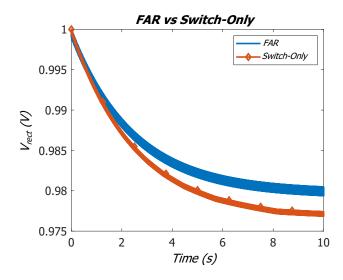

| 3.8.  | Simulated evolution of $V_{rect}$ in FAR and switch-only when $R_L = 48k\Omega$ ,                                                   |    |

|       | with $1V$ initial condition. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                  | 56 |

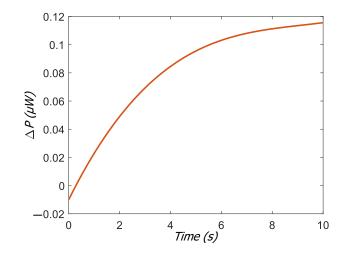

| 3.9.  | Simulated evolution of average power difference $\Delta P$ between FAR                                                              |    |

|       | and Switch-Only for $R_L = 48k\Omega$ .                                                                                             | 56 |

| 3.10. | FAR-CR interface circuit.                                                                                                           | 58 |

| 3.11. | (left) FAR-CR waveforms and control signals, (right) circuit config-                                                                |    |

|       | urations: (a) shorting phase, (b) recycling phase with $I_{peh} > 0$ , (c)                                                          |    |

|       | sharing phase with $I_{peh} < 0$ , (d) energy harvesting with $I_{peh} > 0$ , (e)                                                   |    |

|       | energy harvesting with $I_{peh} < 0.$                                                                                               | 58 |

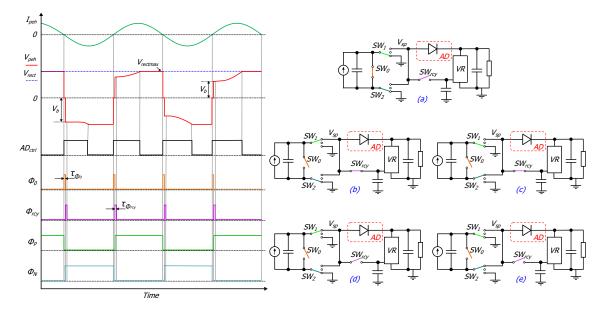

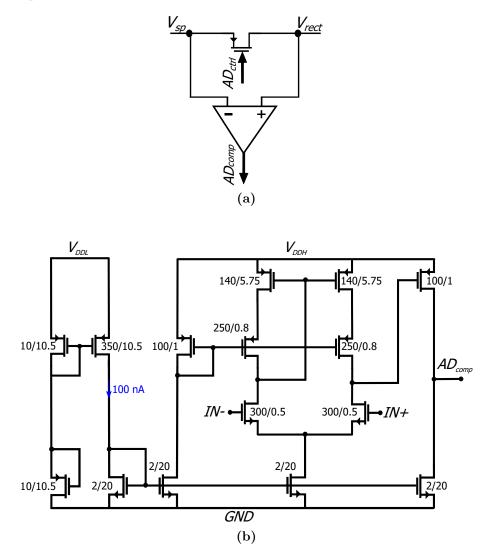

| 3.12. | FAR system architecture combining the basic FAR and the FAR-CR                                                                      |    |

|       | circuits                                                                                                                            | 60 |

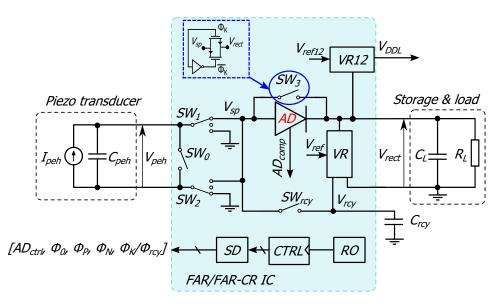

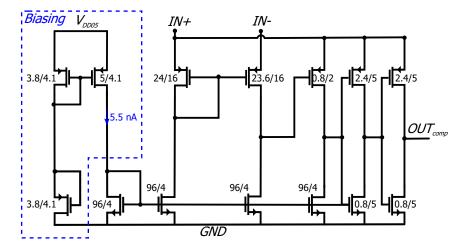

| 3.13. | (a) Active diode diagram block (AD), (b) AD comparator architecture                                                                 |    |

|       | [6]                                                                                                                                 | 61 |

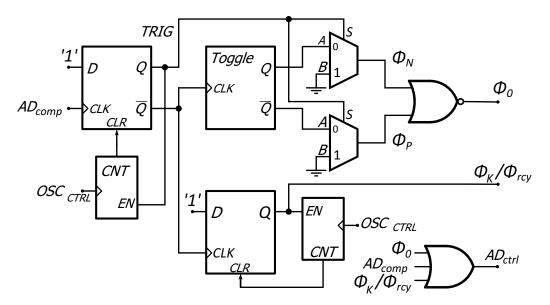

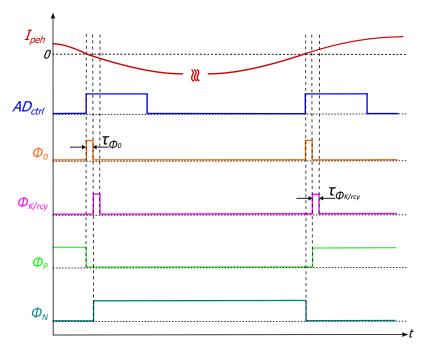

| 3.14. | Control block (CRTL) architecture.                                                                                                  | 62 |

| 3.15. | Timing diagram of the control signals sequence generated by CRTL                                                                    |    |

|       | for FAR and FAR-CR typologies                                                                                                       | 63 |

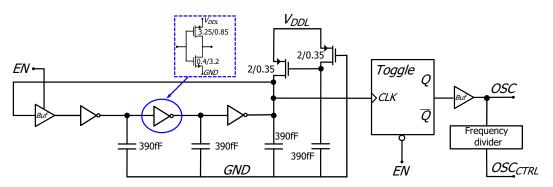

| 3.16. | Ring oscillator (RO) circuit architecture.                                                                                          | 64 |

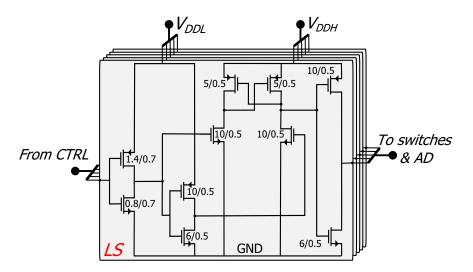

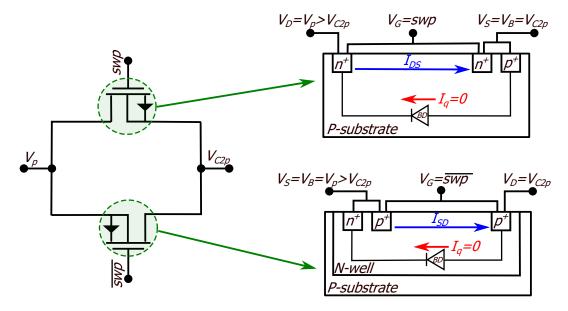

|       | Switch drivers block (SD) consisting of five level-up shifters (LS) [7].                                                            | 65 |

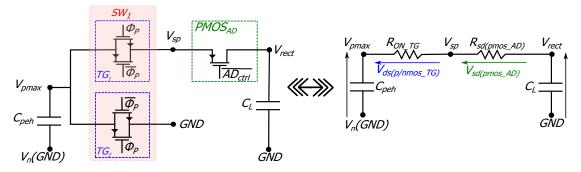

|       | (left) $SW_1$ configuration: $TG_1$ (ON) and $TG_2$ (OFF), and (right)                                                              |    |

| 0.10. | corresponding equivalent circuit when $I_{peh}$ is positive                                                                         | 65 |

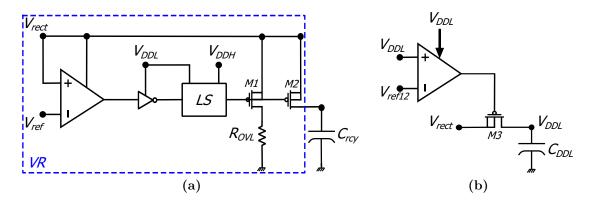

| 3 19  | (a) Circuit diagram of the voltage regulator VR, (b) Circuit diagram                                                                | 00 |

| 0.10. | of the voltage regulator VR12                                                                                                       | 67 |

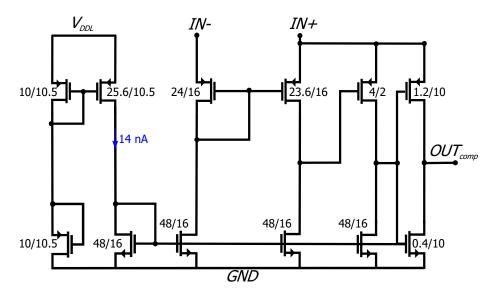

| 3.20. | Common-gate comparator circuit [8]                                                                                                  |    |

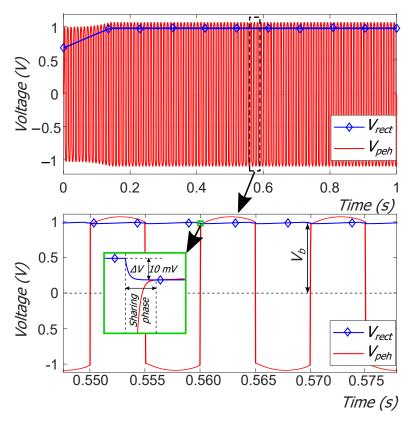

|       | Simulated $V_{peh}$ and $V_{rect}$ when using $C_L = 10 \mu F$ , pre-charged to 0.7V                                                | 00 |

| 0.21. | in FAR circuit. $\dots \dots \dots$ | 69 |

| 3.22. | Simulated $V_{peh}$ , $AD_{ctrl}$ , $AD_{comp}$ and voltage flip sequence of FAR with                                               |    |

|       | $C_L = 10 \mu F$ . As can be noticed, $AD_{comp}$ returns to low shortly after                                                      |    |

|       | the zero-crossing of $I_{peh}$ .                                                                                                    | 69 |

| 3.23. | Simulated $V_{peh}$ , $V_{rect}$ and $V_{rcy}$ when using $C_{cry} = 1\mu F$ , pre-charged                                          |    |

|       | to $0.98V$ in FAR-CR circuit.                                                                                                       | 70 |

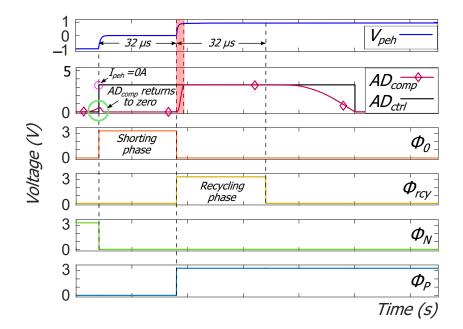

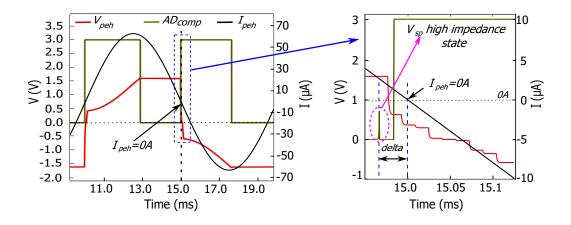

| after the zero-crossing of $I_{peh}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.24. Simulated $V_{peh}$ , $AD_{ctrl}$ , $AD_{comp}$ and voltage flip sequence of FAR-CR with $C_{rcy} = 1\mu F$ . It can be noticed, $AD_{comp}$ returns to low shortly |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

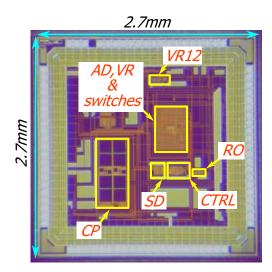

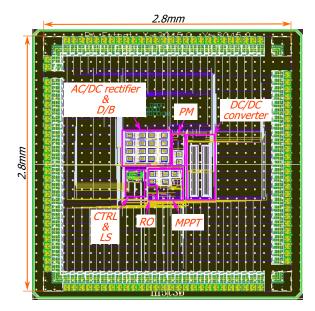

| 3.25. Micrograph of the ASIC chip fabricated in the AMS $0.35\mu m$ HV CMOS foundry process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                           |

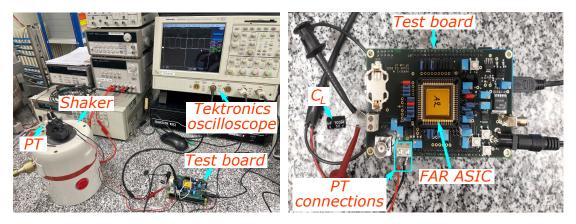

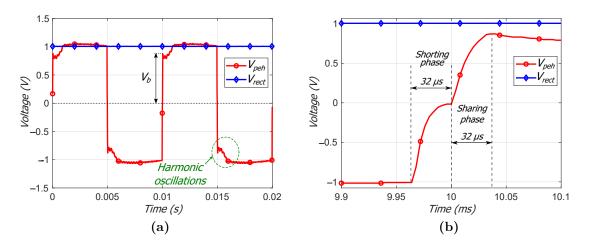

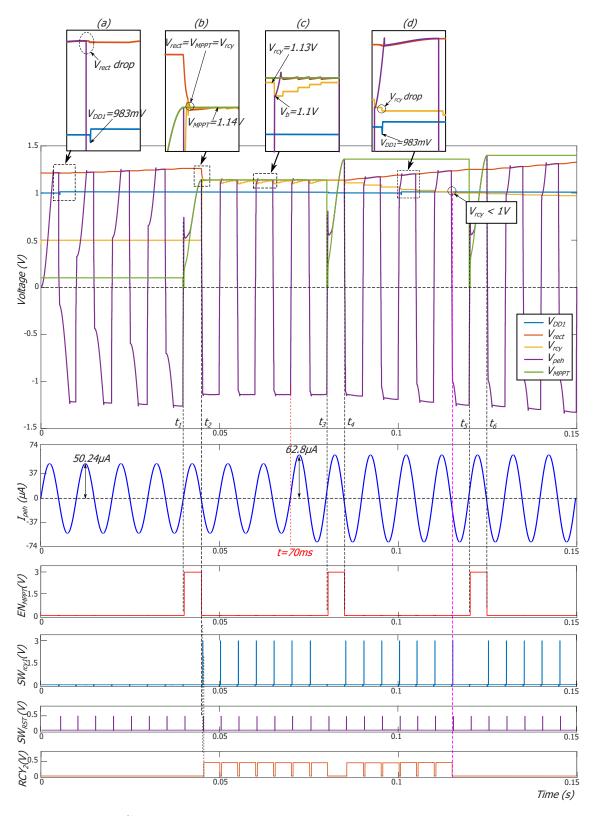

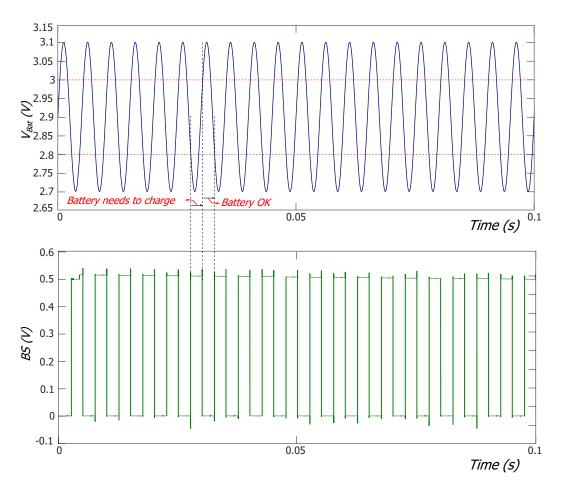

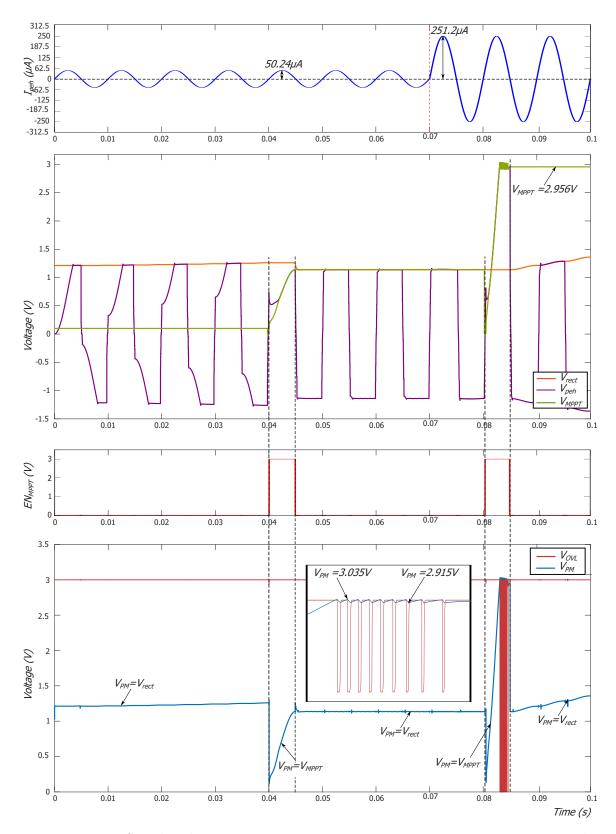

| 3.26. Experimental setup (left), and test board (right).       72         3.27. (a) Measured waveform of $V_{peh}$ and $V_{rect}$ , (b) Zoom view during the voltage flip operation, VR regulates $V_{rect}$ to $\hat{V}_{oc} = 1V$ .       73         3.28. Output power as a function of $1/R_L$ (a), $V_{rect}$ (b).       74         3.29. Measured transient signal of $V_{peh}$ for Switch-Only operation mode (top) and $V_{peh}$ (middle), $V_{rcy}$ (bottom) of FAR-CR operation mode with $C_{rcy} = 1\mu F$ .       75         3.30. Measured transient signal of $V_{rect}$ (top) when switching $R_L$ from 330kΩ to 10kΩ for FBR, Switch-Only operation mode and FAR-CR, and corresponding evolution of $V_{rcy}$ of the FAR-CR (bottom).       76         4.1. (a) One-capacitor SSHC interface circuit, (b) Current, voltage and control signals waveforms.       80         4.2. FAR-FC circuit architecture.       82         4.3. (left) 9-phase flipping capacitors configuration for PC and NC cycles, and (right) evolution of $V_{peh}$ during its flipping phases when the flipping capacitors are fully charged.       82         4.4. Voltage flip efficiency $\eta_F$ as a function of $\frac{C_L}{C_{peh}}$ .       88         4.5. FAR-FC system architecture.       86         4.6. Control block circuit (CTRL).       88         4.7. Equivalent circuit during the second damping phase (Φ_{-2}) with the voltage evolution across both $C_{peh}$ and $C_2$ .       89         4.8. (a) D/B control sequence generator, (b) Charge recycling control circuit.       91         4.10. Timing diagram of | 3.25. Micrograph of the ASIC chip fabricated in the AMS $0.35 \mu m$ HV                                                                                                   |

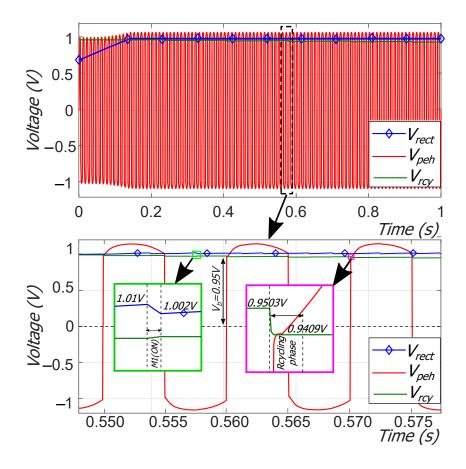

| <ul> <li>3.27. (a) Measured waveform of V<sub>peh</sub> and V<sub>rect</sub>, (b) Zoom view during the voltage flip operation, VR regulates V<sub>rect</sub> to V̂<sub>oc</sub> = 1V</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                           |

| voltage flip operation, VR regulates $V_{rect}$ to $\hat{V}_{oc} = 1V.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                           |

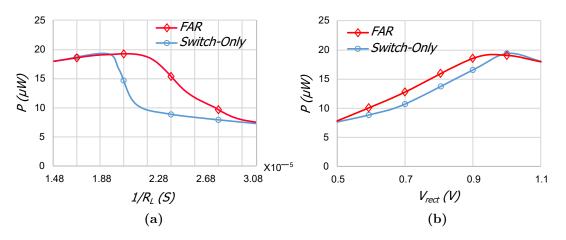

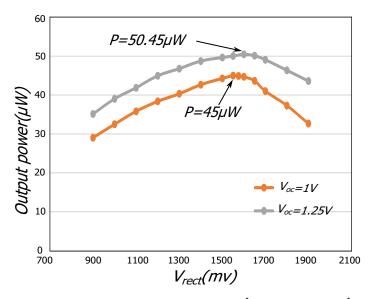

| 3.28. Output power as a function of $1/R_L$ (a), $V_{rect}$ (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>^</b>                                                                                                                                                                  |

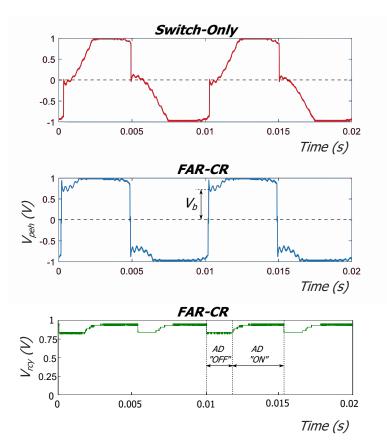

| 3.29. Measured transient signal of $V_{peh}$ for Switch-Only operation mode<br>(top) and $V_{peh}$ (middle), $V_{rcy}$ (bottom) of FAR-CR operation mode<br>with $C_{rcy} = 1\mu F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                           |

| (top) and $V_{peh}$ (middle), $V_{rcy}$ (bottom) of FAR-CR operation mode<br>with $C_{rcy} = 1\mu F$ .753.30. Measured transient signal of $V_{rect}$ (top) when switching $R_L$ from<br>330kΩ to 10kΩ for FBR, Switch-Only operation mode and FAR-CR,<br>and corresponding evolution of $V_{rcy}$ of the FAR-CR (bottom).764.1. (a) One-capacitor SSHC interface circuit, (b) Current, voltage and<br>control signals waveforms.804.2. FAR-FC circuit architecture.824.3. (left) 9-phase flipping capacitors configuration for PC and NC cy-<br>cles, and (right) evolution of $V_{peh}$ during its flipping phases when the<br>flipping capacitors are fully charged.824.4. Voltage flip efficiency $\eta_F$ as a function of $\frac{C_1}{C_{peh}}$ .844.5. FAR-FC system architecture.844.6. Control block circuit (CTRL).884.7. Equivalent circuit during the second damping phase (Φ2) with the<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                           |

| with $C_{rcy} = 1\mu F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                         |

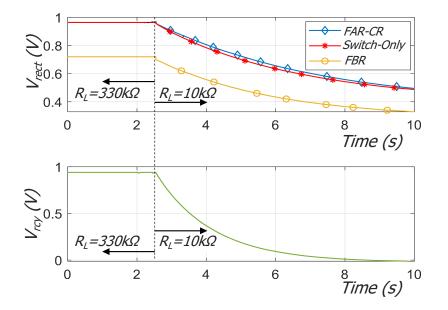

| 3.30. Measured transient signal of $V_{rect}$ (top) when switching $R_L$ from<br>330 $k\Omega$ to 10 $k\Omega$ for FBR, Switch-Only operation mode and FAR-CR,<br>and corresponding evolution of $V_{rcy}$ of the FAR-CR (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |

| 330kΩ to 10kΩ for FBR, Switch-Only operation mode and FAR-CR,<br>and corresponding evolution of $V_{rcy}$ of the FAR-CR (bottom).764.1. (a) One-capacitor SSHC interface circuit, (b) Current, voltage and<br>control signals waveforms.804.2. FAR-FC circuit architecture.824.3. (left) 9-phase flipping capacitors configuration for PC and NC cycles, and (right) evolution of $V_{peh}$ during its flipping phases when the<br>flipping capacitors are fully charged.824.4. Voltage flip efficiency $\eta_F$ as a function of $\frac{C_1}{C_{peh}}$ .844.5. FAR-FC system architecture.864.6. Control block circuit (CTRL).884.7. Equivalent circuit during the second damping phase (Φ2) with the<br>voltage evolution across both $C_{peh}$ and $C_2$ .894.8. (a) D/B control sequence generator, (b) Charge recycling control circuit.924.10. Timing diagram of generated control signal sequence.924.11. Charge pump (CP) circuit architecture [9].934.12. Sacp-SSHC simulated circuit ( $C_{peh} = 100nF$ , $\hat{I}_{peh} = 62.8\mu A$ , $f_{ex} =$<br>$100Hz$ , $C_L = 100\mu F$ , $R_L = 1T$ ).944.13. Simulated $V_{peh}$ and $V_{rect}$ without $V_{rect}$ regulation (a) and with $V_{rect}$<br>regulation (b).954.14. Simulated $V_{peh}$ , $V_{rect}$ and $V_{rcy}$ when using a $C_{rcy}$ of $2\mu F$ pre-charged<br>                                                                                                                                                                                                                                                                                                | , cg                                                                                                                                                                      |

| and corresponding evolution of $V_{rcy}$ of the FAR-CR (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                           |

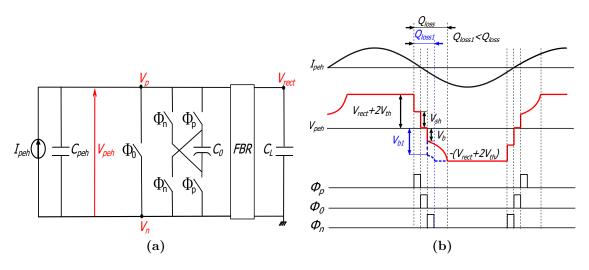

| 4.1. (a) One-capacitor SSHC interface circuit, (b) Current, voltage and control signals waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |

| $\begin{array}{c} \mbox{control signals waveforms.} & \dots & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | and corresponding evolution of $V_{rcy}$ of the FAR-CR (bottom) 76                                                                                                        |

| $\begin{array}{c} \mbox{control signals waveforms.} & \dots & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.1. (a) One-capacitor SSHC interface circuit. (b) Current, voltage and                                                                                                   |

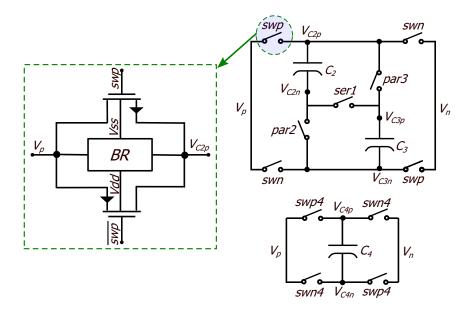

| 4.2. FAR-FC circuit architecture.824.3. (left) 9-phase flipping capacitors configuration for PC and NC cycles, and (right) evolution of $V_{peh}$ during its flipping phases when the flipping capacitors are fully charged.824.4. Voltage flip efficiency $\eta_F$ as a function of $\frac{C_1}{C_{peh}}$ .824.4. Voltage flip efficiency $\eta_F$ as a function of $\frac{C_1}{C_{peh}}$ .844.5. FAR-FC system architecture.864.6. Control block circuit (CTRL).884.7. Equivalent circuit during the second damping phase ( $\Phi_{-2}$ ) with the voltage evolution across both $C_{peh}$ and $C_2$ .894.8. (a) D/B control sequence generator, (b) Charge recycling control circuit.914.9. Rectification control circuit.924.10. Timing diagram of generated control signal sequence.924.11. Charge pump (CP) circuit architecture [9].934.12. Scap-SSHC simulated circuit ( $C_{peh} = 100nF$ , $\hat{I}_{peh} = 62.8\mu A$ , $f_{ex} = 100Hz$ , $C_L = 100\mu F$ , $R_L = 1T$ ).944.13. Simulated $V_{peh}$ and $V_{rect}$ without $V_{rect}$ regulation (a) and with $V_{rect}$ regulation (b).954.14. Simulated $V_{peh}$ , $V_{rect}$ and $V_{rcy}$ when using a $C_{rcy}$ of $2\mu F$ pre-charged with $V_{rcy} = 1.2V$ in FAR-FC circuit.964.15. Simulated $I_{peh}$ , $V_{peh}$ and the AD output voltage $AD_{comp}$ in FAR-FC97                                                                                                                                                                                                                                                                                          |                                                                                                                                                                           |

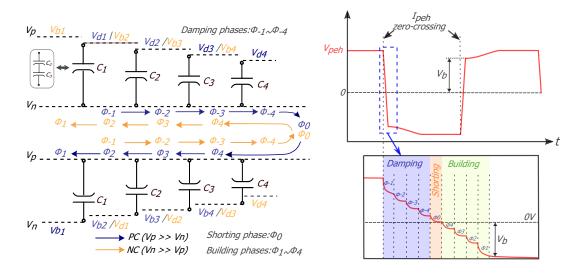

| 4.3. (left) 9-phase flipping capacitors configuration for PC and NC cycles, and (right) evolution of $V_{peh}$ during its flipping phases when the flipping capacitors are fully charged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                         |

| cles, and (right) evolution of $V_{peh}$ during its flipping phases when the<br>flipping capacitors are fully charged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                           |

| flipping capacitors are fully charged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                           |

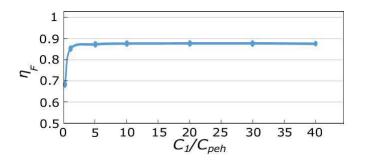

| 4.4. Voltage flip efficiency $\eta_F$ as a function of $\frac{C_1}{C_{peh}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                           |

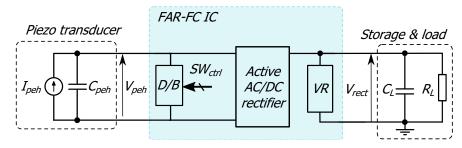

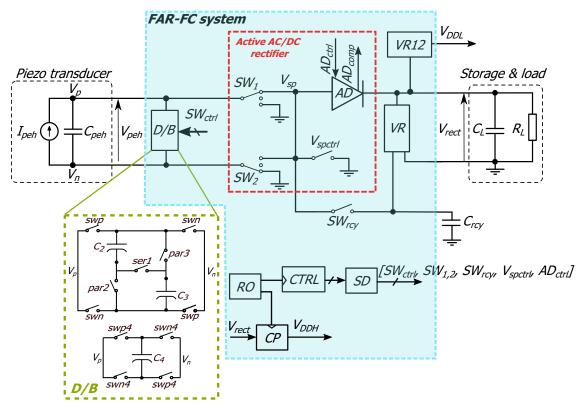

| 4.5. FAR-FC system architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                           |

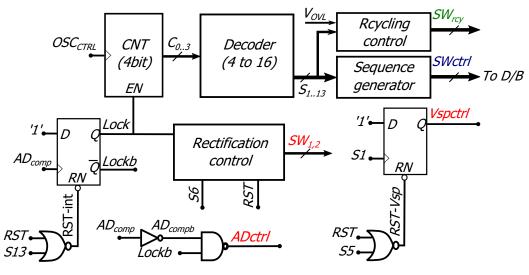

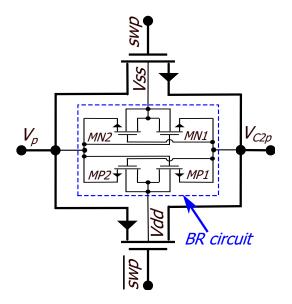

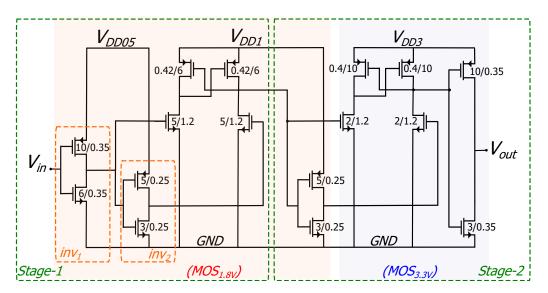

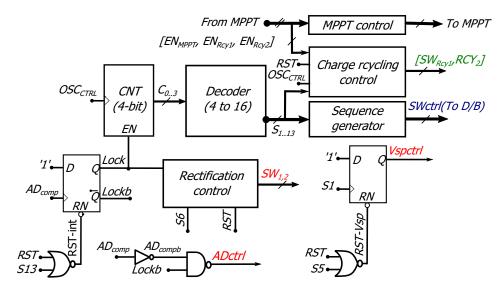

| 4.6. Control block circuit (CTRL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |

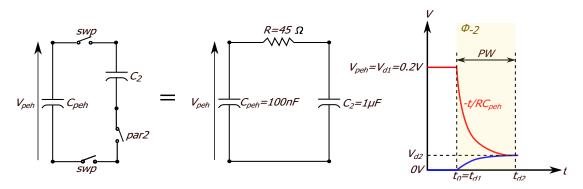

| <ul> <li>4.7. Equivalent circuit during the second damping phase (Φ<sub>-2</sub>) with the voltage evolution across both C<sub>peh</sub> and C<sub>2</sub></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                           |

| voltage evolution across both $C_{peh}$ and $C_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |

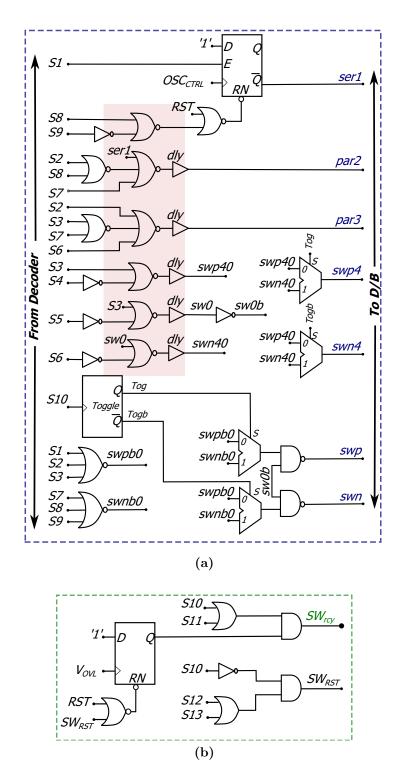

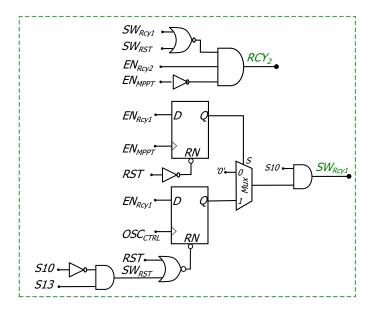

| 4.8. (a) D/B control sequence generator, (b) Charge recycling control circuit. 91<br>4.9. Rectification control circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                           |

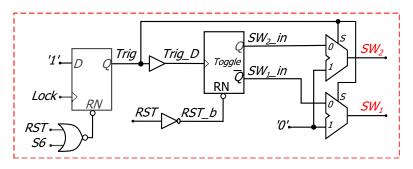

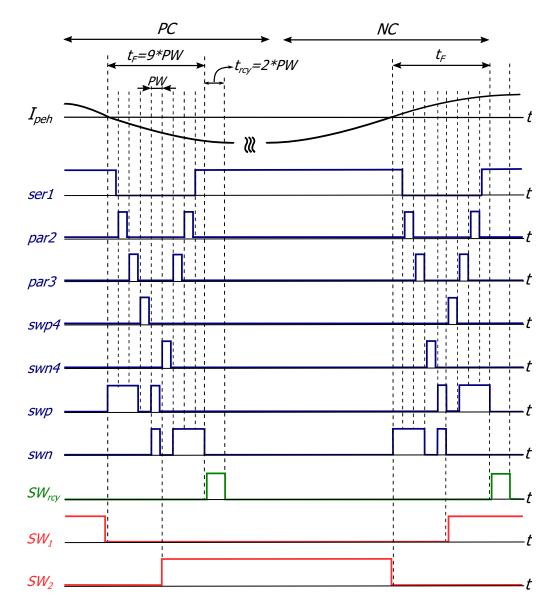

| 4.9. Rectification control circuit.924.10. Timing diagram of generated control signal sequence.924.11. Charge pump (CP) circuit architecture [9].934.12. 3cap-SSHC simulated circuit $(C_{peh} = 100nF, \hat{I}_{peh} = 62.8\mu A, f_{ex} = 100Hz, C_L = 100\mu F, R_L = 1T).$ 944.13. Simulated $V_{peh}$ and $V_{rect}$ without $V_{rect}$ regulation (a) and with $V_{rect}$ regulation (b).954.14. Simulated $V_{peh}, V_{rect}$ and $V_{rcy}$ when using a $C_{rcy}$ of $2\mu F$ pre-charged with $V_{rcy} = 1.2V$ in FAR-FC circuit.964.15. Simulated $I_{peh}, V_{peh}$ and the AD output voltage $AD_{comp}$ in FAR-FC circuit.97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                         |

| 4.10. Timing diagram of generated control signal sequence.924.11. Charge pump (CP) circuit architecture [9].934.12. 3cap-SSHC simulated circuit $(C_{peh} = 100nF, \hat{I}_{peh} = 62.8\mu A, f_{ex} = 100Hz, C_L = 100\mu F, R_L = 1T).$ 944.13. Simulated $V_{peh}$ and $V_{rect}$ without $V_{rect}$ regulation (a) and with $V_{rect}$ 954.14. Simulated $V_{peh}, V_{rect}$ and $V_{rcy}$ when using a $C_{rcy}$ of $2\mu F$ pre-charged964.15. Simulated $I_{peh}, V_{peh}$ and the AD output voltage $AD_{comp}$ in FAR-FC97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                           |

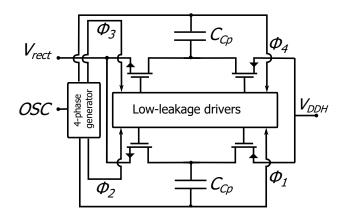

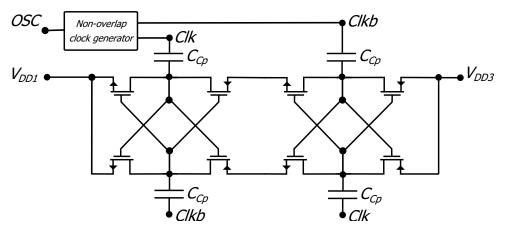

| 4.11. Charge pump (CP) circuit architecture [9].934.12. 3cap-SSHC simulated circuit $(C_{peh} = 100nF, \hat{I}_{peh} = 62.8\mu A, f_{ex} = 100Hz, C_L = 100\mu F, R_L = 1T).944.13. Simulated V_{peh} and V_{rect} without V_{rect} regulation (a) and with V_{rect} regulation (b).954.14. Simulated V_{peh}, V_{rect} and V_{rcy} when using a C_{rcy} of 2\mu F pre-charged with V_{rcy} = 1.2V in FAR-FC circuit.964.15. Simulated I_{peh}, V_{peh} and the AD output voltage AD_{comp} in FAR-FC circuit.97$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |

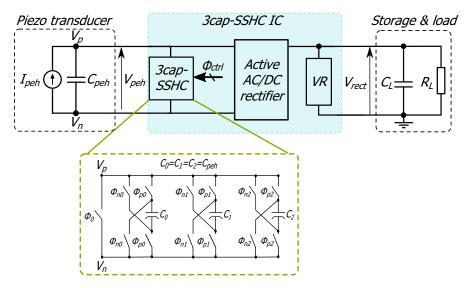

| 4.12. 3cap-SSHC simulated circuit $(C_{peh} = 100nF, \hat{I}_{peh} = 62.8\mu A, f_{ex} = 100Hz, C_L = 100\mu F, R_L = 1T).$ 94<br>4.13. Simulated $V_{peh}$ and $V_{rect}$ without $V_{rect}$ regulation (a) and with $V_{rect}$ regulation (b). 95<br>4.14. Simulated $V_{peh}, V_{rect}$ and $V_{rcy}$ when using a $C_{rcy}$ of $2\mu F$ pre-charged with $V_{rcy} = 1.2V$ in FAR-FC circuit. 96<br>4.15. Simulated $I_{peh}, V_{peh}$ and the AD output voltage $AD_{comp}$ in FAR-FC circuit. 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                           |

| $100Hz, C_L = 100\mu F, R_L = 1T). \qquad 94$ 4.13. Simulated $V_{peh}$ and $V_{rect}$ without $V_{rect}$ regulation (a) and with $V_{rect}$<br>regulation (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.12 3cap-SSHC simulated circuit ( $C_{ret} = 100nF$ $\hat{L}_{ret} = 62.8\mu A$ $f_{er} =$                                                                               |

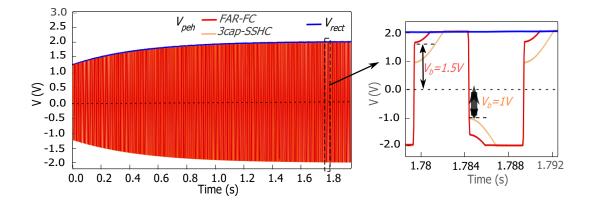

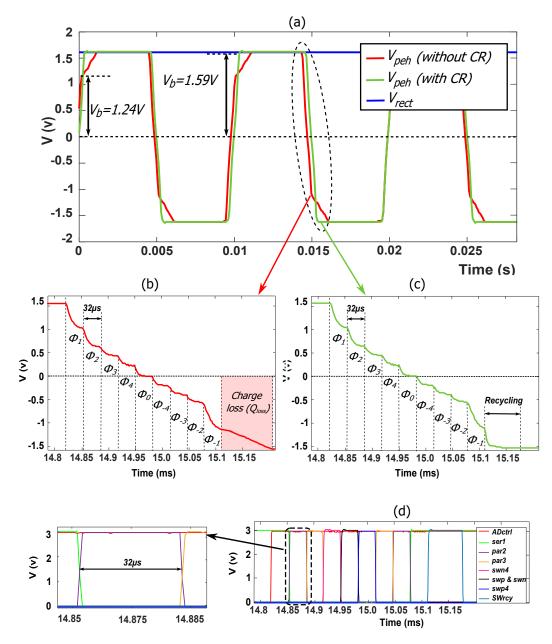

| 4.13. Simulated $V_{peh}$ and $V_{rect}$ without $V_{rect}$ regulation (a) and with $V_{rect}$<br>regulation (b).954.14. Simulated $V_{peh}$ , $V_{rect}$ and $V_{rcy}$ when using a $C_{rcy}$ of $2\mu F$ pre-charged<br>with $V_{rcy} = 1.2V$ in FAR-FC circuit.964.15. Simulated $I_{peh}$ , $V_{peh}$ and the AD output voltage $AD_{comp}$ in FAR-FC<br>circuit.97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                           |

| regulation (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                           |

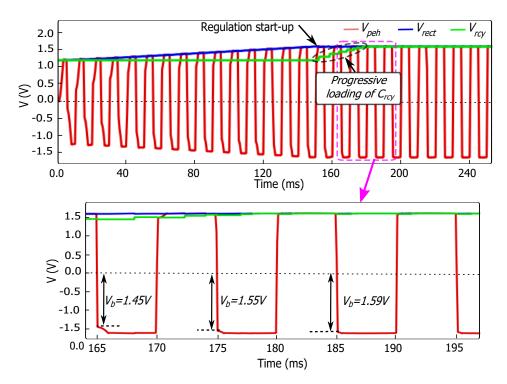

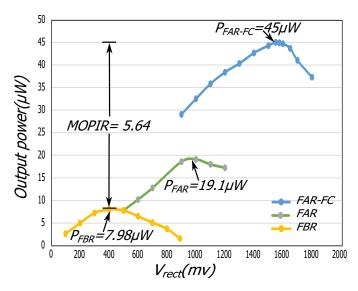

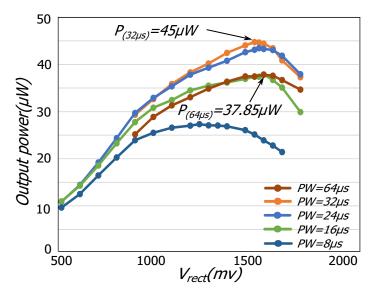

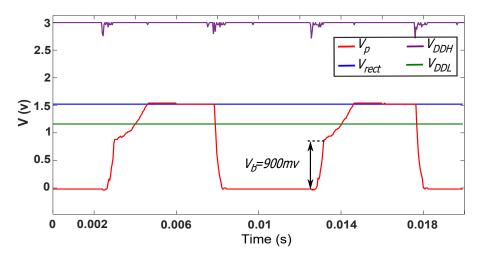

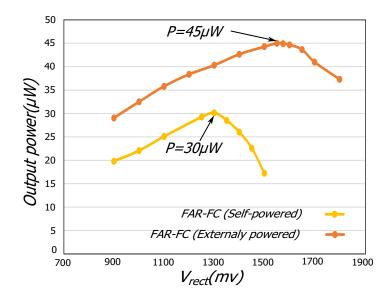

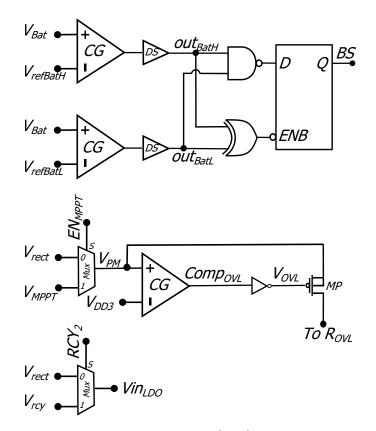

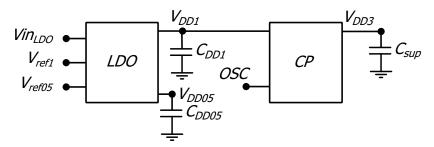

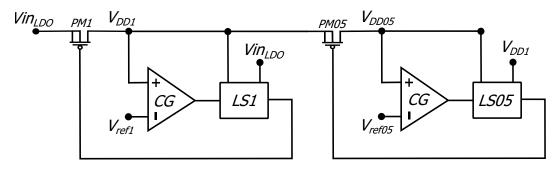

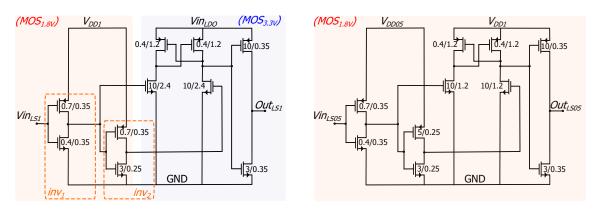

| 4.14. Simulated $V_{peh}$ , $V_{rect}$ and $V_{rcy}$ when using a $C_{rcy}$ of $2\mu F$ pre-charged<br>with $V_{rcy} = 1.2V$ in FAR-FC circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                           |