# Supervised learning in binary dynamical physical systems through energy minimization

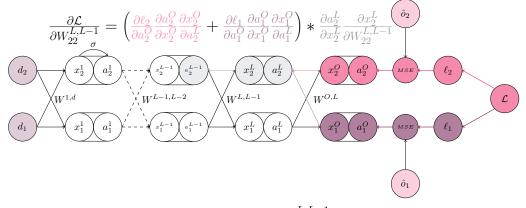

Jérémie Laydevant

#### ► To cite this version:

Jérémie Laydevant. Supervised learning in binary dynamical physical systems through energy minimization. Artificial Intelligence [cs.AI]. Université Paris-Saclay, 2022. English. NNT: 2022UP-ASP112. tel-03956750

### HAL Id: tel-03956750 https://theses.hal.science/tel-03956750

Submitted on 25 Jan 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Supervised learning in binary dynamical physical systems through energy minimization

Apprentissage supervisé dans les systèmes physiques dynamiques binaires grâce à la minimisation de l'énergie

#### Thèse de doctorat de l'université Paris-Saclay

École doctorale n°564 : physique en Île-de-France (PIF) Spécialité de doctorat: Physique Graduate School : Physique, Référent : Faculté des sciences d'Orsay

Thèse préparée dans l'unité de recherche UMPhy (Université Paris-Saclay, CNRS, Thales), sous la direction de Julie GROLLIER, Directrice de recherche

Thèse soutenue à Paris-Saclay, le 20 octobre 2022, par

## Jérémie LAYDEVANT

#### **Composition du jury**

Jean-Michel PORTAL Professeur des Universités, IM2NP, Aix-Marseille Université Daniel BRUNNER Chargé de recherche, HDR, Institut FEMTO-ST Louis HUTIN Expert senior, CEA Leti Julie GROLLIER Directrice de recherche, UMPhy Université Paris-Saclay, CNRS, Thales Président

Rapporteur & Examinateur Rapporteur & Examinateur Directrice de thèse

NNT: 2022UPASP112

**Titre:** Apprentissage supervisé dans les systèmes physiques dynamiques binaires grâce à la minimisation de l'énergie **Mots clés:** Apprentissage profond, Calcul neuromorphique, Réseaux de neurones binaires, Machine d'Ising

**Résumé:** L'apprentissage profond permet d'atteindre des performances jusqu'alors inaccessibles, que ce soit pour de la classification d'images, de la compréhension de parole ou de la génération de texte. Ces performances ont été permises par l'utilisation conjointe de réseaux de neurones profonds et d'un algorithme d'optimisation qui calcule le gradient d'une fonction de coût globale calculée à la sortie du réseau (rétropropagation du gradient) qui permet de faire émerger une hierarchie de détection des caractéristiques de la donnée d'entrée. Cependant, l'entrainement des réseaux de neurones, dont le nombre de paramètres augmente de façon dramatique, avec du matériel digital standard basé sur l'architecture Von Neumann est extrêmement inefficace d'un point de vue de la consommation énergétique puisque l'on doit continuellement transférer les valeurs des paramètres de la mémoire au processeur. Le calcul neuromorphique se pose en alternative basse consommation et rapide à ce matériel standard en proposant de rapprocher physiquement mémoire et éléments de calcul. Cependant, les implémentations matérielles manquent encore aujourd'hui d'algorithmes qui leur permettent d'atteindre les performances offertes par une optimisation basée sur le calcul du gradient d'une fonction de coût globale tout en évitant le surcoût énergétique dû aux circuits complexes qui réalisent la rétropropagation du gradient. Equilibrium Propagation (EP) est un algorithme d'apprentissage alternatif à la rétropropagation du gradient qui calcule le gradient d'une fonction de coût globale. EP permet de réaliser les deux phases d'apprentissage : la phase d'inférence et la phase de rétro-propagation des erreurs grâce à la propriété des systèmes physiques qui évoluent vers leur état le plus probable qui est aussi celui d'énergie minimale. La règle d'apprentissage prescrite

par EP est locale et fait d'EP un bon candidat pour entrainer des implémentations matérielles neuromorphiques sans gros surcoût énergétique. En pratique, aucune implémentation matérielles grande échelle entraînée par EP n'a encore été démontrée. En effet, les dispositifs émergents envisagés pour les implémentations sont encore expérimentaux et souffrent donc d'une forte variabilité qui empêche l'entrainement sur puce. Dans cette thèse nous démontrons que nous pouvons entrainer avec EP un réseau de neurones artificiels dont les poids synaptiques et la fonction d'activation des neurones sont binarisés. Ceci permet d'envisager d'utiliser les dispositifs émergents dans un régime binaire qui réduit de façon considérable leur variabilité et autorise un apprentissage sur puce. Ces résultats peuvent également permettre de concevoir une puce digitale standard dédiée pour l'entrainement de réseaux de neurones binaires sur des dispositifs portables. Nous démontrons ensuite que nous pouvons appliquer EP à un système physique dont la fonction d'énergie est hautement paramétrisable: une Machine d'Ising (MI). La MI de DWave, par le biais de l'algorithme de recuit quantique, minimise successivement l'énergie des deux phases d'EP. Nous avons réussi à entrainer une architecture entièrement connectée sur la MI. Nous tirons également parti de la connectivité de la puce pour réaliser des convolutions et montrons que l'on peut entrainer un réseau convolutionel sur la MI avec EP. Ces travaux ouvrent la voie à l'entrainement supervisé sur puce de systèmes physiques non-conventionnels en s'affranchissant et de la nature expérimentale de nano-dispositifs envisagés pour des implémentations basse-consommation et de l'implémentation physique réelle puisque EP est adapté à entrainer des architectures de réseaux de neurones qui s'adaptent au matériel ciblé.

**Title:** Supervised learning in binary dynamical physical systems through energy minimization **Keywords:** Deep learning, Neuromorphic computing, Binary neural networks, Ising Machine

**Abstract:** Deep learning makes it possible to achieve performances that were previously unattainable, whether for image classification, speech processing or text generation. These performances have been made possible by the joint use of deep neural networks and an optimization algorithm that calculates the gradient of a global cost function computed at the output of the network (backpropagation) which allows the emergence of a detection hierarchy of the input data characteristics. However, the training of neural networks, whose number of parameters is dramatically increasing, on standard digital hardware based on the Von Neumann architecture, is extremely inefficient from an electrical energy point of view since one must continuously transfer the values of the parameters from the memory to the processor. Neuromorphic computing is a low-power and fast alternative to this standard hardware by proposing to physically bring together memory and computing elements. However, hardware implementations still lack algorithms that allow them to reach the performances offered by an optimization based on the computation of the gradient of a global cost function that avoids the energy overhead caused by the complex circuits realizing backpropagation. Equilibrium Propagation (EP) is a learning algorithm that computes the gradient of a global cost function as an alternative to backpropagation. EP allows to realize the two learning phases: the inference phase and the backpropagation phase thanks to the property of physical systems that evolve towards their most probable state which is also the one of minimum energy.

The learning rule prescribed by EP is local and makes EP a good candidate to train neuromorphic hardware implementations without large energy overhead. In practice, no large-scale hardware implementation trained by EP has been demonstrated yet. Indeed, the emerging devices considered for implementation are still experimental and therefore suffer from a high variability that prevents on-chip training. In this thesis we demonstrate that we can train with EP an artificial neural network whose synaptic weights and neural activation functions are binarized. This allows us to consider the use of emergent devices in a binary regime that considerably reduces their variability, compatible with on-chip learning. These results may also allow the design of standard digital chips dedicated to the training of binary neural networks on edge terminals. We then show that we can apply EP to a physical system that is energy-based by nature: an Ising Machine (IM). The DWave IM, through the quantum annealing algorithm, successively minimizes the energy of the two EP phases. We successfully demonstrate a training of a fully-connected architecture on the IM. We also take advantage of the chip layout to perform convolutions and show that we can train a convolutional network on the IM with EP. This work paves the way to supervised on-chip training of non-conventional physical systems by freeing itself from both the experimental nature of nano devices considered for low-power implementations and from the actual physical implementation since EP is adapted to train neural network architectures that fit the targeted hardware.

# Contents

| Re | Remerciements |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |

|----|---------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|

| Ré | ésum          | e de la                                      | thèse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | v                           |  |  |

| тΙ | nesis         | summa                                        | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xi                          |  |  |

| 1  |               | ral net<br>Deep  <br>1.1.1<br>1.1.2<br>1.1.3 | nal digital hardware performing deep learning with over-parametrized<br>works is energy-greedy<br>learning is about learning a non-linear mapping between an input to an output<br>A computation is a mapping of an input to an output, similarly to deep learning<br>The non-linear mapping of deep learning is done by an artificial neural network<br>A neural network learns the mapping by observing a lot of labelled data<br>I networks are usually trained on standard digital hardware that are power- | 1<br>2<br>3<br>8            |  |  |

|    | 1.2           | ineffici                                     | ient and thus exhibit limitations with the current large models                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15<br>18                    |  |  |

|    | 1.0           | 1.3.1                                        | Better machine learning practices and open-source can reduce the energy and carbon footprint                                                                                                                                                                                                                                                                                                                                                                                                                    | 18                          |  |  |

|    |               | 1.3.2                                        | Lighter models and more local learning algorithms improve energy-efficiency<br>with less memory requirements                                                                                                                                                                                                                                                                                                                                                                                                    | 20                          |  |  |

|    |               | 1.3.3                                        | Specialized digital hardware improve energy efficiency with reduced data movement and massive parallelization                                                                                                                                                                                                                                                                                                                                                                                                   | 22                          |  |  |

|    | 1.4           |                                              | ary: sota accuracy with gradient-based global optimization + energy efficiency<br>ess data movement                                                                                                                                                                                                                                                                                                                                                                                                             | 25                          |  |  |

| 2  |               | hardwa                                       | tional physics is a promising low-power alternative to conventional dig-<br>are for deep learning<br>liging physics to perform unconventional computing                                                                                                                                                                                                                                                                                                                                                         | <b>27</b><br>28<br>29<br>34 |  |  |

|    | 2.2           |                                              | in ging the natural tendency of physical systems to evolve toward the ground<br>to parametrize the computation via the energy function                                                                                                                                                                                                                                                                                                                                                                          | 36<br>36<br>38              |  |  |

|    |               | 2.2.4                                        | energy function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39<br>42                    |  |  |

|    | 2.3           | 2.2.5<br>Summ                                | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45<br>47                    |  |  |

| 3 | Introduction to Ising Machines, Equilibrium Propagation and Binary Neural Net- |                                                                                      |            |  |  |  |  |  |

|---|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------|--|--|--|--|--|

|   | wor                                                                            |                                                                                      | 49         |  |  |  |  |  |

|   | 3.1                                                                            | Ising Machines: hardware minimizers of an energy function                            | 51         |  |  |  |  |  |

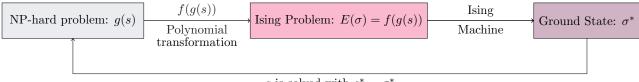

|   |                                                                                | 3.1.1 Solve an Ising Problem, solve them all                                         | 51         |  |  |  |  |  |

|   |                                                                                | 3.1.2 Panorama of existing Ising Machines                                            | 54         |  |  |  |  |  |

|   |                                                                                | 3.1.3 Existing Ising Machines                                                        | 57         |  |  |  |  |  |

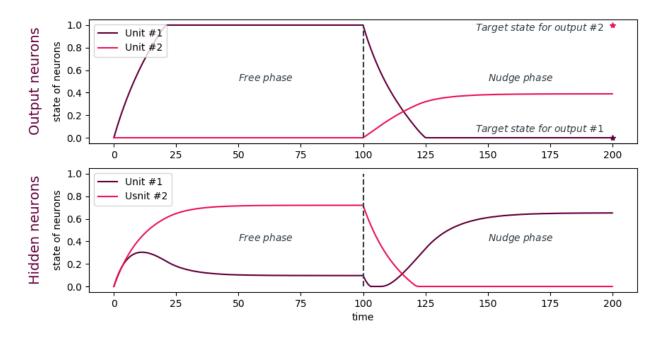

|   | 3.2                                                                            | Equilibrium Propagation: supervised learning with energy-based models                | 62         |  |  |  |  |  |

|   |                                                                                | 3.2.1 Physical intuition behind Equilibrium Propagation                              | 62         |  |  |  |  |  |

|   |                                                                                | 3.2.2 Machine Learning description of EP                                             | 67         |  |  |  |  |  |

|   |                                                                                | 3.2.3 Example: training a simple layered architecture                                | 72         |  |  |  |  |  |

|   |                                                                                | 3.2.4 EP has triggered great attention: benchmark                                    | 73         |  |  |  |  |  |

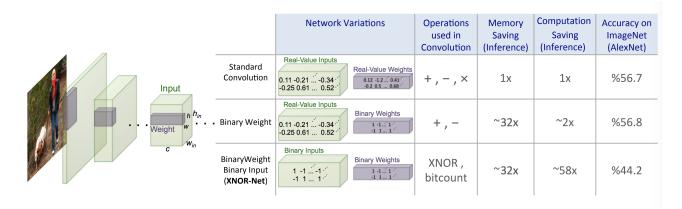

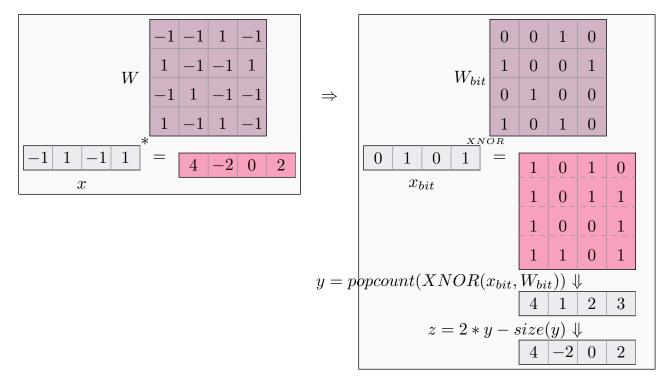

|   | 3.3                                                                            | Binary Neural Networks                                                               | 76         |  |  |  |  |  |

|   |                                                                                | 3.3.1 A historical introduction to Binary Neural Networks and definitions            | 76         |  |  |  |  |  |

|   |                                                                                | 3.3.2 Challenges with BNNs: saturation and optimization                              | 79         |  |  |  |  |  |

|   |                                                                                | 3.3.3 BNNs have triggered great attention for custom hardware                        | 83         |  |  |  |  |  |

|   | 3.4                                                                            | Summary                                                                              | 84         |  |  |  |  |  |

| 4 |                                                                                |                                                                                      |            |  |  |  |  |  |

| 4 |                                                                                | ining Dynamical Binary Neural Networks with Equilibrium Propagation                  | 87         |  |  |  |  |  |

|   | 4.1                                                                            |                                                                                      | 87         |  |  |  |  |  |

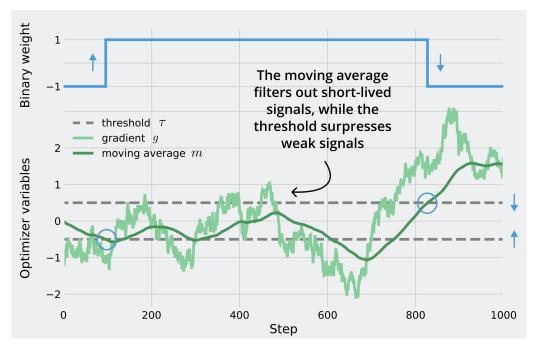

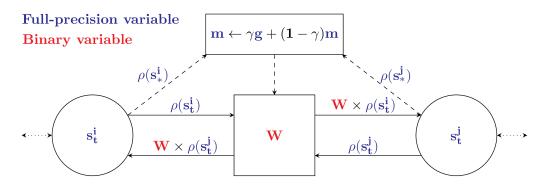

|   | 4.2                                                                            | EP Learning of Recurrent Binary Weights with Full Precision Neural Activations       | 88         |  |  |  |  |  |

|   |                                                                                | 4.2.1 Feeding EP weight updates into BOP                                             | 89         |  |  |  |  |  |

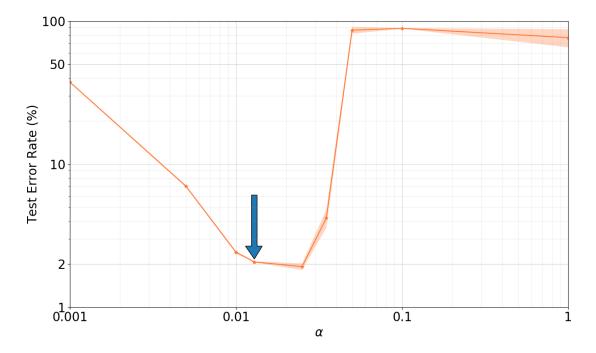

|   |                                                                                | 4.2.2 Normalizing the Binary Weights with a fixed scaling factor                     | 90         |  |  |  |  |  |

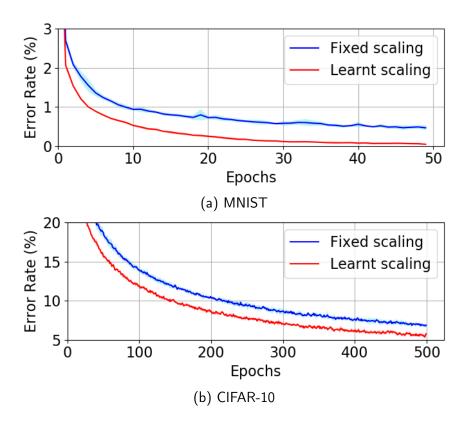

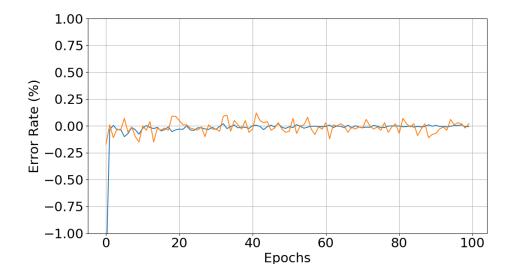

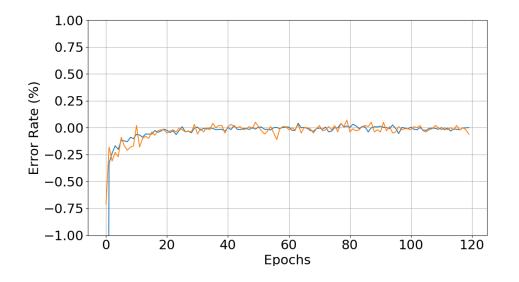

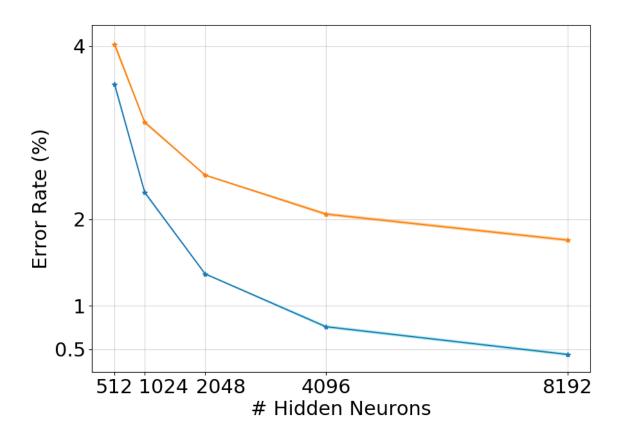

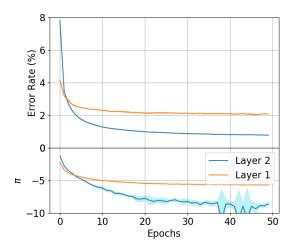

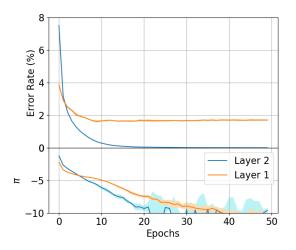

|   |                                                                                | 4.2.3 Normalizing the Binary Weights with a learnt scaling factor                    | 93         |  |  |  |  |  |

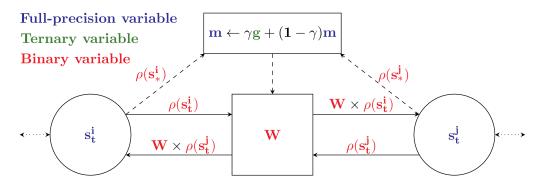

|   | 4.3                                                                            | EP Learning of Recurrent Binary Weights with Binary Neural Activations               | 95         |  |  |  |  |  |

|   |                                                                                | 4.3.1 Convergent neural networks with binary activations.                            | 95         |  |  |  |  |  |

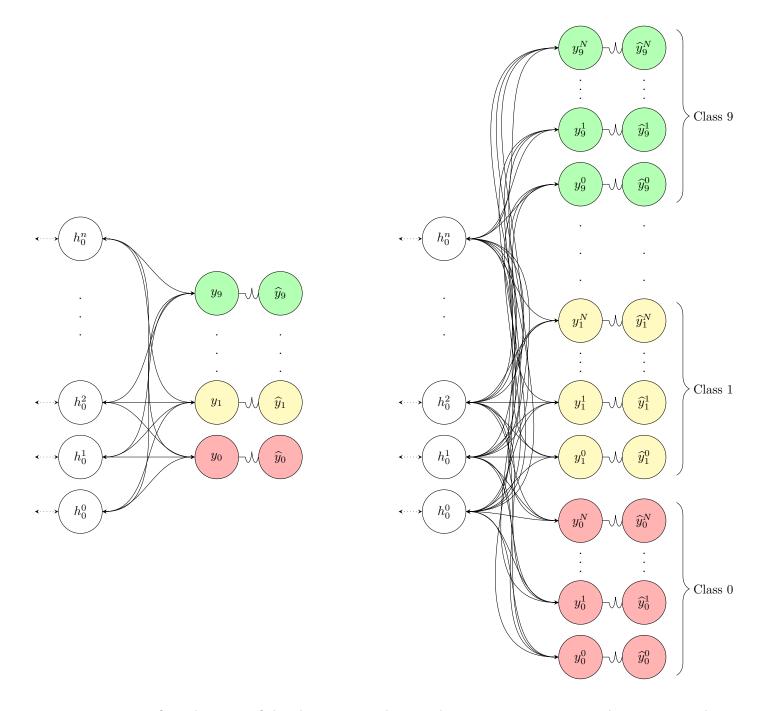

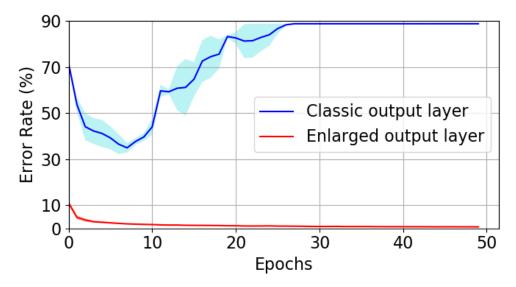

|   |                                                                                | 4.3.2 Augmenting the Error Signal to Nudge Neurons with Binary Activations           | 97         |  |  |  |  |  |

|   |                                                                                | 4.3.3 Results                                                                        |            |  |  |  |  |  |

|   | 4.4                                                                            | Related works                                                                        |            |  |  |  |  |  |

|   | 4.5                                                                            | Impact of Binary Equilibrium Propagation on hardware implementations                 |            |  |  |  |  |  |

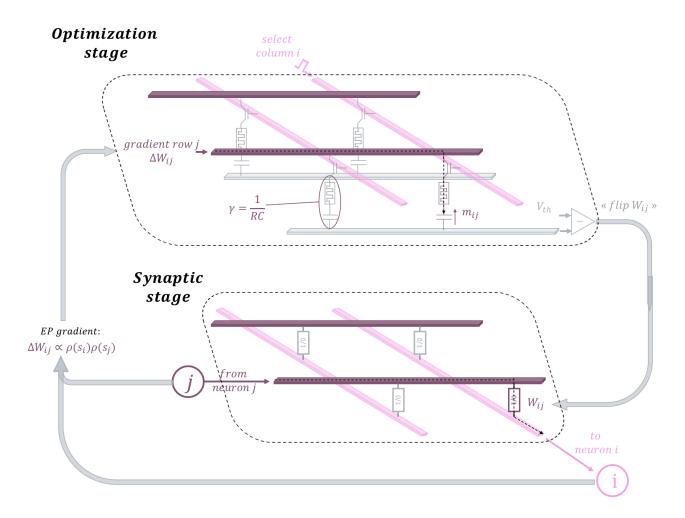

|   |                                                                                | 4.5.1 Implementing in hardware the binary synapses and the optimization stage        |            |  |  |  |  |  |

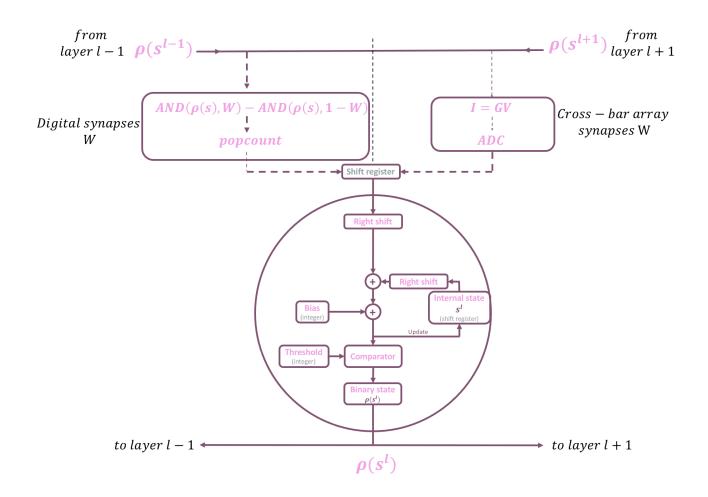

|   |                                                                                | 4.5.2 Hardware implementation of fully binarized Equilibrium Propagation             |            |  |  |  |  |  |

|   |                                                                                | 4.5.3 Stochastic binary neurons?                                                     |            |  |  |  |  |  |

|   | 4.6                                                                            | Conclusion                                                                           | 111        |  |  |  |  |  |

| 5 | Sup                                                                            | ervised learning in an Ising Machine with Equilibrium Propagation                    | 113        |  |  |  |  |  |

|   | 5.1                                                                            | Introduction: an Ising Machine as a parametrizable energy-based model for supervised |            |  |  |  |  |  |

|   |                                                                                | learning: the D-Wave QPU                                                             | 113        |  |  |  |  |  |

|   |                                                                                | 5.1.1 Spin-based hardware are parametrizable energy-based models                     | 114        |  |  |  |  |  |

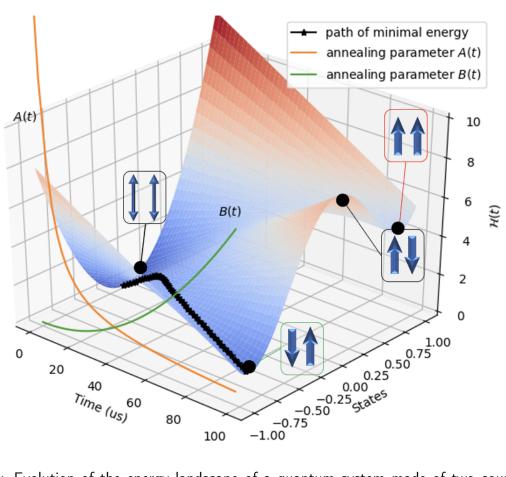

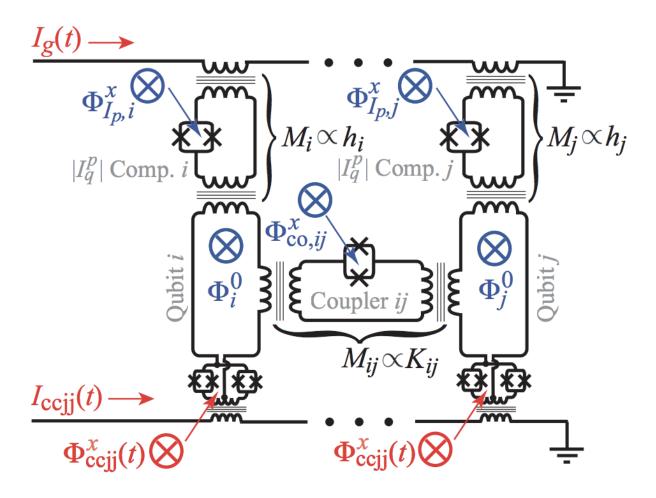

|   |                                                                                | 5.1.2 A specific case: the D-Wave IM                                                 |            |  |  |  |  |  |

|   | 5.2                                                                            | Equilibrium Propagation allows supervised learning in a Ising Machine                |            |  |  |  |  |  |

|   |                                                                                | 5.2.1 D-Wave IM can perform both the inference and the error-backpropagation         |            |  |  |  |  |  |

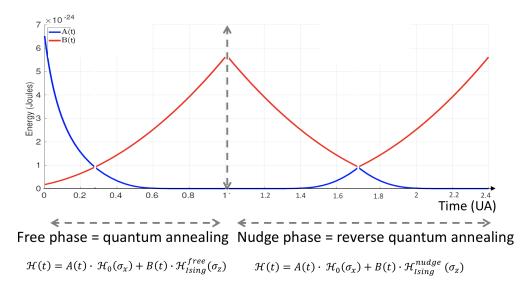

|   |                                                                                | through its intrinsic dynamics alone                                                 | 121        |  |  |  |  |  |

|   |                                                                                | 5.2.2 EP training algorithm with IM in the loop                                      |            |  |  |  |  |  |

|   | 5.3                                                                            | Training a fully-connected architecture on the D-Wave Ising Machine                  |            |  |  |  |  |  |

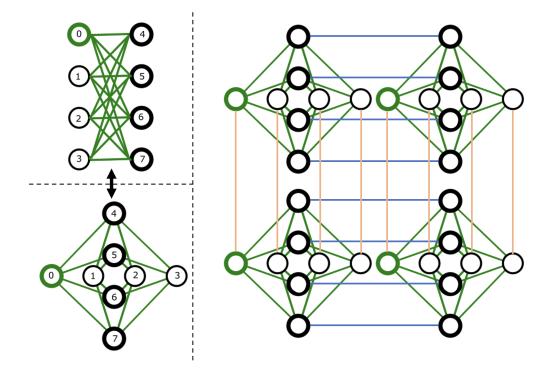

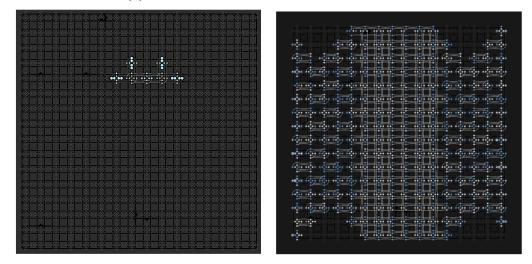

|   | 0.0                                                                            | 5.3.1 Embedding the Fully-Connected neural network on the Ising Machine and          | . <u> </u> |  |  |  |  |  |

|   |                                                                                | updating the parameters                                                              | 125        |  |  |  |  |  |

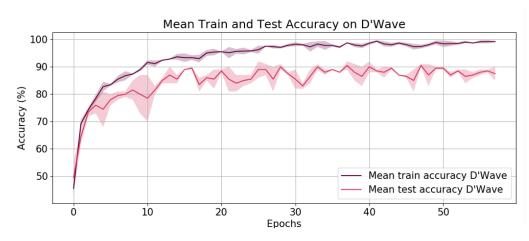

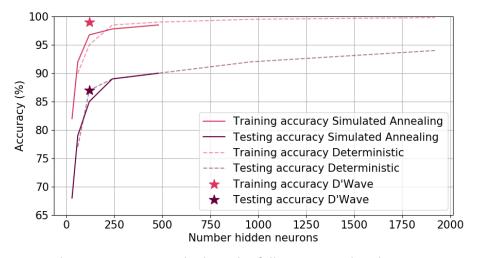

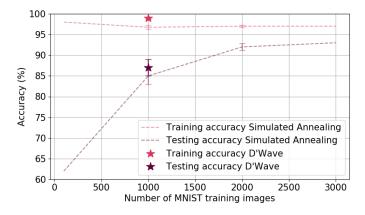

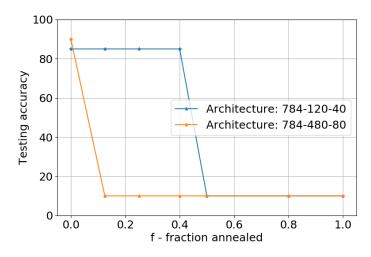

|   |                                                                                | 5.3.2 Results for a fully-connected architecture on MNIST                            |            |  |  |  |  |  |

|   |                                                                                |                                                                                      | . 20       |  |  |  |  |  |

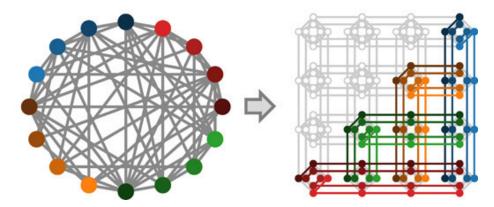

|    | 5.4        | <ul> <li>Training a convolutional architecture on the IM: toward layout-guided architectures .</li> <li>5.4.1 Why layout-guided architectures?</li></ul>                                                                                                 | 135<br>135<br>136<br>138        |

|----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|    | 5.5<br>5.6 | Perspectives                                                                                                                                                                                                                                             | 140                             |

| 6  | 6.1        | clusion and perspectivesConclusionPerspectivesConclusion                                                                                                                                                                                                 |                                 |

| Bi | bliog      | raphy                                                                                                                                                                                                                                                    | 148                             |

| Α  | A.1        | Ining Fully Connected Layers Networks with Equilibrium PropagationEnergy-Based SettingsA.1.1Energy FunctionPrototypical SettingsA.2.1DynamicsA.2.2Primitive FunctionA.2.3Learning Rule                                                                   | 165<br>166<br>166<br>167        |

| В  | B.1        | Ining Convolutional Networks with Equilibrium PropagationOperations involved in the convolutional systemPrototypical SettingsB.2.1 Equations of the dynamicsB.2.2 Learning rulesEnergy-Based SettingsB.3.1 Equations of the DynamicsB.3.2 Learning Rules | 170<br>170<br>170<br>171<br>171 |

| С  | C.1        | caling Factor for Equilibrium Propagation         Learning the Scaling Factor with EP                                                                                                                                                                    | 173<br>174<br>174<br>174        |

### Remerciements

Je voudrais commencer par remercier Julie. Tu m'as fais confiance en me prenant sur un sujet qui n'était pas forcément ma spécialité. Je te remercie pour avoir été une super encadrante de thèse. Merci pour ton enthousiasme permanent, tes francs commentaires, ta patience et ta gentillesse. Merci d'avoir été si disponible, notamment en cette fin de thèse, accélerée par ma faute. Bravo pour ton intuition géniale qui veut concilier matériel et algorithme, et qui, comme on le pense, sera clé pour réduire l'empreinte carbone de l'intelligence artificielle dans le futur. Merci aussi de m'avoir laissé le choix des sujets sur lesquels je voulais travailler. Cela a toujours été un réel plaisir de travailler en sachant que tu nous fais confiance et nous soutient. Tu as su me faire évoluer sur un nombre infini de points, mais merci notamment pour l'amélioration de ma communication avec les autres ! Le groupe a de la chance de t'avoir.

Je veux aussi remercier chaleureusement Damien Querlioz, qui en plus d'avoir été membre de mon jury de thèse a été d'une immense aide tout au long de cette thèse. Merci pour la collaboration pour mon premier article et tes retours constructifs. Merci également pour tes commentaires pendant la deuxième partie de thèse et lors de la soutenance, ils font germer en moi plein d'idées !

Je tiens également à remercier Daniel Brunner, Louis Hutin, Jean-Michel Portal et Damien Querlioz d'avoir accepté d'être membre de mon jury de thèse. Merci pour votre intérêt pour le sujet et pour vos questions qui m'ont permis d'appréhender mon sujet et le calcul neuromorphique sous de nouveaux angles. Merci particulièrement à Daniel Brunner et Louis Hutin pour vos commentaires précieux et méticuleux sur mon manuscript.

Cette thèse n'aurait probablement pas pu avoir lieu sans Geoffroy Lerosey. Tu m'as fais confiance en me prenant comme « stagiaire mi-temps» à Greenerwave début 2018. Cette année et demi passée avec vous m'as permis de reconsidérer un parcours dans la recherche et tes conseils précieux m'ont finalement décidés à postuler à une thèse dont voici le résultat. Merci mille fois pour ta confiance et bravo pour la super aventure qu'est Greenerwave !

Merci à toute l'équipe neuromorphique qui m'a accompagné tout au long de cette thèse. Vous m'avez permis de grandir et murir scientifiquement, de découvrir de nouveaux horizons de recherche et d'obtenir des résultats. Merci notammenet à Dédalo d'avoir été un bon « parrain » de thèse, ton arrivée dans l'équipe le même jour que moi était certainement un signe puisque j'ai pu compter sur tes (plus que) précieux conseils et commentaires pendant ces trois pour améliorer mes travaux. Tout en étant fort, tu restes humble et simple, tu es un exemple de chercheur ! Merci à Alice et Danijela pour leur encadrement. Merci à Jack (et Heidi) d'avoir été un super co-bureau et de nous avoir fait découvrir la culture chinoise/ australienne (nous nous souviendrons longtemps de vos dumplings maison !). Merci à Erwann pour les discussions et nos mises en commun de nos galères respectives avec EqProp. Merci à Marie d'avoir été une super co-thésarde dans l'équipe, ça a toujours été un plaisir d'échanger avec toi ! Merci à Pankaj, bien que nos sujets soient très distants, ça a toujours été agréable de discuter de nos travaux respectifs. Merci à Nathan, Erwan, Tristan, Arnaud, Dongshu, Andrew, Baptiste.

Je réserve une place particulière dans ces remerciements à Maxence Ernoult. Tu m'as initié à EqProp et à la rigueur nécessaire pour obtenir et analyser les résultats que nous avons obtenus ensemble. Ça a été un réel plaisir d'apprendre et d'échanger avec toi tout au long de cette thèse. C'est en partie grâce à toi que j'ai pu me faire une vision personnelle du sujet et du domaine, alors merci ! Je remercie aussi les membres du labo du C2N : Axel et Tifenn.

Merci aux personnes qui font vivre l'UMPhy. Merci à Vincent Cros et à Paolo Bortolotti de diriger ce labo. Merci à Anne Dussart et Florence Hamet pour votre aide au quotidien qui a été très précieuse ! Merci pour votre patience quand il a fallu attendre les factures.

Merci à Enzo, Kevin, Vincent, Sarah, Simon, qui en plus d'être des collègues de travail sont devenus au cours de ces trois années des amis précieux et sans doute indispensables pour la réussite de cette thèse. Bon courage Kevin et Sarah, la fin est proche ! Merci à toutes les autres personnes que j'ai cotoyé au sein de l'UMPhy, ça a été un réel plaisir de travailler à vos côtés.

Je tiens aussi à remercier tous mes amis hors laboratoire. Merci à Joris, qui me donne des leçons de ski depuis maintenant trop longtemps, d'être une bonne excuse pour rentrer à Annecy. Merci à mes amis de prépa : Diane, Eloi, Elodie, Erwan, Guillaume, Hugo, Mathéo, Pauline, Thomas et tout ceux que j'oublie. Merci aussi à mes amis de l'ESPCI : Loïc, Samuel, Jessie, Julie Z, Julie B, Alice, Chloé, Svetlana, Lucile. Merci aussi à Tristan. La distance et nos activités respectives ne permettent pas toujours des rencontres régulières mais vous avez une place particulière dans mon coeur.

Merci également à tout ceux que j'ai pu rencontrer à A Bras Ouverts. Merci à tous les merveilleux accompagnateurs (Adélaïde, Anaïs, ...) et jeunes porteur de handicap que j'ai pu rencontrer au sein du groupe Saint-Gobert. Être responsable de ce groupe pendant cette thèse a été un formidable moteur de motivation et remède au découragement. Merci à toute ma famille pour votre présence permanente malgré la distance. Merci aux moments de partage et de rigolades qui ont été de vrais moments de détente pendant ces trois années. Merci plus particulièrement à ma soeur Laura, qui, malgré notre vision du monde complètement différente, a su me soutenir et me permettre d'être connecté au monde.

Merci papa et maman pour avoir toujours été mes premiers supporters. Vous avez été derrière moi depuis tout petit en me guidant et en acceptant tous mes choix. Merci de m'avoir suivi bien qu'étant étrangers au monde de la recherche. J'espère que cette thèse matérialise un peu plus ce que j'ai pu faire ces dernières années.

Enfin, merci Alice. Je ne sais pas comment te remercier assez pour ton soutien indefectible tout au long de cette thèse. Merci Alice d'avoir été la femme rêvée tout au long de ces trois années, de m'avoir supporté malgré mes sautes d'humeur, de m'avoir poussé à donner le meilleur de moi-même, merci ! Je remercie également notre petite Faustine, qui avec son sens tu timing légendaire est arrivée au moment de commencer la rédaction de thèse. Malgré les nuits blanches et une attention distraite, tes sourires et ta joie de vivre m'ont permis de finir cette thèse merveilleusement. J'ai hâte de voir la suite ensemble.

### Synthèse

**Contexte.** Dans un monde où les données dictent la plupart des décisions, l'enjeu est aujourd'hui d'arriver à traiter ces données de la façon la plus efficace et performante possible. Les algorithmes de d'apprentissage automatique apprennent à découvrir des patterns sous-jacents à ces données en en regardant un très grand nombre. La branche la plus populaire de l'apprentissage automatique est actuellement l'apprentissage profond puisqu'il atteint les meilleures performances en reconnaissance d'image, génération de texte, etc [1]. Ce champ de l'intelligence artificielle repose sur l'utilisation d'algorithmes dits de "réseaux de neurones" artificiels qui apprennent à transformer des entrées de façon non-linéaire vers un espace des caractéristiques, par la présentation d'un grand nombre de ces entrées. L'apprentissage profond tire sa puissance de la façon dont le réseau de neurones est ajusté au fur et à mesure de ses observations pour affiner la transformation qu'il effectue sur les entrées. Une manière d'entrainer les réseaux de neurones artificiels est l'apprentissage supervisé. Cette procédure d'apprentissage requiert un ensemble de données d'entrainement dont les données sont étiquetées, l'étiquette correspondant à la classe de la donnée dans le tâche classique de classification d'images. Ainsi on peut calculer un signal de rétro-action pour mettre à jour les paramètres du réseau de neurones dans le but d'améliorer sa performance. En apprentissage supervisé, les ajustements, qui concernent les connections synaptiques entre neurones, sont appliqués de façon à minimiser une fonction de coût global qui décrit l'écart entre la sortie du réseau de neurones, obtenue pour une certaine donnée d'entrée, avec la sortie théorique attendue, qui est l'étiquette de cette même donnée. Combinée avec une architecture profonde, c'est à dire un réseau où plusieurs couches de neurones artificiels sont empilées, l'apprentissage supervisé, appliqué à la tâche de classification d'images par exemple, permet de faire émerger une hierarchie de détection des caractéristiques où chaque couche, en partant de la couche d'entrée, va détecter des caractéristiques de plus en plus complexes de l'entrée et permettre in-fine une séparation simple des entrées.

Récemment, l'explosion de la puissance de calcul disponible a rendu possible l'entrainement de réseaux de neurones artificiels ayant un nombre de paramètres gigantesque : Dall-E 2: 3B [2], GPT-3: 175B [3], Chinchilla [4], etc. Ceci a permis d'atteindre des performances qui surpassent largement toutes les méthodes existantes. Cependant, l'entrainement de ces très gros modèles s'accompagne d'une augmentation exponentielle de la consommation d'énergie requise pour faire tourner le matériel numérique utilisé pour entrainer les réseaux de neurones. Ces matériels sont basés sur l'architecture "Von Neumann" [5] où la mémoire et l'unité de calcul sont séparés physiquement. C'est une limitation majeure pour entrainer des réseaux de neurones, car la phase d'entrainement requiert de constamment bouger les données de la mémoire au processeur et inversement [6]. De plus, comme l'énergie nécessaire pour déplacer les données dépasse largement l'énergie nécessaire pour effectuer un calcul avec ces mêmes données [7], cela se traduit par une facture énergétique et des émissions de carbone pour entrainer des réseaux de neurones qui deviennent insoutenables. Ainsi, le besoin d'alternatives aux processeurs actuels est pressant.

Motivation de la thèse. Les réseaux de neurones artificiels peuvent être interprétés comme la transformation non-linéaire d'une donnée d'entrée vers un état de sortie. Alors on peut envisager d'utiliser des systèmes physiques, qui réalisent de façon intrinsèque cette transformation non-linéaire entre deux quantités physiques mesurables, pour effectuer cette transformation en lieu et place des processeurs numériques actuels. Tirer partie de la dynamique intrinsèque d'un système physique pour effectuer implicitement des opérations au lieu de calculer explicitement les opérations impliquées dans les réseaux neuronaux dans des simulations logicielles pourrait en effet conduire à des gains d'efficacité énergétique de plusieurs ordres de grandeur par rapport aux approches CMOS digitales traditionnelles [8]. Ces gains sont obtenus grâce à l'absence de déplacement de données et au calcul implicite effectué par la dynamique du système. Cependant, il est nécessaire de pouvoir paramétrer ces systèmes, c'est-à-dire de pouvoir appliquer des paramètres que l'on peut corriger et qui modifient la dynamique du système, afin de guider la dynamique vers la transformation souhaitée pour résoudre une tâche donnée.

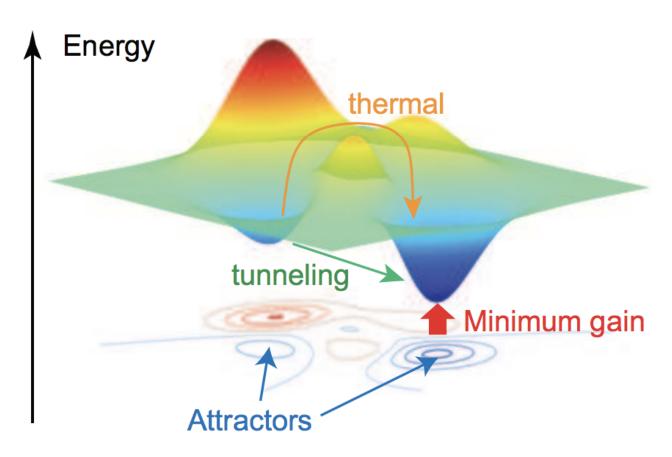

L'une des possibilités pour paramétrer un système composé de nombreuses unités qui intéragissent entre elles, comme un réseaux neuronaux artificiels où les neurones sont couplés les uns aux autres, est d'ajuster ces interactions qui définissent la fonction d'énergie du système physique. En effet, Boltzmann nous a appris que de tels systèmes physiques systèmes physiques évoluent de façon la plus probable vers l'état de moindre énergie :  $p(s, \theta) \propto e^{-\beta E(s, \theta)}$ . Donc, si nous sommes capables de façonner le paysage énergétique à l'aide des paramètres ajustables, en particulier capable d'encoder dans des minima de l'énergie une sortie spécifique, nous pouvons guider le système pour qu'il effectue une tâche d'intérêt. Cette approche a largement inspiré les travaux pionniers en IA qui ont utilisé cette paramétrisation du système via la fonction d'énergie: réseau de Hopfield [9], Mémoire Associative Bi-directionnelle [10], Machine de Boltzmann [11], etc. Mais ces algorithmes peinent aujourd'hui à atteindre les performances des modèles de deep learning car leur procédure d'entrainement n'optimise pas une fonction de coût globale mais plutôt des objectifs intermédiaires [11] voir aucun objectif [12], [13]. Ceci ne permet pas l'émergence d'une hiérachie de détection des caractéristiques de l'entrée et donc une moins bonne performance au final.

Mais aujourd'hui, l'intérêt pour ces modèles regagne en intensité pour la conception de puces basse consommation basées sur la physique de systèmes émergents. Contrairement à backpropagation, qui calcule le gradient de la fonction de coût par rapport aux paramètres du réseau grâce à la règle des dérivées successives, qui est hautement délocalisée et complexe et donc nécessite un circuit périphérique lourd pour être calculée, les algorithmes qui entraînent les modèles basés sur l'énergie se basent sur des règles d'apprentissage qui sont spatialement locales. Il n'y a donc aucun déplacement de données et la complexité du calcul est réduite, ce qui, en fin de compte, réduit les besoins en mémoire et en capacité de calcul requis pour l'apprentissage de ces modèles basés sur l'énergie. Ainsi, les règles d'apprentissage locales utilisées pour entraîner les systèmes physiques, qui sont naturellement basés sur l'énergie, pourraient conduire à des implémentations de réseaux neuronaux matériels à très faible consommation.

**Problématique.** Equilibrium Propagation (EP) [14], est une alternative à la backpropagation pour calculer le gradient d'une fonction de coût globale par rapport aux paramètres d'un réseau de neurones basé sur une fonction d'énergie. EP est donc un algorithme apprentissage prometteur pour la réalisation de systèmes physiques matériels, car il permet d'effectuer un apprentissage supervisé avec des règles d'apprentissage locales.

Cependant, une implémentation matérielle d'EP se heurte aujourd'hui à la nature encore expérimentale des composants basse consommation envisagés pour des implémentations matérielles (memristors, nano-oscillateurs, MRAM, ...) qui engendre une grande variabilité inter-composants [15] ainsi qu'un bruit intrinsèque [16] qui altèrent l'entrainement de tels systèmes.

#### Contributions de la thèse.

Ainsi, dans cette thèse nous allons tout d'abord nous intéresser à réduire la précision requise pour les paramètres et les neurones afin que de tels systèmes basés sur une fonction d'énergie et entrainés par EP parviennent toujours à résoudre des tâches de classification d'image. Plus précisément, nous allons voir que l'on peut binariser les synapses et l'activation des neurones dans de tels réseaux et réussir à faire de la classification avec une précision à l'état de l'art. Ce travail permet d'envisager un entrainement sur puce par EP d'un système matériel fait de composants émergents dans leur régime présentant le moins de variabilité et de bruit possible: le régime binaire, tout en conservant leur intérêt basse-consommation. Ce travail ouvre également l'opportunité d'entrainer des réseaux de neurones binaires (BNNs) sur du matériel numérique standard qui possède à la fois peu de mémoire et peu de capacité de calcul sans entrainement préalable sur un gros matériel (GPU), ce qui était impossible jusqu'à aujourd'hui.

- **Publication** : Ce travail a fait l'object d'une publication *"Training Dynamical Binary Neural Networks with Equilibrium Propagation, Laydevant et al., 2021"* [17] dans le cadre du workshop Binary Vision au sein de la conférence CVPR 2021.

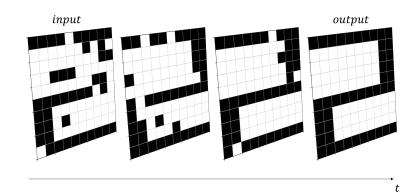

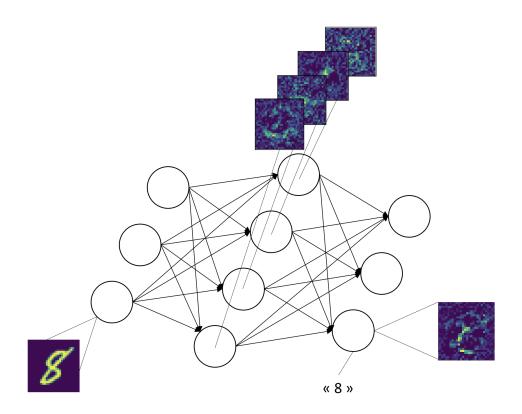

- · Ensuite nous verrons comment nous avons réussi une première implémentation matérielle grande échelle entrainée par EP. Nous avons choisi comme système matériel la machine d'Ising proposée par D'Wave car c'est un système physique qui, par nature, implémente une fontion d'énergie, et qui, de plus, est facilement et rapidement reconfigurable, propriété indispensable pour les réseaux de neurones artificiels dont les paramètres sont continuellement ajustés lors de la phase d'entrainement. Nous allons voir que nous avons réussi à entrainer une petite architecture entièrement connectée sur la base de donnée de chiffres manuscrits MNIST en utilisant la procédure dite "d'embedding", qui assigne à un neurone plusieurs spins sur la puce afin de s'affranchir du problème de connectivité locale seulement offert par la puce. Ensuite nous verrons qu'on peut utiliser la connectivité inhérente au circuit de D'Wave pour faire des opérations plus complexes adaptées au matériel comme des convolutions et ainsi réussir à entrainer un petit réseau convolutionnel sur la puce. Ce travail ouvre la voie à d'autres implémentations matérielles entrainées par EP mais aussi à la possibilité d'utiliser les machines pour d'autres applications que la résolution de problèmes d'optimisation combinatorielle. Nous discuterons enfin du contexte plus global dans lequel s'inscrit cette thématique de recherche focalisée sur la réduction de l'énergie liée à l'entrainement et à l'utilisation des réseaux de neurones en tant que modèles d'inférence ainsi que des perspectives pour ces puces non-conventionnelles.

- **Publication** : Ce travail va être l'objet d'une publication *"Supervised learning in an Ising Machine with Equilibrium Propagation, Laydevant et al."* dans un journal à comité de lecture et est actuellement en cours d'écriture.

Pour résumer, cette thèse s'intéresse à démontrer qu'un système physique non-conventionnel peut être une alternative pertinente aux processeurs clas-

siques pour faire de l'apprentissage profond. Tout au long de ce manuscript nous allons montrer au lecteur qu'utiliser le comportement physique de systèmes ext une voie prometteuse afin de combler les déficiences des approches tradionnelles digitales CMOS pour réaliser les calculs du deep learning.

### Thesis summary

**Context.** In a data-driven world, the challenge today is to process this data in the most efficient and effective way possible. Machine learning algorithms learn to discover the underlying patterns in data by looking at a very large amount of it. The most popular branch of machine learning is currently deep learning because it achieves the best performance on image recognition, text generation, etc [1]. This field of artificial intelligence is based on the use of algorithms called "artificial neural networks" that learn on a large number of examples how to transform inputs in a non-linear way to a space of features. Deep learning gets its power from the way the neural network is adjusted as it observes more and more data to refine the transformation it performs on them. A successful way to train artificial neural networks is the supervised learning way. This learning procedure require a training dataset which inputs are labeled, the label corresponding to the input data category in the standard case of classification, such as we can compute a feedback to update the network parameters in order to improve its performance. In supervised learning, the adjustments, which concern the synaptic connections between neurons, are applied in order to decrease a global cost function that depicts the discrepancy between the output of the neural network, obtained for a specific input and the expected theoretical output, the label of this same input. Combined with a deep architecture, *i.e.* a network where several layers of artificial neurons are stacked, supervised learning, applied to image classification for instance, allows the emergence of a hierarchy of feature detection where each layer, starting from the input layer, will detect more and more complex features of the input and allows in-fine a simple separation of the inputs.

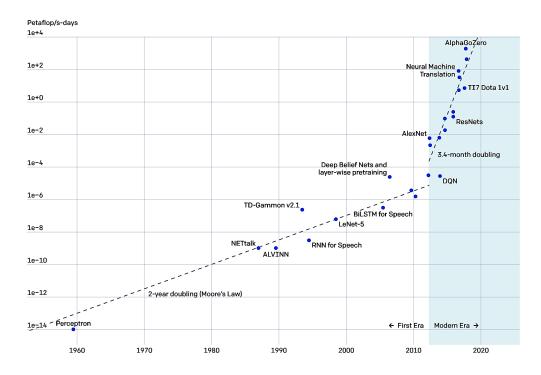

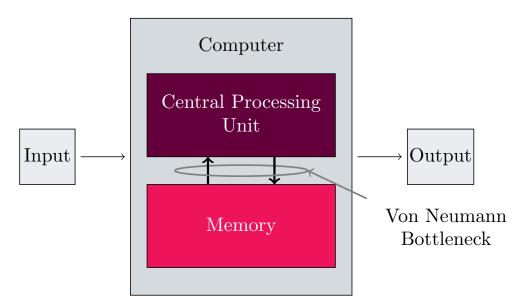

Recently, the explosion of the available computing power has made possible to train artificial neural network models that have a gigantic number of parameters: Dall-E 2 [2]: 3B, GPT-3 [3]: 175B, Chinchilla [4]: 70B, etc. This has made it possible to achieve performances that far exceed all existing methods. However, the training of these very large models is accompanied by an exponential increase in the power consumption required to run the digital hardware that is used to train the neural networks. These hardware are based on the "Von Neumann" architecture [5] where the memory and the processing unit are physically separated. This is a major limitation to train neural networks as we constantly need to move the parameters back and forth between the memory and the processing unit [6]. Furthermore, as the energy to move data largely excels the energy to do an actual computation with the data [7], this results in a energy bill and carbon emissions to train neural networks that become unsustainable. Thus, the need for alternatives to the current processors is pressing.

**Motivation of the thesis.** Artificial neural network algorithms can be interpreted as a non-linear mapping from an input to an output in a non-linear way. Then we can consider using physical systems which intrinsically carry out this non-linear transformation between two measurable physical quantities instead of the current digital processors. Leveraging the intrinsic dynamics of a physical system to perform the computation instead of computing the operations involved in neural networks in software simulations could lead to orders of magnitude gains in energy-efficiency compared to traditional digital CMOS approaches [8]. These gains are obtained because of no data movement and the implicit computation performed through the dynamics of the system. However, it is necessary to be able to parameterize these systems, *i.e.* apply tunable parameter that modify the dynamics of the system, in order to guide the dynamics toward the desired mapping solving a given task.

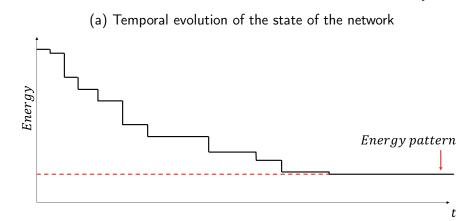

One possibility for parametrizing a system made of many interacting units, such as an artificial neural networks where the neurons are coupled to each other, is to tune the interactions that define the energy function of the physical system. Indeed, Boltzmann taught us that such physical systems most likely evolve towards the state of least energy:  $p(s,\theta) \propto e^{-\beta E(s,\theta)}$ . So if we are able to shape the energy landscape with the help of the tunable parameters, especially encode in minima of the energy a specific output, we can guide the system to perform a task of interest. This approach has largely inspired the pioneering works in AI that have used this parametrization of the system via the energy function: Hopfield network [9], Bi-directionnal Associative Memories [10], Boltzmann machine [11], etc. But these algorithms struggle today to reach the performances of deep learning models because their training procedure does not optimize a global cost function but rather intermediate objectives [11] or no objectives at all [12], [13]. This does not allow the emergence of a hierarchy of input features detection and therefore leads to a lesser performance in the end.

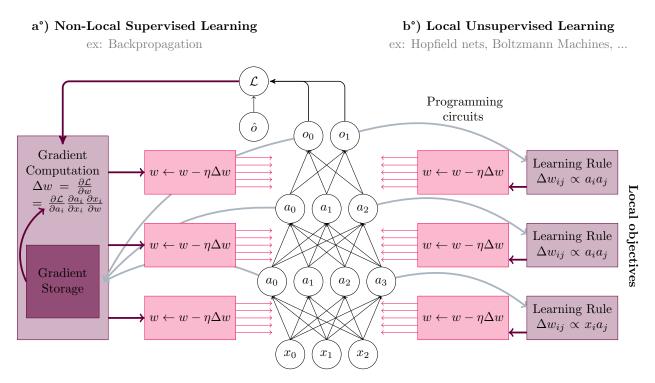

But today, the interest for these models is regaining intensity for the design of low power chips based on the physics of emerging systems. Contrarily to backpropagation, which computes the gradient of the cost function with respect to the parameters with the chain-rule derivation which is highly delocalized and complex hence necessitates a heavy peripherical circuit to be computed, algorithms that train energy-based models build on learning rules that are spatially local. This results in no data movement and a reduced computational complexity which, ultimately, reduce both the memory and computation requirements for training these energy-based models. Hence, local learning rules used to train physical systems, that are naturally energy-based, could lead to ultra low-power hardware neural networks.

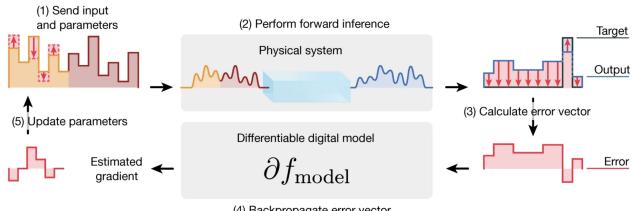

**Problematic.** Equilibrium Propagation (EP) [14], is an alternative to backpropagation to compute the gradient of a global cost function with respect to the parameters of an energy-based neural network. EP is thus a promising learning framework for designing hardware physical systems as it does supervised learning with local learning rules.

However, a hardware implementation of EP is currently hampered by the still experimental nature of the low-power nanodevices considered for hardware implementations (memristors, nano-oscillators, magnetic random access memories, ...) which results in a large device-to-device variability [15] as well as an intrinsic noise that impairs the training of such systems [16].

#### Contributions of the thesis.

- Thus, in this thesis we will first focus on reducing the required precision of parameters and neurons so that such energy-based systems and trained by EP can still solve image classification tasks with high accuracy. More precisely, we will see that one can binarize synapses and neuron activations in such networks and succeed in classification at state-of-the-art levels. This work allows us to consider an on-chip training by EP of a hardware made of emerging components in their regime presenting the least variability and noise possible: the binary regime, while keeping their low-consumption interest. This work also opens the opportunity to train binary neural networks (BNNs) [18], [19] on standard digital hardware that has little memory and computational budgets without prior training on large hardware, which was impossible until now.

- **Publication:** : This work has been published as *Training Dynamical Binary Neural Networks with Equilibrium Propagation, Laydevant et al., 2021"* [17] within the workshop Binary Vision at the CVPR 2021 conference.

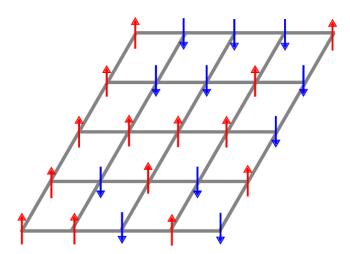

- Then we will describe how we realized a first large-scale hardware implementation driven by EP. We chose the Ising machine proposed by DWave as our hardware system for this purpose because it is an physical system which by nature implements an energy function and, moreover, it is easily and quickly reconfigurable, an indispensable property for artificial neural networks whose parameters are continuously adjusted during the training phase. We will see that we have succeeded in

training a small fully-connected architecture on the handwritten digits dataset MNIST using the so-called "embedding" procedure, which assigns to a neuron several spins on the chip in order to overcome with the local-only connectivity offered by the chip. Then we will see that we can use the inherent connectivity of the D'Wave circuit to perform more complex operations adapted to the hardware like convolutions and thus train a small convolutional network on the chip. This work opens the way to other hardware implementations driven by EP but also to the possibility of using Ising machines for other applications than solving combinatorial optimization problems. Finally, we will discuss the global context in which this research theme is developed, with a focus on the reduction of energy related to training and the use of neural networks as inference models as well as the perspectives for these unconventional chips.

**Publication:** : This work will be the subject of a publication "Supervised Learning in an Ising Machine with Equilibrium Propagation, Laydevant et al." in a peer-reviewed journal and is currently being written.

To summarize, this thesis is interested in demonstrating that an unconventional physical system can be a relevant alternative to classical processors for deep learning. Throughout this manuscript we will show the reader that using the physical behavior of systems to perform deep learning computations offers new routes to overcome the deficiencies of traditional digital CMOS approaches for deep learning computations.

# Conventional digital hardware performing deep learning with over-parametrized neural networks is energy-greedy

The automation of tasks such as image classification, text translation or motion control has recently become widespread. This adoption has been enabled by deep learning [1] which is a branch of artificial intelligence based on the intensive use of artificial neural networks that learn to solve tasks from a large amount of data. However, the methods and hardware currently used to make these networks learn are not optimized, which questions the widespread adoption of deep learning without considering the related energy and ecological costs.

As an introduction to the subject of this thesis, we will first describe what deep learning is and how it works today. We will then see why its backbone (the backpropagation algorithm [20]) makes deep learning, as currently trained, difficult to reconcile with economical and ecological sobriety objectives. Then we will see that a possible alternative to the standard processors and architectures currently used to train deep neural networks can be found in the physics of other richer systems. Finally, we will discuss the challenges of designing such new processors based on the physics of emerging unconventional components for computing to reach the performance achieved on current CMOS processors.

We will start by going back to the definition of computation. This concept refers to how two states of a given physical systems are related to each other [21]. Starting from this principle, we will focus on the computations on which deep learning is based to highlight the type of operation that a deep learning algorithm performs: the transformation of an input data into a vector of interest that constitutes the output. We will also detail the algorithms that allow us to obtain the amazing results of deep learning. This will highlight the limits of current deep learning, whose trend is to increase the number of parameters and therefore the need for computing power, entailed on the current conventional hardware (CMOS) especially its high energy and economic costs. Based on this observation, we will explore two possible approaches that attempt to overcome these limitations.

The first method will be developed in this first chapter. It is based on standard deep learning methods but strives to improve practices, whether at the global system level, at the software level or at the hardware level. Thus, we will see how the advent of cloud computing and open source could be one of the solutions to the carbon emission problems of deep learning models. We will also describe the efforts made to reduce the size and computational requirements of trained models. Finally we will see the research done to improve the standard hardware specialized for deep learning computations, they will be optimized to perform the vector matrix product efficiently. We will dissociate the axes of improvement for hardware dedicated to server use and that dedicated to edge computing.

The second approach will be the one this thesis focuses on and will be introduced in the second chapter.

#### 1.1 . Deep learning is about learning a non-linear mapping between

#### an input to an output

Answering the question "why using physics to compute?" requires first defining what computing means. Before diving into the computations that interest us in this thesis - those performed in the context of deep learning - we will go back to the concept of computation. The definition that we will give : "the mapping from an input to an output to perform tasks of interest", will then serve as a guideline throughout this introductory chapter

We will then see that this mapping from an input to an output is exactly what an artificial neural network, the basic algorithm of deep learning, does. We will then describe what an artificial neuron is and how it is integrated into an artificial neural network by being connected to other neurons through synaptic connections that modulate the propagation of the signal in the network.

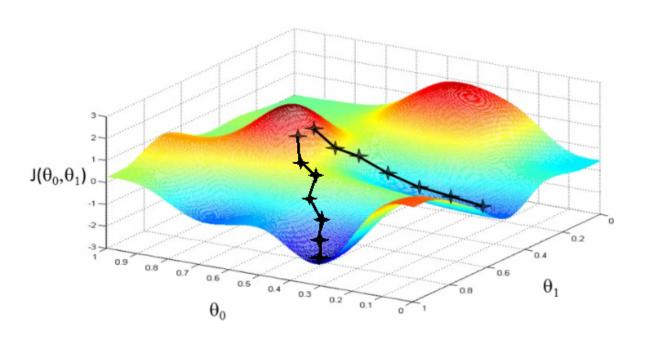

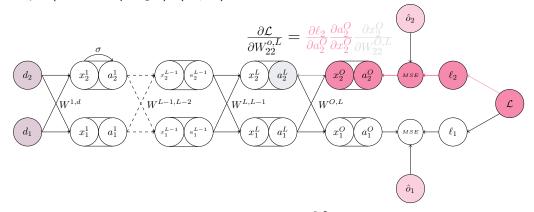

Finally, we will see how these synaptic connections are adjusted so that the network performs the task we want it to do. We will introduce the concept of supervised learning by taking the example of the backpropagation algorithm, the most widespread learning algorithm today, which allows the minimization of a global cost function by stochastic gradient descent.

# 1.1.1 . A computation is a mapping of an input to an output, similarly to deep learning

A mathematical computation speaks to all of us in an implicit way. We know what an addition, a multiplication, etc. are. But in general, it is more difficult to define what a computation is. So we can then refer to the philosophers of science to help us to give this definition.

Gualtiero Piccinini's summary of this account states that a physical system can be said to perform a specific computation when there is a mapping between the state of that system and the computation such that the "microphysical states of the system mirror the state transitions between the computational states" [21].

Thus the concept of computation is intrinsically broad and encompasses many mathematical operations. But we also see that in his attempt to define the concept of computation, Piccinini brings into play the principle of relation between two states of a certain physical system. From then on, the term computation can be understood in different ways. The first one can be the fundamental transition between two states of a physical property of a system such as the on or off state of a transistor or the transition from a non-synchronized state to a synchronized state for an oscillator. The term physical system in the definition can also refer to a more complex physical system composed of different units interacting with each other. The relation between the two states is the "computation" and can be the temporal evolution of a dynamic system for example.

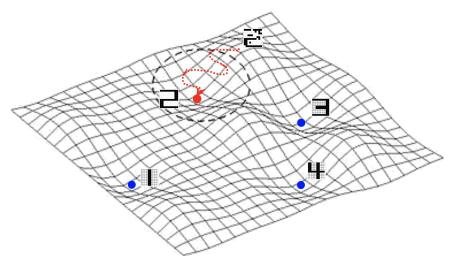

Figure 1.1: Computation can be interpreted as the transformation of an input to an output

In this thesis, we will focus on a very literal use of this definition by placing ourselves in a field of computer science that makes intensive use of this mapping between two states of a physical system. This field of computer science is called deep learning. This discipline is based on the so-called artificial neural network algorithms that perform a transformation (preferably non-linear) of input data in order to perform tasks of interest. These tasks are multiple and can be for example image classification, text generation, ...

In the case of standard deep learning, the physical system described in the definition of computation is in fact the neural network. In this thesis we will take this definition literally and apply it to the case of deep learning and see how a "real" physical system can, by its intrinsic dynamics, perform a computation on data by realizing this mapping between input data and a state of interest which is the output.

# 1.1.2 . The non-linear mapping of deep learning is done by an artificial neural network

Artificial neural networks are the basic algorithms on which deep learning is based. In this part, we detail the important steps that led to artificial neural networks as we know them today, and then introduce the formalism specific to these algorithms.

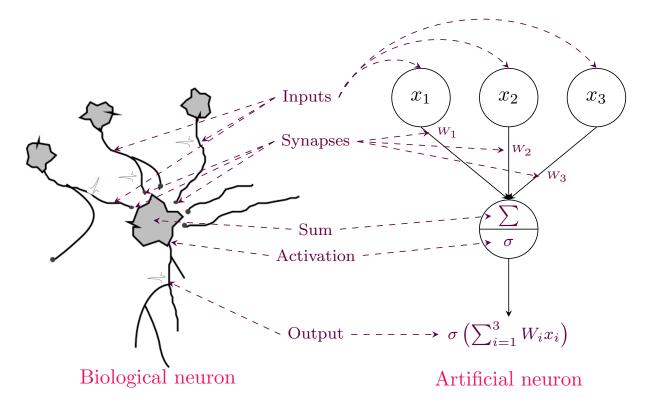

The concept of the artificial neuron was invented in 1943 by McCulloch and Pitts [22]. It was initially conceptualized to model biological neurons which, at that time, were seen as "all-or-nothing" binary units:

$$O_i = H(y) \tag{1.1}$$

where H(y) is the Heaviside step function defined as:

$$H(y) = \begin{cases} 0 \ if \ y < 0\\ 1 \ else \end{cases}$$

(1.2)

and y any input which is a stimulus for the neuron. The activation function of the formal neuron which is the Heaviside step function can be extended to continuous  $\sigma$  functions with a more progressive behavior between two extreme values like the sigmoid or hyperbolic tangent function.

McCulloch-Pitts were also the first to model the concept of artificial synapse by weighting the inputs of the neuron by a real coefficient  $W_{ij}$  (weight of the input j to the neuron i) whose sign and amplitude describe the importance of the input for the neuron. Thus, the formal McCulloch-Pitts neuron receives inputs  $\{X_i\}$  which are weighted by synaptic weights  $W_{ij}$ , realizes the sum of them and then applies a nonlinear activation function which is the Heaviside function in this case:

$$O_i = H(\sum_j W_{ij} X_j) \tag{1.3}$$

The McCulloch-Pitts formal neuron solved logical tasks such as the logical OR<sup>1</sup> or the logical AND<sup>2</sup>. However, it has shown its limitations as an individual neuron since it does not solve the logical exclusive OR task<sup>3</sup> which requires several such neurons to solve. Furthermore, the synaptic weights used for the neuron are chosen and fixed to perform a specific task and do not exhibit plasticity - they have no possibility to change over time.

In 1957, Rosenblatt developed the perceptron [24] which is an algorithm for binary classification of input data that works on the principle of the formal neuron of McCulloch-Pitts, with the addition of a learning rule that allows the neuron to learn to classify the data presented to it. Thus, with the perceptron, the property of synaptic plasticity is introduced and will pave the way for artificial

<sup>&</sup>lt;sup>1</sup>The logical OR is the logical function that given inputs  $X_1$  and  $X_2$ , returns 1 as soon as one of the two inputs is 1, and this also in the case where both inputs are 1

<sup>&</sup>lt;sup>2</sup>The logical AND is a logical function which, given inputs  $X_1$  and  $X_2$ , returns 1 only when both inputs are 1.

<sup>&</sup>lt;sup>3</sup>Logical exclusive OR is a logical function that given inputs  $X_1$  and  $X_2$ , returns 1 only when only one of the two inputs is 1. Regardless of  $X_1$  or  $X_2$ .

Figure 1.2: The building bricks of artificial neurons are inspired from biological neurons. We here show the more general case of the neuron of McCulloch-Pitts where  $\sigma$  can be a continuous activation function. Schematic of the biological neuron is from [23]

neural networks. To learn to classify the presented data, the perceptron requires a training database  $\mathcal{D}$  which contains data pairs  $\{(X^k, y^k)\}_{k \in \mathcal{D}}$  which correspond to data-label pairs. Thus we can know what is the expected theoretical output of the perceptron for a given input and compute a prediction error with the output obtained by the perceptron  $\{O^k\}_{k \in \mathcal{D}}$ . From this a learning rule is derived, which constitutes an indication of the direction and magnitude of the update of a parameter to reduce the prediction error or to improve the prediction success of the perceptron. This type of learning is called supervised learning and has since been used extensively to solve complex machine learning tasks.

The learning rule for the synaptic weights of a perceptron is as follows:

$$\Delta W_{ij} = X_i^k (O^k - y_i^k) \tag{1.4}$$

where the index i indexes the different inputs and the index k denotes the example k presented to the network as well as the state of the corresponding output neuron and the target associated with the input.

This learning rule inspired by Hebb's work [25] minimizes the Mean Squared Error cost function  $C(O^k, y_i^k) = \frac{1}{2} \sum_i (O^k - y_i^k)^2$  which is computed at the output of the perceptron.

The perceptron was a founding step in learning in artificial neural networks. However, the perceptron is only applicable to binary classification tasks (the output of the neuron can only be 0 or 1). And like the formal neuron of McCulloch-Pitts, the perceptron can only solve linearly separable

tasks, which is almost never the case for most databases. Finally, in 1969 the book "Perceptron" [26] by Minsky and Papert, cast a shadow on the perceptron by pointing out its inability to solve the exclusive OR problem.

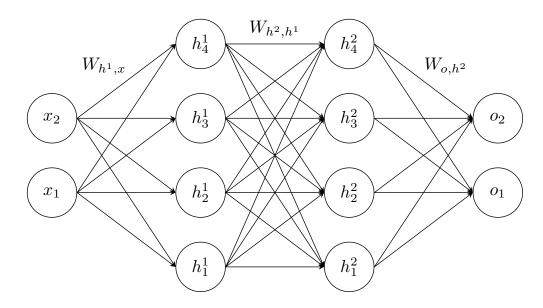

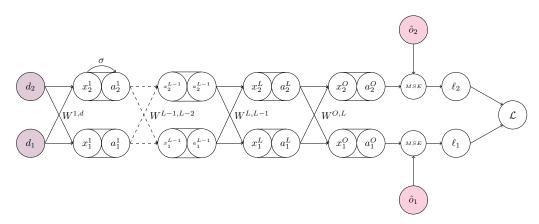

It took more than 10 years for multi-layer perceptrons to appear [27] and to finally solve the exclusive OR problem [27]. These networks are said to be "fully-connected" - that is, each neuron in one layer is connected to all neurons in the next layer via synaptic connections (Fig. 1.3). The synapses modulate the signal propagation of the previous layer in the same way as the inputs of a perceptron are modulated and in a unidirectional way and make the neurons sensitive to distinct features by combining the state of the previous layer in a different way. In fact, these different layers perform in several steps a non-linear transformation of the inputs to a space of features where the different classes are much more easily separable. The state of each layer is then calculated successively according to the state of the previous layer until the state of the output layer o is calculated, which allows to make a prediction on the class to which the presented input x belongs when the network is trained to perform classification.

Figure 1.3: A multi-layered perceptron - or fully connected neural network. x units denote the input nodes,  $h^k$  units denotes the nodes of the k - th hidden layer and o units denotes the output units.

As already suggested by Minsky and Papert in "Perceptron" [26], Rumelhart, Hinton and Williams confirm in their founding paper [20] the importance of introducing neurons between the inputs and the output neurons to build complex representations of the input data that allow a progressive separation in the space of the representations and their classification at the output. This is how the concept of "deep network", with stacked layers of neurons, was born, and this is where deep learning gets its power from.

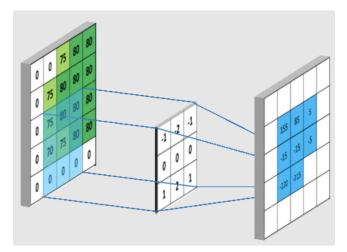

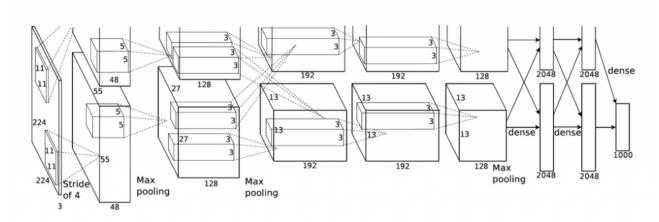

By inserting intermediate - hidden - neurons between the inputs and the output neurons, Rumelhart, Hinton and Williams [20] succeeded in solving the exclusive OR task by training the neural network in a supervised way using the backpropagation procedure. It is also mentioned in the article that the number of times the network must be presented with inputs to be trained decreases as the number of hidden neurons increases. This highlights the importance of hidden units to build a complex representation of the inputs that can be combined to the output layer to perform classification. Finally, between 1986 and 2012, the main advance in the field is the use of convolutional operations instead of "fully-connected" connections in first layers in the so-called convolutional networks (CNNs) [28]. These convolutional operations allow to operate a detection by filtering the input images with filters which, during the process of optimization, will specialize to detect certain spatial features of an input image, or of its internal representations in the network. The first demonstration of the interest of these convolutional networks was to apply a CNN to the recognition of handwritten digits [28].

(a) Convolution operation between an input image and a (3x3) filter. The combination of weights in the filter allows to apply different filters to the input to activate according specific inputs. From [29]

(b) Architecture of the Alexnet CNN [30] that extensively used  $(11\times11)$  filters and Max pooling operations that allow to downsample data.

Figure 1.4: Convolutional neural networks are based on a different operation between layers than a fully-connected operation. The hierarchy of features detected at the output emerges when convolutional layers are stacked.

Unfortunately, as we will see in the next section, the optimization algorithm to minimize the computed error at the output of the network, backpropagation, requires very large memory and computational resources that have been out of reach for a long time for very deep networks (with more than 2 convolutional layers such as the LeNet-5 network [28] that has been for a long time the

reference in the convolutional network field).

2012 is a pivotal year for the research field of artificial neural networks with the first backpropagation training of a deep network containing 5 convolutional layers followed by 2 fully-connected layers [30]. Instead of using standard processors rather specialized in sequential computation (Central Processing Unit (CPU)), Krizhevsky *et al.* had the idea to use graphic processors (GPU), very powerful in parallelized computation, to perform, in a fast and efficient way, the vector-matrix products repetitively realized in the neural networks. This unconventional use of the hardware available at the time allowed them to successfully train such a network with backpropagation. At the time, the authors had to write the operations involved in their network in low-level code. But today, the success of deep learning also comes from the fact that open-source high-level libraries allowing a great abstraction from low-level implications are available to any user: Pytorch, TensorFlow on Python are the best known. These libraries allow the user to train his neural network in an ultra simplified way with a command like network.to(gpu). As we will see later, but they also do a lot for the dissemination of trained models, because they can be made available via these libraries as open-source models and loaded by the user in an extremely simple way.

By halving the classification error obtained previously obtained on Imagenet with other machine learning algorithms, Krizhevsky et al [30] demonstrated the importance of the depth of artificial neural networks to build powerful internal representations.

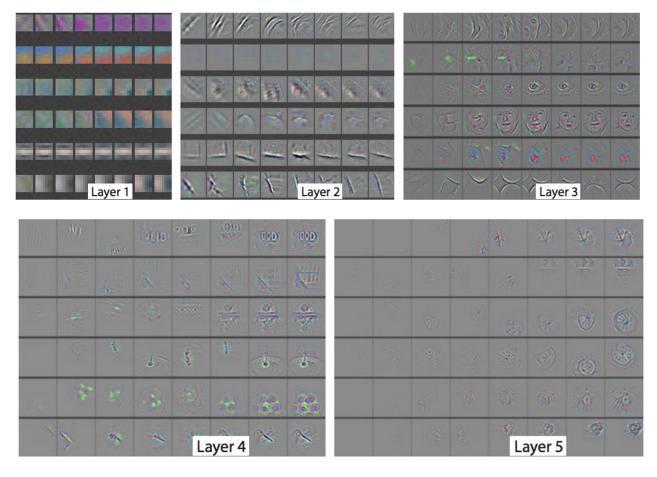

In fact, stacking successive layers in a globally optimized manner allows a hierarchy to emerge in the neural network's internal representation of the input data. The fact that successive layers of neurons are sensitive to increasingly complex features is called a detection hierarchy (Fig. 1.5). The first layer of a network applied to image recognition can for example recognize simple geometrical shapes: vertical, horizontal, diagonal lines, ... . The next layer can be sensitive to combinations of geometric shapes recognized in the previous layer: square, circle, oval, ... . The last layer before the classifier is sensitive to patterns that are close to the different classes to be classified in the database: heads, car, dog, cat, ... The classifier layer for a classification task like here corresponds to the last layer of the network which is fully-connected and combines the last features extracted from the image to assign membership scores for the input to the different classes in the database. Hierarchical feature detection allows for a more intelligent and sparse use of parameters where a feature can be recognized by a combination of several elementary filters.

The emergence of the detection hierarchy allows for better segregation and combination of useful features to make the right prediction at the network output. On the contrary, the learning that was mostly used before backpropagation and the optimization of a global objective was based on the optimization of intermediate objectives [11], [32] that were disconnected from each other, which did not allow a coherent hierarchy to emerge across the entire network - or in a much less powerful way [33], which drastically limited the potential of such approaches.

Since 2012, new approaches have made it possible to have even deeper networks and thus increase the accuracy obtained on ImageNet with the Residual neural networks (ResNets) which can have 18, 34, 50, 101 and even 152 hidden layers [34].

In this section, by quickly going through the history of artificial neural networks, we have discussed the two key concepts that make deep learning successful, which are the joint use of a stack of layers of neurons connected to each other by different operations, together with the minimization of a global cost function through gradient descent. These two methods have allowed deep learning to outperform previous methods by a large margin. We have also seen the interdependence of deep learning as an algorithm with the hardware on which the algorithms run by highlighting the turn taken in 2012 with the use of GPUs for fast highly parallelized computing.

Figure 1.5: Visualization of the features detected on inputs images with varying depths: Layer 1 to 5 of Alexnet-like NN. We clearly see how the features detected are more and more fine-grained when we go deeper in the network. Inside each layer, from left to right is the evolution of the detected feature over training - filters become more and more sensitive to a specific feature. From [31]

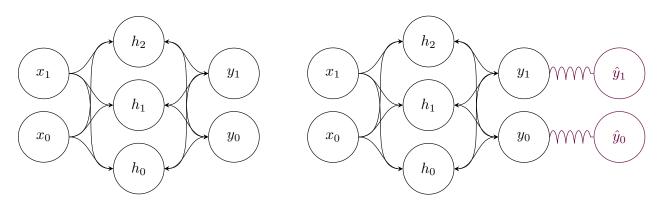

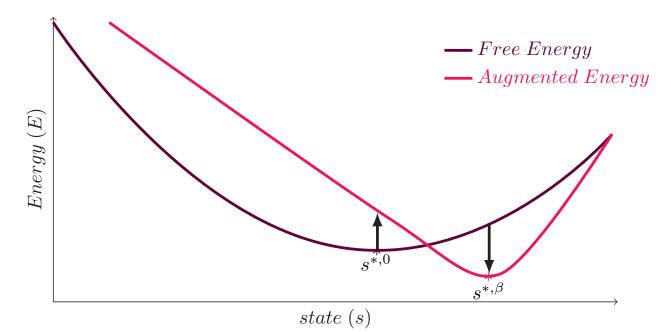

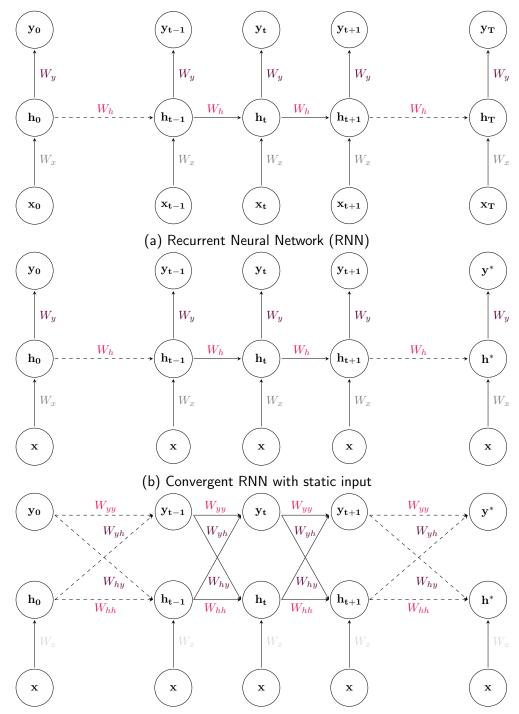

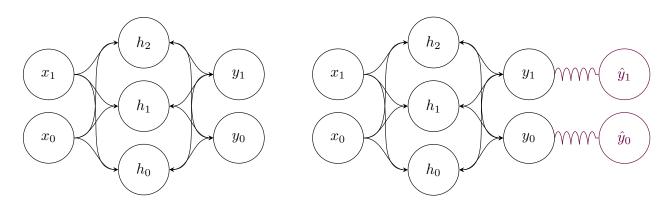

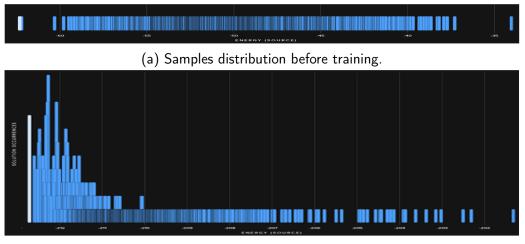

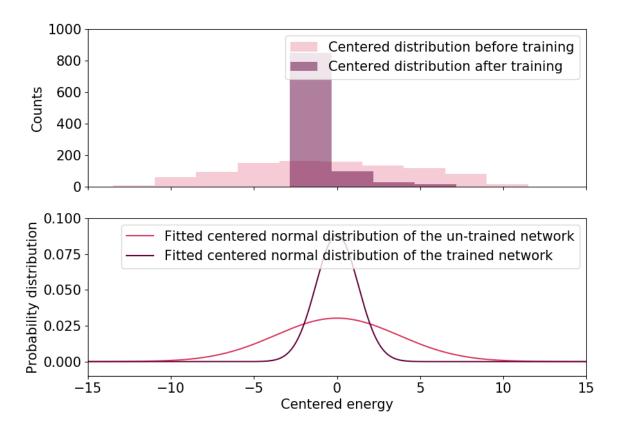

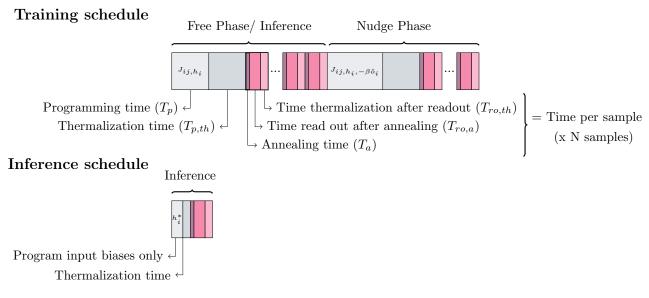

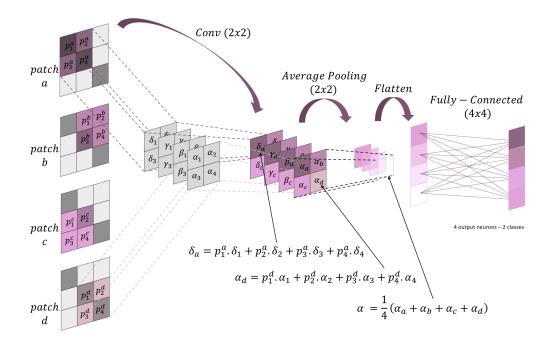

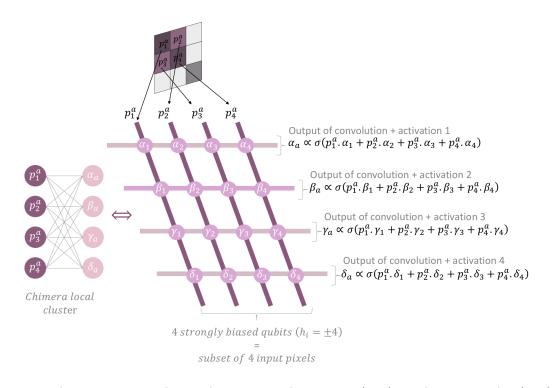

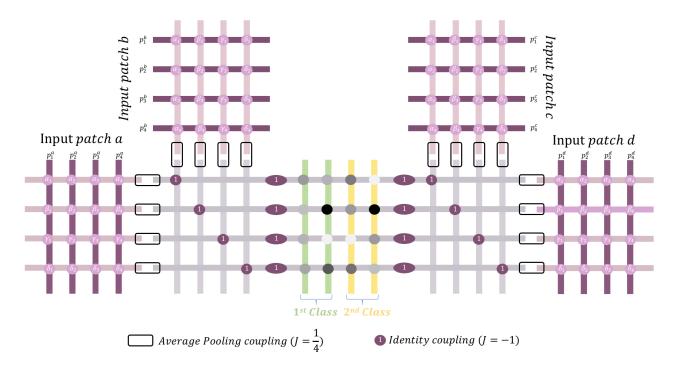

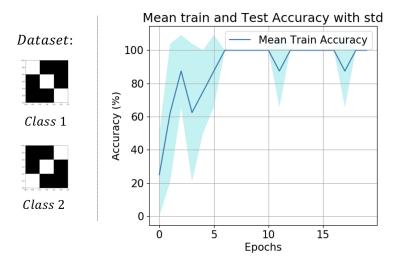

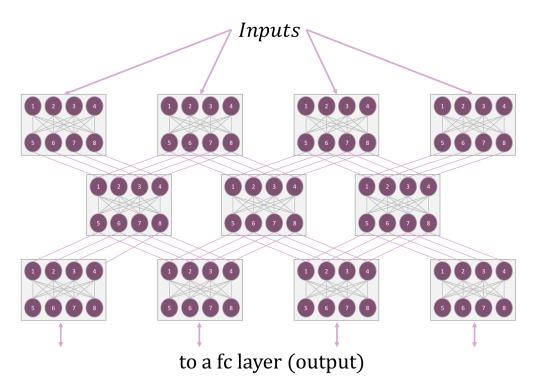

In the next section we will dig in the concept of learning in artificial neural networks that we have just introduced by detailing the backpropagation algorithm.