# Flot de conception pour circuits asynchrones : de la HLS à l'implémentation en FDSOI

Yoan Decoudu

## ► To cite this version:

Yoan Decoudu. Flot de conception pour circuits asynchrones : de la HLS à l'implémentation en FDSOI. Micro et nanotechnologies/Microélectronique. Université Grenoble Alpes [2020-..], 2022. Français. NNT : 2022GRALT076 . tel-03957110

HAL Id: tel-03957110

<https://theses.hal.science/tel-03957110>

Submitted on 26 Jan 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano-Électronique et Nano-Technologies (NENT)

Arrêtée ministériel : 25 mai 2016

Présentée par

**Yoan DECOUDU**

Thèse dirigée par **Laurent FESQUET**

et codirigée par **Katell MORIN-ALLORY**

préparée au sein du **Laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés (TIMA)**

dans l'**École Doctorale Électronique, Électrotechnique, Automatique et Traitement du Signal (EEATS)**

## **Flot de conception pour circuits asynchrones : de la HLS à l'implémentation en FDSOI**

Thèse soutenue publiquement le **23 septembre 2022**,

devant le jury composé de :

**Laurent FESQUET**

Maître de Conférences, Université Grenoble Alpes, Directeur de thèse

**Katell MORIN-ALLORY**

Maître de Conférences, Université Grenoble Alpes, Co-Directrice de thèse

**Habib MEHREZ**

Professeur des universités, Sorbonne Université, Président

**Giovanni DE MICHELI**

Professeur, École polytechnique fédérale de Lausanne, Rapporteur

**Arnaud VIRAZEL**

Professeur des universités, Université de Montpellier, Rapporteur

**Frédéric ROUSSEAU**

Professeur des universités, Université Grenoble Alpes, Examinateur

## Remerciements

Cette thèse a été une grande aventure, dont l'origine commence un peu par hasard au détour d'un projet en école. Je tiens à remercier tous ceux qui de près ou de loin m'ont aidé durant ce voyage passionnant !

Un grand merci à Laurent et Katell, pour m'avoir donné l'opportunité de découvrir l'asynchrone et de réaliser cette thèse. Merci à tous les deux pour m'avoir guidé, formé, poussé pendant ces 4 années intenses. Merci aussi pour les grandes discussions et débats qui ont ponctué cette thèse ! Cela aura été un plaisir de travailler avec vous.

Merci à tous les collègues de l'équipe CDSI pour l'accueil, l'ambiance, les pauses, les bars et les grandes discussions. Merci aux compagnons de route, Grégoire, Ricardo, Mohamed, Rodrigo, Olivier, Florent et à ceux de passage, Nils et Mehdi (et ceux que j'ai probablement oubliés). Et aussi merci aux collègues plus récents, Rosalie, Xavier, Marco, Damiano, Cristiano (et bon courage pour la suite !). Je n'oublie pas non plus les chercheurs, Sylvain (tu comptes quasiment comme un chercheur), Stéphane, Skandar et Martial, merci pour les conseils et les retours. Je tiens aussi à remercier les membres du CIME, notamment Abdelhamid, Mohamed et Robin, que j'ai souvent sollicité.

Merci également à mes amis, de Grenoble et d'ailleurs. Et notamment pour les copains de Bourgogne, qui m'ont vu disparaître de la circulation pendant quelques années et qui ne m'ont pas oublié pour autant.

Enfin, merci à ma famille qui m'a toujours soutenu dans tout mon parcours de vie. Vous m'avez soutenu dans les moments difficiles, changer les idées quand il fallait que je décroche. Donc papa, maman, Prunelle, Allan et Clovis, merci pour tout.

# Table des matières

|                                                                 |           |

|-----------------------------------------------------------------|-----------|

| Remerciements . . . . .                                         | i         |

| Table des matières . . . . .                                    | iii       |

| Table des figures . . . . .                                     | v         |

| Liste des tableaux . . . . .                                    | vii       |

| <b>Introduction</b>                                             | <b>1</b>  |

| <b>I Architecture asynchrone</b>                                | <b>5</b>  |

| <b>1 État de l'art</b>                                          | <b>7</b>  |

| 1.1 Introduction . . . . .                                      | 8         |

| 1.2 Principes des circuits asynchrones . . . . .                | 8         |

| 1.2.1 Protocole de communication . . . . .                      | 8         |

| 1.2.2 Classes des circuits asynchrones . . . . .                | 11        |

| 1.2.3 Avantages de l'asynchrone . . . . .                       | 14        |

| 1.3 Les circuits à données groupées . . . . .                   | 16        |

| 1.3.1 Modélisation des circuits asynchrones . . . . .           | 16        |

| 1.3.2 Méthodes de conception des circuits asynchrones . . . . . | 18        |

| 1.3.3 Vérification des contraintes temporelles . . . . .        | 21        |

| 1.4 Synthèse de haut niveau . . . . .                           | 24        |

| 1.4.1 Principe de la HLS synchrone . . . . .                    | 25        |

| 1.4.2 HLS asynchrone . . . . .                                  | 25        |

| 1.5 Conclusion . . . . .                                        | 27        |

| <b>2 Désynchronisation de circuits</b>                          | <b>29</b> |

| 2.1 Introduction . . . . .                                      | 30        |

| 2.2 Structure du circuit . . . . .                              | 30        |

| 2.2.1 Définition structurelle . . . . .                         | 31        |

| 2.2.2 Chemin de données . . . . .                               | 33        |

| 2.2.3 Chemin de contrôle . . . . .                              | 33        |

| 2.3 Méthode de désynchronisation . . . . .                      | 35        |

| 2.3.1 FSM asynchrone . . . . .                                  | 36        |

| 2.3.2 Preuve de correction . . . . .                            | 40        |

| 2.3.3 Contraintes temporelles . . . . .                         | 44        |

| 2.4 Application à Catapult HLS . . . . .                        | 46        |

| 2.4.1 Architecture des circuits . . . . .                       | 46        |

| 2.4.2 Génération des contraintes . . . . .                      | 47        |

|                                                          |             |

|----------------------------------------------------------|-------------|

| 2.5 Conclusion . . . . .                                 | 48          |

| <b>3 Évaluation de la méthode</b>                        | <b>51</b>   |

| 3.1 Introduction . . . . .                               | 52          |

| 3.2 Étude comparative avec les autres méthodes . . . . . | 52          |

| 3.2.1 Description du circuit . . . . .                   | 52          |

| 3.2.2 Résultats de la désynchronisation . . . . .        | 55          |

| 3.3 Application à la HLS . . . . .                       | 57          |

| 3.3.1 Architecture du prototype . . . . .                | 57          |

| 3.3.2 Résultats . . . . .                                | 59          |

| 3.4 Conclusion . . . . .                                 | 61          |

| <b>II Stratégie de polarisation de substrat</b>          | <b>63</b>   |

| <b>4 Technologie FDSOI</b>                               | <b>65</b>   |

| 4.1 Introduction . . . . .                               | 66          |

| 4.2 Limitations des technologies classiques . . . . .    | 66          |

| 4.3 Alternatives au Bulk CMOS . . . . .                  | 68          |

| 4.3.1 FinFET . . . . .                                   | 68          |

| 4.3.2 FDSOI . . . . .                                    | 68          |

| 4.4 Caractéristiques des technologies FDSOI . . . . .    | 69          |

| 4.4.1 Isolation du substrat . . . . .                    | 69          |

| 4.4.2 Polarisation du substrat . . . . .                 | 70          |

| 4.5 Méthodes de polarisation de substrat . . . . .       | 71          |

| 4.6 Conclusion . . . . .                                 | 72          |

| <b>5 Stratégie de polarisation de substrat</b>           | <b>75</b>   |

| 5.1 Introduction . . . . .                               | 76          |

| 5.2 Définition de la stratégie . . . . .                 | 76          |

| 5.2.1 Principe de la stratégie . . . . .                 | 78          |

| 5.2.2 Éstimation de l'efficacité . . . . .               | 81          |

| 5.3 Implémentation de notre stratégie . . . . .          | 83          |

| 5.4 Évaluation de la méthode . . . . .                   | 86          |

| 5.4.1 Simulations numériques . . . . .                   | 86          |

| 5.4.2 Conception d'un prototype . . . . .                | 88          |

| 5.5 Conclusion . . . . .                                 | 90          |

| <b>Conclusion</b>                                        | <b>93</b>   |

| <b>Bibliographie</b>                                     | <b>I</b>    |

| <b>Publications de l'auteur</b>                          | <b>XI</b>   |

| <b>Liste des acronymes</b>                               | <b>XIII</b> |

| <b>A Prototype ASIC 65 nm</b>                            | <b>XV</b>   |

# Table des figures

|      |                                                                                           |    |

|------|-------------------------------------------------------------------------------------------|----|

| 1    | Flot de conception développé dans cette thèse. . . . .                                    | 3  |

| 1.1  | Principe de communication entre deux systèmes. . . . .                                    | 9  |

| 1.2  | Architecture d'un circuit synchrone. . . . .                                              | 9  |

| 1.3  | Principe de communication à données groupées. . . . .                                     | 9  |

| 1.4  | Protocole de communication (a) 4 phases et (b) 2 phases. . . . .                          | 10 |

| 1.5  | Principe de communication avec un encodage double rail. . . . .                           | 10 |

| 1.6  | Symbol et table de vérité d'une porte de Muller. . . . .                                  | 11 |

| 1.7  | Classification des types de circuits asynchrones (adaptée de [6]) . . . . .               | 11 |

| 1.8  | Fourche isochronique dans les circuits QDI. . . . .                                       | 12 |

| 1.9  | Architecture d'une machine Burst-Mode. . . . .                                            | 13 |

| 1.10 | Architecture d'un circuit à données groupées. . . . .                                     | 14 |

| 1.11 | Exemple d'un STG pour le protocole WCHB. . . . .                                          | 17 |

| 1.12 | Composants de synchronisation [20] (a) totale et (b) sélective. . . . .                   | 17 |

| 1.13 | Principe des protocoles 4 phases précoces et tardifs. . . . .                             | 18 |

| 1.14 | Classification des méthodes de désynchronisation. . . . .                                 | 21 |

| 1.15 | Contraintes temporelles min/max dans un circuit à données groupées. . . . .               | 23 |

| 1.16 | Méthode LCS dans un circuit à données groupées. . . . .                                   | 24 |

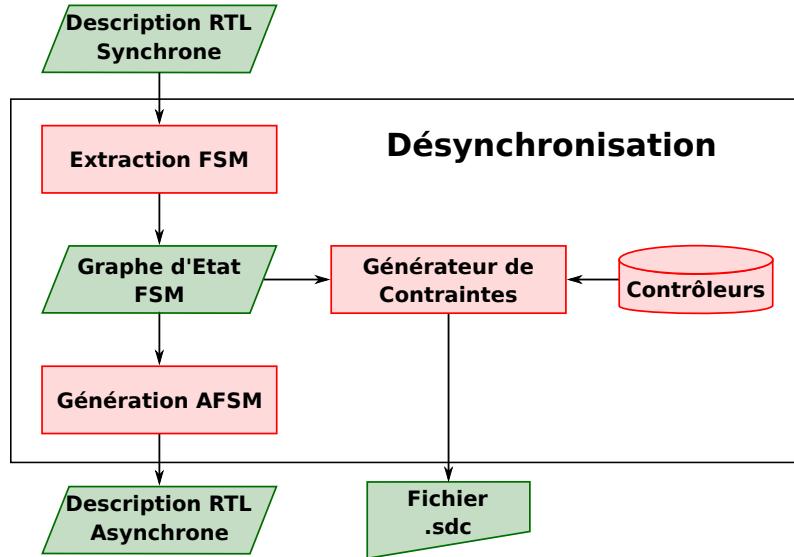

| 2.1  | Flot de désynchronisation. . . . .                                                        | 31 |

| 2.2  | Architecture d'un circuit synchrone. . . . .                                              | 31 |

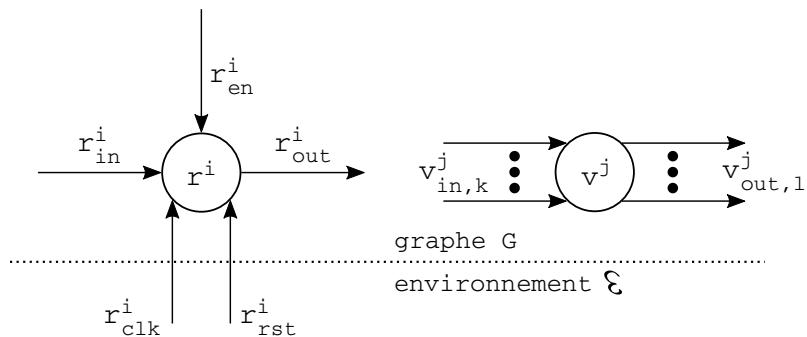

| 2.3  | Définition des sommets $r$ et $v$ d'un graphe orienté $G$ . . . . .                       | 32 |

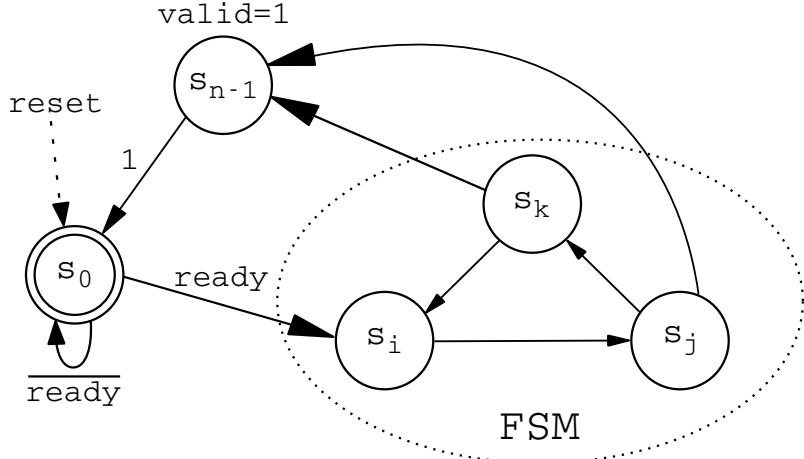

| 2.4  | Exemple d'une FSM issue d'une synthèse HLS. . . . .                                       | 34 |

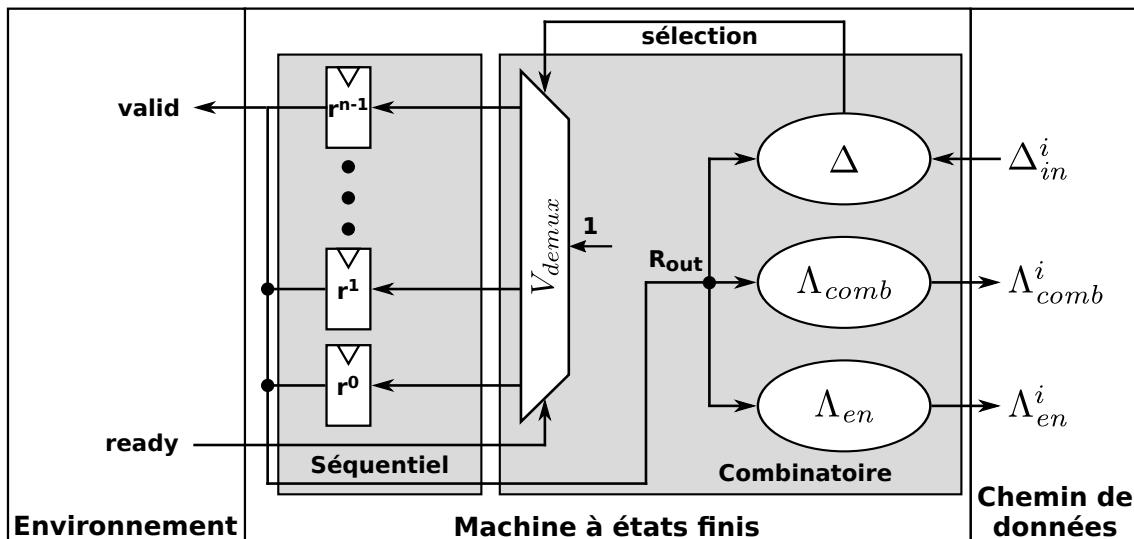

| 2.5  | Implémentation d'une FSM synchrone avec un encodage one-hot. . . . .                      | 35 |

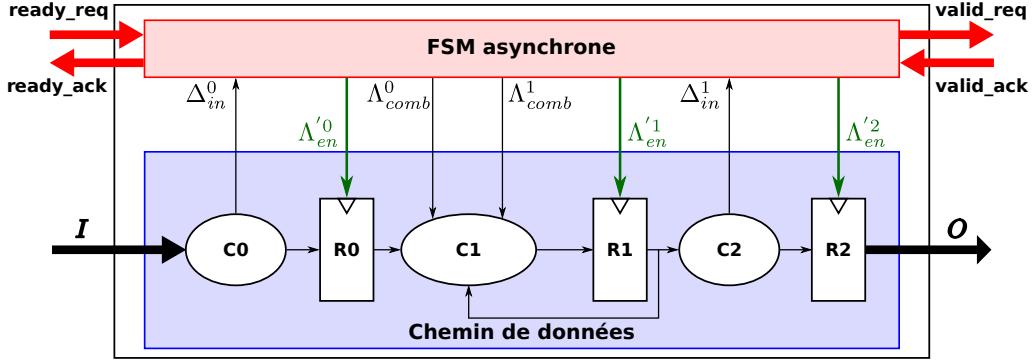

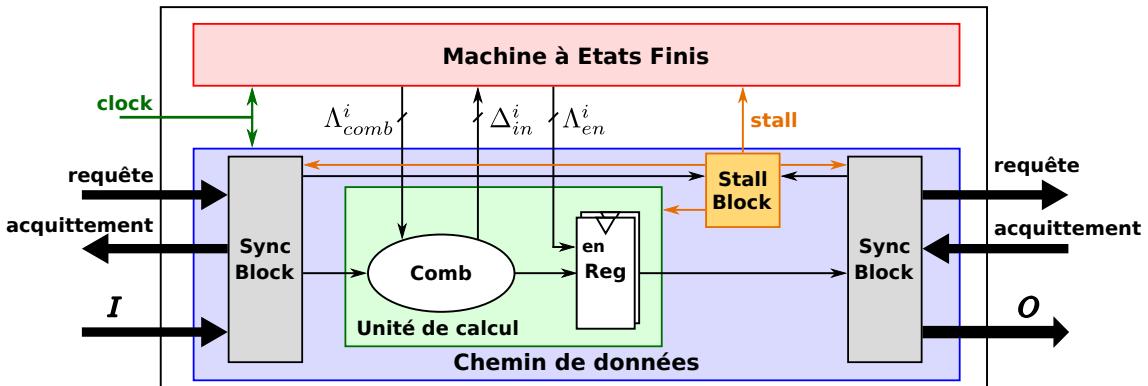

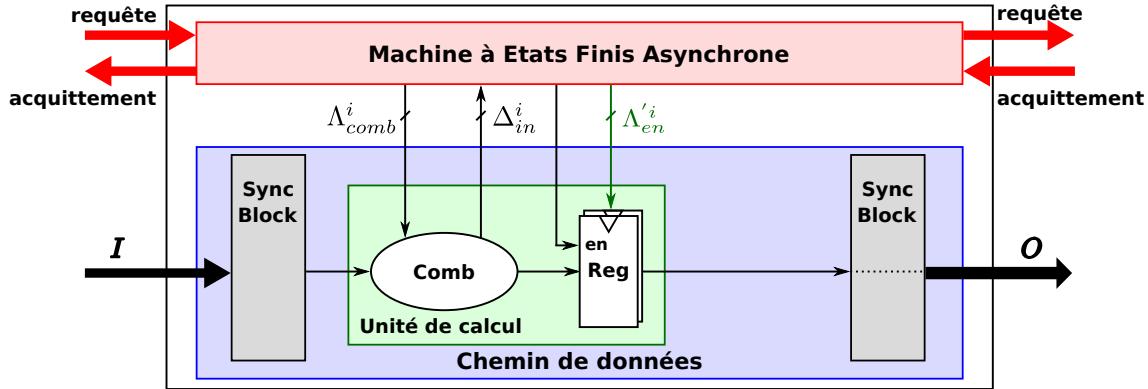

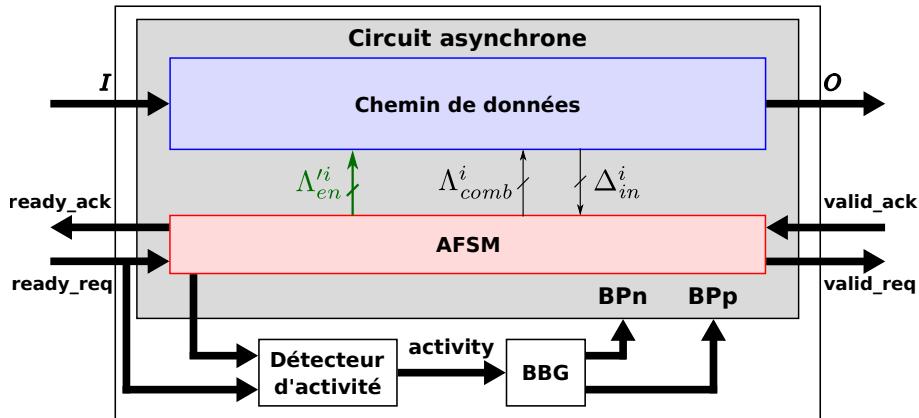

| 2.6  | Circuit désynchronisé avec son chemin de données et une AFSM. . . . .                     | 36 |

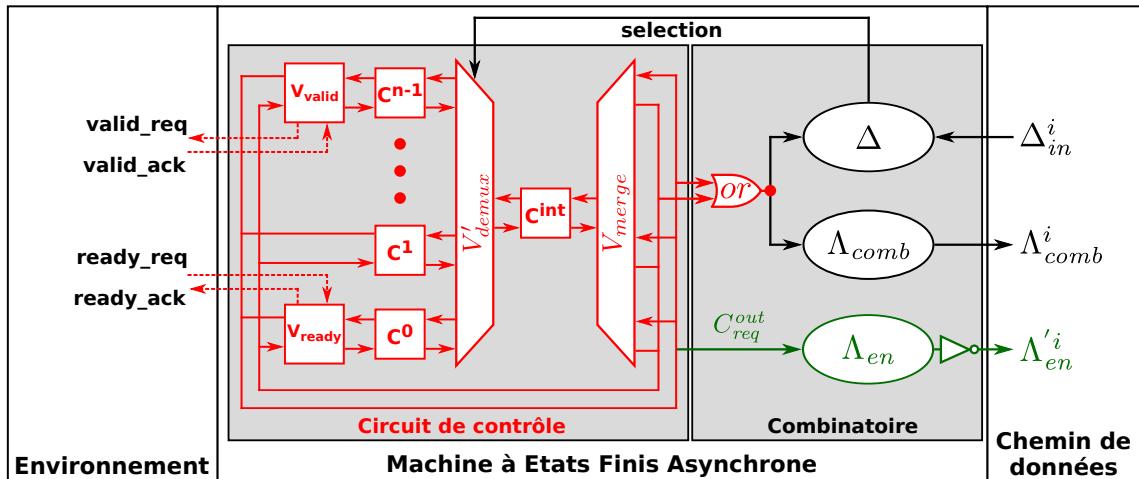

| 2.7  | Implémentation d'une FSM désynchronisée. . . . .                                          | 36 |

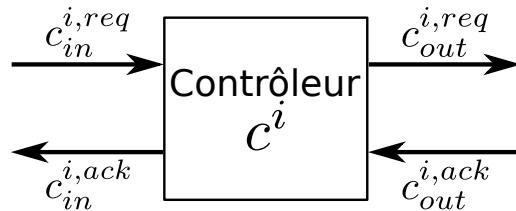

| 2.8  | Modèle de contrôleur. . . . .                                                             | 37 |

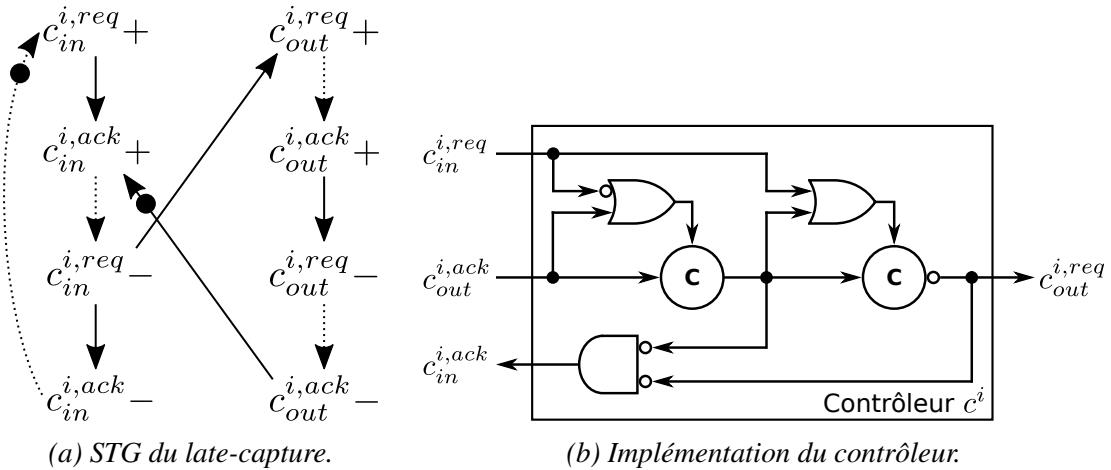

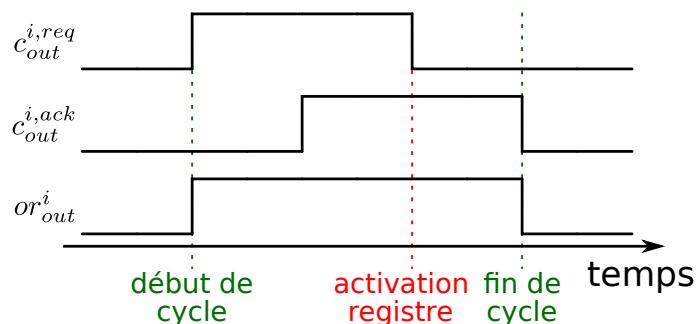

| 2.9  | Protocole <i>late-capture</i> . . . . .                                                   | 37 |

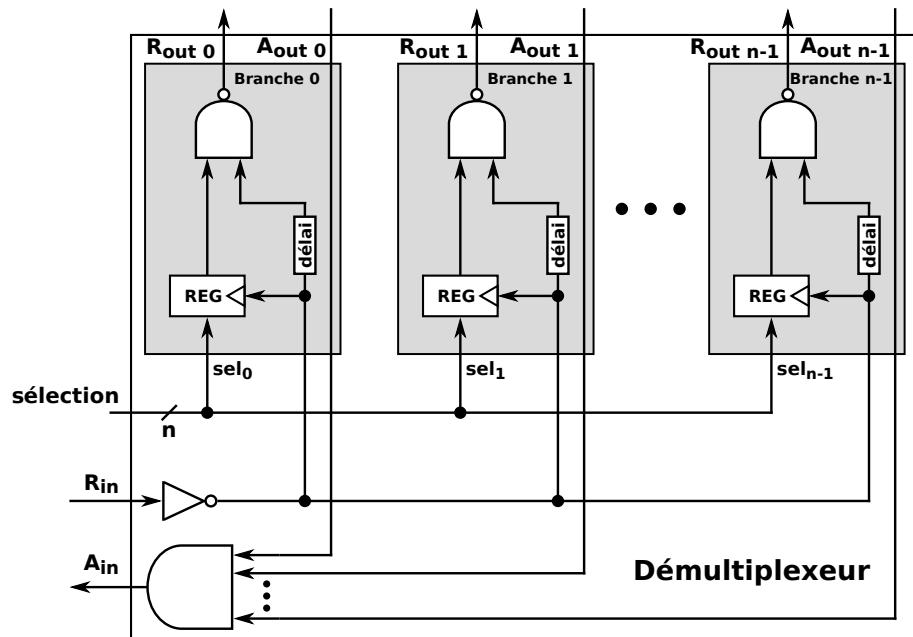

| 2.10 | Architecture d'un démultiplexeur. . . . .                                                 | 38 |

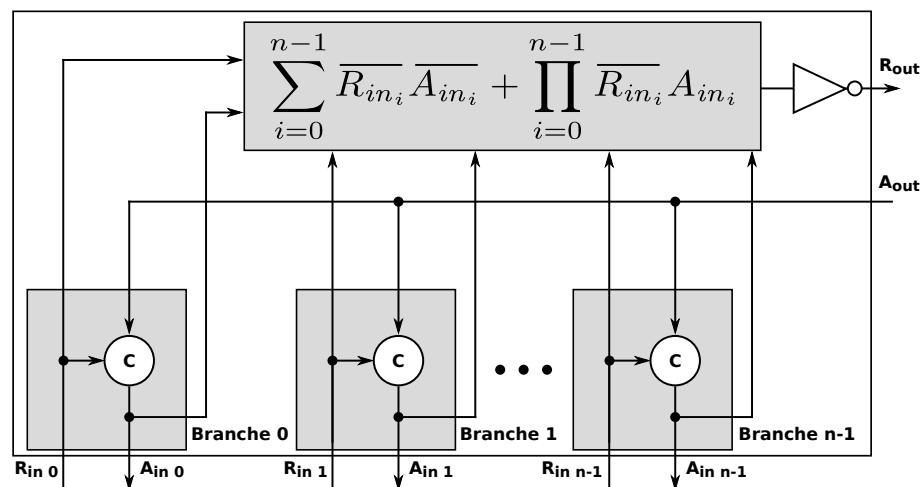

| 2.11 | Architecture d'un merge. . . . .                                                          | 38 |

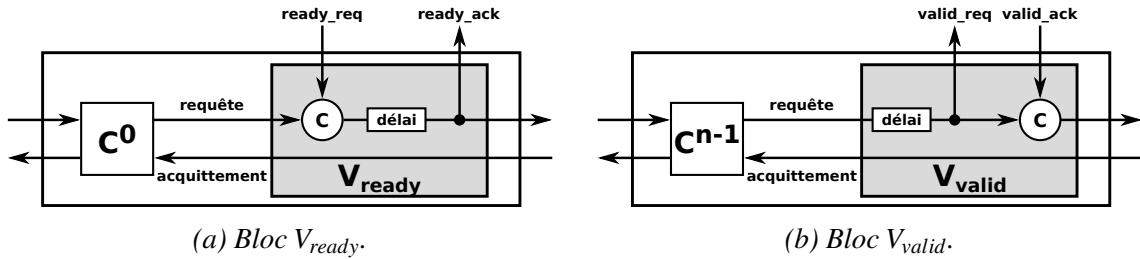

| 2.12 | Implémentation des blocs $V_{ready}$ et $V_{valid}$ . . . . .                             | 39 |

| 2.13 | Génération d'un signal $or_{out}^i$ . . . . .                                             | 39 |

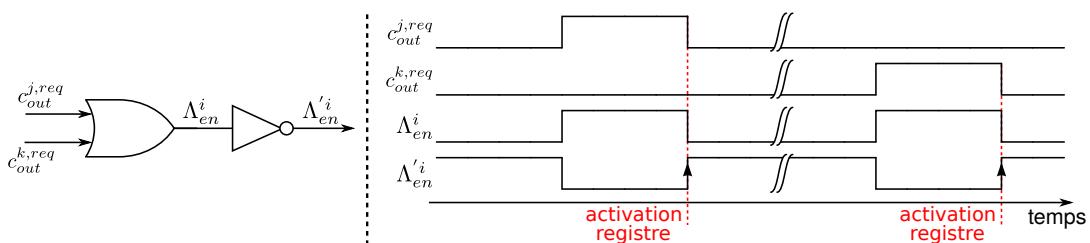

| 2.14 | Exemple d'un bloc $\Lambda'_{en}$ avec le chronogramme associé. . . . .                   | 40 |

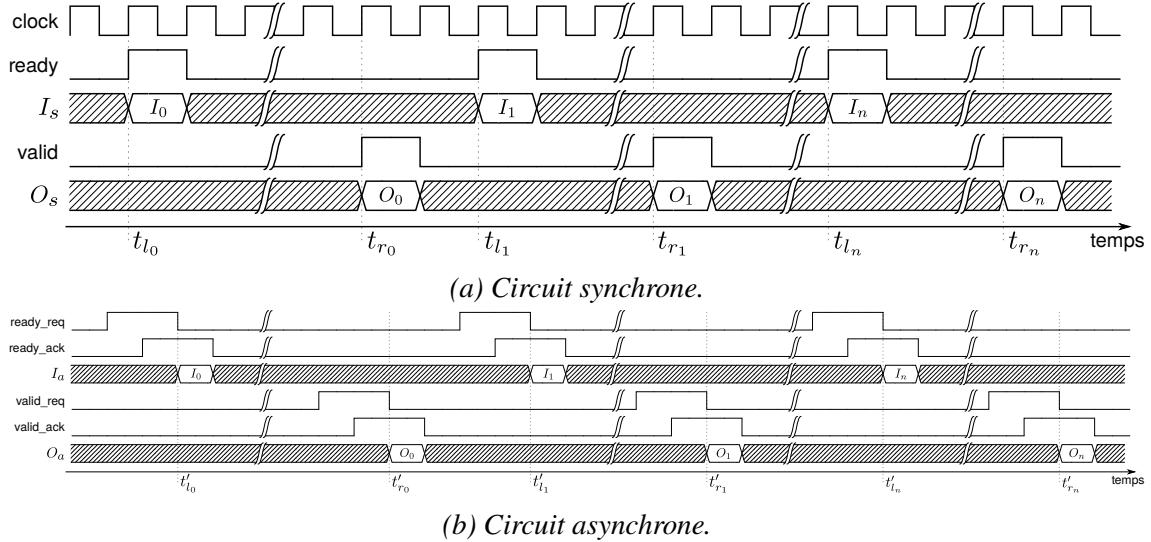

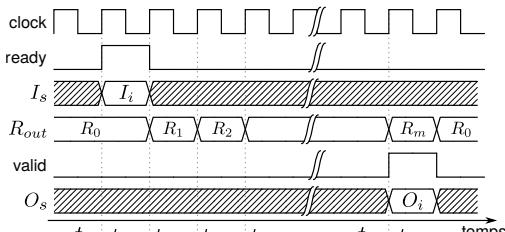

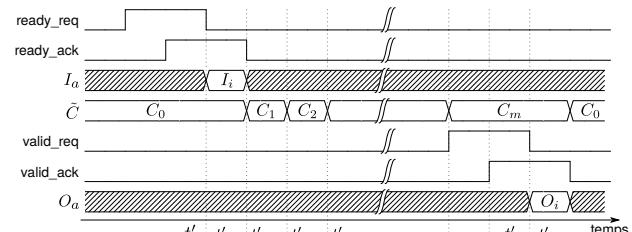

| 2.15 | Chronogrammes des circuits (a) synchrone et (b) asynchrone. . . . .                       | 41 |

| 2.16 | Chronogrammes des séquences d'états des circuits (a) synchrone et (b) asynchrone. . . . . | 42 |

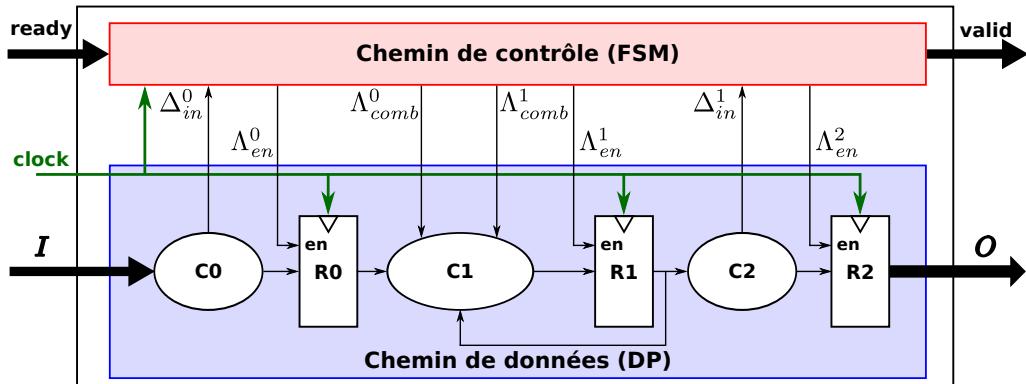

| 2.17 | Architecture d'un circuit synchrone produit par Catapult. . . . .                         | 46 |

| 2.18 | Architecture du circuit désynchronisé. . . . .                                            | 47 |

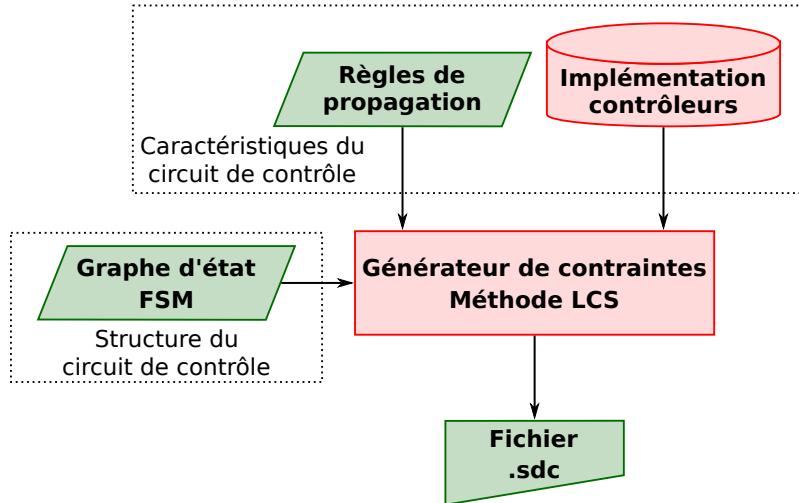

| 2.19 | Générateur de contraintes temporelles. . . . .                                            | 48 |

|      |                                                                                                                                           |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

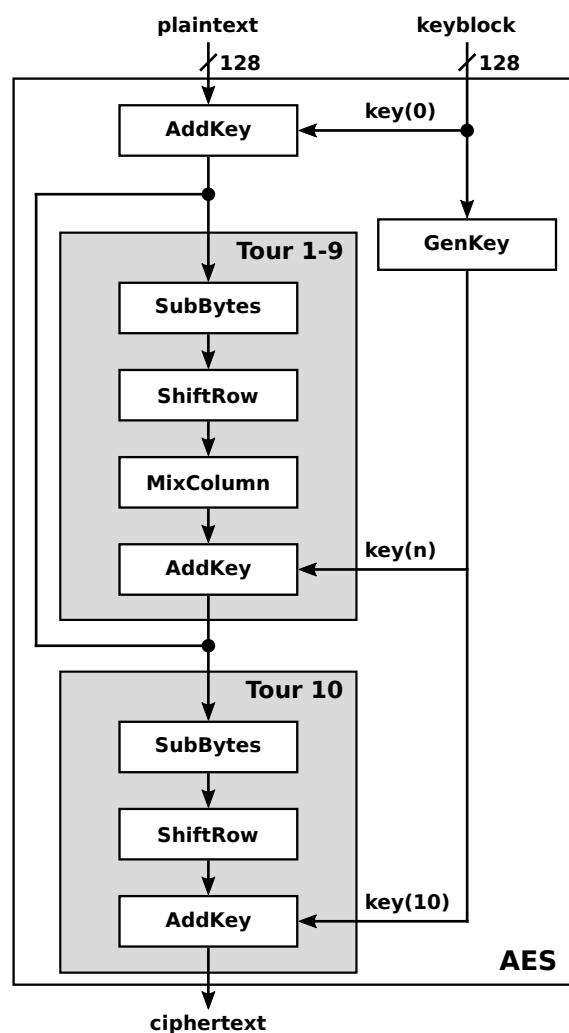

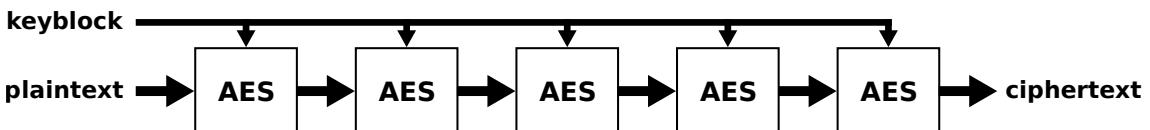

| 3.1  | Algorithme de l'AES avec une clé de 128 bits. . . . .                                                                                     | 53  |

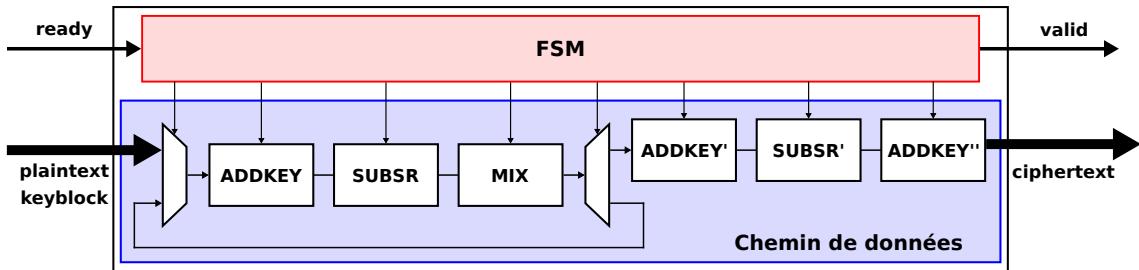

| 3.2  | Schéma bloc de l'architecture du circuit. . . . .                                                                                         | 54  |

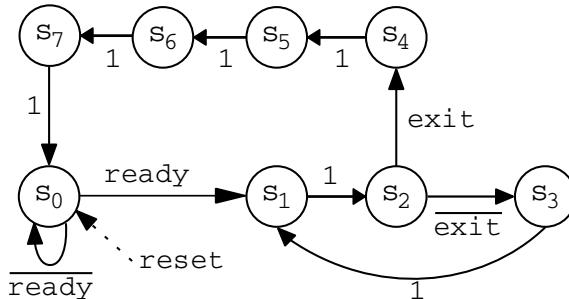

| 3.3  | FSM du circuit AES. . . . .                                                                                                               | 54  |

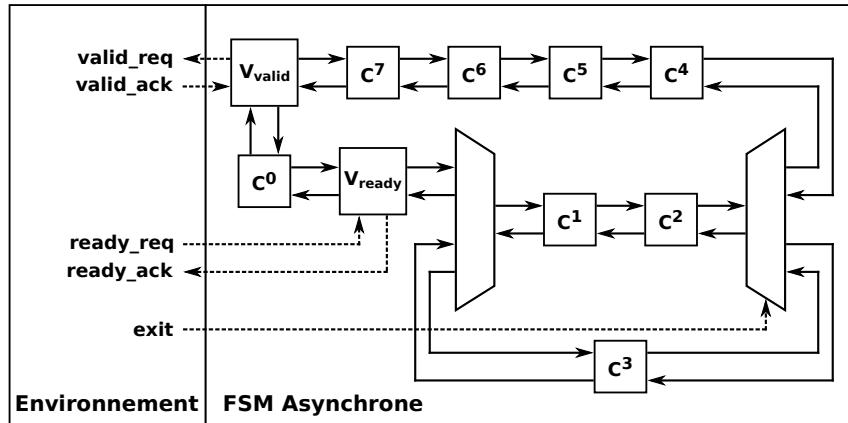

| 3.4  | AFSM du circuit désynchronisé. . . . .                                                                                                    | 55  |

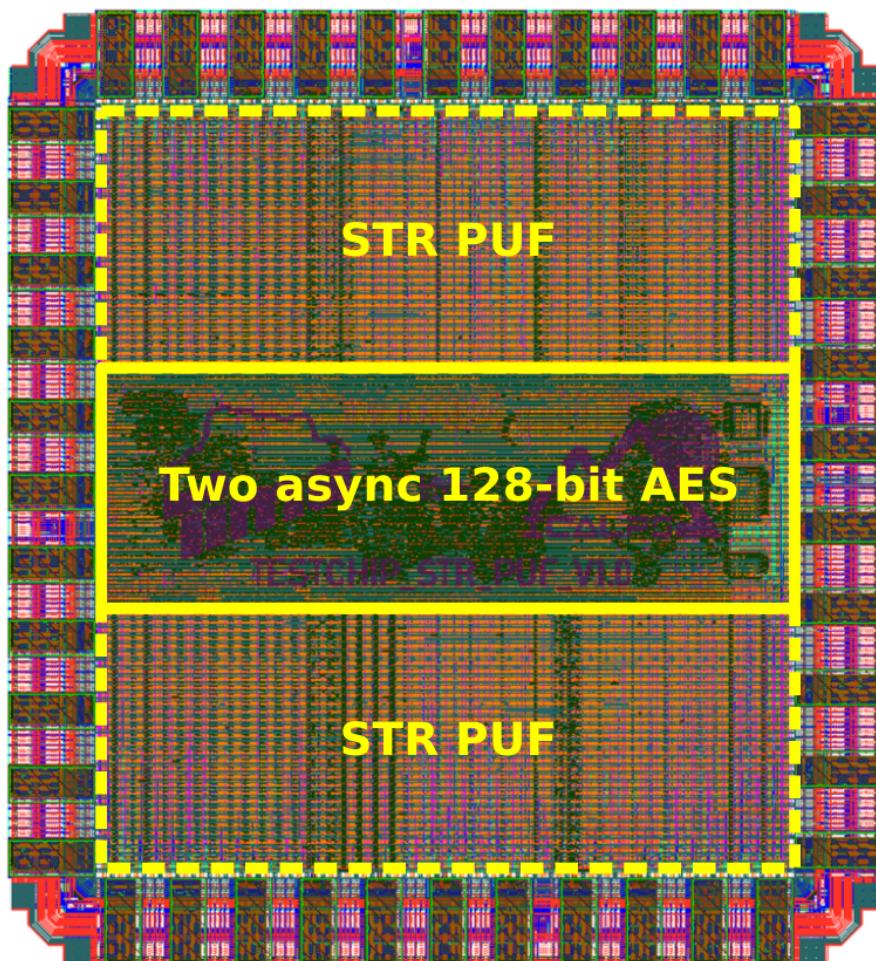

| 3.5  | Layout du prototype en 65 nm. . . . .                                                                                                     | 58  |

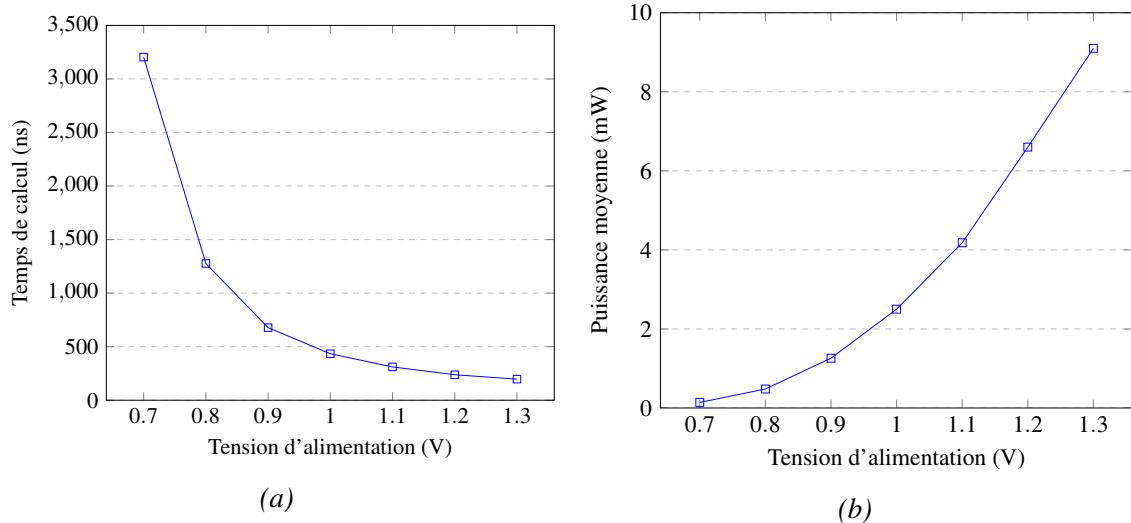

| 3.6  | Caractérisation du prototype suivant la tension d'alimentation pour (a) le temps de calcul et (b) la puissance moyenne consommée. . . . . | 60  |

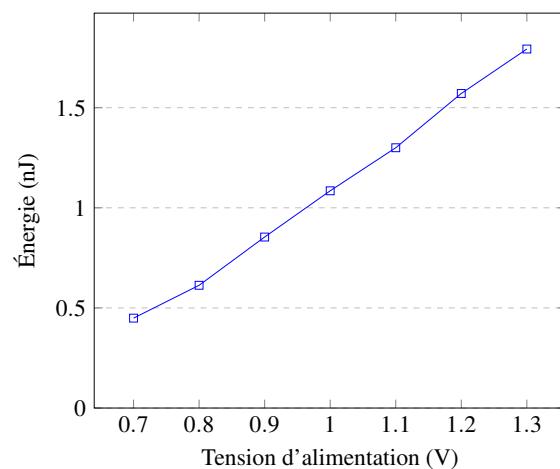

| 3.7  | Mesure de la consommation d'énergie suivant la tension d'alimentation. .                                                                  | 60  |

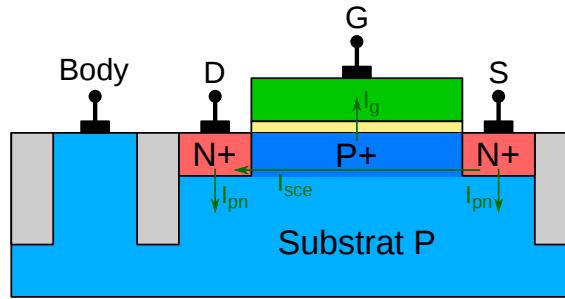

| 4.1  | Schéma d'un transistor NMOS en technologie bulk CMOS. . . . .                                                                             | 67  |

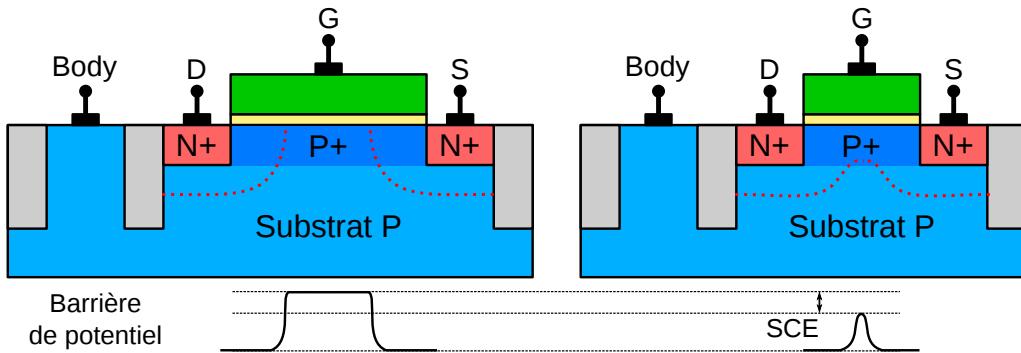

| 4.2  | Apparition des SCE avec la diminution de la taille du canal. . . . .                                                                      | 67  |

| 4.3  | Schéma d'un transistor FinFET. . . . .                                                                                                    | 68  |

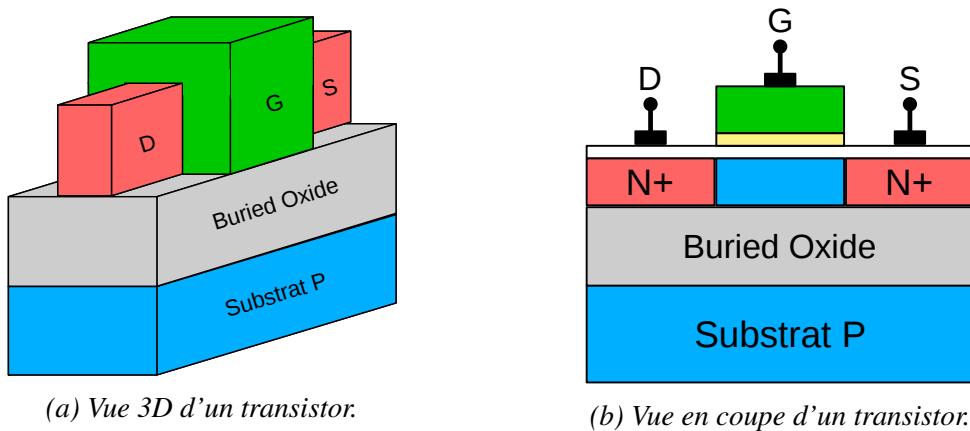

| 4.4  | Transistors NMOS en technologie bulk CMOS (a) et FDSOI (b). . . . .                                                                       | 69  |

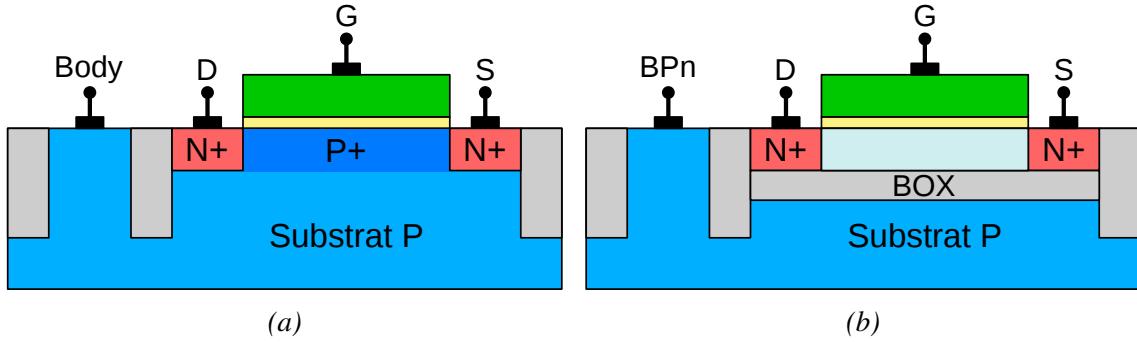

| 4.5  | Schéma des transistors NMOS et PMOS en technologie FDSOI. . . . .                                                                         | 69  |

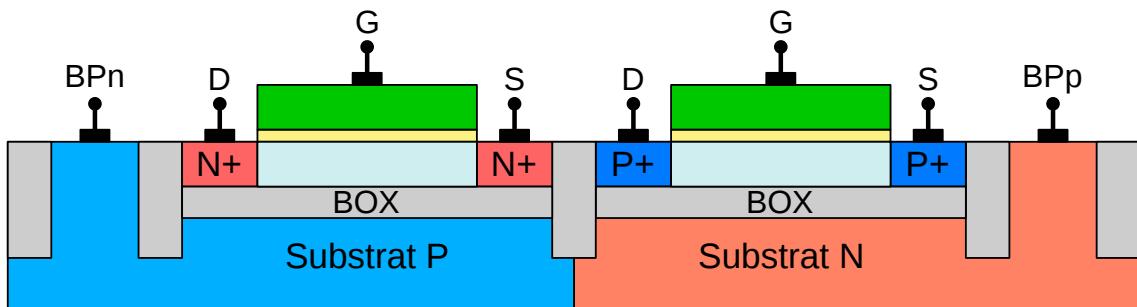

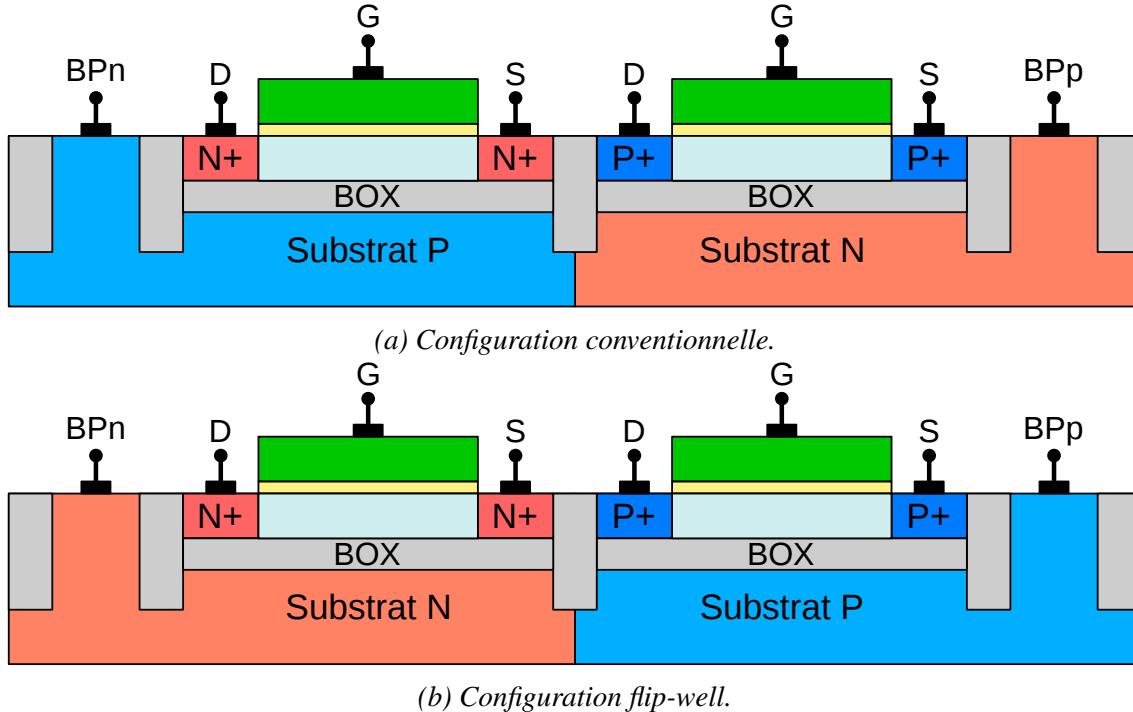

| 4.6  | Configurations possibles pour des transistors FDSOI. . . . .                                                                              | 71  |

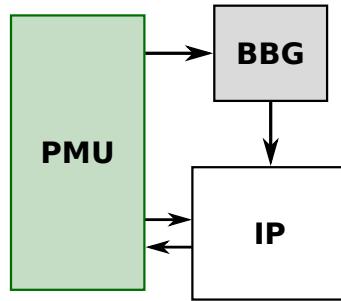

| 4.7  | Architecture d'un système utilisant une polarisation de substrat dynamique. .                                                             | 72  |

| 4.8  | Principe de la méthode de polarisation de substrat pour un circuit linéaire. .                                                            | 72  |

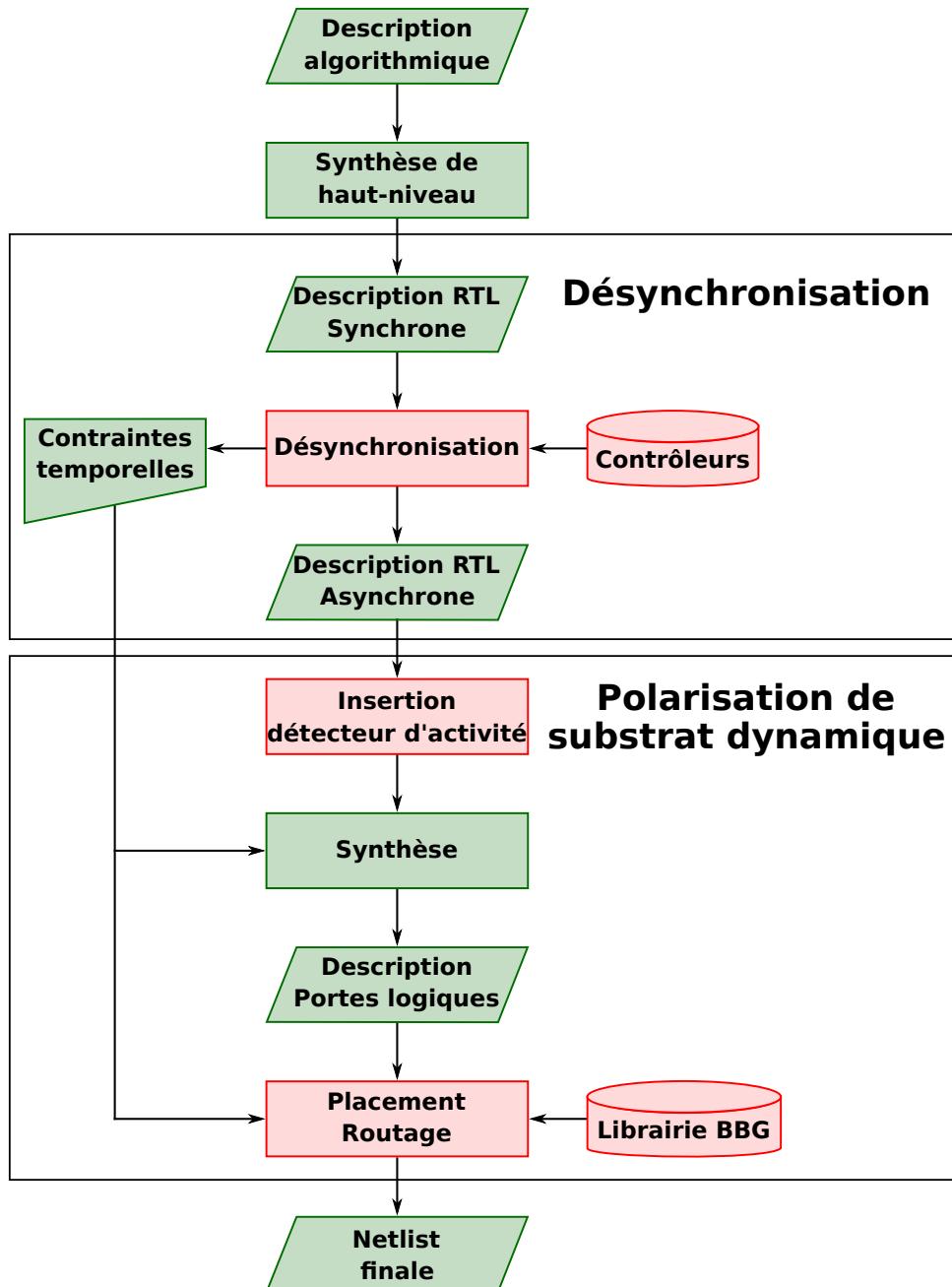

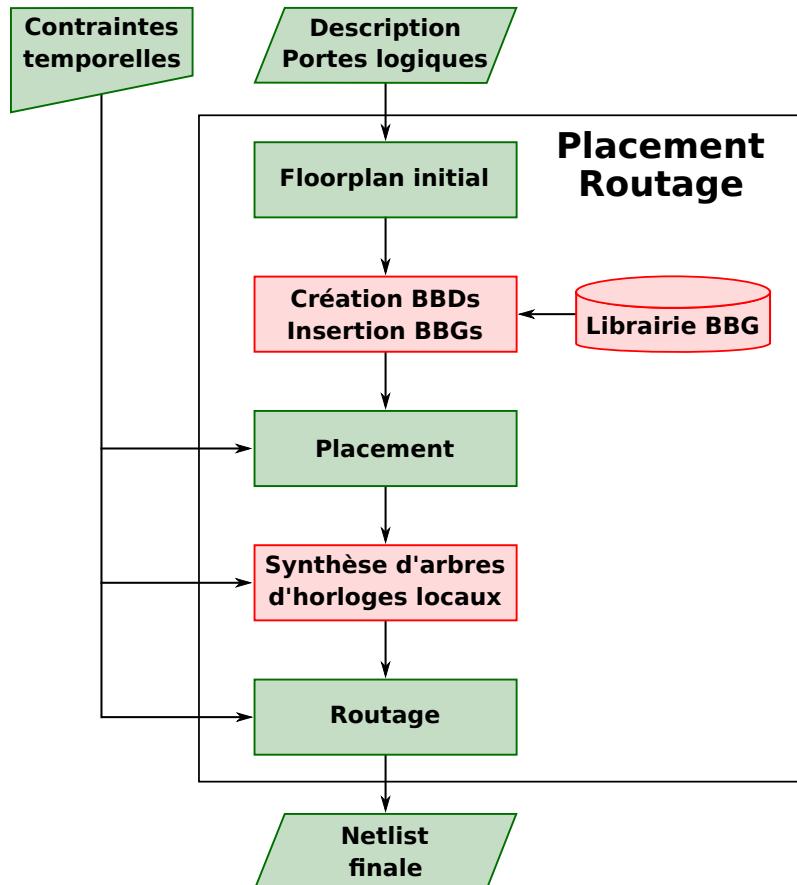

| 5.1  | Flot implémentant la polarisation de substrat dynamique. . . . .                                                                          | 77  |

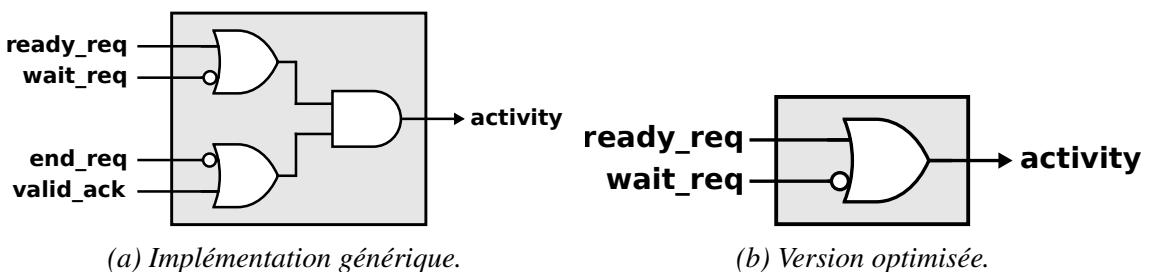

| 5.2  | Principe de la stratégie de polarisation dynamique du substrat. . . . .                                                                   | 79  |

| 5.3  | Implémentation du détecteur d'activité. . . . .                                                                                           | 79  |

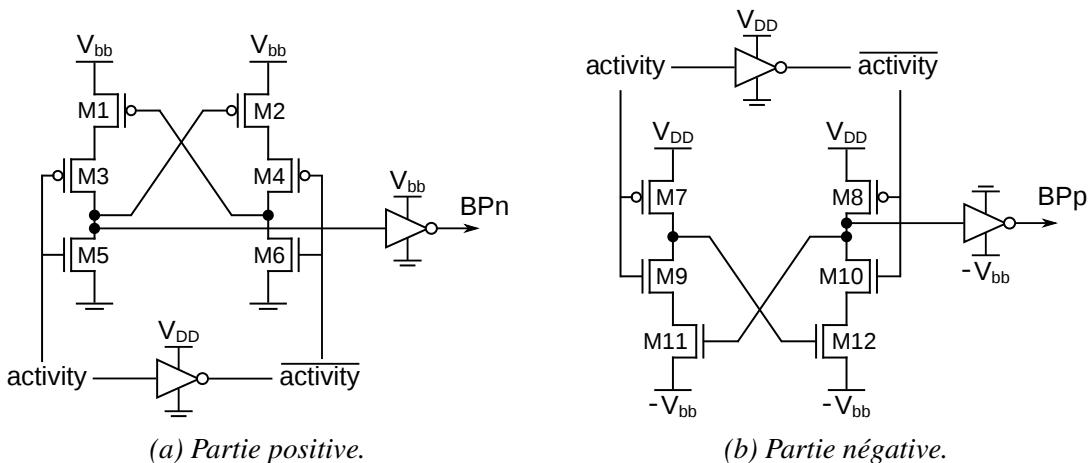

| 5.4  | Architecture d'un BBG. . . . .                                                                                                            | 80  |

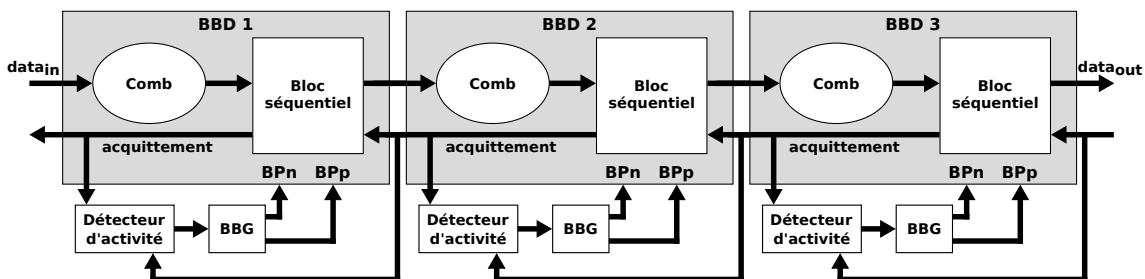

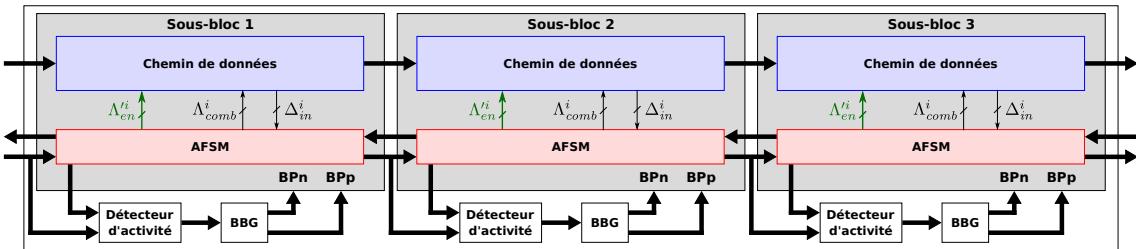

| 5.5  | Exemple d'un circuit avec trois sous-blocs. . . . .                                                                                       | 81  |

| 5.6  | Exemple d'un circuit avec trois sous-blocs. . . . .                                                                                       | 81  |

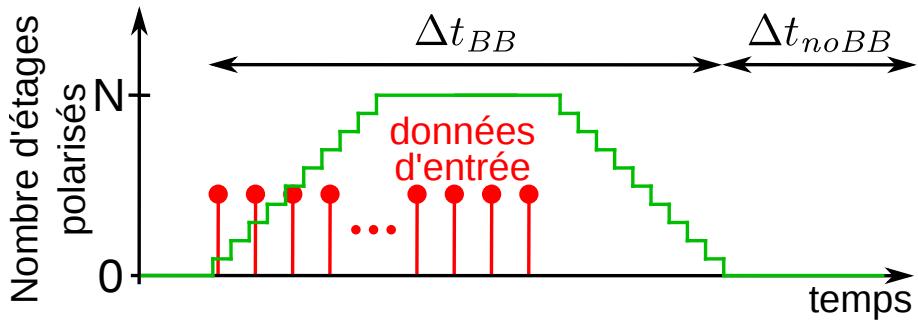

| 5.7  | Variation du nombre de BBDs actifs dans le système (adapté de [114]). . .                                                                 | 82  |

| 5.8  | Flot implémentant la polarisation de substrat dynamique. . . . .                                                                          | 84  |

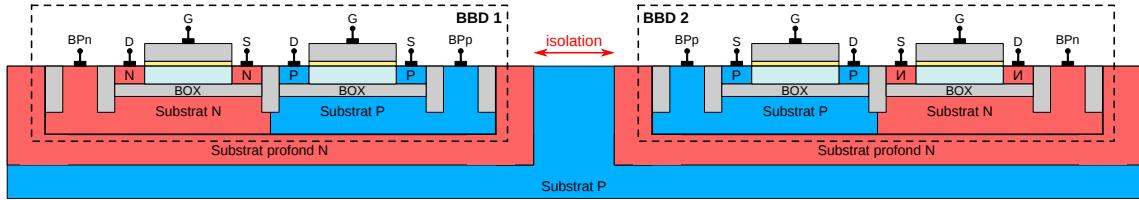

| 5.9  | Vue en coupe de l'isolation de deux BBDs. . . . .                                                                                         | 85  |

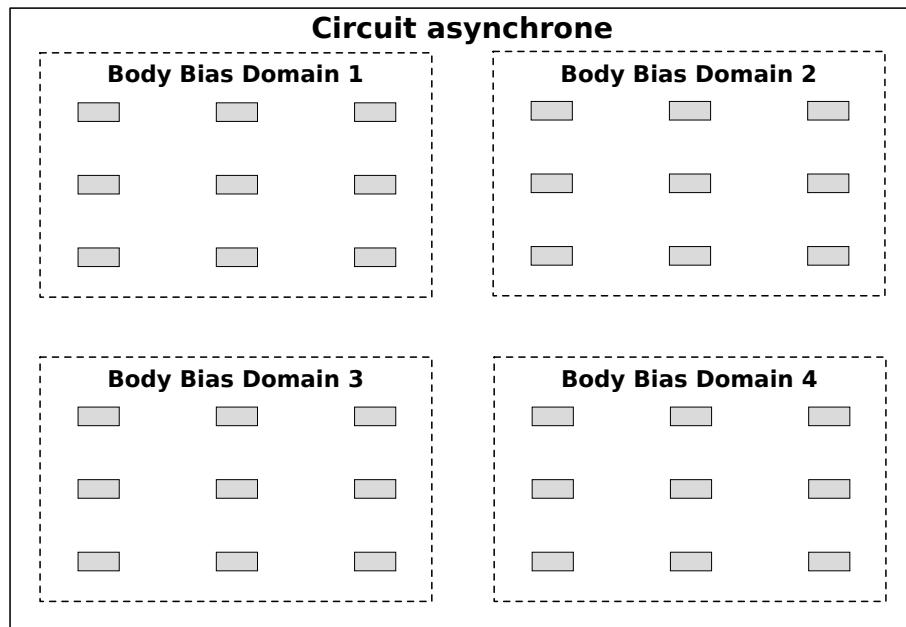

| 5.10 | Partitionnement des BBDs lors de l'implémentation physique d'un circuit. .                                                                | 85  |

| 5.11 | Circuit linéaire avec cinq AES. . . . .                                                                                                   | 86  |

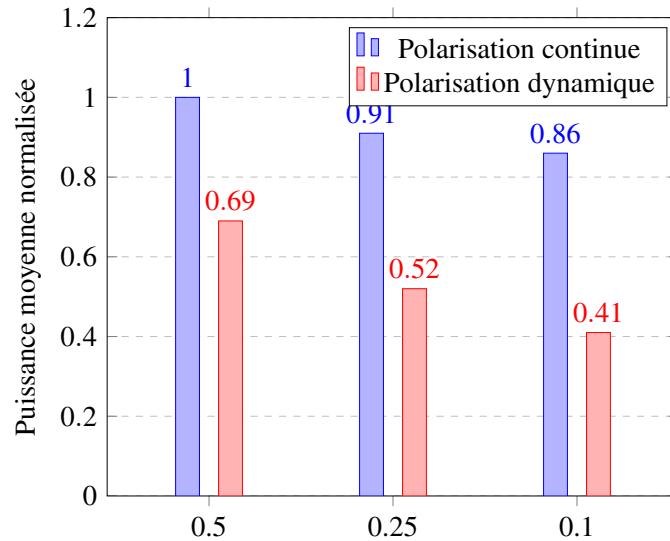

| 5.12 | Puissance moyenne normalisée en fonction du taux d'activité. . . . .                                                                      | 88  |

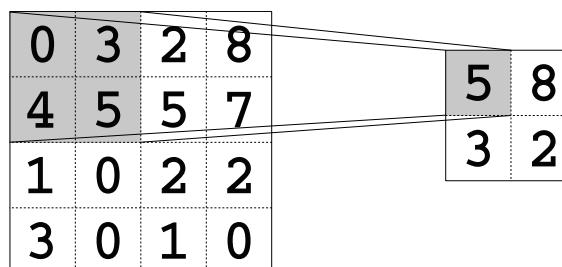

| 5.13 | Exemple d'une couche de <i>max pooling</i> . . . . .                                                                                      | 89  |

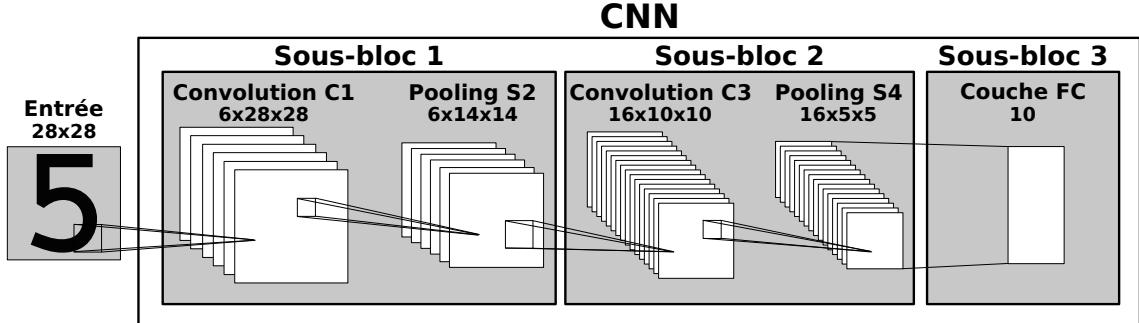

| 5.14 | Architecture du CNN. . . . .                                                                                                              | 90  |

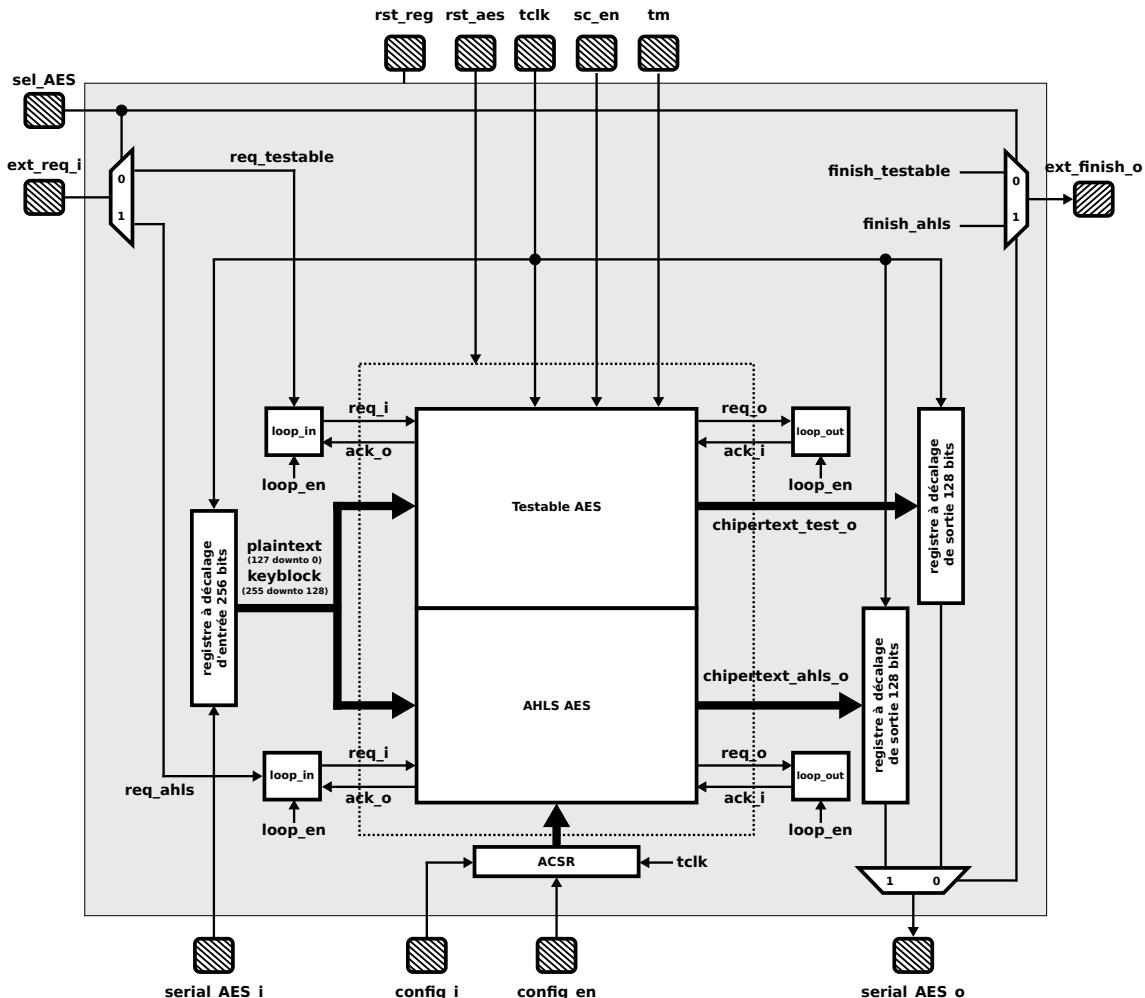

| A.1  | Architecture des circuits AES asynchrones au sein du prototype. . . . .                                                                   | XVI |

# Liste des tableaux

|     |                                                                                             |      |

|-----|---------------------------------------------------------------------------------------------|------|

| 2.1 | Contraintes temporelles sur les registres (signaux $\Lambda_{en}^i$ ) . . . . .             | 45   |

| 2.2 | Contraintes temporelles sur la logique combinatoire (signaux $\Lambda_{comb}^i$ ) . . . . . | 45   |

| 3.1 | Résultat en surface et impact de la désynchronisation . . . . .                             | 55   |

| 3.2 | Caractéristiques des circuits synchrone et désynchronisés . . . . .                         | 56   |

| 3.3 | Simulation du temps de calcul et consommation du prototype . . . . .                        | 59   |

| 5.1 | Impact de la désynchronisation sur l'AES . . . . .                                          | 87   |

| A.1 | Pins d'entrées et sorties de la partie AES du prototype . . . . .                           | XVII |

# Introduction

## Contexte et motivations

Durant ces deux dernières décennies, notre société a vu un nombre de plus en plus important de systèmes électroniques apparaître. La dernière manifestation de cette tendance est l'émergence de l'Internet des Objets, ou *Internet of Things* (IoT). Celui-ci est surtout composé de systèmes autonomes fonctionnant avec ou sans batterie. En outre, la demande globale en énergie électrique ne faisant que croître, il devient nécessaire y compris pour les équipements électroniques de devenir plus efficaces en énergie. Cette nécessité va bien au-delà des besoins de l'IoT. Par exemple, l'amélioration de l'efficacité énergétique des processeurs utilisés dans les *data centers* est un sujet de recherche d'actualité. Par conséquent, l'industrie microélectronique s'est emparée de ce sujet et travaille intensivement à la réduction de la consommation de ces circuits intégrés. La réduction de la consommation était autrefois surtout apportée par la réduction de la taille des transistors, qui réduisait de manière quadratique leur consommation [1]. Mais, avec les noeuds technologiques récents pour lesquels la tension ne diminue plus, le gain en efficacité énergétique n'existe plus et l'on observe une densité de puissance qui augmente. Ainsi, un grand nombre de méthodes ont été mises en place pour réduire la consommation comme le changement dynamique de la tension d'alimentation (le *Dynamic Voltage Scaling* ou DVS), sa désactivation ou bien la polarisation du substrat dans des technologies comme le *Fully Depleted Silicon on Insulator* (FDSOI).

Aujourd'hui, la majorité des circuits intégrés sont en grande partie sur des circuits numériques synchrones. Ceux-ci possèdent un signal global, l'horloge, pour synchroniser l'ensemble du circuit. Pour fonctionner correctement, ce moment d'activation doit être exactement le même dans tout le circuit et être à une fréquence précise. L'activation globale du circuit crée une consommation inutile lorsque le circuit ou une partie de celui-ci n'est pas utilisé. Cette consommation peut alors être supprimée par des moyens additionnels comme le *clock gating* ou le DVS. De plus, les variations des procédés de fabrication dans les noeuds technologiques récents nécessitent d'ajouter des marges de sécurité vis-à-vis du signal d'horloge pour assurer un bon fonctionnement. Ces marges limitent les performances des circuits, que ce soit en vitesse ou en consommation. Dans ce contexte, il est indispensable de développer de nouvelles méthodes pour la gestion de la consommation et de se tourner vers des architectures alternatives pour les circuits intégrés numériques.

Une solution déjà expérimentée dans le milieu de la recherche et dans quelques entreprises est la logique asynchrone. Les circuits asynchrones, contrairement à leurs homologues synchrones, utilisent une synchronisation locale pour fonctionner. Sans la contrainte d'un signal global d'horloge, il est possible de concevoir des circuits avec une plus grande liberté. Ainsi, une grande variété d'architectures asynchrones a été développée au cours du temps. Les circuits asynchrones sont connus pour présenter de nombreux avantages. En

effet, toute consommation dynamique superflue est supprimée, ils sont plus robustes, ont un rayonnement électromagnétique plus faible, sont généralement plus rapides et offrent un vrai potentiel pour la sécurité matérielle. Ils sont donc de parfaits candidats pour les problématiques actuelles de l'industrie microélectronique. Les recherches sur la logique asynchrone ont débuté dès les années 50. Dans les années 80 et 90, des laboratoires de recherche ont commencé à concevoir des processeurs asynchrones dont le premier en 1989 par l'équipe du Professeur Alain Martin à Caltech, suivi par le processeur AMULET de l'université de Manchester et un MISP R3000 asynchrone à Caltech. Les années 2000 ont vu le premier processeur asynchrone européen, ASPRO, conçu au laboratoire TIMA, ainsi que les microcontrôleurs asynchrones MICA (TIMA) et le 8051 asynchrone de la société Philips Semiconductor. Enfin, nous avons assisté à l'éclosion d'entreprises spécialisées dans le domaine de la conception de circuits asynchrones. Handshake Solutions et Theseus Logic ont offert des solutions pour la synthèse des circuits asynchrones. Tiempo se concentre sur des circuits asynchrones robustes et sécurisés. Achronix a développé les premières FPGA très rapides et asynchrones. Pour sa part, ChronosTech propose des systèmes de réseaux sur puce, ou *Network-on-Chip*. Plus récemment, IBM et Intel ont respectivement conçu TrueNorth [2] et Loihi [3], des réseaux de neurones à impulsions asynchrones. Les circuits asynchrones ne sont donc plus une approche inconnue.

Malgré les avantages cités et les avancées de la recherche, les circuits asynchrones n'ont pas réussi à s'implanter durablement et largement dans l'industrie. Ceci peut s'expliquer par plusieurs raisons. D'une part, l'industrie a mis en place un environnement complet d'outils de Conception Assistée par Ordinateur (CAO) pour concevoir les circuits synchrones, couplé à des langages de description matériel spécifiques. De plus, les ingénieurs sont formés à ces outils ainsi qu'à l'architecture synchrone. Le domaine asynchrone a de son côté développé des langages et outils spécifiques pour concevoir au mieux les circuits asynchrones. Mais cet environnement de conception parallèle ajoute des contraintes. Une entreprise voulant concevoir des circuits asynchrones devra donc acheter de nouveaux outils de CAO et former ses ingénieurs, voire développer ses propres logiciels. Cela représente un investissement important qui peut décourager les industriels de choisir l'approche asynchrone. D'autre part, il est possible d'améliorer les performances des circuits synchrones sans recourir à une architecture complètement différente. Par exemple, il est tout à fait possible d'éteindre l'horloge lorsqu'un bloc n'est pas utilisé et de mettre en veille un circuit synchrone. Le passage du synchrone à l'asynchrone semble par conséquent bien souvent trop compliqué pour les gains espérés.

Mais le contexte commence à changer. Les améliorations en consommation demandées par l'IoT poussent à revoir l'architecture des circuits intégrés pour les optimiser en énergie. L'investissement à consentir pour passer à l'asynchrone ne paraît plus si coûteux désormais. Il faut donc rendre plus accessible la conception des circuits asynchrones au monde industriel. Dans cette optique, une pratique intéressante serait d'intégrer leur conception au sein des flots de conception et outils de CAO déjà existants.

## Contributions

Pour favoriser l'adoption de la conception asynchrone par les ingénieurs "synchrones" et ainsi permettre une diffusion plus large de ces circuits dans l'industrie, nous proposons d'exploiter un flot de conception partant d'une description algorithmique. Les difficultés de la conception asynchrone que pourrait rencontrer les non-initiés sont par conséquent cachées. Ensuite, nous nous reposons totalement sur les outils de CAO commerciaux uti-

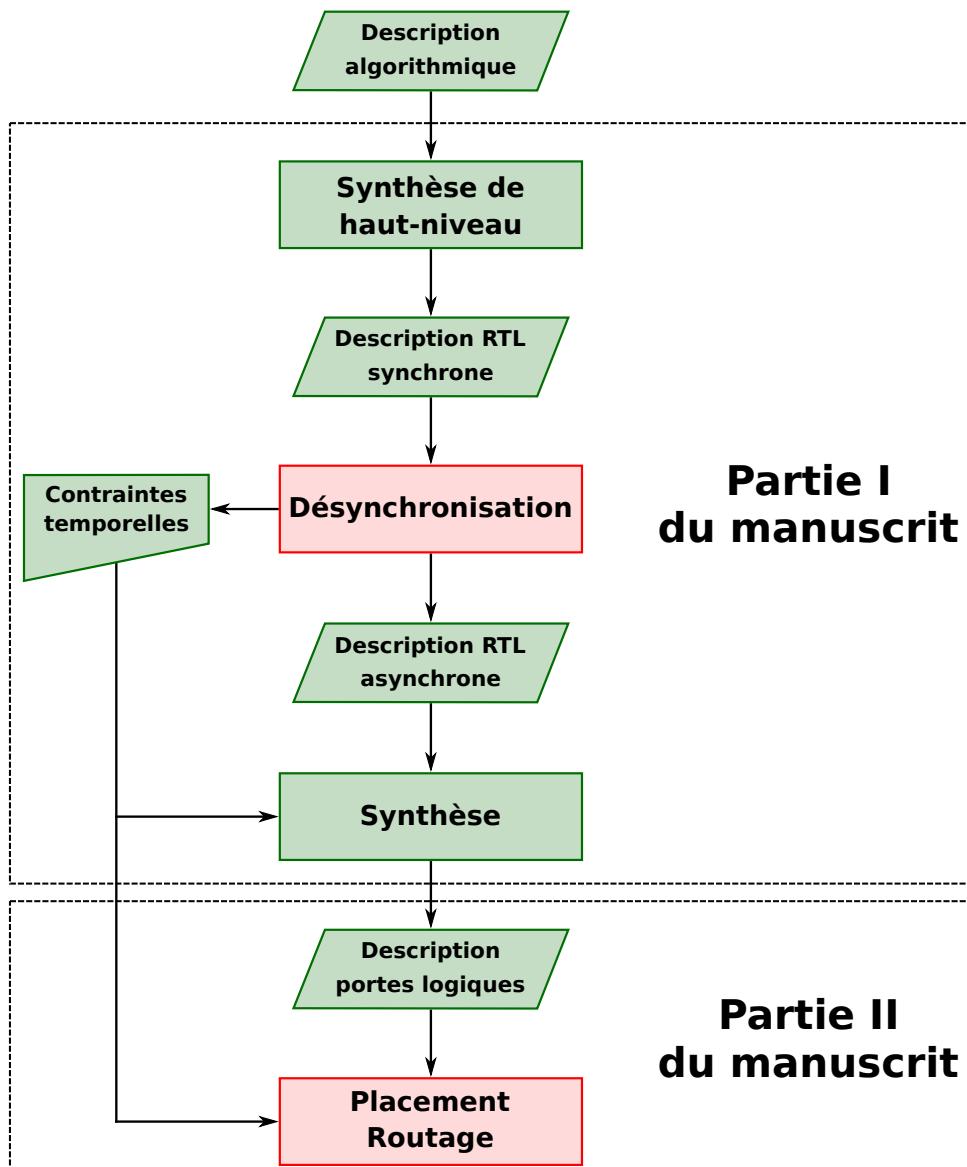

lisés dans l'industrie, et prévus pour de la logique synchrone. En exploitant une synthèse de haut niveau (HLS), nous générerons des circuits synchrones qu'il est ensuite possible de convertir automatiquement en circuits asynchrones grâce à un petit programme. La suite de la conception est effectuée de façon standard avec des outils de CAO commerciaux. Ainsi la conception asynchrone devient compatible avec les flots synchrones habituels de l'industrie. Pour améliorer l'efficacité énergétique des circuits et montrer la pertinence des circuits asynchrones dans le développement de nouvelles méthodes de gestion de la consommation, nous couplons les circuits asynchrones générés par HLS avec une méthode dynamique de polarisation de substrat en FDSOI. Celle-ci permet de changer les paramètres physiques des transistors durant le fonctionnement du circuit. Nous utilisons cette possibilité pour améliorer l'efficacité énergétique des circuits, en augmentant la vitesse des transistors lors des calculs et en économisant l'énergie lors des phases de veille. Afin d'implémenter cette approche, il est nécessaire de respecter des règles précises afin de garantir l'implémentation physique du circuit. Le flot de conception complet est présenté en figure 1.

FIGURE 1 – *Flot de conception développé dans cette thèse.*

Le flot de conception est très semblable à un flot classique, à deux exceptions près : les phases de désynchronisation et de Placement/Routage. La phase de désynchronisation convertit le circuit synchrone en circuit asynchrone en remplaçant la partie contrôle, qui est une machine à états finis, par un circuit de contrôle asynchrone équivalent. Les circuits obtenus sont similaires aux circuits d'origine, mais sont plus robustes. Cette méthode, dont une preuve de concept avait été réalisée dans des travaux antérieurs, a été modélisée dans ce travail de thèse en vue d'en réaliser la preuve formelle. Cette dernière a été effectuée manuellement. De plus, nous avons intégré notre méthode à l'outil industriel Catapult HLS de Siemens EDA pour prouver sa faisabilité dans un cadre industriel. Notre flot de conception permet aussi de rendre la conception des circuits asynchrones aussi accessible que leurs homologues synchrones en exploitant les outils de CAO classiques. Tous ces résultats ont été validés par la conception, la fabrication et le test d'un prototype.

La phase de Placement/Routage permet ensuite d'implémenter la méthode de polarisation du substrat. Cette dernière phase permet de polariser avec un grain fin des sous-systèmes du circuit dès lors qu'une activité est présente. Cette approche favorise une meilleure efficacité énergétique du circuit. Grâce à l'utilisation de circuits asynchrones, le système de contrôle de la tension polarisation peut être également simplifier par rapport aux méthodes classiques. Nous utilisons alors de simples translateurs de tension contrôlés par un petit détecteur d'activité, qui sont intégrés au flot de conception numérique. Dans cette thèse, la méthode a été appliquée aux circuits asynchrones désynchronisés, et le modèle associé est présenté. L'implémentation physique de la méthode est en très grande partie automatisée.

## Plan du manuscrit

Ce manuscrit de thèse est divisé en deux grandes parties. La première se concentre sur la partie conception asynchrone de notre travail, qui correspond à la première partie du flot développé. Le chapitre 1 décrit l'état de l'art des circuits asynchrones, ainsi que des méthodes de conception existantes. Le chapitre 2 présente notre méthode de génération automatique de circuits asynchrones à partir de circuits synchrones. Cette méthode a été intégrée au sein d'un flot de haut niveau reposant sur les outils commerciaux standards. Enfin, les circuits résultants de notre méthode de désynchronisation sont étudiés en termes de surface, vitesse et consommation dans le chapitre 3. Un prototype a aussi été fabriqué pour valider le flot de conception.

La deuxième partie du manuscrit développe la méthode de polarisation dynamique du substrat en FDSOI. Le chapitre 4 donne une présentation de la technologie FDSOI et ses principales caractéristiques, notamment la polarisation de substrat. Notre méthode de polarisation de substrat est définie au chapitre 5, avec son principe, son modèle et son flot d'implémentation physique. De premières simulations numériques ont aussi été réalisées pour donner un aperçu des gains potentiels de la méthode. Enfin nous concluons que les travaux menés permettent à la logique asynchrone de franchir la frontière entre les mondes académique et industriel, permettant ainsi le développement de nouvelles méthodes de gestion de la consommation.

# **Première partie**

# **Architecture asynchrone**

# 1

## État de l'art

### Sommaire

---

|            |                                                 |           |

|------------|-------------------------------------------------|-----------|

| <b>1.1</b> | <b>Introduction</b>                             | <b>8</b>  |

| <b>1.2</b> | <b>Principes des circuits asynchrones</b>       | <b>8</b>  |

| 1.2.1      | Protocole de communication                      | 8         |

| 1.2.2      | Classes des circuits asynchrones                | 11        |

| 1.2.3      | Avantages de l'asynchrone                       | 14        |

| <b>1.3</b> | <b>Les circuits à données groupées</b>          | <b>16</b> |

| 1.3.1      | Modélisation des circuits asynchrones           | 16        |

| 1.3.2      | Méthodes de conception des circuits asynchrones | 18        |

| 1.3.3      | Vérification des contraintes temporelles        | 21        |

| <b>1.4</b> | <b>Synthèse de haut niveau</b>                  | <b>24</b> |

| 1.4.1      | Principe de la HLS synchrone                    | 25        |

| 1.4.2      | HLS asynchrone                                  | 25        |

| <b>1.5</b> | <b>Conclusion</b>                               | <b>27</b> |

---

## 1.1 Introduction

Les circuits synchrones possèdent tous une synchronisation globale. En effet, les éléments mémorisants d'un circuit synchrone sont tous synchronisés par un unique signal d'horloge. Ce signal détermine par la suite la fréquence du circuit. Ce principe, très largement utilisé dans l'industrie, est simple et efficace mais les contraintes sur les signaux d'horloge sont de plus en plus importantes. En effet, l'activation de l'ensemble des éléments d'un circuit à intervalle de temps régulier présente des pics de consommation importants [4]. De même, les variations de fabrication dans les derniers noeuds technologiques rendent de plus en plus compliquées l'activation uniforme de l'horloge dans le circuit [5], limitant les performances. Pour dépasser ces limitations, il est nécessaire de rechercher de nouvelles solutions architecturales.

À l'inverse, les circuits asynchrones utilisent une synchronisation locale pour fonctionner. Sans signal d'horloge, les composants du circuit communiquent alors les uns avec les autres à l'aide de protocoles de communication de type "poignée de main". Pour être fonctionnel, un circuit asynchrone repose par conséquent sur des hypothèses temporelles locales et son fonctionnement est par nature événementiel : seuls les composants nécessaires sont activés. Ce type de circuit possède donc une consommation réduite et une robustesse accrue aux conditions liées à l'environnement ainsi qu'aux variations induites lors de la fabrication. Ces caractéristiques [6] sont prometteuses pour résoudre les problématiques actuelles des circuits synchrones [7, 8], ainsi que pour développer de nouvelles méthodes événementielles de gestion de la consommation.

Mais le domaine des circuits asynchrones est vaste car il existe une grande liberté dans la conception de ces derniers. Nous présenterons donc dans ce chapitre les concepts de base des circuits asynchrones, ainsi que les principales classes de circuits asynchrones existantes. Nous verrons aussi les avantages que peuvent apporter ces circuits, qui restent aujourd'hui pour le moins non-conventionnels. Nous rentrerons plus en détail sur les méthodes de modélisation et de conception de ces circuits, et notamment dans l'environnement des logiciels industriels.

## 1.2 Principes des circuits asynchrones

### 1.2.1 Protocole de communication

Dans un circuit numérique, les différents systèmes du circuit réalisent des opérations sur les données et s'échangent ces données entre eux. Pour que cette communication s'effectue correctement, il est nécessaire d'avoir une méthode de synchronisation entre les systèmes du circuit. La figure 1.1 présente le schéma de principe d'une communication entre deux systèmes d'un circuit, dont un joue le rôle d'émetteur de données et l'autre sert de récepteur. À l'intérieur de ces systèmes, il existe deux types de composants : des portes logiques combinatoires, qui calculent de nouvelles données, et des éléments séquentiels pour enregistrer des données, principalement des registres ou des verrous. La synchronisation va permettre d'indiquer au récepteur à quel moment les données qui lui sont envoyées sont valides et donc quand activer ses composants séquentiels.

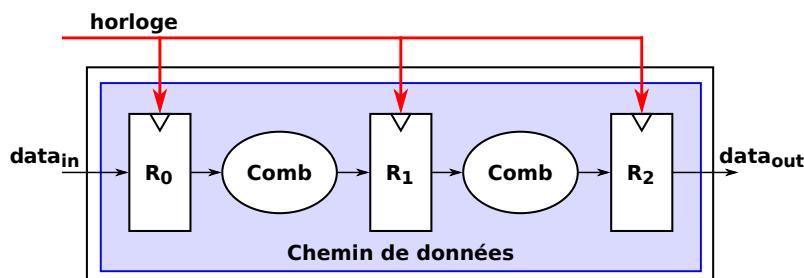

Une manière simple de synchroniser les systèmes d'un circuit est d'utiliser un signal

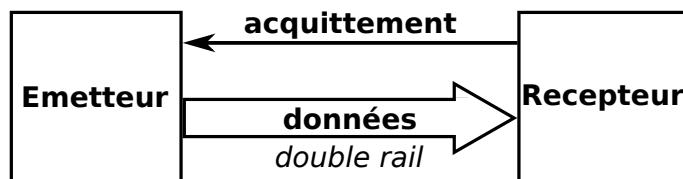

FIGURE 1.1 – Principe de communication entre deux systèmes.

de synchronisation externe global : une horloge. Tous les composants séquentiels du circuit sont donc activés au même moment par l'horloge à intervalle de temps régulier. On obtient alors un circuit synchrone, comme en figure 1.2. Par leur simplicité de conception, les circuits synchrones se sont imposés dans l'industrie et représentent la quasi-totalité des circuits produits dans le monde. La vitesse du circuit est alors déterminée par la fréquence d'horloge, qui dépend elle-même du chemin le plus long entre deux registres dans le circuit. Il s'agit donc d'une approche pire cas.

FIGURE 1.2 – Architecture d'un circuit synchrone.

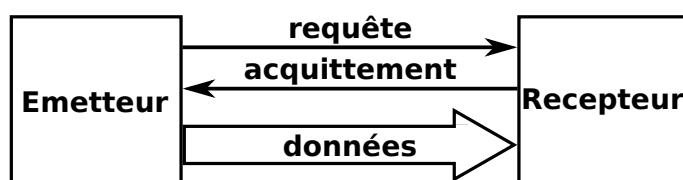

Néanmoins, il existe d'autres façons de synchroniser un circuit. En effet, la validité des données peut être groupée au sein d'une communication. Au lieu d'un signal global, les différents systèmes du circuit communiquent localement à l'aide de signaux de requête et d'acquittement, dont le principe est présenté en figure 1.3. Lors d'une communication, l'émetteur va envoyer un signal de requête en même temps que l'envoi des données. De son côté, le récepteur n'accepte des données que lorsqu'il reçoit le signal de requête. Après l'enregistrement des données et pour indiquer la bonne réception des données à l'émetteur, il envoie à son tour un signal d'acquittement. On appelle ce type de design des circuits à données groupées.

FIGURE 1.3 – Principe de communication à données groupées.

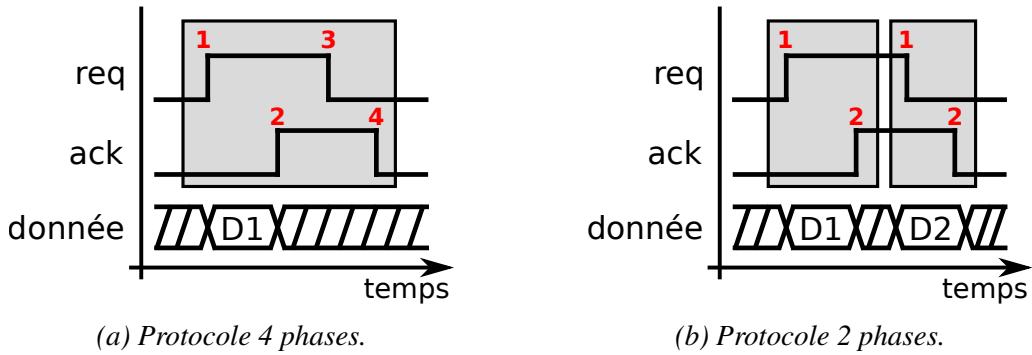

Pour assurer la bonne transmission des données, un protocole de communication doit être défini entre l'émetteur et le récepteur. Ces protocoles, que l'on appelle de *handshake* ou poignée de main, sont très variés mais il en existe deux grandes familles présentées figure 1.4 : les protocoles 4 phases et 2 phases. Les protocoles 4 phases sont les plus simples à implémenter et sont présentés figure 1.4a. Les deux premières phases sont utilisées pour indiquer l'envoi et la réception des données puis les phases 3 et 4 permettent de remettre

FIGURE 1.4 – Protocole de communication (a) 4 phases et (b) 2 phases.

à zéro tous les signaux. Dans un protocole de type 2 phases comme en figure 1.4b, il n'y a pas de retour à zéro des signaux avant une nouvelle communication. C'est donc une nouvelle transition, et non un niveau logique qui indique une nouvelle donnée. Ces protocoles, nécessitant une implémentation plus complexe, sont aussi plus rapides.

Il est aussi tout à fait possible d'intégrer la requête directement dans les données envoyées avec le protocole de communication associé. On parlera alors de validité intégrée aux données. Mais dans ce cas, il n'est plus possible d'utiliser l'encodage classique des données. En effet, il existe habituellement un fil mis à zéro ou à un pour représenter la valeur binaire d'un signal logique. Une autre catégorie de codage, appelée M parmi N, permet de représenter M signaux avec N fils. Ce type d'encodage est moins usité et se traduit souvent par un circuit plus complexe et plus coûteux. Il est le plus souvent employé sous la forme d'un double rail, qui correspond à un codage de 1 parmi 2. L'architecture obtenue est présentée en figure 1.5.

FIGURE 1.5 – Principe de communication avec un encodage double rail.

Il est là encore nécessaire d'utiliser un protocole de communication, mais cette fois-ci l'encodage des données permet de le définir. Dans le cas du double rail par exemple, un encodage à trois états permet de réaliser un protocole 4 phases. Tandis que les codes '01' et '10' représentent respectivement un 1 et un 0 logique, le code '00' correspond au retour à zéro du protocole. Pour les protocoles 2 phases, un encodage sur quatre états sera utilisé.

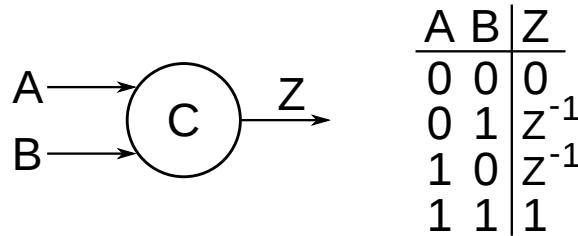

Afin d'implémenter matériellement ces protocoles de communication, il est nécessaire de pouvoir synchroniser des signaux entre eux. Pour réaliser cette fonction, une nouvelle porte séquentielle est introduite. Cette porte logique est la porte de Muller, ou *C-element*, dont le symbole et la table de vérité sont présentés en figure 1.6. La sortie de la porte de Muller prend la valeur des entrées lorsque celles-ci sont identiques, et enregistre la précédente valeur lorsqu'elles sont différentes. Comme ce type de porte n'existe pas dans les librairies standards habituelles, elle doit être conçue soit avec des portes logiques existantes soit comme une cellule standard additionnelle.

FIGURE 1.6 – Symbole et table de vérité d'une porte de Muller.

### 1.2.2 Classes des circuits asynchrones

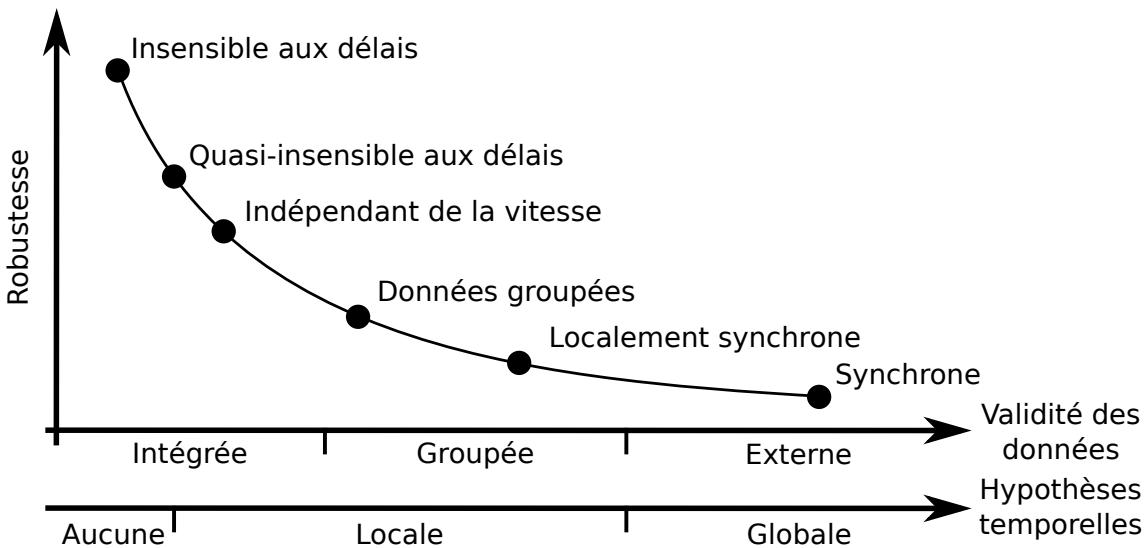

Il existe un grand nombre de type de circuits asynchrones dans la littérature, très différents les uns des autres. Suivant le choix du protocole de communication ou de l'encodage de données, leurs implémentations diffèrent. Il est à noter qu'en fonction des hypothèses temporelles, les circuits ont des propriétés différentes et notamment seront plus au moins robustes aux variations des procédés de fabrication, de la tension et de la température (PVT). Une classification comme en figure 1.7 des principales classes de circuits peut alors en être déduite. Les architectures asynchrones sont classées suivant leurs hypothèses temporelles et le type de validité des données utilisé, du plus local au plus global.

FIGURE 1.7 – Classification des types de circuits asynchrones (adaptée de [6])

À l'extrême gauche du graphique, les circuits insensibles aux délais, ou *Delay Insensitive* (DI), n'ont aucune hypothèse temporelle et sont les circuits les plus robustes existants. Ensuite, des hypothèses temporelles sont progressivement ajoutées très localement avec les circuits quasi-insensibles aux délais puis les circuits indépendants à la vitesse. Les circuits à données groupées et les machines localement synchrones reposent sur des signaux de synchronisation et utilisent des contraintes temporelles plus fortes, quoique toujours locales. Pour finir, les circuits synchrones utilisent un signal d'horloge externe pour indiquer la validité des données, qui détermine la seule hypothèse temporelle globale du circuit suivant la fréquence d'horloge choisie.

## Circuits insensibles aux délais

Les circuits DI ne nécessitent aucune contrainte temporelle pour fonctionner correctement [9]. Ce sont les circuits les plus robustes que l'on peut concevoir. Néanmoins, les contraintes de conception de ces circuits les rendent en pratique inutilisables car les deux seules portes logiques acceptées sont les inverseurs et les portes de Muller [10].

## Circuits quasi-insensibles aux délais

Une classe proche des circuits précédents correspond aux circuits quasi-insensibles aux délais, ou *Quasi-Delay Insensitive* (QDI). Ces circuits reposent sur une seule hypothèse temporelle locale : la fourche isochronique. Pour que les circuits QDI soient fonctionnels, elle suppose, comme présentée en figure 1.8, que certaines fourches présentent des délais égaux sur leurs branches. Cette hypothèse temporelle assez simple permet d'obtenir des circuits très robustes et bien plus pratiques à concevoir que leurs équivalents DI [10].

FIGURE 1.8 – *Fourche isochronique dans les circuits QDI.*

Les circuits QDI ont été largement étudiés au fil des ans, ce qui a amené un grand nombre d'implémentations. Par exemple, l'implémentation *Weak Contention Half Buffer* (WCHB) synthétisée à partir de la méthode *Delay Insensitive Min-terms Synthesis* (DIMS) est simple à concevoir mais présente une grande surface, tandis que la logique *Null Convention Logic* (NCL) [11] peut être générée à partir des outils de CAO classiques et se concentre la basse consommation [12]. Toutes ces implémentations ont en commun une grande robustesse et une sécurité améliorée, au prix d'une plus grande surface comparée à un circuit synchrone.

## Circuits indépendants de la vitesse

Les circuits indépendants de la vitesse, ou *Speed Independent* (SI) sont très similaires aux circuits QDI et sont issus d'un modèle développé par Muller [13]. Ce modèle suppose que les délais des fils sont négligeables mais que les délais des composants sont non bornés. Par conséquent, toutes les fourches sont isochrones. Les circuits QDI sont toutefois préférés aux circuits SI, car un modèle avec des délais d'interconnexion négligeables n'est plus pertinent au vu des technologies CMOS actuelles.

## Machines localement synchrones

Ces circuits, historiquement étudiés par Huffman [14], sont des machines à états finis asynchrones (AFSM). Une implémentation efficace, qui permet la prise en compte

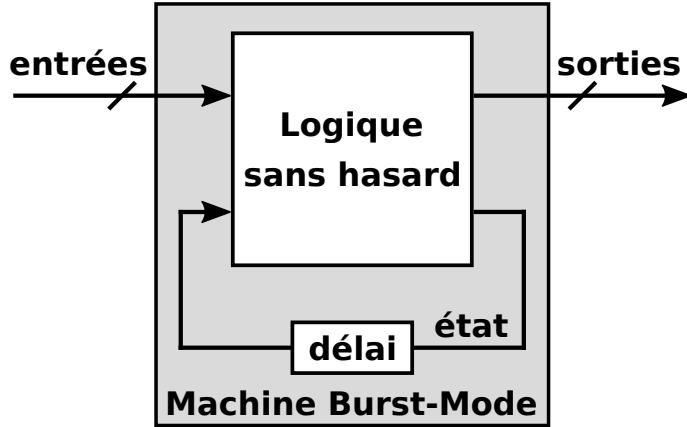

d'un groupe d'entrées pour chaque nouvel état, appelée une machine Burst-mode, a été présentée formellement par Nowick *et al.* [15] dont un schéma de principe est visible en figure 1.9.

FIGURE 1.9 – Architecture d'une machine Burst-Mode.

Ces circuits reposent sur une horloge locale générée par de la logique combinatoire. En revanche, il existe plusieurs contraintes dans ces circuits. Premièrement, la logique combinatoire doit être sans aléa, c'est-à-dire exempte de *glitches*. Ensuite, des délais doivent être présents sur le rebouclage de l'AFSM afin que les données d'états ne soient pas effacées. Et enfin, aucun changement sur les entrées ne doit survenir pendant le calcul d'un nouvel état. Pour ce dernier point, la spécification *Extended Burst-Mode* (XBM) [16, 17] élargit les possibilités de changement des entrées du système.

Toutes ces contraintes rendent la conception des machines Burst-Mode ardue, mais des outils ont été développés pour synthétiser une logique sans aléa, comme par exemple les logiciels de synthèse 3D [17] ou minimalist [18].

### Circuits à données groupées

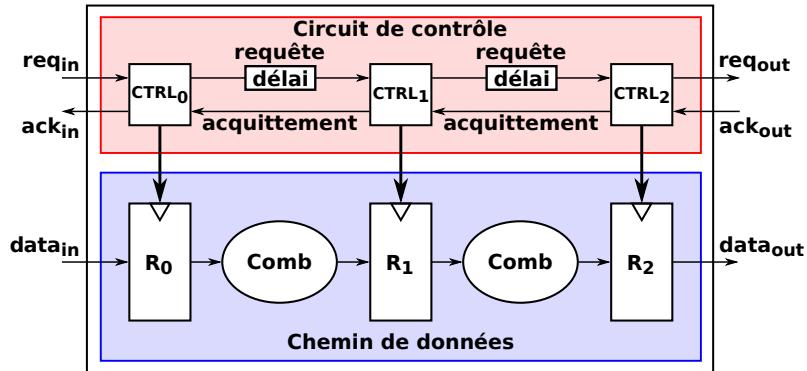

Tout d'abord présentés sous la forme du *micropipeline* par Ivan Sutherland [19], les circuits à données groupées sont très semblables aux circuits synchrones. Alors que leurs chemins de données sont similaires à leurs homologues synchrones, la synchronisation des éléments mémorisants du circuit n'est plus réalisée par un signal global d'horloge mais par un circuit de contrôle [20] (voir figure 1.10). Ce circuit de contrôle est composé de contrôleurs locaux communiquant entre eux à l'aide d'un protocole de communication.

Comme présenté en figure 1.10, chaque contrôleur  $ctrl_i$  est associé à un banc de registres  $R_i$ . Une nouvelle donnée entrante  $data_{in}$  est annoncée au circuit par le signal de communication  $req_{in}$  qui active le premier contrôleur. Quand un contrôleur est actif, il déclenche l'activation du banc de registres associé et lance une communication avec le contrôleur suivant. Afin que le circuit soit fonctionnel, il faut que l'activation des registres se produise après le calcul et la stabilisation des données dans la partie combinatoire. Pour respecter cette contrainte temporelle, il est donc nécessaire d'insérer des blocs de délais sur les lignes de requête dans le circuit de contrôle.

De nombreuses variantes d'implémentations et de protocoles ont été développées pour les circuits à données groupées. De plus, leur proximité avec les circuits synchrones les rend plus simples à concevoir avec des outils de CAO standards. C'est pourquoi nous uti-

FIGURE 1.10 – Architecture d'un circuit à données groupées.

liseros ces circuits dans ce travail de thèse. Toutes leurs caractéristiques seront détaillées dans la section 1.3.

### 1.2.3 Avantages de l'asynchrone

Les circuits asynchrones, de par leur synchronisation locale, possèdent un certain nombre d'avantages comparés à leurs homologues synchrones. Si les circuits synchrones se sont imposés dans l'industrie microélectronique grâce à la simplicité de leur conception, des limites commencent à apparaître du fait de leur synchronisation globale. Les contraintes imposées sur le signal d'horloge en termes de performance et de consommation sont telles que, désormais, de nouvelles approches ont été mises en place, comme les systèmes Globalement Asynchrones Localement Synchrones ou *Globally Asynchronous Locally Synchronous* (GALS).

#### Consommation

Le paradigme asynchrone repose sur la synchronisation locale des éléments du circuit. Un composant n'est donc activé que lorsque cela est nécessaire. Les architectures asynchrones réduisent donc intrinsèquement la consommation dynamique du circuit [12, 21]. De plus, les circuits asynchrones, dont le comportement est événementiel, sont automatiquement mis en veille lors de l'attente d'une nouvelle donnée à traiter. Ils n'ont donc pas besoin d'un système additionnel de mise en veille, réduisant de fait la consommation.

Il est aussi à noter que des améliorations au niveau système sont aussi présentes. En effet, un circuit synchrone nécessite un générateur externe d'horloge. Ce générateur d'horloge, généralement composé d'un oscillateur et d'une *Phase Locked Loop* (PLL), va consommer à moins d'être désactivé lors des moments de veille. Sa suppression est un réel avantage pour l'asynchrone, même si ce phénomène est rarement discuté dans la littérature.

#### Robustesse

En fonction des variations PVT, les délais des portes logiques dans un circuit sont variables. Les générateurs d'horloge procurent un signal à une fréquence précise qui ne prend pas en compte ces variations. Pour résoudre ce problème, des marges sont ajoutées

lors de la conception des circuits pour tenir compte des variations de fréquence de l'horloge d'une part et des délais dans le circuit d'autre part. Ainsi, on garantit que les circuits synchrones fonctionnent sur des plages PVT précises mais au détriment des performances globales.

Les circuits asynchrones de leur côté sont bien plus robustes. Les circuits QDI ne font aucune hypothèse temporelle sur les délais de propagation des portes logiques et des interconnexions hormis quelques fourches dites isochrones. Ils sont par conséquent extrêmement robustes [22] : ils sont fonctionnels tant que les portes logiques restent elles-mêmes fonctionnelles et vont à la vitesse maximale permise par les conditions PVT. Les circuits à données groupées possèdent quant à eux des hypothèses temporelles locales et sont donc moins robustes que les circuits QDI. Néanmoins, les lignes de délais qui assurent ces hypothèses sont intégrées directement en portes logiques sur le circuit. Les délais vont donc varier en même temps et de la même manière que les chemins de données associés, apportant ainsi une amélioration de la robustesse comparée à celle des circuits synchrones.

## Modularité

Avec une synchronisation locale entre les sous-systèmes reposant sur un protocole de communication, les circuits asynchrones possèdent une modularité supérieure à leurs homologues synchrones. En effet, chaque sous-système fonctionne à sa propre vitesse et ne prend pas en compte les contraintes temporelles des autres blocs, ce qui facilite l'assemblage des différents composants d'un circuit. En effet, une validation globale des hypothèses temporelles n'est pas nécessaire. Pour un circuit synchrone, la fréquence de fonctionnement est déterminée par le système le plus lent et peut donc amener de nouvelles itérations de conception pour améliorer les performances. Pour éviter des contraintes trop lourdes sur le signal d'horloge, les systèmes GALS sont apparus ces dernières années, avec un signal d'horloge dédié à chaque bloc. Toutefois, dans ce cas, les interfaces entre les différents domaines d'horloge sont complexes et pas complètement sûres (risque de métastabilité). Cette difficulté est inexistante avec les circuits asynchrones.

## Faibles émissions électromagnétiques

Dans un circuit synchrone, comme l'horloge active globalement le circuit, un fort rayonnement électromagnétique apparaît couplé à la fréquence d'horloge. Ce rayonnement peut poser problème, notamment avec la partie analogique d'un circuit [23], cette dernière, étant assez sensible au bruit environnant, est par conséquent soumise à des normes spécifiques. Dans le cas asynchrone, les activations de composants sont réalisées localement, distribuées spatialement et temporellement au sein du circuit. Le rayonnement électromagnétique est donc diminué [24], de même que le spectre électromagnétique sera plus étalé. Il est même possible de mettre en place des méthodes de contrôle du spectre dès la conception [25], ce qui se révèle très compliqué, voire impossible, pour un circuit synchrone.

Malgré tous ces avantages, les systèmes asynchrones n'ont pas réellement réussi à émerger dans l'industrie même si cela est annoncé depuis de nombreuses années par l'*International Technology Roadmap for Semiconductors*. La question est donc d'identifier les raisons de ces difficultés d'adoption par l'industrie. Plusieurs problématiques

peuvent expliquer ce phénomène. Tout d'abord, les circuits asynchrones sont difficiles à concevoir. Ensuite, les circuits synchrones ont été grandement améliorés au fil des années et ont réduit la différence avec l'asynchrone sur un certain nombre de paramètres. Par exemple, le *clock gating* permet de réduire la consommation, les horloges peuvent maintenant être intégrées en portes logiques pour augmenter la robustesse [26] et les GALS diminuent les contraintes sur les signaux d'horloge.

Une grande difficulté du domaine asynchrone est donc la conception des circuits asynchrones, notamment avec des outils de CAO classiques. En effet, dans un contexte de coût productions importants ainsi que la nécessité d'un *time to market* plus court possible, les entreprises sont réticentes à utiliser de nouveaux outils ou langages. Dans cette optique, nous nous intéresserons dans ce travail à une classe spécifique de circuits asynchrone : les circuits à données groupées. En effet, ceux-ci sont les circuits plus proches des circuits synchrones tout en gardant la majorité des avantages du paradigme asynchrone. La section suivante se concentrera donc sur ces circuits asynchrones ainsi qu'à leur méthode de conception.

## 1.3 Les circuits à données groupées

### 1.3.1 Modélisation des circuits asynchrones

Le circuit de contrôle d'un circuit à données groupées repose sur des événements de signaux, dont l'apparition est intrinsèquement concurrente. Un moyen pratique et efficace de modéliser les protocoles de communication est alors d'utiliser des réseaux de Petri [27].

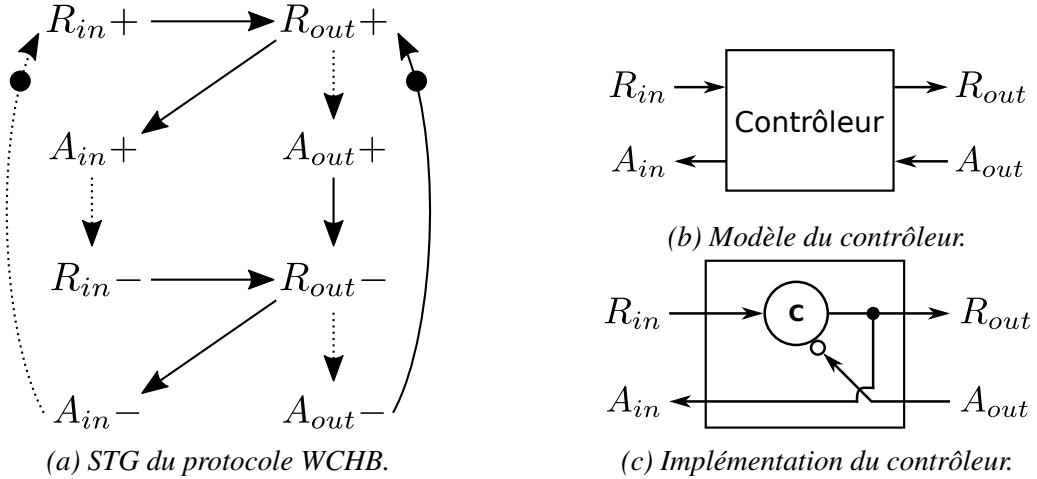

Un modèle populaire pour représenter le comportement asynchrone d'un circuit asynchrone est le graphe de transitions de signaux ou *State Transition Graph* [28] (STG), qui est un réseau de Petri montrant toutes les transitions existantes. Pour tout signal *Sig*, les transitions *Sig*<sub>+</sub> et *Sig*<sub>-</sub> représentent respectivement les fronts montants et descendants de *Sig*. Ces transitions sont reliées à des places. Afin d'améliorer la lisibilité du modèle, les places ne sont pas représentées et sont remplacées par des flèches. Les flèches en pointillées modélisent l'environnement du contrôleur. Un jeton placé sur la flèche signifie que la place est remplie. La transition est effectuée quand chaque place connectée à la transition est remplie.

Pour illustrer le fonctionnement de ce modèle, la figure 1.11a présente le STG du protocole WCHB. L'environnement déclenche le contrôleur en générant un front montant sur le signal d'entrée  $R_{in}$ . Cette transition génère à son tour un front montant sur le signal de sortie  $R_{out}$ . Il est à noter qu'il n'y a pas d'hypothèse temporelle. Par conséquent, l'événement peut apparaître après un délai indéfini. Ensuite, deux nouvelles transitions vont se produire : un front montant sur  $A_{in}$  en interne du contrôleur et un autre sur  $A_{out}$  en passant par l'environnement. Les deux événements apparaissent de manière concurrente et il n'y a donc aucune question d'ordre entre les deux. Les transitions continuent à s'enchaîner de la même manière jusqu'au retour à l'état initial du contrôleur.

Le STG peut ensuite être synthétisé matériellement avec des outils comme *Petrify* [29]. Dans le cas de notre exemple avec le protocole WCHB, *Petrify* implémente le STG sous la forme d'une porte de Muller et d'un inverseur (voir figure 1.11c). Si l'implémentation de

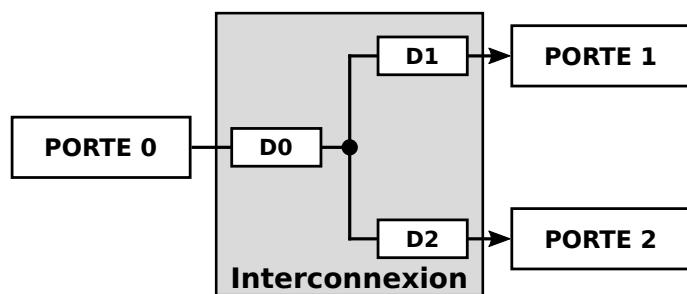

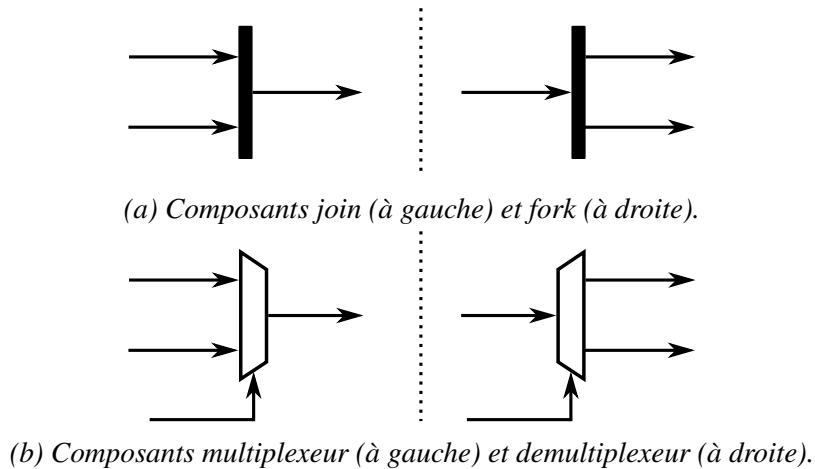

FIGURE 1.11 – Exemple d'un STG pour le protocole WCHB.

ce STG est simple, des STGs plus complexes deviennent difficiles à synthétiser à cause de l'explosion du nombre d'états et du temps de vérification [30] lors de la génération de l'implémentation. Cette méthode est donc peu adaptée pour un circuit de contrôle entier. Par conséquent, la conception d'un circuit asynchrone s'appuie la plupart du temps sur l'assemblage de primitives. Dans ce cadre, les contrôleurs sont construits à partir du STG d'un protocole et contrôlent les registres du chemin de données. Des composants additionnels compatibles avec ce protocole sont utilisés pour synchroniser les contrôleurs entre eux dans le cas d'un circuit non-linéaire, comme par exemple ceux présentés en figure 1.12.

FIGURE 1.12 – Composants de synchronisation [20] (a) totale et (b) sélective.

Dans le cadre des circuits à données groupées, il existe un grand nombre de protocoles offrant différents avantages. Tout d'abord, les protocoles 2 phases visent la performance car ils ne possèdent pas de phase de retour à zéro. On pourra citer le micropipeline [19], le GasP [31], le mousetrap [32] et enfin Click [33]. Ce dernier protocole a aussi l'avantage de ne pas utiliser de porte de Muller pour améliorer l'intégration au flot de conception conventionnel et la testabilité des circuits asynchrones.

Si les protocoles 2 phases sont performants, ils impliquent aussi une conception du circuit plus complexe. Pour faciliter cette conception, l'utilisation des protocoles 4 phases

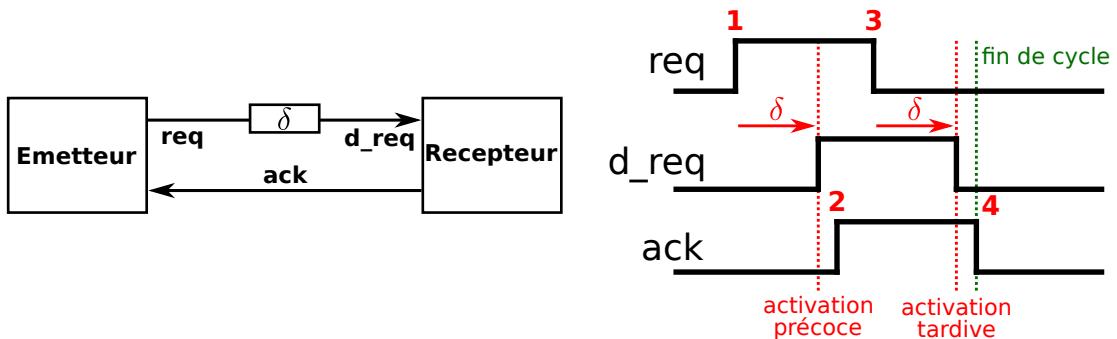

est souvent préférée. La plupart de ces protocoles 4 phases activent les registres lors du front montant de la requête, que l'on appelle des protocoles précoce [34]. Parmi eux, les protocoles découpent plus ou moins les communications d'entrée et de sortie d'un contrôleur [35], ce qui détermine la performance du contrôleur en fonction de sa complexité. Un très grand nombre de ces protocoles ont été développés au cours des dernières décennies et on dénombre aujourd'hui plus d'une centaine de protocoles [36, 37]. La figure 1.13 présente le chronogramme d'une communication entre deux contrôleur. Afin de respecter les contraintes temporelles, il est nécessaire d'avoir une ligne de délais  $\delta$  sur le signal requête qui soit plus grande que le chemin critique du chemin de données. On appelle temps de cycle le temps nécessaire à une communication pour être complète, temps avant lequel une nouvelle communication ne peut s'établir. Dans le cas des protocoles précoce, le temps de cycle du protocole équivaut à plus de deux fois le délai de la ligne de requête car le front descendant est aussi propagé dans le délai  $\delta$  lors de la phase de retour à zéro. Cela mène à une importante diminution de vitesse comparée à un circuit synchrone si le chemin de données est conservé en l'état.

FIGURE 1.13 – Principe des protocoles 4 phases précoce et tardif.

Afin d'être plus efficace, il est préférable d'utiliser un protocole activant les registres sur le front descendant de la requête, appelé protocole 4 phases tardif [34]. Dans ce cas, les fronts montants et descendants du signal de requête sont propagés dans la ligne de délais avant l'activation des registres, comme présenté en figure 1.13. De cette manière, le bloc de délai est réduit à seulement la moitié de celui requis pour un protocole classique à 4 phases. Ces derniers possèdent deux avantages : la vitesse redouble comparable à celle des circuits synchrones et la taille de la ligne de délai est diminuée par 2 ainsi que sa consommation.

Contrairement aux protocoles 4 phases précoce, les protocoles tardifs restent encore peu étudiés dans la littérature. Seulement quatre ont été développés : les protocoles Burst-Mode [38], Early-Ack [39], Late-Capture et Maximus [40]. Tous possèdent des performances similaires à l'exception du protocole Maximus. Ce dernier permet un temps de cycle minimal au prix d'une plus grande surface.

### 1.3.2 Méthodes de conception des circuits asynchrones

Afin de concevoir les circuits asynchrones, il est nécessaire d'avoir des langages HDLs et les outils de CAO associés. Les langages HDLs classiques, le VHDL et le verilog, sont peu adaptés pour décrire les circuits asynchrones. Un certain nombre de travaux visent tout de même l'utilisation des outils de CAO standards pour éviter le surcoût du développement de nouveaux outils. Une meilleure approche serait l'usage d'une description

au niveau transactionnel permettant d'abstraire le protocole de communication et de représenter la concurrence dans les circuits asynchrones ciblés. Dans ce cas, cela implique d'utiliser des langages adaptés à ce niveau de description ainsi que des logiciels dédiés.

### Traduction dirigée par la syntaxe

Une approche pour la conception des circuits asynchrones est le développement de HDLs spécifiques. Ces langages, de plus haut niveau que le VHDL et le verilog, permettent de représenter la concurrence des opérations asynchrones et de traduire la description en macro-composants matériels issus de librairies préexistantes. Dans ce contexte, les outils de synthèse TiDE et Balsa [41] utilisent des composants *handshake* [42]. L'outil TAST [43] utilise quant à lui le langage CHP [44]. Tout comme pour les langages utilisés pour les circuits synchrones, les circuits générés par ces méthodes dépendent fortement de la description, par conséquent les concepteurs doivent avoir de bonnes connaissances sur le langage et l'architecture souhaitée.

### Désynchronisation de circuits

Il est assez compliqué d'utiliser les outils commerciaux standards pour concevoir des circuits QDI du fait de leur architecture assez éloignée du synchrone. Néanmoins Lighthart *et al.* [45] ou plus récemment les travaux en [46, 47] ont mis en place des flots de conception avec les circuits QDI de type NCL. La difficulté réside dans la façon d'écrire le RTL pour représenter correctement le circuit QDI, puis de transformer la sortie de l'outil de synthèse pour obtenir le circuit voulu.

Les circuits synchrones et asynchrones à données groupées ont en revanche des architectures très proches. En effet, ils partagent un chemin de données similaire et seul l'élément de synchronisation diffère avec un signal d'horloge pour les uns et un circuit de contrôle pour les autres. Il est donc possible d'obtenir très rapidement un circuit asynchrone par la conversion d'un circuit synchrone par le biais d'une transformation appelée désynchronisation. L'objectif des méthodes de désynchronisation est de diminuer fortement le temps de conception des circuits asynchrones et de permettre à des ingénieurs non formés au domaine asynchrone de participer au développement de ces circuits.

**Désynchronisation classique** Une méthode assez simple et directe de désynchroniser un circuit synchrone est de remplacer son signal d'horloge par un circuit de contrôle. Néanmoins, cette transformation nécessite de garantir le même comportement par rapport au circuit d'origine.

Cortadella *et al.* [48] ont été les premiers à mettre en place un flot de désynchronisation complet. Dans celui-ci, chaque registre du circuit est converti en une paire de *latches* maître/esclave et ensuite le circuit de contrôle est construit en définissant un contrôleur asynchrone par *latch*. De plus, leurs travaux présentent les différents protocoles [49] compatibles avec la désynchronisation (même si des travaux récents [50] montrent qu'un de ces protocoles n'est finalement pas correct).

La méthode CAR [51] conserve quant à elle les bascules du circuit, tandis que le circuit de contrôle est composé de petits contrôleurs afin de réduire l'augmentation de surface. La classification de [49] ne contient pas ce protocole mais la bonne opération du circuit est garantie en ajoutant des registres tampons dans le chemin de données. Quelques travaux [52, 53] utilisent des protocoles 2 phases pour la conception du circuit de contrôle.

Cependant les seuls circuits étudiés sont des pipelines linéaires, ce qui limite fortement la portée de leur application.

Si les méthodes précédentes attribuent un contrôleur par groupe de registres, certains flots de désynchronisation utilisent une granularité moins fine. Srivastava *et al* [54] divisent le circuit en plusieurs régions de désynchronisation et chacune d'entre elles est dotée d'une paire de contrôleurs. De plus, les lignes de délais sont dépendantes des opérations et vont changer de valeur selon l'activité du chemin de données. Cette méthode améliore grandement la vitesse du circuit tout en diminuant l'augmentation de surface. Néanmoins, cette méthode n'est pas automatique.

Le flot open-source Edge [55] est l'approche la plus haut niveau et utilise seulement deux contrôleurs rebouclés. Un des contrôleurs active les *latches* maîtres tandis que le second contrôle les *latches* esclaves. Même si la cohérence entre les chemins de contrôle et de données est perdue, cette méthode réduit significativement l'augmentation de surface et continue d'apporter une plus grande robustesse aux variations PVT due au paradigme asynchrone.

**Désynchronisation du chemin de contrôle** Dans la section précédente, toutes les méthodes de désynchronisation présentées replacent uniquement l'arbre d'horloge par un circuit de contrôle, même si des changements mineurs peuvent être faits dans le chemin de données d'origine. Pourtant, ce n'est pas la seule façon d'obtenir un circuit désynchronisé. Une désynchronisation du chemin de contrôle supprime naturellement l'horloge. Mais ce type de méthode va aussi remplacer le chemin de contrôle du circuit, généralement une machine à états finis (FSM), pour mettre un circuit asynchrone à la place. Par conséquent, cette FSM asynchrone agit comme un circuit de contrôle et génère tous les signaux nécessaires pour le chemin de données.

Les AFSMs sont très bien étudiées et de nombreuses implémentations existent dans la littérature. Deux grandes familles sont présentées :

- Les AFSMs localement synchrones [15, 16] déjà présentées précédemment. Ce type d'AFSM est très bien formalisé et l'implémentation associée est compacte. Néanmoins, l'utilisation de logique sans aléa peut être une limite car les outils de CAO ne supportent pas ce type de logique.

- Les AFSMs distribuées où chaque état est représenté par un élément mémorisant [56, 57]. Ces architectures utilisant l'encodage *one-hot* sont moins compactes que leurs homologues localement synchrones mais sont plus modulaires et plus faciles à implémenter.

Les AFSMs ne sont pas souvent utilisées pour gérer un chemin de données synchrone. À notre connaissance, seuls quelques travaux expérimentent cette architecture et peuvent être catégorisés suivant la famille d'AFSM choisie.

Certains travaux [58] utilisent une AFSM localement synchrone en remplacement de la FSM synchrone d'origine. Ils ciblent l'amélioration de la latence des circuits sur FPGA. Cependant, l'AFSM doit respecter les spécifications XBM et la transformation de synchrone à asynchrone nécessite d'importants post-traitements de la FSM initiale pour être conforme à ses spécifications. De plus, le chemin de données et l'AFSM doivent être compatibles l'un avec l'autre. Ce dernier point est effectué soit en modifiant le chemin de données soit en utilisant une version altérée des spécifications XBM.

Dans d'autres travaux, l'AFSM est implémentée avec une architecture distribuée. Iizuka *et al* [59] représentent chaque état à l'aide d'un module Q [60]. Tandis qu'un en-

semble de couches logicielles a été développé pour faciliter la conception de l’AFSM, il existe en revanche très peu de détails sur la méthodologie pour déterminer comment faire la conversion entre synchrone et asynchrone, ni sur la vérification de cette transformation. Enfin, Simatic *et al.* [61] utilisent quant à eux des contrôleurs asynchrones plus standards. Cette désynchronisation est associée à un outil de HLS académique, AUGH [62], pour concevoir les circuits plus rapidement.

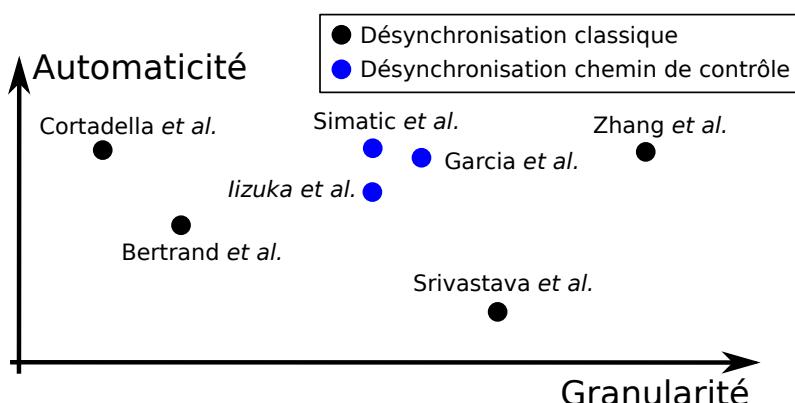

Toutes les méthodes présentées dans cette partie peuvent être classées suivant la granularité utilisée dans le circuit de contrôle. De plus, ces méthodes sont intégrées dans des flots de conception plus ou moins automatiques afin de faciliter la génération des circuits asynchrones. Les principaux travaux de désynchronisation sont catégorisés suivant ces deux paramètres dans la figure 1.14.

FIGURE 1.14 – Classification des méthodes de désynchronisation.

### 1.3.3 Vérification des contraintes temporelles

Pour valider le bon fonctionnement d'un circuit asynchrone, il est nécessaire de s'assurer que les contraintes temporelles locales sont respectées. Pour ce faire, il faut pouvoir calculer les différents délais au sein d'un circuit asynchrone de manière précise. Pour atteindre ce but, deux grandes tendances existent dans le domaine asynchrone.

#### Expression des contraintes temporelles

Dans les circuits à données groupées, les contraintes temporelles s'établissent entre chaque paire des contrôleurs du circuit de contrôle. Ces contraintes correspondent à la relation temporelle entre des chemins appartenant au chemin de données et au circuit de contrôle. On parle alors de contrainte temporelle relative, ou *Relative Timing Constraint* (RTC) [63]. En effet, elles reposent sur le fait que le chemin suivant la ligne de requête jusqu'à l'activation du prochain banc de registres est plus lent que le chemin de la logique combinatoire où sont calculées les données. Ces chemins possèdent un point de divergence, noté *pod*, qui sert de point de départ à la contrainte ainsi que deux points de convergence au niveau de chemin de données et de contrôle, respectivement *poc<sub>data</sub>* et *poc<sub>ctrl</sub>*. Une RTC s'écrit de la manière suivante :

$$pod \mapsto poc_{data} \prec poc_{ctrl}$$

Cette équation signifie qu'un événement se propageant de  $pod$  à  $poc_{ctrl}$  doit mettre un délai supérieur ou égal à la propagation d'un événement de  $pod$  à  $poc_{data}$ . Afin que la mémorisation des données soit correctement réalisée dans les éléments séquentiels, il est nécessaire que les données soient stables avant l'activation du registre et qu'elles restent stables un peu après son activation. Des marges doivent donc être ajoutées pour respecter ces délais supplémentaires. Ces temps sont respectivement les temps d'établissement et de maintien, plus communément appelés temps de *setup* et de *hold*, et sont des paramètres définis par les librairies de cellules standards.

## Développement d'outils spécifiques

Afin de calculer les contraintes temporelles, et notamment les temps de cycle entre deux contrôleurs asynchrones, il est indispensable de manipuler des graphes de délais cycliques. Dans ce cadre, il est possible de calculer le temps exact d'arrivée d'un événement [64]. Par conséquent, plusieurs outils d'analyse temporelle ont été développés récemment [65, 66]. Ces deux approches sont très proches, et diffèrent seulement sur le format des fichiers utilisés : Xiromeritis *et al.* [65] exploitent les fichiers standards des flots de conception synchrones tandis que Hua *et al.* [66] utilisent des formats spécifiques.

## Utilisation des outils commerciaux

Afin de concevoir un circuit asynchrone mais sans utiliser des outils spécifiques, qui peuvent ajouter des surcoûts de licence et de formation, une autre idée est d'utiliser les outils commerciaux. Ces outils de CAO sont bien connus des ingénieurs et ont été optimisés depuis de nombreuses années. En revanche, ils sont développés initialement pour concevoir des circuits synchrones.

Les circuits à données groupées sont la classe de circuits asynchrones la plus proche des circuits synchrones. Une fois le code RTL écrit, les questions majeures qui se posent sont celles de l'application des contraintes temporelles locales sur les chemins de données et de leurs vérifications. Dans les outils de CAO classiques, la vérification repose sur l'analyse temporelle statique ou *Static Timing Analysis* (STA). Cette analyse vérifie que chaque chemin combinatoire entre deux registres possède un temps inférieur à la période de l'horloge.

Dans le cadre des circuits asynchrones, plusieurs problèmes apparaissent lors de l'application de la STA. Il existe deux grandes difficultés :

- D'une part, les boucles combinatoires ne sont pas acceptées par les outils de STA. Or, les circuits de contrôle possèdent un grand nombre de ces boucles, qu'elles soient internes aux contrôleurs ou architecturales lorsque le circuit est non linéaire. Il faut donc trouver un moyen de les couper efficacement.

- D'autre part, et c'est là le problème majeur, la STA repose sur un signal global pour vérifier tous les chemins présents dans le chemin de données. Il est donc nécessaire de définir des chemins locaux pour vérifier que les délais du circuit de contrôle sont adaptés au chemin de données associé.

Ces problèmes doivent impérativement être résolus pour effectuer correctement une STA sur un circuit à données groupées. Plusieurs méthodes ont été développées pour réaliser cette tâche, que nous allons présenter.

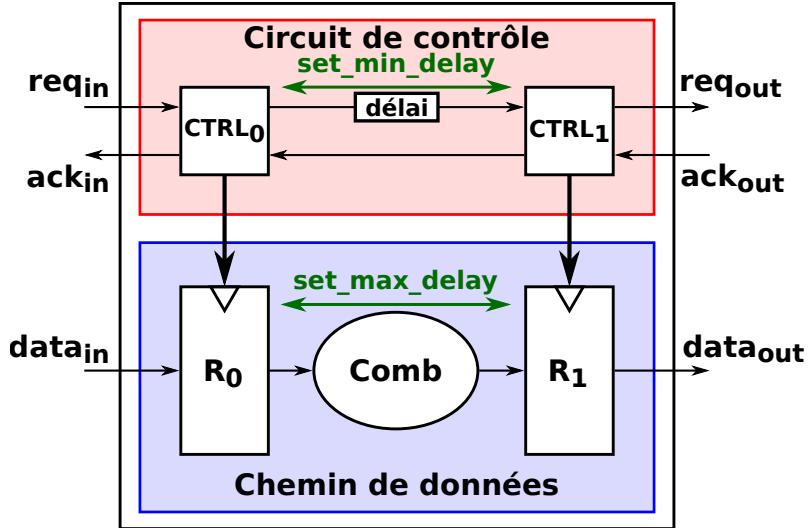

**Méthode min/max** Cette méthode repose sur l'utilisation de commandes non conventionnelles pour contraindre les circuits asynchrones et représenter les RTCs. Les boucles combinatoires sont coupées en désactivant les arcs temporels à l'aide de la commande `set_disable_timing`. Ensuite, les hypothèses temporelles sont appliquées, comme montrées en figure 1.15, en contrignant à la fois les chemins de données et de contrôle avec les commandes `set_min_delay` et `set_max_delay`. Un délai maximal est défini sur la logique combinatoire du chemin de données pour contraindre les performances du circuit et ce dernier détermine le délai minimal à appliquer sur la ligne de requête associée au circuit de contrôle pour garantir le bon fonctionnement du circuit.

FIGURE 1.15 – Contraintes temporelles min/max dans un circuit à données groupées.

Plusieurs travaux ont réussi à intégrer cette méthode dans un flot numérique global [67-69] avec quelques différences entre eux, comme l'utilisation d'horloges virtuelles à la place dans le chemin de données dans [68]. De plus, pour s'assurer de la bonne génération des contraintes, Stevens *et al.* [67] proposent une méthode formelle pour adapter les hypothèses temporelles au format des outils de CAO.

Pourtant, cette méthode possède plusieurs désavantages. Tout d'abord, l'ensemble des chemins n'est pas vérifié tout comme les temps de *setup* et *hold*, mais seulement la partie combinatoire et la ligne de requête. Il est donc toujours possible d'avoir des violations si une marge assez importante n'est pas prise sur la ligne de requête. De plus, cette méthode est dépendante des conditions PVT, et nécessite donc une nouvelle génération des contraintes pour chaque condition (*corner*) étudiée. Ceci peut devenir complexe dans les technologies CMOS avancées qui possèdent un grand nombre de conditions PVT à vérifier.

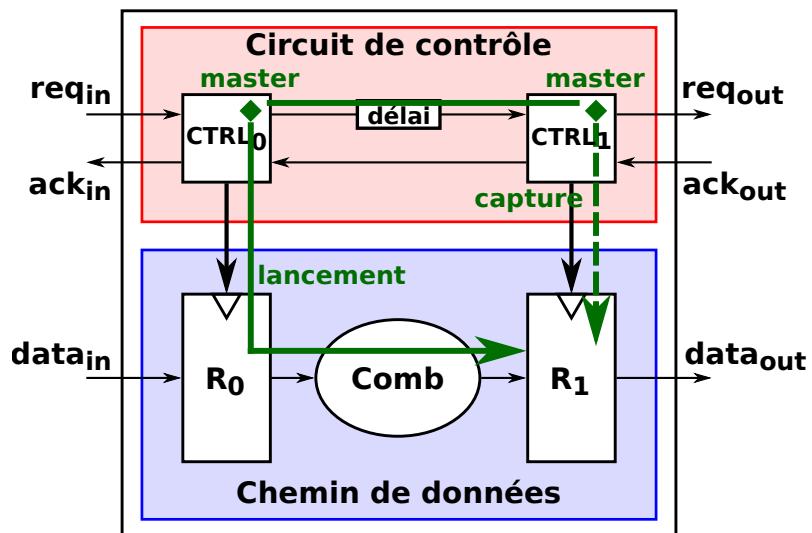

**Méthode LCS** Une méthode récente proposée par Gimenez *et al.* [70], appelée *Local Clock Sets* (LCS), exploite les horloges pour réaliser des STAs de manière locale dans un circuit à données groupées.

Afin de désactiver les boucles combinatoires du circuit de contrôle, des horloges maîtres sont déclarées au sein de chaque contrôleur (les losanges verts sur la figure 1.16). Ensuite, les chemins nécessaires à l'outil de CAO pour réaliser la STA doivent être construits : le chemin de lancement et de capture représente respectivement la propagation des données dans le chemin de données et le chemin d'activation des registres. Le chemin de

lancement est généré directement par l'horloge maître, représenté par la flèche verte sur la figure 1.16 partant du contrôleur  $ctrl_0$  allant jusqu'au registre  $R_1$ . Le chemin de capture, qui passe lui par le circuit de contrôle, doit être propagé à travers l'horloge maître du contrôleur  $ctrl_1$ . Pour cela, la méthode LCS utilise une horloge générée, représentée par la flèche en pointillé. De manière plus générale, le chemin d'horloge générée est défini pour construire le chemin jusqu'au banc de registre. De cette manière et contrairement à la méthode précédente, les contraintes temporelles sont vérifiées sur l'ensemble du chemin et l'outil peut prendre en compte les temps de *setup* et *hold* des registres. Par ailleurs, la méthode LCS est indépendante des conditions PVT, tout comme dans le cas synchrone, et peut aussi être utilisée pour contraindre le chemin de données suivant une fréquence cible.

FIGURE 1.16 – Méthode LCS dans un circuit à données groupées.

Pour conclure, cette méthode prometteuse permet de profiter de toutes les avancées faites dans le domaine synchrone au niveau STA dans le domaine asynchrone. Les règles de construction des LCS peuvent être extraits d'un STG et peuvent s'adapter à n'importe quel type de contraintes temporelles ou d'implémentations [71]. Il reste en revanche à intégrer cette méthode dans un flot de conception global pour la rendre automatique car l'écriture des LCS pour un circuit peut être fastidieuse, ainsi qu'à assurer de manière formelle la génération des contraintes temporelles comme dans [67].

## 1.4 Synthèse de haut niveau

Les outils de HLS prennent en entrée la description haut niveau d'un circuit sans information d'architecture ou de délais [72]. Cette description est synthétisée en un code RTL. De plus, la HLS est capable d'effectuer une exploration des architectures possibles afin d'optimiser le circuit suivant des contraintes spécifiques. Dans le contexte de l'asynchrone, la HLS est une voie prometteuse pour générer rapidement des circuits habituellement considérés comme difficile à concevoir.

### 1.4.1 Principe de la HLS synchrone