## On the Interactions between HPC Task-based Runtime Systems and Communication Libraries

Philippe Swartvagher

### ► To cite this version:

Philippe Swartvagher. On the Interactions between HPC Task-based Runtime Systems and Communication Libraries. Data Structures and Algorithms [cs.DS]. Université de Bordeaux, 2022. English. NNT: 2022BORD0322. tel-03989856

## HAL Id: tel-03989856 https://theses.hal.science/tel-03989856v1

Submitted on 15 Feb 2023  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Inia LaBRI Université

# THÈSE

## PRÉSENTÉE À

# L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DE MATHÉMATIQUES ET D'INFORMATIQUE

## par Philippe SWARTVAGHER

POUR OBTENIR LE GRADE DE

## DOCTEUR

SPÉCIALITÉ : INFORMATIQUE

On the Interactions between HPC Task-based Runtime Systems and Communication Libraries

Sous la direction de Alexandre DENIS et Emmanuel JEANNOT

Soutenue le 29 novembre 2022

#### Devant la commission d'examen composée de :

| M. Denis BARTHOU        | Professeur, Bordeaux INP                                | Président du jury  |

|-------------------------|---------------------------------------------------------|--------------------|

| M. George Bosilca       | Assistant Professor, University of Tennessee            | Examinateur        |

| M. Alexandre Denis      | Chargé de Recherche, Inria, Université de Bordeaux      | Examinateur        |

| M. Emmanuel JEANNOT     | Directeur de Recherche, Inria, Université de Bordeaux   | Directeur de thèse |

| M. Arnaud Legrand       | Directeur de Recherche, CNRS, Université Grenoble Alpes | Rapporteur         |

| Mme Didem UNAT $\ldots$ | Associate Professor, Koç University                     | Rapportrice        |

**Titre** De l'interaction entre les supports d'exécution à tâches HPC et les bibliothèques de communications

**Résumé** Les supercalculateurs sont utilisés pour résoudre des problèmes numériques complexes demandant beaucoup de ressources de calcul (simulations, prévisions météorologiques, modélisations, etc), impossibles à exécuter sur des ordinateurs classiques. Ces supercalculateurs sont composés de nombreux puissants ordinateurs, connectés par un réseau. Bien que la puissance de ces supercalculateurs ne cesse d'augmenter, le développement d'applications exploitant toute leur puissance de calcul est de plus en plus complexe. En effet, de nombreux aspects doivent être considérés : des unités de calculs hétérogènes qui se programment différemment, la hiérarchie mémoire et les transferts de données, les communications réseau, l'ordonnancement, etc. Pour parer à ces difficultés, les supports d'exécutions à tâches ont émergé : ils représentent les applications par des graphes de tâches. Les différentes opérations exécutées par l'application et les dépendances entre elles forment un graphe. Il suffit alors de donner une implémentation de chaque tâche pour les unités de calcul ciblées, les dépendances entre les tâches et le support d'exécution se charge d'exécuter l'application : ordonnancer les tâches sur les différentes unités de calcul, réaliser les transferts mémoire et les communications réseau nécessaires, etc.

Dans cette thèse, nous explorons les différentes interactions possibles entre les supports d'exécution à tâches et la bibliothèque de communication utilisée pour réaliser les transferts réseau. L'objectif est de faire plus collaborer ces deux couches logicielles, pour améliorer la performances des applications exécutées. Pour analyser et comprendre les interactions entre les supports d'exécution et les communications, tracer les applications est une technique pertinente, malgré certaines limitations. C'est pourquoi nous commençons par évaluer les surcoûts possibles en termes de performances induits par un système de traces. Nous proposons des techniques pour réduire ces surcoûts et avons également évalué l'impact de la précision de la synchronisation d'horloge pour les traces distribuées. Ensuite, comme interaction positive entre un support d'exécution à tâches et la bibliothèque de communications, nous proposons une solution pour efficacement envoyer une même donnée à plusieurs destinataires, tout en respectant les contraintes du support d'exécution. D'autre part, nous considérons également les éventuelles interactions négatives, en évaluant les différentes sources d'interférences entre les calculs et les communications exécutés en parallèle, dégradant leurs performances respectives. Ayant observé que la contention mémoire entre les calculs et les communications a le plus d'impact, nous proposons finalement un modèle prédisant la répartition de la bande-passante mémoire entre les calculs et les communications. Ce modèle permet de mieux comprendre le comportement du composant mémoire en cas de contention et de prendre en compte ce phénomène dans les décisions du support d'exécution. Les contributions présentées montrent qu'améliorer les interactions entre les supports d'exécutions à tâches et les bibliothèques de communications a du potentiel pour améliorer les performances des applications HPC.

**Mots-clés** Calcul haute performance, programmation par tâches, calcul distribué, supports d'exécution, bibliothèques de communication, MPI, traces, contention mémoire

Laboratoire d'accueil Inria Bordeaux Sud-Ouest, 200 Avenue de la Vieille Tour, 33400 Talence

**Title** On the Interactions between HPC Task-based Runtime Systems and Communication Libraries

Abstract Supercomputers are used to solve complex and demanding computational problems (simulations, climate and weather forecasting, modelling, *etc*), impossible to run on regular computers. These supercomputers are composed of many powerful computers, interconnected through a network. While the power of these supercomputers increases over time, it becomes more and more challenging to develop applications taking benefit from all offered computing power. Indeed, many aspects have to be considered by the developer: heterogeneous computing units programmed in different manners, memory hierarchy and transfers, network communications, scheduling, *etc.* To overcome these challenges, *task-based runtime systems* have emerged. They model applications by graph of tasks: sub-computations and dependencies between them form a graph. The programmer has to provide the implementations of the tasks for each targeted computing unit, express dependencies between the tasks and then the runtime system is in charge of the application execution: scheduling tasks on different computing units, performing required memory movements between memories and network transfers, *etc.*

In this thesis, we explore the possible interactions between a task-based runtime system and the communication library it relies on to perform network transfers. The goal is to make these two software layers more collaborate, to improve performance of executed applications. To understand and analyze the interactions between the runtime systems and communications, tracing applications is a powerful technique. However, it can have some limitations. Thus, we first evaluate sources of performance overhead when tracing applications, propose solution to alleviate them and evaluate the impact of clock synchronization accuracy for distributed application tracing. Then, as a positive interaction between the task-based runtime system and the communication library, we propose a solution to efficiently send the same piece of data to several nodes, coping with the constraints of the considered runtime system. On the other hand, we also consider possible negative interactions, by evaluating the different sources of interferences between computations and communications being executed in parallel, more or less degrading their respective performance. Since we observe memory contention between computations and communications have the most impact, we finally propose a model predicting the memory bandwidth share between computations and communications, to better understand the behaviour of the memory system in case of contention and be able to take into account this phenomenon into decisions of the runtime system. Contributions presented in this manuscript show that improving interactions and cooperations between task-based runtime systems and communication libraries has potential to increase performance of HPC applications.

**Keywords** High performance computing, task-based programming, distributed computing, runtime systems, communication libraries, MPI, traces, memory contention

**Hosting Laboratory** Inria Bordeaux Sud-Ouest, 200 Avenue de la Vieille Tour, 33400 Talence

# Contents

| R  | emer                 | ciements                                                                                               | 1                            |

|----|----------------------|--------------------------------------------------------------------------------------------------------|------------------------------|

| R  | Éval<br>Broa<br>Inte | <b>é étendu en français</b><br>Juation et amélioration du système de traces                            | <b>3</b><br>4<br>5<br>6<br>7 |

| In | trod                 | uction                                                                                                 | 9                            |

|    | Higł                 | Performance Computing                                                                                  | 9                            |

|    | -                    | ls and contributions of this thesis                                                                    | 10                           |

|    | Orga                 | anization of the document                                                                              | 11                           |

| 1  | Dist                 | tributed Task-based Runtime Systems                                                                    | 13                           |

|    | 1.1                  | The growing complexity of HPC machines                                                                 | 13                           |

|    |                      | 1.1.1 More powerful machines                                                                           | 13                           |

|    |                      | 1.1.2 but more complex to program!                                                                     | 17                           |

|    | 1.2                  | Distributed systems                                                                                    | 19                           |

|    |                      | 1.2.1 Motivation for distributed computing                                                             | 20                           |

|    |                      | 1.2.2 Environment for distributed systems                                                              | 20                           |

|    |                      | 1.2.3 An HPC communication library: NEWMADELEINE                                                       | 22                           |

|    | 1.3                  | Task-based runtime systems                                                                             | 22                           |

|    |                      | 1.3.1 General concepts                                                                                 | 23                           |

|    |                      | 1.3.2 StarPU $\ldots$ | 24                           |

|    |                      | 1.3.3 Distributed STARPU                                                                               | 27                           |

|    | 1.4                  | Goals and contributions of this thesis                                                                 | 29                           |

| 2  | Rel                  | ated Work                                                                                              | 33                           |

|    | 2.1                  | Programming models                                                                                     | 33                           |

|    | 2.2                  | Task-based runtime systems                                                                             | 37                           |

|    | 2.3                  | Communications with task-based runtime systems                                                         | 39                           |

|    | 2.4                  | Work related to our contributions                                                                      | 42                           |

|    |                      | 2.4.1 Broadcasts in task-based runtime systems                                                         | 42                           |

|    |                      | 2.4.2 Interferences between computations and communications                                            | 42                           |

|   |     | 2.4.3 Tracing systems                                                                          | 45       |

|---|-----|------------------------------------------------------------------------------------------------|----------|

|   | 2.5 | Conclusion                                                                                     | 47       |

| 3 | Tra | cing Task-based Runtime Systems                                                                | 49       |

| Ŭ | 3.1 | Background: tracing task-based runtime systems                                                 | 49       |

|   | 0.1 | 3.1.1 Generic tracing systems                                                                  | 50       |

|   |     | 3.1.2 Tracing distributed applications: synchronizing clocks                                   | 50       |

|   |     | 3.1.3 Tracing systems and task-based runtime systems                                           | 51       |

|   |     | 3.1.4 Contributions                                                                            | 51       |

|   | 3.2 | Tracing STARPU's behaviour                                                                     | 51       |

|   | 0.2 | 3.2.1 Trace gathering                                                                          | 52       |

|   |     | 3.2.2 Trace exploitation                                                                       | 53       |

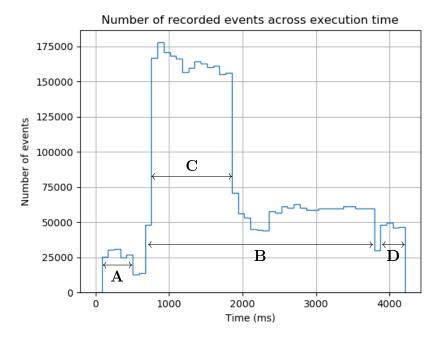

|   | 3.3 | Reducing impact on performance                                                                 | 54       |

|   | 0.0 | 3.3.1 Avoid writing traces on the disk during execution                                        | 54       |

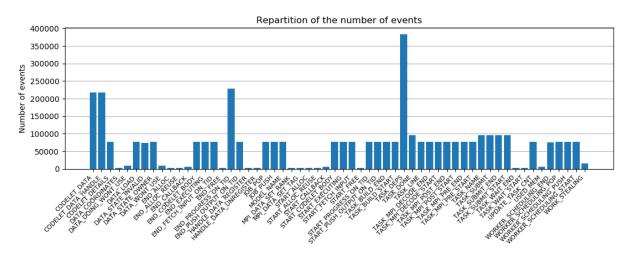

|   |     | 3.3.2 Number of recorded events                                                                | 57       |

|   |     | 3.3.3 Scalability of the number of recording cores                                             | 59       |

|   |     | 3.3.4 Summary about the tracing impact on performance                                          | 62       |

|   | 3.4 | Precise distributed traces                                                                     | 62       |

|   | 0.4 | 3.4.1 Motivation for synchronized clocks                                                       | 62       |

|   |     | 3.4.2 Synchronized clocks in STARPU                                                            | 63       |

|   |     | 3.4.3 Conclusion on synchronizing distributed traces                                           | 03<br>72 |

|   | 3.5 | Lessons learned                                                                                | 72 72    |

|   | 0.0 | 3.5.1 Methodology to apply when tracing applications                                           | 72 72    |

|   |     | 3.5.2 Requirements for an efficient tracing system                                             | 73       |

|   |     | 3.5.3 Extension to other runtime systems                                                       | 73       |

|   | 3.6 | Conclusion                                                                                     | 73<br>74 |

|   | 0.0 |                                                                                                | 14       |

| 4 | Dyr | namic Broadcasts                                                                               | 75       |

|   | 4.1 | Broadcasts in dynamic task-based runtime systems                                               | 75       |

|   | 4.2 | General concepts of dynamic broadcasts                                                         | 77       |

|   |     | 4.2.1 Broadcast detection                                                                      | 77       |

|   |     | 4.2.2 Dynamic broadcast algorithm                                                              | 78       |

|   | 4.3 | Implementation                                                                                 | 80       |

|   |     | 4.3.1 Broadcast detection                                                                      | 80       |

|   |     | 4.3.2 Dynamic broadcast interface                                                              | 80       |

|   |     | 4.3.3 Enforcing communication priorities                                                       | 81       |

|   |     | 4.3.4 Using just received data but still being forwarded                                       | 82       |

|   | 4.4 | Evaluation                                                                                     | 82       |

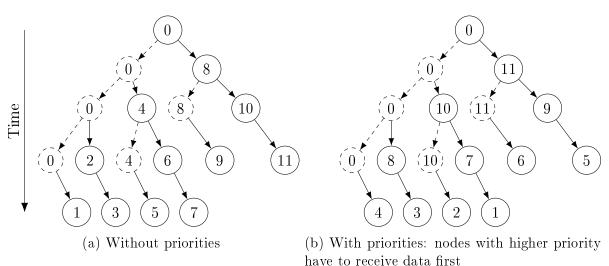

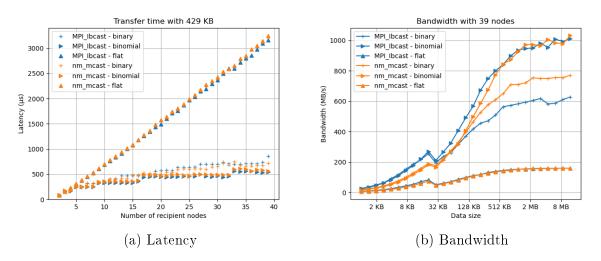

|   |     | 4.4.1 Microbenchmarks                                                                          | 82       |

|   |     | 4.4.2 CHOLESKY factorization                                                                   | 87       |

|   |     | 4.4.3 QR factorization $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 92       |

|   | 4.5 | Discussion                                                                                     | 95       |

|   |     | 4.5.1 Performance analyses                                                                     | 95       |

|   |     | 4.5.2 Generalization and extensions of the concept $\ldots$ $\ldots$ $\ldots$ $\ldots$         | 96       |

|   | 4.6 | Conclusion                                                                                     | 97       |

|   |     |                                                                                                |          |

| 5 | Inte               | erferen | ces between Communications and Computations           | 99                |

|---|--------------------|---------|-------------------------------------------------------|-------------------|

| ļ | 5.1                | Metho   | odology                                               | 100               |

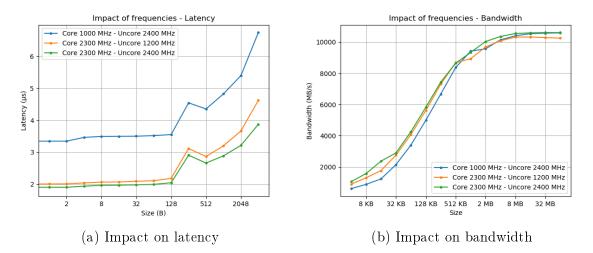

| ļ | 5.2                | Impac   | t of frequencies                                      | 101               |

|   |                    | 5.2.1   | Impact of frequencies on only communications          | 101               |

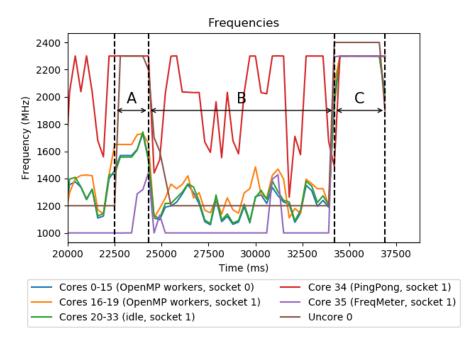

|   |                    | 5.2.2   | Impact of frequency variations caused by computations | 102               |

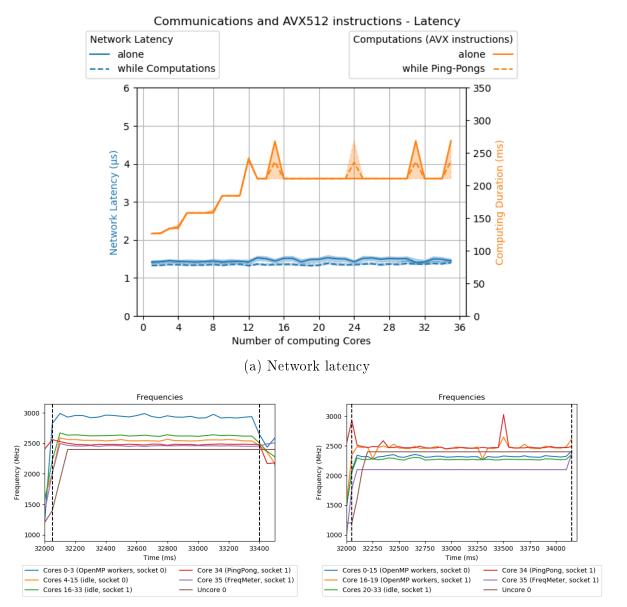

|   |                    | 5.2.3   | Impact of AVX instructions on frequencies             | 104               |

|   |                    | 5.2.4   | Conclusion on the impact of frequency variations      | 104               |

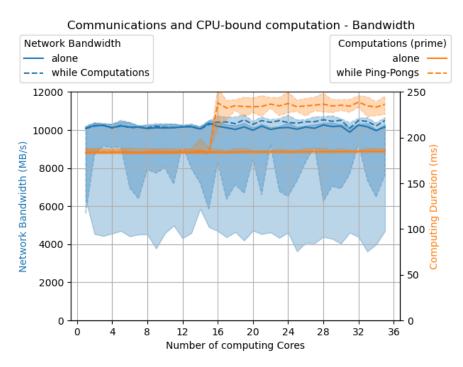

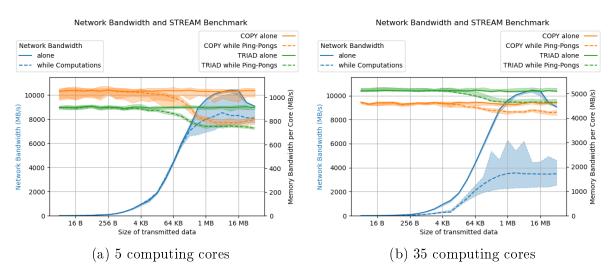

| ļ | 5.3                | Memo    | ry contention                                         | 106               |

|   |                    | 5.3.1   | Benchmarking memory contention                        | 106               |

|   |                    | 5.3.2   | Impact of memory contention                           |                   |

|   |                    | 5.3.3   | Impact of thread and data placement                   |                   |

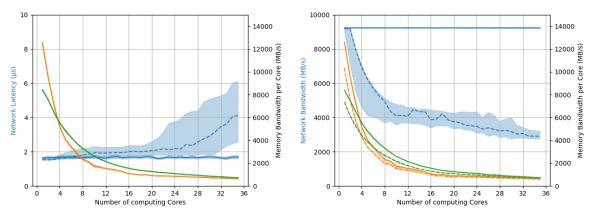

|   |                    | 5.3.4   | Impact of transmitted data size on memory contention  | 110               |

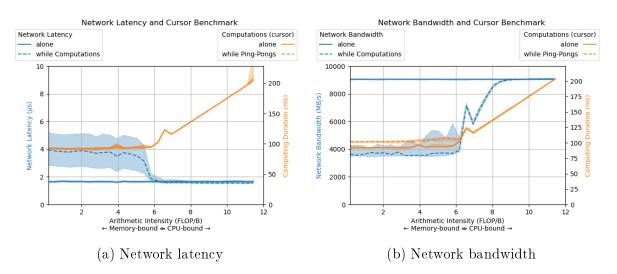

|   |                    | 5.3.5   | From CPU- to memory-bound applications                | 111               |

|   |                    | 5.3.6   | Conclusion on memory contention                       | 112               |

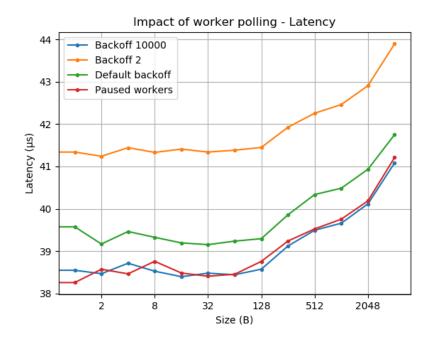

| ļ | 5.4                | Runti   | me system impacts on communications                   |                   |

|   |                    | 5.4.1   | Runtime system overhead                               |                   |

|   |                    | 5.4.2   | MPI thread and data placement                         |                   |

|   |                    | 5.4.3   | Worker polling                                        |                   |

|   |                    | 5.4.4   | Conclusion on runtime system impact                   |                   |

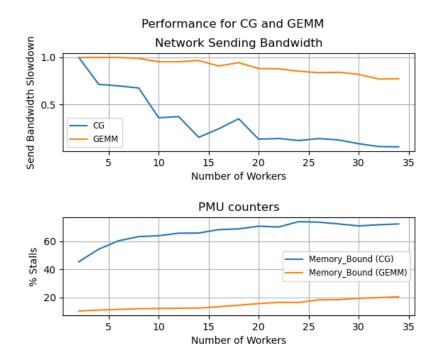

| ļ | 5.5                | Use-ca  | ases: computational kernels                           |                   |

|   | 5.6                |         | usion                                                 |                   |

|   | <b>tati</b><br>6.1 |         | xt and hypotheses                                     | <b>119</b><br>119 |

|   | -                  | 6.1.1   | Contention behaviour                                  |                   |

|   |                    | 6.1.2   | NUMA systems                                          |                   |

|   |                    | 6.1.3   | Last level caches                                     | 121               |

|   |                    | 6.1.4   | Modeling methods                                      | 121               |

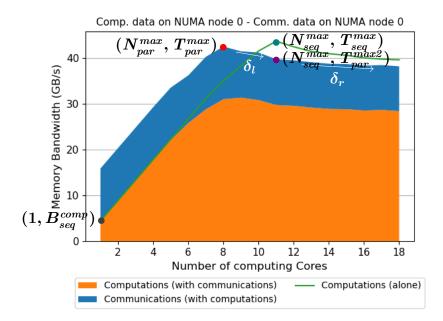

| ( | 6.2                | A mo    | del for memory bandwidth sharing                      |                   |

|   |                    | 6.2.1   | Model parameters                                      |                   |

|   |                    | 6.2.2   | Modeling memory bandwidth                             |                   |

|   |                    | 6.2.3   | Model NUMA effect                                     |                   |

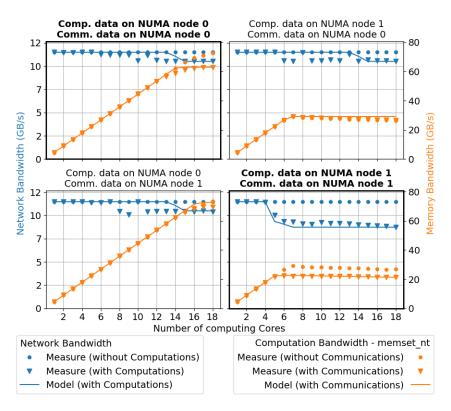

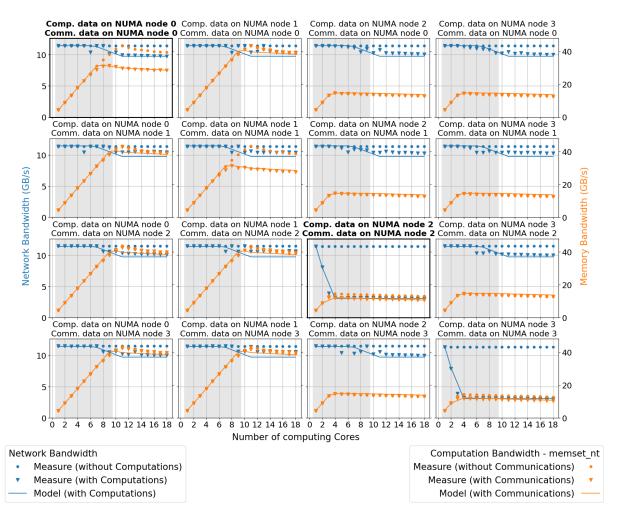

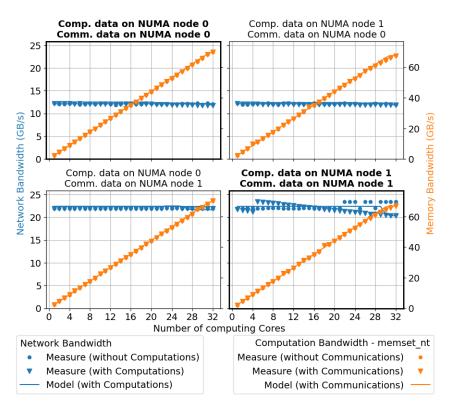

| ( | 6.3                | Evalua  | ation of the model                                    | 127               |

|   |                    | 6.3.1   | Experimental setup                                    | 127               |

|   |                    | 6.3.2   | Results                                               |                   |

|   |                    | 6.3.3   | Discussion                                            | 136               |

| ( | 6.4                | Concl   | usion                                                 | 137               |

| a |                    |         |                                                       | 190               |

|   |                    |         | nd Perspectives                                       | 139               |

| , | Sum                |         | f contributions                                       |                   |

|   |                    |         | ng systems                                            |                   |

|   |                    | •       | nic broadcasts                                        |                   |

| 1 | Domo               |         | erences between computations and communications       |                   |

| _ | r ers              |         | s                                                     |                   |

|   |                    |         | about GPUs?                                           |                   |

|   |                    | vv na t |                                                       | 142               |

#### Contents

|              | Performance model with communications                | . 144<br>. 145      |

|--------------|------------------------------------------------------|---------------------|

| $\mathbf{A}$ | Differences between MPI and NEWMADELEINE backends in |                     |

|              | STARPU<br>MPI backend                                | <b>147</b><br>. 147 |

|              | NEWMADELEINE backend                                 |                     |

| В            | Reproducible Experiments                             | 149                 |

| С            | Machine Descriptions                                 | 151                 |

| D            | Algorithms to Model Memory Contention                | 161                 |

| $\mathbf{E}$ | Parameter Values of Contention Model                 | 165                 |

| Ac           | Acronyms 1                                           |                     |

| Re           | References 1                                         |                     |

| Pτ           | Publications                                         |                     |

| So           | ftware Contributions                                 | 185                 |

# List of Figures

| Typical memory hierarchy.                                                                    | 15                                                    |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Characteristics of different memory kinds.                                                   | 16                                                    |

|                                                                                              | 17                                                    |

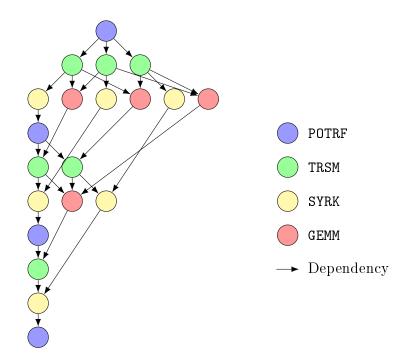

|                                                                                              | 25                                                    |

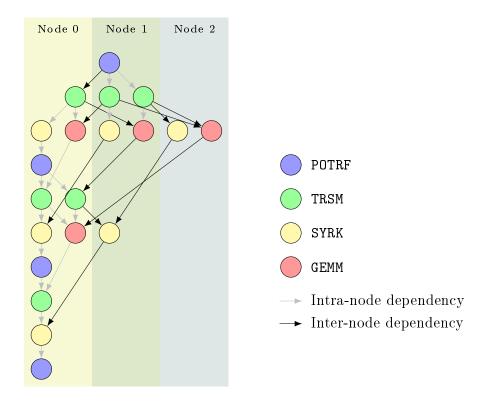

| Distribution of the CHOLESKY DAG on 3 nodes                                                  | 28                                                    |

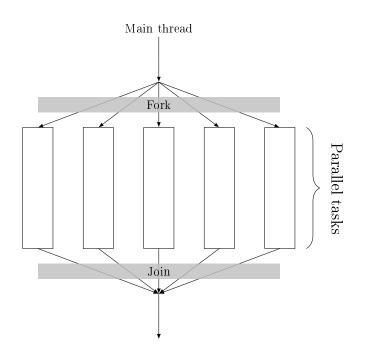

| The fork-join model.                                                                         | 34                                                    |

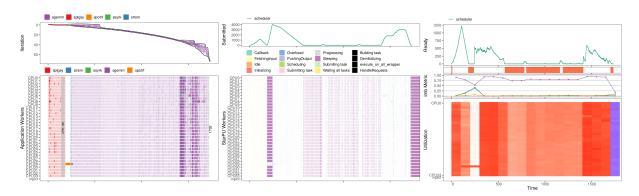

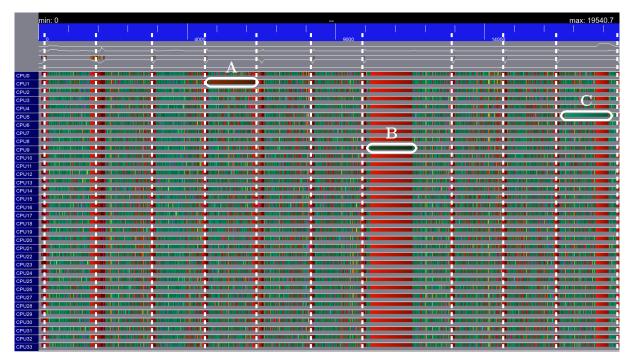

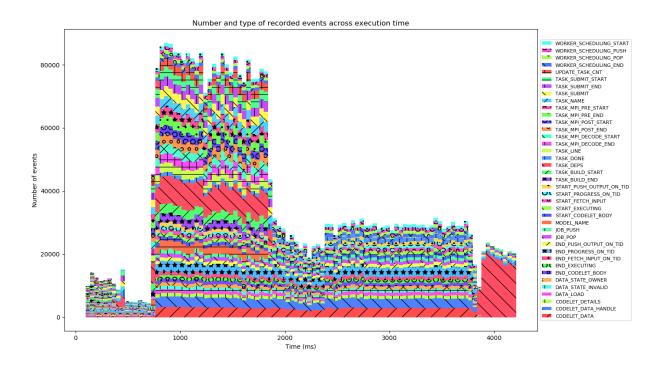

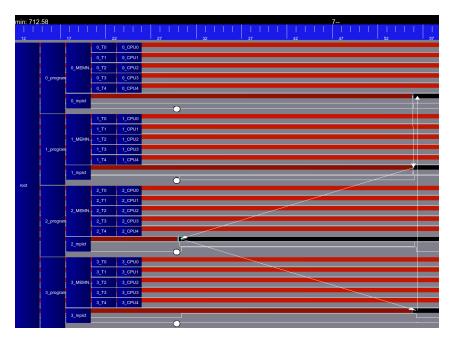

| Example of visualization of an execution of the CHOLESKY algorithm with the STARVZ framework | 53                                                    |

|                                                                                              | 55                                                    |

|                                                                                              | 55                                                    |

|                                                                                              | 00                                                    |

|                                                                                              | 56                                                    |

|                                                                                              | 57                                                    |

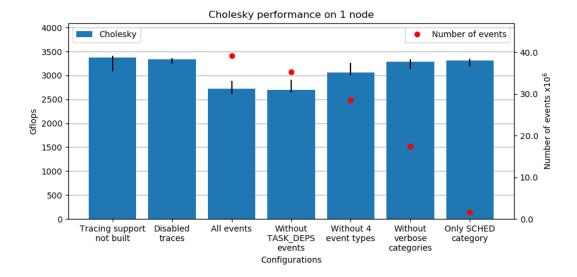

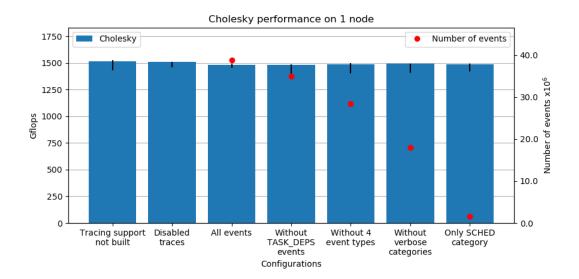

|                                                                                              | 58                                                    |

|                                                                                              | 58                                                    |

|                                                                                              | 60                                                    |

|                                                                                              |                                                       |

|                                                                                              | 60                                                    |

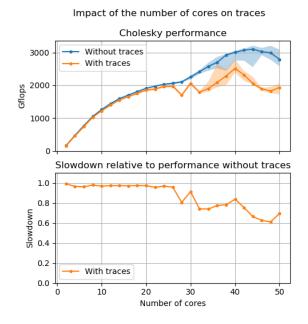

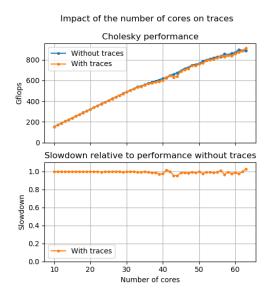

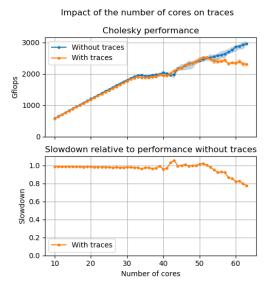

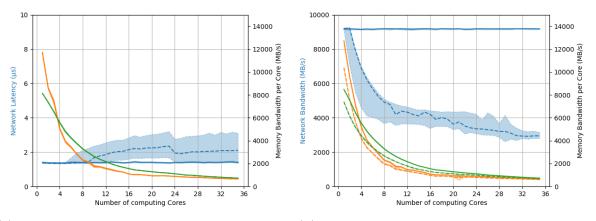

| Impact of the number of cores on performance with traces on peabody                          | 61                                                    |

| Impact of the number of cores on performance with traces on zonda, with                      |                                                       |

| AMD processor and badly configured MKL library.                                              | 61                                                    |

| Impact of the number of cores on performance with traces on zonda, with                      |                                                       |

| AMD processor and correctly configured MKL library.                                          | 61                                                    |

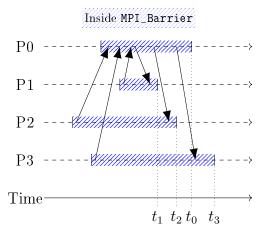

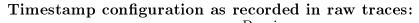

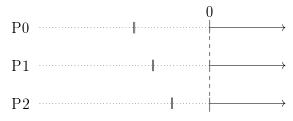

| MPI_Barrier: Not all processes leaves the barrier at the same time                           | 64                                                    |

| The communication from node 1 to node 2 is received before it is sent!                       | 64                                                    |

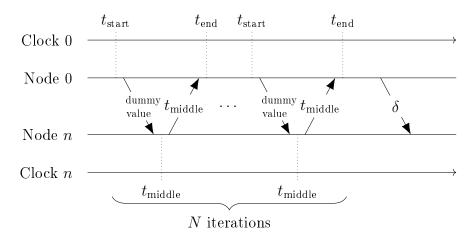

| How clock offset $\delta$ is computed between nodes 0 and $n$                                | 65                                                    |

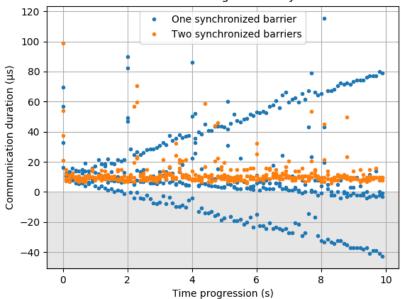

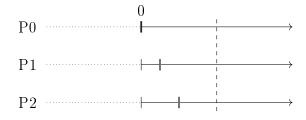

| Communications duration over time: two synchronized barriers are re-                         |                                                       |

| quired to take into account clock drifts                                                     | 67                                                    |

|                                                                                              | 70                                                    |

|                                                                                              |                                                       |

| tive timestamps                                                                              | 71                                                    |

|                                                                                              | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |

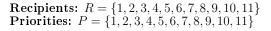

| 4.1  | Examples of routing trees for 6 recipients.                                          | . 78  |

|------|--------------------------------------------------------------------------------------|-------|

| 4.2  | Tree reordering to take into account communication priorities                        | . 81  |

| 4.3  | Microbenchmarks of the dynamic broadcasts with NEWMADELEINE, on                      |       |

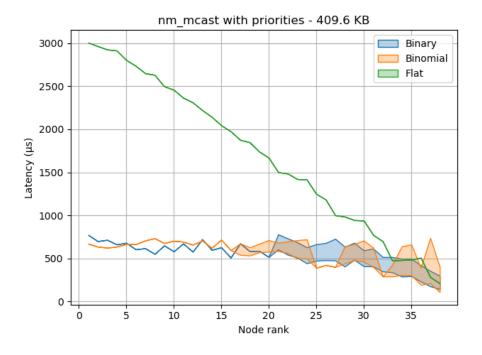

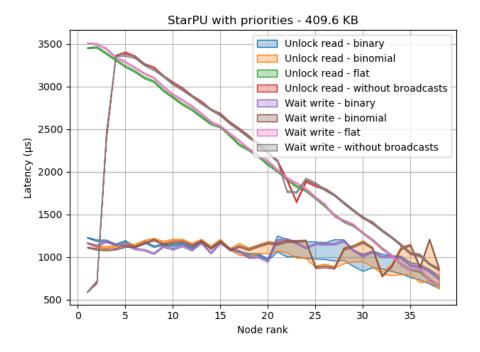

|      | occigen                                                                              | . 83  |

| 4.4  | Microbenchmarks of the dynamic broadcasts with STARPU and NEW-                       |       |

|      | MADELEINE, on occigen.                                                               | . 84  |

| 4.5  | Microbenchmark to check the respect of priorities in dynamic broadcasts              |       |

|      | with NEWMADELEINE, on occigen.                                                       | . 85  |

| 4.6  | Microbenchmark to check the respect of priorities in dynamic broadcasts              |       |

|      | and impact of unlocking tasks as soon as data is received, with STARPU               |       |

|      | and NEWMADELEINE, on occigen                                                         | . 86  |

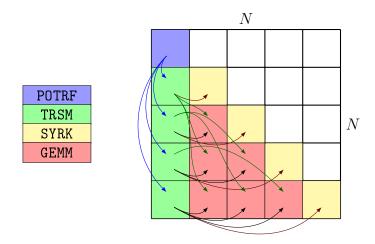

| 4.7  | The two different types of broadcasts for the CHOLESKY factorization.                | . 87  |

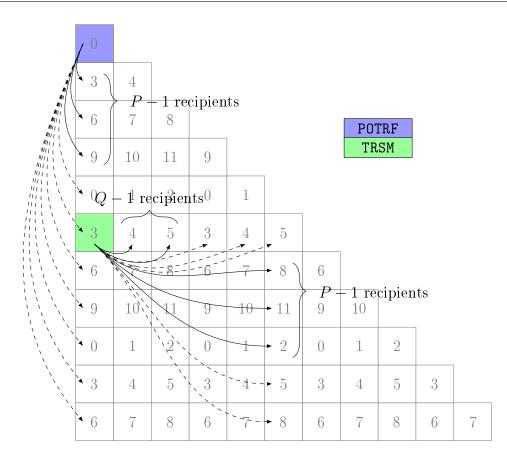

| 4.8  | Recipients in the two types of broadcasts in the CHOLESKY algorithm on               |       |

|      | a 2D-block-cyclic distribution $(P,Q) = (4,3)$ .                                     |       |

| 4.9  | Performance of CHOLESKY factorization, on inti (old implementation).                 | . 89  |

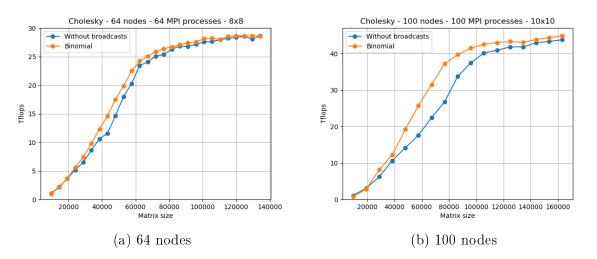

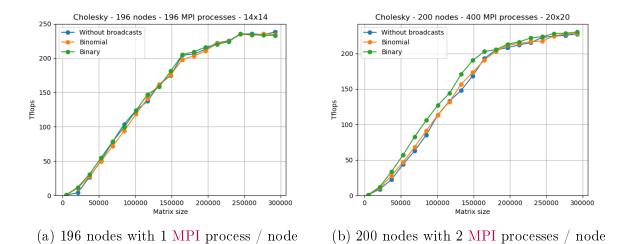

| 4.10 | Performance of CHOLESKY factorization, on occigen                                    | . 90  |

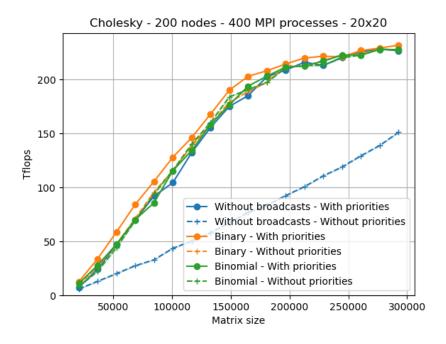

| 4.11 | Impact of priorities on CHOLESKY factorization, on occigen                           | . 91  |

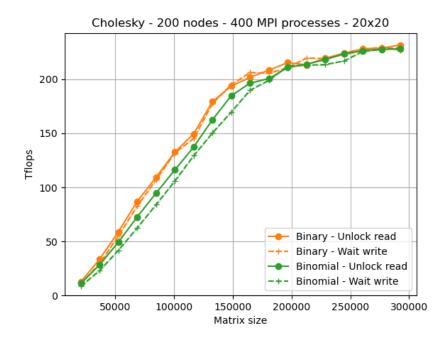

| 4.12 | Impact of reading data as soon as possible on CHOLESKY factorization, on             |       |

|      | occigen                                                                              |       |

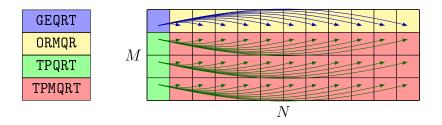

| 4.13 | The two different types of broadcasts for the QR factorization                       |       |

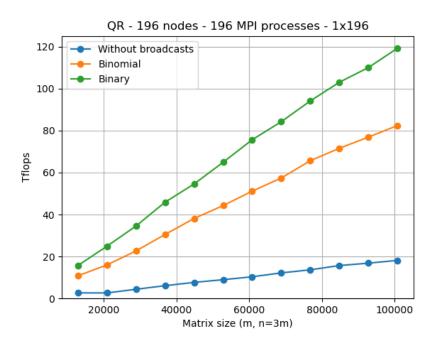

| 4.14 | Performance of QR factorization, on occigen                                          | . 93  |

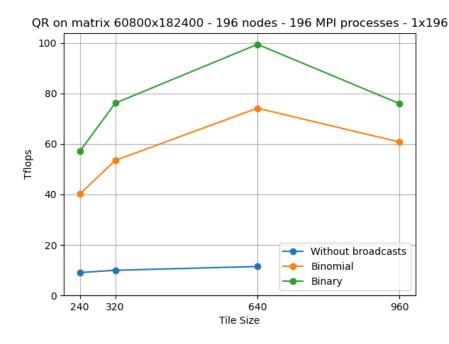

| 4.15 | Impact of the tile size on QR factorization, on occigen.                             | . 94  |

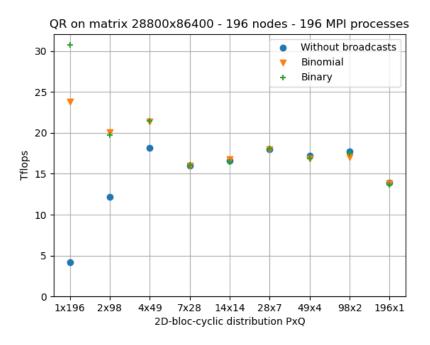

| 4.16 | Impact of the 2D-block-cyclic distribution parameters on $\mathbf{QR}$ factorization | 95    |

| 5.1  | Impact of constant frequencies on network performance, on henri nodes.               | . 102 |

| 5.2  | Frequency variations during only communications, sleep and simultaneous              |       |

|      | communications and computations.                                                     | . 103 |

| 5.3  | CPU-bound computations and network bandwidth performance, on bora                    |       |

|      | nodes.                                                                               | . 103 |

| 5.4  | Impact of AVX512 computations on network latency, on henri nodes with                |       |

|      | turbo-boost.                                                                         | . 105 |

| 5.5  | Diagram of different data streams in an HPC node.                                    |       |

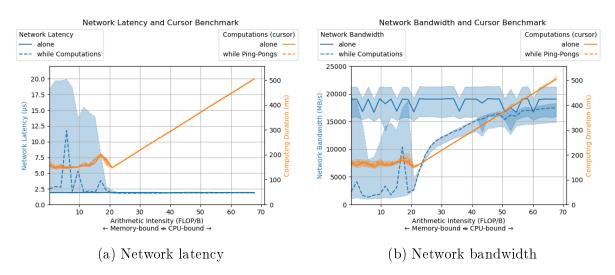

| 5.6  | Memory-bound computations and network performance, on henri nodes.                   |       |

| 5.7  | Memory-bound computations and network bandwidth performance, on                      |       |

|      | bora nodes.                                                                          | . 108 |

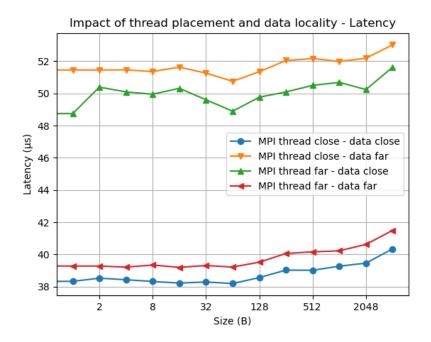

| 5.8  | Impact of communication thread placement and data locality, on henri                 |       |

|      | nodes.                                                                               | . 109 |

| 5.9  | Impact of size of communicated data, on henri nodes.                                 | . 110 |

| 5.10 | Impact of memory pressure on network performance, on henri nodes                     |       |

| 5.11 | Impact of memory pressure on network performance, on billy nodes                     | . 112 |

|      | Impact of data locality and thread placement on network latency with                 |       |

|      | STARPU, on henri nodes.                                                              | . 113 |

| 5.13 | Impact of polling workers on network latency, on henri nodes                         |       |

|      | Network performance and hardware counter values of CG and GEMM execu-                |       |

|      | tions, on henri nodes.                                                               | . 116 |

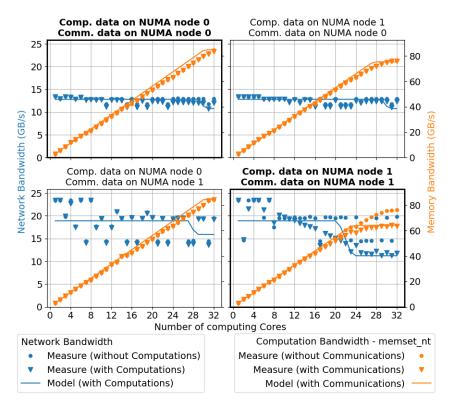

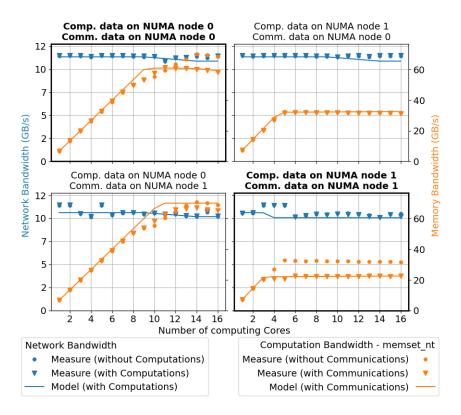

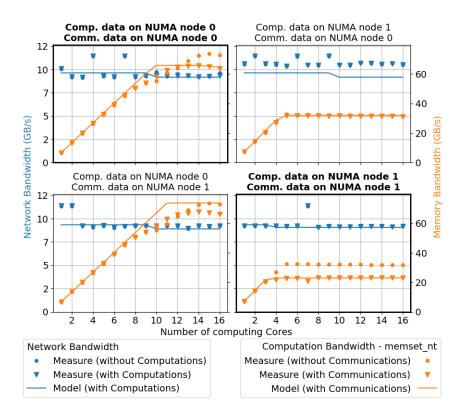

| 6.1  | Stacked memory bandwidth for computations and communications, with  |     |

|------|---------------------------------------------------------------------|-----|

|      | coordinates of the interesting points to instantiate the model      | 123 |

| 6.2  | Performance of computations and communications along with our model |     |

|      | prediction, on henri nodes (INTEL, INIFINIBAND)                     | 129 |

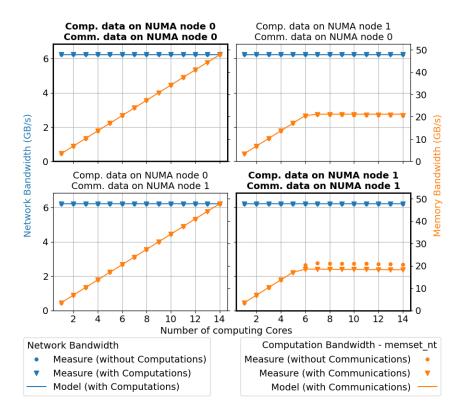

| 6.3  | Performance of computations and communications along with our model |     |

|      | prediction, on henrisubnuma nodes (INTEL, INIFINIBAND)              | 130 |

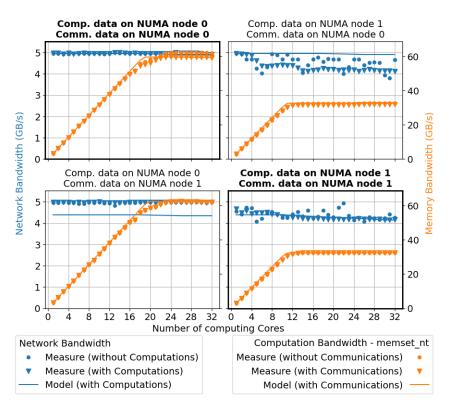

| 6.4  | Performance of computations and communications along with our model |     |

|      | prediction, on diablo nodes (AMD, INIFINIBAND)                      | 131 |

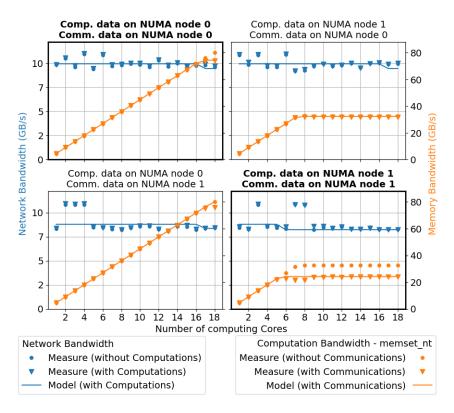

| 6.5  | Performance of computations and communications along with our model |     |

|      | prediction, on billy nodes (AMD, INIFINIBAND).                      | 132 |

| 6.6  | Performance of computations and communications along with our model |     |

|      | prediction, on occigen nodes (INTEL, INIFINIBAND).                  | 132 |

| 6.7  | Performance of computations and communications along with our model |     |

|      | prediction, on pyxis nodes (ARM, INIFINIBAND).                      | 133 |

| 6.8  | Performance of computations and communications along with our model |     |

|      | prediction, on <b>bora</b> nodes (INTEL, OMNI-PATH).                | 134 |

| 6.9  | Performance of computations and communications along with our model |     |

|      | prediction, on dahu nodes (INTEL, OMNI-PATH)                        | 134 |

| 6.10 | Performance of computations and communications along with our model |     |

|      | prediction, on grvingt nodes (INTEL, OMNI-PATH)                     | 135 |

|      |                                                                     |     |

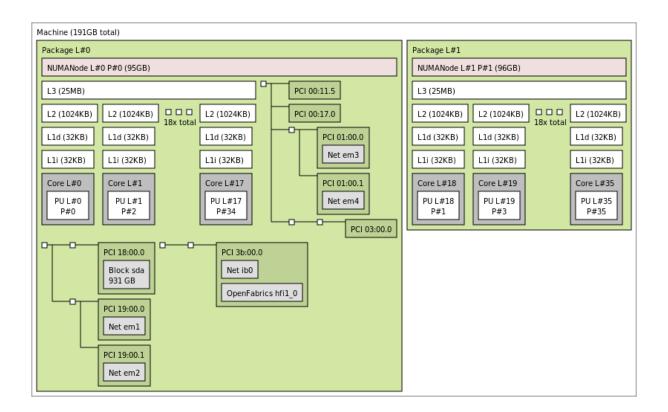

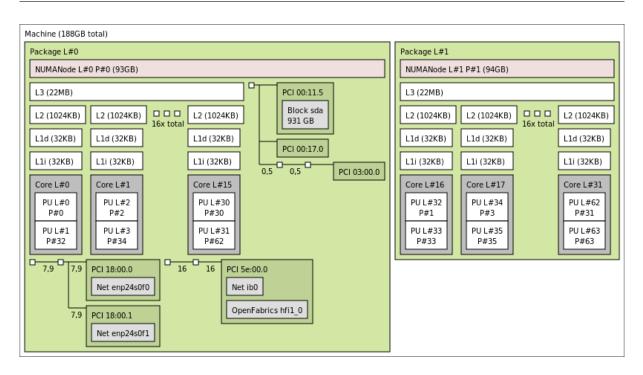

| C.1  | billy's topology.                                                   |     |

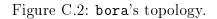

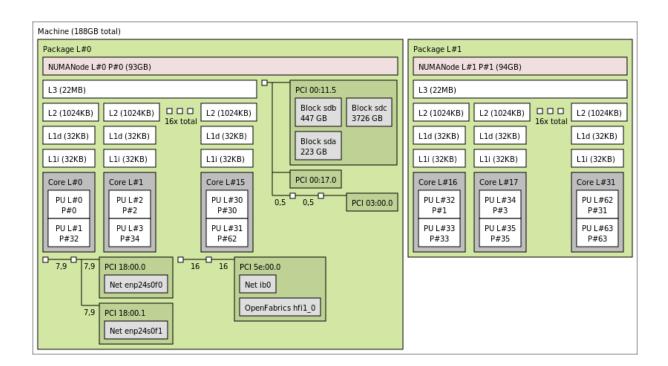

| C.2  | bora's topology.                                                    |     |

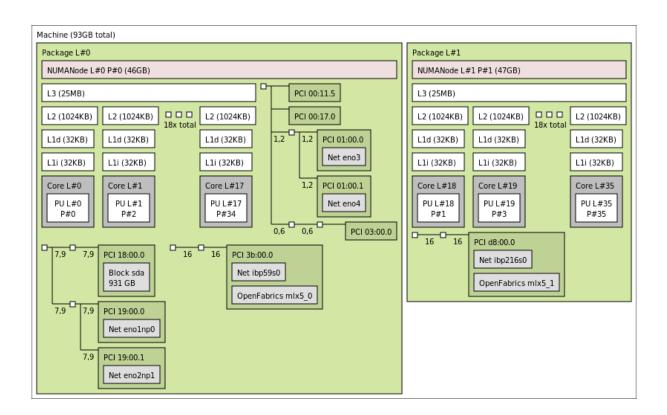

| C.3  | dahu's topology.                                                    |     |

| C.4  | diablo's topology.                                                  |     |

| C.5  | grvingt's topology.                                                 |     |

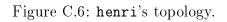

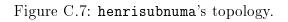

| C.6  | henri's topology.                                                   |     |

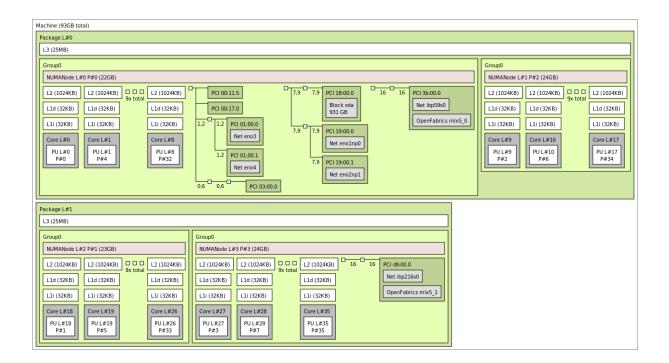

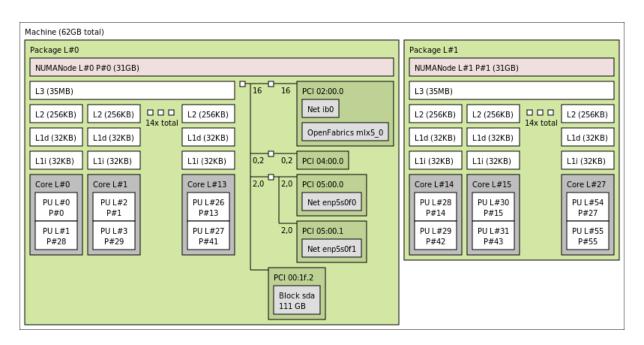

| C.7  | henrisubnuma's topology.                                            |     |

| C.8  | occigen's topology.                                                 | 157 |

| C.9  | peabody's topology.                                                 | 158 |

| C.10 | pyxis's topology.                                                   | 159 |

| C.11 | zonda's topology.                                                   | 159 |

## Remerciements

$\prod$  ROIS années de thèse sont passées, le manuscrit a été rédigé et la soutenance s'est clôturée par le fameux « nous vous décernons le titre de Docteur en Informatique de l'Université de Bordeaux ». Il semblerait bien qu'il ne reste plus qu'à rédiger les remerciements pour vraiment achever cette thèse.

Tout d'abord, merci au jury. Merci à Arnaud et Didem pour avoir relu ce (long et dense) manuscrit. J'espère que vous avez pris autant de plaisir à le lire que j'en ai eu lors de l'écriture. Merci pour vos commentaires constructifs qui ont permis de l'améliorer. Merci à George pour avoir accepté d'être examinateur, avoir un développeur de PARSEC dans le jury d'une thèse qui traite principalement de STARPU me semblait à la fois intéressant et audacieux! Merci à Denis pour avoir présidé le jury.

Les remerciements suivants s'adressent aux deux personnes qui ont permis à cette thèse d'être ce qu'elle est aujourd'hui : Alexandre et Emmanuel. Votre encadrement et votre soutien sans faille pendant ces trois années (voire plus pour Alexandre si on compte sa casquette de maître de stage) ont été très importants pour moi. Merci pour m'avoir transmis (une partie de) votre savoir, pour m'avoir fait découvrir le monde de la recherche ainsi que le raisonnement et la méthode scientifiques en informatique. Je pense qu'on a aussi les mêmes exigences en terme de travail bien fait et pour aller au fond des choses ; je trouve toujours agréable de travailler avec des personnes qui ont les mêmes attentes que moi, j'espère que c'était pareil pour vous. Avoir deux encadrants peut parfois être déstabilisant quand l'un dit *noir* et l'autre dit *blanc*, mais ces divergences d'opinions (finalement peu nombreuses) ont su être masquées par votre complémentarité. Je me demande parfois quelle est la part des encadrants dans le travail et les résultats d'un doctorant, à quel point *ma* thèse est aussi la vôtre : je vous laisse répondre à cette question, et peut-être que le futur me donnera aussi la réponse !

Un merci plus collectif à toute l'équipe TADAAM, la meilleure équipe de l'INRIA BORDEAUX! Merci à Brice, François, Guillaume, Guillaume et Francieli pour hwloc, le droit des logiciels, la théorie qui m'est imperméable, le standard MPI, les I/Os, le Brésil, les Ardennes, le baby-foot, le militantisme syndical, les râleries sur les étudiants, la médiation scientifique, les fous-rires mais aussi le sérieux quand il s'agit de travailler (un petit jeu : saurez-vous relier chaque terme au permanent correspondant ?). Ensuite, merci à l'openspace, tout d'abord pour m'avoir supporté, merci à ceux que j'appelle mes grands-frères de thèse : Valentin, Andrès, Nicolas et Florian. Votre parcours durant la thèse m'a aidé d'une manière ou d'une autre dans ma thèse à moi. Après les grands-frères, les petits-frères de thèse : Alexis, Clément, Robin, Julien et Richard. J'espère (humblement) aussi avoir réussi à vous transmettre ce que mes grands-frères m'ont transmis. Bon courage pour la suite de vos thèses et profitez bien, la fin et l'après-thèse ne sont pas vraiment les périodes les plus agréables... Merci aux autres qui sont passés par l'open-space, quelque soit leur statut : Luan, Clément, Clément, Adrien, Valentin, Corentin et Amaury. Merci aux intrus de l'open-space, Luc et Romain, qui n'étaient pas de TADAAM et qui couvraient les tableaux de signes bizarres ! Un merci particulier à Alexis et Luan, comme fidèles compagnons pour la découverte par deux fois des États-Unis. Pour finir avec les membres de l'équipe, un grand merci à Catherine, qui, avec une grande gentillesse et une patience à toute épreuve, a toujours su m'assister dans toutes mes démarches administratives.

Merci aux autres équipes HPC du centre, STORM et HIEPACS. J'ai tellement travaillé et discuté avec les membres de STORM, que j'avais l'habitude de dire que j'étais à moitié de membre aussi de STORM! Merci en particulier à Samuel et Nathalie pour les discussions techniques (ou pas) et à Mathieu, Emmanuel et Pierre pour, entre autres, leurs explications des algorithmes d'algèbre linéaire.

Merci ensuite à tout ce qui gravite autour de la recherche : le SED pour les discussions techniques (ou pas), le SCM pour la médiation scientifique (mais pas que), les enseignements à l'ENSEIRB-MATMECA (merci à, entre autres, David et Mathieu), Ludovic pour GUIX et les notions de recherche reproductible, le monde du libre en général et tous ceux qui y contribuent. Et parce que c'est presque le seul outil dont on a besoin pour faire de la recherche en HPC, merci aux plateformes de calculs, en particulier les DALTON et PLAFRIM. Merci aux personnes qui les administrent, ça fait toujours plaisir de pouvoir discuter de vive voix de ce qui fonctionne et ce qui ne fonctionne pas!

*Pas* merci au Covid-19, qui nous aura forcé au télétravail une bonne partie de la thèse et nous aura privé de <del>séjours touristiques</del> conférences à Varsovie, Lisbonne, Bonn, Lyon, Seattle, ou encore à Chicago. Difficile de dire quelle voie aurait pris cette thèse sans cette pandémie...

Merci à ma famille pour son soutien indéfectible, sans jamais poser de questions, alors même qu'elle ne comprend pas un mot de mes sujets de recherche (et ce n'est pas faute d'avoir essayé de l'expliquer)! Et merci à Hélène pour s'être gentiment proposée pour faire le dessert de mon pot de thèse.

Pour finir, merci à toutes celles et ceux que j'ai pu oublier, mais qui ont été près ou loin de moi lors de cette thèse.

## Résumé étendu en français

Les problèmes numériques complexes (comme les simulations, les prévisions météorologiques, la climatologie, la cosmologie, la biologie, la chimie, les phénomènes physiques, etc) font parties des applications ciblées par le calcul haute-performance (en anglais HighPerformance Computing – HPC). Ces applications demandent généralement une puissance de calcul importante ainsi qu'une grande quantité de mémoire pour être exécutées, les rendant hors de portée des ordinateurs classiques. A la place, ces applications sont exécutées sur des supercalculateurs qui sont un ensemble d'ordinateurs (appelés  $n \alpha u ds$ ) individuellement très puissants, inter-connectés ensemble par un réseau rapide. Les programmes peuvent alors faire des calculs sur plusieurs nœuds simultanément, permettant d'agréger la puissance de calcul de ces nœuds. Dans ce cas, une bibliothèque logicielle de communication réseau s'occupe de déplacer les données entre les différents nœuds, par exemple lorsque le résultat d'un calcul intermédiaire effectué sur un certain nœud est nécessaire sur un autre nœud pour lancer un autre calcul. Concernant les nœuds de calcul, leur conception ainsi que leur utilisation se sont complexifiées au fil du temps, en même temps que leur puissance de calcul augmentait. De nos jours, les nœuds de calcul équipant les supercalculateurs ont chacun des unités de calcul de différents types (CPU, GPU, FPGA, etc) qui ne se programment pas de la même manière et qui sont plus ou moins efficaces selon le type d'instructions qu'ils doivent exécuter. Cela rend la conception d'applications plus complexe, puisqu'il faut minutieusement choisir quelle unité de calcul va exécuter quelle opération. De plus, cette décision impacte également les transferts de données nécessaires entre les différentes mémoires disponibles au sein d'un nœud. Mal gérés, ces transferts mémoires peuvent être très lents et devenir un facteur limitant de l'application. Pour résumer, l'hétérogénéité présente dans les nœuds de calcul actuels rend difficile l'utilisation efficace de toute la puissance de calcul qu'un nœud est (théoriquement) capable de fournir.

Face à ces difficultés, les *support d'exécutions à tâches* (en anglais *task-based runtime systems*) connaissent un bel essor. Leur modèle de programmation repose sur la représentation des applications par un graphe de tâches : chaque opération de l'application est représentée par une tâche qui est un sommet du graphe. Chaque opération produit des données, qui peuvent être utilisées en entrée d'autres opérations. Ces dépendances entre tâches sont les arêtes du graphe de tâches. Pour chaque tâche, les instructions à effectuer sur chaque unité de calcul ciblée doivent être fournies, ainsi que les dépendances entre les tâches. Le support d'exécution se charge ensuite du reste : ordonnancer les tâches sur les unités de calcul, faire les transferts de données nécessaires, exécuter les tâches, ... L'écriture d'application parallèle est facilitée avec le modèle de programmation à tâches, puisque c'est le support d'exécution qui infère le parallélisme de l'application, à partir des dépendances entre tâches qui forment le graphe de tâches. Dans le cas d'applications distribuées (utilisant plusieurs nœuds), le support d'exécution à tâches peut également découvrir et s'occuper des communications réseau nécessaires, mais en déléguant généralement la réalisation de ces communications à une bibliothèque tierce.

Habituellement, les supports d'exécution et les bibliothèques de communications sont deux briques logicielles bien distinctes. Le support d'exécution utilise l'interface de la bibliothèque de communication, et cette dernière se contente de traiter les requêtes qui lui sont adressées : elle n'a pas d'informations particulières sur l'application exécutée, ni sur l'état courant du support d'exécution. Cependant, le support d'exécution peut avoir des informations qui permettraient d'aider la bibliothèque de communication dans ses prises de décisions (les futures communications à exécuter, les priorités des tâches, le chemin critique de l'application, *etc*). De la même façon, la bibliothèque de communications possède une vision sur le réseau et les communications en cours, et certaines informations pourraient être utiles au support d'exécution (par exemple : les messages reçus incessamment sous peu, une estimation de la durée des communications).

Le but de cette thèse est d'**explorer les interactions possibles entre les supports** d'exécutions à tâches et les bibliothèques de communications, en échangeant plus d'informations entre ces deux couches logicielles, afin d'améliorer les décisions de l'un et l'autre et finalement augmenter les performances des applications.

Ce manuscrit présente les contributions réalisées en ce sens pendant trois années de thèse. Tout d'abord, une évaluation et amélioration des outils de traces pour analyser l'exécution des applications à base de tâches (et ainsi mieux comprendre les interactions entre le support d'exécution et les communications) ont été réalisées. Une première interaction positive entre supports d'exécution à tâches et bibliothèque de communications a été proposée en implémentant une solution pour être capable d'envoyer efficacement une même donnée à plusieurs nœuds différents. Nous avons également étudié les interactions négatives, en évaluant les différentes sources d'interférences possibles entre calculs et communications, lorsqu'ils sont exécutés en parallèle, comme c'est le cas dans de nombreux supports d'exécutions à tâches. Puisqu'il s'est avéré que la contention mémoire entre les accès mémoires pour les calculs et les communications est la plus grande source d'interférences pénalisant leurs performances respectives, nous avons proposé un modèle pour prédire la bande-passante mémoire accordée à chaque type de flux (calculs ou communications). Ce modèle nous a permis de mieux comprendre le fonctionnement de la mémoire en cas de contention et de pouvoir prédire les performances des calculs et des communications. La suite de ce résumé détaille ces différentes contributions.

## Évaluation et amélioration du système de traces

Pour comprendre les performances et le comportement des applications, tracer leurs exécutions et analyser les détails du déroulement de l'exécution peut être une méthode très efficace. Pour être suffisamment robustes, les systèmes de traces doivent avoir une précision satisfaisante et interférer au minimum avec l'exécution de l'application tracée. Avoir un impact sur l'application tracée peut changer son comportement, ce qui signifie que l'exécution décrite dans les traces est différente de l'exécution standard (non tracée). Ce phénomène peut être gênant, puisque les traces servent généralement à comprendre ce qui se passe lorsqu'une application n'est pas tracée! Un système de traces pas assez précis, avec des horloges mal synchronisées, produira des traces incohérentes, notamment concernant les exécutions distribuées (par exemple : un message peut apparaître comme reçu avant d'avoir été envoyé).

Nous avons évalué les différentes sources possibles de surcoût en terme de performances de l'application, pouvant changer le comportement d'une application, lorsqu'une application utilisant un support d'exécution à tâches est tracée. Nous avons également proposé des solutions pour éviter (ou au moins réduire) ces surcoûts. De plus, nous avons implémenté dans le système de traces du support d'exécution des techniques de synchronisation d'horloges correspondant à l'état de l'art, et nous avons évalué l'amélioration de la précision des traces ainsi obtenues.

En plus de proposer des solutions aux problèmes causés par les systèmes de traces, notre travail avait aussi pour but de faire prendre conscience aux personnes utilisant ces systèmes de traces les potentiels problèmes qui peuvent survenir lors de la trace de programmes, potentiellement déformant la réalité.

Ce travail peut être perçu comme un pré-requis pour analyser sereinement les exécutions d'applications, tout en ayant en tête les possibles problèmes.

## Broadcasts dynamiques

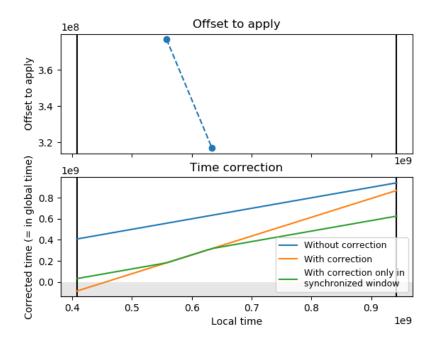

Les communications sont l'un des facteurs limitant pour faire passer les applications à l'échelle sur de nombreux nœuds. Un motif de communications qui peut facilement s'optimiser à l'aide d'algorithmes de routages déjà présents dans la littérature, et qui se retrouve dans les graphes de tâches de certaines applications, est l'envoi de la même donnée à plusieurs nœuds distincts. Ce motif s'appelle un *broadcast*.

Les bibliothèques de communications habituelles en HPC proposent des routines pour exécuter des broadcasts d'une façon optimale. Cependant, plusieurs critères doivent être remplis pour pouvoir utiliser ces fonctions : par exemple, tous les nœuds impliqués dans le broadcast doivent faire appel à la même fonction avec les mêmes paramètres, en particulier la liste de tous les destinataires de la donnée. De plus, ce genre de fonction introduit une sorte de synchronisation, qui, pour des raisons de performances, doit être évitée autant que possible dans les supports d'exécution à tâches. Malheureusement, ces contraintes ne sont pas satisfaites dans le contexte du support d'exécution considéré : les broadcasts n'y sont pas explicites (ils doivent être inférés à partir du graphe de tâches) et seulement l'émetteur du broadcast connaît tous les destinataires. Les destinataires, quant à eux, ne savent même pas s'ils vont recevoir le message par un broadcast ou par une communication point-à-point classique (et donc ne savent pas quelle fonction appeler).

Pour pouvoir profiter d'algorithmes de routages efficaces, tout en respectant les contraintes du support d'exécution à tâches, nous avons proposé des *broadcasts dyna*-

*miques*. Le mécanisme pour détecter les broadcasts a une fiabilité satisfaisante, et une fois qu'une donnée à envoyer par un broadcast est disponible, l'interface que nous avons développée dans la bibliothèque de communication le prend en charge de façon transparente pour le support d'exécution : la donnée venant d'un broadcast est reçue comme si elle était reçue par une communication point-à-point.

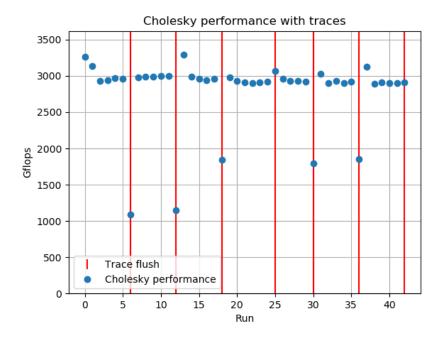

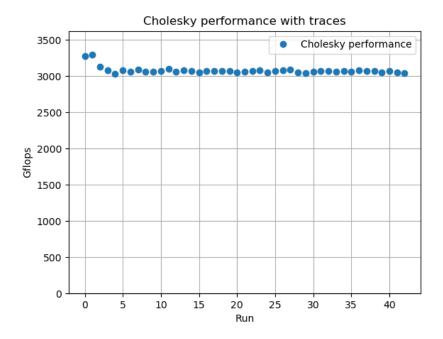

Des microbenchmarks ont montré l'efficacité de notre implémentation. Les gains de performances pour les applications avec des broadcasts dans leurs graphes de tâches dépendent de plusieurs facteurs. Les broadcasts dynamiques ont permis d'améliorer les performances de 30% sur des factorisations de CHOLESKY et de multiplier par 6 les performances de factorisations QR sur des matrices avec une forme et une distribution spécifiques.

La pertinence des broadcasts dynamiques montre le potentiel des interactions entre les supports d'exécution à tâches et les bibliothèques de communications : à l'aide d'une interface simple et générique exposée par la bibliothèque de communications, le support d'exécution peut exécuter des broadcasts plus efficacement.

## Interférences entre calculs et communications

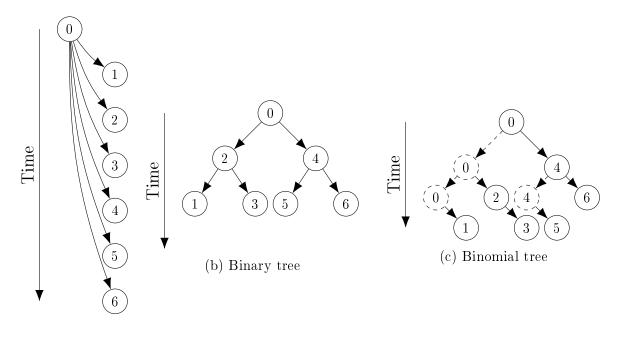

La plupart des supports d'exécutions à tâches permettent d'exécuter en parallèle calculs et communications. Puisque cela signifie exécuter simultanément des calculs et des communications qui partagent ressources matérielles communes, nous avons évalué les possibilités d'interférences entre calculs et communications, impactant leurs performances respectives.

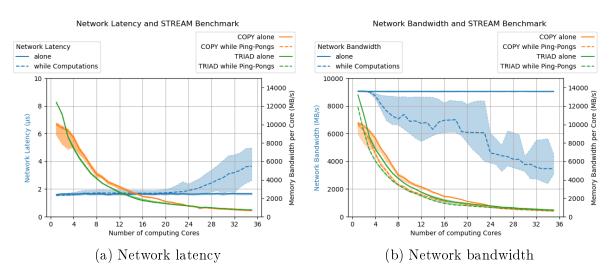

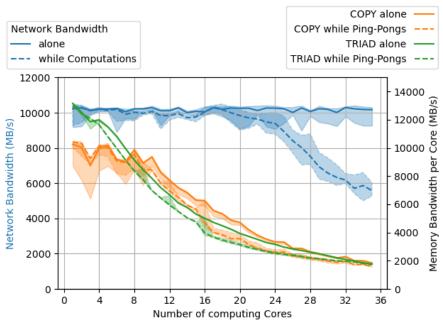

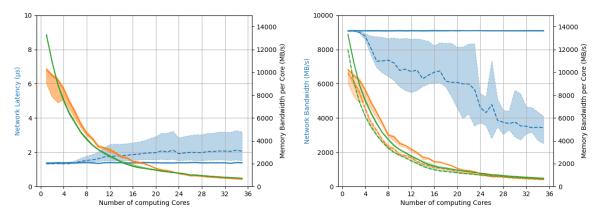

Les variations de fréquences causées par les calculs n'ont pas d'impact majeur sur les performances des communications. Les communications lancées par le support d'exécution peuvent être pénalisées par un surcoût en latence important, à cause de la pile d'appel de fonctions à traverser avant d'atteindre la bibliothèque de communications. Mais la dégradation de performances la plus importante, lorsque calculs et communications sont exécutés en parallèle, provient de la contention mémoire entre les mouvements de données pour les calculs et pour les communications.

La contention mémoire peut être influencée par plusieurs facteurs : le placement des données et des threads, la taille des messages et l'intensité arithmétique des calculs. Lorsque de la contention mémoire se produit, les performances des calculs peuvent être impactées, mais ce sont les communications qui sont le plus pénalisées.

Pour mieux comprendre la contention mémoire se produisant entre calculs et communications et être capable de la prédire, nous avons proposé un modèle de ce phénomène donnant le débit mémoire accordé aux calculs et aux communications, selon le nombre de cœurs exécutant des calculs et le placement des données. La difficulté de conception du modèle venait du fait que la gestion de la contention par les composants mémoire des processeurs est un secret bien gardé des fabriquants. L'évaluation de notre modèle sur une large gamme de machines aux caractéristiques différentes ont confirmé nos hypothèses initiales : tant qu'il n'y a pas de contention, calculs et communications obtiennent la bande-passante mémoire qu'ils requièrent ; lorsque la capacité du bus mémoire est atteinte, la bande-passante pour les communications est d'abord réduite, pour préserver celle des cœurs qui calculent ; une bande-passante minimale est tout de même toujours assurée pour les communications, pour éviter les famines ; finalement, si la demande en débit mémoire continue d'augmenter, alors les cœurs de calcul sont également pénalisés.

Bien que ces interactions négatives entre calculs et communications apparaissent dans tout programme qui exécute simultanément des calculs et des communications, quel que soit le support d'exécution utilisé, les possibilités et l'abstraction offertes par les supports d'exécution à tâches devraient permettre de prendre en compte ces phénomènes et essayer de les éviter. Cette prise en compte de la contention entre calcul et communications par le support d'exécution serait un autre cas d'interaction positive.

## Conclusion

Les supports d'exécution à tâches sont une solution pour tirer plus facilement profit de la puissance des supercalculateurs, en fournissant un haut niveau d'abstraction, allant jusqu'à inférer le parallélisme des applications et les communications réseaux nécessaires.

Cette thèse aura montré que les interactions entre les supports d'exécutions à tâches et les bibliothèques de communications, qu'elles soient positives ou négatives, ne doivent pas être négligées. Dans un cas, elles ouvrent la voie à de considérables améliorations des performances, mais dans l'autre, elles peuvent aussi pénaliser la vitesse d'exécution des applications. Il n'est donc pas possible d'ignorer les communications au niveau des supports d'exécutions à tâches.

## Introduction

### High Performance Computing

B ETWEEN theoretical and experimental work, simulation can be considered as the third pillar of current scientific research. Indeed, simulations allow to verify theories and avoid real experiments, which can be costly and dangerous. Simulation can be used in many research areas: weather forecasting, climate prediction, fluid dynamics, earth-quakes, crash-tests for vehicles, rocket takeoff, biology, genomics, epidemiology, nuclear phenomena, cosmology, *etc.* Many cars can be saved while perfecting the airbag, as well as many rockets while the engine is not finely tuned; phenomena hard to mimic at the human scale, from the atom to the universe scale; dangerous experiments about nuclear reactions or health can be performed; all thanks to simulation.

Simulations are usually performed with computer programs, solving numerous complex equations, tracking the progression of a phenomenon over time steps, handling huge amount of data. These specific programs often require lots of computing power and memory to achieve precise simulations in a reasonable amount of time. More powerful computers allow to increase simulation precision (more precise weather forecasting, for instance) and to treat bigger problems. Using powerful computers to execute simulation programs belong to the High Performance Computing (HPC) domain.

The computing power required for simulations is so important that specific computers are built for this purpose. The most powerful of them are listed twice a year by the TOP500 ranking. In June 2022, the FRONTIER machine holds the first position<sup>1</sup>, with a performance of 1.102 Eflops: about  $10^{18}$  floating operations per second, while a regular laptop treats about 200 Gflops (*i.e.* FRONTIER is equivalent to 5 million laptops!). Such powerful computers aimed at HPC are called *supercomputers* and are in fact composed of many inter-connected *nodes*: individual computers which can be compared to more regular servers. This connection of many nodes gives to the overall supercomputer an important computing power: FRONTIER is composed of 9472 nodes. Moreover, each node has a processor with 64 cores and 4 GPUs. In the end, FRONTIER totals 8 730 112 computing units executing instructions in parallel.

These supercomputers can feature cutting-edge technology and the programming of

<sup>&</sup>lt;sup>1</sup>https://top500.org/news/ornls-frontier-first-to-break-the-exaflop-ceiling/

applications dedicated to HPC machines can be quite challenging: applications have to be parallel (*i.e.* divided in smaller independent parts executed simultaneously) to reduce execution time and fully exploit the computing power of the machine, they have to support different computing units (CPUs and accelerators), correctly manage different memories, *etc.* With the increasing power and complexity of supercomputers, fully exploiting all the computing power becomes more and more difficult. Moreover, each supercomputer is differently designed, which requires abstractions to have performance portability of applications.

To address these difficulties, *runtime systems* are developed, to abstract part of the machine complexity: machine topology, scheduling, accelerator management, *etc.* Different kinds of runtime systems exist, with different features and abstraction levels, like abstracting the machine but letting the developer explicitly express the application parallelism. Runtime systems following the task-based programming model with data dependencies abstract even this level and ease the writing of parallel applications, by requiring only an implicit expression of the parallelism. With task-based runtime systems, the application is divided in small parts represented by tasks, and tasks are connected according to the dependencies between those tasks (*i.e.* order constraints based on data manipulated by each task). Tasks and dependencies form a graph, which, once given to the runtime system, can be efficiently scheduled on parallel computing units.

Specific software libraries (sometimes part of runtime systems) are also developed to communicate between the nodes, by using the high performance network interconnecting them. Exchanged data are mainly results produced by a node, required by another node to perform a computation. Combining several runtime systems and a third-party communication library is common for HPC applications.

## Goals and contributions of this thesis

Usually runtime systems and communication libraries are two distinct and independent software. The runtime system uses the interface provided by the communication library to exchange messages on the network. The communication library is aware only of information related to network communications, and knows nothing about the application nor the status of the runtime system. However, a task-based runtime system may have information that could help the communication library in its decisions (future communications, priorities, application critical path, etc). Conversely, the communication library is aware of the status of communications and could also share its knowledge (incoming communications, estimated time of reception, etc) with the task-based runtime system.

The goal of this thesis is to explore the possible interactions between task-based runtime systems and communication libraries, in order for these two software layers to better exchange their respective information about the application execution and increase each other knowledge to take better decisions.

The main two software libraries used in this work to implement prototypes and make experiments are STARPU and NEWMADELEINE, introduced in Chapter 1.

This manuscript presents the following contributions, made during these last three

years:

**Tracing systems.** Recording application executions permits to later analyze the execution and understand the behaviour of the application, the decision taken by the runtime system, *etc.* However, tracing executions can add a performance overhead, potentially changing the behaviour of the application, making the behaviour represented in traces different than the behaviour in normal conditions, without traces. We evaluated the impact of different sources of overhead and proposed solutions to reduce them. Moreover, when tracing distributed applications, clocks used to timestamp events on each node have to be accurately synchronized to have consistent information recorded in traces, especially regarding communications. We evaluated the impact of clock synchronization on accuracy of communication duration.

Findings in this work are submitted to the journal *Concurrency and Computation: Practice and Experience* [134].

**Dynamic broadcasts.** Some task-based algorithms require to send the same data to different nodes. While common communication libraries provide routines for such usecase, with optimized communication scheme, these routines cannot be used within STARPU because of (among other things) a lack of information by all nodes receiving the data. We proposed a solution to use optimal routing algorithms for such communication patterns that fits with STARPU's constraints.

The idea, its implementation and its evaluation were presented in an article published at the  $26^{th}$  Euro-Par conference [130].

Interferences between computations and communications. Many runtime systems allow to execute simultaneously computations and network communications. Since these two different operations share common resources, interferences between them can occur, impacting their respective performance. We evaluated several possible sources of interferences and measured the impact on performance of both computations and communications.

Results of this study were published in an article at the *ICPP 2021* conference [128].

Model of memory contention. The major source of interferences between computations and communications is the possible memory contention generated by data movements to perform computations and communications. We proposed a model to better understand the contention and to be able to predict the share of memory bandwidth between computations and communications.

Our model and its evaluation got the best paper award of the *APDCM 2022* workshop, in conjunction with the  $36^{th}$  *IPDPS* conference [129]. A research report contains results on more machines [135].

## Organization of the document

Chapters 1 and 2 present the context of this work by respectively introducing distributed task-based runtime systems and reviewing related work. Chapter 3 digs in the tracing

system of STARPU, evaluates possible performance overheads when tracing applications and proposes solutions to reduce these overheads and to improve accuracy of distributed traces. Chapter 4 explains how we developed a broadcast system to fit with STARPU's constraints while using an optimized communication pattern. Chapter 5 studies the possible interferences between computations and network communications, when they are executed in parallel. Chapter 6 focuses on the impact of memory contention on computations and communications, by proposing a model for memory bandwidth sharing. Finally, last chapter summarizes our work and discusses possible perspectives.

Appendix A explains in detail differences between the communication backends of STARPU. Appendix B presents the followed methodology regarding reproducible experiments. Appendix C describes the characteristics of the clusters used for the experiments presented in this thesis. Appendices D and E provide respectively algorithmic versions of equations described in Chapter 6 and the parameter values obtained during the evaluation of the model.

#### | Chapter

# Distributed Task-based Runtime Systems

T HIS first chapter presents the context and the problematic of this thesis. First, it describes the increasing complexity of HPC supercomputers, which makes them harder to program in the most efficient way. Then, we introduce task-based runtime systems, a solution to address these programming difficulties. We explain how they work on a single node but also for distributed applications on several nodes. Finally, we announce the general problematic covered by this thesis and its main contributions.

## 1.1 The growing complexity of HPC machines

Although we reached some physical limits in the conception of processors, preventing from increasing always the same characteristics (*e.g.* processor frequency and Instructions Per Cycle (IPC)), performance of supercomputers did not stop to increase over time. Machine vendors keep innovating, in several directions, to provide always more and more computing power to their users. The diversity of solutions for real high performance computing has a cost: efficiently exploiting the whole computing power offered by the machines is much more difficult, and, moreover, it is a challenge left to application developers.

#### 1.1.1 More powerful machines...

At the core of computers, processors execute all the instructions. To offer better performances and better exploit their possibilities, they present many features, more or less complex to take into account by the application:

Multi-core processors. All available transistors in a processor can be used to split the processor into several processing units (called *cores*), independently executing different instructions at the same time. Nowadays, HPC processors feature several tens of such cores, each executing its own flow of instructions. From the operating system point of view, the different cores appear like different processors.

- Simultaneous multithreading. Since some processor instructions require several clock cycles to complete (floatting-point instructions, memory accesses, *etc*), the progress of the instructions in the pipeline is not assured for each clock cycle. When such long instruction is executed, the core has to wait for the dedicated subsystem to handle the instruction, and thus waste clock cycles. These holes in the instruction pipeline are called *stalls* (or *bubbles*). With *simultaneous multithreading*, physical cores are split in several (usually two) logical cores: when a stall occurs in the instruction flow of a logical core, the physical core executes instructions from another logical core. INTEL implements this technique under the name of *Hyper-Threading*, which became a common term to designate this feature, as well as *hyper-thread* to talk about a logical core. From the operating system point of view, these logical cores appear as regular cores.

- Many-core processors. Another way of exploiting the transistors of a processor is to split the processor into *many cores*. Like multi-core processors, each core manages its own instruction flow, but many-core processors feature much more cores: several hundreds of hyperthreads. This important number of cores is possible at the cost of simpler cores, with a reduced instruction set and less features. The main representative of this class of processors is the INTEL XEON PHI, launched in 2010 and installed for example in the TIANHE-2 supercomputer, first in the TOP500 ranking in 2013.

- Heterogeneous processors. More recently, *heterogeneous* processors have been introduced, especially to reduce the power consumption: a set of cores requiring very few energy is used for generic purpose and another set of cores more powerful, yet consuming more power, is enabled only in case of more demanding computations. The main processor architectures in this family are the ARM's BIG.LITTLE and the INTEL's ALDER LAKE. However, these models have not landed yet on supercomputers.

- Instruction set. The important number of available transistors can be used to create specific processor instructions, for instance implementing arithmetic operation directly as one processor instruction, instead of several instructions called by the software. This kind of optimization can save clock cycles and thus increase the computing power of the processor. Vectorized instructions are also improved over the years: they consist in executing the same operation on multiple registers at the same time (Single Instruction on Multiple Data (SIMD)). The vectorization of the code can be done implicitly by the compiler, or explicitly by the programmer by using the dedicated instructions. The most famous SIMD instruction set is the Advanced Vector Extensions (AVX) from INTEL. The last version, AVX-512, released in 2017 on the SKYLAKE processors, handles 512-bit registers (which can be used as arrays of 16 floats, for instance).

- **GPUs.** While CPUs (*Central Processing Unit*) are designed for a generic purpose (running the operating system, softwares) and have to support a wide range of instructions, including branchings and loops; GPUs (*Graphics Processing Unit*) implement mainly the SIMD architecture, thus they can exhibit a high level of parallelism, much higher than regular CPUs, but have very low performance in case of branching instructions. This specific kind of processor was originally designed for graphic processing such as image rendering, and then other applications with similar requirements (*e.g.* linear algebra and training of machine learning models) adopted it.

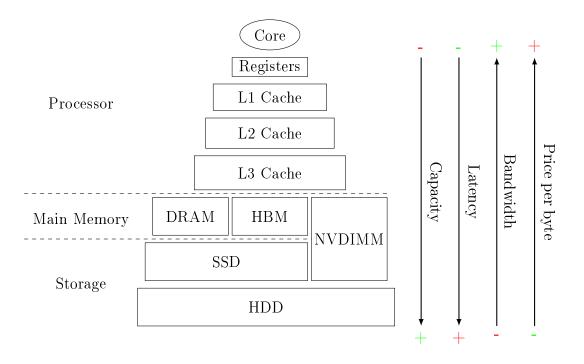

Figure 1.1: Typical memory hierarchy.

**FPGAs.** Field-Programmable Gate Arrays are processors that can be entirely reprogrammed to execute a specific computation. This way, computations can be faster on an FGPA than on a regular CPU, since the circuit of the FGPA is reprogrammed specifically to execute only the desired computation, while the genericity of the CPU can add important overhead. The main advantage of the FPGA is also its main drawback: the programming of the FPGA is made in a specific (low-level) language and the reconfiguration of the FPGA to execute a new program can be very long (several hundreds of milliseconds). Such processors also tend to cost more than CPUs and have a lower frequency.

All these different uses of transistors rely on the *parallel* paradigm: applications are divided in smaller independent instructions flows, each being executed simultaneously by different sets of transistors (*e.g.* several cores or hyper-threads). Parallel applications are the most common in HPC area, since this programming model is required to exploit current powerful computers, featuring these parallel computing units.

Many-core processors, GPUs and FPGAs are examples of *accelerators*: they are installed in addition to a CPU, to accelerate only the kind of computations they are specialized in. While CPUs have direct access to the main memory (RAM) of the computer, accelerators have their own memory. Some accelerators can access the CPU RAM, but with a potential performance overhead if used improperly<sup>1</sup>; a technique to counterbalance this overhead is to explicitly copy data to the accelerator memory, perform the maximum computations on the accelerator manipulating the copied data (now located in the accelerator memory, with quick access) and then copy back the data on the CPU memory.

<sup>&</sup>lt;sup>1</sup>https://developer.nvidia.com/blog/unified-memory-cuda-beginners/

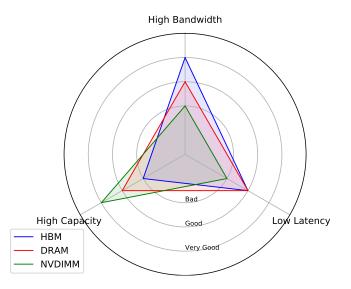

Figure 1.2: Characteristics of different memory kinds. From the PhD thesis of Andrès RUBIO PROAÑO [98].

Speaking of memory, memories accessible by a CPU bring also their set of complexity. Computers feature a so-called *memory hierarchy*, as illustrated by Figure 1.1. Indeed, processors can access several kinds of memory, more or less close to each core. The further the memory is located (from an architectural point of view), the longer it will take to access this memory (to read or write), however, the higher the memory capacity. This hierarchy comes from the complexity (or even impossibility!) to design the perfect memory: fast, with high capacity and cheap: thus faster memories are smaller and closer to computing units, to take benefit from an increased speed.

We can distinguish memory inside and outside the processor. Memory inside the processor are caches, organized in several levels: first levels are private to each core and last levels are shared between cores. The most common memory outside processors is Dynamic Random Access Memory (DRAM). Processors fetch memory from the DRAM in caches and cache lines are evicted and stored back in the DRAM. DRAM memories provide good trade-off in terms of capacity, bandwidth and latency. Again, since there is no perfect memory with outstanding values in all performance metrics, other types of memories exist, each type being better regarding one characteristic, as illustrated by Figure 1.2: Non-Volatile Dual Inline Memory Module (NVDIMM) has a higher capacity and High Bandwidth Memory (HBM) a higher bandwidth.

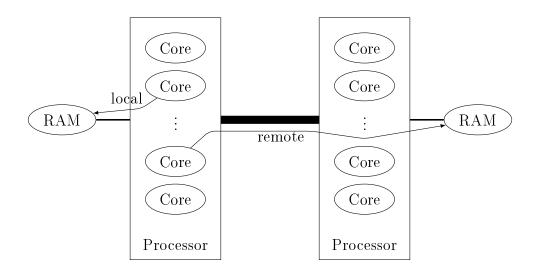

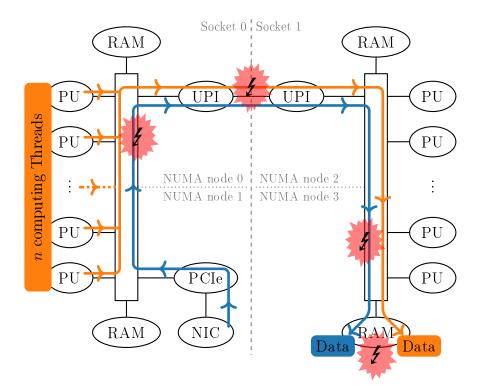

With the current important number of cores per processor, and given the fact that HPC nodes can have several processors (usually two), the memory system cannot serve the memory requests of all cores and exhibit correct performance. To tackle this issue, a Non-Uniform Memory Access (NUMA) architecture is used: the whole memory is segmented and each segment is dedicated to a set of cores, as illustrated by Figure 1.3. A NUMA node is the name of the set composed of several cores and their dedicated segment of memory. Cores can normally access memory located on a NUMA node different from their NUMA node, but this kind of memory request will take longer to achieve.

Figure 1.3: A NUMA machine: each processor has its own memory (*local*), but can also access memory of other processors (*remote*).