# New routing algorithms for heterogeneous exaflopic supercomputers

John Gliksberg

# ▶ To cite this version:

John Gliksberg. New routing algorithms for heterogeneous exaflopic supercomputers. Networking and Internet Architecture [cs.NI]. Université Paris-Saclay; Universidad de Castilla-La Mancha, 2022. English. NNT: 2022UPASG068. tel-03992998

# HAL Id: tel-03992998 https://theses.hal.science/tel-03992998

Submitted on 16 Feb 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# New routing algorithms for heterogeneous exaflopic supercomputers Nouveaux algorithmes de routage pour supercalculateurs exaflopiques hétérogènes

# Thèse de doctorat de l'université Paris-Saclay et de l'université de Castilla-La Mancha

École doctorale  $n^{\circ}580$  : sciences et technologies de l'information

et de la communication (STIC)

Spécialité de doctorat : Informatique

Graduate School: Informatique et sciences du numérique

Référent : Université de Versailles Saint-Quentin-en-Yvelines (UVSQ)

Thèse préparée dans l'unité de recherche LI-PARAD (Université Paris-Saclay, UVSQ) ; sous la direction de Devan Sohier, Professeur HDR, la co-direction de Pedro Javier García García, Professeur équivalent HDR, et le co-encadrement de Antoine Capra, Ingénieur recherche.

Thèse soutenue à Guyancourt, le 25 novembre 2022, par

# John Gliksberg

# Composition du jury

Membres du jury avec voix délibérative

# Maria Engracia Gómez Requena

Professeure des universités, UPV

#### **Brice Goglin**

Directeur de recherche, Inria Bordeaux - Sud-Ouest

# Enrique Vallejo

Maître de conférence, Université de Cantabria

# Marc Pérache

Directeur de recherche, CEA DAM

## **Emmanuelle Saillard**

Chargée de recherche, Inria Bordeaux - Sud-Ouest

# Présidente

Rapporteur & Examinateur

Rapporteur & Examinateur

Examinateur

Examinatrice

**Title:** New routing algorithms for exaflopic heterogeneous supercomputers **Keywords:** Routing, Algorithms, HPC, Interconnection networks

**Abstract:** Building efficient supercomputers requires optimising communications, and their exaflopic scale causes an unavoidable risk of relatively frequent failures. For a cluster with given networking capabilities and applications, performance is achieved by providing a good route for every message while minimising resource access conflicts between messages. This thesis focuses on the fat-tree family of networks, for which we define several overarching properties so as to efficiently take into account a realistic super-

set of this topology, while keeping a significant edge over agnostic methods. Additionally, a partially novel static congestion risk evaluation method is used to compare algorithms. A generic optimisation is presented for some applications on clusters with heterogeneous equipment. The proposed algorithms use distinct approaches to improve centralised static routing by combining computation speed, fault-resilience, and minimal congestion risk.

**Titre:** Nouveaux algorithmes de routage pour supercalculateurs exaflopiques hétérogènes **Mots clés:** Routage, Algorithmes, HPC, Réseau d'interconnexion

Résumé: La construction de supercalculateurs performants nécessite d'optimiser les communications, et leur échelle exaflopique amène un risque inévitable de pannes relativement fréquentes. Pour un cluster avec un réseau et des équipements donnés, on améliore les performances en s'assurant que l'on sélectionne une bonne route pour chaque message tout en minimisant les conflits d'accès aux resources entre messages. Cette thèse se concentre sur la famille des réseaux fat-trees, pour laquelle nous donnons quelques grandes caractéristiques afin de mieux prendre en compte une classe réaliste de cette topologie,

tout en conservant un avantage par rapport aux méthodes agnostiques. De plus, une approche d'évaluation statique partiellement nouvelle du risque de congestion est utilisée pour comparer les algorithmes. Une optimisation générique est présentée pour certaines applications sur des clusters avec des équipements hétérogènes. Les algorithmes proposés forment le résultat de plusieurs approches distinctes pour apporter des contributions dans le domaine du routage statique centralisé, en combinant rapidité de calcul, résilience aux pannes, et minimisation du risque de congestion.

**Titulo:** Nuevos algoritmos de encaminamiento para superordenadores heterogéneos a exaescala **Palabras clave:** Encaminamiento, Algoritmos, HPC, Red de interconexíon

Resumen: La optimización de las comunicaciones es un requisito fundamental para la construcción de superordenadores eficientes. Por otra parte, la escala en el ámbito del "exaflop" de estos superordenadores conlleva un riesgo inevitable de fallos relativamente frecuentes. Para un clúster de computación con determinadas capacidades de red y aplicaciones, un buen rendimiento se consigue proporcionando rutas eficientes y minimizando los conflictos de acceso a los recursos entre los diferentes mensajes. Esta tesis se centra en la familia de topologías "fat-tree", para la que definimos varias propiedades generales con-

siderando un superconjunto realista de esta topología, manteniendo una ventaja sustancial sobre métodos agnósticos. Además, se utiliza un método relativamente novedoso para la evaluación del riesgo de congestión estática de los diferentes algoritmos. Se presenta una optimización genérica para algunos tipos de aplicaciones en clústeres con equipos heterogéneos. Los algoritmos propuestos utilizan enfoques distintos para mejorar el encaminamiento estático centralizado combinando velocidad de cálculo, tolerancia a fallos y minimizando el riesgo de congestión.

# **Contents**

| A  | ckno  | vledgements                                        | vii |  |  |  |  |

|----|-------|----------------------------------------------------|-----|--|--|--|--|

| Tı | ransl | ated introduction                                  | ix  |  |  |  |  |

| 1  | Cor   | ontext and state of the art                        |     |  |  |  |  |

|    | 1.1   | Introduction                                       | 1   |  |  |  |  |

|    | 1.2   | Problem model                                      | 2   |  |  |  |  |

|    |       | 1.2.1 HPC interconnects                            | 2   |  |  |  |  |

|    |       | 1.2.2 Network definitions                          | 4   |  |  |  |  |

|    |       | 1.2.3 Routing for HPC interconnects                | 5   |  |  |  |  |

|    |       | 1.2.4 Centralised static routing                   | 8   |  |  |  |  |

|    |       | 1.2.5 Adaptive routing                             | 8   |  |  |  |  |

|    |       | 1.2.6 Approaches to programming routing algorithms | 9   |  |  |  |  |

|    |       | 1.2.7 Deadlock avoidance                           | 11  |  |  |  |  |

|    |       | 1.2.8 Node-type heterogeneity                      | 12  |  |  |  |  |

|    |       | 1.2.9 Fault resilience                             | 13  |  |  |  |  |

|    | 1.3   | Topologies                                         | 13  |  |  |  |  |

|    |       | 1.3.1 Direct topologies                            | 14  |  |  |  |  |

|    |       | 1.3.2 Indirect topologies                          | 15  |  |  |  |  |

|    |       | 1.3.3 Fat-tree topologies                          | 17  |  |  |  |  |

|    |       | 1.3.4 Irregular fat-trees (IFTs)                   | 22  |  |  |  |  |

|    |       | 1.3.5 Topologies used by interconnect vendors      |     |  |  |  |  |

|    | 1.4   | Routing algorithms for fat-trees                   | 23  |  |  |  |  |

|    |       | 1.4.1 Ftree                                        | 24  |  |  |  |  |

|    |       | 1.4.2 Dmodk                                        | 27  |  |  |  |  |

|    |       | 1.4.3 Smodk                                        | 28  |  |  |  |  |

|    |       | 1.4.4 Random shortest path routing (RandSP)        | 28  |  |  |  |  |

|    |       | 1.4.5 Ranking                                      | 30  |  |  |  |  |

|    |       | 1.4.6 Fat-tree-specific fault resilience           | 31  |  |  |  |  |

|    | 1.5   | Problem statement and plan                         | 32  |  |  |  |  |

| 2  | Qua   | lity comparison of routing algorithms              | 35  |  |  |  |  |

|    | 2.1   | Introduction                                       | 35  |  |  |  |  |

|    | 2.2   | Traffic simulation                                 | 36  |  |  |  |  |

|    |       | 2.2.1 Static traffic patterns                      | 36  |  |  |  |  |

|    |       | 2.2.2 Dynamic traffic simulation                   |     |  |  |  |  |

|    | 2.3   | Static metric                                      | 38  |  |  |  |  |

|    |       | 2.3.1 The µ static congestion metric               | 40  |  |  |  |  |

|    |       | 2.3.2 Generic static traffic patterns of choice    | 41  |  |  |  |  |

|    |       | 2.3.3 Effective diameter                           | 43  |  |  |  |  |

|    | 2.4   | Example application of static metrics              |     |  |  |  |  |

|    |       | OMNeT++-hased simulation                           | 46  |  |  |  |  |

| 3  | Rou  | iting for heterogeneous fat-trees                      | 47         |

|----|------|--------------------------------------------------------|------------|

|    | 3.1  | Heterogeneous clusters                                 | 47         |

|    | 3.2  | Case study topology                                    | 48         |

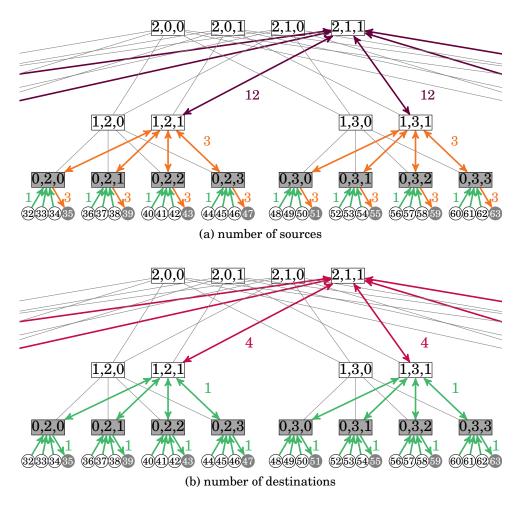

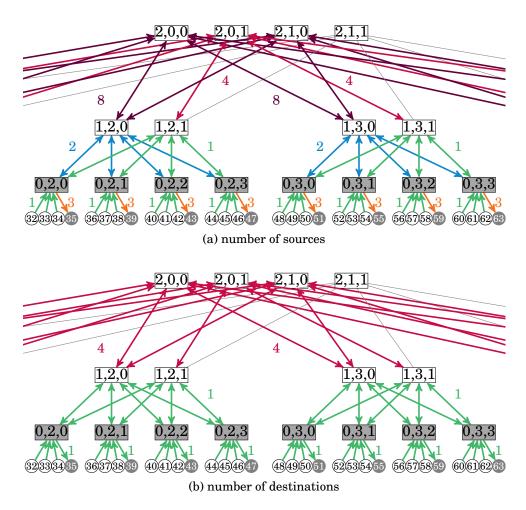

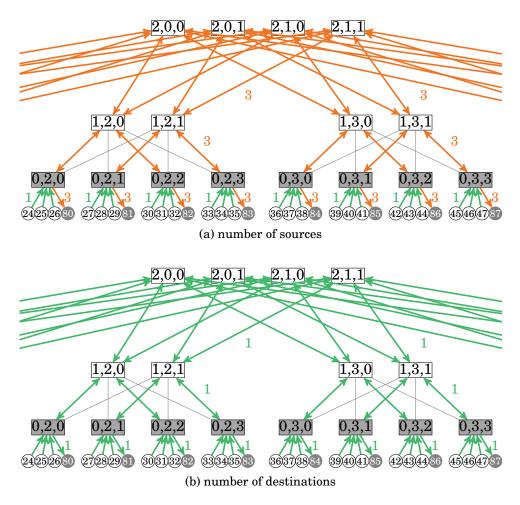

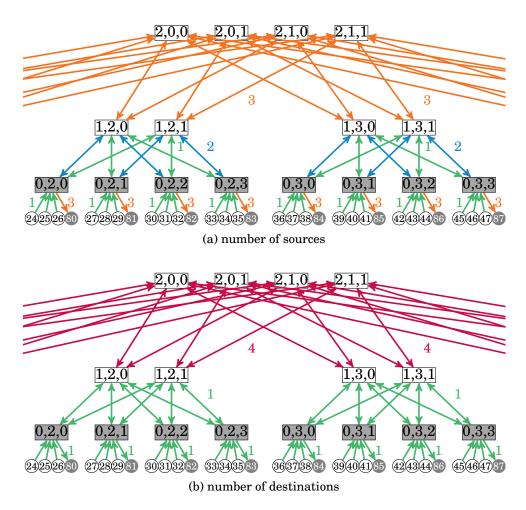

|    | 3.3  | Analysis of a node-type-specific communication pattern | 49         |

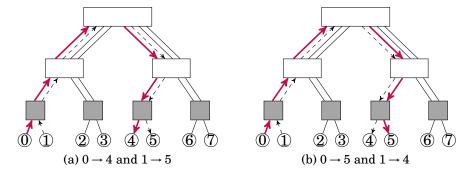

|    |      | 3.3.1 Dmodk/Ftree performance                          | 49         |

|    |      | 3.3.2 Smodk performance                                | 52         |

|    |      | 3.3.3 RandSP performance                               | 52         |

|    | 3.4  | Grouped Xmodk                                          | 53         |

|    |      | 3.4.1 Reindexing NIDs                                  | 53         |

|    |      | 3.4.2 Gxmodk case study                                | 56         |

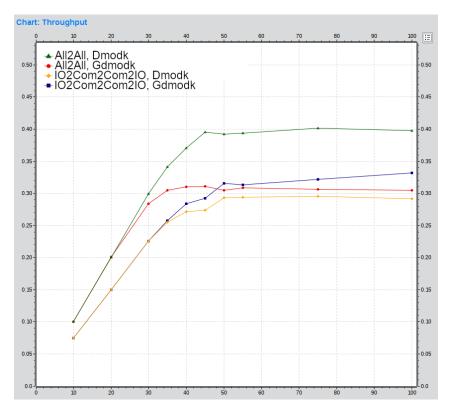

|    | 3.5  | OMNeT++-based simulation of Gdmodk                     | 57         |

|    | 3.6  | Conclusions and future works                           | 58         |

| 4  | Fau  | lt-resilient routing in fat-trees                      | <b>59</b>  |

|    | 4.1  | Reconfiguration mechanisms                             | 59         |

|    | 4.2  | Dmodc                                                  | 60         |

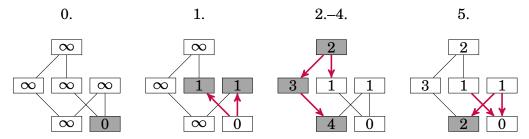

|    |      | 4.2.1 Preprocessing                                    | 60         |

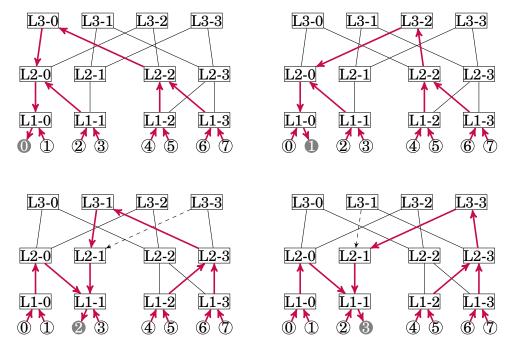

|    |      | 4.2.2 Routes computation                               | 65         |

|    |      | 4.2.3 Primary results                                  | 66         |

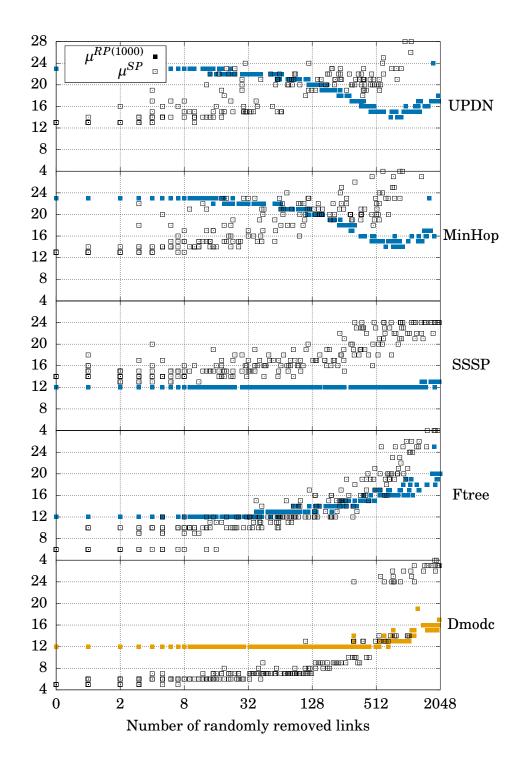

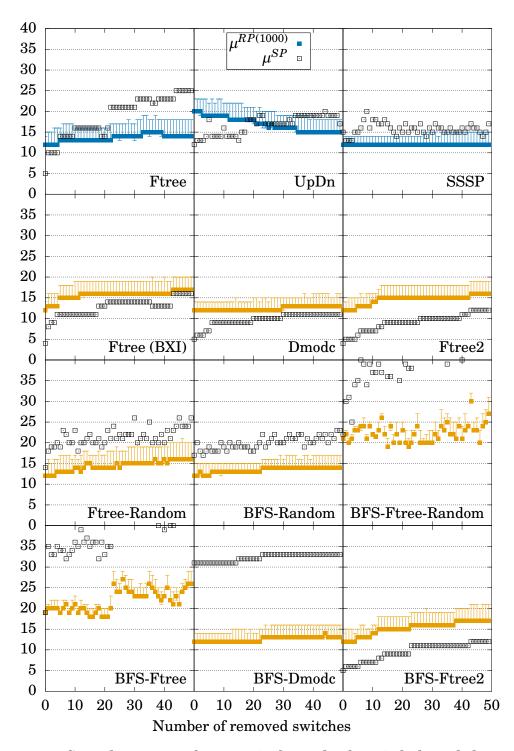

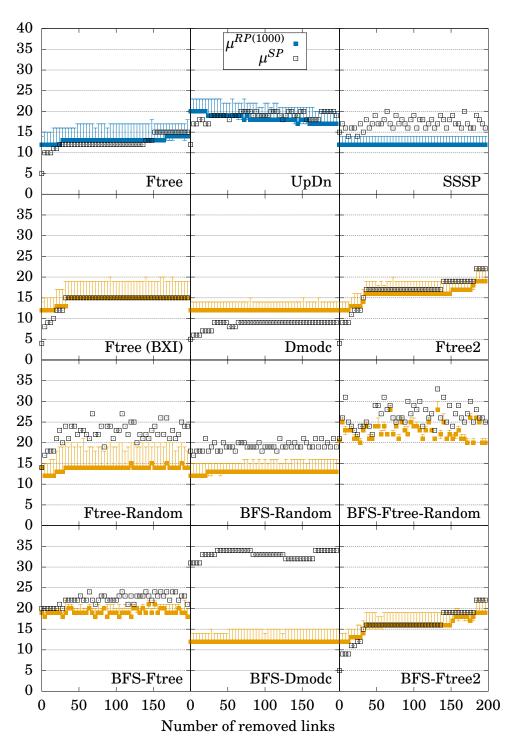

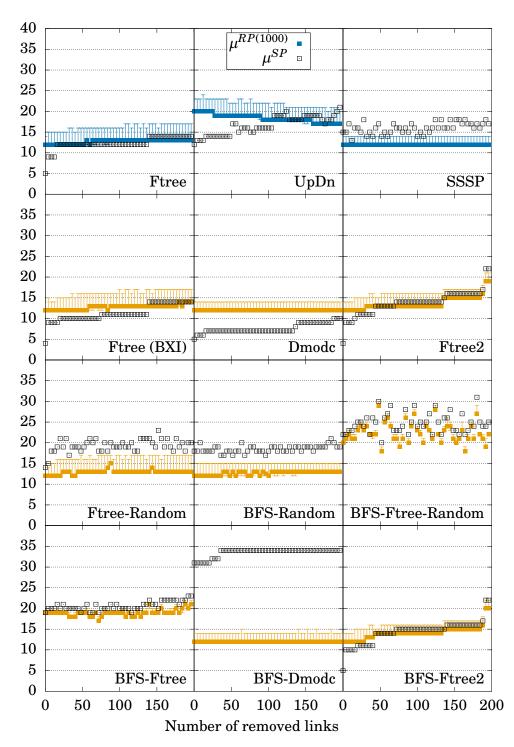

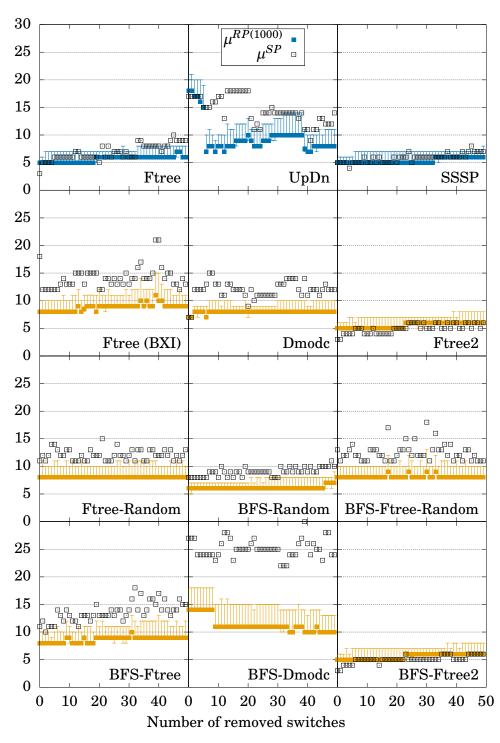

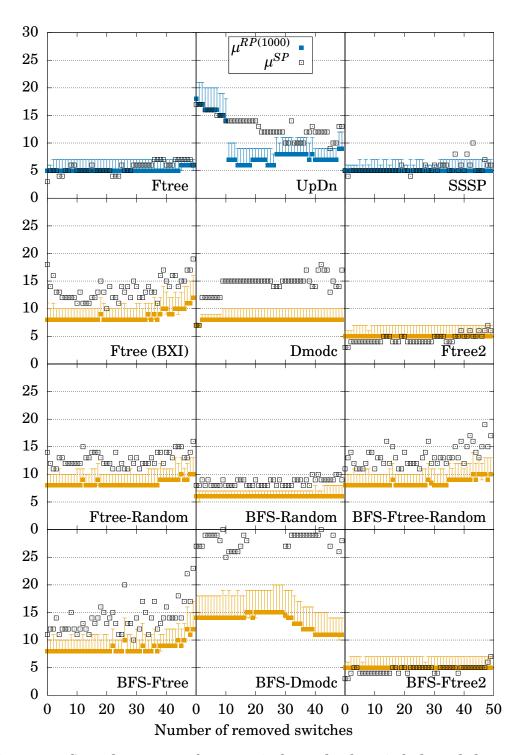

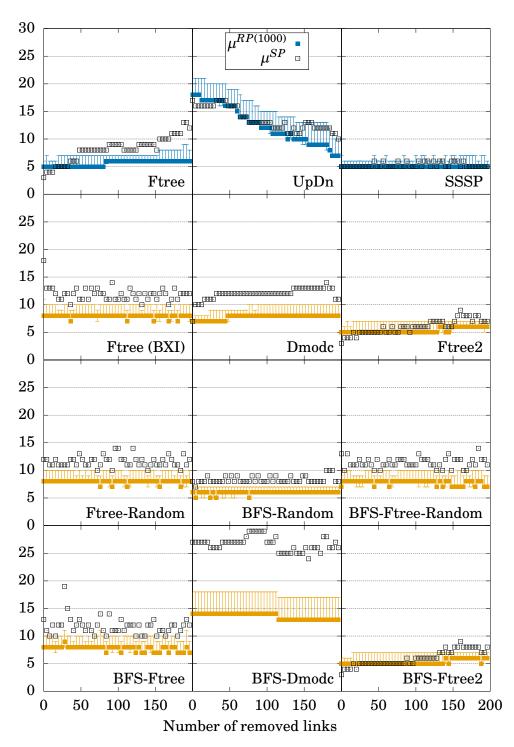

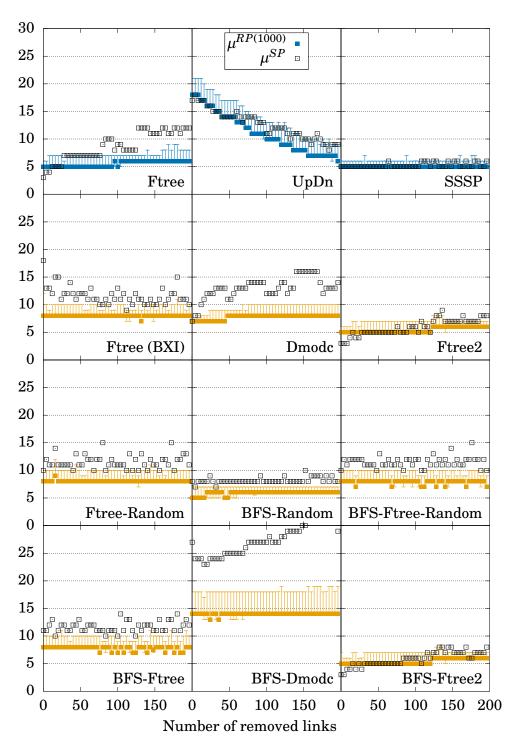

|    |      | 4.2.4 Congestion risk as a function of degradation     | 68         |

|    | 4.3  | Conclusion                                             | 69         |

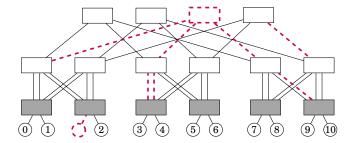

| 5  | Rou  | iting irregular fat-trees                              | <b>7</b> 3 |

|    | 5.1  | Some new IFT-specific routing algorithms               | 73         |

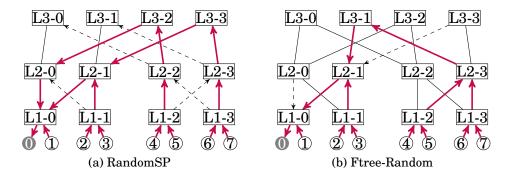

|    |      | 5.1.1 Ftree-Random                                     | 73         |

|    |      | 5.1.2 Ftree2                                           | 75         |

|    |      | 5.1.3 Up*/Down* implementations                        | 78         |

|    | 5.2  | Comparison of algorithms                               | 81         |

|    |      | 5.2.1 Progressively degraded fat-tree                  | 81         |

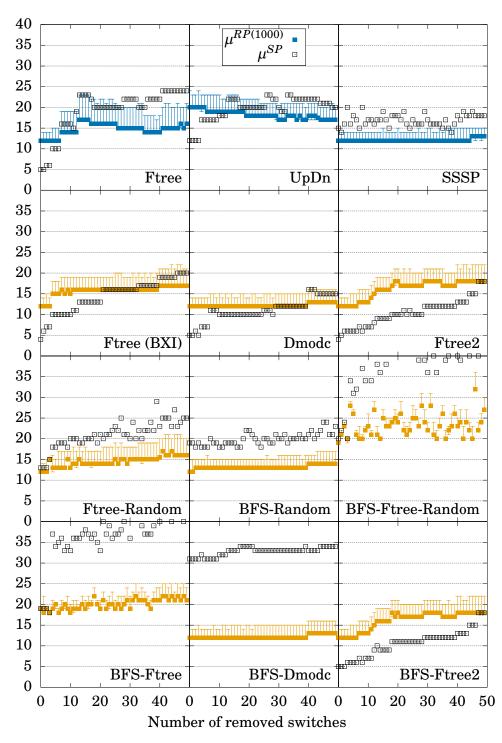

|    |      | 5.2.2 Progressively degraded QFT                       | 83         |

|    | 5.3  | Conclusion                                             | 84         |

| Co | neli | ısion                                                  | 93         |

| CC |      | tributions                                             | 93         |

|    |      | ure research                                           | 95<br>95   |

|    | ruu  | ure research                                           | 90         |

| Tr | ansl | ated conclusion                                        | 97         |

| Ar | nex  |                                                        | 107        |

|    | 1    | Routing Leiserson fat-trees                            | 107        |

|    | 2    | Resilient statistical ranking method                   |            |

|    | 3    | Routing vPGFTs                                         |            |

| Bi | blio | graphy                                                 | 111        |

# Acknowledgements

I must give mille mercis to my director, Devan, who was key throughout the process and pushed me towards an academic rigour that can be lacking in this specific domain, and that I wasn't naturally striving to uphold more than necessary. You endeavoured to learn quite a bit about a subject that otherwise may have seemed rote and undignified, for that I am grateful and I suspect you found a few interesting surprises on the way. My co-director, Pedro, deserves heart-felt gracias as well for his continued sympathy and attention to details; never have I received such amicable praise accompanied with a thoroughly blooddrenched page of corrections. I hope to enjoy many more meals and matches in your company. Antoine, you weren't just a reviewer but also a great inspiration, and along with Alexandre I have fond memories of the three of us getting Dmodc working; thank you both. I have received quite a bit of help from the people at LI-PaRAD, and I must single out Thomas and Pablo for their time and care. I must thank both reviewers for their helpful remarks and kind words, and the rest of the jury members for their efforts. On another note, I would be remiss to forget to acknowledge the character-building challenges brought on by the administrative entities of both universities. I can only recommend the combination of industrial doctorate and international cotutelle to students and advisors of tenacious will.

I must thank my mum profusely for the numerous indispensable nitpicks throughout the manuscript. Please read it only superficially from now on, or you'll find yet more mistakes. Thank you, yiddishe papa, for driving me to the interview back in 2016 and then leaving me to work without any pressure. Thank you Daphné for your infinite patience and loving application of motivational threats. You had to bear with my occasional defeated self ever since we were together.

My colleagues at Atos have always been very motivated to see me go through this doctorate (sometimes more so than myself); and I must thank each of them, both for their work and their fraternity. Alain, Pierre, Safae, Ravaka, Ben, Zakaria, Marc, Marwa, Jean-Yvon, Bruno G, Bruno F, etc, etc, thank you. I must thank Jean-Noël and Pierre V in particular, my first two advisors at Atos. You placed all the necessary blocks for this thesis, and your back-breaking work on BXI helped me learn a lot of my trade.

The times I spent in Albacete (no hay ningún sitio mejor que Albacete) were wonderful, and the people at and around the lab were great to me. Many thanks to Rocher, German, Juanje, Jesús, Pedro Yébenes, Blas, Raúl, Antonía, Hugo, Ester, etc.

Finally, I must shout out to all friends and family, who've been hearing a whole lot about this; now we'll have to find other things to talk about. Thank you, in no particular order, to Sam, Alex, Guillaume, Sarah, Vincent, Louis-Daniel, Laure, Matthieu, Marion, Simon, Léopold, Marie-Liesse, and all the others. And of course, I am eternally indebted to Patate.

# **Translated introduction**

#### **Introduction in French**

Les supercalculateurs actuels les plus puissants construits pour le Calcul Haute-Performance (HPC) sont des grappes de matériel commercial haut-degamme, combinant des millions de cœurs, coûtant des dizaines de millions d'euros, et consommant plusieurs mégawatts [81] : une telle puissance de calcul demeure prohibitive en termes de coût et de consommation énergétique. Le réseau d'interconnexion (l'interconnect) d'un tel système permet aux applications d'être distribuées sur de nombreux nœuds pour accélérer leur temps d'exécution, ou pour augmenter leur échelle ou leur précision. Les performances globales du système dépendent fortement des performances de l'interconnect [24, 3]. En conséquence, les interconnects HPC sont prévus pour assurer une quasi-totale absence de pannes et minimiser l'utilisation de mécanismes de résilience aux pannes. Ce réseau finit donc par représenter une part conséquente de la puissance et du matériel alloués aux supercalculateurs modernes. Néanmoins, l'évolution en termes de puissance et d'échelle de ces systèmes amène un risque inévitable de pannes matérielles. Un volume important de la recherche dans le domaine vise à minimiser le coût et la consommation de ces réseaux tout en maximisant leurs performances et leur résilience aux pannes. Le routage joue un rôle vital dans l'interconnect HPC, qui constitue dans son ensemble un système compliqué dont les choix architecturaux et l'utilisation impactent le coût, les performances et la résilience aux pannes. Cette thèse se concentre sur des améliorations de techniques de routage pour interconnects HPC avec la conception et l'analyse statique de nouveaux algorithmes de routages, et des modifications applicables à des algorithmes existants. Cette décision se place à contre-courant de la majorité de la recherche contemporaine qui se concentre sur des études dynamiques d'aspects plus avancés des interconnects HPC (tels que le routage adaptatif, l'ordonnancement dynamique d'applications, ou autres optimisations dynamiques basées sur le comportement réel des applications) : une partie des soucis de performance qui justifient ces méthodes pourraient être évités en amont au niveau du routage statique. Les techniques de routage proposées offrent des améliorations de performances et/ou de résilience aux pannes, tout en relaxant partiellement les contraintes topologiques de la conception du réseau.

Cette recherche a été motivée par un contexte industriel alors que Bull construisait un interconnect interne pour ses nouveaux supercalculateurs Bull eXascale Interconnect (BXI), avec un nouveau *fabric manager* (le logiciel qui observe et configure le réseau à un haut niveau, ce qui inclut le calcul d'un routage fonctionnel et performant). Les switches BXI sont conçus avec un CPU

ARM embarqué et un réseau de gestion séparé de l'interconnect, ainsi que d'autres spécificités de conception. Pour s'adapter à ces aspects, et profiter de l'occasion de repartir de zéro, le fabric manager BXI (BXI FM) est organisé différemment des subnet managers de ses concurrents. Certains algorithmes et techniques de routage ont été conçus pour ce système pour utiliser pleinement les caractéristiques de switches. Pour améliorer ces techniques, et avec l'intuition que cette nouvelle architecture de matériel pouvait mener à une approche différente dans la recherche, le sujet de thèse initial a été planifié. Cette thèse est menée avec le LI-PaRAD (Laboratoire d'Informatique, Parallélisme, Réseaux, Algorithmes Distribués) à l'UVSQ (Université de Versailles Saint-Quentin-en-Yvelines). Cette thèse est également menée avec le laboratoire RAAP (Redes y Arquitecturas de Altas Prestaciones) à l'UCLM (Universidad de Castilla-la-Mancha) en Espagne, au travers d'une cotutelle internationalle. Le contexte industriel a fortement impacté le déroulement de cette thèse, lors de laquelle plusieurs inventions ont été brevetées et intégrées dans le produit commercialisé par Atos. En revanche, un effort a été fourni pour étudier des cas généraux et les résultats sont, dans l'ensemble, applicables à d'autres situations.

# **Introduction in Spanish**

Los actuales supercomputadores empleados para la computación de altas prestaciones (High-Performance Computing, HPC) están formados por un conjunto de componentes comerciales, incluyen millones de núcleos de cómputo (cores), tienen un coste de decenas de millones de euros, y consumen algunas decenas de megavatios [81]; en resumen, puede decirse que conseguir altas potencias de cómputo sigue siendo caro, y consume muchos recursos. La red de interconexión de estos sistemas permite repartir aplicaciones entre muchos nodos del sistema para acelerar su tiempo de ejecución, o para aumentar su escala, resolución, o precisión. Las prestaciones del sistema en su conjunto dependen enormemente de la red de interconexión [24, 3]. En consecuencia, a menudo las redes de sistemas HPC se han sobredimensionado para no fallar prácticamente nunca y para minimizar los mecanismos de recuperación, pero este enfoque hace que la red represente una fracción muy relevante de los componentes y del consumo del sistema supercomputador. La importancia de este problema ha crecido con el incremento de la escala de estos sistemas (imprescindible para conseguir mayor potencia de cómputo), lo que además ha ocasionado que la aparición de fallos en los componentes sea casi inevitable. Por ello, buena parte de la investigación en este campo se orienta a minimizar el coste y consumo de estas redes, mientras se intenta optimizar sus prestaciones y su resiliencia ante posibles fallos. En este entorno, el encaminamiento es un factor esencial en el funcionamiento de la red, cuyo diseño es clave de cara al coste, las prestaciones y la resiliencia. Esta tesis se centra en mejorar el encaminamiento para redes de sistemas HPC mediante el diseño y análisis de nuevos algoritmos estáticos de encaminamiento, y mediante extensiones de otros ya existentes. Este enfoque se basa en la observación de que una gran parte de la investigación actual en redes de interconexión para sistemas HPC se orienta hacia estudios de técnicas "dinámicas" tales como encaminamiento adaptativo, planificación dinámica de procesos, y optimizaciones basadas en trazas, mientras que muchas de las prestaciones que se pretenden conseguir con estas técnicas podrían abordarse mejor de antemano mediante algoritmos de encaminamiento estáticos. Las propuestas de esta tesis ofrecen mejoras bien respecto a prestaciones, bien respecto a resiliencia ante fallos, o respecto a ambas, relajando a la vez ciertas restricciones del diseño de la topología.

La investigación recogida en esta tesis se inició en un contexto industrial, al estar Bull diseñando su nueva tecnología de red de interconexión propia, llamada BXI (Bull eXascale Interconnect), junto con un nuevo software (fabric manager) para monitorizar y configurar la red a alto nivel, incluyendo el mantenimiento funcional y el encaminamiento eficiente. Los conmutadores BXI integran una CPU de ARM, y se conectados a una red de control y administración paralela y separada de la red de interconexión del sistema supercomputador. Para adaptarse a este entorno, y también para partir de cero, sin ceñirse a modelos previos, el software de control BXI se organiza de forma distinta a los equivalentes en otras tecnologías de red. Algunas técnicas y algoritmos de encaminamiento se diseñaron para este sistema, de cara a optimizar el uso del diseño de los conmutadores BXI. El tema principal de esta tesis surgió con la intención de mejorar estas técnicas, y al intuirse que la nueva arquitectura de hardware BXI permitiría desarrollar la investigación de forma diferente. Esta investigación se ha desarrollado conjuntamente con el laboratorio LI-PaRAD (Laboratoire d'Informatique, Parallélisme, Réseaux, Algorithmes Distribués) de la Universidad de Versailles Saint-Quentin-en-Yvelines (UVSQ) en Francia. La tesis también se ha desarrollado conjuntamente con el grupo de Redes y Arquitecturas de Altas Prestaciones (RAAP) de la Universidad de Castilla-La Mancha (UCLM) en España, mediante una cotutela internacional. El contexto industrial ha tenido una gran influencia en la investigación desarrollada, y varias contribuciones de la tesis se han patentado e integrado en productos comerciales. Sin embargo, se ha tenido especial cuidado en estudiar casos genéricos, y por tanto en general los resultados del trabajo son aplicables a otros entornos.

# 1 — Context and state of the art

## 1.1. Introduction

Today's most powerful supercomputers built for High-Performance Computing (HPC) are clusters of high-end commodity hardware, composed of millions of cores, costing tens of millions of euros, and requiring multiple megawatts [81]: computing power remains prohibitive and resource-consuming. The interconnection network (interconnect) which connects such a system allows applications to be distributed across many nodes to speed up their run time, or increase their scale, resolution, or precision. The performance of the system as a whole is highly dependant on the performance of the interconnect [24, 3]. Correspondingly, the HPC interconnect is over-engineered to almost never fail so as to minimise layers targeting resilience, and this network represents a significant fraction of the power and hardware allocated to modern supercomputers. However, the increase in power and scale of these systems has caused hardware failures to become unavoidable. A significant part of the research in this area aims to minimise the cost and consumption of these networks while maximising their performance and fault resilience. Routing plays a vital role in the HPC interconnect, which is overall an intricate system whose design and usage affect cost, performance, and fault resilience. This thesis focuses on improving routing techniques for HPC interconnects by designing and statically analysing new static routing algorithms and extensions to existing ones. This choice comes from an observation that current research is often largely about dynamic studies of advanced aspects of HPC interconnects (such as adaptive routing, dynamic job scheduling, and trace-based optimisations), whereas many of the underlying performance issues justifying these methods could be better addressed by the static routing algorithm beforehand. The proposed routing techniques offer improvements in either or both performance and fault resilience, while partially relaxing a common design constraint (network topology).

This research was initiated in an industrial context as Bull was designing an in-house interconnect for its new Bull eXascale Interconnect (BXI) clusters, alongside a new *fabric manager* (software to monitor and configure the network at a high level, which includes maintaining functional and efficient routing). BXI switches are designed with an integrated ARM CPU and a management network separate from the interconnect, as well as other design specificities. To adapt to these aspects, and use the occasion to start from a clean slate, the BXI fabric manager (BXI FM) is organised differently from competitors' subnet managers. Some routing techniques and algorithms were designed for this system to make full use of the switch design. Out of desire to improve on these techniques, and an intuition that research could be conducted dif-

ferently with this new hardware architecture, the initial thesis subject was drawn out. Research is conducted in conjunction with the LI-PaRAD laboratory (Laboratoire d'Informatique, Parallélisme, Réseaux, Algorithmes Distribués) at UVSQ (the Université de Versailles Saint-Quentin-en-Yvelines) in France. Research is also conducted with the RAAP laboratory (Redes y Arquitecturas de Altas Prestaciones) at UCLM (the Universidad de Castilla-la-Mancha) in Spain, through an international cotutelle. The industrial setting has strongly influenced the research, and several inventions have been patented and integrated in the commercial product during the doctorate. As a whole, however, care has been taken to focus on general cases and the resulting work is largely applicable to other settings.

The rest of this chapter covers elements of contexts for HPC interconnects, routing, and topologies. Firstly, Section 1.2 introduces general elements of HPC interconnects and their routing. Section 1.3 presents topologies used in HPC interconnects, as well as an overview of their current usage by the main HPC vendors, in order to define the target topologies of this thesis as precisely as possible. From there, Section 1.4 studies several existing fat-tree-specific static routing algorithms on which this thesis is based. Section 1.5 finally lays out the problem statement more precisely in the given context, and plans out the following chapters of contributions accordingly.

## 1.2. Problem model

#### 1.2.1. HPC interconnects

Interconnection networks are designed to allow various devices to communicate. To achieve this goal,  $switches^1$  are needed to forward messages from their sender to their recipient. The devices are called  $nodes^2$ , or endnodes in some literature so as to distinguish them from switches. Switches communicate between one another and with nodes via bidirectional links. Links (either copper or optical) are plugged into switch ports (via a transceiver pod for optical links). There may be multiple links connecting the same two switches; multiple ports of a switch leading to the same remote switch are part of a  $port\ group$ . All the links in each considered network are considered equivalent, in terms of latency and bandwidth. In networks where some switches are not directly connected to nodes ( $indirect\ networks$ , see Section 1.3.2), those connected to at least one node are distinguished by being called  $leaf\ switches$  or simply leaves. Switch ports leading to nodes are called endports.

The target communications of the network are those going from node to node (that is, from endnode to endnode). In the context of BXI, where switches are managed *out-of-band* (through a separate network), switches are never the

<sup>&</sup>lt;sup>1</sup>Switches differ from *routers* because switches connect nodes of the same *subnet*, while routers connect different subnets together—only single subnets will be considered here.

<sup>&</sup>lt;sup>2</sup>Types of nodes include compute blades, service nodes, I/O nodes, and accelerators.

source nor the destination of traffic. This makes the node/switch distinction clear cut, and it will be taken into account in our network model and its properties. In existing literature, switches are at times considered as nodes like any other, to the point where many articles do not specify the nature of graph vertices. Classical graph theory and its results generally do not distinguish vertices either.

Taking into account this distinction in the network model, we hereafter note N the set of nodes, and S the set of switches. Each node has a unique identifier (its NID), decided automatically or manually. A link is defined by the nodes or switches it connects, and a locally unique identifier corresponding to the port number, or port rank. We model links with E, the set of directional edges; E is a subset of  $(S \cup N)^2 \times \mathbb{N}$  since no link can connect more than two elements, and several links can join the same two switches: this network model is a multigraph, noted G(S,N,E). Elements of E are noted ((i,j),k), denoting links from i to j, locally indexed k. This is the only difference with the host-switch graph model [89], if we add the restriction that each node is connected to the rest of the graph by one link only. This restriction is valid throughout this thesis, though there also exists research targeting multi-ported host-switch graphs [90]. From this model we can deduce the set of leaves, noted E:

$$L = \{ s \in S \mid \exists \ n \in \mathbb{N}, \ ((s, n), 0) \in E \}$$

This model of the network is called its (multi)graph or *topology*; though the word topology is also used interchangeably with classes of topologies, discussed in Section 1.3.

Some (classes of) topologies are explicitly defined using up and down directions, possibly through the definition of non-negative integer levels of switches. From this, we prepend an up, same, or down directional prefix to the ports, port groups, links, or neighbouring switches of a switch where it applies. These are used extensively in indirect topologies, defined in Section 1.3.2. Nodes and switches are physically organised in racks, often with a top rack (which may or may not correspond to the topological top level) to facilitate inter-rack cabling. The physical organisation often directs or constrains the topology, though sometimes it is the topology design which causes physical organisation choices.

Interconnection systems such as InfiniBand, Cray and BXI implement some form of *channels*, also referred to as *virtual channels* (VCs), or *virtual lanes* (VLs), depending on the context; wherein a single physical port can be used for multiple traffic flows without affecting one another. VCs require sharing the port's buffer space and temporal link usage, either statically or dynamically. VCs are primarily used for quality of service (QoS), wherein different classes of messages are guaranteed not to interfere with one another. They are also used for deadlock avoidance, as mentioned in Section 1.2.7, though the work in this thesis relies on simple edge-level deadlock avoidance. Furthermore, they

are also used to optimise quality of routing for some topologies [8]. Finally, they are also often used by queueing schemes for congestion avoidance and management as well [33, 91]. VCs are largely out of the scope of this thesis, and simple links will be modelled, though there will be several references to VCs. VCs are defined by an edge and a non-negative integer identifier, the channel rank. They can be modelled by C, the set of channels, a subset of  $E \times \mathbb{N}$ , itself a subset of  $(S \cup N)^2 \times \mathbb{N}^2$ . Other literature often models topologies as G(S, N, C).

Specific notations used in this thesis are provided at the end of this Chapter, in Table 1.1.

#### 1.2.2. Network definitions

We will now go over several network definitions which will be useful later on to assess network characteristics for the context and for some contributions.

**Definition 1.** A path from node a to node b is a sequence of edges  $(e_1, e_2, \dots e_n)$  such that the end of  $e_i$  is the start of  $e_{i+1}$ , and such that  $e_1$  starts at a and  $e_n$  ends at b. The number n of edges in the path is its length, or number of hops.

**Definition 2.** The distance between nodes a and b, noted d(a,b) = d(b,a), is the shortest length attainable by paths from a to b (and conversely b to a, since links are bidirectional). Any path whose length is minimal, or equal to the distance, is called a shortest path.

This distance verifies the triangular inequality.

**Definition 3.** The diameter of a network G is the largest distance between all pairs of nodes:  $D(G) = \max\{d(a,b) \mid a,b \in N\}$ .

For example, the diameter of a fully-connected network is 1 and the diameter of a bidirectional ring with n nodes is  $\left|\frac{n}{2}\right|$ .

**Definition 4.** A partition of N is a couple (A,A') such that  $A \subset N$ ,  $A' \subset N$ ,  $A \cup A' = N$ ,  $A \cap A' = \emptyset$ .

**Definition 5.** A cut (A,B) of G(S,N,E) is a partition of  $S \cup N$ . The cut-set of (A,B) is the set  $\{(u,v) \in E \mid u \in A, v \in B\}$  of edges that have one endpoint in A and the other endpoint in B. The node-partition of (A,B) is the partition  $(N \cap A, N \cap B)$  of N.

**Definition 6.** The bisection (A,B) of a network is a cut whose node-partition  $(N_A,N_B)$  verifies  $|\#N_A-\#N_B| \leq 1$ .

Informally, a cut is a bisection if it splits endnodes evenly. Note that in graph theory in general, where switches and endnodes are not differentiated, a bisection splits all nodes evenly. This is one of many cases where we diverge from general graph theory due to the switch/endnode distinction.

**Definition 7.** The bandwidth of a cut is the number of edges in its cut-set.

In general, bandwidth is computed as the sum of individual link bandwidths, but we instead assume that all links are equivalent.

**Definition 8.** The bisection bandwidth of a network, or cross-bisectional bandwidth (abbreviated CBB), is the minimum number of links of all the bisections of a network, defined as:

$$\min\{\#E_C \mid E_C \text{ the cut-set of a bisection of } G\}$$

For example, the CBB of a fully-connected network with n nodes is  $\lfloor \frac{n}{2} \rfloor \times \lceil \frac{n}{2} \rceil = \lfloor \left( \frac{n}{2} \right)^2 \rfloor$  and the CBB of a ring is 2. The CBB is a theoretical worst-case scenario bandwidth of network-wide group communications assuming perfect path selection. However, the actual path selection might result in significantly lower effective bandwidths [40].

**Definition 9.** The blocking factor of a network is the ratio between the greatest and smallest bandwidths of its bisections, defined as:

$$\frac{\max\{\#E_C \mid E_C \text{ the cut-set of a bisection of } G\}}{\min\{\#E_C \mid E_C \text{ the cut-set of a bisection of } G\}}$$

Informally, the blocking factor represents the maximum variation in worst-case scenario bandwidth of network-wide group communications, depending on communication pattern.

**Definition 10.** A network has constant bisection bandwidth (or constant CBB) if its blocking factor is equal to 1.

This definition means that all the bisections of a network with constant CBB have the same bandwidth.

HPC cluster interconnect design often relies on networks being connected according to specific topologies, which will be discussed in Section 1.3. The aim is generally to guarantee beneficial network properties such as high CBB and low diameter, while simplifying routing design for various criteria.

# 1.2.3. Routing for HPC interconnects

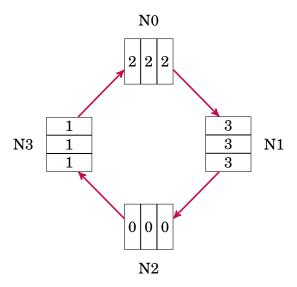

Routing is the exercise of assigning correct paths to all messages. It is different from *switching*, which describes how messages are processed at a lower level. To provide basic functionality, routing should ensure that messages will reach their destination in finite time. Firstly, this means that every message must be directed to its correct destination (and naturally avoid infinite loops). Furthermore, *deadlocks* must be avoided: a deadlock situation occurs when there is a cycle of packets which can never advance because they each require the next channel to be freed [14], as shown in Figure 1.1. Deadlocks

Figure 1.1: Example of a deadlock, with four nodes N0 to N3, each sending a message to the opposite node, and with every buffer full.

are particularly problematic in *lossless* networks (in which packets cannot be dropped), which form the majority of HPC networks. More on deadlock avoidance can be found in Subsection 1.2.7.

It is not sufficient for routing to be functional, it must also result in low congestion for the supercomputer to perform efficiently. Different implementations of routing, or *routing functions*, may affect network performance in various ways. Network latency may be affected by paths being longer than necessary (a routing function is *minimal* if it guarantees shortest paths, and *non-minimal* otherwise). Furthermore, the routing function may cause *contention* of network resources, increasing latency and/or reducing throughput. Sustained contention, or *congestion*, is often shown to take the form of points of contention causing buffers to progressively saturate in routes crossing these points. These trees of congestion are called *congestion trees*, and they evolve towards sources of contending packets. This is sometimes distinguished into low-order head-of-line (HoL) blocking for so-called *hot* message flows directly causing congestion versus high-order HoL blocking for *cold* message flows which happen to go through an already congested edge [46].

In commonly used topologies, path length is constrained. Furthermore, path length has lesser repercussions on application latency than other parameters such as network congestion. For these reasons, the design of high-quality routing algorithms mostly aims to reduce or minimise congestion risk, generally by spreading competing traffic flows across the available resources, or *load balancing*. Depending on the granularity, these resources might be switchpaths, links, or virtual channels. Splitting competing traffic into different virtual channels reduces head-of-line blocking [24]. However, designing and

using more VCs increases latency and hardware complexity, and is only useful when it provides greater benefits than its own cost.

Other mechanisms attempt reactive congestion management by throttling (temporarily slowing down) offending message producers [30, 42] with hard-to-tune results that generally do not scale [102, 31]. However, Cray claims to have implemented a stable and scalable reactive throttling congestion management mechanism [13, 18].

The study of quality of routing is approached in various ways in existing research, where techniques are more often than not studied in experimental and quantititave approaches, and precise characterisation of HoL blocking is not practical. Some techniques are studied in general approaches, such as approximation of effective CBB based on common usage scenarios [40]. Other techniques are studied under specific use cases (for individual target clusters, with Deimos [19] being one example among many others) either by experimentation with sample applications (such as specific benchmarks like the NAS Parallel Benchmark suite in that same cited work, once again with numerous other examples) or by simulation of synthetic traffic (with hotspot traffic [70] being a common example to study congestion) or communication traces from real application runs [9]. The goal is either to directly compare application run times or to estimate effective network metrics potentially transferable to other use cases. Common metrics studied using experimentation or simulation are effective throughput and latency as functions of offered communication load, from which can generally be interpreted comparable characteristics such as saturation load and corresponding max throughput.

A simpler approach is to count the number of paths at each edge, or port, of the network. The maximum value, called edge-forwarding index, reflects the maximum load of the network under sustained communication between all nodes [39].

Other techniques taking into account more information such as job placement, communication pattern matrices, or fault tolerance, usually integrate the corresponding data points in their study. Chapter 2 presents the approach used in this thesis to study quality of routing which is useful for the scope of the proposed techniques. A specific use case will be presented in Section 1.2.8.

In case of equipment failure or other unexpected behaviour, routing must be fault-resilient to remain functional. Fault resilience will be presented in Section 1.2.9. Contexts for these upcoming subjects are impacted by the types of routing implementations, which will therefore be presented beforehand in Sections 1.2.4 and 1.2.5, followed by a categorisation of approaches to programming routing algorithms in Section 1.2.6.

#### 1.2.4. Centralised static routing

Static—or deterministic—routing is the simple and efficient type of routing that is most widely available in HPC. Such a routing can be characterised by a function of the form  $R: N^2 \times S \to E$ , where a message coming from and going to nodes (in  $N^2$ ) via a switch (in S) is routed via an output edge, which must naturally start from the considered switch. In the majority of applications of static routing, however, routing is source-independent, and can be characterised instead by a function of the form  $R: E \times N \to E$ , where each input port (in E) and each destination (in N) are associated with a corresponding output port. In practice, this function is implemented using Linear Forwarding Tables (LFTs, often referred to as routing tables), with generally one entry per switch and destination, valid for all the input ports of the switch (with the shape  $R: S \times N \to E$ ). Edges are used in each model for simplicity, though channels are considered in other works, by substituting E with C. Interconnection networks for HPC usually have a centralised static routing mechanism wherein a subnet manager (responsible for its connectivity) computes LFTs off line and uploads them to the switches. Static routing guarantees in-order delivery in lossless HPC networks.

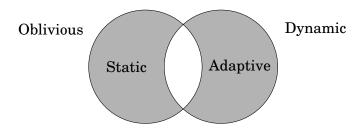

Static routing is *oblivious* insofar as it does not take into account the current state of the network. However, there are also some *dynamic* (i.e. *multi-path*) routing techniques which are oblivious [24, 17, 36]. The only dynamic oblivious techniques commonly found in the existing literature involve a random selection: take for example Valiant routing which chooses a random intermediary switch to send messages, later performing minimal routing from that switch to the destination [82].

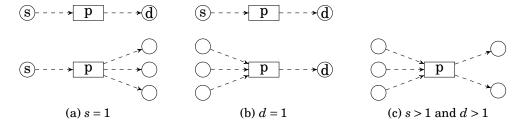

### 1.2.5. Adaptive routing

An *adaptive* routing algorithm, unlike oblivious ones, takes into account the state of the network to make routing decisions [24]. Figure 1.2 summarises algorithmic categories described up to now. This network information may be local information like port/VC congestion or the number of available credits, or global information like switch congestion across the network. A good adaptive routing technique overcomes the inflexibility of static routing by making use of under-used resources to alleviate congestion. However, adaptive techniques that eagerly spread traffic onto a large proportion of network resources tend to increase congestion [70, 71]. Adaptive routing breaks the guarantee of in-order delivery within communication flows [34].

BXI implements adaptive routing for traffic (marked as authorised for outof-order delivery) with a search of lowest contention (measured as buffer usage across VCs) between the deterministic route and a random set of alternative routing tables. The set size and activation threshold are configurable. The alternative routing tables are computed by the routing algorithm and uploaded by the fabric manager.

Figure 1.2: Categories of routing algorithms

Distributed applications that take advantage of BXI NICs indirectly rely on the Portals interface [4]. Some communications are implemented using PtlPut, for which some layer must provide ordering between packets and messages in each flow. Offloading the Portals matching engine to the NIC imposes restrictions on the amount of memory available per flow, and reordering at the destination becomes untenable. Instead, these messages are marked at the source as non-adaptive, so as to benefit from the in-order delivery guaranteed by static routing. This is one reason why good quality static routing was deemed critical and motivated the subject to be explored in this thesis.

# 1.2.6 . Approaches to programming routing algorithms

Several categories of approaches to programming routing algorithms are presented below, with references to corresponding example routing techniques. These are not strictly speaking algorithmic categories, and there is some overlap, but they do outline to some extent the space of possibilities available to the programmer.

Dynamic programming and greedy algorithms A dynamic programming technique breaks down the problem into a sequence of subproblems of the same type, each easier to solve than the full problem. A greedy algorithm progressively builds a global solution through a series of locally optimal choices. These approaches might be intuitive insofar as they could generally be described with the same steps a person might take to solve the problem by hand, such as assigning routes to each destination one after the other, based on previous decisions like Dijkstra or Bellman-Ford algorithms. Greedy algorithms are difficult to distribute or parallelise while also keeping guarantees about global results. Examples include Ftree [97], SSSP [41] (and its slower but deadlock-free counterpart DFSSSP [19]), and Nue [21].

**Closed-form algorithms** Some algorithms determine each element of the solution using a closed-form operation, i.e. based on input alone and no dependency to other elements of the solution. These methods might require a preprocessing phase to prepare the information each element requires, such as topological addresses. This phase can be made more efficient when topological properties are regular. Such a formulation allows implementing a perfectly parallel computation phase. Examples include Dmodk [95] and Smodk [61, 73].

**Randomised algorithms** Routing algorithms are sometimes based on random choices as a means to approximate agnostic load balancing or congestion avoidance. Examples include Valiant's algorithm [82] and Greenberg's RAN-DOM [37].

MILP programming Some routing methods describe the constraints of the problem as a set of linear relationships. This way, load balancing explicitly becomes an optimisation problem. This approach is used mostly for communication-pattern-aware routing. Generic Mixed Integer Linear Programming methods can then be used, with potential tweaks corresponding to the specific nature of the problem space, such as BSOR, BSORM [49], and some with topology-specific tweaks to achieve better routing run time [66]. BeFS [72] is another discrete method, using branch-and-bound.

**Distributed algorithms** In some cases it may be possible to build a globally correct or optimal solution with no central computation unit. In such situations, distributed computation units can communicate with one another and use local information to make decisions. Some routing techniques, especially adaptive ones, rely on switches computing routes based on local information. This might provide fast reaction time to network changes or congesting traffic. Examples include the Chaos router [50] and UGAL [80], two techniques for adaptive routing.

Centralised algorithms are beneficial, because they are generally easier to design than fully distributed ones, even when multithreaded. Like the majority of similar products, BXI indeed uses only centralised algorithms to compute routing tables.

#### 1.2.7. Deadlock avoidance

Deadlock avoidance is a major aspect of the co-design of switches, topologies and routing algorithms. Packet dropping is a simple mechanism to guarantee deadlock-freedom (wherein a packet is simply discarded if it does not advance fast enough), but HPC interconnects are lossless to improve performance, and are therefore at real risk of deadlocks.

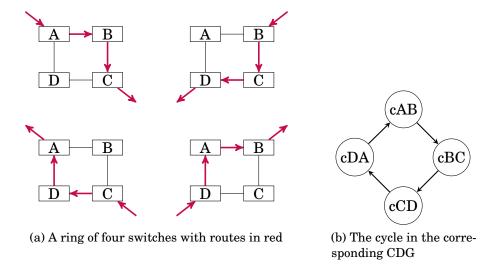

Most approaches used to guarantee deadlock-freedom rely on the absence of channel dependency cycles. A channel dependency  $a \rightarrow b$  corresponds to the potential for channel b to be used by a message after it has used channel a.

**Definition 11.** The channel dependency graph (CDG), for a given interconnection network, I, and routing function, R, is a directed graph, CDG(I,R) = G(E,D). The vertices of CDG(I,R) are the edges of I, and its edges are the pairs of edges connected by R:

$$D = \{(e_i, e_j) \in E^2 \mid \exists \ n \in N, \ R(e_i, n) = e_j\}$$

Since there is no route from an edge to itself, there is no 1-cycle in *CDG*.

**Definition 12.** Channel dependencies are connected in CDG paths as follows:

$$[e_0,e_1,\ldots] = [\ldots,(e_i,e_{i+1}),(e_{i+1},e_{i+2}),\ldots], \quad \forall i,(e_i,e_{i+1}) \in D$$

Dally proved that cycles in the CDG were a necessary condition for deadlocks to arise [14]. Figure 1.3 provides an example potential deadlock situation and the corresponding CDG. From this, it is sufficient to guarantee the absence of cycles in the CDG to prove deadlock-freedom. This only requires a static understanding of the routing function, but ignores some deadlock-free situations that arise dynamically. Guaranteeing cycle-free CDGs is therefore relatively simple, and is generally implemented through directional routing restrictions, as will be explored further in Section 1.3. Some research goes further and explores deadlock-freedom in routing functions which contain cycles in the CDG [78].

Figure 1.3: Example of a potential deadlock situation. Deadlock occurs if all the buffers in the cycle become full.

# 1.2.8. Node-type heterogeneity

Many large supercomputers are used for varied applications, with varied resource needs. To provide adequate resources, these supercomputers are often designed with multiple kinds of available equipments, whose usage impact network usage. In practice the type of equipments encountered are among the following:

- Compute nodes, with powerful central processing units (CPUs);

- Storage nodes, with slower remote access to large regions of memory than local memory;

- General purpose graphic processing units (GPGPUs), with fast parallel units for specialised SIMD (single instruction multiple data) operations;

- Field-programmable gate array units (FPGAs), with reprogrammable gate logic for fast processing of general purpose applications;

- Service nodes, operating network management or interacting with external networks for user access.

These might be connected directly to other components, or to the interconnection network (in which case they are seen as endnodes). There are approaches to extend usability of directly connected equipment to other nodes, such as rCUDA for GPUs [26]. That is outside the scope of the interconnection management layer of the network. On the other hand, use of equipment visible as endnodes can be strongly affected by the network management layer. In particular, one case in which the network might provide inadequate performance as a result of node-type heterogeneity is that of applications in which communications are organised in separate time frames for separate types of equipment. Observation shows that purely static (and therefore oblivious) routing in such cases might restrict traffic to each node-type group to a subset of available network resources and result in lower performance. Such a situation, which happened during the course of this thesis, is studied in more detailed in Chapter 3.

#### 1.2.9. Fault resilience

Network topologies and corresponding routing are often defined statically, while real operation may require replacing or extending network components. Furthermore, as the sheer amount and power of equipment increases in current and future supercomputers, the average rate of equipment failures increases accordingly [76, 20, 88]. Failures are especially frequent with optical links [12] typically used to cover long distances in large scale clusters. For these reasons, fault resilience becomes important to avoid frequent application interruption. A centralised subnet manager (or fabric manager) can react to equipment failures that do not break graph connectivity by uploading updated routing tables. In order to do this, it requires a fault-resilient routing algorithm capable of rapid re-routing. The challenge is to provide these characteristics while maintaining high-quality static load balance.

There are various approaches to guaranteeing deadlock-freedom during transition phases in case of routing change [25, 53], but when possible, a simple approach is to prove that every possible routing function is part of a *super function* which is itself deadlock-free, thus guaranteeing that any transition step between any two possible routing functions is also deadlock-free [68]. This is possible for example when a direction restriction applies uniformly to any degraded state of a network, as will be the case in Section 1.3.2.

More context regarding topology-specific fault resilience will be provided in Section 1.4.6.

## 1.3. Topologies

Topologies are ubiquitous in the design of supercomputers. They help provide guarantees about performance, resilience, or other design goals through their network characteristics. For example, a topology with a lower diameter tends to constrain application latency more, and a topology with a higher CBB tends to accommodate a higher bandwidth. Other aspects can be considered, such as required hardware availability and cost, ease of expansion, and ease of deadlock-free routing.

The purpose of this Section is threefold. Firstly, it should help justify the focus on fat-trees, which are only one among many other usable topologies.

Secondly, it should give some context to help appreciate the pros and cons of fat-tree-specific routing. Lastly, it should define to some extent what the specific target topologies are, given the wide array of topologies called fat-tree in the existing literature.

## 1.3.1. Direct topologies

In *direct* topologies, every switch is connected to nodes (through *internal* links) to give them access to the rest of the network (via *external* links). In such a case, S = L. By considering each switch and its directly connected nodes as one vertex of the network graph, this allows simplifying the graph to its switches and external links. The number of nodes connected to each switch is sometimes specified in the topology definition. For a given switch radix and number of nodes, the external connection scheme affects the corresponding number of switches and links required, directly impacting network cost. Performant direct topologies generally result in networks in which it is difficult to integrate new equipment. Hop count is given only across external links, therefore artificially reducing the diameter by 2 hops, assuming nodes are connected with the same links as inter-switch connections. Examples of direct topologies are provided below.

**Definition 13.** A ring topology is a connected graph where each vertex is connected to exactly two different vertices with one link each. A bus topology is a ring with one link removed.

Both of these topologies are extremely cheap in terms of link count: with N=n switches, only n or n-1 links are required. However, they have low CBB (1 or 2) and high diameter (n-1) or  $\lfloor \frac{n}{2} \rfloor$ , making them perform poorly for concurrent applications. Furthermore, rings are easily affected by deadlocks: guaranteeing cycle-free CDG in a ring or bus requires either direction restrictions or using multiple VCs.

**Definition 14.** A mesh topology is a two-dimensional square grid of vertices, where non-diagonal neighbours are connected with one link. A torus topology is a mesh where the first and last vertices of each row and column are connected with one link.

Meshes are also cheap: with  $N=n\times n$  switches, only 2(N-n) links are required. They provide a slightly higher CBB of  $2\left\lceil\frac{n}{2}\right\rceil$  and a slightly lower diameter of 2(n-1), but still result in poor performance. To avoid deadlocks, either a turn order model [35, 60] or separation into distinct VCs is required [15]. Torus topologies cost only slightly more than meshes (2N links), cut the diameter down to  $2\left\lfloor\frac{n}{2}\right\rfloor$ , and raise the CBB to  $4\left\lceil\frac{n}{2}\right\rceil$ .

**Definition 15.** A Hypercube topology is a higher-dimension 2-by-2 mesh. A k-ary n-cube topology is a generalisation of a torus with n dimensions and k vertices in each dimension.

Note that hypercubes are 2-ary n-cubes, and that toruses are k-ary 2-cubes. k-ary n-cubes provide competitive topological characteristics [16] and are commonly used in massively parallel processors (MPPs) and HPC interconnects (such as the Tofu interconnect, used in the K computer and the Fugaku supercomputer, with each being the most performant at the network-intensive HPCG benchmark at the time of their installation [23]), despite difficulties in cabling, scalability, and deadlock-freedom.

DragonFly (DF) topologies [48] are a more recent field of research. Specific DFs are defined by specifying groups of switches and the intra-group and intergroup connection schemes. A common example is a DF with a flattened butterfly intra-group scheme and a pruned Hamming graph inter-group scheme. Real DFs have diameters ranging from 2 to 5. Routing DFs requires special attention in order to guarantee deadlock freedom [32, 57, 56]. Furthermore, DFs provide low performance for adversarial inter-group traffic patterns unless either fine-tuned non-minimal<sup>3</sup> adaptive routing techniques [48, 44, 67] or group-spreading job placement policies (RDR or RRR in [43]) are used. Similarly, when jobs are placed contiguously, all links connecting groups assigned to different jobs are left unused in case of minimal routing; these links are referred to as dark links [22].

Other large low-diameter direct topologies have been studied in detail [47]. Designing a diameter-2 topology with high bandwidth, path diversity, and node count results in networks with structurally guaranteed low congestion and latency, but requires careful attention and generally requires complicated routing methods.

## 1.3.2. Indirect topologies

An *indirect* topology contains non-leaf switches, wherein  $L \subseteq S$ . This section will present the only common type of indirect topology, *Multistage Interconnection Networks* (MINs).

**Definition 16.** A non-blocking telephone network is always capable of accommodating any new call (from an available caller to an available recipient), regardless of existing traffic.

**Definition 17.** A telephone network is rearrangeably non-blocking if for a given set of calls, there exists a routing function for which the network will not block.

Clos designed indirect topologies for point-to-point telephone networks (using crossbar switches) to guarantee non-blocking switching at reasonable cost [11]. These unidirectional multistage interconnection networks (MINs, or UMINs) are composed of one level of input switches, an odd number of levels of intermediary switches, and finally one level of output switches. Depending on

<sup>&</sup>lt;sup>3</sup>In DFs, *minimal* and *non-minimal* often refer to use of intergroup links only, or not, respectively.

the numbers of input ports, output ports, and input switches, a Clos network can be non-blocking, or only rearrangeably non-blocking.

Unlike UMINs, bidirectional multistage interconnection networks (BMINs), are composed of bidirectional links and have all leaf switches on one side (the bottom one, with levels ordered vertically). The height (in number of levels) of a BMIN is noted h.

**Definition 18.** In a BMIN, a node is down-accessible from a switch if it can be reached with a path made up only of downward hops.

**Definition 19.** The direction of an edge e in a BMIN, noted dir(e), is equal to the difference of levels incurred by following the edge.

For example, an edge leading from level 4 to level 1 has a direction of -3.

**Definition 20.** In a BMIN, a topological group is a subgraph connected to the rest of the graph by up-edges only (with dir > 0), which lead only to switches at a level greater than all those in the subgraph.

**Definition 21.** An up-down path  $(e_1 \dots e_n)$  is such that:

$$\exists 1 < i \le n, \quad \forall j < i, \quad \operatorname{dir}(e_j) > 0,$$

$\forall j \ge i, \quad \operatorname{dir}(e_j) < 0$

**Definition 22.** An up-down routing function is made up only of up-down paths.

**Property 1.** Any up-down routing function is deadlock-free in BMINs.

This advantageous property (applicable to fat-trees, which are described in Section 1.3.3), is claimed in existing literature [64, 24], and Duato extends the notion of strict global ordering of links sufficient to prove deadlock-freedom in UMINs, to a strict local ordering of links in BMINs. A new proof, which doesn't rely on extending the UMIN property, is provided here.

*Proof.* In a BMIN, edge directions are either upwards, samewards, or downwards, and each channel dependency in its CDG has a pair of directions based on starting and ending edges. In an up-down routing function, no such edge is samewards, and valid pairs of directions can only be up-up, up-down, downdown (and not down-up). From this, CDG paths (see Definition 12) can only be formed as a concatenation of a CDG subpath with only upward edges and one with only downward edges, each of length 0 or more. Deadlock-freedom can be proven by showing that no valid path in the CDG contains a cycle, as seen in Section 1.2.7. To have a cycle, there must exist one valid CDG path verifying:

$$i < j$$

,  $e_i = e_j$

If  $e_i$  is upwards, then  $e_j$  must occur in the upward CDG subpath; however, this CDG subpath is strictly monotonous in terms of levels and cannot contain a cycle. The same applies symmetrically if  $e_i$  is downwards. Therefore, there cannot be any cycle in the CDG.

As described in Section 1.2.7, and defined in [68], up—down super routing functions in BMINs are deadlock-free, thus guaranteeing transitively deadlock-free fault-resilient algorithms.

**Property 2.** Any up\*-same?-down\* routing function is deadlock-free in BMINs.

Note that \* means "any number of times" and ? means "at most once", similarly to regular expressions. Informally, this describes routes with at most one samelink between the upward and downward phases. A novel proof, using the proof for Property 1, is provided here.

Proof. In an up\*-same?-down\* routing function in a BMIN, there is no down-up, down-same, same-up, or same-same dependency in any CDG path. We will prove deadlock-freedom by showing that there is no cycle in any valid CDG path. If such a CDG path contains no same edge, then the proof for up-down routing functions provided in Section 1.3.1 applies, and there cannot be any cycle. Otherwise, the sameward edge in the CDG path is preceded only by upward edges, and followed only by downward edges. By virtue of strict monotonicity, neither side contains a cycle. By virtue of uniqueness (and lack of any 1-cycle), the sameward edge cannot induce a cycle. Therefore, there cannot be any cycle in the CDG. □

# 1.3.3. Fat-tree topologies

A majority of current leading network topologies for HPC clusters are fattree variants: the five most powerful clusters of the June 2019 Top500 list [81] had fat-tree topologies. The name fat-tree has been used to describe many different topologies since the original CM-5 version. Despite many differences in definition, fat-trees are always BMINs with at most one downward switchpath from any top switch to any leaf switch. Fat-trees are usually regular and symmetrical. Their "fatness" corresponds to increasing bandwidth when going up levels, and this increase is often designed to provide a constant CBB. Many studies associate fat-trees with this property while others distinguish non-slimmed and slimmed (or oversubscribed) fat-trees. The other important beneficial property is that minimal routing in fat-trees is up-down and therefore deadlock-free.

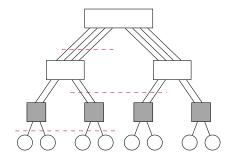

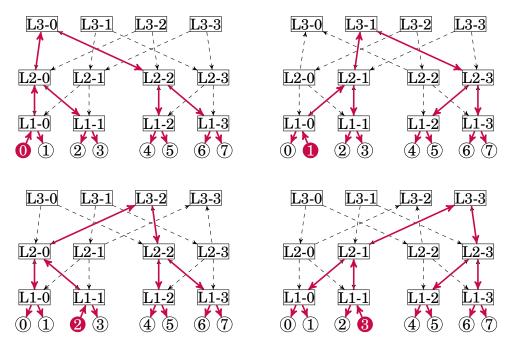

Figure 1.4: Three level binary Leiserson fat-tree. Switches are rectangles (with leaves in grey) and nodes are circles. Several bisections are shown in dashed red lines, illustrating constant CBB.

#### Leiserson fat-trees

Fat-tree topologies were introduced by Leiserson [51] in the CM-5 for their capacity to accommodate any virtual network for a given size. These fat-trees are organised like regular trees (with a constant number of connected links across switches, or arity, k), but with aggregate link bandwidth increasing by a factor k at each level. Note that in their original declination, this rule was only precisely defined for so-called universal fat-trees; however, literature generally considers these only when referring to Leiserson fat-trees. Levels go up from the leaves to the top switches. An example with k = 2 and n = 3, n being the number of levels, is shown in Figure 1.4.

Massive Parallel Systems such as the CM-5 implemented fat-trees using efficient on-chip networks with so-called concentrator switches. Leiserson fat-trees cannot be implemented using the crossbar switches found in clusters because they would require an (#N)-port top switch. Were such a switch available, connecting it to all nodes directly would be the best and cheapest possible network.

A short section regarding routing in Leiserson fat-trees is provided in annex Section 1.

# K-ary n-trees

K-ary n-trees were subsequently formalised by Petrini [64] and describe an implementation of fat-trees using fixed-radix crossbar switches organised in *complete bipartite* subgroups (wherein two sets of switches in adjacent levels are fully connected, but only across levels). The diameter of a k-ary n-tree is twice its number of levels. Bisection bandwidth is constant, which is often described as being rearrangeably non-blocking. That description relates to the potential capacity for such a network to have a non-blocking routing function for any communication permutation<sup>4</sup>, though that is not possible using static routing, and non-permutation communications are to be expected as well. The

$<sup>^4</sup>$ The notion of non-blocking routing functions dates back to circuit-switching networks, in which only permutations can be performed

Figure 1.5: A 2-ary 3-tree (with  $2^3 = 8$  nodes). Each switch is required to have 4 ports except for the top switches (which have only 2 ports).

connection scheme is defined formally using two rules based on switch and node addressing, both n-tuples.

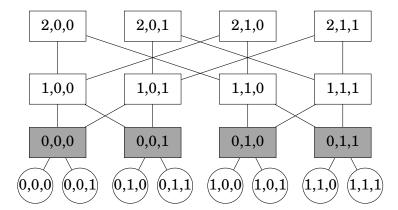

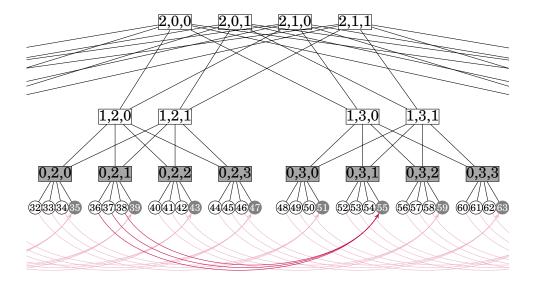

**Definition 23.** In a k-ary n-tree, switches  $(l, w_0, ..., w_{n-2})$  and  $(l', w'_0, ..., w'_{n-2})$  (of level l and l' respectively, with  $l' \ge l$ ) are connected if and only if l' = l+1 and  $w'_i = w_i, \forall i \ne l$ . Leaf switch  $(0, w_0, ..., w_{n-2})$  and node  $(w'_0, ..., w'_{n-2}, p)$  are connected if and only if  $w_i = w'_i, \forall i \in [0, n-2]$ , with  $p \in [0, n[$ .

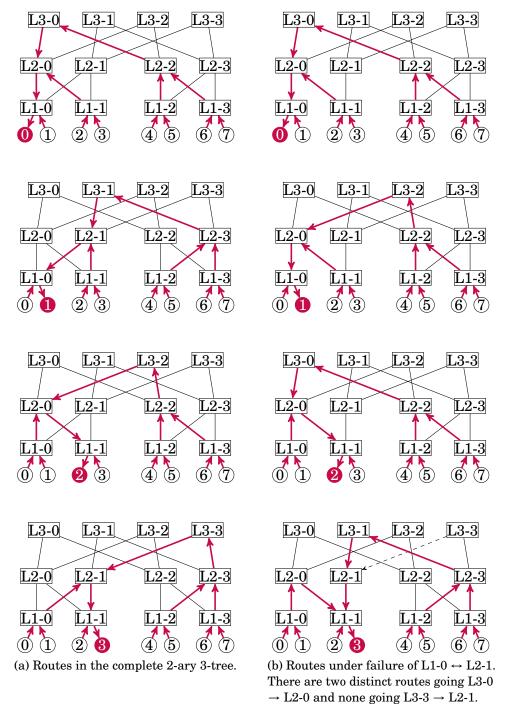

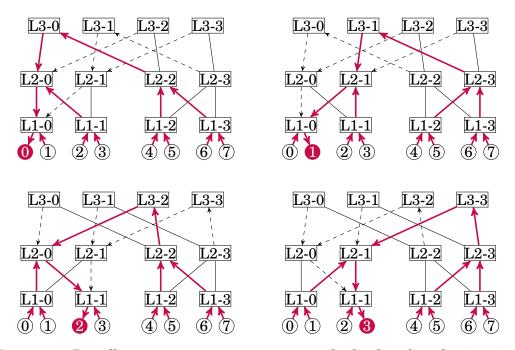

When routing k-ary n-trees, every pair of nodes has multiple nearest common ancestors (NCAs). Optimal routing then comes down to distributing NCAs via which to route to avoid network-congestion from happening in the first place. Deterministic and adaptive routing algorithms have been provided for k-ary n-trees [36].

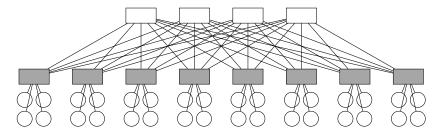

#### GFTs, XGFTs, m-port n-trees

Generalised Fat-Trees (GFTs), introduced by Ohring [61], describe a more general class of topologies for which the upward and downward arities can differ.

**Definition 24.** A graph defined by the formula

is a GFT with h levels, with each switch connected to m switches below and w switches above. It is constructed recursively from m distinct copies of GFT(h-1; m; w). Each of these fat-trees, used to build the complete graph, is referred to as a topological group.

This allows creating oversubscribed fat-trees with smaller and cheaper networks and only partly reduced overall performance. This process of reducing the bisection bandwidth of a network is often called *pruning*. A GFT has  $m^h$

nodes, and  $w^l m^{h-l}$  switches at level l. As a result, the total number of switches is:

$$\sum_{l=0}^{h-1} w^l m^{h-l} = m^h \sum_{l} \left(\frac{w}{m}\right)^l = m^h \frac{1 - \left(\frac{w}{m}\right)^h}{1 - \frac{w}{m}} = \begin{cases} m \frac{m^h - w^h}{m - w}, & \text{if } m \neq w \\ h m^h, & \text{if } m = w \end{cases}$$

In practice, assuming uniform port count for all switches in a network, GFTs are detrimental since top-switches necessarily have unused ports. This issue and others can be solved by *Extended Generalised Fat-Trees* (XGFTs), introduced alongside GFTs, which provide a per-level definition of arities.

**Definition 25.** A graph defined by the formula

$$XGFT(h; m_0,...,m_{h-1}; 1,w_1,...,w_{h-1})$$

is an XGFT with h levels, with each switch of level i connected to  $m_{i-1}$  switches below and to  $m_i$  switches above. It is constructed recursively from  $m_{h-1}$  distinct copies of  $XGFT(h-1; m_0, ..., m_{h-2}; 1, w_1, ..., w_{h-2})$ , its topological groups.

This definition provides even more flexibility in terms of oversubscription. For example, one might decide to provide more bisection bandwidth in the lower levels than in upper levels if few applications are expected to span across topological groups. As a practical example, this is the case in some BXI clusters, connected as fat-trees pruned only in the top level. Experience at Atos has shown that other than benchmarks, few current user applications make strong use of the total bandwidth provided by the interconnect.

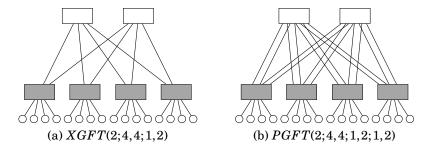

XGFTs also allow designing fat-trees with both constant CBB, often referred to as rearrangeably non-blocking, and fully-plugged fixed-radix switches. These graphs respect the following formula:

$$XGFT(h; k, \ldots, k, 2k; 1, k, \ldots, k)$$

The same topology is also called *m*-port *n*-tree [52], with m = 2k.

#### PGFTs, RLFTs

Parallel Ports Fat-Trees, or Parallel Generalised Fat-Trees (PGFTs), are an extension to XGFTs allowing for multiple interlinks [95]. The definition allows for one value of "parallel ports" per level:

**Definition 26.** A graph defined by the formula

$$PGFT(h; m_0,...,m_{h-1}; 1,w_1,...,w_{h-1}; p_0,...,p_{h-1})$$

is an h level PGFT, with each switch of level i connected to  $m_{i-1}$  switches below (using  $p_{i-1}$  interlinks) and to  $m_i$  switches above (using  $p_i$  interlinks).

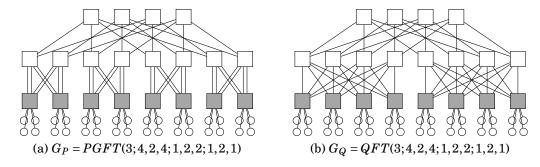

Figure 1.6: Best efforts to build a constant-CBB network with 16 nodes and fully-plugged 8-port switches using XGFT and PGFT topologies.

This allows more link redundancy, but more importantly greater flexibility in network design. In particular it allows describing networks with constant CBB for more configurations than XGFTs can. A simple example is provided in Figure 1.6, which illustrates that a constant-CBB network with 16 nodes and fully-plugged 8-port switches can be designed using PGFT notation, but not using XGFT notation.

*Real-Life Fat-Trees* (or RLFTs) are defined alongside PGFTs to account for several constraints often expected of fat-trees in real life [95].

**Definition 27.** Real-Life Fat-Trees (or RLFTs) are constant-CBB PGFTs with all switches having the same radix and being fully plugged, and each node being connected to one leaf through one link.

This is identical to the requirements of m-ports n-trees, with the added possibility of specifying the number of parallel ports at each level. In some cases, however, RLFTs are equivalent to m-ports n-trees. An RLFT with h levels, K-port switches, and a vector p describing parallel links, has the corresponding PGFT definition:

$$PGFT \left( h; \quad \frac{K}{2}, \ldots, \frac{K}{2p_i}, \ldots, \frac{K}{p_{h-1}}; \quad 1, \ldots, \frac{K}{2p_i}, \ldots; \quad \ldots, p_i, \ldots \right)$$

The PGFT in Figure 1.6.b is an 8-port 2-level RLFT with p = [1,2].

In this thesis, the names fat-tree, or  $regular\ fat$ -tree, will be used for any topology that can be described as a PGFT. This includes Leiserson fat-trees, k-ary n-trees, GFTs, XGFTs, RLFTs.

#### 1.3.4. Irregular fat-trees (IFTs)

Terrain observation of real systems shows that clusters labelled as fat-trees often break properties usually associated with fat-trees. This happens mainly either because fat-tree connection rules are relatively difficult to respect, or in order to attempt improving the performance-to-cost ratio of the network. In this thesis, fat-tree-like networks are categorised as IFTs (a novel nomenclature) if any of the following irregularities applies:

- Multiple down-switch-paths between a top switch and a leaf;

- Variations in arity between switches in the same level (variations due to failures do not strongly apply);

- Connections within a level or skipping a level;

- Leaves in levels higher than others.

Two formally defined topologies which count as IFTs are described below. However, the general case of IFTs does not correspond to formally described topologies, and instead is at best described as fault resilience, as shown in Sections 1.2.9 and 1.4.6.

## **QFTs**

Zahavi defined a slight variation to PGFTs that allows building networks with wider subgroups for a given number of nodes [98]. This *Quasi Fat-Tree* (QFT) topology is defined similarly to PGFTs, but with the p vector referring to cross-connections instead of interlinks:  $p_l = 2$  means that at level l, pairs of groups are linked together. QFTs are defined with the assumption that there is only one level l at which  $p_l > 1$ , with generally l = 1. Connecting two groups together means that every lower element in that group has two distinct up-switch-paths to every top switch, instead of only one. This breaks a core property often associated with fat-trees, making load balancing routing more difficult to express. On the other hand, this is presented as an opportunity for greater fault-tolerance through greater switch-path diversity.

# MegaFly

An indirect variant of the DragonFly, called *MegaFly* (or *DragonFly*+ by Mellanox), uses complete bipartite graphs for the intra-group cabling [10, 79, 28]. The inter-group cabling rules are not stricter than for DFs (there must be at least one direct link connecting each pair of groups). Two advantages of the MF topology over DFs are the increased scalability and path diversity, at the cost of twice the number of switches and an increased average hop count. In this topology, non-leaf switches (called roots) are connected together through samelinks. This topology is a BMIN, and therefore accommodates up\*–same?–down\* routing in a deadlock-free manner (see Property 2). Minimal routing is

up\*-same?-down\* in MFs, and therefore deadlock-free, unlike minimal routing in DFs.

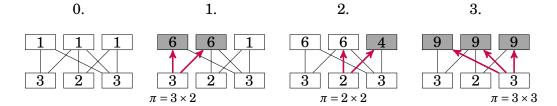

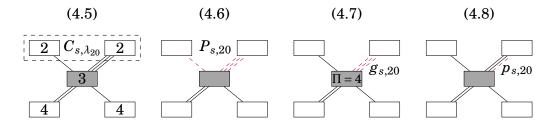

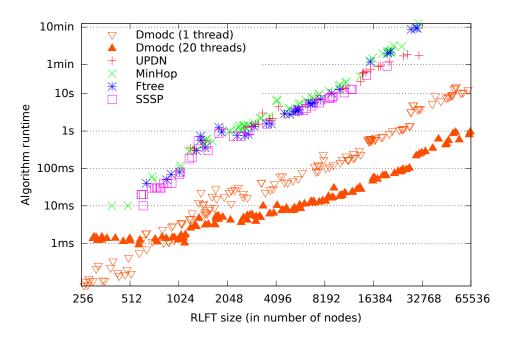

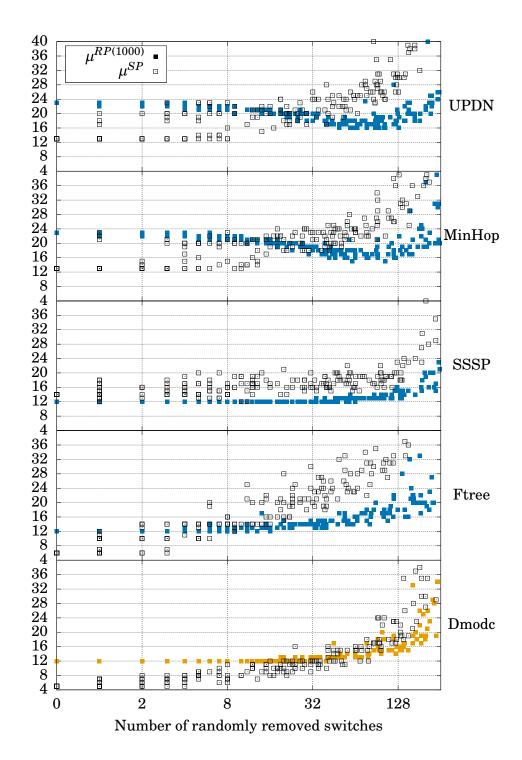

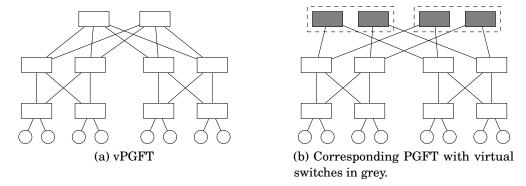

Similarly to DFs, literature has focused on non-minimal routing to overcome low effective bandwidth in MFs for adversarial traffic (potentially resulting from natural job placement). This requires use of multiple VCs to guarantee deadlock-freedom, since consecutive samelink hops incur chainable channel dependencies within the top level.