## Low power, high-reliability class-C voltage-controlled oscillator for space application in 28 nm FD-SOI technology

Ayoub Ait Ihda

### ► To cite this version:

Ayoub Ait Ihda. Low power, high-reliability class-C voltage-controlled oscillator for space application in 28 nm FD-SOI technology. Electronics. Université de Bordeaux, 2022. English. NNT: 2022BORD0442 . tel-04011169

## HAL Id: tel-04011169 https://theses.hal.science/tel-04011169v1

Submitted on 2 Mar 2023  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

# DOCTEUR DE

# L'UNIVERSITÉ DE BORDEAUX

# ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÈNIEUR

## SPÉCIALITÉ ÈLECTRONIQUE

Par Ayoub AIT IHDA

# Low power, high-reliability class-C voltage-controlled oscillator for space application in 28 nm FD-SOI technology

Sous la direction de : Yann Deval

## Soutenue le 16/12/2022

Membres du jury :

M. Yann DEVAL, Professeur, Bordeaux INP

- M. Gilles JACQUEMOD, Professeur, Université Côte d'Azur

- M. Christian ENZ, Professeur, Ecole Polytechnique Fédérale de Lausanne, Suisse

- M. Stéphane ROCHETTE, Ingénieur, Thales Alenia Space

- M. Matthieu GASTALDI, Ingénieur, CNES TOULOUSE

- M. Eric KERHERVE, Professeur, Bordeaux INP

- M. Hervé LAPUYADE, Maître de conférences, Université de Bordeaux

- M. François RIVET, Maître de conférences HDR, Bordeaux INP

- M. Jean-Louis CAZAUX, Ingénieur, Thales Alenia Space

Directeur de thèse Rapporteur Rapporteur Examinateur Examinateur Président du jury Encadrant Encadrant Invité

# Oscillateur commandé en tension de classe C à faible puissance et haute fiabilité pour application spatiale en technologie FD-SOI 28 nm

Des milliers de satellites orbitent autour de la terre et fournissent à des milliards de personnes des informations météorologiques, des communications, des émissions et des informations de navigation. Les services par satellite sont tellement omniprésents et essentiels dans notre vie que l'utilisation des satellites dans notre vie quotidienne est souvent devenue "invisible". Le nombre de satellites lancés dans l'espace augmente chaque année, annonçant une nouvelle course à l'espace. Cette nouvelle ère spatiale encourage la transition des technologies traditionnelles de semi-conducteurs utilisées dans l'espace, qui sont en retard sur l'état de l'art, vers les derniers nœuds technologiques qui offrent de hautes performances à faible coût, comme la technologie CMOS FD-SOI de 28 nm.

Outre des performances spectrales élevées pour les communications à large bande, les émetteurs-récepteurs de satellites doivent être très fiables et consommer peu d'énergie, l'électricité étant une denrée rare dans l'espace. L'oscillateur commandé en tension (VCO) est l'un des blocs de circuit les plus importants dans les émetteurs-récepteurs de satellite en termes de dissipation de puissance et de performance globale. Le travail de thèse se concentre sur la conception d'une nouvelle topologie VCO pour la communication par satellite avec un compromis équilibré entre la fiabilité, le bruit de phase, la consommation d'énergie et la plage d'accord.

**Mots clés :** Oscillateur commandé en tension, FD-SOI, fiabilité, réglage du bruit de phase, oscillateur sans varactor, classe C, polarisation de la grille arrière.

# Low power, high-reliability class-C voltage-controlled oscillator for space application in 28 nm FD-SOI technology

Thousands of satellites orbits around the earth providing billions of people with meteorological and weather information, communications, broadcasting, and navigational information. Satellite services become so omnipresent and essential in our life that the use of satellites in our daily life has often become "invisible". The number of satellites launched into space is increasing every year, heralding a new space race. This new space era encourages the transition from traditional semiconductor technologies used in space, which lag behind the state of the art, to the latest technology nodes that offer high performance at low cost such as 28 nm FD-SOI CMOS technology.

In addition to high spectral performance for broadband communications, satellite transceivers must have high reliability and low power consumption, as electricity is a rare commodity in space. Voltage Controlled Oscillator (VCO) is one of the most important circuit blocks in satellite transceivers in terms of power dissipation and overall performance. The thesis work focuses on the design of a new VCO topology for satellite communication with a balanced trade-off between phase noise, reliability, power consumption, and tuning range.

**Keywords:** Voltage-Controlled Oscillator, FD-SOI, Reliability, Phase Noise Tuning, Varactor-less Oscillator, Class-C, Body-Biasing.

# Laboratoire de l'Intégration, du Matériau au Système (IMS)

UMR 5218

Bâtiment A31, 351 Cours de la Libération, 33405 TALENCE CEDEX

## Acknowledgments

First of all, I would like to express my deep gratitude to my supervisors, Yann DEVAL, Hervé LAPUYADE, and François RIVET for their invaluable guidance, encouragement, and support throughout this thesis. Without their expertise and unwavering belief in my abilities, this thesis would not have been possible.

I would also like to thank all members of the jury Christian ENZ, Gilles JACQUEMOD, Stephane ROCHETTE, Matthieu GASTALDI, Jean-Louis CAZAUX who accepted to be part of my defense's jury. An additional special thanks to Eric Kerherve who accepted to be the president of my jury

I am also indebted to CNES and Thales Alenia Space for providing the financial support that made this research possible.

I would like to thank Magali for her assistance and support throughout the measurement process. Thank you for going above and beyond to ensure the success of the measurements.

I would like to thank Justine for her help, kindness, and support in the writing process.

I am also grateful to my colleagues and friends in the IMS laboratory who have provided me with support and motivation throughout this journey. In particular, I would like to thank Manuel, Benjamin, Andres, Gwennaël, Issam, Marwane, and Mohamed Amine for their valuable contributions and for always being there to listen and offer encouragement.

Finally, I want to extend a heartfelt thank you to my family, especially my parents, Amina and Mbarek, for their constant love and support. Their constant encouragement, guidance, and belief in my abilities have been a constant source of motivation and inspiration throughout my life. I am deeply grateful for everything they have done for me and couldn't have made it this far without their love and support. +₀IEE≤O+

In conclusion, I would like to acknowledge the support and encouragement of my friends, who have been a constant source of inspiration and support throughout this process. Thank you all for your encouragement, patience, and understanding.

# Table of contents

| ACKNOWLED     | GMENTS                                                                                 | I        |

|---------------|----------------------------------------------------------------------------------------|----------|

| TABLE OF CO   | NTENTS                                                                                 |          |

| LIST OF FIGUI | RES                                                                                    | IV       |

| LIST OF TABL  | ES                                                                                     | VIII     |

| INTRODUCTIO   | DN                                                                                     | 1        |

| OVERVIEW O    | F SATELLITE COMMUNICATION TO HARMONIC OSCILLATORS                                      | 3        |

|               | LITE COMMUNICATIONS: THEN AND NOW                                                      |          |

| 2. ELECT      | RONIC CIRCUITS IN SPACE                                                                | 6        |

|               | -SPEED COMMUNICATIONS                                                                  |          |

|               | LATORS                                                                                 |          |

| 5. Phas       | E NOISE                                                                                |          |

| 5.1.          | Phase noise model                                                                      |          |

| 5.2.          | Phase noise trade-offs                                                                 |          |

|               | LATOR TOPOLOGIES                                                                       |          |

| 6.1.          | Class-B                                                                                |          |

| 6.2.          | Class-C                                                                                |          |

| 6.3.          | Class-F                                                                                |          |

| 6.4.          | Topologies comparison                                                                  |          |

|               | LUSION                                                                                 |          |

|               | M FD-SOI TECHNOLOGY OVERVIEW                                                           |          |

|               | A FD-SOI TECHNOLOGY OVERVIEW                                                           |          |

| 1.1.<br>1.2.  | Body biasing                                                                           |          |

| 1.2.<br>1.3.  | Body blasing<br>Back-End-Of-Line (BEOL)                                                |          |

| 1.5.<br>1.4.  | Self-heating and radiation effects on 28nm FD-SOI                                      |          |

|               | 1 HIGH SWING CLASS-C OSCILLATOR TO A CLASS-C OSCILLATOR WITH LONG-TERM RELIABILITY AND |          |

| NOISE 43      |                                                                                        |          |

| 2.1.          | High swing class-C oscillator                                                          | 43       |

| 2.2.          | A class-C oscillator with long-term reliability and adjustable phase noise             |          |

| 2.3.          | Phase noise                                                                            |          |

| -             | LUSION                                                                                 |          |

|               |                                                                                        |          |

|               | GN                                                                                     |          |

| 1. INTRO      | DUCTION                                                                                |          |

| 1.1.          | 10 GHz VCO                                                                             | 66       |

| 1.2.          | 40 GHz VCO                                                                             |          |

| 2. Desic      |                                                                                        |          |

| 3. Tran       | SN FLOW                                                                                |          |

| 2.4           | SN FLOWSFORMER DESIGN                                                                  | 69       |

| 3.1.          |                                                                                        | 69<br>70 |

| 3.1.<br>3.2.  | SFORMER DESIGN                                                                         |          |

| -             | sFORMER DESIGN<br>Transformer design: 40 GHz VCO                                       |          |

| 3.2.<br>3.3.  | SFORMER DESIGN<br>Transformer design: 40 GHz VCO<br>Transformer design: 10 GHz VCO     |          |

| 5. Fr      | REQUENCY TUNING                                 |    |

|------------|-------------------------------------------------|----|

| 5.1.       | 10 GHz VCO                                      |    |

| 5.2.       | 40 GHz VCO                                      |    |

| 6. O       | UTPUT BUFFER                                    |    |

| 6.1.       | 10 GHz VCO                                      |    |

| 6.2.       | 40 GHz VCO                                      |    |

| 7. LA      | AYOUT IMPLEMENTATION                            |    |

| 7.1.       | 10 GHz VCO                                      |    |

| 7.2.       | 40 GHz VCO                                      |    |

| 7.3.       | Full chip                                       |    |

| 8. Co      | ONCLUSION                                       |    |

| Referen    | CES                                             |    |

| MEASUDE    | MENT RESULTS                                    | 96 |

|            |                                                 |    |

|            | $^{\scriptscriptstyle T}$ prototype: 10 GHz VCO |    |

| 1.1.       | Measurement setup                               |    |

| 1.2.       | Measurement results                             |    |

| 1.3.       | Discussion                                      |    |

| 1.4.       | Conclusion                                      |    |

|            | <sup>ID</sup> PROTOTYPE: 10 GHz VCO             |    |

| 2.1.       | Measurement setup                               |    |

| 2.2.       | Measurement results                             |    |

| 2.3.       | Comparison with the state-of-the-art            |    |

|            | <sup>ID</sup> PROTOTYPE: 40 GHz VCO             |    |

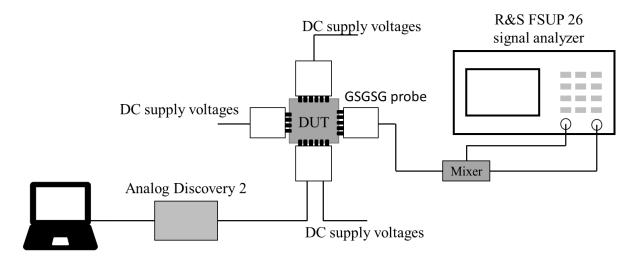

| 3.1.       | Measurement setup                               |    |

| 3.2.       | Measurement results                             |    |

| 3.3.       | Comparison with the state-of-the-art            |    |

| 4. Co      | ONCLUSION                                       |    |

| REFEREN    | CES                                             |    |

| CONCLUSI   | ON AND PERSPECTIVES                             |    |

| 1. Co      | DNCLUSION                                       |    |

|            | ERSPECTIVES                                     |    |

|            | CES                                             |    |

| LIST OF PU | BLICATIONS                                      |    |

|            |                                                 |    |

# List of figures

| Figure 1-1: Arthur C. Clarke sketch describing the coverage of the entire world with three        |    |

|---------------------------------------------------------------------------------------------------|----|

| satellites                                                                                        |    |

| Figure 1-2: A selective communications satellite timeline.                                        |    |

| Figure 1-3: The number of operational satellites by mission type between 2016 and 2020            |    |

| Figure 1-4: 2020 satellite industry revenues worldwide in billions of U.S. dollars                | 6  |

| Figure 1-5: The NTN in the 5G ecosystem [4].                                                      | 9  |

| Figure 1-6: LC oscillator model                                                                   | 10 |

| Figure 1-7: Oscillator feedback model                                                             | 11 |

| Figure 1-8: Frequency response of (a) an ideal oscillator, (b) a real oscillator                  | 12 |

| Figure 1-9: Effect of phase noise on a receiver                                                   | 12 |

| Figure 1-10: Effect of phase noise on a transmitter.                                              | 13 |

| Figure 1-11: Power-law spectrum.                                                                  |    |

| Figure 1-12: Oscillator model with the phase noise of the amplifier and all other component       | S  |

| modeled as random phase $\psi$                                                                    | 14 |

| Figure 1-13: The Lesson effect phase transfer function SφSψ                                       | 15 |

| Figure 1-14: Conversion of device noise to oscillator's phase noise                               | 16 |

| Figure 1-15: (a) Effect of impulse injection at peak of the waveform, (b) effect of impulse       |    |

| injection at zero crossing of waveform.                                                           | 17 |

| Figure 1-16: ISF waveform of an oscillator with a sinusoidal output                               | 18 |

| Figure 1-17: Noise sources in a cross-coupled LC oscillator                                       | 19 |

| Figure 1-18: (a) Cross-coupled oscillator topology, (b) amplitude and phase noise of the          |    |

| oscillator in current-limited and voltage-limited regions                                         | 22 |

| Figure 1-19: Switch capacitor model in ON and OFF state.                                          | 23 |

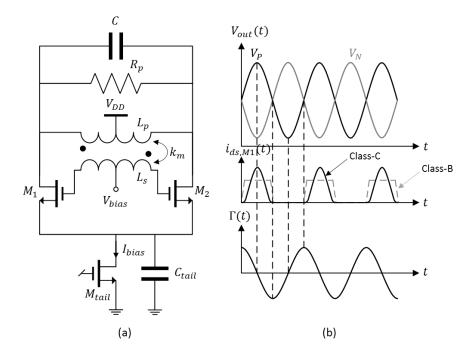

| Figure 1-20: (a) Class-B oscillator topology, (b) differential output voltages, drain current of  | f  |

| M1 ,ids, M1, noise modulating function (NMF) of M1 and ISF of M1 ,Γ                               | 26 |

| Figure 1-21: (a) Class-B oscillator with the tail filter, (b) class-B oscillator with ac-coupling | 5. |

|                                                                                                   | 27 |

| Figure 1-22: (a) Class-C oscillator topology, (b) differential output voltages, drain current of  | f  |

| M1, ids, M1, and ISF of M1, Γ                                                                     | 28 |

| Figure 1-23: (a) Class-F oscillator topology, (b) output voltage waveform                         | 30 |

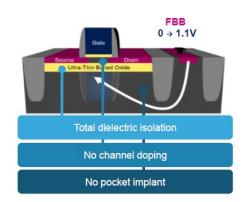

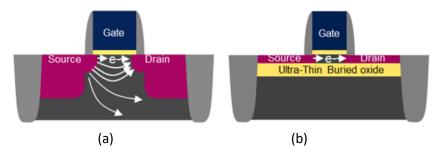

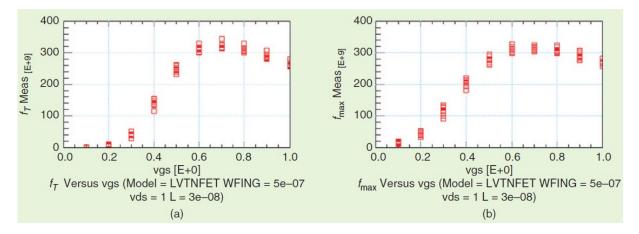

| Figure 2-1: Cross-section of an UTBB FD-SOI transistor                                            |    |

| Figure 2-2: Electron flow (a) bulk technology (b) FD-SOI technology                               | 37 |

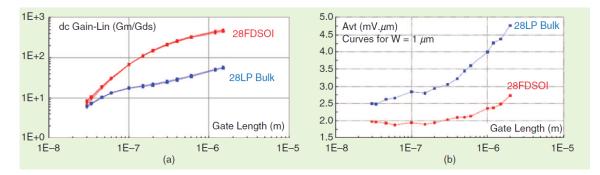

| Figure 2-3: Comparison between 28-nm FD-SOI technology (red) and 28-nm LP bulk (blue              | ;) |

| in (a) Analog gain (Gm/Gds) and (b) matching parameter (Avt) [3]                                  |    |

| Figure 2-4: Comparison between 28-nm FD-SOI technology (red) and 28-nm LP bulk (blue              |    |

| in (a) transconductance over drain current (Gm/Id) and (b) total gate capacitance (Cgg) [3].      | 38 |

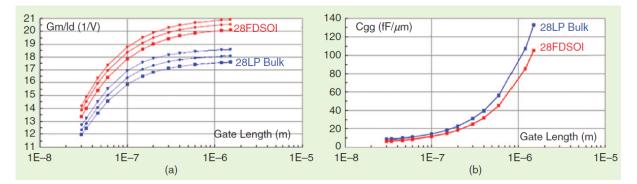

| Figure 2-5: fT and fmax of LVT NMOS 0.5 µm/30 nm in 28-nm FD-SOI CMOS [3]                         |    |

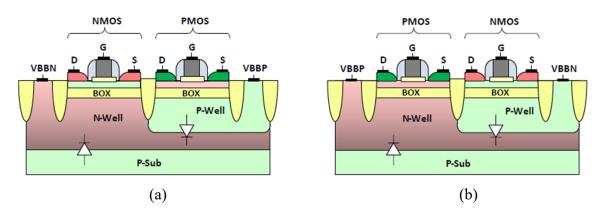

| Figure 2-6: 28-nm UTBB FD-SOI CMOS transistors: (a) RVT transistors and (b) LVT                   |    |

| transistors.                                                                                      | 39 |

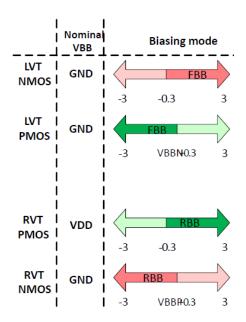

| Figure 2-7: 28nm FD-SOI CMOS technology transistors body biasing mode, limits, and                |    |

| nominal voltage                                                                                   |    |

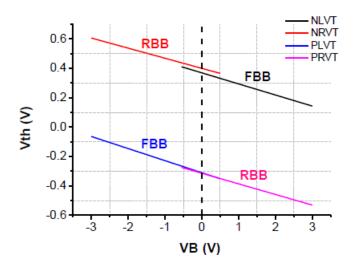

| Figure 2-8: Vth variation range in function of body-biasing voltage for RVT and LVT devic         | es |

| in 28nm FD-SOI technology                                                                         | 40 |

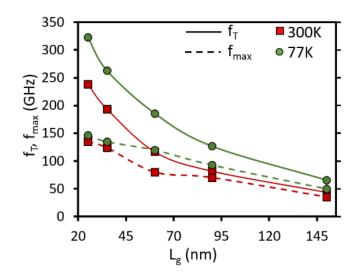

| Figure 2-9: 8 metal layers back-end-of-line of 28nm FD-SOI technology                            | . 41 |

|--------------------------------------------------------------------------------------------------|------|

| Figure 2-10: fT and fmax in function of transistor length Lg for 77 K and 300 K in saturati      | ion  |

| at low-Vds (Vds = 0.6 V) and at Vgs that corresponds to maximum gm [6]                           |      |

| Figure 2-34: High swing class-C oscillator.                                                      | . 44 |

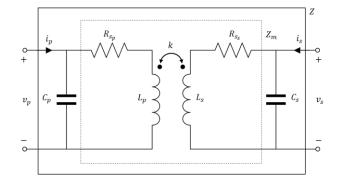

| Figure 2-12: Transformer-based resonator                                                         | . 45 |

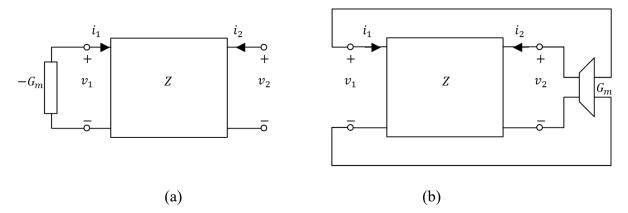

| Figure 2-13: (a) One-port oscillator. (b) Two-port oscillator                                    | . 46 |

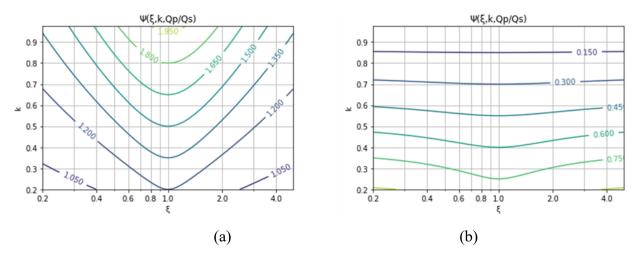

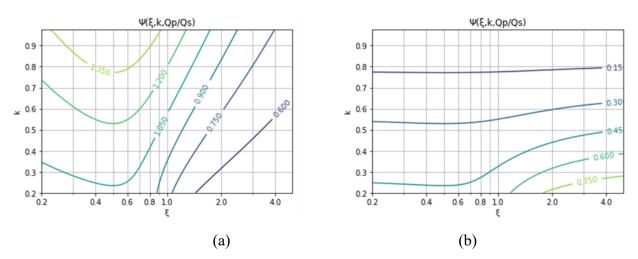

| Figure 2-14: $\Psi(\xi, k, QpQs)$ in the case of $Qp = Qs$ for (a) $\omega L$ and (b) $\omega H$ |      |

| Figure 2-15: $\Psi(\xi, k, QpQs)$ in the case of $Qp < Qs$ for (a) $\omega L$ and (b) $\omega H$ |      |

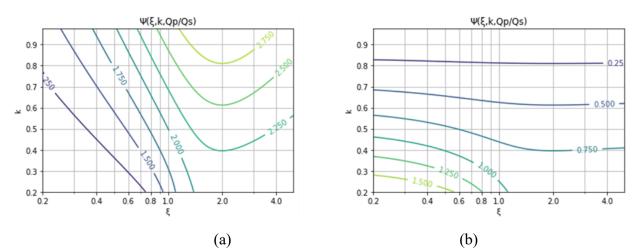

| Figure 2-16: $\Psi(\xi, k, QpQs)$ in the case of $Qp > Qs$ for (a) $\omega L$ and (b) $\omega H$ |      |

| Figure 2-17: Cascode high swing class-C oscillator.                                              |      |

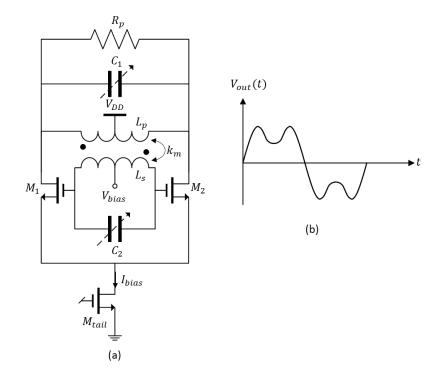

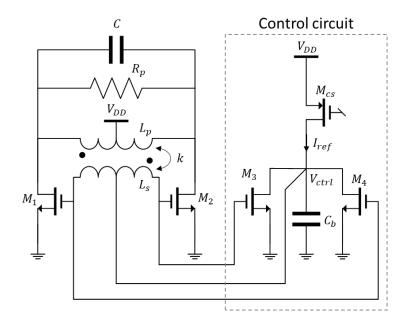

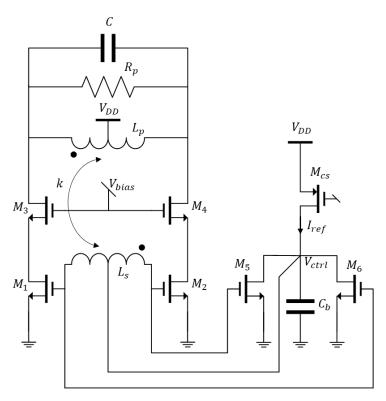

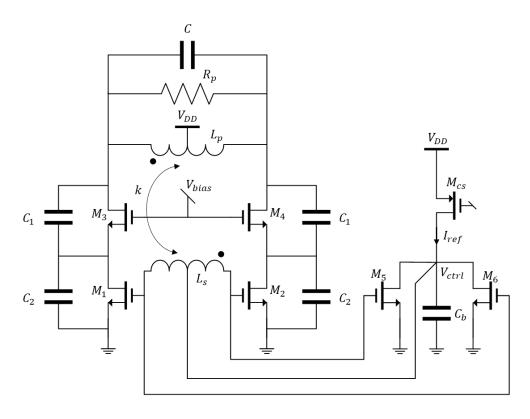

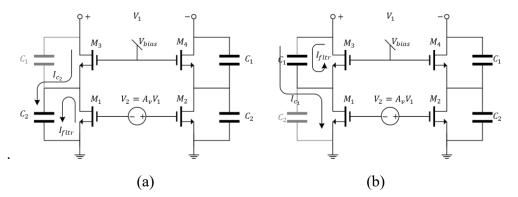

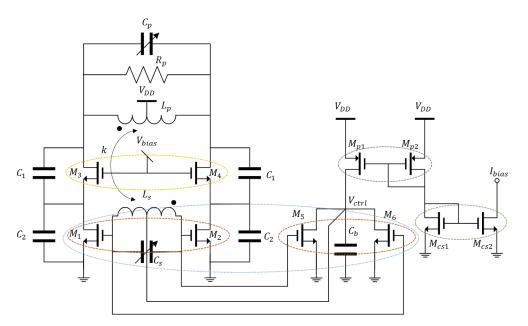

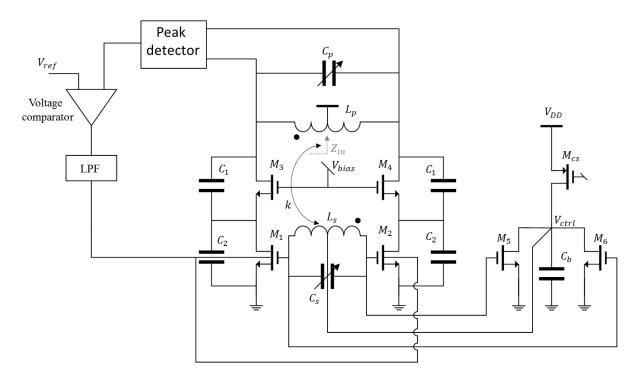

| Figure 2-18: Proposed class-C oscillator.                                                        | . 53 |

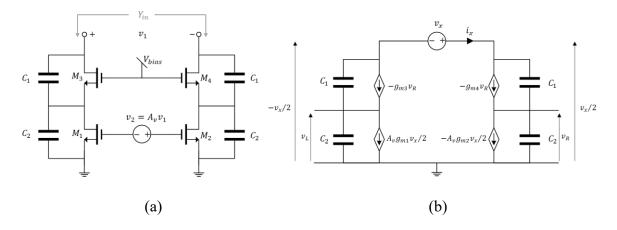

| Figure 2-19: (a) The active device of the proposed oscillator. (b) The small-signal equivale     |      |

| of the active device                                                                             | . 54 |

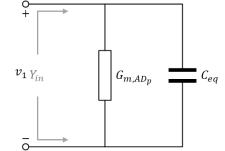

| Figure 2-20: Shunt model of the active device.                                                   | . 54 |

| Figure 2-21: Active device noise current path with (a) C2 and (b) C1.                            |      |

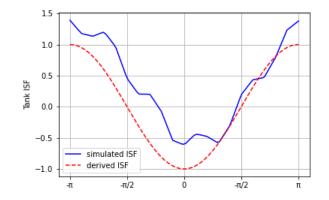

| Figure 2-22: The simulated and derived tank ISF                                                  | . 57 |

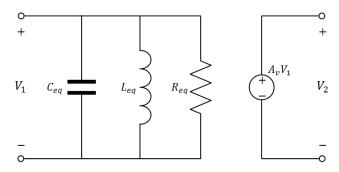

| Figure 2-23: The simplified LC model of the transformer-based resonator.                         | . 57 |

| Figure 2-24: Circuit model of ISF calculation for (a) tank, (b) lower transistor in the active   |      |

| device, and (c) upper transistor in the active device.                                           | . 58 |

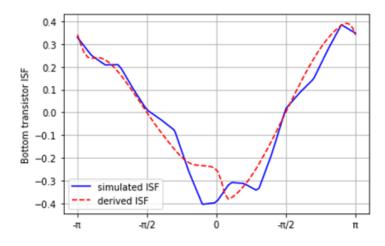

| Figure 2-25: The simulated and derived ISF of : (a) the upper transistor M3 (b) the lower        |      |

| transistor M1                                                                                    | . 59 |

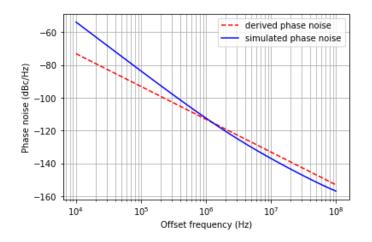

| Figure 2-26: The simulated and derived phase noise of the proposed oscillator                    | . 59 |

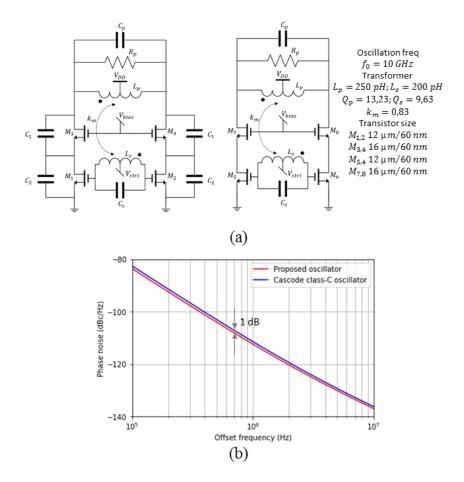

| Figure 2-27: (a) The set-up configuration (b) The phase noise simulation of the proposed         |      |

| oscillator and the cascode class-C oscillator                                                    | . 60 |

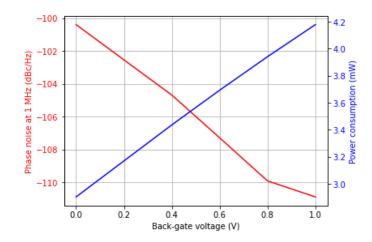

| Figure 2-28: Phase noise at 1 MHz and power consumption as a function of the back-gate           |      |

| voltage of M1 and M2                                                                             | . 62 |

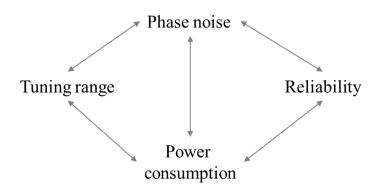

| Figure 3-1: Trade-offs between oscillator parameters.                                            | . 67 |

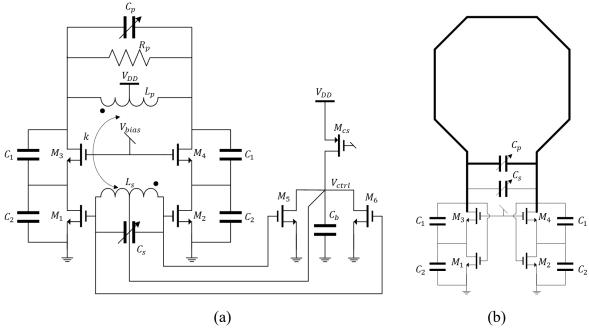

| Figure 3-2: 10 GHz VCO (a) schematic and (b) layout sketch.                                      | . 67 |

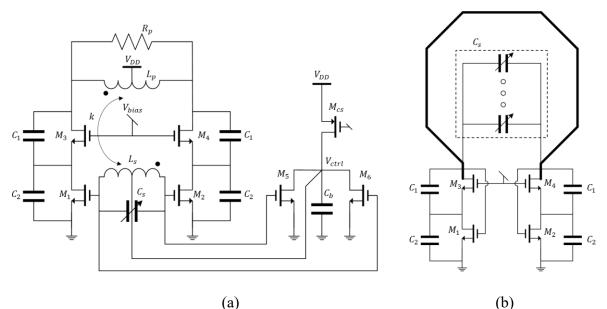

| Figure 3-3: 40 GHz VCO (a) schematic and (b) layout sketch.                                      | . 68 |

| Figure 3-4: Design flow                                                                          | . 69 |

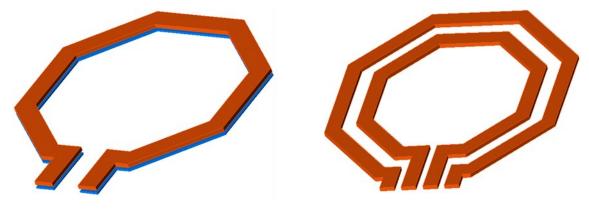

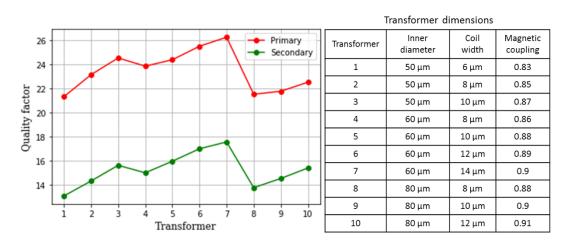

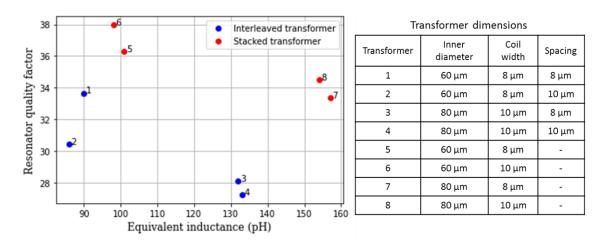

| Figure 3-5: (a) Stacked transformer; (b) Interleaved transformer.                                | . 71 |

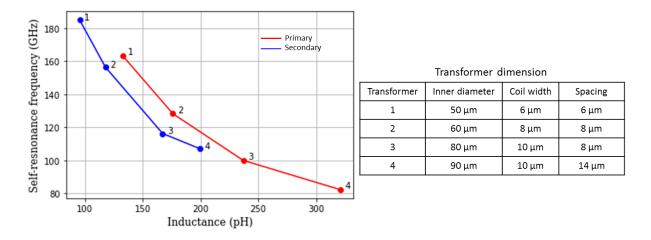

| Figure 3-6: self-resonance frequency in the simulated interleaved transformers                   | . 72 |

| Figure 3-7: self-resonance frequency in the simulated stacked transformers.                      | . 73 |

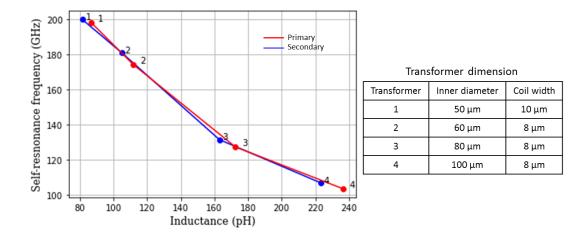

| Figure 3-8: Coils quality factor and magnetic coupling coefficient in the simulated interleav    | ved  |

| transformers                                                                                     | . 74 |

| Figure 3-9: Coils quality factor and magnetic coupling coefficient in the simulated stacked      |      |

| transformers                                                                                     | . 74 |

| Figure 3-10: Comparison of the resonator quality factor of the stacked and interleaved           |      |

| transformers                                                                                     | . 75 |

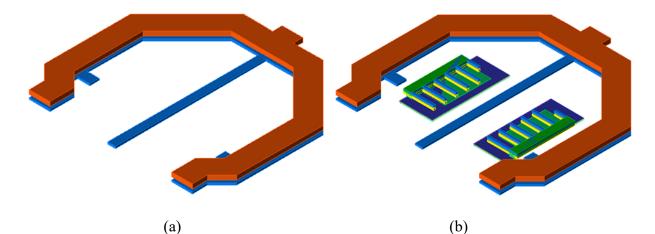

| Figure 3-11: (a) The design Horseshoe-shaped stacked transformer (b) The transformer wit         | ťh   |

| capacitor bank model inside it                                                                   | . 76 |

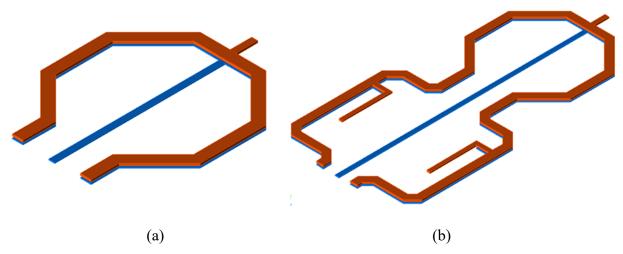

| Figure 3-12: (a) The design 10 GHz VCO transformer and (b) the transformer model with t          | the  |

| routing wires                                                                                    |      |

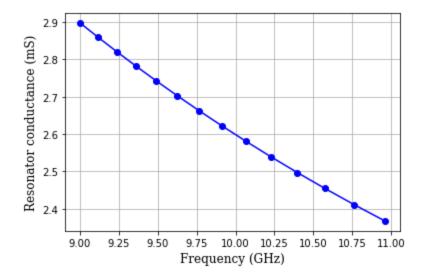

| Figure 3-13: The conductance of the 10 GHz VCO resonator over a 20% tuning range                 | . 79 |

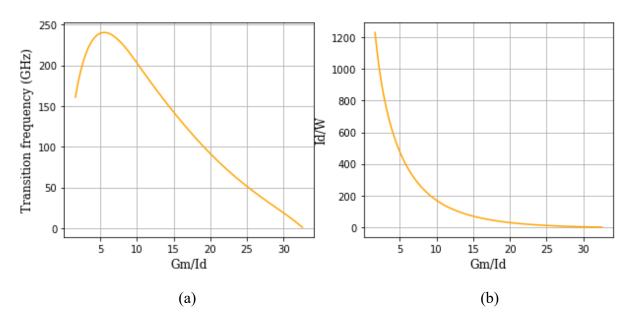

| Figure 3-14: The transistor (a) transition frequency, and (b) drain current normalized to the    | ;    |

| transistor width of the transistor as a function of gm/Id                                        | . 80 |

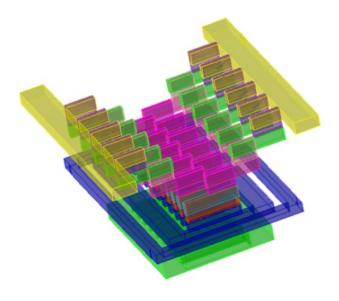

| Figure 3-15: transistor layout with staircase accesses [4].                                          | . 81 |

|------------------------------------------------------------------------------------------------------|------|

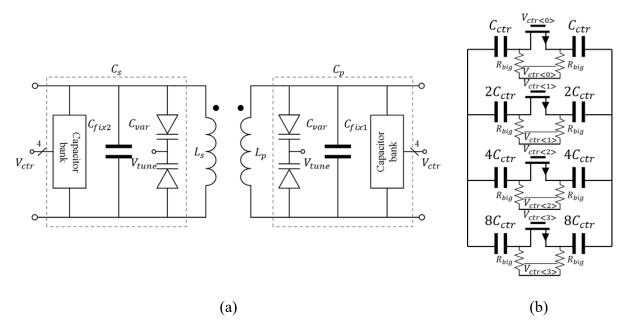

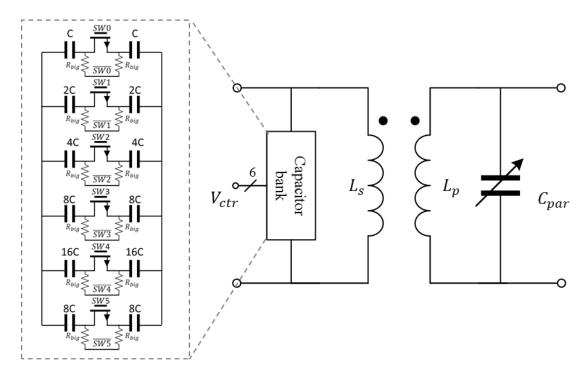

| Figure 3-16: (a) The resonator model of the 10 GHz VCO (b) The 4-bit capacitor bank                  |      |

| structure                                                                                            | . 83 |

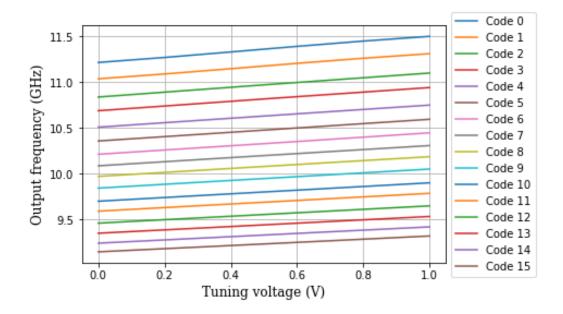

| Figure 3-17: Output frequency according to the 10 GHz VCO 4-bit capacitor-bank control               |      |

| code                                                                                                 |      |

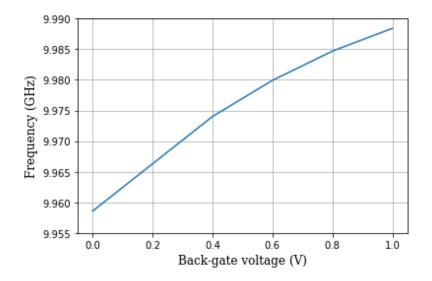

| Figure 3-18: Output frequency variations according to the back-gate voltage                          |      |

| Figure 3-19: 40 GHz VCO resonator with the 6-bit capacitor bank.                                     | . 86 |

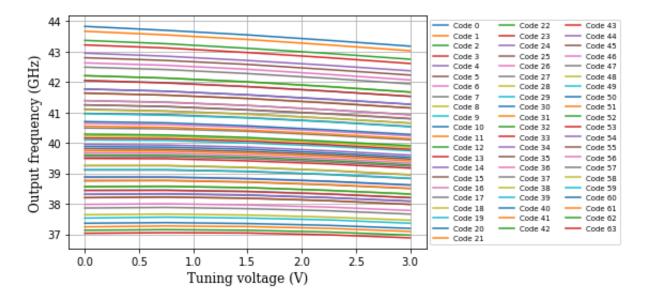

| Figure 3-20: Output frequency according to the 40 GHz VCO 4-bit capacitor-bank control               |      |

| code                                                                                                 |      |

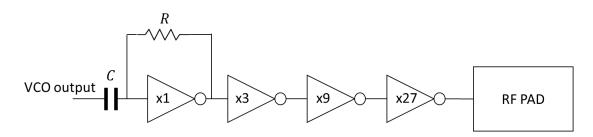

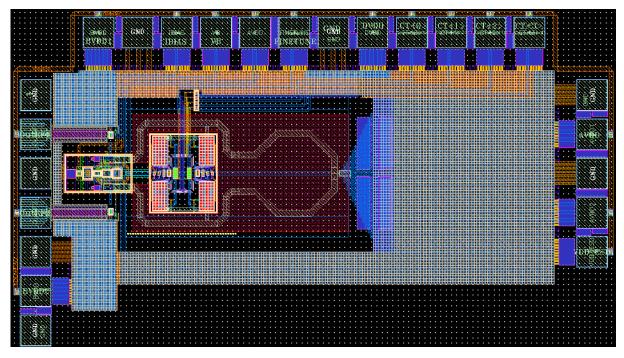

| Figure 3-21: 10 GHz VCO output buffer: tapered inverter chain.                                       |      |

| Figure 3-22: 40 GHz VCO output buffer: common source amplifier with an inductive load.               |      |

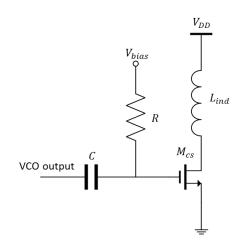

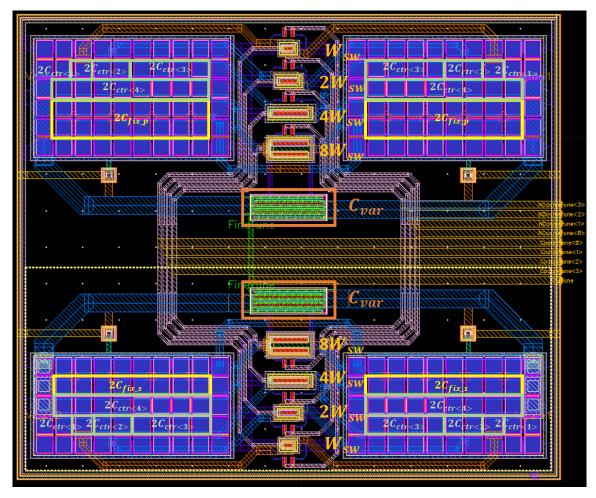

| Figure 3-23: Layout of the 10 GHz VCO core                                                           |      |

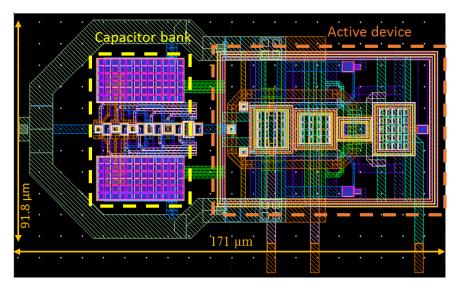

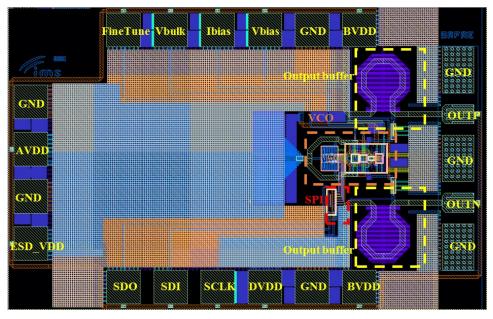

| Figure 3-24: Layout of the complete layout of the 10 GHz VCO with pad ring.                          |      |

| Figure 3-25: Capacitor bank layout                                                                   |      |

| Figure 3-26: Layout of the active device.                                                            |      |

| Figure 3-27: Schematic of a 10 GHz VCO with highlights on the transistors to be matched              |      |

| the circuit.                                                                                         |      |

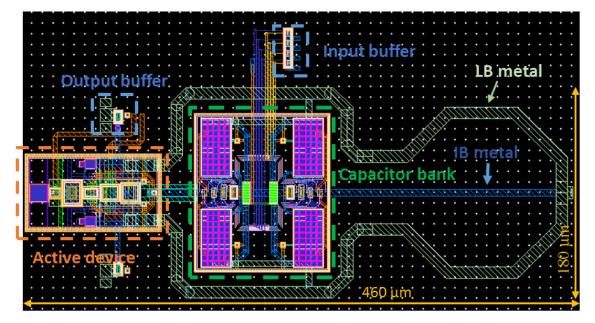

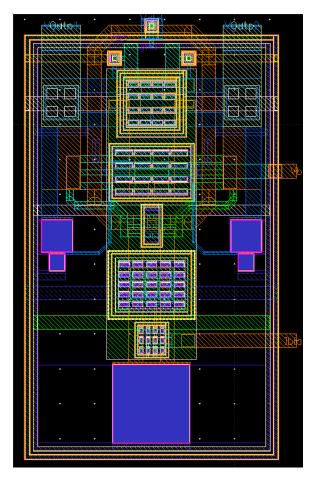

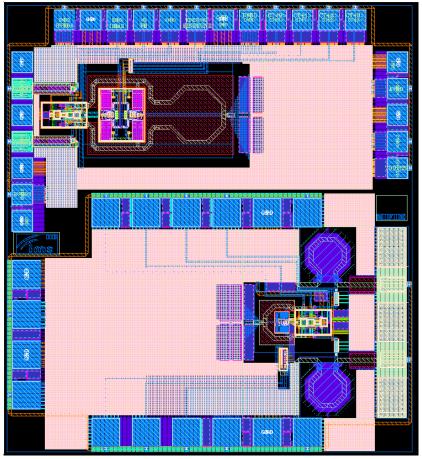

| Figure 3-28: The layout of the 40 GHz VCO.                                                           |      |

| Figure 3-29: Layout of the complete layout of the 40 GHz VCO with pad ring.                          |      |

| Figure 3-30: The complete layout of the implemented chip.                                            | . 93 |

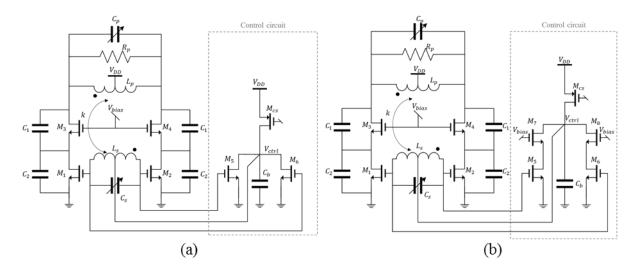

| Figure 4-1: Proposed 10 GHz VCO with (a) the simple control circuit, (b) the improved                | 07   |

| control circuit.                                                                                     |      |

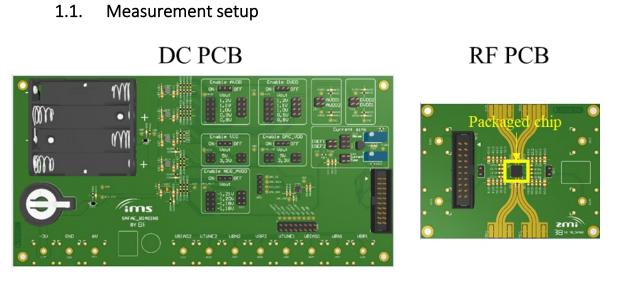

| Figure 4-2: Printed circuit boards of the first prototype                                            |      |

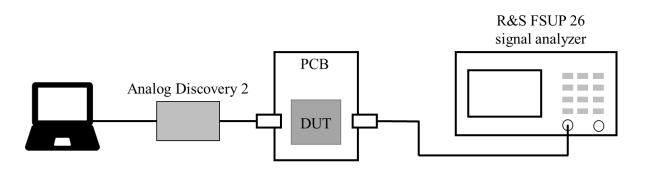

| Figure 4-3: Measurement setup.                                                                       |      |

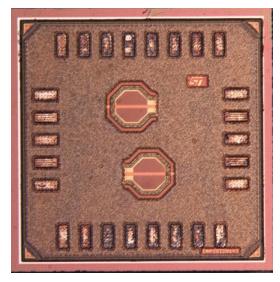

| Figure 4-4: Microphotograph of first prototype 10 GHz VCO.                                           |      |

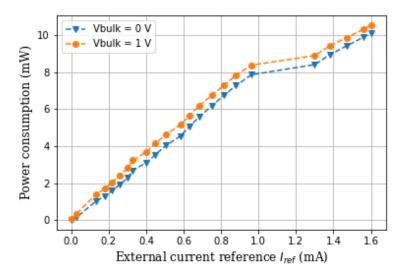

| Figure 4-5: Power consumption as a function of the external current reference Iref.                  |      |

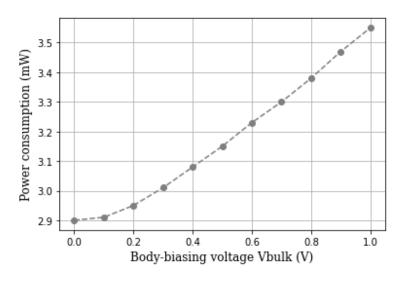

| Figure 4-6: Power consumption as a function of the back-gate voltage Vbulk.                          |      |

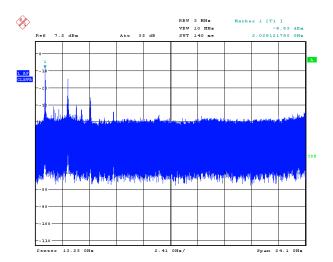

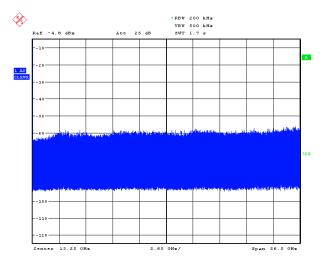

| Figure 4-7: Output spectrum of the oscillator.                                                       |      |

| Figure 4-8: Output spectrum of the oscillator with output buffers under a supply voltage of          |      |

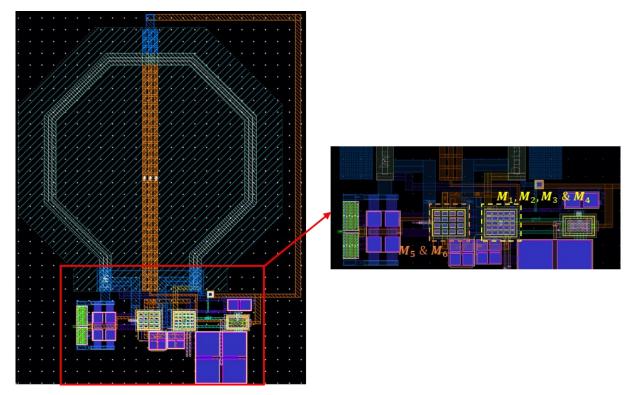

| 0.8 V<br>Figure 4-9: View of the oscillator layout with a zoom into the active device implementation |      |

| rigure 4-9. View of the oscillator layout with a zoom into the active device implementation          |      |

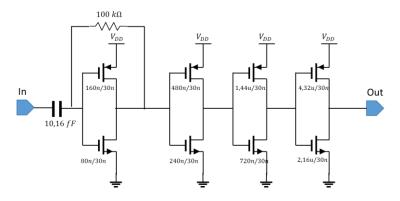

| Figure 4-10: Output buffer schematic.                                                                |      |

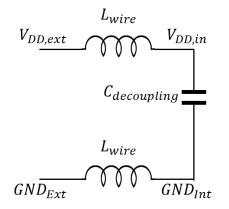

| Figure 4-11: Model of the chip supply voltage and ground connections                                 |      |

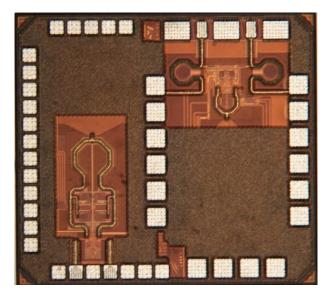

| Figure 4-12: Microphotograph of the second prototype chip.                                           |      |

| Figure 4-13: Measurement setup.                                                                      |      |

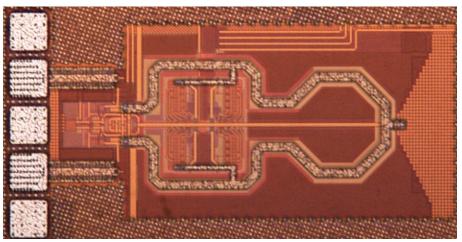

| Figure 4-14: Microphotograph of the second prototype 10 GHz VCO.                                     |      |

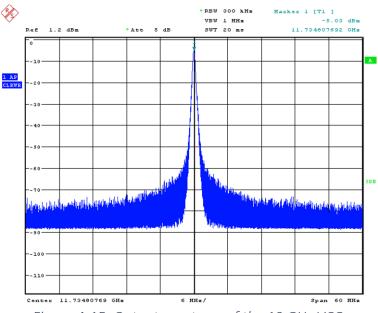

| Figure 4-15: Output spectrum of the 10 GHz VCO.                                                      |      |

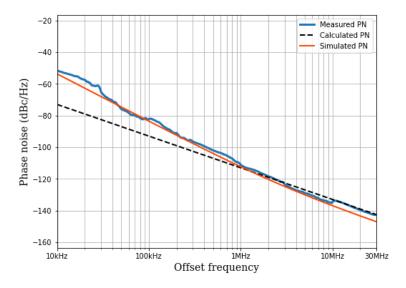

| Figure 4-16: Measured phase noise of the VCO at 11.73 GHz carrier frequency.                         |      |

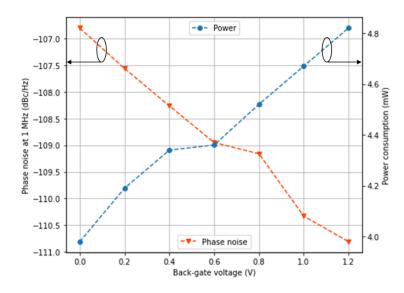

| Figure 4-17: Phase noise and power consumption as a function of the back-gate voltage                |      |

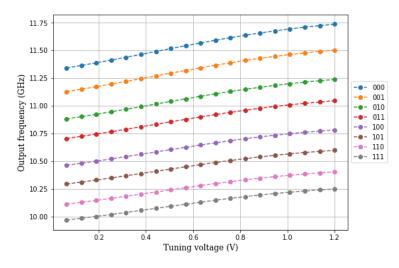

| Figure 4-18: VCO frequency tuning range.                                                             |      |

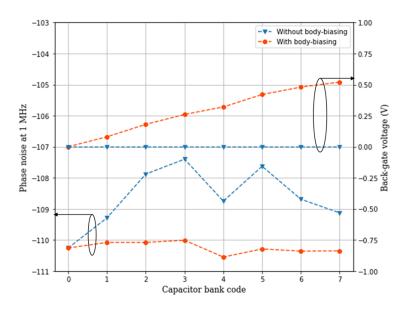

| Figure 4-19: VCO phase noise over the frequency tuning range.                                        |      |

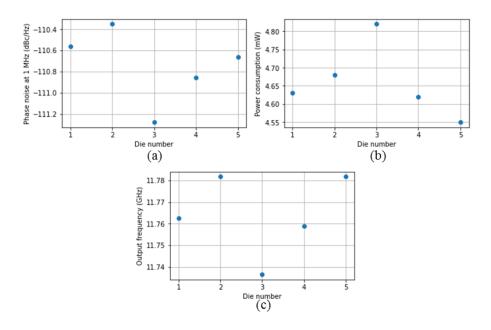

| Figure 4-20: Circuit variability in terms of (a) phase noise at 1 MHz, (b) power consumption         |      |

| and (c) oscillation frequency.                                                                       |      |

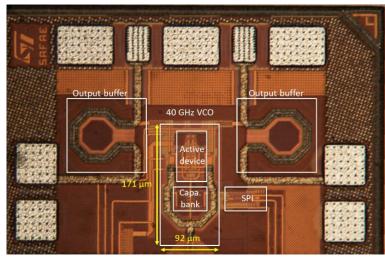

| Figure 4-21: Microphotograph of the 40 GHz VCO                                                       |      |

| Figure 4-22: Measurement setup.                                                                      |      |

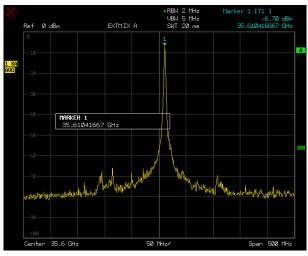

| Figure 4-23: VCO output spectrum.                                                                    |      |

| 6                                                                                                    |      |

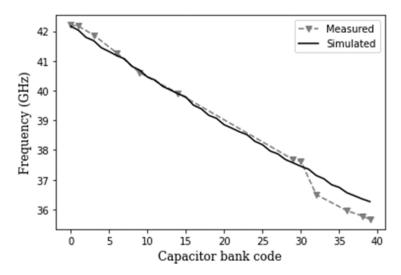

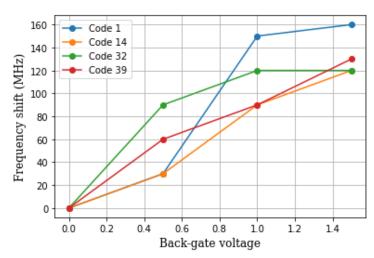

| Figure 4-24: The measured and simulated tuning range of the designed VCO                   | . 112 |

|--------------------------------------------------------------------------------------------|-------|

| Figure 4-25: Measured frequency shift for four capacitor bank codes (0, 14, 32, and 39) as | s a   |

| function of the back-gate voltage                                                          | . 113 |

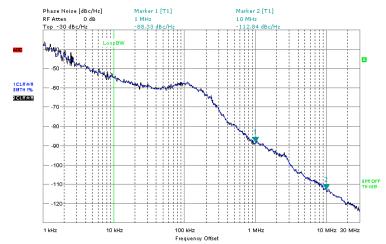

| Figure 4-26: Measured PN at 35.58 GHz with a power consumption of 7.3 mW                   | . 114 |

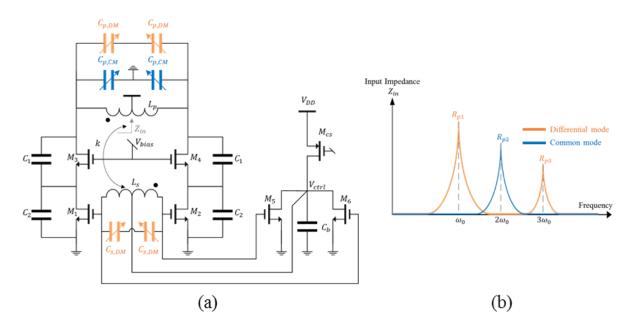

| Figure 5-1: (a) The proposed hybrid class-F/C (b) Input resonator impedance                | . 120 |

| Figure 5-2: Proposed VCO with radiation hardening feedback loop                            | . 121 |

# List of tables

| Table 1-1: Efficiency comparison of oscillator topologies [24]                           | 32  |

|------------------------------------------------------------------------------------------|-----|

| Table 2-1:0 Comparison of noise contribution at 10 GHz between the cascode class-C and t |     |

| proposed class-C                                                                         | 60  |

| Table 3-1:Comparison between the transformer with and without the capacitor model, and   | its |

| equivalent inductance                                                                    | .76 |

| Table 3-2: Comparison between the transformer with and without routing wires, and        | its |

| equivalent inductance                                                                    | .77 |

| Table 4-1: Performances comparison between the transformer with wire connections and t   | the |

| transformer alone10                                                                      | 02  |

| Table 4-2: Comparison with state-of-the-art VCOs1                                        | 10  |

| Table 4-3: Comparison with the state-of-the-art VCOs                                     | 14  |

## Introduction

Thousands of satellites orbits around the earth providing billions of people with meteorological and weather information, communications, broadcasting, and navigational information. Satellite services become so omnipresent and essential in our life to the extent that the use of satellites in our daily life has often become "invisible". The number of satellites launched into space is increasing every year, heralding a new space race, not between governments this time, but between companies. New Space is the term used to describe this new era of the space industry, which is characterized by a desire to democratize access to space through affordable rocket launches and cost-effective satellites. This vision encourages the transition from traditional semiconductor technologies used in space, which lag behind the state of the art, to the latest technology nodes that offer high performance at low cost such as 28 nm FD-SOI CMOS technology.

Satellite communication services are expected to develop more high data rate communications. There are two main reasons for this: 1) the growing demand for streaming media instead of traditional broadcasting media and 2) the motivation to have global coverage, even in isolated areas. The ways to increase data rate are 1) by increasing the bandwidth via moving to higher communication frequencies, such as mm-wave frequencies, or 2) by using advanced modulation techniques to increase the transmitted data, such as Orthogonal Frequency-Division Multiplexing (OFDM), which requires stringent phase noise. In addition to high spectral performance for broadband communications, satellite transceivers must have high reliability and low power consumption, as electricity is a rare commodity in space. Voltage Controlled Oscillator (VCO) is one of the most important circuit blocks in satellite transceivers in terms of power dissipation and overall performance. The thesis work focuses on the design of a VCO for satellite communication aiming at the following goals:

- Development of a new VCO topology in 28nm FD-SOI with an optimal trade-off between reliability, low power, low phase noise, and wide tuning range for millimeter-wave and Ku-band frequencies targeting high data rate satellite communications.

- Explore 28nm FD-SOI CMOS technology for space applications and demonstrate its unique capabilities using the body-biasing feature in the proposed VCO topology.

This manuscript is composed of five chapters. The first chapter outlines the context of this work and presents the main limitations and trade-offs in oscillator design. The main oscillator topologies are presented and compared.

The second chapter presents the 28 nm FD-SOI CMOS technology and introduces the proposed oscillator based on a transformer resonator and a class C topology. The reliability problems of harmonic oscillators are discussed and a solution for the long-term reliability of the proposed oscillator is presented. The chapter provides a theoretical analysis of the phase noise of the proposed oscillator.

The third chapter describes the design methodology used to implement the proposed VCO topology in mm-wave and Ku band frequencies. The challenges and target specifications are presented for each VCO.

The fourth chapter presents the measurement results and proof of concept of the proposed VCO in mm-wave and Ku-band frequencies. The performance of the two designed VCOs is compared with the state-of-the-art.

The last chapter provides a general conclusion of the thesis work and presents the research perspectives of the proposed VCO topology.

## Chapter 1:

## Overview of satellite communication to harmonic oscillators

Satellite communication is an essential asset in our modern communication systems that required reliable and high-speed transceivers to meet the increasing demand for data rate in the consumer market. The first part of this chapter presents the history, financial prospects, and challenges of satellite communication. The second part of the chapter provides an overview of harmonic oscillators, presenting the basics of oscillators and phase noise theory, highlighting the main trade-offs in oscillator design, and comparing the main oscillator topologies.

### 1. Satellite communications: then and now

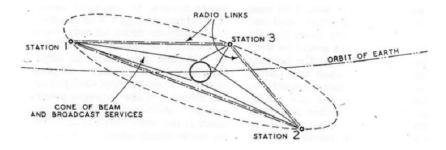

The concept of satellite communications was introduced in 1945 in an article by Arthur C. Clarke in Wireless World magazine. [1]. Clarke described the fundamentals behind the deployment of manned satellites into specific orbit (later known as a geostationary orbit GEO or "Clarke Belt") to relay radio signals. A satellite in Clarke's Orbit covers 44% of the earth's surface. Hence, with only 3 satellites, with inter-satellite communication, the entire globe communication is covered as shown in Figure 1-1. Moreover, thanks to the stationarity of the satellites relative to the earth, ground antennas are simpler to build, and signals sent to the earth are received 24 hours a day without interruption. Thereby increasing the ease of communication.

*Figure 1-1: Arthur C. Clarke's sketch describing the coverage of the entire world with three satellites [1].*

Clarke thought that the satellite required a human presence to replace the radio tubes because the radio tubes of the time had a very short life. So he did not try to patent the idea of a geosynchronous communication satellite. Little did he know that a few years later, Bell Laboratories would announce the invention of the transistor in 1947. This revolutionary invention and the integrated circuits that followed it took satellite communications from science fiction to a possible reality. These devices not only brought reliable satellite technology to life but also enabled the creation of high-speed electronic computers that do the calculations to accurately deploy a satellite in orbit.

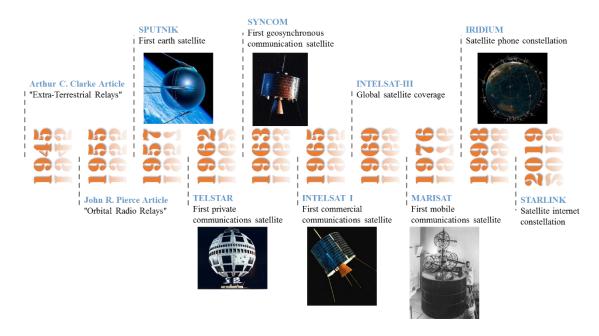

Figure 1-2: A selective communications satellite timeline [2].

Figure 1-2 shows a timeline with a selective communications satellite timeline. The idea of satellite communications became a reality with the launch of the first artificial satellite by the Soviet Union in 1957. Sputnik, a silver orb the size of a bullet, orbited the earth every 96 minutes, sending beeps to earth through an onboard radio transmitter. This achievement triggered the space race between the United States and the Soviet Union, which permitted the quick development of the space sector. In 1962, NASA launched the world's first privately funded communications satellite, TELSTAR, which transmitted the first live transatlantic broadcast between Europe and the United States. The year 1963 saw the launch of the first geosynchronous satellite, SYNCOM, which was used in 1964 to broadcast the Tokyo Olympic Games for the first time. Communication Satellite Corporation (COMSAT) launched Early Bird (Intelsat I) in 1965, the first commercial communication satellite placed in geosynchronous orbit. Its successor, INTELSAT-III series launched in 1969, achieved

global coverage on which the first moon landing was broadcast to 600 million viewers worldwide. At the end of the twentieth century, the space industry developed more specialized satellites that eclipsed the previous ones. Starting in 1976 with the launch of the first communication system to provide mobile services, MARISAT. With the emergence of new technologies such as cell phones, the internet, and the Internet of Things (IoT), global communications have grown exponentially. Hundreds of sophisticated low earth orbit (LEO) satellite constellations have been deployed, providing high-speed, low-latency digital communications and global coverage in even the most remote areas of the world. From the Iridium 66 satellites that provide pole-to-pole phone coverage, launched in 1998, to Starlink which promises to provide low-cost internet to isolated locations with a mega-constellation of 12,000 satellites.

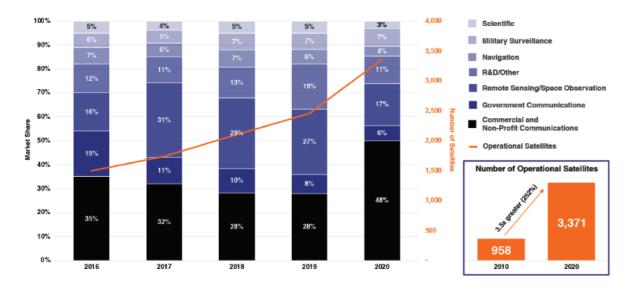

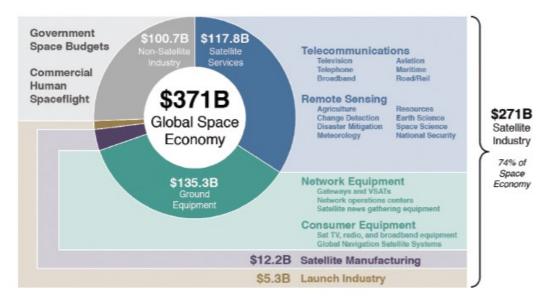

The rapid development of satellite communications is due to its financial prospects. John R. Pierce was one of the pioneers to highlight the economic potential of satellites, in his 1954 speech and 1955 article, where he demonstrated the potential superiority of satellite communication capacity over the first transatlantic telephone cable (TAT-1), which could carry 36 simultaneous telephone calls for \$30-50 million, compared to an estimated 1,000 simultaneous telephone calls by satellite. Pierce wondered if a satellite would be worth a billion dollars. Nowadays, thousands of applications satellites orbits around the earth providing over a billion people with meteorological and weather information, communications, broadcasting, and navigational information. Satellite services have become so ubiquitous that they have become almost commonplace in the space of half a century. To the extent that the use of satellites in our daily life has often become "invisible". Figure 1-3 shows the number of operational satellites by mission type in recent years. The number of satellites increases by 252% in the 10 years between 2010 and 2020. The market for satellite applications will continue to grow rapidly and diversify for many years to come, as the space industry enters a new chapter called the "New Space", characterized by a desire to democratize access to space through more affordable launches (reusable rockets, carpooling) and satellites (small satellites). In 2020, satellite services realized more than \$117 billion in revenue. If we include the costs of the launch industry, satellite manufacturing, and ground equipment, the annual revenues of the satellite industry reach \$271 billion, representing 74% of the global space economy (see Figure 1-4). The satellite industry is a global industry that has been growing steadily for several decades, even in times of global recession. John R. Pierce's prediction was right, it would be worth a billion dollars.

Figure 1-3: The number of operational satellites by mission type between 2016 and 2020 [3].

Figure 1-4: 2020 satellite industry revenues worldwide in billions of U.S. dollars [3].

## 2. Electronic circuits in space

TELSTAR was the first satellite to transmit a transatlantic broadcast in space and the first victim of an electronic failure caused by radiation. Four months after the launch of TELSTAR in 1962, it ceased to function. The problem was linked to a transistor failure due to radiation caused by a nuclear weapon explosion test at a high altitude that took place the day before Telstar's launch. Other satellites have been lost for the same reason - radiation. Since then, the effects of radiation and its mitigation in electronics have become a top priority for the space industry. The construction of satellites requires astronomical costs that reach hundreds of millions of dollars. Therefore, no tolerance is accepted for electronic failure in such systems.

Satellites are so essential to the functioning of the modern world (weather forecasting, navigation ...) that their loss would have catastrophic consequences.

Radiation affects satellite electronics in two main ways: total ionizing dose (TID) and single event effects (SEE). Exposure of the device to radiation in space leads to an accumulation of charges in the device. This results in a progressive deterioration of the device's performance over time. The total accumulated dose is a function of time and altitude and is quantified by the TID measured in units of kilorads (krad). For instance, an unshielded satellite in GEO could absorb a TID of over 20 Megarad (Mrad) in one year. In contrast, the same satellite in LEO would absorb only about 100 krad in a year.

SEE is an instantaneous phenomenon triggered by a strike from a highly energetic particle. The collision can result in data disruption or a complete device latch-up. SEEs are divided into soft errors and hard errors. Soft errors are non-destructive and disappear after a reboot, while hard errors are irreversible and result in system malfunction or, worse, loss of the entire circuit.

For radiation mitigation, the space sector traditionally relied on radiation-hardened by design circuits. Hardened chips are implemented in custom semiconductors In the past, the government and the military led the development of new semiconductor manufacturing processes, as they were the main customers of the semiconductor industry. Today, the semiconductor industry has shifted its focus to the consumer electronics market (cell phones, IoT, gaming...), thus radiation-hardened technologies used for space applications are often far from state-of-the-art. Moreover, radiation-hardened devices are expensive as they are required to undergo rigorous testing.

Traditional space players, such as NASA, ESA, and Roscomos, are committed to a high level of mission reliability and safety and therefore use high-value radiation-hardened products. While the "New Space" actors (startups and smaller companies) are more interested in the democratization of space with affordable satellites, they therefore creatively employ unconventional components, and design techniques to cut costs. Nowadays small satellites for LEO missions are designed by commercial-off-the-shelf (COTS) integrated circuits with plastic packaging rather than the hermetically sealed ceramic packaging preferred in spacecraft, to cut costs. Along with their low price, these components bring the benefits of ultra-submicron microelectronics (higher integration, faster processing, and lower power consumption) to the space industry. However, the use of COTS products significantly increases the risks of the mission. In brief, COTS sacrifices reliability for a low price, unlike radiation-hardened products that provide a high level of reliability for a considerable cost. Radiation-tolerant devices by reputation offer the best of both worlds. These devices are radiation tolerant by design and implemented in a qualified process such as silicon-on-insulator technologies. This eliminates some testing and selection costs. For example, SEE sensitivity testing does not need to be repeated on every batch because it is technology-dependent.

## 3. High-speed communications

The demand for high data rates continues to grow. This increase is driven by the rapid growth of streaming media over broadcast media, and gaming (especially in this covid pandemic), in addition to entertainment, other applications also require high-speed communications, such as telemedicine that can bring low-cost health care to remote areas. High-speed communication is carried out through two main channels: wireless and wireline connections. Wireless communication is primarily used for mobile telephony and broadband data communications like Wi-Fi. Wireline communication is provided by networks such as the local area network (LAN) and the wide-area network (WAN). Wired communication is primary data communication technology thanks to its ability to support high-speed communications.

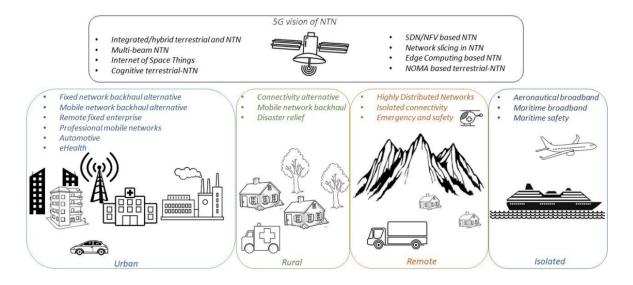

Wireline broadband communication is limited to certain areas because it requires an existing infrastructure. For extended coverage, wireless communication is the answer. With the standardization of 5th generation (5G) mobile technology a new term emerge called Non-Terrestrial Network (NTN), which refers to communication systems via satellites, unmanned aerial systems (UAV), and high altitude platforms (HAPs). The idea is to incorporate these systems into 5G as a complement to terrestrial systems to provide global coverage, even in isolated areas, with high data rates and low latency (see Figure 1-5).

There are two main ways to increase the communication data rate: 1) increasing the channel capacity, which is equivalent to widening the radio bandwidth, and 2) using advanced modulation and coding techniques. Moving to higher frequency provides wide bandwidth, thus operators are interested in shifting from the congested RF bands to millimeter waver bands such as Ka and V-band. However, high frequency faces some challenges related to the environment like rain fading and large transmission loss. On the other hand, modulation techniques increased the data rate such as Orthogonal Frequency Division Multiplexing

(OFDM) used in 4G, WI-FI, and now in 5G. The principle of OFDM is based on the division of data into several orthogonal subcarriers, transmitted in parallel. OFDM systems are sensitive to the phase noise of the local oscillator, so they require strict specifications from the transceiver, especially the oscillator, not only in terms of phase noise but also in terms of power consumption and reliability, a fortiori when it is intended for a space application.

Figure 1-5: The NTN in the 5G ecosystem [4].

### 4. Oscillators

Oscillators are autonomous systems that produce time information. For example, a pendulum, when displaced from its resting position, swings back and forth for a certain period of time. The motion of the pendulum results from the conversion of potential energy into kinetic energy and vice versa. However, the oscillation stops due to air resistance and hinge friction that converts some of the pendulum's energy into heat with each cycle. The oscillation will be sustained if we give the pendulum an impulse at each period to replenish the losses.

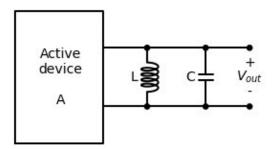

The LC oscillator is shown in Figure 1-6 works in the same way as the pendulum. A charged capacitor in an LC tank discharges into the inductor, converting electrical energy into magnetic energy. When the capacitor is empty, the inductor maintains the current flow in the circuit by charging the capacitor in the opposite direction. Thus, the magnetic energy is converted back into electrical energy. The exchange of energy in the LC tank produces a periodic signal. This signal, like the pendulum, dwindles with time until it stops due to the series resistance of the capacitor, the inductor, and the wires. To maintain the oscillation,

active device A is connected to the LC resonator to compensate for the energy lost due to the circuit imperfections.

Figure 1-6: LC oscillator model.

"Amplifiers oscillate, and oscillators amplify" this common saying among RF circuit designers implies that a poorly designed amplifier may turn into an oscillator and vice versa. In fact, in 1912, Armstrong noticed the appearance of parasitic high-frequency signals while experimenting with his regenerative circuit (positive feedback amplifier). It turned out that the amplifier was oscillating. Armstrong increased the feedback until the amplifier was unstable and thud he invented the first electronic oscillator.

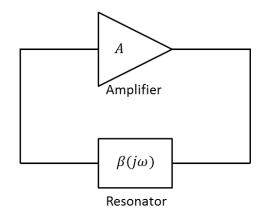

In 1921, Barkhasuen stated that for a positive feedback system, oscillation occurs when the loop gain has a phase shift of zero and a magnitude of unity. Figure 1-7 shows the feedback model of an oscillator. The amplifier A compensates for the resonator  $\beta(j\omega)$  losses at a given frequency  $\omega_0$ . The amplitude and phase conditions for a sustained oscillation, known as the Barkhausen criterion, are:

$$|A\beta(j\omega)| = 1 Eq 1.1$$

$$\arg A\beta(j\omega) = 0$$

Eq 1.2

The resonator provides a 360° phase shift at the resonance frequency  $\omega_0$ . The signal returns itself after a cycle around the loop provided that the loop gain is unity. In reality, the oscillation starts from noise. The noise is amplified with  $|A\beta(j\omega)| > 1$  and the resonator selects only the signal at the frequency  $\omega_0$  defined by Eq (1.2). The oscillation builds up exponentially at  $\omega_0$  until the amplifier's non-linearity saturation reduces the loop gain and limits the amplitude growth. At the steady-state, the loop reaches the sustained oscillation condition  $A\beta(\omega_0) = 1$ . Thus, the amplitude is defined by the circuit non-linear saturation and the oscillation frequency is obtained from Eq (1.2).

Figure 1-7: Oscillator feedback model.

#### 5. Phase noise

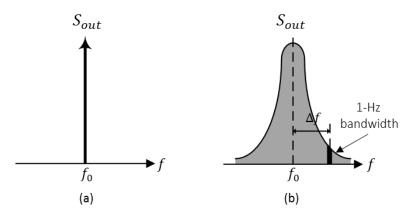

An ideal oscillator generates a sinusoidal signal with a single frequency component, as depicted in Figure 1-8.a. The zero-crossing of such signal occurs regularly at nT/2, where n is the n-th zero crossing. On the other hand, A real oscillator is prone to its intrinsic noise that causes fluctuations in amplitude and phase. Such a noisy signal is expressed as follows:

$$V(t) = V_0[1 + \alpha(t)] \cos(\omega_0 t + \phi(t)) \qquad \text{Eq 1.3}$$

where  $V_0$  is the amplitude,  $\omega_0$  is the oscillation frequency,  $\alpha(t)$  describes the amplitude fluctuation and  $\phi(t)$  denotes phase fluctuation. The saturation of the oscillator at steady-state suppresses amplitude noise, hence only the phase noise matters in oscillators. Phase perturbations cause the zero-crossing instant to drift randomly from its nominal value, this drift is referred to as jitter. The deviation of the zero-crossing of the signal results in a random change in the instantaneous frequency, consequently the signal energy is spread at the vicinity of the center frequency. The spectrum of the oscillator's output signal exhibits bandwidth broadening, as shown in Figure 1-8.b. Intuitively, the more one moves away from the center frequency of the signal, the more the signal strength fades, as the oscillator tends to hold the oscillation at the center frequency. This explains the skirted shape of the oscillator's spectrum.

The spectral purity of the oscillator is measured by the phase noise which is defined by IEEE standards as [5]:

$$\mathcal{L}(f) = \frac{S_{\phi}(f)}{2} \qquad \qquad \text{Eq 1.4}$$

where  $S_{\phi}(f)$  is the one-sided power spectral density of the random phase fluctuation  $\phi(t)$ . In practice,  $\mathcal{L}(f)$  is expressed as  $10 \log_{10}[\mathcal{L}(f)]$  and is given in dBc/Hz. This latter stands for dB below the carrier in a 1 Hz bandwidth.

Figure 1-8: Frequency response of (a) an ideal oscillator, (b) a real oscillator.

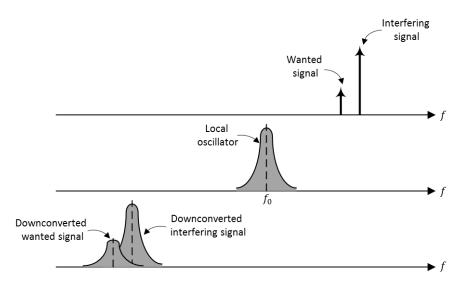

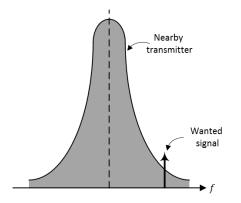

The oscillator phase noise is a major bottleneck in wireless communication systems. In a receiver, the shape of the local oscillator skirt converts the adjacent interfering signal with the wanted signal, as shown in Figure 1-9. This results in an overlap of the spectrum of the interfering signal with the signal of interest, which corrupts the detection. Thus, the communications system, due to phase noise, becomes very sensitive to neighboring interfering signals. In a transmitter, the strong output signal with the skirt spectrum hides the adjacent weak signal that needs to be detected, which again corrupts the detection (cf. Figure 1-10).

Figure 1-9: Effect of phase noise on a receiver.

Figure 1-10: Effect of phase noise on a transmitter.

Stringent requirements were placed on the oscillator phase noise to meet communication standards. In the North American Digital Cellular (NADC) IS-54 system, the phase noise must be -115 dBc/Hz at an offset of 60 kHz from the carrier. To design an oscillator with such low phase noise, designers must have a good understanding of phase noise mechanisms and patterns.

#### 5.1. Phase noise model

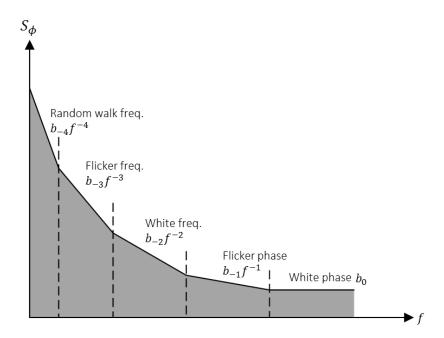

The spectrum of the phase noise of the oscillator is modeled by the power-law spectral densities. The experimentally observed random phase fluctuation can be represented as follows:

$$S_{\phi} = \sum_{i=-4}^{0} b_i f^i \qquad \qquad \text{Eq 1.5}$$

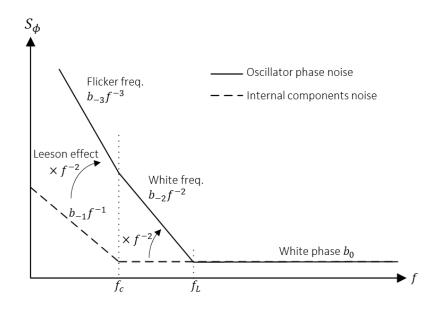

Figure 1-11 depicts the power-law spectrum. Distinct noise regions are observed and in each region, the power spectral density of the noise has a dependence on  $1/f^n$ , where *n* is between 0 and 4. Sometimes higher slope regions add to the power-law spectra such as  $1/f^5$  noise observed experimentally in some oscillators. In practice, not all oscillators display all the regions, one or more regions disappear because the cross-over frequency (frequency at which the power density changes the slope) is out of order.

Each region is named [5] as follows: the first is called white noise,  $f^0$ , the second is flicker noise,  $f^{-1}$ , then white frequency,  $f^{-2}$ , followed by the flicker frequency,  $f^{-3}$ , and random walk frequency,  $f^{-4}$ . Oscillators incorporate all of these noise processes, whereas two-port devices have only the white and flicker noise.

Figure 1-11: Power-law spectrum.

#### 5.1.1. Leeson model

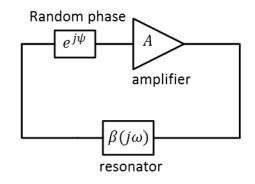

The power law describes the shape of the oscillator's phase noise spectrum but does not give any insight into the physical process behind such noise characteristics. In 1966, Leeson proposed a heuristic model that describes the generation of phase noise in oscillators [6]. Leeson builds his model (cf. Figure 1-12) on 4 assumptions: 1) the amplifier is assumed noiseless; 2) the resonator acts as a bandpass filter and selects the oscillating frequency; 3) the noise source  $\psi$  englobes all noise sources in the oscillator; 4) the amplifier noise is quenched by amplifier saturation, thus only phase noise remains [7].

Figure 1-12: Oscillator model with the phase noise of the amplifier and all other components modeled as random phase  $\psi$ .

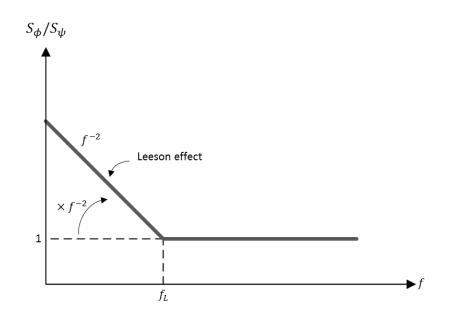

Under these assumptions, the oscillator is considered a first-order filter with a perfect integrator and a cutoff frequency  $f_L$  called Leeson frequency (cf. Figure 1-13) [8]:

$$S_{\phi} = \left(1 + \frac{f_L^2}{f^2}\right) S_{\psi} \qquad \qquad \text{Eq 1.6}$$

where  $S_{\psi}$  is the power spectral density of the amplifier noise,  $f_L = f_0 / 2Q_T$ ,  $f_0$  is the center frequency,  $Q_T$  is the loaded quality factor. The phase noise from the internal components of the oscillator is multiplied by  $1/f^2$  to appear as frequency noise in the oscillator, as shown in Figure 1-13. This mechanism is known as the Leeson effect. The oscillator flicker noise is upconverted to flicker frequency noise  $f^{-3}$  and the white noise becomes white frequency noise  $f^{-2}$  in the passband of the oscillator (cf. Figure 1-14).

Figure 1-13: The Lesson effect phase transfer function  $S_{\phi}/S_{\psi}$ .

The mathematical expression of the Lesson model is [6]:

$$\mathcal{L}(\Delta f) = \frac{2Fk_b T}{P_{RF}} \left( 1 + \left(\frac{f_0}{2Q_T \Delta f}\right)^2 \right)$$

Eq 1.7

where *F* is an empirical parameter (called device excess noise number),  $k_b$  is Boltzmann's constant, *T* is the absolute temperature,  $P_{RF}$  is the power of the oscillating signal, and  $\Delta f$  is the offset frequency from the carrier. The equation gives the phase noise as the ratio of thermal noise power to signal power, multiplied by the resonator bandwidth correction factor  $\left(1 + \left(\frac{f_0}{2Q\Delta f}\right)^2\right)$ . To account for the generation of  $f^{-1}$  and  $f^{-3}$  noise, another term was added to the original equation:

$$\mathcal{L}(\Delta f) = \frac{2Fk_b T}{P_{RF}} \left(1 + \left(\frac{f_0}{2Q\Delta f}\right)^2\right) \left(1 + \frac{f_c}{\Delta f}\right)$$

Eq 1.8

where  $f_c$  is the corner frequency between  $f^{-2}$  and  $f^{-3}$  noise region.

Figure 1-14: Conversion of device noise to oscillator's phase noise.

Leeson's model, although simple to follow, has serious limitations. The factor F accounts for the discrepancy between the noise level predicted by Eq (1.8) and the measured one. This empirical parameter cannot be determined a priori. Moreover, the measurements showed that  $f_c$  is unequal to 1/f noise corner as asserted by the model. Thus,  $f_c$  is also an empirical fitting parameter.

#### 5.1.2. Hajimiri and Lee model

The noise undergoes multiple frequency transformations to appear as phase noise in oscillators. Leeson's linear time-invariant model explains the up-conversion of near DC noise to phase noise, but it does not address the down-conversion of noise around harmonics frequencies to close-in phase noise. Hajimiri and Lee [9] abandon the time-invariant model for a linear time-variant model to include these high-order conversion mechanisms.

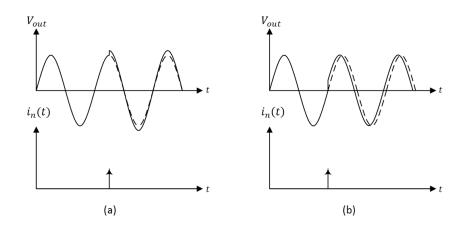

In Hajimiri and Lee's theory, phase noise generation is determined by the instant at which the noise impulse is injected into the circuit. The noise injected at the peak of the oscillating signal produces amplitude modulation with no effect on phase, as depicted in Figure 1-15.a. In contrast, noise injected at the zero-crossing of the signal causes phase noise with no effect on amplitude, as shown in Figure 1-15.b. If noise is injected between these two instances, it causes both amplitude and phase noise. This sensitivity of phase noise to the time of noise injection is quantified by a function called Impulse Sensitivity Function (ISF). The ISF function has its maximum at the zero-crossing of the oscillator signal and its minimum at the peak of the signal. Figure 1-16 shows the ISF of a harmonic oscillator. The oscillator phase response to a noise impulse is [9]:

$$h_{\phi}(t,\tau) = \frac{\Gamma(\omega_0 t)}{q_{max}} u(t-\tau)$$

Eq 1.9

where  $\Gamma$  is the impulsive sensitivity function,  $q_{max} = CV_0$  is the maximum displacement across the tank capacitor, C is the tank capacitance,  $V_0$  is the amplitude of the oscillation signal, t is the observation time and  $\tau$  is the time of the excitation.

*Figure 1-15: (a) Effect of impulse injection at peak of the waveform, (b) effect of impulse injection at zero crossing of waveform.*

The random phase fluctuation, added into the carrier's phase, is obtained by convolving the current noise source and the ISF as:

$$\phi(t) = \frac{1}{q_{max}} \int_{-\infty}^{t} \Gamma(\omega_0 t) i(\tau) d\tau \qquad \text{Eq 1.10}$$

where  $i(\tau)$  is the noise current injected in the oscillator. The ISF is a periodic function, hence it can be expressed as a Fourier series. Thus, Eq (1.10) becomes:

$$\phi(t) = \frac{1}{q_{max}} \left[ c_0 \int_{-\infty}^t i(\tau) d\tau + \sum_{n=1}^{\infty} c_n \int_{-\infty}^t i(\tau) cous(n\omega_0 \tau) d\tau \right]$$

Eq 1.11

Figure 1-16: ISF waveform of an oscillator with a sinusoidal output.

where  $c_n$  are coefficients of the Fourier series. The first term with  $c_0$  coefficient designates noise that is up-converted from the baseband, while the second term represents the contribution of noise near harmonic frequencies down-converted to the oscillator phase noise. The phase noise spectral density at an offset frequency  $\Delta \omega$  from the carrier can be expressed as [9]:

$$\mathcal{L}(\Delta\omega) = 10.\log\left(\frac{\Gamma_{rms}^2}{C^2 V_0^2} \cdot \frac{\overline{\iota_n^2} / \Delta f}{2\Delta\omega^2}\right)$$

Eq 1.12

where  $\overline{\iota_n^2}$  is the power spectral density of the white noise current and  $\Gamma_{rms}$  is the effective impulsive sensitivity function. The LC-tank losses are represented by  $R_p = Q_T / (\omega_0 C)$ . The general phase noise expression becomes:

$$\mathcal{L}(\Delta\omega) = 10.\log\left[\frac{\overline{l_n^2}/\Delta f}{P_{RF}}R_p \cdot \Gamma_{rms}^2 \cdot \left(\frac{\omega_0}{2Q_T\Delta\omega}\right)^2\right]$$

Eq 1.13

where  $P_{RF} = V_0^2 / (2R_p)$  is the signal power. The upconversion of flicker noise to  $1/f^3$  phase noise is expressed as:

$$\mathcal{L}(\Delta\omega) = 10.\log\left(\frac{\frac{\overline{l_n^2}}{\Delta f}c_0^2}{8q_{max}^2\Delta\omega^2}\cdot\frac{\omega_{1/f}}{\Delta\omega}\right)$$

Eq 1.14

where  $\omega_{1/f}$  is the 1/f corner frequency.

#### 5.2. Phase noise trade-offs

Analog circuit design is about choosing the right trade-off between circuit parameters across different topologies, oscillators are no exceptions. This section presents the different parameters that trade-off with the oscillator phase noise.

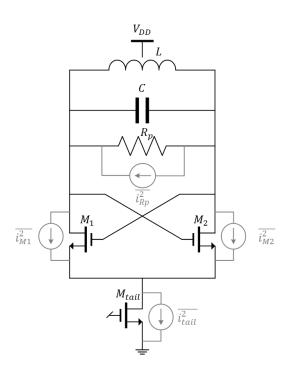

#### 5.2.1. Noise Sources

The spectral purity of the oscillator output waveform depends on the intrinsic noise generated within the oscillator. Generally, in a conventional LC oscillator, there are three main contributors to phase noise, as shown in Figure 1-17, which are the cross-coupled switching transistors M1 and M2, the tail current source, and the thermal noise associated with the loss in the LC resonator.

Figure 1-17: Noise sources in a cross-coupled LC oscillator.

#### Resonator noise

The energy loss in the LC tank, represented by the parallel resistance Rp, induces a thermal noise current, with a power density  $\overline{\iota_{Rp}^2}$ :

$$\overline{\iota_{Rp}^2} = 4k_B T \frac{1}{R_p} \Delta f \qquad \text{Eq 1.15}$$

For a differential harmonic oscillator with a sinusoidal output, the ISF of the resonator noise is a sinusoid in quadrature with the tank voltage giving  $\Gamma_{rms}^2 = 1/8$  [10]. The phase noise generated by the thermal noise from Rp according to Eq (1.12) is:

$$\mathcal{L}(\Delta\omega) = 10.\log\left(\frac{k_B T}{4V_0^2 C^2 R_p \Delta\omega^2}\right) = 10.\log\left[\frac{k_B T}{4V_0^2} \cdot R_p \cdot \left(\frac{\omega_0}{Q_T \Delta\omega}\right)^2\right] \qquad \text{Eq 1.16}$$

The resonator's thermal noise contribution can be reduced by using passive elements with a high-quality factor Q. However, the maximum achievable  $Q_T$  is mainly determined by the characteristics of the technology and can only be slightly improved through design or layout techniques.

#### Tail current noise

The noise at the tail transistor is translated up and down in frequency due to the switching of the commutations transistors. These transistors act as a self-balanced mixer that upconverts tail noise at  $\Delta\omega$  to  $\omega_0 \pm \Delta\omega$  and downconverts noise at  $2\omega_0 \pm \Delta\omega$  to  $\omega_0 \pm \Delta\omega$ . From these two transformations, only the downconverted noise at  $2\omega_0 \pm \Delta\omega$  causes phase fluctuation the other causes just amplitude fluctuation [11]. The phase noise from the tail current is expressed as:

$$\mathcal{L}(\Delta\omega) = 10.\log\left[\frac{2k_BT}{V_0^2 C^2 \Delta\omega^2} \cdot \Gamma_{\text{tail,rms}}^2 \cdot \gamma \cdot g_{m,tail}\right]$$

Eq 1.17

where  $\gamma$  is the noise factor of a transistor and  $g_{m,tail}$  is the transconductance of the tail transistor. The tail current provides a high impedance path when the transistor enters the triode region which prevents them from loading the tank. However, the overdrive voltage of the current tail transistor limits the oscillation output voltage which impacts the phase noise.

#### Differential pair noise

The active device in the oscillator compensates for the losses in the LC tank by transferring the DC power supply to the resonator via periodical current pulses. In the process, the active device injects noise into the tank. This noise contribution inherits the periodicity of the active device, yielding a cyclostationarity noise. The expression of the effective ISF incorporates this cyclostationarity behavior [9]:

$$\Gamma_{eff}(\omega t) = \Gamma(\omega t) \,\alpha(\omega t)$$

Eq 1.18

where  $\alpha$  is the Noise Modulating Function (NMF) that represents the modulation of noise (cyclostationarity). The expression for the phase noise generated by the switches is:

$$\mathcal{L}(\Delta\omega) = 10.\log\left[\frac{2k_BT}{V_0^2 C^2 \Delta\omega^2} \cdot \Gamma_{\text{eff,rms}}^2 \cdot \gamma \cdot \frac{g_m}{\lambda}\right] \qquad \text{Eq 1.19}$$

where  $\gamma$  is the noise factor of the transistor and  $\lambda$  is the voltage gain between the tank and the switching transistors. The differential pair phase noise can be improved by increasing the gain  $\lambda$  or by reducing the effective ISF  $\Gamma_{eff}$ . This latter is reduced if the switching transistors turn on only during the short period where the oscillator is less sensitive to phase noise as indicated by the ISF. Thus, less noise will be converted to phase noise.

#### 5.2.2. Power consumption

Consider the cross-coupled oscillator shown in Figure 1.18.a. The tail transistor  $M_{tail}$  sets the bias current  $I_{bias}$ . The transistors  $M_1$  and  $M_2$  compensate for the tank losses by injecting current into the tank. The resonator with reasonable quality factor Q filters all the current harmonics except the fundamental  $I_1$ . At the resonance frequency, the oscillator impedance is  $R_p$  since the L and C compensate for each other, thus the oscillator amplitude at  $\omega_0$  can be expressed by:

$$V_0 = \beta I_{bias} R_p \qquad \qquad \text{Eq 1.20}$$

where

$$I_1 = \beta I_{bias} \qquad \qquad \text{Eq 1.21}$$

and  $\beta$  is the current efficiency.

The amplitude affects the phase noise as emphasized in Eq (1.12). The phase noise is reduced by a slope of -20 dB/dec with an increase in  $V_0$ . On the other hand,  $V_0$  is linearly related to the bias current  $I_{bias}$ , as shown in Eq (1.20). Hence, an increase in the oscillator power consumption will improve the phase noise.

The reduction in phase noise is not indefinitely proportional to the power consumption. The linear growth of amplitude with bias current in equation (1.20) is valid only when the transistors are in saturation. For larger amplitude, the transistors are pushed into the triode region, which limits the value of the amplitude. Hence, LC oscillators exhibit two modes of operation, namely the current-limited region (M1 and M2 operate in saturation) and the voltage-limited region (M1 and M2 enter in the triode region), as shown in Figure 1-18.b. In the voltage-limited region, when the transistors enter the triode region, the parasitic tail capacitance  $C_{tail}$  adds its low-quality factor to the tank reducing the overall quality factor  $Q_T$ , as result the output phase noise increases. Therefore, for optimum phase noise, the oscillator

amplitude should be at the boundary between the current-limited and the voltage-limited regions.

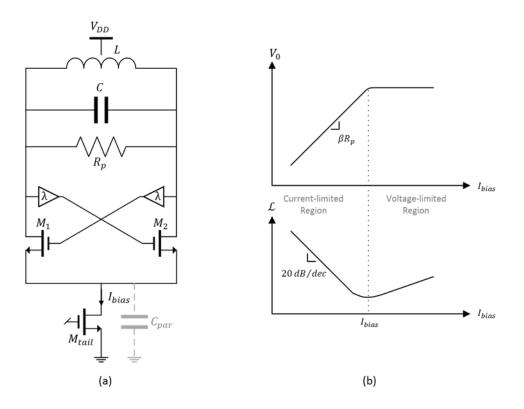

*Figure 1-18: (a) Cross-coupled oscillator topology, (b) amplitude and phase noise of the oscillator in current-limited and voltage-limited regions.*

In the current-limited region, the phase noise trades off with power consumption. This trade-off is evaluated in the oscillator by a Figure of Merit (FoM) defined as:

$$FoM = -\mathcal{L}(\Delta\omega) + 20\log_{10}\left(\frac{\omega_0}{\Delta\omega}\right) - 10\log_{10}P_{DC,mW}$$

Eq 1.22

Replacing Eq (1.13) in Eq (1.22), FoM becomes:

$$FoM = 10 \log_{10} \left[ \frac{2 \cdot Q_T^2 \cdot \eta_p}{R_p \sum \overline{\iota_n^2} / \Delta f \cdot \Gamma_{n,rms}^2} \right]$$

Eq 1.23

where  $\eta_p$  is the power efficiency defined as:

$$\eta_p = \frac{P_{RF}}{P_{DC}} = \frac{I_{RF}}{I_{DC}} \frac{V_{RF}}{V_{DC}} = \eta_I \eta_V$$

Eq 1.24

where  $P_{DC}$  is the DC power,  $P_{RF}$  is the RF power,  $I_{RF}$  and  $V_{RF}$  are the rms values of the fundamental components of current and voltage in the oscillator,  $V_{DC}$  and  $I_{DC}$  are the supply voltage and current. According to Eq (1.23) *FoM* is improved in three ways:

• Maximizing the tank quality factor  $Q_T$ , 6 dB of improvement for every doubling of it,

- Increasing the power transfer efficiency η<sub>p</sub> from DC-to-RF, 3dB for every doubling of it,

- Reducing the oscillator ISF.

#### 5.2.3. Frequency Tuning

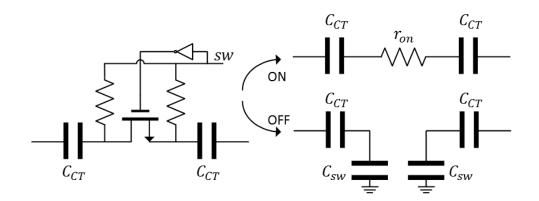

Conventionally, a wide Frequency Tuning Range (FTR) in the oscillator is achieved by combining switching capacitors for coarse tuning and varactors for fine-tuning. The former covers the tuning range with discrete points by connecting/disconnecting fixed capacitors through a switching transistor, as shown in Figure 1-19. The varactors for fine-tuning connect the discrete points to provide continuous tuning on the FTR.

Figure 1-19: Switch capacitor model in ON and OFF state.

The minimum oscillation frequency is reached when all switches in the capacitor bank are turned on. The parasitic capacitance  $C_{p,AD}$  from the active device is also added up to the capacitor-bank capacitance  $C_{CT}$  and reduces the oscillation frequency.

$$f_{min} = \frac{1}{2\pi} \frac{1}{\sqrt{L(C_{CT} + C_{p,AD})}}$$

Eq 1.25

The switch capacitor quality factor  $Q_c$  is determined by the on-resistance  $r_{on}$  of the transistors:

$$Q_c = \frac{1}{\omega_0 C r_{on}}$$

Eq 1.26

where  $r_{on}$  can be expressed as:

$$r_{on} = \frac{1}{\mu_n C_{ox} \left(\frac{W}{L}\right) \left(V_{gs} - V_{th}\right)} = \frac{r_{on,\mu m}}{W}$$

Eq 1.27

with

$$r_{on,\mu m} = \frac{L}{\mu_n C_{ox} (V_{gs} - V_{th})}$$

Eq 1.28

where,  $\mu_n$  is the mobility of the carrier,  $C_{ox}$  is the oxide capacitance, W is the width of the transistor, L is the length of the transistor,  $V_{gs}$  is the gate to source voltage, and  $V_{th}$  is the threshold voltage. Replacing Eq (1.27) in Eq (1.26) the capacitor quality factor becomes:

$$Q_c = \frac{W}{\omega_0 C r_{on,\mu m}}$$

Eq 1.29

The quality factor of the resonator is a parallel combination of the inductor quality factor  $Q_L$  and the capacitor-bank quality factor  $Q_c$ :

$$Q_T = \frac{Q_L Q_C}{Q_L + Q_C}$$

Eq 1.30

On the other hand, the maximum oscillation frequency is reached when all the switches of the capacitor bank are turned off. The tank capacitance, in this case, is composed of the active device's parasitic capacitance  $C_{p,AD}$  and the off-state capacitance  $C_{off}$  of the capacitor bank.

$$f_{max} = \frac{1}{2\pi} \frac{1}{\sqrt{L(C_{off} + C_{p,AD})}}$$

Eq 1.31

where

$$C_{off} = \frac{C_{CT} \cdot C_{sw}}{2C_{CT} + C_{sw}}$$

Eq 1.32

The on-resistance of the transistors in the capacitor-bank lowers the quality factor of the tank  $Q_T$ , thus degrading the phase noise. This effect is mitigated using large transistors as implied by Eq (1.29). In contrast, the parasitic capacitance of the transistor increases with its sized  $C_{sw} \propto W$ , thus reducing the maximum oscillation frequency as pointed out by Eq (1.31) and Eq (1.32). Consequently, the frequency tuning range trades off with the phase noise, i.e. capacitor bank quality factor  $Q_c$ .

Varactors also degrade the phase noise because they introduce AM-to-FM noise [12]. At millimeter frequencies, the quality factor of varactors is so low that it becomes the dominant quality factor compared to the inductor. Therefore, it is preferable to reduce the varactor capacitance and compensate for it with the switching capacitors.

The above discussion elucidates the trade-off between the oscillator phase noise and frequency tuning. This trade-off is evaluated in the oscillator by a tuning range-based figure of merit  $FoM_T$ , which is defined as:

$$FoM_{T} = -\mathcal{L}(\Delta\omega) + 20\log_{10}\left(\frac{\omega_{0}}{\Delta\omega}\right) + 20\log_{10}\left[\frac{FTR(\%)}{10}\right] - 10\log_{10}P_{DC,mW} \quad \text{Eq 1.33}$$

# 6. Oscillator topologies

The previous section presented the trade-offs between the oscillator parameters. These trade-offs are set by the oscillator topology. Thus, it is interesting to compare different oscillator topologies to determine the one with the better performance balance. The following subsections describe the common oscillator architectures. These oscillators are classified as power amplifiers.

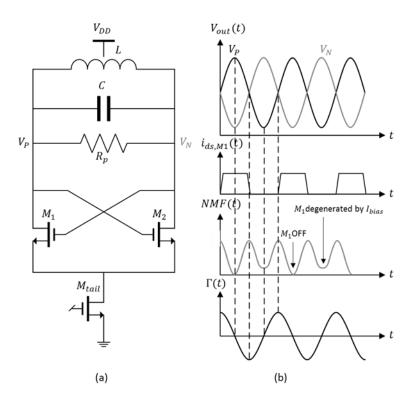

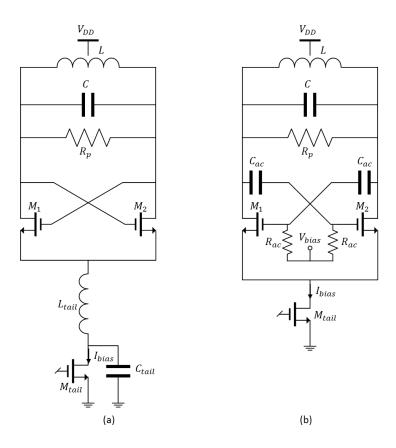

#### 6.1. Class-B

The class-B LC-tank oscillator (cf. Figure 1-20.a) is the most common implementation of harmonic oscillators due to its simplicity, relaxed start-up, and relatively good phase noise. The differential pair, composed of  $M_1$  and  $M_2$ , creates a negative resistance that compensates for the resonator losses modeled as  $R_p$ . The tail transistor  $M_{tail}$  sets the bias current of the oscillator  $I_{bias}$ . The latter flows through each switching transistor for a half period, producing a square wave current at their drain, as shown in Figure 1-20.b. The oscillation amplitude, as stated by Eq (1.20), is the product of the fundamental harmonic current  $I_1$  and the resonator impedance at the oscillation frequency  $R_p$ :

$$A_{class-B} = I_1 R_p = \frac{2}{\pi} I_{bias} R_p$$

Eq 1.34

The tail transistor operates in the saturated region presenting ideally a high impedance to the sources of  $M_1$  and  $M_2$ . This high impedance prevents the switching transistor from injecting noise and loading the tank when they enter the triode region near the amplitude peak. However, at the current transition,  $M_1$  and  $M_2$  work differentially presenting a virtual ground (low impedance) to their common source. Thus, the active device injects noise only at this moment, which unfortunately coincides with the ISF extremum, as depicted in Figure 1.20.b.

Moreover, the parasitic capacitor  $C_{par}$  of  $M_{tail}$  presents an RF path to the ground, distorting the current, and degrading the resonator quality factor when the transistors enter the triode region [13]. The oscillator current efficiency  $\eta_I$  is limited at  $\sqrt{2/\pi}$  to the square shape of the current and is even lower when the switching transistors enter the triode region. The voltage drop  $V_{ds,tail}$  that keeps  $M_{tail}$  in saturation, reduces the voltage efficiency  $\eta_V$ . Increasing the width of  $M_{tail}$  improves  $\eta_I$  but also increases the transistor's transconductance, and consequently its noise injection into the tank Eq (1.17). Those effects degrade the theoretical ideal phase noise performance of the cross-coupled oscillator in a real implementation [13].

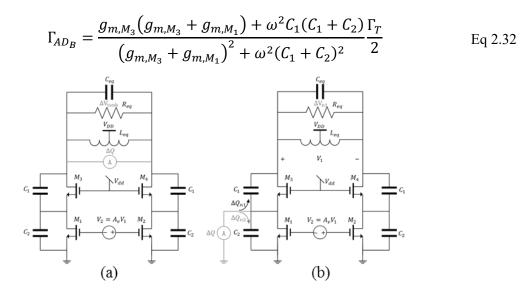

Figure 1-20: (a) Class-B oscillator topology, (b) differential output voltages, drain current of  $M_1$ ,  $i_{ds,M1}$ , noise modulating function (NMF) of  $M_1$  and ISF of  $M_1$ ,  $\Gamma$ .